## Copyright © 2004, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# ADVANCED MATERIALS AND STRUCTURES FOR NANOSCALE CMOS DEVICES

by

Dae-Won Ha

Memorandum No. UCB/ERL M04/46

6 December 2004

# ADVANCED MATERIALS AND STRUCTURES FOR NANOSCALE CMOS DEVICES

by

Dae-Won Ha

Memorandum No. UCB/ERL M04/46

6 December 2004

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### Advanced Materials and Structures for Nanoscale CMOS Devices

by

#### Dae-Won Ha

B.S. (Yonsei University, Korea) 1993M.S. (Yonsei University, Korea) 1995

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Chenming Calvin Hu, Chair Professor Tsu-Jae King Professor Eicke R. Weber

Fall 2004

#### The dissertation of Dae-Won Ha is approved:

Chair Nov. 16, 2004

Date

Nov. 24, 2004

Date

Chile Woler Wor. 30, 2004

University of California, Berkeley

Fall 2004

## Advanced Materials and Structures for Nanoscale CMOS Devices

Copyright 2004

by

Dae-Won Ha

#### **Abstract**

### **Advanced Materials and Structures for Nanoscale CMOS Devices**

by

#### Dae-Won Ha

Doctor of Philosophy in Engineering –

Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Chenming Calvin Hu, Chair

Technological innovations have accomplished the continued scaling of CMOS devices well into nanometer regime. Short channel effects have been suppressed by the use of thinner gate oxide, shallower junction depth, and sophisticated channel doping profile without changing its basic structure. However, further CMOS scaling will be much more intricate due to fundamental materials and process limitations. The advanced thin-body transistor structures can effectively suppress the short channel effects, separating the need of heavy channel doping and the state-of-the-art thin gate oxide. This dissertation investigates the integration of advanced materials in front-end processes with advanced thin-body transistor structures.

Two essential processes in molybdenum (Mo) metal gate technology are developed: damage-free sputtering and high-selectivity dry etching. The physical origin of Mo gate work function engineering is simultaneous modification of the microstructure and chemistry at the gate dielectric interface, as discussed in chapter 2.

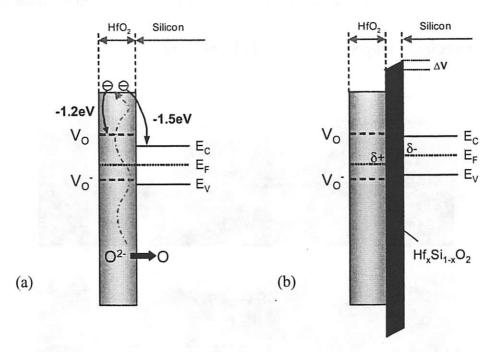

The impact of gate process technology on hafnium oxide (HfO<sub>2</sub>) gate dielectric is explored. The increase in equivalent oxide thickness and leakage current is resulted from the generation of oxygen vacancy, which causes silicon interfacial layer formation and gate electrode Fermi-level pinning in MOS devices, as discussed in chapter 3.

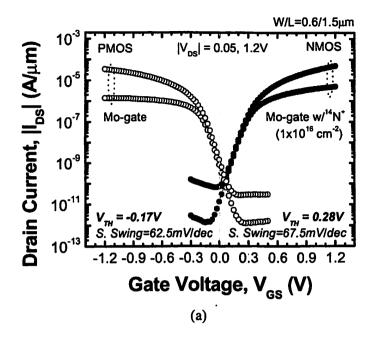

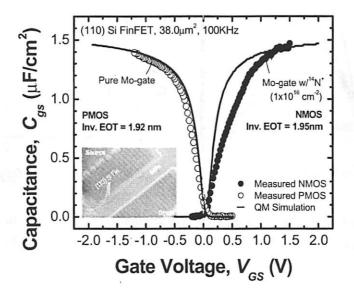

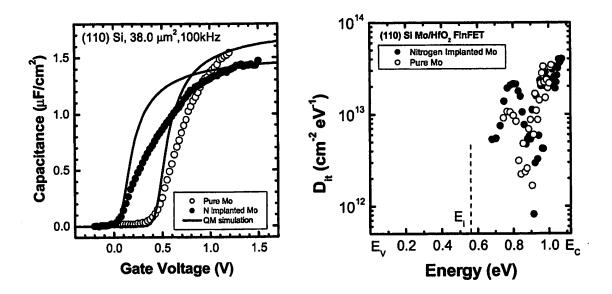

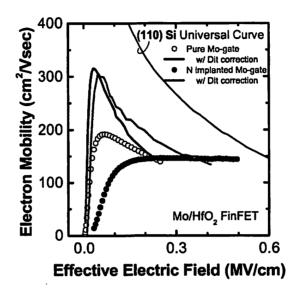

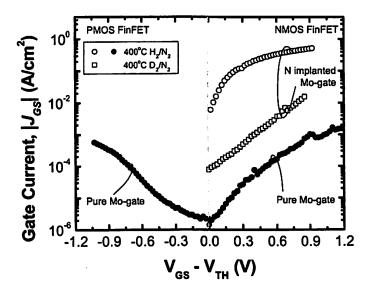

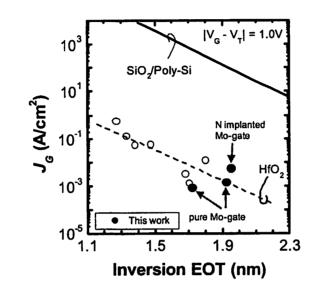

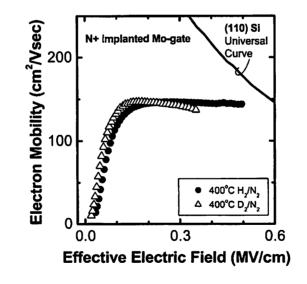

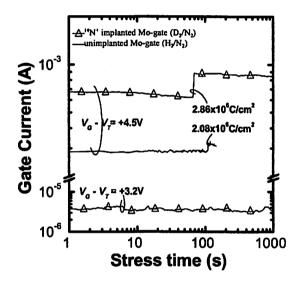

Tunable work function Mo gate is demonstrated for adjusting threshold voltages of ultra-thin body MOSFETs for the first time. Integration of metal gate and high-k gate dielectric employing FinFETs is demonstrated for the first time; Mo-gated HfO<sub>2</sub> CMOS FinFETs reduce gate leakage current over 3 orders-of-magnitude for inversion equivalent oxide thickness (1.72 nm) with comparable carrier mobility, as discussed in chapter 4.

Professor Chenming Calvin Hu

7 Hu Nov. 16, 2004

Dissertation Committee Chair

To my parents, for their unforgettable love and sacrifices

To my wife, for her everlasting love, support and encouragements

To my son, for his brilliant and ambitious future

### **Table of Contents**

| Ac | knowledgements                                                | iv |

|----|---------------------------------------------------------------|----|

| 1. | Introduction                                                  | 1  |

|    | 1.1 Future of CMOSFETs                                        | 1  |

|    | 1.2 Objectives                                                | 5  |

|    | 1.3 References                                                | 7  |

| 2. | Metal Gate Technology                                         | 9  |

|    | 2.1 Introduction                                              | 9  |

|    | 2.2 Material Selection for Gate Electrode                     | 14 |

|    | 2.3 Damage-free Molybdenum Sputtering                         | 19 |

|    | 2.3.1 Sputtering System for Molybdenum                        | 19 |

|    | 2.3.2 Experimental Results and Discussion                     | 22 |

|    | 2.4 Highly Selective Molybdenum Dry Etching                   | 26 |

|    | 2.4.1 Dry Etching System for Molybdenum                       | 26 |

|    | 2.4.2 Experimental Results and Discussion                     | 27 |

|    | 2.5 Tunable-Work-Function Molybdenum Process                  | 34 |

|    | 2.5.1 Experimental Results and Discussion                     | 35 |

|    | 2.6 Summary                                                   | 46 |

|    | 2.7 References                                                | 47 |

| 3. | High-k Gate Dielectric Technology                             | 53 |

|    | 3.1 Introduction                                              | 53 |

|    | 3.2 Material Selection for Gate Dielectric                    | 56 |

|    | 3.3 HfO <sub>2</sub> Gate Dielectric                          | 61 |

|    | 3.3.1 Fabrication of HfO <sub>2</sub> MOS Capacitors          | 62 |

|    | 3.3.2 Experimental Results and Discussion                     | 64 |

|    | 3.3.3 Considerations for Alternative Gate Electrode Materials | 75 |

|    | 3.4 Summary                                                   | 77 |

|    | 3.5 References                                                | 77 |

| 4. | Advanced Transistor Structures                                | 84 |

|    | 4.1 Introduction                                              | 84 |

|    | 4.2 Design         | Methodology and Challenges for Advanced Transistor Structures           | 90  |

|----|--------------------|-------------------------------------------------------------------------|-----|

|    | 4.3 Tunabl         | e Work Function Mo-Gated SiO <sub>2</sub> UTB MOSFET                    | 98  |

|    |                    | Fabrication of Mo-gated SiO <sub>2</sub> p-channel UTB MOSFETs          |     |

|    |                    | Results and Discussion of Mo-gated SiO <sub>2</sub> p-channel UTB MOSFE |     |

|    | 4.4 Tunab          | e Work Function Mo-Gated HfO <sub>2</sub> CMOS FinFETs                  | 108 |

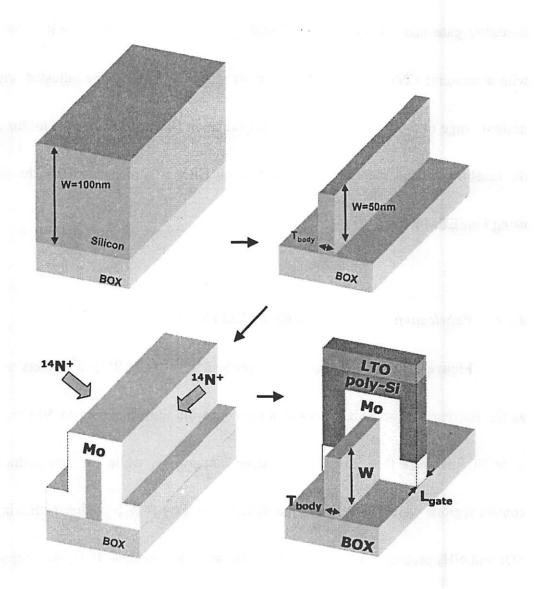

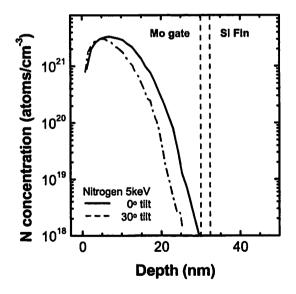

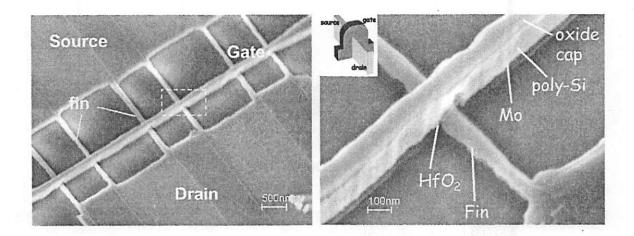

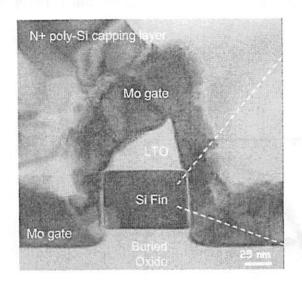

|    | 4.4.1              | Fabrication of Mo-gated HfO2 CMOS FinFETs                               | 109 |

|    |                    | Results and Discussion of Mo-gated HfO2 CMOS FinFETs                    |     |

|    |                    | ary                                                                     |     |

|    |                    | nces                                                                    |     |

| 5. | Conclusion         |                                                                         | 134 |

|    |                    | ary of Contributions                                                    |     |

|    |                    | Metal Gate Technology                                                   |     |

|    |                    | High-k Gate Dielectric Technology                                       |     |

|    |                    | Advanced Transistor Structures                                          |     |

|    |                    | stions for Future Work                                                  |     |

|    |                    | Mobility Enhancement for Advanced Transistor Structures                 |     |

|    |                    | Reliability of Advanced Materials and Transistor Structures             |     |

|    |                    | nces                                                                    |     |

| An | nendix A <i>Fa</i> | abrication Processes for Mo-gated UTB MOSFETs                           | 14: |

| _  | -                  | phrication Processes for Mo-gated HfO2 FinFETs                          |     |

### **Acknowledgements**

First of all, I would like to express my sincere gratitude to many people who have contributed to this work and supported my study at the University of California at Berkeley. It has been my honor and fortune to have had Professor Chenming Calvin Hu as my research advisor during my graduate career. His enthusiasm, inspiration, and excellent knowledge have guided me through all the challenges in my work. He deserves my special thanks for the teleconferences during his industrial leave to TSMC in Taiwan. I wish to express my deepest appreciation to Professor Tsu-Jae King for serving as my research co-advisor and chairing my qualifying examination. Her insightful advices and helpful encouragements have been always beneficial to my research and personal life.

I would like to thank Professor Eicke R. Weber for the insightful feedbacks on my works, who has served in both my qualifying examination and dissertation committees. I am grateful to Professor Borivoje Nikolic who has served in my qualifying examination committee. I am greatly indebted to Dr. Kinam Kim who has mentored and encouraged my research projects throughout my study.

I am very grateful to many former and current members of the device group in 373 Cory Hall. I would particularly like to thank Dr. Yang-Kyu Choi for his guidance and helpful discussions on various aspects of my research and fabrication processes. I especially thank Hideki Takeuchi for his technical supports in the Microlab. I have enjoyed many stimulating discussions and joyful moments with Nick Lindert, Stephen Tang, Qing Ji, Charles Kuo, Kevin Yang, Kevin Cao, Xuejue Huang, Qiang Lu, Jakub Kedzierski, Mark Cao, Pin Su, Pushkar Ranade, Yee-Chia Yeo, Igor Polishchuk, Patrick Xuan, Min She, Leland Chang, Jeong-Soo Lee, Jane Xi, Kenichi Goto, Koji Watanabe, Atsushi Yagishita, Kozo Watanabe, Renichi Yamada, Shiying Xiong, Hui Wan, Gang Liu, Sriram Balasubramanian, Mohan Dunga, Kyoung-Sub Shin, Hiu-Yung Wong, Vidya Varadarajan, Marie-Ange Eyoum, Yu-Chih Tseng, Chung-Hsun Lin, Blake Lin, Alvaro Padilla, Donovan Lee, Pankaj Kalra, Andrew Carlson, Hei Kam, and Kinyip Phoa.

I am very grateful to Judy Fong and Linda Manly for their efficient support in administrative matters, and Ruth Gjerde for her fabulous advices in graduate matters.

Above all, I would like to express my utmost gratitude to my parents for their continued love, understanding, and encouragement throughout my life. I am also very grateful to my son, Jee-Hoon, for his timeless honest smile. He is indeed my motivation

to endure all the hardship. I am indebted to my sister, Min-Jeong, for her love and

support. I would humbly like to thank my parents-in-law for their love, support and

encouragement. I also thank my sisters-in-law for their love and encouragement.

I would like to express my deepest gratitude to my wife, Yeon-Jeong Yoo, for

her everlasting love, immense sacrifices, tremendous understanding, and encouragement.

Dae-Won Ha

November 2004,

Berkeley, California

vi

## **Chapter 1**

## Introduction

### 1.1 Future of CMOSFETs

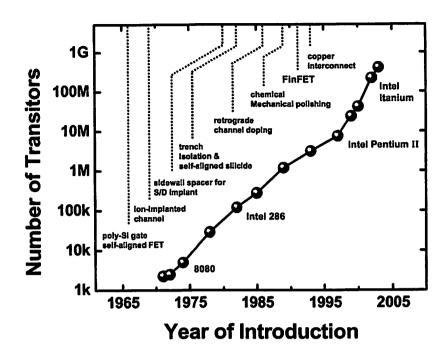

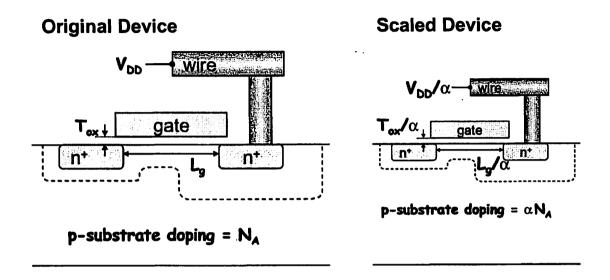

Remarkable progress in semiconductor industry has led to the proliferation of microelectronic devices and information technology. The predominant technology is based on silicon CMOSFETs, the basic building blocks of integrated circuits. Over the past three decades, rapid and steady improvements in circuit performance and packing density have been achieved through the scaling of CMOS devices. The CMOS scaling has been accomplished with technological innovations, and leads the device dimensions well into the nanometer regime, as illustrated in Figure 1.1 [1.1, 1.2].

Figure 1.1 Remarkable progress in integration of transistors into a central processing unit (CPU). Technological innovations have accomplished the continued scaling of silicon-based CMOS devices, and shrunk them into the nanometer regime [1.1, 1.2].

However, new technological barriers should be overcome for future nanoscale CMOS scaling, because some fundamental materials and process limits are rapidly approached [1.3]; emphasis will be on the reduction of standby power consumption without aggravating the device performance.

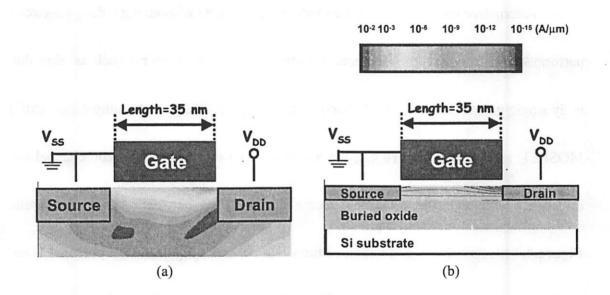

To achieve low off-state leakage current of a bulk-Si MOSFET, the channel potential should be controlled by the gate electrode rather than the drain electrode; thus, the gate-to-channel capacitance should be larger than the drain-to-channel capacitance.

Historically, this has been achieved through the use of thinner gate oxide, shallower source/drain junction depth, and complex channel doping engineering [1.4, 1.5].

Thinner gate oxide, *silicon dioxide*, increases gate capacitance. However, for a silicon dioxide thickness of 2.0 nm or below, direct quantum mechanical tunneling through the dielectric leads to an exponential increase in leakage current with decreasing oxide thickness [1.6]. Therefore, thicker and higher permittivity dielectrics need to be investigated as an alternative gate dielectric to replace the traditional silicon dioxide.

Shallow junction depth decreases the capacitive coupling of the drain to the channel. However, the formation of ultra-shallow junction depth is limited due to the finite energy of ion implantation and transient enhanced dopant diffusion during the thermal budget for dopant activation [1.7]. Parasitic series resistance in the junction regions could degrade the transistor on-state current, demanding technological innovations such as raised source/drain structures or activation of dopants at concentrations higher than the solid solubility.

Higher channel doping concentration with a localized halo in a bulk-Si transistor shields the channel from the influence of the drain potential [1.8]. However, too heavy channel doping decreases carrier mobility, increases parasitic junction capacitance and

leakage current, and worsens the subthreshold slope. These factors combined can significantly deteriorate either performance or standby power consumption. Variations in device properties due to random dopant fluctuation effects may limit chip yield due to the intolerable clock skews or malfunction of the circuits [1.2].

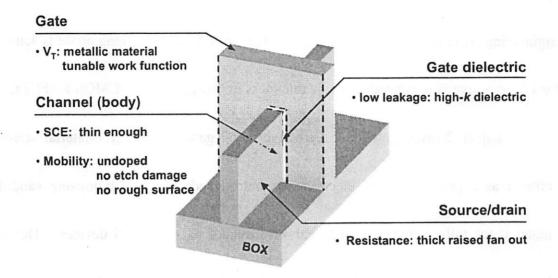

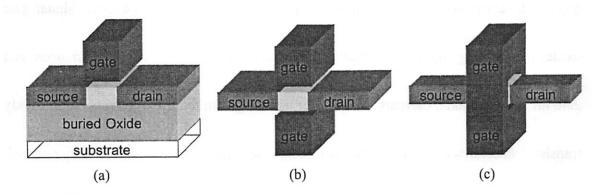

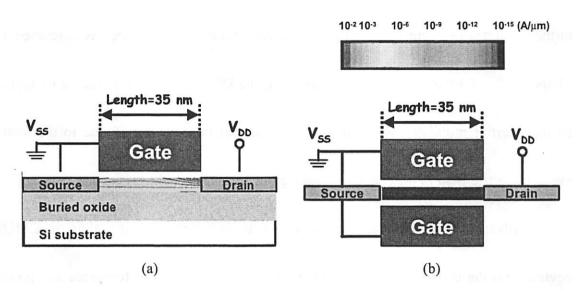

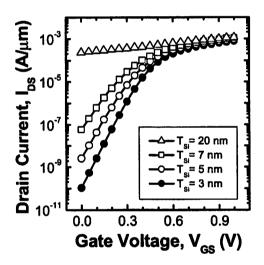

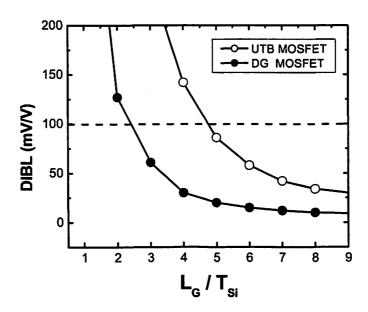

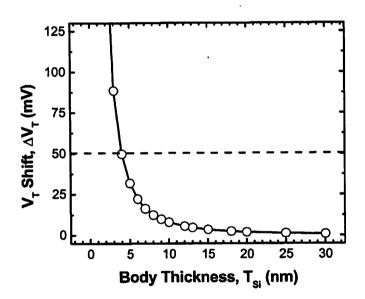

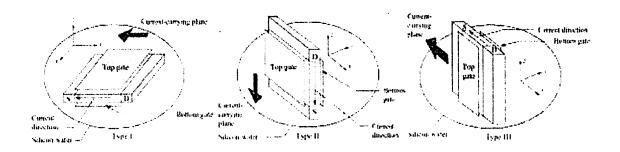

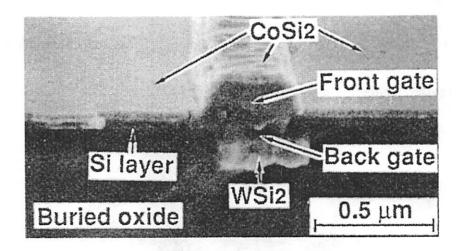

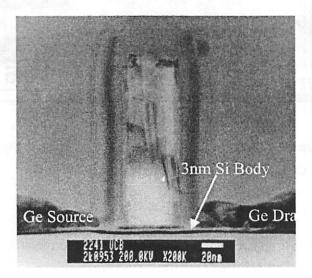

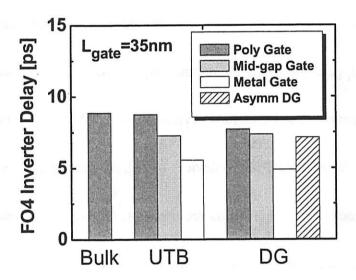

Recently, advanced thin-body transistor structures such as ultra-thin body (UTB) single gate and double gate MOSFETs have been proposed to suppress the off-state leakage current without degrading the on-state current [1.9, 1.10]. The use of ultra-thin undoped channel can effectively suppress the off-state leakage current, overcoming the aforementioned challenges in nanoscale bulk-Si MOSFETs. Reduced vertical electric field improves the gate dielectric reliability and reduces gate tunneling current. Circuit performance can be further increased due to the higher channel carrier mobility and reduced parasitic junction capacitance. However, implementation of such device structures has difficulties in process integration, except for the FinFET which provides self-alignment of top and bottom gates, highest packing density and easy access to all four transistor electrodes [1.11]. Remaining challenges for FinFETs to maximize the performance and minimize the standby power consumption are illustrated in Figure 1.2, and addressed in the subsequent chapters.

Figure 1.2 The FinFET provides relatively simple process integration, thus is one of the most promising double gate structures manufacturable below sub-25 nm gate length. However, technological innovations illustrated are required to maximize the performance benefits.

## 1.2 Objectives

In this dissertation, the key technological innovations illustrated in Figure 1.2 are addressed for the future nanoscale CMOS technologies. The process integration challenges and device performance of the advanced gate stack materials employing the advanced thin-body transistor structures are experimentally explored for the first time. A method of adjusting threshold voltages of ultra-thin body MOSFET and FinFET is

demonstrated for the first time with tunable molybdenum (Mo) gate work function engineering. A reduction of gate leakage current over 3 orders-of-magnitude is achieved for 1.72 nm inversion equivalent oxide thickness in Mo-gated HfO<sub>2</sub> CMOS FinFETs.

Chapter 2 investigates the alternative metal gate technology. Material selection criteria as a promising gate electrode are introduced; Mo is a promising candidate material for fully depleted (FD) silicon-on-insulator (SOI) CMOS devices. Damage-free sputtering with *plasma charge trap* and highly-selective dry etching processes are discussed and the analysis results of the work function shift for nitrogen implanted Mo gate are presented.

Chapter 3 explores the alternative high-k gate dielectric technology. The key basic material properties as a promising gate dielectric are summarized; HfO<sub>2</sub> is one of the most promising materials to replace SiO<sub>2</sub>. The impact of gate process technology is experimentally investigated. Successful integration of HfO<sub>2</sub> depends on minimizing the oxygen vacancy formation during CMOS fabrication through a reduction of post gate deposition thermal budget, and careful selection of the gate electrode material.

Chapter 4 investigates design methodology and process integration challenges for the advanced thin-body transistor structures. Adjustment of the desired threshold

voltages without degrading the performance benefits becomes a serious challenge. Mo gate work function engineering is experimentally demonstrated to be an attractive approach for adjusting the threshold voltages of advanced thin-body transistor structures. Integration of Mo gate and HfO<sub>2</sub> gate dielectric employing FinFET is experimentally demonstrated to reduce the gate leakage current over 3 orders-of-magnitude for 1.72 nm inversion equivalent oxide thickness.

Chapter 5 provides an overall summary of this dissertation. Key research contributions and suggestions for future research directions and possibilities are highlighted.

### 1.3 References

- [1.1] G. E. Moore, "No Exponential Is Forever: But "Forever" Can Be Delayed!," in *Int. Solid State Circuits Conf. Dig.*, pp. 20-23, 2003.

- [1.2] H.-S. P. Wong, D. J. Frank, P. M. Solomon, C. H. J. Wann, and J. J. Welser, "Nanoscale CMOS," *Proc. IEEE*, vol. 87, no. 4, pp. 537-570, 1999.

- [1.3] International Technology Roadmap for Semiconductors, Semiconductor Industry Association, 2003 (available at <a href="http://public.itrs.net">http://public.itrs.net</a>).

- [1.4] R. H. Dennard, F. H. Gaensslen, H. N. Yu, V. L. Rideout, E. Bassous, and A. R. LeBlanc, "Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions," IEEE J. Solid-State Circuits, vol. 9, pp. 256-268, 1974.

- [1.5] J. R. Brews, W. Fichtner, E. H. Nicollian, and S. M. Sze, "Generalized Guide for MOSFET Miniaturization," *IEEE Electron Device Lett.*, vol. 1, pp. 2-4, 1980.

- [1.6] S.-H. Lo, D. A. Buchanan, and Y. Taur, "Modeling and Characterization of Quantization, Polysilicon Depletion, and Direct Tunneling Effects in MOSFETs with Ultrathin Oxides," *IBM J. Res. Develop.*, vol. 43, no. 3, pp. 327-337, 1999.

- [1.7] A. Hokazono, K. Ohuchi, M. Takayanagi, Y. Watanabe, S. Magoshi, Y. Kato, T. Shimizu, S. Mori, H. Oguma, T. Sasaki, H. Yoshimura, K. Miyano, N. Yasutake, H. Suto, K. Adachi, H. Fukui, T. Watanabe, N. Tamaoki, Y. Toyoshima, and H. Ishiuchi, "14 nm Gate Length CMOSFETs utilizing Low Thermal Budget Process with Poly-SiGe and Ni Salicide," in *IEEE Int. Elec. Dev. Meet. Tech. Dig.*, pp. 639-642, 2002.

- [1.8] Y. Taur, C. H. Wann, and D. J. Frank, "25nm CMOS design considerations," in *IEEE Elec. Dev. Meet. Tech. Dig.*, pp. 789-792, 1998.

- [1.9] R.-H. Yan, A. Ourmazd, and K. F. Lee, "Scaling the Si MOSFET: From Bulk to SOI to Bulk," *IEEE Trans. Elec. Dev.*, vol. 39, no.7, pp. 1704-1710, 2000.

- [1.10] D. J. Frank, S. E. Laux, and M. V. Fischetti, "Monte Carlo Simulation of a 30 nm Dual-Gate MOSFET: How Short Can Si Go?," in *IEEE Elec. Dev. Meet. Tech. Dig.*, pp. 553-556, 1992.

- [1.11] X. Huang, W.-C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski, E. Anderson, H. Takeuchi, Y.-K. Choi, K. Asano, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, "Sub 50-nm FinFET: PMOS," in *IEEE Elec. Dev. Meet. Tech. Dig.*, pp. 67-70, 1999.

## **Chapter 2**

## **Metal Gate Technology**

### 2.1 Introduction

Polycrystalline silicon (poly-Si) gate technology has been used in CMOS devices for several decades. One of the primary reasons is its excellent thermal stability on SiO<sub>2</sub> during the high temperature source/drain annealing steps. This allows the source/drain regions to be self-aligned to the gate, thus eliminating parasitic capacitance from overlay misalignment during the lithography process [2.1]. Another reason is the easy controllability of its work function at the SiO<sub>2</sub> interface. Its work function can be modified from a low value (~4.17 eV) to a high value (~5.1 eV) by the ion implantation of appropriate dopants; dual-doped poly-Si gates allow the threshold voltages of NMOS

and PMOS to be adequate for CMOS applications, thus dramatically reducing the circuit power consumption [2.2].

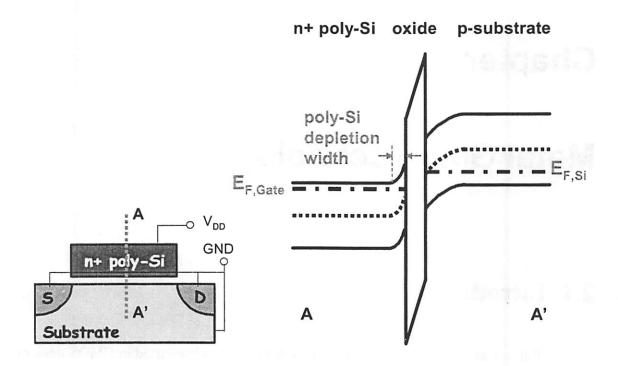

Figure 2.1 Energy band diagram of a n-channel MOS capacitor showing the depletion layer in the poly-Si gate, which typically adds several angstroms to the capacitance equivalent gate dielectric thickness (CET) when the channel is in strong inversion.

However, dual-doped poly-Si gates may not be promising any longer for nanoscale CMOS transistors due to poly-Si gate depletion effect (PDE), high sheet resistance, and boron dopant penetration through the gate oxide, etc. Among these concerns, the poly-Si gate depletion effect (PDE) is the most compelling reason; that is, a heavily doped poly-Si gate becomes slightly depleted at the gate oxide interface when the

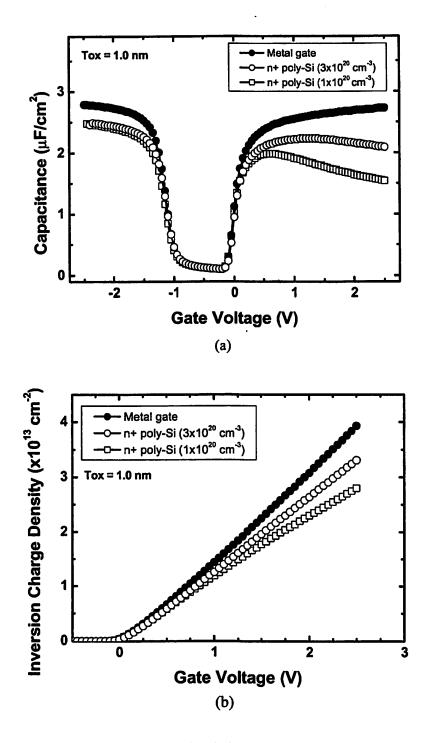

channel is in strong inversion [2.3]. Figure 2.1 illustrates a schematic band diagram across a MOS transistor in strong inversion. When the MOS transistor is biased into the strong inversion, an electric field is developed across the gate oxide. Since the oxide field points in the direction of accelerating a negative charge toward the gate, the bands in the poly-Si gate bend slightly upward toward the oxide interface, which depletes the surface of electrons and forms a thin depletion region  $(W_{d,polv})$  in the poly-Si gate. effectively increases the capacitance-equivalent thickness (CET) of the gate dielectric and decreases the inversion charge density in the channel, thus lowering the total gate capacitance and driving current of transistors. Figure 2.2 shows the quantummechanical simulation results of (a) C-V characteristics, and (b) inversion charge densities of poly-Si and metal gate NMOS transistors [2.4]. Since the oxide field becomes stronger with a thinner oxide (< 1.5 nm), the poly-Si gate depletion effect has more detrimental effects on nanoscale CMOS transistor performance.

Another concern with the poly-Si gate electrode is the high sheet resistance. Since the sheet resistance  $(R_S)$  is a function of thickness (t) and resistivity  $(\rho)$  of the gate electrode material, a thicker poly-Si gate and/or a lower resistivity is helpful to decrease the sheet resistance. However, a thicker gate stack proves to a poor choice due to the

Figure 2.2 Quantum-mechanical (QM) simulation results of (a) C-V characteristics, and (b) inversion charge density of poly-Si (open symbols) and metal gate (solid circle) n-channel MOS transistors.

increased parasitic gate-to-source/drain capacitance, thus compromising the circuit performance [2.5]. Also, in the poly-Si gate, the resistivity is determined by the active dopant concentration, which is limited by the solid solubility and thermal annealing of dopants in silicon. While the solid solubility of dopants is a material property, the use of high temperature annealing is limited due to the need for an abrupt retrograded channel doping and shallow source/drain junction doping profiles in nanoscale CMOS transistors.

Other concerns with dual-doped poly-Si gates include dopant (boron) penetration through thin gate oxide due to the large variation in threshold voltage and degradation in gate oxide reliability [2.6], thermodynamic incompatibility with future high-k gate dielectrics such as ZrO<sub>2</sub> [2.7], HfO<sub>2</sub> [2.8], and so on.

Metal gate electrodes can eliminate all of the aforementioned concerns, thus are indispensable for sub-65 nm CMOS technology node [2.9]. However, there are challenges in process integration that should be overcome to apply the metal gate technology to nanoscale CMOS devices.

### 2.2 Material Selection for Gate Electrode

In selecting alternative CMOS gate electrode materials, several factors must be considered [2.10]; these include the thermal stability on gate dielectric during high-temperature annealing step(s), the compatibility of the material growth and patterning with the conventional CMOS processes, the work function on a gate dielectric, the impact of gate processes on device performance and reliability, and the extendibility to future high-k gate dielectrics.

The highest-temperature annealing step(s) used in today's CMOS fabrication occurs during the source/drain dopant activation. Typically, the dopant activation is accomplished through rapid thermal annealing (RTA) at temperatures around or slightly above 1000°C for a few seconds in an inert ambient. Therefore, prospective gate materials should be thermodynamically stable on the gate dielectric, and have a higher melting point than 1000°C. It is worthwhile to note that choosing a material with a thermal expansion coefficient close to that of silicon is very desirable because the thermally induced stress may result in cracking or peeling of the gate stack materials.

The processes for material deposition and patterning should be compatible with the conventional CMOS processes. The deposition process plays an important role on

the interface quality between gate electrode and dielectric. Most thin metal films are deposited using either chemical vapor deposition (CVD) or physical vapor deposition (PVD) method. While CVD method leads to minimal damage and a smooth interface with the underneath gate dielectric, the precursors for only a limited number of metal films like tungsten (W), aluminum (Al), titanium nitride (TiN) have been well identified. On the other hand, PVD method can be used for most of the metal films with minimal incorporation of impurities, although new techniques need to be developed to prevent physical damage to the gate dielectric from the energetic particles (metal ions and/or electrons). Also, the dry etching process with high selectivity and vertical sidewall profile is indispensable for nanoscale CMOS device fabrication. While wet chemical etching results in high selectivity to the gate dielectric, the inherent isotropic etching characteristic prevents it from patterning the gate electrode in nanoscale CMOS device Therefore, the dry etching process condition should be optimized (or fabrication. developed) for the gate material.

The effect of the work function of gate electrode on the device operation is through its control of the threshold voltage (V<sub>T</sub>), which determines how much a gate voltage should be applied to invert the channel. For conventional bulk transistors, the

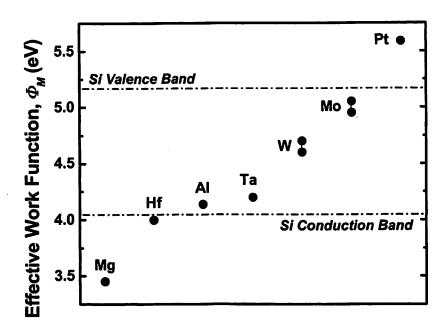

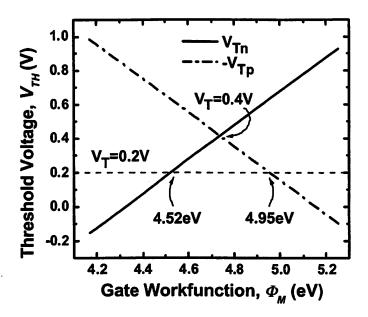

Figure 2.3 Experimental work function data for metals on silicon oxide (SiO<sub>2</sub>) [2.12].

silicon channel has a heavily  $(10^{16} - 10^{18} \text{ cm}^{-3})$  retrograded-doping profile to suppress the short channel effects. Thus, the work function difference between gate electrode and silicon channel affects the threshold voltage. A comprehensive quantum-mechanical (QM) simulation study shows that the device performance and short channel effects can be optimized simultaneously with metal gate electrode whose work function is near the conduction band  $(E_C)$  for NMOS device and the valence band  $(E_V)$  for PMOS device [2.11]. Figure 2.3 shows the experimental work function data for metals on silicon dioxide  $(SiO_2)$  [2.12]. On the other hand, for advanced thin-body transistors, the silicon

channel has an undoped or lightly ( $< 10^{16}$  cm<sup>-3</sup>) uniform doping profile to minimize the dopant fluctuation effect and maximize the carrier mobility. Thus, threshold voltage adjustment should be achieved by the work function of gate electrode due to the negligible depletion charge [2.12]. It is worth to note that a lightly doped thin-body can effectively suppress the short channel effects through the proper design of the device parameters such as the ratio of gate length to body thickness,  $\zeta = L_C/T_{Si}$ . The optimized gate electrode work function is 0.35 eV below (above) the conduction (valence) band for NMOS (PMOS) devices [2.10]. Figure 2.4 shows the theoretical data for threshold voltage of the thin-body MOSFET as a function of the gate work function [2.13].

Several material systems and process integration approaches which satisfy the aforementioned criteria have been investigated to date for CMOS applications: dual metal (Ti/Mo) [2.14], metal interdiffusion (Ti/Ni) [2.15], metal alloying (Ru/Ta) [2.16], fully silicided (NiSi<sub>x</sub>) doped polysilicon [2.17], and tunable-work-function metal (Mo) gate [2.18, 2.19, 2.20].

The tunable-work-function Mo gate technology offers the simplest CMOS process integration and better compatibility with high-k gate dielectric materials [2.19].

Figure 2.3 Theoretical data for threshold voltage of the thin-body MOSFET as a function of the gate work function [2.13].

Gate work function engineering via selective nitrogen implantation into the Mo gate electrode will provide multiple values of threshold voltage ( $V_T$ ) for NMOS and PMOS transistors on a single substrate. A higher melting point (2617°C) [2.21] and thermodynamic stability on SiO<sub>2</sub> and high-k dielectrics such as ZrO<sub>2</sub>, HfO<sub>2</sub>, etc [2.22, 2.23] allow for the self-aligned (gate-first) CMOS transistor fabrication. It should be noted that the adjustable-work-function fully silicided (NiSi<sub>x</sub>) method may not be applied on the future high-k dielectrics due to the thermodynamic instability [2.24]. The following sections will discuss the process details of the tunable-work-function Mo gate technology.

## 2.3 Damage-free Molybdenum Sputtering

Physical vapor deposition (PVD), also known as sputter deposition, and chemical vapor deposition (CVD) are the most widely used techniques for the fabrication of thin-film structures on semiconductor wafers. The physical vapor deposition as compared with chemical vapor deposition provides an important advantage of minimal incorporation of impurities. However, the physical vapor deposition is a relatively violent, atomic-scale process in which an energetic particle strikes a solid, resulting in the emission of one or more atoms from the solid sputtering target; thus, sputtering process may introduce damage to the gate dielectric.

#### 2.3.1 Sputtering System for Molybdenum

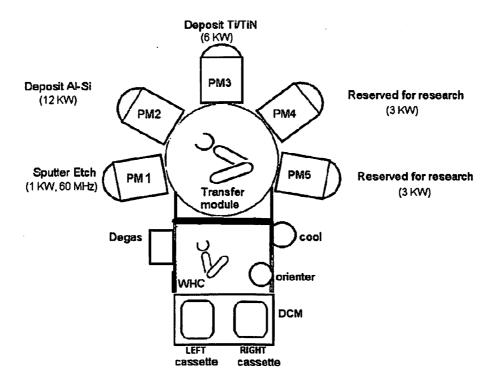

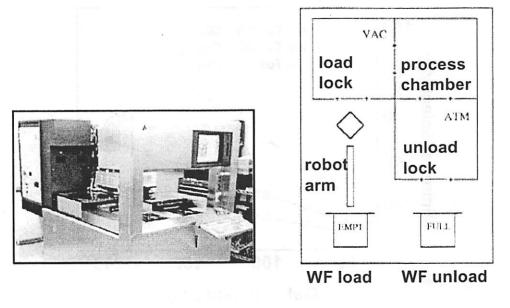

A DC-magnetron sputtering system (Novellus m2i with Quantum source) was used to deposit the Mo gate films. Figure 2.5 illustrates the schematics of the sputtering system; it has two load-lock stations, a wafer degassing station, sputtering chambers, and a cooling station. The base pressure of the sputtering chamber is maintained below  $5 \times 10^{-8}$  Torr, and argon (Ar) gas was used for Mo target sputtering.

Figure 2.5 Schematic of the Mo sputtering system; loaded wafers in load-lock station are transported to process module 5 for Mo sputtering.

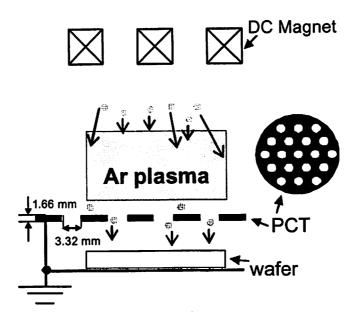

The critical requirements for a gate deposition process are: zero damage to the gate dielectric and good step coverage for non-planar transistor structures. Sputtering damage can result in degraded gate-oxide integrity (GOI) and transistor drive current due to degraded field-effect carrier mobility. The sputtering damage can be minimized by eliminating the high-energy particle bombardment by interposing an electrically grounded *Plasma Charge Trap* (PCT) between the Mo target and substrate, separating the plasma excitation and Mo film deposition [2.25]. **Figure 2.6** illustrates a schematic

of the sputtering chamber with the PCT, which is made of 1.66 mm thick stainless steel and has arrays of closely packed 3.32 mm diameter holes (40.3% aperture area). Since the PCT is electrically grounded, it collects high energy ions as well as a fraction of the neutral Mo atoms which are traveling toward the cathode/sample plane. These particles are deposited onto the PCT, and hence are not deposited onto the wafer surface. Therefore, the sputtering damage can be minimized. It is worth noting that the Mo deposition rate with the PCT is reduced by about 70% and is proportional to the PCT aperture area.

Figure 2.6 Schematic of the sputtering chamber with the plasma charge trap (PCT), which is inserted between the sputtering target (Mo) and wafer.

#### 2.3.2 Experimental Results and Discussion

To investigate the efficacy of the plasma charge trap (PCT) for minimizing the sputtering damage, conventional bulk silicon p-channel MOSFETs were fabricated with Mo gates sputtered either with or without the PCT. Mo-gate films with 50 – 150 nm thicknesses were deposited at 200°C with 10 mTorr process pressure and 300 W sputtering power.

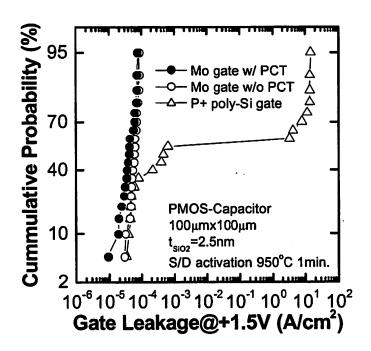

Damage to the gate dielectric can be assessed by measuring the gate leakage current density and gate-dielectric lifetime. Gate leakage current densities for Mo-gated PMOS capacitors are compared against those of p+ poly-Si gated PMOS capacitors (control samples) as shown in **Figure 2.7**. The p+ poly-Si gated devices show a large variation in gate leakage current due to boron dopant penetration through the gate oxide. The Mo-gated devices have lower gate leakage with much tighter distributions; the PCT provides ~30% lower gate leakage due to the lower (more negative) threshold voltage of the Mo-gated devices, even though the electrical stressing condition is more severe compared to the control samples.

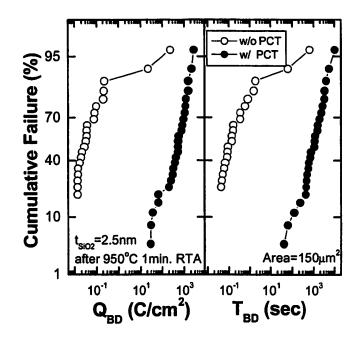

Figure 2.8 shows the Charge-to-Breakdown  $(Q_{BD})$  and measured Time Dependent Dielectric Breakdown (TDDB) of gate oxide. The measured transistor gate

Figure 2.7 Gate leakage current densities of Mo-gated PMOS capacitors are compared against those of p+ poly-Si gated PMOS capacitors.

area is 150  $\mu$ m<sup>2</sup>. For the  $Q_{BD}$  measurements, the devices were biased at a constant gate voltage +4.4 V. Since the devices have the same threshold voltage, the effective stressing condition is the same for both groups of samples. It is worth to note that the breakdown of a thinner gate oxide occurs by bulk trap generation, not by interface trap generation, and is therefore driven by gate voltage [2.26]. With PCT Mo sputtering, the gate oxide integrity is significantly improved; indicating that low sputtering damage to gate dielectric is achieved.

Figure 2.8 Measured Charge-to-Breakdown (Q<sub>BD</sub>) and Time Dependent Dielectric Breakdown (TDDB) of Mo-gated p-channel MOSFETs. With PCT Mo sputtering, the gate oxide integrity is significantly improved, indicating that low sputtering damage to gate dielectric is achieved.

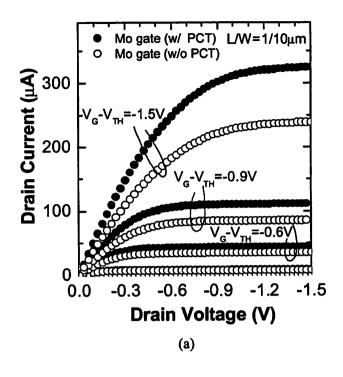

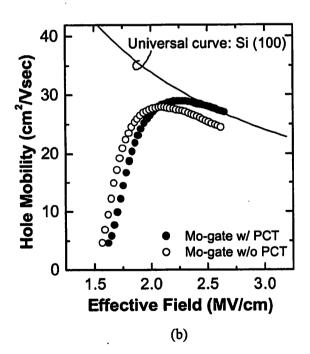

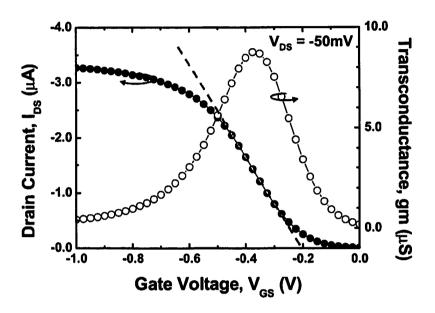

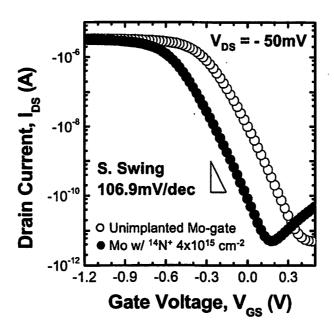

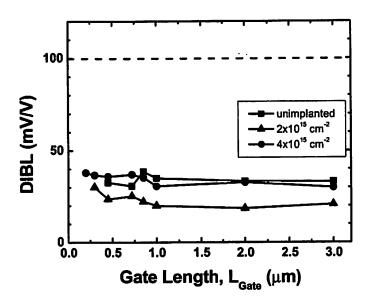

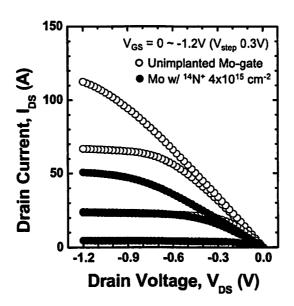

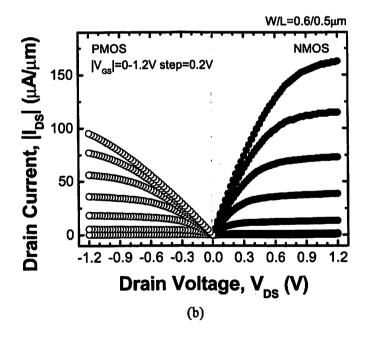

Figure 2.9 (a) shows the measured  $I_D - V_D$  characteristics of Mo-gated bulk-Si p-channel MOSFETs. The drive current achieved with a PCT sputtered Mo gate is higher due to improved hole mobility as shown in Figure 2.9 (b), which matches the universal mobility curve. The improved hole mobility is attributed to reduced interface traps  $(Q_{it})$  and/or fixed charge  $(Q_f)$  due to the damageless Mo gate sputtering process [2.27].

Figure 2.9 (a) Measured  $I_D - V_D$  characteristics, and (b) measured effective hole mobility of Mo-gated p-channel bulk-Si MOSFETs.

## 2.4 Highly Selective Molybdenum Dry Etching

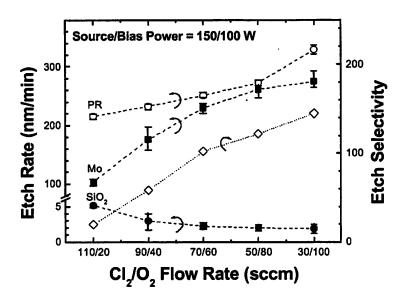

It is known that fluorine (F) and chlorine (Cl) radicals can etch Mo films at an appreciable rate [2.28]. Therefore, Mo-gate films can be etched using either F-based or Cl-based etching gases such as CF<sub>4</sub>, CF<sub>3</sub>Cl, Cl<sub>2</sub>, etc. However, fluorinated carbon compounds like CF<sub>4</sub> and/or CF<sub>3</sub>Cl, which may attack the underneath gate dielectric (SiO<sub>2</sub>) [2.29], are precluded due to the selectivity requirement. Thus, focusing on a Cl<sub>2</sub>/O<sub>2</sub> gas mixture, the dependences of etch rate and selectivity to SiO<sub>2</sub> on Cl<sub>2</sub>/O<sub>2</sub> gas flow rates, source and bias RF powers were investigated.

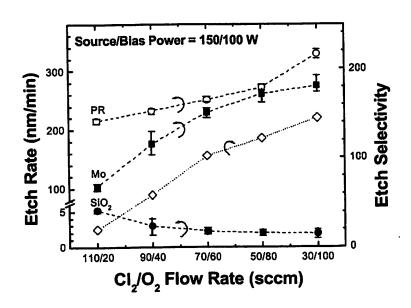

#### 2.4.1 Dry Etching System for Molybdenum

A Transformer Coupled Plasma etcher (LAM Research TCP 9400) was used to etch the Mo gate films. Figure 2.10 illustrates the schematic of the dry etching system; it has load (unload)-lock stations and a process chamber. The process chamber has two RF power (source, bias) supplies running at the same time during the dry etching process, which results in a high-density plasma with adjustable substrate bias.

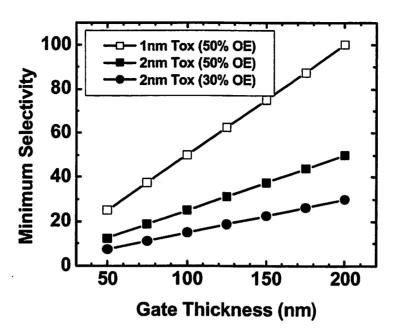

The critical requirements for a gate etching process are high selectivity to the gate dielectric (SiO<sub>2</sub>) and vertically etched profile. Figure 2.11 shows the minimum

Figure 2.10 Schematics of the Mo dry etching system (LAM Research TCP9400).

etch selectivity required, as a function of gate stack thickness. For example, the etching selectivity must be higher than 25:1, assuming that the thicknesses of the Mo gate and  $SiO_2$  gate oxide are 100 nm and 2 nm, respectively, with a 50% over-etch.

#### 2.4.2 Experiment Results and Discussion

Conventional bulk-Si sample wafers with 100 nm thick thermally grown  $SiO_2$  and 300 nm thick Mo film (or 1  $\mu$ m thick photo resist) on the  $SiO_2$  were prepared to investigate the etching characteristics of  $Cl_2/O_2$  gas mixture. To calculate the etch rate of the thin films, physical step-height and optical thickness measurements were adopted

Figure 2.11 Minimum etch selectivity required as a function of gate stack thickness.

before and after the dry etching process of each sample wafer. The Mo film was sputtered in the Novellus system,  $SiO_2$  was thermally grown in a wet oxidation furnace at  $900^{\circ}$ C, and *i*-line (OCG OiR-10i) photo resist was hard baked in 10 minutes at  $120^{\circ}$ C.

Figure 2.12 shows the dependence of the etch rates of Mo, SiO<sub>2</sub> and photo resist (PR) on the oxygen partial pressure in a Cl<sub>2</sub>/O<sub>2</sub> gas mixture. The total gas flow rate was held constant at 130 sccm, and the process pressure was 13 mTorr with 150W/100W source/bias RF powers. With sufficient chlorine and oxygen radicals, the addition of oxygen gas increases the Mo-gate etching rate and decreases the SiO<sub>2</sub> etch rate, and hence improves the selectivity. This implies that the surface of the Mo film can be

easily oxidized and reacted with chlorinated gas to sublimate at ~100°C in the form of molybdenum oxychlorine (MoO<sub>x</sub>Cl<sub>y</sub>) [2.30]. It should be noted that more than 75% oxygen results in significant etching of the photo resist (PR), which may prevent it from being used as a useful masking material.

Figure 2.12 Etch-rate dependences of Mo, SiO<sub>2</sub>, and photoresist (PR) on the oxygen partial pressure in the Cl<sub>2</sub>/O<sub>2</sub> gas mixture. The total gas flow rate was held constant at 130 sccm, and the process pressure was 13 mTorr with 150 W source RF power and 100 W bias RF power.

Figure 2.13 shows the dependence of Mo and  $SiO_2$  etch-rate on source power with a constant gas flow rate ( $Cl_2/O_2 = 70/60$  sccm), process pressure (13 mTorr), and bias power (100 W). The etch rates of Mo and  $SiO_2$  increase linearly with source power

because more chlorine and oxygen radicals are available, but the selectivity decreases due to the faster increase in SiO<sub>2</sub> etch rate. For source powers below 150 W, the etch rate of SiO<sub>2</sub> is constant due to the DC self-bias voltage, so that the etch selectivity is degraded.

Figure 2.13 Etch-rate dependences of Mo and  $SiO_2$  on source power with constant gas flow rate  $(Cl_2/O_2 = 70/60 \text{ sccm})$ , process pressure (13 mTorr), and bias power (100 W).

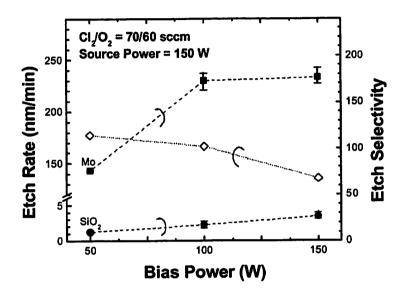

Figure 2.14 shows the dependence of Mo and  $SiO_2$  etch-rate on bias power with constant gas flow rate ( $Cl_2/O_2 = 70/60$  sccm), process pressure (13 mTorr), and source power (150 W). The Mo etch rate saturates above 100 W bias power, whereas  $SiO_2$  etching rate increases monotonically. Therefore, the etch selectivity decreases with increasing bias power. This indicates that energetic ion bombard-ment does not always

increase the Mo etch rate, and that chemical etching plays an important role. It is worth to note that the bond dissociation energy of SiO<sub>2</sub> is larger than that of Mo [2.31].

Figure 2.14 Etch-rate dependences of Mo and  $SiO_2$  on bias power with constant gas flow rate  $(Cl_2/O_2 = 70/60 \text{ sccm})$ , process pressure (13 mTorr), and source power (150 W).

Table 2.1 summarizes the optimized Mo gate etch process condition which yields 230 nm/min etch rate and  $\sim 100:1$  (Mo:SiO<sub>2</sub>) etch selectivity: Cl<sub>2</sub>/O<sub>2</sub> = 70/60 sccm, process pressure = 13 mTorr, source/bias RF power = 150/100 W.

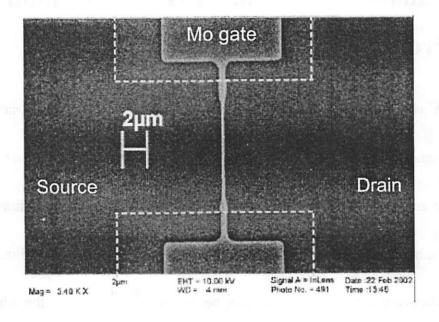

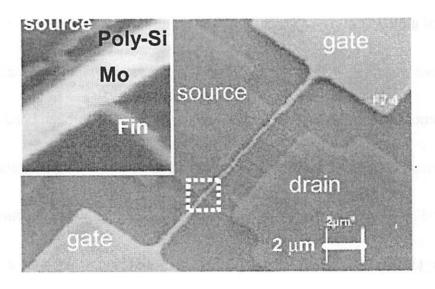

Figure 2.15 shows the plane- and tilted-view scanning electron microscopy (SEM) picture of the etched Mo gate profiles using the optimized etch recipe. Neither micro-trenching nor Mo gate residue was observed due to the high etching selectivity;

thus, this process condition can be directly applicable to the thin-body transistor structures including FinFETs.

Table 2.1 Optimized Mo gate dry-etching process condition.

|                        | Step 1    | Step 2    | Step 3 | Step 4    | Step 5 |

|------------------------|-----------|-----------|--------|-----------|--------|

|                        | Stabilize | Stabilize | Time   | Stabilize | EPD    |

| Gap (cm)               | 5.8       | 5.8       | 5.8    | 5.8       | 5.8    |

| Pressure (mTorr)       | -         | 30        | 30     | 13        | 13     |

| Source Power (W)       | 0         | 0         | 300    | 0         | 150    |

| Bias Power (W)         | 0         | 0         | 120    | 0         | 100    |

| CF <sub>4</sub> (sccm) | 0         | 100       | 100    | 0         | 0      |

| Cl <sub>2</sub> (sccm) | 0         | 0         | 0      | 70        | 70     |

| O <sub>2</sub> (sccm)  | 0         | 0         | 0      | 60        | 60     |

| Time (sec)             | 30        | 30        | 7      | 30        | 30     |

| End-Point-Detect       | -         | -         | -      | -         | Ch A   |

Figure 2.15 Plane- and tilted view scanning electron microscopy (SEM) picture of the etched Mo gate profiles using the optimized process condition.

# 2.5 Tunable-Work-Function Molybdenum Process

A work function, defined as a minimum energy necessary to extract an electron from a metal surface, is a fundamental property of metals that depends on both the electronic and ionic structure at that metal surface. Thus, the work function can be engineered by modifying the microstructure and/or chemistry of a metal film.

Microstructural modification can be achieved by changing the film texture or preferred orientation, crystalline phase, and crystal lattice, etc. For example, the work function of a metal film is, in general, dependent on the surface orientation (also known as the work function anisotropy); closely packed crystallographic surfaces show high work functions due to the smooth surface and relatively fewer broken bonds, while open crystallographic surfaces show low work functions due to a great number of broken bonds [2.32]. Experimentally it has been observed the work function in metals decreases (110) (100) (111) trend [2.33]. In addition, this was experimentally demonstrated for molybdenum (Mo) and tungsten (W) with modification of the film microstructures (surface orientation, crystalline phase) by implanting inert Ar<sup>+</sup> ions and/or controlling the deposition parameters [2.17, 2.34].

Chemical modification can be achieved by nitridizing, oxidizing, and alloying the metal film. It should be noted that the metal film after chemical modification should maintain high metallic conductivity to be used as a gate electrode. Modifying the film chemistry through nitridizing Mo film [2.35, 2.36], and alloying Ru-Ta [2.15] was experimentally demonstrated.

Both microstructural and chemical modifications can be simultaneously achieved by introducing foreign elements such as oxygen and nitrogen into a metal. Ion implantation is the most widely used technique to introduce dopant ions into films due to its precise control of implant dose (#/cm²), energy (eV) and tilt angle. For example, the implantation of nitrogen ions (N¹) into Mo film with subsequent annealing can modify the microstructure and chemical properties with precise control through inducing a nitridation reaction of Mo films [2.17].

#### 2.5.1 Experimental Results and Discussion

Mo-gated capacitors were fabricated on lightly doped ( $\sim 10^{15}$  cm<sup>-3</sup>) p-type Si substrates with thermally grown SiO<sub>2</sub> as a gate dielectric. In order to account for the influence of oxide fixed charge ( $Q_F$ ), multiple SiO<sub>2</sub> thicknesses were obtained on a single

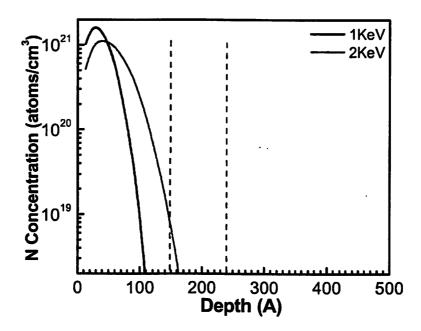

Figure 2.16 Simulated nitrogen concentration-depth profiles in the Mo/SiO<sub>2</sub>/Si stack (Dose =  $5\times10^{15}$ /cm<sup>2</sup>).

substrate by selective etchback using dilute HF solution. 15 nm thick Mo films were sputtered at 200°C in Novellus sputtering system, as described in Chapter 2.3, with a base pressure of  $1\times10^{-8}$  Torr and a process pressure of 10 mTorr. For some wafers, the Mo gate was implanted with nitrogen ions. The implant energies were 1 keV and 2 keV with implant dose of  $5\times10^{15}$  and  $1\times10^{16}$  cm<sup>-2</sup>. Ultra-shallow nitrogen ion implantation to very thin Mo gate films was adopted to minimize the ion penetration into the gate dielectric due to the shallower projected range  $(R_P)$  and smaller straggle  $(\Delta R_P)$  while allowing for high atomic nitrogen content inside the Mo films. Figure 2.16 shows

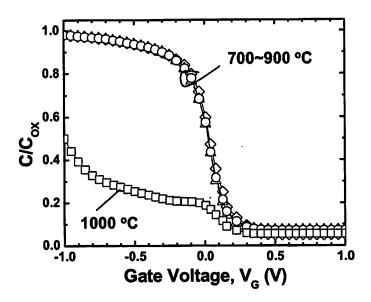

SRIM simulation results of the nitrogen concentration-depth profiles in the Mo/SiO<sub>2</sub>/Si stacks with nitrogen implant dose of 5x10<sup>15</sup> cm<sup>-2</sup>, which is estimated to introduce about 5 % nitrogen inside the 15 nm thick Mo gate [2.37]. After gate patterning, wafers were annealed from 500°C to 900°C in N<sub>2</sub> ambient, followed by forming gas anneal (400°C, 15 min).

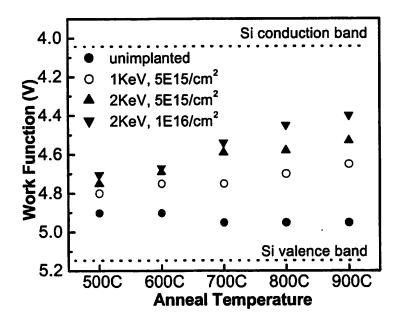

Figure 2.17 The extracted Mo work function with subsequent thermal annealing temperature.

All anneals were 15 min long except for 900°C anneal (15s).

Figure 2.17 shows the extracted work function of Mo gate as a function of subsequent annealing temperature. The flatband voltages  $(V_{FB})$  of the Mo-gated

capacitors was determined from capacitance-voltage (C-V) measurements, and used to extract the work function  $(\Phi_M)$  [2.38]. The work function of un-implanted Mo gates increased slightly upon annealing, but is fairly stable at 4.95 eV. This increase can be ascribed to an improvement in the crystalline quality of the Mo film (increase in the columnar grain size). It is worth to note that this work function value is in good agreement with the published values for the (110) Mo work function. X-Ray Diffraction (XRD) analysis, as shown in Chapter 2.5.1, indicates that the deposited Mo film has a (110) preferred orientation.

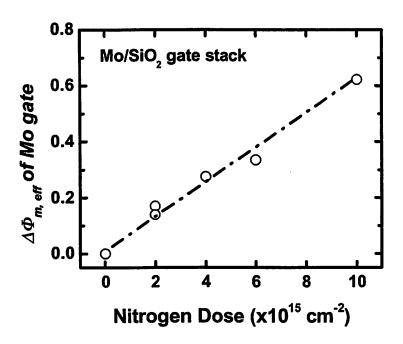

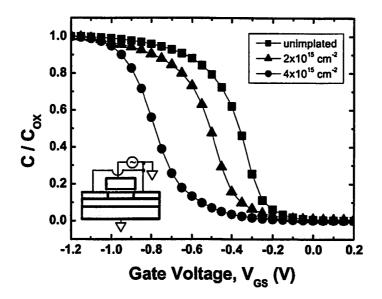

Figure 2.18 The effective work function shift of Mo gate as a function of nitrogen implant dose.

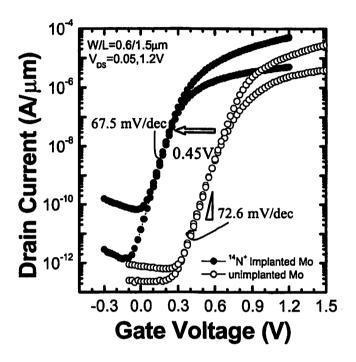

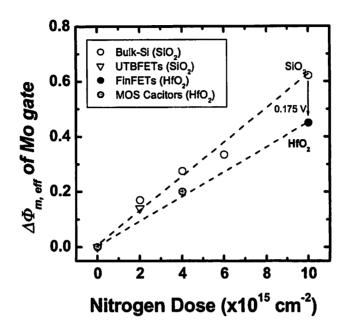

Figure 2.18 shows the effective work function shift  $(\Delta \Phi_{m,eff})$  of Mo gate as a function of nitrogen implant dose. All samples were annealed at 900°C in N<sub>2</sub> ambient. It can be seen that the Mo gate work function decreases with a decrease in nitrogen implant doses. The amount of reduction in gate work function is proportional to the nitrogen implant dose.

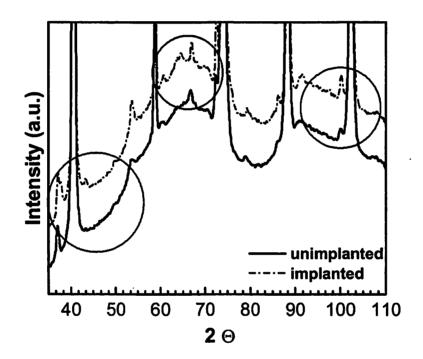

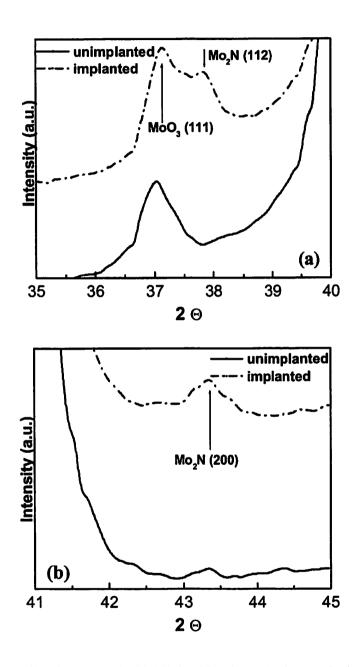

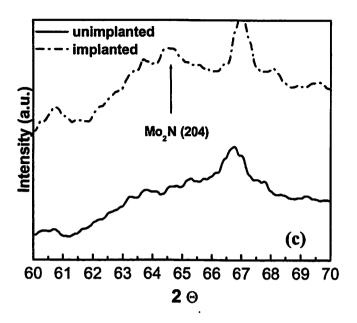

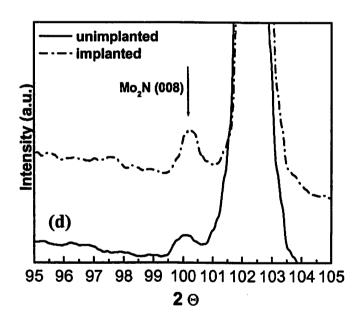

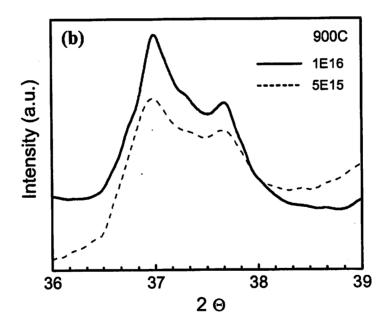

Figure 2.19 XRD analysis of nitrogen implanted and un-implanted Mo films.

In order to investigate the origin of the work function shift, x-ray diffraction (XRD) analysis of nitrogen implanted (dose =  $1 \times 10^{16}$  cm<sup>-2</sup>) and un-implanted wafers were performed (Figure 2.19). Several diffraction peaks corresponding to Mo<sub>2</sub>N can be

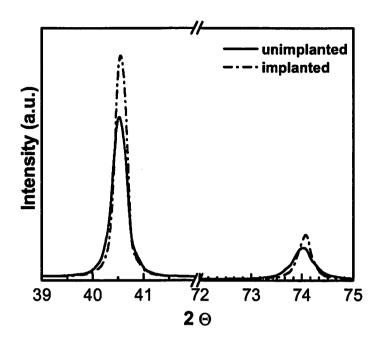

Figure 2.20 Comparison of the XRD intensities for the 110 and 112 peaks.

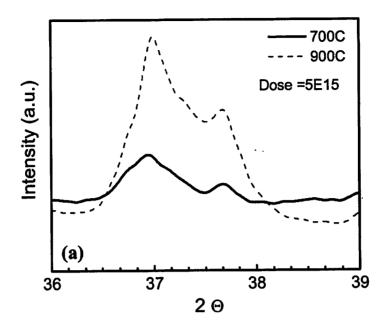

observed in nitrogen implanted wafers. **Figure 2.20** compares the intensities for the (110) and (112) peaks, indicating that both Mo gates have predominantly a (110) texture. **Figures 2.21** (a–d) shows the details of diffraction peaks, indicating that peaks for Mo<sub>2</sub>N are observed in the nitrogen implanted sample while no such peaks are observed in the unimplanted sample. **Figure 2.22** (a–b) compares the dependence of Mo<sub>2</sub>N (112) peak intensity on nitrogen implant dose (5x10<sup>15</sup>, 1x10<sup>16</sup> cm<sup>-2</sup>) and subsequent annealing temperature (700, 900°C). It can be seen that increasing the dose or annealing temperature leads to an increase in the Mo<sub>2</sub>N peak intensity. It is believed that an increase

in annealing temperature enhances segregation of nitrogen at the Mo/SiO<sub>2</sub> interface, resulting in a lowering of the interfacial work function.

Figure 2.21 (a-d) Details of XRD peaks highlighted in Figure 2.19. Peaks indicative of Mo<sub>2</sub>N formation are observed in the nitrogen implanted sample while no such peaks are observed in the control (un-implanted) sample.

Figure 2.21 (a-d) Details of XRD peaks highlighted in Figure 2.19. Peaks indicative of Mo<sub>2</sub>N formation are observed in the nitrogen implanted sample while no such peaks are observed in the control (un-implanted) sample.

Figure 2.22 (a-b) Details of XRD peaks highlighted in Figure 2.19. Peaks indicative of Mo<sub>2</sub>N formation are observed in the nitrogen implanted sample while no such peaks are observed in the control (un-implanted) sample.

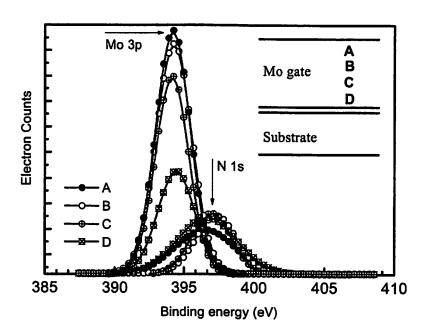

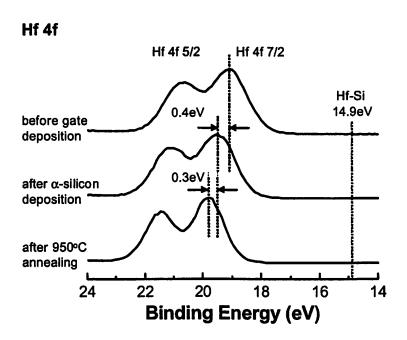

To further analyze the chemical changes in the nitrogen implanted Mo films, x-ray photoelectron spectroscopy (XPS) analysis was performed. Figure 2.23 shows the results of XPS analysis illustrating electron counts vs. binding energy for Mo and N signals at several points through the depth of Mo film. There is a significant overlap between the Mo 3p peak and the N 1s peak since they are separated by ~4 eV. Hence, the overall peak was deconvolved to isolate the Mo and N contributions. A stronger N signal accompanies the Mo signal when approaching the Mo/SiO<sub>2</sub> interface (point D). It is worth to note that the XPS analysis does not show the formation of MoO<sub>2</sub>, MoO<sub>3</sub> or Mo-silicide at the SiO<sub>2</sub>

Figure 2.23 Mo 3p and N 1s binding energy at different positions across the Mo film thickness.

A significant N signal is observed throughout the Mo film, indicating a diffusion of the implanted N across the film thickness.

interface, indicating the thermodynamic stability of Mo on SiO<sub>2</sub> at 900°C.

The diffusivity and solubility of N inside Mo at high temperatures (> 1000°C) have been evaluated [2.39,2.40]. While the relevant data for lower temperatures is not available, the extrapolated N diffusion coefficient at 900°C is very high (~2x10<sup>-8</sup> cm<sup>2</sup>/s). Low temperature diffusivities in poly-crystalline thin films are expected to be much higher, since the grain boundary diffusion would tend to dominate over bulk diffusion in the low temperature regime [2.41]. The low solid solubility of N in Mo (<1% at 1000°C) supports the observed formation of Mo<sub>2</sub>N after N implantation. The implanted N atomic content for a dose of  $1x10^{16}$  cm<sup>-2</sup> into a 15 nm Mo film is ~10%. Thus, a combination of enhanced diffusivity and low solubility leads to the segregation of N and formation of Mo<sub>2</sub>N in N implanted Mo films. Therefore, the work function shift of nitrogen implanted Mo gate results from a simultaneous evolution of the Mo film morphology and chemistry at the gate dielectric interface.

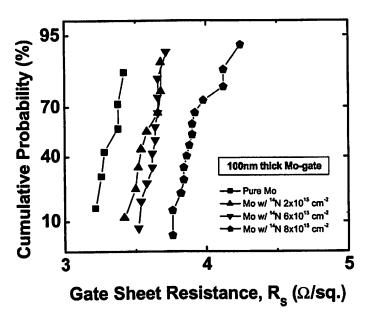

Figure 2.24 shows the sheet resistance  $(R_S)$  of 100-nm-thick Mo films for various nitrogen ion implantation doses after 900°C, 1-minute rapid thermal annealing (RTA) in nitrogen ambient. The sheet resistance increases slightly with implantation dose because of the increased impurity (nitrogen in Mo) scattering. The average grain

Figure 2.24 Sheet resistance (R<sub>S</sub>) of 100 nm-thick Mo films for various <sup>14</sup>N<sup>+</sup> implantation doses.

size was estimated from the full-width at half maximum (FWHM) of X-ray diffraction peaks using the Scherer formula, as shown in Figure 2.20 [2.42]. The estimated grain sizes for pure and nitrogen implanted (dose of  $1x10^{16}$  cm<sup>-2</sup>) Mo films are 46.3 nm and 63.8 nm, respectively. It is worth noting that the grain size increases as more nitrogen is incorporated [2.43].

## 2.6 Summary

This chapter summarized the requirements of metal gate technology for the future nanoscale CMOS technology generations. Molybdenum (Mo) is a promising

candidate gate material for fully depleted (FD) silicon-on-insulator (SOI) CMOS devices. Damage-free sputtering and high-selectivity dry etching processes for Mo gate films have been developed. With a plasma charge trap (PCT), sputtering damage to the gate dielectric can be minimized for improved drive current and gate oxide integrity (GOI). Mo gate electrodes can be patterned without leaving any residue or stringers due to the The work function of a Mo gate can be tuned by nitrogen highly selective etch process. implantation followed by a thermal anneal, to provide a means for adjusting the threshold voltage of thin-body MOSFETs. The work function shift of nitrogen implanted Mo gate is resulted from the simultaneous modification of the microstructure and chemistry of Mo film at the gate dielectric interface. The nitrogen implantation induces a slight increase in sheet resistance due to impurity scattering, although it results in a slightly larger average grain size.

### 2.7 References

[2.1] J. C. Sarace, R. E. Kerwin, D. L. Klein, and R. Edwards, "Metal-Nitride-Oxide-Silicon Field-Effect Transistors with Self-Aligned Gates," *J. Solid-State Electro.*, vol. 11, pp. 653-660, 1968.

- [2.2] F. M. Wanlass, and C.T. Sah, "Nanowatt Logic using Field-Effect Metal-Oxide-Semiconductor Triodes," in *IEEE Int. Solid-State Circuits Conf. Digest*, pp. 32-33, 1963.

- [2.3] C. Y. Wong, J. Y.-C. Y. Taur, C. S. Oh, R. Angelucci, and B. Davari, "Doping of N+ and P+ Polysilicon in a Dual-Gate CMOS Process," in *IEEE Int. Electron Device Meet. Digest*, pp. 238-241, 1988.

- [2.4] Shred simulation (available at <a href="http://www.nanohub.org/">http://www.nanohub.org/</a>)

- [2.5] S. Balasubramanian, L. Chang, B. Nikolic, and T.-J. King, "Circuit-Performance Implications for Double-Gate MOSFET Scaling below 25nm," *IEEE Silicon Nanoelectronics Workshop*, pp. 16-17, 2003.

- [2.6] J. Y.-C. Sun, C. Y. Wong, Y. Taur, and C. Hsu, "Study of Boron Penetration Through Thin Oxide with P+ Polysilicon Gate," in *IEEE VLSI Tech. Symp. Digest*, pp. 17-18, 1989.

- [2.7] C. H. Lee, H. F. Luan, W. P. Bai, S. J. Lee, T. S. Jeon, Y. Senzaki, D. Roberts, and D. L. Kwong, "MOS Characteristics of Ultra Thin Rapid Thermal CVD ZrO<sub>2</sub> and Zr Silicate Gate Dielectrics," in *IEEE Int. Electron Device Meet. Digest*, pp. 27-30, 2000.

- [2.8] C. Hobbs, L. Fonseca, V. Dhandapani, S. Samavedam, B. Taylor, J. Grant, L. Dip, D. Triyoso, R. Hegde, D. Gilmer, R. Garcia, D. Roan, L. Lovejoy, R. Rai, L. Hebert, H. Tseng, B. White, and P. Tobin, "Fermi Level Pinning at the PolySi/Metal Oxide Interface," in *IEEE VLSI Tech. Symp. Digest*, pp. 9-10, 2003.

- K. Shiraishi, K. Yamada, K. Torii, Y. Akasaka, K. Nakajima, M. Kohno, T. Chikyo, H. Kitajima, and T. Arikado, "Physics in Fermi Level Pinning at the PolySi/Hf-based High-k Oxide Interface, in *IEEE VLSI Tech. Symp. Digest*, pp. 108-109, 2004.

- [2.9] International Technology Roadmap for Semiconductors, Semiconductor Industry Association, 2003 (available at http://public.itrs.net).

- [2.10] D. Ha, H. Takeuchi, Y.-K. Choi, and T.-J. King, "Molybdenum Gate Technology for Ultra-Thin-Body MOSFETs and FinFETs," *IEEE Trans. on Elec. Dev.*, vol. 51, pp. 1989-1996, 2004.

- [2.11] I. De, D. Johri, A. Srivastava, and C. M. Osburn, "Impact of Gate Work-Function on Device Performance at the 50 nm Technology Node," J. Solid-State Electro., pp. 1077-1080, 2000.

- [2.12] Y.-C. Yeo, "Gate-Stack and Channel Engineering for Advanced CMOS Technology," *Ph.D Thesis*, University of California, Berkeley, 2002.

- [2.13] L. Chang, S. Tang, T.-J. King, J. Bokor, and C. Hu, "Gate Length Scaling and Threshold Voltage Control of Double-Gate MOSFETs," in *IEEE Int. Electron Device Meet. Digest*, pp. 719-722, 2000.

- [2.14] Y.-C. Yeo, Q. Lu, P. Ranade, H. Takeuchi, K. J. Yang, I. Polishchuk, T.-J. King, C. Hu, S.C. Song, H. F. Luan, D. -L. Kwong, "Dual-Metal Gate CMOS Technology with Ultra-Thin Silicon Nitride Gate Dielectric", *IEEE Elec. Dev. Lett.*, vol. 22, no. 5, pp. 227-229, May 2001.

- [2.15] I. Polishchuk, P. Ranade, T.-J. King and C. Hu, "Dual Work Function Metal Gate CMOS Transistors by Ni-Ti Interdiffusion", *IEEE Elec. Dev. Lett.*, vol. 23, no. 4, pp. 200-201, April 2002.

- [2.16] J. H. Lee, H. Zhong, Y.-S. Suh, G. Heuss, J. Gurganus, B. Chen, and V. Misra, "Tunable Work Function Dual Metal Gate Technology for Bulk and Non-Bulk CMOS," in *IEEE Int. Electron Device Meet. Digest*, pp. 359-362, 2002.

- [2.17] J. Kedzierski, E. Nowak, T. Kanarsky, Y. Zhang, D. Boyd, R. Carruthers, C. Cabral, R. Amos, C. Lavoie, R. Roy, J. Newbury, E. Sullivan, J. Benedict, P. Saunders, K. Wong, D. Canaperi, M. Krishnan, K.-L. Lee, B. A. Rainey, D. Fried, P. Cottrell, H.-S.P Wong, M. Ieong, W. Haensch, "Metal-Gate FinFET and Fully-Depleted SOI Devices using Total Gate Silicidation," in *IEEE Int. Electron Device Meet. Digest*, pp. 247-250, 2002.

- [2.18] P. Ranade, Y. K. Choi, D. Ha, A. Agarwal, M. Ameen, T.-J. King, "Tunable Work Function Molybdenum Gate Technology for FDSOI-CMOS," in *IEEE Int. Electron Device Meet. Digest*, pp. 363-366, 2002.

- [2.19] R. J. P. Lander, J. C. Hooker, J. P. van Zijl, F. Roozeboom, M. P. M. Maas, Y. Tamminga, R.A.M. Wolters, "A Tunable Metal Gate Work Function using Solid State Diffusion of Nitrogen", in *Proc. European Solid-State Dev. Res. Conf.*, pp. 103-106, 2002.

- [2.20] D. Ha, H. Takeuchi, Y.-K. Choi, T.-J. King, W. P. Bai, D.-L. Kwong, A. Agarwal, and M. Ameen, "Molybdenum-Gate HfO<sub>2</sub> CMOS FinFET Technology," in *IEEE Int. Electron Device Meet. Digest*, 2004.

- [2.21] A. G. Dirks, R. A. M. Wolters, A. E. M. De Veirman, "Columnar Microstructures in Magnetron-Sputtered Refractory Metal Thin Films of Tungsten, Molybdenum and W-Ti-(N)," Thin Solid Films, vol. 208, pp. 181-188, 1992.

- [2.22] R. Beyers, "Thermodynamic Considerations in Refractory Metal-Silicon-Oxygen Systems," J. Appl. Phys., vol. 56, no. 1, pp. 147-152, 1984.

- [2.23] Q. Lu, R. Lin, P. Ranade, Y. C. Yeo, X. Meng, H. Takeuchi, T.-J. King, C. Hu, H. Luan, S. Lee, W. Bai, C.-H. Lee, D.-L. Kwong, X. Guo, X. Wang, and T.-P. Ma, "Molybdenum Metal Gate MOS Technology for Post-Sio<sub>2</sub> Gate Dielectrics," in *Int. Elec. Dev. Meet. Digest*, pp. 641-644, 2000.

- [2.24] J. Schaefeer, S. Samavedam, L. Fonseca, C. Capasso, O. Adetutu, D. Gilmer, C. Hobbs, E. Luckowski, R. Gregory, Z.-X. Jiang, Y. Liang, K. Moore, D. Roan, B.-Y. Nguyen, P. Tobin, B. White, "Investigation of Metal Gate Electrodes on HfO<sub>2</sub> Gate Dielectrics," in *Proc. Mat. Res. Symp.*, vol. 811, pp. 137-148, 2004.

- [2.25] T. Fuyuki, T. Furukawa, T. Oka, and H. Matsunami, "Deposition of High-Quality Silicon Dioxide by Remote Plasma CVD Technique," *IEICE Trans. Electron.*, vol. E75-C, no. 9, pp. 1013-1018, 1992.

- [2.26] P. E. Nicollian, W. R. Hunter, and J. C. Hu, "Experimental Evidence for Voltage Driven Breakdown Models in Ultrathin Gate Oxides," in *Int. Reliab. Phys. Symp.*, pp. 7-15, 2000.

- [2.27] H. Takeuchi, M. She, K. Watanabe, and T.-J. King, "Damageless Sputter Deposition for Metal Gate CMOS Technology," in 61th Dev. Res. Conf., pp. 35-36, 2003.

- [2.28] Y. Kuo, "Factors Affecting the Molybdenum Line Slope by Reactive Ion Etching," J. Electrochem. Soc., vol. 137, no. 6, pp. 1907-1911, 1990.

- [2.29] M. Schaepkens, and G. S. Oehrlein, "A Review of SiO<sub>2</sub> Etching Studies in Inductively Coupled Fluorocarbon Plasmas," *J. Electrochem. Soc.*, vol. 148, no. 3, pp. C211-C221, 2001.

- [2.30] Y. Kurogi, and K. Kamimura, "Molybdenum Etching using CCl<sub>4</sub>/O<sub>2</sub> Mixture Gas," *Jpn. J. Appl. Phys.*, vol. 21, no. 1, pp. 168-172, 1982.

- [2.31] CRC handbook of Chemistry and Physics (1985-1986), p. F-178, CRC Press, Inc., Boca Raton, FL, 1985.

- [2.32] R. Smoluchowski, "Anisotropy of the Electronic Work Function of Metals," *Physical Rev.*, vol. 60, pp. 661-674, 1941.

- [2.33] S. Berge, P. O. Gartland, and B. J. Slagsvold, "Photoelectric Work Function of a Molybdenum Single Crystal for the (100), (110), (111), (112), (114), and (332) Faces," Surf. Sci., vol. 43, pp. 275 292, 1974.

- [2.34] P. Ranade, "Advanced Gate Materials and Processes for Sub-70 nm CMOS Technology," *Ph.D Thesis*, University of California, Berkeley, 2002.

- [2.35] R. J. P. Lander, J. C. Hooker, J. P. van Zijl, F. Roozeboom, M. P. M. Maas, Y. Tamminga, R.A.M. Wolters, "A Tunable Metal Gate Work Function using Solid State Diffusion of Nitrogen", in *Proc. European Solid-State Dev. Res. Conf.*, pp. 103-106, 2002.

- [2.36] T. Amada, N. Maeda, and K. Shibahara, "Degradation in a Molybdenum Gate MOS Structure Caused by N+ Ion Implantation for the Work Function Control," in *Proc. Mater. Res. Soc. Symp.*, p.60, 2002.

- [2.37] SRIM simulation (available at <a href="http://www.srim.org">http://www.srim.org</a>)

- [2.38] Q. Lu, R. Lin, P. Ranade, T.-J. King, and C. Hu, "Metal Gate Work Function Adjustment for Future CMOS Technology," in *IEEE VLSI Tech. Symp. Digest*, pp. 45-46, 2001.

- [2.39] G. Qi, W. M. Small, and T. Debroy, "Thermochemistry and Diffusion of Nitrogen in Solid Molybdenum", *Met. Trans. B*, v.22, p. 219, April 1991.

- [2.40] J. H. Evans, and B.L. Eyre, "The Heat of Solution and Diffusivity of Nitrogen in Molybdenum," *Acta Metallurgica*, vol. 17, no. 8, pp. 1109-1115, 1969.

- [2.41] K. T. Ho, M.-A. Nicolet, and D. M. Scott, "Effects of Ion-Implanted Nitrogen Impurities on Molybdenum Silicide Formation," *Thin Solid Films*, vol. 127, pp. 171-179, 1985.

- [2.42] B.D. Cullity, and S.R. Stock, *Elements of X-Ray Diffraction*, 3rd Edit., Prentice Hall, Inc., 2001.

- [2.43] P. Hones, N. Martin, M. Regula, and F. Levy, "Structural and Mechanical Properties of Chromium Nitride, Molybdenum Nitride, and Tungsten Nitride Thin Films," J. Phys. D: Appl. Phys., vol. 36, pp. 1023-1029, 2003.

# **Chapter 3**

# High-k Gate Dielectric Technology

### 3.1 Introduction

Over the past several decades, the successful improvement in CMOS transistor performance and integration of ultra-large scale (ULSI) semiconductor devices has relied on scaling down the silicon dioxide (SiO<sub>2</sub>) or its derivatives (SiO<sub>x</sub>N<sub>y</sub>) gate dielectric. The advantage of primary reasons are that thermally grown amorphous SiO<sub>2</sub> dielectric are low fixed charge densities ( $Q_f$ ) on the order of  $q10^{10}$  cm<sup>-2</sup>, mid-gap interface state densities ( $Q_{it}$ ) of  $\sim q10^{10}$  cm<sup>-2</sup> and a large breakdown electric field over 10 MV/cm [3.1]. Thinner gate oxide increases the drive current of transistors by increasing the areal gate

capacitance and suppresses short channel effects by providing strong gate control of the channel potential.

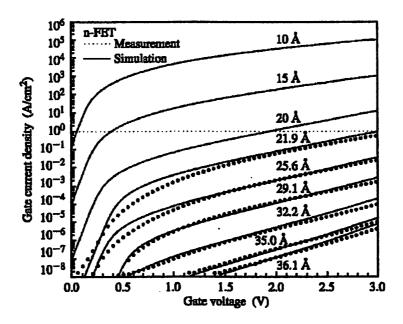

Figure 3.1 Measured and simulated I<sub>G</sub>-V<sub>G</sub> characteristics under inversion conditions of nchannel MOSFETs. The dotted line is indicates the 1 A/cm<sup>2</sup> limit for gate leakage current [3.2]

However, silicon dioxide is not attractive as a gate dielectric when its thickness approaches 1 nm; one of the fundamental issues for scaling of the gate dielectric thickness is the exponential increase in direct tunneling current with decreasing  $SiO_2$  thickness. For example, gate leakage current density can rise to  $0.1 - 10 \text{ A/cm}^2$  at 1.0 V gate voltage for 1.5 - 2 nm thick  $SiO_2$ , as shown in **Figure 3.1** [3.2] This high current can affect the circuit operations and dissipate power. Even though high power

dissipation may be tolerable for high-performance micro-processor applications, this will lead to serious problems for low-power portable applications. Theoretical modeling studies of the SiO<sub>2</sub>/Si interface predicted that the physical thickness of SiO<sub>2</sub> will be fundamentally limited to 0.7 nm due to the overlap of Si-rich interface regions from the silicon channel and the poly-silicon gate, causing an effective electrical short through the dielectric [3.3]. However, the practical scaling limit of SiO<sub>2</sub> as the gate dielectric will be 1.2 nm mainly due to interface roughness, degraded transistor performance, dielectric reliability, etc. [3.4, 3.5, 3.6].

The reduction of the gate leakage current density is, therefore, the most compelling reason for replacing  $SiO_2$ -based dielectrics. For a given CMOS technology generation, devices are designed with a specific areal gate capacitance, which is a function of the dielectric constant (k) and physical thickness  $(T_{ox})$ . In order to decrease the leakage current while maintaining the same gate capacitance (or equivalent oxide thickness, EOT), a thicker film with a higher dielectric constant should be adopted. Many materials appear favorable as an alternative gate dielectric, but very few materials

are promising with respect to the key basic material properties, compatibility with CMOS processes and integration, as will be discussed in the following section.

#### 3.2 Material Selection for Gate Dielectric

Several materials have been investigated for replacing silicon dioxide or silicon nitride as the gate dielectric for sub-65nm CMOS technology generations [3.7]; these include the simple metal oxides such as tantalum oxide (Ta<sub>2</sub>O<sub>5</sub>) [3.8], titanium oxide (TiO<sub>2</sub>) [3.9], lanthanum oxide (La<sub>2</sub>O<sub>3</sub>) [3.10], yttrium oxide (Y<sub>2</sub>O<sub>3</sub>) [3.11], cerium oxide (CeO<sub>2</sub>) [3.12], aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) [3.13], zirconium oxide (ZrO<sub>2</sub>) [3.14], and hafnium oxide (HfO<sub>2</sub>) [3.15, 3.16], and the ferroelectric materials such as barium strontium titanate (BST) [3.17]. As a promising candidate gate dielectric, however, the new materials should demonstrate the key basic material properties including high permittivity (or dielectric constant), large potential barrier heights to prevent tunneling current, thermodynamic stability in contact with silicon, good interface quality and film morphology [3.18]. In addition, the high-k dielectric should be compatible with the gate electrode material(s) and CMOS process integration without compromising device reliability and circuit performance [3.19].

To minimize the gate tunneling current, it seems reasonable to adopt a material whose dielectric constant (k) is as high as possible, allowing an increase in the high-k film thickness for the same  $SiO_2$  equivalent oxide thickness. However, if the high-k dielectric thickness approaches the gate length, fringing fields from source/drain regions to the channel becomes significant, resulting in weak control over the channel potential, hence compromising short channel behavior; this is the so called fringing-induced-barrier-lowering (FIBL) effect [3.20]. Intensive simulation study [3.21] predicted that

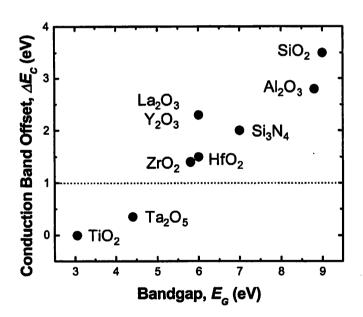

Figure 3.2 Theoretically calculated conduction band barrier height ( $\Delta E_C$ )  $\nu s$ . energy bandgap ( $E_G$ ). In general, a larger bandgap leads to a larger conduction band barrier height [3.3].

when the ratio of dielectric thickness to gate length  $(T_{ox}/L_G)$  is great than 1/5, more than 10% degradation in subthreshold swing occurs, ruling out the use of very high-k (> 40) materials such as TiO<sub>2</sub> and BST.

Together with the high dielectric constant, the conduction barrier height ( $\Delta E_C$ ) should be high enough to prevent a significant tunneling current because both the thickness and height of the barrier have an exponential influence upon the tunneling leakage current. Barrier heights have been theoretically calculated for several potential high-k materials [3.22]. In general, a larger bandgap  $(E_G)$  leads to a larger conduction band offset ( $\Delta E_C$ ), as shown in Figure 3.2. However, for most high-k dielectrics, the bandgap is inversely proportional to the dielectric constant [3.23]. Hence, even if there is a significant reduction of tunneling leakage current due to the increased thickness, this may be compensated by the reduction of the bandgap, or barrier height. Therefore, a high-k dielectric, whose conduction band offset ( $\Delta E_C$ ) is smaller than 1.0 eV, may not replace the silicon dioxide [3.22]. Identifying a dielectric that provides even a moderate increase in dielectric constant, but that also produces a sufficiently large tunneling barrier height is indispensable. La<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, and HfO<sub>2</sub> offer relatively high dielectric constant and conduction band-offset.

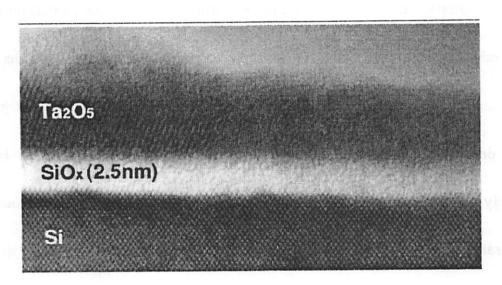

For very thin gate dielectrics, the interface with silicon determines the overall electrical properties. Thermodynamic stability in direct contact with silicon during CMOS fabrication processes is therefore indispensable [3.24]. Most high-k metal oxides including Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub> are not thermally stable on silicon; reacting with silicon to form an undesirable SiO<sub>2</sub> or medium-k interfacial layer, or metal silicide [3.25, 3.26], as shown in Figure 3.3. The underlying SiO<sub>2</sub> or interfacial layer limits the scaling of the equivalent oxide thickness (EOT). For example, if 1.5 nm EOT is required and 1.0 nm SiO<sub>2</sub> is formed at the interface, only 0.5 nm remains for the high-k material, making the use of high-k material ineffective due to the significant increase in tunneling leakage

Figure 3.3 An example of thermodynamic instability of Ta<sub>2</sub>O<sub>5</sub> in direct contact with silicon. A reaction at the interface results in the formation of an undesirable thin SiO<sub>2</sub> layer [3.26]

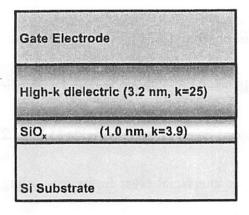

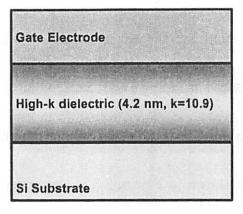

current, as illustrated in Figure 3.4.

Figure 3.4 Comparison of stacked gate dielectric and single layer gate dielectrics in transistor. Both gate dielectrics result in the same equivalent oxide thickness, EOT = 1.5 nm. Ultimate scaling of EOT can be limited due to the interface layer formation.

Glassy phase (amorphous) gate dielectrics during CMOS fabrication are very desirable, because they will have isotropic electrical properties and not have grain boundaries, which typically serve as leakage current paths [3.18]. In addition, grain size and orientation changes lead to significant variations in dielectric constant. However, nearly all metal oxides under investigation form polycrystalline films upon source/drain annealing, which may necessitate an intentionally grown amorphous interfacial layer to reduce the leakage current. It is worthwhile to note that despite relatively low dielectric

constant (9~15), Al<sub>2</sub>O<sub>3</sub> [3.27], ZrSi<sub>x</sub>O<sub>y</sub> [3.28] and HfSi<sub>x</sub>O<sub>y</sub> [3.29] appears promising because their morphology remains amorphous during high temperature annealing.

Low midgap interface state density  $(Q_{it})$  and fixed charge density  $(Q_f)$  are crucial to meet the performance requirements of nanoscale CMOS transistors; channel carrier mobilities, threshold voltage shift, and subthreshold swing can be greatly affected. This will lead to the need for a sufficiently high quality interface with the silicon channel, challenging for high-k dielectrics as compared to SiO<sub>2</sub> [3.19].

Thus, it may be appropriate to replace  $SiO_2$  gate dielectric with a material which provides only moderate increase (15 – 30) in dielectric constant, but also provides a large tunneling barrier height (> 1.0 eV) and high-quality ( $Q_{it}$ ,  $Q_f < 10^{11}$  cm<sup>-2</sup>) interface to the silicon channel.

### 3.3 HfO<sub>2</sub> Gate Dielectric

Hafnium dioxide (HfO<sub>2</sub>) has shown much promise as a candidate to replace SiO<sub>2</sub>, as discussed in Chapter 3.2; it has a high dielectric constant ( $k \sim 25$ ) with the bandgap of 5.7 eV, large energy-band offsets ( $\Delta E_C \sim 1.5$  eV), thermodynamic stability in direct contact with silicon substrate, and negligible frequency dispersion [3.22, 3.30, 3.31,

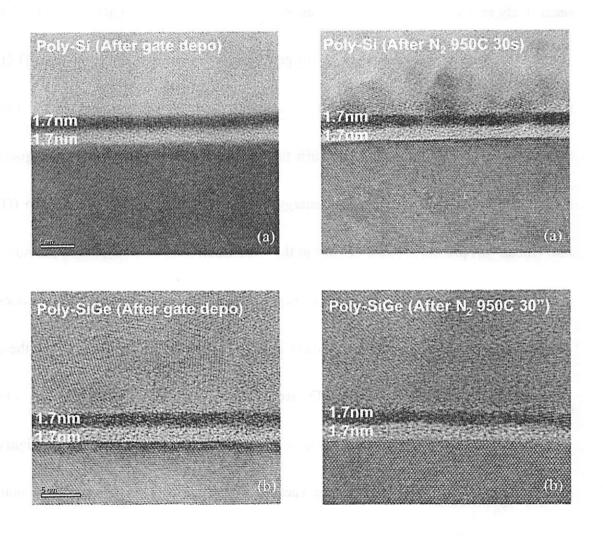

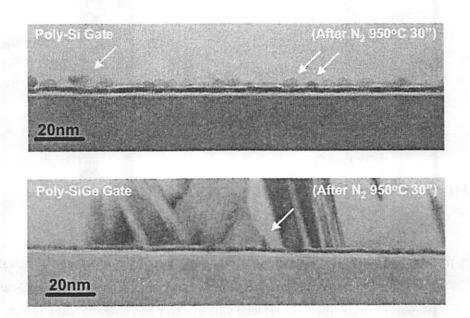

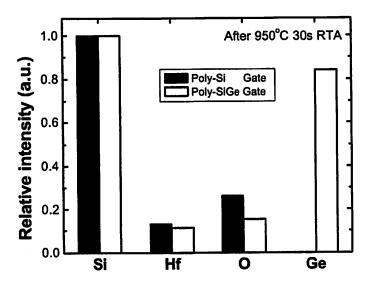

3.32]. For the gate electrode, polycrystalline silicon (poly-Si) has been the preferred material because it offers simplicity of process integration. However, when poly-Si is used as the gate material together with HfO<sub>2</sub> as the gate dielectric, increases in equivalent oxide thickness (EOT) and gate leakage current can result upon high-temperature annealing (e.g. during source/drain dopant activation) due to interfacial layer formation at the HfO<sub>2</sub>/Si interface [3.33]. Recently, polycrystalline silicon-germanium (poly-SiGe) has received much attention as an alternative gate-electrode material, because it alleviates gate depletion and boron penetration issues, and yields thinner EOT for HfO<sub>2</sub> gate dielectric [3.34, 3.35, 3.36].

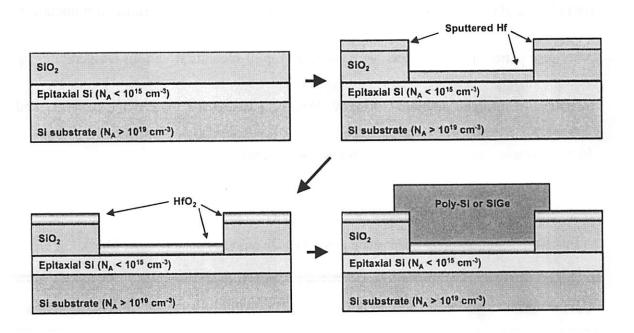

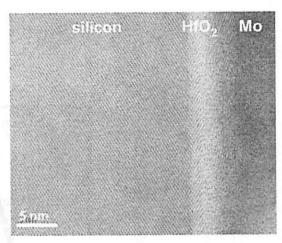

#### 3.3.1 Fabrication of HfO<sub>2</sub> MOS Capacitors

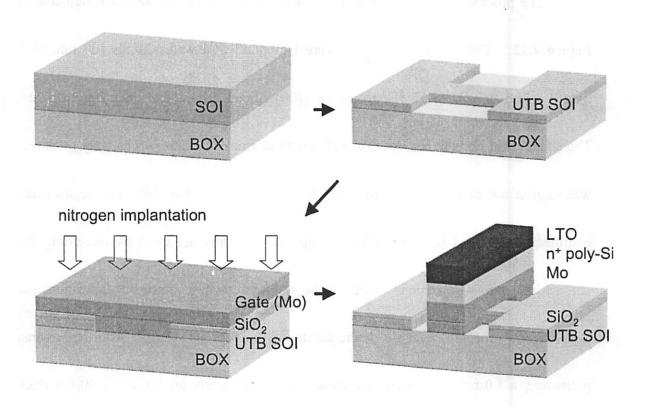

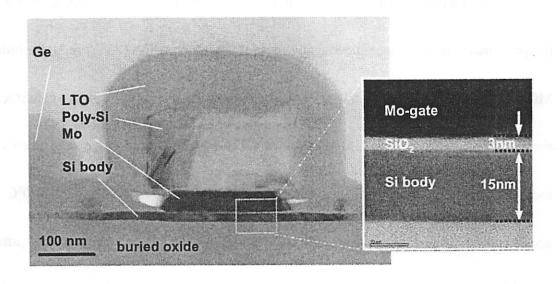

MOS capacitors were fabricated on epitaxially grown silicon (p-type dopant concentration (N<sub>A</sub>) below 10<sup>15</sup> cm<sup>-3</sup>) on heavily doped p+ silicon wafers. Figure 3.5 summarizes the fabrication sequences for HfO<sub>2</sub> MOS capacitors. 100 nm thick SiO<sub>2</sub> was thermally grown in wet oxidation furnace at 950°C and patterned to define the device active regions. Pure Hf was then deposited by DC magnetron sputtering at 300°C and 210 W power (base pressure of 5x10<sup>-8</sup> Torr), and rapid thermal annealing at 700°C, 30s in

Figure 3.5 Fabrication sequences for HfO<sub>2</sub> gate dielectric MOS capacitors.

oxygen ambient was used to form HfO<sub>2</sub>. It is worth noting that the wafers were precleaned in a diluted HF solution to remove the chemical oxide and no intentional interfacial layer was grown before HfO<sub>2</sub> formation. Afterwards, the gate electrode materials (either poly-Si or Si<sub>0.75</sub>Ge<sub>0.25</sub>) were deposited in a conventional low-pressure chemical vapor deposition (LPCVD) furnace at 550°C, using either SiH<sub>4</sub> or Si<sub>2</sub>H<sub>6</sub> as the gaseous Si source, and GeH<sub>4</sub> as the gaseous Ge source. In order to minimize gate depletion, all the gate films were *in-situ* n+ doped using phosphine (PH<sub>3</sub>). The gate deposition conditions are summarized in **Table 3.1**. Shorter deposition times were used

for poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> and Si<sub>2</sub>H<sub>6</sub>-based poly-Si in order to achieve the same film thickness. After gate patterning, the wafers were annealed for 30 seconds at various temperatures up to 950°C in nitrogen ambient. Finally, forming gas anneals were done at 600°C and 400°C sequentially to improve the interface state density [3.37].

Table 3.1 Summary of gate deposition process conditions (100 nm thick gate films).

| Gate material          | Poly-Si          | . Poly-Si                      | Poly-Si <sub>0.75</sub> Ge <sub>0.25</sub> |

|------------------------|------------------|--------------------------------|--------------------------------------------|

| Precursor gas          | SiH <sub>4</sub> | Si <sub>2</sub> H <sub>6</sub> | SiH <sub>4</sub> + GeH <sub>4</sub>        |

| Deposition temperature | 550°C            | 550°C                          | 550°C                                      |

| Deposition time        | 270 min          | 7.5 min                        | 54 min                                     |

#### 3.3.2 Experimental Results and Discussion

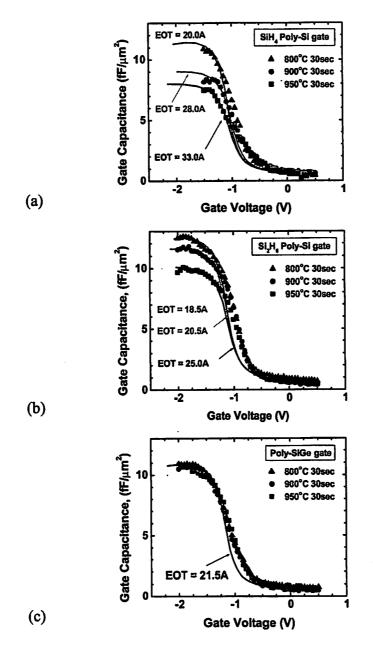

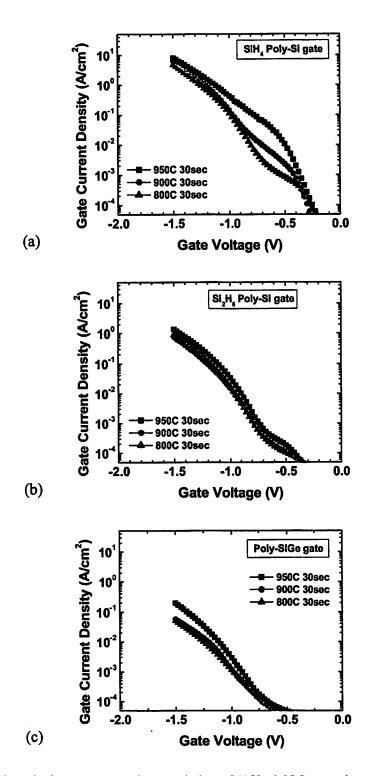

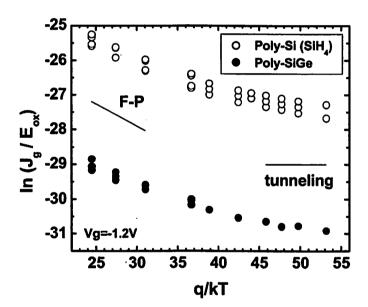

Figure 3.6 shows the measured high-frequency C-V characteristics of the HfO<sub>2</sub> capacitors. For the poly-Si gated capacitors, the capacitance decreases with increasing the subsequent annealing temperature. This is more pronounced for SiH<sub>4</sub>-based poly-Si

gated capacitors ( $\Delta EOT = 1.3$ nm) compared to Si<sub>2</sub>H<sub>6</sub>-based poly-Si gated capacitors ( $\Delta EOT = 0.65$ nm).

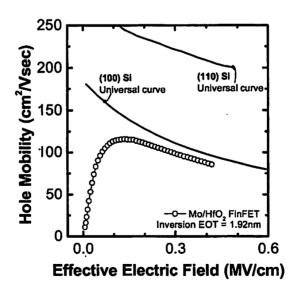

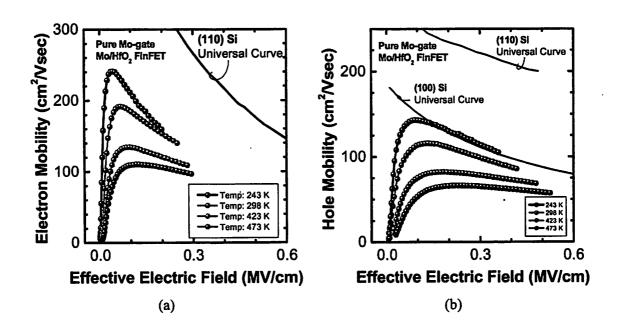

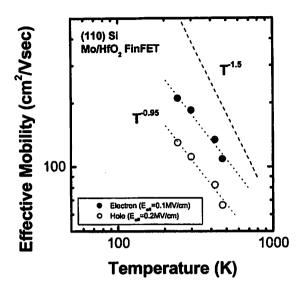

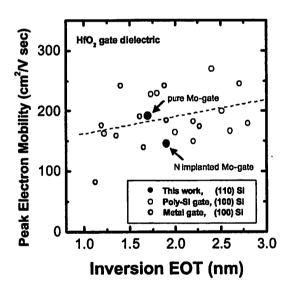

Figure 3.6 High-frequency (100 KHz) C-V curves for HfO<sub>2</sub> MOS capacitors with (a) poly-Si gate deposited using SiH<sub>4</sub>, (b) poly-Si gate deposited using Si<sub>2</sub>H<sub>6</sub>, and (c) poly-Si<sub>0.75</sub>Ge<sub>0.25</sub> gate. The solid lines shown were obtained from quantum-mechanical simulation and used to extract the EOT values as indicated.