Copyright © 2004, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## DESIGN FLOW FOR DEEP SUB-MICRON INTEGRATED CIRCUITS

-

by

Fan Mo

Memorandum No. UCB/ERL M04/9

· · · ·

20 January 2004

## DESIGN FLOW FOR DEEP SUB-MICRON INTEGRATED CIRCUITS

by

Fan Mo

Memorandum No. UCB/ERL M04/9

20 January 2004

## **ELECTRONICS RESEARCH LABORATORY**

.

College of Engineering University of California, Berkeley 94720 Design Flow for Deep Sub-Micron Integrated-Circuits

by

### Fan Mo

B.S. (Fudan University, China) 1996 M.S. (Fudan University, China) 1999

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy in

Engineering-Electrical Engineering and Computer Sciences

in the

#### GRADUATE DIVISION

of the

### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Robert K. Brayton, Chair Professor Alberto Sangiovanni-Vincentelli Professor Alper Atamturk

Fall 2003

## Design Flow for Deep Sub-Micron Integrated-Circuits

Copyright 2003

by

Fan Mo

.

### Abstract

Design Flow for Deep Sub-Micron Integrated-Circuits

by

Fan Mo

### Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Robert K. Brayton, Chair

Regularity is a feature, which can provide better guarantees that the layout designed by a CAD tool is replicated in the fabrication. As the limits of the maskmaking system (finite aperture of projection) are reached with smaller geometries, the actual layout patterns on the wafer differ from that produced by a CAD tool. Although pre-distortion can be added to offset some of the real distortions, the number of layout patterns generated by a conventional design flow can make this task take an unreasonable amount of time and generate an enormous data set. Beyond what optimal pre-distortion could do, regular circuit and interconnection structures can reduce variations further. Another motivation for using regularity is the timing closure problem, which arises because the design flow is sequential; early steps need to predict what the later steps will do. Inaccurate prediction leads to wrong decisions, which can only be discovered later, making design iteration necessary. Preventing such iterations is difficult, but use of regular structures, can make estimation much more accurate.

The following developments have been made to implement a timing-driven Module-Based chip design flow: (1) new regular circuit structures and their design methodologies, (2) a new integrated placement and routing algorithm that simplifies the standard-cell physical design, (3) a new block-level placement and routing algorithm with buffer insertion and (4) a multi-version approach allowing each module to carry several versions that can be selected by the block-level physical design algorithm. Test results show that our design flow can reach timing closure much faster than the Physical Synthesis flow and achieve shorter clock cycle.

> Professor Robert K. Brayton Dissertation Committee Chair

# **Table of Contents**

| Chapter 1. Introduction                    | 1  |

|--------------------------------------------|----|

| 1.1. The Deep Sub-Micron IC Design         | 1  |

| 1.2. Outline of the Thesis                 | 3  |

|                                            |    |

| Chapter 2. Preliminaries                   | 5  |

| 2.1. Overview                              | 5  |

| 2.2. CMOS Technology                       | 5  |

| 2.2.1. Transistors                         | 5  |

| 2.2.2. Gates                               | 8  |

| 2.2.3. CMOS storage components             | 15 |

| 2.2.4. Interconnections                    | 16 |

| 2.3. IC Design and System-On-a-Chip        | 25 |

| 2.3.1. System and constraints              | 25 |

| 2.3.2. Design styles                       | 30 |

| 2.3.3. System-On-a-Chip                    | 32 |

| 2.4. Design Automation                     | 33 |

| 2.5. Challenges in the Deep Sub-Micron Era | 36 |

| 2.5.1. Deep Sub-Micron challenges          | 37 |

| 2.5.2. Dealing with the DSM challenges     | 42 |

| 2.6. Summary                               | 45 |

|                                            |    |

|                                            |    |

| Chapter 3. | Circuit Structures | 47 |

|------------|--------------------|----|

|------------|--------------------|----|

| 3.1. Overview                                                  | 47  |

|----------------------------------------------------------------|-----|

| 3.2. Standard-cell                                             | 48  |

| 3.2.1. The structure and usage of the standard-cell            | 49  |

| 3.2.2. Existing design methodology for the standard-cell       | 52  |

| 3.2.3. An Integrated Standard-cell Physical Design             | 58  |

| 3.2.4. Summary of the standard-cell structure                  | 94  |

| 3.3. PLA                                                       | 95  |

| 3.4. Network of PLAs                                           | 100 |

| 3.5. River PLA                                                 | 102 |

| 3.5.1. Overview                                                | 102 |

| 3.5.2. The structure of the RPLA                               | 105 |

| 3.5.3. The design methodology                                  | 110 |

| 3.5.4. Experimental results                                    | 122 |

| 3.5.5. Summary                                                 | 131 |

| 3.6. Whirlpool PLA                                             | 132 |

| 3.6.1. The circuit structure of the WPLA                       | 133 |

| 3.6.2. Doppio-ESPRESSO                                         | 136 |

| 3.6.3. Experimental results                                    | 155 |

| 3.6.4. Summary                                                 | 167 |

| 3.7. Checkerboard                                              | 169 |

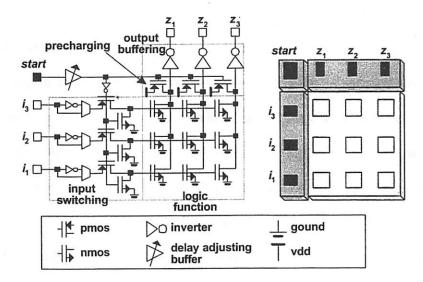

| 3.7.1. The structure of Checkerboard and its dynamic operation | 171 |

| 3.7.2. The algorithm                                           | 181 |

| 3.7.3. Experimental results                                    | 194 |

| 3.7.4. Summary and discussion                                  | 198 |

| 3.8. Comparison of the Structures                              | 200 |

|                                                                |     |

| Chapter 4. | Block Level Placement and Routing                                               | 205 |

|------------|---------------------------------------------------------------------------------|-----|

|            | 4.1. Overview                                                                   | 205 |

|            | 4.1.1. Formulation of the integrated placement and routing                      | 206 |

|            | 4.1.2. Heuristic approaches to the integrated block-level placement and routing | 218 |

|            | 4.2. The Fishbone Scheme                                                        | 219 |

|            | 4.2.1. An overview of the Fishbone scheme                                       | 224 |

|            | 4.2.2. The basics of the Fishbone routing                                       | 225 |

|            | 4.2.3. Interval packing for branches and trunks                                 | 234 |

|            | 4.2.4. I/O-pins                                                                 | 239 |

|            | 4.2.5. The Fishbone placement and routing flow                                  | 242 |

|            | 4.2.6. Experimental results                                                     | 245 |

|            | 4.2.7. Summary of the Fishbone scheme                                           | 257 |

|            | 4.3. Fishbone with Buffer Insertion                                             | 259 |

|            | 4.3.1. The buffers                                                              | 261 |

|            | 4.3.2. Buffer insertion                                                         | 265 |

|            | 4.3.3. The Fishbone-B physical design flow                                      | 273 |

|            | 4.3.4. Experimental results                                                     | 275 |

|            | 4.3.5. Summary of the Fishbone-B                                                | 281 |

|            | 4.4. Summary                                                                    | 282 |

|            |                                                                                 |     |

| Chapter 5. | The Design Flow                                                                 | 285 |

|            | 5.1. Overview                                                                   | 285 |

|            | 5.2. Basics of the Design Flow                                                  | 286 |

|            | 5.2.1. Modules and paths                                                        | 287 |

•

.

•

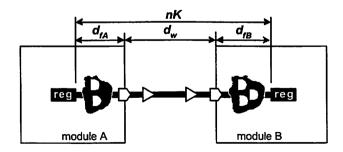

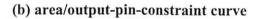

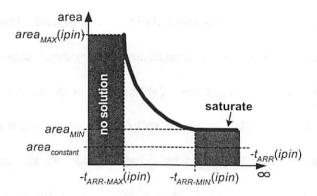

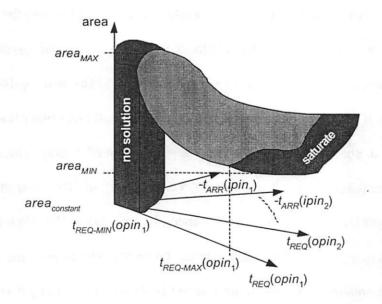

| 5.2.2. Timing constraints for the modules         | 290 |

|---------------------------------------------------|-----|

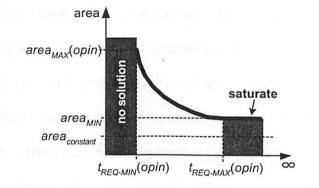

| 5.2.3. The relation of module area and constraint | 295 |

| 5.2.4. The problems and possible solutions        | 298 |

| 5.3. The Physical Synthesis Flow                  | 300 |

| 5.4. The Module-Based Design Flow                 | 307 |

| 5.4.1. Overview                                   | 307 |

| 5.4.2. The version of soft module                 | 309 |

| 5.4.3. The physical design stage                  | 320 |

| 5.4.4. Summary of the Module-Based design flow    | 321 |

| 5.5. Comparison of the Two Flows                  | 323 |

| 5.5.1. Generation of the testing examples         | 323 |

| 5.5.2. The 0.18-micron technology                 | 326 |

| 5.5.3. The testing circuits                       | 327 |

| 5.5.4. The comparison                             | 328 |

| 5.5.5. Case study: A1                             | 333 |

| 5.6. Summary                                      | 336 |

| Chapter 6. Conclusion                             | 339 |

.

1

| Bibliography | ••••••••••••••••••••••••••••••••••••••• | 345 |

|--------------|-----------------------------------------|-----|

| • • •        |                                         |     |

# **List of Figures**

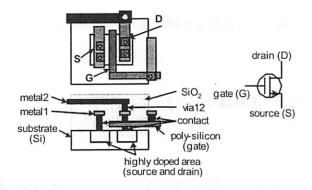

| 2.1.  | A CMOS transistor                                                | 6  |

|-------|------------------------------------------------------------------|----|

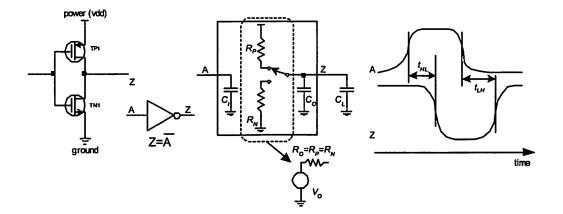

| 2.2.  | CMOS inverter                                                    | 9  |

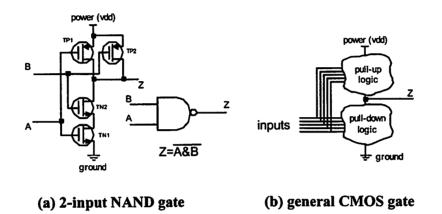

| 2.3.  | CMOS gate                                                        | 11 |

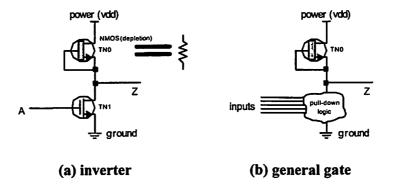

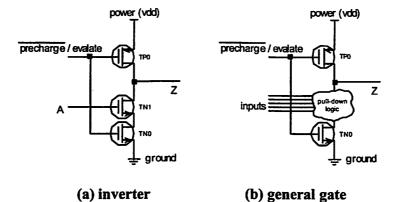

| 2.4.  | NMOS gate                                                        | 12 |

| 2.5.  | Dynamic gate                                                     | 14 |

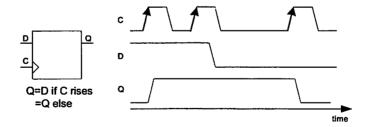

| 2.6.  | Register and its operation                                       | 15 |

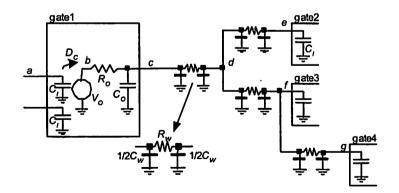

| 2.7.  | Gate delay and wire delay models                                 | 16 |

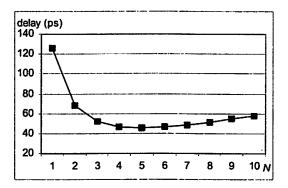

| 2.8.  | Delay versus number of wire segments (N) evenly split by buffers | 22 |

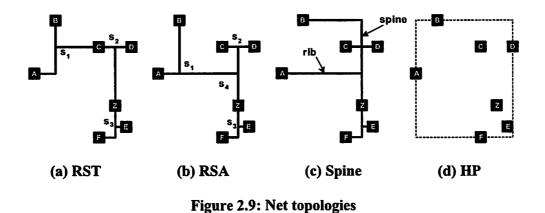

| 2.9.  | Net topologies                                                   | 23 |

| 2.10. | A state machine                                                  | 26 |

| 2.11. | Combinational paths                                              | 27 |

| 2.12. | Design constraints                                               | 29 |

| 2.13. | Three design styles                                              | 30 |

| 2.14. | A simple design flow                                             | 34 |

| 2.15. | A timing-driven design flow                                      | 35 |

| 2.16. | An example of the timing closure problem                         | 38 |

| 2.17. | Another example of the timing closure problem                    | 40 |

| 3.1.  | A typical standard-cell (three-input NOR)                        | 50 |

| 3.2.  | The usage of the standard-cells                                  | 50 |

| 3.3.  | The standard-cell design flow                                    | 53 |

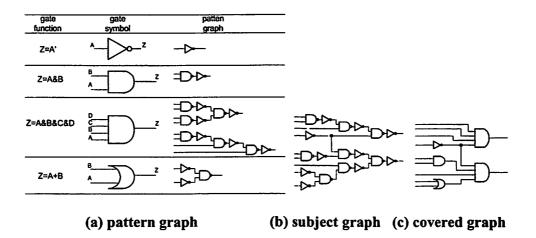

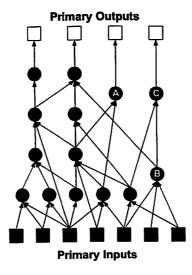

| 3.4.  | An example of the technology mapping                             | 54 |

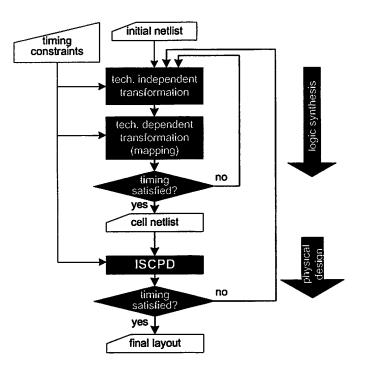

| 3.5.  | The ISCPD in the standard-cell design flow                       | 59 |

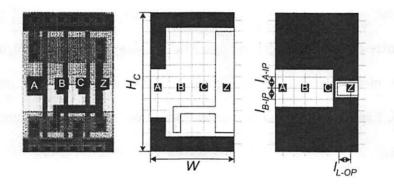

| 3.6. The typical layout of a cell and its views               | 62    |

|---------------------------------------------------------------|-------|

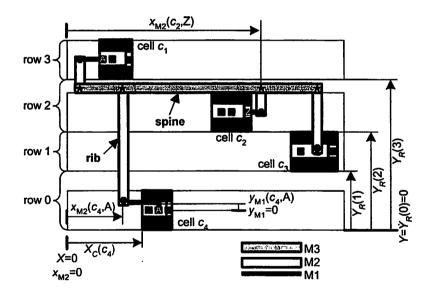

| 3.7. The spine topology and the notations                     | 63    |

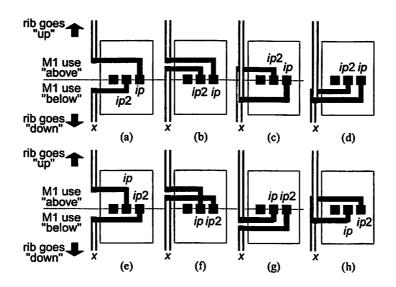

| 3.8. Connections of the input pins and placement of the cell  | 67    |

| 3.9. The M2_Sharing_Rule                                      | 70    |

| 3.10. The operation of <i>All_Cells(</i> )                    | 75    |

| 3.11. I/O Connections                                         | 78    |

| 3.12. The bi-partitioning                                     | 79    |

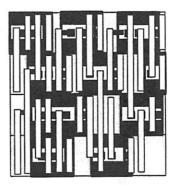

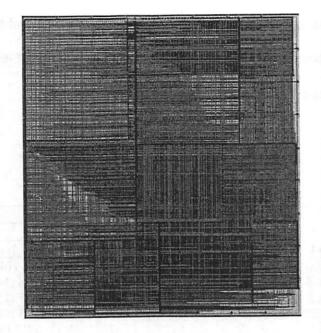

| 3.13. Layout pictures of C7522. A five pin net is highlighted | 92    |

| 3.14. The NOR array                                           | 96    |

| 3.15. The PLA                                                 | 99    |

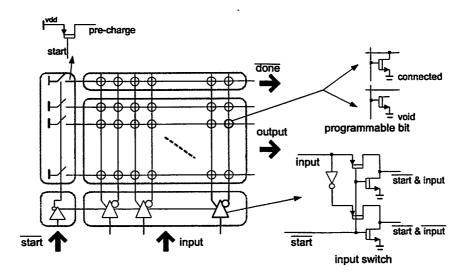

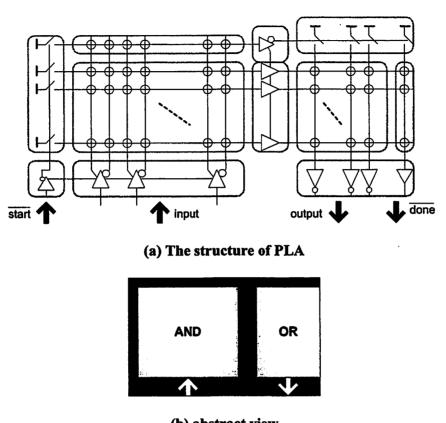

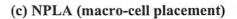

| 3.16. The NPLA                                                | 101   |

| 3.17. The structure of the River PLA                          | 106   |

| 3.18. The consume/provide diagram                             | 108   |

| 3.19. An example of the node level flexibilities              | 112   |

| 3.20. An net ordering example                                 | 116   |

| 3.21. An example of net shifting                              | 119   |

| 3.22. An example of node collapsing                           | 121   |

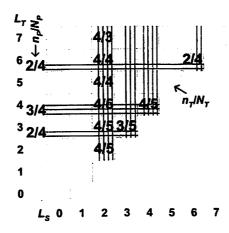

| 3.23. Normalized area/delay                                   | 127   |

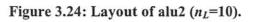

| 3.24. Layout of alu2 ( $n_L$ =10)                             | 127   |

| 3.25. The Whirlpool PLA structure                             | . 134 |

| 3.26. Abstract view of a WPLA                                 | 134   |

| 3.27. The signal labeling                                     | 137   |

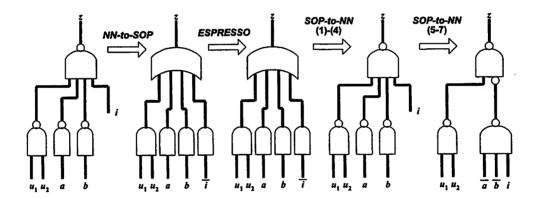

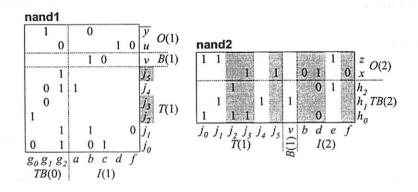

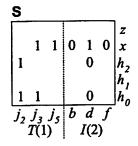

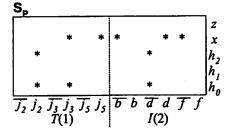

| 3.28. An example of the SOP-to-NN transformation              | 148   |

| 3.29. Normalized area/delay curves                            | 164   |

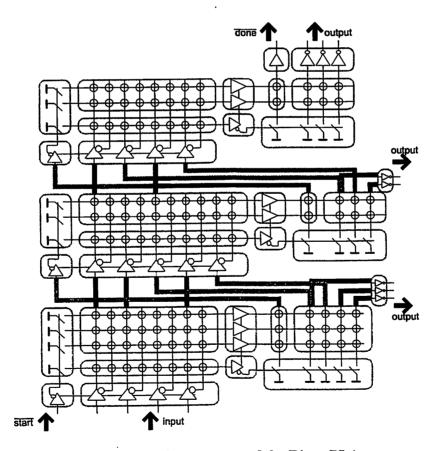

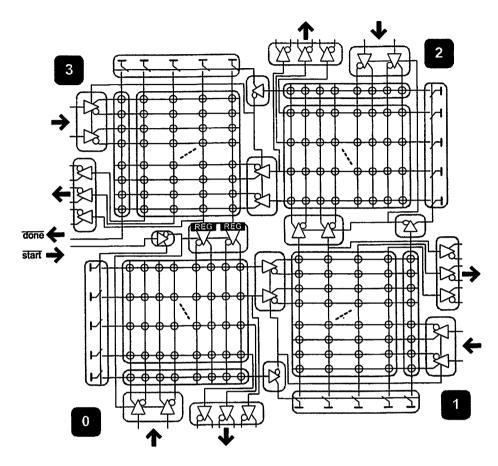

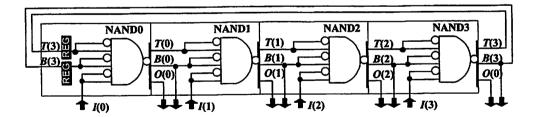

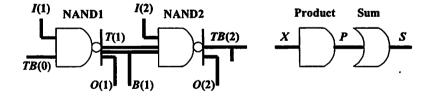

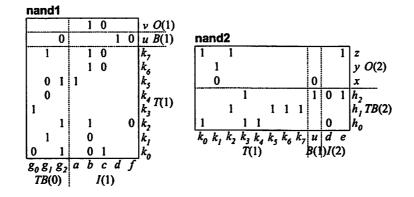

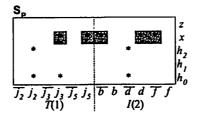

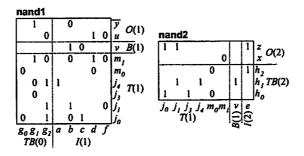

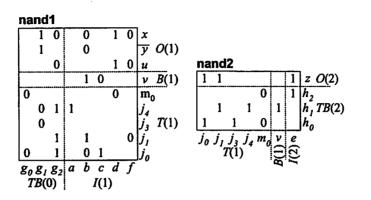

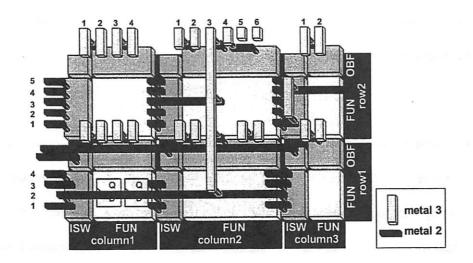

| 3.30. The GOR block of the Checkerboard                       | 171   |

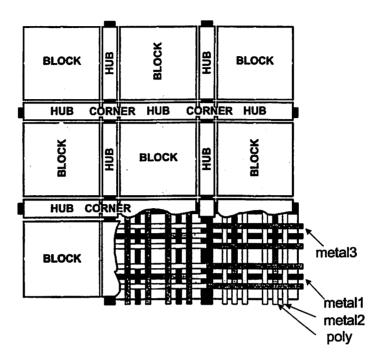

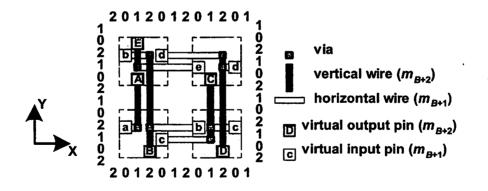

| 3.31. The interconnection system of the Checkerboard          | 173   |

.

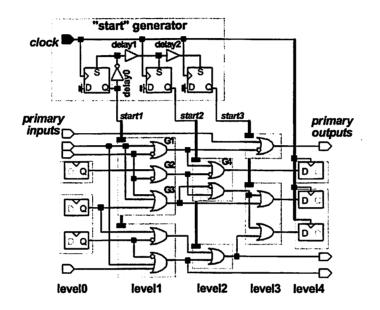

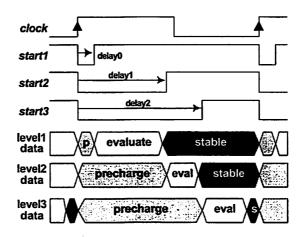

| 3.32. | The dynamic operation of the Checkerboard             | 176   |

|-------|-------------------------------------------------------|-------|

| 3.33. | The timing of the dynamic operation                   | 177   |

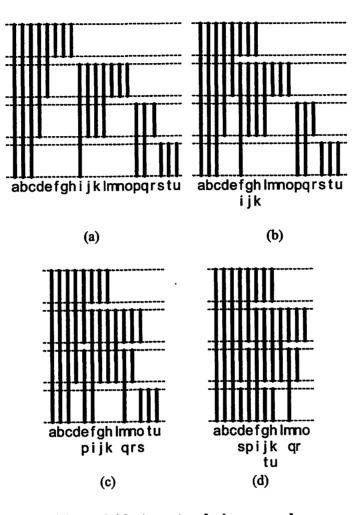

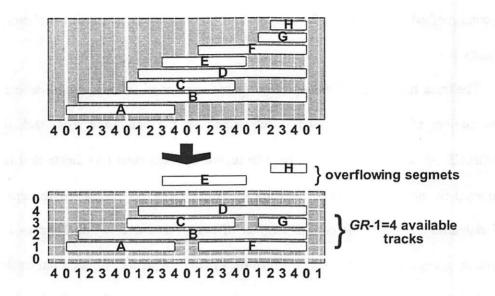

| 3.34. | Interval packing example                              | 187   |

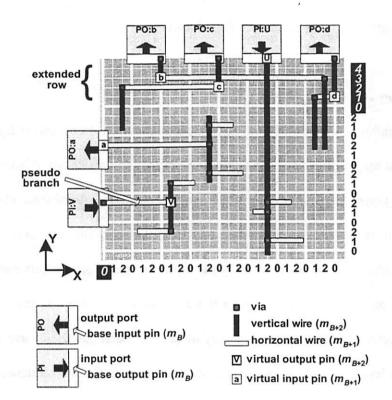

| 3.35. | The planning of the I/O connections                   | 189   |

| 3.36. | The planning of the "start" signals and clock         | 191   |

| 3.37. | Examples of local connections                         | 193   |

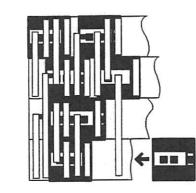

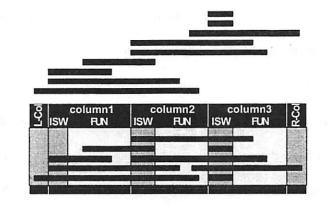

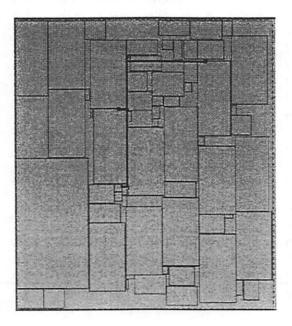

| 3.38. | The Checkerboard layout of mm9a(10)                   | 198   |

| 3.39. | Via-Programmable Checkerboard                         | 200   |

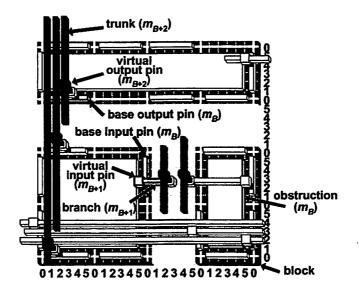

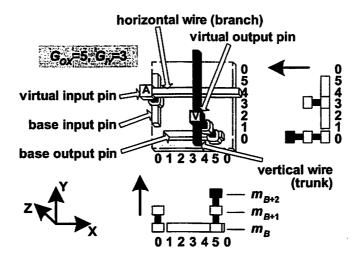

| 4.1.  | The base/virtual pin pair of the Fishbone scheme      | . 225 |

| 4.2.  | The base/virtual pin pair of the Fishbone scheme      | 228   |

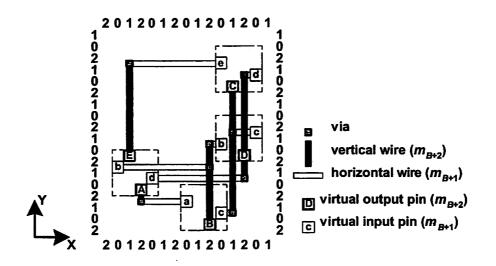

| 4.3.  | Basic Fishbone scheme (GR=3) connecting 4 blocks      | 231   |

| 4.4.  | Dense Fishbone scheme (GR=3) connecting 4 blocks      | 233   |

| 4.5.  | An interval packing example                           | 238   |

| 4.6.  | The I/O-pins and their connections.                   | 240   |

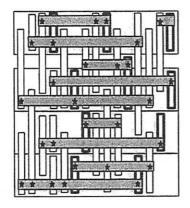

| 4.7.  | The layout of "playout"                               | 256   |

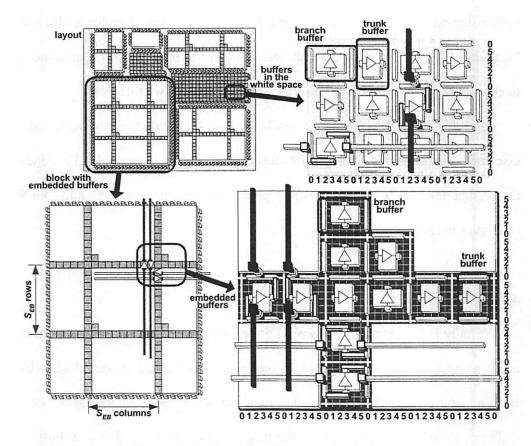

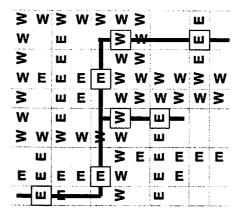

| 4.8.  | The W-buffers and E-buffers                           | 262   |

| 4.9.  | The bit map of the available buffers                  | 266   |

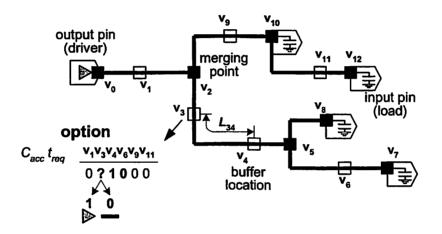

| 4.10. | Applying van Ginneken's algorithm on a buffering tree | 268   |

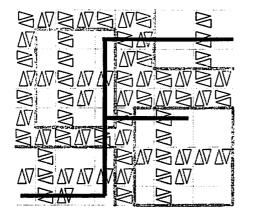

| 4.11. | The layout of ibmB10 (W-buffers only)                 | 280   |

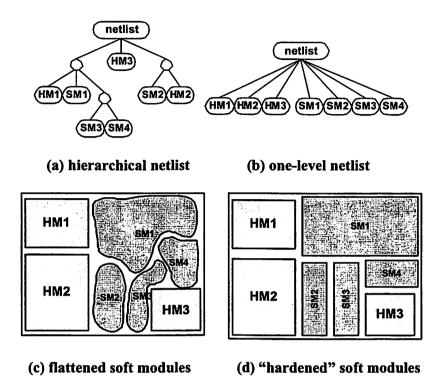

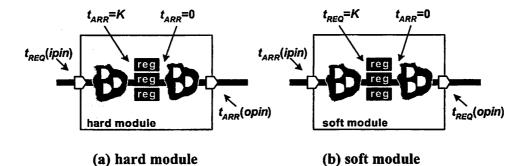

| 5.1.  | Hard modules and soft modules                         | 288   |

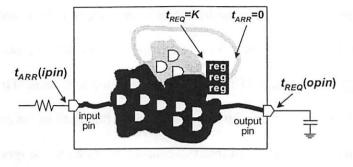

| 5.2.  | The path delay                                        | 288   |

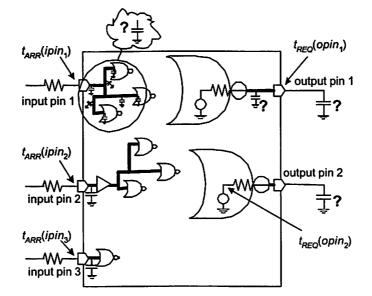

| 5.3.  | The timing constraints set on the pins of the module  | 291   |

| 5.4.  | The arrival and required times, revisited             | 292   |

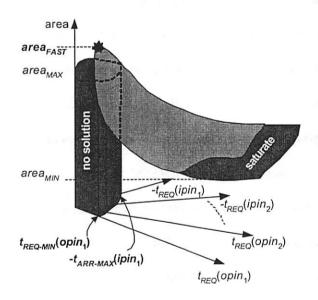

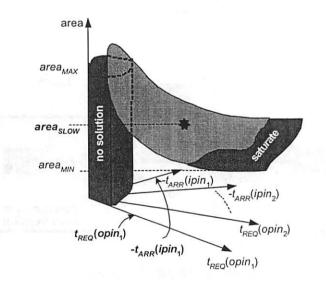

| 5.5.  | The area/constraint curve                             | 294   |

| 5.6.  | The area/constraints surface for a module             | 296   |

| 5.7.  | Non-monotonic area/constraint curve                   | 297   |

.

| 5.8. An example of the Physical Synthesis                           | 300 |

|---------------------------------------------------------------------|-----|

| 5.9. The Physical Synthesis flow                                    | 301 |

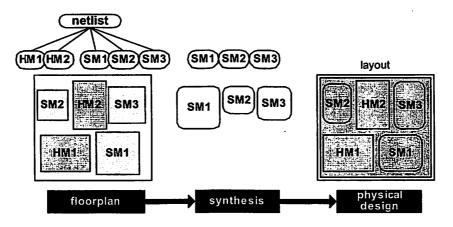

| 5.10. Overview of the Module-Based design flow                      | 307 |

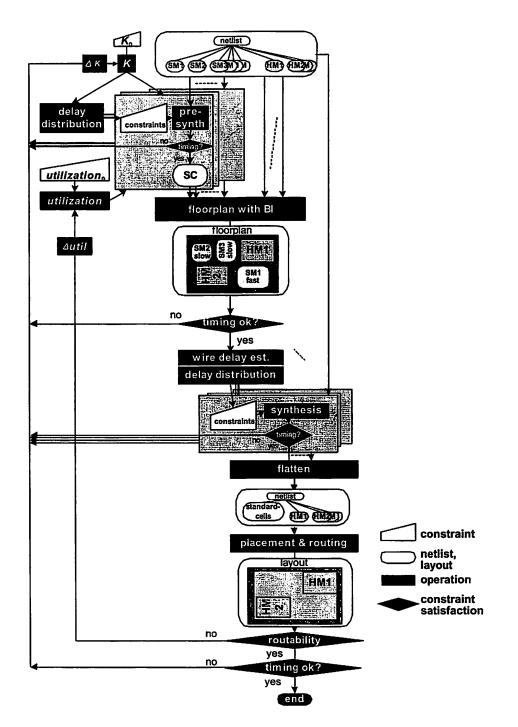

| 5.11. The Module-Based design flow                                  | 308 |

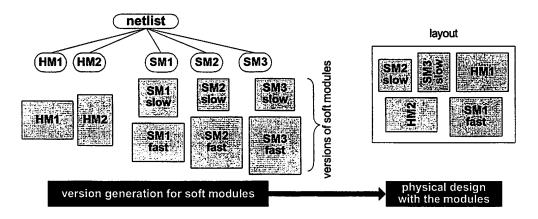

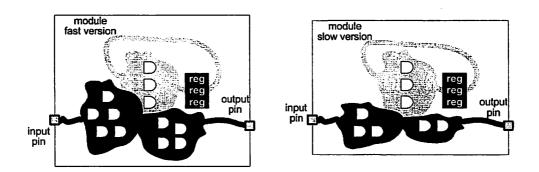

| 5.12. The versions of a soft module                                 | 309 |

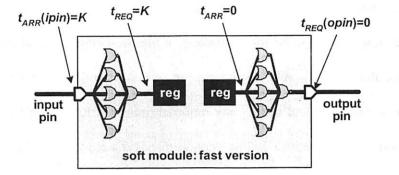

| 5.13. The generation of the fast version                            | 311 |

| 5.14. The generation of the slow version                            | 313 |

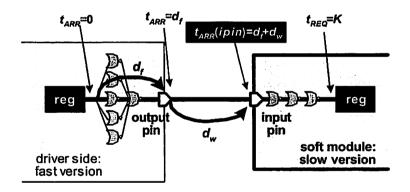

| 5.15. Deriving the constraints for the soft slow version            | 315 |

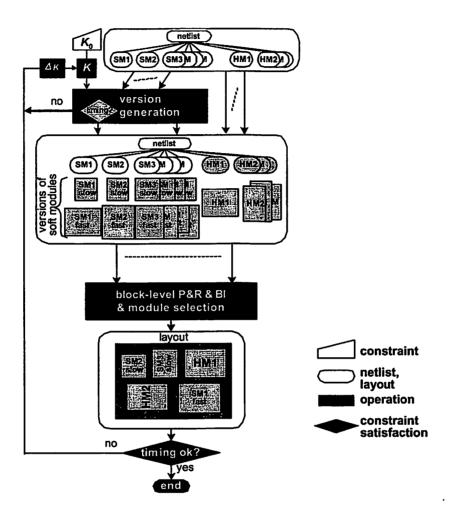

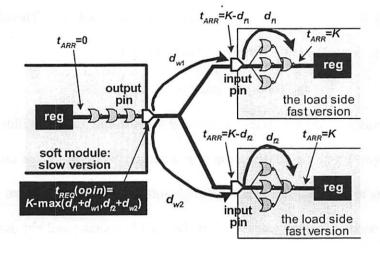

| 5.16. The process of the version generation                         | 318 |

| 5.17. The pin matching                                              | 324 |

| 5.18. Comparison of the two flows (Module-Based/Physical Synthesis) | 331 |

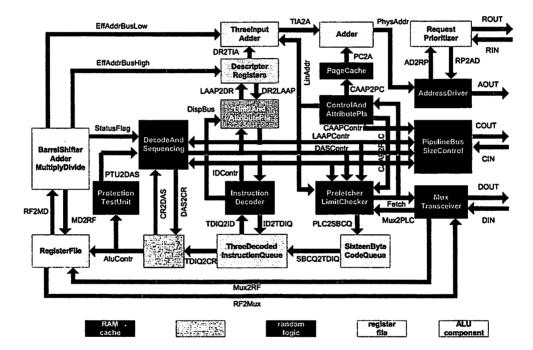

| 5.19. The system diagram of A1                                      | 333 |

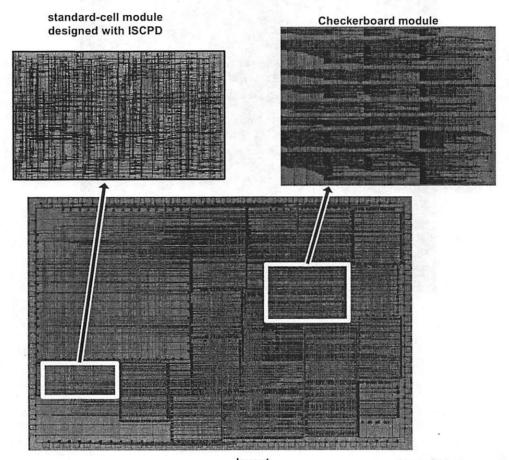

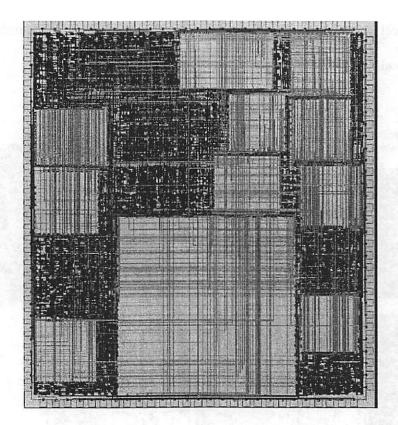

| 5.20. The layout pictures of A1                                     | 335 |

.

.

## **List of Tables**

| 3.1.  | Testing examples                                       | 87  |

|-------|--------------------------------------------------------|-----|

| 3.2.  | Area and total wire length                             | 88  |

| 3.3.  | Wire segments and vias                                 | 89  |

| 3.4.  | Run time (minutes)                                     | 90  |

| 3.5.  | Definitions of PLA parameters                          | 109 |

| 3.6.  | Area comparison of SC-a, SC-d, NPLA, RPLA-a and RPLA-d | 124 |

| 3.7.  | Delay comparison and synthesis time                    | 125 |

| 3.8.  | Configuration parameters                               | 129 |

| 3.9.  | Comparison of GPLA and FPGA                            | 130 |

| 3.10. | Typical parameters of the gate library                 | 156 |

| 3.11. | Typical parameters in the PLA designs                  | 157 |

| 3.12. | Bit counts of NPLA, RPLA (depth=2) and WPLA            | 158 |

| 3.13. | The comparison of area and delay                       | 160 |

| 3.14. | The comparison of synthesis time (minutes)             | 162 |

| 3.15. | Characteristics of the testing examples                | 195 |

| 3.16. | Testing results                                        | 196 |

| 3.17. | Comparison of the circuit structures                   | 201 |

| 4.1.  | The characteristics of the testing examples            | 246 |

| 4.2.  | Technology information                                 | 246 |

| 4.3.  | Experimental results                                   | 249 |

| 4.4.  | Wiring comparison                                      | 251 |

| 4.5.  | Difference of the delays of MST and MST*               | 253 |

.

| 4.6. Difference of the individual net delays of MST and MST*             | 255 |

|--------------------------------------------------------------------------|-----|

| 4.7. Technology information                                              | 275 |

| 4.8. Area and delay                                                      | 276 |

| 4.9. Routing violations and run time                                     | 278 |

| 4.10. The utilization of the buffers number of available buffers (used%) | 279 |

| 5.1. The technology information                                          | 326 |

| 5.2. The testing circuits                                                | 327 |

| 5.3. The record of the Physical Synthesis flow                           | 329 |

| 5.4. The record of the Module-Based flow                                 | 331 |

| 5.5. The selection of the versions for Al                                | 334 |

.

## Acknowledgements

I would like to thank my advisor, Professor Robert K. Brayton, from whom I have learned so much, not only knowledge in various CAD areas but also how to think and create. His enthusiasm and insightfulness have made my PhD study at Berkeley joyful and unforgettable.

I am pleased to express my thanks to members of my qualifying and dissertation committees, Professor Kurt Keutzer of the EECS department, Dean Richard Newton of the College of Engineering, Professor Alper Atamturk of the IEOR department and Professor Alberto Sangiovanni-Vincentelli of the EECS department.

I am grateful to members of the Nexsis Group, Philip Chong, Satrajit Chatterjee, Aaron Paul Hurst and Yinghua Li for many enlightening discussions. Also I gratefully acknowledge the help from Professor Qingjian Yu and Dr. Abdallah Tabbara, who were members of the Nexsis Group. It is my great pleasure to discuss various problems in the thesis with Dr. Andreas Kuehlmann of Cadence Berkeley Labs, Dr. David Kung of IBM T.J. Watson, Dr. Charles Alpert of IBM Austin and members of the Constructive Fabrics Group of GSRC. The work in this thesis was supported by GSRC (grant from MARCO / DAPPA 98DT-660, MDA972-99-1-0001). I would also like to thank the sponsors of my research, including California MICRO program, Cadence and Synplicity.

The consistent support from my family and friends is greatly appreciated. A sincere expression of thanks goes to Professor Qianling Zhang of Fudan University, who let me learn the way of doing research and the way of being an honest and responsible person.

## **Chapter 1**

## Introduction

## **1.1. Deep Sub-Micron IC Design Flow**

The main topic of this thesis is design flow for Deep Sub-Micron (DSM) Integrated-Circuits (IC). The design of IC is a very complex and systematic task; the complexity keeps growing as fabrication technology develops. Computer Aided Design (CAD) has become a key factor in successfully producing ICs with correct behavior, required timing and satisfactory yield. CAD is a set of computer programs, implementing algorithms that solve certain problems in IC design. Design flow is the organization of various algorithms to turn the IC design task into an automatic procedure. IC design has begun to benefit from the DSM technology, which offers higher density of transistor integration and higher performance. However, DSM technologies introduce many new problems [BRYA01, MO02], challenging the feasibility and efficiency of current CAD tools. One of the most critical issues is the timing closure of the design flow, which is mostly due to the growing importance of wiring effects. The separation of logic synthesis and physical design, two sequential stages in a traditional design flow, has become inadequate since the two stages are tightly couple by wiring effects. Timing convergence can no longer be easily guaranteed even if iterations between the stages are done. Various improvements have been made, among which the Physical Synthesis technique is popular [SYNO, CADE]. However the timing closure problem is far from being solved.

In this thesis, a Module-Based design flow is presented. This takes a very different approach to reaching timing closure. Although we do not claim that the timing closure problem is solved by our flow, it does produce better results than the Physical Synthesis flow in terms of the minimum achievable clock cycle. In addition, the run time of our flow is much shorter than for the Physical Synthesis flow. This means that users can get feedback more quickly and make necessary design changes without waiting a long time to get the failure notice. The Module-Based design flow consists of the following developments:

- (1) new circuit structures and their design methodologies,

- (2) a new placement and routing algorithm that simplifies the standard-cell physical design,

- (3) a new block-level placement and routing algorithm with buffer insertion and

- (4) a multi-version approach allowing each module to carry several versions that can be selected by the block-level physical design algorithm.

Test results show that our design flow can reach timing closure much faster than the Physical Synthesis flow, plus it can achieve shorter clock cycles.

## **1.2 Outline of the Thesis**

Chapter 2 gives the preliminaries for the thesis, including an overview of the CMOS technology, delay modeling, timing closure problem and other DSM issues. Since a design flow is always associated with one or more circuit structures, in Chapter 3 we discuss various structures and their design methodologies. These include widely used standard-cell and Programmable Logic Arrays (PLAs), in addition to some new circuit structures. In Chapter 4, a block-level placement and routing scheme called Fishbone is presented. An extension to Fishbone that enables simultaneous buffer insertion is also discussed. The entire Module-Based design flow is presented in Chapter 5, and comparison is made with a typical Physical Synthesis flow. Chapter 6 concludes.

## Chapter 2

## **Preliminaries**

## 2.1. Overview

In this chapter, a quick overview of CMOS technology and basic design automation techniques are given. Several circuit configurations are described: static CMOS, static NMOS and dynamic CMOS. These configurations are widely used in current IC designs and are also fundamental elements of the new structures we propose in the next chapter. Delay formulations for gate and wire are also given. These will be adopted throughout the discussion in the following chapters. Finally DSM challenges are addressed.

## 2.2. CMOS Technology

### 2.2.1. Transistors

The basic component of Integrated Circuits (IC) is transistor [WEST94, SZE85, ONG84, YANG88, MULL86, STRE80]. Interconnected transistors form

logic functions to meet the system requirements. A chip, or an IC unit, is a multiple layer structure. The bottom layers, usually silicon with different types of doping, build the electronic devices like transistors, capacitors and resistors; the upper layers, usually metal, form the interconnections between the electronic devices. During fabrication, the layers are grown from the bottom [CLEI99]. Each layer is associated with a mask, on which patterns indicate which parts of the layer should be kept (or removed). The patterns on the mask are duplicated physically on the wafer through optical and chemical processes [PLUM00]. The task of Computer Aided Design (CAD) for IC is to translate system specification to masks.

CMOS stands for "Complementary Metal Oxide Silicon". It is today's most widely used IC technology. The basic element of CMOS technology is the MOS transistor or MOSFET (Metal-Oxide-Silicon Field Effect Transistor). Figure 2.1 illustrates the physical structure and the schematic view of a MOS transistor.

Figure 2.1: A MOS transistor

A transistor has three terminals, drain (D), source (S) and gate (G). The body of the transistor is built on the silicon substrate. A layer of poly-silicon (poly), being stacked on a very thin layer of silicon-dioxide, forms the gate terminal. The source and drain are the regions on the substrate that are implanted or doped with impurities. To connect a transistor to others, which are built somewhere else on the substrate, multiple metal layers (here only two are shown; in reality, there might be more than six for DSM) are used. The metal layers are connected by vias, which are made of special metals. Metal layer 1 is connected to the substrate or the poly-silicon by contacts, which are also made of special metals. The space between objects is filled with silicon-dioxide, a kind of isolating material. To fabricate the transistor shown in the figure, the CAD tool should produce at least the following masks: substrate doping or implantation, poly-silicon, contact, metal1, via12 (via connecting metal 1 and 2) and metal2.

The transistor can be viewed as a switch with two mutually exclusive states, on and off. Gate is the controlling terminal. When high voltage is applied to the gate, there exists a conductive path, sometimes called "channel", between source and drain. When the gate is low, the conductive path between source and drain is cut off. The transistor shown in Figure 2.1 is an NMOS (N-type MOS) transistor. There is a complementary type called a PMOS (P-type MOS) transistor. The PMOS transistor works as a switch too, but a low controlling signal causes the switch to conduct.

#### 2.2.2. Gates

To build logic functions, transistors are connected to form gates. Here "gate" refers to a circuit unit that implements certain logic functions (it happens to have the same name as the "gate" terminal of the MOS transistor). Three typical gate configurations are discussed: static CMOS, static NMOS and dynamic gates.

### 2.2.2.1. Static CMOS gates

The serializing and paralleling of NMOS and PMOS transistors create CMOS gates [KANG95]. The NMOS transistors build a conductive path to the ground, and the PMOS transistors build a conductive path to power. The conductivities of the transistors are controlled by input signals. The two paths join at the output pin of the gate. At any moment, one and only one path is conductive, which ensures a stable output. To make this possible, the controlling of the two paths should be logically complemented (mutually exclusive and complete).

(a) CMOS inverter gate (b) timing model (c) transient behavior Figure 2.2: CMOS inverter

As shown in Figure 2.2(a), a CMOS inverter is composed of a PMOS and an NMOS transistor. When input A is high, the NMOS transistor is on and the PMOS is off, so the output Z is pulled down by the NMOS to ground (or zero Volts) via its conductive path. When the input A is low, the NMOS turns off and the PMOS turns on, so Z goes high. Figure 2.2(b) outlines the timing model of the inverter. An inverter has an input capacitance  $C_I$  and an output capacitance  $C_O$ . The two resistors,  $R_P$  and  $R_N$ , model the PMOS and the NMOS switches, respectively. The external load capacitance  $C_L$  is the sum of the input capacitances of all the gates the inverter drives. To be more precise,  $C_L$  should include the wire capacitances, because the inverter needs some metal wires to connect to the gates it drives. An "on" transistor can be approximated as a resistor. Charging  $C_L$  and

$C_O$  through resistor  $R_P$  and discharging them through  $R_N$  both take time, which generate transistor delays. The transistor delays depend on many factors, among which the transistor size and the load are the most important. The larger a transistor, the smaller the resistor and the faster it switches. The larger the load is, the slower the switching. If  $R_P$  and  $R_N$  are equal, the two resistors and the switch can be simplified to a voltage source that drives one resistor  $R_O=R_N=R_P$ . A typical waveform of the CMOS inverter is illustrated in Figure 2.2(c). The delays are shown as the intervals between the transition edges of the input and output. In general delay might be different for low-to-high and high-to-low transitions. However, the size ratio of the PMOS and NMOS transistors can be designed such that  $delay=t_{HL}=t_{LH}$ .

To obtain more complex logic functions, transistors can be connected in parallel or in serial. Fundamental logic operations, such as INV ( $\bar{}$ , inversion), AND (&), OR (+), XOR ( $^$ , exclusive-OR) etc., have their transistor-level representations. A logic function might be prefixed with an "N" to indicate that its output is inverted, e.g. an NAND gate, as illustrated in Figure 2.3(a). In general, as shown in Figure 2.3(b), a CMOS gate consists of a network of NMOS transistors between the output and ground, which form the pull-down logic, and a network of PMOS transistors between the output and power to form the pull-up logic. The pull-up and pull down parts are logically complemented; hence conductive pull-down and pull-up paths do not coexist. In this sense, static CMOS gates do not consume *static* power.

Figure 2.3: CMOS gate

A special kind of gate called a buffer. It is two inverters in a chain. A buffer expresses an "=" function, which may sound useless in building circuits, but it isolates heavy load from weak driver when inserted into a wire. Buffer insertion is a powerful means of handling timing problems and is discussed in Section 2.2.4.2.

### 2.2.2.2. Static NMOS gates

Before CMOS technology became popular, only NMOS transistors were used to build logic gates [HODG03].

Figure 2.4: NMOS gate

Figure 2.4(a) illustrates a typical NMOS inverter, which is simply a NMOS transistor (TN1) connected to a depletion-type NMOS transistor. The depletion-type NMOS transistor has a zero or negative threshold voltage such that even if its gate and source are zero biased, the transistor is on. This makes TN0 form the pull-up function, as if it is a resistor. When A is low, TN1 is off and Z is pulled to high through TN0. When A is high, TN1 is on and it overcomes TN0 such that Z becomes low. Figure 2.4(b) shows how general logic functions are constructed with the NMOS configuration. The lower part of the NMOS inverter is replaced by a network of NMOS transistors, the input signals determining the existence of a conductive path from Z to ground.

NMOS gates are compact compared with CMOS gates, because a NMOS gate saves all the PMOS transistors. In addition, PMOS transistors are often laid out such that they are several times larger than NMOS transistors to balance the rising and falling delays [HODG03]. Therefore the area saving of NMOS gates is significant. However static NMOS gates suffer in delay. The choice of the sizes of the NMOS transistors and the sizes of the pull-up transistor is not easy. Consider the inverter in Figure 2.4(a). As the function outputs low, the pull-up transistor TN0 battles with TN1. To ensure reaching a low output level quickly enough, TN1 should strongly overcome TN0. In contrast, when TN1 turns off and the level of Z rises, it is the driving capacity of TN0 that determines the rise time. The two factors are obviously contradictory. Another disadvantage of static NMOS gates is the power dissipation. A static NMOS gate consumes static power when its output is low.

To mitigate the delay and power problems while preserving the compactness of the NMOS gates, a dynamic configuration is introduced.

#### **2.2.2.3.** Dynamic configuration

The CMOS and NMOS gates described above both belong to the static configuration classification, in the sense that the output responds immediately (after some gate delay) to the change at the inputs. The dynamic configuration only requires that the output respond within a certain time period [HODG03]. This is somewhat similar to static NMOS, except that the pull-up transistor is replaced by a pair of pre-charging-control transistors.

Figure 2.5: Dynamic gate

A dynamic inverter is illustrated in Figure 2.5(a), in which TP0 and TN0 control the state of the gate, either "pre-charge" or "evaluate". When precharge/evaluate is low, TN1 is isolated from ground because TN0 is off, and the output Z is pulled up to high by TP0. When precharge/evaluate becomes high, TP0 is off and TN0 is on. TN1 starts to evaluate the logic function controlled by input A, and Z responds accordingly. In a general dynamic gate [DHON92], as illustrated in Figure 2.5(b), the evaluation is done through a network of NMOS transistors.

There are many variations of the dynamic configuration [HODG03], but all require a precharge/evaluate signal that controls the operation of the gate. If dynamic gates are cascaded, timing validity needs to be considered for the

generation of the precharge/evaluate signals for each gate in the chain. In other words, a dynamic gate cannot start to evaluate until all its input signals are evaluated. Several Programmable Logic Array (PLA) based circuit structures described in the next chapter make use of the dynamic configuration.

#### 2.2.3. CMOS storage components

Gates are reactive to their inputs. Other components have a sort of memory function, reacting to the inputs under certain conditions. Such storage components can store previously inputted information. A typical storage component is register, as shown in Figure 2.6. The pins of a register include clock C, data-in D and output Q. The function of a register can be summarized as "whenever C rises, Q copies D and hold it until the next rising edge of C". This kind of edge-triggered register is called a "flip-flop".

Figure 2.6: Register and its operation

Memory components such as Random Access Memory (RAM) also provide storage, which are arrays of storage units. Accessing a bit of the memory (read or write) is at least several times slower than accessing a register. On the other hand, memory components are more compact in layout.

#### 2.2.4. Interconnections

### 2.2.4.1. Wire delay

The Elmore delay formulation is the wire delay model adopted in this thesis [ELMO48]. The Elmore model formulates the propagation delays as a tree with output pin being the root. At each branching point including the root, the delay is the resistance of the last wire segment times the total accumulated capacitance of the sub-tree rooted at the branching point.

Figure 2.7: Gate delay and wire delay models

In Figure 2.7, the driving gate is gate1, the loading gates are gate2 to 4. Gate2, gate3 and gate4 contribute their input capacitances to the load of gate1. For a wire segment with length L, a  $\pi$ -shaped RC structure is assumed, as shown in the figure. The capacitance and resistance of the segment are:

$$C_W = L \cdot C_{//}$$

and  $R_W = L \cdot R_{//}$ ,

where  $C_{//}$  and  $R_{//}$  are the capacitance and resistance of the unit wire length respectively. We examine the propagation delay from point *a* to point *f*. The delay is the sum of the delays of the segments:

$$D(a \rightarrow f) = D(a,b) + D(b,c) + D(c,d) + D(d,f).$$

$D(a,b)=D_C$  is the intrinsic gate delay, which is load independent. The delay from b to c, also part of the gate delay but load dependent, is:

$$D(b,c) = R_o [C_o + C_{ACC}(c)],$$

in which,  $C_{ACC}(c)$  is the accumulated capacitance at node c, to be clarified shortly. D(c,d) and D(d,f) are the delays on wire segment c-d and d-f respectively:

$$D(c,d) = R_{W}(c,d)C_{ACC}(d)$$

$$D(d,f) = R_{W}(d,f)C_{ACC}(f)'$$

in which,  $C_{ACC}(d)$  and  $C_{ACC}(f)$  are the accumulated capacitances at node d and f, and  $R_W(\cdot, \cdot)$  is the  $\pi$ -shaped resistance of the wire segment. The formulation of  $C_{ACC}(\cdot)$  is essential in the Elmore model. A net is a tree  $\{P, E\}$ , where P is the node set and E is the edge set. The output pin is the root, and other nodes are either the input pins of the loading gates or the branching points. Each edge is denoted by a node-pair (i,j) and the signal direction is from *i* to *j*. An edge corresponds to a wire segment, so it is associated with a  $\pi$ -RC, denoted by  $C_W(i,j)$ and  $R_W(i,j)$  and both are linear with the length of the segment. Define for each node a variable  $C_{ACC}(i)$  called the accumulated capacitance. The value of  $C_{ACC}(i)$ is recursively defined:

$$C_{ACC}(i) = \sum_{(h,i)\in E} \left[ \frac{1}{2} C_{W}(h,i) \right] + \sum_{(i,j)\in E} \left[ \frac{1}{2} C_{W}(i,j) + C_{ACC}(j) \right]$$

$$+ C_{I}^{?}$$

for non-leaf nodes. The term  $C_I^{?}$  equals to  $C_I$  if this node is an input pin, or 0 otherwise. For leaf nodes which are always input pins,

$$C_{ACC}(i) = \frac{1}{2} C_{W}(h,i) \bigg|_{(h,i) \in E} + C_{I} \cdot$$

This model can be summarized as "the accumulated capacitance is the sum of all capacitances of the downstream nodes". So at the output pin (node c in the example) or the root of the tree, the accumulated capacitance is the sum of all  $\pi$ -capacitances and all input pin capacitances. Hence,

$$\begin{split} C_{ACC}(e) &= \frac{1}{2} C_{W}(d, e) + C_{I} \\ C_{ACC}(g) &= \frac{1}{2} C_{W}(f, g) + C_{I} \\ C_{ACC}(f) &= \frac{1}{2} C_{W}(d, f) + \frac{1}{2} C_{W}(f, g) + C_{ACC}(g) + C_{I} \\ &= \frac{1}{2} C_{W}(d, f) + C_{W}(f, g) + 2C_{I} \\ C_{ACC}(d) &= \frac{1}{2} C_{W}(c, d) + \frac{1}{2} C_{W}(d, f) + C_{ACC}(f) + \frac{1}{2} C_{W}(d, e) + C_{ACC}(e) \\ &= \frac{1}{2} C_{W}(c, d) + C_{W}(d, f) + C_{W}(f, g) + C_{W}(d, e) + 3C_{I} \\ C_{ACC}(c) &= \frac{1}{2} C_{W}(c, d) + C_{ACC}(d) \\ &= C_{W}(c, d) + C_{W}(d, f) + C_{W}(f, g) + C_{W}(d, e) + 3C_{I} \end{split}$$

Then the delay on each segment can be derived and the total delay is:

$$D(a \to f)$$

=  $D(a,b) + D(b,c) + D(c,d) + D(d,f)$

=  $D_c + R_0 [C_o + C_w(c,d) + C_w(d,f) + C_w(f,g) + C_w(d,e) + 3C_l]$

+  $R_w(c,d) [\frac{1}{2}C_w(c,d) + C_w(d,f) + C_w(f,g) + C_w(d,e) + 3C_l]$

+  $R_w(d,f) [\frac{1}{2}C_w(d,f) + C_w(f,g) + 2C_l]$

Except for a constant part  $D_c$ , the total delay depends on the wire RC parameters and the input pin capacitances of the loading gates. The input pin capacitances are known, but the wire RC's are determined by the actual net topology, wire widths and routing layers. An interesting phenomenon is that the delay along the wire segments c-d-f also depends on the segments d-e and f-g. Since the  $\pi$ -shaped R and C are both linear functions of the length of the wire segment, the wire related delay grows quadratically as the wire length increases. In the above derivation, we assume all the loading gates have the same input

capacitance  $C_I$ . In real circuits,  $C_I$  is proportional to the gate size. As mentioned earlier, to make a gate switch faster, or a smaller  $D_C$ , the gate size should be large. But  $C_I$  becomes large as a result. So to make a gate switch faster by increasing its size, we actually increase the load to the previous gates. Therefore the optimization of the delay of a chain of gates is an interesting and important problem in CAD.

#### 2.2.4.2. Buffer insertion

Buffer is a kind of gate that fulfills the "equal" function. Inserting buffer(s) in a wire does not change the logic function, but provides a powerful means of reducing wire delay [CONG01a, CONG01b]. The main idea is to break a long wire into short segments where buffers are inserted at the break points. The short wire segments reduce the quadratic wire delay effect; although the inserted buffers introduce extra delays because of their intrinsic and load dependent delays. Hence the problems are how many buffers are inserted and where. Here we give a simple description of the buffer insertion for a two pin net (one driver and one load, or fanout=1). In Chapter 4, the buffer insertion problem in blocklevel physical design will be detailed.

Suppose the inserted buffers have the same capacitance  $C_I$  as the input pins and the same driving resistance  $R_O$  as the output pin, and they divide the wire into N segments with equal length. By using  $C_{\prime\prime}$  and  $R_{\prime\prime}$ , the unit length wire capacitance and resistance, the un-buffered wire delay can be expressed as:

$$D = R_o \left( LC_{ii} + C_i \right) + LR_{ii} \cdot \left( \frac{LC_{ii}}{2} + C_i \right),$$

in which, L is the total wire length. The delay after (N-1) buffers are inserted becomes:

$$D' = N \cdot \left[ R_o \left( \frac{LC_{II}}{N} + C_I \right) + \frac{LR_{II}}{N} \left( \frac{LC_{II}}{2N} + C_I \right) \right] + (N - 1) D_{BUF}$$

where  $D_{BUF}$  is the intrinsic buffer delay. Comparing D and D', we see that the total delay is decreased by

$$\Delta D = D - D' = (N - 1) \left[ \frac{L^2 R_{II} C_{II}}{N} - (R_o C_I + D_{BUF}) \right].$$

A positive value is necessary for meaningful buffer insertion. Thus delay cannot be arbitrarily improved by inserting more and stronger buffers. Figure 2.8 shows the wire delay as a function of the number of wire segments (the number of buffers plus one). The parameters used in making the plot are:  $C_{l/}=1.1\times10^{-4}$  $^{4}pF/\mu m^{2}$ ,  $R_{l/}=5.0\times10^{-2}\Omega/\mu m$ ,  $C_{l}=0.001$ pF and  $R_{O}=100.0\Omega$ . The length of the wire is 5.0mm, and the buffers are evenly inserted along the wire.

Figure 2.8: Delay versus number of wire segments (N) evenly split by buffers

The analysis is more complicated for multiple fanout nets. In addition, buffer insertion may increase the chip area, which may in turn change the wire lengths and thus the wire delays, making the prediction of the wire length even harder. Also, to insert a buffer, vias need to be introduced to bring the net, most probably running on higher metal layers, down to the substrate for buffering and bring the buffered signal back to higher layers. The number of vias used to connect to the buffer, and thus the resistance, is hard to predict. Furthermore, the buffer locations may not be arbitrarily chosen, because existing gates and modules may have already occupied a location.

## 2.2.4.3. Net topology

A net is a set of pins that are logically connected. A net must have at least two pins, and one of the pins must be output pin (driver) and the rests are input pins. A bi-directional pin can be either output or input, controlled by some other signal. A net can have more than one bi-directional pin. But to prevent conflicts, one and only one pin of a net drives the rest pins at any time. In this thesis, we do not consider the case that bi-directional pins appear in the nets.

A general net may contain more than one input pin (load), such that intermediate points may exist on the net generating branches of the wires.

Various net topologies exist [SHER93, SHER95]. Some popular and useful net topologies are illustrated in Figure 2.9. The net in the figure is composed of output pin Z and input pins A to F. Criteria are needed to evaluate the quality of the net topology. The most widely used criterion is wire length. Short wire length is likely to result in easy routing, because of the low utilization of the routing resource. For two pin nets, reducing wire length means shorter wire delay. A Rectilinear Steiner Tree (RST) [SHER93], as shown in Figure 2.9(a), is a net

topology that provides the minimum wire length for a set of pins of a net. The non-pin nodes in the tree topology,  $s_1$ ,  $s_2$  and  $s_3$  in the figure, are called Steiner points. However RSTs do not always provide minimum length between any output-input pin pair, for instance the Z-A connection in Figure 2.9(a). Rectilinear Steiner Arborescence (RSA) [CONG97], as illustrated in Figure 2.9(b), is an improved Steiner Tree that each output-input pin connection has minimum length. Unfortunately both of these two topologies are computationally hard. Figure 2.9(c) illustrates a so-called Spine topology. The output pin is on a wire segment called the "spine" and all input pins connect to the spine via "ribs", segments orthogonal to the spine. The construction of the spine for a given set of pins is trivial. Like RSAs, the output-input pin lengths are always the minimum. To quickly estimate the wire length of a net without topologically constructing the net, a Half Perimeter (HP) model is usually adopted. As illustrated in Figure 2.9(d), the HP for a net is the half perimeter of the minimum bounding box surrounding all pins. Strictly speaking, HP is not a net topology, but since a net is physically constructed with RST, RSA, Spine or other topologies, the delay analysis described above can be performed.

Following are some important points regarding the net topologies:

• For a given set of pins and their locations, the RST and RSA may not be unique.

- In reality, the cells carrying the pins are movable; so minimizing wire length or delay is not only the job of choosing a net topology but also placing the cells at good positions.

- The topologies only tell the X/Y information. The Z information, the metal layer a wire segment is placed on, is not known. Whenever a wire switches layers, a via (or vias if it switches to a non-neighboring layer) is introduced. This is usually determined by the router. However delay computations may need layer information to get precise results, because different layers and vias have different physical parameters. Unfortunately, this leads to the conclusion that only after routing is precise delay computation possible.

- Buffer insertion may further change the quality of a net topology.

# 2.3. IC Design and System-On-a-Chip

#### 2.3.1. System and constraints

A digital circuit system can be regarded as a state machine. The storage of the states is implemented with storage components. Digital systems are classified into two categories, synchronous and asynchronous. Asynchronous systems are not in the scope of our discussion.

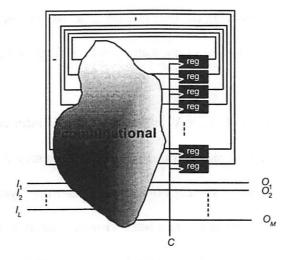

Figure 2.10: A state machine

A synchronous system can be viewed as a state machine, as shown in Figure 2.10. The state machine contains two parts: a combinational part and a sequential part composed of Z registers clocked by signal C. The state is described by a binary value stored in the registers that contains Z bits. Obviously the system has up to  $2^{Z}$  different states. The state is migrated to the new state at the clock edge. Between two clock edges, the combinational part, composed of gates, computes the new value of the state, and the new state is ready at the inputs of the registers when the next clock edge arrives. The external inputs to the system are labeled  $I_1$ ,  $I_2,..., I_L$ , and the outputs are  $O_1, O_2,..., O_M$ . Denote the system clock cycle by K. The behavior of the synchronous system can be formulated as:

$S(t+K)=f(S(t), I(t)) \quad 2^Z \times 2^L \rightarrow 2^Z$

$$O(t) = g(S(t), I(t)) \qquad 2^{Z} \times 2^{L} \to 2^{M}$$

in which, S() is the state, f() is the state transition function, and g() is the output function. In reality, a large system is normally described as a network or hierarchy of many small state machines, because first, hierarchical description is more natural; second, small state machines may be more efficiently implemented with CAD tools. The interconnection of small state machines can result in a single state machine with a huge number of states, although they are functionally equivalent.

Figure 2.11: Combinational paths

To measure the performance of a synchronous system, we need to consider combinational paths, defined as a path starting from a register and ending at a register. In Figure 2.11, various combinational paths are shown. A combinational path can start from a register and end in a register in the same module, e.g. paths feeding register 2 in the left module. A combinational path may cross modules, like the one starting from register 1, passing through pins Z, B, Y and E, and ending at register 4. Note that a path can have branches along the way, and multiple paths may share some common segments. In addition, more than one path can exist between a pair of registers, e.g. register 1 and 4 in the figure.

Timing constraints are normally expressed in terms of "arrival times" and "required times". These are defined on the signal nodes of the circuit such as register pins, the pins of the modules and pins of the I/O ports. Assume all registers update their output values at time 0, i.e., the arrival times of the register output pins are 0. All register input pins should receive the new input no later than  $t_{REQ}=n(path)\cdot K$ , where K is the clock cycle and n(path) is an integer representing the number of cycles allowed for the path reaching that register. If n(path)=1, the path is called a single-cycle path. Satisfaction of the timing constraints can be stated as:

## $t_{ARR}(node) \leq t_{REQ}(node)$

for all nodes. For a path starting from or ending at the environment through an I/O port, we simply assume that there is a register in the environment.

**Figure 2.12: Design constraints**

Figure 2.12 gives an example of the usage of the arrival and required times. When considering a path starting from the environment, e.g. the path through IPAD1 in the figure, we can imagine that it starts from external register rege1. The arrival time at the input I/O port ( $t_{ARR}=0.6K$ ), must be provided in the specification, taking into account the wiring delay in the environment. Similarly, for output port OPAD1, the required time  $t_{REQ}=0.9K$  must be given. Paths coming out of or entering hard macro-cells, like hard-macro1, need to get arrival times on the output pins and set required times on the input pins. These numbers are determined by the internal path delays of the module and given in the specification. In the rest of the circuit, the dotted region in the figure, the register input and output pins are given required and arrival times, respectively. In

Chapter 5, the required/arrival times will be extensively used in a timing driven design flow.

Clock cycle is the main performance measurement of a synchronous system. So the target of designing a high performance synchronous IC is to reduce the clock cycle, or to boost the frequency, which is the reciprocal of the clock cycle.

Finally we point out that path delay should include the wire delay. In modern IC design, wire delays may even dominate cell delays.

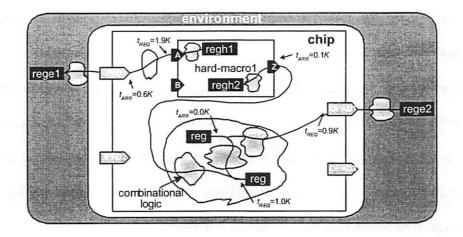

#### 2.3.2. Design styles

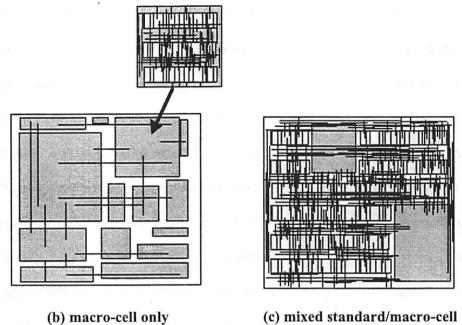

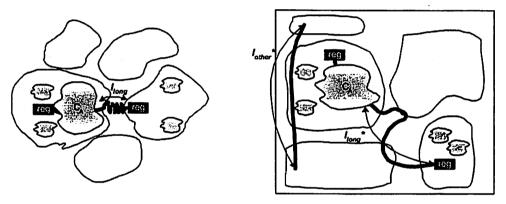

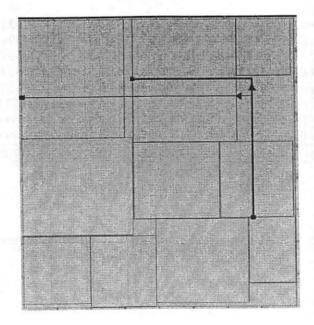

Design style is the way a design is implemented, associated with certain circuit structures, among which standard-cell and macro-cell are popular. In Figure 2.13, three major styles in today's IC design are illustrated.

(a) standard-cell only

Figure 2.13: Three design styles

Figure 2.13: Three design styles

In Figure 2.13(a), a pure standard-cell design is shown. Standard-cells, to be detailed in Chapter 3, are small pre-designed circuit modules that implement simple logic functions. All standard-cells in a design have the same height, so that they can be easily placed in rows. When the standard-cell design style is adopted, the design task is to map the input netlist to a netlist of standard-cells provided in a library, and then place the cells in the layout and construct their interconnections. The fine granularity of the standard-cell provides flexibility in the mapping and the layout design phases. In Figure 2.13(b), a macro-cell design is shown. Unlike standard-cells, macro-cells are modules with coarse granularity;

they are usually several orders of magnitude larger than standard-cells, implementing more complex logic functions. Typical macro-cells include memory modules that are generated by some memory compilers, Intellectual Property (IP) blocks like embedded micro-processors and analog blocks like Phase Lock Loop (PLL). Of course a macro-cell can be a module that is designed with standard-cells. Pure macro-cell design involves much less components in the layout than the standard-cell only style. However this does not necessarily lead to simpler layout design, due to the heterogeneous shapes and sizes of the macrocells. A mixed standard/macro-cell design is shown in Figure 2.13(c), which consists of both macro-cells and standard-cells in a single layout. Standard-cells, which are much smaller than macro-cells, are placed in the space left by macrocells. The previous two styles can be regarded as special cases of this style.

#### 2.3.3. System-On-a-Chip

When the integration density of IC's was low, an IC could only implement part of the system function. To build complex systems, many chips might be needed; and these chips were integrated on a board, leading to the term "System-On-a-Board (SOB)". Multi-Chip-Module (MCM) is another type of integration, putting several raw chips in one package. But this is only a "tiny" SOB. With increasing integration density due to the shrinking feature sizes, the whole system can be implemented on a single chip. The so-called System-On-a-Chip (SOC) is not a "very-tiny" SOB, but a new concept in electronic design [BEDN02]. One of the major advantages is that now the interconnections are also integrated and thus much shorter and denser than those in SOB's. This allows higher speed to be achieved. Another advantage is the reduction of packaging and board cost, because everything is now on a single chip. Unfortunately many new problems accompany the advantages. For example, the complexity of the chip grows, which must be dealt with by the design tools. Timing and power problems are both different from and more difficult than before.

It is interesting to see SOC designers are also pursuing higher and higher speeds, using the fact that an SOC can be faster than its SOB counterpart.

# 2.4. Design Automation

Electronic Design Automation (EDA) is a software approach that automatically, or with little human intervention, translates the initial logic network to a layout.

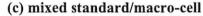

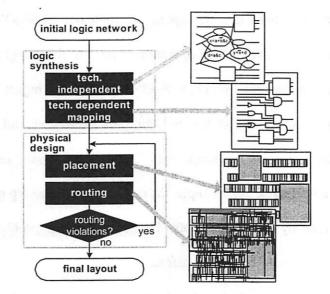

Figure 2.14: A simple design flow

Figure 2.14 shows a simple design flow, containing two stages: logic synthesis and physical design. The task of logic synthesis is to translate the initial logic network to a network that is composed of macro-cells and standard-cells. The logic synthesis can be further divided into a technology independent stage and a technology dependent stage [BRAY90]. The technology independent stage employs various Boolean transformations to reduce the size and/or delay of the circuit. The netlist produced by the technology independent optimization is given to the technology dependent stage, which has a more popular name "technology mapper". The technology mapper translates the Boolean network into a network of cells, while maintaining the same functionality. The cells are chosen from a library of pre-designed and pre-characterized modules called the standard-cells.

The physical design stage works on the mapped netlist. It also contains two parts: placement and routing [SHER93]. Placement finds the positions for each component on the chip and routing determines the structures of the interconnections. The router may fail due to routing violations, in which case placement needs to be restarted with some parameters adjusted.

Figure 2.15: A timing-driven design flow

When there are timing constraints, the design flow becomes a constrained optimization, which is called a timing-driven design flow. As shown in Figure

2.15, upon the completion of each stage, the satisfaction of the timing constraints is tested. Looping is necessary if timing violations are identified. The main cause of these iterations is wiring effects. As mentioned before, a significant part of the path delays are wire delays. We have also stated that the wire topologies might not be finalized until the completion of the routing. These make accurate computation of delays and evaluation of constraint satisfaction very difficult during logic synthesis. Even during placement, wiring still needs to be estimated. Estimation errors may lead to timing problems, and the problems may occur very late in the design flow. Another cause of this non-convergence is that some algorithms do not directly minimize delays. For instance, many placement algorithms focus on minimizing the total wire length, which is helpful in reducing delay but cannot guarantee it.

A timing-driven design flow will be given in more detail in Chapter 5.

## 2.5. Challenges in the Deep Sub-Micron Era

IC fabrication technology is often labeled with the minimum feature size, that is, the minimum width of the patterns that can be correctly fabricated. The feature size has been shrinking from 1-micron (about ten years ago) to about 0.1-micron (sub-micron, today). And it is expected that the feature size will reach 0.05micron (deep sub-micron) in a few years.

#### 2.5.1. The Deep Sub-Micron Challenges

Smaller feature sizes mean higher density and shorter intrinsic gate delays. However, all the parameters are not scaled down at the same rate. Unfortunately, parameters like wire resistance and wire capacitance are scaled down slowly, such that wire delay becomes a dominant part in the total delay. Other new problems such as manufacturability also emerge. We discuss three DSM problems: timing closure, manufacturability and library migration.

## 2.5.1.1. Timing closure

The timing closure problem arises from the fact that the design flow contains a set of sequential steps. Early steps have to predict what the later steps will do. Inaccurate prediction may lead to wrong decisions, which can only be recognized later. When this happens, design iteration is necessary. For instance, at the synthesis stage, the wire delays are not known. So the synthesizer has to estimate wire length based on probability or some other models. When the synthesized circuit is passed to the physical design tool, it might become clear that some wire lengths were incorrectly estimated. Unfortunately this is not the end of the nightmare, because using the "exact" wire length just derived from the routed design to control a new round of synthesis does not guarantee the same layout, and thus does not guarantee those wire lengths. In fact timing closure has been a problem for a long time, but DSM promotes it to the top of the problems.

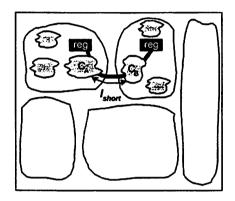

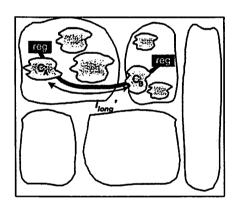

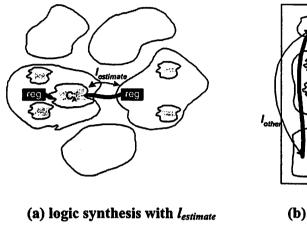

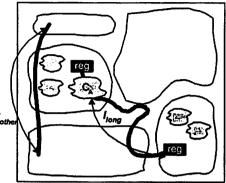

(a) logic synthesis with  $l_{estimate}$

(b) physical design gives *l*<sub>short</sub>

(c) physical design gives  $l_{long}$

- (d) physical design gives llong'

- Figure 2.16: An example of the timing closure problem

.

An example of the timing closure problem is shown in Figure 2.16. A path bridging two modules is highlighted.  $C_A$  and  $C_B$  are the part of the combinational

logic that relates to the path. The two modules also contain logic that is irrelevant to the path. Figure 2.16(a) is the logic synthesis stage, in which the length of the wire under consideration can only be estimated, denoted by  $l_{estimate}$ . Logic synthesis takes the estimated wire length and distributes the path delay among C<sub>A</sub>, the wire and C<sub>B</sub>. Physical design may result in a real wire with length  $l_{short}$  that is very close to  $l_{estimate}$ , as shown in Figure 2.16(b); thus the previous estimation is legal and timing closure is achieved. However, physical design may result in a layout shown in Figure 2.16(c), in which the two modules are placed apart such that the wire length  $l_{long}$  deviates substantially from  $l_{estimate}$ . This shows that the separation of logic synthesis and physical design is a source of wrong estimation. Another source is the logic synthesis itself, because the module size is a result of the synthesis, and thus a result of the estimated wire length. In Figure 2.16(d), the placement seems to be fine, because the modules carrying C<sub>A</sub> and C<sub>B</sub> are close to each other. However the module carrying C<sub>A</sub> becomes so large that the wire length  $l_{long}$ ' still becomes illegal.

The above discussion only involves one path. In SOC designs there are many paths. Also ignored in the discussion is the routability of the wires. Sometimes wires have to detour to fulfill routability, such that the wire lengths and delays become even harder to predict at the early stages like logic synthesis.

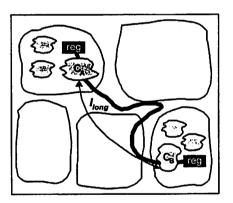

(b) physical design gives  $l_{long}$

(c) logic synthesis with l<sub>long</sub>

(d) physical design gives l<sub>long</sub>\*

Figure 2.17: Another example of the timing closure problem

To illustrate another possible cause of non-convergence, an example is given in Figure 2.17. We focus on the module carrying combinational part  $C_A$ . The synthesis, as shown in Figure 2.17(a), works with an estimated wire length  $l_{estimate}$ . After physical design, as shown in Figure 2.17(b), it turns out that the wire length  $l_{long}$  is too long such that the path constraint is not met. A new iteration is called with  $l_{estimate}$  replaced by  $l_{long}$ . The synthesis now deals with a tighter timing requirement, because  $C_A$  needs to be faster to compensate the larger wire delay. As shown in Figure 2.17(c), this results in larger area of the module, mostly due to the increased size of  $C_A$ . When the new synthesis result is passed to physical design while the original relative module positions in the layout are maintained, as shown in Figure 2.17(d), the problem does not go away. The reason is that the change in the module size affects the placement and thus the wire length. The new wire length  $l_{long}$ \* may not be consistent with  $l_{long}$ . To make things worse, consider a previously good wire, the one with length  $l_{other}$  in Figure 2.17(b). Due to the increase size of the re-synthesized module, this innocent wire may have its length increased to  $l_{other}$ \*, causing a new timing problem.

#### 2.5.1.2. Manufacturability

As the limits of the mask-making system (finite aperture of projection) are reached with smaller geometries, the actual layout patterns on the wafer differ from those produced by a CAD tool [PLUM00]. The patterns after the lithography may have unexpected shapes such as collapsed edges and rounded corners. Although pre-distortion can be added to offset some of the real distortions, the number of layout patterns generated by a conventional design flow can make this task take an unreasonable amount of time and generate an enormous data set. Design-For-Manufacturability (DFM) has become one of today's hot research topics.

#### 2.5.1.3. Library migration

Standard-cell is the most widely used circuit structure in IC design, which will be detailed in Chapter 3. This structure involves a library that contains several hundred library cells with various logic functions and driving capacities. Each cell needs to be manually designed to get an optimal combination of cell area, delay, power and other factors, based on a set of design rules and transistor characteristics that are different from technology to technology. The job of building a modern cell library is very costly, involving layout design, parameter extraction, circuit simulation, design rule checking, electrical rule checking and documentation. Whenever a technology is migrated to an advanced one with a smaller feature size, the whole standard-cell library has to be rebuilt. The reuse of the old library is almost impossible, because factors like cell delay are not scaled proportionally. Especially in the DSM era, the cell characterization becomes extremely complicated because of many new effects.

## 2.5.2. Dealing with the DSM challenges

To deal with the DSM challenges discussed above, efforts can be made in several aspects. Individual algorithms in the design flow might be improved to allow better wiring predictability. The entire design flow may also be modified to reduce the possibility of being trapped in endless iterations. New circuit structures are also sought, which offer predictable area and performance. These factors are not totally isolated. The main ideas include:

- The manufacturability and library migration problems are handled mainly through the applications of new circuit and interconnection structures.

- The timing closure problem is dealt with through the development of new design flow.

- New algorithms bridge the structures and the flow.

Effective integrating of circuit structures and algorithms into a design flow is what we study in this thesis. This does not mean that new structures and algorithms that do not fit in the new design flow are worthless; they are still valuable.

It has been proposed [MO02a] that regular circuit structures, sometimes called "regular fabrics", can provide better guarantees that the layout designed by a CAD tool is correctly replicated in the fabrication. Regular fabrics use extensively simple and repeatable layout patterns in building the circuits. Memory and Programmable Logic Array are two typical regular structures. A PLA is composed of regular patterns and its area and delay are directly related to the logic function it implements. A network of Sum-of-Products (SOP) nodes can be mapped directly to a PLA [RUDE88]. Technology mapping, required in standard-

cell designs, is not necessary, nor are placement and routing necessary for a single-PLA circuit. The PLA structure is also library free. PLA and its variations will be detailed in Chapter 3.

Regularity exists not only in the lower layers of the layout, where transistors are made, but also in the interconnection layers. Regularity in the interconnections is very helpful in predicting wiring effects. A new regular global wiring scheme will be discussed in Chapter 4.

Regular structures certainly offer simpler and possibly better optical correction in enhancing manufacturability. Beyond what optical pre-distortion could do, regular fabrics can reduce manufacturing variations further. Unfortunately a quantitative measurement of any improved manufacturability of a layout due to regularity is still missing. The numbers of layout patterns, wire segments and vias might give can be reasonable metrics when comparing two designs in terms of manufacturability, but this study remains to be done. When such a study becomes available, manufacturability can become another trade-off that can be made along with area, delay, power etc, and the role of regularity towards these goals can be assessed.

The separation of the logic synthesis and physical design in the traditional design flow is a major cause of timing closure problems. Following are two approaches that help solve the timing closure problems: (1) One approach is to do some physical design before synthesis starts, such that wiring effects can be more

precisely estimated based on the pre-synthesis physical design results, for example the rough positions of the modules. Then logic synthesis uses these to guide its operations. If the synthesis results, module area for instance, have no conflicts with the pre-synthesis results, then convergence is reached. Today's commonly adopted "Physical Synthesis" flow is such an approach. (2) Another approach is to leave certain flexibilities in the synthesis results such that they can be used to solve potential timing problem during the physical design. The socalled Module-Based design flow that we have developed belongs to this category. In Chapter 5, these two kinds of design flows will be described and compared.

# 2.6. Summary

In this chapter, we presented the preliminaries of modern IC design, including CMOS transistor, static and dynamic configurations, delay modeling of gate and wire, various design styles and timing-driven design flow. New DSM challenges were discussed also. The strategies proposed in Section 2.5 to handle the DSM problems are the main topic in the following chapters.

# **Chapter 3**

# **Circuit Structures**

## 3.1. Overview

The following circuit structures as well as their design methodologies are described in this chapter.

- Standard-cell (SC): An existing structure with a new integrated placement and routing algorithm.

- Programmable Logic Array (PLA): Review of an existing structure.

- Network of PLAs (NPLA): Review of an existing structure.

- River PLA (RPLA): A new structure and its design methodology.

- Whirlpool PLA (WPLA): A new structure and its design methodology.

- Checkerboard (CB): A new structure and its design methodology.

Structures like standard-cells and PLAs are not new, but worth having a quick review because of their importance in Very Large Scale Integrated-Circuit (VLSI) design. A novel physical design algorithm for SC is presented. River PLA, Whirlpool PLA and Checkerboard are relatively new; both their circuit structures and design methodologies are discussed. Since the design flow proposed in this thesis is module based, we focus on the design of modules with these structures. The sizes of the modules normally range from several hundreds to ten thousand gates. Actually some of the structures such as standard-cell, NPLA and Checkerboard can be used for full chip design. The PLA based structures can be extended to programmable or reconfigurable versions, at a cost of some area and delay.

In this chapter, we only consider how to use a structure to implement a given netlist. The created layout is a module. To implement the whole chip, many such modules might be needed. The way such modules, possibly made of with different structures, are organized will be discussed in Chapters 5.

## 3.2. Standard-Cell

Standard-cell is the most widely used style in VLSI design. A standard-cell library is associated with a specific technology, containing tens to hundreds of library cells. Each library cell in the library implements a logic function. Several library cells may implement the same function, but they provide different driving capacities. A standard-cell netlist is composed of the instantiations of the librarycells (simply called "cells"). The term "standard" comes from the fact that all the library cells of a library have the same height (Y-size of the layout). When placing the cells in a layout, they can be arranged in rows.

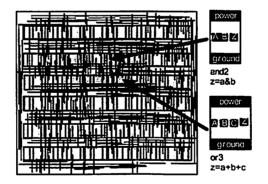

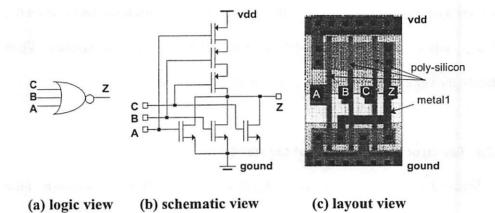

#### 3.2.1. The structure and usage of the standard-cell

Figure 3.1 shows a typical standard-cell (three-input NOR). It is shown in the layout view that a power stripe (vdd) is laid out horizontally at the top of the cell and a ground stripe is at the bottom. The PMOS transistors in the schematic view are placed in the upper half of the cell layout and the NMOS transistors in the lower half. The input pins, which are normally placed halfway between the power and ground stripes, connect to vertical poly-silicon lines that control the PMOS and NMOS transistors. Most library cells occupy the poly-silicon layer and the metal 1 layer, and all the pins are on metal 1. The power and ground stripes are also on metal 1. The width of a standard-cell is mainly determined by the complexity of the schematic and the driving capacity. Simple and weak cells are usually narrow.

Figure 3.1: A typical standard-cell (three-input NOR).

Figure 3.2: The usage of the standard-cells.

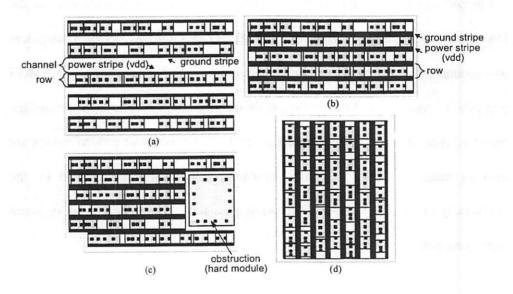

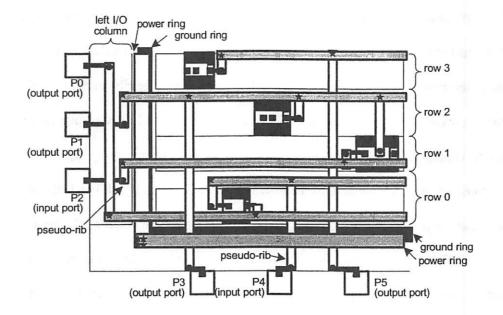

The usage of the standard-cell is shown in Figure 3.2. In Figure 3.2(a), cells are placed in a rectangular region which is sliced horizontally into rows. The

height of a row is the same as the height of the library cells. In the early days of the standard-cell design, as shown in Figure 3.2(a), the rows were split by channels in which wires are routed to connect the cells. The cells in a row may not be seamlessly placed, and they can only be X-flipped. However to supply power to all the cells in the row, a power stripe, which is on metal 1, extends along the entire row. So does the ground stripe. In this sense, the power and ground stripes on the cells can be regarded as power and ground pins. Power stripes of all the rows are connected on the left and/or right side of the rows; so are the ground stripes. As more metal layers become available for routing, rows can be vertically abutted and routing only takes place above the cells. Note that to abut two adjacent rows, the cells in one row must all be Y-flipped such that their power (or ground) pins are compatible with the power (or ground) of the abutted row. A simple approach to this is to let all even numbered rows, thus the cells placed in these rows, be Y-flipped. Modern physical design tools even allow cells to be placed in a non-rectangular region and obstructions like hard modules may exist in the region, as shown in Figure 3.2(c). The whole layout can be rotated, as shown in Figure 3.2(d), such that rows look like columns. As a convention, we call the columns "vertical rows", and the normal layout configuration "horizontal rows".

Finally the term "area utilization" is defined. It is basically the ratio of pure cell area and the layout area. The utilization is no greater than 1. Even in the abutted-row case, the area utilization cannot get very close to 1 for two reasons. One is that the widths of the cells are fixed. When cells are placed in a row, they may not fully occupy the row. But of course one row in the layout may have all cells in it placed without white space, and that row determines the row width of the layout. The other rows may not have 100% utilization. The other reason is that sometimes gaps must be created between the cells just to increase the layout area such that more routing resources are allocated. Therefore, especially in the abutted-row case, neither layout area nor utilization is a direct goal.

The standard-cell design flow includes three stages. The first stage, called logic synthesis, generates a netlist of cells which instantiate library cells. The next two stages, usually called the physical design, is to place the cells in rows (placement) and then to make the interconnections of the cells (routing). The existing design methodology for standard-cell is discussed in the next subsection. After that, we will present a new physical design algorithm for standard-cell, in which placement and routing are integrated.

## 3.2.2. Existing design methodology for the standard-cell

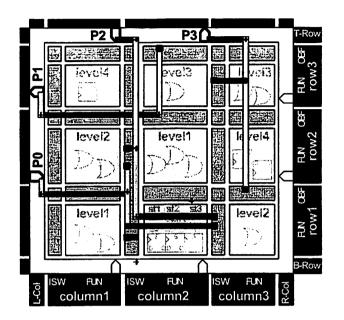

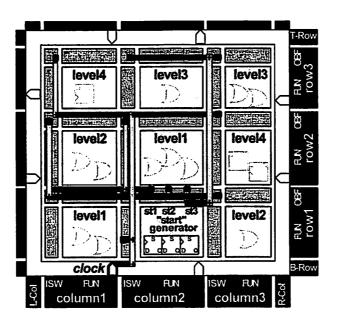

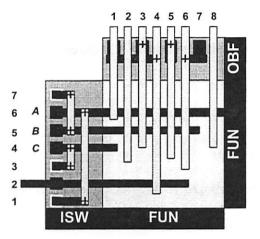

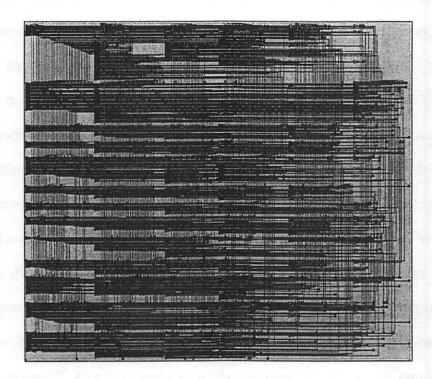

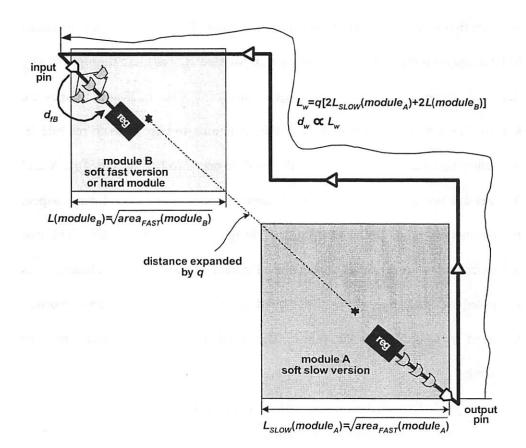

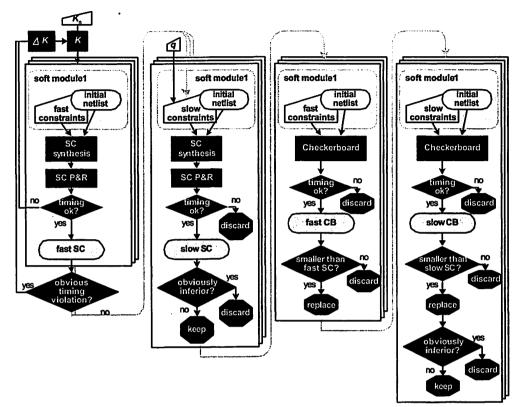

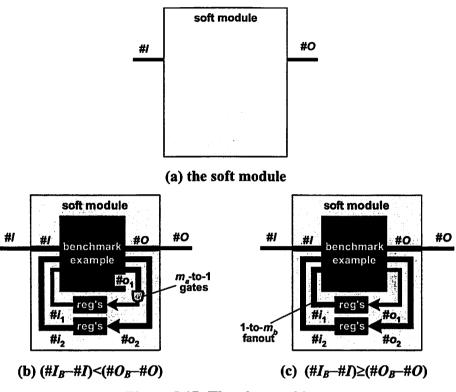

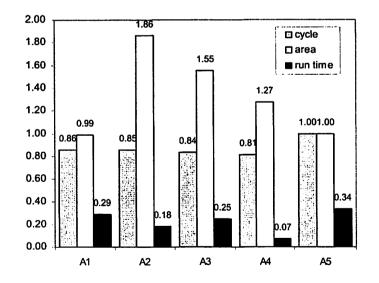

A typical standard-cell design flow is shown in Figure 3.3. Logic synthesis, including a technology independent stage and a technology dependent stage, translates the input design description into a netlist of library cells [BRAY90, SENT92]. Technology dependent transformation is widely known as technology