Copyright © 2004, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### ULTRA LOW POWER ROBUST DESIGN FOR NANOMETER CMOS TECHNOLOGY: PROCESS, CIRCUIT AND ARCHITECTURE PERSPECTIVES

by

Ruth Ann Wang

Memorandum No. UCB/ERL M05/3

20 December 2004

### ULTRA LOW POWER ROBUST DESIGN FOR NANOMETER CMOS TECHNOLOGY: PROCESS, CIRCUIT AND ARCHITECTURE PERSPECTIVES

by

Ruth Ann Wang

Memorandum No. UCB/ERL M05/3

20 December 2004

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## Ultra Low Power Robust Design for Nanometer CMOS Technology Process, Circuit and Architecture Perspectives

Ruth Ann Wang University of California, Berkeley Department of Electrical Engineering and Computer Sciences

December 20, 2004

### Ultra Low Power Robust Design for Nanometer CMOS Technology: Process, Circuit and Architecture Perspectives by Ruth Ann Wang

### **Research Project**

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, in partial satisfaction of the requirements for the degree of Master of Science, Plan II.

Approval for the Report and Comprehensive Examination:

**Committee:** Professor Jan Rabaey Research Advisor 12/13 04 Date 4

Professor Robert Brayton Second Reader

<u>12 | 15 | 0 4</u> Date

### Ultra Low Power Robust Design for Nanometer CMOS Technology: Process, Circuit and Architecture Perspectives

Copyright 2004

by Ruth Ann Wang

.

## Abstract

VLSI designs for wireless applications have increasingly relied on aggressive voltage and device size scaling in order to achieve reductions in area, cost and power dissipation. However, as the power supply voltage decreases and device sizes scale into the nanometer regime, fluctuations in environmental and physical factors become more difficult to control. Variations in supply voltage, transistor gate length and threshold voltage increase in proportion to their respective nominal values, causing a widened overall distribution of values for all performance metrics, particularly gate propagation delay. Consequently, traditional worst case design leads to prohibitively large delay overheads at ultra low supply voltages. This work investigates a novel timing methodology that designs for variation-induced timing errors, using robust design techniques to ensure proper system functionality. Monte Carlo simulation environments are used to simulate variability in circuit performance metrics by subjecting process and operating parameters to controlled fluctuation levels. The resulting robustness of circuits is evaluated and techniques of supply and threshold voltage scaling are studied to explore trade-offs between yield and energy. Furthermore, individual parameter contributions to delay variability are isolated in order to identify potential sources of improvement in manufacturing processes. Finally, a fault tolerant approach to finite state machine design is proposed and studied using MVSIS, in which transistor-level timing errors are modeled as faulty system behavior.

## **Table of Contents**

| Ał | ostra | :t                                                     | 1   |

|----|-------|--------------------------------------------------------|-----|

| Li | st of | Figures                                                | iii |

| Li | st of | Tables                                                 | vii |

| Ac | knov  | vledgments                                             | ix  |

| 1  | Mot   | ivation: Ultra Low Power                               | 1   |

| 2  | Pro   | cess/Circuits Co-Design: Energy-Delay Tradeoffs        | 7   |

|    | 2.1   | Sources of Delay Variability                           | 7   |

|    |       | 2.1.1 Delay Sensitivity to Operating Voltage           | 8   |

|    |       | 2.1.2 Delay Sensitivity to Physical Process Parameters | 9   |

|    | 2.2   | Previous Research                                      | 10  |

|    | 2.3   | Experimental Setup                                     | 12  |

|    |       | 2.3.1 Monte Carlo Simulation Framework                 | 12  |

|    |       | 2.3.2 Circuits Under Study                             | 17  |

|    | 2.4   | Statistical Analysis Model                             | 20  |

|    |       | 2.4.1 Lognormal Distribution                           | 20  |

|    |       | 2.4.2 Least Sum of Squares Error                       | 21  |

|    |       | 2.4.3 Fitted Distribution Curves                       | 22  |

|    |       | 2.4.4 Performance-Based Yield Definition               | 23  |

|    | 2.5   | Simulations and Results                                | 27  |

|    |       | 2.5.1 $V_{dd}$ and $V_{th}$ Optimization               | 27  |

|    |       | 2.5.2 Yield-Energy Tradeoffs                           | 31  |

|    | 2.6   |                                                        | 34  |

|    |       | 2.6.1 Future Work                                      | 35  |

| 3  | Pro   | cess/Circuits Co-Design: Power and Delay Variability   | 39  |

|    | 3.1   | Experimental Setup                                     | 41  |

|    |       | 3.1.1 Monte Carlo Simulation Framework                 | 41  |

|    |       | 3.1.2 Circuits Under Study                             | 45  |

|    | 3.2   | Result  | S                                                | 57 |

|----|-------|---------|--------------------------------------------------|----|

|    |       | 3.2.1   | Delay and Power Variability                      | 57 |

|    |       | 3.2.2   | Individual Parameter Contributions               | 63 |

|    |       | 3.2.3   | Discussion                                       | 67 |

|    | 3.3   | Future  | Work                                             | 68 |

| 4  | Arc   | hitectu | re Study: Robust Design of Finite State Machines | 71 |

|    | 4.1   | Previo  | us Research                                      | 74 |

|    | 4.2   | Propos  | sed Solution                                     | 75 |

|    | 4.3   | -       | mental Setup                                     | 77 |

|    |       | 4.3.1   | FSM Under Study                                  | 77 |

|    |       | 4.3.2   | Modeling Tool: MVSIS                             | 79 |

|    |       | 4.3.3   | Error Correction Scheme                          | 82 |

|    |       | 4.3.4   | Error Injection Scheme                           | 84 |

|    | 4.4   | Results | · · · · · · · · · · · · · · · · · · ·            | 88 |

|    |       | 4.4.1   | Repairing Faulty Output Values                   | 88 |

|    |       | 4.4.2   | Repairing Undesired State Transitions            | 89 |

|    | 4.5   | Future  | Work                                             | 91 |

| 5  | Con   | clusion | L                                                | 93 |

| Bi | bliog | raphy   |                                                  | 97 |

|    |       |         |                                                  |    |

ii

## List of Figures

|      | THE A Line for law never operation (2003)                                                                          | 4        |

|------|--------------------------------------------------------------------------------------------------------------------|----------|

| 1.1  | ITRS scaling projections for low power operation (2003). $\ldots$                                                  | -        |

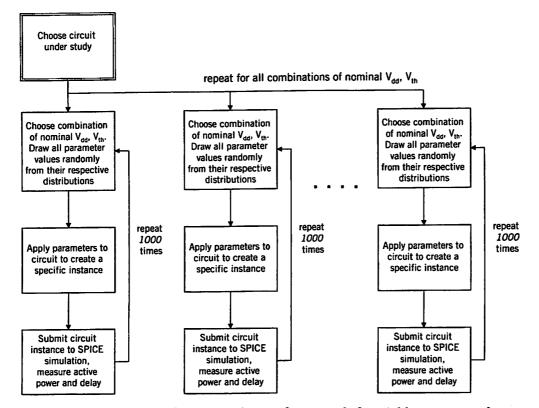

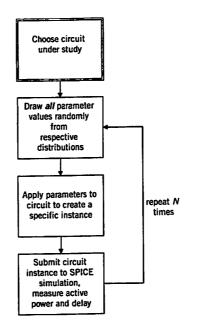

| 2.1  | Monte Carlo simulation framework for yield-energy study.                                                           | 16       |

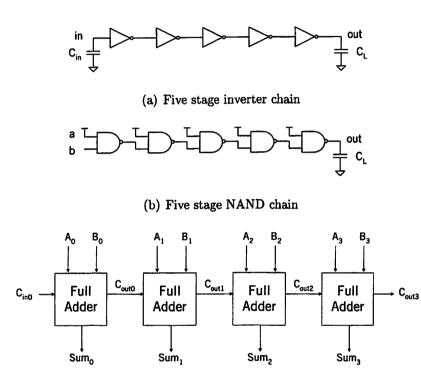

| 2.2  | Block diagrams for representative circuits under study.                                                            | 18       |

| 2.2  | (a) Five stage inverter chain                                                                                      | 18       |

|      | (b) Five stage NAND chain                                                                                          | 18       |

|      | (c) Four-bit ripple carry adder                                                                                    | 18       |

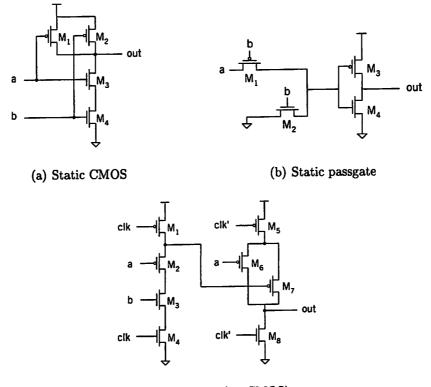

| 2.3  | Five stage NAND chain implementations.                                                                             | 19       |

| 2.0  | (a) Static CMOS $\ldots$          | 19       |

|      | (b) Static passgate                                                                                                | 19       |

|      | (c) $\rightarrow$ Dynamic ( <i>np</i> -CMOS)                                                                       | 19       |

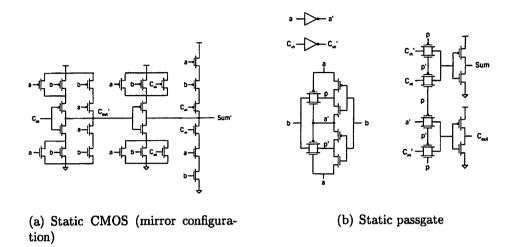

| 2.4  | Four-bit adder implementations.                                                                                    | 20       |

|      | (a) Static CMOS (mirror configuration)                                                                             | 20       |

|      | (b) Static passgate                                                                                                | 20       |

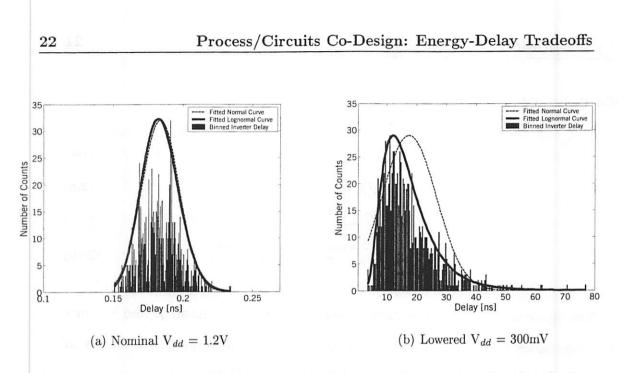

| 2.5  | Comparison of fitting normal and lognormal curves to delay distribu-                                               |          |

|      | tion of inverter chain. $\ldots$                                                                                   | 22<br>22 |

|      | (a) Nominal $V_{dd} = 1.2V$                                                                                        | 22<br>22 |

|      | (b) Lowered $V_{dd} = 300 \text{mV} \dots \dots$ | 22       |

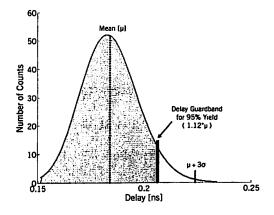

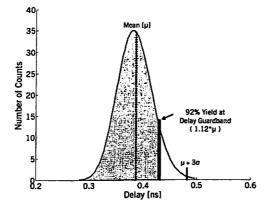

| 2.6  | Performance-based yield definition based upon inverter chain under                                                 | 24       |

|      | nominal conditions.                                                                                                | 24<br>25 |

| 2.7  | Yield of inverter chain under lowered $V_{dd}$ .                                                                   | 20<br>26 |

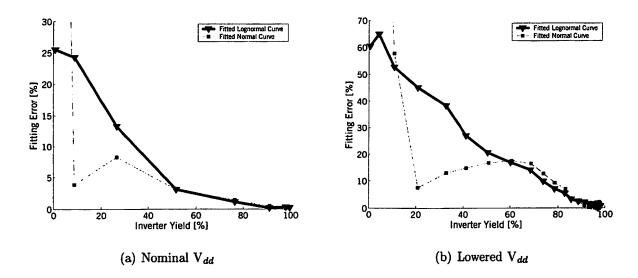

| 2.8  | Fitting error between inverter data and normal and lognormal curves.                                               | 20<br>26 |

|      | (a) Nominal $V_{dd}$                                                                                               | 20<br>26 |

|      | (b) Lowered $V_{dd}$                                                                                               | 20       |

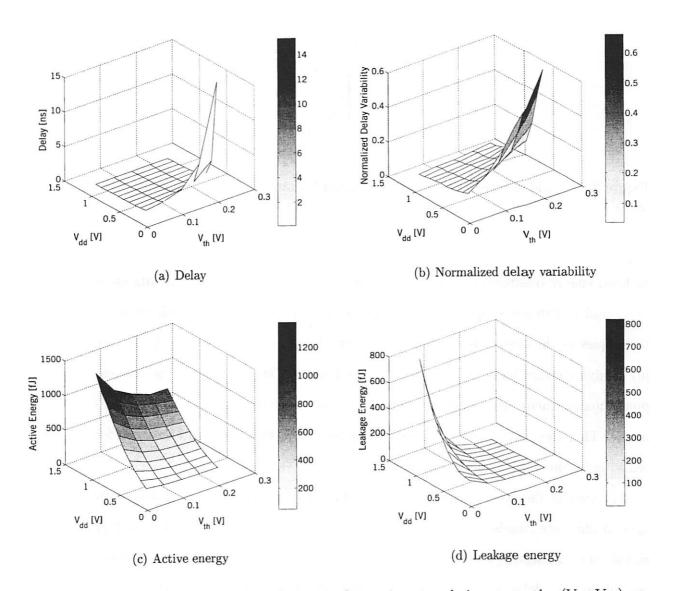

| 2.9  | Surface plots of performance for an inverter chain across the $(V_{dd}, V_{th})$                                   | 29       |

|      | design space.                                                                                                      | 29       |

|      | (a) Delay $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                      | 29       |

|      | (b) Normalized delay variability                                                                                   | 29       |

|      | (c) Active energy $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                   | 29       |

|      | (d) Leakage energy                                                                                                 | 30       |

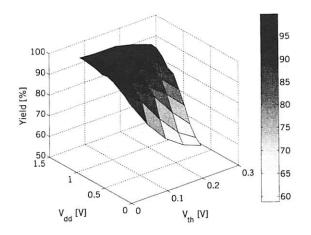

| 2.10 | ) Yield of inverter chain under lowered $V_{dd}$ and $V_{th}$                                                      | 31       |

| 2.11 | Circuit level yield dependence on $v_{dd}$ , $v_{th}$ of an inverter chain.                                        |          |

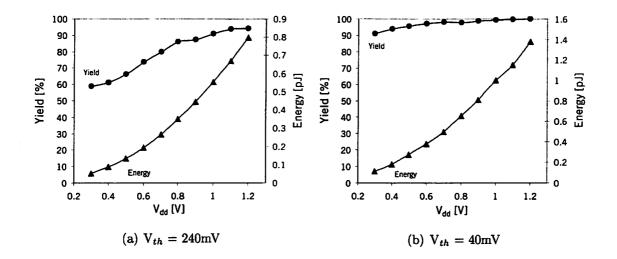

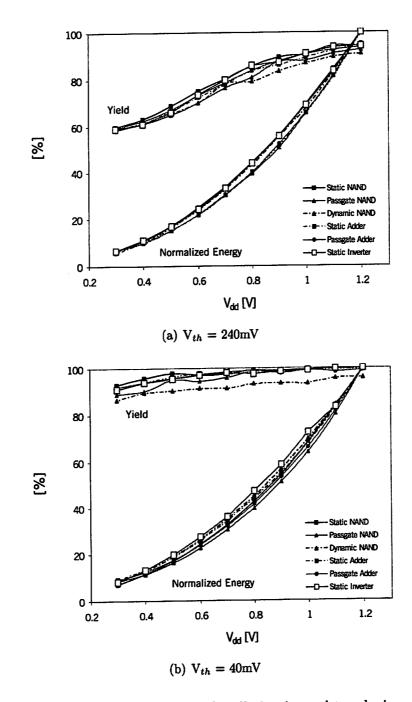

| 2.12       | Yield                   | l-energy tradeoffs for inverter chain at nominal and reduced $V_{th}$ .                                                                              | 32 |

|------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | (a)                     | $V_{th} = 240 \text{mV}$                                                                                                                             | 32 |

|            | (b)                     | $\mathbf{V}_{th} = 40 \mathrm{mV} \dots \dots$ | 32 |

| 2.13       | Yield                   | l degradation trends for all circuits and topologies evaluated.                                                                                      | 33 |

| 2.10       | (a)                     | $V_{th} = 240 \text{mV}$                                                                                                                             | 33 |

|            | (b)                     | $\mathbf{V}_{th} = 40 \mathrm{mV} \dots \dots$ | 33 |

|            | (-)                     |                                                                                                                                                      |    |

| 3.1        |                         | te Carlo simulation I: All parameters varying                                                                                                        | 43 |

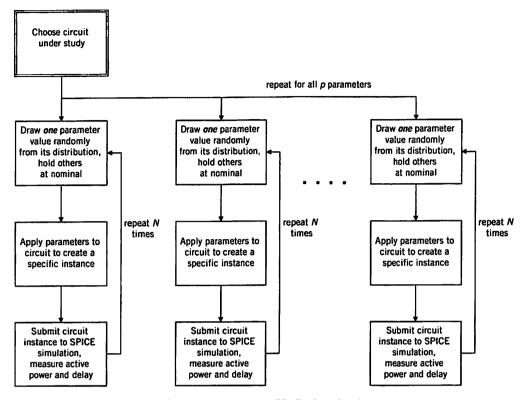

| 3.2        |                         | te Carlo simulation II: Individual parameters varying.                                                                                               | 44 |

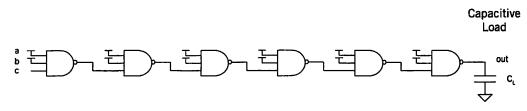

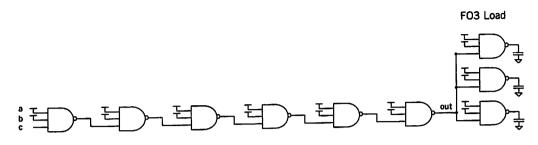

| 3.3        | NAN                     | D chain with static capacitive loading.                                                                                                              | 46 |

| 3.4        | NAN                     | D chain with FO3 loading.                                                                                                                            | 47 |

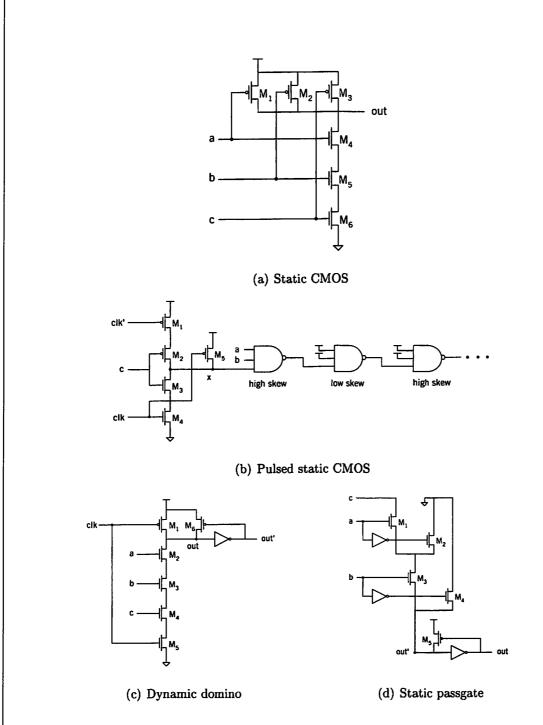

| <b>3.5</b> | Thre                    | e-input NAND gate implemented in various logic evaluation styles.                                                                                    | 48 |

|            | (a)                     | Static CMOS                                                                                                                                          | 48 |

|            | (b)                     | Pulsed static CMOS                                                                                                                                   | 48 |

|            | (c)                     | Dynamic domino                                                                                                                                       | 48 |

|            | (d)                     | Static passgate                                                                                                                                      | 48 |

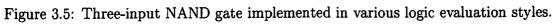

| 3.6        | Mano                    | chester carry chain for ripple carry adder.                                                                                                          | 51 |

|            | (a)                     | Static implementation                                                                                                                                | 51 |

|            | (b)                     | Dynamic implementation                                                                                                                               | 51 |

| 3.7        | · ·                     | en-bit, logarithmic carry select adder.                                                                                                              | 51 |

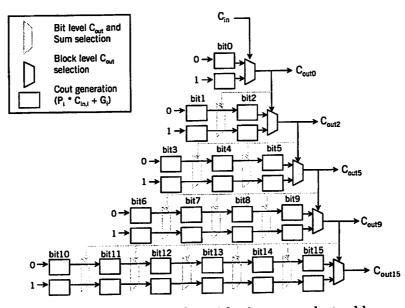

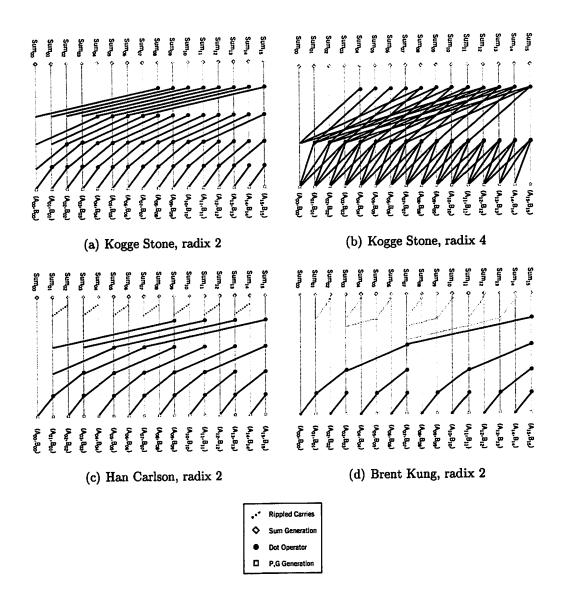

| 3.8        |                         | bus carry lookahead tree architectures for a 16-bit adder                                                                                            | 53 |

|            | (a)                     | Kogge Stone, radix 2                                                                                                                                 | 53 |

|            | (b)                     | Kogge Stone, radix 4                                                                                                                                 | 53 |

|            | (c)                     | Han Carlson, radix 2                                                                                                                                 | 53 |

|            | (d)                     | Brent Kung, radix 2                                                                                                                                  | 53 |

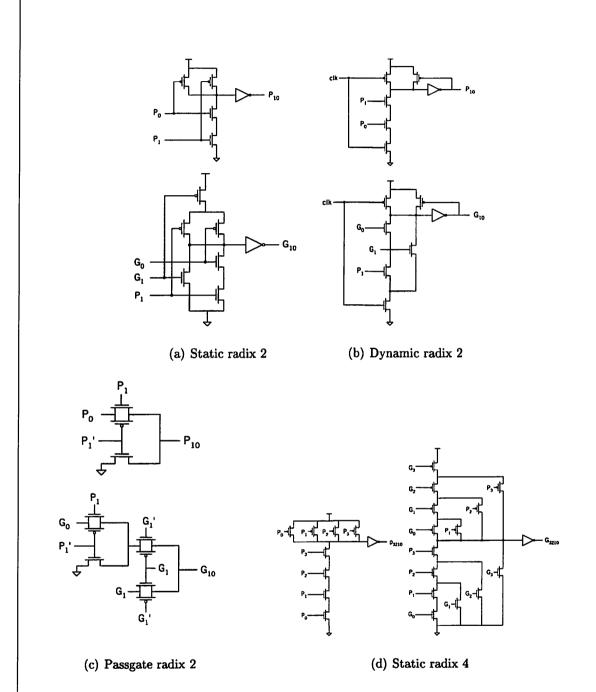

| 3.9        | • •                     | it implementations of dot operators used in carry lookahead trees.                                                                                   | 54 |

| ••••       | (a)                     | Static radix 2                                                                                                                                       | 54 |

|            | (b)                     | Dynamic radix 2                                                                                                                                      | 54 |

|            | (c)<br>(c)              | Passgate radix 2                                                                                                                                     | 54 |

|            | (d)                     | Static radix 4                                                                                                                                       | 54 |

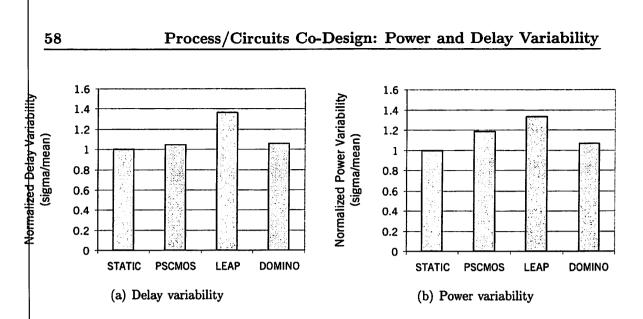

| 3.10       |                         | alized performance variabilities of NAND chain with static ca-                                                                                       |    |

| 0.10       |                         | ive loading.                                                                                                                                         | 58 |

|            | (a)                     | Delay variability                                                                                                                                    | 58 |

|            | ( <sup>w</sup> )<br>(b) | Power variability                                                                                                                                    | 58 |

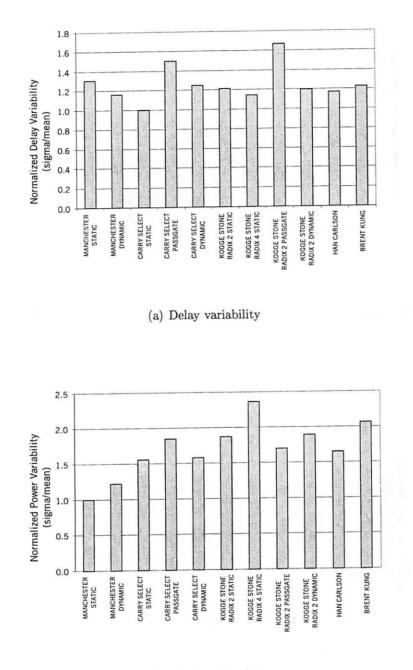

| 3.11       | · ·                     | alized performance variabilities of 16-bit adders.                                                                                                   | 61 |

| 0.11       | (a)                     | Delay variability                                                                                                                                    | 61 |

|            | (b)                     | Power variability                                                                                                                                    | 61 |

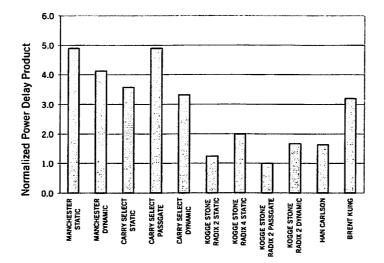

| 3 1 2      | · /                     | alized power delay product of 16-bit adders.                                                                                                         | 62 |

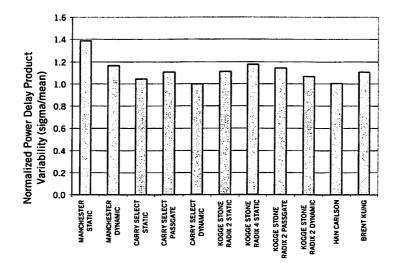

|            |                         | alized power delay product variability of 16-bit adders.                                                                                             | 62 |

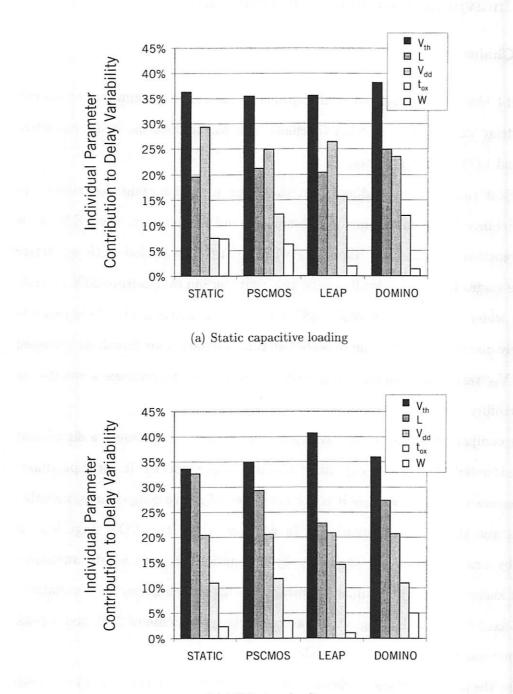

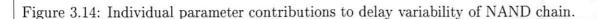

|            |                         | idual parameter contributions to delay variability of NAND chain.                                                                                    | 64 |

| 0.14       | (a)                     | Static capacitive loading                                                                                                                            | 64 |

|            |                         | FO3 stage loading                                                                                                                                    | 64 |

|            | (b)                     | I. OD SPARE MAUTIR                                                                                                                                   | 04 |

\_\_\_\_\_

### LIST OF FIGURES

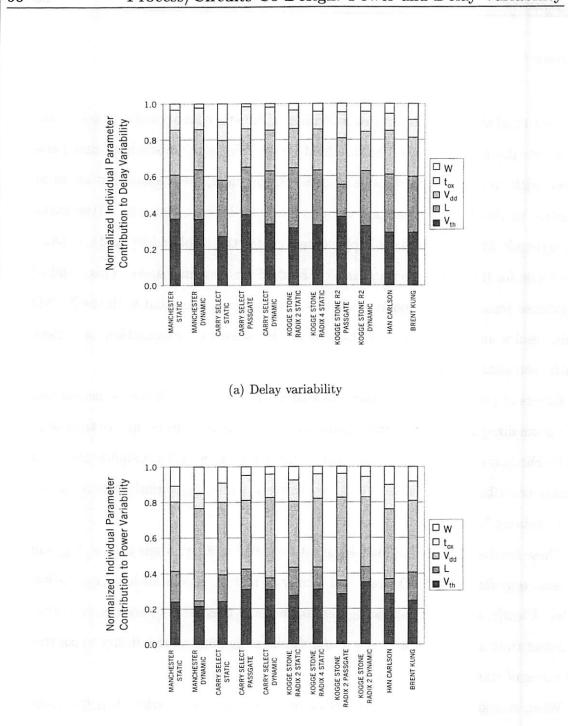

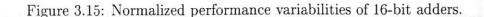

| 3.15 | Normalized performance variabilities of 16-bit adders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66 |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|      | (a) Delay variability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66 |  |

|      | (b) Power variability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66 |  |

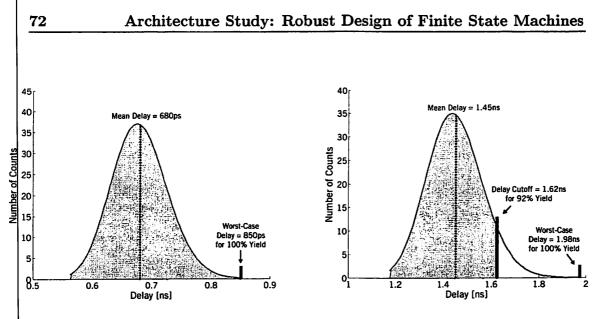

| 4.1  | Fitted lognormal distributions to delay data for static adder at nominal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |  |

|      | and reduced voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72 |  |

|      | (a) Nominal voltages: $V_{dd} = 1.2V, V_{th} = 240mV$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72 |  |

|      | (b) Reduced voltages: $V_{dd} = 300 \text{mV}, V_{th} = 40 \text{mV} \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72 |  |

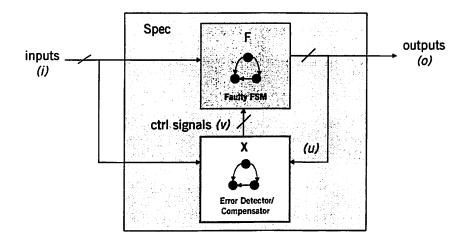

| 4.2  | Topology of proposed error compensation scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76 |  |

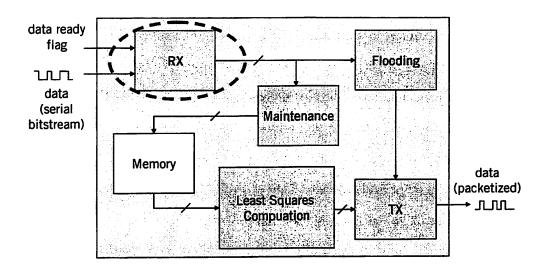

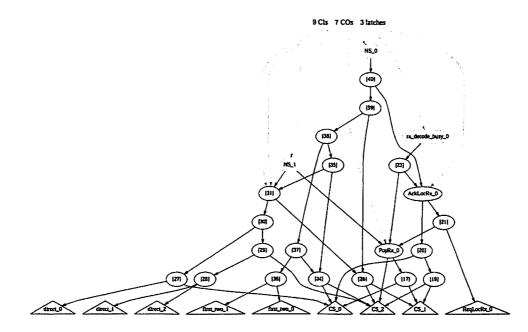

| 4.3  | The second |    |  |

|      | charm chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78 |  |

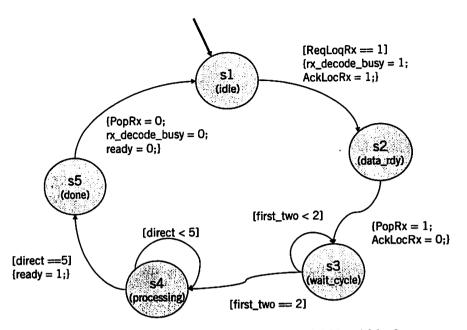

| 4.4  | State transition diagram of RX subblock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79 |  |

| 4.5  | Behavioral representation of RX controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81 |  |

| 4.6  | Structural representation of RX controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82 |  |

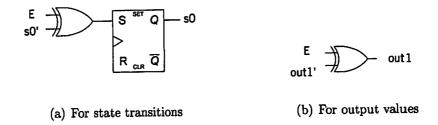

| 4.7  | Methods for adding error control at the structural level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83 |  |

|      | (a) For state transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83 |  |

|      | (b) For output values $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83 |  |

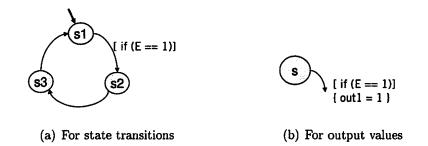

| 4.8  | Methods for adding error control at the behavioral level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84 |  |

|      | (a) For state transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84 |  |

|      | (b) For output values $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84 |  |

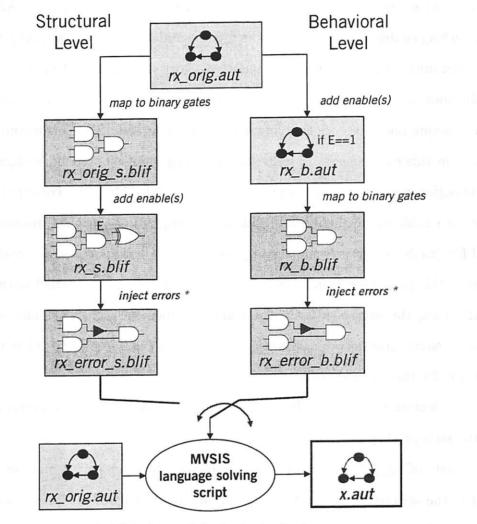

| 4.9  | MVSIS-based simulation flow describing the method of comparing be-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |

|      | havioral and structural level error compensation schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 85 |  |

.

## List of Tables

| 2.1 | Technology specifications for parameters varied in Monte Carlo simu-    | 1 5 |

|-----|-------------------------------------------------------------------------|-----|

|     | lation. $\ldots$                                                        | 15  |

| 2.2 | Summary of inverter chain performance for nominal and reduced voltages. | 28  |

| 4.1 | MVSIS synthesis algorithm to produce an optimized structural repre-     |     |

|     | sentation from a behavioral specification.                              | 81  |

| 19  | MVSIS results: Repairing outputs.                                       | 89  |

| 4.2 | Wysis results. Repairing outputs                                        | 89  |

| 4.3 | MVSIS results: Repairing state transitions at the structural level      |     |

| 4.4 | MVSIS results: Repairing state transitions at the behavior level        | 90  |

.

## Acknowledgments

I would like to thank my advisor, Professor Jan Rabaey, for his guidance and support throughout the years.

I am grateful to Professor Robert Brayton and Alan Mishchenko for offering EE290N during the Spring of 2004 and spending office hours twice a week teaching me everything I know about MVSIS.

Thanks to members of the YODA group at the Berkeley Wireless Research Center: Yu Cao, Huifang Qin, Liang-Teck Pang, Paul Friedberg and Professor Andrei Vladimirescu, for their ideas and invaluable feedback.

To my mentors Kerry Bernstein and Dale Pearson.

To Nancy B. Green, who still has the binary half-adder that I built in my high school physics class.

Thank you Mom, Dad and Chris, for a lifetime of love and support.

and Brian Otis, for being a source of constant inspiration, always.

# Chapter 1 Motivation: Ultra Low Power

Despite forecasts in the 1970s proclaiming that the scaling of integrated circuits (ICs) would not succeed beyond critical dimensions of  $0.5 \mu m$  [1], the state of the art has accelerated well into the nanometer regime with unprecedented momentum. Presentday low power application drivers, such as truly ambient intelligent systems and highly energy-efficient sensor networks, have increasingly pushed technology innovation and motivated research thrusts to realize novel design techniques. In particular, the VLSI designs for these applications have combined aggressive device and voltage scaling techniques to achieve reductions in power, area and cost, with extremely high levels of integration.

The challenge of reducing the power consumption of a system is a primary concern for designers, and is especially critical as device sizes and form factors continue to scale. The total power dissipation in a digital CMOS circuit design is attributed to two primary sources of current flow: static leakage current and active switching current. Leakage current is lost through resistive paths between voltage supply and ground, leading to static power dissipation, which may be described as follows [2, 3]:

$$P_{static} \propto I_s \cdot exp\left[\frac{-(V_{th} - \gamma V_{dd})}{S}\right] \cdot V_{dd}$$

(1.1)

where  $I_s$  is the zero-threshold leakage current,  $V_{th}$  is the threshold voltage,  $V_{dd}$  is the supply voltage, S is the subthreshold slope and  $\gamma$  is a fitted parameter modeling the effects of drain-induced barrier lowering (DIBL).

While the circuit is active and signals are dynamically switching, current is alternately drawn from and pulled into the supply rails in order to charge and discharge capacitive loads. The total active power dissipated is the amount of energy consumed for each switching operation, with switching energy defined as follows [3]:

$$E_{active} = \alpha \cdot C_L \cdot V_{dd}^2 \tag{1.2}$$

where  $\alpha$  represents the average activity factor of gates that compose the design,  $C_L$  represents the total load capacitance, and  $V_{dd}$  is the operating supply voltage. The total dynamic power consumed is determined by the frequency f with which the switching operations are performed:

$$P_{dynamic} = \alpha \cdot C_L \cdot V_{dd}^2 \cdot f \tag{1.3}$$

Among the diverse field of applications for ultra low power CMOS designs, one primary application of this work is in the emerging space of wireless sensor networks. These low power systems may be used for a wide range of military, medical and environmental monitoring applications, and are the focus of study for researchers at the Berkeley Wireless Research Center at the University of California, Berkeley. The behavioral model of an ultra low power sensor node contains two states: idle and processing. Each node is primarily in the idle state until an event is detected, such as the arrival of a data packet, at which point the circuits are activated for data processing. After this burst of activity, the system returns again to its idle state and remains there until the next event occurs. Because wireless sensor networks are characterized by long periods of inactivity, highly efficient power management techniques may be implemented that eliminate static leakage current (e.g. disconnecting circuits from the power supply [4]) while the system idles. Therefore, while total power consumption is the sum of both static and dynamic components, this work focuses on reducing dynamic power dissipation because it is assumed that high levels of static leakage power are mitigated by system-level techniques.

It is clear from Equations (1.1) and (1.3) that one of the most effective techniques for reducing total power in a CMOS design is by reducing the supply voltage. Specifically, when considering only the dynamic component, power dissipation falls quadratically with  $V_{dd}$ , suggesting that significant reductions in power consumption may be achieved with relatively small decreases in the supply voltage.

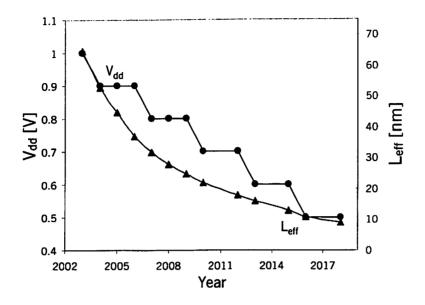

The technique of scaling supply voltage in low power designs is combined with the scaling of device sizes, which reduces capacitive loading as well as circuit area, further reducing power consumption and form factors. Near- and long-term trends in the scaling of supply voltage and effective gate length  $(L_{eff})$  for digital circuits in low power operation have been projected by the International Technology Roadmap for Semiconductors (ITRS) [5] and are shown in Figure 1.1.

These scaling predictions indicate that within the next two decades, supply voltages will reduce to 500mV, while effective gate lengths will shrink as low as 9nm. This combination of aggressive scaling techniques, with critical dimensions nearing the atomic scale of angstroms  $(10^{-10} \text{ m})$ , induces increased variation in circuit designs, a problem that remains largely unresolved. Topping the 2003 ITRS list of most difficult challenges for sub-20nm CMOS transistor designs are the fundamental issues associated with atomic-level, statistical process fluctuations; process imperfections become more difficult to control as physical parameters scale, leading to a wider

Figure 1.1: ITRS scaling projections for low power operation (2003).

spread of manufactured device parameters. Further contributing to this physical variability source are environmental factors, such as increased noise in power supply voltages and changes in operating temperature. According to industrial predictions and observations in deep submicron designs, variations in  $L_{eff}$  were projected to increase from 30% to nearly 50% across the span of three technology generations [6]. Variations in  $V_{dd}$  and  $V_{th}$  were also projected to rise, both from 10% to 15%. The combination of increased variability in both physical device parameters and circuit operational conditions leads to a widening distribution of values for all performance metrics.

With circuit behavior increasingly less predictable as technology scales, a new, robust circuit design methodology is of paramount importance to the success of future nanometer designs. A *robust* product or process is defined as:

[one that] performs properly even in the presence of uncontrolled variation

that may affect performance, such as manufacturing variations, operating conditions, and product deterioration. [7]

When applied to ultra low power circuits, robust design refers to the variationaware design methodologies required to ensure proper functionality across all worstcase parameter corners. To ensure the most effective approach to robust design, these techniques should be considered at all layers of the system design hierarchy: from low levels of manufacturing and process control, to intermediate levels of transistor, circuit and logic design, ultimately reaching the highest levels of architecture, algorithm, and system organization.

The objective of this work is to investigate the robust design of ultra low power CMOS circuits, which operate under aggressively scaled supply voltages and comprise nanometer-scale transistors. The research is performed while considering process, circuit and architecture perspectives, and is described in three parts. First, the impact of parameter variations on circuit performance is investigated in Chapter 2 using a SPICE simulation environment in 130nm bulk CMOS technology. Next, Chapter 3 details the extension of this study to an industrial, 90nm partially depleted siliconon-insulator (pd-SOI) technology, in which robust design is also approached from a manufacturing and process control perspective. Chapter 4 explores the impacts of parameter variability on higher layers of the design hierarchy, with a focus on techniques for robust finite state machine design. Finally, Chapter 5 offers concluding remarks and directions for future work.

## Chapter 2

## Process/Circuits Co-Design: Energy-Delay Tradeoffs

An understanding of the nature of errors that may occur in aggressively scaled, ultra low power digital circuits is crucial for building the foundations of a robustness study. Thus, the first step is to simulate a realistic environment in which circuits are operated under reduced supply voltages and subjected to variations in physical parameter values, in order to induce errors from fundamental sources. This study is performed in a standard bulk CMOS technology, and compares the robustness of a number of representative circuit blocks of varying complexity and implemented in a variety of logic styles. Physical and environmental sources of parameter variation are now introduced.

## 2.1 Sources of Delay Variability

The propagation delay of a transistor is related to its operating supply and threshold voltages, as well as the physical process parameters that define its intrinsic logic evaluation capability. Therefore, the scaling of operating voltage and physical dimensions affects raw values of transistor performance to a first-order, and also causes higher order effects, which manifest as performance variation. The extent to which delay is sensitive to these variations is extremely difficult to predict accurately; this section provides a basic intuition for understanding these relationships.

### 2.1.1 Delay Sensitivity to Operating Voltage

While the reduction of supply voltage leads to quadratic savings in active energy and power dissipation, it is known to increase both delay and delay variability [8]. To investigate this phenomenon, the delay of a logic gate is modeled by the following equation, which is based on the alpha power law [2, 3]:

$$\tau_d \propto \frac{V_{dd}}{(V_{dd} - V_{th})^{\alpha}} \tag{2.1}$$

where  $V_{dd}$  is the supply voltage,  $V_{th}$  is the operating threshold voltage and  $\alpha$  is a fitted parameter with a value between one and two, modeling the effects of velocity saturation.

It is clear from this relationship that raw values of delay will increase with reduced supply voltages, because the order of the denominator term is greater than the order of the numerator. Moreover, while the increased propagation delay poses challenges for maintaining competitive clock frequencies in future designs, the ability to control the range in which the delay varies is a substantially more crucial challenge. Tolerating an absolute, fixed delay offset is a trivial task when compared with designing for a spread of delays that may vary as widely as the nominal delay itself. To gain insight into the extent to which reduced supply voltage affects delay variability, the following definition for the sensitivity of gate delay with respect to  $V_{th}$  is presented:

$$S_{\tau_d}^{V_{th}} \triangleq \frac{\partial \tau_d}{\partial V_{th}} \tag{2.2}$$

Solving for the partial derivative of the gate delay with respect to  $V_{th}$  yields the following sensitivity of delay to threshold voltage:

$$\frac{\partial \tau_d}{\partial V_{th}} \propto -\alpha V_{dd} (V_{dd} - V_{th})^{-\alpha - 1} (-1)$$

$$= \frac{\alpha V_{dd}}{(V_{dd} - V_{th})^{\alpha + 1}}$$

(2.3)

$$\therefore \quad S_{\tau_d}^{V_{th}} \propto \frac{\alpha V_{dd}}{(V_{dd} - V_{th})^{\alpha + 1}} \tag{2.4}$$

As  $V_{dd}$  is lowered, the denominator term of this sensitivity relationship decreases at a greater rate than the numerator term, leading to exponentially higher  $V_{th}$  sensitivity at low supply voltages. This result confirms a known challenge to the continued success of digital design for future scaled generations: not only do absolute delay values increase with lowered supply voltages, but so does the variability of those delays. Adding to these variability levels are variations in physical parameters, which are now discussed.

### 2.1.2 Delay Sensitivity to Physical Process Parameters

The threshold voltage of a transistor is determined by physical parameters set by the manufacturing process and is affected by imperfections in process steps. The following expression is used to estimate the standard deviation of the manufactured threshold voltage from its mean design value [9]:

$$\sigma_{V_{th}} \propto \frac{t_{ox}\sqrt[4]{NT}}{\sqrt{W_{eff}L_{eff}}}$$

(2.5)

where  $t_{ox}$  is the thickness of the gate oxide, N is the channel doping density, T is the absolute temperature, and  $W_{eff}$  and  $L_{eff}$  are the effective width and length of the

transistor, respectively. Variations in these manufactured physical parameters induce variability in  $V_{th}$ , further contributing to variability in gate delay, as seen in Equation (2.4). Based upon the above delay sensitivity analysis, parameter variations in a design are attributed to two sources: fluctuations in environmental conditions ( $V_{dd}$ , T) and imperfections in physical device structure ( $L_{eff}$ ,  $t_{ox}$ , W and  $V_{th}$ ). Interactions between these distinct variation sources produce an increased spread of delays, relative to their nominal values. Methods for reducing the extent of this variability, including a metric for quantifying the impact of delay variability on performance-based yield, are the basis of this robustness study.

### 2.2 Previous Research

Previous work in the field of robust circuit design serves as background knowledge and provides directions for further study. This related body of research includes comparisons of performance between logic evaluation styles, studies on circuit delay variability for a range of process variations, and techniques for achieving robust low power design using threshold voltage optimization. After related work is introduced, the contributions of this work and corresponding experimental setup are discussed.

While numerous studies have compared circuits across complexity and logic evaluation style for metrics such as performance, power, and area, few have included a discussion of inherent robustness of logic topology to process parameter variations. In [10], standard delay-power tradeoffs were studied for various circuits, including full adders and 2-input NAND gates, implemented in both static CMOS and passgate logic. Results from HSPICE simulations showed static CMOS to be the more favorable topology for use in low power design, due to significant gains in power dissipation that outweigh its comparably lower performance. Although this work illustrated a rigorous technique for evaluating the tradeoff between power and speed in low power design, it did not include parameter variability as a significant factor affecting circuit performance. Thus, one direction for further investigation is to compare the relative robustness of various logic evaluation styles, when these designs are subjected to variations in operating and physical parameters.

Recent efforts to study the impacts of increased device parameter variations on circuit performance have treated only relatively simple circuits, typically implemented only in static CMOS. In [11], a Monte Carlo analysis was conducted for a 2-stage inverter chain in order to study the implications of worst-case variation for several physical and environmental parameters (including  $L_{eff}$ ,  $t_{ox}$ ,  $V_{dd}$  and  $V_{th}$ ). The resulting analysis confirmed the underlying challenge for scaled designs in the nanometer regime: as technology parameters are scaled, their variations increase relative to nominal values, thus exacerbating delay variability. While techniques of aggressive buffer insertion and careful wire sizing were suggested as a means for controlling excessive variability, circuit-level timing consequences were not discussed. An extension of this work was conducted in [12], with the inclusion of the more complex NAND chain in a similar variability investigation. However, all circuits in this study were implemented in static CMOS and thus the impact of circuit topology on delay distribution was not considered. Furthermore, while both studies confirmed the trend of increasing global delay variations with device size scaling, neither quantified the extent to which the increased variability may affect circuit timing methodologies.

Guidelines for achieving minimum power dissipation in a circuit while maintaining robustness to parameter variation were set in [13]. The technique of scaling  $V_{th}$  along with  $V_{dd}$  was found to improve performance under low voltage conditions. Furthermore, longer effective channel lengths were chosen in order to reduce variations in  $V_{th}$  and thus lower delay variability. The optimal voltage ranges used in this work were relatively high;  $V_{dd}$  was scaled to a minimum of 600mV while  $V_{th}$  values were chosen between 340mV – 450mV. Because these threshold and supply voltages were maintained near their nominal values, the spread of delay values was sufficiently contained such that a worst-case timing methodology was reasonable for determining the clock frequency. Thus, aggressively scaled voltages and their impact on increased delay variability were not explored.

Given the unknown design space and questions unaddressed by existing research, the focus of this work is to explore the field of robust circuit design for dramatically scaled voltages, across circuits of varying complexity and logic topology. Therefore, a set of representative circuits is designed and subjected to exhaustive Monte Carlo simulations, and the effects of parameter variations are investigated. The remainder of this chapter is organized as follows. Section 2.3 describes the simulation setup, including technology specifications and circuits under study. Section 2.4 discusses the statistical model used to analyze the simulation results and presents a performancebased yield metric to quantify tradeoffs between energy and delay for a given circuit. Results are presented in Section 2.5 and Section 2.6 concludes the analysis.

### 2.3 Experimental Setup

The experimental setup for this work is described in two parts: the Monte Carlo simulation framework and the various circuits under study.

### 2.3.1 Monte Carlo Simulation Framework