## Automated Mapping of Domain Specific Languages to Application Specific Multiprocessors

William Lester Plishker

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2006-123 http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-123.html

October 5, 2006

Copyright © 2006, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Automated Mapping of Domain Specific Languages to Application Specific Multiprocessors

by

William Lester Plishker

B.S. (Georgia Institute of Technology) 2000

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY

> Committee in charge: Professor Kurt Keutzer, Chair Professor Rastislav Bodik Professor Robert Cole

> > Fall 2006

## Automated Mapping of Domain Specific Languages to Application Specific Multiprocessors

Copyright 2006 by William Lester Plishker

#### Abstract

### Automated Mapping of Domain Specific Languages to Application Specific Multiprocessors

by

William Lester Plishker

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Kurt Keutzer, Chair

Application specific multiprocessors are capable of high performance implementations while remaining flexible enough to support a range of applications. Architects of these systems achieve high performance through domain specific optimizations such as multiple processing elements, dedicated logic, and specialized memory and interconnection. However, these features are often introduced at the expense of programming productivity. For application-specific programmable systems to succeed, it is necessary to deliver high performance implementations quickly. Three of the most important and time-consuming steps to arriving at implementations on these platforms are (1) to extract parallelism from applications descriptions, (2) to arrive at a model of the architecture, and (3) to map the parallelized application to the architectural model. We examine this problem for the networking domain and target a commercial family of network processors: Intel's IXP series. We propose and demonstrate a solution that starts with a domain specific language, which allows the extraction of parallelism without designer intervention. We show that high level application information enables optimizations and automated transformations to a task graph. A task graph is a model of an application that exposes its computation, data, and communication. The elements of the task graph can be mapped to processing elements, memory, and interconnect of the target architecture. We formulate the mapping problem as an integer linear programming (ILP) problem. We demonstrate that this method finds efficient solutions with fast run times on the data plane of network applications of different scales and complexity including IP forwarding, differentiated services, network address translation, and web switching. Using this design flow designers enjoy design times up to 3.5 times shorter than other new productive approaches. The resulting implementations are within 17% of hand mapped approaches. While the demonstration vehicle for this work has been network processing, we believe it will have wider applicability to other application domains that are starting to employ more single chip multiprocessing.

> Professor Kurt Keutzer Dissertation Committee Chair

To my parents,

whose support, wisdom, and love have made this all possible.

## Contents

| List of Figures |       |        |                                                         | v   |

|-----------------|-------|--------|---------------------------------------------------------|-----|

| Li              | st of | Tables | 5                                                       | vii |

| 1               | Intr  | oducti | ion                                                     | 1   |

|                 | 1.1   | Emerg  | ging Trends                                             | 2   |

|                 | 1.2   | Applic | eation Specific Multiprocessors                         | 6   |

|                 |       | 1.2.1  | Programming Application Specific Multiprocessors        | 8   |

|                 |       | 1.2.2  | Existing Common Design Flow                             | 14  |

|                 | 1.3   | Object | tives of Research                                       | 16  |

|                 | 1.4   | Organ  | ization of this Dissertation                            | 17  |

| <b>2</b>        | Net   | work I | Processing                                              | 19  |

|                 | 2.1   | Motiva | ation for Networking Focus                              | 20  |

|                 | 2.2   |        | rk Applications                                         | 21  |

|                 |       | 2.2.1  | IP Forwarding                                           | 24  |

|                 |       | 2.2.2  | Network Address Translation                             | 25  |

|                 |       | 2.2.3  | Differentiated Services                                 | 27  |

|                 |       | 2.2.4  | Web Switch                                              | 28  |

|                 | 2.3   | Netwo  | rk Processors                                           | 29  |

|                 |       | 2.3.1  | Intel IXP1200                                           | 31  |

|                 |       | 2.3.2  | Intel IXP2xxx                                           | 33  |

|                 |       | 2.3.3  | EZChip NP-2                                             | 33  |

|                 |       | 2.3.4  | Cisco SSP                                               | 35  |

|                 | 2.4   | Comm   | nercial Programming Environments for Network Processors | 35  |

|                 |       | 2.4.1  | Assembler                                               | 36  |

|                 |       | 2.4.2  | C-variants                                              | 38  |

|                 |       | 2.4.3  | ТејаNР                                                  | 39  |

|                 |       | 2.4.4  | Microblocks                                             | 42  |

|                 | 2.5   | Domai  | in Specific Languages                                   | 43  |

|                 |       | 2.5.1  | Click                                                   | 44  |

|   |       | 2.5.2 NesC                                                                                                                                                          |

|---|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

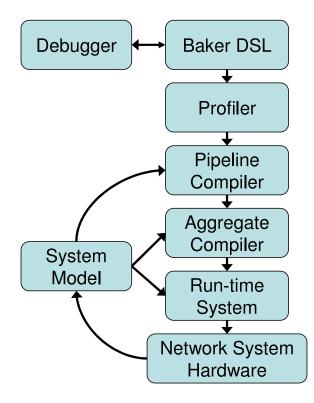

|   |       | 2.5.3 Baker                                                                                                                                                         |

|   | 2.6   | Networking Implementation Gap 48                                                                                                                                    |

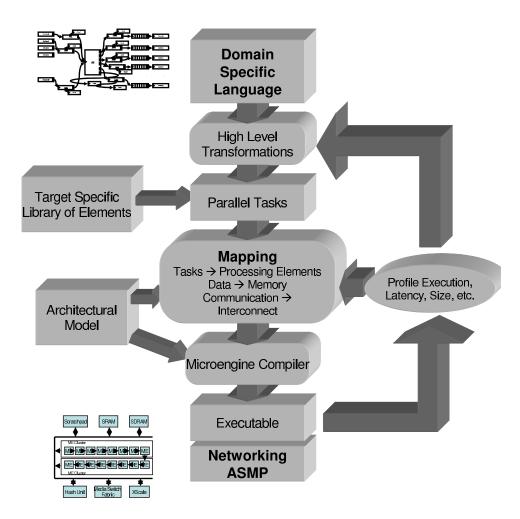

| 3 | Cro   | ssing the Networking Implementation Gap 50                                                                                                                          |

|   | 3.1   | Properties of an Ideal Solution                                                                                                                                     |

|   | 3.2   | Proposed Approach                                                                                                                                                   |

|   |       | 3.2.1 Domain Specific Language Application Representation 53                                                                                                        |

|   |       | 3.2.2 Application Level Transformations and Optimizations 55                                                                                                        |

|   |       | 3.2.3 Application Model                                                                                                                                             |

|   |       | 3.2.4 Architectural model                                                                                                                                           |

|   |       | 3.2.5 Mapping                                                                                                                                                       |

|   |       | 3.2.6 Code Generation and Compilation                                                                                                                               |

|   |       | 3.2.7 Feedback                                                                                                                                                      |

|   | 3.3   | Other solutions to crossing the implementation gap 60                                                                                                               |

|   |       | 3.3.1 SMP Click                                                                                                                                                     |

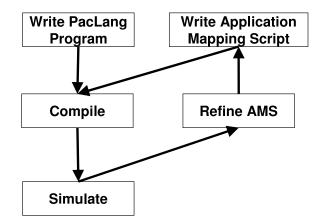

|   |       | 3.3.2 PacLang                                                                                                                                                       |

|   |       | 3.3.3 Shangri-La                                                                                                                                                    |

|   |       | 3.3.4 NP-Click                                                                                                                                                      |

|   |       | 3.3.5 Differences to this approach                                                                                                                                  |

|   | 3.4   | Summary                                                                                                                                                             |

| 4 | Λ 114 | omated Mapping 74                                                                                                                                                   |

| 4 | 4.1   | Motivation                                                                                                                                                          |

|   | 4.1   | Mapping Framework                                                                                                                                                   |

|   | 4.2   | 4.2.1 Integer Linear Programming                                                                                                                                    |

|   |       | 4.2.2 Pseudo-Boolean Problems                                                                                                                                       |

|   | 4.3   | Prior Mapping Work                                                                                                                                                  |

|   | 4.0   | 4.3.1 Existing Multiprocessor Mapping Approaches                                                                                                                    |

|   |       | 4.3.2 Existing Integer Linear Programming Approaches                                                                                                                |

|   | 4.4   | Application Model                                                                                                                                                   |

|   | 4.4   | 4.4.1       Tasks       87                                                                                                                                          |

|   |       | 4.4.2 Data                                                                                                                                                          |

|   |       | 4.4.2       Data                                                                                                                                                    |

|   | 4.5   | Architectural Model                                                                                                                                                 |

|   | 4.0   | 4.5.1       Processing elements       93                                                                                                                            |

|   |       | 4.5.2 Memory                                                                                                                                                        |

|   |       | 4.5.2 Interconnection                                                                                                                                               |

|   | 4.6   | Mapping Formulation                                                                                                                                                 |

|   | 4.0   | 4.6.1 Core Formulation                                                                                                                                              |

|   |       | 4.6.1       Core Formulation       99         4.6.2       IXP1200 Specific Constraints       102                                                                    |

|   |       | 4.6.3 IXP2xxx Specific Constraints                                                                                                                                  |

|   |       | $\pm 0.0$ $121 2 \text{AAA}$ optime constraints $\dots \dots \dots$ |

|              | 1 7                           | 4.6.4 User Constraints                                                                                                                                  | 107          |  |  |

|--------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|

|              | 4.7                           | Complexity Analysis                                                                                                                                     | 108          |  |  |

| <b>5</b>     | Application Transformations   |                                                                                                                                                         |              |  |  |

|              | 5.1                           | Motivation                                                                                                                                              | 112          |  |  |

|              | 5.2                           | Domain Specific Language Additions                                                                                                                      | 113          |  |  |

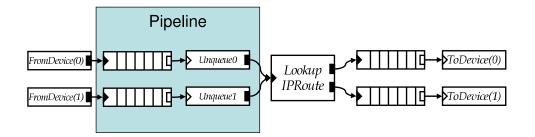

|              |                               | 5.2.1 Packet Distribution                                                                                                                               | 114          |  |  |

|              |                               | 5.2.2 Writing Library Elements                                                                                                                          | 115          |  |  |

|              | 5.3                           | Task Graph Generation                                                                                                                                   | 121          |  |  |

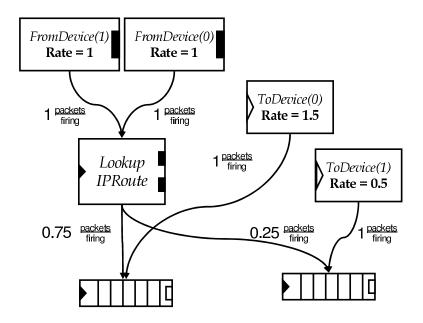

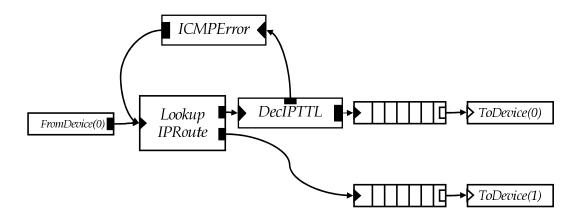

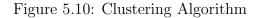

|              | 0.0                           | 5.3.1 Click Graph Notation                                                                                                                              | 126          |  |  |

|              |                               | 5.3.2 Task Graph Notation                                                                                                                               | 128          |  |  |

|              |                               | 5.3.3 Algorithms                                                                                                                                        | 130          |  |  |

|              | 5.4                           | -                                                                                                                                                       | 130          |  |  |

|              | 0.4                           | Optimizations                                                                                                                                           |              |  |  |

|              |                               | 5.4.1 Software Caching                                                                                                                                  | 140          |  |  |

|              |                               | 5.4.2 Retiming                                                                                                                                          | 147          |  |  |

|              |                               | 5.4.3 Replication                                                                                                                                       | 149          |  |  |

|              |                               | 5.4.4 Automated Optimizations                                                                                                                           | 152          |  |  |

| 6            | Eva                           | luation                                                                                                                                                 | 155          |  |  |

|              | 6.1                           | Metrics                                                                                                                                                 | 156          |  |  |

|              | 6.2                           | Test Benches                                                                                                                                            | 156          |  |  |

|              | -                             | 6.2.1 Simulators                                                                                                                                        | 156          |  |  |

|              |                               | 6.2.2 Profiling                                                                                                                                         | 157          |  |  |

|              |                               | 6.2.3 Solvers                                                                                                                                           | 157          |  |  |

|              | 6.3                           | Applications                                                                                                                                            | 157          |  |  |

|              | 0.5                           |                                                                                                                                                         | $150 \\ 159$ |  |  |

|              |                               | 8                                                                                                                                                       |              |  |  |

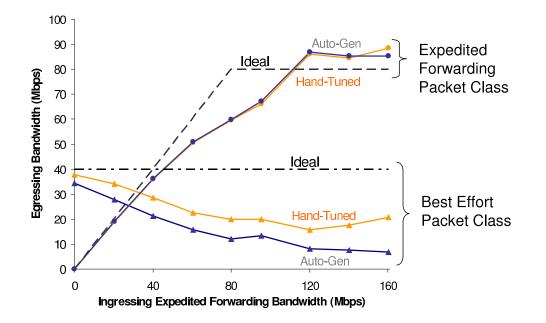

|              |                               | 6.3.2 Diffserv                                                                                                                                          | 168          |  |  |

|              |                               | 6.3.3 Network Address Translation                                                                                                                       | 174          |  |  |

|              | ~ (                           | $6.3.4 Web Switch \ldots \ldots$ | 181          |  |  |

|              | 6.4                           | Summary                                                                                                                                                 | 184          |  |  |

| 7            | Con                           | clusions                                                                                                                                                | 187          |  |  |

|              | 7.1                           | A Powerful New Design Flow Can Be Achieved                                                                                                              | 188          |  |  |

|              | 7.2                           | The Design Flow Can Be Applied to a Wider Range of Applications .                                                                                       | 195          |  |  |

|              | 7.3                           | Future Work is Needed to Extend this Approach to Larger Problems                                                                                        | 200          |  |  |

|              | 1.0                           | and Other Domains                                                                                                                                       | 196          |  |  |

|              |                               |                                                                                                                                                         |              |  |  |

| Bi           | bliog                         | raphy                                                                                                                                                   | 198          |  |  |

| $\mathbf{A}$ | Acr                           | onyms                                                                                                                                                   | 208          |  |  |

|              | D. Design Standards Matrice   |                                                                                                                                                         |              |  |  |

| В            | B Design Structure Matrix 210 |                                                                                                                                                         |              |  |  |

# List of Figures

| 1.1 | Market and technology summary 3                              |

|-----|--------------------------------------------------------------|

| 1.2 | ASIC versus ASSP design starts                               |

| 1.3 | Implementation Gap                                           |

| 1.4 | Keys to crossing the Implementation Gap                      |

| 1.5 | Existing design flow to cross implementation gap 15          |

| 2.1 | OSI and TCP stacks                                           |

| 2.2 | Block diagram of a NAT router                                |

| 2.3 | Web Switch Functionality                                     |

| 2.4 | Block Diagram of the Intel IXP1200                           |

| 2.5 | Block Diagram of the Intel IXP2400                           |

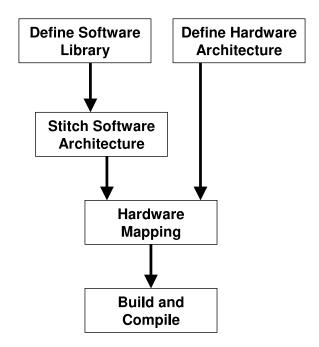

| 2.6 | Design flow of TejaNP                                        |

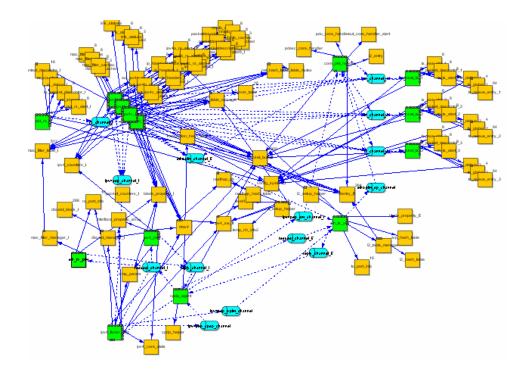

| 2.7 | Application representation in TejaNP                         |

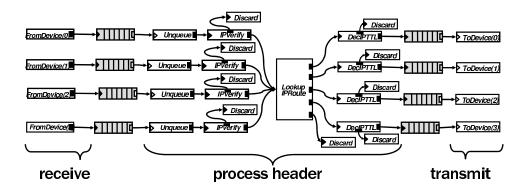

| 2.8 | A Simple Click 2 Port Forwarder                              |

| 2.9 | Networking implementation gap                                |

| 3.1 | Proposed flow to cross implementation gap                    |

| 3.2 | Design flow using PacLang                                    |

| 3.3 | Shangri-La flow                                              |

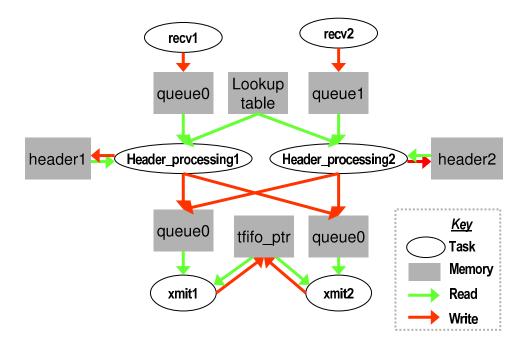

| 4.1 | Task graph as an application model    85                     |

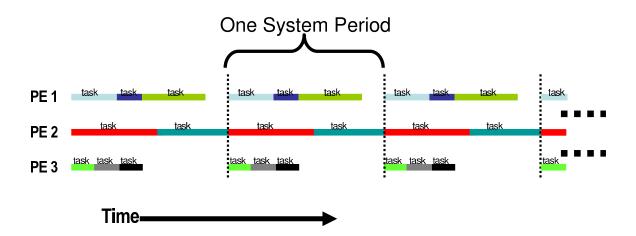

| 4.2 | System period                                                |

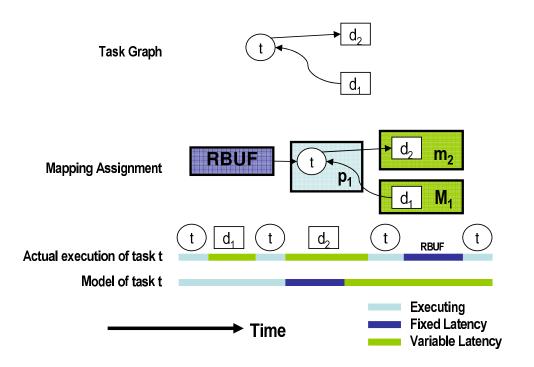

| 4.3 | Our model of hardware multithreading                         |

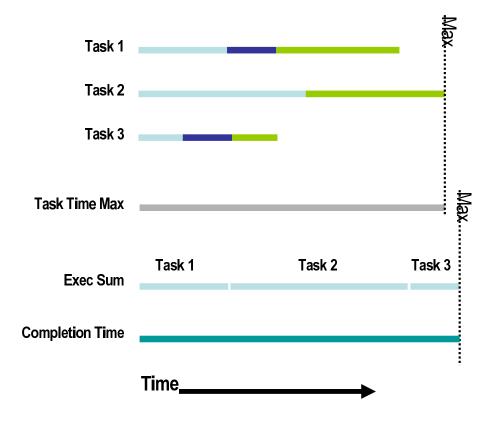

| 4.4 | Our combining tasks on a multithreaded processing element 96 |

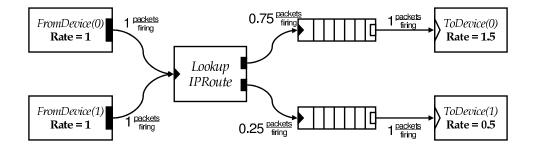

| 5.1 | Simple two port forwarder                                    |

| 5.2 | Simple 2 port forwarder described in Click                   |

| 5.3 | LookupIP Element Description                                 |

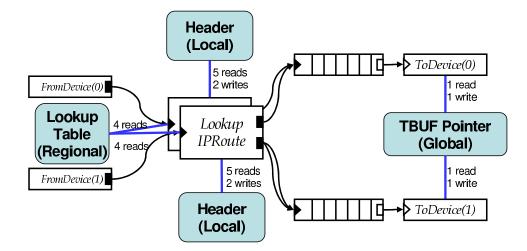

| 5.4 | Examples of data scoping 118                                 |

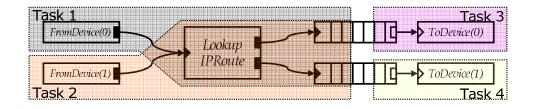

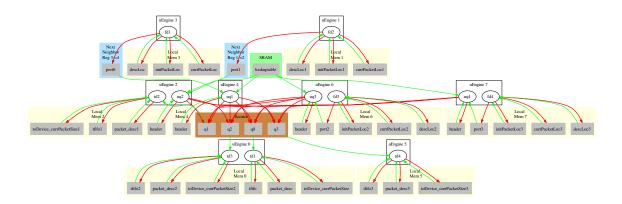

| 5.5 | Covering Click elements with tasks                           |

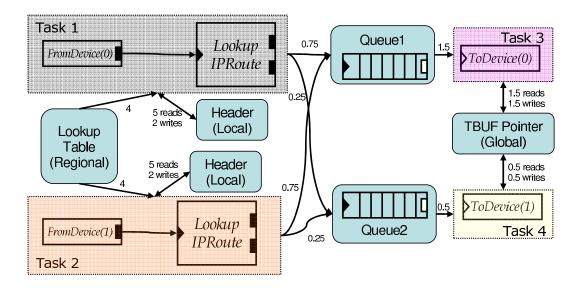

| 5.6 | Task graph generated from a simple forwarder                 |

| 5.7 | Activity graph of the simple forwarder                       |

| 5.8        | Compute Partial Execution Rates Algorithm                             | 132        |

|------------|-----------------------------------------------------------------------|------------|

| 5.9        | Example of a cyclic Click graph                                       | 134        |

| 5.10       | Clustering Algorithm                                                  | 136        |

|            | Find Data Algorithm                                                   | 138        |

| 5.12       | Example of a memory access pattern for a local variable               | 141        |

| 5.13       | Example of optimization of a local variable                           | 142        |

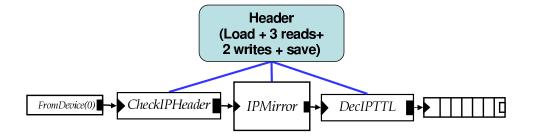

| 5.14       | Function for determining loaders for software caching                 | 144        |

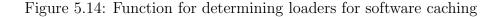

|            | Function for determining savers for software caching                  | 145        |

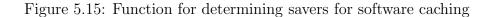

| 5.16       | Element description adjusted to support software caching              | 146        |

|            | Simple forwarder with pipelining                                      | 148        |

|            | Tasks generated from a pipelined simple forwarder                     | 148        |

|            | Simple forwarder with replication                                     | 151        |

|            |                                                                       |            |

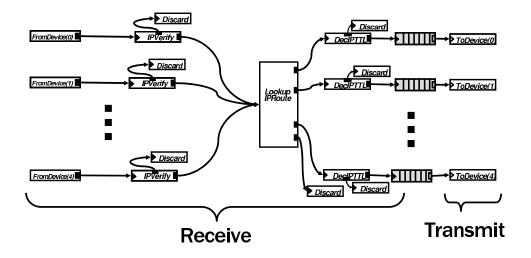

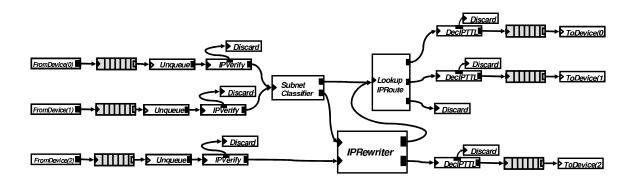

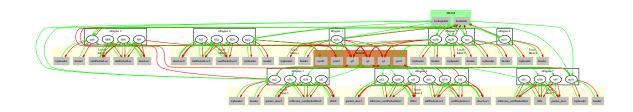

| 6.1        | Click description of the dataplane of the IP forwarding               | 159        |

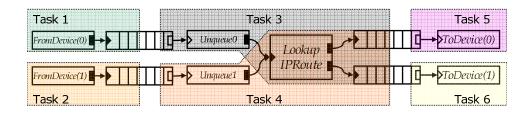

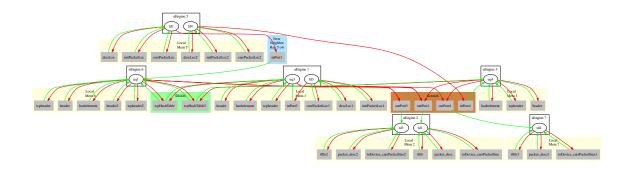

| 6.2        | 16 port IP forwarder on the IXP1200                                   | 161        |

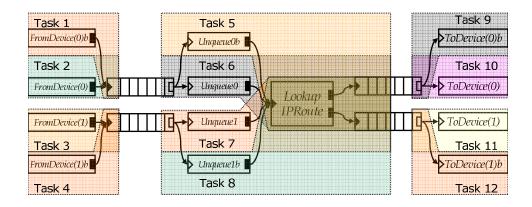

| 6.3        | Retimed IP forwarder for the IXP2400                                  | 162        |

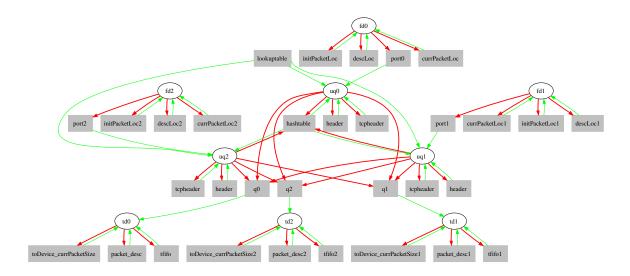

| 6.4        | 4 port IP forwarder task graph                                        | 163        |

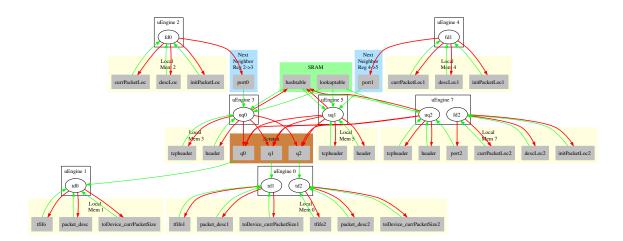

| 6.5        | 4 port IP forwarder mapped to the IXP2400                             | 164        |

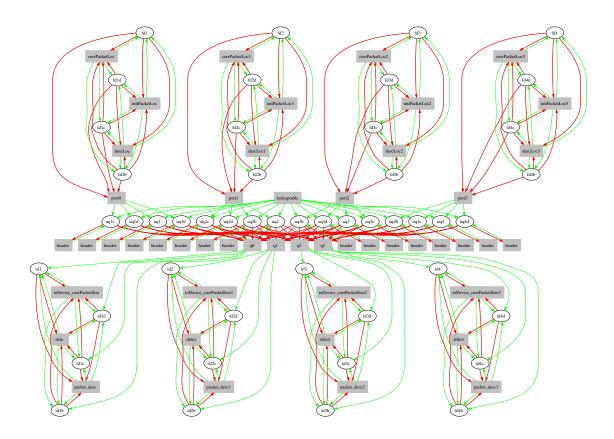

| 6.6        | 4 port IP forwarder task graph with replication                       | 165        |

| 6.7        | 4 port IP forwarder mapped to the IXP2400                             | 165        |

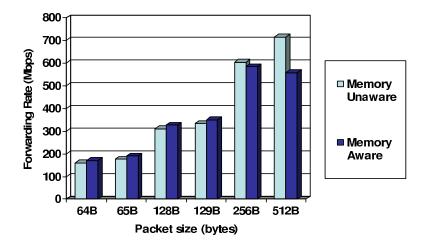

| 6.8        | 4 port IP forwarder mapped to the IXP2400 without considering memory  |            |

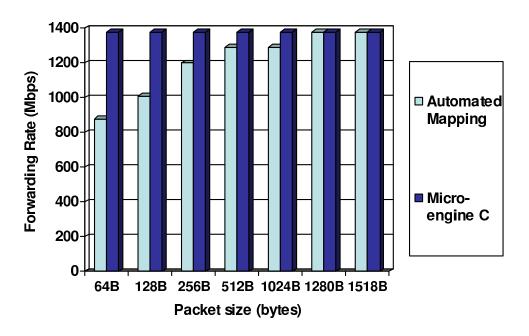

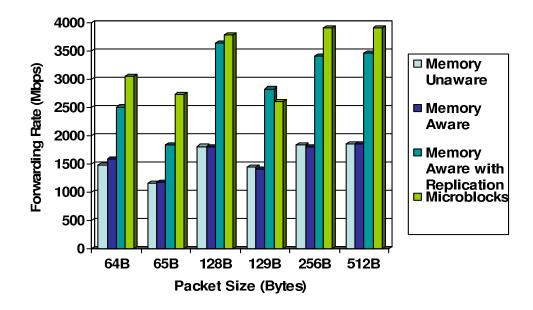

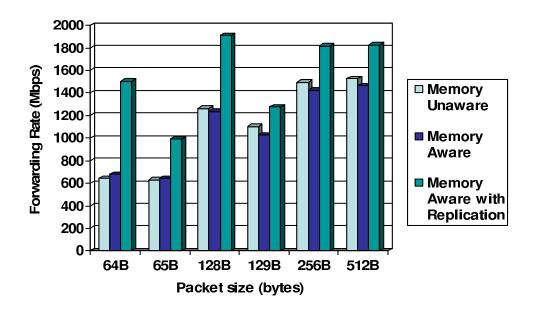

| 6.9        | IPv4 forwarding results                                               | 167        |

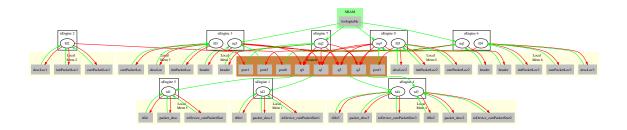

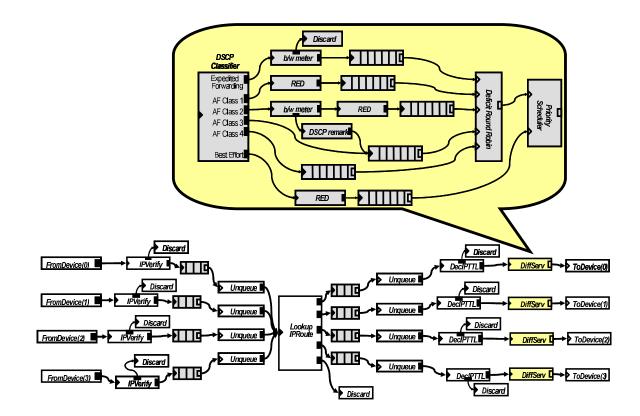

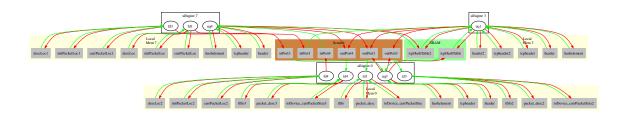

|            | DiffServ Click graph                                                  | 169        |

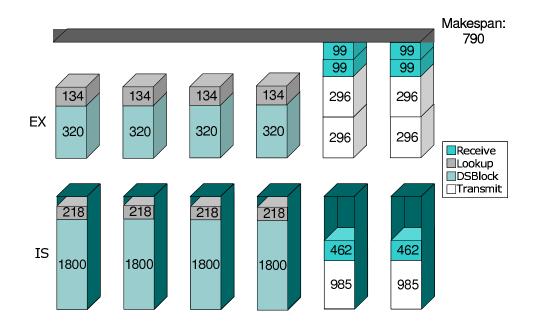

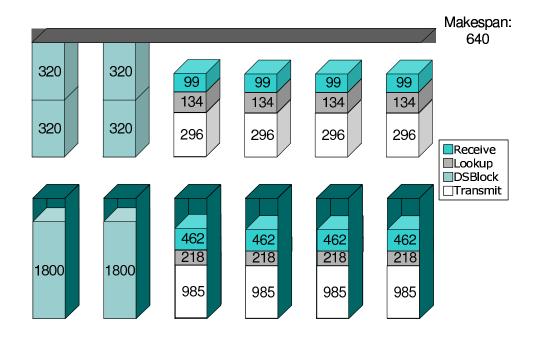

|            | DiffServ mapped with a greedy heuristic                               | 171        |

|            | DiffServ mapped optimally                                             | 171        |

|            | DiffServ results comparisons                                          | 173        |

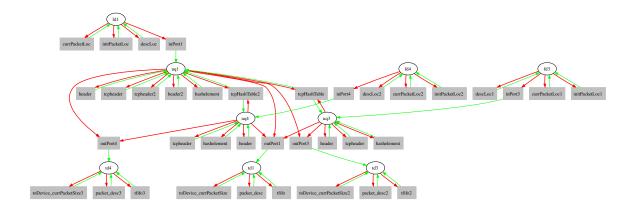

|            | NAT Click graph                                                       | 175        |

|            | NAT task graph                                                        | 176        |

| 6.16       | NAT task graph                                                        | 177        |

|            | NAT task graph with replication                                       | 178        |

|            | NAT forwarder with replication mapped                                 | 178        |

| 6.19       | NAT forwarder mapped to the IXP2400 without considering memory        | 179        |

| 6.20       | NAT results                                                           | 179        |

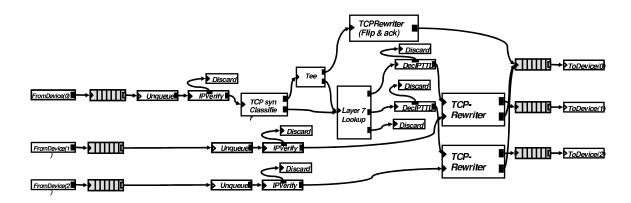

| 6.21       | Web switch Click graph                                                | 182        |

| 6.22       | Web switch task graph                                                 | 183        |

| 6.23       | Memory aware mapping of the web switch                                | 183        |

| 6.24       | Memory unaware mapping of the web switch                              | 183        |

|            | Forwarding rate of the web switch                                     | 184        |

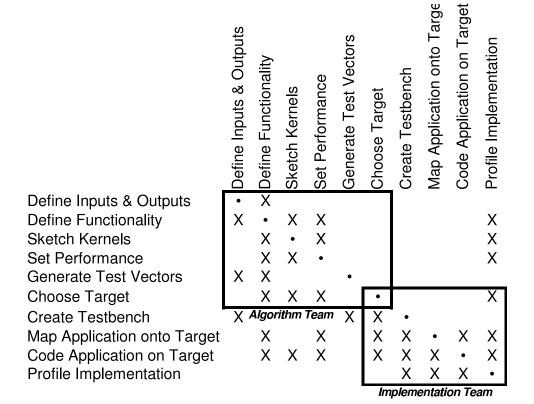

| B.1        | An introduction to design structure matrices                          | 211        |

| В.1<br>В.2 | The design structure matrix of the existing design flow               | 211 214    |

| Б.2<br>В.3 | The design structure matrix of the design flow enabled by this work . | 214<br>216 |

| D.0        | The design structure matrix of the design now enabled by this work .  | ∠10        |

## List of Tables

| Design environment characterization                       | 70                   |

|-----------------------------------------------------------|----------------------|

| Related work summary with respect to keys                 | 72                   |

| Related Work Summary                                      | 73                   |

| Heuristic solution for retiming and replication           | 153                  |

| IPv4 forwarding task characteristics                      | 160                  |

| IPv4 mapping to the IXP1200                               | 161                  |

| 4 port forwarder task characteristics                     | 163                  |

| DiffServ task characteristics                             | 168                  |

| DiffServ mapped to the IXP1200                            | 172                  |

| NAT task characteristics                                  | 176                  |

| NAT implementation comparison of programming environments | 181                  |

| Runtime summary                                           | 185                  |

|                                                           | Related Work Summary |

#### Acknowledgments

I want to thank each member of the Mescal team for the help contributed to this work. I was fortunate enough to work with Scott Weber and Andrew Mihal for my first project with the group. They got me started on the right foot. I next want to thank Yujia Jin, N.R. Satish, Jike Chong, and Matt Moskewicz for the friendship and sound technical advice that they have given me over the years. Bryan Catanzaro and Martin Trautmann have shown great patience by working with my research tools and improved my project through their work. They all have been great sounding boards for ideas and have lent much needed eyes for proofreading this work. Dave Chinnery has been a great source of information a variety of topics and was always happy to talk with me. Most especially I want to thank Niraj Shah, whose research paved the way for this work. His mentorship has shaped much of this work both technically and non-technically and for that I thank him greatly.

My friends and family have been great during this time in my life. Their support and understanding have allowed me to get the most out of this experience. Starting graduate school with Doug Densmore, Donald Chai, Kaushik Ravindran, Adam Zoss, and Roger O'Brient has made classes, homeworks, projects, and working late that much easier. All of the members of the Mayfield Fellows Program have made my time here at Berkeley so interesting. Brenda Haendler has been amazing. I appreciate all of her support, proofreading, and lending of a sympathetic ear. My parents have supported me through this entire experience. I have always felt I could fly as close to the sun as I want, and they would be there to catch me if my wings melted.

My dissertation committee members have provided invaluable feedback. They have donated their time to hear me talk, to read this dissertation, and to discuss my research. Other people at Berkeley have made working here such an enjoyable experience including Ruth Gjerde, Jennifer Stone, and Dan MacLeod. A number of professors have taken the time to discuss my research including Wen-mei Hwu, David Patterson, and Drew Isaacs. For this work, for my graduate career, and for many internships, I owe a great deal of gratitude to my adviser Kurt Keutzer. His guidance to me ranging from research, career, and life has been indispensable. I will miss our lunchtime conversations and taking his money in poker.

## Chapter 1

## Introduction

Application specific multiprocessors (ASMPs) represent an enormous potential boon to electronic system designers. As applications become more complex and more computationally intensive, ASMPs are capable of providing high-performance implementations through domain specific architectural optimizations, while retaining flexibility through programmability. However the difficulty of programming these devices has greatly inhibited their adoption. Long design times and rigid implementations of programs have eliminated many of the benefits of these architectures. The key to unlocking the potential of these architectures is a fast, robust tool flow that can take a natural application description, automate difficult design decisions, and quickly produce an efficient implementation. The goal of this dissertation is to present a framework which satisfies each of the objectives for a representative application area using a popular application description language mapped onto commercial ASMPs.

### 1.1 Emerging Trends

The growing proliferation of applications on embedded devices continues to change how the world works. This explosion of platforms increases what is possible in many application domains. In networking routers and edge devices are securing and accelerating our networks using intrusion detection, denial of service attacks defense, and packet content based routing. In media new video codecs enable full motion playback on handheld devices like cell phones. In the automotive industry drive-by-wire technologies are creating more robust and responsive car subsystems. In medicine segmentation and three dimensional rendering allow doctors to more quickly and accurately diagnose patients.

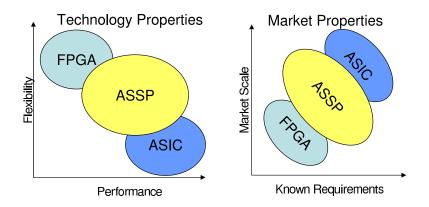

Electronic system designers have facilitated this explosion by creating the products that implement these applications. Among their many design decisions, they must set the platform on which each of the product's features will be implemented. Electronic system designers have a variety of options for this including application specific integrated circuits, general purpose processors, field programmable gate arrays, and application specific standard parts, allowing them to trade-off efficiency, implementation time, *non-recurring engineering* (NRE) cost, and per part cost. The technology summary and market suitability of each of these options is shown pictorially in Figure 1.1.

Of all the solutions available to an electronic system designer, those based on application specific integrated circuits (ASICs) achieve the highest performance. An

Figure 1.1: Market and technology summary of solutions available to system designers Source: Allan Armstrong from Ryan Hankin Kent (RHK), 2004

ASIC is a custom designed silicon chip specifically created for a single application. The design flow starts with a *hardware description language* (HDL). Designers explicitly define how concurrently executing computational blocks connect and relate temporally to each other. To arrive at an implementation, automated tools perform extensive optimizations to improve performance, power, cost, and yield. The result is an implementation that for any given process generation, is the fastest, smallest, lowest power solution. However, this result comes at a long design time with an increasingly high NRE, which is up to \$25 million for 90nm ASIC [6]. These design costs are due largely to the increasing cost of development, verification, and masks. While ASICs offer an attractive solution to designers, their NRE costs make them suitable for only the highest volume markets. Further, because ASICs are hardware solutions, they are inflexible to changes in the applications they implement. Any flux in the application's behavior will cause a new long design iteration including re-verification and the purchase of new masks. Consequently, ASICs are increasingly used for only high-volume applications.

Field programmable gate arrays (FPGAs) are another general purpose solution for electronic system designers. With programmable lookup tables for boolean functions and configurable interconnections, programmers can create arbitrary combinational and sequential logic out of this fabric. Like ASICs, the typical design flow for FPGAs starts with a hardware description language, again used to define computational blocks and their interconnection. This description facilitates utilization of the inherently parallel blocks of the fabric. Automated tools perform the typical steps of hardware design, but specialized for targeting fabric instead of raw silicon. Since FPGAs are a general purpose off-the-shelf technology, designers can implement their target application quickly compared to traditional hardware flows. Their field programmability is also an asset to nascent applications that may need to change after they are deployed. This fast time-to-market and flexibility comes at a cost. FPGA's underlying technology puts them at a severe performance disadvantage to application specific solutions. Compared to ASICs they require 40 times the area, 10 times the power, and are 3 times slower than ASICs [42]. Furthermore, while they are an offthe-shelf solution, their per part costs are generally the highest of the options, making them suitable for lower volume markets, where NRE costs are not easily overcome.

General purpose processors (GPPs) are another solution not specifically tuned to an application domain. They provide the easiest path to a low performance implementation of an application. GPPs for embedded applications like ARM, Intel's Pentium M, IBM's PowerPC are tuned for general purpose computation and each has robust tool flows and support for multiple operating systems. These devices typically have large and diverse communities of users ensuring that tools used to arrive at implementation will be robust for a variety of applications. Regardless of the application's original description language (provided the language has functional support to execute it), minimal effort is required by the designer to arrive at a functional implementation. Electronic system designers enjoy the benefits of a software solution, flexibility, fast design times, and low NRE cost, but these come at a heavy price of low performance, poor power efficiency, and potentially high per post cost. As a result, designers use this solution only for computationally light or control dominated tasks. With more design effort, designers can significantly improve performance (be it clock frequency or power) and lower per part cost.

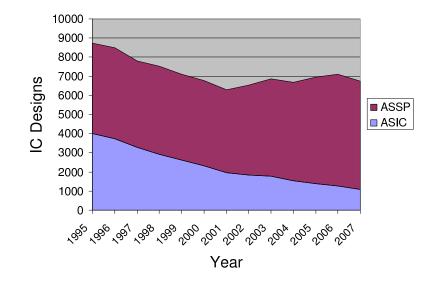

Application Specific Standard Parts (ASSPs) are off-the-shelf chips that are tailored to a set of applications. ASSPs are capable of achieving higher performance by incorporating domain specific architectural features such as special purpose hardware, multiple multithreaded processing elements, distributed heterogeneous memories, and special purpose peripherals. ASSPs have different degrees of flexibility, ranging from simple parameterization to being completely programmable capable of running arbitrary programs. For example, NEC's D/A Converter for Audio System [55] is a parameterizable ASSP. Designers can configure the device in a few ways including its system clock and the data format of its serial input. This flexibility makes this ASSP suitable for multimedia terminals, MPEG audio equipment, video CDs, game machines, and electronic musical instruments. By contrast a network processor, like Intel's IXP2800 [35], has fully programmable processing elements which have an instruction set and a memory architecture tailored for packet processing. These processing elements can be programmed for any desired feature, giving the programmer of the device complete flexibility. Because of their high performance, low NRE costs, and relatively low per part costs, ASSPs have been making gains in the market place. Figure 1.2 displays the ASSP trend. ASSP have yet to approach their full market potential. Impeding adoption and reducing their utility to designers is the fact that completely programmable ASSPs are difficult to program. The reasons for this is discussed in depth in Section 1.2.1, but the implication is that while these devices are capable of implementing high performance, complex applications, they are not currently used for it. While the market for ASSPs is large and growing, its full potential will only be tapped when electronic system designers are able to use them for complex, performance intensive applications, even in small, niche markets. ASSPs will then fuel the continued explosion of new applications across many areas.

### **1.2** Application Specific Multiprocessors

Application specific standard parts (ASSPs) present electronic system designers with the potential to service a set of applications with high performance implementations, fast design times, and low per part costs. Single-chip multiprocessing is becom-

Figure 1.2: ASIC versus ASSP design starts Source: Handel Jones, IBS 9/23/2002

ing increasingly popular in mainstream computing to conquer power problems, but it has existed for several years in certain application domains to exploit the highly parallel nature of a set of applications. Single chip multiprocessing has been successfully deployed in embedded computing markets including graphics, digital signal processing, and networking.

Narrowly focused ASSPs such as a D/A converter do not employ fully programmable processing elements and consequently have limited flexibility. An ASSP based on multiple processing elements, such as Intel's IXP2xxx series, has flexibility limited only to the programs which can compile to it. In practice for the IXP2xxx, the set of applications which can be efficiently supported by the architecture includes a variety of network applications [49] [14] [53] along with other applications that happen to map well to the architecture [70]. High performance is achieved on these kinds of platforms through multiple processing elements, distributed memory, specialized hardware, and a customized interconnect topology. We call a platform which utilizes these features to deliver implementations an *application specific multiprocessor* (ASMP). Once an electronic system designer has selected an ASMP to implement an application, programmers must be able to produce high quality software quickly in order to tap into the potential of the device.

#### **1.2.1** Programming Application Specific Multiprocessors

The ability to buy these high performance solutions off-the-shelf makes ASMPs an attractive option to electronic system designers. Once chosen, the task of harnessing the power of the platform and implementing the features needed falls to a programmer. Programmers would like to utilize these devices by:

- Producing *efficient* implementations that exploit the power of the architecture

- Programming *productively* such that they may arrive at implementations quickly

- Having *portable* application descriptions that can target multiple devices

- Creating a *verifiably* correct implementation

While all of these are desired properties of a programming environment, the time it takes to arrive at an implementation and its resulting efficiency are the two critical features which determine the success or failure of it. The programming environments for a given ASMP will largely determine its success in the marketplace.

#### **Domain Specific Languages**

Domain Specific Languages (DSLs) provide programmers with a natural way of describing applications. Developed by domain experts, DSLs match their mental model of an application domain. DSLs enable higher productivity by providing component libraries, communication and computation semantics, visualization tools, and test suites tailored to a given application domain. In digital signal processing, MATLAB [46] uses simple syntax for vectors and an extensive library of digital signal processing kernels to enable natural design capture. Simulink [47] is an actor oriented approach for capturing dataflow style or control applications. The built-in simulator and visualization tools create an environment where application designers can describe and iterate on an application design quickly and accurately. LabVIEW [54] is another modular, dataflow-like language specialized for testing instruments. For networking, a popular DSL is Click [39], which is an actor oriented language customized for packet processing and packet flow visualization.

#### **Programming Environments**

While domain specific languages are commonly employed for application exploration, the programming environments for ASMPs tend to force programmers to code at a much lower level. On the whole, programming environments for these devices have opted for exposing much of the architecture to the programmer. The ability to arrive at high performance solutions is given the highest priority and the programmer manages all of the features of the architecture. Most of these devices initially ship with only assemblers, giving programmers the ability to tighten their kernels at the instruction level.

The perceived ability to arrive at efficient implementations comes at a heavy price. To enable the use of special purpose hardware and exposed memories, vendors of these ASMPs often extend popular sequential models. Programmers end up overwhelmed with details of these idiosyncratic devices. Utilizing memories, balancing computation, and coordinating communication are daunting tasks when handled in low level programming environments that are built on Assembly or C. Even mundane tasks such as communicating with special purpose hardware can be a serious time sink. Saddled with the task of negotiating all of the architectural detail and programming at a low level, programmers require long design cycles to arrive at reasonable implementations.

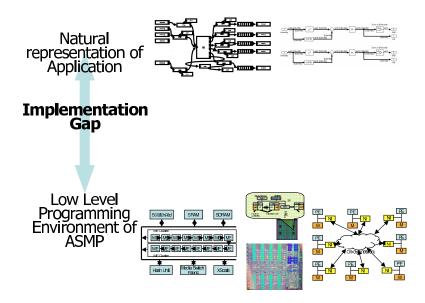

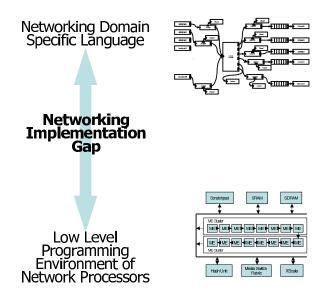

#### Implementation gap

The task of describing the functionality of an application and the process of implementing that application is separated by a wide chasm that we call the *implementation* gap as shown graphically in Figure 1.3. Regardless of the application domain and the target ASMP, many obstacles are necessary to overcome to arrive at efficient implementation.

Besides the mundane but real annoyances of application design for these devices,

Figure 1.3: Implementation Gap

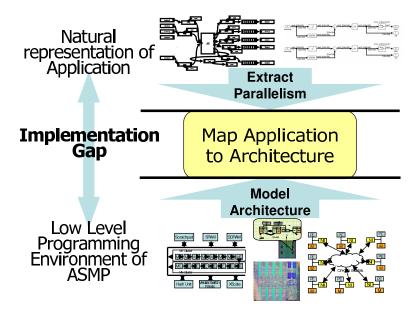

there exist three fundamental problems to effectively traversing the implementation gap shown pictorially in Figure 1.4.

- Creating an architectural model capturing the performance salient features.

- Constructing an application representation that exposes enough information to be efficiently implemented.

- Mapping this representation of the application to the architecture.

The paradigm of manually writing programs for each of thread of each processing elements creates many difficult design decisions for programmers. Programmers must balance the computation across processing elements to ensure that there is no single computational bottleneck on any processing element. If the architecture has

Figure 1.4: Keys to crossing the Implementation Gap

exposed distributed memories, programmers must take care to locate program data in appropriate memories. Small frequently accessed data should generally be located in memory local to a processing element, while larger infrequently accessed data should be located in off-chip memory. Multiprocessing complicates these rules of thumb by forcing the designer to account for how data is connected to programs on different processing elements. For example, a piece of data simultaneously shared between two programs on different processing elements cannot be mapped to the local memory of one processing element if the memory is not accessible to the other processing element. More generally, set of architectural restrictions describing which processing elements may directly communicate to which memories and other processing elements is referred to as an architecture's *topology*. Topology must be respected by the designer to ensure that an application's communication patterns may be mapped to the interconnect resources in the architecture. Because of the architectural details, the problem space for the mapping problem is large and irregular. Since evaluating a design point requires a significant amount of time due to writing, debugging, and testing, a model of the architecture is needed for fast design space exploration. The model must be constructed with care capturing those features that have the greatest impact on performance while hiding those which needlessly complicate the model and increase the evaluation time.

This model is used by programmers or tools to make mapping decisions about how the application is to be distributed onto the architecture. Exacerbating the problem is the fact that each of these design decisions (allocating computational tasks to processing elements, laying out data in memory, and assigning application communication to architectural interconnect) are interrelated. A programmer can be easily overwhelmed by this large, irregular design space. As the number of processing elements and distributed memories increases and the topology gets more complicated with every generation, the problem becomes increasingly difficult.

To make these mapping decisions, the designer must have a description of the application that these difficult design decisions can be applied to. Often the application description is devoid of the information needed to do this. For example, a whiteboard or prose description of an application may not have state information for the computational tasks, so a feasible solution could not be made that included memories. A model of the application must be constructed that exposes the critical features of the application.

While architects have been spending much effort maximizing the performance of their devices, the real key to ensuring the success of an ASMP is enabling the efficient and productive traversal of the implementation gap shown in Figure 1.3. Providing programmers the ability to harvest most of the performance of the architecture is more important than its raw performance.

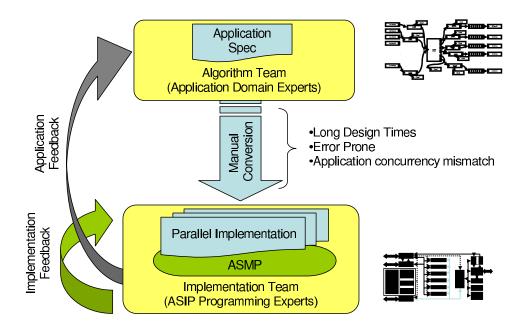

#### 1.2.2 Existing Common Design Flow

While the key to unlocking the potential of these devices lies in the ability to cross the implementation gap effectively, the design flow that commonly exists in industry is woefully flawed. While it varies from industry to industry and company to company, the typical design flow for one of these application descriptions is shown in Figure 1.5.

First an application team makes the application level choices about what features to implement, the basic algorithms for the kernels needed, and based on their estimates, the target platform to be used. Describing the application can be as informal as a whiteboard sketch or English prose, but it often takes the form of a functional description. This is commonly done in a popular sequential programming language, but for larger application domains, domain specific languages are growing in popularity.

While capturing the functionality of an application can be done quickly, the job of

Figure 1.5: Existing design flow to cross implementation gap

implementing it on ASMPs is notoriously difficult. Driven by performance pressures, system designers perceive that to reap the benefits of using an ASMP, they often start implementation entry at the lowest level. Typically this task is done by one or more individuals who are experts of the target platform, called the *implementation team*. The implementation team is by and large required to overcome each of the fundamental obstacles of crossing the implementation gap. Their model of the architecture is usually implicit and based on their own experiences. Mapping decisions are made manually based on intuition. Arriving at an implementable form of the application is done by writing code in the target environment. Programmers must write multiple, often multithreaded, sequential assembler or C programs according to this mapping.

Humans manage to persevere despite the difficulty presented by these environ-

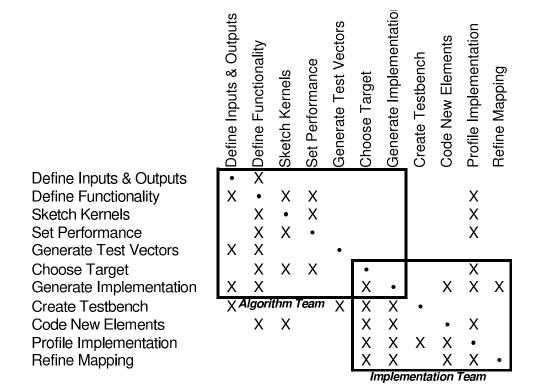

ments and settle on a mapping of the application. Programmers eventually create a functional design, but arriving at a working implementation is not enough, as the *raison d'être* of these devices is to deliver high performance solutions. Simplicities of the model and biases of the programmers invariably leads to a solution with an unforeseen bottleneck. Programmers must utilize information at this fully evaluated design point to refine the solution by rewriting kernels, redistributing the computational load, or relocating data in memories. These changes to the application require additional testing and design time, but fortunately they are feedback loops contained within the implementation team. The dependencies and feedback loops of this design process is given more rigorous consideration using a Design Structure Matrix [64] in Appendix B. Figure B.2 indicates that teams are well grouped for this design flow, but that significant intergroup dependencies and feedback exist.

The advantage of using an ASMP is its ability to provide high performance with short design time. The software path to implementation should afford short design times with fast changes. However, a flawed design flow to cross the implementation gap mitigates each of these. Unfortunately, this current design methodology leads to long design times and to being locked into a particular system mapping.

### 1.3 Objectives of Research

The work presented here seeks to provide a framework with supporting algorithms and tools to make the job of crossing the implementation gap more productive, while still producing implementations comparable to hand crafted designs. Specifically, it focuses on the fundamental problems of crossing the implementation gap between an application described in a domain specific languages to ASMPs: architectural model creation, application representation construction, and application to architecture mapping this representation of the application to the architecture.

To study this throughly and practically, this work focuses on one particular application domain. While there are many potential areas to choose from to study this domain, networking is well suited to the task for reasons that are discussed in the following chapter. We select a representative domain specific language and common, high performance commercial network processors, and then we construct a framework. It is with these two endpoints the fundamental problems of crossing the implementation gap have been examined.

#### **1.4** Organization of this Dissertation

This dissertation is organized in the following manner. Chapter 2 gives an overview of the field of networking, including the representative applications that will test this approach. Chapter 3 describes our overall approach to crossing the implementation gap along with some related work. To efficiently target these devices, programmers must first capture what are the salient features of the architecture, while abstracting away those details that are not important. Chapter 4 presents these features for network processors, based on my own experience with common commercial architectures. We present a mathematical model of these features so that it is amenable to automated design space exploration. There are optimizations and transformations that are enabled by starting with a more abstract, domain restricted representation of the application. Chapter 5 discusses techniques that we have arrived at that produce the task graph automatically and provide significant performance improvements. To demonstrate this approach, Chapter 6 presents results of this approach by mapping the data plane of representative network applications onto high performance commercial network processors. Chapter 7 summarizes and concludes this work, while presenting some possible future directions.

## Chapter 2

## **Network Processing**

For an in depth examination of the problem of an application specific implementation gap, we focus on the field of networking. The networking domain continues to create more functionality in the network through new applications running within the network. Performance pressure coupled with changing functionality has prompted the rise of network processors. Indicative of the wider application specific multiprocessor trend, network processors achieve high performance through architectures customized to exploit parallelism inherent in the networking domain. While many programming approaches have appeared for these powerful devices, their focus on performance has lead to difficult design cycles. Domain specific languages in networking provide an ideal alternative to describing applications using packet abstractions and the common communication style of networking applications. The implementation gap between networking domain specific languages and existing network processor programming environments is wide.

### 2.1 Motivation for Networking Focus

The field of networking has been a plentiful area of research and innovation. Years of study have produced a variety of applications across different parts of the network and different layers of the protocol stack. Besides being interesting from a research standpoint, networking is a huge market. According to the the Telecommunication Industry Association, telecommunication industry spending reached \$856.9 billion in 2005 and is projected to keep growing at around 9% annual growth rate [26]. Growth was lead by network equipment and new applications on the network such as voice over IP, web conferencing, and video conferencing. These trends are indicative of a field which has maturity and size, but is still growing and evolving based on new applications.

These new applications drive not only new features in the network, but continue to drive the Internet's growth in bandwidth. In fact, data traffic on the Internet is doubling every 12 months [20], outpacing Moore's Law. The desire for new features along with performance pressures driven by increasing traffic demands precipitated the rise of high performance programmable solutions: network processors. These application specific multiprocessors are tailored to packet processing and provide the potential of high performance software solutions to networking's most demanding problems. The networking area is large but still evolving. The interest in new applications has fueled the creation of domain specific languages. The sheer size of the domain supports a large community of users with a common set of rules or design philosophies. The size and continuing interest in new applications in networking have made it a fertile area for domain specific languages. The independent creation of domain specific languages and application specific multiprocessors makes networking an ideal niche for exploring the key problems of crossing the implementation gap.

The extensive study of how to utilize parallelism on single chip multiprocessors makes networking of particular interest to mainstream computing. The diversity of architectures, application, and programming methodologies can provide useful guidance to the general purpose community. Existing solutions to general purpose parallel programming will suffice for a small number of processors, thanks to the parallelism of independent jobs. But as the general purpose cores increase and multiprocessor parallelism must be exploited directly by applications, the key problems of the implementation gap exhibited in networking may manifest in the general purpose processing. A careful examination of the challenges and potential solutions in networking could hold broad insights for the mainstream multiprocessor world of the future.

### 2.2 Network Applications

Network applications are primarily defined by their location in the network. The edge of a network is the boundary between one managed network and another. An

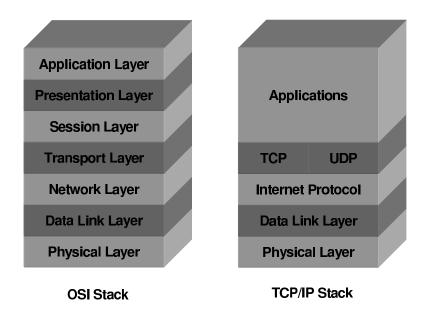

Figure 2.1: OSI and TCP stacks

edge network device may serve as the gateway for a handful of hosts to the Internet or a high bandwidth device that connects two Internet Service Providers. Within the boundaries of a managed network is the *core*. Core networking devices provide the services of the network. In the Internet core routers provide high bandwidth routing with best effort. A corporate network that merges data and voice traffic has core devices which provide quality of service guarantees along with basic routing functionality.

Besides location in the network, applications can also be classified by where they exist in the Open Systems Interconnection (OSI) model [11]. Layers of the OSI stack represent various levels of abstraction of communication from bits to packets to flows to application data shown in Figure 2.1. Much of the innovation on network devices occurs at the Network and Transport layer. The Network layer covers routing packets, segmentation/reassembly, and sending error packets. The Transport layer ensures packets are reliably delivered in-order and manages flow control and congestion. In practice these correspond to the Internet Protocol (IP) for the Network layer and Transmission Control Protocol (TCP) and User Datagram Protocol (UDP) for the Transport layer. The separation of layers allows designers to design network applications with a particular abstraction of packets and packet flow.

Thanks to its long history, many traditional network benchmarks have defined the area to measure the performance of the devices. However a longstanding uniform test-bench has been elusive because the demands on the application change rapidly from generation to generation. For example, *Internet protocol* (IP) packet routing has been a basic application for decades, but each generation of equipment has different port bandwidths, physical protocols, routing table sizes, and number of ports.

Along with the canonical networking benchmarks, new applications have appeared in different parts of the network. These have added new features to networks to service applications that need more than the best effort routing of most networks. Another driving force for new applications in the network is the desire to distributed more of the computational workload to the network. This steady trend of exporting more functionality out of the end hosts onto the network includes intrusion detection, quality of service guarantees, protocol translation, and routing based on packet content. The following section gives examples of common networking benchmarks along with new ones that are driving the networks of the future.

#### 2.2.1 IP Forwarding

Internet Protocol version 4 (IPv4) packet forwarding [9] is a common kernel of many network applications. The Network layer application forms the foundation of packet processing in the core of networks including the Internet. It provides the functionality needed to provide end-to-end delivery of packets. IP forwarding enables global connectivity with lossy, best effort routing of packets. There are no guarantees on bandwidth, latency, or in-order delivery of the packets. This limited feature requirements allows designers to deliver the highest performing implementations so that core routers of the Internet are able to achieve the highest possible throughput.

For the base case of IP forwarding, a packet is first received by the router. Being a Network layer application, the computation is confined to the IP header of the packet. Many implementations separate packet headers from the packet payload to limit the amount of memory passed between processing elements. The packet header is checked its validity by ensuring various fields are consistent with the IP fields including checksum, header length, and IP version. The egress port of the packet is determined by a performing a longest prefix match route table lookup of the destination address. The time-to-live (TTL) field which indicates the maximum number of hops a packet can traverse is decremented. Finally the packet header is recombined with the payload and transmitted on the appropriate port.

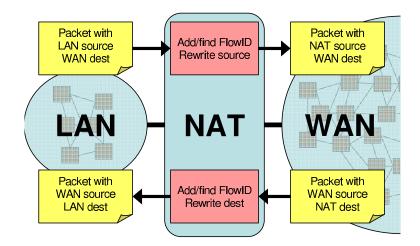

## 2.2.2 Network Address Translation

Network address translation (NAT) [63] is a widely used edge application that enables communication between networks with conflicting address spaces. A traditional configuration is shown in Figure 2.2. On one side of the router with NAT functionality is a *local area network* (LAN) while on the other is a *wide area network*. As with many local networks, the address space used by the LAN is not coherent with respect to the larger WAN. This can happen for a variety of reasons including a shortage of WAN addresses or a legacy address allocation. A NAT device allows a single WAN address or a set of WAN addresses to be used among hosts on the LAN. This conserves address of the WAN and decouples the LAN infrastructure from the WAN.

To allow these two networks to communicate, a NAT router rewrites the packets that it forwards between these two networks. Hosts on the LAN with data requests or responses to hosts on the WAN have their packets forwarded to the NAT router. These packets' addresses are rewritten to use the address or addresses reserved to the NAT router in the WAN's address space. In order to keep address rewriting consistent and to forward responses from the WAN back to the appropriate hosts in the LAN, NAT routers keep a record of which packet flows are active between the LAN and WAN. Packet flows are often classified by a flow identifier (flow ID) which is a unique identifier of a network session. With TCP/IP packets, this four-tuple is typically: (source IP address, source TCP port, destination IP address, destination

Figure 2.2: Block diagram of a NAT router

TCP port).

A typical scenario is depicted in Figure 2.2 in which a single WAN IP address is used for an entire LAN. A host on the LAN sends a request packet with a destination on the WAN. The packet is forwarded to the NAT router, where it searches its table of flow IDs for an existing connection. If one is found, it rewrites the packet's source address and port to match the entry in its table. If it is not found, the NAT router reserves a new port for the flow and adds it to the flow ID table. The packet header is rewritten and forwarded on to the WAN. A response packet from the WAN undergoes similar processing except that the destination address and port are rewritten instead of the source address. Connections are eventually removed from the table based on a time-out or a packet signaling the end of the session.

## 2.2.3 Differentiated Services

The basic functionality provided by the Internet's infrastructure is that of connectivity. Routers forward packets with best effort in an attempt to deliver as much data as fast as possible to their destinations. While this is sufficient for many applications which run on the network, others require more than just delivery to destinations. For example, people having a voice conversation over the network are sensitive to latency. Conversely for most web page data throughput is more important than latency. To provide bandwidth, latency, or jitter guarantees to packet flows, network administrators employ Quality of Service (QoS) architectures.

One type of QoS architecture is *Differentiated Services* (DiffServ) [12]. It is a provisioned model in which network administrators design the network infrastructure with broad categories of traffic. Interior nodes of the network apply different *per hop behaviors* (PHBs) to various classes of traffic. The classes of PHBs recommended by IETF include:

- Best Effort no guarantees of packet loss, latency, or jitter

- Assured Forwarding 4 classes of traffic, each with varying degrees of packet loss, latency and jitter

- Expedited Forwarding low packet loss, latency and jitter

Routers are augmented with special schedulers, queue sized specifically for each type of packet class, and with bandwidth rating mechanisms to police the number of packets annotated in each flow. End applications bin their packets into each of these flows to indicate which data require which guarantees.

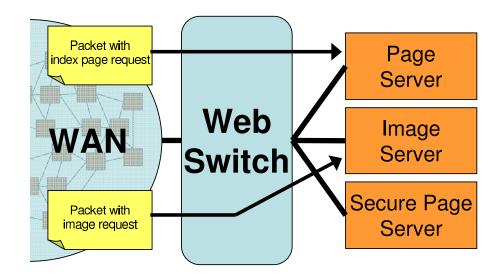

## 2.2.4 Web Switch

Much of the performance growth in the Internet can be explained by an increase in network functionality. By locating more of the computation in the network, end hosts are able to scale more with demand. A web switch is the offloading of one such application. A web switch uses the content of a packet to route it. For web requests, this could include the directory of the URL requested, the type of file, or the cookie of the client. With this Application layer information, a web switch can intelligently distribute traffic across a set of heterogeneous servers. Like NAT, it is transparent to both client and server.

Figure 2.3 shows an example of a configuration with a web switch which classifies HTTP requests into regular page requests, secure page requests, and image requests. This allows a single website to be hosted by multiple servers without a single host bottleneck. Other options for load balancing requests across multiple servers include random selection of a server, selection based on the least loaded server, and selection based on hashing. Each strategy can make use of a web switch by offloading the distribution computation to it.

Since even simple requests can involve exchanging multiple packets between client and server, session state is often stored in the web switch to ensure coherence between

Figure 2.3: Web Switch Functionality

client and server. Such session state is part of the Transport layer which keeps track of states such as connection setup, packet ordering, and connection tear down. To ensure that the web switch is transparent to both client and server, web switches often employ "connection splicing" in which the router handles the initial setup connection with the client before the request flows are sent to the appropriate server. This allows the webswitch to see the first real packet of application data so that it can use that information to select the correct server.

## 2.3 Network Processors

The variety and complexity of networking applications is a natural fit for a programmable solution. This fact coupled with the increasing performance demands of these parallel applications has feuled the rise of network processors which is representative of the larger trend toward application specific multiprocessors. Complex applications with varied feature sets that may change over time necessitated the use of a programmable solution, while application performance requirements demanded application specific optimizations to the platforms. A variety of network processors have come into existence in the past decade. They are distinguished by where they are deployed in the network and the principles the architects believed would bring the highest performance for the intended applications. A recent survey of network processors identified the key features and the major architectural axes of network processor designs [4]. These include number and type of processing elements, issue width, pipeline depth, memory structure, hardware accelerators, and on-chip topology.

To retain high performance, architects have employed a variety of techniques. These include customizing instruction sets to packet processing, using multiple processing elements and multithreading to exploit the inherent parallelism between packets and packet flows, tailoring memory architectures to packet header and payload movement, and specialized hardware for compute intensive packet operations such as hash engines and cryptography engines. The architectural details create a wide diversity of network processors. Differences include the instruction set used, the number of processing elements, how they are connected, and the size and number of distributed memories used. The following sections examines a few representative network processors sors to highlight some of the commonalities and differences between network processor architectures.

## 2.3.1 Intel IXP1200

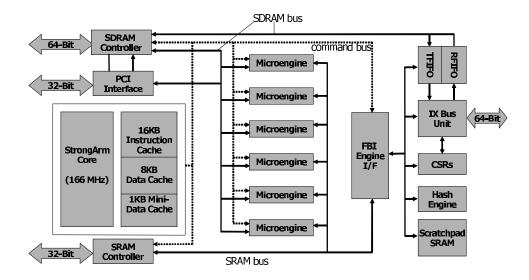

The IXP1200 [32] is one of Intel's network processors based on their Internet Exchange Architecture. It has six identical RISC processors, called *microengines* (MEs), plus a StrongARM processor as shown in Figure 2.4. The StrongARM is used mostly to handle control and management plane operations. The microengines are geared for data plane processing and each has hardware support for four threads that share an instruction store of 1K-2K instruction words. Fast context swapping is enabled by a hardware thread scheduler that takes only a few cycles to swap in ready thread. The IXP series uses cooperative multithreading, meaning threads swap out voluntarily and are not preempted by other threads. The register file itself is split logically into individual areas for each thread, so a thread's state does not have to be pushed to memory. There is also a shared region which threads can used for sharing data between threads.

To cope with small size of the instruction store, each of the threads on a processing element may share instruction memory. Register addressing within an instruction may operate in different modes: *Context relative addressing* is addressing a registers in the region local to a thread and *Absolute addressing* is the registers in the shared pool that are common to all threads. In context relative addressing and instruction adds an offset such that the register in the appropriate pool is addressed by any thread that enters that context.

The memory architecture is divided into several regions: large off-chip SDRAM,

Figure 2.4: Block Diagram of the Intel IXP1200

faster external SRAM, internal scratchpad, and local register files for each microengine. Each region is under the direct control of the user and there is no hardware support for caching data from slower memory into smaller, faster memory (except for the small cache accessible only to the StrongARM). The interconnection of the memories and processors to peripherals is customized for packet movement. A dedicated bus between DRAM and the ingress and egress buffers is intended for movement of the packet payload to and from memory without impeding the progress of existing computation. Interconnection also exists between microengines and the ingress and egress buffers too allowing designers to move packet headers directly to the register files so that they may be immediately operated on.

## 2.3.2 Intel IXP2xxx

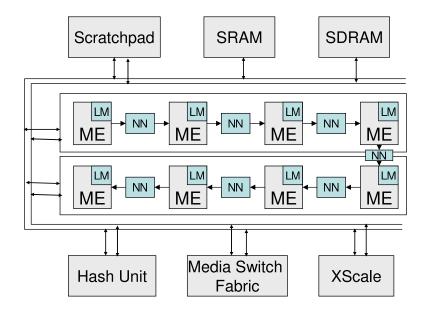

The IXP2xxx is Intel's most powerful family of network processors to date, capable of up to 23.1 GIPs [33] [35]. Each member of the family has an XScale processor that is intended for control and management plane operations. Like the IXP1200, there are multiple RISC processors with instruction sets tuned for packet processing called *microengines* (MEs). With instruction set architectures geared towards data plane processing, each microengine has hardware support for eight threads with a shared instruction store. To permit fast context swapping, each also has a hardware thread scheduler monitoring the readiness of each thread. To keep these cores busy, the memory architecture is divided into several regions: large off-chip DRAM, faster external SRAM, internal scratchpad, next neighbor registers (NNs), and local memories (LMs) and register files for each microengine. Each region is under the direct control of the user, and there is no built-in cache structure for the microengines. Next neighbor registers allow producer-consumer relationships between neighboring microengines to avoid communicating through slower, globally shared memory. Shown in Figure 2.5, the IXP2400 is a midrange performer member of the IXP2xxx family with 8 microengines running up to 600 MHz, each with 8 hardware supported threads.

#### 2.3.3 EZChip NP-2

EZChip's third generation family of network processors is NP-2 [22]. Geared for 10Gbps of packet processing, the NP-2 integrates multiple processing elements,

Figure 2.5: Block Diagram of the Intel IXP2400