### Short Range Pulse Based Inductive Transceiver

Davide Guermandi Simone Gambini Jan M. Rabaey

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2006-155 http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-155.html

November 22, 2006

Copyright © 2006, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Contents

| Introduction |     |                                                                                                                                                          |    |  |  |

|--------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| 1            | Sho | t Range Wireless and Inductors Coupling                                                                                                                  | 3  |  |  |

|              | 1.1 | Coupled inductors                                                                                                                                        | 3  |  |  |

|              | 1.2 | Pulse Based Radio                                                                                                                                        | 7  |  |  |

|              | 1.3 | Inductor design                                                                                                                                          | 9  |  |  |

|              | 1.4 | SNR and Pulse Duration trade-off                                                                                                                         | 11 |  |  |

|              | 1.5 | Receiver duty cycling and synchronization issues                                                                                                         | 16 |  |  |

| <b>2</b>     | Tra | sceiver Implementation 1                                                                                                                                 | 9  |  |  |

|              | 2.1 | Transceiver Overview                                                                                                                                     | 20 |  |  |

|              | 2.2 | $Transmitter \dots \dots$                          | 21 |  |  |

|              |     | 2.2.1 Transmitter control logic                                                                                                                          | 22 |  |  |

|              | 2.3 | Receiver                                                                                                                                                 | 25 |  |  |

|              |     | 2.3.1 LNA                                                                                                                                                | 26 |  |  |

|              |     | 2.3.2 Gain Stages $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                       | 28 |  |  |

|              |     | 2.3.3 Differential to single-ended converter                                                                                                             | 32 |  |  |

|              |     | 2.3.4 Comparators $\ldots \ldots \ldots$ | 34 |  |  |

|              |     | 2.3.5 Data and Clock Recovery                                                                                                                            | 34 |  |  |

|              |     | 2.3.6 Receiver control logic                                                                                                                             | 35 |  |  |

|              | 2.4 | Bias circuits                                                                                                                                            | 36 |  |  |

|              | 2.5 | Amplifier simulations                                                                                                                                    | 37 |  |  |

|              | 2.6 | PLL and Synchronization scheme                                                                                                                           | 41 |  |  |

|              |     | 2.6.1 VCO                                                                                                                                                | 42 |  |  |

|              |     | 2.6.2 Frequency Divider                                                                                                                                  | 43 |  |  |

|              |     | 2.6.3 PFD-CP                                                                                                                                             | 14 |  |  |

|              |     | 2.6.4 Programmable loop filter                                                                                                                           | 15 |  |  |

|              |     | 2.6.5 Programmability of the loop filter                                                                                                                 | 17 |  |  |

|              |     | 2.6.6 Operational amplifier design                                                                                                                       | 48 |  |  |

|              |     |                                                                                                                                                          |    |  |  |

|              | 2.7               | Synchronization procedure and related hardware |                 |  |

|--------------|-------------------|------------------------------------------------|-----------------|--|

| 3            | <b>Tes</b><br>3.1 | t Chip Pin Out<br>Control Bits                 | <b>59</b><br>63 |  |

| 4            | Me                | asurement results                              | 67              |  |

|              | 4.1               | General results and main issues                | 67              |  |

|              |                   | 4.1.1 New pulse rates                          | 68              |  |

|              | 4.2               | Inductor measurements                          | 69              |  |

|              | 4.3               | Stand-by currents                              | 70              |  |

|              | 4.4               | Transmitter characterization                   | 72              |  |

|              | 4.5               | Inductive channel characterization             | 74              |  |

|              | 4.6               | Receiver and data link characterization        | 78              |  |

|              |                   | 4.6.1 Loopback measurement                     | 78              |  |

|              |                   | 4.6.2 LNA input impedance                      | 82              |  |

|              | 4.7               | PLL and Synchronization                        | 86              |  |

|              |                   | 4.7.1 Leakage effects                          | 87              |  |

|              |                   | 4.7.2 Synchronization on duty cycled operation | 90              |  |

| С            | onclu             | isions                                         | 95              |  |

| $\mathbf{A}$ | Appendix          |                                                |                 |  |

## List of Figures

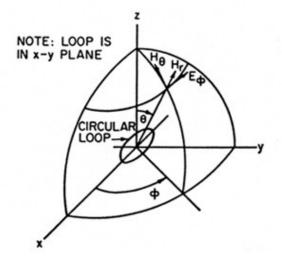

| 1.1  | E.M. filed generated by a magnetic dipole     | 4 |

|------|-----------------------------------------------|---|

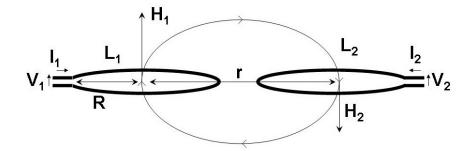

| 1.2  | Coupled inductors                             | 5 |

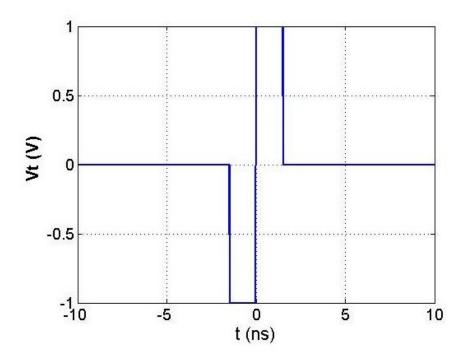

| 1.3  | Voltage pulse across the inductor             | 8 |

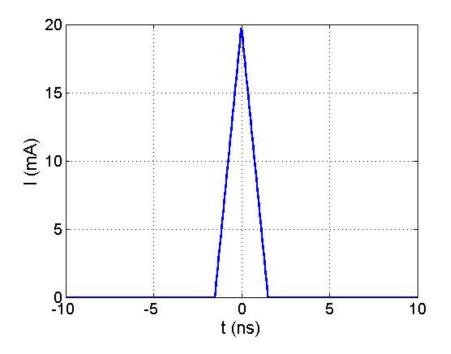

| 1.4  | Current pulse through the inductor            | 9 |

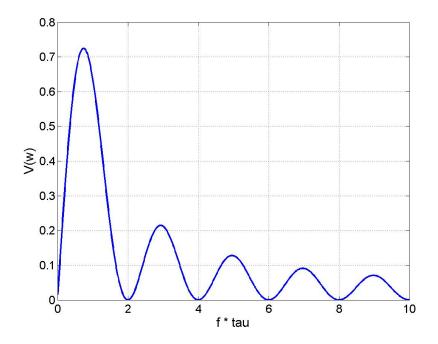

| 1.5  | Voltage pulse spectrum                        | D |

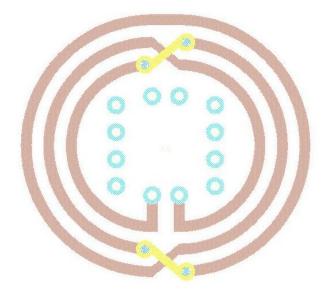

| 1.6  | Antenna layout                                | 1 |

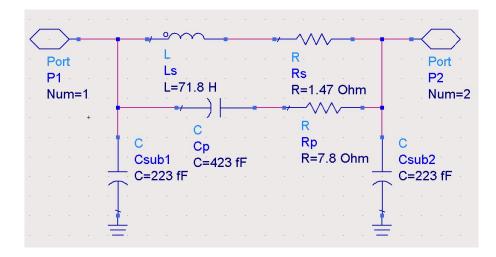

| 1.7  | Antenna equivalent model                      | 2 |

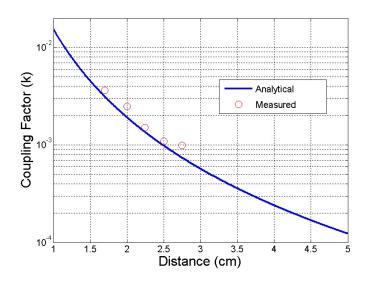

| 1.8  | Coupling factor as a function of the distance | 3 |

| 1.9  | Receiver Filter                               | 3 |

| 1.10 | Receiver duty cycling                         | 6 |

| 1.11 | Data stream in TDMA fashion                   | 8 |

| 0.1  |                                               | ~ |

| 2.1  | Transceiver block diagram                     |   |

| 2.2  | Transmitter and transmitter signals           |   |

| 2.3  | Transmitter delays and signal generation      | 2 |

| 2.4  | Transmitter voltage spectrum                  | 3 |

| 2.5  | Simulated transmitter output voltage          | 4 |

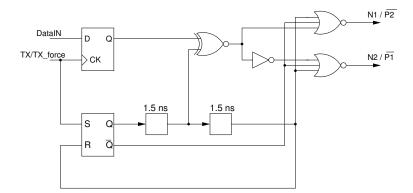

| 2.6  | Transmitter Logic                             | 4 |

| 2.7  | Receiver block diagram                        | 5 |

| 2.8  | SF-CG LNA                                     | 7 |

| 2.9  | Real part of the LNA input admitance          | 8 |

| 2.10 | Amplifier Stage                               | 9 |

| 2.11 |                                               | 1 |

| 2.12 | Offset Cancellation                           | 2 |

| 2.13 | Differential to single-ended amplifier        | 3 |

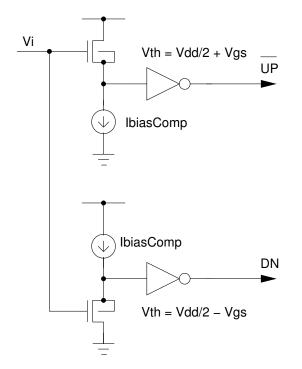

|      | Comparators                                   | 4 |

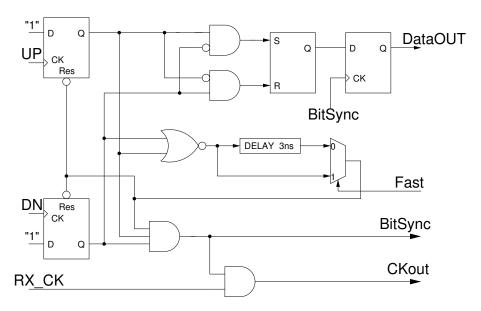

| 2.15 | Data and clock recovery circuit               | 5 |

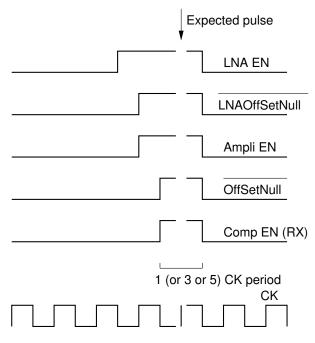

|      | Enabling signals in the receiver              | 6 |

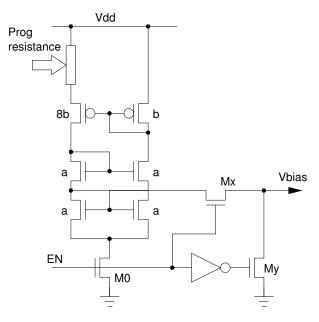

|      | Bias Circuit                                  |   |

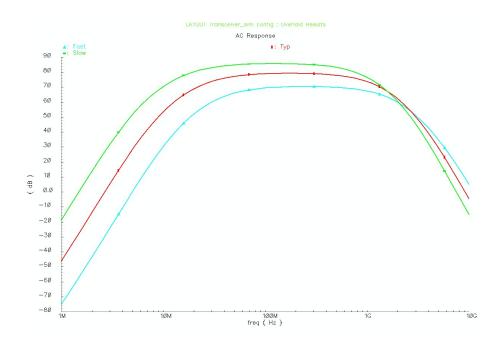

|      | AC gain of the Receiver chain                 |   |

|      |                                               |   |

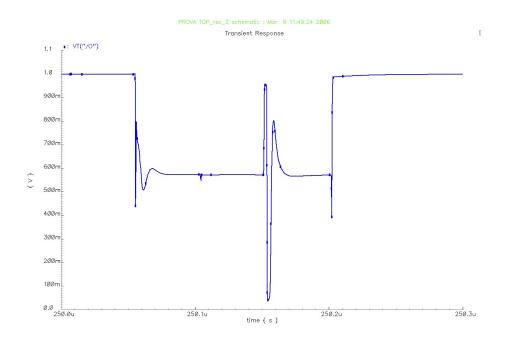

| 2.19  | Receiver chain output                                             | 39 |

|-------|-------------------------------------------------------------------|----|

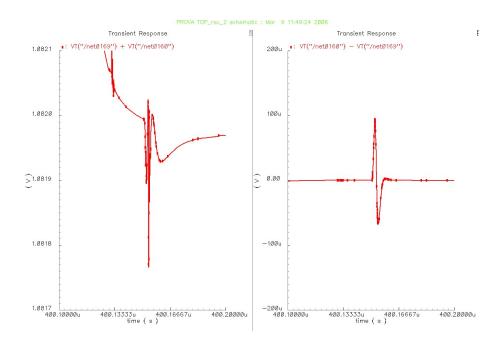

| 2.20  | LNA inputs sum and difference                                     | 40 |

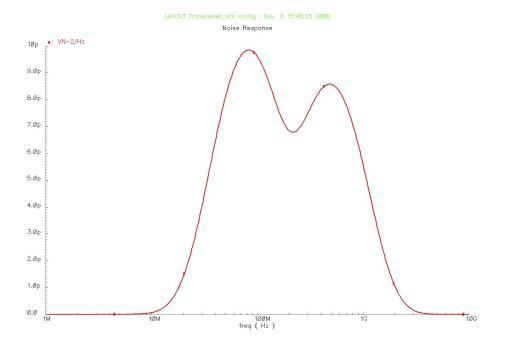

|       | Amplifier output noise                                            | 40 |

|       | Receiver block diagram                                            | 41 |

| 2.23  | PLL block diagram                                                 | 42 |

|       | Ring oscillator stage (+ common bias)                             | 43 |

|       | Frequency Divider                                                 | 44 |

|       | Phase Frequency Detector                                          | 44 |

| 2.27  | Charge Pump                                                       | 45 |

| 2.28  | PLL passive loop filter                                           | 46 |

|       | PLL Programmable loop filter                                      | 47 |

| 2.30  | OPAMP offset compensation                                         | 49 |

|       | Filter Phases                                                     | 50 |

|       | OP AMP schematic                                                  | 50 |

| 2.33  | PLL loop filter control signal for 160 kHz reference frequency    | 51 |

| 2.34  | PLL filter simulation                                             | 52 |

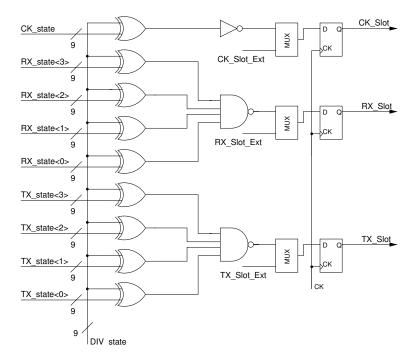

| 2.35  | RX_Slot, CK_Slot and TX_Slot generation                           | 53 |

| 2.36  | Synchronization hierarchy                                         | 55 |

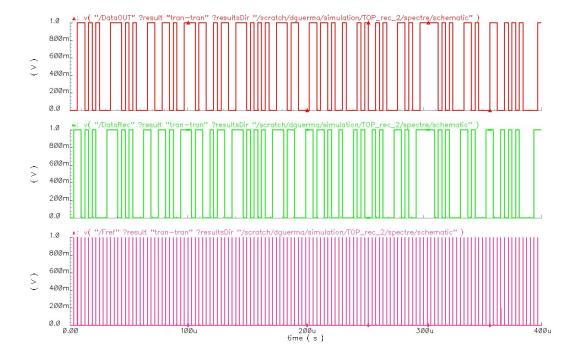

| 2.37  | Received bits, transmitted bits, synchronization signal gener-    |    |

|       | ated by the receiver                                              | 56 |

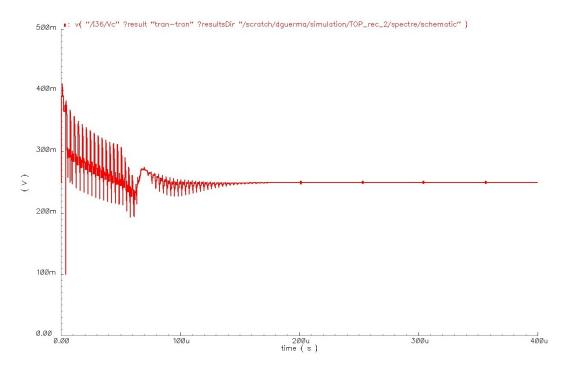

| 2.38  | PLL control voltage                                               | 57 |

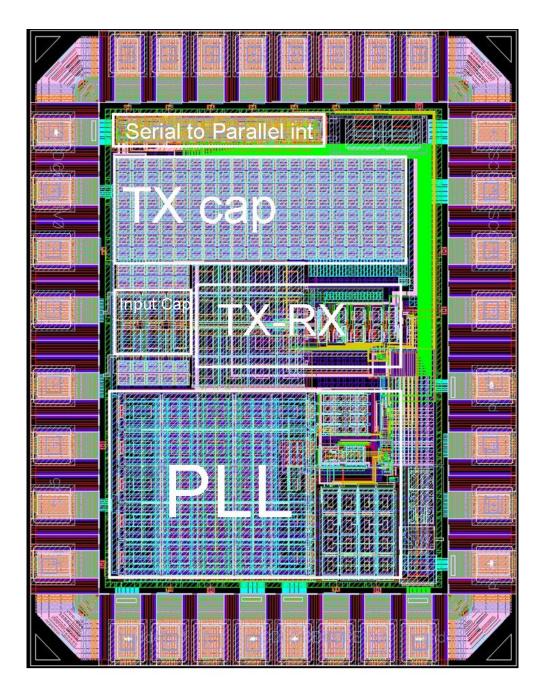

| 3.1   | Top Layout                                                        | 61 |

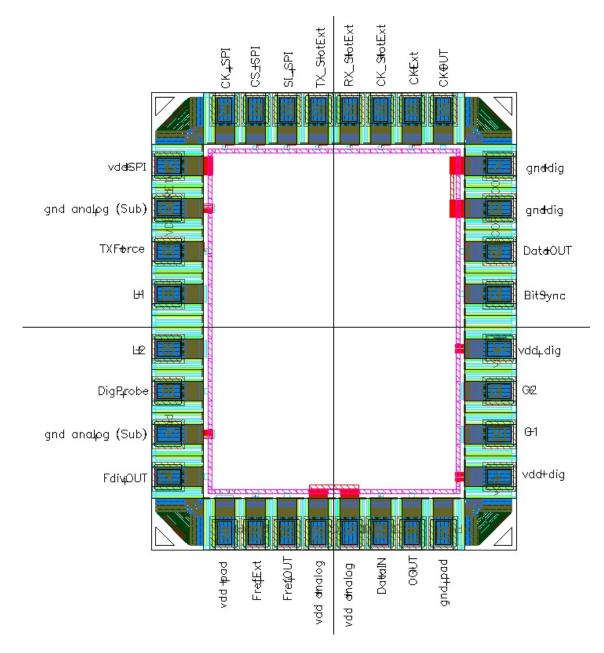

| 3.2   | Pad Ring                                                          | 62 |

|       | Ŭ                                                                 |    |

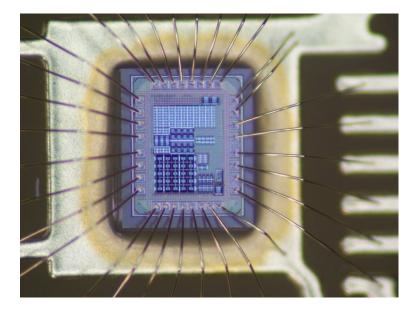

| 4.1   | Chip-On-Board assembly                                            | 68 |

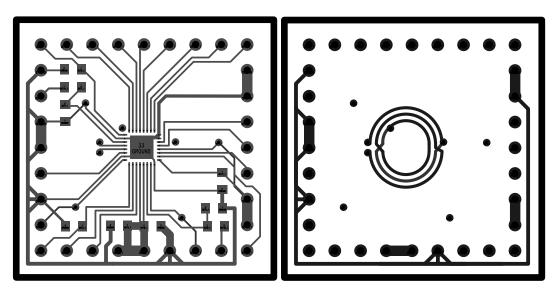

| 4.2   | Top (left) and bottom (right) layers of the board                 | 69 |

| 4.3   | On board inductor                                                 | 70 |

| 4.4   | Measured and modeled inductor reflection coefficient              | 71 |

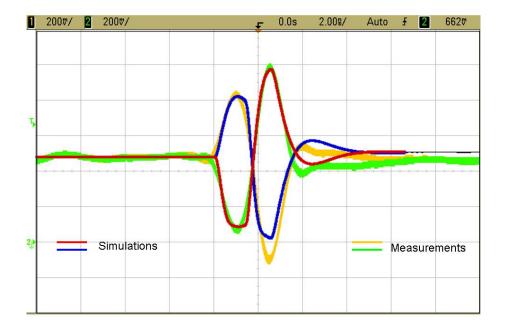

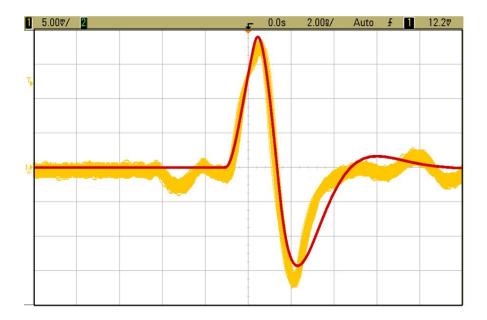

| 4.5   | Measured and simulated pulse                                      | 72 |

| 4.6   | Measured and simulated pulse (k=0.05, C=14 pF, R = 50 $\Omega$ ). | 73 |

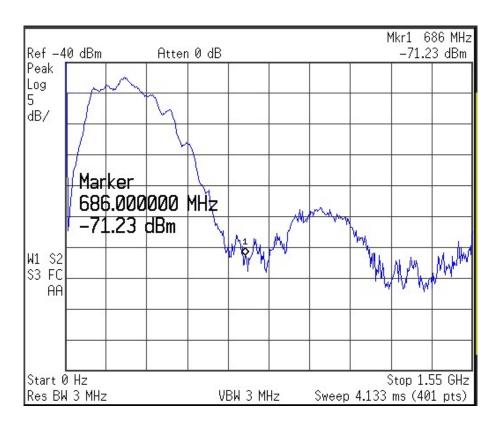

| 4.7   | Measured Spectrum at 1 mm distance                                | 74 |

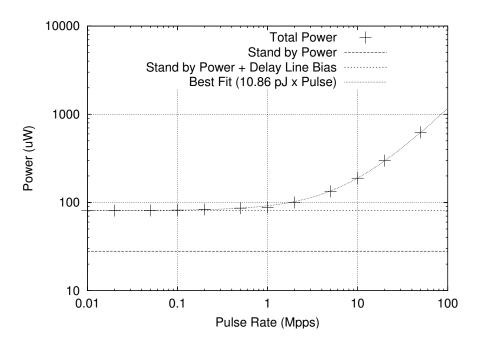

| 4.8   | Measured power of the transmitter, not duty cycled                | 75 |

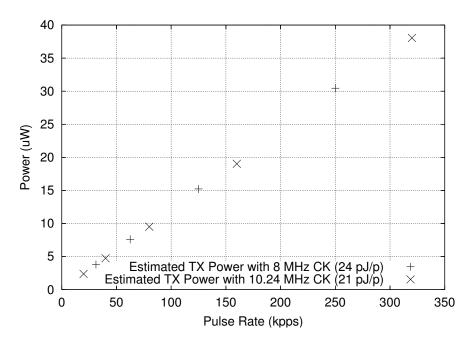

| 4.9   |                                                                   | 76 |

| 4.10  | Analytical and (indirectly) measured coupling factor for the      |    |

|       | stacked inductors                                                 | 77 |

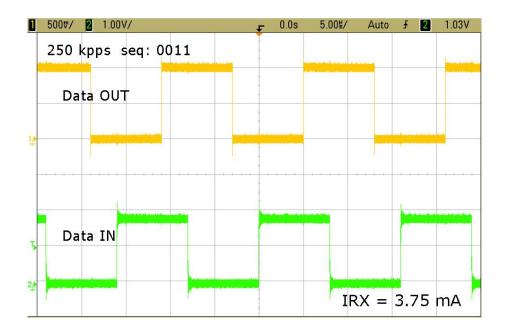

| 4.11  | Transmitted and received sequence for 9 mm distance               | 79 |

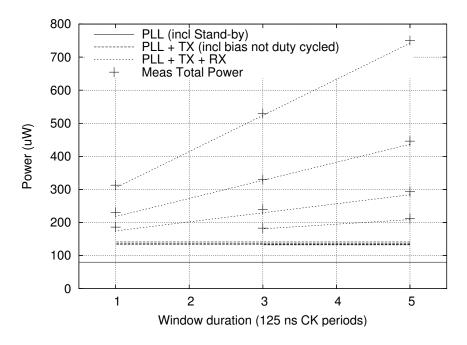

|       | Transceiver power consumption                                     | 80 |

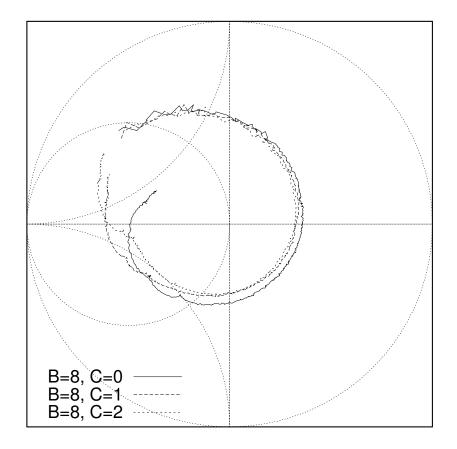

|       | Input reflection coefficient for different input capacitance      | 83 |

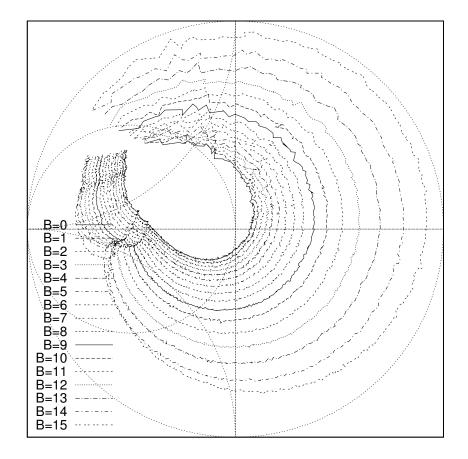

| 4 4 4 | Input reflection coefficient for different LNA bias currents      | 84 |

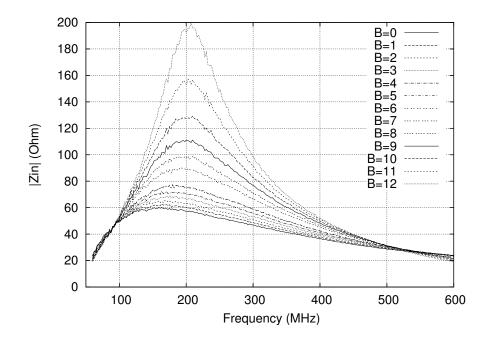

| 4.15 | Input impedance moduli for different LNA bias currents                           | 85  |

|------|----------------------------------------------------------------------------------|-----|

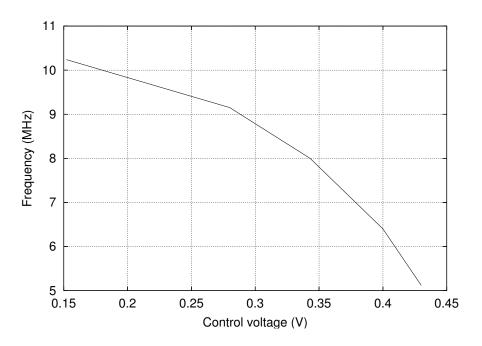

| 4.16 | VCO frequency versus control voltage                                             | 87  |

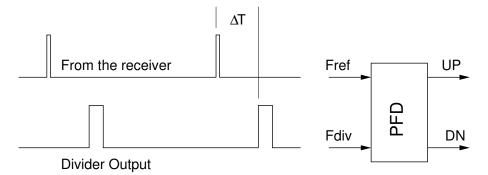

|      | PFD inputs in lock condition                                                     | 87  |

| 4.18 | Detailed PLL filter operations                                                   | 88  |

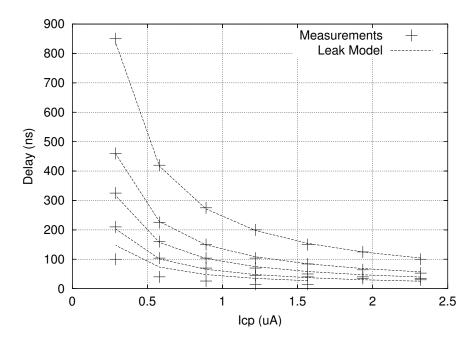

| 4.19 | PFD edges delay $\Delta T$ as a function of the charge pump current              |     |

|      | $I_{CP}$ for different VCO control voltages $\ldots \ldots \ldots \ldots \ldots$ | 90  |

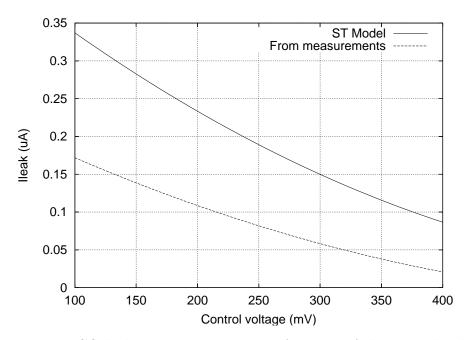

| 4.20 | VCO leakage current $I_{leak}$ as a function of the control voltage -            |     |

|      | ST model and curve extracted from measurements                                   | 91  |

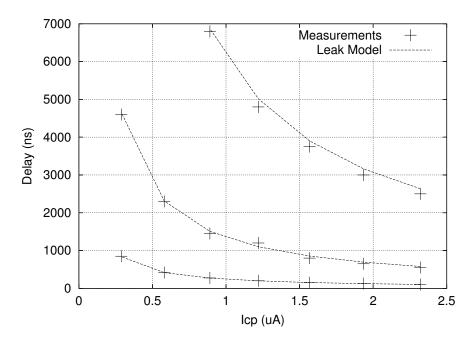

| 4.21 | PFD edges delay $\Delta T$ as a function of the charge pump current              |     |

|      | $I_{CP}$ for different division ratio at 10.24 MHz VCO frequency                 | 92  |

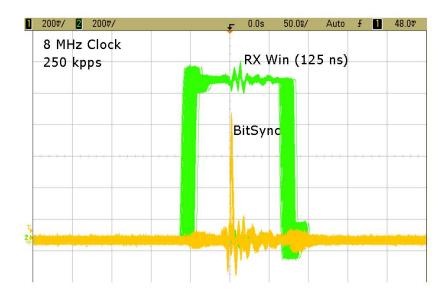

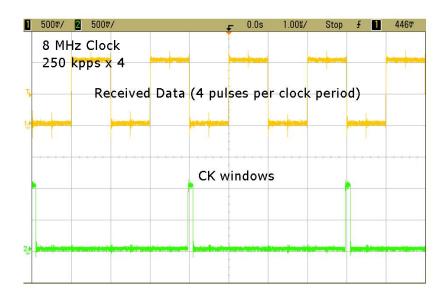

| 4.22 | Received pulse fitted by the clock receiving window                              | 92  |

| 4.23 | 3 received pulses at 250 kpps fitted by the clock receiving win-                 |     |

|      | dows of 125 ns                                                                   | 93  |

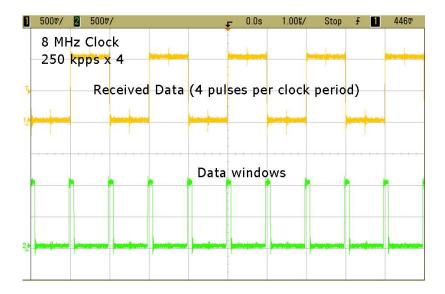

| 4.24 | Received multiple data and clock windows                                         | 93  |

| 4.25 | Received multiple data and data windows                                          | 94  |

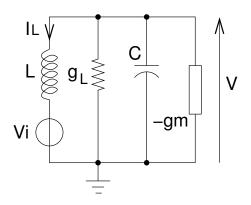

| 4.26 | LC tank including losses and negative gm                                         | 100 |

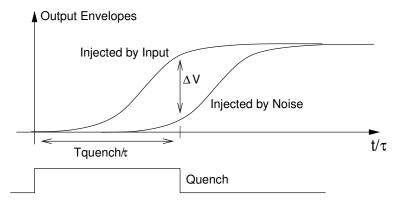

| 4.27 | Start up envelope of a VCO in presence and absence of induced                    |     |

|      | signal on the inductor                                                           |     |

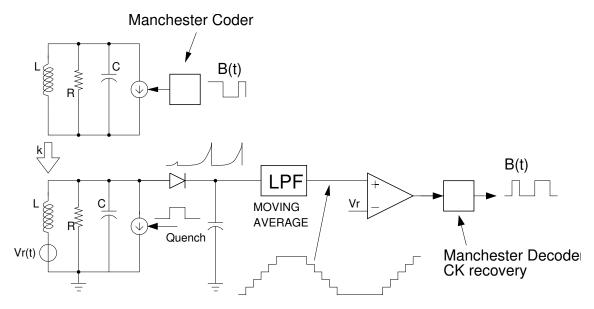

| 4.28 | VCO and super-regenerative receiver                                              | 106 |

| 4.29 | Possible transceiver based on a super-regenerative principle                     | 107 |

## Introduction

The present wireless sensor network scenario is characterized by networks made of tens of nodes spaced by some meters (e.g. fire alarm sensors, anti-intrusion systems and so on). The development of new wireless sensor network applications such as biomedical sensing or wearable-paintable computers requires hundreds of ultra low power nodes communicating over small distances (1-5 cm) at low-to-moderate bit rates [1],[2].

Because the distance between nodes turns to be lower than the wavelength up to many GHz, a near file approach can gives better performance in terms of energy per bit, and will be considered in this work. Moreover, the antenna size for an efficient transmitter must be 1/4 of the wavelength, and this is not feasible for a 1 cm node and for frequencies lower than 7.5 GHz. The above considerations lead to the adoption of a pulse based inductive approach similar to the one presented in [3] for chip-to-chip communications.

In a pulse based communication with low bit rate the information is concentrated in narrow time slots with respect to the pulse repetition period and the average power consumption of the receiver can be strongly reduced by means of duty cycling [4],[5]. However, differently form [4] and [5], a main objective of this work is to exploit the maximum level of integration avoiding the requirements of a precise local oscillator (quartz) on each node for the synchronization and duty cycling. In the proposed architecture the oscillator is replaced with a Phase Locked Loop (PLL) that locks the local time base on the incoming signal. In a strongly connected network the above solution allows to achieve a global synchronization by locking all the nodes to a small set of master nodes providing a common time reference with a reduced set of crystal oscillators.

## Chapter 1

## Short Range Wireless and Inductors Coupling

Before going through the description of the implementation, this chapter gives an overview of the system starting from the analysis of the inductive coupling between inductors to the inductor design and the architecture definition. Finally the proposed synchronization scheme for an impulsive radio, based on a local PLL is described an analyzed.

#### 1.1 Coupled inductors

Since the communication is based on coupled inductor, in this section an introduction on the problem is given.

Assuming that the current  $I_1$  flows through an inductor  $L_1$  made of  $N_1$  turns of radius  $R_1$  (each one of area  $A_1 = \pi R_1^2$ ), from a distance greater than 5 times the coil radius the coil can be described as a magnetic dipole MD.

$$MD = N_1 A_1 I_1 = N_1 \pi R_1^2 I_1 \tag{1.1}$$

The electromagnetic filed surrounding a magnetic dipole of magnetic moment MD can be written as [6]

$$E_{\phi} = \xi \frac{\beta^3}{4\pi} MD\left(\frac{1}{\beta r} - \frac{j}{(\beta r)^2}\right) \sin(\theta) e^{j\beta r}$$

(1.2)

$$E_{\theta} = 0 \tag{1.3}$$

$$E_r = 0 \tag{1.4}$$

$$H_{\phi} = 0 \tag{1.5}$$

$$H_{\theta} = -\frac{\beta^3}{4\pi} MD\left(\frac{1}{\beta r} - \frac{i}{(\beta r)^2} - \frac{1}{(\beta r)^3}\right)\sin(\theta)e^{j\beta r}$$

(1.6)

$$H_r = \frac{\beta^3}{2\pi} MD\left(\frac{j}{(\beta r)^2} + \frac{1}{(\beta r)^3}\right) \cos(\theta) e^{j\beta r}$$

(1.7)

and where r is the observation distance,  $\beta = 2\pi\lambda$  and the angles  $\phi$  and  $\theta$  are illustrated in figure 1.1.

The Poynting vector is defined as

Figure 1.1: E.M. filed generated by a magnetic dipole

$$\vec{W} = \vec{E} \times \vec{H}^* \cdot \hat{r} \tag{1.8}$$

that is given by a real part (radiative field) and an imaginary part (reactive field).

$$W = -\frac{E_{\phi}H_{\theta}}{2} \frac{\pi}{2} \xi \frac{MD^2}{\lambda^4} \frac{1}{r^2} \sin^2(\theta) \left[1 + j\frac{1}{(\beta r)^2}\right]$$

(1.9)

The radiated (active) power is given by the integral of the real part of 1.9 over a surface including the dipole. Assuming a sphere it is

$$P = \int_{s} W ds = \int_{0}^{2\pi} d\phi \int_{0}^{\pi} d\theta W r^{2} \sin(\theta) d\theta$$

that is

$$P = \frac{4}{3}\pi^{3}\xi \frac{MD^{2}}{\lambda^{4}}$$

(1.10)

Note that is a lossless space the radiated power does not depend on the sphere radius.

Assuming now that a second inductor  $L_2$  with radius  $N_2$  and number of turns  $N_2$  is put on the same plane of  $L_1$ ; neglecting the radiated power P, the equation of the system can be written as

Figure 1.2: Coupled inductors

$$V_1 = L_1 \frac{\mathrm{d}I_1}{\mathrm{d}t} + M_{12} \frac{\mathrm{d}I_2}{\mathrm{d}t}$$

(1.11)

$$V_2 = M_{12} \frac{\mathrm{d}I_1}{\mathrm{d}t} + L_2 \frac{\mathrm{d}I_2}{\mathrm{d}t} \tag{1.12}$$

(1.13)

and the coupling factor k is defined as

$$k = \frac{M_{21}}{\sqrt{L_1 L_2}} = \frac{M_{12}}{\sqrt{L_1 L_2}}$$

If the second inductor is open  $(I_2 = 0)$  and  $L_1 = L_2 = L$ , equations 1.11 become

$$V_1 = L_1 \frac{\mathrm{d}I_1}{\mathrm{d}t} \tag{1.14}$$

$$V_2 = M_{12} \frac{\mathrm{d}I_1}{\mathrm{d}t}$$

(1.15)

and then

$$k = \frac{V_2}{V_1}$$

The coupling factor can therefore be computed as the ratio of the induced voltage  $V_2$  over the voltage  $V_1$ .

The concatenated flux with  $L_2$  is given by

$$\Phi_c = \mu H_\theta N_2 A_2 =$$

and if the distance is small with respect to the wavelength (near field approximation)

$$\beta r = \frac{2\pi}{\lambda} r \ll 1 \quad \Rightarrow \quad \frac{r}{\lambda} \ll \frac{1}{2\pi}$$

$$\Phi_c = \mu N_2 A_2 M D \frac{16\pi^5}{\lambda^6 r^3}$$

so the induced e.m.f. is

$$V_2 = \frac{\mathrm{d}\Phi_c}{\mathrm{d}t} = \mu N_2 A_2 M D \frac{\mathrm{d}H_\theta}{\mathrm{d}t}$$

and replacing the expression of MD

$$V_2 = \mu A_1 A_2 N_1 N_2 \frac{1}{4\pi r^3} \frac{\mathrm{d}I_1}{\mathrm{d}t}$$

The the mutual inductance is therefore

$$M_{12} = M_{21} = \frac{\mu A_1 A_2 N_1 N_2}{4\pi r^3} = \frac{\mu \pi R_1^2 R_2^2 N_1 N_2}{4r^3}$$

and the coupling factor k is

$$k = \frac{M_{21}}{L} = \frac{\mu \pi R_1^2 R_2^2 N_1 N_2}{4Lr^3}$$

(1.16)

that with the two inductor equals it is

$$k = \frac{\mu \pi R^4 N^2}{4Lr^3} = \frac{V_2}{V_1} \tag{1.17}$$

Note that k is proportional to the squared inductor area and the squared number of turns. It also goes as the distance up to the minus 3 and rapidly decreases as the distance increases; however it does not depends on the frequency (as long as  $\beta r \ll 1/(2\pi)$ ) but only on the geometry of the system.

#### 1.2 Pulse Based Radio

In this section a brief analysis of the pulse based communication used in this design is given. All the equations and the plots reported in this section refers to the pulse shape chosen for the implementation.

Because the inductor behave like a short circuit for the DC, the voltage pulse forced across the inductor must have a zero average value to avoid useless power dissipation.

For maximum hardware simplicity, in this design a squared signed pulse is considered; the voltage levels are assumed to be  $\pm 1$  V, to be compliant with the further implementation in 90 nm CMOS technology.

Applying the voltage pulse  $V_t(t)$  (figure 1.3) of duration  $\tau_p$  to an inductor, the resulting current waveform is shown in figure 1.4.

Since  $V_t(t)$  is the superimposition of two pulses, the spectrum can be easily calculated as

$$V_t(\omega) = \frac{V_0 \tau_p}{2} \frac{\sin\left(\frac{\omega \tau_p}{4}\right)}{\frac{\omega \tau_p}{4}} e^{\frac{j\omega \tau_p}{4}} - \frac{V_0 \tau_p}{2} \frac{\sin\left(\frac{\omega \tau_p}{4}\right)}{\frac{\omega \tau_p}{4}} e^{\frac{-j\omega \tau_p}{4}}$$

and with few algebra

$$V_t(\omega) = -jV_0\tau_p \frac{\sin\left(\frac{\omega\tau_p}{4}\right)^2}{\frac{\omega\tau_p}{4}}$$

The spectrum is shown in figure 1.5.

The energy needed to produce the pulse is given by

$$E = \int_{-\infty}^{+\infty} V_0 I(t) \mathrm{d}t = \frac{V_0 I_M \tau_p}{2}$$

Figure 1.3: Voltage pulse across the inductor

and considering the relationship between current and voltage into the inductor L it is

$$E = \frac{V_0^2 \tau_p^2}{2L}$$

while the energy (in  $V^2$ ) carried by the pulse is

$$E_p = V_0^2 \tau_p^2$$

that, as known by the Parseval's theorem, is equal to

$$E_p = \frac{1}{2\pi} \int_{-\infty}^{+\infty} \|V(\omega)\|^2 \mathrm{d}\omega$$

The maximum of the spectrum is located at  $f \simeq 0.742/\tau_p$  and is about  $0.725V_0\tau_p$ . The energy in the first lobe of  $V(\omega)$ , hence for  $f < 2/\tau_p$  is the 85% of the signal energy. Being  $E_1$  the energy of the first lobe, it is

$$E_1 = \frac{1}{2\pi} \int_{-4\pi/\tau_p}^{+4\pi/\tau_p} \|V(\omega)\|^2 d\omega = \frac{(V_0\tau_p)^2}{2\pi} \frac{2}{\pi\tau_p} \int_{-\pi}^{+\pi} \frac{\sin(x)^4}{x^2} dx$$

Figure 1.4: Current pulse through the inductor

$$\simeq \frac{2}{\pi} V_0^2 \tau_p 1.334 \simeq 0.85 E_p$$

#### 1.3 Inductor design

The inductor to be used as antenna must satisfy certain requirements, due both to technological and functional issues.

- The features must be compatible with a standard low-cost PCB technology (minimum width and spacing greater than 6-7 mils). The substrate must be a standard PCB material, like FR4. No special materials are considered.

- The self resonant frequency must be higher than the maximum frequency of the transmitter bandwidth, otherwise a non negligible amount of the signal energy does not go through the inductor but is shorted by the parasitic capacitance.

- The size of the inductor cannot be as large as one wants. Because of the node size physical limitations and the parasitic capacitance, the area

Figure 1.5: Voltage pulse spectrum

should be kept lower than  $1 \text{ cm}^2$ .

• The value of the inductance can not be too small, otherwise high peak currents are required in the transmitter. High transmitter peak currents require a very low transmitter output impedance, together with a power supply able to provide such a peak.

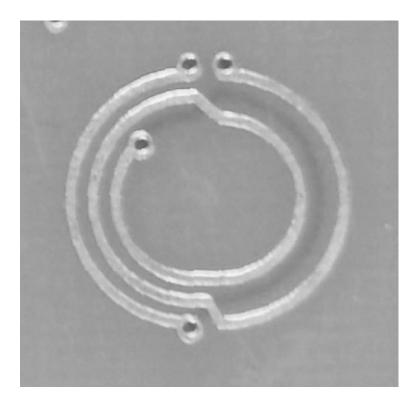

Considering these limitations, a 3 turns, 8.1 mm diameter symmetrical inductor has been designed (figure 1.6) and simulated with Agilent ADS Momentum. A inductance value of 76 nH is found.

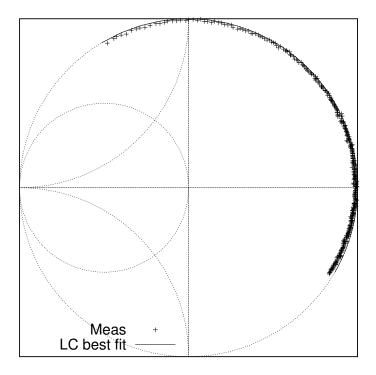

Figure 1.7 shows the model extracted from measurements, that are in good agreements with simulations. The self resonate frequency is about 800 MHz.

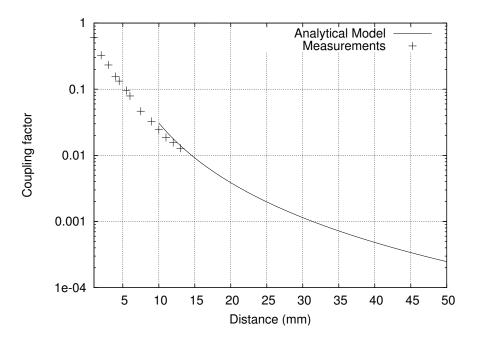

The coupling factors between two inductors laid out on the same plane as a function of the distance has been measured too. Measurement results are shown in figure 1.8, together with the analytical model based on eq. 1.17. Since the three turns of the inductor are very different in terms of radius due to the planar implementation, instead of  $N\pi R^2$  an "effective area"  $A_{eff}$  has

Figure 1.6: Antenna layout

been used in eq. 1.17.

$$A_{eff} = \sum_{i=1}^{N_{turns}} \pi R_i^2$$

#### **1.4** SNR and Pulse Duration trade-off

The receiver antenna is sensible to the coupled magnetic filed, but is really poor in term of "radiative field" antenna in the band of interest. In fact if we consider the maximum linear "length" of the antenna, that is the diameter, it is about 1 cm, that is a quarter of the wavelength at 7.5 GHz.

This means that the antenna has a very low efficiency for electromagnetic waves in the range between 0 and 1 GHz, and therefore the performance of the receiver can be assumed to be noise limited (unfortunately further measurements will show that this statement is not true).

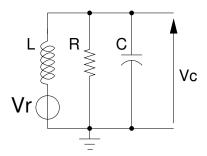

Once the spectrum of the pulse is found and the antenna is chosen, a key point in the receiver design is to determine the optimal filter needed on the receiver to maximize the Signal to Noise ratio (SNR). For maximum simplicity and to avoid any external component apart from the inductor, only a capacitor and a resistor are putted in parallel with the inductor to create a parallel

Figure 1.7: Antenna equivalent model

resonator, as shown in figure 1.9.

With an LC resonator the pulse can be detected over the noise, that is generated by both the L series resistance and the damp resistor. Assuming a parallel resonator structure, to maintain the signal waveform without ringing, a quality factor lower than 1 must be used. Simulation can be done for a quality factor Q = 0.8 to determine the optimal value of the capacitance, hence of the resonance frequency. Since the Q of the resonator is much lower than the Q of the inductor itself, only the resistance R will be considered as a noise source.

The transfer function with respect to the input is low pass and is given by

$$H_s(\omega) = \frac{V_c}{V_r} = \frac{\omega_0^2}{\omega_0^2 - \omega^2 + j\omega\frac{\omega_0}{Q}}$$

with

$$\omega_0 = \frac{1}{\sqrt{LC}} \qquad Q = \frac{R}{\omega_0 L}$$

while the output noise PSD is given by

$$P_n = \left\|\frac{j\omega/C}{\omega_0^2 - \omega^2 + j\omega\frac{\omega_0}{Q}}\right\|^2 \frac{4KT}{2\pi R}$$

and the squared effective noise is

$$V_n^2 = \int_{-\infty}^{+\infty} P_n d\omega = \frac{1}{4\omega_0 C^2} Q \frac{4KT}{R}$$

Figure 1.8: Coupling factor as a function of the distance

Figure 1.9: Receiver Filter

and, being  $Q = \omega_0 C R$

$$V_n^2 = \frac{KT}{C}$$

Simulations show that to achieve the best ratio  $V_p^2/V_n^2$ , where  $V_p$  is the peak of the output pulse, while  $V_n^2$  is the noise power expressed as squared effective value, it must be

$$\omega_0 = 0.612 \frac{2\pi}{\tau_p} \tag{1.18}$$

and the (positive) peak of the output signal is

$$V_p = 0.775 V_{r0} = 0.775 k V_0 \tag{1.19}$$

Since the noise only depends on the capacitor value, and the received signal depends on the coupling factor, the SNR of the receiver can easily be calculated as a function of the capacitance C and the coupling factor k.

$$SNR = \frac{V_p^2}{V_n^2} = \frac{0.775kV_0C}{KT}$$

(1.20)

Increasing the quality factor at fixed frequency does not change the noise level, that depends only on the tank capacitance, but the response of the filter becomes oscillating (ringing). Considering the peak of the damped sine wave, the signal peak to noise ratio can be increased of a ratio up to about 4 (spectre sim) even if the detection is then more difficult due to the pulse tails. In this implementation the quality factor has been chosen equal to 0.8, so to

avoid any ringing in the circuit and use a pulse polarity detection.

As can be noted from eq. 1.19, if the coupling factor k is small, the received voltage is very small, regardless of the current used into the transmitter (assuming that the transmitter and the receiver inductor have the same characteristics). Even if the signal to noise ratio can be kept greater than 10 dB, the signal bandwidth remains huge. To amplify the signal to a detectable level an amplifier with a high gain, high bandwidth and low noise figure is required (the input referred noise should be in the order of some microvolts).

Nevertheless, increasing the maximum current into the transmitter allows the use of longer pulses, and consequently to reduce the bandwidth according with eq. 1.18 and to increase the SNR, but has no effects, in principle, on the received voltage  $V_r$ . However the receiver power consumption can take advantage of the band reduction, payed by a higher one in the transmitter.

Considering the value of the coupling factor previously computed for the inductors, it is possible to find the minimum bandwidth required for the pulse at a desired output SNR (eq 1.20).

At 5 cm distance  $k \simeq 1.25 \cdot 10^{-4}$  and with 1 V pulse amplitude in the transmitter the zero-peak received signal is (from eq. 1.19)

$$V_r = 97 \mu V$$

To achieve a SNR of 13 dB on the receiver, that means a 10 dB SNR at the receiver input plus 3 dB margin for the receiver Noise Figure, it is

$$V_n \simeq 22\mu V$$

and the (minimum) capacitance required on the receiver is

$$C = \frac{KT}{V_n^2} \simeq 8.5 \ pF$$

therefore the maximum resonance frequency for the receiver is given by

$$f_0 = \frac{1}{2\pi\sqrt{LC}} \simeq 204MHz$$

and from eq. 1.18, the minimum pulse duration is

$$\tau_p = \frac{0.612}{f_0} \simeq 3.1 \ ns$$

$$R = \frac{Q}{2\pi C f_0} \simeq 78 \ \Omega$$

When a constant voltage is applied to an inductor, the current grows linearly with time. If the total pulse duration is  $\tau_p$ , the peak current in the inductor is

$$I_{MAX} = \frac{V\tau_p}{2L} \simeq 20 \ mA \tag{1.21}$$

Note that this current, even if it is needed only for a very short time, and therefore the power turns out to be negligible, it must be handled by the transmitter and the power supply. An on-chip decoupling capacitor is necessary to avoid this 20 mA/3 ns pulses to flows over the  $V_{DD}$  bond wires and lines and spreading a large amount of di/dt noise. For the chosen number for the inductor and the pulse duration, a reasonable value of the capacitor is found.

The total charge required by the transmitter for a single pulse is given by

$$Q = \frac{I_{MAX}\tau_p}{2} = 30 \ pC$$

Assuming to tolerate voltage drop of 100 mV on a "charge tank" capacitance that supplies the transmitter, the minimum value required for this capacitance  $C_T$  is given by

$$C_T = \frac{Q}{\Delta V} = 300 \ pF$$

that can be integrate in a relatively small area on chip. Moreover this capacitance is not required to be linear and MOS capacitance can be extensively used. Apart from the capacitor, the transmitter driver must be able to drive 20 mA peak current with a voltage drop lower than 100 mV; this fixes a constraint on the transmitter output resistance  $R_{out,T}$ .

$$R_{out,T} < \frac{\Delta V}{I_{MAX}} = 50 \ \Omega$$

# 1.5 Receiver duty cycling and synchronization issues

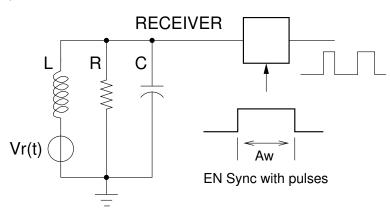

The main advantage of a pulse based system with respect to a narrow band one is that the all the information is squeezed in a very small time interval (in this case  $\tau_p = 3$  ns) within the pulse period (i.e.  $T_p = 50 \ \mu s$  at 20 kpps pulse rate).

This means that the receiver is really "needed" for only 3 ns over 50  $\mu$ s, or in other words that the receiver can be hardly duty cycled to dramatically reduce its average power consumption (figure 1.10).

Realistically, the receiver must be turned on some time before the pulse is

Figure 1.10: Receiver duty cycling

coming and can be turned off some time after the pulse. In order to open this "window" for the receiver, and to avoid the use of a wake-up radio, a local time base must be kept in the receiver so the node knows when the next pulse is coming and wake up the receiver.

Of course there is an obvious trade off between the window duration  $A_w$  and its accuracy. A longer window will result in a lower receiver duty cycle, but in the same time in a lower power consumption in the local time base, since the required accuracy is lower. On the other hand a window that perfectly fit the pulse leads to the minimum power for the receiver, but requires a very accurate and power hungry time base.

As example, be  $T_1$  and  $T_2$  the period of the local clock of the nodes 1 (transmitter) and 2 (receiver) respectively. The relative accuracy is indicated with  $\alpha$ . Assuming a communication scheme based on packets of N bits and an ideal synchronization system that is perfectly locked during the packet

reception, the local time base in the node 2 must keep the time only between one packet and the next one.

At the beginning of the new packet, the time difference between the clock of the two nodes that want to communicate must be lower than half a window  $(A_w/2)$ , otherwise the pulse is missed by the receiver and the communication fails. In a full duplex communication scenario, the minimum separation between packets must be as long ad the packet itself, to allow for a bidirectional communication. In this case

$$NT_1 - NT_2 = \frac{N}{F_1} - \frac{N}{F_2} = \frac{N}{F_1} - \frac{N}{F_1(1+\alpha)} \simeq T_1 N\alpha < \frac{A_w}{2}$$

With packet of N = 1000 pulses at 20 kpps pulse rate  $(T_1 = 50 \ \mu s) \ NT_1$  must be longer than 50 ms. If  $NT_1 = 50$  ms and  $A_w = 100$  ns (that is about 30 times the pulse duration) the accuracy must be

$$\alpha < \frac{A_w}{2NT_1} \simeq 1 \text{ppm}$$

A so stringent accuracy can only be achieved by providing each node of a crystal oscillator. The requirement of a crystal oscillator leads to an expansive and not fully integrated solution, that is not desired. The receiver duty cycle achieved in this case is

$$DC = \frac{T_{on}}{T} = \frac{NBA_w}{NBT_1 + NT_1} \simeq 10^{-3}$$

The receiver duty cycle could be further reduced by increasing the interleaving between packets, but this will results in an even higher clock frequency accuracy, or in the needing of a wake-up radio.

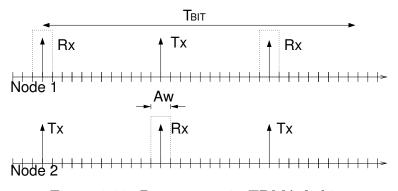

An opposite approach is to assume a streamed data flow, that means that 20 kbps are always exchanged between the transmitter and the receiver. Since the pulse is very narrow compared to the bit rate, many communications can be interleaved in a TDMA fashion (figure 1.11). With the previous numbers for bit rates and window duration  $A_w$ , and assuming another  $A_w$  guard interval between two adjacent windows, up to 250 communications can be established at the same time.

In this case the maximum time without a received pulse is given by the pulse period itself, and the previous equation applies with N = 1.

$$\alpha < \frac{A_w}{2T_1} \simeq 1000 \text{ppm}$$

Figure 1.11: Data stream in TDMA fashion

The required accuracy in this case is quite relaxed, and it does not need for a reference crystal on the receiver. It can continuously track the received signal by means of local D/PLLs.

The receiver duty cycle turns out to be

$$DC = \frac{T_{on}}{T} = \frac{A_w}{T_1} \simeq 2 \cdot 10^{-3}$$

Note that in the stream communication model, the communication is always sets between nodes, and the synchronization is initialized only once at system start up and not at every packet.

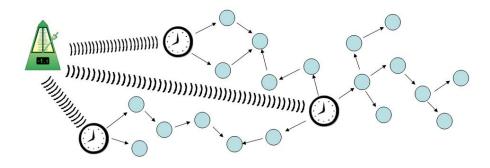

At the network start up, a "master clock" node (provided of a crystal oscillator) starts to transmit pulse so to lock the PLLs of all the neighbor nodes. Once they are locked they can start to transmit pulses to their own neighbors, and in this way the synchronization is propagate to the whole network starting from the "master node" clock.

The main theoretical limitation of this synchronization system remains the locking phase of the PLLs of all the nodes that must be set at (each) power up.

It is well known that the locking time of a PLL is in the order of many hounded of reference periods, and being the reference frequency given by the pulse rate, it is in the order of milliseconds. During this initial interval the receivers cannot be duty cycle.

Further detail on the synchronization scheme will be given in the next chapter or in [7].

## Chapter 2

## **Transceiver Implementation**

The proposed architecture has been implemented in 90 nm STMicroelectronics CMOS technology. The power supply is 1 V and only "standard threshold" (svt) transistors have been used both for analog and digital parts. This allows for compatibility of the transceiver with a system which uses either low threshold or high threshold ones.

The process allows for high density MIM caps (Metal Insulator Metal capacitors) and double oxide transistors, that has been extensively used to realize low leakage high capacitance supply bypass. All the digital parts have been realize with standard cells in triple well to reduce interference with the analog parts. Separated supplies are used for analog and digital parts to reduce interference.

It is well known that standard cells are generally designed for high speedhigh performance systems, and usually employ transistors that are greater than the minimum size. On the other hand in this application the clock frequency is about 10 MHz, that for a 90 nm technology implies that the leakage power of the gates is dominant with respect to the dynamic power due to the switching activity. As result of that, the power of the digital part is given almost by the leakage, that is excessively high because of the standard cell. This can be dramatically reduced by redesigning the logic cells to operate at a lower frequency applying the techniques adopted for ultra-low-power digital design (high threshold devices, lower W, lover supply voltage, sleeping transistors). However standard cell design has been preferred because of design time constraints and because the optimization of the digital circuits is out of the purposes of this work.

As will be discussed later, the circuit requires about 200 bits for programming the PLL, the transceiver and for the digital calibration of the analog parts. These bits are provided by a Serial to Parallel Interface (SPI) interface, designed by Nathan Pletcher and Simone Gambini, Graduate Students at EECS, UC Berkeley.

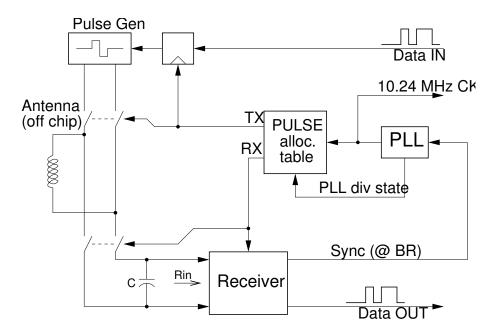

#### 2.1 Transceiver Overview

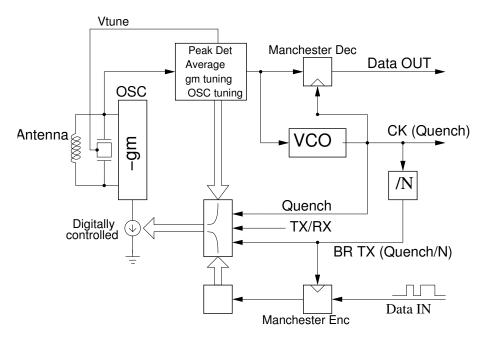

Figure 2.1 shows the block diagram of the implemented transceiver. The chosen nominal pulse rate is 20 kpps.

The main building blocks, that will be discussed in this chapter, are the transmitter, the receiver and the PLL for the clock recovery/generation. As previously described, the received pulses are used to synchronize a local PLL. The PLL frequency has been chosen equal to 10.24 MHz, that is 512 times the 20 kpps pulse rate. This results in a time resolution on 97.7 ns for the local clock.

Figure 2.1: Transceiver block diagram

#### 2.2 Transmitter

The purpose of the transmitter circuit is to force a square pulse on the antenna.

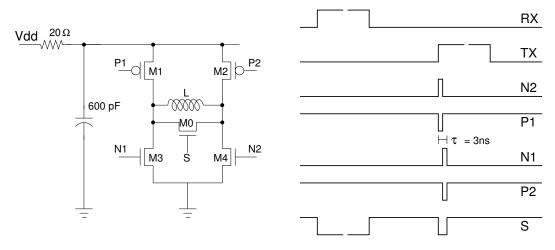

To achieve the maximum swing of the voltage, a differential bridge topology has been used, as shown in figure 2.2 [3] together with the signals waveform. In absence of losses due to the MOS transistors and the inductor finite Q, and

Figure 2.2: Transmitter and transmitter signals

considering that the inductor is a very bad antenna and it does not irradiate power, the transmission of the pulses ideally does not cost power. Assuming the transmitted pulse is "1", during the first semi pulse the current flows from Vdd through M1 and M4 down to ground. During the second pulse instead, the current is forced by the inductor through M2 and M3, and again through the power supply. The opposite phases act if the transmitted pulse is "0". If an RC filter with a proper cut-off frequency is used to power the bridge, during the second semi-period the charge is re-injected into the capacitor by the inductor, and (part of) the energy is recovered. Moreover, the capacitor acts as a charge tank and provides the peak current, that can be relatively high, without loading the Vdd line. In this case, with a theoretical 76 nH inductor and a 3 ns pulse, the peak current is 20 mA.

The transistor M0 is switched on at the end of the pulse and shorts the antenna. This operation damps any current still stored in the inductance caused by a not perfect symmetry between the two phases of the pulse. The transistor M0 is then switched off during the reception phase.

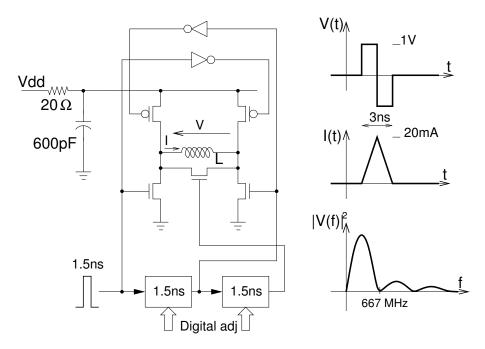

Figure 2.3 shows the generation of the transmitter signals, together with the

voltage and current waveforms and spectrum.

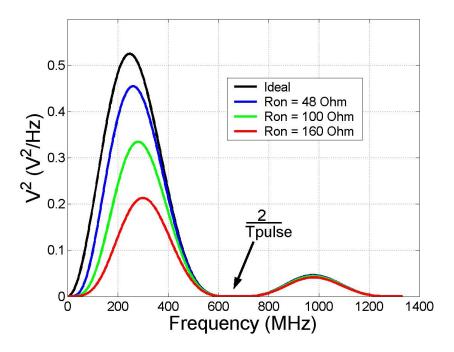

When the voltage pulse is applied to the inductor, because of the finite resis-

Figure 2.3: Transmitter delays and signal generation

tance of the MOS transistors and the current drawn by the inductor, the real voltage signal across the inductor differs from the theoretical one of figure 2.3. Being  $R_{ON}$  the ON resistance of the transistor in the bridge, figure 2.4 shows the power spectrum of the voltage applied to the antenna as a function of the MOS resistance. 50  $\Omega$  series resistance can be achieved with relatively small transistors and do not degrade the signal in an significant way. Post layout simulation results of the transmitter outputs are shown in figure 2.5.

#### 2.2.1 Transmitter control logic

The 3 ns pulse is generated by means of an analog tunable delay (programmable delay line) and an asynchronous logic network sketched in figure 2.6. The programmable delay line is similar to the ring oscillator described in section 2.6.1 and to save power it is activated only 1 CK period before the transmission. This means that the delay line is active only for two clock period each transmitted pulse; with a bit pulse rate of 20 kpps and a clock at 10.24 MHz, the delay

Figure 2.4: Transmitter voltage spectrum

line bias current of 57  $\mu$  results in the negligible average power of 220 nW. An external signal *TXforce* can be used as trigger to force the transmitter. This input will be used for testing the transceiver up to the maximum operating pulse rate, when the receiver is active all the time and the transmitter pulses are packed one after the other. Simulation shows that the maximum achievable pulse rate should be in the order of 200 Mbps that, however, requires a very high SNR and therefore a reduced distance between the transmitter and the receiver.

Figure 2.5: Simulated transmitter output voltage

Figure 2.6: Transmitter Logic

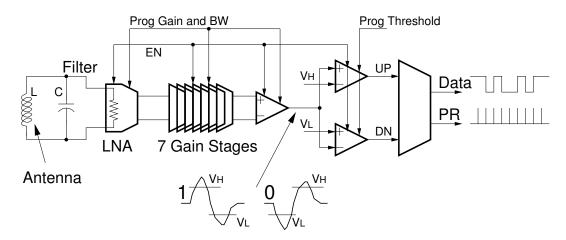

#### 2.3 Receiver

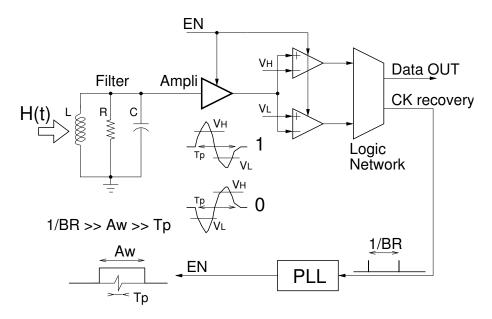

The receiver should amplify the received signal and detect its polarity so to recognize "1" and "0". The receiver block diagram is shown in figure 2.7. Since the channel is supposed to be noise limited, only the noise will be con-

Figure 2.7: Receiver block diagram

sidered and the receiver can operate in a pure energy detection mode (asynchronous or incoherent receiver).

In a fully asynchronous implementation, the amplifier stage must completely recover the attenuation due by the channel. The receiver is therefore an amplifier whose gain is equal to the channel attenuation (80dB) and the total bandwidth is equal to the signal bandwidth (in this chapter the signal bandwidth is assumed to be the bandwidth of the first lobe of the transmitted spectrum of figure 1.5).

Similar gain and bandwidth cannot be achieved with a single stage, therefore the receiver has been splitted in 3 main parts:

- LNA: like in every receiver, the first stage provides a high gain with low noise, so that its output signal is relatively strong with respect to the noise of the following stages. To maximize the supply and substrate noise rejection, a fully differential implementation is mandatory.

- Gain Stages: after the LNA a certain number of gain stage is required to amplify the signal up to a level detectable by the comparators.

- Differential to single-ended Converter: because the comparators are realized in a single-ended topology, a differential to single-ended converter

is needed at the end of the amplifier chain. Note that at the input of this last stage the signal level is relatively high and therefore almost insensible to supply and substrate noise.

- Comparators: the comparators compare the received signal with a couple of threshold, so to determine if the received pulse is either a "0" or "1"

- Logic network: the outputs of the comparators feed a logic circuit able to determine the pulse polarity.

Note that for duty cycling the receiver, it must be capable to be switched off and on periodically. If a few ns switch on and off time is required, it means that all the time constants within the amplifier must be lower than 1 ns, that agrees with the amplifier bandwidth to be in the order of 1 GHz.

#### 2.3.1 LNA

In order to minimize the noise figure of the system, an LNA with a real input impedance is used; in this way an ohmic "noisy" resistor is not required to realize the RLC filter since the real part of the LNA input impedance can be used.

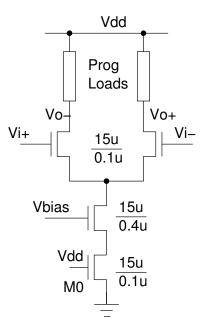

Because of the inductive nature of the link, inductively degenerated LNA is not considered to avoid interference between the antenna and the degeneration inductance. Moreover the wide band nature of the signal recommends to use a broad band LNA. Common gate or shunt feedback LNAs seem to be the best choices. However, as shown in [8], combined common gate - shunt feedback LNA achieves the same input impedance using only one quarter of the current. The schematic is shown in figure 2.8, together with the transistor sizing.

The LNA has been designed to achieve the required  $78\Omega$  real input impedance that is given by

$$Z_{in} \simeq \frac{1}{4g_m} \tag{2.1}$$

where  $g_m$  is the transconductance of the N or P mos. From the previous equation

$$g_m \simeq \frac{1}{4Z_{in}} = 3.21 \mu A/V$$

(2.2)

and assuming  $g_m/Id = 20$  this results in a (minimum) bias current of 160  $\mu$ A for each branch. The effective bias current to ensure the proper input impedance

Figure 2.8: SF-CG LNA

has been chosen equal to 200  $\mu$ A.

It should be noted that the input capacitance of this amplifier is not very critical, because it is resonated out by the antenna (some extra capacitance must be added to reach 8 pF of differential capacitance required). This allows one to increase both the W and the L of the transistors, to to achieve a higer transistors output resistance and then a higher gain. On the other side, 4 transistor (plus the dummy switch M0) must be stacked in 1 V and must be carefully designed to avoid triode region operation of the current sources.

The coupling capacitors C1-C4 (20 pF each one) give a high pass behavior in the transfer function, that does not affect the signal since it has very low power spectral density at low frequency (figure 2.4).

Due to the different DC levels, the LNA is AC coupled with the following stage. Coupling capacitors are used for the cancellation of LNA output offset also, in a fashion similar to the one described later for the gain stages.

Because of the input coupling capacitance needed by the LNA, the turning on time of the LNA is relatively long. The capacitances must reach the nominal bias voltage before the LNA get ready to correctly operate. With a bias current of 200  $\mu$ A for each branch and with 20 pF, 100 ns enables the capacitance to be charged up to 1 V. For this reason in duty cycle mode it is turn on 1 CK

period (97.7 ns) in advance with respect to the following stages.

Simulation shows a differential gain of 21.5 dB and a 3 dB bandwidth from 20 to 950 MHz. The real part of the input admittance  $(\mathcal{R}\{Y_{in}\})$  is shown in figure 2.9.

Figure 2.9: Real part of the LNA input admitance

#### 2.3.2 Gain Stages

The amplifier is implemented with 7 stage 8 dB differential gain. The schematic of the single stage is shown in figure 2.10.

Because of the broad band nature of the input signal, a broad band stage has been used. A resistive load approach has been preferred to a PMOS saturated load because it does not need a common mode feedback circuitry, and because the higher bandwidth than can be achieved thanks to the very small parasitic capacitances of the poly resistors with respect to the PMOS.

Figure 2.10: Amplifier Stage

#### **Design Consideration**

The stages have been designed to optimize the ratio between the gain expressed in dB and the bias current, so to achieve the maximum gain for the minimum current over the required bandwidth.

The design optimization has been performed in MATLAB starting from simulation data. Some considerations on the design are summarized here.

As mentioned before, the required gain is in the order of 80 dB for the whole chain. In the hypothesis that the LNA has 20 dB gain and the differential to single-ended stage has 10 dB gain, the required gain for the gain stage chain is about 50 dB.

It is well known that achieving high gains with a single stage requires to use non minimal length transistors, because of the limited  $g_m/g_d$  ratio (about 10 in 90 nm technology). Moreover the use of resistive loads instead of active ones, limits the maximum available load for the stage to be compliant with the saturation of the transistor.

With a reasonable per-stage gain around 7 dB (2.24), a 50 dB gain can be realized with 7 stages. This means that, with a single pole model for the amplifiers, the bandwidth of each stage must be 7 times the bandwidth required for the whole chain.

| Gain      | $A_v = 2.24$          |

|-----------|-----------------------|

| Bandwidth | B = 3.15  GHz         |

| Load      | $C_L = 50 \text{ fF}$ |

Table 2.1: Differential stage requirements

In section 1.2 the bandwidth of the input signal has been assumed to be limited at the first lobe (666 MHz). However to get the maximum signal to noise ratio, the received signal must be filtered with a bandpass filter with a center frequency  $f_0 = 204$  MHz and a quality factor Q = 0.8, as described in section 1.4.

With a 204 MHz center frequency and Q = 0.8, the upper bandwidth of the signal is limited at  $f_0(1 + 1/(2Q)) = 335$  MHz; a 450 MHz bandwidth for the amplifier chain is reasonably enough to preserve the signal integrity. This constraint results in a 3.15 GHz bandwidth for each stage.

The load is given by the load resistor  $R_L$  and the input capacitance of the following stage, plus the interconnection lines. A load capacitance  $C_L$  of 50 fF on the last stage has been assumed during optimization, to takes into account for the quite large input capacitance of the differential to single-ended converter. The same total load capacitance, probably overestimated, has been assumed for every stage of the chain.

The requirements for the amplifier are summarized in table 2.3.2.

With a single pole model for the amplifier, and neglecting the transistor output resistance, it is

$$A_v \simeq g_m R_L \tag{2.3}$$

$$B \simeq \frac{1}{2\pi R_L C_L} \tag{2.4}$$

that gives

$R_L = 1.01 \ k\Omega \qquad \qquad g_m = 2.22 \ \mathrm{mA/V}$

Assuming the transistor in sub-threshold operation with  $g_m/I_d \simeq 20$ , a minimum bias current of 111  $\mu$ A is required, that gives a minimum bias current of 222  $\mu$ A for the differential pair.

A more detailed model for the transistors, taking into account the effective  $g_m(I_d)$  and  $g_d(I_d)$  relationships, has been used for the design. The resulting optimal bias current is 300  $\mu$ A per stage and the transistor sizing are shown

in figure 2.10. The nominal load resistance turns to be 1200  $\Omega$ .

Simulation shows a gain of 8.8 dB with a -3 dB bandwidth of 3 GHz at nominal condition and bias, when the stage is loaded by another stage and 10 fF capacitances to ground that take into account for interconnections. It should be noted that, since the transistors operate in sub-threshold/weak inversion region, the gate source capacitance is proportional to the bias current (like in a bipolar transistor) and usually it is small compared with the overlap capacitance, enhanced by the miller effect, and the interconnection ones.

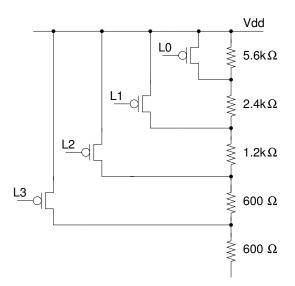

The bias current is programmable around the nominal value; the loads are programmable as well, in order to compensate for variation of gain and bandwidth due to the current adjustment. The programmable load schematic (just one side) is shown in figure 2.11.

Figure 2.11: Programmable load of the amplifier stages

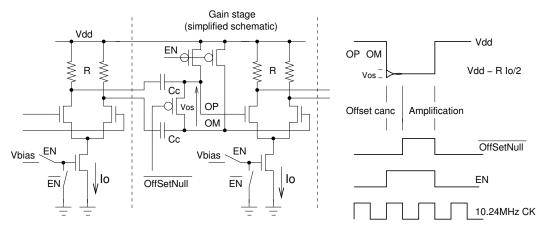

#### Offset cancellation

Clearly a 50 dB gain amplifier is quite sensible to the input offset, given by process mismatches in the transistors and load resistors; an offset cancellation technique is needed to avoid the saturation of the amplifier because of its own offset.

Because of the small gain of the stage (about 2.5 in linear scale) and the relatively low input offset due to the differential pair mismatch (5 mV), the offset cancellation has been performed once each two stages, by means of coupling

capacitors and switches, as shown in figure 2.12 together with the voltage waveforms.

When the stages are off (EN=0) all the outputs potentials move to  $V_{DD}$  and the

Figure 2.12: Offset Cancellation

coupling capacitors  $C_c$  are discharged by means of PMOS transistors. When the stages is enabled (EN=1) the outputs moves to the nominal bias voltage (800 mV), and the following stage is biased through the capacitors at the same voltage. To remove the offset propagation, the input of the following stage are shorted for half CK period ( $\simeq 50$  ns) so to equalize the bias voltages on the inputs; when the short is released the inputs remain at the same bias voltage and the transistors are biased at  $V_{GD} \simeq 0$ .

Note that this "dynamic" bias works only because the amplifier is kept on for short time intervals, during which the capacitors  $C_c$  can keep the bias point almost constant.

A branch realized with PMOS transistor in diode configuration and not shown in figure 2.12 is used to static bias the stages when the amplifier is kept on for a long period of time. In this case the coupling capacitors and the bias transistors result in a high pass behavior in the global transfer function of the amplifier; since the signal spectrum has a band pass shape (figure 2.4) this property turns to be useful to remove flicker and low frequency noise without limiting the signal bandwidth.

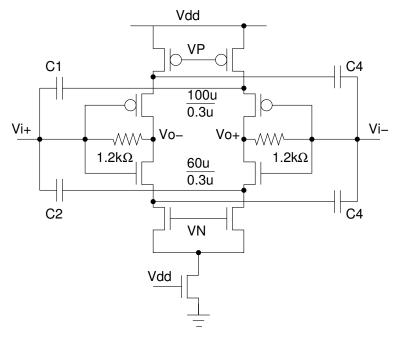

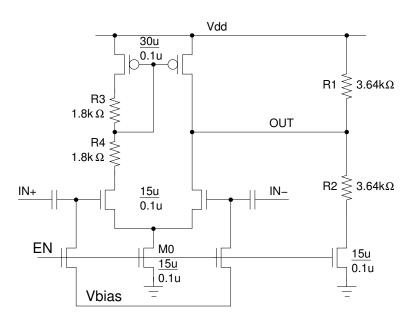

#### 2.3.3 Differential to single-ended converter

The 7 stages amplifier is followed by a pseudo-differential Differential to Signalended converter. This circuit is needed to drive with a rail to rail signal the comparators.

The differential to single-ended amplifier is shown in figure 2.13. It has been designed to allows for the maximum output swing assuming a 50 fF load. Because of the different common mode with respect to the output of the pre-

Figure 2.13: Differential to single-ended amplifier

vious stage, an AC input coupling is mandatory.

Resistors  $R_3$  and  $R_4$  in figure 2.13 bias the PMOS current mirrored transistor with the same  $V_{DS}$  while showing the same (dynamic) load to the differential pairs. Since this stage is pseudo-differential (transistors M0 is only used to switch off the amplifier and it is not a current source)  $R_3$  and  $R_4$  have been designed to minimize the common mode gain. Resistors  $R_1$  and  $R_2$  perform the current to voltage conversion with high linearity.

The simulated gain (differential to single-ended) is 7.1 dB with a -3 dB bandwidth of 1.7 GHz on a 50 fF load. The nominal bias current is 160  $\mu$ A (plus 137  $\mu$ A in the resistors  $R_1$  and  $R_2$ ). The bias current is programmable though 16 levels, as will be described in section 2.4; the load resistance are fixed. Since this amplifier works almost with rail-to-rail single-ended signals, is has been connected to the digital power supply instead of the analog one. This should avoid single-ended feedback to the differential input through the supply line.

#### 2.3.4 Comparators

For maximum simplicity and low power, the comparators have been realized using two inverters whose threshold have been moved by means of source followers, as shown in figure 2.14.

The threshold of the comparators can be varied by adjusting the bias current

Figure 2.14: Comparators

into the followers. The NMOS is realized in triple well in order to have  $V_{SB} = 0$  for every value of  $V_i$  (such as for the PMOS in N-well).

#### 2.3.5 Data and Clock Recovery

A simplified schematic of the data and clock recovery circuit is sketched in figure 2.15, where UP and DN represent the outputs of the comparators. The output bitSync is activated for each pulse received, while CKout only when a pulse is received during the CK window.

To improve the noise immunity of the system and avoids that a noise spike produces an error in the output signal, a pulse is recognized and detected only when both comparators switch between a time interval that is not greater

Figure 2.15: Data and clock recovery circuit

than the duration of the pulse itself. The second pulse of the opposite polarity should follow the first with a maximum delay, otherwise the pulse is not considered. Since the presence of this delay in the data recovery circuit slows down the maximum achievable pulse rate, this features can be disabled by means of the signal *Fast* to operate at very high pulse rates.

### 2.3.6 Receiver control logic

For maximum simplicity of design, the control logic is based on a 8 states Gray counters. The outputs are then combined to generate the signals needed to enable the receiver. The Gray counter, instead of a standard binary one, is use to avoid critical races into the logic that generates the signal.

Because of the temporizing required, the counter must be triggered 3 clock period in advance to the clock edge when the pulse is expected. The generation of the trigger signal is described in section 2.7, while the signals are shown in figure 2.16.

At the beginning of the reception phase the LNA is activated 1 CK period before the desired reception window. After half clock period the offset cancellation phase for the LNA is completed (its outputs are unshorted) and at the same time the amplifiers and the differential to single-ended converter are enable. After another half clock period the offset cancellation phase is completed for the amplifier and the comparators are activated. Then the system

Figure 2.16: Enabling signals in the receiver

is kept on (reception window) for a programmable time variable between 1 to 6 ck period, and at the end all is switched off and all the differential outputs are shorted together.

## 2.4 Bias circuits

All the bias circuits have been implemented according the PTAT circuit (Proportional To Absolute Temperature) of figure 2.17 in order to have a constant  $g_m$  over temperature variations [9].

The current is programmable though 4 bits (16 theoretically equal levels) by means of 4 binary sized PMOS operating in deep triode region. The nominal bias current is set with the configuration "1000", in order to have the maximum possible range above and below the nominal bias point. The transistor M0 is used to switch off the bias circuit in stand by mode. Transistor MX and MY are then used to shorted the bias voltage on the cells. The letters a and b in figure 2.17 are referred to the relative ratio of the transistors [9].

Figure 2.17: Bias Circuit

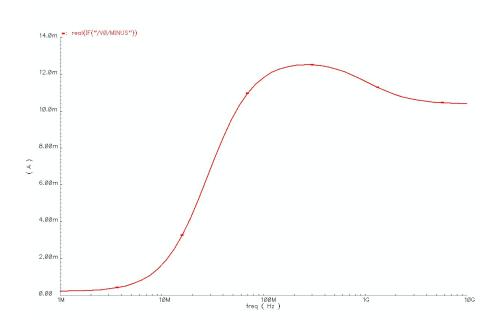

## 2.5 Amplifier simulations

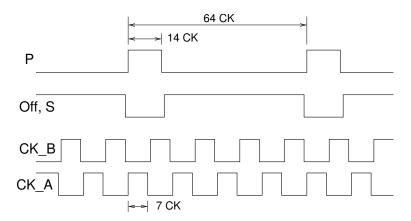

Figure 2.18 shows the simulated gain of the receiver chain (LNA, 7 differential stages and differential to single-ended converted) in standard bias condition and for TYP-Rtyr-Ctyp, SS-Rmax-Cmax and FF-Rmin-Cmin corners at 27°C. In TYP condition the gain is 79 dB and the bandpass from 40 to 740 MHz. Only small variation in the in-band gain can be observed through the corners, and can be easily compensated by means of the digital calibration of bias currents and loads. The big difference in the low frequency part of the curves is due to the AC coupling between the stages (the corners are considered for MIM cap also). The total bias current in TYP condition (including the bias circuits and the comparators, is 3.75 mA.

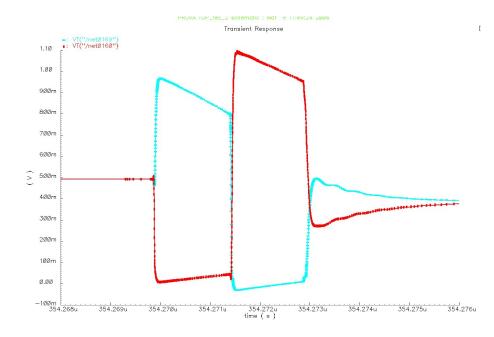

Figure 2.19 shows the voltage at the differential to single-ended output node in duty cycled mode. When the amplifier is off the output is equal to  $V_{DD} = 1 V$ . Then the amplifier is activated and the first half clock ( $\simeq 50 \text{ ns}$ ) is used to switch on the chain and to cancel the offset, as previously discussed. After that the amplifier and the comparators are active for a programmable time from 1 to 5 clock periods. In figure 2.19 the received pulse is exactly in the center of the window (whose duration is one clock period, hence 97.7 ns).

Figure 2.18: AC gain of the Receiver chain

Great concerns in this design come from the stability issues of an amplifier with such an high gain and bandwidth. Post layout simulations across corners show a minimum stability factor around 7.

Because of the single-ended nature of the last stage (even if it is supplied by the digital power line), another source of concern is the feedback through the supply and the ground from the output to the input. The amplifier has been simulated considering 1 nH bondwire inductance on every supply and ground lines. Figure 2.20 shows the LNA input sum and difference in correspondence or a received pulse. The common mode has almost the same amplitude of the differential mode and is easily reduced by the high amplifier CMRR. No oscillation is found (in agreement with the stability factor greater than 1).

Finally figure 2.21 shows the output noise power spectral density  $(V^2/\text{Hz})$ . As expected the maximum of the noise is allocated within the signal bandwidth. The square output effective noise is given by

$$V_{n,eff}^2 = \int \frac{V_n^2}{\Delta f} \mathrm{d}f = 0.0113V^2$$

Figure 2.19: Receiver chain output

and therefore the effective noise is

$$V_{n,eff} = \sqrt{0.0113} = 0.104 \ V$$

Assuming the output signal rail from 0.1 to 0.9 V, the output peak over noise ratio can be written as (equation 1.20)

SNR =

$$\frac{V_p^2}{V_{n,eff}^2} = \frac{(0.9/2)^2}{0.0113} = 15.6 \simeq 12 \ dB$$

Figure 2.20: LNA inputs sum and difference

Figure 2.21: Amplifier output noise

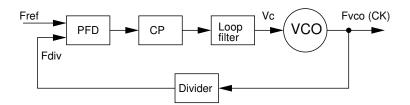

## 2.6 PLL and Synchronization scheme

As previously stated, in order to duty cycle the system a local time base is needed on the receiver. Moreover this time base must be synchronous with the transmitter one. Instead of using crystal oscillator to keep the time base, this design exploit a high level of integration and looks for synchronization techniques that do not require for a precise time base on the receiver. As described in section 1.5, the local time base is kept by a Phase Locked Loop that is locked on the incoming data stream, as shown in figure 2.22.

Assuming that the minimum time interval required the circuit is 100 ns, and

Figure 2.22: Receiver block diagram

the nominal pulse rate is 20 kHz, a 10.24 MHz PLL ( $512 \times 20$  kHz corresponds to a 97.65 ns period) has been designed.

This PLL (see figure 2.23 for a block diagram) is used as internal clock for the node and therefore also to drive the transmitter of the same node. This means that the jitter added by the PLL itself degrades the time accuracy of the signal that is propagated to the next nodes. Because of this, there is a maximum number on nodes through which the synchronizatin can be propagate. For a larger numbers of hop the jitter accumulated on the pulse times becomes so high that the receiver does not work anymore (see [7] for further details on the synchronization).

Figure 2.23: PLL block diagram

To increase the flexibility of the system, the PLL has been modified in order to accommodate 5 different pulse rates. These pulse rates are 20, 40, 80, 160 and 320 kbps, programmable by changing the division ratio in the frequency divider and adjusting the pole, the zero and the gain of the loop filter. For test purposes, an external clock can be injected into the chip through a proper pin. This can be used to vary the clock frequency over the VCO tuning range or to test the receiver in case of problems with the PLL. Furthermore, the PLL output can be carried out of the chip to test the PLL functionality and phase noise.

In the next paragraph the PLL building blocks are described in details.

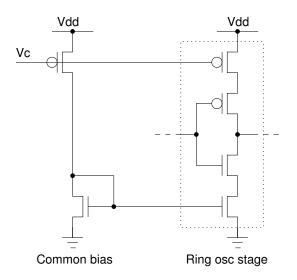

#### 2.6.1 VCO

For low frequency and low power controlled oscillators, when external tanks or MEMS are not considered and jitter (or phase noise) specification are not too stringent, ring oscillators are widely used.

The single-ended ring oscillator is realized with 9 current starved inverters (one stage plus the bias circuit is shown in figure 2.6.1). Single-ended implementation has been preferred to a differential one because of the reduced power consumption and the rail-to-rail output signal that can directly drive digital circuits.

Since the control voltage acts on the PMOS, the VCO pulling factor  $K_{VCO}$  is negative, and the PLL requires a (180°) phase inversion in the loop, that is achieved by the active loop filer.

The VCO has been designed to get the maximum  $V_{gs}$  over the current starving transistor compliant with the required oscillation frequency over the process variations and temperature, in order to achieve the minimum phase noise [10]. The current consumption of the oscillator is about 15  $\mu$ A. Actually this current relatively high and can be reduced by reducing the width of the transistors; however this would result in a higher VCO jitter. Since the jitter added by the PLL pollutes the purity of the clock signal from one node to the next, in this

Figure 2.24: Ring oscillator stage (+ common bias)

first implementation it was preferred to spend a few more microamp instead of risking a lock failure.

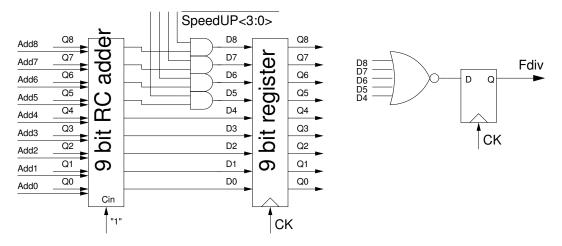

#### 2.6.2 Frequency Divider

The divider has been realized in a synchronous fashion with standard cells (as the rest of the logic blocks of the system). This is perfectly allowed by the fact that 10 MHz is an extremely low frequency for a 90 nm technology. The divider logic diagram is shown in figure 2.25.

Since the state of the PLL divider represents the state of the system for the synchronization mechanism, and the state "0" (when the frequency divider state reaches "0" the divider edge is generated and the reference edge is expected) is the state when the PLL must resynchronized by the incoming pulse, a ripple carry adder is used to force a new initial state in divider, so to change the absolute time position of the "0" state. This adder is also used to increase by one the register content during the count, thus minimizing the divider hardware. The inputs "Speed\_UP" are used to reduce the counting modulus (hence the division ratio) from 512 down to 256, 128, 64 and 32.

The divider output is resynchronize with the VCO output (CK) so to minimize the edges delay and jitter.

Figure 2.25: Frequency Divider

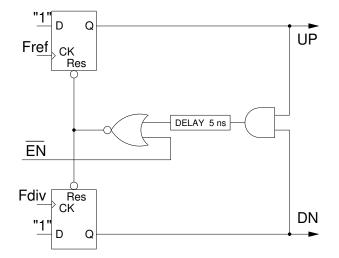

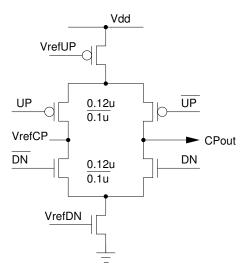

### 2.6.3 PFD-CP

The Phase and Frequency Detector (PFD) and the Charge Pump (CP) have been realize in an extremely standard way, as shown in figures 2.26 and 2.27 [11]. Because the PLL is integer, charge pump current mismatch and PFD dead zone are not so critical issues as in a fractional one [12]. Moreover the adopted loop filter reduces the sensitivity on the charge pump current mismatch [13]. The charge pump current has been chosen equal to 1  $\mu A$ .

As will be discussed in the next section, because of the low cut of frequency

Figure 2.26: Phase Frequency Detector

Figure 2.27: Charge Pump

of the loop filter, a lower charge pump current would be preferred to keep reasonable values of the filter capacitors and resistor. Anyway, control a current lower than 1  $\mu$ A can result in high errors because leakage currents cannot be neglected when the charge pump is off. A technique to scale the charge pump injected charge by means of switched capacitors will be discussed in the next section.

The charge pump reference voltage has been integrated by means of a voltage divider. Its bias current is 2.5  $\mu$ A.

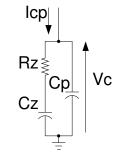

#### 2.6.4 Programmable loop filter

It is well known [14] that the open loop unity frequency of a PLL must be in the order of 1/20 of the reference frequency to get a stable loop.

Assuming a standard lead-lag network for the PLL filter (figure 2.28) the transfer function can be written as

$$F_L(s) = \frac{V_c}{I_{cp}} = \frac{1 + s\tau_z}{s(C_p + C_p)(1 + s\tau_p)}$$

with

$$\tau_p = R_z \frac{C_p C_z}{C_p + C_z} = \simeq R_z C_p \qquad \tau_z = R_z C_z \tag{2.5}$$

and the unity gain frequency turns out to be

$$\omega_c = \frac{I_{CP} R_z K_{VCO}}{N}$$

being  $I_{CP}$  the charge pump current,  $K_{VCO}$  the VCO pulling factor and N the division ratio.

With a reference frequency of 20 kHz, the required PLL bandwidth should be

Figure 2.28: PLL passive loop filter

in the order of 1 Hz, that results in a very high capacitance and resistance values for the filter components.

For a 60° phase margin, fixing the capacitance  $C_z$  to be 197 pF (about 0.1 mm<sup>2</sup>), the components for a passive filter should be

$$C_z = 197 \ pF \quad C_p = 8.25 \ pF \quad R_z = 3.21 \ M\Omega \quad I_{CP} = 62.5 \ nA$$

It must be noted that both a 3.21 M $\Omega$  and a 62.5 nA current cannot be easily achieved. For this reasons switched capacitors have been strongly used in the filter design. With respect to PLLs made for wireless communication RF synthesize, in this particular application the output phase noise is less critical and the filter design can be relaxed.

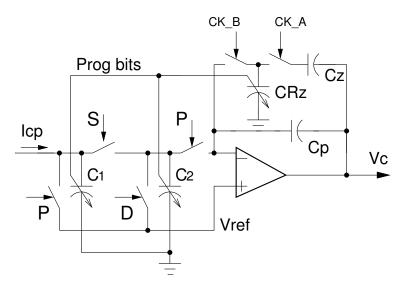

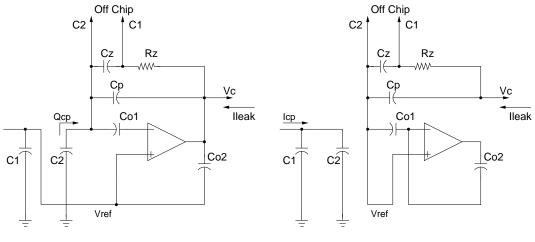

The implemented PLL loop filter is shown in figure 2.29.

The switches driven by the non overlapping phases S (Share) and P (Pass), together with the capacitors  $C_1$  and  $C_2$  perform a charge scaling between the charge injected by the charge pump and the charge injected into the active loop filter. During the charge pump comparison S = 1, P = 0 and the charge is injected into  $C_1$  and  $C_2$ . At the end of the comparison phase, the control logic deactivates S and activates P (S = 0, P = 1) and only the charge in  $C_2$  is integrated by the loop filter, while  $C_1$  is shorted.

The "effective" charge pump current is therefore given by

$$I_{CP,eff} = I_{CP} \frac{C_2}{C_1 + C_2}$$

(2.6)

With a charge pump current  $I_{CP} = 1\mu A$  it easy to obtain a 62.5  $\mu A$  effective current by choosing  $C_2 = 15C_1$ .

Figure 2.29: PLL Programmable loop filter

The switch D is used to dump the charge injected in  $C_1$  if a "false comparison" is detected. In order to achieve the synchronization, the reference frequency of the PLL is given by the incoming pulses; a misdetection would be erroneously interpreted as a PLL unlock state, resulting in a "wrong" charge injected in the filter. For this reason a logic network detects that both the pulses of  $F_{ref}$  and  $F_{div}$  has been accounted by the PFD (see figure 2.26) during the on window of the receiver. If it does not happen, the comparison is assumed as "wrong" and the charge injected by the pump dumped by D; the total charge in the filter ( $C_p$  and  $C_z$ ) does not change and the VCO frequency remains constant. The resistor  $R_z$  is realized by means of switched capacitors. The switching frequency is derived from the frequency divider as the VCO frequency divided by 16 (640 kHz). The corresponding capacitance is therefore 482 fF.

#### 2.6.5 Programmability of the loop filter

As stated in section 2.6, the pulse rate can be changed between 5 different values (20, 40, 80, 160 and 320 kpps). Since the received pulse is also used to lock the PLL, the division ratio of the PLL must be changed through the values 512, 256, 128, 64, 32. Apart from this, the bandwidth of the PLL can be increase to reduce the settling time and keep a constant  $F_{ref}/\omega_c$  ratio. In order to do not change the capacitance  $C_p$  and  $C_z$ , both  $R_z$  and  $I_{CP,eff}$  must be changed.  $R_z$  must be adjusted to move the pole and the zero according to equations 2.5, while  $I_{CP,eff}$  to keep the unity gain frequency between the zero

and the pole and ensure the proper phase margin.

Considering that the output frequency is constant, while the unity gain frequency is scaled as  $F_{ref}/20$ , it is

$$\omega_c = \frac{2\pi F_{ref}}{20} \simeq \frac{I_{CP,eff} R_z K_{VCO}}{N} = \frac{F_{ref} I_{CP,eff} R_z K_{VCO}}{F_{VCO}} \quad \Rightarrow$$

$$I_{CP,eff} \simeq \frac{F_{VCO}}{20 K_{VCO} R_z}$$

While  $R_z$  must be decreased for increasing pulse rate, the effective charge pump current must be increased of the same factor.

The reduction of  $R_z$  can be achieved increasing the switching frequency of the switch capacitor. However, the two non overlapping phase  $CK_A$  and  $CK_B$  for the switching capacitor are obtained with a finite state machine driven by the VCO and its output frequency cannot be easily increased. For this reason the capacitance  $C_{Rz}$  has been increased instead.

The tuning on the charge pump effective current is easily obtained by changing the ratio between  $C_1$  and  $C_2$ , according to equation 2.6.

#### 2.6.6 Operational amplifier design

It is easy to understand that both the finite voltage gain and the operational amplifier (OPAMP) offset will results in a phase difference between the two inputs of the PFD when the PLL is locked, hence in a phase difference between the divider output and the incoming pulse. Because the duty cycling of the receiver is based on the clock, hence the VCO output, any systematic misalignment between the divider output (hence the clock itself) and the incoming pulses must be avoided; it if happens, the amplifier on-window will be not aligned with the pulses causing the failure in both synchronization and reception.

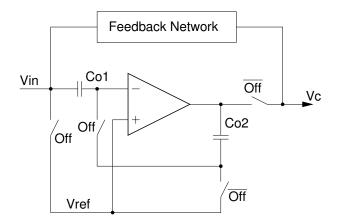

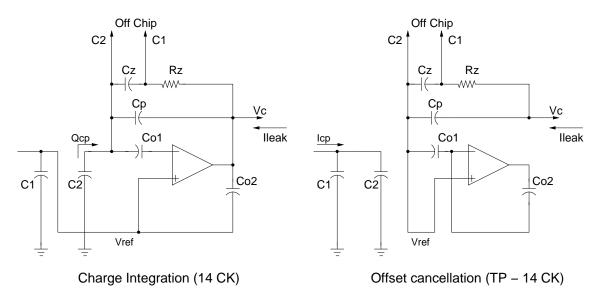

To avoid that, an offset and finite gain compensation technique has been adopted for the OPAMP, as shown in figure 2.30 [15].

Usually the offset compensation is performed by closing the OPAMP in a unity gain feedback loop and storing the offset voltage on the capacitance  $C_{o1}$ in series with the "-" input. However, this poor and simple technique results in a residual input voltage given by the OPAMP initial differential voltage (the offset plus the finite differential input) divided by the loop gain. A more accurate offset cancellation can be done by means of the capacitor  $C_{o2}$  connected to the output. In this case, during the offset cancellation phase, the

Figure 2.30: OPAMP offset compensation

OPAMP output voltage is kept at the same voltage, and the residual differential voltage is given by the original one divided by the square of the gain [15].

In this scheme, however, during the offset cancellation the OPAMP cannot drive the output voltage. During the offset cancellation the output voltage is kept by the feedback network (CRC network) between the input  $V_{in}$  (that is connected to  $V_{ref}$ ) and  $V_c$ . To allow that, the OPAMP has been designed to be fast enough to integrate the charge pump charge in only 14 VCO periods (1.37  $\mu$ s). After that period the charge of  $C_2$  has been completely transfered to the feedback network (Off=0); then there are at least (32 - 14) VCO periods (in the worst case) while the filter output depends only on the charge sharing between  $C_p$  and  $C_z$  through  $C_{R_z}$  (Off=1). Note that since the OPAMP is connected to the output only for a fraction of the reference period, his noise contribution is scaled down, sensibly reducing the PLL output jitter.

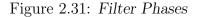

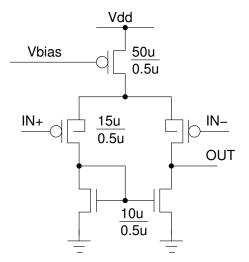

These two phases are shown in figure 2.31; on the left the charge is injected in the filter, on the right the offset is canceled.