# Technologies for enhancing multi-gate Si MOSFET performance

Kyoungsub Shin

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2006-192 http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-192.html

December 21, 2006

Copyright © 2006, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Technologies for enhancing multi-gate Si MOSFET performance

by

## Kyoungsub Shin

B.S. (Seoul National University, Korea) 1992 M.S. (Seoul National University, Korea) 1994

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Chenming Hu Professor Eugene E. Haller

Fall 2006

| The dissertation of Ky | oungsub Shin is approved: |

|------------------------|---------------------------|

| Chair                  | Date                      |

|                        | Date                      |

|                        | Date                      |

University of California, Berkeley

Fall 2006

Technologies for enhancing multi-gate Si MOSFET performance

Copyright 2006

by

Kyoungsub Shin

#### **ABSTRACT**

#### Technologies for enhancing multi-gate Si MOSFET performance

by

#### Kyoungsub Shin

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

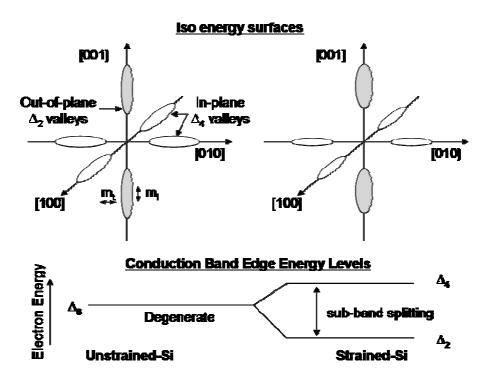

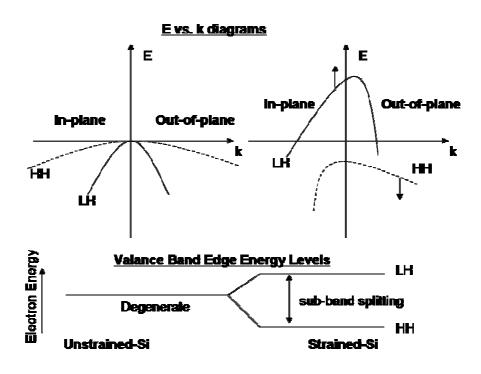

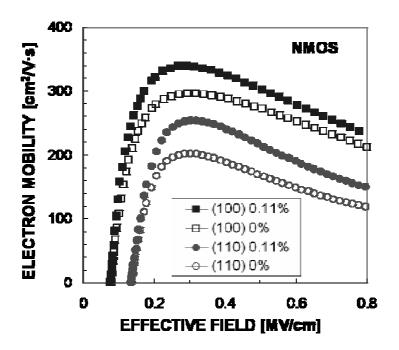

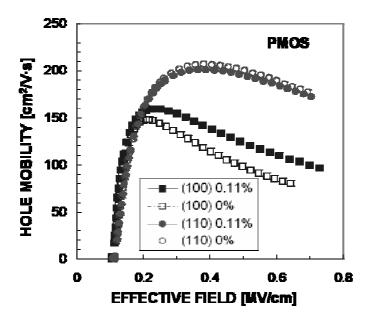

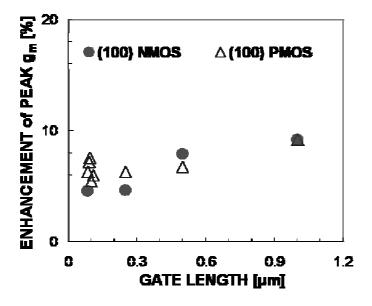

Suppression of short-channel effects (SCE) and reduction in device-to-device variability will be key challenges for transistor scaling in sub-45nm CMOS technologies. Multi-gate transistor structures such as the FinFET may eventually be needed to meet performance requirements in the sub-20nm gate length regime because SCE can be effectively suppressed without the need for high channel doping concentrations, resulting in enhanced carrier mobilities. However, these advanced device structures will likely require a metal gate technology that offers tunable work function to allow for threshold voltage ( $V_T$ ) adjustment for proper CMOS circuit operation. Strained-Si has also been considered as a key technology for enhancing carrier mobilities via modification of the electronic band structure of the channel material. Optimization of the channel surface crystalline orientation can further increase on-state drive current ( $I_{on}$ ), *e.g.*, electron mobility is highest for a (100) Si channel surface while hole mobility is highest for a (110) Si channel surface.

In this dissertation, various technologies for optimizing the performance of multi-

gate Si MOSFETs are presented. Firstly, both symmetrical and asymmetrical double-gate

MOSFET designs are considered and shown to be reasonably tolerant of process-induced

variations. From device simulation results, it is found that both the SDG and ADG

designs are reasonably tolerant of process-induced variations.

Secondly, a molybdenum gate technology with tunable effective work function for

threshold-voltage adjustment is presented. With high-temperature forming-gas annealing

(HTFGA), the work functions of Mo gate electrodes are successfully tuned in the range

4.6eV to 5.1eV. It is also found that the tuned work function of Mo by HTFGA is not

retained during the subsequent source/drain activation annealing step unless a TiN

capping layer is used to prevent nitrogen out-diffusion.

Finally, strain-induced mobility enhancement for multiple-gate (MuG) Si

MOSFETs with optimized channel surface crystalline orientations for CMOS application

((100) NMOS and (110) PMOS, respectively) via a strained SOI substrate, strained SiN<sub>x</sub>

capping layer, tensile metal gate, and/or biaxial tensile wafer bending is discussed. The

impact of strain on device performance is shown to be well modeled using the classic

bulk-Si piezoresistance (PR) coefficients.

Professor Tsu-Jae King Liu

Committee Chair

2

To my family and to the memory of my father

## **Table of Contents**

| Chapter 1 : Introduction                                    |    |

|-------------------------------------------------------------|----|

| 1.1 CMOS technology scaling                                 | 1  |

| 1.2 Advanced MOSFET structures                              |    |

| 1.3 Materials and process requirements for nanoscale CMOS   | 4  |

| 1.4 Organization                                            | 6  |

| 1.5 References                                              | 7  |

| Chapter 2 : Double-Gate MOSFET Design for Manufacturability | 15 |

| 2.1 Introduction                                            |    |

| 2.2 Symmetric vs. Asymmetric Structures                     |    |

| 2.3 Performance sensitivity to process variations           | 23 |

| 2.4 Conclusion                                              |    |

| 2.5 References                                              |    |

| Chapter 3 : Mo Gate Technology                              | 35 |

| 3.1 Introduction                                            |    |

| 3.2 $\Phi_M$ reduction by N implantation                    |    |

| 3.3 $\Phi_{M}$ reduction by FGA                             | 41 |

| 3.4 Theory for $\Phi_M$ reduction                           | 47 |

| 3.5 Conclusion                                              | 55 |

| 3.6 References                                              | 56 |

| Chapter 4 : Strained-Si Technologies                        | 59 |

| 4.1 Introduction                                            | 59 |

| 4.2 Physics of strained Si                                  | 61 |

| 4.3 Piezoresistance Model                                   | 67 |

| 4.4 Conclusion                                              | 72 |

| 4.5 References                                              |    |

| Chapter 5 : Strain Effects on MuGFET Performance            | 78 |

| 5.1 Introduction                                            | 78 |

| 5.2 Substrate-induced strain: Impact of sSOI substrate on MuGFET perfe               | ormance 80 |

|--------------------------------------------------------------------------------------|------------|

| 5.3 Process-induced strain                                                           | 87         |

| 5.4 Bending-induced strain: Biaxial convex bending-induced strain effect performance |            |

| 5.5 Conclusion                                                                       | 111        |

| 5.6 References                                                                       | 112        |

| Chapter 6 : Conclusion                                                               | 119        |

| 6. 1 Summary                                                                         | 119        |

| 6.2 Contributions                                                                    | 122        |

| 6.3 Suggestions for future work                                                      |            |

| 6.4 References                                                                       | 125        |

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to express my deepest gratitude to my research advisor, Professor Tsu-Jae King Liu, for her advising and mentoring through all the years of my graduate studies. Without her guidance, I would have never made this work possible. She has been really supportive of my work not only with her remarkable knowledge and keen insight in the field of semiconductor devices, but also with her kind consideration and encouragement.

I would like to thank Professor Chenming Hu, for his invariant consideration and advice, for chairing my qualifying examination committee, and for serving on my dissertation committee as well. I am very grateful to Professor Eugene E. Haller for serving on my dissertation committee, and especially for his great cooperation in reviewing to file this dissertation timely. I would also like to express my appreciation for the efforts of Professor Nathan Cheung and Eicke R. Weber, who served on my qualifying examination committee.

I must thank Dr. Waize Xiong in ADTF for providing MuGFET wafers for mechanical bending-induced strain experiment and sharing his experimental data. I would also like to thank Hideki Takeuchi for preparing the mechanical bending apparatus. His vast knowledge and technical expertise was a most valuable asset in our lab. I am also grateful Dr. Michael Ameen and Dr. Aditya Agarwal for helping me with a very low energy nitrogen implantation. I would like to thank Dr. Xiaoyu Xu, a former graduate student in Professor Weber's group, for her high resolution TEM analyses. I am indebted to Dr. Erik Anderson, Dr. Alex Liddle, Bruce Harteneck, and Deirdre Olynick for helping me with e-beam lithography in the Nanofabrication Lab at the Lawrence Berkeley

National Lab. I also would like to thank Katalin Voros, Sia Parsa, Xiaofan Meng, Joe Donnelly and all the other staff members of the Microfabrication Lab for their help and support.

I am very thankful to Linda Manly for her warmhearted support as a grants administrator. I am also grateful to Ruth Gjerde for her invariant kindness and timely information regarding department policy. I am also thankful to Samsung Electronics, for giving me an opportunity to study abroad for a Ph. D degree program with full financial support.

I am thankful to many former and current members of the device group in 373 Cory Hall. I would like to thank Yang-Kyu Choi for his kind help and indispensable guidance on my research. I would also like to thank other seniors who were in the group, Jeong-Soo Lee, Leland Chang, Charles Cuo, Pushkar Ranade, Kevin Yang, Yu (Kevin) Cao, Igor Polishchuk, Yee-Chia Yeo, Qiang Lu, Min She, Patrick Xuan, Jin He, Jane Xi and others who left really great achievements and motivations for new students. I am especially grateful to Daewon Ha, who kindly helped me to be settled in Berkeley. I would also like to thank visiting scholars from industry and academy for their sharing invaluable experience. I am thankful to Kojo Watanabe, Koji Watanabe, Ren-ichi Yamada, Atsushi Yagishita, Takuro Matsutoya, Yuri Yasuda, Akira Hokazono, Yongchul Oh, Jinwoo Kim, Koichi Fukuda, Nathan Emley, and Wooyoung Choi.

I would like to acknowledge Hiu Yung Wong, Vidya Varadarajan, Sriram Balasubramanian, Mohan Dunga, Marie-Ange Naida Eyoum for their sharing and close friendship since we had joined the Device Group at the almost same time. I am also thankful to my fellow graduate students, Donovan Lee, Joanna Lai, Chung-Hsun Lin,

Blake Lin, Hui Wan, Gang Liu, Kinyip Phoa, Alvaro Padilla, Andrew Carlson, Hei (Anderson) Kam, Daniel Good, Yu-Chih Tseng, Pankaj Calra, Anupama Bowonder, Xin Sun, Rhesa Nathanael, Reinaldo Vega, Cheuk Chi Lo, David Carlton and all the other group members for their friendship and fruitful discussion.

I would also like to thank all of my family members. First of all, I am really thankful to my mother for her unconditional love and sacrifice. I am also grateful to my father-in-law and mother-in-law for their restless prayer and sincere encouragement. I would like to thank my sister, brother, and their family for their love and support. I am also thankful to my brother-in-law and his family for their trust and encouragement.

Finally, I would like to thank my wife, Jiyoun, for her true love and great support throughout our marriage. I am also thankful to my lovely two daughters, Yeeun (Grace) and Yejin (Clara). I have been always feeling so happy to be with you.

Thank God for your blessing!

## **Chapter 1: Introduction**

### 1.1 CMOS technology scaling

Since the innovative concept of an integrated circuit (IC) was invented by J. Kilby in 1958, the number of circuit components on a microchip has increased exponentially and the performance of a unit transistor has improved, resulting in incredible reductions in cost-per-function with enhanced performance. This has been enabled by the successful scaling, *i.e.*, miniaturization of geometrical parameters, of planar bulk-Si CMOS devices. Over the past four decades, the semiconductor industry has followed the trend first noted by G. Moore, *i.e.*, that the complexity of ICs approximately doubles every two years [1]. C. G. Hwang even suggested a new growth model for the memory industry: "a two fold increase per year in memory density [2]."

However, as the gate length ( $L_g$ ) of a metal-oxide-semiconductor field-effect transistor (MOSFET) decreases, capacitive control of the channel potential by the gate becomes more difficult. This is because the drain potential can significantly influence the channel potential, resulting in severe short channel effects (SCE), such as increased off-state leakage current ( $I_{off}$ ), threshold voltage ( $V_t$ ) roll-off, *i.e.*, smaller  $V_t$  at shorter  $L_g$ , and drain-induced barrier lowering (DIBL), *i.e.*, smaller  $V_t$  at higher drain voltage ( $V_d$ ) due to modulation of the source-channel potential barrier by the drain voltage. Above all, increased  $I_{off}$  is a severe concern that may limit CMOS scaling because of significant passive power consumption [3].

In order to suppress the SCE in bulk MOSFETs, other parameters have been scaled down together with L<sub>g</sub>, such as the gate oxide thickness (T<sub>ox</sub>), the channel depletion width (X<sub>d</sub>), and the source/drain junction depth (X<sub>j</sub>). However, the thickness of SiO<sub>2</sub>-based gate dielectrics is approaching physical limits (<2nm), for which quantum mechanical tunneling induces severe gate leakage current through the gate dielectric [4]. Alternative gate dielectric materials with higher permittivity ("high-k gate dielectrics") can be used to further reduce the equivalent oxide thickness (EOT) with a physically thick dielectric to suppress gate leakage current. However, there are still many process integration challenges to be solved, including optimization of the interfacial layer to minimize carrier mobility degradation [5].

To scale down the depletion width, increased channel doping concentration is necessary. This reduces the off-state leakage current not only by increasing the channel potential relative to the source, which makes  $V_t$  high, but also by eliminating leakage current paths far from the gate dielectric interface. However, the high channel doping concentration degrades carrier mobility due to increased vertical electric field and more impurity scattering. It also increases band-to-band tunneling across the reverse-biased drain junction and gate-induced drain leakage (GIDL). In addition, statistical fluctuation of channel dopants causes more  $V_t$  variations, especially in the nanoscale regime [6].

Shallow source/drain junctions reduce the lateral junction capacitance, and thereby decrease the capacitive coupling of the source/drain to the channel. However, the formation of ultra-shallow junction depth is limited by process difficulties for low-energy ion implantation together with low thermal budget dopant activation to minimize dopant diffusion. The source/drain junction depth reduction can also increase parasitic series

resistance, resulting in degraded on-state drive current. Thus, raised source/drain technology is necessary to minimize parasitic series resistance.

Most of the scaling challenges faced by bulk-Si MOSFETs can be circumvented through the adoption of advanced MOSFET structures [7] such as ultra-thin-body (UTB) and double-gate (DG) silicon-on-insulator (SOI) MOSFETs described in the next section.

#### 1.2 Advanced MOSFET structures

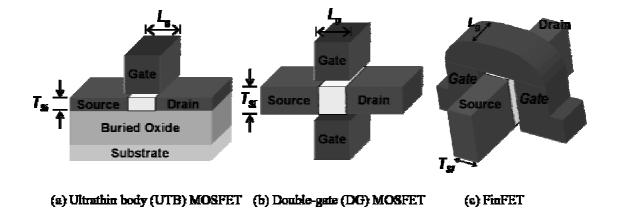

The off-state leakage current ( $I_{\rm off}$ ) increases as gate length ( $L_g$ ) decreases because capacitive control of the channel potential by the gate becomes more difficult. Actually, the dominant leakage path is located far from the gate, which is least effectively controlled by the gate [8]. Therefore, advanced SOI MOSFETs with thin body thickness ( $T_{\rm Si}$ ) can suppress the leakage current by eliminating the part of the channel that is not effectively modulated by the gate (Fig. 1.1). However, an ultra-thin body (thinner than 50% of  $L_g$ ) is necessary to effectively suppress the leakage current, which makes this approach technically challenging. The body thickness requirement for the double-gate (DG) MOSFET can be relaxed (to be 50% to 70% of  $L_g$ ) due to enhanced channel control by the two gates.

In addition, the DG device does not require high channel doping to scale  $X_d$  because it is defined by the body thickness. As a result, mobility degradation and statistical dopant fluctuation problems can be eliminated. Similarly,  $X_j$  is also defined by the body thickness, thus the shallow junction can be realized relatively easily without developing complicated doping techniques. Therefore, the DG MOSFET is a promising structure for scaling CMOS into the sub-15nm  $L_g$  [9, 10].

Figure 1.1: Advanced SOI MOSFET structures with a thin body thickness (T<sub>Si</sub>).

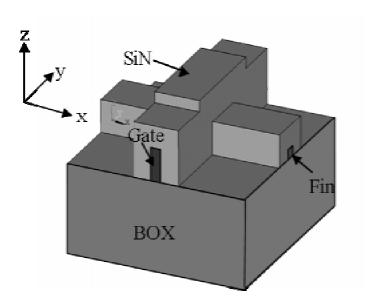

However, the manufacturability of DG MOSFETs is still challenging. Many different methods have been proposed to fabricate DG devices but most of them suffer from technical challenges mainly due to the process complexity [11-21]. A FinFET is known to be the most manufacturable DG structure due to self-aligned gate electrodes compatible with conventional planar bulk CMOS process [14, 21]. In particular, a third gate can be easily implemented by utilizing the top surface of fin as a channel, which enables further relaxation of  $T_{\rm Si}$  constraints [22].

## 1.3 Materials and process requirements for nanoscale CMOS

Advanced MOSFET structures such as the ultra-thin-body (UTB) MOSFET and the double-gate (DG) MOSFET are expected to be eventually adopted in CMOS technology nodes toward the end of the roadmap [10] due to improved control of short channel effects [23]. However, threshold voltage ( $V_T$ ) adjustment for CMOS application will be difficult because the channel/body should be lightly doped ( $< 10^{17} \text{ cm}^{-3}$ ) or

undoped in order to achieve high carrier mobilities and to minimize threshold-voltage  $(V_T)$  variations induced by channel dopant fluctuations.

In this case, a metal gate technology that offers tunable work function ( $\Phi_M$ ) for  $V_T$  adjustment is very desirable. In addition, metal gate enables further MOSFET scaling because it eliminates the issues of poly-Si gate technology, namely the gate depletion effect and boron penetration. The ranges of  $\Phi_M$  required to fully adjust the  $V_T$  values of thin-body (fully depleted) MOSFETs for various applications is 4.4eV to 4.6eV for n-channel devices and 4.8eV to 5.0eV for p-channel devices [24]. Recently, A. Carlson *et al.* reported that a single metal gate technology with ~4.6eV work function should be advantageous for achieving large read and write margins in six-transistor (6-T) FinFET SRAM cells [25]. V. Varadarajan *et al.* showed that a single gate technology with near-midgap work function (~4.7eV) can be suitable for low-power DG CMOS technology, if fine-tuning of  $V_T$  is achieved by engineering the electrical channel length ( $L_{eff}$ ) [26]. Thus, the ability to tune  $\Phi_M$  near mid-gap should be useful for various applications.

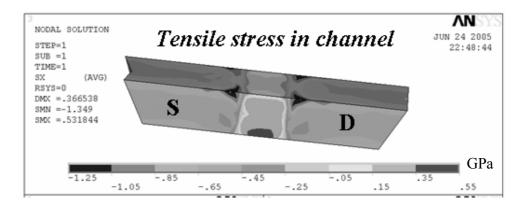

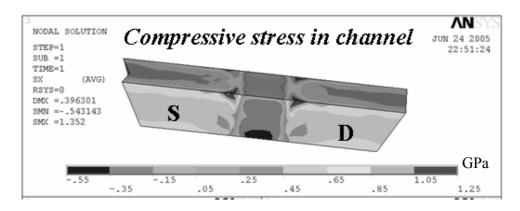

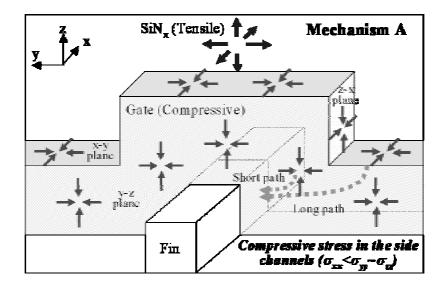

To overcome the current geometrical scaling limit, the industry needs a new scaling vector. Strained Si technologies have been widely studied as a new promising scaling vector (mobility scaling) to improve on-state drive current without degrading off-state leakage current [27-37]. Mobilities of both electrons and holes can be improved by applying stress to induce appropriate strain in the channel, *e.g.*, tensile strain for n-channel MOSFETs and compressive strain for p-channel MOSFETs [33, 34]. To induce appropriate strain in the channel region of MOSFETs, various techniques have been introduced such as substrate-induced strain, process-induced strain, and bending-induced strain.

Optimization of channel surface crystalline orientations for maximum carrier mobilities can also provide for a significant improvement in CMOS performance [38]. Therefore, the ultimate CMOS technology will utilize each of these approaches (advanced MOSFET structures, metal gate with tunable  $\Phi_M$ , strained Si, and channel orientation optimization) for performance enhancement.

#### 1.4 Organization

In this dissertation, various technologies for optimizing the performance of multigate Si MOSFETs are investigated for the future nanoscale CMOS technologies. Key issues of double-gate MOSFET design for manufacturability are explored through device simulation and a new work function tuning method for Mo gate technology is demonstrated experimentally. Effects of strain on MuGFET performance are examined and modeled with classic bulk-Si piezoresistance (PR) coefficients [39].

Chapter 2 presents the effects of process induced parameter variations on the performance of DG MOSFETs. The differences in operation schemes of symmetric and asymmetric DG MOSFETs are briefly described by using energy band diagrams. The device performance sensitivity to process induced parameter variations such as body thickness  $(T_{Si})$ , gate length  $(L_g)$ , gate oxide thickness  $(T_{ox})$ , and gate misalignment (MA) is also investigated for n-channel symmetric and asymmetric MOSFETs, via device simulation (ISE DESSIS).

In Chapter 3, Mo gate work function reduction by N<sup>+</sup> implantation is reviewed and issues for this approach are addressed. As an alternative approach to reduce Mo gate work function, the impact of HTFGA on Mo gate work function is investigated and

CMOS process integration issues are discussed. Finally, a theory for Mo gate work function reduction is presented.

The physics of strained Si is reviewed in Chapter 4 using electronic band structures and the simple piezoresistance model is also introduced to quantify mobility enhancement induced by strain.

In Chapter 5, the effects of strain on the performance of n-channel and p-channel MuGFETs with {110}/<110> and {100}/<100> surface-orientation/current-direction are investigated. Three typical types of strain (substrate-induced, process-induced, and bending-induced strains) for enhancing MuGFET performance are introduced. First, impact of strained SOI (sSOI) substrate on MuGFET performance is experimentally studied. For process-induced strain approaches, the impacts of a strained capping layer and tensile metal gate are then discussed. Finally, the impact of biaxial convex bending on MuGFET performance is presented. Mechanisms affecting carrier mobility in thin-body (fully depleted) MOSFET structures are also elucidated by using the PR model introduced in Chapter 4.

An overall summary of this dissertation is presented in Chapter 6. Key research contributions and suggestions for future research directions are highlighted.

#### 1.5 References

[1] G. E. Moore, "Progress in digital integrated electronics," *International Electron Devices Meeting*, pp. 11-13, 1975.

- [2] C.-g. Hwang, "Nanotechnology enables a new memory growth model," *Proceedings of the IEEE*, vol. 91, pp. 1765-1771, 2003.

- [3] W. Haensch, E. J. Nowak, R. H. Dennard, P. M. Solomon, and et al., "Silicon CMOS devices beyond scaling," *IBM Journal of Research and Development*, vol. 50, p. 339, 2006.

- [4] Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S.-H. Lo, G. A. Sai-Halasz, R. G. Viswanathan, H. J. C. Wann, S. J. Wind, and H.-S. Wong, "CMOS scaling into the nanometer regime," *Proceedings of the IEEE*, vol. 85, pp. 486-504, 1997.

- [5] D.-L. Kwong, "CMOS integration issues with high-k gate stack," in *Proceedings* of the 11th International Symposium on the Physical and Failure Analysis of Integrated Circuits, pp. 17-20, 2004.

- [6] T. Tanaka, T. Usuki, T. Futatsugi, Y. Momiyama, and T. Sugii, "Vth fluctuation induced by statistical variation of pocket dopant profile," *IEEE International Electron Devices Meeting*, pp. 271-274, 2000.

- [7] C. Leland, C. Yang-Kyu, J. Kedzierski, N. Lindert, X. Peiqi, J. Bokor, H. Chenming, and K. Tsu-Jae, "Moore's law lives on [CMOS transistors]," *IEEE Circuits and Devices Magazine*, vol. 19, pp. 35-42, 2003.

- [8] Y. K. Choi, "Nanofabrication technologies and novel device structures for nanoscale CMOS," *Ph.D. Thesis*, University of California, Berkeley, 2001.

- [9] D. J. Frank, S. E. Laux, and M. V. Fischetti, "Monte Carlo simulation of a 30 nm dual-gate MOSFET: how short can Si go?," *IEEE International Electron Devices Meeting*, pp. 553-556, 1992.

- [10] International Technology Roadmap for Semiconductors, http://public.itrs.net.

- [11] S. Taichi, J. P. Denton, and G. W. Neudeck, "New planar self-aligned double-gate fully-depleted P-MOSFETs using epitaxial lateral overgrowth (ELO) and selectively grown source/drain (S/D)," *IEEE international SOI conference*, pp. 110-111, 2000.

- [12] P. M. Solomon, K. W. Guarini, Y. Zhang, K. Chan, E. C. Jones, G. M. Cohen, A. Krasnoperova, M. Ronay, O. Dokumaci, H. J. Hovel, J. J. Bucchignano, C. Cabral, Jr., C. Lavoie, V. Ku, D. C. Boyd, K. Petrarca, J. H. Yoon, I. V. Babich, J. Treichler, P. M. Kozlowski, J. S. Newbury, C. P. D'Emic, R. M. Sicina, J. Benedict, and H. S. P. Wong, "Two gates are better than one [double-gate MOSFET process]," *IEEE Circuits and Devices Magazine*, vol. 19, pp. 48-62, 2003.

- [13] S. Zhang, X. Lin, R. Huang, R. Han, and M. Chan, "A self-aligned, electrically separable double-gate MOS transistor technology for dynamic threshold voltage application," *IEEE Transactions on Electron Devices*, vol. 50, pp. 2297-2299, 2003.

- [14] D. Hisamoto, W.-C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.-J. King, J. Bokor, and C. Hu, "FinFET-a self-aligned double-gate MOSFET scalable to 20 nm," *IEEE Transactions on Electron Devices*, vol. 47, pp. 2320-2325, 2000.

- [15] J.-H. Lee, G. Taraschi, W. Andy, T. A. Langdo, E. A. Fitzgerald, and D. A. Antoniadis, "Super self-aligned double-gate (SSDG) MOSFETs utilizing

- oxidation rate difference and selective epitaxy," *IEEE International Electron Devices Meeting*, pp. 71-74, 1999.

- [16] H. S. P. Wong, K. K. Chan, and Y. Taur, "Self-aligned (top and bottom) double-gate MOSFET with a 25 nm thick silicon channel," *IEEE International Electron Devices Meeting*, pp. 427-430, 1997.

- [17] M. Masahara, Y. Liu, T. Sekigawa, S. Hosokawa, K. Ishii, T. Matsukawa, H. Tanoue, K. Sakamoto, H. Yamauchi, S. Kanemaru, H. Koike, and E. Suzuki, "Demonstration of threshold voltage control techniques for vertical-type 4-terminal double-gate MOSFETs (4T-DGFET)," *Proceeding of 34<sup>th</sup> European Solid-State Device Research Conference*, pp. 73-76, 2004.

- [18] L. Mathew, Y. Du, A. V. Y. Thean, M. Sadd, A. Vandooren, C. Parker, T. Stephens, R. Mora, R. Rai, M. Zavala, D. Sing, S. Kalpat, J. Hughes, R. Shimer, S. Jallepalli, G. Workman, W. Zhang, J. G. Fossum, B. E. White, B. Y. Nguyen, and J. Mogab, "CMOS Vertical Multiple Independent Gate Field Effect Transistor (MIGFET)," *IEEE international SOI conference*, pp. 187-189, 2004.

- [19] T. Schulz, W. Rosner, L. Risch, and U. Langmann, "50-nm vertical sidewall transistors with high channel doping concentrations," *IEEE International Electron Devices Meeting*, pp. 61-64, 2000.

- [20] J. M. Hergenrother, D. Monroe, F. P. Klemens, A. Komblit, G. R. Weber, W. M. Mansfield, M. R. Baker, F. H. Baumann, K. J. Bolan, J. E. Bower, N. A. Ciampa, R. A. Cirelli, J. I. Colonell, D. J. Eaglesham, J. Frackoviak, H. J. Gossmann, M. L. Green, S. J. Hillenius, C. A. King, R. N. Kleiman, W. Y. C. Lai, J. T. C. Lee, R. C. Liu, H. L. Maynard, M. D. Morris, S. H. Oh, C. S. Pai, C. S. Rafferty, J. M.

- Rosamilia, T. W. Sorsch, and H. H. Vuong, "The Vertical Replacement-Gate (VRG) MOSFET: a 50-nm vertical MOSFET with lithography-independent gate length," *IEEE International Electron Devices Meeting*, pp. 75-78, 1999.

- [21] Y.-K. Choi, L. Chang, P. Ranade, J.-S. Lee, D. Ha, S. Balasubramanian, A. Agarwal, M. Ameen, T.-J. King, and J. Bokor, "FinFET process refinements for improved mobility and gate work function engineering," *IEEE International Electron Devices Meeting*, pp. 259-262, 2002.

- [22] B. Doyle, B. Boyanov, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, R. Rios, and R. Chau, "Tri-Gate fully-depleted CMOS transistors: fabrication, design and layout," *Symposium on VLSI Technology*, pp. 133-134, 2003.

- [23] L. Chang, Y.-k. Choi, D. Ha, P. Ranade, S. Xiong, J. Bokor, C. Hu, and T. J. King, "Extremely scaled silicon nano-CMOS devices," *Proceedings of the IEEE*, vol. 91, pp. 1860-1873, 2003.

- [24] L. Chang, S. Tang, T.-J. King, J. Bokor, and C. Hu, "Gate length scaling and threshold voltage control of double-gate MOSFETs," *IEEE International Electron Devices Meeting*, pp. 719-22, 2000.

- [25] A. Carson, Z. Guo, S. Balasubramanian, L.-T. Pang, T.-J. King Liu, and B. Nikolic, "FinFET SRAM with Enhanced Read/Write Margins," *IEEE International SOI Conference*, pp. 105-106, 2006.

- [26] V. Varadarajan and T.-J. King Liu, "VT Adjustment by Leff Engineering for LSTP Single Gate Work-function CMOS FinFET Technology," *IEEE 16th Biennial University Government Industry Microelectronics Conference*, 2006.

- [27] S. E. Thompson, G. Sun, Y. S. Choi, and T. Nishida, "Uniaxial-process-induced strained-Si: extending the CMOS roadmap," *IEEE Transactions on Electron Devices*, vol. 53, pp. 1010-1020, 2006.

- [28] T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr, "A 90nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors," *IEEE International Electron Devices Meeting*, pp. 978-980, 2003.

- [29] T. Numata, T. Irisawa, T. Tezuka, J. Koga, N. Hirashita, K. Usuda, E. Toyoda, Y. Miyamura, A. Tanabe, N. Sugiyama, and S. Takagi, "Performance enhancement of partially and fully depleted strained-SOI MOSFETs," *IEEE Transactions on Electron Devices*, vol. 53, pp. 1030-1038, 2006.

- [30] K. J. Chui, K. W. Ang, H. C. Chin, C. Shen, L. Y. Wong, C. H. Tung, N. Balasubramanian, M. F. Li, G. S. Samudra, and Y. C. Yeo, "Strained-SOI n-Channel Transistor With Silicon– Carbon Source/Drain Regions for Carrier Transport Enhancement," *IEEE Electron Device Letters*, vol. 27, pp. 778-780, 2006.

- [31] J. L. Hoyt, H. M. Nayfeh, S. Eguchi, I. Aberg, G. Xia, T. Drake, E. A. Fitzgerald, and D. A. Antoniadis, "Strained silicon MOSFET technology," *IEEE International Electron Devices Meeting*, pp. 23-26, 2002.

- [32] I. Aberg, O. O. Olubuyide, C. N. Chleirigh, I. Lauer, D. A. Antoniadis, J. Li, R. Hull, and J. L. Hoyt, "Electron and hole mobility enhancements in sub-10 nm-

- thick strained silicon directly on insulator fabricated by a bond and etch-back technique," *IEEE International Electron Devices Meeting*, pp. 52-53, 2004.

- [33] S. Pidin, T. Mori, K. Inoue, S. Fukuta, N. Itoh, E. Mutoh, K. Ohkoshi, R. Nakamura, K. Kobayashi, K. Kawamura, T. Saiki, S. Fukuyama, S. Satoh, M. Kase, and K. Hashimoto, "A novel strain enhanced CMOS architecture using selectively deposited high tensile and high compressive silicon nitride films," *IEEE International Electron Devices Meeting*, pp. 213-216, 2004.

- [34] C. D. Sheraw, M. Yang, D. M. Fried, G. Costrini, T. Kanarsky, W. H. Lee, V. Chan, M. V. Fischetti, J. Holt, L. Black, M. Naeem, S. Panda, L. Economikos, J. Groschopf, A. Kapur, Y. Li, R. T. Mo, A. Bonnoit, D. Degraw, S. Luning, D. Chidambarrao, X. Wang, A. Bryant, D. Brown, C. Y. Sung, P. Agnello, M. Ieong, S. F. Huang, X. Chen, and M. Khare, "Dual stress liner enhancement in hybrid orientation technology," *IEEE International Electron Devices Meeting*, pp. 12-13, 2005.

- [35] K. Uchida, R. Zednik, C.-H. Lu, H. Jagannathan, J. McVittie, P. C. McIntyre, and Y. Nishi, "Experimental study of biaxial and uniaxial strain effects on carrier mobility in bulk and ultrathin-body SOI MOSFETs," *IEEE International Electron Devices Meeting*, pp. 229-232, 2004.

- [36] W. Zhao, J. He, R. E. Belford, L. E. Wernersson, and A. Seabaugh, "Partially depleted SOI MOSFETs under uniaxial tensile strain," *IEEE Transactions on Electron Devices*, vol. 51, pp. 317-323, 2004.

- [37] B. M. Haugerud, L. A. Bosworth, and R. E. Belford, "Mechanically induced strain enhancement of metal--oxide--semiconductor field effect transistors," *Journal of Applied Physics*, vol. 94, pp. 4102-4107, 2003.

- [38] M. Yang, M. Ieong, L. Shi, K. Chan, V. Chan, A. Chou, E. Gusev, K. Jenkins, D. Boyd, Y. Ninomiya, D. Pendleton, Y. Surpris, D. Heenan, J. Ott, K. Guarini, C. D'Emic, M. Cobb, P. Mooney, B. To, N. Rovedo, J. Benedict, R. Mo, and H. Ng, "High performance CMOS fabricated on hybrid substrate with different crystal orientations," *IEEE International Electron Devices Meeting*, pp. 453-456, 2003.

- [39] C. Smith, "Piezoresistance effect in germanium and silicon," *Physical Review*, vol. 94, pp. 42-49, 1954.

# **Chapter 2 : Double-Gate MOSFET Design for**

# **Manufacturability**

#### 2.1 Introduction

For the past four decades, the cost-per-function and the performance of integrated circuits have been dramatically improved by successful scaling of planar bulk Si CMOS devices. However, as the gate length ( $L_g$ ) decreases, the capacitive control of the channel potential by the gate becomes more difficult. Instead, the source and drain influence significantly the channel potential, resulting in severe short channel effects (SCE), such as increased off-state leakage current ( $I_{off}$ ), threshold voltage ( $V_t$ ) roll-off, *i.e.*, smaller  $V_t$  at shorter  $L_g$ , and drain-induced barrier lowering (DIBL), *i.e.*, smaller  $V_t$  at higher drain voltage ( $V_d$ ) due to modulation of source-channel potential barrier by the drain voltage.

In order to suppress the SCE in bulk devices, other parameters have been scaled down together with  $L_g$ , such as the gate oxide thickness  $(T_{ox})$ , the gate-controlled channel depletion width  $(X_d)$ , and the source/drain junction capacitance  $(X_i)$ .

A thin gate oxide increases the capacitive control of the channel by the gate. Therefore, the influence on the channel by the source/drain becomes relatively small. At the same time, more inversion charges are induced by  $T_{ox}$  scaling, resulting in higher on-state drive current ( $I_{on}$ ). However, the thickness of  $SiO_2$ -based gate dielectric is already

approaching down to almost physical limit (<2nm), where the quantum mechanical gate tunneling induces severe gate leakage current through the gate dielectric [1]. The alternative high-κ gate dielectric is known to further reduce the equivalent oxide thickness (EOT) with a large physical dielectric thickness, which suppresses gate leakage current. However, in order to apply high-κ gate dielectric especially for sub-1nm EOT devices, there are still a lot of technical challenges including engineering of the interfacial layer degrading the carrier mobility [2].

To scale the gate-controlled depletion width, increased channel doping concentration is necessary, which reduces the off-state leakage current not only by increasing the channel potential relative to the source, which makes  $V_t$  high, but also by eliminating leakage current paths far from the gate dielectric interface. In particular, the locally high channel doping concentration near the source/drain regions has been widely implemented via lateral channel engineering such as halo or pocket implants [3, 4], which also increases the average channel doping concentration especially for sub-100nm  $L_g$  devices. However, the high channel doping concentration degrades carrier mobility due to increased vertical electric field and more impurity scattering. It also increases band-to-band tunneling across the junction and gate-induced drain leakage (GIDL). In addition, statistical fluctuation of channel dopants causes more  $V_t$  variations, especially for the nanoscale regime [5].

Shallow source/drain junctions reduce the junction capacitance, thereby decreasing the capacitive coupling of the source/drain to the channel. However, the formation of ultra-shallow junction depth is limited by the process difficulties in low-energy ion implantation together with low thermal budget dopant activation to minimize

dopant diffusion. The source/drain junction depth reduction also increases parasitic series resistance, resulting in degraded on-state drive current. The raised source/drain technology is necessary to minimize the parasitic series resistance.

The double-gate (DG) MOSFET is a promising structure for scaling CMOS into the sub-15nm  $L_g$  regime because of its excellent suppression of short channel effects (SCE) for a given equivalent gate-oxide thickness [6, 7]. For example, the DG device doesn't need to have high channel doping to scale  $X_d$  because it is defined by body thickness, which is normally 50 to 70% of  $L_g$  to suppress the SCE effectively. As a result, mobility degradation and statistical dopant fluctuation problems can be eliminated. Similarly,  $X_j$  is also defined by the body thickness, thus the shallow junction can be realized relatively easily without developing complicated junction implantation techniques.

Even though DG device structures can effectively suppress SCE due to aforementioned superiorities of DG devices over the conventional planar bulk MOSFETs, their manufacturability is still challenging. Many different methods have been proposed to fabricate DG devices but most of them suffer from technical challenges mainly due to the process complexity [8-18]. For example, the vertical devices with pillar-like channel [14-17] has a large gate overlap capacitance and the required processes are very complicated. In particular, it is not easy to have different gate lengths which are controlled by deposition thicknesses and/or etch back amounts. A FinFET is also a vertical device, the most manufacturable DG structure due to process compatibility with conventional planar bulk MOSFETs [11, 18]. However, the channel surface (fin sidewall) roughness induced by photolithography and dry etching degrades carrier mobilities

without subsequent surface smoothening process [18]. Since the effective channel widths are controlled by the number of fins, the independent control for two gates is almost impossible with limited physical spacing between fins required for layout efficiency, even though the gate separation process is available [15]. Independent gate control is relatively easy for the planar DG devices but it is not trivial to align the front and back gates without complicated process integration [8-10, 12, 13]. Above all, the performance fluctuation induced by process induced parameter variations is expected to be more significant for DG devices because nominal device parameters are already restricted to be very small.

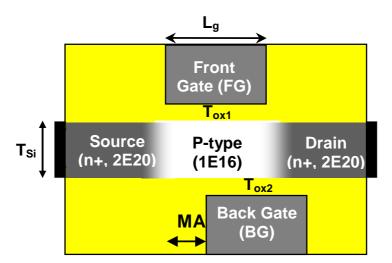

In this chapter, the effects of process induced parameter variations on the performance of DG MOSFETs are presented [19, 20]. First, the differences in operation schemes of symmetric and asymmetric DG MOSFETs are briefly described by using energy band diagrams. Secondly, the device performance sensitivity to process induced parameter variations such as body thickness ( $T_{Si}$ ), gate length ( $L_g$ ), gate oxide thickness ( $T_{ox}$ ), and gate misalignment (MA) is investigated for n-channel SDG and ADG MOSFETs with nominal gate length of 13nm and light body doping, via device simulation (ISE DESSIS).

## 2.2 Symmetric vs. Asymmetric Structures

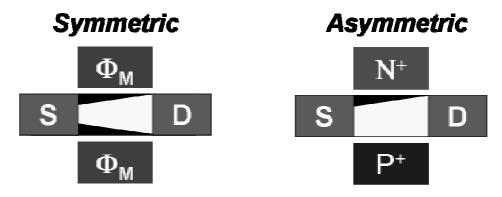

As shown in Fig. 2.1, there are two types of DG MOSFETs: 1) symmetric (SDG), in which the gates have identical work function ( $\Phi_M$ , intermediate to  $N^+$  poly-Si and  $P^+$  poly-Si work functions), and 2) asymmetric (ADG), in which the gates have different work functions ( $N^+$  poly-Si for the front gate,  $P^+$  poly-Si for the back gate, for an n-

channel device) [21]. At on-state, the two conductive channels (inversion layers) are formed for the SDG device but only one is formed for the ADG device unless the operation voltage is extremely high to form the other inversion layer near the P<sup>+</sup> gate. In addition, the SDG device shows higher carrier mobility due to its lower transverse electric field as compared to the ADG device.

Figure 2.1: Symmetric and asymmetric double gate MOSFET structures.

The threshold voltage  $(V_t)$  of a SDG MOSFET must be adjusted by tuning the effective work function  $(\Phi_M)$  of a metallic gate material, if light body doping is used to avoid dopant fluctuation effects (significant in the nanoscale regime). The range of required work functions for low power thin body CMOSFETs are 4.4-4.6 eV for PMOS and 4.8-5.0 eV for NMOS, respectively [22]. Without the metal gate technology with tunable or dual work functions, which will be introduced in chapter 3, the SDG device will not satisfy the  $V_t$  requirements. In contrast, the  $V_t$  of an ADG MOSFET can simply be adjusted by changing the body thickness  $T_{Si}$  and/or the gate-oxide thickness  $T_{ox}$ , without the need for exotic gate materials [23].

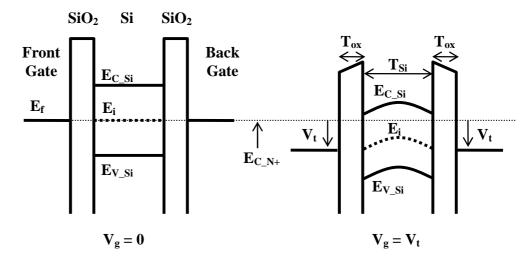

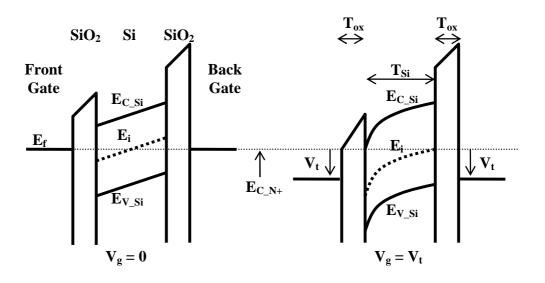

Fig. 2.2 shows the energy band diagram along the vertical direction (across the front and back gates) of the two structures shown in Fig. 2.1. It describes how conductive channels are formed for the undoped n-channel SDG and ADG MOSFETs, respectively.

(a) Symmetric DG MOSFET

(b) Asymmetric DG MOSFET

Figure 2.2: Schematic energy band diagrams for n-channel SDG and ADG MOSFETs.

$(E_f: Fermi \ level, \ E_i: intrinsic \ Fermi \ level, \ E_{C\_Si}: conduction \ band \ of \ the \ silicon \ body,$   $E_{C\_N+}: conduction \ band \ edge \ of \ the \ N^+ \ source/drain)$

For the SDG device, the silicon bands are flat for the midgap gate work function at zero gate voltage. At  $V_g=V_t$ , the conduction band edge of the silicon body ( $E_{C_s}$ ) near the surface is bent and approaches the conduction band edge of the  $N^+$  source/drain ( $E_{C_s}$ ). Since the work functions of two gates are identical, the conduction bands in both surfaces (under the front and back gates) are bent by the exactly same amount. As a result, at on-state, two conductive channels are formed for the SDG device, unless the silicon body thickness is not very thin (e.g., <5nm). In that case, as the gate voltage approaches  $V_t$ , the bands of the whole silicon body including the center follow  $V_g$ , thus volume inversion takes place [24].

For the ADG device, the silicon bands have a nearly constant slope at zero gate voltage. Since this slope defines the transverse vertical electric field, the ADG device shows higher vertical electric field than the SDG device especially when the body thickness ( $T_{Si}$ ) is small, resulting in mobility degradation. At  $V_g=V_t$ , further bend bending occurs at the silicon body surfaces, more at the left surface where the inversion charge layer is formed under  $N^+$  front gate. In this case, the conduction band edge in the silicon body only near the left surface reaches the  $N^+$  source/drain conduction band edge, resulting in one conductive channel formation at on-state. However, if  $V_g$  is larger than 1V, two conductive channels will be formed even for the ADG device [21].

## 2.3 Performance sensitivity to process variations

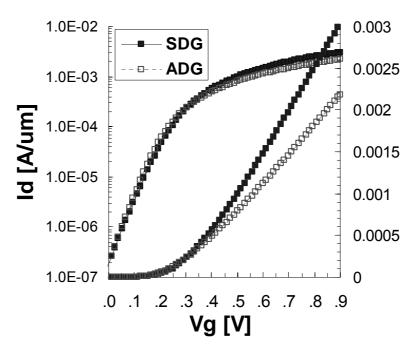

The nominal DG MOSFET design with slightly larger effective gate length, defined as the distance between the positions where the source and drain dopant concentrations fall to  $2\times10^{19} \text{cm}^{-3}$  (Fig. 2.3), was previously optimized for maximum onstate current [25]. For the SDG device, the gate work function is set to 4.414eV to achieve the same off-state leakage  $I_{\text{off}}$  as the ADG device. As can be seen from the  $I_d$ - $V_g$  characteristics in Fig. 2.4, the SDG device achieves higher  $I_{\text{on}}$ , for a supply voltage of 0.9V. This is because it has two conductive channels and higher electron mobility due to lower transverse electric field as compared to the ADG device.

Figure 2.3: DG MOSFET structure used for simulations. Nominal parameter values:  $L_g = 13$ nm,  $T_{ox1} = T_{ox2} = 1$ nm,  $T_{Si} = 5$ nm,  $V_{dd} = 0.9$ V, S/D gradient = 1.4nm/dec (optimal design for maximizing  $I_{on}$ ) [25].

Figure 2.4: Nominal  $I_d$ - $V_g$  curves ( $V_{ds}$ =0.9V) for SDG and ADG MOSFETs in both logarithmic and linear scales. The gate work function in the SDG device is 4.414eV to achieve the same  $I_{off}$  as the ADG device (n+ poly-Si front gate, p+ poly-Si back gate).

#### 2.3.1 Impact of Parameter Variations

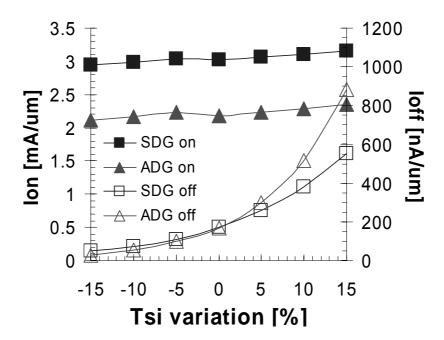

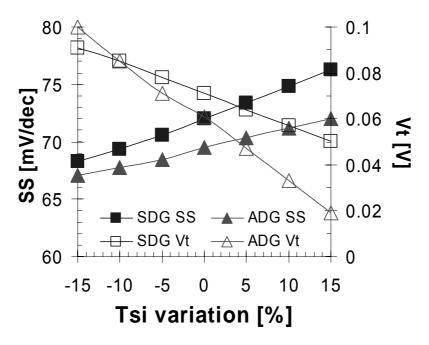

A thin body ( $T_{Si} < L_g/2$ ) is necessary to effectively suppress SCE without body doping.  $I_{off}$  increases superlinearly with increasing  $T_{Si}$  (Fig. 2.5), more strongly so for the ADG device because its  $V_t$  is a sensitive function of  $T_{Si}$  (Fig. 2.6).  $I_{on}$  increases linearly with  $T_{Si}$  for both SDG and ADG devices due to reduced parasitic series resistance. The sub-threshold swing (SS) is steeper for the ADG device and is less sensitive to  $T_{Si}$  variation due to better suppression of drain-induced barrier lowering (DIBL) [23].

Figure 2.5: Impact of body thickness variation on drain current. ( $I_{on} = I_d$  for  $V_{gs} = V_{ds} = 0.9V$ .  $I_{off} = I_d$  for  $V_{gs} = 0.9V$  and  $V_{ds} = 0.9V$ .) The ADG device shows larger  $I_{off}$  sensistivity as  $T_{Si}$  increases.

Figure 2.6: Impact of body thickness variation on SS and  $V_t$ . The ADG device shows larger  $V_t$  sensitivity, but slightly lower SS sensitivity.

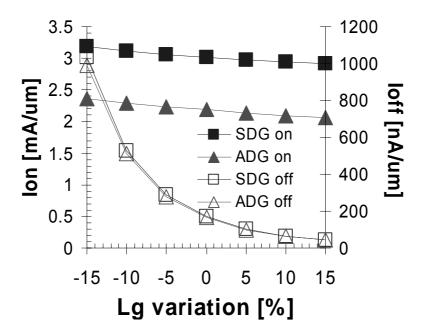

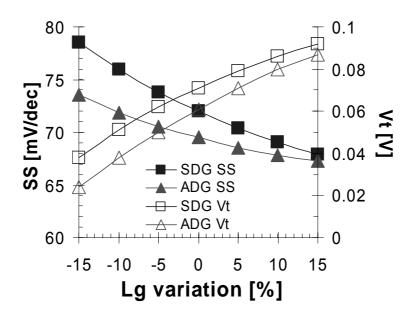

Similarly,  $I_{off}$  increases superlinearly with decreasing  $L_g$  (Fig. 2.7), but comparably so for the SDG and ADG devices.  $I_{on}$  also increases ~linearly with decreasing  $L_g$  due to increased lateral electric field. The SDG and ADG  $V_t$  roll-off characteristics are similar, as shown in Fig. 2.8. Again, the ADG device shows better SS with less sensitivity to  $L_g$  due to better DIBL suppression.

Figure 2.7: Impact of (front and back) gate length variation on drain current. Both SDG and SDG devices show large  $I_{\text{off}}$  sensitivity as  $L_g$  decreases.

Figure 2.8: Impact of (front and back) gate length variation on SS and  $V_t$ . SDG and ADG devices show similar  $V_t$  roll-off and SS degradation as  $L_g$  decreases.

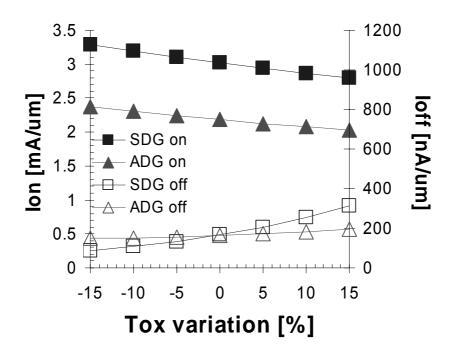

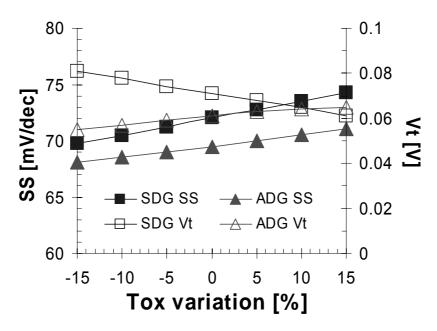

As shown in Fig. 2.9,  $I_{off}$  is less sensitive to percentage variations in  $T_{ox}$ , particularly for the ADG device, because SCE are effectively suppressed by using a thin  $T_{Si}$ .  $I_{on}$  is more sensitive to percentage variations in  $T_{ox}$  (vs.  $T_{Si}$  or  $L_g$ ) for both the SDG and ADG devices because inversion-layer charge density is proportional to the gate capacitance. SS degrades slightly as  $T_{ox}$  increases due to reduced capacitive coupling between the gate and the channel, but less so for the ADG device due to its better DIBL suppression (Fig. 2.10). The  $V_t$  of the ADG device increases with  $T_{ox}$  because the equilibrium electron potential at the front channel is higher for thicker  $T_{ox}$  (*i.e.*, the fraction of the built-in vertical potential difference between the back and front gates,  $\Phi_{(p+poly-Si)}$ – $\Phi_{(n+poly-Si)}$ , dropped across the front gate oxide increases with increasing  $T_{ox}$ ). This is offset by worsening SCE (acting to lower  $V_t$ ) with increasing  $T_{ox}$ , so that the sensitivity of  $V_t$  to  $T_{ox}$  variation is lower for the ADG vs. the SDG device.

Figure 2.9: Impact of  $T_{ox}$  variation on drain current. The SDG device shows larger  $I_{off}$  sensitivity.  $I_{on}$  increases inversely with  $T_{ox}$  as expected for both SDG and ADG devices.

Figure 2.10: Impact of  $T_{ox}$  variation on SS and  $V_t$ . SS improves as  $T_{ox}$  decreases due to better SCE control. The SDG and ADG devices show opposite trends in  $V_t$ , with the ADG device showing less  $V_t$  sensitivity to  $T_{ox}$  variation.

### 2.3.2 Impact of back gate misalignment Variations

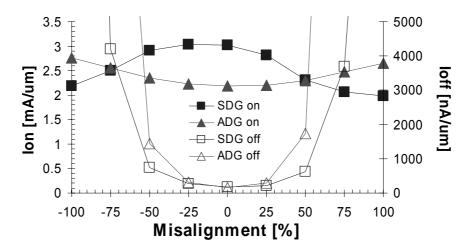

Capacitive coupling between the back-gate and channel decreases with increasing misalignment (MA) of the back gate. (MA < 0 if the misalignment is toward the source; MA > 0 if the misalignment is toward the drain.) Therefore,  $I_{off}$  increases with the magnitude of MA, particularly for MA > 50% (Fig. 2.11), and more so for the ADG device because it relies more heavily on the back gate to suppress leakage.  $I_{on}$  is more sensitive to MA for the SDG device because it results in a gate-underlapped source or drain at the back channel, which reduces the current drive there due to increased parasitic resistance; whereas it results in slightly improved  $I_{on}$  for the ADG device due to the reduced influence of the back gate on  $V_t$ , to keep it high. Reduced coupling between the back-gate and channel results in poorer control of SCE and hence degraded  $V_t$  and SS in both ADG and SDG devices (Fig. 2.12).

Figure 2.11: Impact of BG misalignment on drain current. The SDG device shows  $I_{on}$  degradation with increasing MA due to significantly increased parasitic resistance for the back channel. The ADG device shows higher  $I_{on}$  with increasing MA due to reduced  $V_t$ .  $I_{off}$  is very sensitive for |MA| > 25%, more for the ADG device than for the SDG device.

Figure 2.10: Impact of BG misalignment on SS and V<sub>t</sub>. Both SDG and ADG devices show degraded SCE with increasing misalignment, due to reduced back-gate control.

### 2.4 Conclusion

Advanced ultrathin body (UTB) DG device structures are necessary for sub-15nm  $L_g$  MOSFETs. Two DG structures (SDG and ADG) are introduced and their operation schemes are compared by using schematic energy band diagrams.

We have also investigated the effect of process induced parameter variations (as large as  $\pm 15\%$ ) in  $T_{Si}$ ,  $L_g$ ,  $T_{ox}$ , and back-gate misalignment (as large as  $\pm 100\%$ ) on the performance of n-channel SDG and ADG MOSFETs with nominal gate length = 13nm and light body doping, via device simulation (ISE DESSIS). If the limits for variations in  $I_{on}$  and  $I_{off}$  are  $\pm 5\%$  and +300nA/ $\mu$ m, respectively, the tolerable ranges of variation are:

- for  $T_{Si}$ : -15% to 5% for both SDG and ADG

- for  $L_g$ : -5% to 15% for SDG, -5% to 10% for ADG

- for  $T_{ox}$ : -5% to 5% for SDG, -5% to 10% for ADG

#### • for MA: ±25% for both SDG and ADG

Considering the capability of the modern device process technology, it is expected that both the SDG and ADG designs are reasonably tolerant of process-induced variations.

#### 2.5 References

- [1] Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S.-H. Lo, G. A. Sai-Halasz, R. G. Viswanathan, H. J. C. Wann, S. J. Wind, and H.-S. Wong, "CMOS scaling into the nanometer regime," *Proceedings of the IEEE*, vol. 85, pp. 486-504, 1997.

- [2] D.-L. Kwong, "CMOS integration issues with high-k gate stack," in *Proceedings* of the 11th International Symposium on the Physical and Failure Analysis of Integrated Circuits, pp. 17-20, 2004.

- [3] Y. Okumura, M. Shirahata, A. Hachisuka, T. Okudaira, H. Arima, and T. Matsukawa, "Source-to-drain nonuniformly doped channel (NUDC) MOSFET structures for high current drivability and threshold voltage controllability," *IEEE Transactions on Electron Devices*, vol. 39, pp. 2541-2552, 1992.

- [4] B. Yu, C. H. J. Wann, E. D. Nowak, K. Noda, and C. Hu, "Short-channel effect improved by lateral channel-engineering in deep-submicronmeter MOSFET's," *IEEE Transactions on Electron Devices*, vol. 44, pp. 627-634, 1997.

- [5] T. Tanaka, T. Usuki, T. Futatsugi, Y. Momiyama, and T. Sugii, "Vth fluctuation induced by statistical variation of pocket dopant profile," *IEEE International Electron Devices Meeting*, pp. 271-274, 2000.

- [6] D. J. Frank, S. E. Laux, and M. V. Fischetti, "Monte Carlo simulation of a 30 nm dual-gate MOSFET: how short can Si go?," *IEEE International Electron Devices Meeting*, pp. 553-556, 1992

- [7] International Technology Roadmap for Semiconductors, http://public.itrs.net.

- [8] S. Taichi, J. P. Denton, and G. W. Neudeck, "New planar self-aligned double-gate fully-depleted P-MOSFETs using epitaxial lateral overgrowth (ELO) and selectively grown source/drain (S/D)," *IEEE international SOI conference*, pp. 110-111, 2000.

- [9] P. M. Solomon, K. W. Guarini, Y. Zhang, K. Chan, E. C. Jones, G. M. Cohen, A. Krasnoperova, M. Ronay, O. Dokumaci, H. J. Hovel, J. J. Bucchignano, C. Cabral, Jr., C. Lavoie, V. Ku, D. C. Boyd, K. Petrarca, J. H. Yoon, I. V. Babich, J. Treichler, P. M. Kozlowski, J. S. Newbury, C. P. D'Emic, R. M. Sicina, J. Benedict, and H. S. P. Wong, "Two gates are better than one [double-gate MOSFET process]," *IEEE Circuits and Devices Magazine*, vol. 19, pp. 48-62, 2003.

- [10] S. Zhang, X. Lin, R. Huang, R. Han, and M. Chan, "A self-aligned, electrically separable double-gate MOS transistor technology for dynamic threshold voltage application," *IEEE Transactions on Electron Devices*, vol. 50, pp. 2297-2299, 2003.

- [11] D. Hisamoto, W.-C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.-J. King, J. Bokor, and C. Hu, "FinFET-a self-aligned double-gate MOSFET scalable to 20 nm," *IEEE Transactions on Electron Devices*, vol. 47, pp. 2320-2325, 2000.

- [12] J.-H. Lee, G. Taraschi, W. Andy, T. A. Langdo, E. A. Fitzgerald, and D. A. Antoniadis, "Super self-aligned double-gate (SSDG) MOSFETs utilizing oxidation rate difference and selective epitaxy," *IEEE International Electron Devices Meeting*, pp. 71-74, 1999.

- [13] H. S. P. Wong, K. K. Chan, and Y. Taur, "Self-aligned (top and bottom) double-gate MOSFET with a 25 nm thick silicon channel," *IEEE International Electron Devices Meeting*, pp. 427-430, 1997.

- [14] M. Masahara, Y. Liu, T. Sekigawa, S. Hosokawa, K. Ishii, T. Matsukawa, H. Tanoue, K. Sakamoto, H. Yamauchi, S. Kanemaru, H. Koike, and E. Suzuki, "Demonstration of threshold voltage control techniques for vertical-type 4-terminal double-gate MOSFETs (4T-DGFET)," *Proceeding of 34<sup>th</sup> European Solid-State Device Research Conference*, pp. 73-76, 2004.

- [15] L. Mathew, Y. Du, A. V. Y. Thean, M. Sadd, A. Vandooren, C. Parker, T. Stephens, R. Mora, R. Rai, M. Zavala, D. Sing, S. Kalpat, J. Hughes, R. Shimer, S. Jallepalli, G. Workman, W. Zhang, J. G. Fossum, B. E. White, B. Y. Nguyen, and J. Mogab, "CMOS Vertical Multiple Independent Gate Field Effect Transistor (MIGFET)," *IEEE international SOI conference*, pp. 187-189, 2004.

- [16] T. Schulz, W. Rosner, L. Risch, and U. Langmann, "50-nm vertical sidewall transistors with high channel doping concentrations," *IEEE International Electron Devices Meeting*, pp. 61-64, 2000.

- [17] J. M. Hergenrother, D. Monroe, F. P. Klemens, A. Komblit, G. R. Weber, W. M. Mansfield, M. R. Baker, F. H. Baumann, K. J. Bolan, J. E. Bower, N. A. Ciampa, R. A. Cirelli, J. I. Colonell, D. J. Eaglesham, J. Frackoviak, H. J. Gossmann, M. L.

- Green, S. J. Hillenius, C. A. King, R. N. Kleiman, W. Y. C. Lai, J. T. C. Lee, R. C. Liu, H. L. Maynard, M. D. Morris, S. H. Oh, C. S. Pai, C. S. Rafferty, J. M. Rosamilia, T. W. Sorsch, and H. H. Vuong, "The Vertical Replacement-Gate (VRG) MOSFET: a 50-nm vertical MOSFET with lithography-independent gate length," *IEEE International Electron Devices Meeting*, pp. 75-78, 1999.

- [18] Y.-K. Choi, L. Chang, P. Ranade, J.-S. Lee, D. Ha, S. Balasubramanian, A. Agarwal, M. Ameen, T.-J. King, and J. Bokor, "FinFET process refinements for improved mobility and gate work function engineering," *IEEE International Electron Devices Meeting*, pp. 259-262, 2002.

- [19] H. Y. Wong, K. Shin, and M. Chan, "The gate misalignment effects of the subthreshold characteristics of sub-100 nm DG-MOSFETs," pp. 91-94, 2002.

- [20] Q. Chen and J. D. Meindl, "A comparative study of threshold variations in symmetric and asymmetric undoped double-gate MOSFETs," *IEEE Hong Kong Electron Devices Meeting*, pp. 30-31, 2002.

- [21] K. Suzuki and T. Sugii, "Analytical models for n<sup>+</sup>-p<sup>+</sup> double-gate SOI MOSFET's," *IEEE Transactions on Electron Devices*, vol. 42, pp. 1940-1948, 1995.

- [22] L. Chang, S. Tang, T.-J. King, J. Bokor, and C. Hu, "Gate length scaling and threshold voltage control of double-gate MOSFETs," *IEEE International Electron Devices Meeting*, pp. 719-22, 2000.

- [23] T. Tanaka, K. Suzuki, H. Horie, and T. Sugii, "Ultrafast operation of V<sub>th</sub>-adjusted p<sup>+</sup>-n<sup>+</sup> double-gate SOI MOSFET's," *IEEE Electron Device Letters*, vol. 15, pp. 386-388, 1994.

- [24] Y. Taur, "Analytic solutions of charge and capacitance in symmetric and asymmetric double-gate MOSFETs," *IEEE Transactions on Electron Devices*, vol. 48, pp. 2861-2869, 2001.

- [25] S. Balasubramanian, L. Chang, B. Nikolic', and T.-J. King, "Circuit-performance implications for double-gate MOSFET scaling below 25 nm," in *Silicon Nanoelectronics Workshop*, Kyoto, Japan, 2003.

# **Chapter 3 : Mo Gate Technology**

### 3.1 Introduction

Metal gate technology can facilitate MOSFET scaling because it eliminates the issues of poly-Si gate technology, namely the gate depletion effect and boron penetration. Advanced transistor structures such as the ultra-thin-body (UTB) MOSFET and the double-gate (DG) MOSFET are more scalable than the classic bulk-Si MOSFET because of their superior control of short channel effects [1]; hence they may be adopted for CMOS technology nodes toward the end of the roadmap [2]. In order to achieve high carrier mobilities and to minimize threshold-voltage (V<sub>T</sub>) variations, the channel/body should be lightly doped (< 10<sup>17</sup> cm<sup>-3</sup>) or undoped. In this case, a metal gate technology that offers tunable work function  $(\Phi_M)$  for  $V_T$  adjustment is very desirable. The ranges of  $\Phi_M$  required to fully adjust the  $V_T$  values of thin-body (fully depleted) MOSFETs for various applications is 4.4V to 4.6V for n-channel devices and 4.8eV to 5.0eV for pchannel devices [3]. Recently, A. Carlson et al. reported that a single metal gate technology with ~4.6eV work function should be advantageous for achieving large read and write margins in six-transistor (6-T) FinFET SRAM cells [4]. V. Varadarajan et al. showed that a single gate technology with near-midgap work function (~4.7eV) can be suitable for low-power DG CMOS technology, if fine-tuning of V<sub>T</sub> is achieved by engineering the electrical channel length ( $L_{eff}$ ) [5]. Thus, the ability to tune  $\Phi_M$  near midgap should be useful for various applications.

P. Ranade *et al.* demonstrated that the work function of a molybdenum (Mo) gate electrode can be tuned over a wide range (4.5eV to 5.0eV) by nitrogen ion (N<sup>+</sup>) implantation inducing structural and/or chemical changes in the Mo near at the gate dielectric interface [6]. Damage to the gate dielectric is a potential issue for this approach, however. Furthermore, high-tilt ion implantation would be needed to dope the gate electrodes of vertical transistor structures such as the FinFET [7], which limits device packing density (to avoid shadowing effects). To avoid these issues, nitridation of Mo by high-temperature forming gas annealing (HTFGA) [8] is an attractive alternative approach.

In this chapter, Mo gate work function reduction by  $N^+$  implantation is reviewed and issues of for this approach are addressed. As an alternative approach to reduce Mo gate work function, the impact of HTFGA on Mo gate work function is investigated and CMOS process integration issues are discussed [9]. Finally, a theory for Mo gate work function reduction is presented.

# 3.2 $\Phi_{M}$ reduction by N implantation

Molybdenum (Mo) is an attractive candidate for tunable- $\Phi_M$  metal gate technology due to its strongly anisotropic work function [10], which is believed to arise from differences in interatomic spacing and atomic plane smoothness with crystal orientation [11]. In addition, it has excellent compatibility with Si CMOS processing

because of its high melting point (~2610°C), and low resistivity (~5 $\mu\Omega$ -cm). A significantly lower  $\Phi_M$  (~4.0eV) of Mo was observed for Mo gate electrodes with structural damage induced by Ar ion implantation, indicating that amorphous Mo has a very low work function [6]. However, upon thermal annealing the Mo recrystallizes, increasing  $\Phi_M$  to ~5.0eV.

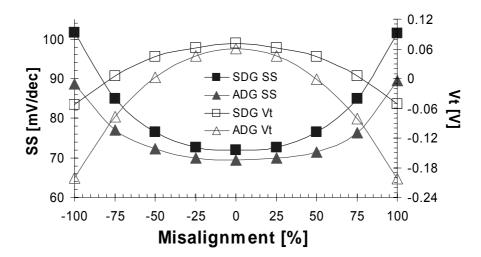

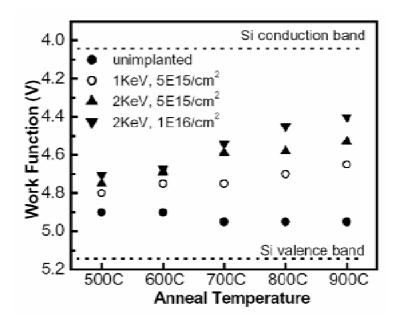

On the other hand,  $\Phi_M$  reduction by  $N^+$  implantation becomes more significant as thermal annealing temperature increases, as shown in Fig. 3.1 [6], suggesting that the  $\Phi_M$  reduction is induced by chemical modification of the Mo film (*i.e.*, nitridation). The  $\Phi_M$  increase of un-implanted Mo with increasing annealing temperature can be explained by the recrystallization and/or grain growth effect.

Figure 3.1: Variation of Mo (15nm) work function with thermal annealing. All anneals were 15 min long except for the 900°C anneal (15s) [6].

Fig. 3.1 also shows that higher N<sup>+</sup> implantation energy and dose are necessary for larger reduction of Mo work function. The implantation energy and dose determine the distribution profile of implanted ions into Mo. As long as the dose is higher than 10<sup>12</sup>cm<sup>-2</sup>, the distribution can be described statistically and is often modeled to first order by a symmetric Gaussian distribution given by [12]

$$C(x) = C_p \exp \left[ -\frac{\left(x - R_p\right)^2}{2\Delta R_p^2} \right]$$

where  $R_p$  is the average projected range normal to the surface,  $\Delta R_p$  is the straggle about that range, and  $C_p$  is the peak concentration given by

$$C_p = \frac{Q}{\sqrt{2\pi}\Delta R_p}$$

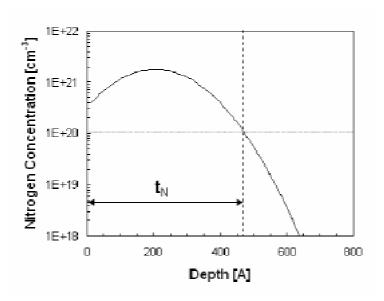

where Q is the implantation dose. Therefore, the distribution can be obtained if the implantation energy and dose are known. For example, Fig. 3.2 shows the plot of implanted  $N^+$  into Mo with the energy of 15keV and the dose of  $5\times10^{15}$ cm<sup>-2</sup>.

Figure 3.2: Distribution of  $N^+$  implanted into Mo with the energy of 15keV and the dose of  $5\times10^{15}$ cm<sup>-2</sup>.

For a fixed Mo film thickness ( $t_{Mo}$ ), the relative implantation depth of  $N^+$  is defined by subtracting the implantation depth ( $t_N$ ), where nitrogen concentration is  $10^{20} \text{cm}^{-3}$ , from  $t_{Mo}$ . This relative depth is uniquely determined by the energy and dose of implanted  $N^+$  together with  $t_{Mo}$ . For a given Mo film thickness, the relative depth decreases and becomes negative as the implantation energy and dose increase. (Negative  $t_{Mo}$ -  $t_N$  indicates that a significant fraction of the implanted nitrogen profile is located below the Mo film.)

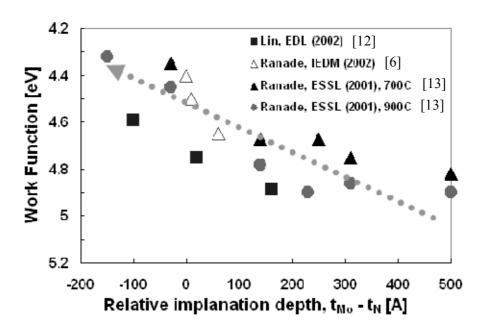

From the experimental data reported previously [6, 13, 14], the relationship between the  $\Phi_M$  of Mo and the relative implantation depth is plotted in Fig. 3.3. It is found that smaller (or even negative) relative implantation depth is required for more  $\Phi_M$  reduction of Mo, indicating the damage to the gate dielectric is a potential issue for this approach. Actually, abnormal C-V curves were obtained for Mo gated capacitors with

high  $N^+$  implantation energies [13]. Increased gate leakage current was also reported for the Mo gate capacitors with high  $N^+$  implantation energy and dose [15].

Figure 3.3: Experimentally observed work functions of Mo with different  $N^+$  implantation conditions plotted as a function of relative implantation depth.

Metal gate technology is expected to be adopted for advanced transistor structures such as the FinFET [7]. However, high-tilt ion implantation would be needed to dope the gate electrodes of such a vertical transistor structure, which limits device packing density (to avoid shadowing effects). As an alternate approach to reduce Mo gate work function, without the aforementioned issues, the impact of HTFGA on Mo gate work function is investigated and CMOS process integration issues are discussed in the following section.

### 3.3 $\Phi_{M}$ reduction by FGA

In order to investigate the impact of high-temperature forming gas annealing (HTFGA) on the Mo gate work function reduction, Mo-gate capacitors were fabricated on lightly doped p-type silicon wafer substrates. Thermally grown SiO<sub>2</sub> was used as the gate dielectric. In order to account for the influence of oxide fixed charge, multiple SiO<sub>2</sub> thicknesses were obtained on a single wafer by the selective etchback method [6]. The Mo gate film (50nm thick) was sputter deposited with a PCT (Plasma Charge Trap) to minimize gate oxide damage [16]. Some samples received a post-deposition anneal for 1m at 900°C in N<sub>2</sub>. Large-area capacitor electrodes (100μm×100μm) were then defined using i-line photolithography followed by highly selective dry etching of Mo over the gate oxide [17]. Polymer residue generated during the dry etching process was removed in EKC4000. To prevent the oxidation of Mo, the photoresist was stripped in PRS3000 solution at 80°C for 10 minutes followed by a de-ionized water rinse. Flat-band voltages  $(V_{FB})$  were determined from capacitance  $\emph{vs.}$  voltage (C-V) measurements, and  $\Phi_M$  values were extracted from plots of V<sub>FB</sub> vs. gate oxide thickness [18]. The capacitors were then subjected to various 15-minute anneals in forming gas (10%  $H_2$  / 90%  $N_2$ ) or  $N_2$ , and  $\Phi_M$ was tracked.

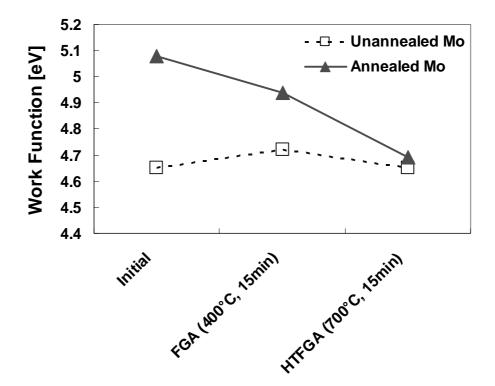

Fig. 3.4 shows the work functions of Mo gate electrodes after various annealing treatments. Consistent with a previous report, annealed Mo starts out with a higher work function than unannealed Mo, due to a more columnar grain structure with (110) planes parallel to the substrate [18]. Regardless of the initial  $\Phi_{\rm M}$  value, the Mo gate work function converges to ~4.7eV after a 700°C HTFGA. This can be attributed to a

chemical change in the Mo film, induced by the HTFGA treatment. Indeed, it was previously reported that  $H_2$  helps  $N_2$  to react with Mo to form  $Mo_2N$  during HTFGA at temperatures greater than  $600^{\circ}C$  [8]. After the HTFGA treatment, the oxide fixed charge density ( $Q_f$ , extracted from the slope of the  $V_{FB}$  vs. oxide thickness plot) is lowered by one order of magnitude, and low resistivity (in the range from 10 to 20  $\mu\Omega$ -cm) is maintained.

Figure 3.4: Work functions of Mo gate electrodes after various 15-minute annealing treatments. Annealed (1m at 900°C in  $N_2$ ) Mo shows a higher initial work function than unannealed Mo, indicating that further crystallization of Mo increases its work function [18]. After a 700°C HTFGA, the Mo work function converges to  $\sim$ 4.7eV regardless of the initial value.

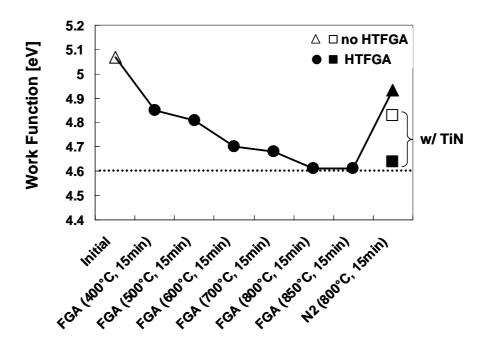

Fig. 3.5 shows that  $\Phi_M$  decreases with HTFGA temperature ( $T_{anneal}$ ) and saturates at a minimum value of 4.6eV for  $T_{anneal} > 800^{\circ}$ C. However, the reduction in  $\Phi_M$  is not retained with subsequent thermal annealing at 800°C in  $N_2$  (ref. the filled triangle in Fig. 3.5), indicating that the incorporated nitrogen can easily out-diffuse. In order to prevent out-diffusion, a TiN capping layer can be used, so that low  $\Phi_M$  is maintained with additional thermal annealing (ref. the filled square in Fig. 3.5). It has been reported that a nitrogen-rich TiN capping layer can serve as a source of nitrogen to reduce the Mo work function during a high-temperature anneal in  $N_2$  [19]. In this work, a stoichiometric TiN film was used, so that a relatively small reduction in  $\Phi_M$  with thermal annealing in  $N_2$  is seen for TiN-capped Mo (ref. the open square vs. the filled triangle in Fig. 3.5). Therefore, we deduce that the TiN capping layer serves as an effective barrier to nitrogen out-diffusion (rather than a source of nitrogen) for a nitrided Mo film.

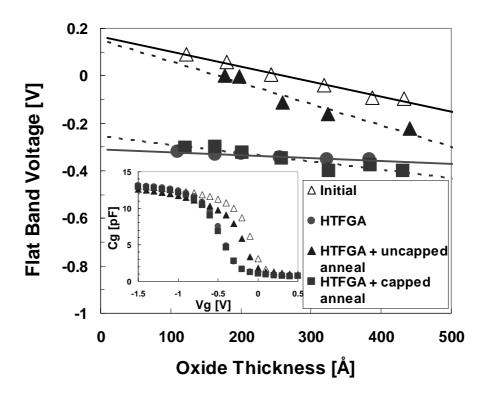

Figure 3.6 shows how the  $V_{FB}$  vs. gate oxide thickness characteristic (which is used to determine  $\Phi_M$  and  $Q_f$ ) changes after various 15-minute anneals, for capacitors with annealed Mo gate electrodes. The measured C-V curves for 25nm oxide thickness are shown in the inset for reference. A HTFGA treatment reduces  $\Phi_M$  and  $Q_f$  (ref. filled circles vs. open triangles in Fig. 3.6). Subsequent high-temperature (800°C) annealing in  $N_2$  causes nitrogen out-diffusion so that the HTFGA-induced reduction in  $\Phi_M$  is lost and  $Q_f$  is increased (ref. filled triangles in Fig. 3.6). A TiN capping layer is effective for blocking nitrogen out-diffusion during the high-temperature anneal in  $N_2$ , so that low  $\Phi_M$  and  $Q_f$  are retained (ref. filled squares in Fig. 3.6).

Figure 3.5: Evolution of Mo gate work function with sequential annealing.  $\Phi_M$  decreases with increasing forming gas annealing temperature ( $T_{anneal}$ ), and saturates at 4.6eV for  $T_{anneal} > 800^{\circ}$ C. Unless a TiN capping layer is applied, the reduction in  $\Phi_M$  is not retained with additional high-temperature annealing in  $N_2$ . Considering that a much smaller reduction in  $\Phi_M$  is induced by the TiN capping layer itself (ref. the open square), these results indicate that TiN is an effective barrier to nitrogen out-diffusion.

Figure 3.6: Flat band voltage vs. oxide thickness for capacitors with annealed Mo gate electrodes. The measured C-V curves for 25nm oxide thickness are shown in the inset for reference. A 15-minute, 800°C HTFGA reduces the Mo work function and lowers the fixed charge density (Q<sub>f</sub>). N<sub>2</sub> annealing (15m at 800°C) after HTFGA causes the  $\Phi_{\rm M}$  reduction to be lost and results in worse Q<sub>f</sub>. However, the  $\Phi_{\rm M}$  reduction and low Q<sub>f</sub> are retained with a TiN capping layer.

Figure 3.7 shows how dual work function Mo gate electrodes may be achieved in an integrated CMOS process flow. In this flow, a HTFGA step is used to globally reduce the Mo gate work function; afterwards, the n-channel devices are selectively capped with TiN so that the low gate work function (4.6eV) is retained through the remainder of the device fabrication process. Since the p-channel devices are not capped, the Mo gate work

function will return to a high value ( $\sim$ 5.0eV) as nitrogen out-diffuses during the various thermal process steps (e.g., the source/drain dopant activation anneal). The ability to etch TiN with high selectivity to Mo is crucial for implementing this process flow. Fortunately, a standard  $Cl_2+O_2$  dry etch process shows very high (>100:1) TiN etch selectivity to Mo.

Well Doping

Gate stack deposition (Moly/Gox)

HTFGA (H<sub>2</sub>/N<sub>2</sub>, 800°C, 15min)

TiN sputtering

Selective TiN etching for PMOS region

Channel doping

Gate patterning

Slim spacer formation

S/D extension IIP

Spacer formation

S/D IIP

S/D Activation annealing

Figure 3.7: Proposed CMOS process flow to achieve dual Mo gate work functions.

Therefore, high temperature forming gas annealing is an effective technique for tuning the gate work function of Mo.  $\Phi_{\rm M}$  decreases with increasing  $T_{\rm anneal}$  and saturates at 4.6eV for  $T_{\rm anneal} > 800^{\circ}{\rm C}$ . The reduction in  $\Phi_{\rm M}$  is not retained with subsequent thermal annealing (e.g. 15m at 800°C in N<sub>2</sub>) due to nitrogen out-diffusion, however. In order to prevent out-diffusion, a TiN capping layer can be used, so that low  $\Phi_{\rm M}$  is maintained with

additional thermal annealing. By selectively using a TiN capping layer in the n-channel device regions, the HTFGA technique can be applied to achieve dual work function Mo gate electrodes suitable for advanced CMOS technologies employing thin-body MOSFETs.

## 3.4 Theory for $\Phi_{M}$ reduction

Structural and chemical modifications have been considered as major mechanisms for changing the work function of Mo by  $N^+$  implantation and/or thermal annealing [20]. In general, densely packed crystallographic surfaces yield high work functions since these surfaces are smooth and relatively inert with few broken atomic bonds. On the other hand, open crystallographic surfaces yield low work functions due to a greater number of broken bonds. In the case of Mo, the densest plane is the (110) plane [21], and Mo films deposited by sputtering show a substantial fraction of grains with this orientation. Thus, the  $\Phi_M$  of an as-deposited Mo film is normally high, increasing slightly with additional thermal annealing and becoming stable around at 5eV. This high  $\Phi_M$  can be reduced by structural modification of the Mo film, such as amorphization by  $Ar^+$  implantation. However, the Mo film is easily recrystallized and shows higher  $\Phi_M$  again with subsequent thermal annealing, as indicated from the increased intensity of the (110) measured by X-ray diffraction (XRD) patterns.

$N^+$  implantation is also expected to amorphize the Mo film and is known to reduce  $\Phi_M$ . In contrast, the reduced work function by  $N^+$  implantation is retained or even reduced further as annealing temperature ( $T_{anneal}$ ) increases, indicating that chemical

modification occurs. The metal work function in vacuum ( $\Phi_{M, VAC}$ ), defined by the minimum energy required to remove an electron from the metal surface at 0K [22], is commonly assumed to be the same as the effective work function ( $\Phi_{M, EFF}$ ), determined by the energy band alignment between the metal gate and gate dielectric. However, since  $\Phi_{M, EFF}$  is found by plotting flat band voltage ( $V_{FB}$ ) as a function of oxide thickness ( $T_{ox}$ ) derived from C-V measurements, it additionally reflects the presence of dipole layers in the insulator layer of the MOS structure [23]. A centroid of charge at a fixed distance from the metal-insulator interface also affects  $\Phi_{M, EFF}$  [24]. Nitrogen segregation to the Mo-SiO<sub>2</sub> interface is believed to result in a dipole moment and hence reduction in the  $\Phi_{M, EFF}$  of Mo. Actually, nitrogen segregation the Mo-SiO<sub>2</sub> interface was observed from secondary-ion mass spectroscopy (SIMS) analysis of an annealed  $N^+$  implanted Mo sample [14].

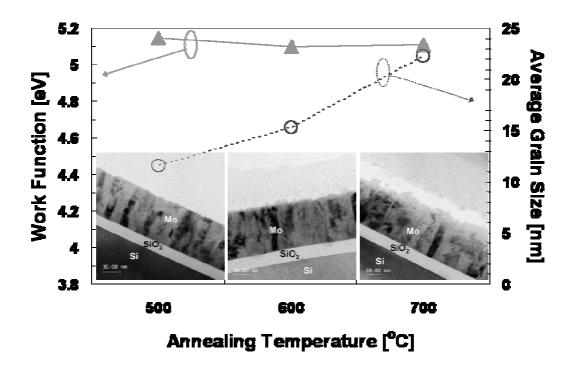

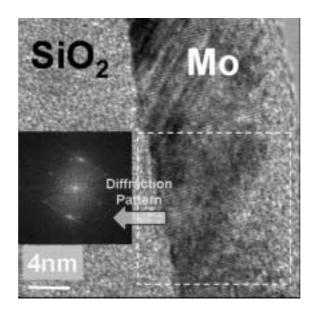

In order to clarify the mechanism of Mo  $\Phi_M$  reduction, the physical microstructure and chemical composition were investigated using high-resolution transmission electron microscopy (HR-TEM, Courtesy of Dr. Xiaoyu Xu and Prof. Eicke Weber). Fig. 3.8 shows the effect of  $T_{anneal}$  on  $\Phi_M$  and average grain size of un-implanted Mo.  $N_2$  annealing was performed for 15 minutes at 500°C, 600°C, or 700°C. All samples show similarly high  $\Phi_M$  (~5.1eV) even though the average grain size becomes larger as  $T_{anneal}$  increases, while showing the same columnar grain structures (*i.e.*, (110) texture), indicating  $\Phi_M$  is independent of the grain size. The crystalline quality, especially near to the Mo-SiO<sub>2</sub> interface, is also good for all the samples as shown in Fig. 3.9.

Figure 3.8: Annealing temperature effect on  $\Phi_M$  and grain size of un-implanted Mo.

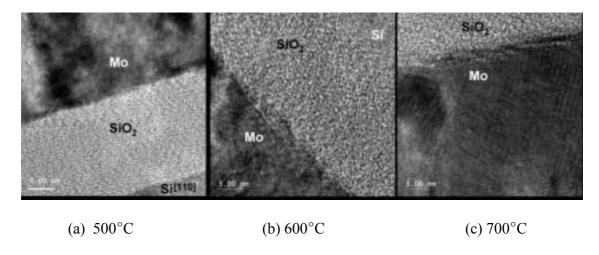

Figure 3.9: HR-TEM pictures showing crystalline quality near Mo-SiO<sub>2</sub> interface for unimplanted Mo.

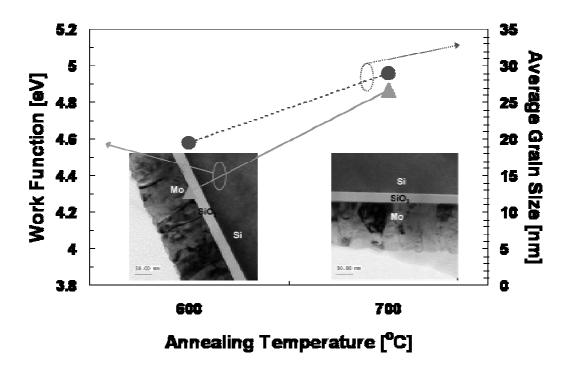

Fig. 3.10 shows the effect of  $T_{anneal}$  on  $\Phi_M$  and grain size, for Mo implanted with  $N^+$  with  $10^{16} \text{cm}^{-2}$  dose and 40keV energy.  $N_2$  annealing was performed for 15 minutes at  $600^{\circ}\text{C}$  or  $700^{\circ}\text{C}$ . Again, HR-TEM pictures show columnar grain structures induced by thermal annealing; high  $\Phi_M$  of Mo is anticipated. However, only the Mo sample annealed at  $700^{\circ}\text{C}$  shows high  $\Phi_M$  (~4.9eV), while the Mo sample annealed at  $600^{\circ}\text{C}$  still shows reduced  $\Phi_M$  (~4.3eV). Similar data has been reported in [14], showing that the  $\Phi_M$  reduction by  $N^+$  implantation is restored (becomes high again) as  $T_{anneal}$  increases. In that case, even more nitrogen segregation at the Mo-SiO<sub>2</sub> interface was observed by SIMS, excluding the possibility of  $N_2$  out-diffusion. Instead, it was found that the intensity of the (110) diffraction peak further increased at higher  $T_{anneal}$ , indicating an improvement of crystalline quality of the film is a dominant effect for  $\Phi_M$  change as compared to chemical modification effects. In addition, the average grain size of  $N^+$  implanted Mo film is larger than that of un-implanted one with the same  $T_{anneal}$ . This can be explained by defect-assisted grain growth induced by ion implantation.

Figure 3.10: Annealing temperature effect on  $\Phi_{\rm M}$  and grain size of N<sup>+</sup> implanted Mo.

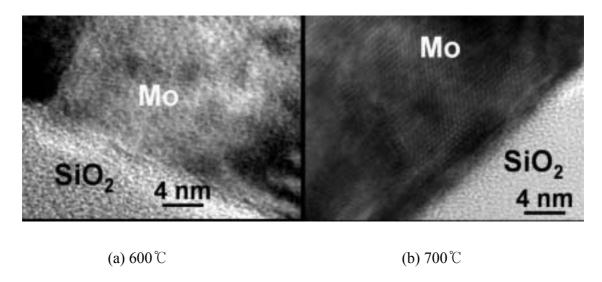

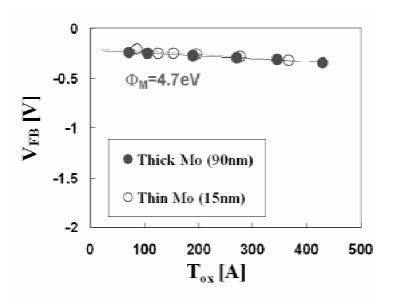

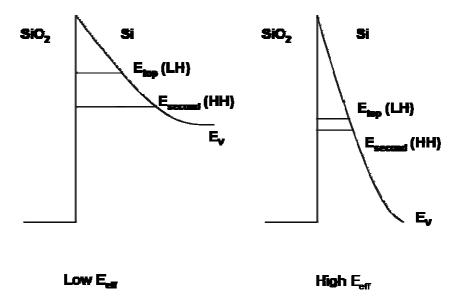

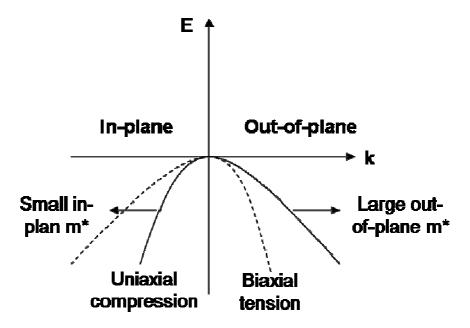

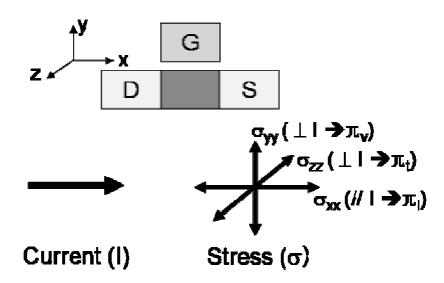

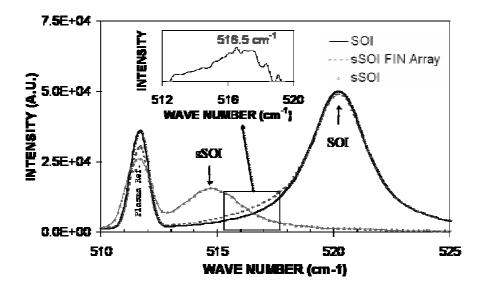

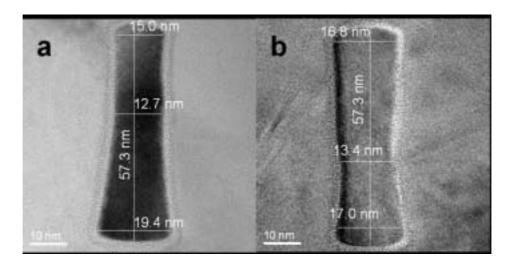

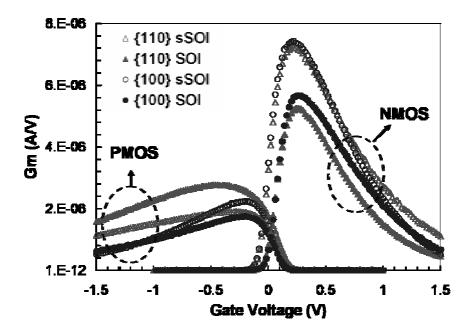

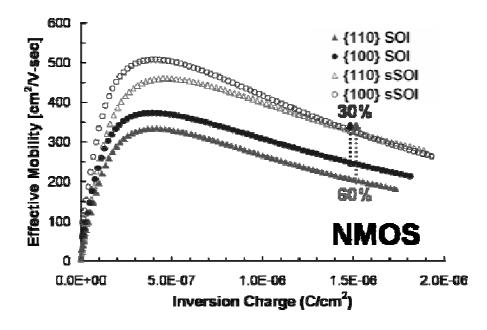

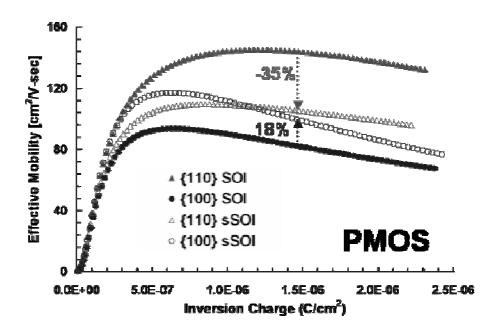

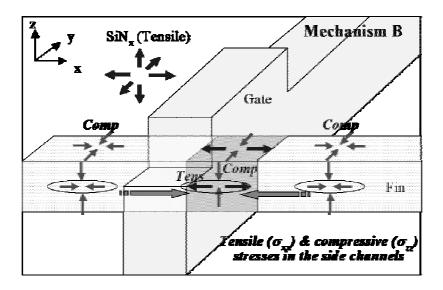

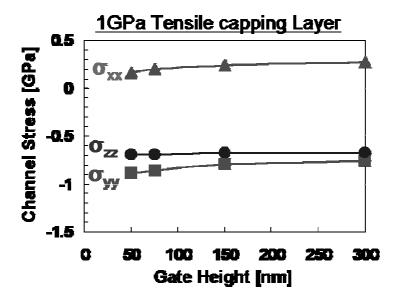

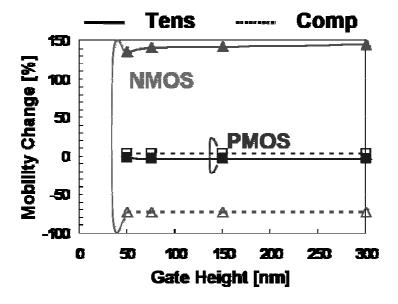

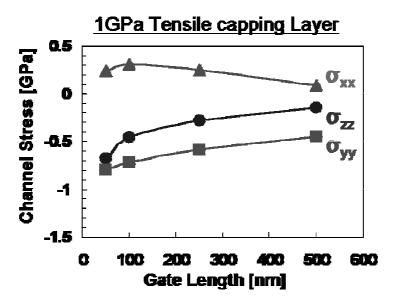

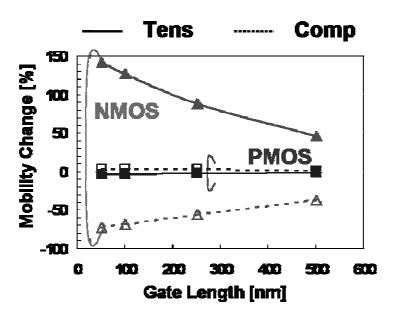

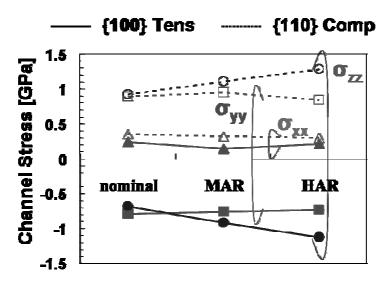

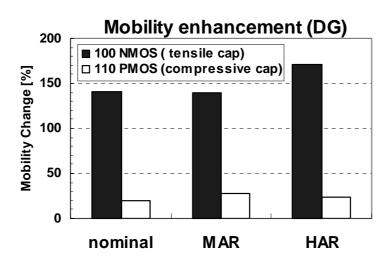

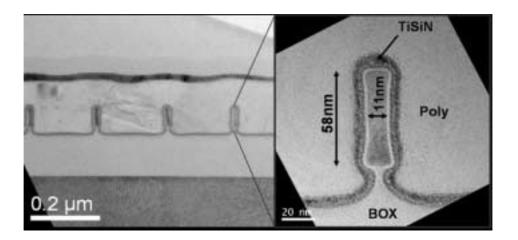

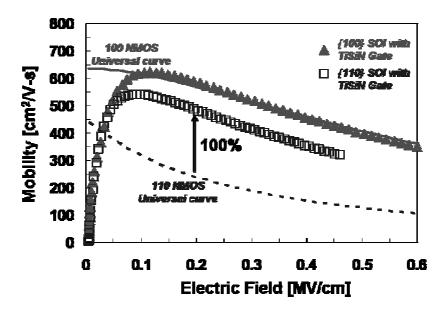

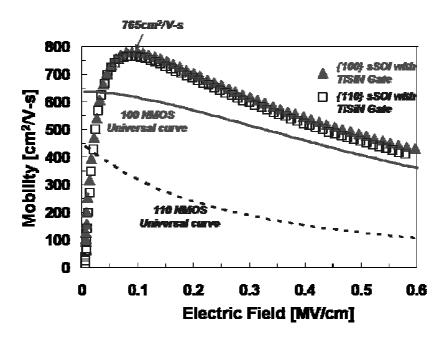

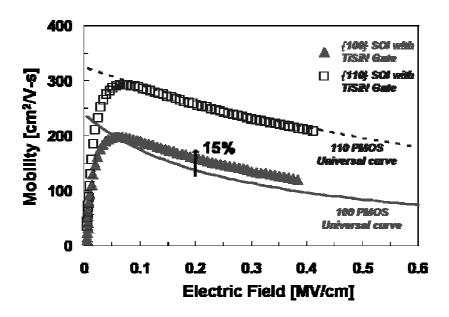

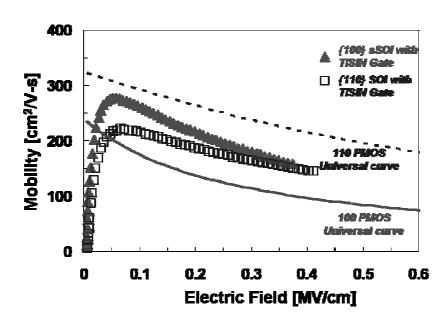

HR-TEM pictures in Fig. 3.11 consistently confirm that the crystalline quality of  $N^+$  implanted Mo with higher  $T_{anneal}$  is better than that with lower  $T_{anneal}$ . However, these results are contradictory with those shown in Fig. 3.1, which show that  $\Phi_M$  reduction induced by  $N^+$  implantation further grows as  $T_{anneal}$  increases, indicating the importance of chemical modification (nitrogen segregation) for  $\Phi_M$  reduction. Coincidentally, the low  $\Phi_M$  was restored back to high  $\Phi_M$  for thick Mo films (90nm, 150nm) but retained for thin Mo film (15nm). Therefore, it is clear that  $\Phi_M$  of  $N^+$  implanted Mo is determined by the combination of structural and/or chemical modification effects, but it seems that structural modification effects might become dominant as  $T_{anneal}$  increases unless the Mo film is very thin. Actually, thick Mo film has relatively small amount of nitrogen