# **Ultra-Low-Cost Printed Electronics**

Steven Edward Molesa

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2006-55 http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-55.html

May 15, 2006

Copyright © 2006, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### **Ultra-Low-Cost Printed Electronics**

by

Steven Edward Molesa

B.S. (Hope College) 2001 B.A. (Hope College) 2001 M.S. (University of California, Berkeley) 2004

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Vivek Subramanian, Chair Professor Jeffrey Bokor Professor Costas Grigoropoulos

Spring 2006

## Ultra-Low-Cost Printed Electronics

© Copyright 2006

By

Steven Edward Molesa

| Chair | Date |

|-------|------|

|       |      |

|       | Date |

|       |      |

|       | Date |

The dissertation of Steven Edward Molesa is approved:

University of California, Berkeley Spring 2006

#### Abstract

#### **Ultra-Low-Cost Printed Electronics**

by

#### Steven Edward Molesa

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vivek Subramanian, Chair

Ultra-low-cost printed electronics seek to reduce the manufacturing cost of electronics with less expensive, all-additive printing methods that conventional silicon manufacturing cannot replicate. But, in order to print these electronics, there is a trade-off in performance. Despite this, there are several applications for low-cost printed electronics including radio frequency identification (RFID) tags, electronic sensors, displays, smart cards, packaging, and printed circuit boards (PCB). In this work, inkjet and gravure printing are used to fabricate electronic devices. Particular emphasis is placed on inkjet printing. Based on performance requirements for the above applications, suitable electronic materials for printing are examined, including a soluble gold nanoparticle ink for metallization, printable organic dielectrics including polyimide and PVP, and a high performance pentacene precursor semiconductor ink. All of these materials have plastic substrate compatible activation temperatures (<200°C). Due to the "donut effect", and other complex inkjet phenomena such as differential wetting, each ink must be optimized to allow printing of smooth, well-defined structures and lines. The processing techniques developed for each ink are presented. Using these techniques,

printed high-Q passive components and transistors were fabricated on plastic. The resulting devices represent some of the highest performance printed devices published to date and both their AC and DC properties are studied in-depth. Finally, based on the fabricated transistors, a manufacturing route to achieve the necessary performance,  $f_t > 500 \, \text{kHz}$ , for the discussed applications is proposed.

#### Acknowledgements

This project was made possible through the generous help and support of many friends and family along with the direct contributions of fellow co-workers at the University of California, Berkeley. In particular, I would like to thank the entire Cory Hall machine shop: Ben Lake, Warner Carlisle, Bob Amaral, and Joseph Gavazza. Each person in the machine shop contributed to the fabrication of the printer in some manner. Furthermore, I enjoyed sharing conversations about the latest radio control models or weekend plans.

The microlab staff also deserves thanks for their invaluable support and maintenance of the Organic Electronics Laboratory. In particular Phill Guillory and Bob Donnelly were particularly helpful with laboratory infrastructure problems and enhancement of the working conditions in our office. The jokes and discussion always made for a pleasant time as well.

I also owe a large thanks to my fellow lab members. I would like to thank the whole group including all the members that came and went over the past five years for making it an enjoyable time. The football, jokes, and conversation always made the day easier. In particular, though, there are several people that deserve special thanks as they where here for the majority of the duration I was. Paul Chang, Josephine Chang, Alejandro de la Fuente Vornbrock, Steve Volkman, Tuyen Lee, Brian Mattis, and Qintao Zhang always provided advice, help in the form of wafer fabrication, and good conversation.

Although the Eliassen family did not provide direct help at the research lab, they provided me with a home away from home and for that I am thankful. Also, I would like to thank my good friend Bill Johnson for always being someone to talk to- ta gra.

I also owe special thanks to my advisor, Vivek Subramanian. You provided the resources, knowledge, and guidance I needed to finish this degree. Your vast knowledge of electronics was an invaluable source of information and helped me choose the right experiments to form a more complete picture of the problem while your guidance helped me mature as a person and as an engineer. You were also a very enjoyable advisor to work for and I particularly enjoyed our football discussions and summer football games. I am a much better engineer and person because of you and, looking back, I could not have had a better advisor.

My mother and father, Catherine Osip and John Molesa, deserve special thanks as well. Over the years you have always provided me with your time, emotional support, and the financial support I needed to reach this point in my life. In particular, I am grateful for all the rides you gave me to sporting or academic events, financial support you have provided me with for education or social endeavors, and your attendance at sporting or academic events. Of course our numerous family vacations and your trips out to California to visit me were obviously enjoyable, as well. One of my aspirations in life is that I can repay some of this support and that I can provide the same for my children.

Finally, I want to give special thanks to my beautiful fiancée, Annalise Van Wyngarden. You have provided me with immeasurable emotional support over the past five years. You always help brighten a bad day and I thoroughly enjoyed the time I spent

with you over the past five years. I look forward to a wonderful and happy life together with you.

# **Table of Contents**

| Chapter 1: Introduction to Low Cost Printed Electronics               | 1  |

|-----------------------------------------------------------------------|----|

| 1.1 Introduction                                                      | 1  |

| 1.2 Silicon's Shortfalls                                              | 3  |

| 1.3 The Cost Solution: All-Printed Electronics                        | 5  |

| 1.4 Applications                                                      | 7  |

| 1.5 Methodology                                                       | 9  |

| 1.6 Organization                                                      | 10 |

| Chapter 2: Inkjet Printing Technology and Experimental Testbed        | 12 |

| 2.1 Inkjet Technology Background                                      | 13 |

| 2.2 General Inkjet Printer Components                                 | 15 |

| 2.2.1 Bubble Jet Dispensers                                           | 15 |

| 2.2.2 Piezoelectric Dispensers                                        | 17 |

| 2.3 Experimental Inkjet Testbed and Specifications                    | 17 |

| 2.3.1 Motion Stages                                                   | 18 |

| 2.3.2 Dispenser and Dispensing Theory                                 | 19 |

| 2.3.3 Pressure and Meniscus Control                                   | 23 |

| 2.3.4 Solvent Delivery Path                                           | 25 |

| 2.3.5 Substrate Chuck                                                 | 26 |

| 2.3.6 Software and Computer Interface                                 | 26 |

| 2.3.7 Alignment Algorithm                                             | 27 |

| 2.3.8 Support Structure                                               | 30 |

| 2.4 Conclusions                                                       | 31 |

| <b>Chapter 3: Inkjet Processing Techniques and Passive Components</b> | 34 |

| 3.1 Introduction to Passive Components                          | 34         |

|-----------------------------------------------------------------|------------|

| 3.2 Introduction to Printing                                    | 37         |

| 3.3 Introduction to Low Cost Electronic Inks                    | 40         |

| 3.3.1 Interconnect Inks                                         | 40         |

| 3.3.2 Dielectric Inks                                           | 44         |

| 3.4 Experimental Setup                                          | 46         |

| 3.5 Results and Discussion                                      | 46         |

| 3.5.1 Conductor Film Development                                | 46         |

| 3.5.2 Dielectric Film Development                               | 51         |

| 3.5.3 Multilayer Interconnect and Inductive Component Demons    | stration53 |

| 3.6 Conclusions                                                 | 54         |

| Chapter 4: Low Cost Semiconductors and Printing                 | 56         |

| 4.1 Introduction to Low Cost Semiconductors and Transport Proce | sses56     |

| 4.2 Common Organic Semiconductors                               | 60         |

| 4.3 Introduction to Printed Thin Film Transistors               | 64         |

| 4.4 Precursor Optimization Experimental Setup                   | 65         |

| 4.4.1 Experimental Parameters                                   | 66         |

| 4.4.2 Results and Discussion                                    | 67         |

| 4.5 Material Improvements                                       | 71         |

| 4.5.1 Solvent Distillation Experiment                           | 71         |

| 4.5.2 Results                                                   | 72         |

| 4.5.3 Further Improvements                                      | 73         |

| 4.6 Conclusions                                                 | 74         |

| Chapter 5: A Baseline Process for All-Printed Transistors       | 76         |

| 5.1 Introduction                                                | 76         |

| 5.2 Experimental Setup                                | 76  |

|-------------------------------------------------------|-----|

| 5.2.1 Ink Formulation                                 | 77  |

| 5.2.2 Baseline Process Flow                           | 78  |

| 5.3 Jetting Techniques                                | 81  |

| 5.3.1 Electrodes                                      | 82  |

| 5.3.2 Dielectric                                      | 82  |

| 5.3.3 Semiconductor                                   | 83  |

| 5.4 Results and Discussion                            | 83  |

| 5.5 Conclusions                                       | 87  |

| Chapter 6: Gate Dielectric Scaling                    | 89  |

| 6.1 Introduction                                      | 89  |

| 6.2 Experimental Setup                                | 90  |

| 6.3 Substrate Engineering                             | 91  |

| 6.4 Process Flow                                      | 92  |

| 6.4.1 Gate Stack Structures                           | 94  |

| 6.5 Jetting Techniques                                | 94  |

| 6.6 Results and Discussion                            | 95  |

| 6.6.1 Gate Stack Optimization                         | 95  |

| 6.6.2 Scaled Device DC Performance                    | 95  |

| 6.7 Conclusions                                       | 100 |

| Chapter 7: Frequency Performance and Characterization | 102 |

| 7.1 Introduction                                      | 102 |

| 7.2 f <sub>t</sub> : Transition Frequency             | 104 |

| 7.3 Measurement Technique                             |     |

| 7.4 Results and Discussion                            |     |

| 7.4.1 Improving f <sub>t</sub>                            | 111 |

|-----------------------------------------------------------|-----|

| 7.4.1.1 Mobility Effects                                  | 112 |

| 7.4.1.2 Electrode Overlap Capacitance                     | 112 |

| 7.5 Conclusions                                           | 114 |

| Chapter 8: Gravure Printing and Future Work               | 116 |

| 8.1 Introduction to Gravure Printing                      | 116 |

| 8.2 Experimental Setup                                    | 118 |

| 8.3 Results and Discussion                                | 119 |

| 8.3.1 Incomplete Dissolution                              | 119 |

| 8.3.2 Spreading and Distortion                            | 120 |

| 8.3.3 Directional Printing                                | 121 |

| 8.3.4 Solvent Mixture and Binders                         | 122 |

| 8.4 Future Work                                           | 124 |

| 8.4.1 Gravure Printing                                    | 124 |

| 8.4.2 Hybrid Printing                                     | 126 |

| 8.4.3 Semiconductors                                      | 127 |

| 8.4.4 Dielectrics                                         | 128 |

| 8.4.5 Improving Integration                               | 128 |

| 8.4.6 Circuit Prototyping                                 | 129 |

| 8.5 Conclusions                                           | 129 |

| Chapter 9: Summary and Conclusions                        | 131 |

| 9.1 Summary                                               | 131 |

| 9.1.1 Introduction to Low Cost Printed Electronics        | 131 |

| 9.1.2 Inkjet Printing Technology and Experimental Testbed | 132 |

| 9.1.3 Inkiet Processing Techniques and Passive Components | 132 |

| 9.1.4 Low Cost Semiconductors and Printing                 | 133   |

|------------------------------------------------------------|-------|

| 9.1.5 A Baseline Process for All-Printed Transistors       | 134   |

| 9.1.6 Gate Dielectric Scaling                              | 134   |

| 9.1.7 Frequency Performance and Characterization           | 135   |

| 9.1.8 Gravure Printing and Future Work                     | 135   |

| 9.2 Concluding Comments                                    | 136   |

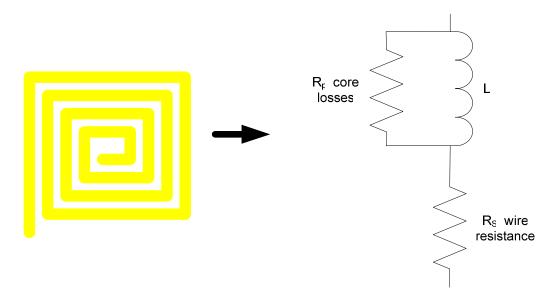

| Appendix A: Passive Components and Tank Circuit Theory     | 138   |

| A.1 Passive Component Quality Factor, Q                    | 138   |

| A.1.1 Inductor Q                                           | 138   |

| A.1.2 Capacitor Q                                          | 139   |

| A.2 Tank Circuit Theory                                    | 140   |

| A.3 Tank Circuit Quality Factor                            | 143   |

| Appendix B: Gold Nanoparticle Synthesis                    | 145   |

| B.1 Introduction                                           | 145   |

| B.2 Chemicals Required                                     | 145   |

| B.3 Laboratory Equipment                                   |       |

| B.4 General Process                                        |       |

| B.5 Detailed Synthesis                                     | 147   |

| B.5.1 Synthesis                                            |       |

| B.5.2 Purification                                         |       |

| Appendix C: Electronic Transport in Organic Semiconductors |       |

| C.1 Introduction                                           |       |

| C.2 Introduction to Band Transport Theory                  |       |

| C.3 Temperature Effects on Organic Semiconductor Transport |       |

| C.3.1 MTR Model                                            |       |

| v. v ivid dividuel                                         | 1:3.3 |

| C.3.2 VRH Model                                               | 154 |

|---------------------------------------------------------------|-----|

| C.4 Electric Field Effects on Organic Semiconductor Transport | 157 |

| C.4.1 Gate Dependent Mobility in FET's                        | 157 |

| Appendix D: Pentacene Precursor Synthesis                     | 159 |

| D.1 Introduction                                              | 159 |

| D.2 Chemicals Required                                        | 159 |

| D.3 Laboratory Equipment                                      | 159 |

| D.4 General Process                                           | 160 |

| D.5 Detailed Synthesis                                        | 161 |

| D.5.1 Pentacene Sublimation Purification                      | 161 |

| D.5.2 NSO Synthesis                                           | 162 |

| D.5.3 Reflux Reaction (Diels Alder)                           | 163 |

| D.5.4 Flash Column Purification                               | 154 |

| References                                                    | 166 |

# List of Figures

| Figure 1.1: Example of an all-additive, reel-to-reel, printed manufacturing   |     |

|-------------------------------------------------------------------------------|-----|

| process                                                                       | 6   |

| Figure 2.1: Cross section of a typical bubble jet dispenser showing how       |     |

| droplet generation occurs                                                     | 16  |

| Figure 2.2: Cross section of a piezoelectric inkjet dispenser showing how     |     |

| droplet ejection occurs                                                       | 17  |

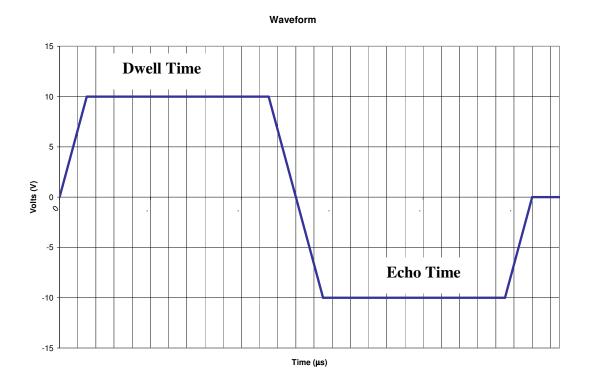

| Figure 2.3: Bipolar voltage waveform                                          | .20 |

| Figure 2.4: Illustration of pressure wave propagation in a piezoelectric      |     |

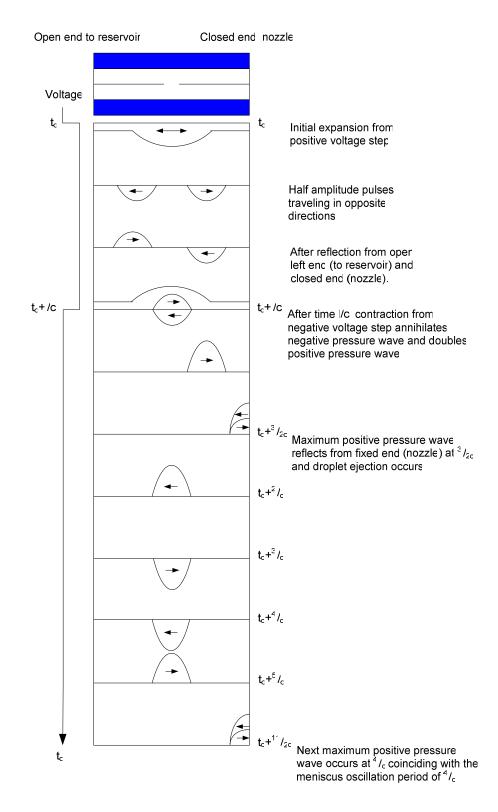

| dispenser                                                                     | .22 |

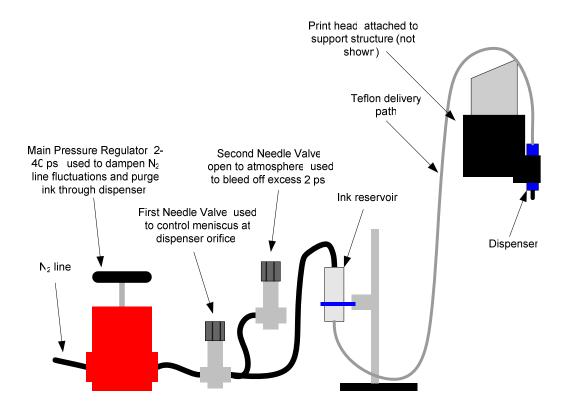

| Figure 2.5: Side view of the pressure control system and the ink delivery     |     |

| pathway                                                                       | .24 |

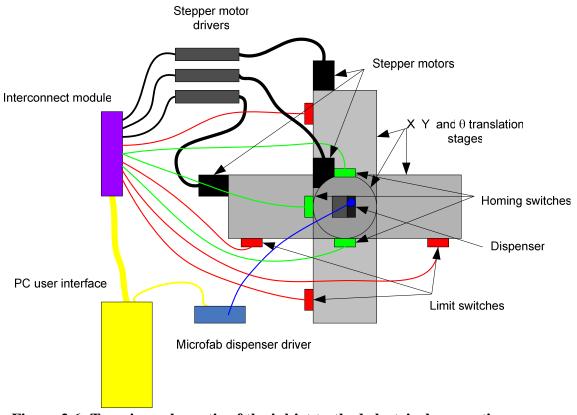

| Figure 2.6: Top view schematic of the inkjet testbed electrical connections   | .27 |

| Figure 2.7: Alignment geometry                                                | .30 |

| Figure 2.8: Side view schematic of the inkjet testbed support structure and   |     |

| optics system                                                                 | 31  |

| Figure 2.9: Custom built inkjet testbed                                       | .32 |

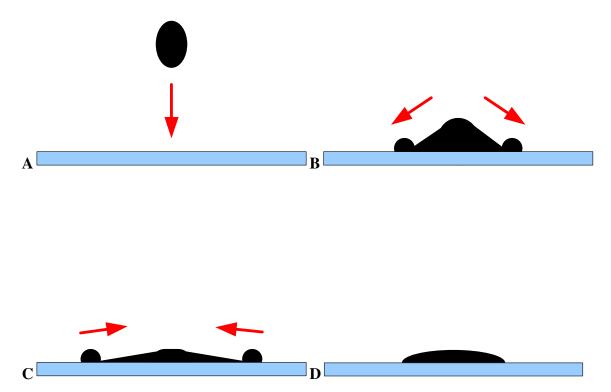

| Figure 3.1: A-C; Cross sectional, conceptual depiction of a droplet impinging |     |

| on a surface                                                                  | .39 |

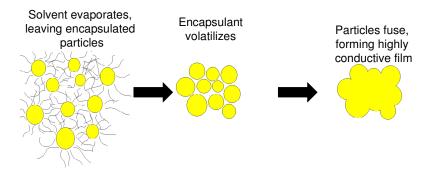

| Figure 3.2: Nanoparticle annealing process                                    | .42 |

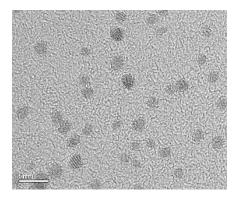

| Figure 3.3: TEM of 1.5 nm Au particles used for interconnects and metal       |     |

| contacts                                                                      | .44 |

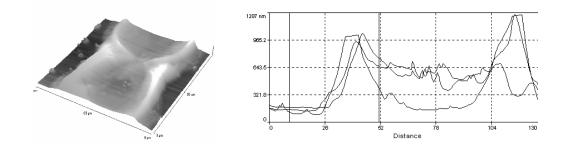

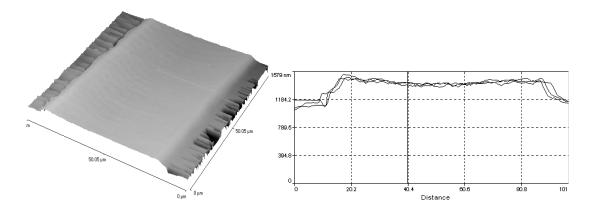

| Figure 3.4: Atomic force micrograph showing the characteristic                |     |

| "coffee-ring" structure that results from splashing during droplet            |     |

| deposition, and profilometry of a typical film formed using this               |          |

|--------------------------------------------------------------------------------|----------|

| process, showing the substantial roughness                                     | 47       |

| Figure 3.5: Effect of substrate temperature during deposition on coffee-ring   |          |

| splash effect                                                                  | 48       |

| Figure 3.6: Overlaying of successive drops to reduce the coffee-ring splash    |          |

| effect                                                                         | 48       |

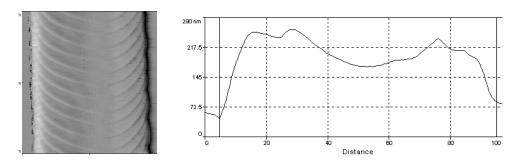

| Figure 3.7: Smooth conductor lines obtained by printing gold nanoparticles     |          |

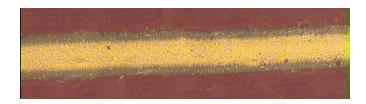

| dissolved in α-terpineol at a substrate temperature of 160°C                   | 49       |

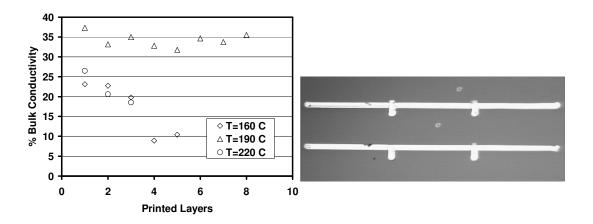

| Figure 3.8: Variation in conductivity with temperature and number of           |          |

| syncopated layers [23], as measured using a four-point sheet                   |          |

| resistance structure                                                           | 50       |

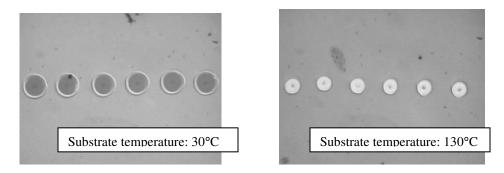

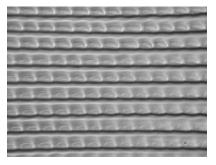

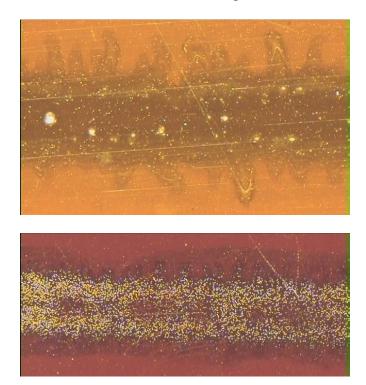

| Figure 3.9: Printed dielectric layers showing the agglomeration that results a | t        |

| low temperatures, and the smooth films achieved at intermediate                |          |

| temperatures                                                                   | 53       |

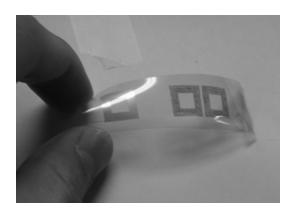

| Figure 3.10: The conductor and dielectric technologies developed herein allo   | W        |

| us to demonstrate multilevel interconnects with few shorts, and also           |          |

| demonstrate inductors with high Q's                                            | 54       |

| Figure 4.1: Delocalized $\pi$ orbitals form a continuous electron cloud        |          |

| where electrons are free to move                                               | 58       |

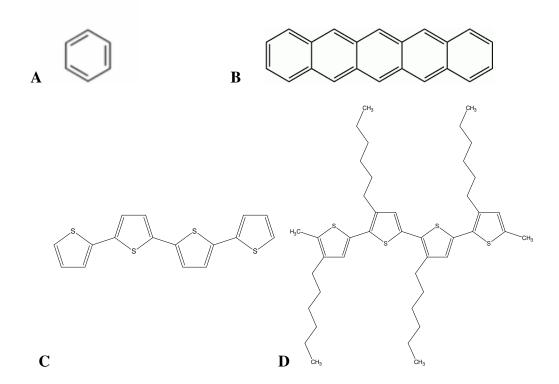

| Figure 4.2: Benzene molecule (A) is the basic building block of pentacene (B)  | ).       |

| The thiophene backbone of the tetrathiophene molecule (C) has the same         | <b>;</b> |

| backbone as regioregular polyhexylthiophene (D)                                | 61       |

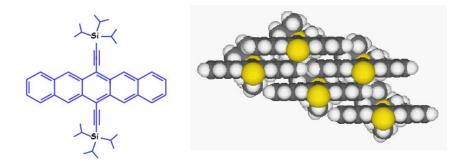

| Figure 4.3: TIPS pentacene and its packing configuration                       | 63       |

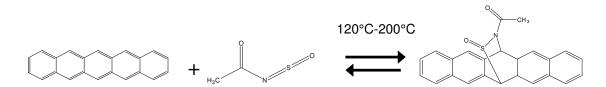

| Figure 4.4: Diels-Alder pentacene precursor formation                          | 65       |

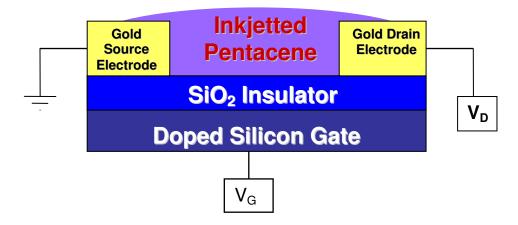

| Figure 4.5: Device structure cross section                                     | 67       |

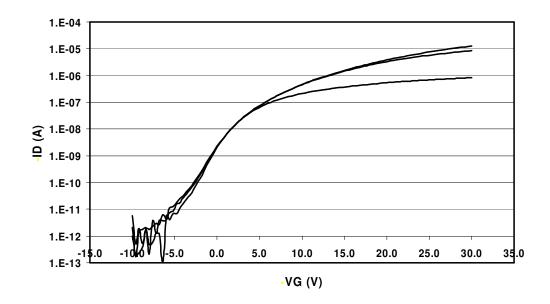

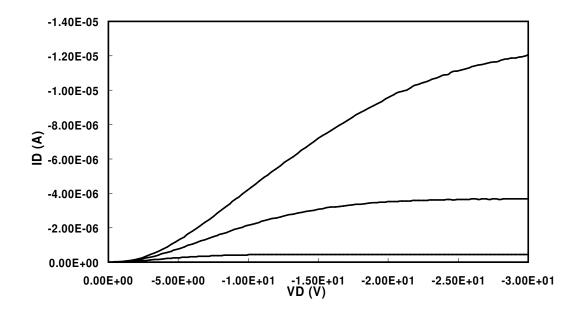

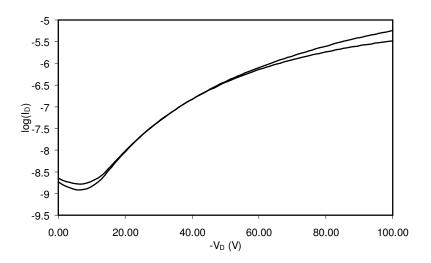

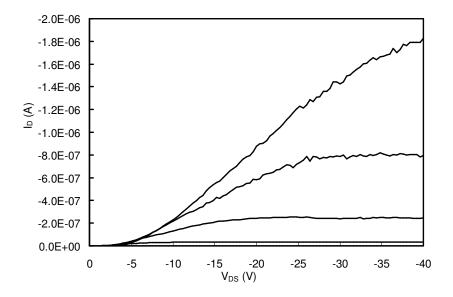

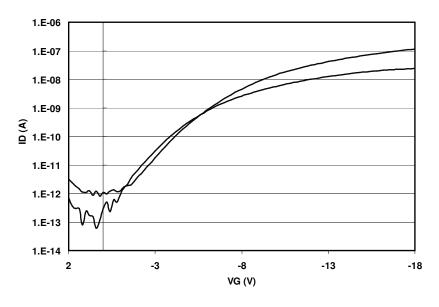

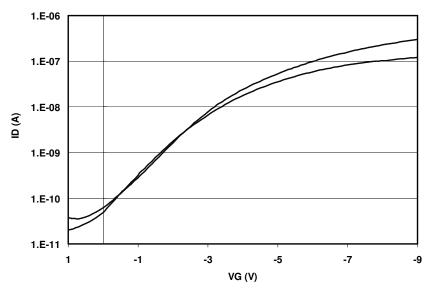

| Figure 4.6: Typical $I_D$ - $V_G$ (top) and $I_D$ - $V_D$ (bottom) curves; W/L=100/5 $\mu$ m,                               |    |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| $\mu$ =0.099cm <sup>2</sup> /V-s, I <sub>on/off</sub> =10 <sup>4</sup>                                                      | 69 |

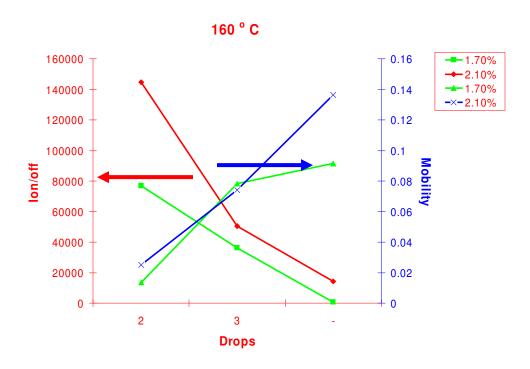

| Figure 4.7: Average performance of transistors annealed at 160°C                                                            | 70 |

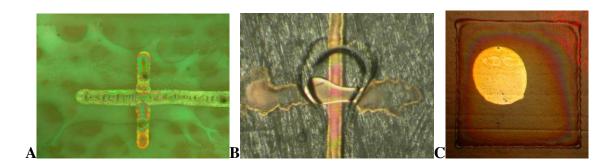

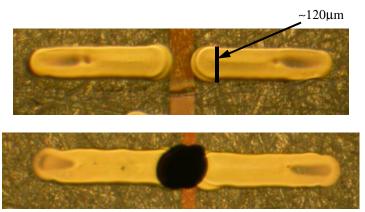

| Figure 5.1: A; Printed polyimide gate dielectric. B; Printed PVP dielectric with                                            |    |

| PGMEA solvent. C; Printed PVP dielectric with hexanol solvent                                                               | 78 |

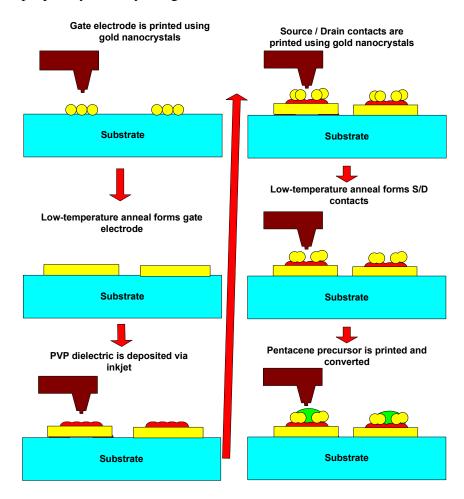

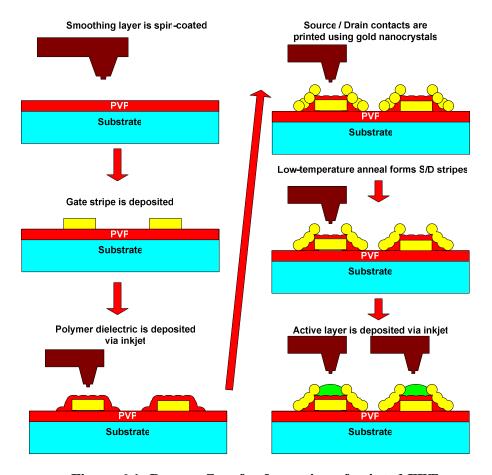

| Figure 5.2: Process flow for formation of printed FETs                                                                      | 79 |

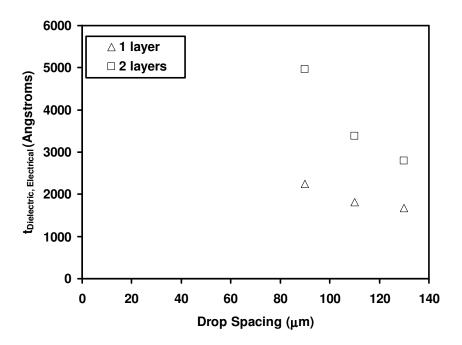

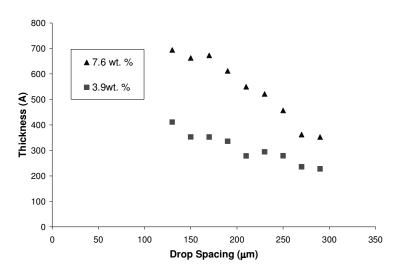

| Figure 5.3: Effect of jetting parameters on thickness of inkjetted dielectric                                               | 80 |

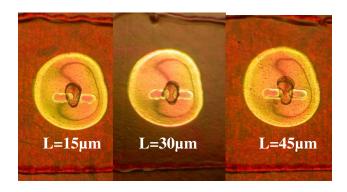

| Figure 5.4: Optical micrographs of various printed FETs                                                                     | 81 |

| Figure 5.5: Discontinuous semiconductor film resulting from thick electrodes                                                | i  |

| and "pooling" of drops                                                                                                      | 83 |

| Figure 5.6: Transfer characteristics for a 120 $\mu$ m/45 $\mu$ m device, $t_{dielectric} \sim 5000 \mbox{\AA}$             | ;  |

| μ ~0.17cm²/V-s                                                                                                              | 84 |

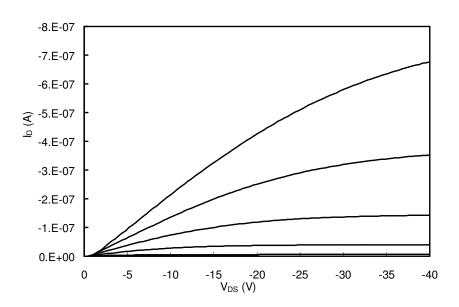

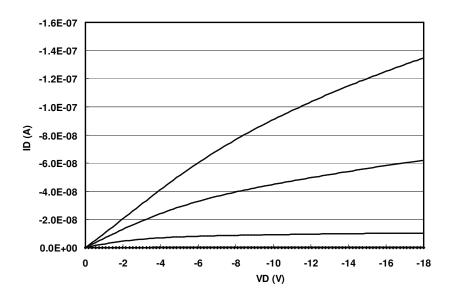

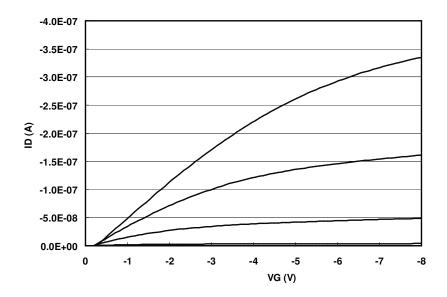

| Figure 5.7: Output characteristics for a 120 $\mu$ m/45 $\mu$ m device, $t_{dielectric} \sim 5000 \mbox{\normalfont\AA}$ (p | u  |

| ~0.17cm <sup>2</sup> /V-s)                                                                                                  | 85 |

| Figure 5.8: Transfer characteristics for a 100 $\mu$ m/15 $\mu$ m device, $t_{dielectric}\sim 5000 \mbox{\AA}$              | ;  |

| μ ~0.1cm²/V-s                                                                                                               | 85 |

| Figure 5.9: Output characteristics for a 120 $\mu$ m/15 $\mu$ m device, $t_{dielectric} \sim 5000 \mbox{\normalfont\AA}$ (  | μ  |

| ~0.1cm²/V-s)                                                                                                                | 86 |

| Figure 5.10: Output Characteristics of OFET on Si/100nm SiO <sub>2</sub> stack, showing                                     | J  |

| similar characteristics to printed FET at equivalent fields                                                                 | 86 |

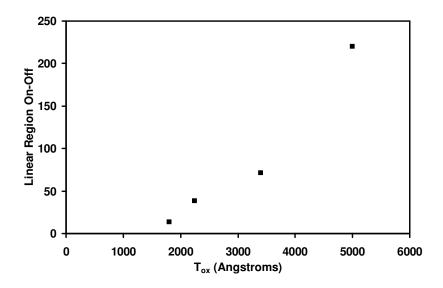

| Figure 5.11: Variation in on-off ratio (in linear regime, at low S/D bias, to ensu                                          | re |

| uniform gate leakage) with dielectric thickness                                                                             | 87 |

| Figure 6.1: Process flow for formation of printed FETs                                                                      | 92 |

| Figure 6.2: Effect of jetting parameters on thickness of inkjetted dielectric for                                           |    |

| two PVP solution concentrations                                                                                             | 93 |

| Figure 6.3: Optical micrographs of low overlap gate stack structure and final                     |

|---------------------------------------------------------------------------------------------------|

| printed FET94                                                                                     |

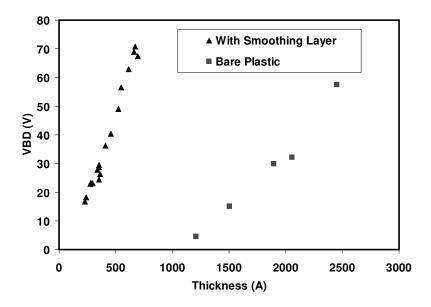

| Figure 6.4: Breakdown voltages of capacitors made on smoothed plastic and                         |

| bare plastic95                                                                                    |

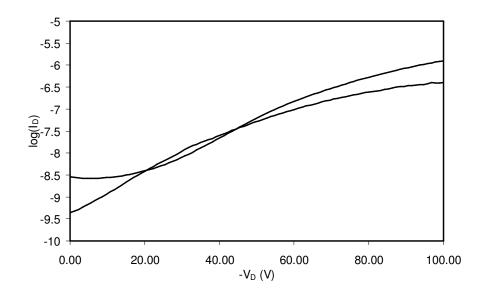

| Figure 6.5: Transfer characteristics for a 26 $\mu$ m/27 $\mu$ m device with $t_{ox}$ ~45nm96     |

| Figure 6.6: Output characteristics for a 26 $\mu$ m/27 $\mu$ m device with $t_{ox}$ ~45nm ( $\mu$ |

| =0.051cm <sup>2</sup> /V-s)                                                                       |

| Figure 6.7: Transfer characteristics for a 75 $\mu$ m/10 $\mu$ m device with $t_{ox}$ ~25nm97     |

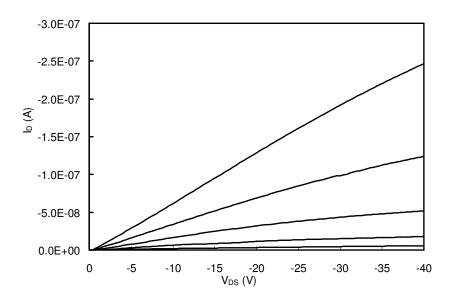

| Figure 6.8: Output characteristics for a 75μm/10μm device with t <sub>ox</sub> ~25nm (μ           |

| =0.043cm <sup>2</sup> /V-s)98                                                                     |

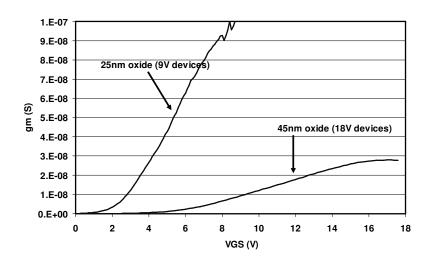

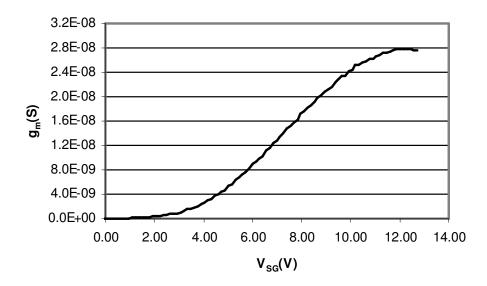

| Figure 6.9: Transconductance as a function of gate voltage demonstrating that                     |

| sufficient electric fields are achieved99                                                         |

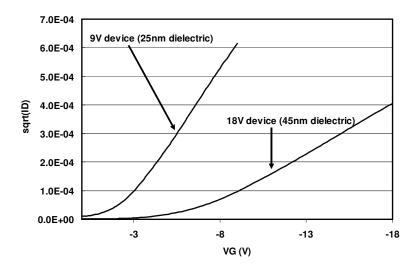

| Figure 6.10: Square root drain current vs. gate voltage showing excellent                         |

| square law behavior99                                                                             |

| Figure 6.11: Normalized transconductance measured at 4.4MV/cm vs. channel                         |

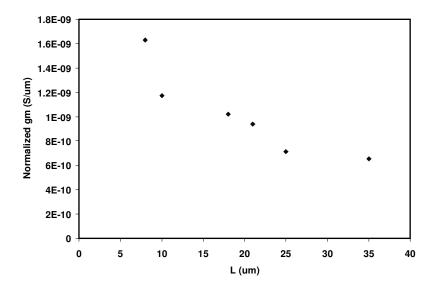

| length demonstrating the predicted inverse linear behavior100                                     |

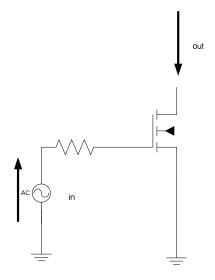

| Figure 7.1: Common source circuit configuration used to measure $f_t$ and $f_{\text{max}}$ . 104  |

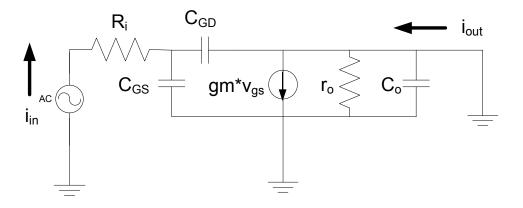

| Figure 7.2: Small signal model of a common source circuit                                         |

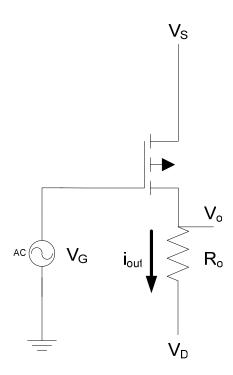

| Figure 7.3: Common source measurement circuit used to measure f <sub>t</sub> 108                  |

| Figure 7.4: Transconductance as a function of gate bias for the device used                       |

| to measure f <sub>t</sub> 109                                                                     |

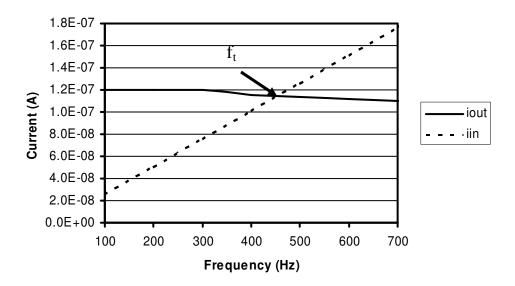

| Figure 7.5: i <sub>out</sub> and i <sub>in</sub> as a function of frequency110                    |

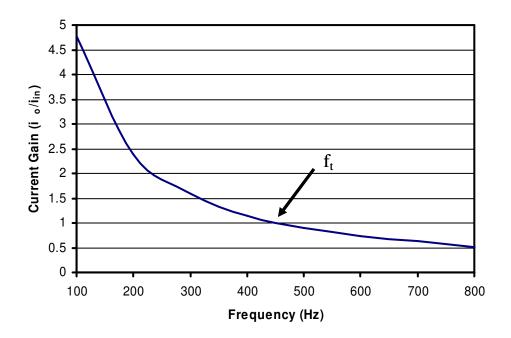

| Figure 7.6: Current gain (i₀/i₀) as a function of frequency111                                    |

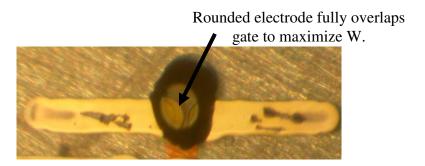

| Figure 7.7: Transistor used to measure f <sub>t</sub> showing the electrode overlap113            |

|                                                                                                   |

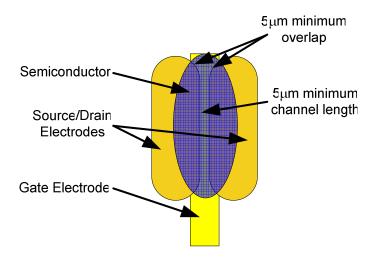

| Figure 7.8: Example of an optimized device structure with minimum overlap                         |

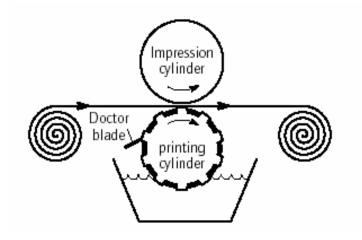

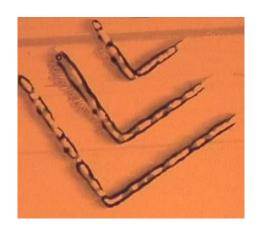

| Figure 8.1: Roll-to-roll gravure printer                                               | .117  |

|----------------------------------------------------------------------------------------|-------|

| Figure 8.2: Ink I, group A ink, forms a discontinuous film                             | .120  |

| Figure 8.3: Ink IV, group B ink, forms a continuous film, but the edges are            |       |

| deformed and there is a high degree of spreading                                       | .120  |

| Figure 8.4: Gravure printed $\alpha$ -terpineol ink showing the distortion that occurs | \$    |

| before drying                                                                          | .121  |

| Figure 8.5: Gravure printed nanoparticle ink with chloroform/anisole solvent           |       |

| showing the well-defined line                                                          | .122  |

| Figure 8.6: Gravure printed nanoparticle ink with chloroform/anisole solvent           |       |

| showing the poor multi-directional printing                                            | .122  |

| Figure 8.7: Leaching and branching effect for toluene and $\alpha$ -terpineol,         |       |

| and chloroform and anisole                                                             | .123  |

| Figure 8.8: Gravure printed ink consisting of nanoparticle gold, chloroform,           |       |

| and PMMA binder                                                                        | .124  |

| Figure 8.9: Gravure printed nanoparticle ink with silver powder                        | .124  |

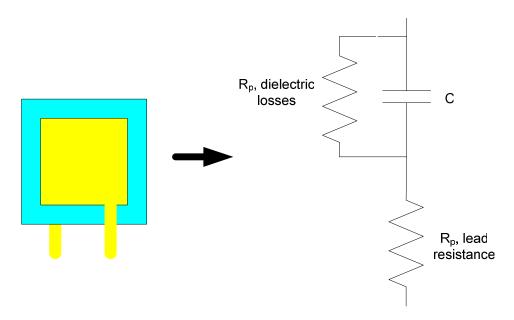

| Figure A.1: Model of losses in an inductor                                             | .138  |

| Figure A.2: Model of losses in a capacitor                                             | . 139 |

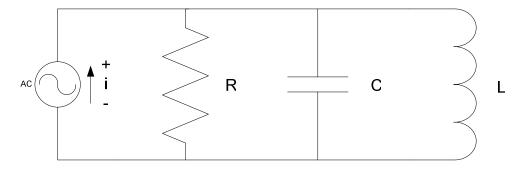

| Figure A.3: Electrical schematic of a tank circuit                                     | . 140 |

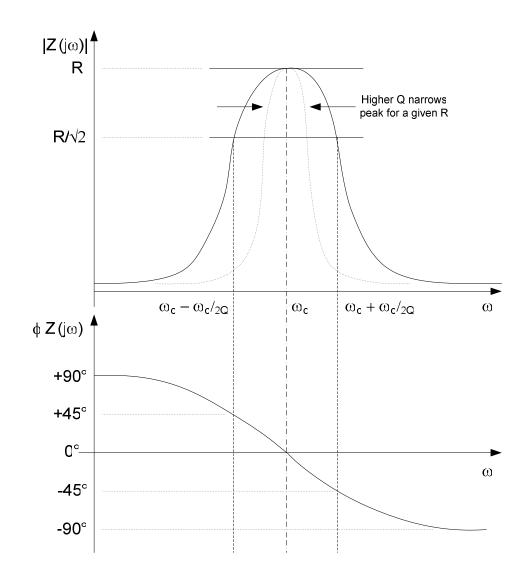

| Figure A.4: Impedance and phase as a function of frequency for a tank circui           | t     |

|                                                                                        | .142  |

# **List of Tables**

| Table 3.1: Summary of the performance range of the three main ink families | 43    |

|----------------------------------------------------------------------------|-------|

| Table 4.1: Experimental parameters                                         | 67    |

| Table 4.2: Comparison of best transistors at 160°C and 180°C anneals       | 70    |

| Table 4.3: Thickness vs. number of drops                                   | 71    |

| Table 4.4: Results of distilled hexane rinse experiment                    | 72    |

| Table 8.1: Summary of conductor ink formulation                            | .119  |

| Table 8.2: Summary of spreading for various inks                           | .121  |

| Table B.1: Properties of chemicals used in nanoparticle synthesis          | . 149 |

| Table B.2: Surfactant ratios for Au nanoparticles                          | .149  |

| Table D.1: Properties of chemicals used in pentacene precursor synthesis   | . 165 |

| Table D.2: Chemical ratios in pentacene precursor synthesis                | . 165 |

## Chapter 1

## **Introduction to Low Cost Printed Electronics**

Low cost printed electronics have gained a great deal of interest over the past 5 years because of their promise to greatly reduce the cost of many electronic applications. In particular these applications include radio frequency identification (RFID) tags, displays, printed circuit boards (PCB)/keypads, chemical sensors, etc. In the end, if the cost goals are achieved, the ubiquity of these electronics would be greatly increased. However, before manufacturing these products, basic research must be carried out to determine feasibility and performance limitations. Therefore it is the goal of this work to determine the best materials, develop printing processes for those materials, and investigate performance limitations. This chapter describes the reasons why printing has such a large cost advantage over conventional silicon processing and describes some of the applications in greater detail. The methodology, motivation, and organization of this entire work are also discussed.

#### 1.1 Introduction

Many engineering achievements have helped fundamentally alter the world. The development of the printing press in Europe by Johann Gutenberg is one such achievement that many historians credit for bringing the European continent out of the medieval period [1]. The printing press created the ability to quickly mass produce information in the form of books, journals, periodicals, etc. By quickly replicating this

information, the spread of knowledge was enhanced. This greater sharing of knowledge thus helped end the medieval period in Europe.

Although an interesting historical development in itself, more relevant to this work is the manner in which the printing press quickly replicates text. For example, a master pattern with protruding text is dipped in ink. The wet master is then pressed onto the media, usually paper, and the copy is made. This is repeated many times until the desired number of copies are made [2].

In many ways the idea of the printing press represents an ideal method of manufacturing as there are numerous cost advantages. Once the master pattern is made, there are only small incremental costs resulting from the use of paper and ink. Furthermore, there is very little waste generated within the printing process and this has two distinct advantages. First, since the only ink used is the ink deposited onto the paper, there is little cost associated with the use of excess ink. Second, because there is little excess ink, there is little excess material that requires costly disposal. Since there is no major disposal this process is also friendlier to the environment. Along with the previous cost advantages there is also an inherent advantage of the high throughput associated with printing. The master pattern does take some time to fabricate, however once made it can replicate copies many times.

Furthermore, by printing multiple layers of different colors, color copies can be fabricated. These additional steps have all the advantages associated with the advantages of the first layer as described. Because this process of making color copies involves the "addition" of multiple layers and does not involve removal of any previously added material, this type of manufacturing is quite often termed "all additive."

In a cost analysis of printing, the product's price includes the materials, the depreciation of the equipment, and labor, which is minimal as long as the process is automated. As long as throughput is high the depreciation is minimal per product, thus a printing system is among the cheapest manufacturing methods available. If these principals could be applied to semiconductor manufacturing processes, prices for these products could be minimized as well.

#### 1.2 Silicon's Shortfalls

In many aspects silicon processing uses many of the ideas in printing to achieve low costs and rapid manufacturing, however it is in the differences where it is rather difficult to reduce costs further. Some of the high costs associated with silicon processing include energy, the limited availability of area, and the pattern transfer or photolithography itself. Energy costs remain high because of the high temperatures needed and the energy required to purify and keep the processing clean.

Another area where silicon processing is fundamentally different from printing is in the fact that there is a limited area on which the circuits can be "printed." In contemporary printing of newspapers or magazines the printing is done in reel-to-reel processes. In these processes the paper is rolled down the line as the graphics are printed onto it. Because of this large area, continuous printing is done; both result in reduced costs. But in silicon processing the method is different. The cost of processing is mainly dictated by the number of processing steps required for each wafer. Furthermore, because the size of a silicon wafer is limited due to mechanical stability and equipment size/cost restrictions, it is difficult to achieve cheaper dies by scaling up the wafers. Thus it is

difficult to lower the cost per die except through reduction of feature size (i.e. scaling creates more die per wafer) [3].

In the final issue, pattern transfer or photolithography, silicon processing benefits from its similarities to printing. But, similar to the previous issues described, it suffers from its differences. Photolithography is a modern term associated with silicon integrated circuit manufacturing that refers to the use of light imaging in photopolymers and pattern transfer [4]. This particular technology could be considered to be at the intersection of pattern transfer and printing. The printing is done when the pattern on a mask is transferred using light onto a light sensitive polymer. Upon development of the polymer the polymer now acts as a mask to transfer its pattern to the layers beneath it. The imaging of the polymer can be done almost simultaneously over the whole wafer. Thus silicon processing can achieve relatively high manufacturing speeds. At the same time, though, the pattern transfer adds costs and time to the process. This is because each layer is added as a full sheet (thin film). This is a time consuming and costly process in itself, sometimes requiring high vacuum. Then, the film is etched using the photopolymer as a mask. Thus material, often >90%, is wasted. This adds costs from both the excess material and disposal of the waste material.

There are also many steps involved with "printing" the image onto the photoresist. These include 1) spinning the photoresist, 2) exposing the photoresist, 3) developing the photoresist, 4) etching the underlying material, and 5) striping the photoresist. Overall, there are many more steps required in silicon processing - to both "print" the image in the photoresist and transfer the pattern into the underlying material - than there is in all-additive printing process that simply has one step: 1) print. Because

cost generally scales with the number of steps, there is a substantial cost savings in direct printing, and, if silicon processing could more purely resemble printing, it could achieve much lower costs.

### 1.3 The Cost Solution: All-Printed Electronics

If electronics manufacturing could shift to a process resembling more of a purely printed technique, then the cost could be greatly reduced. This is essentially true for all the reasons mentioned above. This printing process would be all-additive; thus material cost and waste disposal are reduced. Furthermore there would be no need for expensive equipment needed for vacuum processing, photoimaging, etching, etc.

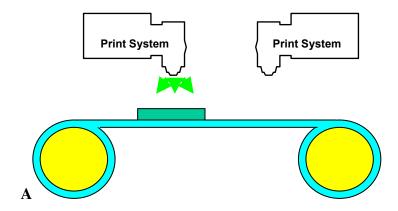

Additionally, a larger sized substrate could be processed since both the substrate and the printers are not limited in size as silicon equipment and wafers are. An even bigger advantage is the fact that the use of plastic would facilitate reel-to-reel printing so throughput could be increased further (Figure 1.1).

Figure 1.1: Example of an all-additive, reel-to-reel, printed manufacturing process.

The first layer is deposited (A) and the substrate is reeled to the next station (B)

where the next layer is deposited (C).

Since plastic substrates are used the temperatures are limited to <200°C. Also clean rooms are no longer needed since individual printers could be encased in clean boxes. These two issues would reduce energy costs.

However, it is important to note that in order to facilitate this technology only certain materials can be used. In particular, these materials must be solution processable so that they can be printed and they must have processing temperatures <200°C so that they are compatible with the plastic substrates. Because of these two properties, quite often these materials have inferior performance than those in silicon manufacturing [5].

Furthermore there are also performance reductions because the minimum feature sizes are much larger as a result of the limitations of the printers. For example, submicron all-additive printing has yet to be realized. Because the minimum feature size is larger, printed electronics have a higher cost per logic function than silicon.

As a result of the material and printer limitations, low-cost electronics have substantially reduced performance, but as a tradeoff, offer substantially reduced cost per unit area than silicon electronics.

## 1.4 Applications

Electronics made using printing techniques would have greatly reduced cost over conventional silicon electronics, and, as a result these electronics are typically referred to as low-cost printed electronics. Despite the reduction in performance, there are still a wide variety of applications where low-cost printed electronics could be used. Some of the more obvious applications include displays [6], radio frequency identification (RFID) tags [7], smart cards, electronic sensors [8], packaging, and printed circuit boards (PCB)/key pads used in cell phones, remote controls, car keys, etc. The common element among all these applications is the fact that all of these applications do not need either ultra fast circuitry or ultra dense circuitry like that in CPUs used today.

RFID tags represent the largest technical challenge to low cost electronics. The idea behind this technology is that product level bar codes could be replaced by active circuit tags as long as the tags are cheap enough; <2 cents per tag. The advantage to this is that mundane tasks such as inventory and checkout could be greatly sped up and labor

would be minimized. Other features such as real time pricing updates could also be implemented easily.

This application represents the largest technical challenge to this field of research because the circuit speed required is relatively high. The circuit speed is dictated by the communication frequency and, given the preferred reading distance along with the available band/power output (mandated by the FCC), RFID will likely occur at 13.56 MHz [9, 10]. On chip clock frequencies for such circuits are in the range of 200 kHz. Few low cost semiconductors can achieve a mobility of 1 cm²/V-s or greater, but the transistors made with these materials will likely result in devices with transition frequencies in the range of approximately 500 kHz. Thus this technology tests the current limits of what is achievable with low cost electronics. As a result, quite often the required specifications for RFID are quoted without loss of generality because if a device will work in an RFID application, it will function in most other low cost applications.

Low cost display manufacturing seeks to capitalize on the fact that low cost manufacturing can easily print over large areas with a sparse number of transistors. Because of this ability, low cost, printed manufacturing may be able to reduce the cost of active matrix displays by 10-200X. On-state performance is a non-issue since several hundred kHz is more than adequate for these applications. Note that off-state performance will be an issue, however, since the "blackness" of black is typically determined by leakage current through pixel transistors.

There are also a wide variety of applications that spin-off from the previously mentioned applications. For example, the passive component technologies developed (inductors, capacitors, and interconnects) could be used in PCB/key pad applications

such as cell phones, remote controls, car keys, etc. By using low cost manufacturing, the use of expensive photolithography to make PCB's could be eliminated and the throughput could be greatly increased.

Another application is to use printing to make electronic noses. Electronic noses use a variety of active devices as sensing elements. When exposed to a chemical or chemicals, each element produces a unique response. By using pattern recognition algorithms to decode the response from a matrix of sensors, the chemical or chemicals can be identified. Typically, the larger the matrix, the better the sensitivity and the higher the guarantee of correct recognition. Typically these sensors are made as individual components and connected to a central processor. This is quite costly - thousands of dollars to tens of thousands of dollars. By using printing techniques and integrating the sensor onto a single chip, these low cost manufacturing methods seek to reduce the cost well below \$1. With such low costs these devices could be made much more available and sensors could be used to detect spoiled food or contaminated air.

## 1.5 Methodology

While the promise of these low cost applications has generated great interest over the last five years, in general, there have been few extensive studies detailing the requirements of the materials, equipment, and printing techniques needed for these electronic applications. It is necessary to view these items as a whole since all are interdependent. To date many of the studies have focused on a particular material or material set. As a result, these studies have not addressed many of the integration

problems with these electronic materials and, furthermore, they have been unable to provide a larger picture detailing the performance limitations of the materials.

Therefore, the purpose of this work is to create a more extensive study that will form the starting point for the realization of fully-printed low-cost electronic systems. It will identify materials that may be suitable for low cost printed electronics, and it will study and develop different printing methods available for these materials. Furthermore, this work will identify any limits to this technology and project what performance may actually be achievable.

## 1.6 Organization

Chapter 2 begins with an introduction to inkjet technology and contrasts it with another competing manufacturing technology - gravure printing. It goes on to identify the components important to an inkjet printer. It motivates the need for a custom built inkjet testbed and describes the design methodology of the testbed. A discussion of inkjet dispensing theory is also discussed in this chapter.

Chapter 3 begins by motivating the need for high quality interconnect materials in the context of passive components. It then identifies a gold nanoparticle ink as the best candidate for inkjetting high performance interconnects. Printing techniques are developed for this material as well as polyimide and PVP dielectric materials. Finally, these techniques are used to create high performance multilevel interconnects and passive components.

Chapter 4 discusses organic semiconductors and printing techniques to optimize performance. It begins by introducing electron transport in the context of molecular

structure. Printable organic semiconductor candidates are identified and, finally, the optimization schemes for a pentacene precursor are described.

Chapter 5 develops a baseline all-printed transistor technology based on the work in the previous chapters. The performance limitations of these devices are discussed. These limitations are addressed and solved in Chapter 6.

Chapter 7 discusses  $f_t$  and  $f_{max}$  and the frequency performance requirements for RFID circuits. It goes on to develop a method to characterize the frequency performance,  $f_t$ , of the optimized devices made in Chapter 6.

In Chapter 8, gravure printing is discussed along with its advantages over inkjet printing. Some initial experiments are described and the need for an ink tailored for gravure printing, versus inkjet, is discussed. Future work is also described in this chapter. Finally, the conclusions are in Chapter 9.

## Chapter 2

# Inkjet Printing Technology and Experimental Testbed

Two of the most promising printing technologies for fabricating low-cost printed electronics include inkjet printing and gravure printing. Inkjet printing is a well known technology that makes use of individual droplet dispensers. Inkjet heads are composed of several dispensers that deposit individual drops to form patterns. By properly placing each drop, coherent patterns can be made on a substrate. Gravure printing is a lesser known technology that uses a cylinder with an etched pattern on it. Ink is deposited into the pattern on the cylinder and when the cylinder is rolled over a substrate, the pattern on the cylinder is transferred to the substrate. Because of the fundamental methods of pattern transfer, each technology offers distinct advantages over the other. In general, inkjet printing offers both easier and more flexible alignment capabilities because of its ability to deposit individual drops onto any location on the substrate. Gravure printing is more difficult to align patterns because the whole cylinder must be properly aligned to the underlying substrate. This is cumbersome due to the size of the cylinder and is exacerbated by flexible substrates that can distort. Gravure printing, however, offers much better throughput since the whole pattern can be transferred in a single roll of the cylinder.

Given these general characteristics, this chapter provides an in-depth discussion of inkjet technology along with a discussion of its advantages over gravure printing. An in-depth discussion of gravure printing is in Chapter 8. Also, the development of an inkjet testbed for use in the experiments in this thesis is discussed in this chapter.

## 2.1 Inkjet Technology Background

While inkjet printing can offer higher throughput then conventional silicon processing, it generally has much less throughput than gravure printing. This is due to the serial nature of the printing dispenser - each drop much be deposited in sequential fashion. There are many on going efforts, however, to increase throughput by using arrays of dispensers numbering in the hundreds [1, 2]. The typical commercial printer (for example the Epson Stylus) has 100-300 dispensers and thus does not have throughput issues given its application (household printing). However, it does not have precise droplet volumes and thus this makes its use in low-cost electronics printing impractical.

Despite this throughput disadvantage, inkjet printing offers several advantages that gravure printing does not. Inkjet printing offers extremely flexible pattern making abilities. This is because inkjet printing is fundamentally an all-additive process where the pattern is made from the commands given to the printer from the computer. Since the computer's commands are generated from the software, updates can be made in real-time to the patterns. This is in contrast to gravure printing where the patterns are engraved into rollers.

Inkjet printing also offers real-time dynamic alignment [3]. Alignment is critical when printing multiple patterns or when printing onto a prepatterned substrate. Generally speaking, alignment with inkjet can be done by using a camera with a fixed distance from the printer's dispenser. For example, a drop can be dispensed onto the substrate and the amount that the drop is offset from a desired location can be input into the computer. The

computer then re-zeros the position taking into account this offset. X and Y offsets can be found using this technique while rotational error requires two desired locations (i.e. grids) on the substrate. How rotational alignment is accomplished is discussed in greater detail later in this chapter.

The concept of alignment can be split to include global alignment across an entire substrate and local alignment on an individual transistor. Both types of alignment can be programmed into the software such that the pattern placement is altered to correctly place the current layer over the already deposited layer. This software update is essentiality the same as altering a pattern.

While global alignment is necessary to print multiple layer patterns, local alignment is particularly applicable to low cost electronics when cheap substrates made of plastic are used. Most plastic substrates in the experiments in this work were susceptible to considerable shrinking (5 – 500µm) [3]. As a result, local alignment is quite useful while printing onto these substrates, especially in critical areas such as electrode overlap in transistors. For example, if the electrodes do not overlap the gate, the transistor will not function at all, while if there is too much overlap, the added parasitic capacitance will degrade frequency response. An example of how this might occur is the following. If a substrate underwent a certain amount of distortion such that two transistors were closer together than planned for in the original pattern then, without local alignment, the printer would print the source and drain electrodes on one transistor correctly, but on the other transistor, one electrode would have too much overlap over the gate while the other electrode would not even cover the gate. This error can be corrected by printing the last 50 µm using local alignment where a camera images the gate. Then,

since the distance from the camera to the dispenser is known, the last 50µm of the electrodes could be printed with equal overlap over the gate. This ensures an optimally performing device, and, in this manner, local alignment would correct these alignment errors resulting from substrate distortion.

It is also valuable to point out how local alignment and real-time pattern altering can become a very useful tool in combination. For instance, given the above example where local alignment is used to print source and drain electrodes, the pattern for the interconnects used to connect the electrodes will not be identical on every chip. As a result, the pattern will need to be modified to fabricate the correct dimensions of the interconnects. With the proper software this can all be accomplished in real time.

## 2.2 General Inkjet Printer Components

The main components of most inkjet printers are generally the same. They include the printer dispenser (head), the ink reservoir and ink delivery path, the motion stages, and the driver and controllers for the head and stages. The two most common types of inkjet dispensers available today are piezoelectric crystal dispensers (piezoheads), and thermoelectric dispensers (bubble jet heads). Fluid ejection occurs in a similar manner in both cases; a pressure wave is created in an ink chamber that expels the ink through an orifice. However, the dispensers differ in the manner that they create the pressure wave and how the pressure wave causes ejection.

#### 2.2.1 Bubble Jet Dispensers

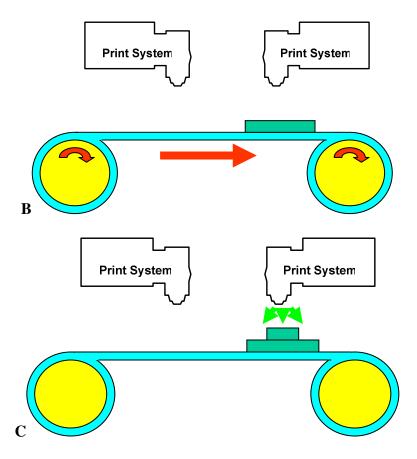

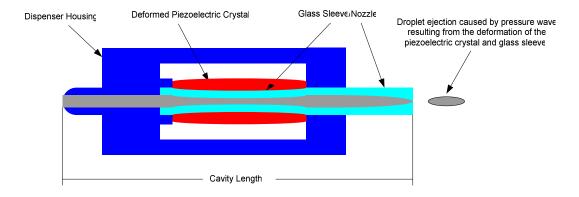

The bubble jet type dispenser (Figure 2.1) uses a heater in the form of a resister to super heat the ink to its spinodalian limit, 312° C for water, whereby the ink boils and a bubble is created. The bubble is created in the time span of microseconds and causes pressures typically >1 MPa that cause droplet ejection [4, 5]. The advantage to this type of technology is its simplicity to manufacture, which translates into lower cost. The heaters are typically made from polysilicon or platinum and thus these dispensers can be made using conventional silicon and MEMs processing techniques. Due to the low cost, the heads can also be disposable such as those made by Hewlett-Packard. The added advantage to this disposability is that if the head clogs due to dust or debris it can be discarded. This is a concern in all print heads since orifice diameters are typically in the range of 100μm down to as low as 5μm.

Figure 2.1: Cross section of a typical bubble jet dispenser showing how droplet generation occurs.

However, the drawback to these heads is that this heating step poses concern to low-cost electronics printing where the inks are usually temperature sensitive. For example, gold nanoparticles that sinter at ~120°C have been demonstrated for use in interconnects [6]. Since they sinter at such low temperatures, the heat required to boil the

ink causes the nanoparticles to sinter onto the heater. After a thick enough metal layer is sintered onto the heater, the heater's resistance drops, and it no longer produces high enough temperatures to cause droplet ejection.

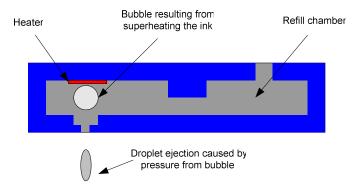

#### 2.2.2 Piezoelectric Dispensers

Piezoelectric heads (Figure 2.2) work through use of a piezoelectric crystal. By applying a potential across the crystal, the crystal deforms or contracts, and, if properly oriented onto the chamber of a dispenser, it will create a pressure wave that expels ink droplets [7]. This ejection process will be described in-depth later in this chapter. The main disadvantage to this technology it that it is harder to integrate the crystal using conventional silicon processing and thus these types of heads are usually more costly. Because of this, they are almost never disposable and thus in the event of a clog the head will need to be replaced. Most important, though, is that ink degradation is no longer a concern since the pressure wave is generated strictly through mechanical deformation. For this reason, the inkjet testbed designed for all of the experiments in this work uses a piezo head.

Figure 2.2: Cross section of a piezoelectric inkjet dispenser showing how droplet ejection occurs.

# 2.3 Experimental Inkjet Testbed and Specifications

Commercial inkjet printers are not adequate for low-cost electronics fabrication for a variety of reasons. First, the ink deposition volume can vary as much as 50%, while electronics fabrication require minimal variation (<10-20%) to ensure that the smallest possible lines and gaps can be repeatably and precisely made. Second, structure size is inherently coupled to the precision of the motion stages and most commercial printers do not have adequate precision for electronics fabrication. Third, most commercial printers are made for water based inks and as a result, cheap plastics are used for the ink delivery pathways. Because of this, the ink delivery pathways in commercial printers are not resistant to aggressive solvents such as acetone or toluene. This is critical since many of the inks used in low-cost electronics fabrication require these as solvents. Due to these inadequacies an inkjet testbed had to be designed and assembled to carry out the low-cost electronics experiments for this thesis.

Most commercial printers are designed so that the printer's head moves while the substrate stays stationary. This is practical since the motors needed to move the head can be small because the heads are lightweight, and it is also difficult to move the entire sheet of paper. However, for the purposes of a testbed that will print onto a 6 inch radius (the maximum size of easily available wafers) or smaller, it is much simpler to design a system with a stationary head and a moving substrate. Thus the testbed was designed so that the ink dispenser remains fixed while the substrate below it moves on X and Y translation stages. The testbed also incorporates a rotational stage so that proper alignment can be achieved on prepatterned substrates.

## 2.3.1 Motion Stages

The motion stages used have  $1.3\mu m$  precision in the X and Y directions, and 0.5 arc minutes of angular precision. Despite this precision, the drop placement varies  $10\mu m$  or more due to drift in flight. However, because of the precision of the motion stages, it is ensured that the drop placement is limited to the precision of the dispenser and not the stages.

## 2.3.2 Dispenser and Dispensing Theory

In order to fabricate low-cost electronics a dispenser must be able to print lines <100μm, it must be tunable to a wide range of inks, and it must be able to print aggressive solvents. Inkjet dispensers manufactured by MicroFab fit these criteria. The orifice diameter is 100μm which allows them to print the requisite ~100μm sized lines. These dispensers can operate in continuous or drop-on-on demand mode. Continuous mode is where the drops are continuously ejected at a given frequency while drop-on-demand mode is where each individual droplet ejection event is specified. The voltage waveform used to drive these dispensers can be tuned and thus these dispensers can be used with a wide variety of inks with different fluid properties. This is discussed more indepth below. These dispensers are also made of tiny glass tubes (D~500μm and L~0.75 cm) with a piezocrystal epoxied around the circumference of the tube. The epoxy is semi resistant to solvents and thus as long as the solvents only contact the inside of the tube (minimal exposure to the outside is tolerated) as in normal operating conditions, the head is resistant to most solvents encountered in the inks.

A generic head schematic for piezoelectric inkjet dispensers is shown in Figure 2.2. These dispensers use either a unipolar or bipolar voltage waveform to inkjet the material. The bipolar wave is shown in Figure 2.3. The proper model describing droplet ejection for this type of waveform was first described by Bogy and Talke [7]. This was the first published analysis that assumed fluid compression in the dispenser. By allowing this assumption, they were able to use linear acoustics theory to describe the wave propagation phenomena. The theory of ejection is as follows (Figure 2.4). Upon initial contraction of the piezo crystal, two negative pressure waves propagate in opposite directions away from the crystal located at the center of the dispenser. When one pressure wave reaches the end of the dispenser at the supply side it reflects and changes to a positive pressure wave. Conversely, when the pressure wave hits the closed end or dispenser side it reflects with the same sign or negative pressure. After time L/C where L

Figure 2.3: Bipolar voltage waveform.

meet at the center. This is the optimum time at which to apply the negative voltage step because the contraction will annihilate the reflected negative pressure wave and double the reflected positive pressure wave. This optimum time is referred to as the dwell time as shown in Figure 2.3. After another L/2C this positive pressure wave reaches the tip and fluid is ejected out. Thus the total time from initial contraction to ejection is 3L/2C. As the pressure wave continues, it is again reflected at the tip and then again at the open end. At this point is has changed sign to a negative pressure wave and will reach the middle of the dispenser at 3L/C after initial contraction. This negative pressure wave can be damped out with the final positive contraction so that it will not cause further ejections from the tip. The time between the last negative contraction and this final positive contraction is known as the echo time (Figure 2.3).

In practice the dwell time optimization is carried out by changing the dwell time with a fixed strobe delay until the drops are farthest from the dispenser (the drops are viewed using a strobe LED, a camera, and a monitor). At this point the drops are moving with the fastest velocity for any voltage and thus the optimal driving condition is achieved. As previously stated, the echo time or the length of the negative pulse parameter helps to damp out some of the pressure waves in the dispenser. This non-critical parameter is usually about twice as long as the dwell time, but is not necessary for higher viscosity materials.

All of the parameters (positive and negative voltage, dwell time, echo time, and ramp rates) of the voltage waveform can be adjusted. As a result these heads have a high degree of tunability, which allows them to work well with a variety of different inks with

Figure 2.4: Illustration of pressure wave propagation in a piezoelectric dispenser.

varying fluid properties. In conjunction with the relatively high resistance to solvents, this makes these heads an ideal choice for the testbed. However, it is important to note that although extremely flexible they are not optimized for any particular material. The heads are made of glass and each solvent wets the orifice differently. As a result accurate pressure control is required for each ink so that the proper meniscus is created. The way this is accomplished is discussed in the pressure control section. Ideally, though, in an industrial application, the dispensers will be tailored for the specific ink they print and the same pressure can be maintained on all the dispensers. This can be done by using the proper metal that has the proper surface energy and thus achieves the desired wetability. Furthermore, some heads need to withstand higher temperatures when substrate heating is used. The reasons for substrate heating are discussed in Chapter 3. Despite these drawbacks, the flexibility of these MicroFab dispensers allows them to work well in a research environment.

#### 2.3.3 Pressure and Meniscus Control

In most commercial inkjet systems pressure control is not a critical issue since the specifications on droplet variation are relaxed. Furthermore, the inks are mostly water-based, having similar wetting properties, and thus the heads are inherently easier to design since there are less types of inks to design for. The reservoir usually sits directly above the head and pressure is maintained via gravity and wetting. In these MicroFab heads a variety of different inks are used with different wetting properties. Therefore, pressure control at the tip of the dispenser is crucial in order to maintain the proper meniscus for jetting. If the meniscus wets the bottom of the dispenser (higher pressure)

the required jetting voltage will be too high. On the other hand, if the meniscus is to far into the head (lower pressure), then there is a risk the fluid will get siphoned out of the head and back into the reservoir.

In this system (Figure 2.5) the reservoir sits ~4 inches below the dispenser and thus a small positive pressure is required for meniscus formation. The pressure is controlled by a pressure regulator and two needle valves. The pressure regulator controls pressure from 2psi to 40psi and therefore serves as a coarse pressure control. It also dampens out pressure variations in the house nitrogen line. One needle valve is used to bleed off the extra 2 psi of pressure and is kept fully open while printing. The other needle valve acts a fine pressure control. With this setup pressure can be controlled down to less than one inch of water.

Figure 2.5: Side view of the pressure control system and the ink delivery pathway.

#### 2.3.4 Solvent Delivery Path

As previously stated, commercial printers are not required to be solvent resistant since they mainly use water based inks. Also, since the reservoir is directly above the head, the delivery path is usually integrated into the head itself. In this testbed (Figure 2.5) the reservoir sits ~1-2 feet away from the head. This allows height adjustment of the reservoir along with easier removal for cleaning and replacement. The Teflon delivery path consists of a machined Teflon reservoir connected to 2 ½ feet of 0.062" Teflon tubing. The tubing and reservoir are connected using adapters. The reservoir rests about 4 inches below the dispenser therefore a positive pressure must be maintained in the reservoir in order to keep the proper meniscus in the dispensing device.

It is crucial to keep the delivery path ultra clean since particles can cause adverse jetting and even clogs. To clean the delivery path the Teflon tubing is flushed with 20 mL of acetone filtered though a 0.2 µm membrane while the Teflon reservoir is sonicated in acetone for at least 10 minutes. After sonication, the reservoir is rinsed with filtered acetone. To ensure that this delivery path is clean, the tubing is connected to the dispenser and flushed with more filtered acetone. Then the reservoir is connected and filled with 2 mL of filtered acetone. The nitrogen pressure line is connected and turned on so that the acetone flushes completely through the system. The stream emanating from the dispenser is monitored to make sure there are no obstructions. This process ensures that the full delivery path is free of particles before filling with ink. Note that there is no filter in the delivery path once the ink is in the reservoir. The absence of a filter ensures

that the pressure at the inkjet head is accurately controlled by the pressure applied to the reservoir (since the pressure loss downstream of the filter is avoided).

#### 2.3.5 Substrate Chuck

Commercial inkjet printers only require the ability to print onto paper, but this testbed requires the ability to print onto a variety of substrates including plastic and silicon substrates. Furthermore, the testbed requires a way to control substrate heating. The reasons for this will be discussed in Chapter 3. In order to provide vacuum and substrate heating with relatively good uniformity a hot chuck was used that was controlled by a custom-built temperature controller.

#### 2.3.6 Software and Computer Interface

The main control program for the testbed is run off of a PC. Its basic function is to synchronize the motion of the stages with the deposition of droplets. It also incorporates some added features such as wafer alignment, printing onto multiple dies with the same pattern, and pattern file input. The PC interfaces with the MicroFab driver via a serial cable. The Printer program sends digital signals through the serial cable to the driver specifying the parameters of the voltage waveform and when to fire. The driver for the translation stages fits into a PCI slot in the PC and the PCI card driver sends digital signals to the stepper motor drivers specifying direction, number of steps, speed, and acceleration. A schematic of these electrical connections is shown in Figure 2.6.

Figure 2.6: Top view schematic of the inkjet testbed electrical connections.

The pattern file inputs are read in as text files and assume the dispenser is in drop on demand mode. These files specify individual Cartesian coordinates for each drop location and the number of drops for that location. A separate program generates these text files from specified shape functions including lines, squares, rectangles, inductors, etc. All functions allow the user to tune the parameters including dimensions, drop spacing, wait state, number of layers, etc. The reason for the wait state will be discussed later.

## 2.3.7 Alignment Algorithm

The testbed uses an automated alignment routine to align the printer head to the substrate. This routine works by dispensing a drop in two grids in opposite corners of the substrate. Each grid is then viewed in a camera where the user types in the offset of each drop relative to the center of each grid. The software then calculates the offset and centers the wafer. The algorithm in this software works by first calculating the x offset as follows:

$$x_{error} = \frac{(x_1 + x_2)}{2}$$

Eqn (2.1)

where  $x_1$  and  $x_2$  represent the offsets of each drop in their respective grid. Similarly the y offset is calculated as:

$$y_{error} = \frac{(y_1 + y_2)}{2}$$

Eqn (2.2)

where  $y_1$  and  $y_2$  represent the offsets of each drop in their respective grid. For both of these errors, the sign of the error will indicate the direction of substrate movement; a positive error will mean the substrate must move positive with respect to the head and vice versa for the negative.

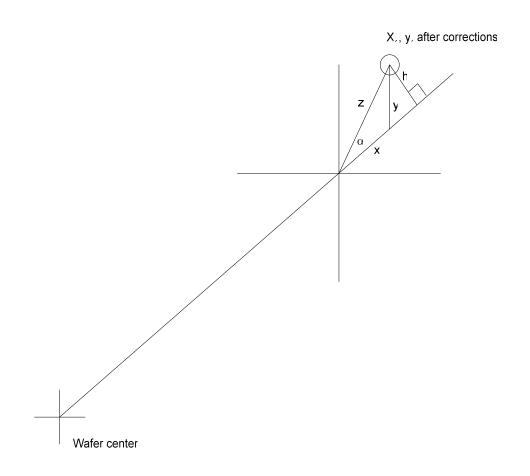

After correcting for these errors, only the rotational error remains. This is calculated by finding the distance between the corrected offset coordinate and the line passing through the center of the grid as shown in Figure 2.7. This is found using the formula:

$$h = z * \sin(\alpha)$$

Eqn (2.3)

where z is a straight forward calculation using the Pythagorean Theorem,  $x_1$ , and  $y_1$ :

$$z = \sqrt{{x_1}^2 + {y_1}^2}$$

Eqn (2.4)

However,  $\alpha$  requires more calculation.  $\alpha$  can be found based on the law of cosines if x and y are known as shown in Figure 2.7:

$$\alpha = \cos^{-1} \left\{ \frac{y^2 - x^2 - z^2}{-2xz} \right\}$$

Eqn (2.5)

The length of x and y are found as follows. For x:

$$|x| = \sqrt{\left\{ \left( \frac{y_g}{x_g} * x_1 \right)^2 + x_1^2 \right\}}$$

Eqn (2.6)

where  $y_g$  is the y coordinate of the grid on the wafer and similarly  $x_g$  is the x coordinate of the grid on the wafer. Thus  $y_g/x_g$  is the slope of the line passing though the center of the wafer and center of the grid. The length of y is:

$$|y| = \left| y_1 - \frac{y_g}{x_g} * x_1 \right|$$

Eqn (2.7)

Therefore  $\alpha$  is found and h can be calculated. In order to convert h to radians, h is divided by the radius of the circle passing through the center of the grid:

$$r = \sqrt{(x_g^2 + y_g^2)}$$

Eqn (2.8)

The direction of rotation is found based on the sign of Equation 2.7 inside the absolute value parenthesis. If this is less than 0 then the rotation is clockwise and vice versa for a value larger than zero.

After calculating these errors the stages move to the current zero position, then the stages move the corrected offset, and finally the position is re-zeroed. Thus, the dispenser is at the center of the pattern on the substrate. Overall, this alignment allows accuracy to less than 5µm based on the user's ability to accurately determine the position of the drop

in the grids. However, in practice the accuracy is limited to  $5\mu m$  to  $10~\mu m$  due to variations in drop placement.

Figure 2.7: Alignment geometry.

## 2.3.8 Support Structure

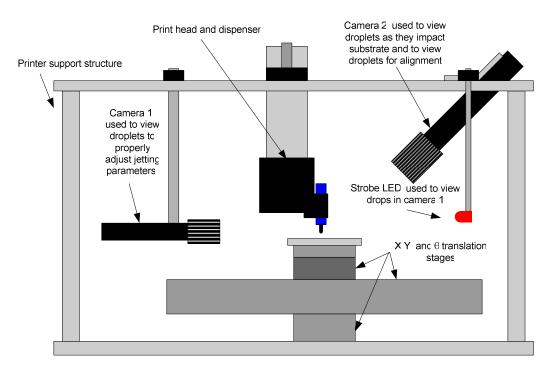

The support structure of the inkjet testbed supports both the print head dispenser and the optics system and was custom machined. The optics system includes a camera for use with the alignment function and in-situ viewing of the drops during printing and another camera for droplet calibration (Figure 2.8).

Figure 2.8: Side view schematic of the inkjet testbed support structure and optics system.

The printer is enclosed in an acrylic box. This box allows the user to purge the oxygen and creates a nitrogen atmosphere with less than ~10 ppm oxygen. This is required for various electronic materials that are sensitive to oxygen or for performing anneals that require an oxygen free atmosphere. The testbed with the acrylic enclosure is shown in Figure 2.9.

## 2.4 Conclusions

In comparison to gravure printing inkjet printing has much less throughput, but has advantages in both pattern making flexibility and ease of alignment. Patterns can be changed as well as aligned in real-time by updating the pattern software. Most

commercial printers have an array of dispensers to speed up throughput since the printing speed is limited by the serial nature of inkjet dispensers. Dispenser technologies include both bubble jet and piezoelectric. Bubble jet dispensers work by generation of a pressure wave via rapid boiling while piezoelectric heads generate the pressure wave via a mechanical deformation.

Figure 2.9: Custom built inkjet testbed.

Commercially available printers are deficient in their droplet placement accuracy, motion precision, solvent compatibility, and substrate accommodations for use in electronics fabrication. As a result a custom testbed was designed and assembled that had all the necessary characteristics. For the testbed designed here, it uses one dispenser for each material. Because of the stringent requirements in electronics fabrication, careful attention and design was carried out for each of the subsystems. This includes the choice

of motion stages, the choice of dispenser, pressure system design, ink delivery path design, the choice of substrate chuck, software design, and alignment routine design.

The piezoelectric dispensers from MicroFab facilitate the printing of  $\sim 100 \mu m$  lines, are compatible with a variety of inks, and are resistant to aggressive solvents. The functional theory of these dispensers is based on the original work by Bogy and Talke and relies on the assumption that the fluid in the dispenser is compressible.

The printer includes an acrylic box to allow printing in a nitrogen atmosphere. It will be used in the majority of experiments in the following chapters to fabricate printed interconnects, capacitors, inductors, and transistors.

# **Chapter 3**

# **Inkjet Processing Techniques and Passive Components**

# 3.1 Introduction to Passive Components