# A Power/Area Optimal Approach to VLSI Signal Processing

Dejan Marko Markovic

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2006-65 http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-65.html

May 18, 2006

Copyright © 2006, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### A Power/Area Optimal Approach to VLSI Signal Processing

by

Dejan Marko Marković

Eng. (University of Belgrade, Yugoslavia) 1998 M.S. (University of California, Berkeley) 2000

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION  $\qquad \qquad \text{of the} \\ \text{UNIVERSITY OF CALIFORNIA, BERKELEY}$

Committee in charge:

Professor Robert W. Brodersen, Co-chair

Professor Borivoje Nikolić, Co-chair

Professor Jan M. Rabaey

Professor Paul K. Wright

Spring 2006

| The dissertation of Dejan Marko M | arković is approved |

|-----------------------------------|---------------------|

|                                   |                     |

| Co-chair                          | Dav                 |

| Co-chair                          | Da                  |

|                                   | Da                  |

|                                   | Da                  |

University of California, Berkeley

Spring 2006

### A Power/Area Optimal Approach to VLSI Signal Processing

Copyright 2006

by

Dejan Marko Marković

#### Abstract

A Power/Area Optimal Approach to VLSI Signal Processing

by

Dejan Marko Marković

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Robert W. Brodersen, Co-chair

Professor Borivoje Nikolić, Co-chair

The complexity of integrated circuits (ICs) in wireless communication devices has been steadily increasing to support more functionality and new ideas from information theory. Computational requirements can be quite drastic, especially in multi-antenna (MIMO) communication systems which use multi-dimensional signal processing algorithms. The required increase in computational efficiency in MIMO systems can be far greater than the improvements provided by scaling of IC technology alone.

This work will present a methodology for power/area efficient ASIC realization of signal processing algorithms for wireless communications, taking into account unique features of scaled technology such as leakage power and process variation. A sensitiv-

ity based optimization framework will be applied to multiple layers of design abstrac-

tion: circuits, micro-architecture, and macro-architecture. The proposed approach

enables power and area optimizations across the boundary of algorithm, architecture,

and circuits, which is essential for creating globally optimal designs.

In wireless baseband chip realization, the design cycle traditionally requires reen-

tering data at various abstraction levels, thus constraining the implementation choices

and increasing time-to-market. An approach using a unified design description for

algorithm verification and architecture exploration is also presented. The proposed

graphical block-based design entry and retargetable design flow provide the ability to

track technology features in the process of architectural selection.

As a proof of concept, the design methodology will be demonstrated on a wide-

band  $4 \times 4$  MIMO channel decoupling through singular value decomposition. The

computational throughput of 70GOPS was implemented with 0.5 million gates at a

100MHz clock and 385mV supply, dissipating 34mW of power. The chip achieves a

power efficiency of 2.1 GOPS/mW in just  $3.5 mm^2$  in a standard 90 nm CMOS process.

Professor Robert W. Brodersen

Dissertation Committee Co-chair

Professor Borivoje Nikolić

Dissertation Committee Co-chair

To my parents

# Contents

| Lis           | st of | Figures                                     | vi  |

|---------------|-------|---------------------------------------------|-----|

| Lis           | st of | Tables                                      | xi  |

| $\mathbf{Ac}$ | knov  | vledgments                                  | xii |

| 1             | Intr  | oduction                                    | 1   |

|               | 1.1   | Power-Limited Design                        | 2   |

|               |       | 1.1.1 Architectural Considerations          | 4   |

|               |       | 1.1.2 Design Productivity                   | 6   |

|               | 1.2   | MIMO Technology                             | 7   |

|               | 1.3   | Overview of Previous Work                   | 8   |

|               | 1.4   | Dissertation Outline                        | 11  |

| <b>2</b>      | Sens  | sitivity-Based Optimization                 | 15  |

|               | 2.1   | Optimization Principle                      | 15  |

|               | 2.2   | Layered Optimization Approach               | 18  |

| 3             | Circ  | uit Optimization                            | 21  |

|               | 3.1   | Technology Calibration                      | 22  |

|               |       | 3.1.1 Delay Model                           | 22  |

|               |       | 3.1.2 Energy Model                          | 24  |

|               | 3.2   | Optimization Approach                       | 26  |

|               |       | 3.2.1 Reference Point                       | 26  |

|               |       | 3.2.2 Optimization Procedure                | 27  |

|               | 3.3   | Sensitivity Analysis                        | 27  |

|               |       | 3.3.1 Sensitivity to Gate Size, W           | 29  |

|               |       | 3.3.2 Sensitivity to Supply Voltage, Vdd    | 30  |

|               |       | 3.3.3 Sensitivity to Threshold Voltage, Vth | 31  |

|               | 3.4   | Optimization Examples                       | 32  |

*CONTENTS* iii

|   |      | 3.4.1   | Inverter Chain                       | 32         |

|---|------|---------|--------------------------------------|------------|

|   |      | 3.4.2   | Memory Decoder                       | 36         |

|   |      | 3.4.3   | Tree Adder                           | 40         |

|   |      | 3.4.4   | Takeaway Points                      | 44         |

|   |      | 3.4.5   | Multi-Variable Optimization          | 46         |

| 4 | Mic  | ro-Arc  | chitectural Optimization             | 49         |

|   | 4.1  | Choos   | ing Optimal Circuit Topology         | 50         |

|   |      | 4.1.1   | Combinational Logic                  | 55         |

|   |      | 4.1.2   | Low-Swing Clocking                   | 57         |

|   | 4.2  | Paralle | elism vs. Pipelining                 | 64         |

|   |      | 4.2.1   | Optimal Leakage and Switching Energy | 66         |

|   |      | 4.2.2   | Optimal Level of Parallelism         | 67         |

|   |      | 4.2.3   | Optimal Vdd and Vth                  | 69         |

|   | 4.3  | Time-   | Multiplexing                         | 73         |

|   | 4.4  | Energy  | y-Area Trade-Off                     | 74         |

| 5 | Sign | nal Pro | ocessing Techniques                  | <b>7</b> 8 |

|   | 5.1  |         | Stream Interleaving                  | 79         |

|   | 5.2  |         | g                                    | 82         |

|   | 5.3  | Loop 1  | Retiming                             | 84         |

|   |      | 5.3.1   | Hierarchical Loop Retiming           | 85         |

|   |      | 5.3.2   | CPU Runtime Considerations           | 86         |

|   | 5.4  | Delaye  | ed Iteration                         | 88         |

|   | 5.5  |         | ive Square Rooting and Division      | 88         |

|   |      | 5.5.1   | Error Dynamics                       | 90         |

|   |      | 5.5.2   | Initial Condition                    | 91         |

| 6 | Tax  | onomy   | of MIMO Algorithms                   | 94         |

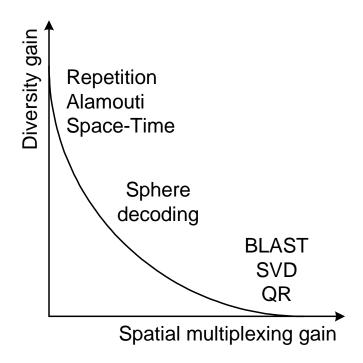

|   | 6.1  | Divers  | sity vs. Spatial Multiplexing        | 94         |

|   |      | 6.1.1   | Diversity Gain                       | 95         |

|   |      | 6.1.2   | Spatial Multiplexing Gain            | 96         |

|   |      | 6.1.3   | Optimal Trade-Off Curve              | 97         |

|   | 6.2  | Divers  | sity Algorithms                      | 97         |

|   |      | 6.2.1   | Repetition Scheme                    | 98         |

|   |      | 6.2.2   | Alamouti Scheme                      | 99         |

|   |      | 6.2.3   | Space-Time Coding                    | .00        |

|   | 6.3  | Spatia  |                                      | 100        |

|   |      | 6.3.1   |                                      | 01         |

|   |      | 6.3.2   | SVD                                  | 105        |

|   |      | 6.3.3   | QR Decomposition                     | 106        |

|   | 6.4  | Unifie  | d Algorithms                         | 107        |

CONTENTS

|    |       | 6.4.1 Sphere Decoding                                  | 107          |

|----|-------|--------------------------------------------------------|--------------|

|    | 6.5   | Survey of VLSI Implementations                         | 109          |

| 7  | CAI   | D Methodology and Flow                                 | 112          |

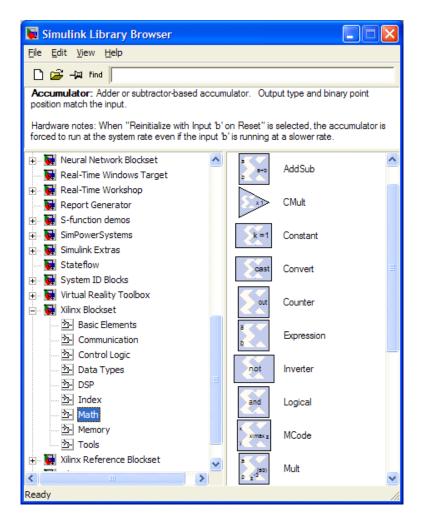

|    | 7.1   | Simulink Design Environment                            | 113          |

|    | ,     | 7.1.1 Design Description                               | 115          |

|    |       | 7.1.2 Functional Verification                          | 116          |

|    |       | 7.1.3 Word-length Optimization                         | 117          |

|    | 7.2   | Characterization Methodology                           | 119          |

|    | • • • | 7.2.1 Power Estimation                                 | 120          |

|    |       | 7.2.2 Area Estimation                                  | 121          |

|    | 7.3   | "Chip-in-a-Day" Design Flow                            | 122          |

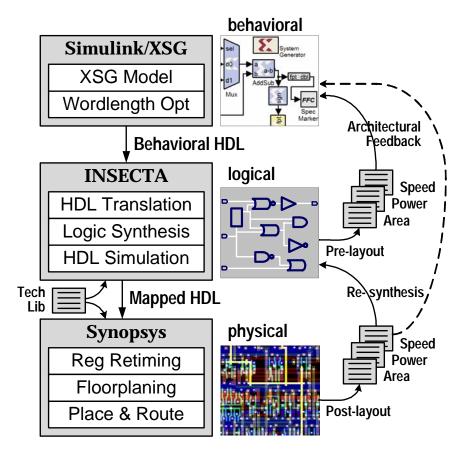

|    |       | 7.3.1 INSECTA                                          | 123          |

|    |       | 7.3.2 Chip Synthesis                                   | 125          |

|    | 7.4   | Design Example: Iterative Square Rooting               | 127          |

| 0  | Dani  | in Francis 4 × 4 CVD                                   | 195          |

| 8  |       | ign Example: 4 × 4 SVD                                 | 137          |

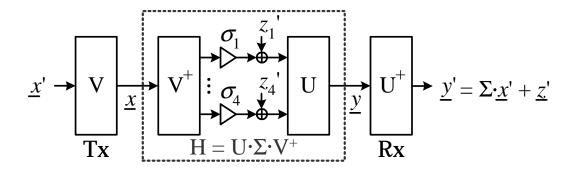

|    | 8.1   | MIMO System Model                                      | 137<br>139   |

|    | 8.2   | SVD: Signal Processing View                            | 139 $139$    |

|    |       | 8.2.2 Estimation of V matrix                           | 139<br>141   |

|    | 0.2   |                                                        | $141 \\ 142$ |

|    | 8.3   | SVD: Circuit Perspective                               | 142 $143$    |

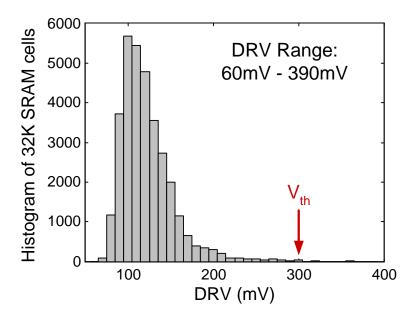

|    |       | 8.3.1 Voltage Scaling Limit: SRAM Memory               | 143<br>144   |

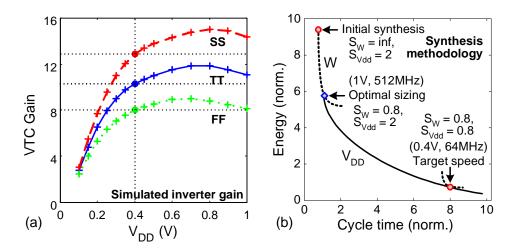

|    | 0.4   | 8.3.2 Optimal Design at Scaled Vdd                     |              |

|    | 8.4   | Optimizing VLSI Architecture                           | 146          |

|    |       | 8.4.1 Architecture for Eigen-mode Decomposition        | 148          |

|    |       | 8.4.2 Architecture for Grahm-Schmidt Orthogonalization | 151          |

|    | 0 5   | 8.4.3 Routing: Memory as a MUX                         | 152          |

|    | 8.5   | Estimates from Synthesis                               | 153          |

|    |       | 8.5.1 Timing and Power                                 | 153          |

|    |       | 8.5.2 Study of Energy and Area Efficiency              | 154          |

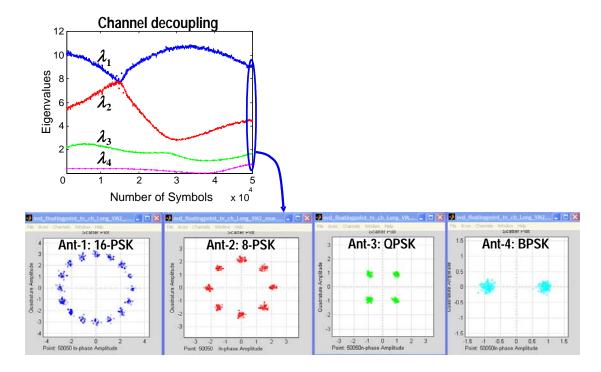

| 9  | Exp   | erimental Verification                                 | 158          |

|    | 9.1   | Test Chip                                              | 158          |

|    |       | 9.1.1 Eigen-mode Decomposition Core                    | 159          |

|    |       | 9.1.2 On-Chip Level Converter                          | 160          |

|    | 9.2   | Experimental Setup                                     | 161          |

|    | 9.3   | Measured Results                                       | 163          |

| 10 | Con   | clusion                                                | 168          |

|    |       | Research Contributions                                 | 169          |

|    |       | Future Work                                            | 172          |

| CONTENTS   | I |

|------------|---|

| CONTIDITIO | V |

| Bibliography                             | 174 |

|------------------------------------------|-----|

| A Chip Synthesis & Test  A.1 CPU Runtime |     |

# List of Figures

| 1.1 | Architectural choices for wireless baseband chip design: Microproces-        |    |

|-----|------------------------------------------------------------------------------|----|

| 1.0 | sors, Programmable DSPs, Direct-mapped logic                                 | 4  |

| 1.2 | Wireless technology today: 802.11a WLAN transceiver chip                     | 6  |

| 1.3 | Future wireless technology: Multi-antenna (MIMO) communication.              | 8  |

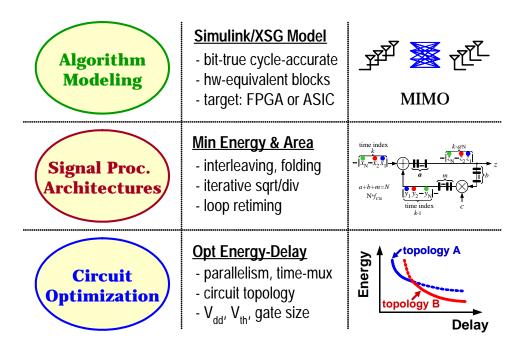

| 1.4 | Layered optimization approach                                                | 9  |

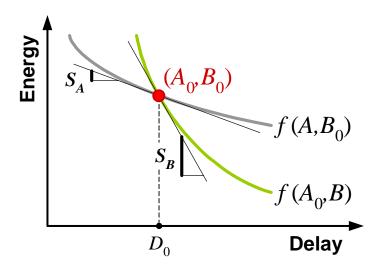

| 2.1 | Illustration of Energy-Delay sensitivity                                     | 16 |

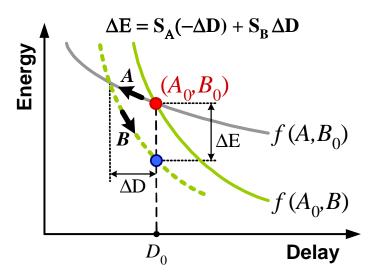

| 2.2 | Process of balancing sensitivities                                           | 17 |

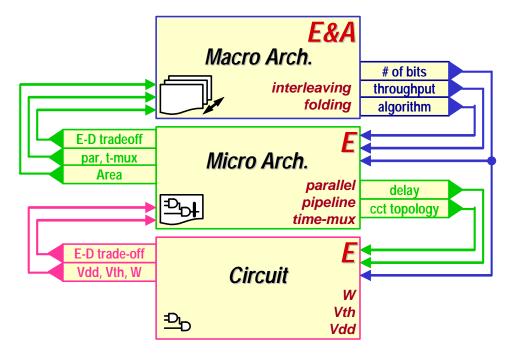

| 2.3 | Block diagram illustrating various abstraction layers in the optimiza-       |    |

|     | tion. Energy is the objective function at the circuit and micro-architectura | al |

|     | layers, while achieving proper energy-area trade-off is the objective at     |    |

|     | the macro-architectural layer                                                | 18 |

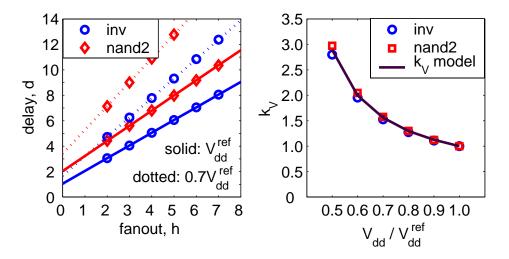

| 3.1 | Delay vs. fanout and supply                                                  | 24 |

| 3.2 | Delay profile in an inverter chain after sizing optimization: a) fixed, b)   |    |

|     | variable number of stages.                                                   | 33 |

| 3.3 | Per-stage supply optimization of an inverter chain with variable num-        |    |

|     | ber of stages: a) optimal stage supply, b) delay profile                     | 35 |

| 3.4 | Sizing and supply optimization of an inverter chain: a) energy reduc-        |    |

|     | tion vs. delay increment, b) energy-delay sensitivity                        | 36 |

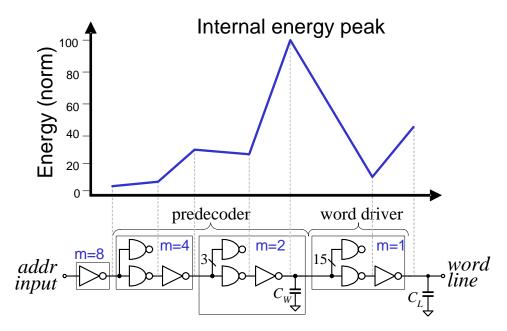

| 3.5 | Critical path of 8/256 wordline SRAM decoder. Energy profile is also         |    |

|     | shown                                                                        | 37 |

| 3.6 | Energy profile in SRAM decoder: a) reference design, b) design with          |    |

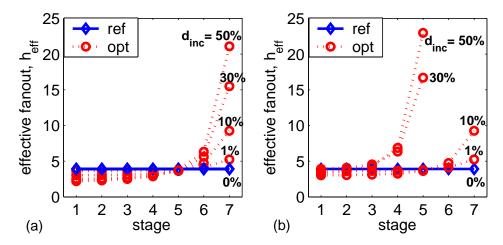

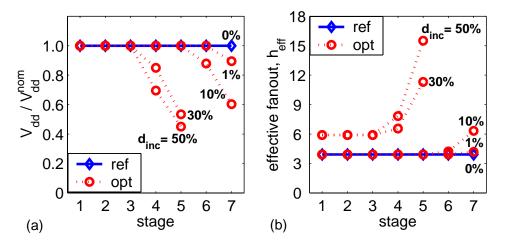

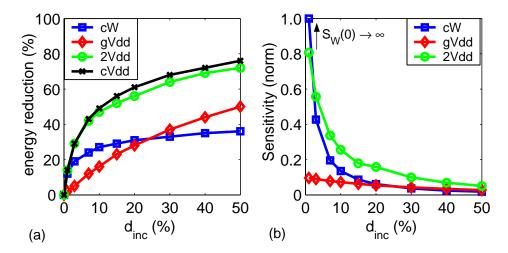

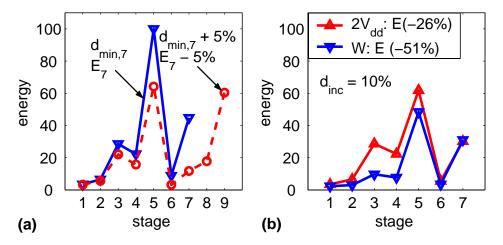

|     | 10% incremental delay. $(W_L = 128, \alpha = 15\%)$                          | 39 |

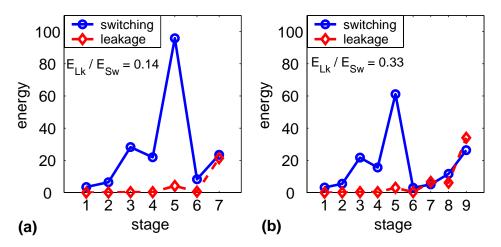

| 3.7 | Energy profile in SRAM decoder with: a) 7 stages, b) 9 stages. Leakage       |    |

|     | energy increases with the number of inactive gates. $(d = d_{min}, W_L =$    |    |

|     | $128, \alpha = 15\%$ )                                                       | 39 |

| 3.8 | Schematic of a 16-bit Kogge-Stone tree adder                                 | 41 |

LIST OF FIGURES vii

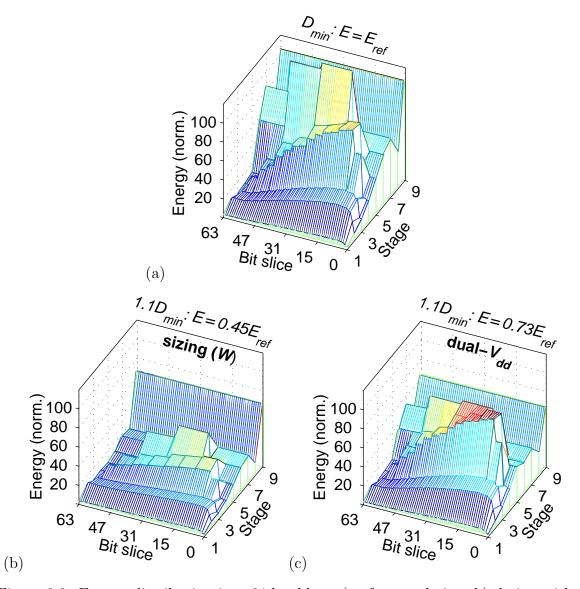

| 3.9        | Energy distribution in a 64-b adder: a) reference design, b) design with 10% additional delay after optimal sizing, c) design with 10% additional delay, after dual- $V_{dd}$ optimization. Each sum output is loaded with $C_{dd} = 22$ input data activity is $10\%$ | 49               |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 3.10       | with $C_L = 32$ , input data activity is 10%                                                                                                                                                                                                                           | 42               |

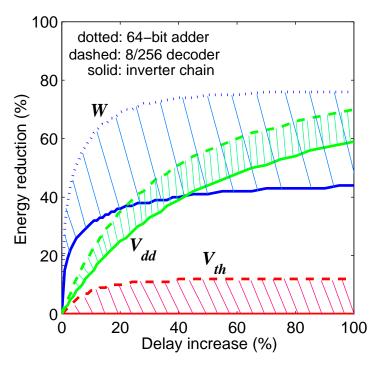

| 3.11       | reduction are shown                                                                                                                                                                                                                                                    | 44<br>45         |

| 3.12       | Optimal energy-delay trade-off in a 64-bit adder after performing $V_{dd} - V_{th} - W$ optimization. Reference is the design sized for minimum delay under $V_{dd}^{max}$ and $V_{th}^{ref}$ . Sensitivity to each of the tuning variables is marked on the graph     | 47               |

| 11         |                                                                                                                                                                                                                                                                        | ξO               |

| 4.1<br>4.2 | Simplified model of one bit-slice of a 64-bit ALU Flip-flops used in implementation of the ALU register in Fig.4.1: (a) high-performance cycle-latch (CL), (b) low-energy static master-slave                                                                          | 50               |

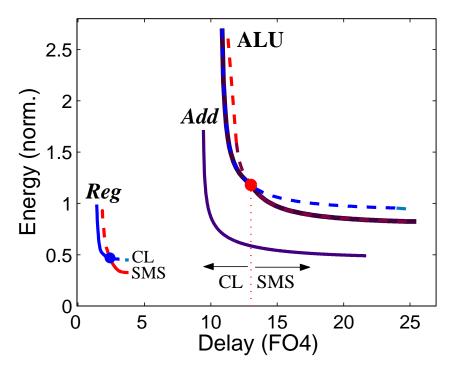

| 4.3        | latch-pair (SMS)                                                                                                                                                                                                                                                       | 51               |

| 4.0        | timization. The dots indicate transition between CL- and SMS-based register                                                                                                                                                                                            | 52               |

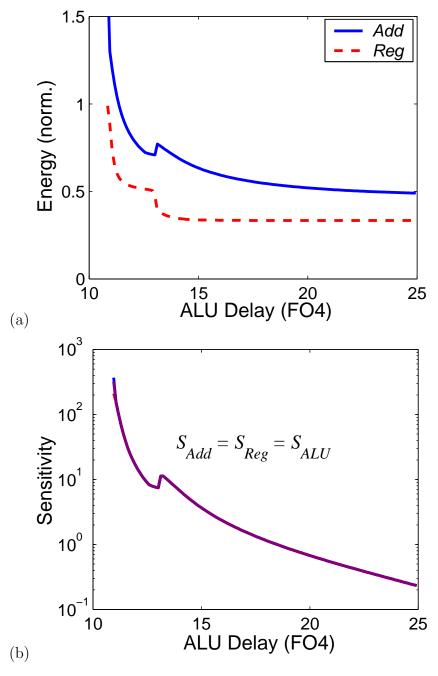

| 4.4        | Plots after optimal sizing and change in register topology. (a) Energy of adder and register when they are combined as the ALU, (b)                                                                                                                                    | 02               |

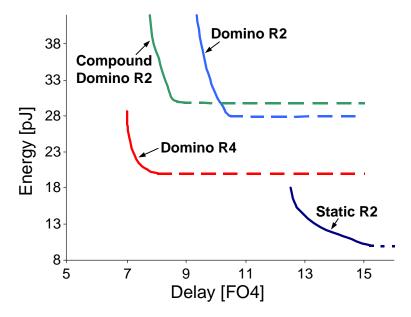

| 4.5        | Corresponding sensitivity of register, adder, and ALU Energy-Delay space in 64-bit CLA adder implemented using domino                                                                                                                                                  | 54<br>5 <i>c</i> |

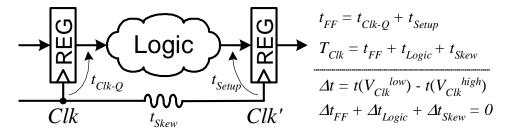

| 4.6        | and static CMOS logic styles (courtesy of R. Zlatanovici) To maintain cycle time $T_{Clk}$ at low- $V_{Clk}$ , logic must absorb increase in                                                                                                                           | 56               |

| 1.0        | flip-flop delay, $\Delta t_{FF}$ , and clock skew, $\Delta t_{Skew}$                                                                                                                                                                                                   | 58               |

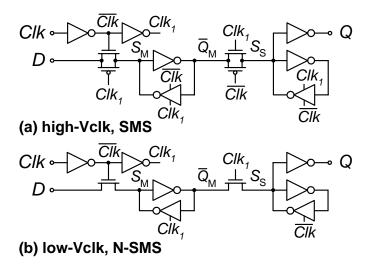

| 4.7        | Flip-flops for non-critical paths: (a) high- $V_{Clk}$ , static master-slave latch-pair (SMS), (b) low- $V_{Clk}$ , NMOS-only clocked SMS (N-SMS)                                                                                                                      | 59               |

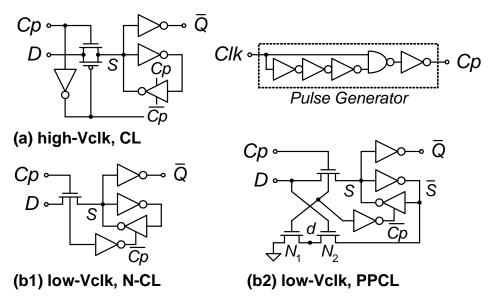

| 4.8        | Flip-flops for performance-critical paths: (a) high- $V_{Clk}$ , cycle-latch (CL), (b1) low- $V_{Clk}$ , NMOS-only clocked cycle-latch (N-CL), (b2) low- $V_{Clk}$ ,                                                                                                   |                  |

| 4.0        | push-pull NMOS-only clocked cycle-latch (PPCL)                                                                                                                                                                                                                         | 60               |

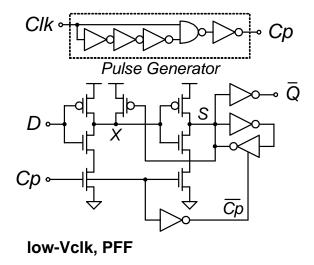

| 4.9        | Pulsed flip-flop (PFF) suitable for low- $V_{Clk}$ operation                                                                                                                                                                                                           | 61               |

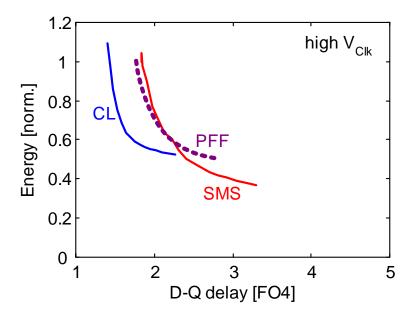

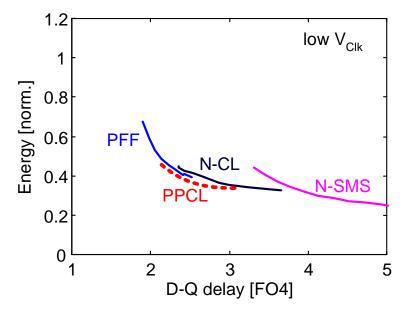

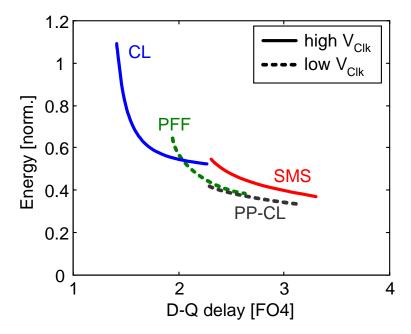

| 4.10       | Energy-Delay space for flip-flops optimized for high- $V_{Clk}$ operation. Preferred high- $V_{Clk}$ flip-flops are CL and SMS                                                                                                                                         | 62               |

| 4.11       | Energy-Delay space for flip-flops optimized for low- $V_{Clk}$ operation. Pre-                                                                                                                                                                                         |                  |

|            | ferred low- $V_{Clk}$ flip-flops are PFF/PPCL and N-SMS. ( $V_{Clk} = 0.7V_{dd}$ )                                                                                                                                                                                     | 62               |

| 4.12       | Low- $V_{Clk}$ flip-flops cannot achieve the top speed of high- $V_{Clk}$ flip-flops,                                                                                                                                                                                  |                  |

|            | but have lower energy at less aggressive delays                                                                                                                                                                                                                        | 63               |

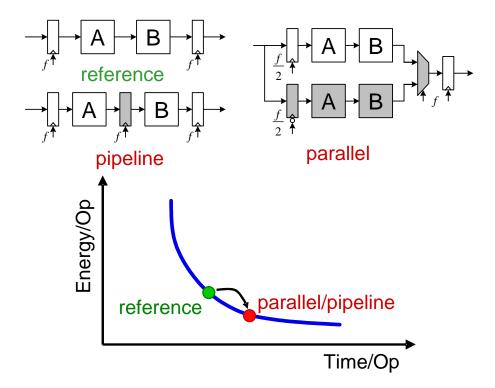

| 4.13       | Parallelism and pipelining relax timing constraints on logic blocks                                                                                                                                                                                                    | 64               |

LIST OF FIGURES viii

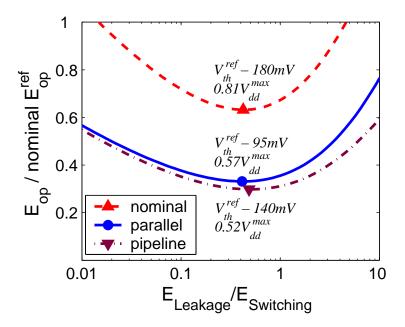

| 4.14       | Energy-per-operation as a function of the leakage-to-switching energy ratio in nominal, parallel, and pipeline designs. All designs operate at                                      |            |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | the throughput of the nominal design sized for minimum delay under $V_{dd}^{max}$ and $V_{th}^{ref}$                                                                                | 66         |

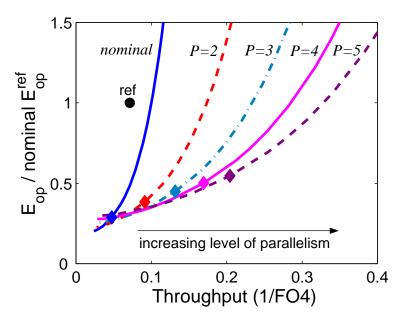

| 4.15       | Energy-per-operation as a function of the clock cycle in energy-efficient                                                                                                           |            |

|            | designs with levels of parallelism from $P=2$ to $P=5$ . Delay and energy penalty due to multiplexers is included. Diamond dots indicate                                            |            |

|            | min EDP, circle indicates nominal design initially sized for minimum                                                                                                                |            |

|            | delay at $V_{dd}^{max}$ , $V_{th}^{ref}$                                                                                                                                            | 68         |

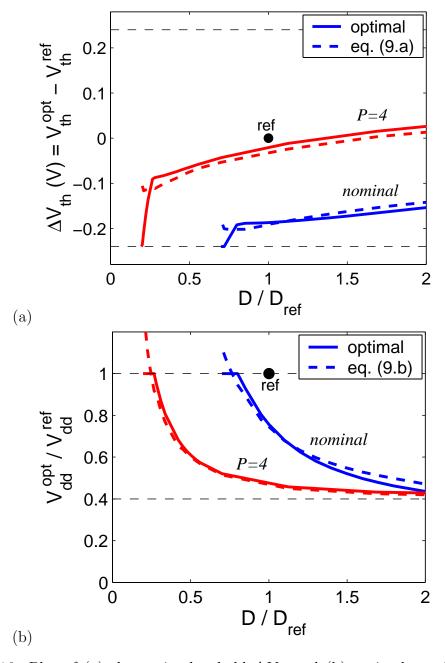

| 4.16       | Plot of (a) change in threshold $\Delta V_{th}$ and (b) optimal supply voltage $V_{dd}^{opt}/V_{dd}^{ref}$ after performing energy-efficient $V_{dd}$ - $V_{th}$ — $W$ optimization |            |

|            | on nominal and parallel-4 designs. Dot represents initial sizing for                                                                                                                |            |

|            | minimum delay at $V_{dd}^{max}$ , $V_{th}^{ref}$                                                                                                                                    | 72         |

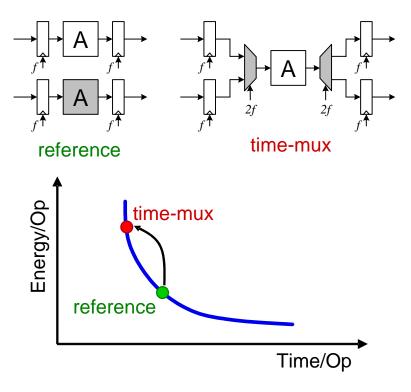

|            | Time-multiplexing tightens timing constraints on logic block $A$                                                                                                                    | 73         |

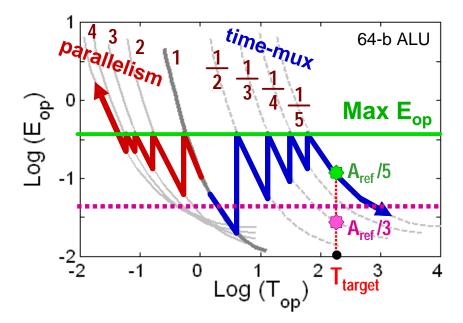

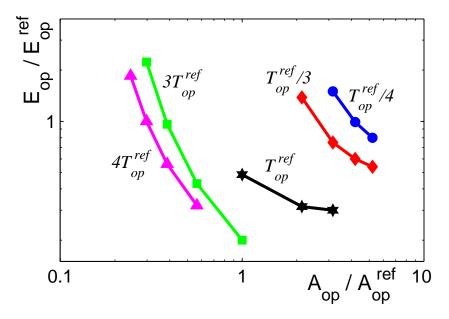

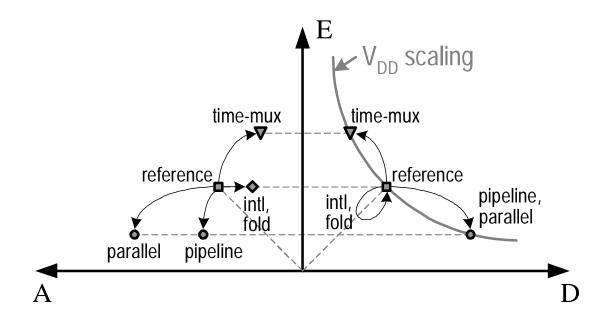

| 4.18       | Energy-delay space for designs with various levels of parallelism and                                                                                                               |            |

|            | time-multiplexing. Desired cycle time $T_{target}$ can be achieved with several architectures that differ in energy and area. Numbers represent                                     |            |

|            | the area of respective architectures                                                                                                                                                | 75         |

| 4.19       |                                                                                                                                                                                     |            |

|            | are normalized to reference architecture optimized for speed under $V_{dd}^{ref}$                                                                                                   |            |

|            | and $V_{th}^{ref}$                                                                                                                                                                  | 76         |

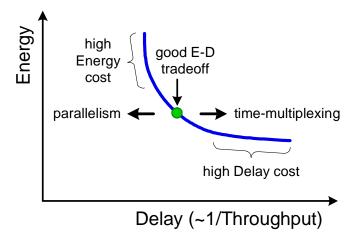

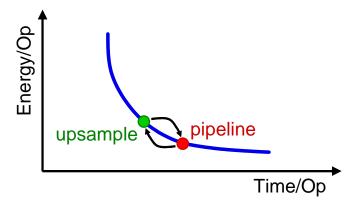

| 5.1        | Energy-delay trade-off in digital circuits                                                                                                                                          | 79         |

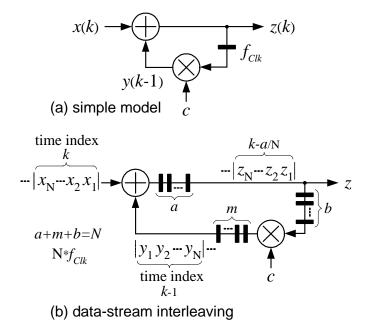

| 5.2        | Concept of data-stream interleaving. (feedback example)                                                                                                                             | 81         |

| 5.3        | Interleaving and Folding are area saving techniques. Timing and en-                                                                                                                 |            |

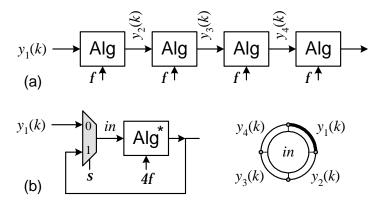

| E 1        | ergy stay approximately the same (neglecting register overhead)                                                                                                                     | 82         |

| 5.4        | Concept of folding: (a) time-serial computation, (b) operation folding. Block $Alg$ performs some algorithmic operation. (star indicates deeper                                     |            |

|            | pipelining)                                                                                                                                                                         | 83         |

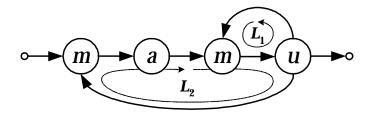

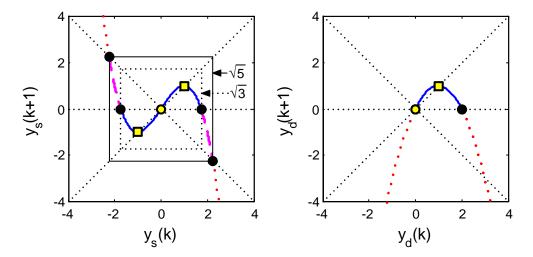

| 5.5        | Data-flow graph model of iterative division. $(m, a, u \text{ indicate latency})$                                                                                                   | 84         |

| 5.6        | Data-flow graph model of an iterative eigen-mode decomposition algo-                                                                                                                |            |

|            | rithm. Iterative division in Fig.5.5 is used. $(m, a, u \text{ indicate latency})$                                                                                                  | 87         |

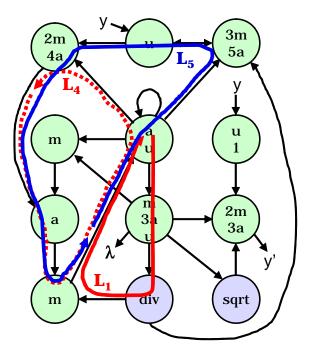

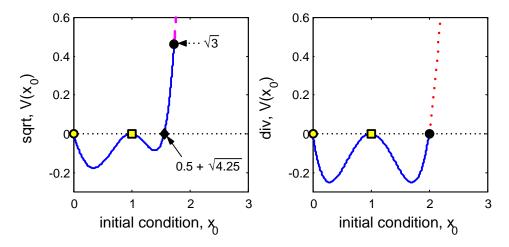

| 5.7        | Convergence region of iterative square rooting and division. (solid line: convergence, dashed line: converging stripes, dotted line: divergence)                                    | 91         |

| 5.8        | Choice of initial condition for decreasing absolute error. ( $V < 0$ : de-                                                                                                          | 91         |

|            | scending error, dotted line: divergence)                                                                                                                                            | 93         |

| 6.1        | Classification of MIMO algorithms in the diversity-multiplexing plane.                                                                                                              | 98         |

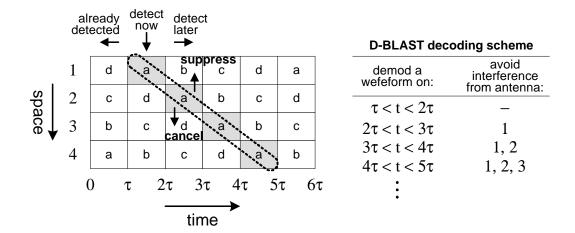

| 6.2        | D-BLAST decoding scheme. Each codeword is partitioned into four                                                                                                                     |            |

|            | blocks and distributed over time and space                                                                                                                                          | 102        |

| 6.3<br>6.4 | Vertical BLAST MIMO communication link                                                                                                                                              | 104<br>105 |

| 0.4        | DECOUPLING OF MILMO CHAINED MILOUGH SYD                                                                                                                                             | TUG        |

LIST OF FIGURES ix

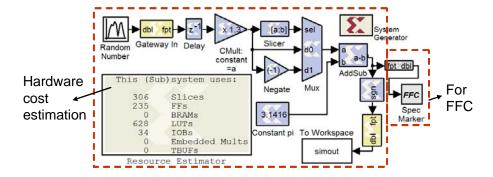

| 7.1  | Simulink environment illustrating XSG block library                                     | 114 |

|------|-----------------------------------------------------------------------------------------|-----|

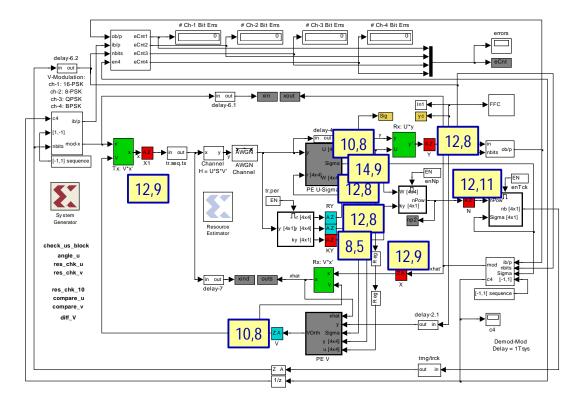

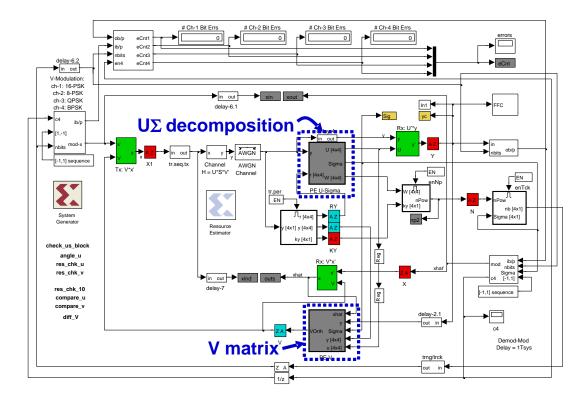

| 7.2  | Example of Simulink design entry: model of a MIMO communication.                        |     |

|      | Numbers indicate total and fractional bits                                              | 115 |

| 7.3  | Example of functional verification in Simulink                                          | 117 |

| 7.4  | Illustration of FFC-enhanced Simulink model, [1]                                        | 118 |

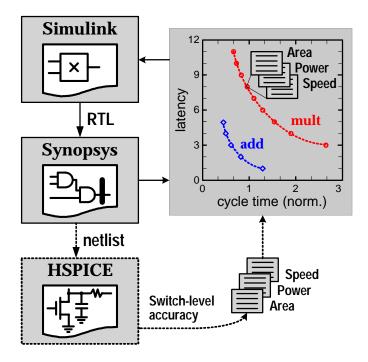

| 7.5  | Block-level characterization (mult, add examples)                                       | 120 |

| 7.6  | Simulink based "Chip-in-a-Day" design flow                                              | 123 |

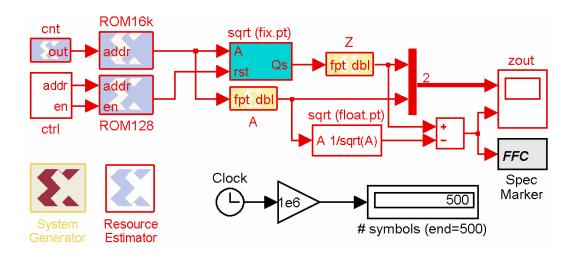

| 7.7  | Simulink model of inverse square rooting algorithm from Chapter 5                       | 128 |

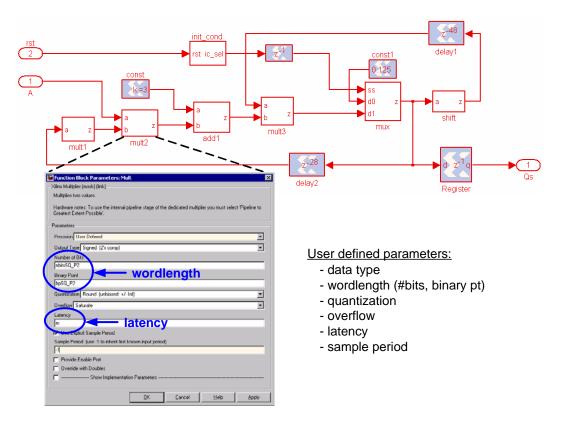

| 7.8  | Simulink/XSG model of "sqrt (fix.pt)" block from Fig.7.7. Each mod-                     |     |

|      | ule has a mask with user-defined parameters (word-length and latency                    |     |

|      | are emphasized).                                                                        | 129 |

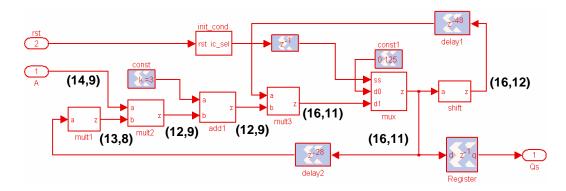

| 7.9  | Word-length optimized design. The numbers indicate (total, frac-                        |     |

|      | tional) bits, respectively. Area before opt: 743 slices, area after opt:                |     |

|      | 668 slices                                                                              | 130 |

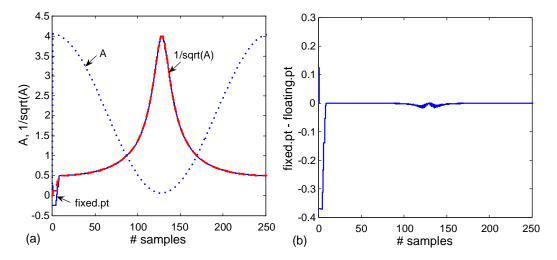

| 7.10 | Functional verification of iterative square rooting: a) fixed and floating              |     |

|      | point outputs for sinusoidal input $A$ , b) error due to finite wordlength              |     |

|      | effects                                                                                 | 131 |

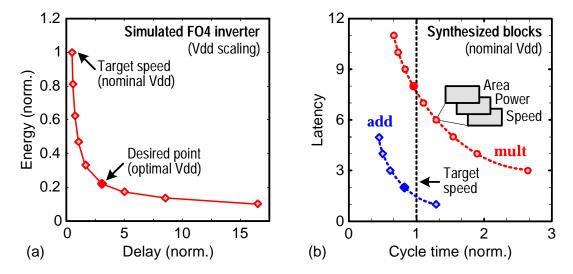

| 7.11 | Technology characterization: a) Simulated Energy vs. Delay of a FO4                     |     |

| ,    | inverter (normalized to nominal Vdd), b) Latency vs. Cycle time of                      |     |

|      | building blocks                                                                         | 132 |

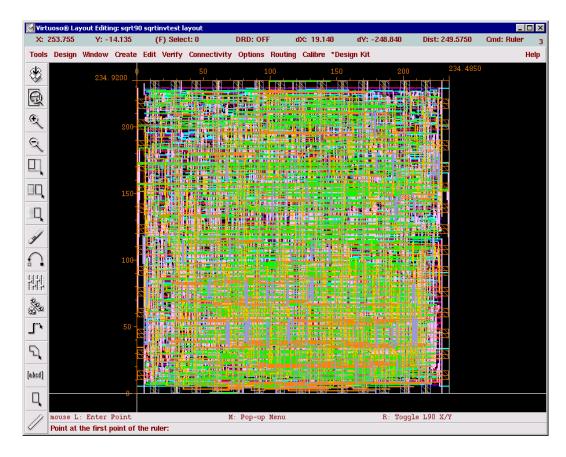

| 7.12 | Layout view of the inverse sqrt design. $(235\mu m \times 235\mu m, 90nm \text{ CMOS})$ |     |

|      | ζ ( τ-γ ) τ-γ , τ-γ                     | , - |

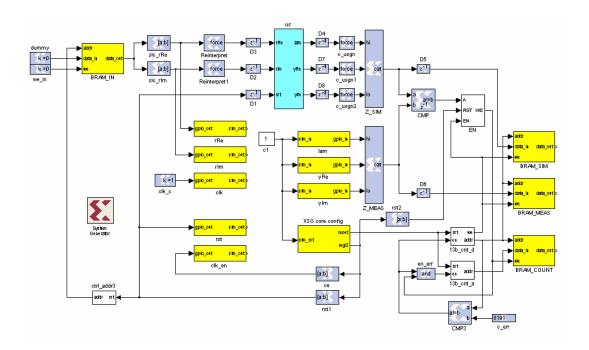

| 8.1  | Simulink model of adaptive SVD                                                          | 138 |

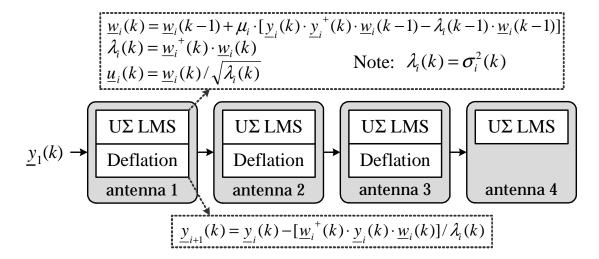

| 8.2  | Adaptive 4-by-4 eigen-mode decomposition algorithm                                      | 140 |

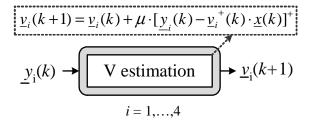

| 8.3  | Adaptive algorithm for tracking of $V$ matrix                                           | 141 |

| 8.4  | Histogram of data retention voltage in SRAM cells (130nm process)                       | 144 |

| 8.5  | (a) Inverter VTC does not degrade at $V_{DD}$ =0.4V. (b) Energy mini-                   |     |

|      | mization via gate sizing and $V_{DD}$ reduction                                         | 145 |

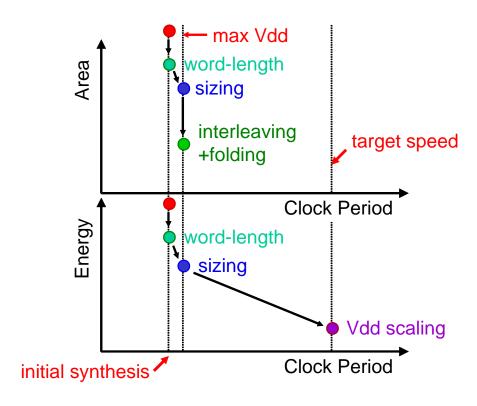

| 8.6  | Basic Energy-Area-Delay trade-offs for constant throughput                              | 147 |

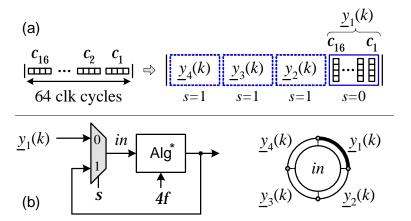

| 8.7  | (a) Vectoring and time-serial ordering of interleaved data. (b) Folding                 |     |

|      | of $Alg$ operation (U $\Sigma$ LMS and deflation)                                       | 148 |

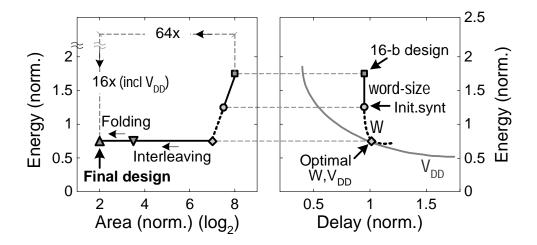

| 8.8  | Energy and Area minimization in $U\Sigma$ decomposition example                         | 150 |

| 8.9  | Conceptual view of optimization techniques used in $U\Sigma$ block                      | 150 |

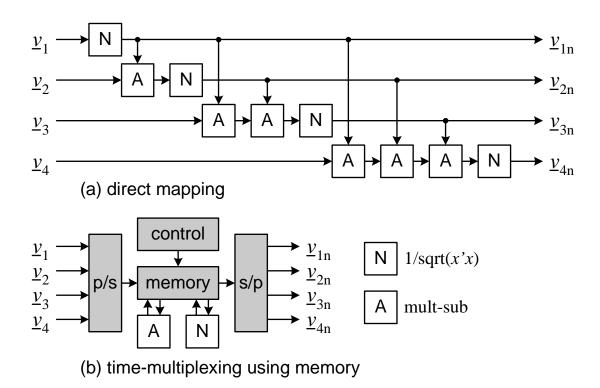

| 8.10 | Grahm Schmidt Orthogonalization: (a) direct mapped architecture,                        |     |

|      | (b) memory based time-multiplexing approach                                             | 151 |

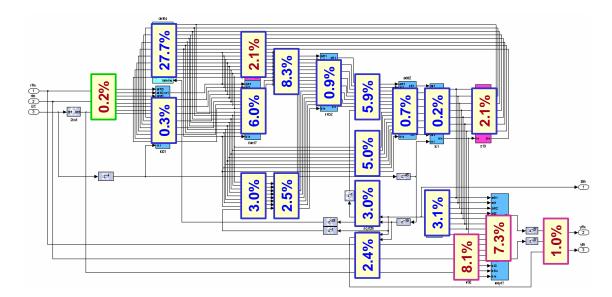

| 8.11 | Power estimates back-annotated to Simulink environment                                  | 154 |

|      |                                                                                         |     |

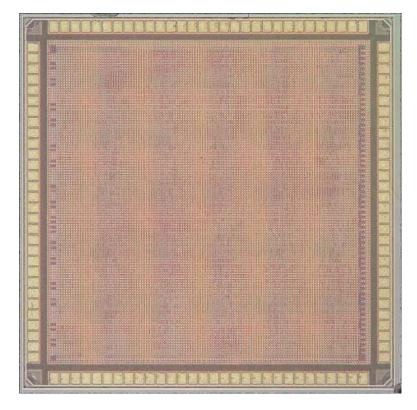

| 9.1  | Die micrograph of eigen-mode decomposition chip. Die size: $2.3 \times 10^{-10}$        |     |

| 0.0  | $2.3mm$ , chip core: $1.9 \times 1.9mm$ . (7M 1P $90nm$ CMOS technology).               | 160 |

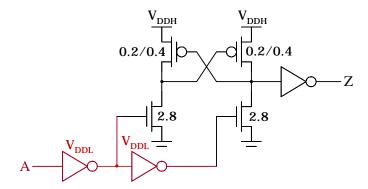

| 9.2  | Schematic of an on-chip level converter $(V_{DDL} = 0.4V, V_{DDH} = 1V,$                |     |

|      | numbers indicate transistor W in $\mu m$ , $L = L_{min}$ unless indicated oth-          |     |

|      | erwise)                                                                                 | 161 |

LIST OF FIGURES x

| 9.3  | Simulink environment for real-time hardware comparison                 | 162  |

|------|------------------------------------------------------------------------|------|

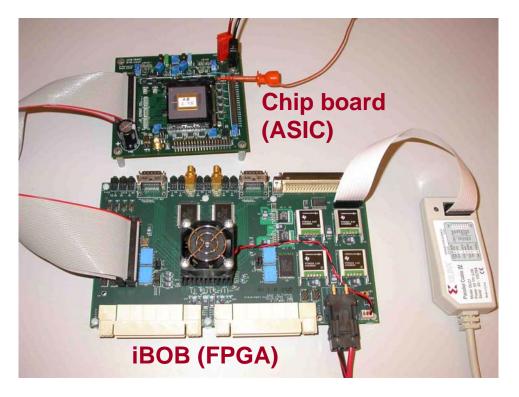

| 9.4  | Test setup that performs real-time hardware comparison                 | 163  |

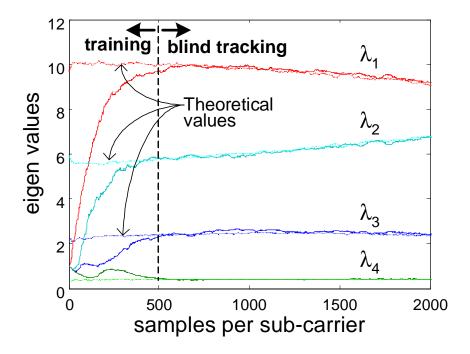

| 9.5  | Measured tracking of slowly varying eigen-modes in a $4 \times 4$ MIMO |      |

|      | channel                                                                | 164  |

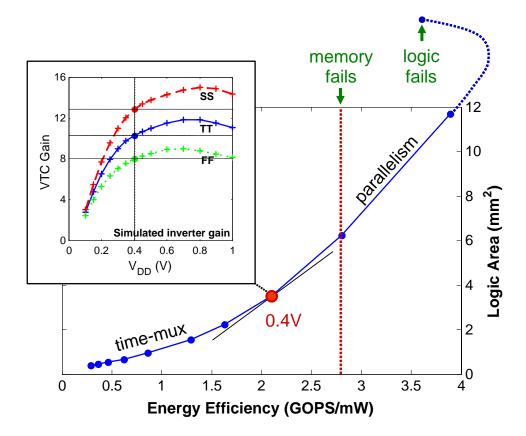

| 9.6  | Trade-off between Energy-Efficiency and Logic Area in the test design. | 166  |

| 10.1 | Decision and the disc                                                  | 1.00 |

| 10.1 | Design space exploration                                               | 109  |

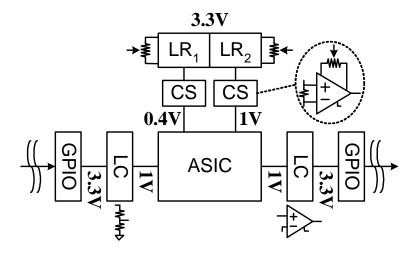

| A.1  | Conceptual diagram of ASIC test board                                  | 183  |

# List of Tables

| 3.1 | Activity map of 8/256 wordline SRAM decoder                                                                            | 37  |

|-----|------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Convergence speed of iterative sqrt and div                                                                            | 92  |

| 6.1 | Summary of ASIC Implementations of $4 \times 4$ MIMO Decoders                                                          | 110 |

| 8.2 | Area of U $\Sigma$ block architectures. $(A^{SEQ}/A^{LOG}=1\%,A_{Def}/A_{U\Sigma}=0.5)$ Summary of GSO implementations |     |

|     | Summary of main optimization techniques                                                                                | 165 |

| A 1 | CPU runtime of back-end steps for chip in Fig. 9.1                                                                     | 182 |

#### Acknowledgments

My sincere gratitude goes to my advisors, Professor Bob Brodersen and Professor Bora Nikolić. Their stimulating guidance has sparked many ideas that carried my research. Bob's constant drive for his students to succeed is truly exceptional, and I would not be typing this if it were not for him. The rightness and enthusiasm have been with me at every step along the way. Bora's understanding and technical support has greatly transcended my knowledge about circuit design. I am indebted to both of them for their faith in my research and their tolerance of my weaknesses. Their patient, trustful, and encouraging support has made me a better scholar and a better person. Professor Jan Rabaey and Professor Paul Wright provided thoughtful evaluation of my research proposal and review of this dissertation.

My early work in energy-performance optimization started as a hobby project together with my friend Vlada Stojanović, who was at Stanford University at that time. I am grateful to him and his advisor Professor Mark Horowitz for their contributions in this work. I am especially grateful to professor Jan Rabaey for giving me a unique opportunity to experience teaching as a graduate student and for many inspiring technical discussions. Professor Seth Sanders gave me the opportunity to pursue my Ph.D. at Berkeley. I thank Professor Vojin Oklobdžija for starting my research during my undergraduate diploma project, and his selfless guidance ever since.

The multi-disciplinary, open minded setting of the BWRC created many opportunities to further develop my work in collaboration with others. Special gratitude goes

Acknowledgments xiii

to Danijela Cabrić. She and Vlada have been peers for endless technical discussions and also great friends since college. Ada Poon developed the SVD algorithm that was being used as a demonstration example for my work. Changchun Shi provided the FFC tool for word-length optimization. Rhett Davis did early development of an automated Simulink-to-Silicon design flow, which was later revised by Kimmo Kuusilinna and constantly updated by Brian Richards. Brian helped me understand intricacies of many IC design tools. Engling Yeo, Mike Sheets, Farhana Sheihk and Tufan Karalar shared the burden in setting up the IC design flow. Chen Chang and Pierre-Yves Droz created the BEE, an FPGA based emulation platform, which turned out to be also applicable to my work for ASIC test and debug. Zhengya Zhang shared experience in using the FPGA boards.

Pam Atkinson gave me the opportunity to master my teaching skills by facilitating UC Berkelev distance learning program to working professionals and students.

The support of many fellow students has helped me get through pressures of graduate school. Chris Rudell, Jeff Weldon, Tom Burd, and Ian O'Donnell have been very supportive by sharing their wisdom and experience. I am also thankful to my classmates Fred Chen, Johan Vanderhaegen, Yun Chiu, Radu Zlatanovici, David Sobel, Chinh Doan, Brian Limketkai, Dragan Petrović, Kevin Camera, Hayden So, and Ning Zhang for stimulating discussions and friendship. Nathan Chan has been the resident guru for electronic gadgets and continuous source of various software updates. Kostas Sarrigeorgidis added his unique character to the BWRC group.

Acknowledgments xiv

Members of the DCDG group engaged in many hard-core discussions about research.

This research was supported by the MARCO/C2S2 program and BWRC member companies. ST Microelectronics provided fabrication support. Special gratitude goes to Gary Kelson, Tom Boot, Brenda Vanoni, and Elise Mills for doing a wonderful job in organizing and administering many activities of the center.

Personal gratitude goes to Siniša for being a great roommate and for his support over the years. Srdjan, Nenad, Bora, Voja, Filip, Dragan, Richard, and Nate have kept my passion for various sports alive. Thanks to Daniel Bukumirović from B92 sports studio in Belgrade, I have also experienced other side of sports, as a reporter. Special thanks go to Vlade, Pedja, and Žarko for making it a truly unique experience.

I am truly indebted to Tomašević-Wakeman family for providing the best housing in Berkeley, which greatly eased my transition into the new world. I thank čika Nikola for lessons about virtually everything. Talking to him is like communicating with a live encyclopedia, apart from his unusual talent to speak almost every language on the planet. Teta Desa has also provided enormous support with her personal advice and encouragement. I have been blessed to meet these people.

I would like to thank Aleksandra for her loving support and understanding for my hectic schedule, especially during chip tapeout. She has been a constant source of inspiration and encouragement.

Finally, and most importantly, I would like to express gratitude to my parents and my brother. This work is a product of their endless love and continued support.

# Chapter 1

## Introduction

...It is difficult to predict at the present time just how extensive the invasion of the microwave area by integrated electronics will be. The successful realization of such items as **phased-array antennas**, for example, using a multiplicity of integrated microwave power sources, could completely revolutionize radar.

G. Moore, 1965

The nature of integrated circuit design has experienced a major change in recent years due to continued scaling of the underlying technology. In the past, the amount of functionality that could be integrated on chip was limited by area; today, power dissipation is the primary limiting factor. Technology scaling over the past four decades has provided about one million times higher integration complexity, and this trend is continuing. Smaller transistors consume less power, but higher transistor density and speed result in overall higher chip power consumption and more generated heat. This is not the only challenge. As technology scales into the deep sub-micron regime (beyond  $0.25\mu m$  node) designers are starting to see some unique technological features

that they did not have to think about before. Power leakage has been increasing exponentially up to 90nm node, and the impact of process parameter variations on power and performance has been increasing with each technology generation. As a result, technology has been degrading, in a way, while design complexity kept increasing. To address the issue of increased variability and leakage, modern technologies offer devices with several thresholds. The multiplicity of transistor thresholds from which to choose gives the designer even more flexibility and makes design more challenging.

### 1.1 Power-Limited Design

The characteristics of power constraints are different for desktop processors and mobile devices, but in both cases the maximum achievable performance depends on the degree of energy-efficiency in performing a computation. Focusing primarily on performance for high-speed circuits results in too much power dissipation. Focusing only on energy for mobile applications is equally inadequate, since this approach rarely achieves the required performance. The correct optimization either minimizes energy consumption, subject to a throughput constraint, or maximizes the amount of computation for a given energy budget.

At the same time, the complexity of chip implementations has been steadily growing, both in desktop and portable devices. To meet the power challenge, microprocessor designs now use a multi-core approaches to increase overall performance, without increasing the baseline frequency of the operation [2]. Growing demand for mobile,

multi-functional devices stresses the issue of power efficiency perhaps even more due to limited energy capacity of portable batteries. Finally, new ideas from communication theory such as using multiple antennas also add to this complexity quite substantially. This dissertation will present general concepts related to power and area minimization while focusing on wireless communication designs.

The scaling of the semiconductor technology has provided an exponential increase in integration complexity, with the number of transistors that can be integrated on a chip doubling every 18 to 24 months. This trend is called "Moore's Law" after Gordon Moore of Intel who made an observation in 1965 that the number of transistors per integrated circuit doubled about every year. The pace wasn't able to sustain quite this level, but Moore made a downward revision in 1975, saying that they doubled about every two years. Such a trend has been steadily in place, resulting in integration capability exceeding a billion transistors on chip today. The question is what could a designer do with so many components? The dual-core Itanium® processor is a good example of successfully tracking the historical trend, with 1.72B transistors integrated on a single die, [3]. It is hard to predict what kind of designs will be needed in the future, but the very last sentence of the famous article by Gordon Moore quoted in the beginning of this chapter [4] is quite indicative. The last visionary statement in the article predicted the use of scaled technology for realization of phased-array antennas for radar applications. This dissertation addresses a similar problem in principle: realization of multiple-antenna (MIMO) wireless communication.

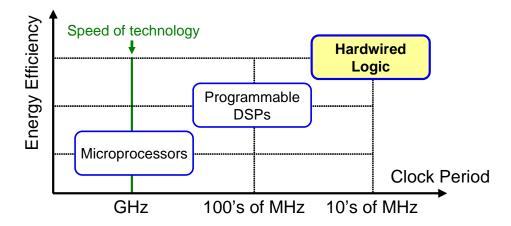

Figure 1.1: Architectural choices for wireless baseband chip design: Microprocessors, Programmable DSPs, Direct-mapped logic.

#### 1.1.1 Architectural Considerations

Before investigating realization of MIMO technology, it is interesting to review basic architectural solutions available for the realization of signal processing algorithms in wireless baseband chips, Fig. 1.1. Digital baseband functionality in wireless local area network (WLAN) chips is typically provided with direct-mapped, hardwired logic<sup>1</sup>. This approach offers the highest energy-efficiency, which is a prime concern in battery operated devices. Another extreme is the heavily time-multiplexed microprocessor architecture, which has the highest flexibility, but it is also the least energy-efficient because of overhead to support the time multiplexing. Between these two extremes are programmable DSP solutions, such as those found in cellular phones.

Another look at the three architectural choices along the horizontal axis reveals that the clock speed required from direct-mapped parallel architectures is significantly

<sup>&</sup>lt;sup>1</sup>Hardwired logic can achieve a much higher speed in general. Clock rate shown in this plot is for the typical case of a wireless local area network baseband.

lower than the speed of technology tailored for microprocessor designs. The difference in clock rate also hints to architectural differences, for example a faster clock is required for time-multiplexing. This discrepancy can be viewed as an opportunity for further energy and area reduction in chip implementations. It is thus interesting to study an example built on the concept of a direct-mapped architecture to see what kind of power and area improvements can be achieved.

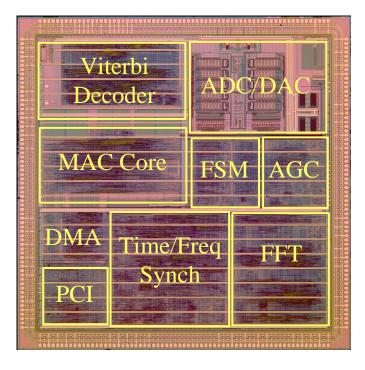

#### Case Study: A 802.11a WLAN Transceiver

Figure 1.2 illustrates an example of a commercial transceiver chip [5], for the 802.11a wireless LAN standard, [6]. The digital baseband operates with a 80 MHz clock, [7]. In fully parallel direct-mapped transceiver architecture, the clock rate is consistent with an 80 MHz sampling rate of the ADC. Baseband processor executes 40 billion operations per second (GOPS) while consuming 200mW of power in a  $0.25\mu m$  CMOS. The total die area that includes digital core, ADCs and DACs, I/Os, and PLL is  $46.2mm^2$ . The design as such is not the most power/area efficient because the speed of a  $0.25\mu m$  technology is greater than the required 80 MHz clock rate. The excess speed could be used to reduce power and area. Power could be reduced by lowering core supply voltage, for example. Area could be reduced by introducing time-multiplexing.

In a commercial environment, design architecture is typically ported to two or three successive technology generations by simply shrinking all device dimensions. Such an approach works well in terms of power and area due to benefits of scal-

Figure 1.2: Wireless technology today: 802.11a WLAN transceiver chip.

ing, but the original architecture, often called "lead architecture", would not be the most power/area efficient in the new technology. With scaling of technology, speed-area-power characteristics of the underlying devices change, rendering a previously optimal architecture sub-optimal in the new technology. In order to achieve the best power/area efficiency, the architecture has to track the energy-performance characteristics of the underlying circuits.

### 1.1.2 Design Productivity

The process of re-designing at the architectural level requires significant amount of engineering resources since it typically involves the close interaction of multiple engineering teams spanning algorithms, architecture, and circuits. The situation is further complicated by the fact that these various teams use different design tools to verify their ideas. Algorithm designers use Matlab or C, for example, while hardware designers like to work with synthesis tools from Synopsys or Cadence. This creates the scenario in which the same design needs to be re-entered multiple times. The ability to re-target an algorithm to a different technology in a power/area efficient way using a unified design description is crucial to improving design productivity. It also enables an efficient way to add flexibility required by future wireless devices.

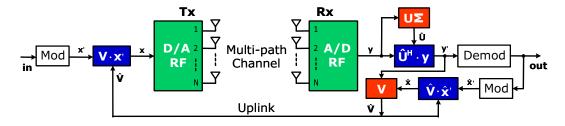

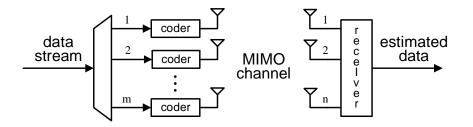

### 1.2 MIMO Technology

Future devices are going to be much more complex. To satisfy the growing need for higher capacity and extended range, WLAN devices are moving to using multiple-input multiple-output (MIMO) algorithms as being defined in the 802.11n standard, [6]. Particular interest of this work is to find out how this impacts the digital baseband in terms of power and area. Figure 1.3 shows conceptual diagram of a multi-antenna communication system, requiring multiple transmit and receive antennas. This system will be described in more detail in Chapters 8, 9. For now, observe that the 802.11a chip works with scalar information to estimate the wireless channel. In the MIMO case, the channel information is in a matrix form, where elements of the matrix represent transfer function between various antenna pairs. The complexity of matrix-based signal processing for an  $N \times N$  MIMO channel would be approximately

Figure 1.3: Future wireless technology: Multi-antenna (MIMO) communication.

$N^2$  higher than for the single antenna case, while scaling of technology can provide only linear increase  $(2\times)$  in computational complexity.

The power and area of a simple direct-mapped parallel implementation would increase quadratically with the number of antenna-pairs N, for a fixed process. Such complexity outpaces Moore's law in terms of area. A simple way to reduce area, demonstrated in Chapter 4, is to use time-multiplexing, but this increases power dissipation. On the other hand, supply voltage scaling with parallelism increases the area. Simultaneous optimization for power and area is therefore needed.

### 1.3 Overview of Previous Work

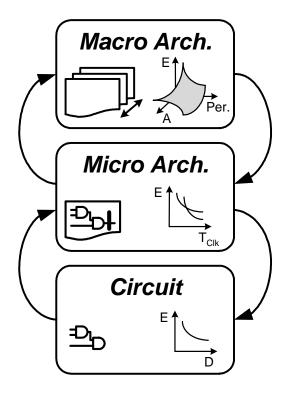

The methods for achieving optimum performance are well explored, [8]. Establishing the balance between performance and power consumption has been a popular research topic in the past as well. An optimum in the energy-delay space has been searched for through minimization of objective functions that combine energy and delay. Today, designers work at each level of design abstraction, Fig. 1.4 separately, which leads to sub-optimal designs.

Figure 1.4: Layered optimization approach.

#### Circuit Techniques

Minimizing the energy-delay product (EDP) [9], [10] of a circuit results in a particular design point in the energy-delay space where 1% of the energy can be traded for 1% of the delay. Although the EDP metric is useful for comparison of different implementations of a design, the design optimization points targeting EDP may not correspond to an optimum under desired operating conditions. Metrics in a general form of  $E \cdot D^n$  [11] or energy-performance ratio by Hofstee [12] have been used instead. For example, the  $E \cdot D^2$  metric [13] puts more weight on the delay than the energy, and is a  $V_{dd}$ -invariant metric. Minimizing  $E \cdot D^n$ , however, has limited applicability since it gives only one (E, D) point in the energy-delay space at which the energy

E is minimized for a fixed delay D. A complete understanding of the energy-delay trade-off for a design is obtained by minimizing the energy subject to an arbitrary delay constraint.

Sizing optimization of digital circuits has been explored extensively resulting in several optimization tools such as TILOS [14], JiffyTune [15] and EinsTuner [16]. Most such tools can at least approximate energy-constrained sizing by constraining the total transistor width available for the circuit. In addition, a number of researchers have derived analytical solutions for area and energy optimization through gate sizing. The analysis is typically restricted to simple logic gates and inverter chains [17], [18]. Like TILOS, a simple analytical timing model is used to guarantee a convex optimization problem, but the delay dependence on  $V_{dd}$  and  $V_{th}$  is explicitly used to allow multivariable optimization to be done.

#### **Architectural Techniques**

Supply voltage scaling is another common technique that is used to minimize energy under performance constraints. It was one of the key techniques in the low-power DSP work of Chandrakasan et al. [19] and has been practically demonstrated in [20], [21]. With the emerging importance of leakage power consumption, the threshold voltage becomes a critical tuning variable and is generally considered together with supply voltage. Liu and Svensson hinted about the existence of an optimal supply and threshold for a given design [22]. Gonzalez et al. [10] investigated joint supply and

threshold voltage scaling for energy-delay product minimization. Kuroda et al. [20] and Nose and Sakurai [23] extended this work and proposed closed-form expressions for the optimum supply, threshold, and leakage-to-switching power ratio.

Various architectural techniques in the energy-area-performance space are evaluated in order to minimize power and area. Prior work applied similar techniques to simple building blocks such as FIR filters [24] in standard VLSI design environments. The methodology presented in this dissertation is scalable to large degrees of complexity. This work uses the graphical Matlab/Simulink environment, familiar to both algorithm developers and chip designers, thus giving practical insight to algorithm developers as well providing a better understanding of the algorithms to VLSI architects.

### 1.4 Dissertation Outline

Chapter 2 introduces a general sensitivity-based optimization framework. Sensitivity is defined as the absolute gradient of a cost function to a constraint when changing some design variable. In a multi-variable optimization, the optimization procedure exploits the tuning variable with the largest marginal return. A fixed point in the optimization is reached when marginal costs of tuning all tuning variables are equal. In this work sensitivities are used to formalize the trade-off between energy and performance.

In order to create more globally optimal designs, the optimization is applied to several design abstraction layers as shown in Fig. 1.4. Prior work is expanded by applying a sensitivity-based optimization framework to multi-variable optimizations across several abstraction layers, allowing for a comparison of power, area and performance for different solutions. Optimization is performed at three layers of abstraction: system architecture, micro-architecture, and fixed circuit topology optimization.

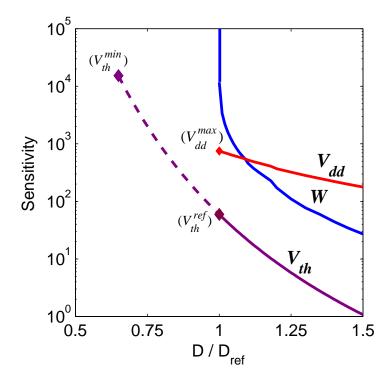

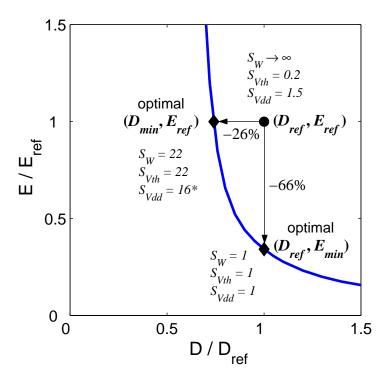

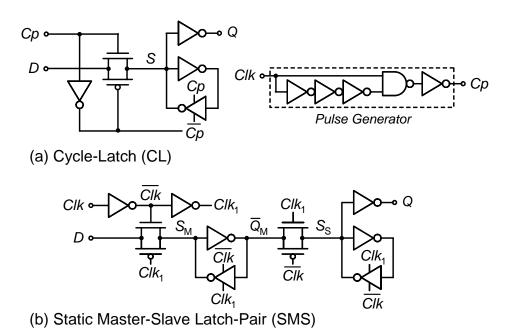

Chapter 3 presents circuit-level optimization that minimizes energy subject to delay constraint using gate size (W), supply  $(V_{dd})$  and threshold voltage  $(V_{th})$  as variables. All variables are jointly considered to yield the highest energy-efficiency. The sensitivity framework is applied to circuit logic blocks with significantly different topologies: an inverter chain, a memory decoder, and a 64-bit adder. The effectiveness and scope of all variables in the optimization are analyzed. Since circuit-level optimization is only effective in a very narrow performance range, micro-architectural optimization is considered.

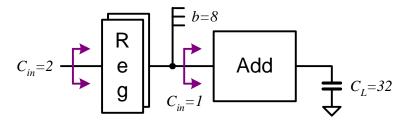

Chapter 4 takes results from the circuit-level optimization and provides insight for the micro-architectural optimization. The best choice of circuit topology and optimal level of parallelism is made by investigating a set of optimal energydelay trade-off curves corresponding to various circuits. Design issues such as determination of the optimal balance between leakage and switching power, the optimal  $V_{dd}$  and  $V_{th}$ , and the investigation of energy-area trade-offs are addressed.

Chapter 5 extends the lessons from micro-architectural optimization and reviews signal processing techniques such as data-stream interleaving and folding. Implementation cost in terms of cycle latency is also considered. Since different arithmetic blocks vary in complexity, this also raises a question how to optimally distribute pipeline registers, both in feed-forward and feedback based computations. To address this, the methodology for loop retiming is presented, followed by analysis of iterative square rooting and division techniques.

Chapter 6 provides general classification of MIMO algorithms starting from fundamental diversity versus spatial multiplexing trade-off. An overview of diversity methods such as BLAST and spatial-multiplexing methods such as QR-decomposition and SVD is provided. The goal is to classify basic concepts used in MIMO detection and investigate the computational complexity involved. The chapter concludes with a brief survey of published ASIC implementations related to MIMO baseband signal processing.

Chapter 7 presents the use of the design optimization methodology within a commercial CAD environment. The procedure starts with design entry in Matlab/Simulink, followed by word-length optimization. Technology specific block characterization is used to determine the optimal micro-architecture and the op-

erating supply voltage. Finally, the design is taken through highly automated back-end synthesis tools that incorporate gate sizing and supply voltage optimization. Design procedure is illustrated on the inverse square rooting example.

Chapter 8 applies concepts developed in previous chapters on design and optimization of a  $4\times4$  adaptive MIMO algorithm, to demonstrate the level of complexity that can be supported using proposed methodology. An ASIC chip is fabricated to verify the validity of the methodology.

Chapter 9 discusses measured results from the ASIC chip. An FPGA-based test setup for efficient ASIC verification is also described.

Chapter 10 concludes this work and proposes some steps for future research.

# Chapter 2

# Sensitivity-Based Optimization

This chapter briefly introduces the general sensitivity-based optimization framework that will be used throughout this dissertation. The framework quantifies the cost of tuning each variable in the design and balances sensitivities to all design variables in order to minimize the cost function subject to design constraints.

### 2.1 Optimization Principle

Sensitivity analysis is based on simple gradient expression as given by Eq. (2.1),

$$S_A(A_0) = \frac{\partial E/\partial A}{\partial D/\partial A} \bigg|_{A=A_0}$$

(2.1)

where E is a cost function and D is a design constraint. For example, E could be the energy dissipation and D could be the delay in a digital circuit. Both E and D

Figure 2.1: Illustration of Energy-Delay sensitivity.

are functions of some general design parameter A, for example supply voltage. The sensitivity  $S_A$  to variable A provides intuition about the profitability of optimization, i.e. how much change in E and D is achieved by tuning design variable A around operating point  $A_0$ .

The concept of sensitivity is illustrated in Fig. 2.1 for an example of energy-delay trade-off, which is described with function f(A, B). Assuming that the design is positioned at the operating point  $(A_0, B_0)$ , the sensitivity to variable A, for example, is simply defined as the slope of the line tangent to function  $f(A, B_0)$ . The function  $f(A, B_0)$  is obtained by varying variable A around  $(A_0, B_0)$ . In this example, variable B has higher sensitivity than variable A resulting in a sub-optimal design.

The key concept to realize is that at the optimal solution point, sensitivities should be equal. An optimization mechanism based on this principle is illustrated for the general energy-delay trade-off shown in Fig. 2.2. The goal is to minimize energy

Figure 2.2: Process of balancing sensitivities.

subject to a delay constraint  $D_0$ . Assume that the operating point  $(A_0, B_0)$  is the initial design point. Starting from this point, delay can be reduced  $\Delta D$  by lowering the value of variable A. This results in an energy increase<sup>1</sup> proportional to sensitivity  $S_A$ ,  $\Delta E = S_A \cdot (-\Delta D)$ . The delay slack  $\Delta D$  provided by tuning variable A can be utilized by tuning a more sensitive variable B to return to the starting delay point  $D_0$ . Overall, an energy reduction of  $\Delta E = (S_B - S_A) \cdot \Delta D$  is achieved because energy cost of tuning variable B is higher than the energy cost of tuning variable A. In other words, the energy reduction is possible because sensitivities  $S_A$  and  $S_B$  are not equal at the initial operating point  $(A_0, B_0)$ . A fixed point in the optimization, corresponding to  $\Delta E = 0$ , is therefore achieved when all sensitivities are equal. During the process of balancing sensitivities, some variables may reach the upper or lower limit, resulting in a constrained solution.

Note that  $S_A$  is negative. The minus sign represents decrease in delay.

Figure 2.3: Block diagram illustrating various abstraction layers in the optimization. Energy is the objective function at the circuit and micro-architectural layers, while achieving proper energy-area trade-off is the objective at the macro-architectural layer.

# 2.2 Layered Optimization Approach

The general sensitivity based framework is applied to multiple layers of abstraction as illustrated in Fig. 2.3. The goal is to minimize the overall cost function of a design, such as energy or area, subject to some constraint, such as performance.

The nature of performance constraints is different at various abstraction layers in the optimization. For instance, the performance of a circuit is measured by the circuit delay, while the performance of a micro- or macro-architecture is related to the cycle time or the number of instructions per cycle. Each new layer in the optimization introduces more degrees of freedom, such as the level of parallelism at the microarchitectural layer or the area of the macro-architecture. However, designs of higher complexity can be still optimized based on the optimal energy-performance trade-offs of their building blocks. This is computationally much more efficient than performing large-scale optimization at the gate level.

The procedure is illustrated in Fig. 2.3, where the goal is to be able to obtain trade-offs at individual layers and understand the interaction among the different layers. Also, if the desired operating point in E-D space is known, which corresponds to some sensitivity, then the optimization problem can be decoupled into a sequential procedure where independent variables are optimized individually. Decoupling the problem into independent spaces provides good intuition about various trade-offs comprising the overall design optimization.

At the circuit level, the goal is to minimize the energy subject to the delay constraint in data-path logic and flip-flops, using the gate sizing, supply and threshold voltage as variables. The result is the values of optimization variables for the optimal energy-delay (E-D) trade-off. Traversing upward through the design abstraction stack, additional variables in the optimization can be considered, such as the amount of parallelism or time-multiplexing at the micro-architecture level. (Figure 2.3 is by no means complete, it illustrates some of the most commonly used variables.)

At the micro-architecture level, the optimal energy-delay trade-off curves from the circuit level are used to hierarchically extend the optimization. Information about the optimal E-D trade-off in individual circuit blocks is used, along with top-level

specifications such as throughput, word-size, algorithm, etc. These trade-off curves coupled with optimal W,  $V_{dd}$ , and  $V_{th}$  are strategically combined to obtain the optimal energy-performance trade-off for circuit macros. With this optimal energy-performance curve, the designer can select the appropriate circuit topology for each pipeline stage or choose an optimal level of parallelism based on the circuit optimization results. However, the optimal  $V_{dd}$  and  $V_{th}$  in the individual circuits are rarely the same for all pipeline stages. In order to achieve the most energy-efficient solution under a single  $V_{dd}$  and  $V_{th}$  combination, several iterations may be required to optimize all the circuits under that particular  $V_{dd}$  and  $V_{th}$ . This includes finding the optimal  $V_{dd}$  and  $V_{th}$  for a given architecture based on balancing the leakage and switching components of energy under some performance constraint. The result is an optimal E-D curve, along with area information, that becomes important when parallelism and time-multiplexing are applied to large blocks. Finally, at the top-level the goal is to find the optimal compromise between the energy and area of the implementation.

The general framework presented in this chapter will be applied to multiple design abstraction layers. In the next two chapters, individual optimizations at the circuit-level (Chapter 3) and the micro-architectural level (Chapter 4) are analyzed.

# Chapter 3

# Circuit Optimization

This chapter presents methods for efficient energy-performance optimization at the circuit level. Optimizations are performed based on the alpha-power law gate delay model and switching and leakage components of energy. The sensitivity-based approach is applied to energy minimization subject to a delay constraint, using gate size, supply and threshold voltage as variables. General energy-delay sensitivity to each of the variables is derived to provide an understanding of the effectiveness of various variables in multi-variable optimization. The impact of basic topological characteristics found in logic gates such as branching and path reconvergence is also analyzed and illustrated by examples of an inverter chain, a memory decoder, and an adder. It is demonstrated that energy savings of about 65% can be achieved without delay penalty with equalization of sensitivities to sizing, supply, and threshold voltage in a 64-bit adder, compared to the reference design sized for minimum delay.

# 3.1 Technology Calibration

The energy and the delay of a logic gate are functions of its size, supply voltage, and transistor threshold voltage. In order to calculate the sensitivities of larger logic blocks comprised of simple logic gates, it is necessary to develop simple and accurate models of the energy and delay of the gate. For the optimization purposes, the models work with continuous variables. General conclusions derived from continuous optimizations are applied to synthesis environment that works with discrete variables, such as standard-cell sizes (Chapter 7).

## 3.1.1 Delay Model

While there are many different models that can be used, our prior work [25], [26] suggests the use of the alpha-power law model of [27] as a baseline for derivation of the gate delay formula:

$$t_{p} = \frac{K_{d} \cdot V_{dd}}{(V_{dd} - V_{on} - \Delta V_{th})^{\alpha_{d}}} \cdot \left(\frac{w_{out}}{w_{in}} + \frac{w_{par}}{w_{in}}\right)$$

$$= \tau_{ref} \cdot g \cdot \left(h + \frac{p}{g}\right)$$

$$= \tau_{ref} \cdot d$$

(3.1)

This is a curve-fitted expression and parameters  $V_{on}$  and  $\alpha_d$  are intrinsically related, yet not necessarily equal, to the transistor threshold voltage and velocity saturation index.  $\Delta V_{th}$  is the change from the standard threshold voltage given by technology;

$K_d$  is a fitting parameter;  $h = w_{out}/w_{in}$  is the electrical fan-out of a gate; and  $w_{par}/w_{in}$  is a measure of its intrinsic delay. Gate and parasitic capacitances are both linearized and the effects of transistor capacitance non-linearities are lumped into the fitting parameters  $V_{on}$ ,  $\alpha_d$ , and  $K_d$ .

The simple delay model fits SPICE simulated data within 5% over a range of supply voltages from  $0.4V_{dd}^{max}$  to  $V_{dd}^{max}$  and fanout factors from 2 to 10, assuming equal input and output rise and fall times [18]. Using the linear delay model from the method of logical effort [21], the delay formula can be expressed simply as a product of the process-dependent time constant  $\tau_{ref}$  and the unit-less delay d. This delay d consists of the intrinsic delay p due to the self-loading of the gate, and the fanout delay  $g \cdot h$  which is the product of the logical effort g and the fanout h. The logical effort g represents the relative ability of a gate to deliver current for a given input capacitance. The fanout h is the ratio of the total output to input capacitance. The simple linear delay model naturally extends to logic paths and multiple-supply voltages [25]. The delay of a logic path is simply  $D = d_{path} \cdot \tau_{ref}$ , where  $d_{path}$  is the sum of the normalized gate delays along the path.

When there are multiple supply voltages, the perception of a "process constant" to which delays are normalized changes. A gate that operates at a reduced supply voltage has a smaller device current for the same input capacitance. Thus, if  $V_{dd}$  is scaled down, the logical effort and the parasitic delay increase, as modeled by

<sup>&</sup>lt;sup>1</sup>Small letters label gate parameters, capital letters label circuit and system parameters

Figure 3.1: Delay vs. fanout and supply.

the voltage-dependent factor  $k_v$  in Eq. (3.2) and demonstrated in Fig. 3.1. When a regular gate is placed at the interface between the high and low supply domains, the pull-up path operates at reduced supply, thus with a higher logical effort. The size of the pull-up must increase in order to equalize the logical effort of each path. This is modeled through voltage and gate topology dependent scaling factors.

$$k_v = \frac{V_{dd}^{low}}{V_{dd}^{ref}} \cdot \left(\frac{V_{dd}^{ref} - V_{on}}{V_{dd}^{low} - V_{on}}\right)^{\alpha_d}$$

(3.2)

## 3.1.2 Energy Model

Switching and leakage energy are considered as the two dominant components in this analysis. The analysis based on the gate-level model is expanded to data-path logic, taking into account the impact of switching activity and state-dependent leakage.

#### Switching Energy

The switching component is the standard dynamic energy term given by Eq. (3.3),

$$e_{Sw} = \alpha \cdot K_e \cdot (w_{out} + w_{par}) \cdot V_{dd}^2 \tag{3.3}$$

where  $K_e \cdot w_{out}$  is the load capacitance,  $K_e \cdot w_{par}$  is the self-loading of the gate, and  $\alpha$  is the probability of an energy-consuming transition at the output of the gate. The main optimization parameters are supply voltage  $V_{dd}$  and capacitances which are directly proportional to gate size.

#### Leakage Energy

Static leakage of a logic gate at  $V_{gs} = 0$  is modeled as:

$$e_{Lk} = D \cdot w_{in} \cdot I_0(S_{in}) \cdot \left(V_{th}^{ref} + \Delta V_{th} - \gamma \cdot V_{dd}\right) \cdot V_{dd}$$

(3.4)

where  $D = d_{critical-path} \cdot \tau_{ref}$  is the cycle time,  $I_0(S_{in})$  is the normalized leakage current of the gate with inputs in state  $S_{in}$ ,  $V_{th}^{ref}$  is the standard threshold voltage provided by the technology, and  $V_0 = n \cdot kT/q$  and  $\gamma$  account for the sub-threshold slope and DIBL factor, respectively. The model in Eq. (3.4) is calibrated in HSPICE over the full range (defined by lower and upper limits) of design parameters  $V_{dd}$ ,  $V_{th}$ , W, and also over the entire set of states  $S_{in}$  for each of the gates. The model neglects gate leakage that occurs due to direct tunneling of carriers through a thin gate oxide.

Gate leakage is expected to become a problem with oxides thinner than 2nm [28], or below the 90nm node. (For reference, the diameter of an atom is about 0.1nm.) With further shrinking of the gate oxide, gate leakage is predicted to increase at a rate of  $500\times$  per technology generation while sub-threshold leakage is predicted to increase  $5\times$  for each technology generation [29].

In large circuit blocks, the logic state and the switching probability of the internal gates are obtained through logic simulation. This way, the gate-level models given by Eqs. (3.3), (3.4) are extended to compute the total circuit energy.

# 3.2 Optimization Approach

Optimization procedure starts by finding the reference point for a design and then minimizing energy subject to a delay constraint normalized to the reference delay.

### 3.2.1 Reference Point

Reference point for design optimization is the minimum delay  $D_{min}$  design obtained through gate size optimization, under the standard supply  $V_{dd}^{ref}$  and threshold voltage  $V_{th}^{ref}$  for a technology. The minimum delay point is one of the points on the energy-efficient curve and is convenient reference, because it is well defined.

Reference supply voltage corresponds to the maximum supply  $V_{dd}^{max}$  specified by the technology reliability limit. In this chapter, the nominal threshold voltage is the low- $V_{th}$  from a dual- $V_{th}$  0.13 $\mu m$  technology, and this value is labeled as reference  $V_{th}^{ref}$ , corresponding to  $\Delta V_{th} = 0$  in the model, Eqs. (3.1), (3.3), (3.4). In this particular 0.13 $\mu m$  technology, for example,  $V_{on}^{ref} = 0.34V$ ,  $V_{dd}^{max} = 1.2V$ . The minimum delay  $D_{min}$  is achieved for some specified output load  $C_L$  and a fixed input capacitance  $C_{in}$ . All capacitances are normalized to the input capacitance of a unit inverter.

## 3.2.2 Optimization Procedure

In the optimization procedure, some percentage incremental change in delay,  $d_{inc}$ , relative to the reference point is specified. The energy is minimized for the new target delay  $D = D_{min}(1 + d_{inc}/100)$ , by using supply voltage, threshold voltage, gate size, and optional buffering as optimization variables. Supply optimizations investigated include global supply reduction, two discrete supplies, and per-stage supplies. In the discrete supply optimizations, supply voltage can only decrease from input to output of a block assuming that low-to-high level conversion is done in registers, while sizing is allowed to change continuously.

# 3.3 Sensitivity Analysis

In energy-delay optimization, the objective is to utilize available timing slack for maximal energy reduction. There are usually several tuning variables that can be used to trade timing slack for energy at various levels in the design hierarchy. As pointed out in Chapter 2, the energy-efficient design is achieved when the marginal costs of all the tuning variables are balanced. Each design variable x carries a certain energy reduction potential per delay cost, at each point in the energy-delay space, as given by Eq. (3.5).

$$S_x(X) = \frac{\partial E/\partial x}{\partial D/\partial x} \bigg|_{x=X}$$

(3.5)

Analysis using relative sensitivity, which was termed hardware intensity, was proposed in [30]. The relative sensitivity simply represents percent power per percent performance for an energy-efficient design as given by Eq. (3.6). However, formulation in Eq. (3.5) is preferred since relative contributions of energy and delay from various blocks are unknown and also may change during the optimization.

$$\eta_x(X) = S_x(X) \cdot \frac{D}{E} \tag{3.6}$$

The true power minimization method always exploits the tuning variable with the largest capability for energy reduction. This ultimately leads to the point where the energy reduction potentials of all tuning variables are equalized. In order to further develop the understanding of these relative gradients, practical expressions (sensitivities) are derived for different tuning variables. The variables considered include gate size W, supply voltage  $V_{dd}$ , and change in threshold voltage  $\Delta V_{th}$  as knobs in the optimization. By analyzing sensitivities, the efficiency of W,  $V_{dd}$ , and  $\Delta V_{th}$  optimizations