# Solution Processing Techniques for Low-Cost Circuit Fabrication

David Howard Redinger

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2007-3 http://www.eecs.berkeley.edu/Pubs/TechRpts/2007/EECS-2007-3.html

January 5, 2007

Copyright © 2007, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Solution Processing Techniques for Low-Cost Circuit Fabrication

by

#### David Howard Redinger

B.S. (University of Illinois at Urbana-Champaign) 2000

M.S. (University of California, Berkeley) 2003

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Vivek Subramanian, Chair Professor Ali Niknejad Professor Eugene E. Haller

Fall 2006

| Chair | Date |

|-------|------|

|       |      |

|       |      |

|       | Date |

|       |      |

|       |      |

|       | Date |

The dissertation of David Howard Redinger is approved.

University of California, Berkeley Fall 2006

Solution Processing Techniques for Low-Cost Circuit Fabrication

Copyright © 2006

by

David Howard Redinger

#### Abstract

Solution Processing Techniques for Low-Cost Circuit Fabrication

by

#### David Howard Redinger

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vivek Subramanian, Chair

With the high performance and cost associated with today's silicon integrated circuits there is a market for lower-performing, yet extremely inexpensive circuits. This work focuses on the materials, processes, and techniques of ultra-low-cost fabrication. In particular the fabrication of devices using inkjet printing and aqueous deposition is addressed in detail.

Low-cost RFID tags would enable automated inventory and checkout in retail stores by replacing the ubiquitous UPC barcode. In this work the fabrication of the passive components for RFID tags is achieved primarily by inkjet printing, using a gold nanoparticle ink to generate conductive lines on plastic substrates. After considering the performance requirements of 13.56 MHz RFID passive devices, the all-printed devices are improved by using a combination of inkjet patterning with an electroless copper deposition. The results of this hybrid approach are shown to be far superior to printing alone, generating inductors with quality factors above 20.

The concept of solution-processing is then expanded to cover semiconductor and insulator materials, with a focus on transparent TFTs for active-matrix OLED dis-

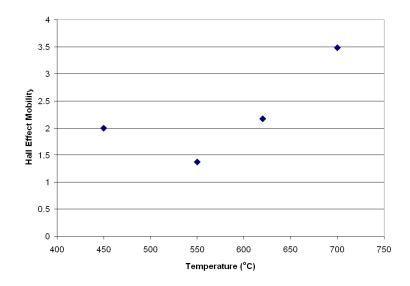

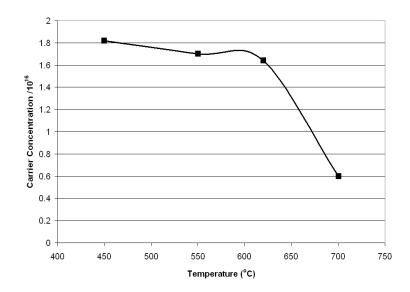

plays. Zinc oxide TFTs are fabricated using chemical bath deposition followed by an anneal in oxygen ambient. Electron mobility as high as 3.5 cm<sup>2</sup>/Vs is achieved, and mobility of 1.5 cm<sup>2</sup>/Vs is achieved at low anneal temperatures (450 °C), enabling the use of cheap glass substrates. These results present a significant improvement over amorphous silicon, and will allow the development of low-power high-resolution OLED displays.

Professor Vivek Subramanian Dissertation Committee Chair

| To my beloved grandmother Hannah Stannard, who passed away at the age of 92                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2, 2006. She missed my sister's wedding and my graduation by a few months.                                                               |

| To my parents Sarah Stannard and Howard Redinger, for their unwavering support and faith in their son. To them I owe a debt I can never repay. |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

# Contents

| $\mathbf{C}$ | ontei | nts                                       | ii |

|--------------|-------|-------------------------------------------|----|

| Li           | st of | Figures                                   | vi |

| Li           | st of | Tables                                    | х  |

| $\mathbf{A}$ | ckno  | wledgements                               | xi |

| 1            | Inti  | $\operatorname{roduction}$                | 1  |

|              | 1.1   | Radio Frequency Identification            | 3  |

|              | 1.2   | Transparent TFTs for Display Applications | 5  |

|              | 1.3   | Organization                              | 8  |

| <b>2</b>     | Pri   | nting Technology                          | 9  |

|              | 2.1   | Introduction                              | 9  |

|              | 2.2   | Reel-to-Reel Fabrication                  | 9  |

|              | 2.3   | All-Additive Processes                    | 11 |

|              | 2.4   | Printing Methods                          | 11 |

|              |       | 2.4.1 Inkjet Printing                     | 11 |

|              |       | 2.4.2 Gravure                             | 13 |

|              |       | 2.4.3 Microcontact Printing               | 14 |

|              | 2.5   | Description of Custom Inkjet System       | 16 |

|              | 2.6   | Gold Nanoparticles                        | 18 |

|              | 2.7   | Solvent Choice                            | 19 |

|              | 2.8   | Plastic Substrates                        | 21 |

|   | 2.9 | Concl  | usion                                                                | 21 |

|---|-----|--------|----------------------------------------------------------------------|----|

| 3 | Pri | nted P | assive Components for RFID                                           | 23 |

|   | 3.1 | Introd | luction                                                              | 23 |

|   | 3.2 | Theor  | y of RFID Coupling                                                   | 24 |

|   |     | 3.2.1  | Power Constraints                                                    | 24 |

|   |     | 3.2.2  | Mutual Inductance                                                    | 25 |

|   |     | 3.2.3  | Induced Voltage                                                      | 27 |

|   |     | 3.2.4  | Using Resonance to Boost the Supply Voltage                          | 30 |

|   |     | 3.2.5  | Summary of Components Necessary                                      | 34 |

|   | 3.3 | Impac  | et of Inductor Quality Factor on Coupled Voltage                     | 34 |

|   |     | 3.3.1  | Quality Factor of Tag Front End                                      | 35 |

|   |     | 3.3.2  | Quality Factor Degradation Due to Finite Inductor Quality            | 36 |

|   |     | 3.3.3  | Optimizing Inductor Geometry                                         | 37 |

|   |     | 3.3.4  | Summary of Inductor Quality Requirements                             | 39 |

|   | 3.4 | Fabric | eation of All-Printed Passive Components on Plastic                  | 39 |

|   |     | 3.4.1  | Printing Nanoparticle Solutions                                      | 40 |

|   |     | 3.4.2  | Low Resistance Gold Lines                                            | 41 |

|   |     | 3.4.3  | Crossovers and Interconnect                                          | 43 |

|   |     | 3.4.4  | Inductors                                                            | 45 |

|   |     | 3.4.5  | Capacitors                                                           | 49 |

|   | 3.5 | Discus | ssion                                                                | 54 |

|   | 3.6 | _      | Quality Inductors Fabricated Using Inkjet Printing and Electrolating | 55 |

|   |     | 3.6.1  | Electroplating Problems                                              | 56 |

|   | 3.7 | Electr | oless Deposition - A Brief Introduction                              | 59 |

|   |     | 3.7.1  | Immersion Plating                                                    | 60 |

|   |     | 3.7.2  | Continuous Electroless Deposition of Copper                          | 62 |

|   |     | 3.7.3  | Rate of the Electroless Reaction                                     | 65 |

|   |     | 3.7.4  | Metal Catalysis                                                      | 67 |

|   |     | 3.7.5  | Competing Side Reactions                                             | 68 |

|   |     | 3.7.6  | Printed Nanoparticles as a Seed Layer                                | 69 |

|   |      | 3.7.7   | Seed layer preparation                              | 70         |

|---|------|---------|-----------------------------------------------------|------------|

|   |      | 3.7.8   | Plating Solution                                    | 71         |

|   |      | 3.7.9   | Plated Copper Results                               | 72         |

|   |      | 3.7.10  | High-Quality Inductors                              | 75         |

|   | 3.8  | Conclu  | ısion                                               | 76         |

| 4 | Solu | ıtion-F | Processing – An Introduction                        | <b>7</b> 9 |

|   | 4.1  | Introd  | uction                                              | 79         |

|   | 4.2  | Materi  | als Available                                       | 81         |

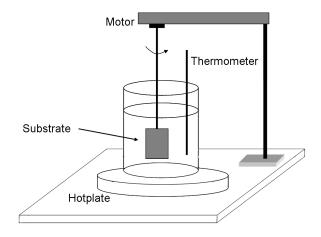

|   | 4.3  | Chemi   | cal Bath Deposition                                 | 82         |

|   |      | 4.3.1   | Deposition Setup                                    | 82         |

|   |      | 4.3.2   | Growth Mechanisms                                   | 83         |

|   |      | 4.3.3   | Common Bath Components                              | 84         |

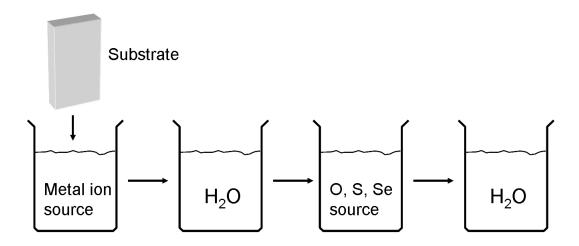

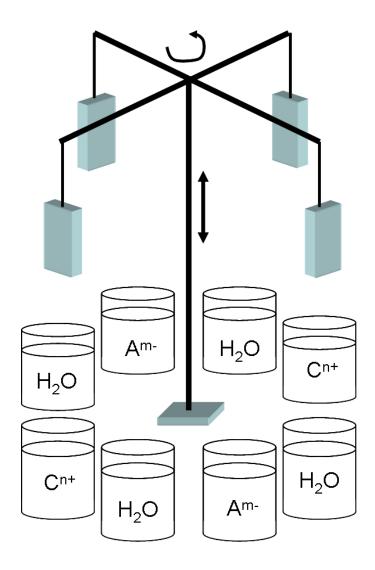

|   | 4.4  | Succes  | sive Ion Layer Adsorption and Reaction              | 86         |

|   | 4.5  | Liquid  | Phase Deposition                                    | 88         |

|   | 4.6  | Selecti | ve Deposition                                       | 90         |

|   |      | 4.6.1   | Exploiting Hydrophilic/Hydrophobic Surfaces         | 91         |

|   |      | 4.6.2   | Selectivity via Self-Assembled Monolayers           | 92         |

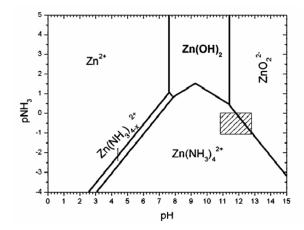

|   | 4.7  | Chemi   | cal Bath Deposition of ZnO                          | 92         |

|   |      | 4.7.1   | Background                                          | 93         |

|   |      | 4.7.2   | Soluble Zinc Species in Basic Solutions             | 94         |

|   |      | 4.7.3   | Precipitation of Zinc Species                       | 95         |

|   | 4.8  | Depos   | ition of ZnO for use as a Transparent Semiconductor | 96         |

|   | 4.9  | Comm    | ercial Applications of CBD                          | 97         |

|   | 4.10 | Conclu  | ısion                                               | 98         |

| 5 | Zino | Oxid    | e Transparent TFTs for AM-OLED Displays             | 99         |

|   | 5.1  | Introd  | uction                                              | 99         |

|   | 5.2  | OLED    | Displays                                            | 100        |

|   |      | 5.2.1   | OLED Device Structure                               | 100        |

|   |      | 5.2.2   | OLED Colors                                         | 102        |

|   |      | 523     | OLED Current-Voltage Characteristics                | 103        |

|              | 5.3   | OLED    | Versus LCD - A Technology Comparison                  | 104       |

|--------------|-------|---------|-------------------------------------------------------|-----------|

|              | 5.4   | OLED    | Pixel Drive Techniques                                | 105       |

|              |       | 5.4.1   | Pixel TFT Considerations                              | 107       |

|              |       | 5.4.2   | Pixel Scaling                                         | 108       |

|              |       | 5.4.3   | Power                                                 | 109       |

|              | 5.5   | Transp  | parent TFTs                                           | 110       |

|              |       | 5.5.1   | Analysis of ZnO CBD TFT Requirements                  | 111       |

|              |       | 5.5.2   | Summary of Transparent TFT Requirements               | 113       |

|              | 5.6   | Zinc C  | Oxide TFTs Fabricated by Chemical Bath Deposition     | 113       |

|              |       | 5.6.1   | Background                                            | 114       |

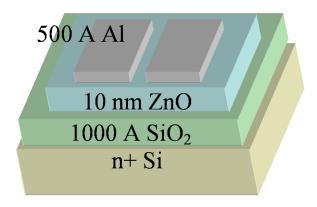

|              |       | 5.6.2   | TFT Fabrication                                       | 115       |

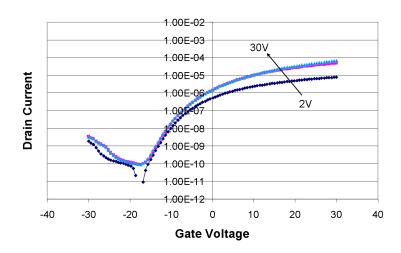

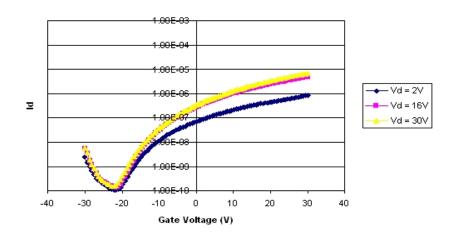

|              |       | 5.6.3   | Extraction of Field-Effect Mobility                   | 117       |

|              |       | 5.6.4   | Dependence of Field-Effect Mobility on Bath pH        | 121       |

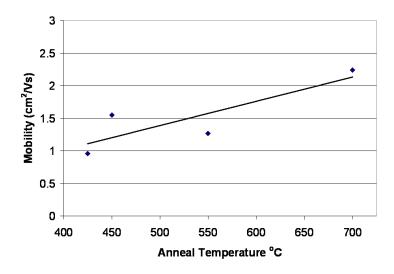

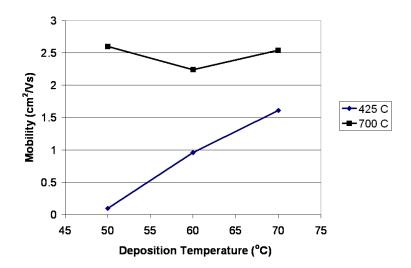

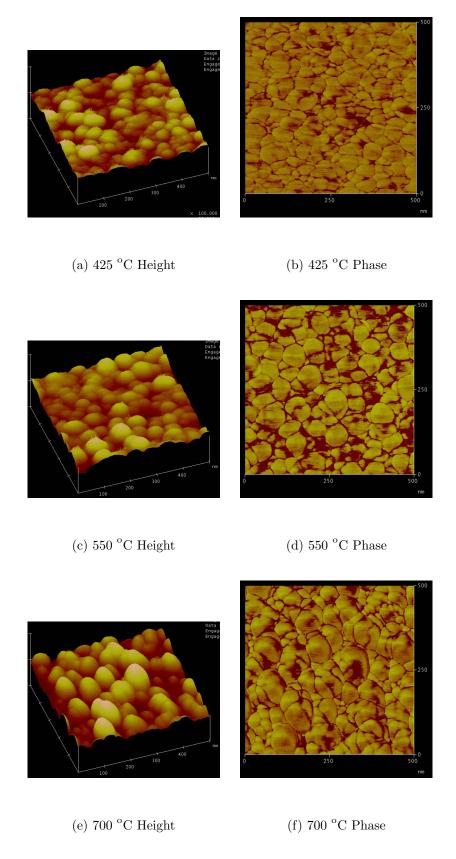

|              |       | 5.6.5   | The Effects of Bath and Anneal Temperatures           | 122       |

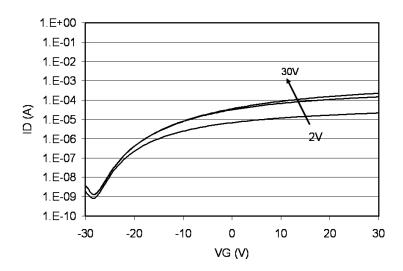

|              |       | 5.6.6   | Current-Voltage Characteristics                       | 127       |

|              |       | 5.6.7   | Dependence of Film Thickness                          | 127       |

|              | 5.7   | Hall E  | ffect Measurements of CBD ZnO Films                   | 130       |

|              | 5.8   | Conclu  | ısion                                                 | 132       |

| 6            | Con   | clusion | ns and Future Work                                    | 134       |

|              | 6.1   | Low-C   | ost Fabrication Techniques                            | 134       |

|              | 6.2   | Future  | e Work                                                | 135       |

| Bi           | bliog | graphy  |                                                       | 137       |

| $\mathbf{A}$ | Alg   |         | s and Methods for Inkjet Printing of Electronic Struc | c-<br>149 |

| В            | Gol   | d Nand  | ocrystal Synthesis                                    | 155       |

# List of Figures

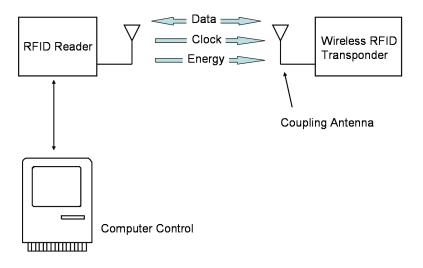

| 1.1 | Diagram of an RFID system                                                                                  | 5  |

|-----|------------------------------------------------------------------------------------------------------------|----|

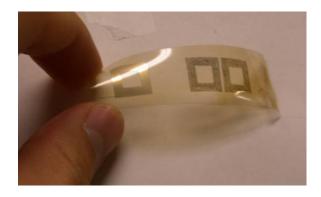

| 1.2 | Spiral inductor printed onto a flexible plastic substrate                                                  | 4  |

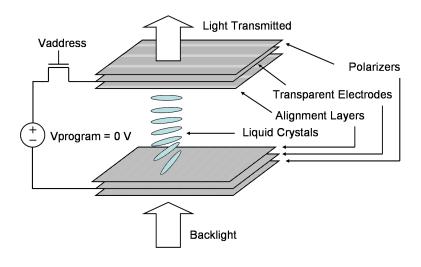

| 1.3 | A liquid-crystal pixel in the transparent state                                                            | 5  |

| 1.4 | A liquid-crystal pixel in the blocking state                                                               | 6  |

| 1.5 | Circuit diagram of an active-matrix LCD pixel                                                              | 7  |

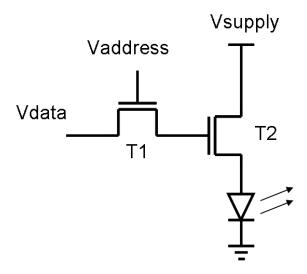

| 1.6 | Circuit diagram for an active-matrix OLED pixel                                                            | 7  |

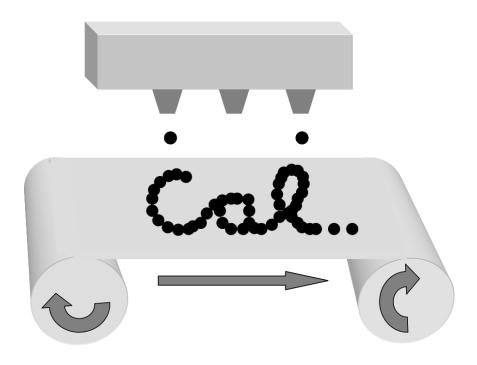

| 2.1 | Low-cost reel-to-reel fabrication system                                                                   | 10 |

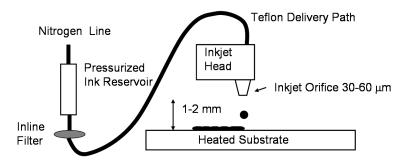

| 2.2 | Typical inkjet printer configuration                                                                       | 12 |

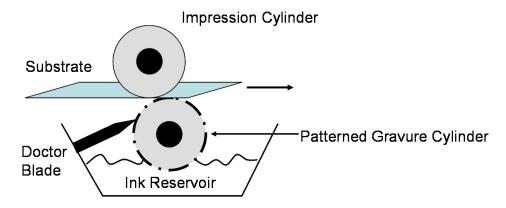

| 2.3 | A typical gravure system consisting of an ink reservoir, patterned roll, doctor blade, and impression roll | 13 |

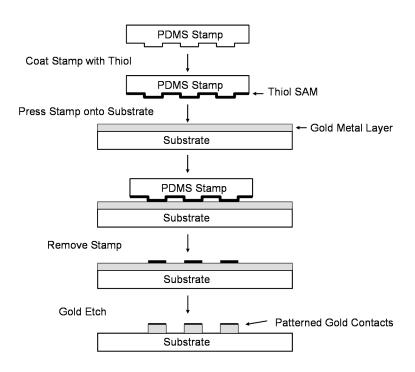

| 2.4 | High-resolution patterning of gold using a PDMS stamp                                                      | 15 |

| 2.5 | The printer used to fabricate devices in this work                                                         | 17 |

| 2.6 | (a) Gold nanocrystal showing alkane-thiol encapsulant. (b) TEM image of nanoparticles                      | 19 |

| 2.7 | (a) $\alpha$ -terpineol and (b) dihydroterpineol structures                                                | 20 |

| 3.1 | Diagram of full RFID tag including rectification and voltage regulation components                         | 24 |

| 3.2 | Magnetic flux shared by two inductors in close proximity                                                   | 26 |

| 3.3 | Circuit diagram used to evaluate the coupled voltage. $R_L$ represents the load of the tag internals       | 28 |

| 3.4 | Circuit diagram used to evaluate the coupled voltage, with resonant capacitor                              | 30 |

| 3.5 | Increase in coupled voltage due to resonant capacitor                                                      | 32 |

| 3.6 | Circuit used to calculate the RLC tank quality factor                                                      | 35 |

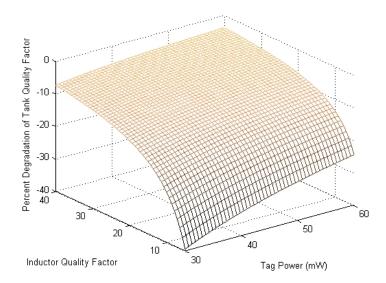

| 3.7  | Decrease in RLC tank quality factor as a function of tag power and inductor quality factor                                                                                                                               | 3 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

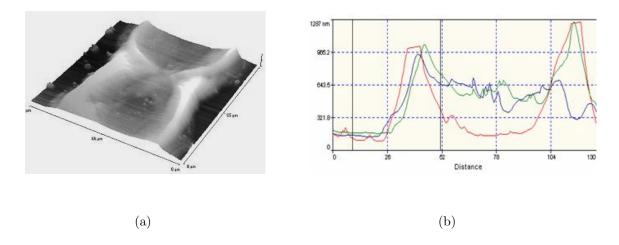

| 3.8  | (a) AFM of line printed with non-linear method showing extremely rough surface. (b) Cross section                                                                                                                        | 4 |

| 3.9  | (a) AFM of line printed with linear overlay method showing smoother surface. (b) Cross-section of smoother line                                                                                                          | 4 |

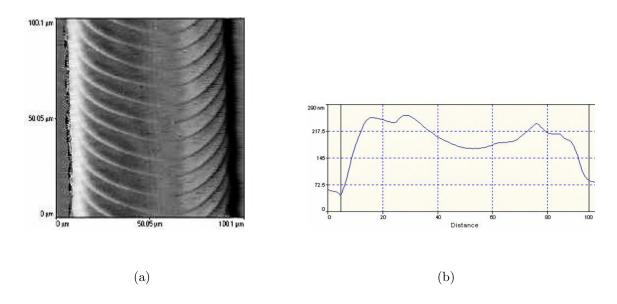

| 3.10 | Average line height plotted versus number of printed layers                                                                                                                                                              | 4 |

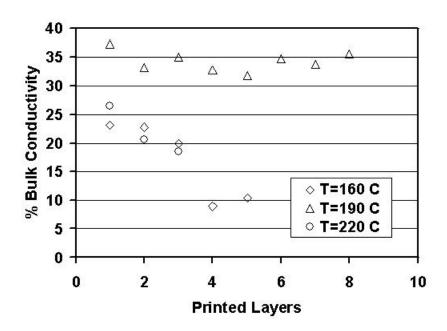

| 3.11 | Quality of printed gold as a function of bulk conductivity showing no degradation at 190 $^{\rm o}{\rm C}$ as the number of layers increases                                                                             | 4 |

| 3.12 | Inverse relationship between sheet resistance and number of printed layers at 190 $^{\rm o}$ C                                                                                                                           | 4 |

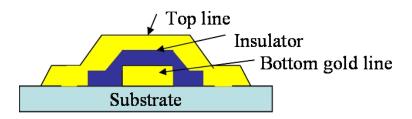

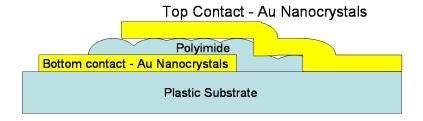

| 3.13 | Cross section of printed crossover structure enabling multi-layer inter-<br>connect                                                                                                                                      | 4 |

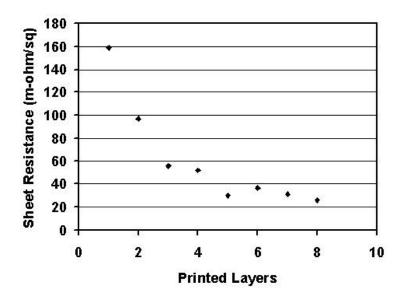

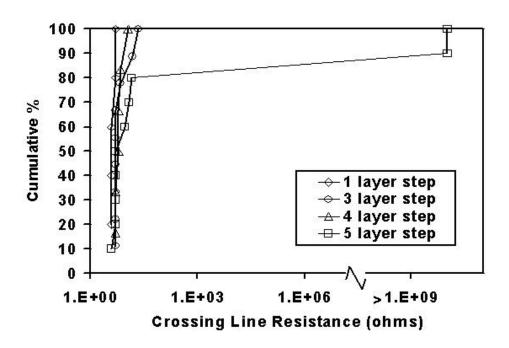

| 3.14 | Good step coverage is achieved for gold lines up to 2.5 $\mu$ m thick. Crossing line resistance represents the resistance of a line passing over another insulated line. High crossing line resistance indicates an open | 4 |

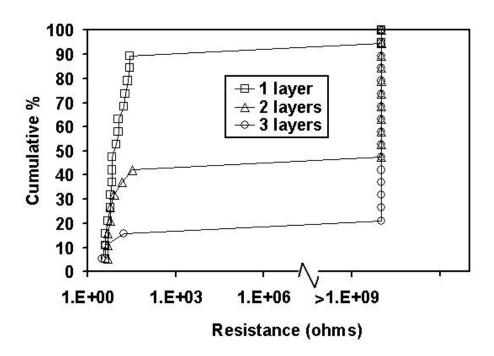

| 3.15 | Three layers of polyimide provides adequate isolation. The resistance measured is between the top and bottom conductors. High resistance indicates an open circuit and therefore good isolation                          | 4 |

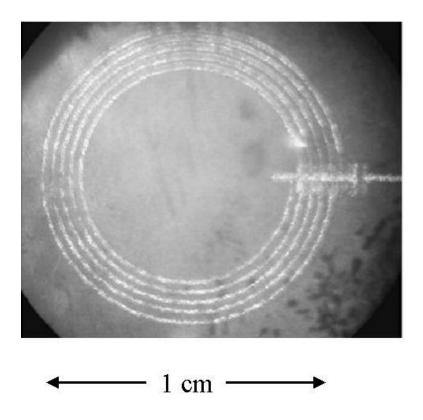

| 3.16 | 350 nH inductor complete with contact to center coil achieved using the crossover process                                                                                                                                | 4 |

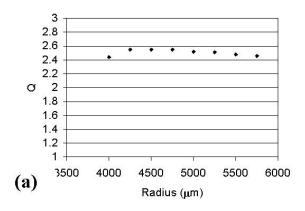

| 3.17 | (a) Simulated results showing variation of Q with inductor radius at 13.5 MHz. Realizable quality factor is fairly independent of inductor radius. (b) Quality factor decreases slightly as line spacing is increased.   | 5 |

| 3.18 | Cross-section of a printed capacitor                                                                                                                                                                                     | 5 |

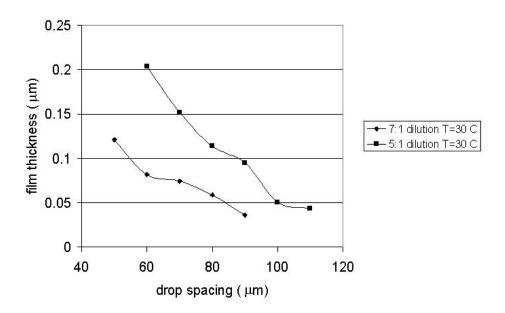

| 3.19 | Effect of drop spacing on polyimide film thickness at 30 $^{\circ}$ C                                                                                                                                                    | 5 |

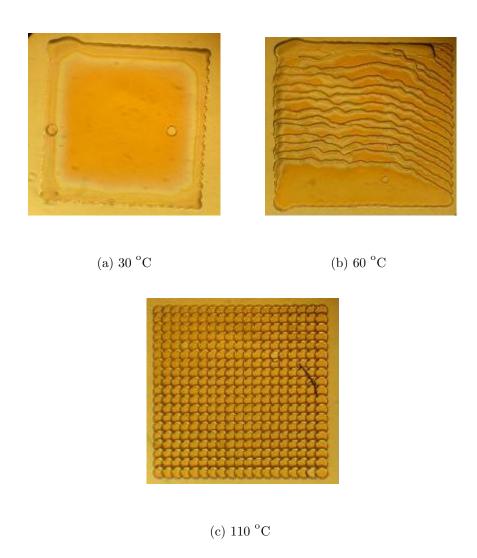

| 3.20 | Effect of substrate temperature on polyimide surface using 80 $\mu$ m drop spacing                                                                                                                                       | 5 |

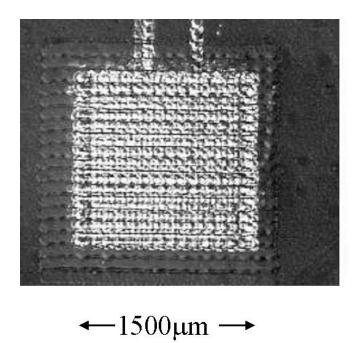

| 3.21 | All-printed capacitor fabricated on plastic                                                                                                                                                                              | 5 |

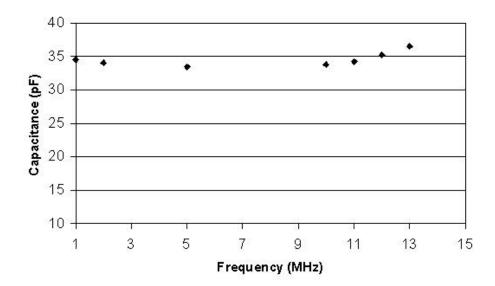

| 3.22 | Dispersion characteristics of printed capacitors. The upturn at high frequency is within the error bars of the measurement                                                                                               | 5 |

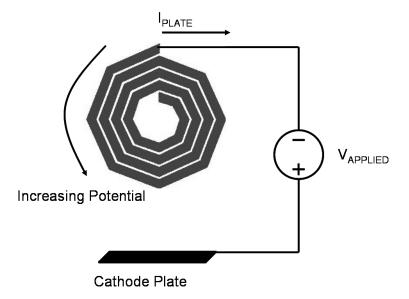

| 3.23 | Electroplating current causes a potential that opposes the applied potential                                                                                                                                             | 5 |

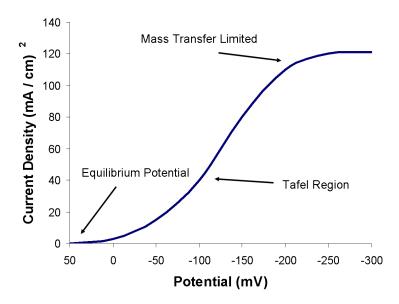

| 3.24 | Electroplating current density versus potential curve                                                                                                                                                                    | 5 |

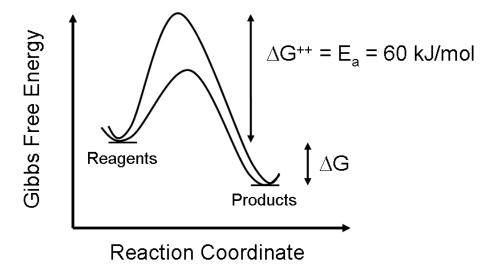

| 3.25 | Gibbs free energy diagram showing reduced activation energy in presence of metal catalyst                                                                                                                                | 6 |

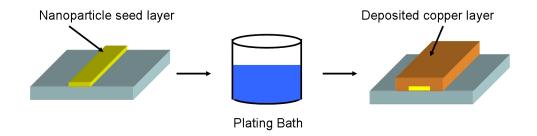

| 3.26 | Process flow for electroless plating on nanoparticle seed layer                                                                                                                                                          | 7 |

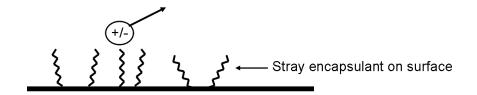

| 3.27 | Polar reagents are repelled by the non-polar encapsulant                                                                                                                                 | 71   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

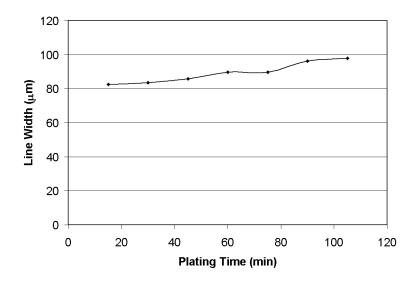

| 3.28 | Variation in line width versus plating time                                                                                                                                              | 73   |

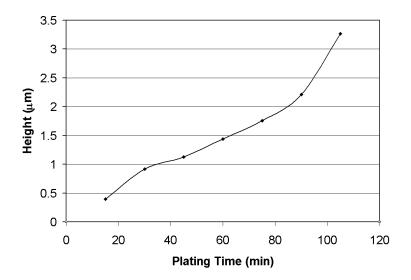

| 3.29 | Line height versus plating time. There is a linear increase in line height until approximately two hour when the bath becomes unstable. Better aeration can prolong bath life            | 74   |

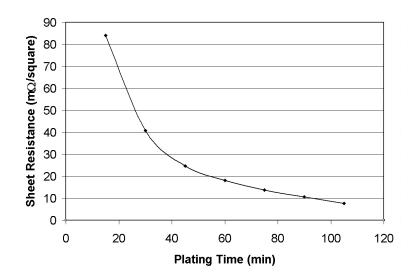

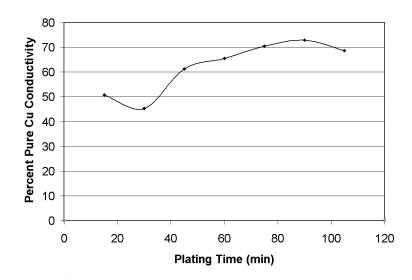

| 3.30 | Sheet resistance falls off as expected with plating time. 7.5 m $\Omega/\Box$ is achievable                                                                                              | 74   |

| 3.31 | Copper quality is excellent until the bath becomes unstable. 73 percent of bulk conductivity is achievable                                                                               | 75   |

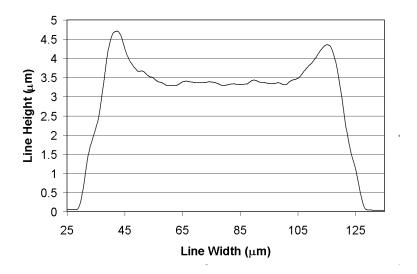

| 3.32 | Cross section of a line plated for 105 minutes. Peaks at the edges are a result of the plating reaction starting sooner, due to a higher concentration of nanoparticles on the substrate | 76   |

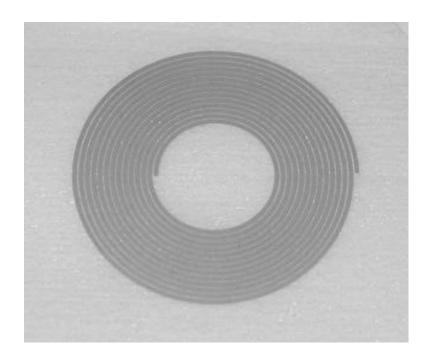

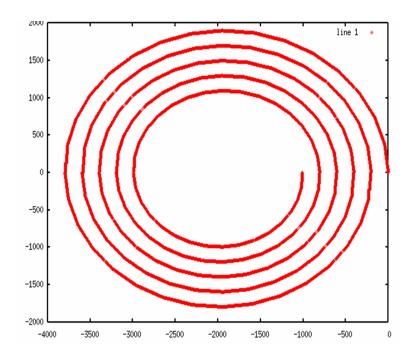

| 3.33 | $3.2~\mu\mathrm{H}$ inductor fabricated on plastic with a Q of 21.3 at 13.56 MHz.                                                                                                        | 77   |

| 4.1  | CBD deposition apparatus described by Pavaskar et al                                                                                                                                     | 83   |

| 4.2  | Structure of the complexing agent EDTA                                                                                                                                                   | 85   |

| 4.3  | Description of the SILAR process flow                                                                                                                                                    | 87   |

| 4.4  | Nicolau's apparatus designed to automate SILAR                                                                                                                                           | 89   |

| 4.5  | (a) OTS molecule used for hydrophobic surface modification. (b) FOTS                                                                                                                     | . 91 |

| 4.6  | Zinc species in solution based on pH and ammonia concentration, from (11)                                                                                                                | 95   |

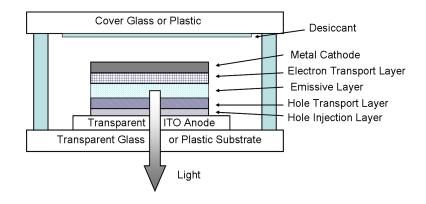

| 5.1  | Structure of the bottom emitting OLED                                                                                                                                                    | 101  |

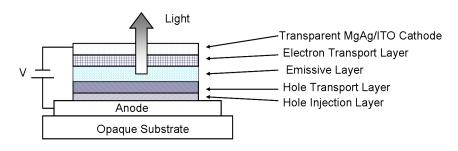

| 5.2  | Structure of the top emitting OLED                                                                                                                                                       | 101  |

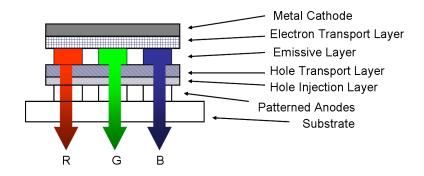

| 5.3  | Color generated by doping OLED emitting layer                                                                                                                                            | 102  |

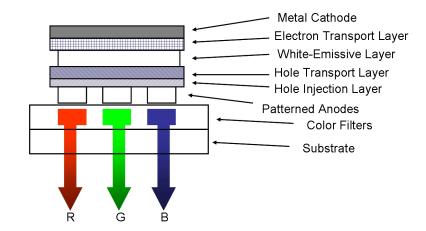

| 5.4  | Color generated with a white OLED and color filters                                                                                                                                      | 102  |

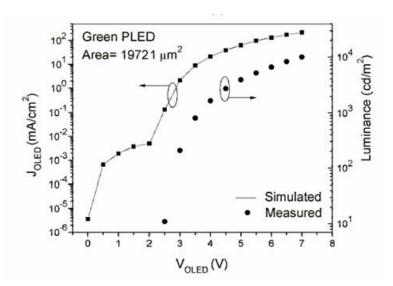

| 5.5  | Typical OLED current-voltage characteristic, from (72)                                                                                                                                   | 103  |

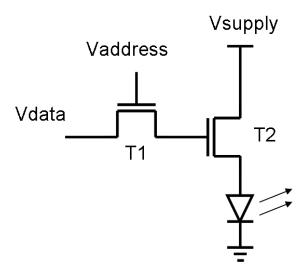

| 5.6  | Two transistor pixel design                                                                                                                                                              | 106  |

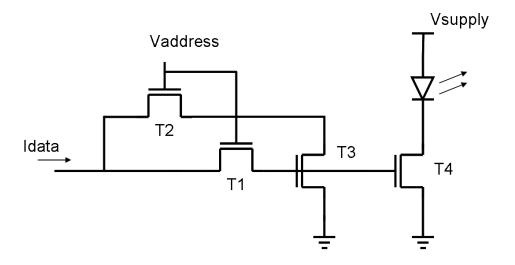

| 5.7  | Four transistor pixel design                                                                                                                                                             | 107  |

| 5.8  | As pixel size decreases the area required for pixel TFTs does not scale.                                                                                                                 | 108  |

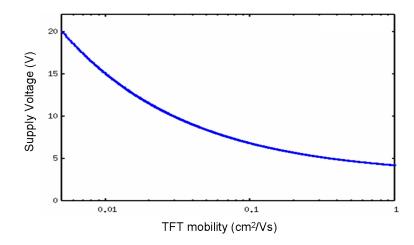

| 5.9  | Simulated TFT mobility requirements for a given supply voltage                                                                                                                           | 112  |

| 5.10 | Structure of a substrate-gated top-contact ZnO TFT test device                                                                                                                           | 115  |

| 5.11 | ID-VG curve for device annealed at 700 $^{\rm o}{\rm C.}$ $\ \ldots$ $\ \ldots$ $\ \ldots$ $\ \ldots$                                                                                    | 116  |

| 5.12 | (a) IDVG curve for device with 15 second contact anneal. (b) After an additional 1 minute contact anneal                                                                                 | 118  |

| 5.13 | Square root of drain current with extrapolated $V_{th}$                                                                                    | 120   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.14 | Dependence of mobility on bath pH                                                                                                          | 122   |

| 5.15 | Variation in deposited film thickness with bath pH for fixed deposition time, showing change in deposition rate                            | 123   |

| 5.16 | Variation in TFT mobility with anneal temperature, for bath temperature of 60 $^{\rm o}{\rm C}.$                                           | 123   |

| 5.17 | Variation in TFT mobility with bath temperature for different anneal temperatures                                                          | 124   |

| 5.18 | AFM images of CBD ZnO films after anneal                                                                                                   | 125   |

| 5.19 | Transfer characteristics for a typical CBD ZnO TFT (W/L =<br>400/100 $\mu\mathrm{m}$                                                       | ).126 |

| 5.20 | Output characteristics for the above transistor                                                                                            | 126   |

| 5.21 | Variation in TFT on/off ratio with anneal                                                                                                  | 128   |

| 5.22 | Variation in TFT on/off ratio with film thickness                                                                                          | 129   |

| 5.23 | Variation in TFT mobility with film thickness                                                                                              | 129   |

| 5.24 | ID-VG curves for a TFT with a 4.3 nm ZnO film annealed at 450 $^{\rm o}{\rm C}$ .                                                          | 130   |

| 5.25 | Structure of the Hall Effect samples                                                                                                       | 131   |

| 5.26 | Measured Hall Effect mobility versus anneal temperature                                                                                    | 131   |

| 5.27 | Hall Effect carrier concentration versus anneal temperature                                                                                | 132   |

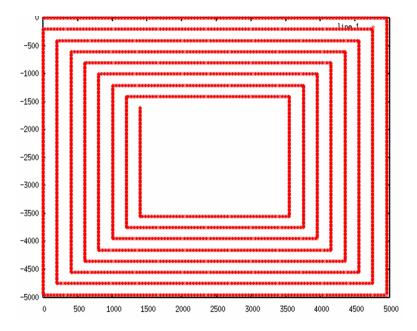

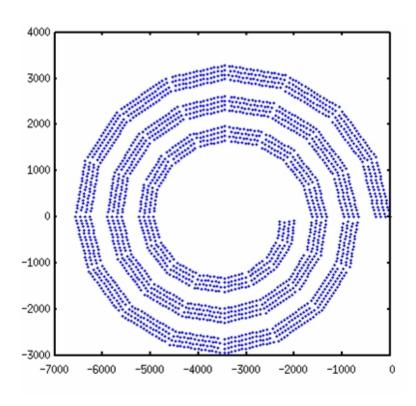

| A.1  | Output of printer file simulator showing square inductor                                                                                   | 150   |

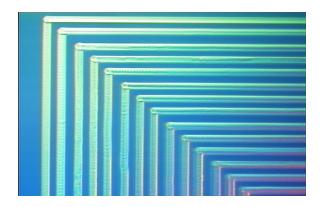

| A.2  | Close-up of actual printed square spiral structure                                                                                         | 151   |

| A.3  | The error created by rounding can be significant. The lower line was the intended one, but instead the upper line would have been printed. | 152   |

| A.4  | Spiral inductor generated using segment and shift method for almost vertical lines                                                         | 152   |

| A.5  | Drop pattern for inductors of arbitrary line width.                                                                                        | 154   |

# List of Tables

| 2.1 | Properties of nanoparticle solvents                                           | 20 |

|-----|-------------------------------------------------------------------------------|----|

| 3.1 | Field strength limitations imposed at 13.56 MHz                               | 25 |

| 3.2 | Standard reduction potentials for selected half reactions                     | 6  |

| 3.3 | Activation energies for the electroless copper process with various catalysts | 68 |

| 4.1 | SAMs used for aqueous deposition of oxides and sulfides                       | 93 |

#### Acknowledgements

In a research area that is very diverse, interaction among labmembers and other faculty is a necessity. The field of Organic Electronics, or to be more general, Low-Cost Fabrication, is certainly an example of just such an area. Our research group is primarily composed of electrical engineers specializing in device design, but we are forced to learn many topics outside our specialty. It is through our interactions with experts in other fields, such as chemistry and material science, that we gain the knowledge necessary to design, build, and test these new systems. In this respect Berkeley offers many opportunities for curious graduate students to explore new areas by encouraging so called "interdisciplinary research." Professors Ali Niknejad and Eugene Haller served on both my Qualifying Exam and Dissertation Committees, and have always been willing to give their invaluable advice.

I need to recognize the staff of the Berkeley Microfabrication Lab, especially Phill Guillory and Bill Flounders, for their assistance setting up lab equipment, answering my pestering questions, and providing me the facilities to process zinc oxide in a world of silicon. Especially Phill for installing air conditioning in our office. And for the refrigerator.

I would like to thank my labmates, of which there were many over the years, but especially Steven Volkman, Brian Mattis, Alejandro de la Fuente Vornbrock, Teymur Bakhishev, Paul and Josei Chang, Daniel Huang, and Steven Molesa. This work would not have been possible without the discussions, debates, and assistance they provided.

## Chapter 1

### Introduction

For over 40 years silicon has been the material of choice for circuit fabrication. Moore's law has been fulfilled time and time again, and today microprocessors are functioning at frequencies orders of magnitude faster than perhaps the first researchers ever imagined. Silicon circuit fabrication is one of the most reliable and well controlled processes known to man. However, silicon is quite expensive to process and package. The capital investment necessary for a new fabrication facility runs into the billions of dollars, and then it costs thousands of dollars to process each wafer.

The development of low-cost circuits, even with degraded performance, would enable the use of electronics and automated systems where they previously would be cost-prohibitive. The main premise of low-cost fabrication is the use of inexpensive materials which can be processed without the use of a cleanroom environment or special lithographic techniques. The avoidance of vacuum systems (e.g. sputtering and evaporation) is also preferred. These sacrifices come at the cost of performance, but there are many applications where the high performance of silicon is not required.

For example, amorphous silicon has become the dominant technology for active matrix display backplanes.

The low-cost fabrication of circuits must be approached from several directions. Material development, especially soluble materials, is obviously a major focus of current research, but there are also challenges in deposition and patterning methods. Much of the work in this thesis focuses on the use of inkjet printing as a patterning tool because of its flexibility, capacity for large area throughput, and compatibility with a large number of soluble materials. However, significant challenges remain in the development of printable metals and semiconductors. Alternatives to inkjetting alone are proposed and examined in detail. A major focus of this work is the development of a hybrid approach where inkjet printing is used to define an area rather than deposit electrically active materials. This approach is shown to give far superior results compared to inkjet printing alone. The use of aqueous deposition methods in combination with inkjet patterning has been investigated for both metal and semiconductor materials.

The poster child of the low-cost fabrication field has been Radio Frequency Identification (RFID), with the intention of replacing the ubiquitous Universal Product Code (UPC) barcodes. However, low-cost fabrication techniques could also be applied to supply developing nations with electronics for display or other applications. It is this market segment, where the ultra-high performance of silicon is not required, where low-cost techniques become economically advantageous. In the following sections the specific motivation for considering application of printed electronics to RFID and displays will be considered in more detail.

Figure 1.1. Diagram of an RFID system.

#### 1.1 Radio Frequency Identification

Low-Cost RFID tags would allow the replacement of UPC barcodes with a wire-less system, which would allow faster checkout and inventory. The system, depicted in Figure 1.1, consists of a computer-controlled reader antenna, and the RFID tag itself. At lower communication frequencies (such as 13.56 MHz) data and power are transferred via a coupling magnetic field. At higher frequencies (above 900 MHz) communication occurs via an electromagnetic field. Since the reader is plugged into a power outlet its functionality is not limited by power consumption, circuit speed, or cost since each implementation typically has only a few readers. In contrast, the tags are limited by power and cost.

In order to be economically viable as a replacement for UPC barcodes these tags have to be manufactured cheaply, typically for less than one cent per tag (124). A fabrication method that does not involve expensive processes or the use of silicon substrates is highly desirable. The development of a solution-based process on a flexible substrate would allow reel-to-reel fabrication, which is an extremely inexpensive

Figure 1.2. Spiral inductor printed onto a flexible plastic substrate.

way to mass-produce circuits since it eliminates vacuum processing, lithography, and subtractive processing steps.

Passive components such as inductors and capacitors are required on the RFID tag because they are used in circuits such as filters, oscillators, and memory, and also for power transfer. Inductive coupling is used to transfer power from a reader to a RFID tag. The tag inductor is placed in the near field of a reader coil, causing a voltage to be induced on the tag inductor. Typically a capacitor is put in parallel with the tag inductor to create a resonant circuit, in order to boost the tag voltage at the tuned frequency. This voltage is then rectified and used as the DC source for any analog or digital processing necessary for communication. High quality components are needed to allow adequate communication range. The main challenge in building high quality inductors is reducing the sheet resistance of the metal layer, because resistance is the dominant loss mechanism at low frequencies.

The development of passive devices suitable for use in a RFID system operating in the 100 kHz to 15 MHz range is the subject of the first half of this thesis. Inductors, capacitors, and interconnect are fabricated on flexible plastic substrates. After an analysis of the performance requirements of the coupling inductor an improved inductor process that combines inkjet printing and electroless copper plating is described.

Figure 1.3. A liquid-crystal pixel in the transparent state.

#### 1.2 Transparent TFTs for Display Applications

Thin-film transistors (TFTs) have been used in active-matrix liquid crystal display (LCD) backplanes for decades. Each pixel of LCD (shown in Figure 1.3) contains at least one TFT that acts as a switch to program the liquid-crystal (LC) material. The pixel itself consists of a linear polarizer, transparent electrode, alignment layer, liquid-crystal material, then another alignment layer, transparent electrode, and polarizer oriented 90 degrees relative to the first. As light from a backlight passes through through the display it is either allowed to pass, or is blocked by the opposed polarizers. The LC material is chiral, and will rotate the polarization of the incident light if no bias is applied, thus aligning the light polarization with the second polarizer and allowing it to pass. If a bias is applied, the LC molecules will align with the applied field and not rotate the light. This results in a dark pixel (Figure 1.4).

Transistors fabricated from amorphous silicon ( $\alpha$ -Si) have found wide application in LCDs, and processing cost has been reduced to a point where a high-resolution LCD display can be fabricated for a few hundred dollars. A typical active-matrix pixel circuit diagram is shown in Figure 1.5. When the gate bus line is activated the

Figure 1.4. A liquid-crystal pixel in the blocking state.

TFT samples the voltage on the data bus line and programs the liquid crystal cell with voltage  $V_A$ . Amorphous silicon is well suited to this task because the power consumption of the display is dominated by the dynamic power associated with charging the cell. There is no static power consumption, and thus, the high drive voltages required are tolerable.

However,  $\alpha$ -Si is not well suited for other types of displays such as those fabricated from organic light-emitting diodes (OLEDs). The cross-section of an OLED pixel is much simpler because the OLED is an emissive device, and no polarizers or backlight is needed. A simple circuit diagram is shown in Figure 1.6. An OLED is a current-driven device, and requires a static current for emission.  $\alpha$ -Si simply cannot provide enough current without the use of high supply voltages. This results in displays with unacceptably high power consumption. Increasing the size of the TFT is not a viable solution because it would consume too much of the pixel area, requiring higher OLED brightness and resulting in decreased device lifetime.

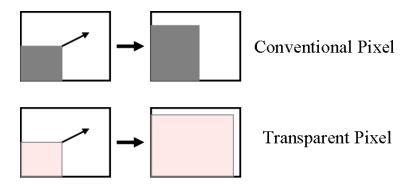

A solution to this problem that many people have pursued is the fabrication of transparent transistors that consume the entire pixel area without significantly impacting display brightness. By taking advantage of the larger area available for

# Data Bus Line C<sub>S</sub> T C<sub>LC</sub> Gate Bus Line

Figure 1.5. Circuit diagram of an active-matrix LCD pixel.

Figure 1.6. Circuit diagram for an active-matrix OLED pixel.

device layout the operating voltage, and hence display power, can be reduced to acceptable levels.

#### 1.3 Organization

In Chapter 2 the deposition of electronic materials using printing techniques is discussed, with a focus on specific materials used for inkjet printing. A background of RFID operation is given in Chapter 3, with a detailed analysis of the performance requirements for the coupling inductor of an RFID tag. The results of an all-inkjetted passive component process for RFID fabricated at low temperature on plastic substrates are shown. Simulation results show that even in the best-case scenario printing alone cannot generate inductors suitable for RFID, so Chapter 3 concludes with an improvement to the process that uses an aqueous deposition combined with inkjet printing to fabricate high quality components. The aqueous deposition of semiconductor and insulator materials is the subject of Chapter 4, with a focus on zinc oxide. Chapter 5 provides a background of the use of TFTs in active-matrix displays, and gives an analysis of the performance requirements of a transparent TFT for use in active-matrix organic light-emitting diode (AM-OLED) displays. After motivating the use of transparent zinc oxide, Chapter 5 presents the first demonstration of zinc oxide thin-film transistors fabricated using an aqueous deposition of the semiconductor layer. Finally, Chapter 6 provides conclusions and insight into the future directions of this work.

## Chapter 2

# **Printing Technology**

#### 2.1 Introduction

In recent years there has been a great deal of interest in alternative patterning methods. Cost models show that the highest throughput fabrication systems will be reel-to-reel, necessitating the use of flexible substrates and all-additive processing steps. Several printing techniques have been developed or adapted to suit device manufacture. Of these the most promising appear to be inkjet printing, gravure printing, and microcontact printing. In this chapter the different printing techniques are discussed, followed by a brief overview of the inkjet printer and techniques used in this work.

#### 2.2 Reel-to-Reel Fabrication

Reel-to-reel fabrication is the ultimate low-cost fabrication scheme. Throughput is extremely high in part because it is compatible with large-area substrates. Ide-

Figure 2.1. Low-cost reel-to-reel fabrication system.

ally flexible substrates such as plastic are used so they can be stored in rolls. As depicted in Figure 2.1, processing is done by sequential additive processing steps. However, there are practical limitations regarding what types of processing can be achieved. Plastic is a convenient low-cost substrate material that is highly available, non-conductive, and flexible. However it has several drawbacks. Plastic is generally limited to temperatures below 200 °C, and those that are stable at high temperatures are significantly more expensive than conventional plastics. Plastic also tends to shrink under elevated temperatures, which can make alignment difficult. Also, processing is limited to steps that do not require vacuum. While in theory a reel-to-reel system could be placed in a vacuum environment, in practice it would be difficult to integrate the vacuum steps with non-vacuum steps and still maintain the cost benefits of a reel-to-reel process. Therefore printing techniques such as inkjet, gravure, and microcontact are promising.

#### 2.3 All-Additive Processes

Traditional lithography and patterning techniques require several steps: spinning photoresist, pre-bake, exposure, development, post bake, etch, and finally a photoresist strip. Each step adds to the cost of the process by increasing the time required and by decreasing yield. There is also substantial material wasted when entire wafers are coated with photoresist or other material (for instance, polysilicon or aluminum) and then a majority of the material is removed after patterning. Not only does this consume more material than necessary, but the excess material must be disposed of properly, adding additional cost. An all-additive process is defined as one where no material is removed after deposition. This dramatically cuts down on cost because material is only deposited where it is needed.

#### 2.4 Printing Methods

In order to realize an all-additive process a method of selectively depositing the material is needed. Printing techniques have been used for centuries for the selective deposition of inks, and are seen as a logical choice for the selective deposition of "electronic ink." The main techniques are inkjet, gravure, and microcontact printing. The advantages and disadvantages of each is discussed below, with regard to resolution, material compatibility, and flexibility of design.

#### 2.4.1 Inkjet Printing

Inkjet printing has been used in manufacturing processes such as food packaging (potato chip bags), and of course has found wide application in the computer industry. A typical configuration is shown in Figure 2.2. The throughput is determined

Figure 2.2. Typical inkjet printer configuration.

mainly by the number of print heads and the volume of material required. Epson inkjet printers for desktop use have around 80 individual orifices, and a commercial configuration may have thousands. Inkjet heads specifically developed for electronics by Dimatix Inc. have 128-256 individually controlled orifices with resolution up to 900 dpi. That translates to a drop size of approximately 30  $\mu$ m. The minimum feature size is determined by the accuracy with which the drops can be placed rather than the drop size. Dimatix has achieved drop accuracy of 2  $\mu$ m, which would allow fabrication of a TFT with a channel length of a few microns.

Material compatibility is excellent with inkjet. Both aqueous and organic materials can be used depending on the ink delivery path. The heads themselves are piezoelectric and fabricated out of glass or silicon micromachined. As Table 2.1 shows, inkjet is compatible with a wide range of ink viscosity, ranging from less than 1 to over 40 cP, again increasing the range of material compatibility. This is a clear advantage for inkjet printing over other methods such as gravure, which require higher viscosities of approximately 30-100 cP. Typically polymer binders are used to increase ink viscosity, but these materials are typically highly resistive, and the resulting deposited layer is a mixture of desired material and binder. Thus, the overall resistance of the material is increased. Since inkjet is not as dependent on viscosity as other methods, the use of binders is not required (130).

Figure 2.3. A typical gravure system consisting of an ink reservoir, patterned roll, doctor blade, and impression roll.

From a development standpoint inkjet printing is extremely flexible. Designs can be modified simply by changing computer code, rather than having to modify a master pattern such as a photolithographic mask or gravure roll.

#### 2.4.2 Gravure

Gravure is a high-throughput printing technique that has been used for food labels, magazines, and wallpaper. Inherently compatible with a reel-to-reel process, gravure is currently being investigated for the deposition of electronic materials. The apparatus is shown in Figure 2.3. The patterned roll is typically made from copper and patterned with small hexagonal wells. As the roll is drawn through the reservoir it is covered in ink. A doctor blade then removes excess ink, leaving ink only in the wells. The patterned roll then comes into contact with the substrate under pressure from a second roll and the ink is transferred to the substrate.

To date, the smallest wells fabricated on a copper roll are approximately 50  $\mu$ m in diameter. During the impression the ink spreads slightly resulting in a feature of 60-80  $\mu$ m. Thus the minimum feature size is on the order of 50  $\mu$ m, much greater than the resolution of inkjet. Both organic and aqueous inks are compatible with gravure, but

high-viscosity materials are not easily transferred from the cylinder to the substrate. The result is an incomplete pattern with possible voids in lines that were intended to be continuous. Inks that are not viscous enough will not be completely removed by the doctor blade and will result in excess ink deposited on the substrate. Therefore gravure is considered more sensitive to ink viscosity than inkjet.

While the throughput of gravure is higher than inkjet the initial cost is significantly higher. The equipment itself is expensive, and each copper roll must be fabricated at a cost of several thousand dollars. In a production environment this is not a large concern, but it makes for expensive experimentation.

#### 2.4.3 Microcontact Printing

Microcontact printing is analogous to stamping, but with a very high resolution stamp. Traditional silicon lithographic techniques are used to create a master pattern on a silicon wafer with features approximately 500 nm to 1  $\mu$ m in height, which is then used to create a stamp, typically out of the polymer polydimethylsiloxane (PDMS). The stamp is then coated with an "ink" that it transfers to the substrate during patterning. The process is quick, requiring only about ten seconds to transfer the material to the substrate (133). Alkanethiols are typically used as the "ink" because they transfer very well and adhere well to gold (and other metal) substrates (70). Microcontact printing has been used to pattern source and drain contacts for organic thin-film transistors with channel lengths of approximately 100 nm (69), demonstrating that high-resolution printing is possible so long as the substrate is very smooth. The tradeoff, however, is compatibility with large-area substrates. Uniformity of transfer over large area is difficult when using flexible substrates, due to the need to apply uniform pressure without flexing the substrate. In addition, the stamp size is

Figure 2.4. High-resolution patterning of gold using a PDMS stamp.

limited to approximately the diameter of a silicon wafer. Contamination can also be a concern, as with any technique requiring contact to the substrate.

The stamp fabrication process is not complex and although it requires silicon processing to create a master pattern, this pattern only needs to be made once. Several PDMS stamps can be patterned from the master. The process starts by coating a silicon substrate with a monolayer of vinyloctadecyltricholorosilane, then defining a pattern using e-beam lithography using polymethylmethacrylate (PMMA) as a mold for the precursor to PDMS. The PMMA is coated with dodecyltrichlorosilane before deposition of the PDMS precursor to ensure release of the stamp after curing. Curing is done at room temperature to prevent shrinkage (which results in distortion of the pattern) at approximately 8 bar pressure for 5 hours (69). The resulting PDMS layer should be 2  $\mu$ m thick, or approximately twice the height of the master-defined pattern.

There are several variations on this theme. Offset liquid embossing (OLE) is sim-

ilar to microcontact printing, but the stamp is used to create a pattern in a blanket-deposited film rather than transfer material. After the pattern has been created another substrate is pressed onto the original, and the film transfers. This technique has been used to pattern nanoparticle films and spin-on-glasses (142), however, the resolution is somewhat less than microcontact printing with a minimum feature size of approximately 2  $\mu$ m. A second variation uses thermal imaging to transfer the organic conductor DNNSA-PANI/SWNT for use as organic transistor source and drain electrodes (8). Not surprisingly, this technique has degraded resolution of approximately 20  $\mu$ m.

#### 2.5 Description of Custom Inkjet System

The printer used to deposit materials in this work is a custom drop-on-demand design with a temperature-controlled vacuum chuck so drops may be deposited onto a heated substrate (Figure 2.5). The ability to jet onto heated substrates is important since it enables greater flexibility in the control of surface fluid viscosity and evaporation rate. Elevated substrate temperatures reduce the amount printed materials spread after contacting the substrate, and also effects adhesion of some materials such as polyimide.

The delivery path consists of a pressurized Teflon reservoir, Teflon tubing, an inline filter, and finally the glass inkjet head (See Figure 2.2). Teflon is an excellent choice because it is very resistive to organic solvents (unlike most plastic tubing) and it is transparent, allowing the user to easily see air bubbles or other problems with the line. Stainless steel is also another good choice in terms of material compatibility, but it is then difficult to diagnose problems. The in-line filter is extremely important to avoid clogged heads from dust or other small particles. The pore size was 5  $\mu$ m,

Figure 2.5. The printer used to fabricate devices in this work.

which allowed nanoparticle solutions to flow through without too much pressure, and effectively eliminated clogs in the head from dust particles. Head clogging resulting from nanoparticles drying inside or at the tip of the head was still a problem, but manageable again by the choice of solvent and substrate temperature.

The printer is enclosed in a nitrogen box so that inert atmospheres can be used. Since the printed materials used in this work were not oxygen sensitive all printing was done in air. Now that the different printing techniques have been discussed and a detailed description of the inkjet system used here has been given, it is appropriate to discuss the specific inks used to deposit metal layers. Gold nanoparticles that are soluble in organic solvents can be printed to form conductive gold, and this technique is used extensively in this work. These nanoparticles are discussed in detail in the next section, followed by a discussion of the various solvent choices, and finally a survey of the available flexible plastic substrates used for the fabrication of ultra-low-cost devices.

#### 2.6 Gold Nanoparticles

The deposition of metals is typically done via sputtering or thermal evaporation. However, these processes are blanket depositions, require vacuum, and in the case of thermal evaporation, require very high temperatures. None of which is compatible with an all-additive low-cost process. Therefore a metallic "ink" is necessary to selectively deposit metals. This is achieved by printing layers of metallic nanoparticles.

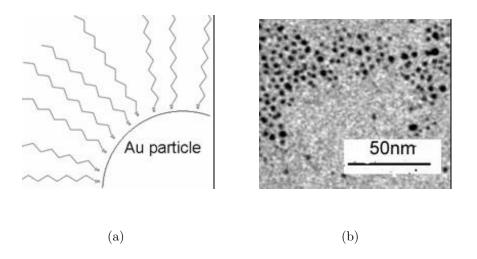

Gold nanoparticles were used for the majority of this work, although processes for many other metals including silver and copper exist. Gold nanoparticles are made using a wet chemical process, where gold is encapsulated with an alkane thiol, depicted in Figure 2.6(a).

A TEM image of the nanocrystals is shown in Figure 2.6(b). The encapsulant keeps the gold particles separate from each other, and also makes them soluble in organic solvents, allowing the particles to be printed. Once deposited, the nanocrystals are heated, the thiol burns off, and the gold particles anneal together. Due to the extremely large surface area to volume ratio of these particles the melting temperature is approximately 130 °C, which is significantly lower than the 1000 °C bulk melting temperature of gold. This low processing temperature enables the use of flexible plastic substrates. When combined with an inkjet printer, nanocrystals are used to create gold patterns on plastic substrates.

The concentration of alkane thiol determines the nanocrystal size, and the length of the alkane chain determines the temperature at which the thiol burns off. Optimal results were found using hexane thiol, resulting in nanocrystals approximately 2 nm in diameter (50; 51). The process for making gold nanocrystals is given in Appendix B.

Figure 2.6. (a) Gold nanocrystal showing alkane-thiol encapsulant. (b) TEM image of nanoparticles.

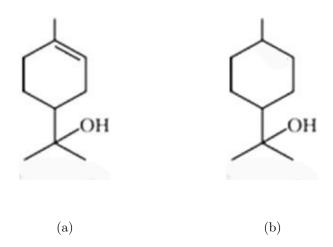

### 2.7 Solvent Choice

Additional process margin is obtained through careful choice of the solvent used, with particular attention paid to solvent viscosity (to produce stable droplets) and evaporation rate (to minimize in-head clogging). The solvent used for a majority of this work,  $\alpha$ -terpineol, printed cleanly due to its high viscosity, and also worked well over a heated substrate because of its high boiling point (94). If a material with low boiling point is used the solvent will evaporate while it is still in the head, leading to a buildup of material and eventually a clogged head. All devices presented in this work were fabricated using a 60  $\mu$ m head manufactured by MicroFab Technologies, Inc. (3). This head has an all-glass delivery path, making it compatible with a wide range of solvents, and uses a piezo-based actuation mechanism that is compatible with the inks and temperatures used herein.

The alkane chains that encapsulate the gold particle are non-polar, and therefore make the particles soluble in non-polar solvents such as toluene and butylbenzene. However, the solvent needs to be fairly viscous to print cleanly, and also needs to

Table 2.1. Properties of nanoparticle solvents

| Solvent             | Boiling Point(°C) | Vapor Pressure (Torr) | Viscosity (cP) |

|---------------------|-------------------|-----------------------|----------------|

| Toluene             | 110               | 28.5                  | 0.59           |

| Butylbenzene        | 183               | 1.06                  | 0.95           |

| $\alpha$ -terpineol | 217               | 0.1                   | 39.23          |

| Dihydroterpineol    | 199               | N/A                   | N/A            |

have a high boiling point to print over a heated substrate. If a material with low boiling point is used the solvent will evaporate while it is still in the head, leading to a buildup of material and eventually a clogged head. Two solvents,  $\alpha$ -terpineol shown in Figure 2.7(a), and dihydroterpineol shown in Figure 2.7(b), were found to have excellent printing properties.

Figure 2.7. (a)  $\alpha$ -terpineol and (b) dihydroterpineol structures.

Note that  $\alpha$ -terpineol is not a toluene derivative and that it is actually an alcohol, but has sufficient non-polar character to solubilize the nanocrystals. A summary of solvent properties is shown in Table 2.1. Dihydroterpineol has very similar properties to  $\alpha$ -terpineol (and can be produced via hydrogenation of  $\alpha$ -terpineol with a platinum catalyst) but exact numbers for vapor pressure and viscosity were not available.

Now that gold nanoparticles and the solvents used to print them have been discussed, the available plastic substrates are presented. There are several types of plastic, each with different thermal and chemical properties, with more desirable properties generally costing more.

### 2.8 Plastic Substrates

The plastics commonly used as substrates are Polyethylene Terephthalate (PET) and Polyethylene Naphthalate (PEN). PET is used to make soft drink bottles, but is permeable to oxygen, which drove the development of PEN. PEN is a superior oxygen barrier, making it suitable for packaging perishable foods such as beer. In general PEN has a higher temperature stability, and has a glass transition temperature of 120 °C, compared to 80 °C for PET (95). Plastics are available with temperature compatibility up to 350 °C, for instance, DuPont's Kapton polyimide films. However, these films are extremely expensive compared to the lower-temperature plastics, so processing temperature should be kept as low as possible.

The best performing substrate with respect to melting temperature and gold adhesion for our purposes was found to be Melinex (35), a polyester made by DuPont Teijin Films. The glass transition temperature was in excess of 220 °C, and gold adhered well.

### 2.9 Conclusion

Inkjet printing, gravure, and microcontact printing are all capable of patterning electronic materials. To date, microcontact printing has shown the highest resolution, but inkjet printing is compatible with a wider range of materials. It is also easier to

prototype systems than with gravure because the design can be easily changed in computer code rather than having to create a new gravure roll. Thus, inkjet was the method of choice for this work. Having provided an introduction to printing technology, it is now possible to investigate applications of printing to specific problems in low-cost electronics. In the next chapter, the use of printing in the fabrication of passive components for low-cost RFID is investigated.

### Chapter 3

## Printed Passive Components for

### **RFID**

### 3.1 Introduction

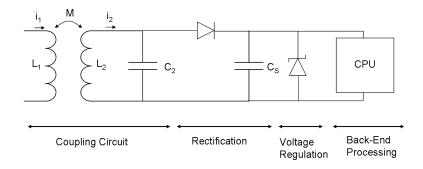

An RFID tag consists of three main components: the passive front-end that contains an inductor and capacitor, a rectification and voltage regulation system, and finally the back-end circuitry which is responsible for doing calculations, encryption, data storage, barcode comparison, or anti-collision, depending on the application (Figure 3.1). In this work the focus is on the fabrication of the passive front-end using patterning technology, materials, and temperatures that are compatible with a low-cost plastic substrate.

Figure 3.1. Diagram of full RFID tag including rectification and voltage regulation components.

### 3.2 Theory of RFID Coupling

RFID tags in the 13.56 MHz band use inductive coupling for power and information transfer between the reader and tag. The 13.56 MHz band is ideal for low-cost RFID systems because reader output power is maximized based on FCC specifications, and better range is achieved in metal contaminated environments (36). The tag must be in the near field of the reader antenna, typically  $\lambda/2\pi$ , or 3.5 meters at 13.56 MHz. In this scheme the reader and tag inductors are intimately connected by a magnetic field. The tag inductor receives information and power from the reader, and via load modulation can affect the current in the primary, thus transferring information back. The principles of this scheme are covered in the next sections.

### 3.2.1 Power Constraints

The useful range of the tag is governed by the ability of the tag to generate a supply voltage for its back-end circuitry. If the supply drops below a defined minimum logic circuits will fail to operate properly. The Federal Communications Commission (FCC) (33) limits the electric field strength that may be emitted by the reader. At frequencies between 13.553 MHz and 13.567 MHz the maximum electric field  $(E_{max})$

Table 3.1. Field strength limitations imposed at 13.56 MHz.

| Location      | Field Measured | Field Limit                     | At Distance |

|---------------|----------------|---------------------------------|-------------|

| United States | $E_{max}$      | $10,000 \; \mu V/m$             | 30 m        |

| Europe        | $B_{max}$      | $42~\mathrm{dB}\mu\mathrm{A/m}$ | 10 m        |

| Japan         | $E_{max}$      | $47,544 \; \mu V/m$             | 10 m        |

measured at a distance of 30 meters is  $10,000 \mu V/m$  (1). This can be converted to maximum magnetic field  $(B_{max})$  using the relationship:

$$\frac{E_{max}}{B_{max}} = v \tag{3.1}$$

where v is the velocity of propagation given by:

$$v = \frac{c}{\sqrt{\mu_r \epsilon_r}} \tag{3.2}$$

where c is the speed of light,  $\mu_r$  is the relative permeability, and  $\epsilon_r$  is the relative permittivity. The value of  $B_{max}$  is more useful than  $E_{max}$  because the tag and reader transfer power and information via the magnetic field.

While the FCC regulates emissions in the United States, there are separate rules governing emissions in Europe (32) and Japan. Table 3.1 describes the major differences between the regulations (31; 84). They are, however, all equivalent.

### 3.2.2 Mutual Inductance

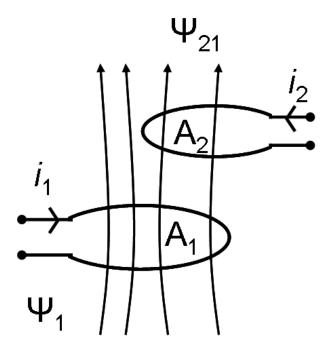

It is useful to think of the reader and tag inductors as a transformer with a very low coupling coefficient (typically 0.01 to 0.05). Current in the primary will create a magnetic field, which will induce a current (and hence a voltage) on the secondary. This scheme is depicted in Figure 3.2.

Figure 3.2. Magnetic flux shared by two inductors in close proximity.

The magnetic flux  $\Phi$  is related to the magnetic field by:

$$\Phi = BA \tag{3.3}$$

where B is the magnetic field, and A is the area of the inductor. If the inductor has n turns then it is more useful to refer to the total flux  $\Psi$ :

$$\Psi = n\Phi \tag{3.4}$$

Inductance L relates the total flux to the current in the inductor:

$$L = \frac{\Psi}{I} \tag{3.5}$$

The coupling between two inductors can be represented by the mutual inductance, which is a measure of the flux shared by the two inductors.

$$M_{21} = \frac{\Psi_{21}(I_1)}{I_1} = \oint_{A_2} \frac{B_2(I_1)}{I_1} dA_2 \tag{3.6}$$

If there are only two inductors in the system then a single mutual inductance is sufficient to describe the system:

$$M_{21} = M_{12} = M (3.7)$$

While the mutual inductance is significant, it does not give a feel for how intimately the inductors are coupled because several factors, including the layout and physical size of the inductor influence the shared flux. The coupling coefficient k gives a number between 0 and 1 that describes the extent of the coupling.

$$k = \frac{M}{\sqrt{L_1 L_2}} \tag{3.8}$$

Inductors that are not coupled will have a coupling coefficient of 0, and inductors that are perfectly coupled (and share all magnetic flux) have a coupling coefficient of 1.

### 3.2.3 Induced Voltage

Faraday's Law states that the induced voltage on an inductor is equal to the negative time rate of change of the flux. This can be used to calculate the voltage

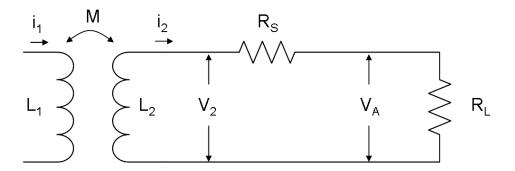

Figure 3.3. Circuit diagram used to evaluate the coupled voltage.  $R_L$  represents the load of the tag internals.

induced on the tag inductor, which is the value that determines the available supply voltage (and hence the range) of the tag.

$$V_i = \oint_C E_i dl = \frac{-d\Psi}{dt} = -N \frac{d\Phi}{dt}$$

(3.9)

Of course no inductor is ideal and has an associated series resistance. Although this resistance is distributed throughout the entire structure it is usually modeled as a discrete resistor in series with the inductor. This resistor affects the available supply voltage, and is depicted in Figure 3.3. Reducing the effect of this resistance is the subject of Section 3.6.

The voltage  $V_2$  across inductor  $L_2$  consists of two parts. The first is due to the incident flux and is given by Faraday's Law:

$$V_{2a} = -N\frac{-d\Phi}{dt} = M\frac{di_1}{dt} \tag{3.10}$$

Since the tag inductor is part of a closed circuit, a current  $i_2$  will flow and generate

a magnetic flux which opposes the incident flux. This resulting flux also creates a voltage:

$$V_{2b} = -L_2 \frac{di_2}{dt} \tag{3.11}$$

The total voltage across the inductor is then a superposition of the two induced voltages:

$$V_2 = M \frac{di_1}{dt} - L_2 \frac{di_2}{dt} (3.12)$$

From here is it simple to derive the supply voltage available to the internals of the tag, denoted  $V_A$ .

$$V_A = M \frac{di_1}{dt} - L_2 \frac{di_2}{dt} - i_2 R_s \tag{3.13}$$

Typically when analyzing these types of linear time-invariant circuits it is useful to take advantage of the Laplace Transform to convert from the time domain to the frequency domain. The task of solving differential equations is reduced to algebraic equations, greatly simplifying the math. In the frequency domain:

$$V_A = j\omega M i_1 - j\omega L_2 i_2 - i_2 R_s \tag{3.14}$$

Using the equation  $V_A = i_2 R_L$ , the above equation can be simplified to a form which relates  $V_A$  to the current in the primary, the mutual inductance, and component parameters.

$$V_A = j\omega M i_1 - j\omega L_2 \frac{V_A}{R_L} - R_s \frac{V_A}{R_L}$$

$$(3.15)$$

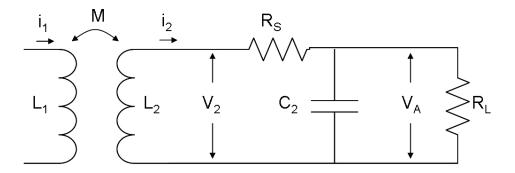

Figure 3.4. Circuit diagram used to evaluate the coupled voltage, with resonant capacitor.

$$V_A = \frac{j\omega M i_1}{1 + \frac{j\omega L_2 + R_s}{R_L}} \tag{3.16}$$

For RFID systems operating at 13.56 MHz,  $R_L$  is typically a few kilohms,  $R_s$  is a few ohms to tens of ohms, the inductor is a few microhenries, and the coupling factor  $\kappa$  is 0.01-0.05. These values are useful to keep in mind when simplifying equations derived in the next section.

### 3.2.4 Using Resonance to Boost the Supply Voltage

Since the range of the tag depends on the ability to couple a minimum supply voltage it is important to make the available voltage  $V_A$  as high as possible. A simple way employs resonance by adding a capacitor in parallel with the tag inductor, shown in Figure 3.4. The resulting RLC resonant tank will boost the available voltage by a factor equal to the quality factor (Q) of the tank. The tank quality is proportional to the energy stored over the energy dissipated per cycle, and is discussed in detail in Section 3.3.

The value of the capacitor is chosen to resonate with the inductor.

$$\omega = \frac{1}{\sqrt{L_2 C_2}} \tag{3.17}$$

$$C_2 = \frac{1}{L_2 \omega^2} {(3.18)}$$

To calculate the effect on  $V_A$  the load resistor in Equation 3.16 is replaced by a resistor in parallel with a capacitor.

$$R_L / \frac{1}{j\omega C_2} = \frac{R_L}{1 + j\omega C_2 R_L}$$

(3.19)

Plugging in to Equation 3.16 we get:

$$V_A = \frac{j\omega M i_1}{1 + \frac{j\omega L_2 + R_s}{\frac{R_L}{1 + j\omega C_2 R_L}}}$$

(3.20)

$$V_A = \frac{j\omega M i_1}{1 + \frac{(j\omega L_2 + R_s)(1 + j\omega C_2 R_L)}{R_L}}$$

(3.21)

$$V_A = \frac{j\omega M i_1}{1 + \frac{j\omega L_2 + R_s - \omega^2 L_2 C_2 R_L + j\omega C_2 R_s R_L}{R_L}}$$

(3.22)

$$V_A = \frac{j\omega M i_1}{(1 + \frac{R_s}{R_L} - \omega^2 L_2 C_2 R_L) + j(\frac{\omega L_2}{R_L} + \omega C_2 R_s)}$$

(3.23)

The magnitude of  $V_A$  can now be easily calculated:

$$|V_A| = \frac{\omega M i_1}{\sqrt{(1 + \frac{R_s}{R_L} - \omega^2 L_2 C_2 R_L)^2 + (\frac{\omega L_2}{R_L} + \omega C_2 R_s)^2}}$$

(3.24)

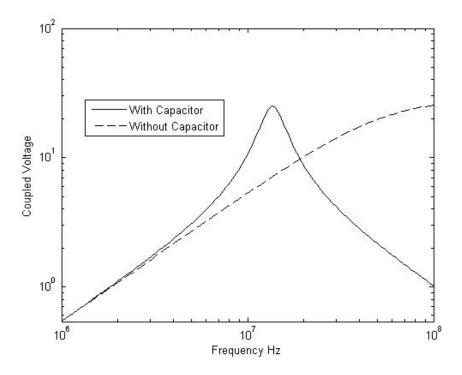

Figure 3.5. Increase in coupled voltage due to resonant capacitor.

$$|V_A| = \frac{\omega k \sqrt{L_1 L_2} i_1}{\sqrt{(1 + \frac{R_s}{R_L} - \omega^2 L_2 C_2 R_L)^2 + (\frac{\omega L_2}{R_L} + \omega C_2 R_s)^2}}$$

(3.25)

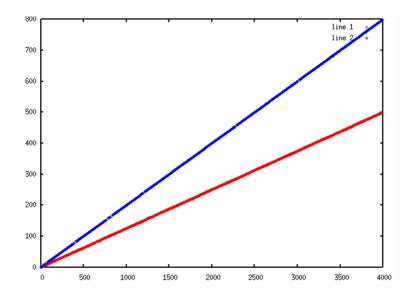

Plotting Equations 3.25 and 3.16 on the same graph illustrates the advantage of including the resonant capacitor, which boosts the coupled voltage by a factor of Q. Figure 3.5 was created with the following values:  $f_0 = 13.56$  MHz, k = 0.05,  $L_1 = 3 \mu$ H,  $L_2 = 3 \mu$ H,  $R_s = 10 \Omega$ ,  $R_L = 1 k\Omega$ ,  $C_2 = 46$  pF, and  $i_1 = 1$  A.

To calculate the RLC tank quality factor, the magnitude of Equation 3.25 is compared to the magnitude of Equation 3.16 at resonance. The ratio will be the quality factor Q. Starting with Equations 3.16 and 3.22:

$$Q = \left| \frac{\frac{1+j\omega L_2 + R_s}{R_L}}{1 + \frac{j\omega L_2 + R_s - \omega^2 L_2 C_2 R_L + j\omega C_2 R_s R_L}{R_L}} \right|$$

(3.26)

Using  $\omega^2 = 1/L_2C_2$  to simplify:

$$Q = \left| \frac{R_L + R_s + j\omega L_2}{R_s + j\omega L_2 + j\omega C_2 R_s R_L} \right|$$

(3.27)

Substituting for  $\omega$ :

$$Q = \left| \frac{R_L + R_s + j\sqrt{\frac{L_2}{C_2}}}{R_s + j\sqrt{\frac{L_2}{C_2}} + jR_sR_L\sqrt{\frac{C_2}{L_2}}} \right|$$

(3.28)

$$Q = \left| \frac{1 + R_s / R_L + j \frac{1}{R_L} \sqrt{\frac{L_2}{C_2}}}{\frac{R_s}{R_L} + j \frac{1}{R_L} \sqrt{\frac{L_2}{C_2}} + j R_s \sqrt{\frac{C_2}{L_2}}} \right|$$

(3.29)

After clearing the denominator, simplifying using  $(R_s/R_L)^2 \ll 1$ , and eliminating the insignificant terms:

$$Q = \left| \frac{-j \left( \frac{1}{R_L} \sqrt{\frac{L_2}{C_2}} + R_s \sqrt{\frac{C_2}{L_2}} \right) + \frac{1}{R_L} \sqrt{\frac{L_2}{C_2}} \left( \frac{1}{R_L} \sqrt{\frac{L_2}{C_2}} + R_s \sqrt{\frac{C_2}{L_2}} \right)}{\left( \frac{1}{R_L} \sqrt{\frac{L_2}{C_2}} + R_s \sqrt{\frac{C_2}{L_2}} \right)^2} \right|$$

(3.30)

$$Q = \left| \frac{\frac{1}{R_L} \sqrt{\frac{L_2}{C_2}} - j}{\frac{1}{R_L} \sqrt{\frac{L_2}{C_2}} + R_s \sqrt{\frac{C_2}{L_2}}} \right|$$

(3.31)

Before taking the absolute value, note that  $1/R_L\sqrt{L_2/C_2} = \omega L_2/R_L$ . If the tank has a high quality factor, this term must be very small. In fact, if the inductor were ideal, this value would equal 1/Q of the tank. Therefore, Equation 3.31 can be simplified to give an approximate value of the tank quality factor:

$$Q = \frac{1}{\frac{1}{R_L} \sqrt{\frac{L_2}{C_2}} + R_s \sqrt{\frac{C_2}{L_2}}}$$

(3.32)

Note that this is precisely the equation (3.39) derived in Section 3.3.1, where the quality factor is calculated from an energy perspective.

The net consequence of these equations is clear, use of high-Q inductors is desirable to boost voltage available to the tag circuitry; this is achieved through a minimization of series resistance of the inductor, necessitating the development of the associated materials and printing processes.

### 3.2.5 Summary of Components Necessary

In order to create an RFID front-end it is necessary to fabricate inductors, capacitors, and interconnect layers, preferably on a low-cost plastic substrate. This challenge is met using inkjet printing as a patterning tool, along with careful choice of "inks" to deposit conductive metal and insulating dielectric layers.

# 3.3 Impact of Inductor Quality Factor on Coupled Voltage

Maximizing the coupled voltage of Equation 3.24 requires fabrication of a high quality factor inductor. Quality factor is defined as the energy stored over the energy lost per cycle, and for an inductor is equal to:

$$Q_L = \frac{\omega L}{R_s} \tag{3.33}$$

where  $\omega$  is the frequency (rad/s), L is the inductance, and  $R_s$  is the series resistance. Recall that the coupled voltage is boosted by a factor Q, but it is the Q of the resonant RLC tank, not simply the inductor that is important. The energy consumed by the tag back-end circuitry, which will be optimized for low-power consumption, will also reduce the Q of the resonant circuit. Ideally the back-end should dominate the Q of

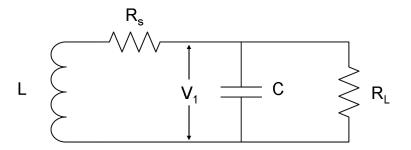

Figure 3.6. Circuit used to calculate the RLC tank quality factor.

the tank. This means that as much coupled energy as possible is transferred to the back-end and not dissipated in the coupling inductor.

### 3.3.1 Quality Factor of Tag Front End

In order to determine the quality requirements for the tag inductor it is necessary to derive an equation for the tank quality factor that incorporates the inductor quality factor. This is done using the circuit in Figure 3.6.

Quality factor is mathematically defined as:

$$Q = \frac{\omega(\text{time average energy stored in system})}{\text{energy loss per second}}$$

(3.34)

For the circuit in Figure 3.6 this is expressed as:

$$Q = \frac{\omega_{\frac{1}{2}}^{1}C|V_{1}|^{2}}{\frac{1}{2}\frac{|V_{1}|^{2}}{R_{L}} + \frac{1}{2}R_{s}|I_{L}|^{2}}$$

(3.35)

Where  $I_L$  is the current through the inductor:

$$I_L = \frac{V_1}{R_s + j\omega L} \tag{3.36}$$

Solving for  $|I_L|^2$  gives:

$$|I_L|^2 = \frac{|V_1|^2}{R_s^2 + \omega^2 L^2} \tag{3.37}$$

Equation 3.37 can now be substituted into Equation 3.35 and simplified:

$$Q = \frac{\omega C}{\frac{1}{R_L} + \frac{R_s}{R_s^2 + \omega^2 L^2}}$$

(3.38)

In order to further simplify this equation it is assumed that the inductor has a quality factor greater than 1, and  $\omega^2 L^2 \gg R_s^2$ . This is a reasonable assumption, given that the goal is to maximize inductor quality factor.

$$Q = \frac{\sqrt{\frac{C}{L}}}{\frac{1}{R_L} + \frac{R_s}{\omega^2 L^2}} = \frac{1}{\frac{1}{R_L}\sqrt{\frac{L}{C}} + R_s\sqrt{\frac{C}{L}}}$$

(3.39)

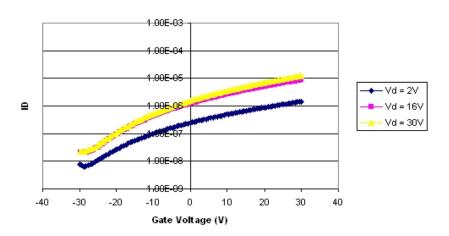

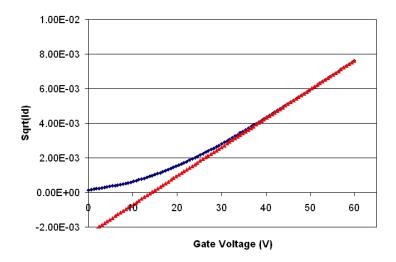

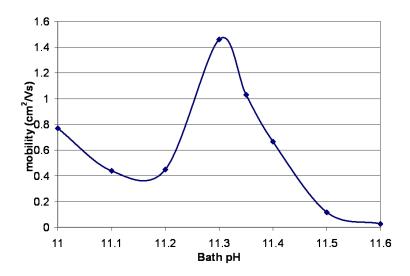

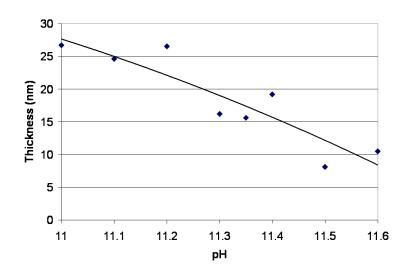

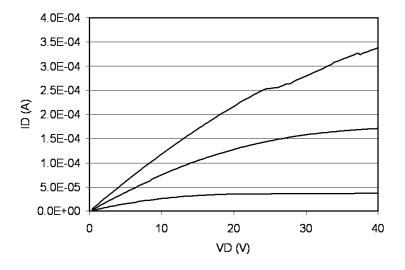

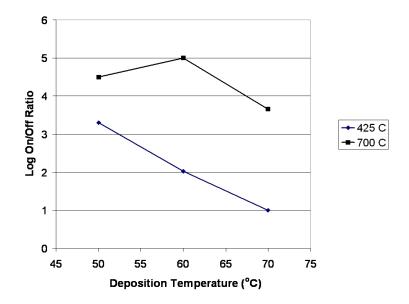

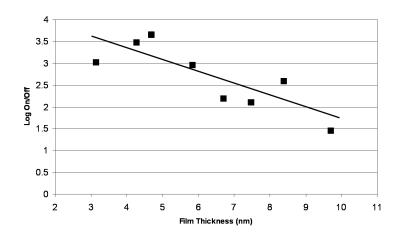

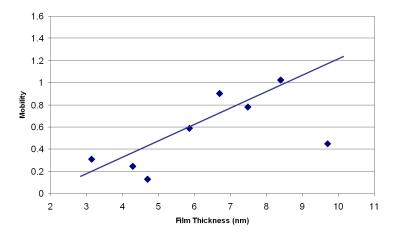

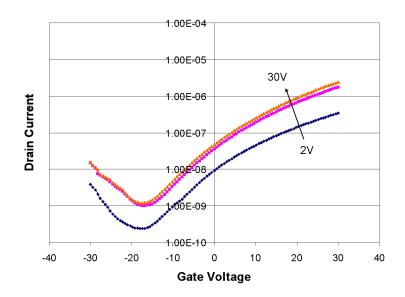

It is now possible to rearrange the equation in terms of  $Q_L$ , the inductor quality factor: