## Thin-Body Silicon FET Devices and Technology

Varadarajan Vidya

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2007-51 http://www.eecs.berkeley.edu/Pubs/TechRpts/2007/EECS-2007-51.html

May 9, 2007

# Copyright © 2007, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Acknowledgement

I would like to thank my advisor Prof. Tsu-Jae King Liu for her excellent advising. I would like to thank Prof. Chenming Hu and Prof. Eugene Haller for serving on my dissertation committee. I would like to thank Prof. Jan Rabaey, Prof. Nathan Cheung and Prof. J.W. Morris for their invaluable feedback during my Qualifying Examinations. I would like to thank the Microfabrication facility and staff for making this work possible. I would like thank all colleagues and my family for their support.

#### Thin-Body Silicon FET Devices and Technology

by

#### Varadarajan Vidya

B.Tech. (Indian Institute of Technology, Bombay) 2001 M.Tech. (Indian Institute of Technology, Bombay) 2001

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Chenming Hu Professor Eugene E. Haller

Spring 2007

| The  | dissertation   | of V | aradarai    | an Vi | dva      | is anı | proved:  |

|------|----------------|------|-------------|-------|----------|--------|----------|

| 1110 | aibbei tatioii | 01   | ai aaai a j | an i  | $\alpha$ | ואש פי | oro voa. |

| Chair | Date |

|-------|------|

|       |      |

|       | Date |

|       |      |

|       | Date |

University of California, Berkeley

Spring 2007

## Thin-Body Silicon FET Devices and Technology

Copyright 2007

by

Varadarajan Vidya

#### **Abstract**

### Thin-Body Silicon FET Devices and Technology

by

#### Varadarajan Vidya

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

Continued miniaturization of bulk silicon CMOS transistors is being limited by degrading short channel effects. Traditionally, higher channel doping, shallower source/drain junctions, and thinner gate dielectrics have been employed to improve gate control and enhance performance as the gate length is scaled down. However, these techniques are rapidly approaching material and process limits. Alternate transistor architectures such as the planar ultra-thin body (UTB) FET and double-gate MOSFET may be necessary to continue gate length scaling down to the sub-10nm regime.

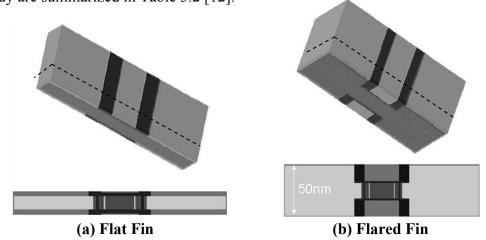

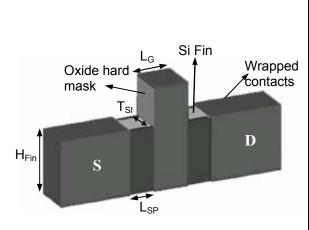

The non-planar FinFET is perhaps the most promising double-gate structure for integrated circuit manufacture. However, some key fabrication issues that are yet to be resolved include super-steep source/drain junction formation with high uniformity and dual metal gate technology with work function engineering for dense layouts. Furthermore, statistical variations due to factors such as dopant fluctuation effects and line-edge roughness demand the need for variation-tolerant device and circuit designs.

One way to tackle the challenges in the formation of uniform and steep source/drain junctions in FinFETs is to completely eliminate all p-n junctions in the device. By having the source/drain and channel regions of the same doping type, the device can be operated in accumulation mode instead of inversion mode. It is found that this architecture shows comparable intrinsic delay and lower gate leakage compared to the enhancement mode FinFET, but higher sensitivity to process variations.

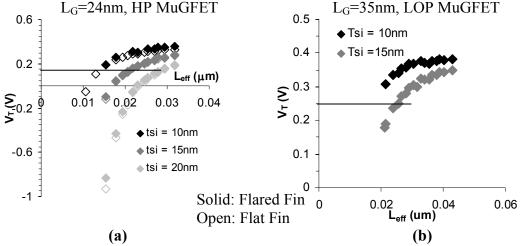

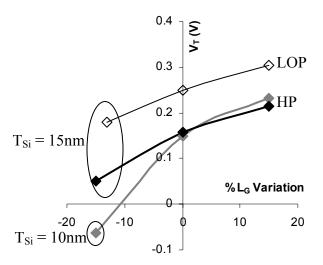

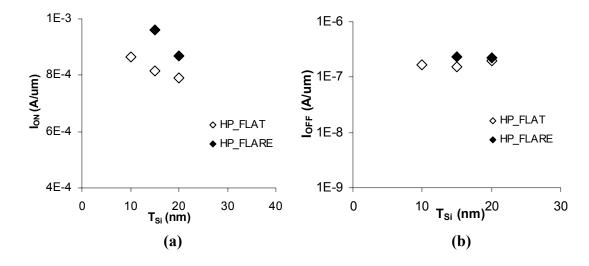

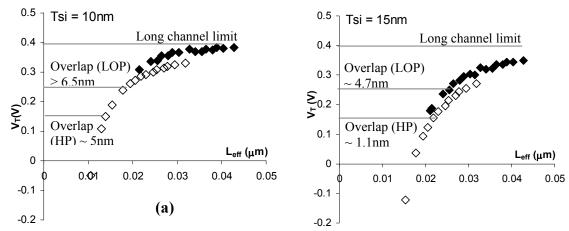

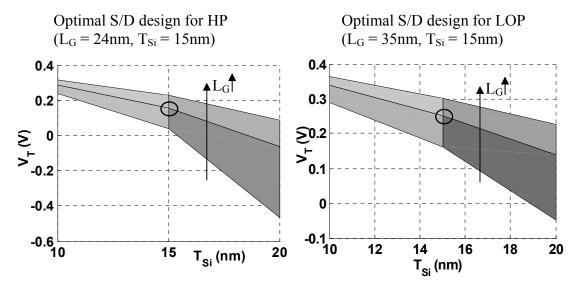

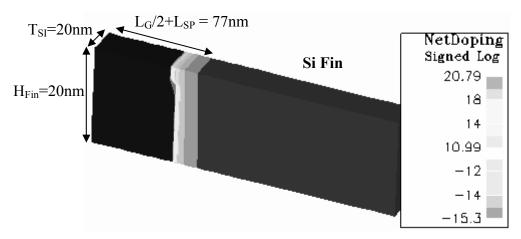

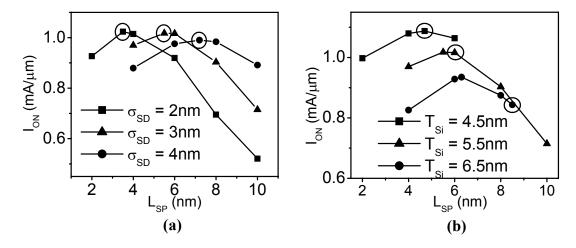

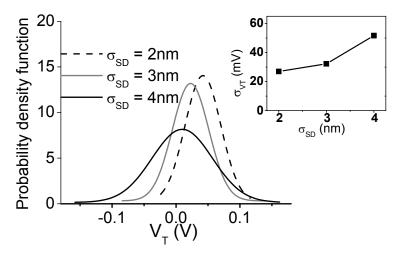

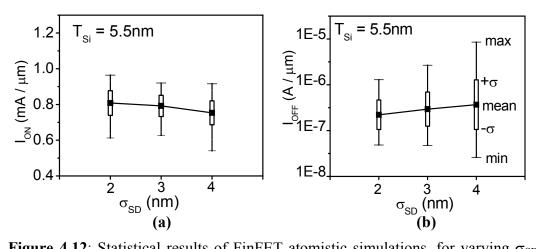

Single gate work function CMOSFET design is studied to make metal gate technology more practical for FinFETs. It is shown that high performance, low standby power, and low operating power CMOS can be implemented by utilizing the electrical channel length ( $L_{eff}$ ) as a  $V_T$  tuning variable, where,  $L_{eff}$  is optimized through an optimum choice of side-wall spacer thickness ( $L_{SP}$ ) and source/drain gradient abruptness ( $\sigma_{SD}$ ). In this methodology,  $L_{eff}$  and silicon fin thickness ( $T_{Si}$ ) are the only optimization variables and a tradeoff between performance and variability is inherent to this device design scheme. Through 3D atomistic simulations, it is identified that lean spacers and steep junctions, along with a relatively thick  $T_{Si}$  will be necessary to minimize variations.

The concept of thin-body MOSFETs is extended to three-dimensional integration through a novel, low thermal budget, cost-effective integration methodology. Unlike conventional techniques, the proposed method focuses on building FETs directly within interconnect wires. The technique has been demonstrated on the aluminum-silicon system using the concept of aluminum induced crystallization of silicon.

Professor Tsu-Jae King Liu Dissertation Committee Chair

2

## **Table of Contents**

| Chapter 1 : Introduction  1.1 Challenges of Bulk Silicon CMOS Scaling  |    |

|------------------------------------------------------------------------|----|

| 1.2 Advanced MOSFET Structures                                         |    |

| 1.3 Interconnect Scaling and 3-D Integration                           |    |

| 1.4 Organization                                                       |    |

| 1.5 References                                                         |    |

| Chapter 2 : Accumulation Mode Thin-body MOSFETs                        |    |

| 2.2 Thin-body Accumulation Mode MOSFETs                                | 18 |

| 2.2.1 Device Structure and Operation                                   | 18 |

| 2.2.2 Potential Benefits and Issues                                    | 21 |

| 2.3 Device Design                                                      | 21 |

| 2.3.1 Design Optimization                                              | 22 |

| 2.3.2 Short Channel Effects and Sensitivities                          | 28 |

| 2.4 Device Fabrication Issues                                          | 29 |

| 2.4.1 Gate Last Process                                                | 30 |

| Shortcomings of Gate Last Process                                      | 33 |

| 2.4.2 Gate First Process                                               | 34 |

| 2.5 Summary                                                            | 35 |

| 2.6 References                                                         | 36 |

| Chapter 3 : V <sub>T</sub> Adjustment via L <sub>eff</sub> Engineering |    |

| 3.2 V <sub>T</sub> Tuning by S/D Engineering                           | 42 |

| 3.2.1 Device Simulation Set-up                                         | 43 |

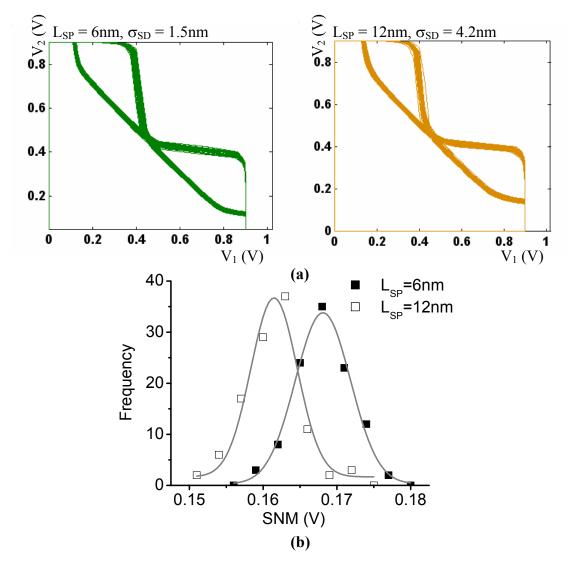

| SRAM Noise Margin Variation Simulation Setup                           | 45 |

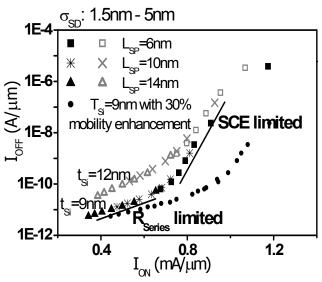

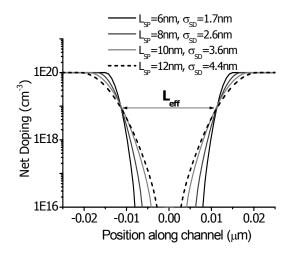

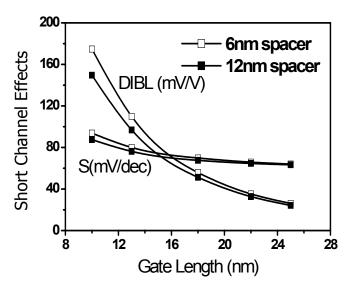

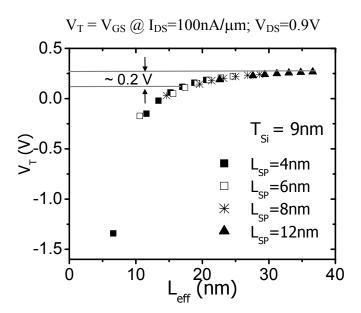

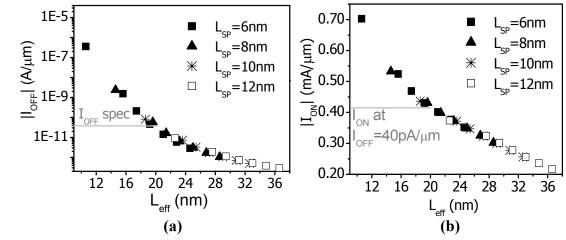

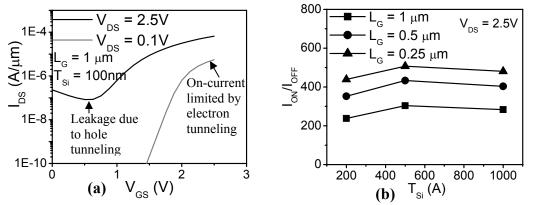

| 3.2.2 Impact of L <sub>eff</sub> on I <sub>ON</sub> -I <sub>OFF</sub>  | 47 |

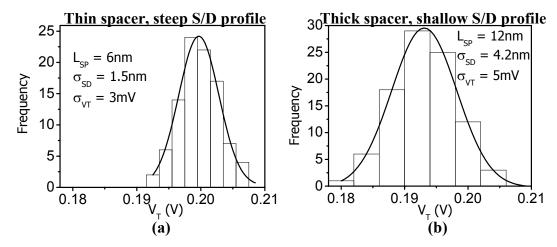

| 3.2.3 Choice of a Good S/D Design: Impact of Variations                | 51 |

| 3.2.4 Evaluating HP and LOP Designs with Single Gate Work Function | 54  |

|--------------------------------------------------------------------|-----|

| V <sub>T</sub> Adjustment and Sensitivity to Variations            | 55  |

| 3.3 S/D Process Requirements for L <sub>eff</sub> Engineering      | 60  |

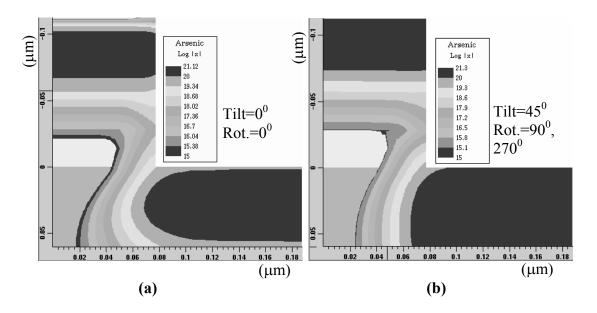

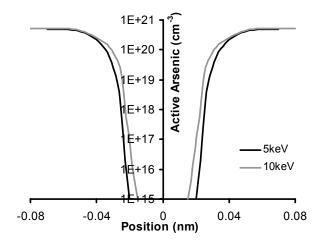

| 3.3.1 Effect of Ion-Implantation Conditions                        | 61  |

| Effect of Tilt and Rotation                                        | 62  |

| Effect of Implant Energy                                           | 63  |

| 3.4 Summary                                                        | 64  |

| 3.5 References                                                     | 65  |

| Chapter 4 : Statistical Dopant Fluctuation Effects in FinFETs      |     |

| 4.1.1 Sources of Variations                                        | 70  |

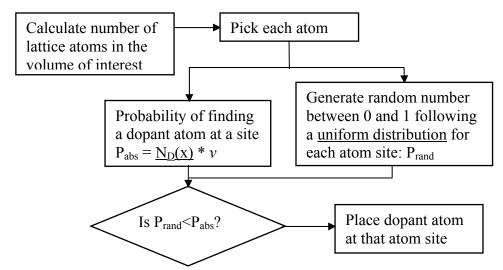

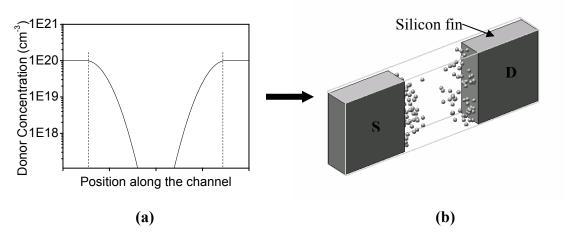

| 4.2 3D Atomistic Simulation Setup                                  | 72  |

| 4.2.1 Random Dopant Generation and Placement                       | 72  |

| 4.2.2 Dopant Definition in a Drift-Diffusion Simulator             | 76  |

| 4.2.3 Complete 3D Atomistic Simulation Algorithm                   | 81  |

| 4.3 Variation Tolerant FinFET Design                               | 82  |

| 4.3.1 Continuum domain device optimization                         | 82  |

| 4.3.2 Design Strategies for Variation Tolerance to SDF             | 84  |

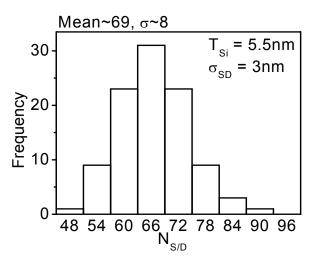

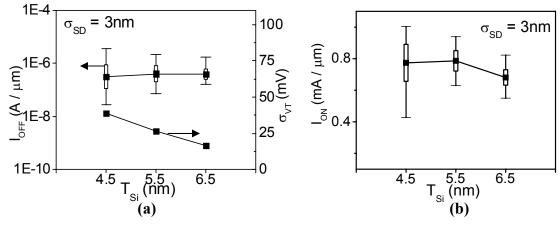

| Requirement of S/D Abruptness $\sigma_{SD}$                        | 84  |

| Optimization of T <sub>Si</sub>                                    | 85  |

| Shortcomings of the Current Approach                               | 87  |

| 4.4 Summary                                                        | 87  |

| 4.5 References                                                     | 88  |

| Chapter 5: WireFET Technology                                      |     |

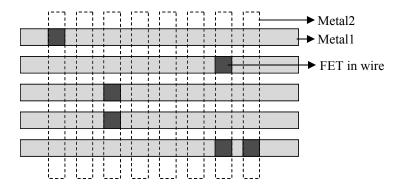

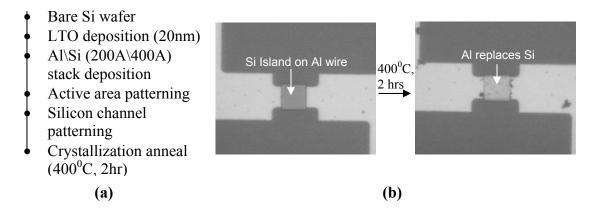

| 5.1.1 Concept of WireFET                                           | 96  |

| 5.1.2 Initial Simulations                                          | 96  |

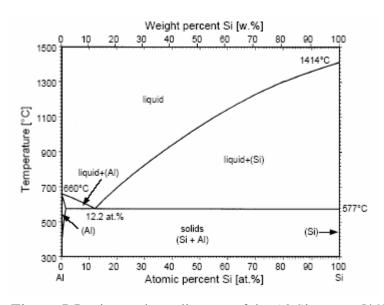

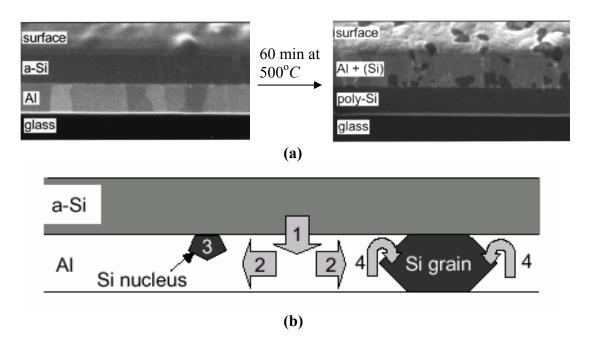

| 5.2 Aluminum Induced Crystallization (AIC) of Silicon              | 98  |

| 5.3 AIC Process Optimization                                       | 100 |

| 5.3.1 Proof-of-Concept                                             | 100 |

| 5.3.2 Role of Native Oxide Layer                                   | 101 |

| 5.3.3 Optimum Si:Al Thickness Ratio                                | 103 |

| 5.3.4 TEM Analysis of AIC Polysilicon              | 105 |

|----------------------------------------------------|-----|

| 5.4 Improved WireFET Process                       | 106 |

| 5.4.1 Improved WireFET Process Flow                | 106 |

| 5.4.2 Electrical Measurements                      | 107 |

| 5.4.3 Further Material Characterization            | 110 |

| 5.5 Summary                                        | 114 |

| 5.6 References                                     | 115 |

| Chapter 6 : Conclusions 6.1 Summary                |     |

| 6.2 Suggestions for Future Research                | 123 |

| Appendix A: Accumulation mode MOSFET Process Steps | 126 |

| Gate Last Process                                  | 126 |

| Gate First Process                                 | 131 |

| Appendix B: Useful Codes for Atomistic Simulations | 136 |

| Appendix C: WireFET Process Steps                  | 144 |

|                                                    |     |

## Acknowledgements

I would like to express most sincere and heartfelt gratitude to my advisor, Prof. Tsu-Jae King Liu, for her excellent guidance and encouragement through all years of my doctoral research. Her vast knowledge and technical expertise immensely helped me in getting a good understanding of device engineering and identifying the relevant research problems. At a personal level, she has been very kind and considerate to me and I am especially thankful to her for allowing me to work from home during my final semester.

I would like to thank Prof. Chenming Hu and Prof. Eugene Haller for serving on my dissertation committee. I am grateful to Prof. Jan Rabaey for serving on my Qualifying Examination committee. His valuable feedback led to a significant portion of my doctoral work and made my research more relevant. I would also like to thank Prof. J. W. Morris and Prof. Nathan Cheung for serving on my Qualifying Examination committee.

I would like to thank the Microfabrication Laboratory staff for providing the infrastructure as well as technical support for running my processes. I am especially thankful to Joe Donnelly for all his timely efforts and ensuring smooth running of my processes in the Novellus tool. Thanks also to Jimmy Chang for providing practical solutions and ideas for implementing my processes in the Microlab. I would also like to thank Dr Xiaofan Meng for helping me with evaporations and AFM measurements.

I am very grateful to Hideki Takeuchi, without whose guidance, it would have been very difficult for me start working in the microlab. He has been very patient with me and has taught me almost all the tools I have used and all processes I have run. I am indebted to him for his selfless efforts over many months, even after office hours, in helping me debug my processes and in coming up with the most practical solutions.

I would like to thank Dr. Lee Smith from Synopsys Inc., for sharing his extensive knowledge and guiding me with the development of the tool for atomistic simulations. I would like to thank Dr. Hsing-Huang Tseng from Sematech for giving me the wonderful opportunity to work with him as a summer intern and gain the knowledge on high-k gate dielectrics and their characterization. I would also like to thank Dr. Wade Xiong and Dr. Cleavelin Rin from ATDF for insightful discussions on single gate FinFET technology.

I am thankful to Ruth Gjerde for very patiently answering all my administrative queries and I am very grateful for her timely guidance through all the administrative responsibilities at all stages of my PhD. I would also like to thank Linda Manly, Charlotte Jones and Misty Kiuchi for ensuring smooth monetary transactions.

It has been a great pleasure to work with and share the friendship of my batchmates, Sriram Balasubramanian, Marie-Ange Naida Eyoum, Mohan Dunga, Blake Lin, Kyoungsub Shin, and Hiu-Yung Wong. I would also like to thank my seniors, Leland Chang, Pushkar Ranade, Igor Polishchuk, Qiang Lu, Yang-Kyu Choi, Kevin Yang, Charles Kuo, Yu (Kevin) Cao, Yee-chia Yeo, Shiying Xiong, Min She, Patrick Xuan, Jane Xi, and Daewon Ha for helping me get started with my research and gaining the relevant background. Thanks to all the current students at 373 Cory, Joanna Lai, Pankaj Kalra, Andrew Carlson, Donovan Lee, Chung-Hsun Lin, Alvaro Padilla, Noel Arellano, Darson Lu, Xin Sun, Reinaldo Vega, Dan Good, Hei (Anderson) Kam, Hui Wan, Kinyip Phoa, Yu-Chih Tseng, Anupama Bowonder, Pratik Patel, Cheuk Chi Lo, David Carlton, and Rhesa Nathaniel, for making my stay in Berkeley, an enjoyable and

unforgettable experience. I would like to thank Joanna for her timely and significant help with my final processes in the microlab. I would like to thank the visiting scholars and post doctoral members, Koichi Fukuda, Woo Young Choi, Wesley Chang, Yuri Yasuda, Takuro Matsutoya, Akira Hokazono and Taro Osabe for sharing their technical expertise with us. I am particularly thankful to Koichisan, Yurisan, Woo Young, Wesley, and Noel for their friendship and for making it easy to work long hours in the lab!

I am deeply indebted to my parents and my family for their love, their sacrifices, and encouragements all through my life. I am very grateful to my father for building my foundations in physics and to my brother for my foundations in mathematics. My mother has been most encouraging with all my endeavors in life and she always inspired me to work all the way towards a PhD and beyond. I am very thankful to my brother Venkatesh, and my Manni Ramyaa for making my stay in the Bay Area so comfortable and for being by my side through all good and bad times, from the day I started. I am also very fortunate to have the immense love of my little niece Prerana (Bumble), who has always been very caring and relieved all my stresses in moments! Finally, I would like to thank my dear husband, Srinath, for his love, for being with me in good and bad times and for walking me through my doctoral work. I am grateful to him for encouraging me, inspiring me and valuing my work over all the years, and of course, for helping me in sustaining through all the all-nighters in the lab! Without his programming expertise, it would have been very difficult for me to develop the atomistic simulator. I would also like to thank my in-laws Amma and Nannaru for their love and encouragement.

Most of all, I sincerely thank God for His blessings, for showing me the way and giving me the capability to receive a good education.

## Chapter 1 : Introduction

The journey of the modern day Integrated Circuit (IC) began in the late 1950s with the first ICs independently demonstrated by Jack Kilby (1958) and Robert Noyce (1959) [1], and has led to the present semiconductor industry. Since its conception, there has been an exponential scaling down of transistor dimensions (following the trend predicted by G. E. Moore [2]) targeted towards making the circuits smaller in order to fit more and more functionalities in a given chip area. The modern day circuits have over 100 million transistors [3] per chip and this exponential growth since early 1960s is expected to continue for at least another decade [4].

## 1.1 Challenges of Bulk Silicon CMOS Scaling

The main goals behind scaling transistors in a circuit are achieving (i) improved performance ( $I_{ON}$ ) (ii) more on-chip functionality and hence, (iii) reduced cost per functionality. The transistors in ICs have been traditionally implemented using Bulk Silicon CMOS technology. As the lateral and vertical dimensions of the transistor are scaled, several effects come into play, which make further scaling of the traditional device architecture increasingly challenging.

As the gate length  $(L_G)$  of a transistor is decreased (lateral scaling), the source and drain regions come closer and the drain electric field starts reducing the source-channel

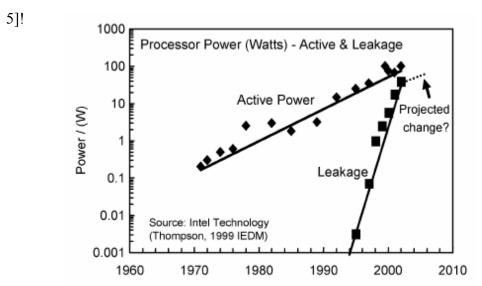

potential barrier. The capacitively coupled gate tends to lose control on the channel, especially in the sub-surface region. This capacitive coupling can be improved by decreasing the gate dielectric thickness (vertical scaling). The chief outcome of this is an increase in the off-state leakage (I<sub>OFF</sub>) of the transistors which contribute to the total stand-by power in a circuit. The key sources of leakage include (i) subthreshold leakage and parasitic components like (ii) sub-surface leakage due to poor short channel control and (iii) gate leakage due to direct tunneling through the gate dielectric, which are all exponential functions of the dielectric thickness or the source-channel potential barrier height. Therefore, there has been an exponential increase in the standby power of chips (**Figure 1.1**) and modern day ICs can dissipate almost 50% power in standby leakage [3,

**Figure 1.1**: Trend in microprocessor active versus leakage power with scaling [5]. The leakage power is almost 50% of the total power on a modern-day chip.

Conventionally, the sub-surface leakage and subthreshold leakage components have been alleviated by increasing the channel doping (and hence the source-channel potential barrier). With scaling however, channel doping becomes a serious concern due

to statistical dopant fluctuation effects [6]. The gate leakage however, can be mitigated by the use of high-k gate dielectrics, though it faces multiple challenges in practical realization [7, 8].

Bulk CMOS technology faces other challenges as well. In order to keep short channel effects under control, ultra shallow junctions with very high doping abruptness and yet, high degrees of dopant activation, are required. Although methods such as laser annealing and flash lamp annealing are currently being investigated these may not work for future technology nodes. In addition, the poly-Si gate depletion effect contributes significantly towards the effective oxide thickness and hence the threshold voltage and performance. This effect can be completely eliminated by moving back to metal gate technology. NMOS and PMOS devices, however, need separate gate materials to achieve the required work functions, leading to process integration challenges.

Even though bulk CMOS technology with SiO<sub>2</sub> gate dielectric and poly-Si gates has been the most suitable and well-understood technology, the above mentioned challenges (and others not mentioned here) strongly push the need for alternate device structures and processing techniques.

#### 1.2 Advanced MOSFET Structures

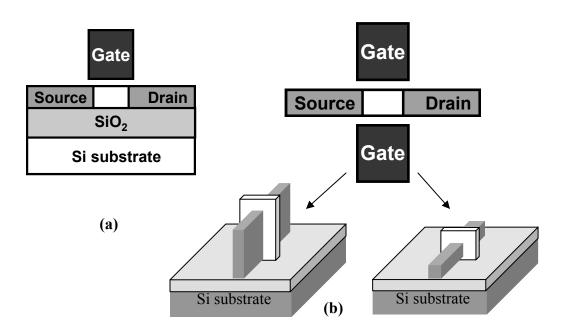

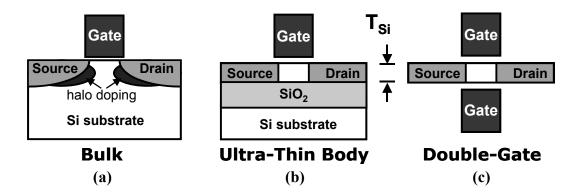

In order to mitigate some of the issues of the bulk CMOS MOSFET, advanced transistor structures such as ultra-thin body FET (UTB FET), Fully-depleted SOI (FD-SOI), Double-gate FET (DG-FET) like FinFET, Multi-Gate FET (MuGFET) and tri-gate FET (**Figure 1.2**) [9-13] have been studied as alternatives to the conventional device architecture. The key benefit of all these structures is that the conduction is confined to a thin silicon film, thereby physically eliminating the sub-surface leakage component. The

**Figure 1.2**: Schematic representation of advanced FET devices like the (a) Ultra-thin body MOSFET (UTB FET) and (b) Multiple-gate MOSFETs like FinFET and the Trigate MOSFET. Confining the channel to a thin silicon film provides better short channel control, performance and scalability compared to the bulk MOSFET.

layouts and process steps are very close to the conventional bulk CMOS flow. An undoped channel is used to reduce the effect of statistical dopant fluctuations. They also have additional benefits of better short channel control and reduced parasitic capacitance (no source-bulk or drain-bulk capacitances exist). Overall, these devices show superior performance ( $I_{ON}/I_{OFF}$  as well as intrinsic delay) compared to their bulk counterpart [14, 15]. For reasonable performance, the body thickness requirement for a UTB-FET is about  $L_G/3$ , while that for a DG-FET is about  $2L_G/3$  [16, 17]. This proves the better scalability of the DG-FET. The benefits of advanced FET structures are promising enough that the 2005 International Technology Roadmap for Semiconductors (ITRS [4]) predicts

possible introduction of these technologies in manufacturing in future technology nodes, summarized in **Figure 1.3**.

| L <sub>G</sub> (HP)   | 2005 | 2007 | 2008 | 2011 | 2012 | 2015 | 2018 | 2020 |

|-----------------------|------|------|------|------|------|------|------|------|

| Bulk (nm)             | 32   | 25   | 22   | 16   | 14   | -    | -    | -    |

| UTB (nm)              | 1    | 1    | 22   | 16   | 14   | 10   | -    | -    |

| DG (nm)               | -    | -    | -    | 16   | 14   | 10   | 7    | 5    |

| (a)                   |      |      |      |      |      |      |      |      |

| L <sub>G</sub> (LSTP) | 2005 | 2007 | 2008 | 2012 | 2013 | 2015 | 2018 | 2020 |

| Bulk (nm)             | 65   | 45   | 37   | 22   | 20   | 1    | -    | -    |

| UTB (nm)              | 1    | 1    | 1    | 22   | 20   | 17   | 14   | 12   |

| DG (nm)               | -    | -    | -    | 22   | 20   | 16   | 12   | 10   |

| (b)                   |      |      |      |      |      |      |      |      |

| $L_{G}$ (LOP)         | 2005 | 2007 | 2008 | 2011 | 2012 | 2013 | 2016 | 2020 |

| Bulk (nm)             | 45   | 32   | 28   | 20   | 18   | -    | -    | -    |

| UTB (nm)              | -    | -    | -    | 20   | 18   | 16   | 11   | -    |

| DG (nm)               | -    | -    | -    | 20   | 18   | 16   | 11   | 7    |

(c)

Figure 1.3: International Technology Roadmap predictions (of gate lengths used in high-volume IC manufacturing) [4] for the expected termination of bulk CMOS and introduction of advanced FETs for (a) High Performance, (b) Low Standby Power and (c) Low Operating Power applications.

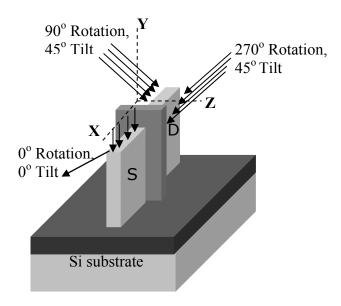

Even though some of the issues of bulk CMOS technology get resolved in moving to advanced FETs, some challenges still question the practical implementation of these devices. Some of the issues are introduced here, though this is, by no means, a comprehensive list. For non-planar architectures, such as the FinFET, the topography poses an important integration challenge. In order to achieve uniform S/D doping along the height of the Si Fin, large angle tilted ion implantation or alternative doping strategies like plasma doping [18], will be needed. For dense memory layouts, like SRAM arrays it is impossible to have angular implants (due to shadowing effects), thereby, forcing the

need for introduction of alternate doping techniques. The p-n junction gradient requirements however, would be similar to the conventional MOSFET. Another issue that remains unresolved is the high-k dielectric with metal gate integration. With an undoped channel, NMOS and PMOS FinFETs require different gate work functions for optimum performance [15], which do not correspond to Si band edge values as in bulk MOSFETs, thus making it inevitable to introduce metal gate technology. Separate gate work functions for NMOS and PMOS can be obtained through gate work function engineering by selective ion implantation [19, 20]. However, with scaling and reduction in fin pitch, gate work function engineering would become impossible, and it would be necessary to implement single gate work function CMOS technology.

With scaling, we are quickly approaching material and process limits (no matter what device architecture is used) and this leads to a new inevitable problem arising out of statistical fluctuations in processes, which reveal themselves in the form of variations in the performance and power of a circuit. Some examples of the sources of variations include (i) statistical dopant fluctuations in the channel and/or source and drain [6, 21-23], (ii) Line-edge roughness of gate and fin coming from lithography and etching [24, 25], (iii) layout dependence on mechanical strain and performance [26] (iv) film thickness variations [6], (v) on-chip temperature gradients [27] and (vi) electrical stress related change in parameters [27]. Considering the complexity and cost of modern day chips, it is very important to quantify the overall variations and acquire design solutions prior to fabricating them. This requires significant and timely contribution from the Computer Aided Design (CAD) industry, and many of the above phenomena are yet to be modeled

accurately for complicated layouts. It is also important to identify variation-tolerant device designs, in conjunction with variation-tolerant circuit designs and architectures.

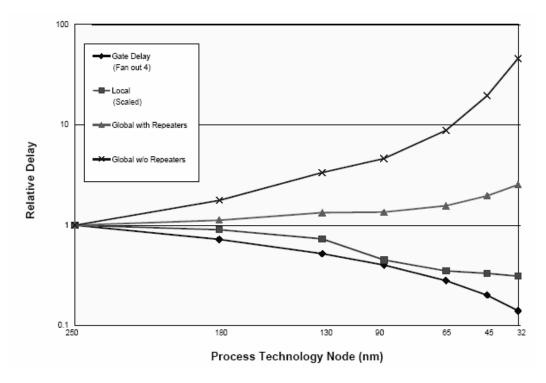

**Figure 1.4**: Non-scaling or reverse scaling of global interconnects makes their contribution to the total chip delay significant [29] with progressing technology nodes.

### 1.3 Interconnect Scaling and 3-D Integration

A lot of emphasis is given to extract the maximum possible performance from a MOSFET in a given technology. But interconnect scaling has been following an altogether different trend and the interconnect delay has become a significant fraction of the total delay in modern ICs [28]. Global interconnects are typically not scaled or reverse scaled to maintain the required resistivity and to handle high current densities. However, the global interconnect delay increases with technology node (as shown in **Figure 1.4** [29]) due to gradually increasing resistivities. The local interconnects lengths scale with technology [29] and do not contribute significantly towards the increasing

percentage of interconnect delay. Advanced solutions like 3-dimensional (3-D) integration and optical interconnects will be required in future technology nodes to keep the interconnect loading overhead under control.

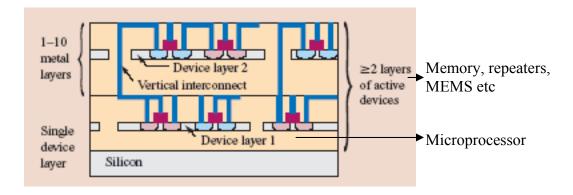

**Figure 1.5**: Schematic representation of a 3-dimensionally integrated circuit [31]. The first device layer could be the microprocessor function, followed by multiple active layers to execute memory, repeaters and other functions.

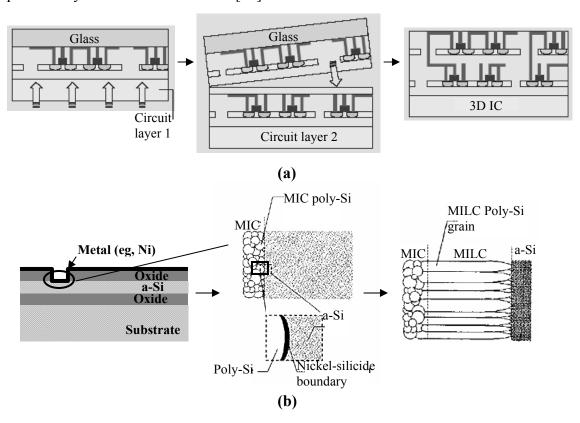

3-D Integration focuses on stacking different parts/functionalities of a chip in the vertical dimension rather than laterally (**Figure 1.5**). This way, interconnects routing together different blocks of a chip (which are typically several millimeters in length) can be significantly reduced in size (to several micrometers) and their contribution to the overall chip delay can be considerably reduced. Several fabrication schemes have been explored for this solution such as (i) epitaxial growth of silicon, (ii) low temperature crystallization of silicon [30] and (iii) processed wafer bonding [31], with wafer bonding being one of the more popular approaches. Approaches (i) and (ii) suffer from the big challenge of thermal budget. The crystallized silicon film can be a large grained poly crystalline film rather than a single crystalline film, which may affect performance. In

approach (iii) above, the different parts of the chip are fabricated on different silicon substrates and then individually transferred to a primary substrate by wafer bonding techniques. This is a favorable method in terms of the processing thermal budget and the ability to achieve good performance through the use of single crystalline silicon. But this is certainly a complex fabrication scheme and it has inherent issues like ultra high aspect ratio via etching and stringent alignment requirement between different device layers. The available approaches till date are therefore, not very cost-effective. The concept of 3-D integration is very promising but needs a lot more research and development before introduction into real products in a cost-effective manner.

## 1.4 Organization

In this dissertation, some of the above discussed problems have been approached with the aim of making advanced FET structures more manufacturable. Since FinFETs and MuGFETs have a more relaxed silicon body thickness requirement and are more scalable compared to FDSOI or UTB FETs, we will focus on FinFET type devices for the most part. Several designs of FinFETs have been optimized and analyzed through process and device simulations to judge their performance and manufacturability. A methodology to study statistical dopant fluctuations using commercial drift-diffusion simulators has been developed to study variations in highly scaled FinFET devices. A new approach toward 3-D integration has also been introduced and some initial results with ultra-thin body MOSFETs have been shown. Even though a FinFET like architecture may be developed using this 3-D integration scheme, it requires further process optimization and development beyond the work presented here.

This dissertation has been organized into six chapters. In Chapter 2, the double-gate MOSFET will be studied in the accumulation mode of operation rather than the conventional enhancement mode. The key benefits and disadvantages of opting for accumulation mode of operation, in terms of manufacturability and electrical operation will be presented. Two approaches for device fabrication will be illustrated (for planar back-gated architecture) and the issues of using a planar architecture will be highlighted.

Chapter 3 focuses on studying the conventional FinFET design, with the primary goal of implementing single gate CMOS technology. Using a single mid-gap work function gate, the feasibility to implement CMOS for High-Performance (HP), Low-Operating Power (LOP) and Low Standby Power (LSTP) devices will be evaluated. A device design optimization scheme will be developed through 2-D and 3-D device and process simulations. Sensitivities to gate length, body thickness variations and statistical dopant fluctuations for optimal designs will be presented and a brief discussion on SRAM noise-margin variability will be provided.

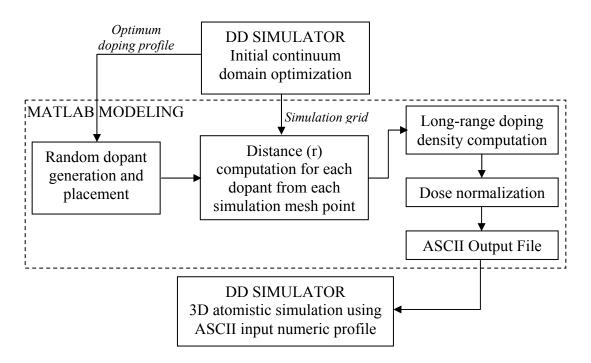

In Chapter 4, an attempt at modeling statistical dopant fluctuation effects has been presented. The developed methodology aims at using a conventional drift-diffusion simulator to run 3-D atomistic simulations. Various details of the methodology and algorithms will be discussed. This methodology will be applied to a highly scaled HP FinFET and simple device design rules for tolerance to variation from statistical dopant fluctuation effects will be put forward.

In Chapter 5, a novel, low-thermal budget, simple and cost-effective approach to 3-dimensional integration, called wireFET will be introduced. Initial process optimizations towards building these devices and some preliminary device fabrication

data will be shown. The issues with the current process will be demonstrated through electrical and material characterizations. Approaches to refine the process further will be discussed in chapter 6.

The key points of this dissertation are summarized in Chapter 6. Key research contributions and suggestions for future work will be highlighted. The appendices following the conclusive chapter provide the detailed process flows of various processes presented in this work and the programs to run atomistic device simulations.

#### 1.5 References

- [1] <a href="http://nobelprize.org/educational">http://nobelprize.org/educational</a> games/physics/integrated circuit/history/.

- [2] G. E. Moore, "Cramming more components onto integrated circuits," *Electronics*, vol. 38, pp. 114 117, 1965.

- [3] G. E. Moore, "No exponential is forever: but "Forever" can be delayed!," in Proceedings of IEEE International Solid-State Circuits Conference, 2003, pp. 2023.

- [4] International Technology Roadmap for Semiconductors, PIDS Chapter, <a href="http://public.itrs.net">http://public.itrs.net</a>.

- [5] S. E. Thompson, R. S. Chau, T. Ghani, K. Mistry, S. Tyagi, and M. T. Bohr, "In Search of "Forever" Continued Transistor Scaling One New Material at a Time," *IEEE Transactions on Semiconductor Manufacturing*, vol. 18, No. 1, pp. 26-36, Feb 2005.

- [6] A. Asenov, A. R. Brown, J. H. Davies, S. Kaya, and G. Slavcheva, "Simulation of intrinsic parameter fluctuations in decananometer and nanometer-scale MOSFETs," *IEEE Transactions on Electron Devices*, vol. 50, pp. 1837-52, 2003.

- [7] J. D. Plummer, "Material and Process Limits in Silicon VLSI Technology," *Proceedings of the IEEE*, vol. 89, No. 3, pp. 240-58, 2001.

- [8] E. P. Gusev, V. Narayanan, and M. M. Frank, "Advanced high-K dielectric stacks with polySi and metal gates: recent progress and current challenges," *IBM Journal of Research and Development*, vol. 50, pp. 387-410, 2006.

- [9] Y.-K. Choi, K. Asano, N. Lindert, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, "Ultrathin-body SOI MOSFET for deep-sub-tenth micron era," *IEEE Electron Device Letters*, vol. 21, pp. 254-5, 2000.

- [10] Y.-K. Choi, T.-J. King, and C. Hu, "Nanoscale CMOS spacer FinFET for the terabit era," *IEEE Electron Device Letters*, vol. 23, pp. 25-7, 2002.

- [11] D. Hisamoto, W.-C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.-J. King, J. Bokor, and C. Hu, "FinFET-a self-aligned double-gate MOSFET scalable to 20 nm," *IEEE Transactions on Electron Devices*, vol. 47, pp. 2320-5, 2000.

- [12] B. Doyle, B. Boyanov, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, R. Rios, and R. Chau, "Tri-Gate fully-depleted CMOS transistors: fabrication, design and layout," in *2003 Symposium on VLSI Technology*, 2003, pp. 133-4.

- [13] P. Verheyen, N. Collaert, R. Rooyackers, R. Loo, D. Shamiryan, A. De Keersgieter, G. Eneman, F. Leys, A Dixit, M.Goodwin, Y.S.Yim, M. Caymax, K. De Meyer, P. Absil, M. Jurczak, and S. Biesemans, "25% Drive Current Improvement for p-type Multiple Gate FET (MuGFET) Devices by Introduction

- of Recessed Si<sub>0.8</sub>Ge<sub>0.2</sub> in the Source and Drain Regions," in *2005 Symposium on VLSI Technology*, 2005, pp. 194-5.

- [14] L. Chang, "Nanoscale Thin-Body CMOS Devices," in *PhD Thesis*: University of California, Berkeley, 2003.

- [15] L. Chang, S. Tang, T.-J. King, J. Bokor, and C. Hu, "Gate length scaling and threshold voltage control of double-gate MOSFETs," in *International Electron Devices Meeting*, 2000, pp. 719-22.

- [16] B. Doyle, R. Arghavani, D. Barlage, S. Dutta, M. Doczy, J. Kavalieros, A. Murthy, and R. Chau, "Transistor Elements for 30nm Physical Gate Lengths and Beyond," *Intel Technology Journal*, vol. 6, No. 2, pp. 42-54, May 2002.

- [17] D. J. Frank, Y. Taur, and H. S. Wong, "Generalized scale length for two-dimensional effects in MOSFETs," *IEEE Electron Device Letters*, vol. 19, pp. 385-7, 1998.

- [18] D. Lenoble, K. G. Anil, A. De Keersgieter, P. Eybens, N. Collaert, R. Rooyackers, S. Brus, P. Zimmerman, M. Goodwin, D. Vanhaeren, W. Vandervorst, S. Radovanov, L. Godet, C. Cardinaud, S. Biesemans, T. Skotnicki, and M. Jurczak, "Enhanced performance of PMOS MUGFET via integration of conformal plasmadoped source/drain extensions," in 2006 Symposium on VLSI Technology, 2006, pp. 168-9.

- [19] P. Ranade, Y.-K. Choi, D. Ha, A. Agarwal, M.Ameen, and T.-J. King, "Tunable work function molybdenum gate technology for FDSOI-CMOS," in *IEEE International Electron Devices Meeting*, 2002, pp. 363-6.

- [20] W. P. Maszara, Z. Krivokapic, P. King, J. S. Goo, and M. R. Lin, "Transistors with dual work function metal gates by single full silicidation (FUSI) of polysilicon gates," in *IEEE International Electron Devices Meeting*, 2002, pp. 367-70.

- [21] T. Ezaki, T. Ikezawa, and M. Hane, "Investigation of realistic dopant fluctuation induced device characteristics variation for sub-100 nm CMOS by using atomistic 3D process/device simulator," in *IEEE International Electron Devices Meeting*, 2002, pp. 311-14.

- [22] M. Hane, T. Ikezawa, and T. Ezaki, "Coupled atomistic 3D process/device simulation considering both line-edge roughness and random-discrete-dopant effects," in *IEEE International Conference on Simulation of Semiconductor Processes and Devices*, 2003, pp. 99-102.

- [23] V.-Y. A. Thean, M. Sadd, and J. Bruce E. White, "Effects of Dopant Granularity on Superhalo-Channel MOSFET's According to Two- and Three-Dimensional Computer Simulations," *IEEE Transactions on Nanotechnology*, vol. 2, No. 2, pp. 97-101, June 2003.

- [24] A. Asenov, S. Kaya, and A. R. Brown, "Intrinsic Parameter Fluctuations in Decananometer MOSFETs Introduced by Gate Line Edge Roughness," *IEEE Transactions on Electron Devices*, vol. 50, No. 5, pp. 1254-60, May 2003.

- [25] S. Xiong, J. Bokor, Q. Xiang, P. Fisher, I. Dudley, P. Rao, H. Wang, and B. En, "Is Gate Line Edge Roughness A First Order Issue In Affecting The Performance Of Deep Sub-micron Bulk MOSFET Devices?," *IEEE Transactions on Semiconductor Manufacturing*, vol. 17, pp. 357-61, August 2004.

- [26] V. Moroz, G. Eneman, P. Verheyen, F. Nouri, L. Washington, L. Smith, M. Jurczak, D. Pramanik, and X. Xu, "The Impact of Layout on Stress Enhanced Transistor Performance," *International Conference on Simulation of Semiconductor Processes and Devices (SISPAD)*, pp. 143-6, 2005.

- [27] K. Bernstein, D. J. Frank, A. E. Gattiker, W. Haensch, B. L. Ji, S. R. Nassif, E. J. Nowak, D. J. Pearson, and N. J. Rohrer, "High-performance CMOS variability in the 65-nm regime and beyond," *IBM Journal of Research and Development*, vol. 50, pp. 433-49, 2006.

- [28] J. A. Davis, R. Venkatesan, A. Kaloyeros, M. Beylansky, S. J. Souri, K. Banerjee, K. C. Saraswat, A. Rahman, R. Reif, and J. D. Meindl, "Interconnect limits on gigascale integration (GSI) in the 21st century," *Proceedings of the IEEE*, vol. 89, pp. 305-24, 2001.

- [29] International Technology Roadmap for Semiconductors, Interconnect Chapter, 2005, (http://public.itrs.net).

- [30] V. Subramanian and K. C. Saraswat, "A Novel Technique for 3-D Integration: Ge-seeded Laterally Crystalluzed TFTs," 1997 Symposium on VLSI Technology, pp. 97-98, 1997.

- [31] A. W. Topol, D. C. La Tulipe Jr., L. Shi, D. J. Frank, K. Bernstein, S. E. Steen, A. Kumar, G. U. Singco, A. M. Young, K. W. Guarini, and M. Ieong, "Three-dimensional Integrated Circuits," *IBM Journal of Research and Development*, vol. 50, No. 4/5, pp. 491-506, 2006.

## Chapter 2 : Accumulation Mode Thin-body

## **MOSFETs**

#### 2.1 Introduction

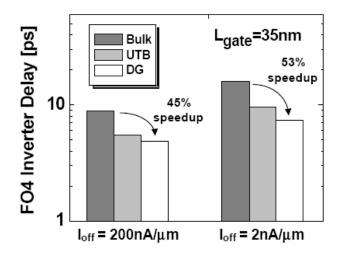

As a consequence of scaling, state-of-the-art ICs today have transistors with gate length (L<sub>G</sub>) below 35nm [1]. In order to suppress short channel effects, very thin gate dielectric (EOT<1nm using high-k gate dielectrics) and ultra-shallow source/drain junctions are employed. Further, to alleviate the issue of polysilicon gate depletion effect, metal gates will be employed in the near future [2]. These new materials and processes have been facing a lot of challenges [3] in getting introduced in the conventional CMOS process flow. In spite of these changes, short channel effects (e.g, DIBL and sub-surface leakage) are likely to be a major showstopper in scaling bulk CMOS FETs down to 10nm L<sub>G</sub>. The ultra-thin body MOSFET (UTB FET) and double-gate MOSFET [4-6] (**Figure 2.1**) are alternative device structures which limit the channel conduction to a thin semiconductor layer, thus eliminating sub-surface leakage and improving short channel control. The multiple gate FET architectures like the Multi-gate FET (MuGFET) [7], Trigate FET [8] and Gate All Around FET (GAA FET) [9] have the additional benefit of controlling the channel from more than one direction, thus providing superior gate

control (hence performance) [10] compared to the UTB FET and the bulk MOSFET, as shown in **Figure 2.2**.

**Figure 2.1**: Schematic cross-sections showing the (a) conventional bulk MOSFET and advanced FET structures such as (b) planar Ultra-Thin Body (UTB) MOSFET and (c) double-gate (DG FET) MOSFET [10]. Confining conduction to a thin silicon film, significantly improves gate control of the channel.

**Figure 2.2**: Owing to thin silicon channel and increased gate control, DG FET has better performance than UTB and bulk MOSFET [10].

In this chapter, double gate MOSFET design will be studied and evaluated for the accumulation mode design rather than the conventional enhancement mode [11]. The

working principle, device design and, potential advantages and disadvantages will be discussed in detail. Ideally, in enhancement mode of operation, the optimum gate work function for NMOS and PMOS are different [12], making it necessary to have two different gate metals for a CMOS process. Single gate work function CMOS design and technology will be dealt in greater detail in the next chapter. In this chapter, the feasibility and tradeoffs of implementing accumulation mode single gate work function CMOS technology will be briefly presented.

## 2.2 Thin-body Accumulation Mode MOSFETs

#### 2.2.1 Device Structure and Operation

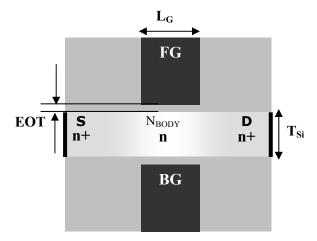

The structure of an accumulation mode DG FET (**Figure 2.3**) is very similar to an enhancement mode DG FET. The main difference lies in the channel doping for the two cases. For an accumulation mode (ACC) MOSFET, the S/D doping type is the same as the channel doping type, thus eliminating source-channel and drain-channel p-n junctions.

**Figure 2.3**: Schematic diagram of a 2D Accumulation mode DG nMOSFET.

| Parameter                | Value                      |  |  |  |

|--------------------------|----------------------------|--|--|--|

| EOT                      | 6A of SiO <sub>2</sub>     |  |  |  |

| $N_{BODY}$ (ACC)         | 2E16-1E19 cm <sup>-3</sup> |  |  |  |

| N <sub>BODY</sub> (ENH)  | $2E16 \text{ cm}^{-3}$     |  |  |  |

| $N_{S/D}$                | $1E20 \text{ cm}^{-3}$     |  |  |  |

| $L_{G}$                  | 13nm, 9nm                  |  |  |  |

| $V_{\mathrm{DD}}$        | 0.6V                       |  |  |  |

| $T_{Si}$ ( $L_G$ =13nm)  | $\sim 2L_G/3$              |  |  |  |

| $I_{OFF}$ ( $L_G$ =13nm) | 1E-6 A/μm                  |  |  |  |

**Table 2.1**: Device parameters used in simulations

In bulk accumulation mode MOSFETs, a buried channel device is utilized [13]. The conduction path being physically far away from the gate-oxide interface, gives the benefit of lower noise in ACC mode devices, but leads to poor short channel control than its bulk enhancement mode (ENH) counterpart (i.e degrades performance). By utilizing a heterostructure thin-body device [14], it is possible to reap the benefits a buried channel device without sacrificing performance, but at the cost of additional process complexity.

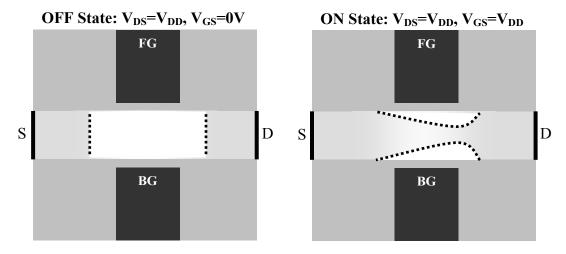

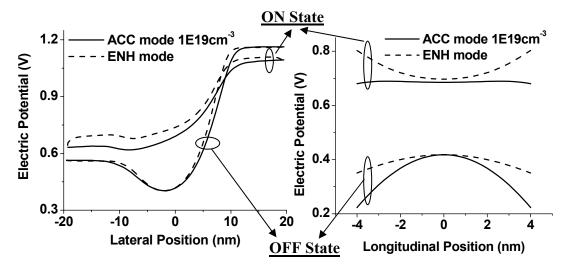

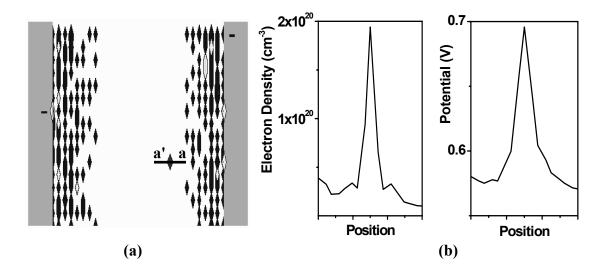

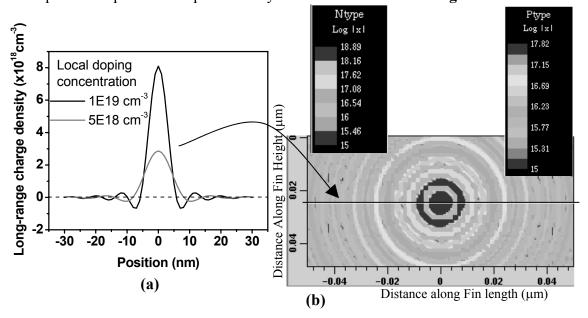

The device operation of the device architecture studied in this work is summarized in Figure 2.4. In the OFF-state (V<sub>DS</sub>=V<sub>DD</sub> and V<sub>GS</sub>=0V), the gate completely depletes the channel region, while in the ON-state (V<sub>DS</sub>=V<sub>DD</sub> and V<sub>GS</sub>=V<sub>DD</sub>), the depletion region recedes leading to resistive conduction. Further increase in gate bias leads to the formation of a channel accumulation region. It must be noted that in the OFFstate, the depletion region spreads in the lateral and longitudinal directions, thus leading to a larger effective channel length (Leff) than in the ON-state. The electric potential profiles in the ON and OFF states, perpendicular and parallel to the direction of current flow, are shown in Figure 2.5. In the OFF state, the ACC mode design has more energyband-bending in the vertical direction (perpendicular to current flow) than the ENH mode design, indicating that carriers are confined more to the center of the semiconductor film, resulting in higher leakage current I<sub>OFF</sub> for a given ON-state current specification. In the ON state, the shape of the vertical potential profile is similar for the ACC mode and ENH mode designs. The lateral (parallel to current flow) potential profile is similar for the ACC mode and ENH mode designs in the OFF state. The ON-state lateral potential profiles are similar, except that the voltage drop between the source and drain regions is smaller for the ENH mode design due to non-zero voltage dropped across parasitic source/drain series resistances (absent in ACC mode design due to heavy channel doping).

**Figure 2.4**: Pictorial representation of the ACC mode DG FET operation. In the OFF state, the L<sub>eff</sub> is larger than in the ON state owing to the extent of the depletion region. Current conduction is through the center of the fin (in ON and OFF state) for heavily doped channel.

**Figure 2.5**: Electric potential in the lateral (direction of current flow) and longitudinal (perpendicular to current flow) direction in ON and OFF state for the two FET designs. For ACC mode FET (heavily doped),  $V_{GS} > V_{DD}$  eventually leads to a longitudinal profile similar to ENH mode FET and, volume conduction.

#### 2.2.2 Potential Benefits and Issues

From a first glance at the ACC mode structure, it is simpler to fabricate than its ENH mode counterpart due to absence of S/D p-n junctions. The ON and OFF state behavior also provides some benefits over the ENH mode architecture. The longitudinal direction (perpendicular to current flow) potential profile results in good quantum confinement in the OFF-state which is good for lower OFF-state current. In the ON state however, the depletion region band bending is eliminated thus reducing the quantum confinement effect, making it better for conduction. However, the shrinking of the L<sub>eff</sub> in the ON state is likely to degrade the short channel effects.

It is possible to adjust the body doping of the ACC mode device to achieve single gate work function for NMOS and PMOS (will be discussed in a later section), which makes it a potentially manufacturable solution. A high body doping yields lower parasitic series resistance (can yield better performance), but leads to (i) ionic scattering and (ii) high dopant fluctuation effects, which can lead to performance degradation as well as higher variability. Clearly, different phenomena contribute towards performance enhancement or degradation. The net effect on performance will be analyzed in the sections to follow and the accumulation mode MOSFET will be evaluated as a potential candidate for highly scaled CMOS technology.

## 2.3 Device Design

In this section, device design strategy will be discussed through 2D Device simulations of DG ACC mode nMOSFETs. The simulations have been done using the Taurus-Device simulator [15], with drift-diffusion transport and 1D Schrödinger solution

for quantum confinement effects. The device structure is as shown in **Figure 2.3** and the device parameters (taken from ITRS roadmap [16]) are summarized in **Table 2.1**.

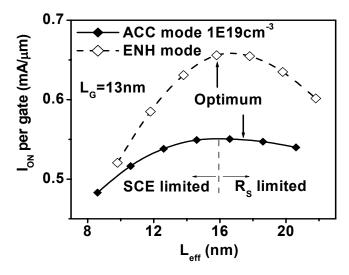

**Figure 2.6**:  $I_{ON}$  vs  $L_{eff}$  showing short channel effect limited and series resistance limited regions of operation. Optimum device is identified as one with maximum  $I_{ON}$  for DIBL < 100 mV/V. Ionic scattering limits the performance of heavily doped ACC mode FET.

#### 2.3.1 Design Optimization

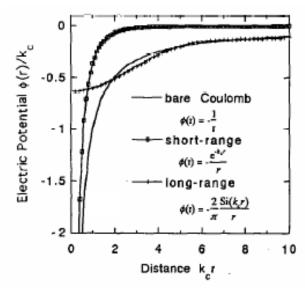

The ACC and ENH mode transistor designs are each optimized for maximum performance ( $I_{ON}$ ) by adjusting the effective channel length,  $L_{eff}$ . For each value of  $L_{eff}$ , the gate work function is adjusted so as to meet the ITRS leakage current specification. If  $L_{eff}\sim L_G$ , short channel effects limit the ON-state current ( $I_{ON}$ ). As  $L_{eff}$  is increased, short channel control and hence  $I_{ON}$  improves; but beyond a certain value of  $L_{eff}$ , increasing series resistance due to gate-to-source/drain underlap results in decreasing  $I_{ON}$  [17]. The optimized device design is selected to be the one which provides the highest  $I_{ON}$ , with DIBL less than or equal to 100 mV/V. The  $I_{ON}$  vs.  $L_{eff}$  curves for  $13 \text{nm } L_G$  ACC-mode and ENH-mode FETs are shown in **Figure 2.6**. Due to heavy channel doping which

extends into the 'underlap' region as well, the accumulation mode MOSFET current does not fall off as fast as the ENH mode device in the series resistance limited regime. However, Coulombic scattering leads to a lower optimal  $I_{ON}$  for the ACC mode FET compared to the ENH mode FET. It should be noted that in general the peak performance point in the  $I_{ON}$ - $L_{eff}$  plot may not be the optimum point from short channel effects point of view. (An example of this will be seen in Chapter 4).

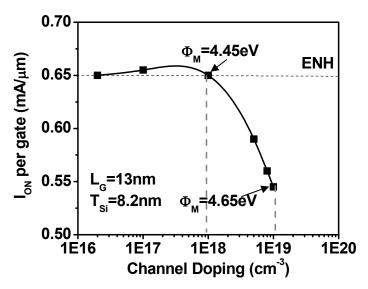

**Figure 2.7**: Optimum  $I_{ON}$  (per gate) as function of channel doping for ACC mode FET. Single gate work function CMOS with midgap work function is feasible by appropriately tuning the channel doping ( $I_{ON}$  is degraded for high channel doping).

Since the optimum  $I_{ON}$  is limited by Coulombic scattering, it would strongly depend on the body doping. **Figure 2.7** shows  $I_{ON}$  as a function of channel doping for the ACC mode FET, where each point has been independently optimized for best performance for the target  $I_{OFF}$  and DIBL specifications. At low channel doping, the channel charge is almost insignificant and the device behaves exactly like an

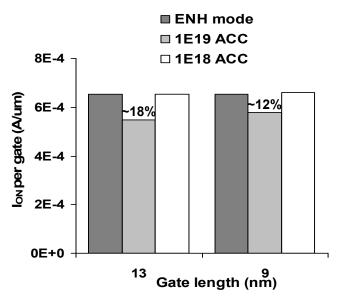

enhancement mode device. The histogram shown in **Figure 2.8** summarizes the optimized I<sub>ON</sub> for differently doped ACC mode designs and the ENH mode design for two different gate lengths. To achieve high performance (comparable to the ENH mode FET), body doping less than 1E18cm<sup>-3</sup> is desirable. However, the low doped device behaves essentially like an undoped body device (in this case enhancement mode and accumulation mode are merely two different ways of referring to exactly the same operation).

**Figure 2.8**:  $I_{ON}$  comparison for ACC mode and ENH mode FET for different  $L_G(s)$ . Coulombic scattering limits the performance of the heavily doped ACC mode FET.

An important consideration for transistor scaling is the gate work function requirement. The optimum gate work function for an undoped channel ENH mode double gate design requires two different gate work functions for NMOS and PMOS devices  $(4.45 \text{eV} \text{ for NMOS} \text{ and } \sim 5 \text{eV} \text{ for PMOS})$  to achieve symmetric threshold voltages  $(|V_{TNMOS}| = |V_{TPMOS}|)$  [12]. Referring back to **Figure 2.7**, the required gate work function for an ACC mode device depends on the channel doping level. For channel doping of

~1E19cm<sup>-3</sup>, the required gate work function for a NMOS ACC mode FET is about 4.65eV (midgap). Therefore, a PMOS ACC mode FET with the same structure and channel doping (but p-type instead of n-type) will also require the same work function for optimal performance and a complementary threshold voltage. This indicates the viability of a single gate work function technology at the expense of a slightly lower performance. Along the same lines, an ENH mode NMOS and ACC mode PMOS (with appropriate body doping) can also be used with a single gate work function technology.

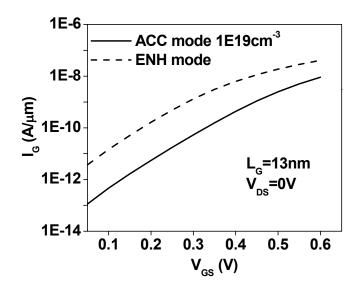

**Figure 2.9**: Comparison of gate leakage current densities for ACC vs. ENH mode designs. The ACC mode design has a significantly lower gate current due to lower vertical electric field.

An important benefit of the ACC mode device lies in its lower gate current (direct tunneling current), which is a very serious concern for future generations of MOSFETs. For a heavily doped ACC mode device, the carrier centroid lies at the center of the channel in both OFF and ON state, leading to a lower vertical electric field in the channel. On the other hand the undoped body device has its carrier centroids closer to the two

gates in the ON state, leading to a higher vertical electrical field in the channel and a higher gate current density (**Figure 2.9**).

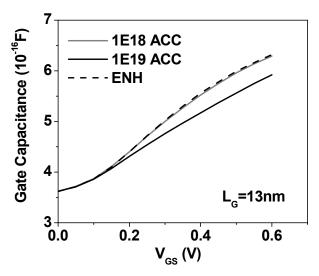

**Figure 2.10**: Gate capacitance comparison showing lower ON state capacitance for heavily doped ACC mode FET. This is another outcome of the lower vertical electric field due to the position of the charge centroid.

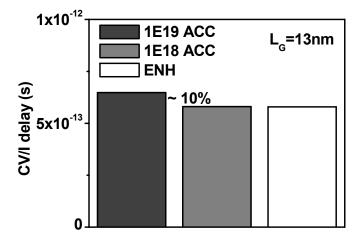

**Figure 2.11**: The intrinsic delay of heavily doped ACC mode design is within 10% of ENH mode design in spite of it much lower  $I_{ON}$ .

The charge centroid location in the ON state also provides a benefit in the capacitance for the heavily doped ACC mode design, while the lightly doped ACC mode

design behaves like the ENH mode design. The intrinsic charging delay of a transistor is determined not only by its  $I_{ON}$  but also by its gate capacitance ( $C_G$ ):  $\tau = C_G * V_{DD} / I_{ON}$ . Figure 2.10 and Figure 2.11 compare the gate capacitances and intrinsic delays of the two devices. Even though the  $I_{ON}$  of a heavily doped ACC mode FET is significantly lower than that of the ENH mode device, the lower gate capacitance of the ACC mode device compensates for it and helps to improve its intrinsic delay. As shown in Figure 2.11, this delay, for an ACC mode design, is within 10% of the intrinsic delay of the ENH mode device. Thus, the accumulation mode DG FET performance is comparable to the enhancement mode DG FET, with benefits in (i) S/D design (ii) lower gate current (iii) lower parasitic S/D resistance and, (iv) feasibility of single gate work function CMOS implementation. In the next subsection, we shall focus on short channel control comparisons and sensitivities to gate length and body thickness variations, which are also very important for highly scaled MOSFETs.

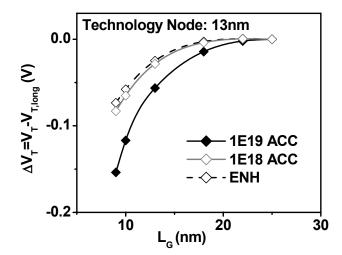

**Figure 2.12**:  $V_T$  roll-off plot comparing the ACC and ENH mode devices. Inherent poor short channel control leads to higher gate-length sensitivity of the heavily doped ACC mode design.

#### 2.3.2 Short Channel Effects and Sensitivities

Figure 2.12 plots the  $V_T$  roll-off curves (sensitivity to gate length variations) for the different ACC mode designs and the ENH mode design. The heavily doped ACC mode design is much more sensitive to  $L_G$  variations. This is expected because the intrinsic source-to-channel potential barrier for this device is almost zero since the source and the channel are doped heavily of the same type. This leads to easier penetration of the drain electric field to the source-channel barrier, thus providing weaker short channel control. Figure 2.13 compares the sensitivity of the devices to body thickness variations. Once again, the heavily doped ACC mode device has a much higher sensitivity than the ENH mode FET. Small changes in the body thickness of a heavily doped channel correlate to significant changes in the channel ionic charge contributing towards the  $V_T$  and higher sensitivities.

**Figure 2.13**: The heavily doped ACC mode design shows higher sensitivity to body thickness variations. A change in  $T_{Si}$  leads to significant change in channel ionic charge and hence  $V_T$ .

An important aspect of variations not been explored here, is the effect of statistical dopant fluctuations. For a very small channel volume, the number of dopant atoms is very few and therefore, their location and number (presence or absence of a dopant atom) becomes important with respect to variations. For a heavily doped ACC mode MOSFET, variations due to SDF effects will further add on to the sensitivities in  $L_G$  and  $T_{Si}$  fluctuations caused by LER effects. Overall, the accumulation mode MOSFET is more prone to variations than the enhancement mode design.

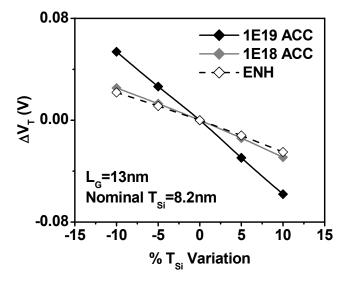

**Figure 2.14**: Schematic cross-section of the fabricated ACC mode FET. The channel doping was targeted  $\sim 5E19\text{cm}^{-3}$  requiring  $T_{Si} < 11\text{nm}$ . A planar architecture is designed in order to minimize topography related issues.

#### 2.4 Device Fabrication Issues

The fabrication of the accumulation mode MOSFET was attempted using (i) gate last as well as (ii) gate first approaches. Planar MOSFETs have an inherent topography advantage over non-planar architectures like the FinFET architecture. Therefore, in this work, a planar architecture was targeted and the device was designed in the back-gated mode (substrate is used as the back-gate and the silicon channel is formed on super thin buried oxide for reasonable back-gate control). A schematic cross-section of the target

device structure is shown in **Figure 2.14**. It can be clearly seen that in order to turn off the device, a very thin silicon channel will be needed. In order to avoid an impractically thin silicon channel thickness, back-gate control is required. Further, to maintain a reasonable gate control, a very thin buried oxide (BOX) layer is needed. Even though the S/D design becomes rather simple, the rest of the process turns out to be more complicated in the attempt to maintain a planar structure. The process optimization and the issues in fabrication of the back-gated accumulation mode MOSFET will be briefly discussed in this section.

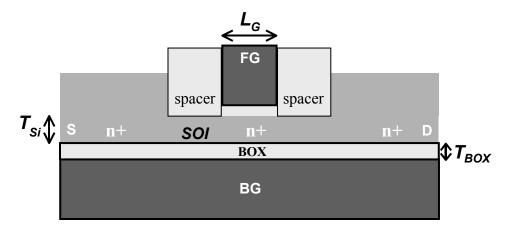

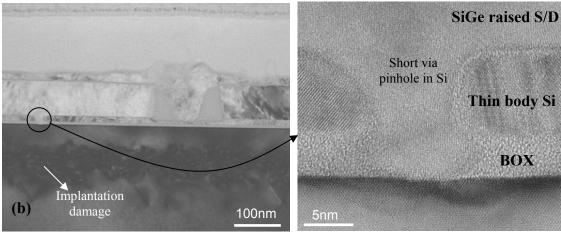

Figure 2.15: Basic process flow for the gate last process.

#### 2.4.1 Gate Last Process

A *gate last* approach was first adopted to fabricate the ACC mode back-gated MOSFET. The process flow is summarized diagrammatically in **Figure 2.15** and the flow table is provided in Appendix A. The motivation for looking at this approach is twofold:

(i) the  $L_G$  of the FET can be made very small using an inverse spacer process, rather than relying on lithography techniques like photoresist ashing and trimming and, (ii) the device can be subjected to high temperature processing almost until the last process steps, thus providing process flexibility.

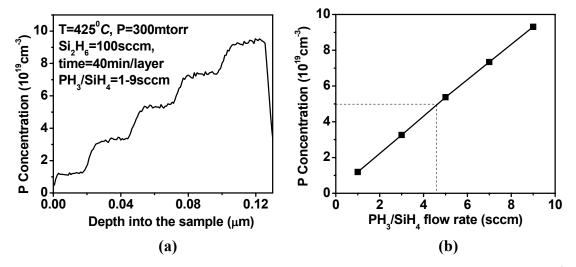

**Figure 2.16**: SIMS analysis to identify precise process conditions for 5E19cm<sup>-3</sup> channel doping. (a) SIMS raw data shows phosphorus concentration as a function of depth for a 5 step deposition process and (b) phosphorus concentration for each step (varying PH<sub>3</sub> flow rate) showing required PH<sub>3</sub>/SiH<sub>4</sub> flow rate to be 4.7sccm.

In this process, since the BOX layer is very thin, standard available SOI wafers could not be used. An amorphous silicon (a-Si) film was deposited and solid-phase crystallized to achieve a polycrystalline silicon channel. Heavily doped polysilicon is expected to have similar transport properties as single crystalline silicon, therefore, justifying the use of a polycrystalline film. The heavy doping in the silicon channel was achieved by in situ doping during the a-Si deposition in an LPCVD furnace (tystar19). A short flow process run was conducted to identify the doping concentration of phosphorus

in silicon using the in situ doping process. The deposition was done at  $425^{\circ}$ C and 300mtorr, using Si<sub>2</sub>H<sub>6</sub>=10sccm, PH<sub>3</sub>/SiH<sub>4</sub>=1-9sccm (in steps), and time=40min/layer. The SIMS analysis for phosphorus is shown in **Figure 2.16**. In order to achieve a doping concentration of ~5E19cm<sup>-3</sup>, PH<sub>3</sub>/SiH<sub>4</sub> flow rate of 4.7 sccm was identified. The channel silicon deposition was targeted for thicknesses of 5nm and 10nm at  $425^{\circ}$ C. In order to achieve a uniform deposition with minimal pin-hole density, a two step deposition process (10A seed layer deposition + doped silicon film deposition) was implemented. The films were crystallized by SPC (furnace, tylan6) at  $550^{\circ}$ C for 12 hours.

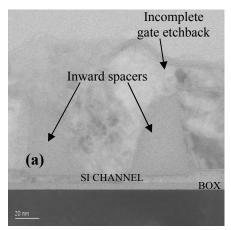

**Figure 2.17**: Issues of the gate last process: (a) Cross-sectional TEM micrograph of the completed gate last process for the ACC mode FET (b) Pinholes in Si layer cause HF etching of underlying BOX and shorts to substrate during SiGe S/D deposition.

With the above mentioned process for the channel, the complete process (as described in Appendix A) was implemented. This process required five lithography steps, two being critical. The inverse spacer process is promising from lithography point of view, but is very difficult to implement since identifying the etching end point (for inwards spacer) is challenging, especially for very short gate length devices. A two step etching (initial timed dry etch up to 90% + final wet etch in 100:1 HF) is required to ensure complete etching of the inverse spacer. The overetch time should also be carefully chosen to make sure that the inverse spacer is not completely lost. The TEM image of the completed device is shown in Figure 2.17(a) showing the complete device structure. One issue seems that the gate etchback process is not completed, as it was a timed etch process. Further, zooming into the S/D regions, as shown in Figure 2.17(b), 5nm shorts from S/D to substrate are observed. The most likely step at which these shorts were formed, are at the wafer precleaning step with a 100:1 HF dip prior to the SiGe raised S/D deposition. The HF could have percolated through tiny pinholes in the silicon film and etched through the ultra thin BOX film, to create the shorts to the substrate. A pure SiO<sub>2</sub> BOX layer is therefore, not recommended.

### **Shortcomings of Gate Last Process**

Summarizing, the gate last process faces several drawbacks, listed as follows:

- The inverse spacer etch process is difficult to implement due to inability to identify the end point.

- An ultra thin SiO<sub>2</sub> buried oxide film is undesirable to avoid accidentally etching it during wafer precleaning steps (which are unavoidable for a conventional process flow). A pure Si<sub>3</sub>N<sub>4</sub> dielectric is also undesirable, as Si:Si<sub>3</sub>N<sub>4</sub> dry etch selectivity is

difficult to achieve for the active area etching step. A double layer stack of  $Si_3N_4$  and  $SiO_2$  is therefore, the most appropriate buried oxide definition to evade all the problems.

• There is a lot of additional process complexity because of the replacement gate process. Moreover, it is not easy to time the end of gate etch back process.

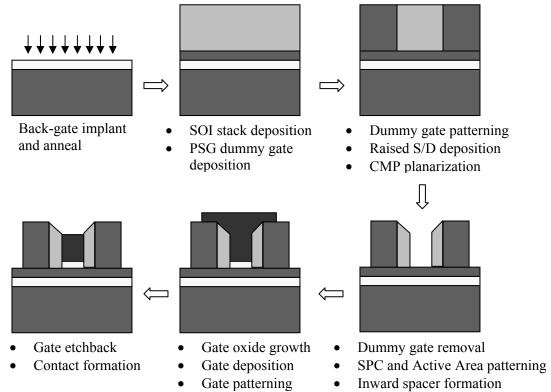

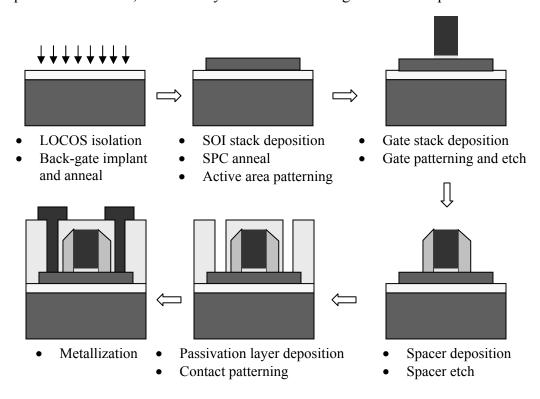

**Figure 2.18**: Process flow for gate first process. It is much simpler and closer to the standard bulk CMOS process than the gate last process. However, this process poses stringent requirements on the selectivities for active and gate etching steps.

#### 2.4.2 Gate First Process

In order to circumvent some of the issues of the gate last process, the *gate first* approach was tested. Once again, the process flow is summarized pictorially in **Figure**2.18 and in tabular form in Appendix A at the end of this thesis. In this process, a double

layer stack was used for the back-gate dielectric and Molybdenum gate with polysilicon cap was used for the top/front gate. The Mo layer is kept thin (200A) in order to be able to successfully stop the Mo etch on the ultra-thin silicon channel without completely etching away the thin silicon. This process is simpler than the previous process flow, but still suffers from the stringent dry etching requirements and was therefore, not implemented successfully. The ultra-thin Mo layer was easily oxidized during the furnace loading process for poly-Si cap deposition right after the Mo sputtering. Additionally, the active area dry etch went too deep on some wafers, once again, yielding shorts to the substrate.

Even though a planar architecture is very promising from a topography standpoint, implementing a reliable ultra-thin buried oxide process still remains a challenge. For future studies, increasing the metal gate thickness and reducing the polysilicon thickness may help alleviate the Mo oxidation problem, though the Mo gate-etch (to stop on polysi channel) selectivity would become even more stringent. It may therefore, be more suitable to opt for a non-planar architecture if there is a reasonable performance benefit from using the ACC mode design!

# 2.5 Summary

In this chapter, Accumulation mode double-gate MOSFET has been studied as a possible alternative to the conventional enhancement mode double-gate MOSFET for highly scaled sub-15nm MOSFETs. The chief benefit of the accumulation mode FET lies in the more manufacturable channel and S/D design, and feasibility to implement single gate work function CMOS technology. The performance of a heavily doped channel FET is limited by Coulombic scattering as expected, but has the important benefits of (a)

lower capacitance and (b) lower gate leakage current than the undoped channel enhancement mode design. These benefits arise from a lower vertical electric field in the on-state owing to a favorable charge centroid position (center of the channel). Therefore, intrinsic delay of the doped channel accumulation mode MOSFET is within 10% of its undoped channel enhancement mode counterpart. However, due to absence of an intrinsic source-channel barrier, the accumulation mode MOSFET has poorer short channel control, thus making it more sensitive to variations. In addition, statistical dopant fluctuation effects will add another component to the variations.

It has been shown that a planar architecture is not very simple to fabricate due to the challenges caused by the need for ultra-thin BOX and ultra-thin channel layers. These films make the etching processes very stringent and require highly selective etch recipes. It may therefore, be more beneficial to look at the non-planar FinFET-like architecture using spacer lithography process to fabricate this device.

Putting together all the pros and cons of the accumulation mode design, its device behavior, from performance as well as processing standpoints, is not significantly better over the enhancement mode design.

## 2.6 References

P. Bai, C. Auth, S. Balakrishnan, M. Bost, R. Brain, V. Chikarmane, R. Heussner, M. Hussein, J. Hwang, D. Ingerly, R. James, J. Jeong, C. Kenyon, E. Lee, S. H. Lee, N. Lindert, M. Liu, Z. Ma, T. Marieb, A. Murthy, R. Nagisetty, S. Natarajan, J. Neirynck, A. Ott, C. Parker, J. Sebastian, R. Shaheed, S. Sivakumar, J. Steigerwald, S. Tyagi, C. Weber, B. Woolery, A. Yeoh, K. Zhang, and M. Bohr, "A 65nm logic technology featuring 35nm gate lengths, enhanced channel strain,

- 8 Cu interconnect layers, low-k ILD and 0.57 μm<sup>2</sup> SRAM cell," in *2004 International Electron Devices Meeting. San Francisco, CA*, 2005, pp. 657-60.

- P. Ranade, T. Ghani, K. Kuhn, K. Mistry, S. Pae, L. Shifren, M. Stettler, K. Tone, S. Tyagi, and M. Bohr, "High performance 35nm L<sub>GATE</sub> CMOS transistors featuring NiSi metal gate (FUSI), uniaxial strained silicon channels and 1.2nm gate oxide," in *International Electron Devices Meeting*, 2005, pp. 217-20.

- [3] E. P. Gusev, V. Narayanan, and M. M. Frank, "Advanced high-K dielectric stacks with polySi and metal gates: recent progress and current challenges," *IBM Journal of Research and Development*, vol. 50, pp. 387-410, 2006.

- [4] L. Chang, Y.-K. Choi, D. Ha, P. Ranade, S. Xiong, J. Bokor, C. Hu, and T.-J. King, "Extremely scaled silicon nano-CMOS devices," *Proceedings of the IEEE*, vol. 91, pp. 1860-73, 2003.

- [5] Y.-K. Choi, T.-J. King, and C. Hu, "Nanoscale CMOS spacer FinFET for the terabit era," *IEEE Electron Device Letters*, vol. 23, pp. 25-7, 2002.

- [6] D. Hisamoto, W.-C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.-J. King, J. Bokor, and C. Hu, "FinFET-a self-aligned double-gate MOSFET scalable to 20 nm," *IEEE Transactions on Electron Devices*, vol. 47, pp. 2320-5, 2000.

- [7] P. Verheyen, N. Collaert, R. Rooyackers, R. Loo, D. Shamiryan, A. De Keersgieter, G. Eneman, F. Leys, A Dixit, M.Goodwin, Y.S.Yim, M. Caymax, K. De Meyer, P. Absil, M. Jurczak, and S. Biesemans, "25% Drive Current Improvement for p-type Multiple Gate FET (MuGFET) Devices by Introduction

- of Recessed Si<sub>0.8</sub>Ge<sub>0.2</sub> in the Source and Drain Regions," in *2005 Symposium on VLSI Technology*, 2005, pp. 194-5.

- [8] B. Doyle, B. Boyanov, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, R. Rios, and R. Chau, "Tri-Gate fully-depleted CMOS transistors: fabrication, design and layout," in 2003 Symposium on VLSI Technology, 2003, pp. 133-4.

- [9] H. Lee, L.-E. Yu, S.-W. Ryu, J.-W. Han, K. Jeon, D.-Y. Jang, K.-H. Kim, J. Lee, J.-H. Kim, S. C. Jeon, G. S. Lee, J. S. Oh, Y. C. Park, W. H. Bae, H. M. Lee, J. M. Yang, J. J. Yoo, S. I. Kim, and Y.-K. Choi, "Sub-5nm all-around gate FinFET for ultimate scaling," in *2006 Symposium on VLSI Technology*., 2006, pp. 58-9.

- [10] L. Chang, "Nanoscale Thin-Body CMOS Devices," in *PhD Thesis*: University of California, Berkeley, 2003.

- [11] E. Rauly, B. Iniguez, and D. Flandre, "Investigation of deep submicron single and double gate SOI MOSFETs in accumulation mode for enhanced performance," *Electrochemical and Solid-State Letters*, vol. 4, pp. G28-30, 2001.

- [12] L. Chang, S. Tang, T.-J. King, J. Bokor, and C. Hu, "Gate length scaling and threshold voltage control of double-gate MOSFETs," in *International Electron Devices Meeting*, 2000, pp. 719-22.

- [13] S. Wolf, *Silicon Processing for the VLSI Era* vol. 3 The Submicron MOSFEt Lattice Press, Sunset Beach, California.

- [14] T. Krishnamohan, C. Jungemann, and K. C. Saraswat, "A novel, very high performance, sub-20nm depletion-mode double-gate (DMDG) Si/Si<sub>x</sub>Ge<sub>(1-x)</sub>/Si

- channel PMOSFET," in *IEEE International Electron Devices Meeting*, 2003, pp. 687-90.

- [15] "Taurus-Device, v. 2003.12," Synopsys Inc., 2003.

- [16] International Technology Roadmap for Semiconductors, PIDS Chapter, <a href="http://public.itrs.net">http://public.itrs.net</a>.

- [17] S. Balasubramanian, L. Chang, B. Nikolic, and T.-J. King, "Circuit-Performance Implications for Double-Gate MOSFET Scaling below 25nm," *Proceedings of the 2003 Silicon Nanoelectronics Workshop*, pp. 16-17, June 2003.

# Chapter 3: V<sub>T</sub> Adjustment via L<sub>eff</sub> Engineering

## 3.1 Introduction

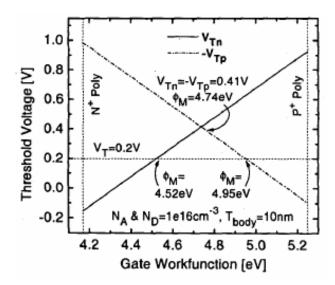

Thin-body enhancement-mode MOSFETs with enhanced carrier mobilities, will likely be required to meet power-performance targets with gate-length scaling. The FinFET [1-3] is a promising structure because it offers the superior scalability of the double-gate structure together with a fabrication process and layout similar to that of the conventional bulk-Si MOSFET [3]. An undoped channel is desired to eliminate V<sub>T</sub> variations due to statistical dopant fluctuation (SDF) effects in the channel, and to attain the highest possible carrier mobilities to achieve high I<sub>ON</sub> [1]. However, it necessitates an alternative means for adjusting V<sub>T</sub>. Figure 3.1 [4] shows the threshold voltage dependence on gate work function for undoped channel NMOS and PMOS FinFETs. In order to achieve symmetric V<sub>T</sub> (s), two different gate work functions are needed and dual gate work function  $(\Phi_{\rm M})$  technology has been explored as one of the techniques for adjusting the threshold voltages. Different work functions for NMOS and PMOS can be achieved by engineering the work function by methods such as phase engineering [5, 6], and masked ion-implantation [7-10]. These are promising approaches, but face drawbacks when applied to dense circuits.

**Figure 3.1**: Threshold voltage requirement for undoped channel thin body NMOS and PMOS FinFETs [4]. Different gate work functions for NMOS and PMOS are needed to achieve symmetric high performance (HP) V<sub>T</sub> values, thus motivating dual gate technology.

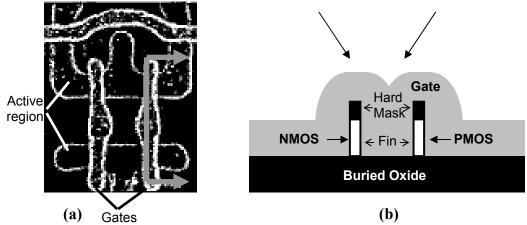

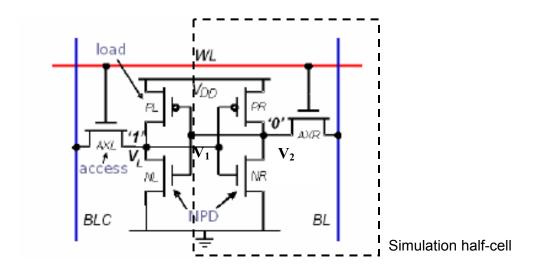

For compact circuit layouts such as those used in static memory (SRAM) arrays [11], it is not possible to separately implant the gate electrodes in the n- and p-channel regions if the FinFET structure is employed. This is because the gate layer fills the entire region in-between the n-channel and p-channel fins (Figure 3.2) making it impossible to selectively and reliably change the work function of one of the FET gates. Thus, a single gate work function must be used for both devices, and another means for adjusting the threshold voltage should be investigated. In this chapter,  $L_{\rm eff}$  engineering (by S/D engineering) is explored as the alternative means to adjust  $V_T$ , and the advantages and limitations of this technique are presented.

**Figure 3.2**: (a) SRAM layout and (b) schematic cross-section of a CMOS FinFET SRAM [11] inverter. If the separation between NMOS and PMOS active areas (Si fins) is less than twice the gate thickness, the gate completely fills the region inbetween, so that it is difficult to achieve different gate work functions for the NMOS and PMOS gates.

# 3.2 V<sub>T</sub> Tuning by S/D Engineering

For a given technology node, the transistor physical parameters such as gate length ( $L_G$ ) and gate oxide thickness ( $T_{OX}$ ) are predetermined [12]. The fin thickness ( $T_{Si}$ ) is somewhat flexible, based on the desired control of short channel effects [13, 14] and the available process window (to minimize  $V_T$  variations due to fin line-edge roughness), but is likely to be identical for NMOS and PMOS devices for a given technology node. The threshold voltage ( $V_T$ ) for a FinFET structure can therefore be adjusted using one or more of three device parameters: channel doping ( $N_{Body}$ ), gate work function ( $\Phi_M$ ), and electrical channel length ( $L_{eff}$ ). Since channel doping and gate work function engineering are not good strategies for  $V_T$  tuning for high density FinFET layouts, the methodology available for  $V_T$  tuning is  $L_{eff}$  engineering, keeping a fixed gate work function for all devices.

Previous studies [15] have shown that, in order to optimize the trade-off between parasitic series resistance and short-channel effects, a gate-underlapped structure will be required to achieve peak circuit performance for sub-20nm gate length.  $V_T$  becomes a strong function of  $L_{eff}$ , in this case. The  $L_{eff}$  can be adjusted by engineering the S/D profile, which in turn, is a function of the gate-sidewall spacer thickness ( $L_{SP}$ ) and doping lateral abruptness ( $\sigma_{SD}$ ). Since the S/D profile is the only control "knob", either the short channel effect or the  $V_T$  (and not both at the same time) can be adjusted using this method. Our goal will be to achieve the desired  $V_T$  and performance by the appropriate S/D design. To operate within a target  $V_T$  roll-off constraint, the fin thickness ( $T_{Si}$ ) is used as another variable (partially), but the same value must be maintained for NMOS and PMOS devices. In the following sections, the feasibility of implementing single-gate work function CMOS FinFETs is investigated by 2D and 3D device simulations.

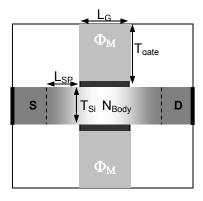

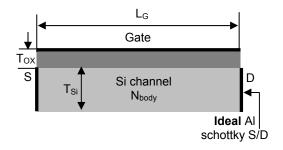

## 3.2.1 Device Simulation Set-up

To investigate the methodology discussed above, 2-D and 3-D device simulations have been carried out using Taurus-Device [16] using self-consistent Drift-diffusion transport and 1D-Schrodinger (or MLDA quantum model) solutions. It should be noted that all simulations have (i) the quantum mechanical model for inversion charge confinement, (ii) no carrier temperature dependent current enhancement models and (iii) no mobility enhancement models (strain engineering) implemented. These simulations therefore, underestimate the performance (I<sub>ON</sub>) owing to the models that have been used. 2D simulations have been implemented for LSTP FinFETs in this section to demonstrate

the  $L_{\text{eff}}$  engineering concept. 3D simulations have been used to extend the concept to HP and LOP devices, and are presented in section 3.2.4.

**Figure 3.3**: Schematic of the 2D simulation structure.  $L_{SP}$  denotes the location at which the S/D gradient begins (referenced to the gate edge).

| Device Parameters                 |                       |  |

|-----------------------------------|-----------------------|--|

| Gate length L <sub>G</sub>        | 18 nm                 |  |

| Gate-dielectric EOT               | 9 Å                   |  |

| Body thickness, T <sub>Si</sub>   | 9 or 12 nm            |  |

| Gate thickness, T <sub>Gate</sub> | 27 nm                 |  |

| Body doping, N <sub>body</sub>    | 1E16 cm <sup>-3</sup> |  |

| S/D doping, N <sub>S/D</sub>      | 1E20 cm <sup>-3</sup> |  |

| Gate $\phi_M$                     | 4.7 eV                |  |

| $V_{ m DD}$                       | 0.9 V                 |  |

| Target I <sub>OFF</sub>           | 80 pA/μm              |  |

| Target I <sub>ON</sub>            | 880 μA/μm             |  |

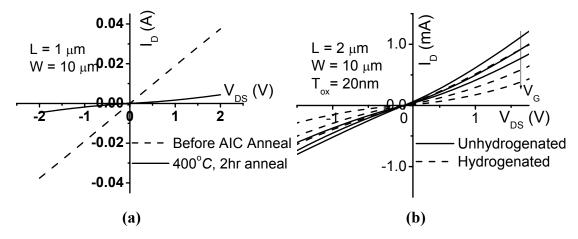

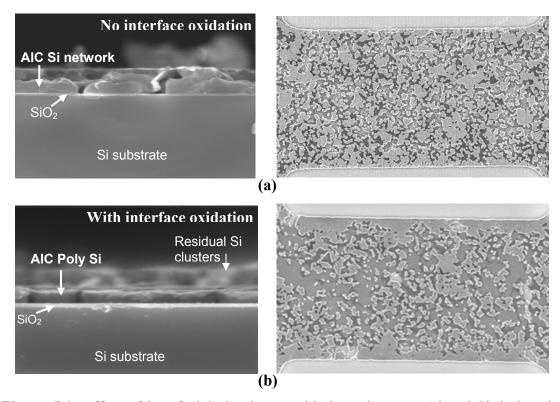

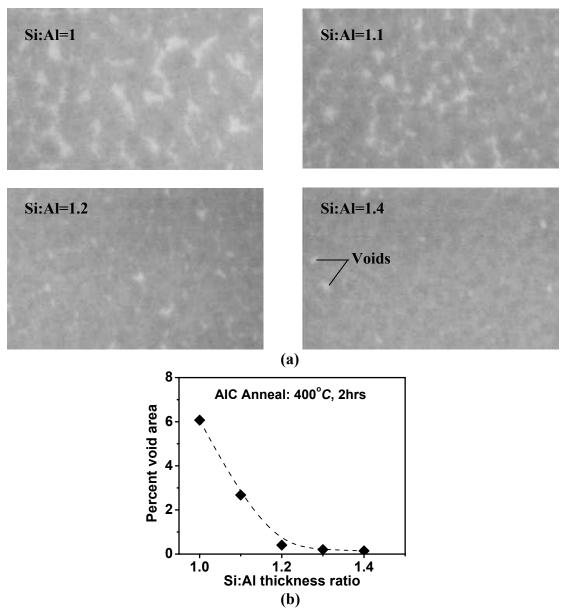

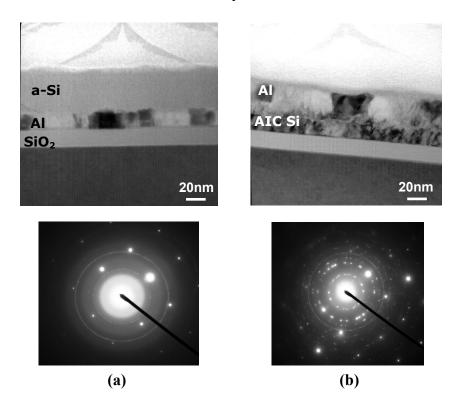

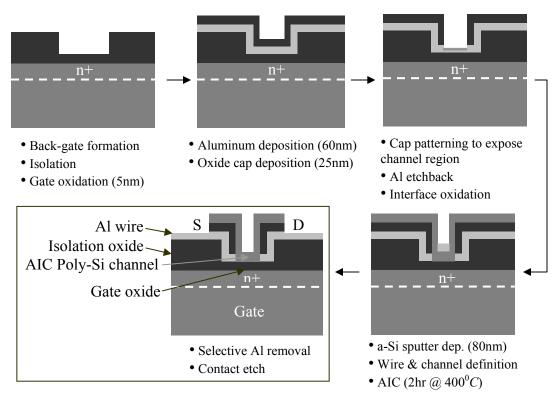

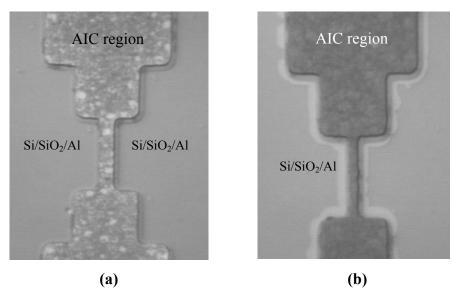

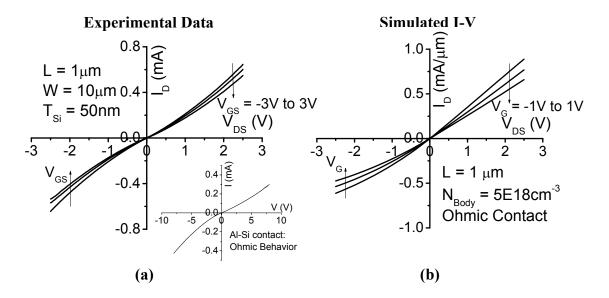

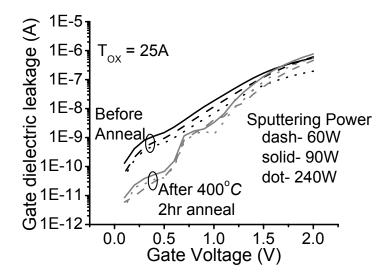

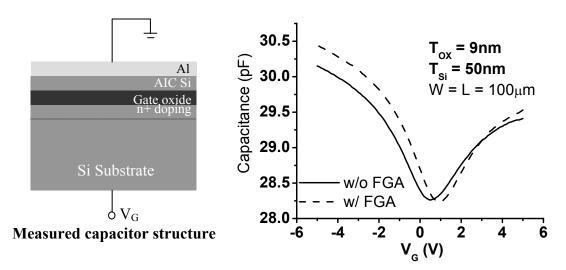

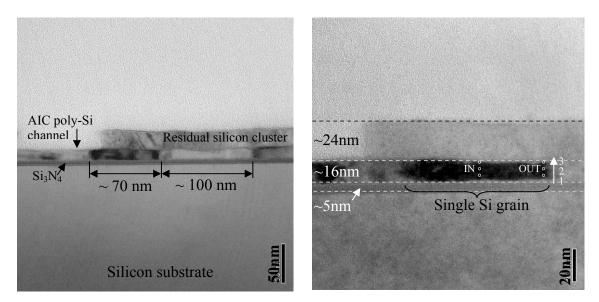

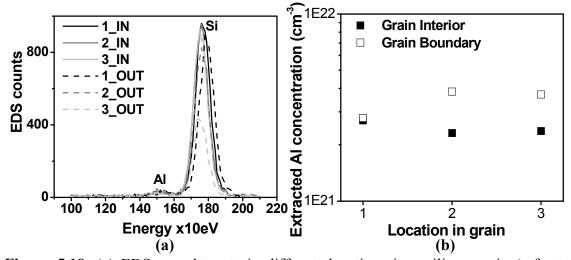

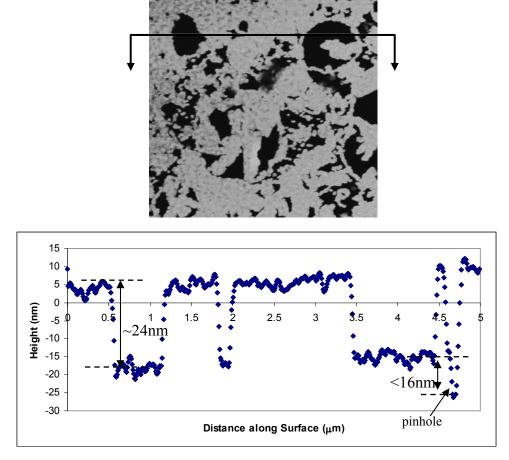

**Table 3.1**: Nominal device parameter values used for the simulations.