# Novel Processes for Poly-Si Thin-Film Transistors on Plastic Substrates

Daniel Albert Good

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2007-62 http://www.eecs.berkeley.edu/Pubs/TechRpts/2007/EECS-2007-62.html

May 17, 2007

Copyright © 2007, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Novel Processes for Poly-Si Thin-Film Transistors on Plastic Substrates

by

#### Daniel Albert Good

B.S. (Massachusetts Institute of Technology) 2002 M.Eng. (Massachusetts Institute of Technology) 2002

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Vivek Subramanian Professor Oscar Dubon

Spring 2007

| Chair | Date |

|-------|------|

|       |      |

|       |      |

|       |      |

|       | Date |

|       |      |

|       |      |

|       | Date |

The dissertation of Daniel Albert Good is approved.

University of California, Berkeley Spring 2007 Novel Processes for Poly-Si Thin-Film Transistors on Plastic Substrates

Copyright © 2007

by

Daniel Albert Good

#### Abstract

Novel Processes for Poly-Si Thin-Film Transistors on Plastic Substrates

by

#### Daniel Albert Good

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

Flat panel display costs have been decreasing rapidly in recent years, due to swift progress in thin-film transistor (TFT) processing technology. The next step to a lower cost and more versatile display is the fabrication of displays on flexible plastic substrates. In order to realize this goal, high performance devices need to be fabricated in a process compatible with the low thermal budget of these substrates. Plastic compatible polycrystalline silicon (poly-Si) TFT processes are widely known, but several crucial steps have not been adapted to the low-temperature substrates. This work seeks to address several of the limiting factors in the plastic-compatible poly-Si TFT process.

Poly-Si devices have a large number of crystalline defects, which are typically made electrically inactive through a hydrogen plasma annealing process. However, hydrogen plasma annealing requires temperatures not compatible with low-cost plastic substrates. This work demonstrates an alternative passivation technique, implanting an impurity into the amorphous silicon film immediately after deposition. During subsequent laser crystallization, the impurity species is able to diffuse to grain boundaries and passivate defects, achieving an effect similar to hydrogen passivation. Performance and reliability of

this defect passivation process is compared with hydrogen plasma passivation in low and

high temperature fabrication processes.

Two other novel processes were investigated. A reactively sputtered gate dielectric layer

was used to replace one deposited with a more conventional high density plasma. Device

performance was limited compared with high-quality  $\mathrm{SiO}_2$  deposition processes, but was

sufficient for demonstration of passivation effects in a plastic-compatible process using the

previously described technique.

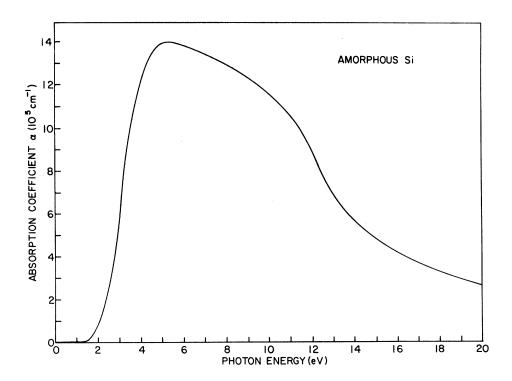

Finally, the use of a visible copper vapor laser as an alternative to UV excimer

laser for crystallization of amorphous silicon was demonstrated. Uniformity of

fabricated devices without any passivation treatment was far superior when the

copper vapor laser was used for crystallization. This is due both to its better pulse

energy stability and to the lower sensitivity of the process at longer wavelengths.

Professor Tsu-Jae King Liu Dissertation Committee Chair

2

To my wonderful friends and family.

## Contents

| $\mathbf{C}$ | onter            | ts                                                                  | ii           |

|--------------|------------------|---------------------------------------------------------------------|--------------|

| Li           | st of            | Figures                                                             | $\mathbf{v}$ |

| Li           | $\mathbf{st}$ of | Tables                                                              | ⁄iii         |

| A            | ckno             | wledgements                                                         | ix           |

| 1            | Intr             | oduction                                                            | 1            |

|              | 1.1              | Display Technologies                                                | 1            |

|              |                  | 1.1.1 Cathode Ray Tubes to Flexible Displays                        | 1            |

|              |                  | 1.1.2 Liquid Crystal Display Technology                             | 3            |

|              |                  | 1.1.3 Thin-Film Transistor Performance Requirements                 | 5            |

|              | 1.2              | Thin-Film Transistor Fabrication Technologies                       | 7            |

|              |                  | 1.2.1 Amorphous Silicon                                             | 8            |

|              |                  | 1.2.2 Polycrystalline Silicon                                       | 9            |

|              | 1.3              | Challenges for Poly-Si TFTs on Plastic Substrates                   | 12           |

|              |                  | 1.3.1 Process Thermal Budget Limitations                            | 12           |

|              |                  | 1.3.2 Device Uniformity                                             | 14           |

|              |                  | 1.3.3 Device Reliability                                            | 16           |

|              | 1.4              | Thesis Organization                                                 | 16           |

|              | 1.5              | References                                                          | 17           |

| 2            |                  | n Film Transistor Passivation by Ion Implantation and Excimer Laser | <b>01</b>    |

|              |                  |                                                                     | 21           |

|              | 2.1              | Introduction                                                        | 21           |

|   | 2.2   | Thin Film Transistor Passivation Techniques                                       | 22      |

|---|-------|-----------------------------------------------------------------------------------|---------|

|   | 2.3   | Motivation                                                                        | 26      |

|   | 2.4   | Process Flow                                                                      | 29      |

|   | 2.5   | Device Results                                                                    | 30      |

|   | 2.6   | Summary                                                                           | 38      |

|   | 2.7   | References                                                                        | 38      |

| 3 |       | ra-Low Temperature Poly-Si Thin Film Transistor Fabrication an<br>ect Passivation | d<br>43 |

|   | 3.1   | Ultra-Low Temperature Process Challenges                                          | 43      |

|   | 3.2   | Deposition of a $SiO_2$ Gate Dielectric Layer by Reactive Sputtering of $Si$      | 45      |

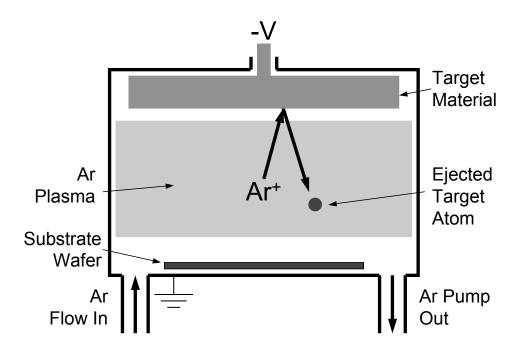

|   |       | 3.2.1 Sputter Deposition Background                                               | 45      |

|   |       | 3.2.2 Damage Reduction By Plasma Charge Trap                                      | 48      |

|   |       | 3.2.3 Reactive Sputtering Process Development                                     | 49      |

|   |       | 3.2.4 UV Photo-oxidation Pretreatment                                             | 52      |

|   |       | 3.2.5 Laser Oxide Annealing                                                       | 55      |

|   | 3.3   | Ultra-Low Temperature Thin Film Transistor Process                                | 56      |

|   | 3.4   | Device Performance                                                                | 58      |

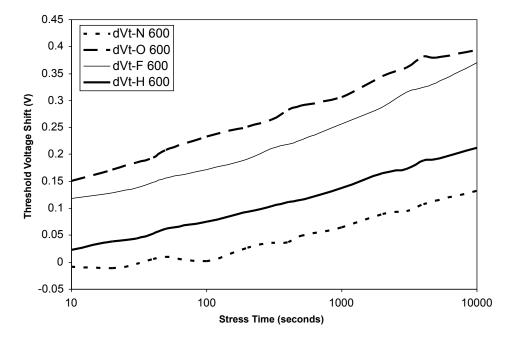

|   |       | 3.4.1 Nominal Device Performance                                                  | 58      |

|   |       | 3.4.2 Effects of Passivation Implant                                              | 60      |

|   |       | 3.4.3 Effects of Non-Melt Laser Annealing                                         | 61      |

|   |       | 3.4.4 Effects of Gate Oxide Laser Annealing                                       | 62      |

|   | 3.5   | Device Reliability                                                                | 65      |

|   |       | 3.5.1 Effects of Passivation Implant                                              | 66      |

|   |       | 3.5.2 Effects of Non-Melt Laser Annealing                                         | 66      |

|   |       | 3.5.3 Effects of Gate Oxide Laser Annealing                                       | 69      |

|   | 3.6   | References                                                                        | 70      |

| 4 | Silio | con Crystallization by Copper Vapor Laser Annealing                               | 73      |

| - | 4.1   | Laser Properties                                                                  | 73      |

|   | 4.2   | Process Flow                                                                      | 76      |

|   | 4.3   | Device Results                                                                    | 78      |

|   |       | 4.3.1 Unpassivated Devices                                                        | 78      |

|   |       | 4 3 2 Passivated Devices                                                          | 82      |

|   | 4.4 | Summ    | nary                                                              | 87  |

|---|-----|---------|-------------------------------------------------------------------|-----|

|   | 4.5 | Refere  | ences                                                             | 87  |

| 5 | Cor | ıclusio | ns                                                                | 89  |

|   | 5.1 | Summ    | nary                                                              | 89  |

|   | 5.2 | Contr   | ibutions                                                          | 90  |

|   | 5.3 | Recon   | nmendations for Future Work                                       | 92  |

|   |     | 5.3.1   | Defect Passivation by Ion Implantation and Pulsed-Laser Annealing | 92  |

|   |     | 5.3.2   | Reactive Sputtering of Silicon Dioxide                            | 94  |

|   |     | 5.3.3   | Silicon Crystallization by Copper Vapor Laser Annealing           | 94  |

|   | 5 4 | Refere  | PACES                                                             | Q.F |

# List of Figures

| 1.1  | A cathode ray tube display                                                                                                   | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | A liquid crystal light modulator                                                                                             | 4  |

| 1.3  | Circuit schematic of an LCD active matrix backplane                                                                          | 5  |

| 1.4  | Cross-section of a bottom-gated $\alpha$ -Si:H thin-film transistor                                                          | 8  |

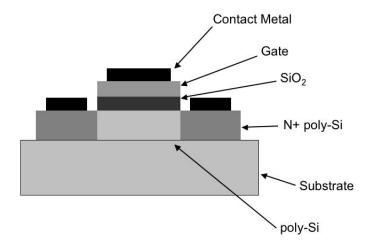

| 1.5  | Cross-section of a top-gated polycrystalline silicon thin-film transistor                                                    | 11 |

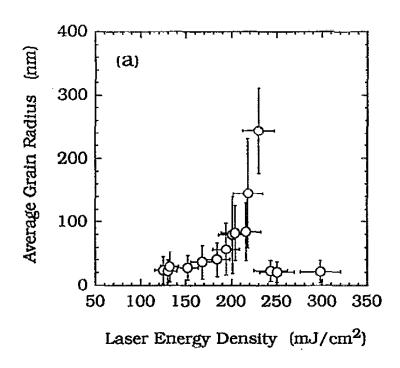

| 1.6  | Measured polysilicon grain size vs. excimer laser annealing energy                                                           | 15 |

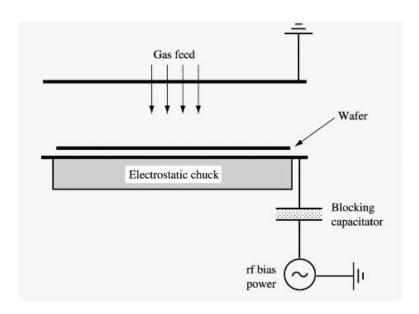

| 2.1  | Schematic drawing of a parallel-plate plasma reactor                                                                         | 23 |

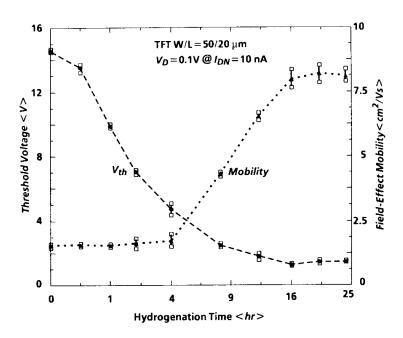

| 2.2  | Threshold voltage and field-effect mobility as functions of hydrogen plasma annealing time                                   | 24 |

| 2.3  | Unpaired spins in polycrystalline silicon after hydrogen plasma annealing at different temperatures                          | 24 |

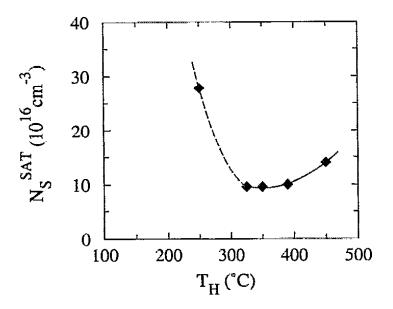

| 2.4  | Dark conductivity and photoconductivity in polycrystalline silicon films after high-pressure $\rm H_2O$ treatment            | 25 |

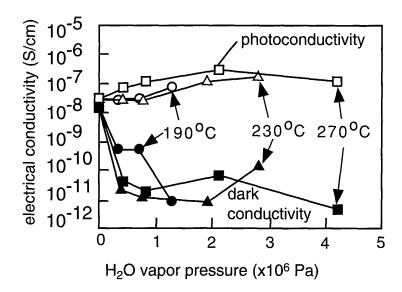

| 2.5  | Transfer curves and extracted parameters of polysilicon TFTs with and without fluorine passivation                           | 26 |

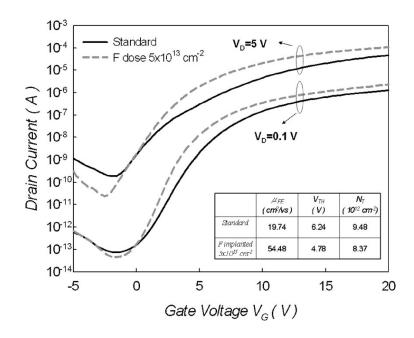

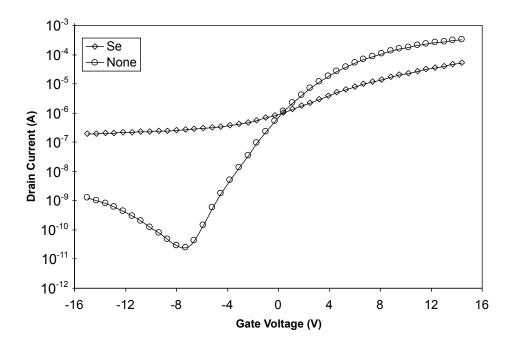

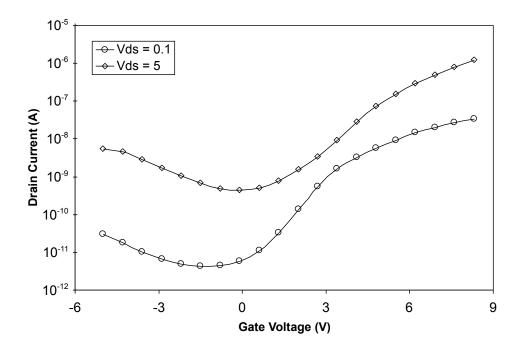

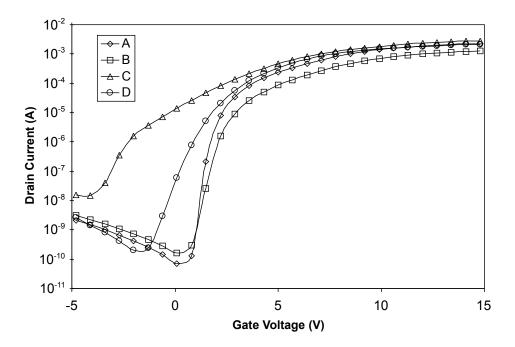

| 2.6  | $I_D$ vs. $V_{GS}$ transfer curves for unimplanted TFTs vs. TFTs implanted with Se                                           | 32 |

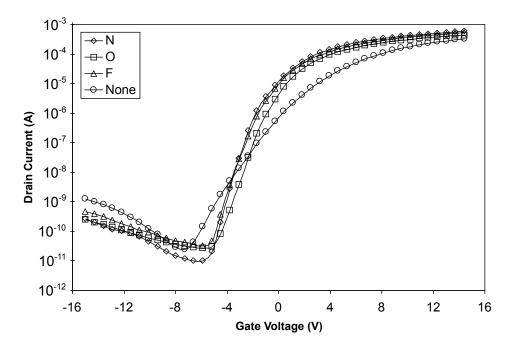

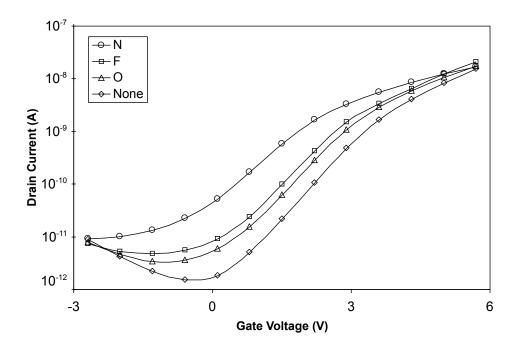

| 2.7  | $I_D$ vs. $V_{GS}$ transfer curves for unimplanted TFTs vs. TFTs implanted with F, O, and N                                  | 33 |

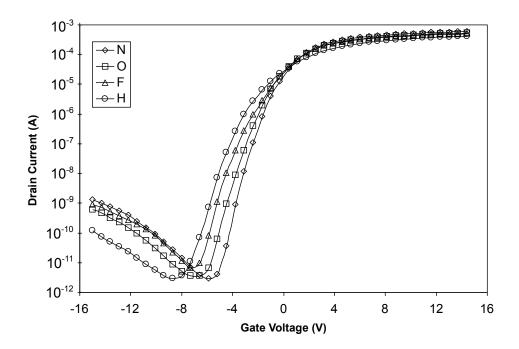

| 2.8  | $I_D$ vs. $V_{GS}$ transfer curves for hydrogen plasma passivated TFTs vs. TFTs implanted with F, O, and N                   | 34 |

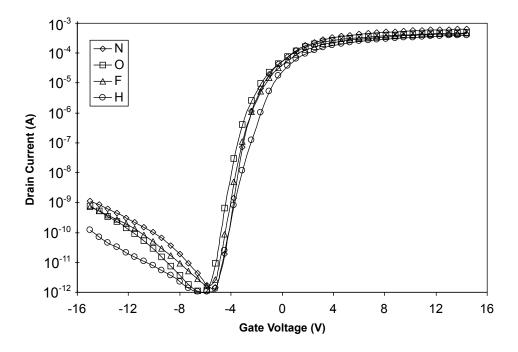

| 2.9  | $I_D$ vs. $V_{GS}$ transfer curves for $600^{\circ}C$ annealed TFTs passivated by hydrogen plasma and by F, O, and N implant | 35 |

| 2.10 | Unpassivated TFTs with and without $600^{\circ}\mathrm{C}$ annealing after excimer laser crystallization                     | 36 |

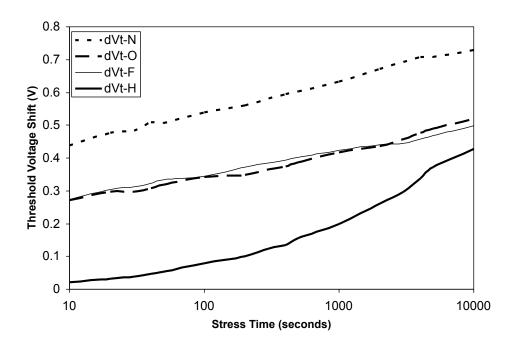

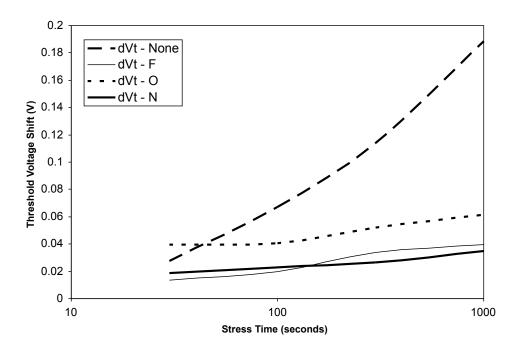

| 2.11 | Threshold voltage shift vs. stress time for low temperature processed devices.                                               | 37 |

| 2.12 | Threshold voltage shift vs. stress time for devices which received 600°C annealing after laser crystallization                                                                                      | 37 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | 150 °C processed TFTs fabricated by Gosain et al                                                                                                                                                    | 44 |

| 3.2  | A typical dc sputter chamber                                                                                                                                                                        | 46 |

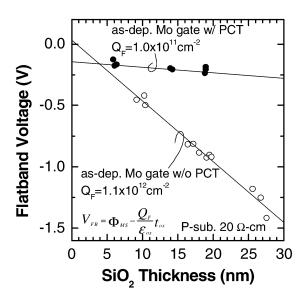

| 3.3  | A dc sputter chamber with plasma charge trap                                                                                                                                                        | 48 |

| 3.4  | Reduction of charge incorporated into a sputtered Mo thin film by plasma charge trap                                                                                                                | 49 |

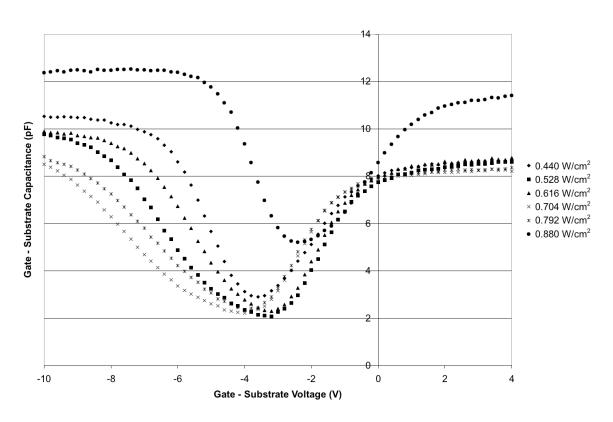

| 3.5  | Capacitance - Voltage curves for reactively sputtered gate ${\rm SiO_2}$ layers varying deposition power density from $0.44{\rm W/cm^2}$ to $0.88{\rm W/cm^2}$                                      | 50 |

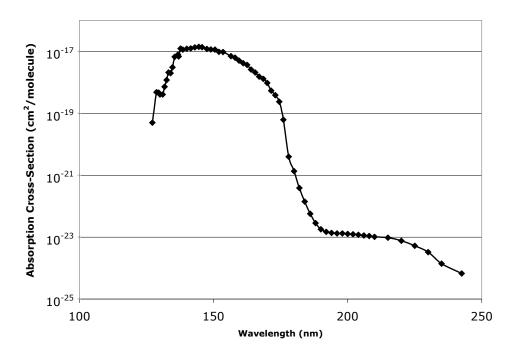

| 3.6  | Oxygen absorption of light in the range 125 nm - 250 nm                                                                                                                                             | 53 |

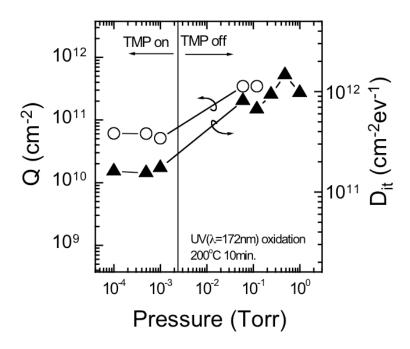

| 3.7  | Fixed charge and interface trap density of thin $SiO_2$ films grown by UV photooxidation, varying pressure between $1\times 10^{-4} \rm Torr$ and $1 \rm Torr.$                                     | 54 |

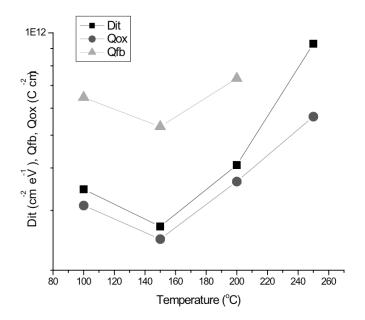

| 3.8  | Fixed charge, charge at flatband, and interface trap density of thin SiO $_2$ films grown by UV photooxidation, varying temperature between 100 $^{\circ}\mathrm{C}$ and 250 $^{\circ}\mathrm{C}$ . | 54 |

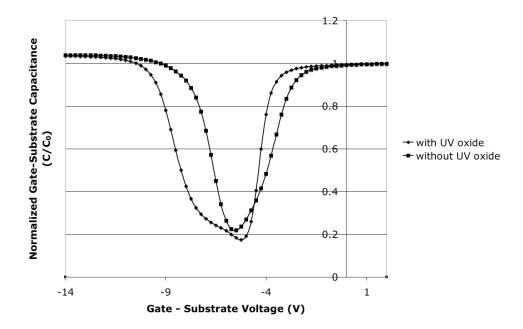

| 3.9  | Capacitance - Voltage plots for capacitors made with reactively sputtered ${ m SiO}_2$ with and without photooxidation pretreatment                                                                 | 55 |

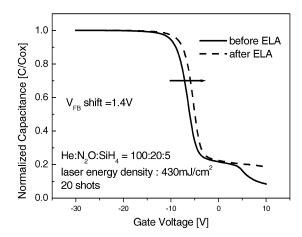

| 3.10 | Capacitance - Voltage plots for capacitors made with ICP-CVD at $150^{\circ}$ C before and after excimer laser annealing                                                                            | 56 |

| 3.11 | Transfer characteristics of a TFT fabricated at 150 °C with reactively sputtered gate oxide                                                                                                         | 60 |

| 3.12 | Transfer characteristics of TFTs processed at 150 °C with N, O, and F passivation implants                                                                                                          | 62 |

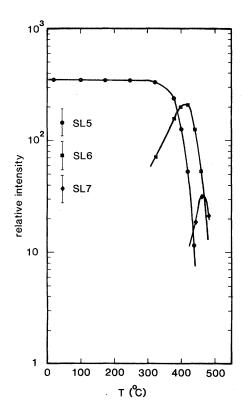

| 3.13 | Electron paramagnetic resonance measurements of nitrogen doped silicon after 20 minutes annealing at varying temperatures                                                                           | 63 |

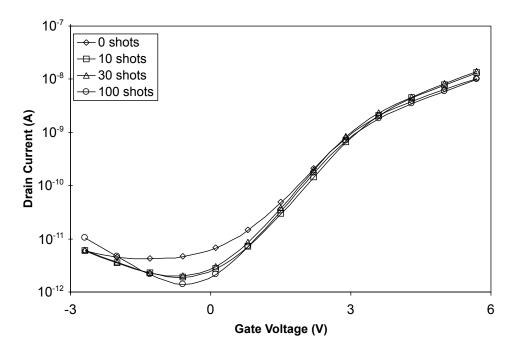

| 3.14 | Transfer characteristics of 150 °C processed, unpassivated devices with 0 - 100 pulses of non-melt laser annealing after crystallization                                                            | 64 |

| 3.15 | Transfer characteristics of TFTs processed at 150 °C with N, O, and F passivation implants and gate oxide laser annealing                                                                           | 65 |

| 3.16 | Threshold voltage shift with electrical stressing time of devices with N, O, and F implant, and control devices                                                                                     | 67 |

| 3.17 | Threshold voltage shift with electrical stressing time of devices with passivation implant and non-melt laser annealing                                                                             | 68 |

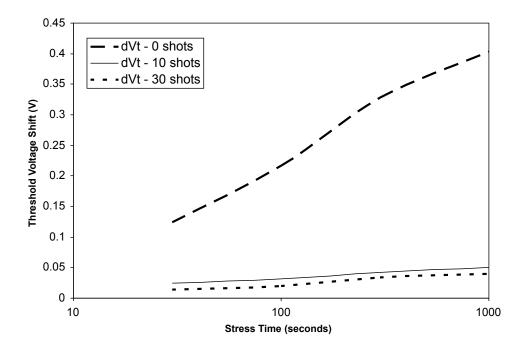

| 3.18 | Threshold voltage shift with electrical stressing time of devices with 0 - 100 non-melt laser annealing pulses                                                                                      | 68 |

| 3.19 | Threshold voltage shift with electrical stressing time of devices with passivation implant, non-melt laser annealing, and gate oxide laser annealing.                                               | 69 |

| 3.20 | Threshold voltage shift with electrical stressing time of devices with 0 - 30 non-melt laser annealing pulses and gate oxide laser annealing                                   | 70 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | Optical absorption coefficient for amorphous silicon                                                                                                                           | 74 |

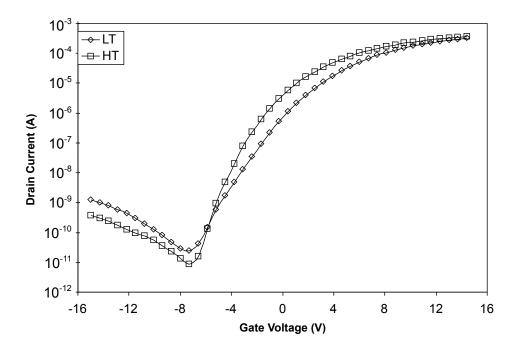

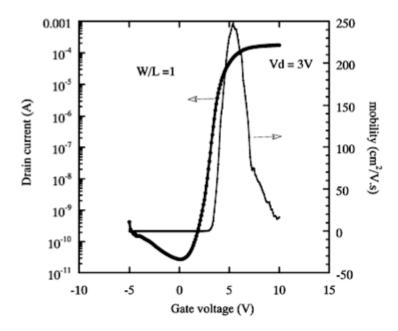

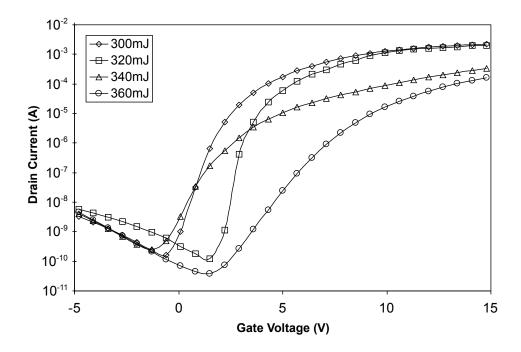

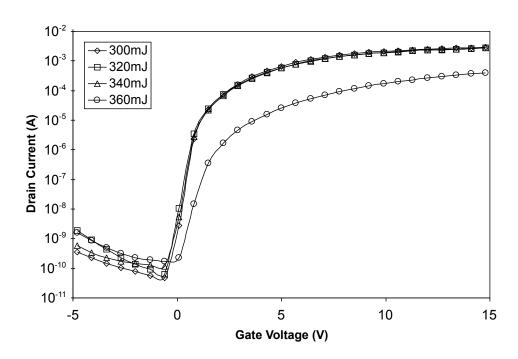

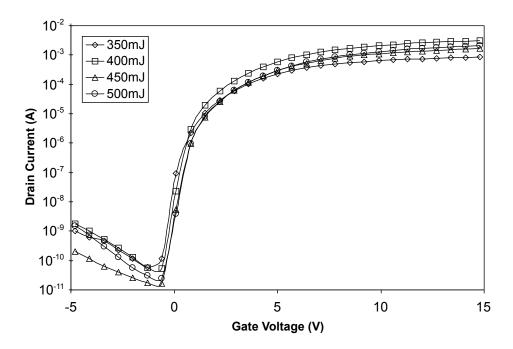

| 4.2  | Typical TFT performance for silicon films crystallized by excimer laser annealing at $300\mathrm{mJ/cm^2}$ to $360\mathrm{mJ/cm^2}$ , before hydrogen plasma passivation.      | 79 |

| 4.3  | TFT performance for four devices crystallized by excimer laser annealing at $300\mathrm{mJ/cm^2}$ , before hydrogen plasma passivation                                         | 80 |

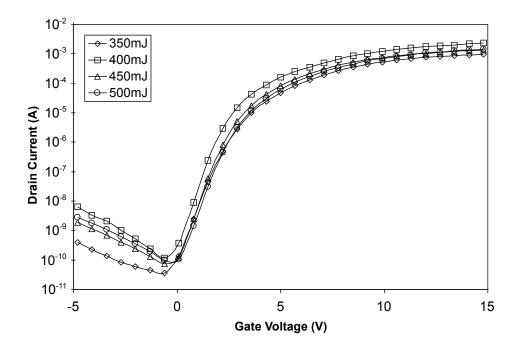

| 4.4  | Typical TFT performance for silicon films crystallized by copper vapor laser annealing at $350\mathrm{mJ/cm^2}$ to $500\mathrm{mJ/cm^2}$ , before hydrogen plasma passivation. | 81 |

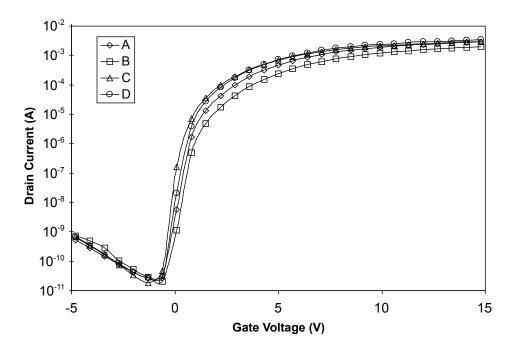

| 4.5  | TFT performance for four devices crystallized by copper vapor laser annealing at $400\mathrm{mJ/cm^2}$ , before hydrogen plasma passivation                                    | 82 |

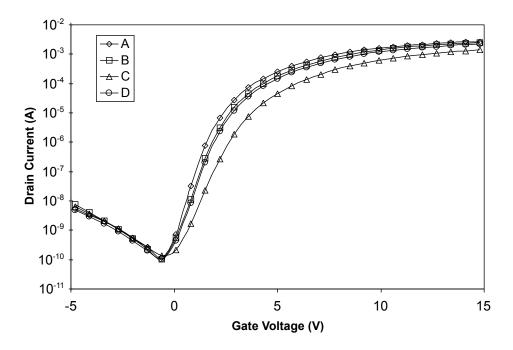

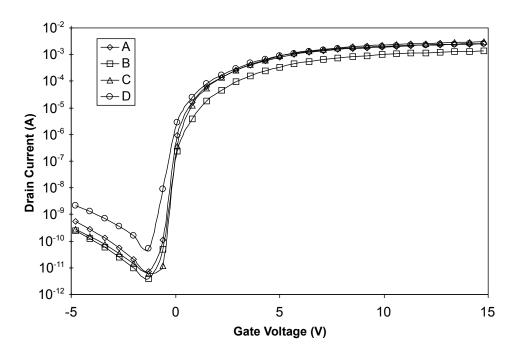

| 4.6  | Typical TFT performance for silicon films crystallized by excimer laser annealing at $300\mathrm{mJ/cm^2}$ to $360\mathrm{mJ/cm^2}$ , after hydrogen plasma passivation.       | 83 |

| 4.7  | Typical TFT performance for silicon films crystallized by copper vapor laser annealing at $350\mathrm{mJ/cm^2}$ to $500\mathrm{mJ/cm^2}$ , after hydrogen plasma passivation.  | 84 |

| 4.8  | TFT performance for four devices crystallized by excimer laser annealing at $300\mathrm{mJ/cm^2}$ , after hydrogen plasma passivation                                          | 86 |

| 4.9  | TFT performance for four devices crystallized by copper vapor laser annealing at $400 \mathrm{mJ/cm^2}$ , after hydrogen plasma passivation                                    | 86 |

## List of Tables

| 2.1 | Performance of 450 °C Processed Devices and 600 °C Processed Devices<br>Before and After 350 °C Annealing | 31 |

|-----|-----------------------------------------------------------------------------------------------------------|----|

| 3.1 | Performance of 150 $^{\circ}\mathrm{C}$ Processed Devices without Gate Oxide Annealing                    | 58 |

| 3.2 | Performance of 150 $^{\circ}\mathrm{C}$ Processed Devices with Gate Oxide Annealing                       | 59 |

| 4.1 | Copper Vapor Laser Annealing Schedule                                                                     | 77 |

| 4.2 | Measured Performance for Unpassivated Excimer Laser Annealed and Copper Vapor Laser Annealed Devices      | 78 |

| 4.3 | Measured Performance for Passivated Excimer Laser Annealed and Copper Vapor Laser Annealed Devices        | 83 |

| 4.4 | Statistics for Devices Annealed by Excimer Laser and by Copper Vapor Laser.                               | 85 |

#### Acknowledgements

I would like to thank my research advisor, Professor Tsu-Jae King Liu, for her kind guidance through my time in the device group. She provided me with the freedom to do the research I wanted to, and the knowledge and support to make it successful. She additionally gave me the assistance I needed to reenter Berkeley after taking some time away from school. I have been very happy to have her as my research mentor.

I would like to thank Professor Vivek Subramanian for serving on my qualifying examination committee and dissertation committee, and for many useful discussions both before and after my decision to return to graduate school. His guidance eased my transition back to school and got my research started in the right direction. I am additionally very grateful to Professor Oscar Dubon for serving on my qualifying examination committee and dissertation committee, and for his great support of my research during my time at Berkeley. He has always provided a valuable perspective on my work and helped me to remain excited about it. I would also like to thank Professor Borivoje Nikolic for serving on my qualifying examination committee.

I am grateful to Paul Wickboldt of JEM Enterprises, as well as to Potomac Photonics Inc., Sencera LLC., and SEMATECH for providing me with financial support.

I also owe a great deal of thanks to Monty Cleeves, Pat Smith, Arvind Kamath, and everyone else at Kovio. Monty was a great teacher when I was first learning the laboratory skills that have taken me to where I am now. Pat's expertise in laser annealing was invaluable as I learned how to form poly-Si films. Additionally, Pat and Arvind were very generous with their time and resources, assisting me with laser processing and a crucial metal deposition step.

I greatly appreciate the efforts of Xiaofan Meng, for assisting me with  $SiO_2$  deposition, and of Seung Yeul Yang, for helping me with x-ray diffraction measurements.

I owe many thanks to everyone who helped me get my work done in the lab successfully and on time. Many people assisted me with equipment, but in particular, Noel Arellano helped me more times than I can count, staying in the lab until late just to help me get started on new tools. Additionally, the efforts of the Microlab staff to keep everything running are appreciated. The assistance I have received from Joe Donnelly has been essential to my laboratory work. He was always available to make sure the sputter deposition system was ready for me when I needed it, and to get me through on time even when it was having difficulties.

I am very grateful to Ruth Gjerde for her unfailing support throughout my graduate career, particularly as I was finding my out of and back into graduate school. Our department is lucky to have her.

There are many students and visitors who I wish to thank for the contributions they have made to my graduate experience. I learned a great deal from the students in Professor King's research group I have had the pleasure to spend my time here with: Hiu Yung Wong, Sriram Balasubramanian, Marie-Ange Eyoum, Vidya Varadarajan, Kyoungsub Shin, Carrie Low, Blake Lin, Alvaro Padilla, Joanna Lai, Donovan Lee, Drew Carlson, Pankaj Kalra, Hei Kam, Xin Sun, Reinaldo Vega, and Rhesa Nathanael. I have enjoyed working with visitors to our group Akira Hokazono, Takuro Matsutoya, Yuri Yasuda, Taro Osabe, Koichi Fukada, and Woo Young Choi. Hideki Takeuchi was a tremendous help as staff to Professor King's group, maintaining essential processes in the lab and developing new ones. Professor Bokor's students Nathan Emley, Cheuk-Chi Lo, Yu-Chih Tseng, and Dave Carlton have been great office-mates. I wish to thank BSAC members Frank Zendejas, Michael Helmbrecht, Hyuck Choo, Will Holtz, Turi Aytur, Tomo Ishikawa, Jonathan Foster, and Justin Black for welcoming me to Berkeley when I first arrived. Additionally, I would like to thank Steve Volkman, Alejandro de la Fuente Vornbrock, Tim Bakhishev, Anand Sarwate, and Kate Jenkins for entertaining discussions and for attending to my sanity.

Finally, I wish to thank my parents for their unconditional love and support.

### Chapter 1

### Introduction

#### 1.1 Display Technologies

#### 1.1.1 Cathode Ray Tubes to Flexible Displays

Cathode ray tube displays (CRTs) were invented and made practical in the final years of the 19th century, before semiconductors, electronics, or even electrons were well understood. The operation of a magnetically guided electron beam exciting a phosphor layer was an important tool in the discovery of the subatomic nature of the electron [1]. Simple oscilloscopes were constructed with CRTs to understand the properties of the first vacuum tube electronic devices, allowing design of the first analog electronics. By the 1950s, CRT technology and vacuum tube electronics had advanced to the point where electronic displays for use in the home were practical, revolutionizing contemporary society. Today, due to the long history of the CRT and the relatively simple technology involved, costs have descended to the point where even large, high-quality displays are inexpensive.

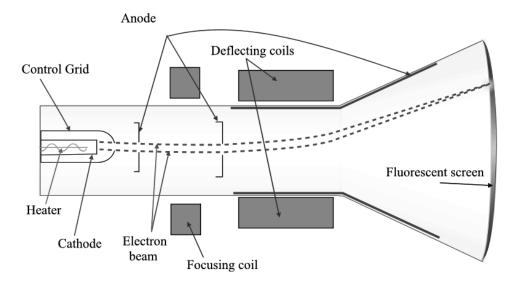

The drawback of CRT displays is their physical size. There is a minimum depth associated with the geometry of the display area, causing a CRT to have an undesirably large footprint and total volume. A schematic diagram of a CRT is seen in Fig. 1.1 [2]. The deflecting coils can only bend electrons up to a maximum angle, so the minimum tube

Figure 1.1. A cathode ray tube display [2].

depth is set by the maximum vertical or horizontal distance the electrons need travel, plus the depth of the electron gun. Since the depth is related to the display width and height, very large displays would necessarily have a massive total volume and are thus not practical. Ever since the popularization of the CRT, there has been a search for a display technology which is flat, and does not have the same constraint on total volume.

Both plasma display panels and liquid crystal displays have been investigated for over 20 years as flat replacements to a CRT. Recently they have left the research lab and entered mainstream consumer electronics, selling approximately \$7.7 billion and \$69.8 billion respectively in 2006 [3]. A number of new technologies remain over the horizon, including organic light-emitting diode displays, field-emission displays, and electrophoretic "e-paper" displays.

Looking further into the future, one can imagine a world where information display has become ubiquitous. Displays may be found not just in computer monitors and televisions, but replacing billboards, covering walls, and appearing on consumer products and even clothing. These applications require the displays to not only be flat, but extremely inexpensive, flexible, and self-contained. Flexibility is desirable not just because of the

new applications it may enable but because manufacturing on a flexible plastic substrate can be much less expensive than manufacturing on a glass substrate, thanks to roll-to-roll processing technology. A self-contained display, with no parts external to the display panel itself, is desirable to minimize costs and total unit size. For instance, even if a display can be built and integrated into a piece of clothing, it loses its usefulness if it requires bulky external control electronics.

Realizing these goals requires two directions of improvement in process technology. First, the display process must be modified such that it includes transistors capable of data processing on the panel itself. Second, the process for fabricating the display, along with the data-processing devices, must not damage the flexible substrate it is created on. This imposes a temperature limit on the device fabrication. The following section will review the requirements on the device performance, and the technologies which have been proposed to achieve that performance.

#### 1.1.2 Liquid Crystal Display Technology

Presently, the leading flat panel display technology is the active matrix liquid crystal display (AM-LCD), comprising approximately 84% of the total flat panel display market [3]. AM-LCDs are found in televisions, desktop and laptop computer displays, cell phones, handheld electronics, and many more devices. Each pixel of an AM-LCD consists of a light valve, using a liquid crystal to modulate the pixel transmittance; a color filter, to select the pixel color; and a thin film transistor circuit, to apply the correct electric field to the liquid crystal.

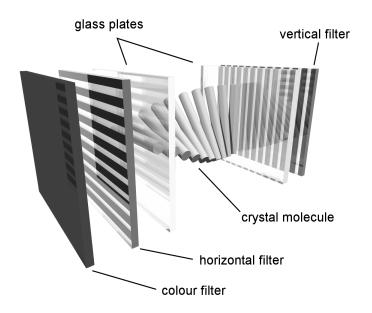

A cross-section of a liquid crystal light valve is shown in Fig. 1.2 [4]. The liquid-crystal layer and two orthogonal polarizing filters transmit or block light depending on the potential applied to electrodes in front of and behind the liquid crystal. With no potential applied, the liquid crystal naturally twists, acting as a waveguide for the light and allowing it to pass through both polarizers. Application of a vertical electric field through the liquid crystal causes it to untwist, stopping light from passing through both filters. In front of the liquid

Figure 1.2. A liquid crystal light modulator [4].

crystal sits a color filter, allowing only one color of light to be transmitted by each pixel. Formation of three differently colored sub-pixels allows three colors of light to be modulated independently.

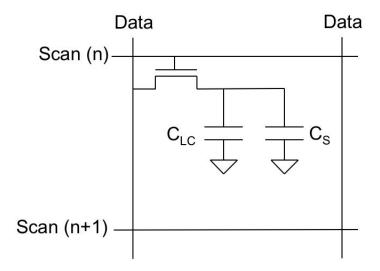

The AM-LCD pixel is shown in Fig. 1.3 from an electrical circuit point of view. Metal lines for each row and column are drawn along the display, with a thin-film transistor (TFT) at each intersection. Typically, the TFT gates are connected to the row lines, such that every TFT in a given row is turned on simultaneously. The column lines are connected to the TFT source, and the liquid crystal to the TFT drain, such that when the TFT is turned on, the voltage on the column line is passed to the liquid crystal capacitance. One row is enabled at a time, and data are sent to that entire row by the column lines. The row is disabled, the data on the column lines are changed, and the next row is enabled, allowing the entire display to be drawn row by row. An extra storage capacitor, C<sub>S</sub> is used to increase the pixel capacitance to reduce the voltage change due to TFT leakage during the scan time, when the other rows are sequentially enabled. Without the TFT, it would be impossible to fabricate a large high-contrast display while still controlling the display as a matrix [5].

Figure 1.3. Circuit schematic of an LCD active matrix backplane.

Performance requirements for the active-matrix devices in each pixel are very different from the requirements on the data processing devices we hope to add. Active-matrix devices act as pass transistors, may be only of one type (NMOS or PMOS), and have relatively low performance requirements, as the display refresh rate is slow on an electrical time scale. In contrast, data processing applications require complementary devices with fast settling time, to accomplish low-power logical operations at the high data rate coming into the panel. Current AM-LCD panels have highly optimized and well-understood pixel transistors; however, much higher performing devices need to be engineered in order to add logical functionality to the panel.

#### 1.1.3 Thin-Film Transistor Performance Requirements

In order to estimate the relative transistor performance requirements, approximate values of the required mobility can be found for the two types of device, assuming a display format and drive voltage. A color VGA display has 1024 columns  $\times$  3 colors  $\times$  768 rows, or 2,359,296 total pixels. At a 60 Hz refresh rate, the time to refresh a full frame is  $\frac{1}{60}$  seconds, or 16.7 ms, and the time to refresh a single line is  $\frac{1}{60} \times \frac{1}{768}$  seconds, or 21.7  $\mu$ s.

Pixel access TFTs are required to settle to their final voltage in the time available for refreshing one line of the display,  $21.7 \,\mu s$ . A rough approximation of the settling time is simply the time constant of the RC circuit formed by the liquid crystal capacitance and the TFT, used as a pass transistor. The time constant

$$T_{\rm RC} = R_{\rm pass} \cdot (C_{\rm LC} + C_{\rm S}), \tag{1.1}$$

with

$$R_{\text{pass}} = \frac{1}{\mu C_{\text{ox}} \frac{W}{L} (V_{\text{GS}} - V_{\text{T}})}$$

$$\tag{1.2}$$

[6]. Using typical values for liquid crystal capacitance

$$C_{LC} + C_{S} = 5 \,\mathrm{pF}$$

and for transistor and drive parameters

$$t_{ox} = 50 \,\mathrm{nm}$$

$V_{\mathrm{T}} = 1 \,\mathrm{V}$   $V_{\mathrm{GS}} = 5 \,\mathrm{V}$

we find

$$\mu \frac{W}{L} = 0.83 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}.\tag{1.3}$$

To get an estimate of the required clock rate for the logic devices, we assume that they are being used in a shift register which has to store an entire frame of data during the time the previous frame of data is sent to the display. Thus, they must be able to shift 2,359,396 times in 16.7 ms, or with a total clock period of 7 ns. The rising and falling edge times should be less than half the clock period, or 3.5 ns. An estimate of the propagation time of a logic gate is

$$T_{\rm P} = 0.5 \frac{C_{\rm L} V_{\rm DD}}{I_{\rm D}} \tag{1.4}$$

[6]. Assuming the n-type to p-type mobility ratio is 3 and the devices are appropriately sized:

$$\frac{\mu_{\rm N}}{\mu_{\rm P}} = \frac{W_{\rm P}}{W_{\rm N}} = 3,$$

(1.5)

the load capacitance is

$$C_{\rm L} = 4W_{\rm N}LC_{\rm ox}.\tag{1.6}$$

So, the propagation time is

$$T_{\rm P} = 0.5 \frac{4L^2}{\mu_{\rm N}(V_{\rm GS} - V_{\rm T} - \frac{V_{\rm DS}}{2})}.$$

(1.7)

Plugging in typical values

$$L = 3 \,\mu\text{m}$$

$V_{\text{DD}} = 5 \,\text{V}$   $V_{\text{T}} = 1 \,\text{V}$

we can find a value for mobility

$$\mu_{\rm N} = 34.2 \, \frac{\rm cm^2}{\rm V \cdot s}.\tag{1.8}$$

From these estimates, we learn that in order to design conservatively, our pixel TFT should have a mobility on the order of  $0.5 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}$  -  $1 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}$  with a  $\frac{W}{L}$  ratio considerably greater than 1, and the logic TFT should have a mobility on the order of  $50 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}$  -  $100 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}$ . It is therefore clear that a technology designed to be optimal for the pixel TFTs will not necessarily be usable for the logic TFTs.

#### 1.2 Thin-Film Transistor Fabrication Technologies

Conventional silicon MOSFETs are made from single crystal silicon, engineered to have high purity and very few defects, thereby attaining very high performance. Single crystal devices would easily satisfy the performance requirements for all devices on a AM-LCD panel; however, it is not practical to use them on a display panel. It is not economical to bond a silicon wafer to a panel and etch away the unused areas due to the low density of devices compared with more conventional uses of the silicon wafer. Fabrication of devices at high density on a wafer and transferring them individually to the display panel is also too expensive, due to the number of devices which would need to be placed with high precision over the large panel. The most practical method to build semiconductor devices over the entire area of the panel is to use thin-film deposition methods to coat the panel and then etch away the unused areas. There is no known method to form a thin-film semiconductor on an amorphous substrate with performance comparable to single-crystal material; however, performance can be made acceptable.

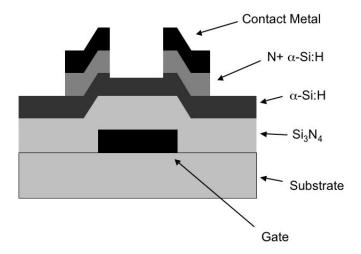

Figure 1.4. Cross-section of a bottom-gated  $\alpha$ -Si:H thin-film transistor.

Many different thin film materials systems have been investigated for use in a display backplane. The first attempts commonly used cadmium selenide, due to its ease in forming a good quality semiconducting thin film through vacuum evaporation. Presently, hydrogenated amorphous silicon is used in the vast majority of LCD backplanes, while polycrystalline silicon is used in a smaller number.

#### 1.2.1 Amorphous Silicon

Amorphous silicon has no long-range order, causing many silicon atoms to not be able to form the desired four bonds. When a silicon atom is missing a bond, it appears electrically in the film as a localized trap state, located between the conduction band edge and about 0.2 eV below [7]. Amorphous silicon has a very large number of these defects, and hence is a very poor semiconductor. The electrical effect of these defects can be reduced somewhat by the inclusion of large amounts of hydrogen in the silicon film, typically on the order of 10-15 atomic percent.

The process used to fabricate hydrogenated amorphous silicon ( $\alpha$ -Si:H) TFTs for LCD backplanes uses a bottom-gated structure with a metal gate, a silicon nitride gate dielectric,

and an  $\alpha$ -Si:H semiconducting layer, as shown in Fig. 1.4. Deposition of the gate dielectric and semiconducting layers is performed by plasma-enhanced chemical vapor deposition (PECVD), typically at 350 °C during dielectric deposition and 250 °C during semiconductor deposition. A higher temperature is desirable for the dielectric deposition in order to encourage growth of stoichiometric Si<sub>3</sub>N<sub>4</sub>, while a lower temperature is desirable during  $\alpha$ -Si:H deposition to control diffusion of hydrogen out of the film as it is forming.

Carrier transport through an amorphous silicon layer is highly inefficient. The primary mode of transport is thermally-assisted hopping between localized trap states [7], leading to a very low mobility as compared with crystalline silicon, typically on the order of  $1 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}$  for well-engineered devices [8]. Performance at this level is acceptable for pixel TFTs, and these devices have a number of other desirable properties. When properly hydrogenated, defect density is low, leading to good turn-on characteristics, with subthreshold slope under 1 V/decade and threshold voltage under 1 V. Good quality large area PECVD tools have been developed to deposit extremely uniform  $\alpha$ -Si:H and Si<sub>3</sub>N<sub>4</sub> films on the glass substrate, leading to extremely uniform devices [9].

The most significant shortcoming of  $\alpha$ -Si:H TFTs, aside from low mobility, is their reliability. The randomly arranged silicon network has many weak Si-Si bonds, which are easly broken under the influence of vertical field. Charge can also easily be trapped at the poor quality  $\alpha$ -Si:H-Si<sub>3</sub>N<sub>4</sub> interface. Both of these lead to shifts in the device threshold voltage over time [10]. Hole mobility in  $\alpha$ -Si:H devices is also extremely low, causing PMOS devices to be of too poor quality to be useful and preventing fabrication of CMOS circuits. Overall, the quality of NMOS  $\alpha$ -Si:H devices is good enough that they have become ubiquitous as pixel TFTs in AM-LCD displays; however, they are not usable as logic devices, so another solution must be found.

#### 1.2.2 Polycrystalline Silicon

Polycrystalline silicon (poly-Si) is a form of silicon which consists of many small crystalline grains oriented randomly with respect to one another. Within each grain, the

crystalline quality can be high, possessing only a small number of defects. However, there are large concentrations of defects at the boundaries between grains. Depending on the fabrication process, the size of the crystalline grains can be as small as tens of nanometers or as large as several micrometers. Large grains are preferable, as the average trap density is low and the distance between high trap density regions is high. If the grains can be made larger than the transistor channel length, device performance can start to approach that of single crystal silicon.

There are many different methods to fabricate poly-Si. A silicon thin film can be deposited in a polycrystalline state, or it can be deposited as an amorphous film and further treated to transform it into polycrystalline material. The latter tends to be preferable despite the extra process complexity, as larger grain size is typically achieved. Silicon deposition can be performed by low-pressure chemical vapor deposition (LPCVD), PECVD, or sputter deposition, each process operating in a different temperature range. LPCVD is performed in the range of 530 °C - 620 °C, with temperatures above approximately 580 °C producing polycrystalline films, and lower temperature depositions producing amorphous films. PECVD processes are typically run between 250 °C and 400 °C, though they will still function at considerably lower temperatures. Sputter deposition can be run as low as room temperature or as high as is safe for the tool. Quality of sputter deposited silicon films varies with temperature much less than LPCVD or PECVD, as it is a physical deposition process rather than a chemical one. Materials quality only begins to change once the deposition temperature approaches its melting point.

Once a silicon thin film has been deposited, crystallization can be performed either by annealing in a furnace above 600 °C or by laser annealing. Laser annealing can produce large-grained polycrystalline silicon and is compatible with low-temperature substrates, despite raising the temperature of silicon thin film above its melting point of 1414 °C. Excimer laser pulses are extremely short, approximately 30 ns, and the entire heating and cooling cycle associated with one pulse takes under 1 ms [11]. If an appropriate barrier layer

Figure 1.5. Cross-section of a top-gated polycrystalline silicon thin-film transistor.

is used below the silicon film, the molten silicon will cool back to room temperature before enough heat can diffuse into the substrate layer to damage it.

Poly-Si mobility largely depends on the grain size and therefore on the method used for crystallization. Silicon deposited by LPCVD in polycrystalline form can have electron mobility as high as about  $10 \frac{\text{cm}^2}{\text{V·s}}$ , and furnace crystallized poly-Si typically has electron mobility of about  $30 \frac{\text{cm}^2}{\text{V·s}}$  [12]. Excimer laser crystallized silicon can have much larger grains than furnace crystallized silicon and can typically achieve electron mobility as high as  $100 - 200 \frac{\text{cm}^2}{\text{V·s}}$  [13]. Using specialized laser annealing techniques such as sequential lateral solidification (SLS) or grain engineering, electron mobility can be raised even as high as  $300 - 500 \frac{\text{cm}^2}{\text{V·s}}$  [14, 15], approaching that of single-crystal silicon. Electron mobilities this high, combined with a comparable hole mobility in polysilicon, allows fabrication of CMOS circuits capable of high-speed data processing.

After a polycrystalline silicon thin film has been formed, it is typically fabricated into top-gate planar transistors. These devices have a process flow very similar to SOI MOSFETs, and can approach their performance if the silicon thin film is of very high quality. The cross section of a typical poly-Si TFT is shown in Fig. 1.5.

#### 1.3 Challenges for Poly-Si TFTs on Plastic Substrates

As described in section 1.1.1, in order to achieve our ultimate goal of ubiquitous displays, we need high-performance data processing devices produced on inexpensive flexible substrates. The initial goal of demonstrating high-performance devices on a flexible substrate has been accomplished by several research groups [16, 17, 18]. However, challenges still exist that prevent their widespread adoption.

#### 1.3.1 Process Thermal Budget Limitations

The initial challenge that needs to be addressed when designing a thin film transistor process is the thermal budget of the substrate material. Modern AM-LCD panels use a glass substrate that has a strain point of  $666\,^{\circ}$ C [19], and thus can be safely processed up to approximately  $600\,^{\circ}$ C. This limit is entirely compatible with  $\alpha$ -Si:H TFTs, which reach a maximum temperature of  $450\,^{\circ}$ C during processing. Higher temperature annealing would be detrimental to device performance, as hydrogen would be driven from the layers, depassivating defects.

Typical processes for poly-Si deposition and crystallization all take place under or at 600 °C, so that they are compatible with glass. Gate oxide formation suffers for the temperature limitation, however. The highest quality Si-SiO<sub>2</sub> interface is formed by high-temperature oxidation, the process used in conventional MOSFETs. Thermal growth of SiO<sub>2</sub> is very slow at our limit of 600 °C, so a deposition process must be used, typically LPCVD or PECVD. Device performance suffers as a result of the poorer interface, however, good quality devices can be fabricated.

Moving from a glass substrate to a flexible one lowers the available thermal budget considerably. Many high-temperature flexible plastics have been engineered, but their cost increases commensurately with their temperature compatibility. For instance, polyimide materials, which have a peak processing temperature in the range of  $250\,^{\circ}\text{C}$  -  $400\,^{\circ}\text{C}$ , have a typical bulk cost of  $150\,\frac{\dot{\text{C}}}{\text{in}^3}$ . This is compared with polyethersulfone (PES), which costs

approximately  $20 \frac{\dot{\zeta}}{\text{in}^3}$ , but can only safely reach  $200 \,^{\circ}\text{C}$ . At the low end of the cost spectrum is polyethylene terepthalate (PET), costing only  $4 \frac{\dot{\zeta}}{\text{in}^3}$  [20], but with maximum processing temperature limited to only  $150 \,^{\circ}\text{C}$ . PET is widely used in consumer products, in such applications as soda bottles, textiles (known under the trade name Dacron), and as a thin-film coating (known as Mylar). Its low cost enables it to achieve the kind of ubiquity we are seeking for flexible electronics, so we must develop a device process which is compatible with its thermal limit.

Adapting a process to a lower thermal limit can be a matter of running existing processes at a lower temperature and learning to compensate for the poor quality materials which result, or it can require development of entirely new processes. For instance, PECVD processes will typically deposit material when run anywhere between room temperature and  $400\,^{\circ}$ C. It is therefore possible that adapting an  $\alpha$ -Si:H process to a plastic substrate simply consists of lowering the temperature of the reactor and evaluating whether materials performance is sufficient for the application. This work was reported by Sazonov et al. [21], where it was established that functional devices could be fabricated at temperatures as low as 75 °C with only moderate loss in performance compared with conventionally processed  $\alpha$ -Si:H TFTs.

Many of the fabrication steps necessary for polycrystalline silicon TFTs can be adapted with little modification from a higher-temperature process. Examining the process options for forming polysilicon described in section 1.2.2, the techniques available below 150 °C include sputter deposition, adaptation of a PECVD process to low temperatures, and laser crystallization. Use of a PECVD process in laser crystallized devices has been demonstrated [17], but adds unnecessary complexity. PECVD silicon films contain large quantities of hydrogen, which will rapidly diffuse out at high temperatures. Laser processing causes the silicon film to rise in temperature so rapidly that severe damage is done as the hydrogen evolves from the film. If a PECVD silicon film is to be used in a laser crystallized polysilicon process, the hydrogen must first be carefully removed through a very low energy laser

treatment [22]. Sputtered silicon contains no hydrogen, thereby avoiding an extra processing step.

Laser crystallized sputtered silicon is usable on a PET substrate without substantial modification, but not all process steps in a polysilicon TFT are so easily adaptable. The gate oxide formation process for conventional MOSFETs was not usable for glass-compatible TFTs and will need to be further modified for plastic compatible TFTs. High-density PECVD has been used to deposit good quality gate oxide at 150 °C [18]. However, high-density PECVD is not easily adaptable to large area substrates, the largest reported deposition system with good uniformity is 30 cm diameter [23]. Additionally, glass-compatible polysilicon TFTs typically use a plasma hydrogenation process to passivate defects after the crystallization process is completed, improving performance in a similar way to the hydrogenation in  $\alpha$ -Si:H. This process requires annealing at 350 °C [24], and is not adaptable to plastic-compatible processes.

#### 1.3.2 Device Uniformity

The main performance drawback to the use of polycrystalline silicon (poly-Si), and in particular laser crystallized poly-Si, is the large variation between devices. Whereas amorphous silicon has a uniformly high density of defects throughout, poly-Si has both low defect concentration regions (grains) and high defect concentration regions (grain boundaries). Good quality material will have large grains; only a small number of grain boundaries will appear within each device. Fluctuations in the exact number and location of grain boundaries in a given device will cause large variations in the total number of defects within the device, leading to large performance variations between devices.

Crystallization using a laser adds an additional source of performance variation on top of the variation inherent to polysilicon. Laser annealing of silicon is typically done with a pulsed excimer laser, due to its high power density. Each pulse is only large enough to cover a small fraction of the total area of the panel, hence the laser beam must be scanned

Figure 1.6. Measured polysilicon grain size vs. excimer laser annealing energy [25].

across the panel to anneal the entire film. There are fluctuations in the energy delivered in each pulse, leading to variations in the grain size of the crystallized film.

The problem of pulse energy variation is enhanced by the silicon crystal growth mechanisms during the laser pulse. Looking at Fig. 1.6 [25], it is seen that the peak of grain size vs. laser annealing fluence is steep and narrow. The laser pulse is absorbed into the surface of the silicon film, melting the silicon to a depth determined by the fluence of the pulse. As the molten silicon cools, grains nucleate from the unmelted layer below, yielding a grain size roughly corresponding to the melt depth. The peak grain size arises when nearly all of the film is melted and only a few nucleation sites remain. Once the film is completely melted and no nucleation sites remain, the molten silicon is able to supercool, leading to spontaneous nucleation throughout the film and growth of very small grains. Therefore, when the process is designed to produce films with the largest possible grain size, fluctuations in the laser fluence will lead to the highest degree of grain size nonuniformity [25].

In a higher-temperature polysilicon TFT process, device uniformity can be addressed through the use of hydrogen passivation. Passivation reduces the electrical effect of crystalline defects by completing broken silicon bonds. This has the dual effect of improving performance and uniformity, as defects are responsible for degrading both. It would be highly desirable if a suitable plastic-compatible replacement for hydrogen passivation could be found.

#### 1.3.3 Device Reliability

Good quality high-temperature processed poly-Si often has poor reliability, exhibiting shifts in threshold voltage over time. After fabrication, broken Si bonds are passivated with hydrogen, forming Si-H bonds. These bonds are weak compared with Si-Si bonds, however. When a hydrogenated thin film silicon device is subjected to heat or to electrical stress, Si-H bonds are broken and the defect is depassivated. Devices degrade in this way slowly over time to their original, unpassivated, condition. Performance shift over time is highly undesirable for devices to be used in digital circuits.

Hydrogen passivation is not usable in plastic-compatible devices due to temperature incompatibility, but finding a replacement is essential to the feasibility of flexible electronics. If a passivation technique could be found which has inherently better reliability than hydrogen passivation, it would be very important for the future of plastic-compatible devices.

#### 1.4 Thesis Organization

This dissertation addresses each of these remaining challenges to plastic compatible poly-Si thin-film transistor formation. The focus of the research has been on a passivation technique which is both compatible with low temperature flexible substrates and has better reliability than hydrogen passivation. This is accomplished by implanting a passivating species into the  $\alpha$ -Si thin film prior to excimer laser annealing. During laser processing this

impurity reacts with silicon defects, accomplishing the desired effect of electrical passivation. This technique has been demonstrated with N, O, and F impurities, each of which forms a stronger bond to Si than H, thereby improving reliability. The theory, experimental design, and measured data for this process is detailed in Chapter 2.

In order to demonstrate the effectiveness of this passivation technique for ultra low temperature devices, a baseline plastic-compatible process needed to be established. Chapter 3 details the fabrication process and development done in order to realize plastic-compatible devices. A reactively sputtered SiO<sub>2</sub> process was used to form a gate dielectric in a process compatible with large-area substrates. The Si thin film was first treated with O<sub>2</sub> under UV light emission to achieve an Si–SiO<sub>2</sub> interface with a minimal number of defects. After SiO<sub>2</sub> film deposition, a laser annealing step was used to heat the Si–SiO<sub>2</sub> interface, further removing defects. Efficacy of the implant passivation technique was measured in devices fabricated with this process.

Chapter 4 demonstrates laser annealing with a copper vapor laser, as a possible alternative to excimer laser annealing. Copper vapor lasers are widely used in laser machining and have better pulse-pulse nonuniformity and lower cost-of-ownership than excimer lasers. Here the feasibility of their use for formation of polycrystalline silicon is established, and performance and uniformity characteristics are measured.

Chapter 5 summarizes the contributions of this work and provides suggestions for further studies in plastic-compatible device fabrication and defect passivation.

#### 1.5 References

- [1] George E. Smith. J. J. Thompson and the electron, 1897-1899. In Jed Z. Buchwald and Andrew Warwick, editors, *Histories of the Electron*. MIT Press, 2001.

- [2] Theresa Knott. Cathode\_ray\_Tube.PNG [online, cited April 28, 2007]. Available from: http://en.wikipedia.org/wiki/Image:Cathode\_ray\_Tube.PNG.

- [3] DisplaySearch. Reported in Flat panel display growth predicted to slow. *Reuters*, January 5 2007.

- [4] Marvin Raaijmakers and Ed Sanders. LCD\_subpixel\_(en).png [online, cited February 24, 2007]. Available from: http://en.wikipedia.org/wiki/Image:LCD\_subpixel\_% 28en%29.png.

- [5] Paul M. Alt and Peter Pleshko. Scanning limitations of liquid-crystal displays. *IEEE Transactions on Electron Devices*, 21(2):146–155, 1973.

- [6] Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic. Digital Integrated Circuits, second edition. Prentice Hall, 2003.

- [7] P. G. Le Comber and W. E. Spear. Electronic transport in amorphous silicon films. *Physics Review Letters*, 25(8):509–511, 1970.

- [8] T. Tiedje, C. R. Wronski, B. Abeles, and J. M. Cebulka. Electron transport in hydrogenated amorphous silicon: Drift mobility and junction capacitance. Solar Cells, 2(3):301–318, 1980.

- [9] R. Sobbia, L. Sansonnens, and J. Bondkowski. Uniformity study in large-area showerhead reactors. *Journal of Vacuum Science and Technology A*, 23(4):927–932, 2005.

- [10] Yoshiyuki Kaneko, Akira Sasano, and Toshihisa Tsukada. Characterization of instability in amorphous silicon thin-film transistors. *Journal of Applied Physics*, 69(10):7301, 1991.

- [11] P. M. Smith, P. G. Carey, and T. W. Sigmon. Excimer laser crystallization and doping of silicon films on plastic substrates on plastic substrates. Applied Physics Letters, 70(3):342–344, January 1997.

- [12] Vivek Subramanian, Paul Dankoski, Levent Degertekin, Butrus T. Khuri-Yakub, and Krishna C. Saraswat. Controlled two-step solid-phase crystallization for high-performance polysilicon TFT's. IEEE Electron Device Letters, 18(8):378–381, 1997.

- [13] T. Sameshima, S. Usui, and M. Sekiya. XeCl excimer laser annealing used in the fabrication of poly-Si TFT's. *IEEE Electron Device Letters*, EDL-7(5):276–278, 1986.

- [14] M. A. Crowder, P. G. Carey, P. M. Smith, Robert S. Sposili, Hans S. Cho, and James S. Im. Low-temperature single-crystal Si TFT's fabricated on Si films processed via sequential lateral solidification. *IEEE Electron Device Letters*, 19(8):306–308, 1998.

- [15] G. K. Giust, T. W. Sigmon, J. B. Boyce, and J. Ho. High-performance laser-processed polysilicon thin-film transistors. *IEEE Electron Device Letters*, 20(2):77–79, 1999.

- [16] Paul G. Carey, Patrick M. Smith, Steven D. Theiss, and Paul Wickboldt. Polysilicon thin film transistors fabricated on low temperature plastic substrates. *Journal of Vacuum Science and Technology A*, 17:1946–1949, Jul./Aug. 1999.

- [17] Sang-Myeon Han, Min-Cheol Lee, Moon-Young Shin, Joong-Hyun Park, and Min-Koo Han. Poly-Si TFT fabricated at 150°C using ICP-CVD and excimer laser annealing. Proceedings of the IEEE, 93(7):1297–1305, 2005.

- [18] Yeh-Jiun Tung, Paul G. Carey, Patrick M. Smith, Steven D. Theiss, Xiaofan Meng, Robert Weiss, Gary A. Davis, Verle Aebi, and Tsu-Jae King. An ultra low-temperature fabricated Poly-Si TFT with stacked composite ECR-PECVD gate oxide. In *Technical Digest of SID 1998*, page 887, 1998.

- [19] Corning EAGLE XG glass substrates [online, cited April 28]. Available from: http://www.corning.com/displaytechnologies/ww/en/products\_applications/ eaglexg/.

- [20] Plastics Technology Online [online, cited February 2007]. Available from: http://www.ptonline.com/articles/200702rprice.html.

- [21] Andrei Sazonov, Denis Striakhilev, Czang-Ho Lee, and Arokia Nathan. Low-temperature materials and thin film transistors for flexible electronics. *Proceedings of the IEEE*, 93(8):1420–1428, 2005.

- [22] P. Mei, J. B. Boyce, M. Hack, R. A. Lujan, R. I. Johnson, G. B. Anderson, D. K. Fork, and S. E. Ready. Laser dehydrogenation/crystallization of plasma-enhanced chemical vapor deposited amorphous silicon for hybrid thin film transistors. *Applied Physics Letters*, 64(9):1132–1134, 1994.

- [23] Wataru Miyazawa, Shigekazu Tada, Kohichi Ito, Hironori Saito, Shoji Den, Yuzo Hayashi, Yukio Okamoto, and Yuichi Sakamoto. A large-area ECR processing plasma. Plasma Sources Sciences and Technology, 5:265–267, 1996.

- [24] N. H. Nickel, N. M. Johnson, and W. B. Jackson. Hydrogen passivation of grain boundary defects in polycrystalline silicon thin films silicon thin films. Applied Physics Letters, 62(25):3285–3287, June 1993.

- [25] James S. Im, H. J. Kim, and Michael O. Thompson. Phase transformation mechanisms involved in excimer laser crystallization of amorphous silicon films. *Applied Physics Letters*, 63:1969–1971, October 1993.

# Chapter 2

# Thin Film Transistor Passivation by Ion Implantation and Excimer Laser Annealing

# 2.1 Introduction

Formation of a silicon film with a minimum of defect states is essential to fabrication of high-performance polycrystalline silicon thin-film transistors. Defects arising from broken bonds at grain boundaries and from lattice imperfections within silicon grains lead to traps within the silicon bandgap, both at deep and shallow levels [1]. Trap states cause an increase in the device threshold voltage, subthreshold slope, and leakage current, and a reduction in mobility [2, 3, 4]. Additionally, nonuniformities in laser processing lead to nonuniformities in trap formation, and thus to an increase in the variation between devices [5].

Two approaches are taken to reduce the number of trap states in the polycrystalline silicon film. The silicon film is first annealed at high temperature, either in a furnace or with a laser, in order to cause large, high-quality grains to form. Extensive studies have been performed to find processes which grow the largest possible grains, and therefore have

the smallest defect density [6, 7]. Once the silicon film has been formed, a treatment is performed in order to render as many as possible of the defect states electrically inactive, called defect passivation. Defects are predominantly silicon atoms with one or more incomplete bonds, and thus can be passivated by adding atoms to complete the broken bonds. After a passivation treatment, lattice defects are electrically neutral and do not affect the electrostatics of the device.

# 2.2 Thin Film Transistor Passivation Techniques

There are several different techniques which have been attempted for defect passivation, but the one which is by far the most common is hydrogen annealing. Furnace annealing in an atmosphere of hydrogen diluted in an inert gas is a common step in the fabrication of conventional MOSFETs, used to reduce defects at  $SiO_2$ –Si and metal—Si interfaces [8]. The density of defects in a polycrystalline silicon thin film is very high compared with that at an interface in a conventional device, so the process has been adapted to use an anneal in hydrogen plasma to increase the rate of defect passivation.

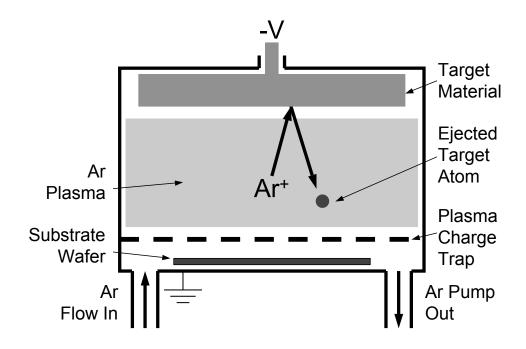

A hydrogen plasma annealing process is performed in a plasma reactor similar to one which could be used for plasma enhanced chemical vapor deposition (PECVD) or plasma etching. A schematic drawing is shown in Fig. 2.1 [9]. The wafer is loaded on a heated chuck and the chamber is filled with hydrogen gas, which is then ionized with RF energy. Ionized hydrogen diffuses into the silicon film and reacts with dangling bonds, accomplishing the desired passivation. The efficacy of the hydrogen plasma annealing process depends on the temperature and time of passivation, as well as the gas mixture and type of plasma reactor used, and has undergone extensive characterization with regard to each of these variables [10, 11, 12, 13, 14].

Data for performance of a hydrogen passivation process vs. processing time and processing temperature are shown in Fig. 2.2 [11] and Fig. 2.3 [10], respectively. Fig. 2.2 shows the evolution of threshold voltage and mobility vs. time, and Fig. 2.3 shows the

Figure 2.1. Schematic drawing of a parallel-plate plasma reactor [9].

reduction of unpaired spins in Si vs. temperature as measured by electron spin resonance. From these plots we can conclude that hydrogen plasma annealing is very effective for passivation of defects but only when the anneal is performed for many hours at temperatures near 350 °C. This is acceptable for a glass-compatible thin-film transistor process; however, is not usable in a plastic compatible process. Even high-temperature plastics such as polyimide will undergo significant shrinkage after many hours at elevated temperature, and low-cost plastics will burn at temperatures well below what is necessary for hydrogenation.

An initial attempt to lower the time and temperature necessary for adequate passivation was undergone by Sameshima [15], using  $H_2O$  vapor annealing. The anneals were conducted at very high pressure, up to  $4\times10^6$  Pa, in order to speed diffusion of reactive species into the silicon film. The use of  $H_2O$  additionally enhances passivation by introducing both reactive oxygen atoms and hydrogen atoms to terminate broken silicon bonds. Measured data from Si films treated with the high-pressure  $H_2O$  anneal at different temperatures is shown in Fig. 2.4. Defect reduction is measured as the ratio of photocurrent to dark current, as defects prevent low off-current or high on-current. Improvement by five orders of magnitude of on/off ratio is seen after annealing for 1 hour at 190 °C, at approximately  $1.5\times10^6$  Pa. However, this process is still impractical for plastic compatible TFT fabrication. A low-cost

Figure 2.2. Threshold voltage and field-effect mobility as functions of hydrogen plasma annealing time [11].

Figure 2.3. Unpaired spins in polycrystalline silicon after hydrogen plasma annealing at different temperatures [10].

Figure 2.4. Dark conductivity and photoconductivity in polycrystalline silicon films after high-pressure  $\rm H_2O$  treatment [15].

plastic substrate will likely undergo severe damage if subjected to the thermal budget and high pressure necessary for this anneal, even though it is considerably lower thermal budget than a conventional plasma hydrogenation.

There has recently been research into defect passivation using fluorine [16, 17, 18, 19]. Fluorine is introduced into silicon either through ion-implantation or by solid-source diffusion from a fluorinated silicon dioxide layer. It cannot be diffused into a silicon film from an ambient gas due to its volatility. The processes used to introduce and activate fluorine in silicon require a high temperature anneal to activate or diffuse the fluorine impurities; passivation with fluorine in a plastic-compatible process has not yet been shown. Fig 2.5 [19] compares device data from thin-film transistors passivated with fluorine and with no passivation. The devices were fabricated in a glass-compatible process, using a long 600 °C anneal to crystallize the silicon and activate the implanted fluorine. Improvement in mobility and subthreshold slope of a factor of 2 is seen in the fluorine implanted devices as compared with the unpassivated devices.

Finally, the use of nitrogen as a passivating species has also been investigated. Performance gains have been seen in passivation processes using a  $NH_3$ ,  $N_2O$ , or  $N_2$  plasma,

Figure 2.5. Transfer curves and extracted parameters of polysilicon TFTs with and without fluorine passivation [19].

similar to hydrogen plasma annealing. These processes are typically conducted at 250 °C [20] or 300 °C [21], and show comparable performance to hydrogen annealing, in some cases with improved reliability [22]. Implanting nitrogen after furnace crystallization and annealing at 850 °C has also been shown to achieve modest improvements in performance and reliability [23]. These processes are not plastic-compatible, nor in the latter case glass-compatible, but they show feasibility of passivation with nitrogen, and its compatibility in a high-performance polycrystalline silicon TFT.

# 2.3 Motivation

In order to achieve high performance with good uniformity in a plastic compatible polycrystalline silicon thin film transistor process, a plastic compatible passivation technique must be developed. The difficulty lies in the fact that forming bonds between silicon and a passivating element requires more thermal energy than an inexpensive flexible substrate can withstand. However, silicon crystallization and activation of dopants in the source and

drain regions in a plastic compatible process face the same problem, for which a solution has already been found. Both of these steps are performed using an excimer laser to locally heat a silicon thin-film without damaging the substrate below. If these laser processing techniques can be adapted to activate a passivating impurity, a plastic compatible passivation technique can be found.

Laser processing can take a lot of time, however. Fully melting a silicon thin film with an excimer laser takes an energy density of approximately  $400 \,\mathrm{mJ/cm^2}$ , depending on the thickness and film quality of silicon used and on the wavelength and pulse width of the laser. The maximum pulse energy of a typical state of the art XeCl excimer laser is 1050 mJ, at a pulse repetition rate of 300 Hz [24]. A typical industrial laser crystallization process [25] shapes the beam into an 350  $\mu$ m by 75 cm rectangle and scans it in 17.5  $\mu$ m steps, resulting in a scan rate of 5.25 mm/s. Modern 8th generation display substrates measure 2.16 m by 2.46 m [26], and could be annealed with this process in three passes, in a total time of 23.42 minutes per panel. This is a long and costly time to spend processing each panel, so adding additional laser steps is highly undesirable. For this reason, rather than adding a step specifically for laser activation of passivating impurities, it is advantageous to attempt to combine passivation either with channel crystallization or source and drain activation. During excimer laser activation of source and drain dopants, laser light is reflected by the gate line, and the channel region under the gate is not heated. Therefore, passivation must be combined with the channel crystallization step. Laser crystallization is typically the first step performed after silicon channel film deposition, so the passivating impurities must either be added in-situ during film deposition, or in a separate step immediately after deposition.

One well-known difficulty with laser processing is its incompatibility with hydrogenated silicon [27]. The diffusivity of hydrogen in silicon at its melting point of 1414 °C is extremely high, approximately  $5 \times 10^4 \,\mu\text{m}^2/\text{s}$  [28]. Even though the Si film is only molten for about 200 ns during a crystallization pulse [29], this leads to a diffusion length of 100 nm, twice the typical film thickness used in a polycrystalline silicon thin-film transistor process. All of the

hydrogen in the silicon film is therefore able to escape during a single laser pulse. Evolution of hydrogen from silicon during laser processing is so rapid that the silicon film is irreversibly damaged [30]. Giust and Sigmon studied TFT performance from laser-annealed sputtered silicon thin films with controlled amounts of hydrogen incorporated during the sputtering process [31]. The laser process was modified to be compatible with hydrogenated silicon films, starting with low-energy pulses and ramping the energy slowly. It was found that the maximum hydrogen content devices had the worst performance, and the minimum hydrogen content devices had the best performance. The predominant effect of adding hydrogen to a silicon film before crystallization is thus seen to be damage during laser processing, rather than any passivating effects.

We seek to passivate polycrystalline silicon TFTs by introducing a passivating impurity into the silicon film prior to laser crystallization. The impurity best known to passivate silicon TFTs, hydrogen, will not work for this process, as it will diffuse out of the silicon film during laser processing, causing damage along the way. Therefore, we have attempted this technique with other elements known to passivate defects in polycrystalline silicon TFTs, namely oxygen, fluorine, and nitrogen. These elements all have a much lower diffusion coefficient in silicon than hydrogen. At the melting point of silicon, nitrogen has a diffusivity of  $1.2 \times 10^{-3} \, \mu \mathrm{m}^2/\mathrm{s}$ , and oxygen has diffusivity of  $3.6 \times 10^{-1} \, \mu \mathrm{m}^2/\mathrm{s}$  [28]. Diffusivity of fluorine in silicon has only been measured up to 700°C, but extrapolating to 1414°C for comparison yields a diffusivity of  $2.7 \,\mu\text{m}^2/\text{s}$  [32]. These are all at least 4 orders of magnitude lower than diffusivity of hydrogen in Si, leading to diffusion lengths below 1 nm. It is therefore reasonable to expect these impurities to stay in the silicon film during the laser annealing process, unlike hydrogen. Additionally, selenium has been shown to passivate surface states in metal-Si contacts, due to its ability to form a surface reconstruction on crystalline silicon with no broken bonds [33]. It is possible that similar effects will be seen on the silicon surfaces at grain boundaries, so passivation using selenium was attempted as well. For simplicity of experimentation and control over dose, the passivating impurities were introduced into the silicon film by ion implantation.

### 2.4 Process Flow

Self-aligned top-gate TFTs were fabricated on oxidized silicon wafer substrates as follows. A  $1\,\mu\mathrm{m}$  thick layer of SiO<sub>2</sub> was deposited by LPCVD onto the Si wafer, followed by a 50 nm layer of Si deposited by DC sputtering at room temperature. Ion implantation of the passivation species (Se, N, O, or F) was then performed through a 45 nm capping SiO<sub>2</sub> layer deposited at 450 °C. The implant energy was chosen so that the projected range is at the interface between the capping oxide layer and the Si layer, and the implantation dose was chosen to place a dose of  $1\times10^{14}\,\mathrm{ions/cm^2}$  into the Si film. This dose corresponds to an impurity density of  $2\times10^{19}\,\mathrm{cm^{-3}}$ , chosen to be approximately one order of magnitude higher than a typical density-of-states for fine-grain poly-Si [10], in order to encourage as complete passivation as possible.

After the capping oxide was removed in dilute HF, pulsed XeCl excimer laser annealing (three pulses at a fluence of  $275\,\mathrm{mJ/cm^2}$ ) was performed on the bare Si film, in air. This annealing fluence was chosen to be near the measured full melt threshold of  $325\,\mathrm{mJ/cm^2}$  in order to promote growth of large grains, but sufficiently below it to maintain good device to device uniformity. Following the ELA, some samples were given a  $600\,\mathrm{^\circ C}$  anneal in  $N_2$  for 12 hours. The poly-Si films were patterned and dry etched to form TFT active regions, and a  $50\,\mathrm{nm}$  gate  $\mathrm{SiO}_2$  layer was deposited by LPCVD at  $450\,\mathrm{^\circ C}$ .

The 80 nm Al gate layer was deposited by DC sputtering at 300 °C, patterned, and wet etched. SiO<sub>2</sub> gate-sidewall spacers 50 nm thick were then formed by LPCVD at 400 °C and anisotropic dry etching. Heavy n-type doping of the source and drain regions was accomplished with phosphorus ion implantation, at a dose of  $1 \times 10^{15}$  ions/cm<sup>2</sup> and energy of 34 keV. The source and drain implant was activated with a second ELA step, using three shots at  $175 \,\mathrm{mJ/cm^2}$ . This annealing fluence was the highest fluence that could be used without damaging the oxide layer covering the source and drain regions. Next, a 130 nm SiO<sub>2</sub> insulation layer was deposited by PECVD, and contact holes were patterned and dry etched. Finally, a 700 nm Al/2% Si layer was deposited by DC sputtering, patterned, and wet etched. The devices were then tested, sintered in N<sub>2</sub> for 2 hours at 350 °C, and retested.

Control devices were fabricated using the same process as described above, but without any passivation species implant. After initial testing, these devices were annealed in hydrogen plasma at 350 °C for 2 hours, in order to compare implant passivation to conventional hydrogen passivation.

# 2.5 Device Results

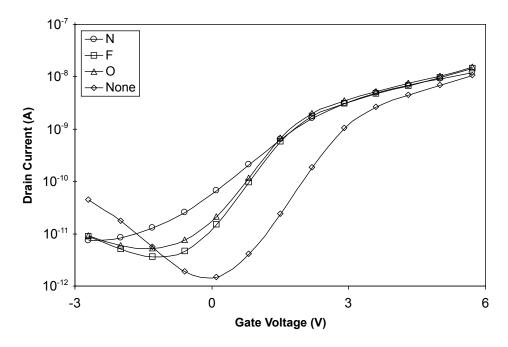

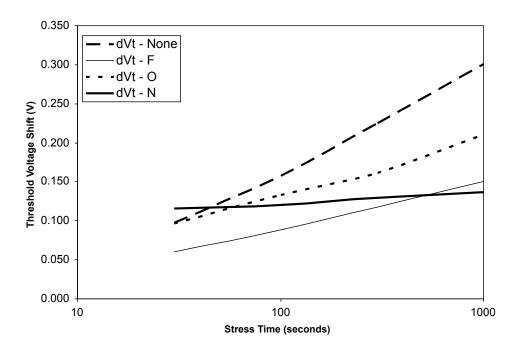

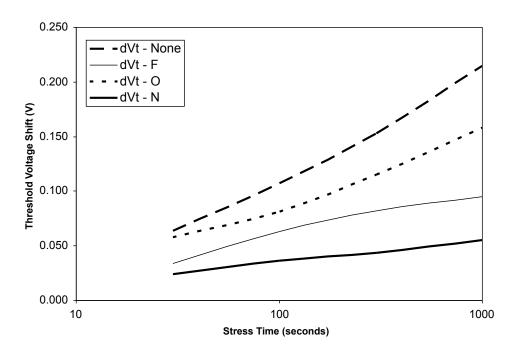

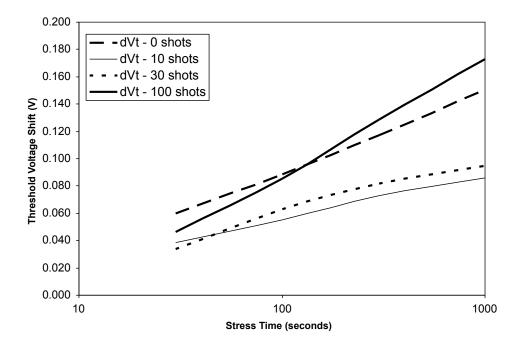

Measurements from devices measuring W/L =  $50 \,\mu\text{m}/5 \,\mu\text{m}$  are shown in the following figures.  $I_D$  vs.  $V_{GS}$  transfer characteristics were measured with  $V_{DS} = 1 \, \text{V}$ . Table 2.1 shows extracted parameters for the F, O, and N implanted devices and the control devices. Devices labelled -HT received the 12 hour 600 °C anneal, and devices labelled -LT did not. Devices labelled -Ann received 350 °C post-metallization annealing, as described in section 2.4.  $I_{max}$  and  $I_{min}$  were measured as the maximum and minimum  $I_{DS}$  with  $V_{DS} = 1 \, \text{V}$  and  $-15 \, \text{V} \leq V_{GS} \leq 15 \, \text{V}$ .  $\mu_{eff}$  was measured as the maximum value of  $\frac{g_m^2}{2I_D C_{ox} \frac{W}{L}}$  with  $V_{DS} = 5 \, \text{V}$  and  $-15 \, \text{V} \leq V_{GS} \leq 15 \, \text{V}$ . Threshold voltage  $V_T$  was extracted as the voltage  $V_{GS}$  for which  $I_{DS} = 20 \, \text{nA}/\mu\text{m}$  of device width, with  $V_{DS} = 1 \, \text{V}$ . The subthreshold slope was computed from the peak value of the slope of log  $I_{DS}$  with  $V_{DS} = 1 \, \text{V}$ .