## A Hierarchical Coordination Language for Reliable Real-Time Tasks

Arkadeb Ghosal

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-10 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-10.html

January 31, 2008

Copyright © 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### A Hierarchical Coordination Language for Reliable Real-Time Tasks

by

Arkadeb Ghosal

B.Tech. (Indian Institute of Technology, Kharagpur) 2001M.S. (University of California, Berkeley) 2004

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

### GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Alberto Sangiovanni-Vincentelli, Chair Professor Thomas A. Henzinger Professor Edward A. Lee Professor J. Karl Hedrick

Spring 2008

The dissertation of Arkadeb Ghosal is approved:

Professor Alberto Sangiovanni-Vincentelli, Chair

Professor Thomas A. Henzinger

Professor Edward A. Lee

Professor J. Karl Hedrick

University of California, Berkeley

Spring 2008

Date

Date

Date

Date

### A Hierarchical Coordination Language for Reliable Real-Time Tasks

Copyright  $\bigodot$  2008

by

Arkadeb Ghosal

#### Abstract

A Hierarchical Coordination Language for Reliable Real-Time Tasks

by

Arkadeb Ghosal

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley

Professor Alberto Sangiovanni-Vincentelli, Chair

Complex requirements, time-to-market pressure and regulatory constraints have made the designing of embedded systems extremely challenging. This is evident by the increase in effort and expenditure for design of safety-driven real-time controldominated applications like automotive and avionic controllers. Design processes are often challenged by lack of proper programming tools for specifying and verifying critical requirements (e.g. timing and reliability) of such applications. Platform based design, an approach for designing embedded systems, addresses the above concerns by separating requirement from architecture. The requirement specifies the intended behavior of an application while the architecture specifies the guarantees (e.g. execution speed, failure rate etc). An implementation, a mapping of the requirement on the architecture, is then analyzed for correctness. The orthogonalization of concerns makes the specification and analyses simpler. An effective use of such design methodology has been proposed in Logical Execution Time (LET) model of real-time tasks. The model separates the timing requirements (specified by release and termination instances of a task) from the architecture guarantees (specified by worst-case execution time of the task).

This dissertation proposes a coordination language, Hierarchical Timing Language (HTL), that captures the timing and reliability requirements of real-time applications. An implementation of the program on an architecture is then analyzed to check whether desired timing and reliability requirements are met or not. The core framework extends the LET model by accounting for reliability and refinement. The reliability model separates the reliability requirements of tasks from the reliability guarantees of the architecture. The requirement expresses the desired long-term reliability while the architecture provides a short-term reliability guarantee (e.g. failure rate for each iteration). The analysis checks if the short-term guarantee ensures the desired long-term reliability. The refinement model allows replacing a task by another task during program execution. Refinement preserves schedulability and reliability, i.e., if a refined task is schedulable and reliable for an implementation, then the refining task is also schedulable and reliable for the implementation. Refinement helps in concise specification without overloading analysis.

The work presents the formal model, the analyses (both with and without refinement), and a compiler for HTL programs. The compiler checks composition and refinement constraints, performs schedulability and reliability analyses, and generates code for implementation of an HTL program on a virtual machine. Three real-time controllers, one each from automatic control, automotive control and avionic control, are used to illustrate the steps in modeling and analyzing HTL programs.

> Professor Alberto Sangiovanni-Vincentelli, Chair Date

#### Acknowledgements

I thank Prof. Alberto Sangiovanni-Vincentelli for his help, guidance and support. The course he taught on embedded systems has been a foundation for my research. I have been surprised again and again with his enthusiasm and energy, and thank him for making time from his busy schedule; our discussions have always been a great learning experience for me.

I thank Prof. Thomas A. Henzinger for his guidance and support in my research. Many of the research directions explored in this thesis grew out of discussions with him. He has been relentless in providing feedback, comments, suggestions and directions for the work presented here. His classes on algorithms and formal verification have been central in understanding many concepts. The experience of seeing him work from close will be a memory of a life-time.

Prof. Christoph Kirsch has been truly a *friend*, *philosopher* and *guide*. The hours of discussions that I had with him in the last six years led the foundation of my research. I am grateful for his time and patience. His guidance on language design, writing styles and research presentations have helped me immensely.

Prof. Edward A. Lee was a reader of my Masters report, served as the chair of my qualifying exam committee, has agreed to be a member of my dissertation committee, taught an excellent course on embedded systems and has always given valuable feedback on my research. I would like to thank him for his help and support.

I would like to thank Prof. J. Karl Hedrick for being in my qualifying exam committee and agreeing to be in the dissertation committee. I am grateful for his comments and feedback on a research project I was working with his student, Carlos Zavala. Daniel Iercan has been a strong support for this work with his excellent skills in programming and implementation. We have never met but spent hours on Skype discussing theoretical details, designs, proofs, examples, papers, presentations, and bugs. He has been relentless in implementing many of the concepts presented here.

I would like to thank Prof. Andreas Kuehlmann, Prof. Kurt Keutzer, Prof. George Necula, Prof. Satish Rao, and Dr. John Koo, for the excellent classes they taught. A special thanks to Prof. Kurt Keutzer who was equally comfortable in teaching CAD design flow and business of software.

During the course of the research, I had an opportunity to work with General Motors Research on cost modeling of embedded systems. I would like to thank Tom Fuhrman, Alan Baum, Paolo Giusto, Sri Kanajan and Randall Urbance for their help and guidance for the project. I am particularly grateful to Sri Kanajan for his support and time.

I would like to thank the Management of Technology Program for providing an excellent opportunity to learn the basics of business. I am grateful to Prof. Andrew Isaacs, Prof. Reza Moazzami, Prof. Charles Wu and Prof. Sarah Beckman for the amazing courses they taught.

I would like to extend my gratitude for the support and help I received from my friends: Mohan Dunga, with whom I shared apartment, cooking and television time for six years; Satrajit Chatterjee, with whom I discussed everything under the sun and beyond; Kaushik Ravindran, who has surprised me repeatedly with his knowledge; Krishnendu Chatterjee, whose skills in music and in games are captivating; Arindam Chakrabarti, who amazed me by his ability to passionately debate any topic; Rahul Tandra, whose poker and cricket skills could have been better utilized; Pankaj Kalra, who has been always a gentleman; Anshuman Sharma, whose company always brought a smile; Abhishek Ghose, who was usually the coolest dude in town; and Vinayak Prabhu, who has been an excellent office mate. I would like to acknowledge the following friends at the DOP center who have been a source of joy and encouragement: Alvise Bonivento, Mike Case, Elaine Cheong, Abhijit Davare, Douglas Densmore, Ben Horowitz, Jorn Janneck, Marcin Jurdzinski, Animesh Kumar, Yanmei Li, Cong Liu, Slobodan Matic, Rupak Mazumdar, Mark McKelvin, Trevor Meyerowitz, Claudio Pinello, Alessandro Pinto, William Plishker, Marco Sanvido, N. R. Satish, Farhana Sheikh, Gerald Wang, Chang-Ching Wu, Guang Yang, Haibo Zeng, Yang Zhao, Haiyang Zheng, Wei Zheng, and Qi Zhu.

I am lucky to enjoy support of my friends Sombuddha Chakraborty, Arnab Chowdhury, Neha Dave, Sohini Mitra, Shubrangshu Nandi, Binayak Roy, and Sabyasachi Siddhanta. Life would have been no fun without the "Davis gang": Ravi Shankar Rao, Renuka Sriram, Shankar Guhados, Chintamani Kulkarni, and Jaya Nair.

Outside the academic program, music classes with Judith Meitez and work-outs at Funky Door Yoga and Recreational Sports Facility made life enjoyable.

I thank the members of the EECS Department administration for maintaining and supporting an excellent workplace : Mary Byrnes, Ruth Gjerde, Jontae Gray, Patrick Hernan, Cindy Keenon, Brad Krepes, Ellen Lenzi, Loretta Lutcher, Dan MacLeod, Marvin Motley, Jennifer Stone, and Carol Zalon. A special thanks to Ruth Gjerde of EE Graduate Student Affairs for her help in so many situations.

A major portion of the thesis was written at Bel Forno (at Shattuck and Rose), Starbucks (at Cedar and Shattuck) and Mishka's Cafe (at Davis).

The last few years would not have been so wonderful without the smile and encouragement from Deboshmita.

The last six years in graduate school would not have been possible without the support of my parents, Sipra and Basudev Ghosal. When I was low, they made me forget the troubles. When I was sad, they made me smile. When I felt lonely, they gave me company. When I felt weak, they inspired me. No thanks would be enough to express my gratitude for them.

#### **Publications, Co-Authors and Grants**

Chapters 2, 3, 4, 5 and 6 are based on the following publications: (1) A hierarchical coordination language for interacting real-time tasks (in Proceedings of the 6th ACM & IEEE International conference on Embedded software, 2006) authored by Arkadeb Ghosal, Thomas A. Henzinger, Daniel Iercan, Christoph M. Kirsch and Alberto Sangiovanni-Vincentelli; and, (2) Hierarchical Timing Language (Technical Report, UC Berkeley, 2006) authored by Arkadeb Ghosal, Thomas A. Henzinger, Daniel Iercan, Christoph M. Kirsch and Alberto Sangiovanni-Vincentelli.

Chapter 8 is based on the publication Separate compilation of hierarchical realtime programs into linear-bounded embedded machine code (in Online Proceedings of Workshop on Automatic Program Generation for Embedded Systems, 2007) authored by Arkadeb Ghosal, Daniel Iercan, Christoph M. Kirsch, Thomas A. Henzinger and Alberto Sangiovanni-Vincentelli. Daniel implemented a prototype compiler.

Chapters 2 and 7 are based on the publication *Logical Reliability of Interacting Real-Time Tasks* (in Proceedings of International Conference on Design, Automation and Test in Europe, 2008) authored by Krishnendu Chatterjee, Arkadeb Ghosal, Thomas A. Henzinger, Daniel Iercan, Christoph M. Kirsch, Claudio Pinello and Alberto Sangiovanni-Vincentelli.

The HTL modeling in Chapter 9 is a joint work with Daniel Iercan. Daniel implemented the tank controller and a simulation environment for the Javiator.

I am grateful to my co-authors for their help, suggestions and guidance.

This work was supported by the GSRC grant 2003-DT-660, the NSF grant CCR-0208875, the HYCON and Artist II European NoE, the European Integrated Project SPEEDS, the SNSF NCCR MICS, the Austrian Science Fund Project P18913-N15, General Motors, United Technologies Corp., and the CHESS at UC Berkeley, which is supported by the NSF grant CCR-0225610, the State of California Micro Program, Agilent, DGIST, Hewlett Packard, Infineon, Microsoft, and Toyota.

Dedicated to my parents, Mrs. Sipra Ghosal and Mr. Basudev Ghosal

# Contents

| Li       | st of | Figures                                  | x    |

|----------|-------|------------------------------------------|------|

| Li       | st of | Tables                                   | xiii |

| 1        | Intr  | oduction                                 | 1    |

|          | 1.1   | Automotive Industry                      | 4    |

|          | 1.2   | Separation of Concerns                   | 6    |

|          | 1.3   | Logical Execution Time                   | 7    |

|          | 1.4   | Logical Reliability Model                | 9    |

|          | 1.5   | Refinement                               | 10   |

|          | 1.6   | Hierarchical Timing Language             | 12   |

|          | 1.7   | Overview                                 | 13   |

| <b>2</b> | Pro   | gramming Model                           | 15   |

|          | 2.1   | Logical Execution Time Model             | 16   |

|          | 2.2   | Extension of LET Model                   | 19   |

|          | 2.3   | Communicators and Logical Execution Time | 20   |

|          | 2.4   | Logical Reliability Model                | 22   |

|          | 2.5   | Reliability Analysis                     | 25   |

|          | 2.6   | Refinement                               | 33   |

| 3        | Hie            | rarchical Timing Language                      | 36  |

|----------|----------------|------------------------------------------------|-----|

|          | 3.1            | Overview of HTL                                | 37  |

|          | 3.2            | Abstract Syntax                                | 44  |

|          | 3.3            | Hierarchy and Relation between Components      | 48  |

|          | 3.4            | Task Invocation and Relation with Input/Output | 50  |

| 4        | Ope            | erational Semantics                            | 55  |

|          | 4.1            | Execution State                                | 56  |

|          | 4.2            | Execution Trace                                | 58  |

| <b>5</b> | Det            | erminism                                       | 64  |

|          | 5.1            | Well-Formed Program                            | 64  |

|          | 5.2            | Structural Properties                          | 69  |

|          | 5.3            | Execution Properties                           | 74  |

|          | 5.4            | Determinism                                    | 76  |

| 6        | $\mathbf{Sch}$ | edulability Analysis                           | 79  |

|          | 6.1            | HTL Implementation                             | 80  |

|          | 6.2            | Semantics of Implementation                    | 81  |

|          | 6.3            | Schedulable Implementation                     | 88  |

|          | 6.4            | Schedulability-Preserving Implementation       | 91  |

| 7        | Rel            | iability Analysis                              | 99  |

|          | 7.1            | Extension of HTL Syntax                        | 100 |

|          | 7.2            | Implementation                                 | 101 |

|          | 7.3            | Semantics of Implementation                    | 102 |

|          | 7.4            | Reliable Implementation                        | 103 |

|          | 7.5            | Reliability Analysis                           | 103 |

|    | 7.6                                                                                                         | Reliability-Preserving Implementation                                                                          | 106                                                                                      |

|----|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|    | 7.7                                                                                                         | Extension of Program Structure                                                                                 | 107                                                                                      |

| 8  | Con                                                                                                         | npiler                                                                                                         | 109                                                                                      |

|    | 8.1                                                                                                         | The Embedded Machine $\ldots$ | 109                                                                                      |

|    | 8.2                                                                                                         | Hierarchical E Code                                                                                            | 111                                                                                      |

|    | 8.3                                                                                                         | HTL in HE Code                                                                                                 | 117                                                                                      |

|    | 8.4                                                                                                         | HE Code Generator for HTL                                                                                      | 120                                                                                      |

|    | 8.5                                                                                                         | Design Flow                                                                                                    | 129                                                                                      |

| 9  | Con                                                                                                         | trol Applications                                                                                              | 131                                                                                      |

|    | 9.1                                                                                                         | Three-tank-system Controller                                                                                   | 131                                                                                      |

|    | 9.2                                                                                                         | Steer-by-Wire Controller                                                                                       | 141                                                                                      |

|    | 9.3                                                                                                         | Helicopter Controller                                                                                          | 148                                                                                      |

| 10 | Rela                                                                                                        | ated Work                                                                                                      | 152                                                                                      |

|    | 10.1                                                                                                        | Giotto                                                                                                         | 152                                                                                      |

|    | 10.2                                                                                                        | Other Timed Languages                                                                                          |                                                                                          |

|    | 10.2                                                                                                        |                                                                                                                | 155                                                                                      |

|    |                                                                                                             | Synchronous Languages                                                                                          | 155 $158$                                                                                |

|    | 10.3                                                                                                        |                                                                                                                |                                                                                          |

|    | 10.3<br>10.4                                                                                                | Synchronous Languages                                                                                          | 158 $160$                                                                                |

|    | 10.3<br>10.4<br>10.5                                                                                        | Synchronous Languages       Real Time Extensions                                                               | 158<br>160<br>162                                                                        |

|    | 10.3<br>10.4<br>10.5<br>10.6                                                                                | Synchronous Languages                                                                                          | 158<br>160<br>162<br>163                                                                 |

| 11 | 10.3<br>10.4<br>10.5<br>10.6<br>10.7                                                                        | Synchronous Languages                                                                                          | 158<br>160<br>162<br>163<br>165                                                          |

| 11 | <ul> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li>10.6</li> <li>10.7</li> <li>Contained</li> </ul>         | Synchronous Languages                                                                                          | <ol> <li>158</li> <li>160</li> <li>162</li> <li>163</li> <li>165</li> <li>167</li> </ol> |

| 11 | <ul> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li>10.6</li> <li>10.7</li> <li>Com</li> <li>11.1</li> </ul> | Synchronous Languages                                                                                          | 158<br>160<br>162<br>163                                                                 |

| Appendix A   | Reliability of Networks         | 174 |

|--------------|---------------------------------|-----|

| Appendix B   | Flattening of HTL               | 178 |

| Appendix C   | Giotto to HTL                   | 184 |

| Appendix D   | HTL Program for 3TS Controller  | 190 |

| Appendix E   | HTL Program for SBW Controller  | 193 |

| Appendix F   | HTL Program for Heli Controller | 197 |

| Bibliography |                                 | 204 |

# **List of Figures**

| 1.1  | Move to drive-by-wire 5                                    |

|------|------------------------------------------------------------|

| 1.2  | Growth of electronic control and software in automobiles 6 |

| 1.3  | Platform-based design                                      |

| 1.4  | Overview of task refinement                                |

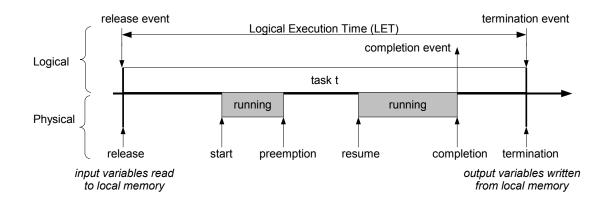

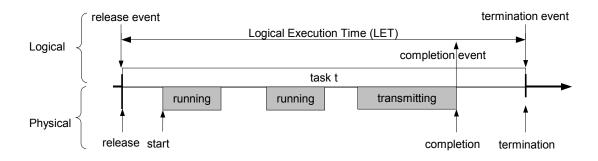

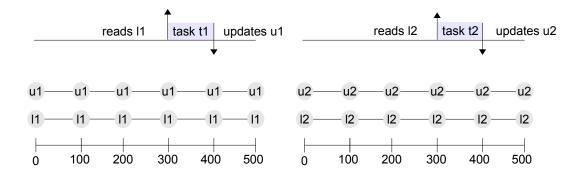

| 2.1  | LET model of task execution                                |

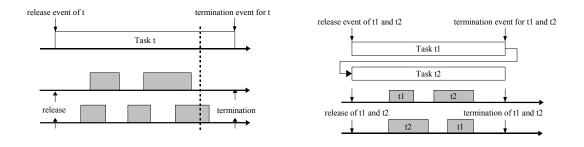

| 2.2  | Time determinism                                           |

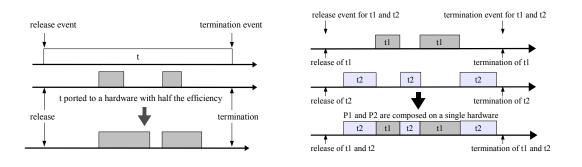

| 2.3  | Value determinism                                          |

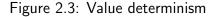

| 2.4  | Portability                                                |

| 2.5  | Composability                                              |

| 2.6  | Task execution and transmission    19                      |

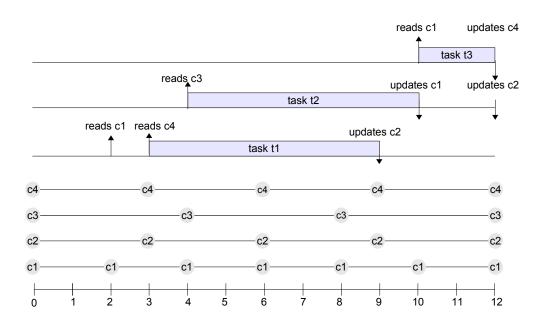

| 2.7  | Communicators and tasks                                    |

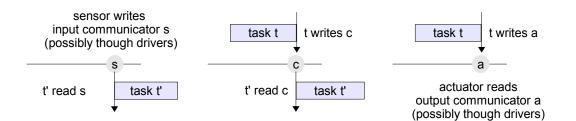

| 2.8  | Communication via communicators                            |

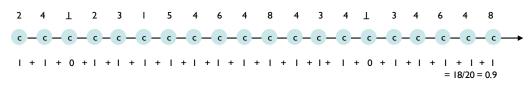

| 2.9  | Fraction of reliable values                                |

| 2.10 | Intro to reliability analysis                              |

| 2.11 | Reliability preserving refinement                          |

| 3.1  | An HTL mode                                                |

| 3.2  | Two HTL modes 39                                           |

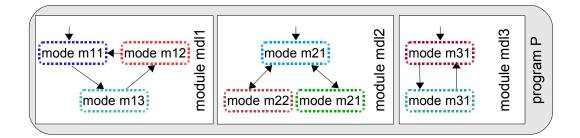

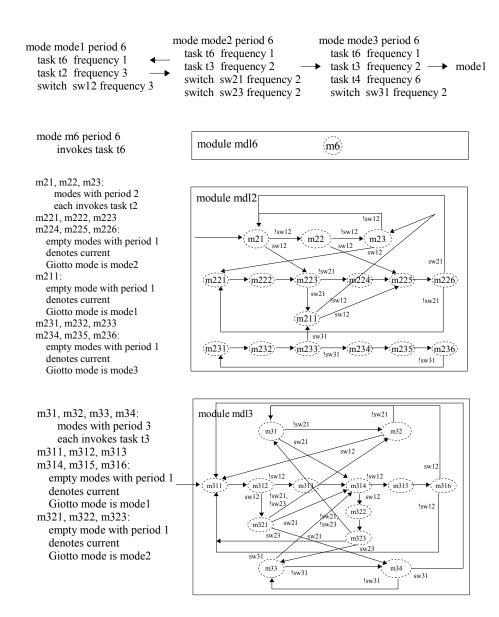

| 3.3  | An HTL program with three modules                          |

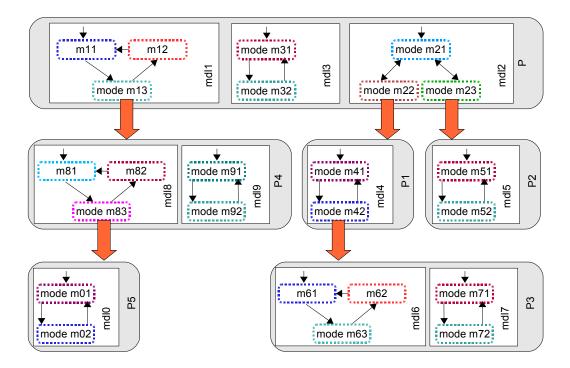

| 3.4  | An HTL program                                               | 41  |

|------|--------------------------------------------------------------|-----|

| 3.5  | Refinement in HTL                                            | 43  |

| 4.1  | Successor configurations                                     | 61  |

| 5.1  | Mode switching through hierarchy                             | 76  |

| 6.1  | Schedulability-preserving implementation                     | 92  |

| 7.1  | Reliability-preserving implementation                        | 107 |

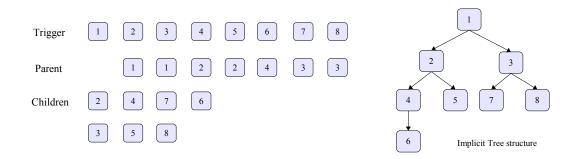

| 8.1  | Triggers, queue of triggers and implicit tree                | 111 |

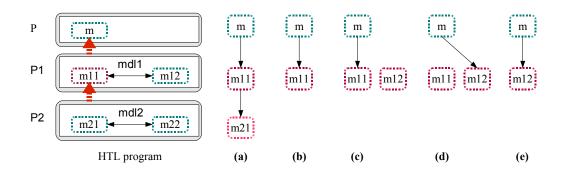

| 8.2  | Handling switch checks in HE code                            | 119 |

| 8.3  | Handling switch checks in HE code                            | 119 |

| 8.4  | Structure of compiler and runtime system                     | 130 |

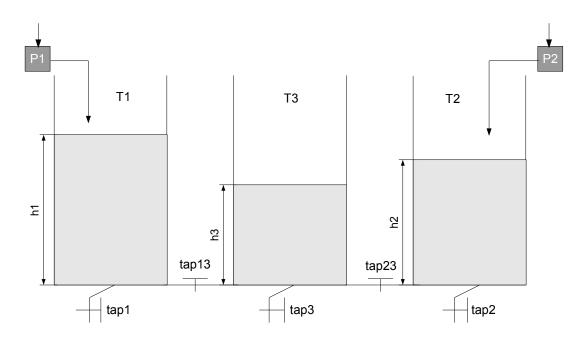

| 9.1  | Overview of 3 tank system                                    | 132 |

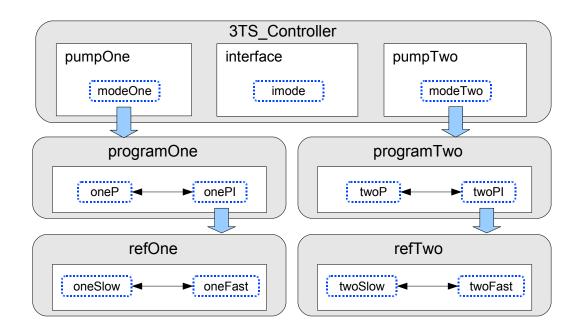

| 9.2  | HTL program for 3TS controller                               | 133 |

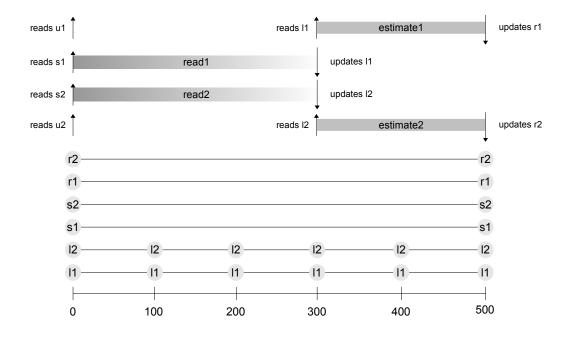

| 9.3  | Timing behavior of the tasks $\texttt{t1}$ and $\texttt{t2}$ | 135 |

| 9.4  | Timing behavior of the tasks in mode imode                   | 135 |

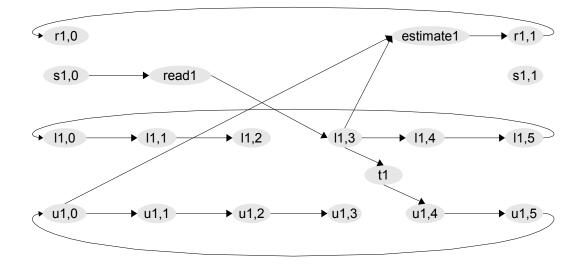

| 9.5  | Program graph                                                | 137 |

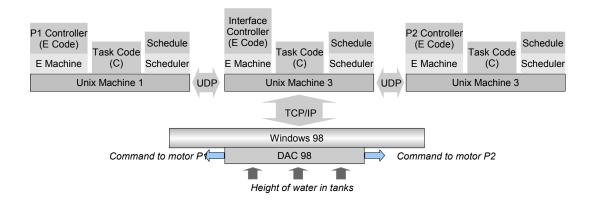

| 9.6  | Implementation                                               | 140 |

| 9.7  | 3TS setup                                                    | 140 |

| 9.8  | 3TS system while running                                     | 140 |

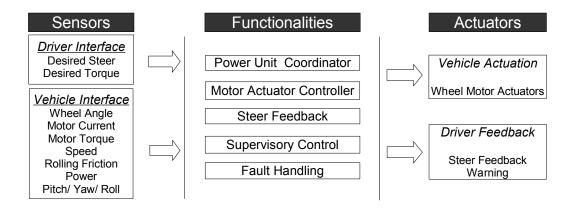

| 9.9  | Data flow and functional blocks                              | 141 |

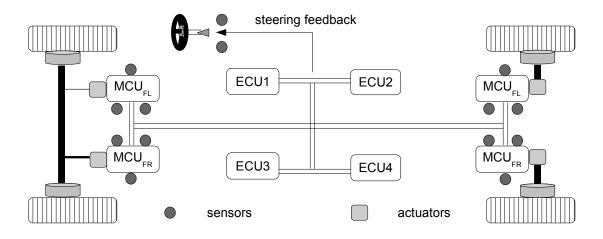

| 9.10 | Implementation of SBW system                                 | 142 |

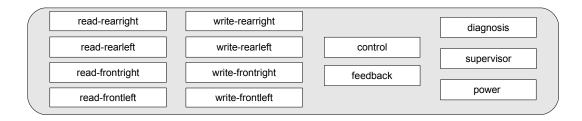

| 9.11 | Modules for the SBW implementation                           | 143 |

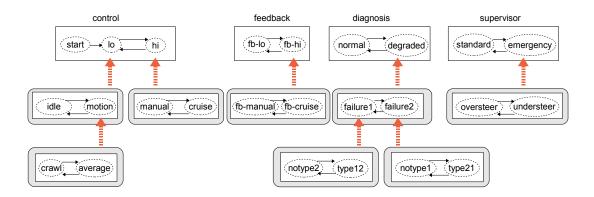

| 9.12 | Modes for the modules                                        | 144 |

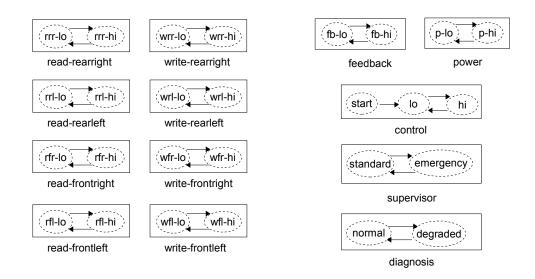

| 9.13 | Refinement programs in the SBW description                   | 145 |

| 9.14 | SBW controller                                               | 146 |

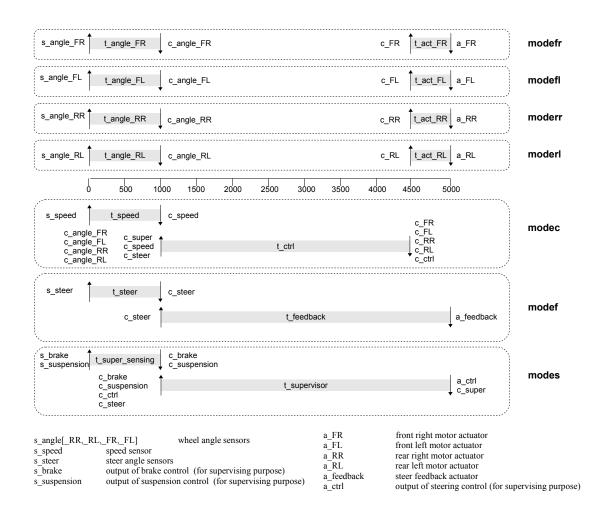

| 9.15 | Timing and communication in the SBW controller                  | 147 |

|------|-----------------------------------------------------------------|-----|

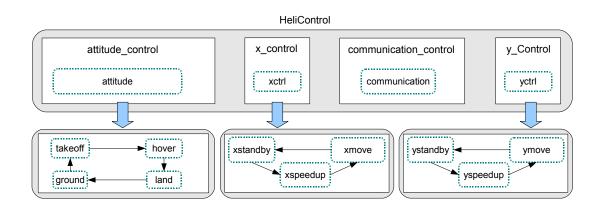

| 9.16 | Helicopter control program                                      | 149 |

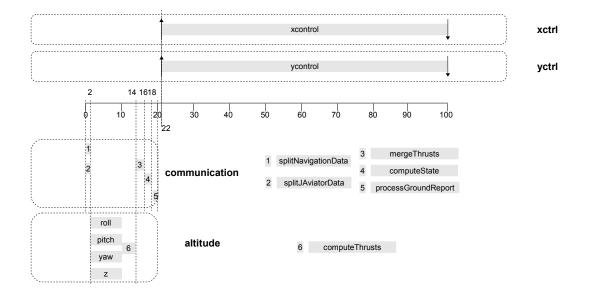

| 9.17 | Helicopter control tasks                                        | 150 |

|      |                                                                 |     |

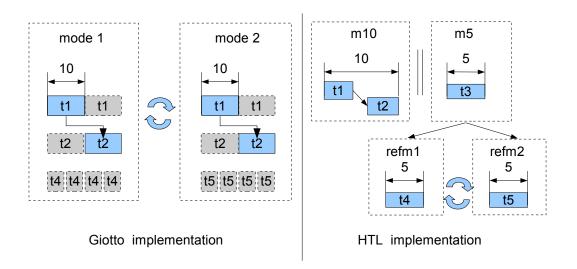

| 10.1 | Giotto modes                                                    | 153 |

| 10.2 | HTL code fragments                                              | 154 |

| 10.3 | Schematic view of differences in Giotto and HTL implementations | 155 |

|      |                                                                 |     |

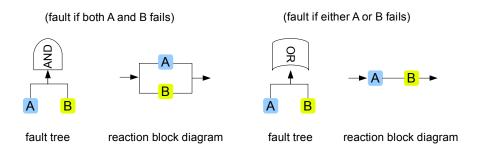

| A.1  | Series and parallel reaction block diagrams                     | 176 |

| A.2  | Comparison between RBDs and Fault trees                         | 177 |

|      |                                                                 |     |

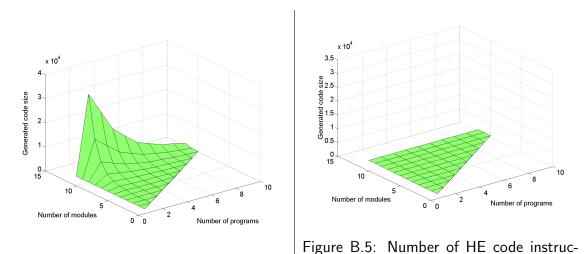

| B.4  | Number of E code instructions                                   | 183 |

| B.5  | Number of HE code instructions                                  | 183 |

|      |                                                                 |     |

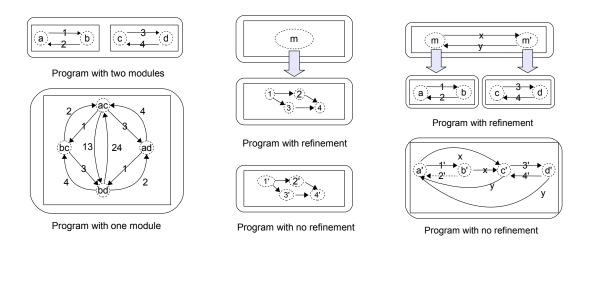

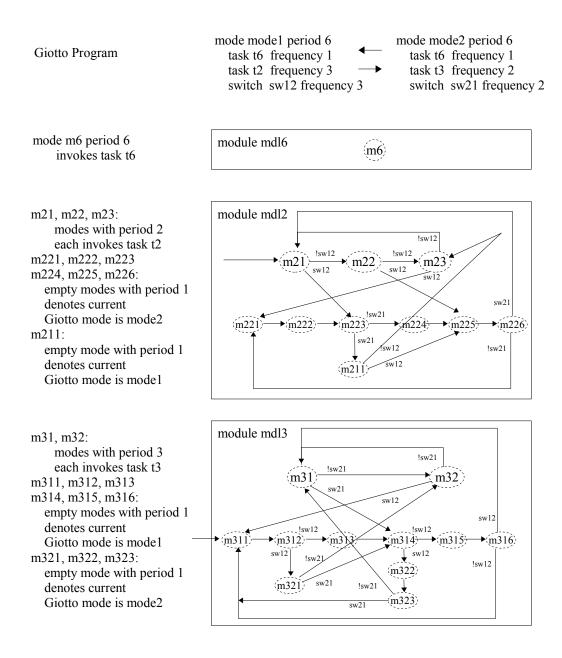

| C.1  | Example 1                                                       | 185 |

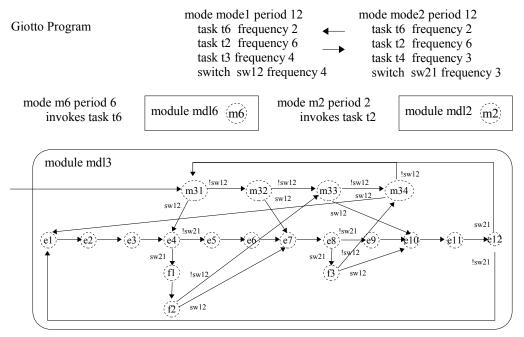

| C.2  | Example 2                                                       | 187 |

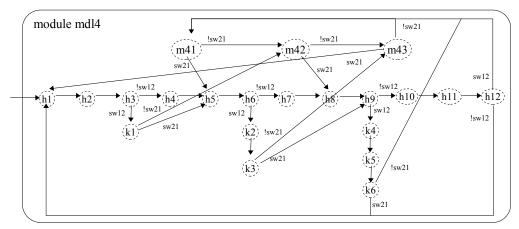

| C.3  | Example 3                                                       | 189 |

# List of Tables

| 8.1 | Variable update and task release instructions  | 114 |

|-----|------------------------------------------------|-----|

| 8.2 | New trigger instructions                       | 114 |

| 8.3 | Control flow instructions                      | 115 |

| 8.4 | Instruction for handling registers             | 116 |

| 8.5 | Symbolic addresses and their significance      | 121 |

| 9.1 | Reliabilities of tasks for the implementations | 137 |

## Chapter 1

## Introduction

Embedded systems are present everywhere: from large-scale industrial plants to minuscule sensors. They are used in automotive stability controllers, avionic fly-by-wire controllers, medical devices, intelligent buildings, distributed sensor networks and smart machines. The design of such systems has two challenges: the development of required hardware resources (e.g. ecus, sensors, actuators) and the use of solid design methodologies for implementing applications on the hardware resources. While the design of hardware resources is challenging and interesting, the focus of this dissertation would be design methodologies for implementing applications on existing hardware resources.

As the complexity of the applications is growing constantly, designer productivity is decreasing. Since these applications are often safety critical and time sensitive, errors are a very expensive proposition and are to be avoided at all costs. For flexibility reasons, system designers favor software solutions. The productivity of embedded software designers is notoriously very low; industry reports indicate about 10 lines of code per day. The reason for such a low productivity is rooted in the extensive verification needed to make sure that the design satisfies all constraints including realtime ones that are typical of important applications such as automotive and avionic controllers. The high verification cost is due to the absence of solid design methods: the current processes are empirical and ad-hoc.

The seriousness of the problem is reflected in the opening paragraph of article "Programming Languages for Real-Time Systems" [Bouyssounouse and Sifakis, 2005]: The interdependence between functional and real-time semantics of real-time software makes its design, implementation and maintenance especially difficult. Providing a programming language that directly supports the characteristics of embedded real-time software can significantly ease these difficulties. In addition, embedded software systems are not portable as they depend on the particular underlying operating system and hardware architecture. Providing implementation-independent programming models also increases the portability.

The challenges in design of software controllers for embedded systems comes from both the formal constraints of the design space and the practical constraints of the industry. The formal constraints include *concurrency*, *composability*, *time-criticality*, *heterogeneity*, *distributiveness* and *constraints on resources* (e.g. limit to execution speed, communication latency, unreliability etc). The industrial constraints include factors like faster time to market, OEM based supply chain, option packaging in the same product line, extensibility/flexibility/reuse of design, standardization, regulation, market dynamics, concerns for safety, and validation effort.

This dissertation focuses on improving design productivity by raising level of abstraction (in the form of a programming language) for system specification and using formal verification (for validation of system implementation). The need for good abstraction that efficiently combines real-time semantics and formal verification is of utmost importance. Instead of being a computation model, the abstraction expresses interaction of a task with other tasks (e.g. data dependency) and response of a task to changes in environment (e.g. progress of clock). The computation is expressed and implemented in a conventional language e.g. C or C++, while the abstraction is captured in a coordination language. A coordination language is the linguistic embodiment of a coordination model, offering facilities for controlling synchronization, communication, creation and termination of computational activities [Gelernter and Carriero, 1992] [Ciancarini, 1996] [Papadopoulos and Arbab, 1998]. The choice for coordination language is two-fold. *First*, there is a large amount of legacy code for functionalities in real-time controllers. *Second*, the need is to verify system issues which largely depend on task interaction instead of task definition. By defining a coordination language, the model focuses on checking system properties related to task interaction rather that functional properties of task definition. Timing and reliability of the system are the two primary concerns.

The correctness of a real-time system depends not only on the logical result of the computation, but also on the time at which the results are produced. [Burns and Wellings, 2001]. Thus the execution of a time critical system should be available when it is due, neither before nor after the deadline. There are applications where the timing may be slightly relaxed (soft real-time system); however for most applications the timing is a crucial property (hard real-time systems).

In the domain of safety-driven embedded applications, such as automotive stability controllers and medical devices, reliability and fault tolerance are increasingly important as regulatory bodies and customers demand robust products. Much research has been carried out over the years on topics such as reliability analysis, fault tolerant architectures, and fault analysis. However, we are still at the early stages for design methodologies and tools that take into consideration, constraints on reliability and fault tolerance. The design processes are further limited when reliability and fault tolerance analysis needs to be combined with timing and schedulability analysis. The thesis proposes a model that effectively captures reliability requirements and that is amenable to efficient formal verification. Earlier several industries, where embedded systems play a pivotal role, were mentioned; Section 1.1 discusses one of them: the automotive industry. Section 1.2 presents the design methodology on which the proposed model is based. Section 1.3 and Section 1.4 provide an overview of the timing and reliability model for interacting real-time tasks respectively. Section 1.5 proposes a technique for efficient analysis. An overview of the new coordination language is presented in Section 1.6.

## 1.1 Automotive Industry

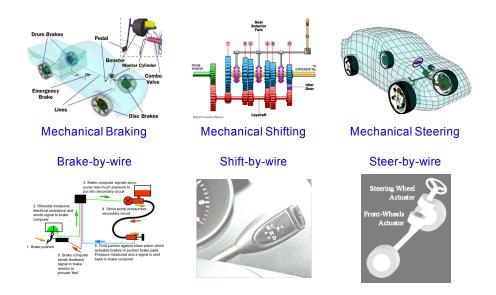

The effect of growing complexity in the design and deployment of embedded systems is crucial in automotive industry. While there has been an explosion in car electronics related to infotainment, communications with external world, safety, and climate-and-body control, embedded systems have become a major player in the core functionalities of a car e.g. braking, shifting and steering. This has enabled the replacement of traditional mechanical coupling with x-by-wire technology (Figure 1.1) which in turn allows fine-tuning vehicle handling without changing the mechanical components of a vehicle. For example, traditionally steering wheel rotation is accompanied by a mechanical link rotation which signals the change in direction of the wheel. In steer-by-wire system, the change in steering angle is recorded by a sensor. The data is sent to an electronic control unit (ECU). The ECU also receives data from a motor control unit which reads the driving conditions (wheel speed, angle, yaw, pitch, roll etc). The ECU computes the required wheel angle based on the above signals and sends the evaluation to motor control units which in turn update the wheel motor actuators. Due to inherent fault behavior of an ECU, the computation may be replicated on several ECUs. A steer feedback is computed and send back to the steer for realistic driving feeling. Depending on system requirements, a supervisor module may coordinate between different x-by-wire controllers.

Figure 1.1: Move to drive-by-wire

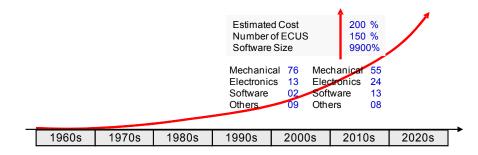

The shift to x-by-wire systems has increased the importance of design and development of electronic control and software in design, development and manufacturing of automotive product lines. In the last two decades, General Motors reports (Fig. 1.2), the number of electronic control unit in cars have increased by 150% and the size of software modules increased by 9900%. This increased the cost associated with electronic control and software by 200%. In the future, cost is predicted to rise. Nihon Keizai Shimbun reports that cost associated with development effort (in Japan) for automotive related software would grow from 903 million US dollars (in 2006) to 9.1 billion US dollars (in 2014).

Figure 1.2: Growth of electronic control and software in automobiles

## 1.2 Separation of Concerns

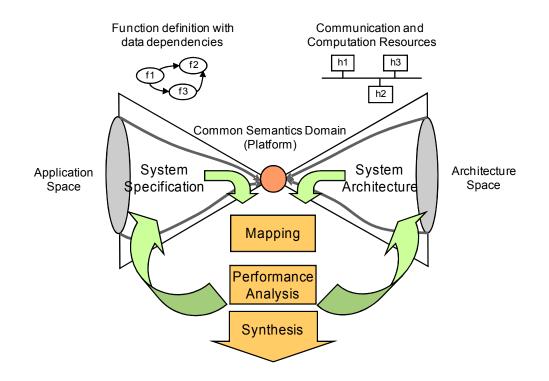

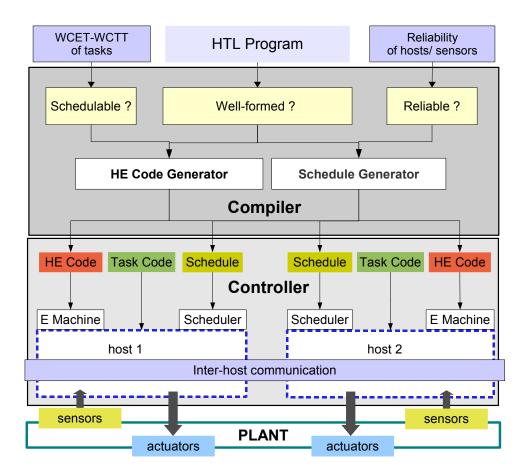

One of the proposed approaches for embedded systems design is *platform-based de-sign* [Sangiovanni-Vincentelli *et al.*, 2004] that emphasizes separating functional specification from architecture. Functional specification (e.g. a set of functions with data dependencies) denotes what the system is supposed to do. Architecture (e.g., a set of computational resources connected through communication links) accounts for the available hardware resources. An implementation of the specification on an architecture is an allocation of the specification to the architecture, e.g. an implementation can be a mapping of the functions to computational resources and the data dependencies to communication links. An implementation can be analyzed to check whether constraints posed by the designer such as power consumption, latency, and deadlock freedom have been met or not. If the constraints are not met, then the designer can update/modify the architecture. The architecture can be modified independent of the functional specification which speeds up the exploration of different architectures and mapping. Once the implementation meets design constraints, the specification is synthesized (e.g. code is generated) for the target architecture.

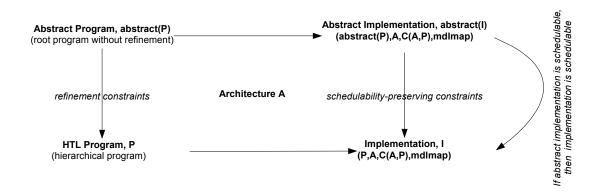

Figure 1.3: Platform-based design

### 1.3 Logical Execution Time

An effective utilization of the separation-of-concerns approach has been used in *Logical Execution Time* (LET) Model [Henzinger *et al.*, 2003] for task execution where specification of a task is captured by release and termination events while the actual execution time is obtained by analyzing the task relative to an architecture. At release event, a LET task is released for execution; the task output is available only when the termination event occurs. Even if the task completes its execution before the termination event arrives, the task output is not released. The interval between the release and termination event is the LET for the task. An execution of a LET task is *time-safe*  if the task completes execution within the respective LET. The LET model makes the program execution time-deterministic (no jitter) and value-deterministic (no race conditions); this supports efficient schedulability analysis which checks whether all tasks are time-safe or not. The separation of timing from functionality also helps in architecture exploration and portability.

The LET model is a meet-in-the-middle approach when compared to more traditional paradigms used to ensure timing and predictability of real-time systems Burns and Wellings, 2001, [Edwards, 2000], [Buttazzo, 1997]. Previous attempts can be broadly classified on the basis of when the evaluation of a task is available. In one approach, task evaluations are made available as soon as the execution is complete. Priorities are used to specify (indirectly) the relative deadlines of tasks. The approach is supported by efficient code generation based on scheduling theory [Buttazzo, 1997]. However the execution time of tasks varies from one real-time platform to other and this causes race conditions (non-determinism in program variables), which in turn makes program verification and analysis extremely difficult. The other approach is based on the synchrony assumption [Halbwachs, 1993] that the underlying platform is much faster than the response time of tasks and the task may be assumed to be executing in zero time (logically). In other words, analysis of the system is performed assuming task evaluations are available as soon as they are released. The approach is mathematically very expressive and supports determinism and formal verification. However compiling synchronous languages is non trivial when it comes to tasks with non-negligible execution time and distributed computing. LET model, which allows task outputs to be available only after certain instances, trades code efficiency in favor of code predictability when compared with the first approach, which makes all outputs visible as soon as they become available. When compared with the second approach, LET model (where all logical execution times are assumed to be strictly positive) trades mathematical expressiveness in favor of computational realities.

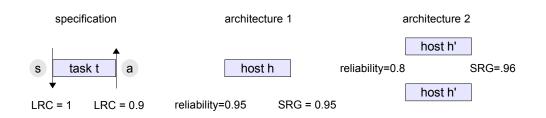

## 1.4 Logical Reliability Model

The separation-of-concerns approach used for schedulability has been extended for reliability analysis [Chatterjee *et al.*, 2008] thus setting the foundations for a joint schedulability/reliability analysis methodology. The main idea is the separation of application dependent ("logical") information from platform dependent ("physical") data. The reliability requirements (of real-time tasks) is separated from the reliability characteristics of hosts (on which the tasks execute). Reliability requirements are specified by *Logical Reliability Constraint* (LRC) and the architecture ensures *Singular Reliability Guarantee* (SRG). In the analogy between timing and reliability, LRCs play the role of release times and deadlines, while SRGs play the role of worst-case execution times. The timing analysis checks that all tasks get access to execution no less than the respective worst-case execution time (WCET); in case of transmission of output, worst-case transmission time (WCTT) should also be accounted. The reliability analysis checks that SRG for all tasks meets the respective LRC.

In the reliability model, each input and output variable of a task is assigned a LRC. As tasks read and write the variables, this implicitly defines LRCs for the tasks. Each variable is associated with a LRC which is a real number between 0 and 1. LRC denotes the fraction of all periodic writes (to the variable) in the long run that are required to be valid e.g. if LRC of a variable is 0.9, then in the long run, at least 0.9 fraction of all periodic writes to this variable are required to be valid values; thus LRC is also referred as *long-term reliability constraint*. LRC, similar to release and termination event, is independent of the architecture.

Given an architecture on which a task (writing to a variable) executes, SRG of the variable (relative to that architecture) can be computed. SRG, a real number between 0 and 1, denotes the probability with which the variable would be assigned a reliable value at an update instance. Similar to WCET/WCTT, SRG depends on the underlying architecture, and is computed from the reliability of the components of the architecture. For example, consider a task executing on a host; the task periodically reads from a reliable input and writes to a variable. The host has a reliability of 0.8 i.e., the probability that the variable has a valid value at the end of task execution is 0.8; in other words SRG of the variable for the architecture is 0.8. If the task is replicated on two such hosts, the updated SRG is .96 (=  $1 - .2^2$ , i.e., the probability that at least one host is executing), assuming reliable communication and reliable inputs. If the SRG is no less than the LRC, then the implementation (of the task on the host) is reliable for the variable. SRG is a guarantee for each invocation of the task i.e., it ensures short-term reliability; thus SRG is also referred as *short-term reliability guarantee*. The analysis checks whether the SRG ensures the LRC or not; this is similar to schedulability analysis which checks whether the WCET/WCTT can be accommodated within the LET or not.

## 1.5 Refinement

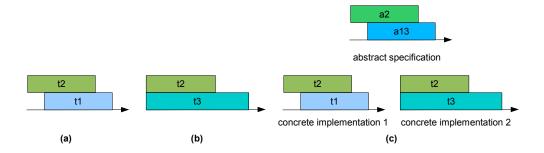

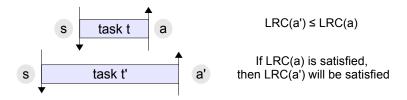

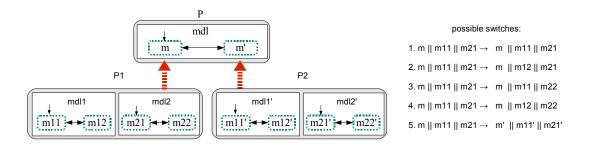

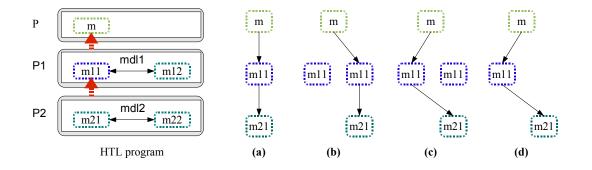

Given a LET task and a host on which the task is implemented, schedulability analysis checks whether the WCET of the task (on that host) is less then the LET of the task. If there are multiple tasks, then a detailed schedulability analysis (e.g. aperiodic task scheduling) may be performed. Consider two tasks t1 and t2 executing in parallel (Fig. 1.4.a). The LET of respective tasks are denoted by the rectangles. An aperiodic EDF scheduling analysis can be performed to check whether the tasks are time-safe or not. If there is another set of tasks, t2 and t3 (Fig. 1.4.b), then the schedulability analysis need to be repeated. Consider the schedulability analysis is done for a third set of tasks a2 and a13 (Fig. 1.4.c). The LET and WCET of the tasks t2 and a2 are identical; also the release event of a13 is later than the release events of t1 and t3, termination event of a13 is earlier than the terminations events of t1 and t3,

and WCET of a13 is larger than both t1 and t3. Under the above conditions, if a2 and a13 are time-safe, then the other two combinations are also time-safe. Thus if schedulability analysis is performed on a2 and a13, the analysis need not be repeated for the other two sets of tasks which reduces the number of checks. The combination a2 and a13 is referred as an abstract specification and the other two combinations are concrete implementations of the abstract specification. Task t2 is a *refinement* of task a2; while both tasks t1 and t3 are *refinement* of task a13. Refinement reduces the validation effort: only abstract specification need to be analyzed and if each concrete task (in the concrete implementation) is a refinement of a task in the abstract specification, then the validation need not be repeated. In the above example, there are only two concrete specifications; in real example there can be arbitrary number of concrete specifications.

Figure 1.4: Overview of task refinement

If an abstract specification is time-safe (schedulable), then any concrete implementation that refines the abstract specification is also time-safe (schedulable). This is a sufficient condition i.e. there may be concrete implementations which are schedulable but the corresponding abstract specification may not be schedulable. The condition being sufficient denotes that resource usage is over-approximated; however refinement reduces the validation effort significantly and introduces flexibility in system design. Refinement constrains the timing interface of the tasks and not the IO interface or the task functionalities.

The approach can be extended for reliability analysis too. Consider a situation where task a13 reads from a reliable input and writes to a variable v13. If the reliability of the host for the period of execution of a13 is 0.9, then the SRG for v13 is 0.9. It can be shown that if the LRC of v13 is not greater than 0.9, then the implementation is reliable. Let task t1 reads from a reliable input and writes to a variable v1. If the LRC of v1 is less than the LRC of v13, then the implementation is reliable for task t1; in other words, if implementation of abstract specification is reliable, then the implementation is reliable for a concrete specification, with some restrictions on LRCs of output variables. Note the analysis (for concrete specification) is done by comparing the LRCs of the outputs of the tasks instead of comparing the SRG and the LRC of v1.

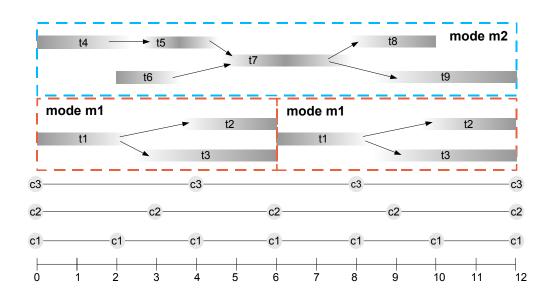

### **1.6 Hierarchical Timing Language**

Hierarchical Timing Language (HTL) is a coordination language for hard real-time systems. Like it predecessor Giotto [Henzinger *et al.*, 2003], HTL builds on the LET model of task execution. The HTL model allows sequential, parallel and conditional composition of LET tasks; and encompasses the refinement model to offer hierarchical layers of abstraction. While the layers of abstraction add structural conciseness to program specification, the refinement property reduces effort in schedulability and reliability analysis. Thus, feasible schedules for lower layers can be efficiently constructed from feasible schedules for higher layers; and if implementation is reliable for higher layers, then the implementation is reliable for lower layers. The HTL model accommodates a more general model than the LET as it extends composition and refinement from single tasks to task group with precedence. While the model of task execution in HTL is LET, the tasks in HTL communicate with each other (and with the environment) through so-called *communicators*. A communicator defines a sequence of real-time instances of a static variable. Sensors and actuators are special cases of communicators. Task *reads* and *writes* specify communicator instances. As the read and written time instances of communicators are fixed by a program, they remain unchanged when the context of the program is modified e.g. ported to another architecture. This implies that the communicator instances (a task reads from and write to) specify the LET for the task. Each communicator is also specified a LRC. Tasks read from and write to communicators; thus LRC of the communicators implicitly specify the LRC of the task. In other words, the communicators specify both the timing and reliability requirements on tasks. Composition and refinement constraints, and program execution ensures determinism.

## 1.7 Overview

Chapter 2 presents an overview of the LET model of task execution, the communicator model of communication and the logical reliability model. Next the schedulability and reliability analysis is defined for a group of periodic tasks, followed by a discussion of schedulability- and reliability-preserving refinement.

Chapter 3 presents an overview of HTL: the structural components (programs, modules, modes and refinement), the communication model (communicators and ports), and the task model (declaration and invocation). The formal definitions and the relation between components across levels of refinement are also presented.

Chapter 4 discusses the operational semantics of HTL. The semantics is independent of the implementation (distribution of program modules) or performance guarantee of the architecture on which the program is implemented. Chapter 5 presents certain structural constraints on HTL and discusses key properties on execution behavior of such constraints. The constraints ensures that there is no race in updating program variables. This makes the program execution deterministic i.e., given sufficient execution speed the values of program variables are determined by the values of the sensors.

Chapter 6 discusses the schedulability analysis for an HTL implementation which is a mapping of an HTL program on an architecture. The chapter presents the execution of an implementation followed by the formal definition of schedulability analysis. Lastly, it is shown that for schedulability- preserving implementation, if the implementation of the root program without refinement is schedulable, then the whole program (root program with refinement) is schedulable.

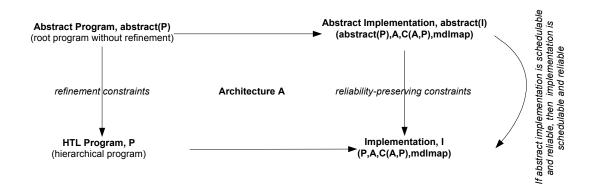

Chapter 7 discusses how to incorporate the LRC model into HTL and to perform reliability analysis. The formal definition of reliable HTL implementation is followed by reliability analysis. The chapter concludes with a discussion of how reliabilitypreserving refinement helps is avoiding repetitive reliability analysis.

Chapter 8 presents an HTL compiler for a virtual machine, the Embedded Machine. An overview of the Embedded Machine is followed by the algorithms for code generation from HTL to Embedded Machine code.

Chapter 9 presents HTL modeling and subsequent analysis of three controllers: a controller for three tank system, a steer-by-wire controller for automotive system, and a fly-by-wire controller for unmanned helicopter.

Chapter 10 compares the work with other programming languages including timed languages (Giotto and its successors), real-time extensions of conventional languages and languages for specialized real-time applications.

Chapter 11 concludes the thesis by reviewing the core concepts presented and possible future directions.

## Chapter 2

## **Programming Model**

The computation model is based on LET model of task execution. A brief overview of LET model from previous work is presented in Section 2.1 followed by a discussion on the extension of LET models used in this work.

The communication model in the framework is centered around communicators. A communicator [Ghosal et al., 2006a] is a typed variable that can be accessed (read from or written to) only at specific time instances. These time instances are periodic and specified through a communicator period. Communicators are used to exchange data between tasks. A task reads from certain instances of some communicators, computes a function, and updates certain instances of the same or other communicators. Communicators are also used to exchange data between tasks and environment. Input communicators are updated by physical sensors (possibly through drivers) and read by tasks. Output communicators are updated by tasks and read by physical actuators (possibly through drivers). Expressing LET with communicators is discussed in Section 2.3. Section 2.4 discusses the reliability model: the logical requirement and performance guarantee. Section 2.5 formally presents the reliability analysis for a set of periodic tasks. Section 2.6 extends the analyses for refinement.

# 2.1 Logical Execution Time Model

The Logical Execution Time (LET) model of task execution separates logical timing requirements from actual physical platform execution. A LET task is sequential code with its own memory space (henceforth referred as *local memory*) and without internal synchronization points. The logical specification consists of a set of program variables (henceforth referred as *input variables*) read by the task, a set of program variables (henceforth referred as *output variables*) updated by the task and timing constraints. The program variables are *global* i.e. they can be accessed by any other task; local memory of a task cannot be accessed by any other task. Logical timing constraints are specified by a release event and a termination event; the events are triggered by clock ticks or sensors interrupts. The release and termination events determine the LET of the task; the termination time strictly follows the release time. At release event, the task reads input variables to the local memory of the task. At termination event, the task updates program variables by the result of the computation (defined by the sequential code) on the state of local memory at the release event. The copying of program variable to local memory (and vice versa) is done synchronously i.e. in logical zero time. The task may not immediately start execution at release event. The underlying platform (or the scheduling strategy) determines when the task execution should start, get preempted and resumed. Between the release and termination event, the task may be preempted and resumed any number of times. Upon completion it may give out a completion event (if required by specification) and stores the value of the computation to local memory. At the termination event, the output variables are updated from the local memory.

A LET task is *time-safe* for a given host if the task completes execution on that host before the termination event occurs. A task, executing on a host (where no other task is executing), is time-safe if the *worst-case execution time* (WCET) is less than

Figure 2.1: LET model of task execution

the LET duration. For multiple tasks, this entails a detailed schedulability check. If tasks are race free (i.e. at any instance at most one task writes a program variable) and a program variable is written before it is read (at any update instance), then time-safe LET tasks are time and value deterministic, portable and composable [Henzinger and Kirsch, 2002].

The output variables of a LET task are updated when the termination event occurs, even if the task completes its physical execution earlier. The input variables are read to local memory when the release event occurs, and not when the task actually starts executing. As a consequence, a LET task always exhibits the same behavior in the value and time domain on different hosts as long as the task is time-safe. Fig. 2.2 shows LET task t and two possible physical executions of the task. Consider any instant in the execution (shown by the vertical dashed line): irrespective of the execution pattern, the values of output variables remain invariant. Fig. 2.3 shows two tasks t1 and t2 with identical LETs. Task t2 reads the output of t1. For the two possible physical execution pattern shown, the value of the output variable (written by t1) will be identical because output is not updated (and thus cannot be used by task t2) until the termination event. This makes the model value-deterministic.

Figure 2.2: Time determinism

Time-safe LET tasks are portable. Task t (Fig. 2.4) is ported to a host with half the speed than the original one without modification of the LET. Thus LET tasks can be ported to different hosts as long as they are time-safe; the bound on the scaling is determined by the host speed. The LET model also supports composition. Two LET tasks from two hosts, can be composed on a single host without modifying individual LET of the tasks (Fig. 2.5). Refer to [Matic and Henzinger, 2005] for detailed analysis of portability and composability of LET model.

Figure 2.4: Portability

Figure 2.5: Composability

# 2.2 Extension of LET Model

To account for distributed implementation, the LET model is extended to include both execution and transmission of output (Fig. 2.6). In particular, along with WCET of a task, *worst-case transmission time* (WCTT) for the communicating network is required to decide whether the task is time-safe or not.

Figure 2.6: Task execution and transmission

The LET model is also extended to account for failures of the input variables. Three models are considered:

- series if one of the input variables is not reliable the task fails to execute

- *parallel* if any one of the input variables is not reliable, then the task may execute (possibly with an pre-assigned value for the input variable); the task fails to execute if all of the input variables are unreliable

- *independent* if an input variable is unreliable, the task considers a pre-assigned value for that input variable; the task may execute even if all of the input variables are unreliable.

The LET model is extended to account for reliability of output program variables. A output variable may have an unreliable value if a task fails to execute and/or the memory fails to store the value of the variable. The task algorithms are assumed to be *correct* i.e., if a task executes reliably, then the task generates the desired output for given input. The model is formally discussed in Section 2.5.

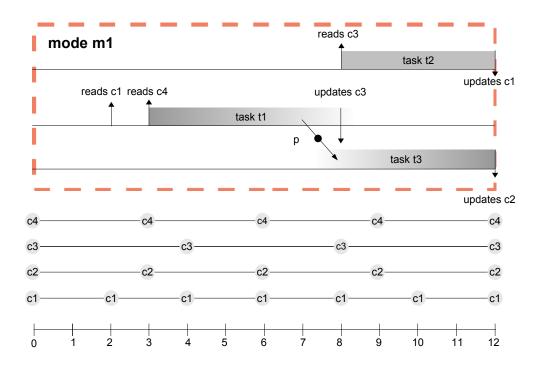

# 2.3 Communicators and Logical Execution Time

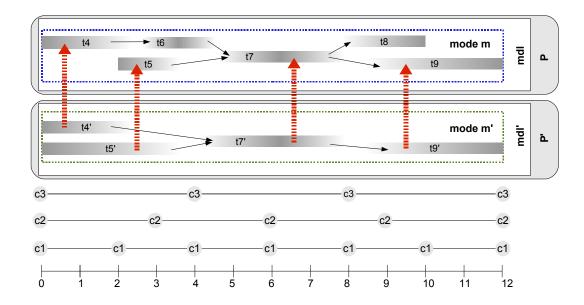

A task reads from certain instances of some communicators, computes a function, and updates certain instances of the same or other communicators. Fig. 2.7 shows the interaction between four communicators (c1, c2, c3, and c4 with periods 2, 3, 4 and 3 time units respectively) and three tasks (t1, t2 and t3). Task t1 reads the second instances of c1 and c4 and updates the fourth instance of c2. Task t2 reads the second instance of c3 and updates the sixth instance of c1 and the fifth instance of c2. Task t3 reads the sixth instance of c1 and updates the fifth instance of c4. The *latest read* and *earliest write* instances specify the LET for the tasks: the *latest* read instance determines the release time, and the earliest write instance determines the termination time. The task can read any communicators before the latest read time but cannot be released; similarly it must complete execution before the earliest communicator instance it writes to. Task t1 reads c1 at time 2 and stores the value in local memory; the task cannot be released at time 2 as it has not read all the inputs it needs to read. At time 3, the task reads c4; as all inputs have been read, the task is released for execution. Task t2 writes c1 and c2; as the update of c1 is earlier the task must complete execution by time 10. Thus LET of t1 spans from time 3 to time 9, the LET of t2 from time 4 to time 10, and the LET of t3 spans from time 10 to time 12. Note that the time unit is logical and has no physical significance. Only at implementation the time unit is bound to a clock, e.g., millisecond or second. For schedulability analysis, the communicator periods and execution time for tasks are assumed to be bound to the same clock.

Figure 2.7: Communicators and tasks

Communicators communicate between the environment and tasks (Fig. 2.8). The input communicators can only be written by the environment; i.e., values of input communicators are input from the environment. Typically an input communicator is updated by a physical sensor, possibly through drivers and read by a task. The output communicators can only be read by the environment, i.e., values of output communicators are output to the environment. Typically a task updates an output communicator, and a physical actuator reads the output communicator, possibly through a driver. Any other communicators can both be read and written by tasks.

Tasks define the input/output interface through communicators and thus communicators are the key to compose tasks. Task composition is deterministic i.e. given sufficient CPU speed for time-safety, the real-time behavior of the LET tasks is determined by the input (i.e., the values of all sensor communicator instances), independent of the host speed and utilization. The determinism in task composition is ensured in two ways. First, update races on communicators are prohibited i.e. different tasks

Figure 2.8: Communication via communicators

cannot write to the same instance of a communicator. Second, if a communicator update is due at any instance then the communicator is updated before it is read. The first is ensured by structural properties (e.g. task input and output) and the second is ensured by execution properties.

# 2.4 Logical Reliability Model

A communicator may have an unreliable value if a task fails to execute and/or the memory fails to store the value of the communicator. An application accessing the communicator must specify the tolerance of the unreliable values for the communicator: the tolerance is specified through *Logical (long-term) Reliability Constraint* (LRC). Each communicator has a specified LRC, where the LRC denotes the desired fraction of reliable values of the communicator that the system expects in the long-run. For example, if LRC for a communicator **c** is 0.9, then .9 fraction of all instances of communicator **c** on all execution (in the long-run) should have reliable values. Fig. 2.9 shows a sample execution trace with the value of communicator **c** at the first twenty instances. The communicator has type integer; an unreliable value is denoted by  $\perp$ . For the given trace, there are 20 instances of communicator **c** out of which 18 are reliable i.e. the fraction of reliable values is 18/20 = .9. If an implementation used the communicator **c**, then the above fraction must be .9 for all execution traces

in the long-run. It is assumed if a task fails to execute or memory fails to hold value,  $a \perp$  would be generated; i.e. any integer value (in the last example) is reliable.

Figure 2.9: Fraction of reliable values

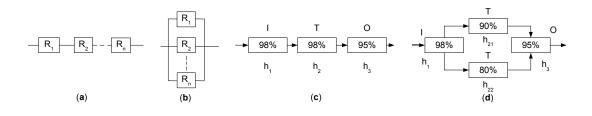

Similar to LRC, each communicator is associated with an Singular (short-term) Reliability Guarantee SRG, a fraction between 0 and 1. SRG=0.95 means the probability that a host fails during the execution of a task (writing to the communicator) is 0.05; i.e., given reliable inputs to a task executing on the host, the probability that the task writes  $\perp$  to the communicator is 0.05. Fig. 2.10 shows a task t which reads from an input communicator  $\mathbf{s}$  (with LRC=1) and writes to an output communicator a (with LRC=0.9) periodically. LRC=1 suggests that the sensor is 100% reliable. The task can only fail if the host on which it is implemented fails to execute. The task algorithm is assumed to be correct. Consider the task is implemented on a host h with reliability .95. There being no replication the SRG is also equal to .95. In other words for every iteration of task t, the probability that there is reliable output at a is at least 0.95. In this case, the LRC is satisfied by the SRG as SRG is greater than LRC; Section 2.5 presents the formal reasoning. In a different scenario if a host h' with reliability 0.8 is considered then the LRC is not satisfied (LRC > SRG). However if two replications of h' are available, then task t can be replicated on both the hosts. The new SRG =  $1 - (1 - .8)^2 = .96$  (probability that at least one host is reliable) which is greater than the required LRC. The SRG is computed by *reaction* block diagram (RBD) modeling. Refer Appendix A for details on RBDs. The hosts are assumed to be connected over a reliable broadcast network. Section 2.5 present the analysis for multiple inputs and different input failure models.

Figure 2.10: Intro to reliability analysis

Reliability analysis on the logical reliability model can be preserved over refinement. Fig. 2.11 shows two tasks t and t' where t' refines t. Both the tasks read from identical input and execute on same host. Task t writes to actuator a, while task t'writes to actuator a'. Let the host be reliable for t i.e. the SRG is no less than the LRC of a. If the LRC of a' is no more than the LRC of a, then host is also reliable for t'; the SRG cannot be less than the LRC of a' from mathematical comparison. Instead of repeating the reliability analysis, comparison of the LRCs of the outputs of the tasks concluded the reliability of the host to task t'.

Figure 2.11: Reliability preserving refinement

As discussed in Chapter 1, LRC and SRG is an approach to reliability analysis, as LET and WCET is an approach for timing analysis. The idea is based on separating requirements from guarantees. Timing requirements are expressed through release and termination events while performance guarantee (for an architecture) is expressed through WCETs. Release and termination events are application dependent "logical" information while WCETs are architecture dependent "physical" data. Similarly, LRC is application dependent "logical" information for desired reliability, while SRG is architecture dependent physical data on reliability that can be guaranteed. Timing analysis checks whether the "physical" data ensures the "logical" requirement for timing i.e. whether the LET is enough to ensure allocation for WCET time units. Similarly reliability analysis checks whether the "physical" data ensures the "logical" requirement for reliability i.e. whether the SRG is enough to ensure the LRC.

# 2.5 Reliability Analysis

The section presents the reliability analysis (based on the logical reliability model) for a set of periodic tasks running on a set of hosts connected over a broadcast network.

#### System

A system (S, A, I) consists of specification S, architecture A and implementation I. A specification S = (tset, cset) consists of a set of tasks tset and a set of communicators cset, where tasks and communicators are declared as follows.

A communicator declaration (c, type, init,  $\pi$ ,  $\mu$ ) consists of a communicator name c, data type type, an initial value init, an accessibility period  $\pi \in \mathbb{N}_{>0}$  and LRC  $\mu \in \mathbb{R}_{(0,1]}$ . All communicator names are unique i.e. if  $(c, \cdot, \cdot, \cdot, \cdot)$  and  $(c', \cdot, \cdot, \cdot, \cdot)$ are two distinct communicator declarations then  $c \neq c'$ . Given a communicator  $c \in \text{cnames}(P)$ , the type type[c] denotes the range of values the communicator can evaluate to and init[c]  $\in$  type[c] denotes the initial value of the communicator. The data type includes a special symbol  $\perp$  to indicate unreliable communicator value; a non- $\perp$  value indicates that the communicator has a reliable value. The evaluation of a communicator val[c] is a function that maps c to a value in type[c]. The period and LRC of a communicator c is denoted as  $\pi[c]$  and  $\mu[c]$  respectively. A task declaration (t, ins, outs, fn, fmodel, default) consists of a task name t, a list of inputs ins, a list of outputs outs, a function fn, an input failure model fmodel  $\in \{1, 2, 3\}$  and a list of default values default. All task names are unique i.e. if  $(t, \cdot, \cdot, \cdot, \cdot, \cdot)$  and  $(t', \cdot, \cdot, \cdot, \cdot, \cdot)$  are two distinct task declarations then  $t \neq t'$ . Given a task t, the inputs, outputs, function, fault model and default values are denoted as ins[t], outs[t], fn[t], fmodel[t] and default[t] respectively. An element of the input/output list is a pair (c, i) consisting of a communicator name  $c \in cset$  and a communicator instance number  $i \in \mathbb{N}_{\geq 0}$ . The *j*-th element of the input list is denoted as  $ins_j[t]$  where  $1 \leq j \leq |ins[t]|$ . The *k*-th element of the input list is denoted as  $outs_k[t]$  where  $1 \leq k \leq |outs[t]|$ . For a task t, the length of input list is |ins[t]| and the length of output list is |outs[t]|. If  $ins_j[t] = (c, \cdot)$ , then  $type(ins_j[t]) = type[c]$ ; similarly if  $outs_k[t] = (c', \cdot)$ , then  $type(outs_k[t]) = type[c']$ . If |ins[t]| = m and |outs[t]| = n, then the function fn[t] is, fn[t] :  $\Pi_{1\leq j\leq m}type(ins_j[t]) \to \Pi_{1\leq k\leq n}type(outs_k[t])$ . Let rcset[t] be the set of communicators read by task t.

The input failure model fmodel[t] denotes the action of a task if one or more inputs are unreliable; the list default[t] is a list of default values for the communicators in rcset[t]. The three failure models are:

- series (fmodel[t] = 1): if any one of the inputs fails, the task fails to execute

- parallel (fmodel[t] = 2) if an input is unreliable, the task may execute by using the default value of the communicator from the list default[t]. If all of the inputs are unreliable the task fails to execute.

- independent (fmodel[t] = 3) if an input is unreliable, the task uses the corresponding default value for that input from the list default[t]. The task may execute even if all inputs are unreliable.

For a task t, read time rtime[t] is the latest communicator instance t reads from and write time ttime[t] is the earliest communicator instance t writes to. Formally, rtime[t] =  $\max_j(\pi[c] \cdot i)$  where  $\operatorname{ins}_j[t] = (c, i)$  and  $\operatorname{ttime}[t] = \min_k(\pi[c'] \cdot i)$  where  $\operatorname{outs}_k[t] = (c', i)$ . The tasks repeat with periodicity  $\pi[S]$  where  $\pi[S] = \operatorname{lcm}(\operatorname{cset}) \cdot [(\max_{t \in tset} ttime[t])/(\operatorname{lcm}(\operatorname{cset})]$  and  $\operatorname{lcm}(\operatorname{cset})$  is the least common multiple of the communicator periods.

The restrictions on task declarations are as follows: (1) all tasks read from some communicators and write to some communicators, (2) for all tasks, read time is strictly earlier than the write time, (3) no two tasks write to the same communicator, and, (4) no task can write a communicator instance multiple times. In other words, a communicator can be written by at most one task at any instance, i.e., the specification is *race free*.

An architecture A is a tuple (hset, sset, C[S]) where hset is a set of hosts (connected over a reliable broadcast network), sset is a set of sensors and C[S] is a set of architectural constraints for a given specification  $S = (tset, \cdot)$ . The constraints are: (1) reliability of hosts and sensors specified by host reliability map hrel : hset  $\rightarrow \mathbb{R}_{(0,1]}$ , and sensor reliability map srel : sset  $\rightarrow \mathbb{R}_{(0,1]}$ ; and, (2) execution metrics for the tasks specified by worst-case-execution-time (WCET) map, wemap : tset  $\times$  hset  $\rightarrow \mathbb{N}_{>0}$  and worst-case-transmission-time (WCTT) map, wtmap : tset  $\times$  hset  $\rightarrow \mathbb{N}_{>0}$ .

The hosts are assumed to be *fail-silent* [Cristian, 1991] i.e. if a host fails, then it does not produce any *garbage* output. In other words, a host works correctly or stops functioning (becomes silent). If tasks are replicated on several fail silent hosts, then all faulty components do not produce any output while all working components produce identical output for a given cycle of computation. In [Baleani *et al.*, 2003], the authors argue that fail-silence can be achieved at reasonable cost. To keep the analysis simple, the broadcast network is assumed to be reliable. Non-reliability in broadcast network can be accounted in the model as long as the faulty behavior is *atomic* i.e. if the broadcast fails then none of the hosts receives any input. The WCTT is measured as the broadcast time for each task from each host. Memory is assumed to be 100% reliable.

Given a specification  $S = (tset, \cdot)$  and an architecture  $(hset, \cdot, \cdot)$ , an *implementation* I is a function from tasks to a set of hosts i.e. I :  $tset \rightarrow 2^{hset} \setminus \emptyset$ . The implementation is assumed to distributed i.e. there are multiple hosts and all tasks are not implemented on a single host. Tasks can also be replicated on multiple hosts. If a task t is mapped to multiple hosts then each host h executes a local copy of t; the local copy is referred as a *task replication* (t, h). All communicators c are replicated on all hosts h; each local copy of communicator is referred as a *communicator replication* (c, h). When a task replication completes execution, it broadcasts the output to all hosts (to update relevant communicator replications).

# Semantics

An execution of an implementation, also called an *implementation trace* (or simply *trace*), is a (possibly infinite) sequence of communicator values for every time instance. A *time instance* (or simply an instance) is a sequence of positive integers and denotes the harmonic fraction of all communicator periods. In practice, time instances are generated by the architecture through clock interrupts. We will assume the following. (1) Time instances are global i.e. synchronized across all hosts. (2) If a sensor **s** is replicated over multiple hosts, then the environment writes identical values to all replications of **s** when the update is due. (3) At any instance, if a communicator **c** is updated, then all replications of **c** are first updated and then read. The above constraint and exclusion of races ensure that all communicator replications have unique values when they are read. (4) When a task replication (**t**, **h**) completes execution, it broadcasts the output (to be written to a communicator **c**)

to all hosts  $hset/{h}$ . Every host receives the values from each replication of t and stores them in a local memory space (assigned to c). When update of c is due, voting is used to decide on the final value to be written to the communicator replication on the host. All tasks are functionally correct and given identical inputs provide identical outputs. All replications of a task have identical input failure models. At any given iteration, the replications of a task either generate  $\perp$  (unreliable execution) or the correct value. Thus if some replications generated a non- $\perp$  value then all other replications which executed reliably generated the identical non- $\perp$  value. This makes the voting straightforward. If there is at least one non- $\perp$  value, the communicator replication is assigned that value.

The semantics is formally defined as follows. For  $i \ge 0$ , let  $X_i$  be a function from the communicator set to the set of values, with possibly the empty set i.e.,  $X_i : \mathtt{cset} \to \mathtt{type}^{\mathtt{hset}} \cup \emptyset$ , where  $\mathtt{type} = \bigcup_{\mathtt{c} \in \mathtt{cset}} \mathtt{type}[\mathtt{c}]$ . If  $i \mod \pi_{\mathtt{c}} = 0$ , then  $X_i(\mathtt{c}) \in \mathtt{type}_{\mathtt{c}}^{\mathtt{hset}}$ , otherwise  $\emptyset$ . A trace is an infinite sequence  $(X_i)_{i\ge 0}$  of such functions. The semantics is the set of all possible traces.

## Reliability