# Synchronous Reactive Communication: Generalization, Implementation, and Optimization

**Guoqiang Wang**

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-178 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-178.html

December 19, 2008

Copyright 2008, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Synchronous Reactive Communication: Generalization, Implementation, and Optimization

by

### Guoqiang Wang

B.E. (Xi'an Jiaotong University, China) 1995

M.E. (Xi'an Jiaotong University, China) 1998

M.S. (University of California, Berkeley) 2007

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering Science - Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION  $\qquad \qquad \text{of the} \\ \text{UNIVERSITY OF CALIFORNIA, BERKELEY}$

Committee in charge:

Professor Alberto Sangiovanni-Vincentelli, Chair

Professor Robert K. Brayton

Professor Zuojun Shen

Fall 2008

|       | dissertation of Guoqiang wang is | s approved. |

|-------|----------------------------------|-------------|

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

| Chain |                                  | Date        |

| Chair |                                  | Date        |

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

|       |                                  | Dat         |

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

|       |                                  |             |

|       |                                  | D-4         |

|       |                                  | Dat         |

|       |                                  |             |

|       |                                  |             |

Fall 2008

University of California, Berkeley

# ${\bf Synchronous\ Reactive\ Communication:\ Generalization,\ Implementation,}$ and ${\bf Optimization}$

Copyright 2008

by

Guoqiang Wang

#### Abstract

Synchronous Reactive Communication: Generalization, Implementation, and Optimization

by

### Guoqiang Wang

Doctor of Philosophy in Engineering Science - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Alberto Sangiovanni-Vincentelli, Chair

A fundamental asset of a model-based development process is the capability of providing an automatic implementation of the model that preserves its semantics, and at the same time makes efficient use of the execution platform resources. Synchronous Reactive (SR) models are increasingly used in model-based design flows for the development of embedded control applications.

The implementation of communication links between functional blocks in an SR model requires buffering schemes and access procedures implemented at the kernel level. Platform-based design methodology is introduced to synthesize a real-time operating system when implementing SR models. Previous research has proposed two methods for sizing the communication buffer. This dissertation demonstrates how it is possible to improve on the

state of the art, providing not only tighter bounds by leveraging task timing information, but

also an approach that is capable of dealing with a more general model and implementation

platform configuration.

To achieve rigorous model semantics, this dissertation presents semantics pre-

serving implementations of SR communication for multi-rate systems on single processor

architectures. The implemented protocols define the assignment of indices of shared buffers

to writer and reader tasks at activation time, rather than at execution time. Two constant-

time portable solutions are developed in the C language and with the automotive OSEK

OS standard. Run-time complexity and memory requirements are discussed for the two

protocol implementations, and tradeoffs are analyzed. This dissertation completes the SR

model-based design flow by supporting automatic code generation for the double buffer

and the dynamic buffering protocols. To support software portability and reusability, the

ePICos18, compliant to the OSEK OS standard, is used. The generated code is validated

by emulation on the PIC18F452 microcontroller through the MPLAB IDE simulator.

An implementation of communication links with a minimum buffer size is often

desirable, but it may require a longer access time and it may also lead to the violation of

deadline constraints in real-time applications. This dissertation demonstrates the feasibility

of an MILP-based optimization approach that provides the minimum memory implementa-

tion of a set of communication channels within the deadline constraints of the tasks.

Professor Alberto Sangiovanni-Vincentelli

Dissertation Committee Chair

|  | • |

|--|---|

|  |   |

To My Daughter, My Wife, and My Parents.

## Contents

| Li       | st of        | Figures                                                 | $\mathbf{v}$ |

|----------|--------------|---------------------------------------------------------|--------------|

| Li       | ${f st}$ of  | Tables                                                  | vii          |

| Ι        | Ba           | ckground and Problem Statement                          | 1            |

| 1        | Intr         | roduction                                               | 2            |

|          | 1.1          | Embedded Systems and Design Methodology                 | 2            |

|          |              | 1.1.1 Embedded Systems                                  | 2            |

|          |              | 1.1.2 Design Methodology                                | 4            |

|          | 1.2          | Model-Based Design                                      | 9            |

|          |              | 1.2.1 Models of Computation                             | 10           |

|          |              | 1.2.2 Model Implementation Tools                        | 16           |

|          | 1.3          | Scheduling and Communication Mechanisms                 | 20           |

|          |              | 1.3.1 Scheduling Policies                               | 21           |

|          |              | 1.3.2 Communication Mechanisms                          | 24           |

|          | 1.4          | Goal of Dissertation                                    | 30           |

| <b>2</b> | Stat         | te of the Art and Problem Statement                     | 33           |

|          | 2.1          | State of the Art of SR Communication                    | 34           |

|          |              | 2.1.1 Synchronous Reactive Communication Semantics      | 34           |

|          |              | 2.1.2 Synchronous Reactive Communication Implementation | 35           |

|          | 2.2          | Problem Statement                                       | 42           |

|          |              | 2.2.1 Generalization, Implementation, and Optimization  | 43           |

|          |              | 2.2.2 Limitations of Current Solutions                  | 44           |

|          |              | 2.2.3 Motivation                                        | 45           |

|          |              |                                                         |              |

| Η        | $\mathbf{T}$ | heory Generalization, Implementation, and Optimization  | <b>47</b>    |

| 3        | Imp          | plementation Technology                                 | 48           |

|          | 3.1          | Platform-Based Design Methodology                       | 49           |

|   | 3.2 | 1 0 0                                                                  | 50<br>51   |

|---|-----|------------------------------------------------------------------------|------------|

|   |     |                                                                        | 52         |

|   | 3.3 |                                                                        | 54         |

|   | 3.3 | ,                                                                      | 54         |

|   |     |                                                                        | 56         |

|   |     |                                                                        | 59         |

|   | 3.4 | • 0                                                                    | 60         |

| 4 | The | eory Generalization and Bound Improvement                              | <b>62</b>  |

|   | 4.1 | Generalized One-to-Many Communication                                  | 63         |

|   |     | 4.1.1 SR Semantics under Arbitrary Link Delay                          | 63         |

|   |     | 4.1.2 One-to-Many Communication                                        | 65         |

|   | 4.2 | Generalized SR Communication Protocols                                 | 66         |

|   |     | 4.2.1 Generalized Dynamic Buffering Protocol                           | 68         |

|   |     | 4.2.2 Generalized Temporal Concurrency Control Protocol                | <b>7</b> 4 |

|   | 4.3 | Buffer Bound Based on Hybrid Scheme                                    | 78         |

|   |     | 4.3.1 Buffer Bound Improvement                                         | 78         |

|   |     | 4.3.2 Generalization Based on Hybrid Scheme                            | 80         |

|   |     | 4.3.3 Buffer Requirement Evaluation                                    | 82         |

| 5 | Por | •                                                                      | <b>89</b>  |

|   | 5.1 |                                                                        | 90         |

|   |     |                                                                        | 90         |

|   |     | 1                                                                      | 91         |

|   | 5.2 | <u>.</u>                                                               | 92         |

|   |     | 5.2.1 Dispatcher, Application, and Initialization Tasks                | 94         |

|   |     | 5.2.2 OIL Configuration File                                           | 07         |

|   | 5.3 | * *                                                                    | 06         |

|   |     | 5.3.1 Code Generation Environment                                      | 06         |

|   |     | 5.3.2 SR Communication Protocol Code Generation                        | 11         |

|   |     | 5.3.3 Code Validation Environment and Results                          | 21         |

| 6 | Buf | fer Sizing Optimization with Timing Constraints                        | <b>32</b>  |

|   | 6.1 | 0 1                                                                    | 33         |

|   |     | 6.1.1 Parameters, Variables, Cost Function, and Timing Constraints $1$ | 34         |

|   |     | 6.1.2 Complete Formulation                                             | 38         |

|   | 6.2 | ePICos18-Based Evaluation                                              | 40         |

|   |     | 6.2.1 Application Tasks and Dispatcher                                 | 41         |

|   |     | 6.2.2 Context Switch Latency of ePICos18                               | 42         |

|   | 6.3 | MILP Reformulation                                                     | 44         |

|   |     | 6.3.1 Ceiling and Minimum/Maximum Functions                            | 44         |

|   |     |                                                                        | 46         |

|   |     | 6.3.3 Complete MILP Formulation                                        | 48         |

|   | 6.4 | Experiments                                                            | 52         |

|     |              | 6.4.1<br>6.4.2              |      |      | • |      |      |  |  |  |  |  |  |  |  |            |

|-----|--------------|-----------------------------|------|------|---|------|------|--|--|--|--|--|--|--|--|------------|

| III | $\mathbf{S}$ | umma                        | ary  |      |   |      |      |  |  |  |  |  |  |  |  | <b>159</b> |

|     | 7.1          | clusion<br>Conclu<br>Future | usio | ns . |   | <br> | <br> |  |  |  |  |  |  |  |  |            |

| Bil | bliog        | raphy                       | ·    |      |   |      |      |  |  |  |  |  |  |  |  | 165        |

# List of Figures

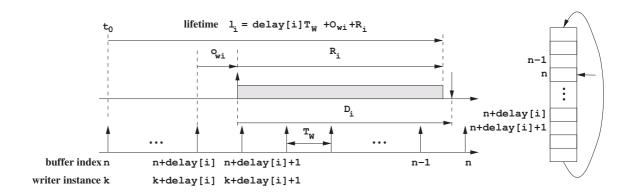

| 2.1  | How Preemption May Change Values Read by Reader Tasks                    | 36  |

|------|--------------------------------------------------------------------------|-----|

| 2.2  | The Double Buffer Mechanism                                              | 37  |

| 2.3  | The Dynamic Buffering Mechanism                                          | 39  |

| 3.1  | Platform-Based Design for RTOS                                           | 51  |

| 3.2  | The Complete Design Flow                                                 | 61  |

| 4.1  | A General Scenario: Tasks with Link Delays and Priority Levels           | 66  |

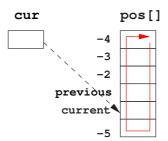

| 4.2  | Data Structures for Writer Side                                          | 68  |

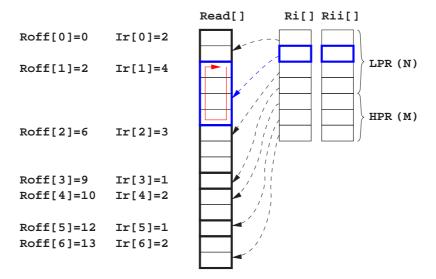

| 4.3  | Data Structures for Reader Side $(D > T)$                                | 69  |

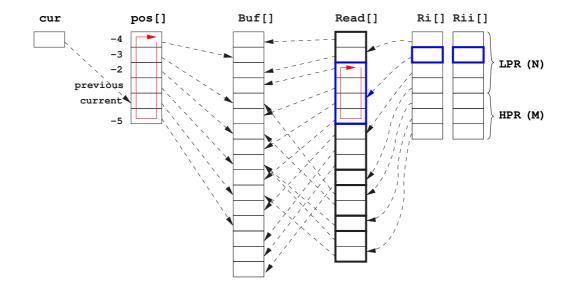

| 4.4  | Communication Scheme Based on Spatially-out-of-Order Writes              | 70  |

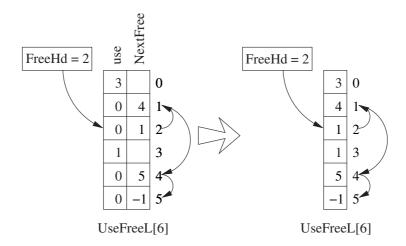

| 4.5  | A Use Free List Data Structure                                           | 72  |

| 4.6  | Data Structures and Supporting Routines for the Generalized CTDBP        | 73  |

| 4.7  | Writer/Reader Code for the Generalized CTDBP                             | 73  |

| 4.8  | Communication Scheme Based on Spatially-in-Order Writes                  | 75  |

| 4.9  | Data Structures and Supporting Routines for the Generalized TCCP         | 77  |

| 4.10 | Writer/Reader Code for the Generalized TCCP                              | 77  |

| 5.1  | Data Structures and Supporting Routines for CTDBP $(D \le T)$            | 91  |

| 5.2  | Writer/Reader Code for CTDBP $(D \le T) \dots \dots \dots$               | 91  |

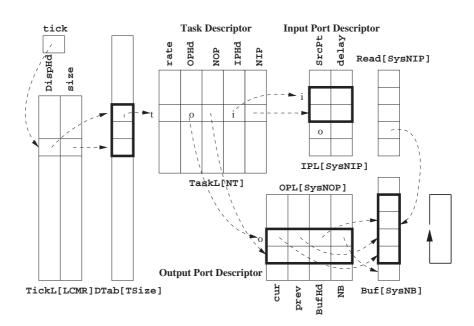

| 5.3  | Data Structures and Supporting Routines for TCCP $(D \le T) \dots \dots$ | 92  |

| 5.4  | Writer/Reader Code for TCCP $(D \le T)$                                  | 92  |

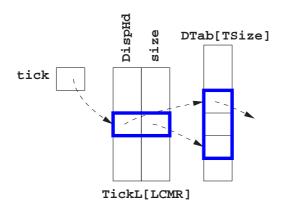

| 5.5  | Task Dispatcher Data Structures                                          | 95  |

| 5.6  | Declaration, Initialization, and Implementation of Task Dispatcher       | 96  |

| 5.7  | Alternative Implementation of Task Dispatcher                            | 97  |

| 5.8  | Common Data Structure Declaration                                        | 97  |

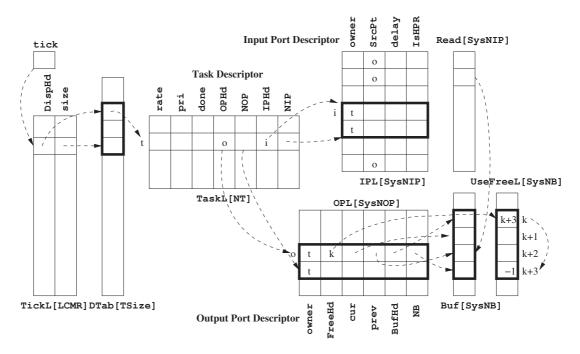

| 5.9  | Data Structures of System Implementation with CTDBP                      | 98  |

| 5.10 | Data Structure Declaration and Initialization for CTDBP                  | 99  |

| 5.11 | Implementation of CTDBP                                                  | 100 |

| 5.12 | OSEK Implementation of Application Task with CTDBP                       | 101 |

| 5.13 | Achieve Atomicity of Termination Code via Dispatcher                     | 102 |

| 5.14 | Data Structures of System Implementation with TCCP                       | 103 |

| 5.15 | Data Structure Declaration and Initialization for TCCP           | $10^{4}$ |

|------|------------------------------------------------------------------|----------|

| 5.16 | Implementation of TCCP                                           | 104      |

| 5.17 | OSEK Implementation of Application Task with TCCP                | 105      |

| 5.18 | General Structure of Task Init                                   | 106      |

| 5.19 | OIL Configuration File                                           | 107      |

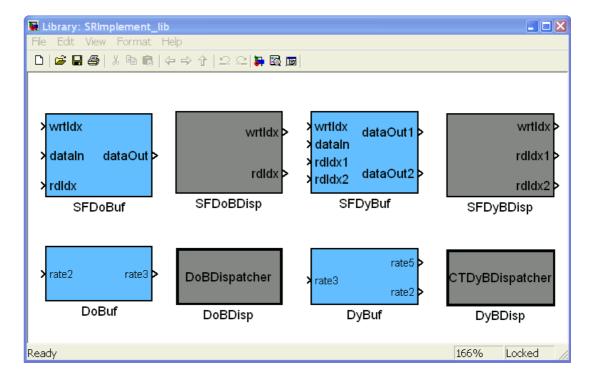

| 5.20 | SR Communication Implementation Library Blocks                   | 113      |

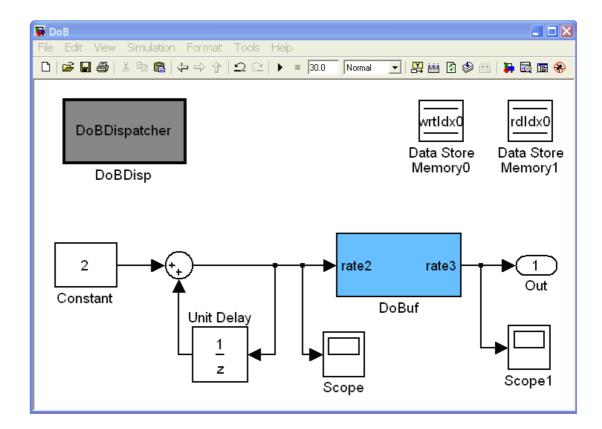

| 5.21 | Example of the Double Buffer Mechanism                           | 117      |

| 5.22 | Code of the DoB Task Dispatcher                                  | 118      |

| 5.23 | Code of the DoB Task init                                        | 119      |

| 5.24 | Code of Application Task SubRate_2                               | 119      |

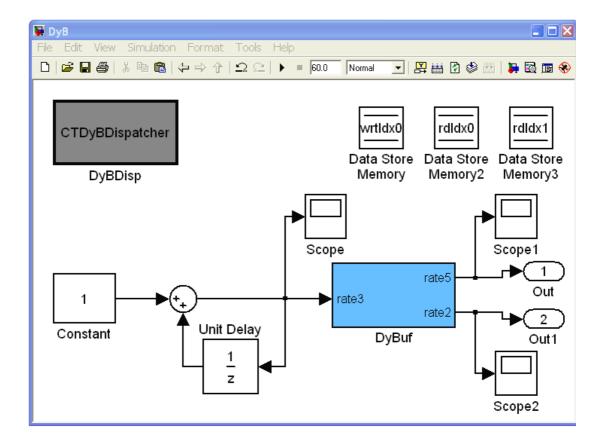

| 5.25 | Example of the Dynamic Buffering Mechanism                       | 120      |

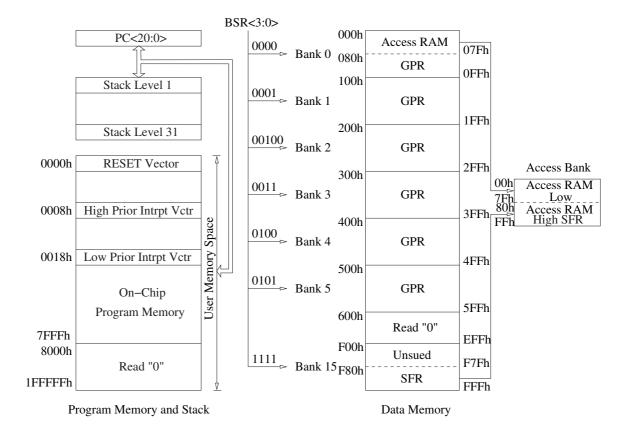

| 5.26 | Memory Layout of the PIC18F452 Microcontroller                   | 123      |

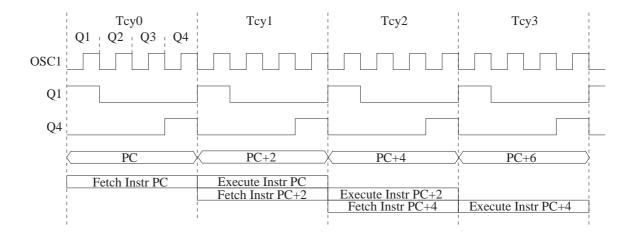

|      | Instruction Pipeline of the PIC18F452 Microcontroller            | 124      |

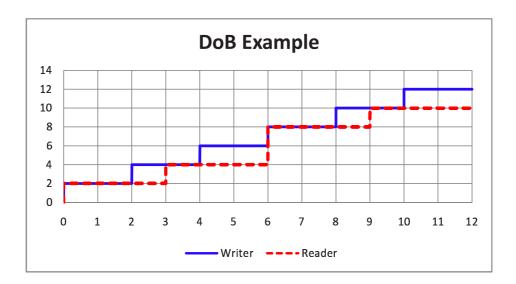

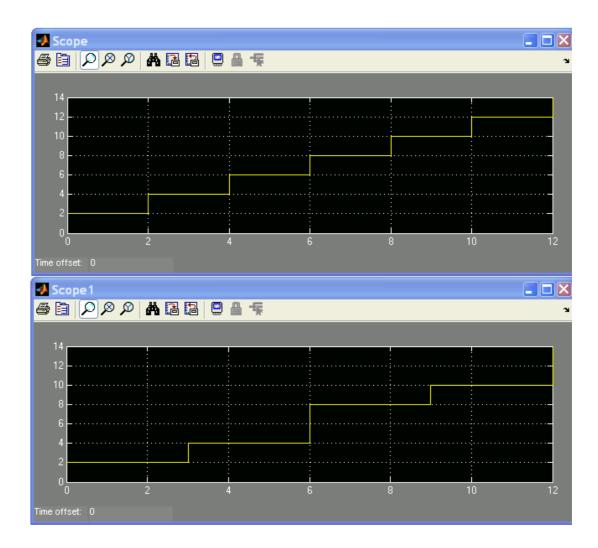

|      | MPLAB SIM Result of the DoB Example                              | 127      |

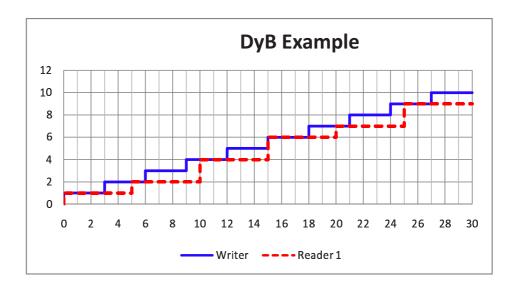

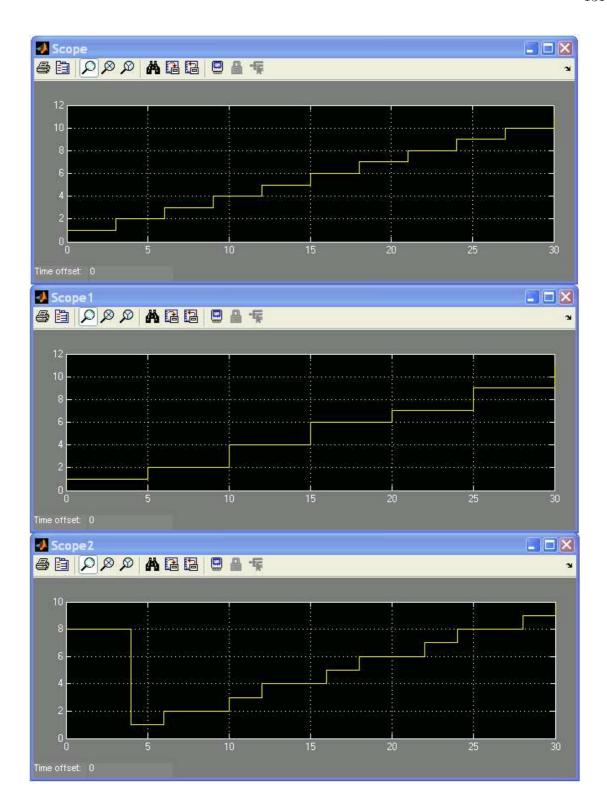

| 5.29 | MPLAB SIM Result of the DyB Example (1)                          | 128      |

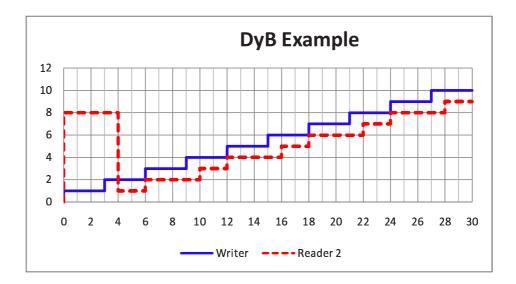

| 5.30 | MPLAB SIM Result of the DyB Example (2)                          | 128      |

|      | RTW SIM Result of the DoB Example                                | 130      |

| 5.32 | RTW SIM Result of the DyB Example                                | 131      |

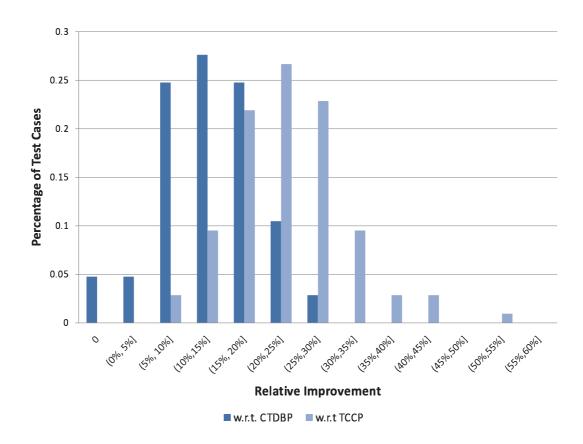

| 6.1  | Systems with a Smaller Buffer Size under CTDBP                   | 153      |

| 6.2  | Systems with a Smaller Buffer Size under TCCP                    | 154      |

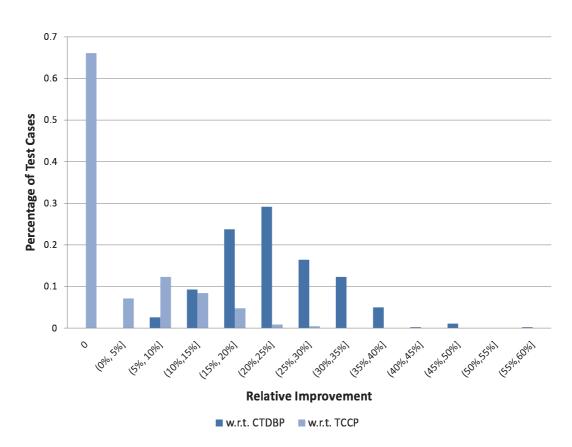

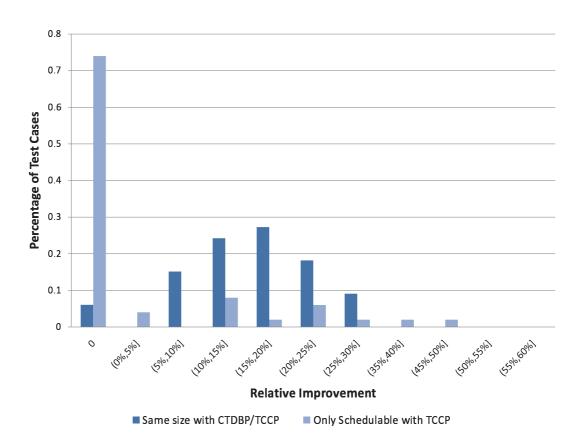

| 6.3  | Systems with an Equal Buffer Size or Those only TCCP-Schedulable | 155      |

| 0.0  | Systems with an Equal Bullet Size of Those only 1001 Schedulasie | 100      |

## List of Tables

| 3.1 | Minimum Requirements for OSEK CC                                                           |

|-----|--------------------------------------------------------------------------------------------|

| 3.2 | Summary of the OSEK OS Standard                                                            |

| 3.3 | OIL Objects and Their Properties                                                           |

| 4.1 | An Example of Single-Writer Multiple-Reader Configuration $(R \le T)$ 67                   |

| 4.2 | An Example of Single-Writer Multiple-Reader Configuration $(R \le T \text{ or } R > T)$ 83 |

| 4.3 | An Example Derived from an Automotive Industrial Application 85                            |

| 4.4 | Experimental Results of the Automotive Example                                             |

| 5.1 | Notations Used to Describe a System                                                        |

| 5.2 | Memory Requirement for System Implementation with CTDBP 103                                |

| 5.3 | Memory Requirement for System Implementation with TCCP 105                                 |

| 5.4 | Features of the PIC18F452 Microcontroller                                                  |

| 6.1 | Application Task Overhead Comparison (in ICs)                                              |

| 6.2 | Dispatcher Performance Evaluation (in ICs)                                                 |

| 6.3 | Cost of Context Switches from Clock Interrupt (in ICs)                                     |

| 6.4 | Cost of Context Switches from a Task (in ICs, assume $\pi_1 > \pi_1$ ) 144                 |

| 6.5 | Experimental Results of Case Study II                                                      |

### Acknowledgments

At the very first, I would like to thank my parents for bringing me up and affording steadfast support for my study. They have been providing considerable opportunities for me to pursue my dreams. Without their eternal love, long-term spiritual as well as financial supports, and great encouragement, I would not be able to complete my advanced studies.

I would like to express my greatest gratitude to my advisor, Professor Alberto Sangiovanni-Vincentelli, who guided me into the field of Electrical Engineering and Computer Sciences and offered me this invaluable opportunity to learn interdisciplinary expertise. I would possibly fail to accomplish what I have achieved without his generous support and guidance.

I am deeply indebted to Professor Robert K. Brayton. Bob served on my dissertation committee and was the Chair of my qualifying examination committee. He is always willing to discuss with me. Bob led me into the area of sequential synthesis and offered me an opportunity to collaborate. Besides, he shared his views on being a prominent researcher in academia and industry.

I wish to express my sincere appreciation to Professor Zuojun Max Shen from IEOR and Professor Sanjit A. Seshia for serving on my qualifying examination committee.

In addition, Max was also on my dissertation committee.

Special gratitude extends to Professor Marco Di Natale from Scuola Superiore Sant'Anna, Pisa, Italy. Marco helped with defining and mentoring my dissertation project. He shared a wealth of hands-on experiences on being an eminent researcher in general.

I have furthermore to thank Professor Andreas Kuehlmann. Andreas guided me

into the area of logic synthesis and verification. Afterwards he provided me an opportunity for research collaboration and mentored my project on symmetry detection.

I am highly thankful to Professor Randy H. Katz. Randy was of great help for reading my master's degree thesis and offering comments on experimental setup for performance analysis. He taught me my very first lesson in digital system design.

I am very much obliged to Professor Edward A. Lee for bringing me to the palace of the models of computation. Knowledge on computation models provided me a solid theoretical foundation and facilitated my dissertation project. I was honored to be hooded by Edward.

I owe special thanks to Dr. Alex Kondratyev and Dr. Yosinori Watanabe from Cadence Research Labs for exposing me to hardware scheduling and behavioral synthesis as well as mentoring my research project.

Sincere thanks are also due to Professors James Demmel, Anthony D. Joseph, Richard M. Karp, George Necula, Christos Papadimitriou, and Pravin Varaiya for spending time uncovering my confusion.

I would also like to say thanks a lot to Ms. Ruth Gjerde and Ms. La Shana Porlaris for taking good care of the graduate students in the Department. They have really done a great logistics job for us.

I wish to extend my thanks to GSRC and CHESS for their sponsorship of my research projects. During the period of my study at Berkeley, I also received enormous help from friends as well as colleagues and staff members in the DOP Center and the BWRC. I genuinely appreciate this great environment and thank them for their help and support.

I am deeply grateful to my wife, Jia Yang, for her patient love and careful consideration for the family. She has been taking more responsibility on raising our daughter, Hannah. Meanwhile, she has been doing most of the housework. This enabled me to fully concentrate on my research work. I also want to express my gratitude to Hannah for the few time I spent with her. Fortunately, both my parents and my parents-in-law offered tremendous help with raising Hannah, which made it possible for Jia and I to attend graduate school. I greatly appreciate their help.

For all those who helped me in one way or another, may God Bless you!

### Part I

# Background and Problem

Statement

### Chapter 1

### Introduction

### 1.1 Embedded Systems and Design Methodology

In this section, embedded computing is first introduced with examples and its common characteristics are described. Then embedded system design requirements and challenges are presented. Finally, to cope with the challenges, system-level design methodology, the enabler of ubiquitous computing, is discussed in details.

### 1.1.1 Embedded Systems

Since the first computer was invented in 1930s, it has been experiencing significant development: programmable computers, personal computers, workstations, laptop computers, etc, all of which share the same common characteristics: general-purpose computing. Another type of computation, called embedded computing, abounds in people's daily life. Any computing systems other than a computer can be considered as an embedded system. Nowadays, in electronic industry, there are more embedded system products in the mar-

ket than personal computer products. According to ERCIM news [110], more than 98% of processors applied in 2003 are in embedded systems. This explicitly indicates that it has already been in the post-PC era. There are many applications for embedded systems and they mainly fall into two categories, depending whether or not they are safety-critical. Typical examples of safety-critical embedded systems include transportation systems (e.g., aircrafts, automobiles, and railways), military systems (e.g., missiles and radars), medical diagnostic systems (e.g., robotic surgeons), identity checking equipments (e.g., fingerprint identifiers, card-key readers), etc. The other category is very broad: examples used for communication include bluetooth devices, cell phones, fax machines, modems, pagers, routers, etc; examples used for entertainment include camcorders, cameras, CD players, DVD players, MP3 players, radios, set-top boxes, stereo systems, televisions, VCRs, etc; examples of office use are printers, scanners, etc; examples for kitchen use are dishwashers, microwaves, etc.

Unlike general-purpose computers, embedded systems share the following common characteristics. They usually function for a particular purpose only and are based on programmable components such as microcontrollers and Digital Signal Processors (DSP). Embedded systems usually do not have direct interaction or control from end users. However, they engage the physical world via directly interacting with sensors and actuators. Reactive embedded real-time systems react to changes in the external environment usually through performing computation based on data from sensors and producing results to control actuators in a timely manner. Ideally, the close interaction with the environment never terminates. The wide range of examples of embedded systems listed above reveals that there

exist both small and large scale systems in the embedded application arena. Embedded system functionality is very heterogeneous. They may need to meet stringent constraints such as time, power, and weight/size as well as have a higher level of dependability such as reliability, robustness, fault-tolerance, and availability.

Embedded systems are usually implemented as Systems-On-a-Chip (SOC). Designing embedded electronic products is a complex process, which involves modeling, implementation, testing, and manufacturing. Functionality of most embedded systems is mapped into both hardware and software. However, embedded systems are increasingly more software driven and functionality has steadily shifted from hardware to software, i.e., more and more functionalities are achieved via embedded software [67].

Ubiquitous embedded computing has been demanded by accident-free automotive, free and safe aerospace, continuously seamless connectivity, etc. This pervasive computing demand has been enabled by new technologies, intelligent sensors/actuators, new methodologies for embedded system design. Among these enablers, design methodologies are particularly important, which are the focus of the next subsection.

#### 1.1.2 Design Methodology

Steadily increasing networked embedded devices are usually small, mobile, adaptable, and configurable. They need to provide strong guarantees of availability and performance. Demands for more elaborate application functionalities further increase embedded software complexity. Development efforts increase greatly due to the rising design complexity. The dynamics of electronic system market demands for shorter and shorter development time. Synchronization, concurrency, and heterogeneity are the essential aspects of reactive

embedded systems. Among them, heterogeneity is the fundamental problem that embedded system designers have to face. Composition of essential properties such as safety and liveness is the key to characterize heterogeneous systems. It is essential for the system designers to be able to specify, manage, and verify the functionality and performance of concurrent behavior.

There exist multiple design metrics [117]: unit manufacturing cost, Non-Recurring Engineering (NRE) cost (the one-time cost of designing the system, e.g., from tooling of systems), physical size, performance (latency and throughput), power consumption, flexibility for functionality adaption, time-to-market (if outside of the market window, the revenues may drop dramatically), system maintainability, etc. The biggest challenge for embedded system design is to simultaneously optimize numerous design metrics. This may be very difficult because some of the metrics compete against each other. Therefore, in practice, the goal of electronic embedded system design is to balance costs from development time as well as product performance and functionality.

Key embedded system technologies are discussed in [117]. There are three types of architectures of the computing engine used to perform system functionality: general-purpose, application-specific, and single-purpose. Unlike single-purpose processors, general-purpose and application-specific processors have program memory. Designs with general-purpose processors may achieve low time-to-market, low NRE cost, and high flexibility while designs with application-specific and single-purpose processors are featured with good performance, small size, and low power. Application Specific Instruction Set Processors (ASIP) [103][42] are a cost-effective design style due to the flexible support for cost or

power reduction and the increased functionality complexity in newer generations of design. Similarly, there are three types of Integrated Circuit (IC) technologies to support embedded hardware: full-custom, semi-custom, and programmable logic device (e.g., Field-Programmable Gate Array (FPGA)). From full-custom to programmable logic, performance, time-to-market, and NRE cost decrease while size and power consumption increase.

Embedded system manufacturing cost, area, power consumption, and weight mainly depend on its hardware components while functional correctness and timeliness are mostly dependant upon its software components. Embedded software is hard to design [67] because it requires domain-specific expertise. It is important to deliver low-cost and efficient implementations in both hardware and software.

Traditional design methods are usually based on Register Transfer Level (RTL) Hardware Description Languages (HDL) or programming languages such as C/assembly. There are problems with past electronic design methods: e.g., lack of unified hardware-software representation which makes specification revision difficult; partitions into hardware and software are defined a priori so that it cannot verify the entire system and is difficult to find incompatibilities across the hardware-software boundary; lack of well-defined design flow which leads to a time-to-market problem. On the other hand, traditional general software development techniques cannot be directly applied for embedded software design due to the poor product quality, long development time, and low development productivity. In addition, monolithic execution platform dependent implementations are unfriendly to port, upgrade, or customize, thus they have limited chances for reuse. Furthermore, traditional design methodology cannot model concurrency due to the lack of enabling semantic

constructs.

With more and more design challenges emerging, the winning strategies for embedded system design are design methodology, testing, and automation. The next generation of tool chain for modeling, design, validation, and implementation should be capable of producing embedded hardware/software systems that are cost-efficient, performance-optimal, ultra-stable, and highly dependable with reduced time-to-market.

To accomplish these, it may require knowledge from multi-disciplines. Verification and validation of system properties and functionality to meet design constraints should be supported as early as possible during the development process. To effectively reduce the cost and development time, design reuse in all shapes and forms should be well supported. A system-level design approach is the key for successful development of hardware and software products characterized as real-time, distributed, parallel, and reactive. Electronic System-Level (ESL) [43] design methodology starts with a high level of abstraction. Moving to a higher level of abstraction makes designs in hardware and software indistinguishable so that it enables to take best advantage of design freedom and prevents errors from the interaction between software and hardware designs. Hence, it may effectively reduce design time. This technique has been successfully used several times [39]: design methodology from simulationbased at transistor level (prior to early 1980s) to simulation-based at gate level (in 1980s), and then to synthesis-based at register-transfer level (between late 1980s and late 1990s). Finally, it comes to refinement-based design methodology at system level (from early 2000s). It is important for system-level design methodology to separate/orthogonalize concerns [60], for example, to separate the various design aspects: functionality versus architecture and computation versus communication. This enables more effective exploration of alternative solutions, better design complexity management, and component reuse.

Embedded real-time software design must take into consideration of the laws of physics to control the environment. The design framework should have properties that better match the application domain and define a model of computation that governs the interaction of components. The requirements for embedded software development tools are compilation retargetability, multilevel simulation, source-level debugging tool with links to In-Circuit Emulation (ICE), and computer-aided exploration of processor architectures.

To cope with the increasing SOC design complexity, increased system design productivity, as well as decreased time-to-market, system-level methodology is the key. System-level design methodologies have already be around for about a decade. Fundamentals with object-oriented design methods for development of formal executable models at system level are discussed in [118]. The synthesis/refinement-based ESL approach is the most appealing because it reduces the risk of making mistakes and uses powerful optimization techniques to reduce cost (e.g., power, performance, and area) and time of designs, and verifies designs a lot faster than traditional methodologies. System-level design languages [32] may reduce the semantics gap between system-level specifications and Intellectual Property (IP) level implementation decisions.

System-level hardware/software co-design provides a unified design environment. It consists of three parts at four different abstraction levels. To support reuse, an IP library incorporates pre-designed implementations of hardware/software/operating systems, cores, RT components, and gate cells at the system, behavioral, register, and gate levels, respec-

tively. Synthesis/compilation tools (system synthesis, behavior synthesis, RT synthesis, and logic synthesis) automatically explore the design space and insert low level implementation details in the best way with respect to design constraints. Verification tools (model checking, hardware/software co-simulator, HDL simulator, and gate simulator) ensure correctness at each level.

Basic principles on system-level methodology are presented in [39]. A system-level design methodology starts with a well-defined executable specification model that serves as the golden reference. The most important for functional specification is the underlying mathematical model of computation. Well-defined (clear/unambiguous) formal mathematical model semantics for system-level methodology may bridge the gap between system specification and implementation. Models should be abstract enough and defined at each level of abstraction. Model refinements from high to low level give the best implementation. Model equivalence based on simulation semantics specifies that two models are equivalent if they have the same simulation result. The behavior of a correct implementation should be consistent with that of the abstract model. Details about model-based design are presented in next section.

### 1.2 Model-Based Design

In this section, model-based design, a particular instance of system-level design methodology is discussed. First of all, commonly used models of computation are introduced, and then some representative model implementation tools are presented.

### 1.2.1 Models of Computation

Model-based development of embedded real-time software aims at improving quality by enabling design-time verification as well as simulation and fostering reuse. This subsection introduces those commonly used models of computation. There are excellent academic articles for each of them. In addition, there are great courses offered in universities addressing models of computation. Two typical examples are EE249 [97] and EE290N [98], which are graduate-level classes offered at the University of California, Berkeley.

Models of computation provide a high level of abstraction for behavioral design. They need to be expressive, general, simple, compilable/synthesizable, and verifiable. A model of computation is a framework in which to express what sequence of actions must be taken to complete a computation, e.g., Finite State Machine, Turing machine, continuous time models (differential equation), etc. There exist many different models of computation and different models signify different properties. Turing-complete models might be too powerful and some properties may be undecidable. A good model of computation needs to be powerful enough for the application domain and has appropriate synthesis and validation algorithms. The model of a design needs to have a precise, unambiguous semantics. Models of computation provide a formal framework for reasoning about certain aspects/properties of an object in embedded systems. In the following, commonly used models of computation are briefly discussed. Note that the following list is never attempted to be complete.

**Process Networks** Process Networks (PN) are a model of computation that is based on asynchronous message passing, where the writer does not need to wait for the reader to be ready for communication. The blocking read and non-blocking write mechanism

guarantees the model determinacy. Under the blocking read mechanism, processes cannot test input queues for emptiness. Typical examples of process networks are the Kahn's process networks [57][58], where First-In-First-Out (FIFO) queues with an infinite capacity are used to model communication between processes. Process networks are Turing-complete. It is very expressive but key system properties such as deadlock and memory boundedness are undecidable.

Finite State Machine The Finite State Machine (FSM) model of computation is like a graphical language. It consists of states and transitions of a system. In terms of reactiveness, FSMs can be categorized as either Moore or Mealy machine, while in terms of communication mechanism, FSMs can be either synchronous or asynchronous. There exist powerful algorithms for software/hardware synthesis and verification. However, FSM models may have problems such as over-specification of implementation, incompact specification of numerical computation, and state explosion. To solve these problems, FSMs can be used together with other models of computation. A representative example is the Statecharts formalism [46], which extends conventional FSMs to have an instantaneous broadcast synchronous communication mechanism. Another example is the Codesign Finite State Machine (CFSM) model of computation [8]. A CFSM is an FSM extended with the support for data handling and asynchronous communication. In CFSM models, synchronicity (zero and infinite time) and asynchronicity (non-zero, finite, and bounded time) are combined in a globally-asynchronous and locally-synchronous way. A CFSM model preserves formality and efficiency in implementation.

Synchronous Reactive In the Synchronous Reactive (SR) [11] model of computation, time is abstracted as global discrete ticks. All events in an SR model are synchronized with ticks, i.e., computation is triggered by a global clock. Conceptually, an SR system takes zero time to react to events, i.e., computation is simultaneous and instantaneous, which is the underlying synchrony assumption. Unlike discrete time discussed later, a signal in an SR model does not need to have a value at every clock tick. Based on the SR model of computation, synchronous languages have been designed: Esterel [14][13], Lustre [45][19], Signal [64][44], Statecharts [46]. SR models have strong formal properties and many key questions are decidable. One of the nice properties is that buffer memory is bounded. The fixed point semantics of the SR model of computation only addresses the behavior at a clock tick. The behavior across clock ticks requires a clock calculus [96]. SR models are suitable for designing applications with concurrent and complex control algorithms.

Discrete Event The Discrete Event (DE) model of computation has an explicit notion of global time and communication is based on events consisting of a pair of value and time stamp. Typical examples that use DE are HDLs: Verilog [114] and VHDL [95]. In DE models, a global event queue is usually maintained according to the event stamps, which unfortunately leads to tight coordination. The discrete event semantics needs to deal with simultaneous events and Zeno conditions. Simultaneous events lead to a nondeterministic behavior and some simulators use delta delay to prevent nondeterminacy. For example, in Verilog, simultaneous events are handled nondeterministically while in VHDL, the notion of delta time is introduced to separate a sequence of two simultaneous distinct events so that they can be processed deterministically. A Zeno condition means that there may be

an infinite number of time stamps between two finite time stamps. In [66], it is shown that delta-causality guarantees the absence of Zeno conditions. The problem with DE models is that it may be difficult to maintain a globally consistent notion of time. To solve this problem, distributed discrete event modeling is presented in [88].

Dataflow The seminal work on Dataflow (DF) is the computation graphs given by Karp and Miller [59]. As a special case of the process networks, the dataflow model of computation [69] is based on asynchronous message passing. A dataflow network is a collection of functional nodes (commonly called actors) connected over unbounded FIFO queues. Stateless actors perform computation while unbounded FIFOs perform communication via sequences of tokens carrying values. A unique output sequence corresponds to a unique input sequence. At each time, one actor is fired. During firing, actors consume input tokens and produce output tokens. Actors can be fired only if there are enough tokens in the input queues. The key property of DF networks is that output sequences do not depend on the time of firing of actors. There are variant types of dataflow networks. Static dataflow procedure language is discussed in [30]. Synchronous (or better Static Schedulable) Dataflow (SDF) [68] [92] networks can be statically scheduled by solving the balance equations at compile time. In SDF models, an actor is executed when it is known to be fireable. There is no overhead due to the sequencing of concurrency and buffers can be sized statically. In Dynamic Dataflow (DDF) [3] models, firings are scheduled only at run time. In Boolean Dataflow (BDF) [15] and Integer Dataflow (IDF) [16] models, balance equations involving unknown production/consumption rates are solved symbolically so that data-dependent routing of tokens is supported. For all DDF, BDF, and IDF models, deadlock, memory

boundedness, and scheduling are undecidable. In summary, dataflow networks are a powerful formalism for specifying data-dominated systems. They are a partially-ordered model (no over-specification) and their execution is deterministic (independent of scheduling). DF models have explicit concurrency and may be used for simulation, scheduling, memory allocation, and code generation for digital signal processors. Similar to a graphical language, DF networks are easy to use. There exist powerful verification and synthesis algorithms. But efficient synthesis is only for restricted models and a DF model cannot describe reactive control due to blocking read.

Petri Nets Petri Nets (PN) are named after Dr. Carl Adam Petri, in honor of his pioneer work in communication with automata. As an asynchronous model, Petri nets [91] explicitly and graphically describe sequencing/causality, conflict/nondeterministic choice, and concurrency. Petri nets have nice properties: the behaviors are dependent upon the initial marking; the reachability problem with Petri nets is decidable; the behavioral property of boundedness implies that the number of tokens in any place cannot grow indefinitely; the liveness property signifies that any transition can become fireable from any marking; the conservation property means that the total number of tokens in the net is constant. Petri nets are added with the time notion in [56] to satisfy the timing constraints of communication protocol architectures for reliable conversion functions.

Continuous Time In the Continuous Time (CT) model of computation [74], communication is via continuous time signals that depend on the real numbers. A continuous time model describes Ordinary Differential Equations (ODE) and differential algebraic equa-

tions, which govern the operation of physical systems, e.g., analog circuits, chemical reaction processes, mechanical systems, etc. The ODEs may be solved by different numerical schemes such as the Trapezoidal Method, the Forward/Backward Euler Solver, the Runge-Kutta Solvers, etc.

Discrete Time Discrete Time (DT) [37] is an extension of the synchronous dataflow model of computation. It is very similar to the synchronous reactive model of computation with the exception that every signal has a value at every clock tick. On top of the desirable properties that synchronous dataflow models have, the DT model of computation is temporally causal, which requires that the outputs depending on the inputs are never produced before the time of the inputs.

Communicating Sequential Processes Hoare's Communicating Sequential Process (CSP) [50] is a rendezvous model, where concurrent processes communicate via the so-called rendezvous, a synchronous message passing mechanism. Between two communicating processes, the one that reaches the rendezvous communication point earlier will need to stall to synchronize with the other process.

Calculus of Concurrent Systems Similar to Hoare's Communicating Sequential Processes, Milner's Calculus of Concurrent Systems (CCS) [87] is another model of computation that is based on rendezvous.

Giotto The Giotto [47] model of computation defines a time-triggered programming language for implementing embedded control systems of hard real-time type. In a Giotto

model, all software tasks are periodically invoked according to their respective sampling periods. Together with the FSM model of computation, Giotto is useful for implementing model models.

The Tagged Signal Model The tagged signal model [70] provides a very general conceptual framework for comparing and reasoning about models of computation. It provides a natural model for design refinement, which offers the possibility of type-system-like formal structures that deal with dynamic behavior in addition to static structures. The tagged signal model provides a mathematical denotational framework, within which the essential properties of models of computation can be analyzed and compared. With the tagged signal model semantics, three categories of abstract semantics can be defined: process networks type, firing type, and stateful firing type. Examples of concrete semantics conforming to the process networks abstract semantics are Hoare's CSP, Milner's CCS, and Kahn's process networks; examples conforming to the firing abstract semantics include DF, DE, and Giotto; and those that conform to the stateful firing abstract semantics include SR and CT.

#### 1.2.2 Model Implementation Tools

After introducing models of computation, in this subsection existing implementation tools are discussed for some of them. There are two big categories of the implementation tools: from either academia or industry. In the following, the first five examples are from academia, which aim at a better research and development environment. Meanwhile, industry has paid a close attention to model-based design methodology and the last six are typical representatives. Giotto Giotto defines two virtual machine platforms to implement embedded software consisting of hard real-time periodic tasks with deterministic mode changes. The Embedded Machine (E-Machine) [48] defines conditions that enable tasks while the Schedule Machine (S-Machine) [49] defines task switching for execution. Task enabling events include external interactions a task may have. Scheduling code can describe standard scheduling policies such as rate monotonic and earliest deadline first. Giotto compiler automatically targets the E-Machine and the S-Machine. To achieve data determinism, Giotto [47] delays committing output data on every connection, which means that there is one additional unit sampling delay form input to output in any communication.

Metropolis Metropolis [9], successor of Polis [8], is developed at the University of California, Berkeley. Metropolis provides a design environment for heterogeneous systems. In the Metropolis framework, the infrastructure consists of models of communication through abstract semantics, design methodologies at different abstraction levels, and communication refinement as well as base tools used for design imports, user interface, and simulation. In Metropolis, system functions are specified via a network of processes, where a process is a sequential function plus ports. Metropolis does not commit to any particular communication semantics. Ports are interconnected by communication media, which define the communication semantics. Examples of communication media include queues, shared memory, and so on.

Modelica Modelica [102] is developed and maintained by Modelica Association [4], a nonprofit organization. Modelica consists of three parts: object-oriented language, standard

libraries, and simulation environment. The underlying model of computation of Modelica is captured by a set of differential, algebraic, and discrete equations with real-time constraints. Modelica is primarily used for modeling large, complex, and heterogenous physical systems including mechanical, electrical, hydraulic, thermal, power, and control subsystems.

Ptolemy Ptolemy [52][35] is a research project at the University of California, Berkeley. The goal of the project is to research modeling, simulation, and design of heterogenous concurrent embedded real-time systems. Ptolemy is a framework that supports design of embedded software based on well-defined models of computation that govern the interaction among concurrent components. It started with static dataflow model of computation for digital signal processing and the current version of the project, Ptolemy II, supports many of the models of computation discussed above.

The Generic Modeling Environment The Generic Modeling Environment (GME) [65][1] is developed at Vanderbilt University. The GME is a model-integrated program synthesis tool and is featured with configurable modeling, meta-modeling, and model visualization. The configuration of the GME is via metamodels that specify the modeling language of the application domain. The metamodeling language of the GME is based on the Unified Modeling Language (UML) and Object Constraint Language (OCL). The GME supports design reuse by metamodel composition. Decorator interfaces of the GME enables customization of model visualization.

LabVIEW LabVIEW [27] is developed at National Instruments Corporation and the best supported underlying model of computation is synchronous dataflow. LabVIEW can

be viewed as a high level graphical programming language (known as G code). LabVIEW combines design, simulation, prototyping, and deployment of embedded software in a single graphical programming tool-chain so that system development time is reduced. Via using the LabVIEW graphical development environment, it is easy to program systems with heterogenous executing devices quickly and reliably.

**OPNET** Developed by OPNET [55], OPNET Modeler is used for modeling and simulation of networks, devices, and protocols. With discrete event as the underlying model of computation, OPNET Modeler is designed to support hierarchical object-oriented modeling to facilitate both research and development of communication networks. From the highest to the lowest level, the hierarchical modeling architecture is network (e.g., LAN), node (e.g., devices such as routers), and process (e.g., protocols such as IP/TCP).

SCADE SCADE [34] represents Safety Critical Application Development Environment. It is the visual editor for Lustre, one of the popular synchronous languages. Lustre and SCADE are developed for safety-critical embedded software such as avionics software, where tasks are aligned to a master clock and its sub-clocks. Consistency and deadlock are checked via clock calculus [96]. The current version of SCADE is Version 6, which supports a unified design, modeling, and code generation environment.

Signal Processing Worksystem/Designer Signal Processing Worksystem (SPW) is developed at Cadence and later sold to CoWare. CoWare renamed SPW to Signal Processing Designer (SPD) [54]. The underlying model of computation of SPD is synchronous dataflow. SPD is an integrated environment used for system-level design, modeling, sim-

ulation, and implementation of complex digital signal processing systems such as wireless and multimedia products.

Simulink Simulink with Real-Time Workshop (RTW) [79] is developed at The Math-Works Incorporation for embedded control software and has been widely used in the automotive industry. The underlying models of computation that Simulink supports include synchronous reactive, continuous time. For models with the synchronous reactive semantics, Simulink achieves data determinism with snapshot of inputs and delayed commit of outputs. Note that Simulink introduces a unit delay only on slow to fast sampling rate changes.

**Stateflow** Stateflow [81] is also developed at The MathWorks Incorporation. It is a powerful model-based design and development tool. As its name implies, the underlying model of computation is finite state machine. Stateflow is good for designing complex control and supervisory logic systems.

### 1.3 Scheduling and Communication Mechanisms

For model-based software design, upon implementation, the functionality of each model block is accomplished by a run-time task. There are two options to implement a multi-rate model on a single processor system. In a single task implementation, all the functionality of the specification is implemented by a single run-time task (or executive), running at the base rate of the system. Such an implementation is easier to construct, but often characterized by poor resource utilization. A multi-task implementation typically

uses one task for each execution rate, and possibly more. All tasks are executed under the control of an operating system. Each implementation task  $\tau_i$  is characterized by a set of parameters: priority  $\pi_i$ , period (periodically activated) or minimum inter-arrival time (sporadically activated)  $T_i$ , worst-case computation time  $C_i$ , worst-case response time  $R_i$ , and relative deadline  $D_i$ . The task execution time is usually finite and a task can be preempted according to its priority. Schedulability of tasks requires that  $R_i \leq D_i$ . Multi-task implementations allow for a much better schedulability. However, due to preemption, there may exist problems with inter-task communication, e.g., nondeterministic communication or data integrity problems. To address these problems, communication protocols have been proposed in literature. In the rest of this section, scheduling policies and communication mechanisms are discussed.

#### 1.3.1 Scheduling Policies

Given a system specification consisting of a set of concurrent functional blocks, a software implementation, consisting of a set of software tasks, can be obtained by software synthesis tools. In a software synthesis process, there are two sub-problems: automatic code generation for each task and dynamic scheduling of the generated tasks. Software synthesis aims at minimizing real-time scheduling overhead. There are three classes of scheduling: static (schedule completely determined at compile time), dynamic (schedule determined at run time), quasi-static (most of the schedule computed at compile time, some scheduling decisions made at run time, but only when necessary). Among them, dynamic scheduling is usually used for real-time controls featured with preemption and suspension, static scheduling is good for data processing, and quasi-static scheduling is primarily for

data-dependent controls. In the following, real-time scheduling and quasi-static scheduling policies are summarized.

Real-Time Scheduling A real-time system implemented as software consists of a set of tasks. Tasks are enabled by repeating events in the environment and their execution must satisfy timing requirements. Real-time scheduling is difficult. There are various types of scheduling policies proposed for real-time tasks in literature [18], e.g., preemptive and non-preemptive policies. Under preemptive scheduling, the running task can be preempted by another active task with a higher priority, i.e., the enabled task with the highest priority is scheduled for execution at any time; while under non-preemptive scheduling, the running task cannot be interrupted after it is dispatched, i.e., once a task is chosen to be executed, it will run to completion even if some tasks with a higher priority become enabled.

In terms of the parameters on which scheduling decisions are based, real-time scheduling policies can be static or dynamic. For example, for priority-based scheduling, priorities can be either static or dynamic. Static priorities are assigned offline while dynamic priorities may change at run time. When there are multiple tasks enabled, the task with the highest priority is executed.

In terms of the schedule generation time, there are offline and online scheduling policies. An offline scheduling algorithm is executed on all the tasks in the system before actual task activation while an online scheduling algorithm is executed at run time upon new task arrival and running task termination. Offline scheduling is static and typical examples are Round-Robin (RR) scheduling and static cyclic scheduling. A Round-Robin schedule picks a task order and executes them forever in that order. A static cyclic executive [75]

picks a task sequence and executes that sequence forever. Online scheduling is dynamic. Typical online scheduling policies are priority-based. For online scheduling, the tasks can be either preemptive or non-preemptive. Compared with online scheduling, it is easy to construct and analyze an offline schedule. Without preemption and priority calculation, the overhead with offline scheduling is very low. But it may delay service to more urgent tasks. Liu-Layland [73] considers systems consisting of periodic tasks with fixed execution time. It is assumed that the worst-case response time of a task is smaller than the period of the task. It is proved that with preemptive static priority scheduling, the critical instant occurs when a task is enabled at the same time as all higher priority tasks. For Rate Monotonic (RM) [71] scheduling, a higher priority is assigned to a task with a shorter period. It is demonstrated that scheduling policies based on static priorities can schedule systems with a utilization less than 0.69. If scheduling based on static priority does not work, online scheduling based on dynamic priority can be used. The typical examples of dynamic scheduling policy is Earliest Deadline First (EDF) [73][31]. Its main idea is to assign the highest priority to the task with the closest deadline. It is shown that EDF can schedule any set of tasks with a utilization less than 1.

Quasi-Static Scheduling Petri nets model of computation provides a unified model for mixed control and data processing specifications. As presented in Section 1.2.1, most of the properties of Petri nets are decidable. Quasi-Static Scheduling (QSS) [29][28] of embedded software is based on Free-Choice Petri Nets (FCPN), where free choice means that the choice depends on the token value rather than the token arrival time. For FCPNs, schedulability can be checked before code generation. QSS finds one schedule for every conditional branch

at compile time while it chooses one of these schedules according to the actual value of the data at run time. QSS minimizes run-time overhead with respect to dynamic scheduling by automatically partitioning the system functions into a minimum number of concurrent tasks.

#### 1.3.2 Communication Mechanisms

There are different ways to classify inter-task communication, for example, blocking versus non-blocking and synchronous versus asynchronous. Communication is non-blocking if the communication call may return before the communication operation completes, otherwise it is blocking. Specifically, for blocking read, processes cannot test for emptiness of input and must wait for an input to arrive before proceeding. For blocking write, processes must wait for a successful write before continuing. Both Milner's Calculus of Communicating Systems and Hoare's Communicating Sequential Processes use blocking write/read. Shared variables are examples of non-blocking write/read. FIFOs used in CF-SMs and SDL (Specification and Description Language) are examples of non-blocking write and blocking read.

Communication is asynchronous if its execution proceeds at the same time with the execution of the programm, otherwise it is synchronous. A typical example of synchronous message passing is rendezvous and a representative example of asynchronous communication is asynchronous buffered communication. For rendezvous, no space is allocated for communication data. If one of the communicating blocks (either producer or consumer) reaches the point of communication, it stalls for synchronization until the other one is also ready to exchange data, i.e., the read and the write occur simultaneously.

Note that a non-blocking communication is not necessarily asynchronous. Both asynchronous and non-blocking communication routines need a separate wait or test call to make sure that the communication has completed and that resources can be safely reused [22]. Reading can be consumable or non-consumable, i.e., the result of each write can be read at most once or several times. For shared memory, multiple nondestructive reads are possible and writes delete previously stored data.

Communication can be either lossless or lossy. Events or tokens may be lost in lossy communication. For multi-rate concurrent systems, buffers are usually used to adapt different rates of the sender and the receiver(s). To achieve lossless communication with bounded memory, an appropriate buffer sizing is needed, otherwise it may need to block the sender. As a special example, FIFO communication buffers can be either bounded (e.g., CFSMs) or unbounded (e.g., SDL, Khan Process Networks, Petri Nets).

Any (real-time) communication of data between concurrent tasks that cannot be made atomic at the hardware level must be implemented by using some communication protocol to protect against access of the reader(s) while a write is in progress or against modification of the data by the writer task while a read is in progress. In the rest of this subsection, different implementation mechanisms in terms of blocking and non-blocking are discussed. A blocking mechanism is also called lock-based and usually requires semaphore (or spin lock) support from a real-time operating system. Non-blocking mechanisms do not need a support of locking and can be further sub-categorized as lock-free and wait-free as discussed below. Note that, though communication is emphasized in the discussion, these mechanisms are actually general models for resource sharing.

**Blocking Mechanism** For lock-based schemes, when a task wants to access the communication data while another task holds an exclusive lock, it blocks (usually on a semaphore), and releases the CPU voluntarily. When the lock is released, the task is restored in the ready state and can safely access the data. Lock-based mechanisms guarantee exclusive access to shared resources. Semaphores [112] are the most common method for locking a shared resource. Typical problems associated with resource sharing are priority inversion and deadlock. A radical solution consists in avoiding preemption during the execution of the critical sections, but this method affects all tasks (not only those using the given resource) and is only effective for very short critical sections. Different protocols have been developed to deal with this problem. The Priority Inheritance Protocol (PIP) [111] limits the priority inversion caused by resource constraints to a known upper bound in case critical sections are not nested. In the PIP, the blocking task inherits the highest priority of the tasks that are waiting for the resources it is currently holding, therefore avoiding preemption from tasks with a medium priority. The PIP allows to bound the priority inversion in most cases, but has a costly implementation and does not prevent chained blocking and even deadlock in case of nested critical sections. The Priority Ceiling Protocol (PCP) [111][26] avoids these two problems by extending the PIP. The PCP allows to bound the worst-case blocking time caused by priority inversion to a known value (one critical section, better than the PIP bound) in all cases, and avoids deadlock. The PCP introduces a priority ceiling for each semaphore equal to the highest priority of any task that can possibly lock it. A task is allowed to enter a critical section only when its priority is higher than the priority ceilings of all semaphores currently locked by other tasks. When a task blocks another one with a

higher priority, the blocking task gets the priority of the blocked task when it is in the critical section. The Immediate PCP (IPCP) and the Stack Resource Policy (SRP) [7], which is its generalization to dynamic priority schemes, further extend the PCP by supporting multi-unit resources and sharing of the application run-time stack. Compared with the PCP, a preemption level is statically introduced for each task. Each resource is assigned a current ceiling equal to the highest preemption level and the system ceiling is defined to be the maximum of the ceilings of all the locked resources at any given time. When a task uses a resource, its preemption level is immediately raised to the ceiling level of the resource even if it is not blocking any task, and the maximum between its preemption level and its priority becomes its execution priority. This means that any task that can be possibly blocked by it is not even allowed to start execution until the resource is unlocked. The worst-case bound on the blocking time is the same as that in the PCP, but the implementation of these protocols is considerably easier.

Non-blocking Mechanism The non-blocking mechanism can be either lock-free or waitfree. For a lock-free scheme, when a reader wants to access the communication data, it does

so without blocking. At the end of the operation, it checks the consistency of the data.

If it realizes there was a possible concurrent operation by the writer and the possibility of

having read an inconsistent value, the reader task performs the read operation again. By

leveraging the timing properties of tasks, the number of retries can be upper bounded.

A better non-blocking scheme is wait-free. Under the wait-free mechanism, readers and writers are protected against concurrent access to data by means of replication of the communication buffers and by leveraging information about the points in time when they are going to access the resource or possibly other information that constrains the access to the resource (such as the priority or other scheduling-related information). Wait-free communication protocols have been mostly researched from the perspective of the programmers of concurrent real-time applications, interested in preserving the consistency of the data. The corresponding communication semantics is the so-called freshest value at execution time, meaning that each reader always obtains the latest data written by the writer task into the channel. Most of the protocols presented in the literature try to optimize the buffer size based on assumptions on tasks.

In the sequel, typical wait-free protocols with the execution-time freshest value semantics are reviewed. The first category of the methods provides buffer sizing and access procedures based on the number of readers that ensures mutual exclusion access. In [24], an asynchronous protocol is proposed to preserve data consistency for communication between a single writer and a single reader running on a shared-memory multiprocessor. With no assumption on task priorities and periods, three buffers are needed: one for the data being read, one for the data last written (current) by the writer, and another one for the writer to write a new data item into when the latest written buffer has not been read yet. To achieve data integrity, a hardware-supported Compare-And-Swap (CAS) instruction is used to atomically assign the reading position in the buffer array to reader tasks and to update the pointer to the last written value. This three-slot asynchronous protocol is extended to systems with single writer and multiple readers in [23]. The multi-reader asynchronous protocol needs (N+2) buffer slots, where N is the number of the readers in the system.

The other method provides buffer sizing and buffer indexing by using the Tempo-

ral Concurrency Control (TCC) that ensures writer and reader tasks never access the same data item at the same time. The size of the buffer can be computed by upper bounding the number of times the writer can produce new values while a given data item is considered valid by at least one reader. This concept is first introduced in [61] and [25], assuming as the data validity time the worst-case execution time of a reader. In [61], the Non-Blocking Write (NBW) protocol is presented for a single-writer multiple-reader system executing with a priority-based preemptive scheduling from a real-time operating system on a distributed real-time system consisting of a set of nodes connected by a broadcast communication channel. The writer has its own communication controller, therefore the writer task cannot be preempted or preempt other reader tasks and thus the non-blocking property of the writer is achieved. In [25], a timing-based wait-free mechanism called asynchronous circular buffering protocol is proposed for single-writer multiple-reader systems running on a shared-memory multiprocessor system with a single global clock. Priority-based preemptive scheduling on the same processor is assumed. It is further supposed that the worst-case response time is smaller or equal to the deadline and the deadline is smaller than or equal to the period. Under this protocol, data sharing is implemented through a sequential algorithm using a circular buffer and the size of the circular buffer is configured through the timing property of the set of tasks.

A combination of the previous two buffer sizing methods may be used to obtain a better buffer size through exploiting the temporal characteristics of real-time tasks. A transformation mechanism used to optimize buffer sizing based on [23] and [25] is proposed in [51] for implementations with the execution-time freshest value semantics. Based on timing properties, the reader tasks are categorized as either fast or slow. The fast readers leverage the lifetime-based bound of the NBW [25], and the slow ones leverage the bound based on the maximum number of active reader instances as in [23]. Overall the space and temporal performance are both improved. The transformation is applicable to protocols for both single processor and multiprocessor systems.

### 1.4 Goal of Dissertation

Among those models of computation that are surveyed in this chapter, the synchronous reactive model of computation has strong formal properties, e.g., decidable termination and execution with bounded memory, which can be used to verify synchronous reactive systems. This model of computation is good for specifying periodic real-time tasks. There has been a steadily increasing interest in this model in both academia and industry. Synchronous reactive models have been traditionally used in hardware logic design and more recently for modeling control-dominated embedded applications. The synchronous reactive zero-time semantics is very popular because of the availability of the tools for simulation and formal verification of system properties. When implementing a high-level model into code, it is important to preserve its semantics, in order to retain the simulation and verification results. However, this requires that the run-time behavior when the functions are implemented by a program with a finite execution time and possibly subject to preemption is provably equivalent to the synchronous reactive model with zero execution time and no preemption. In general, defining such a provably correct implementation is nontrivial.

In the following, possible solutions based on the synchronous reactive commu-

nication mechanisms are discussed. There usually exists a time-space tradeoff between different communication mechanisms. Lock-based mechanisms are space-efficient because data buffers (usually in Random Access Memory (RAM)) do not need to be replicated, however, they typically require complex management procedures (usually in Read-Only Memory (ROM)). As discussed earlier, especially, they may introduce large blocking times. Lock-free mechanisms improve time efficiency, but they still suffer from long retry times in the worst case. Wait-free mechanisms are the most time-efficient, but may require a higher memory cost for the replicated buffer space.

In spite of the thread of research on wait-free communication with the freshest value semantics, this non-blocking communication has been rediscovered in the context of model-based software development and reformulated with the goal of finding communication mechanisms (typically with a minimum buffer size) for implementing a synchronous reactive semantics in the communication of a single writer with multiple reader tasks/blocks. The problem is somewhat different and yet both the optimization problems and the protocol solutions show many similarities that are not only worth a comparative study, but can possibly lead to a general theory and further improvement with respect to the state of the art. The communication mechanisms that provide data consistency with the freshest value semantics at task execution time cannot guarantee time determinism. The value that is read by a reader task depends upon the scheduling of the tasks, that is, on their execution times and the possible occurrence of preemption. For many control applications, this is not a concern, given the robustness of the control algorithm with respect to time delays. In other cases where the application may be sensitive to the ensuing jitter, the implementation

needs to satisfy more stringent requirements. The correct implementation of a synchronous reactive semantics for the above cases requires assigning a buffer index to the reader, which maintains the same value during the reader's execution. Reduction of memory cost due to communication is an open research issue. Hence this dissertation particularly focuses on the synchronous reactive model of computation and attempts at providing new results in this context.