# A Baseband Mixed-Signal Receiver Front-End for 1Gbps Wireless Communications at 60GHz

David Amory Sobel

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-45 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-45.html

May 2, 2008

Copyright © 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# A Baseband Mixed-Signal Receiver Front-End for 1Gbps Wireless Communications at 60GHz

by

David Amory Sobel

A.B. (Harvard University) 1997 M.S. (University of California, Berkeley) 2000

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in Charge Professor Robert W. Brodersen, Chair Professor Borivoje Nikolic Professor Paul K. Wright

Spring 2008

|       | The dissertation of David Amory Sobel is approved: |      |

|-------|----------------------------------------------------|------|

|       | The dissertation of David Amory Sober is approved. |      |

|       |                                                    |      |

| Chair | •                                                  | Date |

|       |                                                    |      |

|       |                                                    | Date |

|       |                                                    | Date |

|       |                                                    |      |

|       |                                                    | Date |

|       |                                                    |      |

|       | University of California, Berkeley                 |      |

|       |                                                    |      |

# A Baseband Mixed-Signal Receiver Front-End for 1Gbps Wireless Communications at 60GHz

Copyright 2008

by

David Amory Sobel

#### **Abstract**

A Baseband Mixed-Signal Receiver Front-End for 1Gbps

Wireless Communications at 60GHz

by

#### David Amory Sobel

Doctor of Philosophy in Engineering–Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Robert W. Brodersen, Chair

In 1995, the FCC allocated the spectrum from 59GHz to 64GHz as an unlicensed band, and shortly thereafter, extended this unlicensed band to 57-64GHz, thus providing 7GHz of unlicensed spectrum for general purpose use. Similarly, regulatory bodies across the globe have also set aside multi-GHz blocks of spectrum at 60GHz for unlicensed use. The presence of a true multi-GHz worldwide band has sparked immense interest in developing high-throughput 60GHz communications systems. Furthermore, the demonstration of CMOS mm-wave circuitry in recent years has made feasible the possibility of a highly integrated, all-CMOS 60GHz transceiver.

However, the design of such a system is made quite difficult by several factors: first, the 60GHz indoor channel has increased transmission loss due to both the increased free-space loss and the poor transmissivity of common building materials. As a result, systems employing omnidirectional antennae cannot achieve Gbps rates, and more complex systems employing adaptive beamforming must be architected. Secondly, the

2

limited performance of CMOS mm-wave components requires new approaches to system

and architecture design, as the high level of system performance must be maintained with

relatively low quality mm-wave circuits.

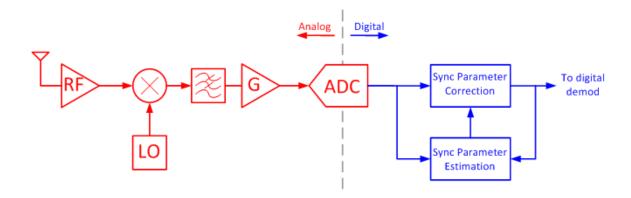

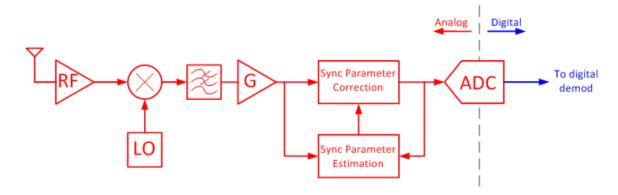

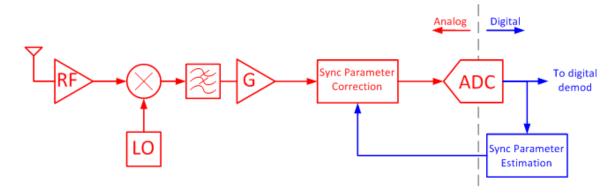

The work presented in this dissertation focuses on the analysis, specification, and

design of a baseband system and architecture for 1Gbps, 60GHz wireless receiver.

System exploration is conducted in order to find a suitable architecture for a high-

performance system composed of limited-performance CMOS mm-wave circuitry. A

mixed-signal baseband receiver design is proposed in order to minimize the overall

power dissipation and implementation complexity. The proposed system performs much

of the signal processing related to the task of synchronization in the analog domain, so

that the signal is properly conditioned prior to sampling and quantization. This approach

reduces the resolution requirements of the high-speed analog-to-digital converters

(ADCs), dramatically reducing system power consumption.

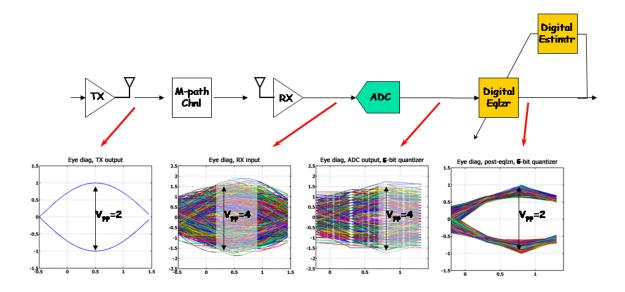

The proposed architecture was designed and fabricated in a 90nm standard digital

CMOS process. The design consists of a mixed-signal carrier phase rotator block with

500Ms/s DDFS DAC, a 16-tap mixed-signal complex decision-feedback equalizer

running at 1Gs/s, and two 2Gs/s, 4-bit flash ADCs. This analog front-end achieves a peak

SNDR of 24.8dB at the full Nyquist rate, has linearity exceeding 38dB, and dynamic

range greater than 31dB. Overall chip power consumption is 55mW.

Professor Robert W. Brodersen

Dissertation Committee Chair

To Eli, who continually fills my heart with joy.

# **Table of Contents**

| Ta | able of ( | Contents                                                          | ii |

|----|-----------|-------------------------------------------------------------------|----|

| A  | cknowle   | edgements                                                         | v  |

| 1  | Intro     | oduction                                                          | 1  |

|    | 1.1       | Trends in High Data-Rate Wireless Systems                         | 1  |

|    | 1.2       | Recent Developments in 60GHz Regulatory and Industrial Landscape. | 3  |

|    | 1.3       | Research Goals and Contributions                                  | 4  |

|    | 1.4       | Organization of the Dissertation                                  | 5  |

| 2  | The       | 60GHz Communications Channel                                      | 7  |

|    | 2.1       | Review of Directional Antenna Technology                          | 7  |

|    | 2.1.1     | Definition of Terminology                                         | 8  |

|    | 2.1.2     | Types of Directional Antennae                                     | 11 |

|    | 2.1.3     | Performance of a Directional Antenna                              | 17 |

|    | 2.2       | Key Characteristics of the 60GHz Channel                          | 21 |

|    | 2.2.1     | Reduced Performance of CMOS mm-wave Components                    | 22 |

|    | 2.2.2     | Oxygen Absorption and Material Penetration                        | 23 |

|    | 2.2.3     | Path Loss and Antenna Directionality                              | 26 |

|    | 2.2.4     | Feasibility of a High Directionality Antenna                      | 31 |

|    | 2.2.5     | Regulatory Issues and Spectral Efficiency                         | 32 |

|    | 2.3       | Literature Review of 60GHz Channel Studies                        | 34 |

|    | 2.3.1     | Material Properties                                               | 35 |

|    | 2.3.2     | Channel Properties                                                | 36 |

|    | 2.3.3     | Summary of Literature Review                                      | 42 |

|    | 2.4       | Conclusions                                                       | 44 |

| 3  | Syst      | em Design Considerations                                          | 46 |

|    | 3.1       | RF Circuit Limitations                                            | 47 |

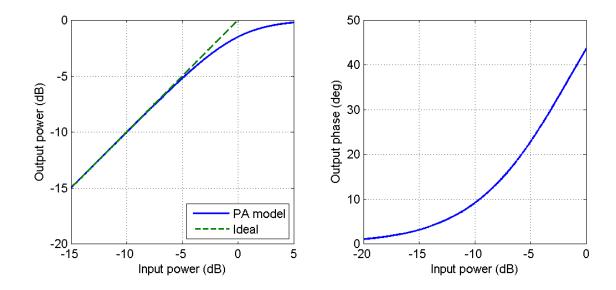

|    | 3.1.1     | Power Amplifier Linearity                                         | 47 |

|    | 3.1.2     | Local Oscillator Phase Noise                                      | 52 |

|    | 3.2       | Modulation Schemes                                                | 54 |

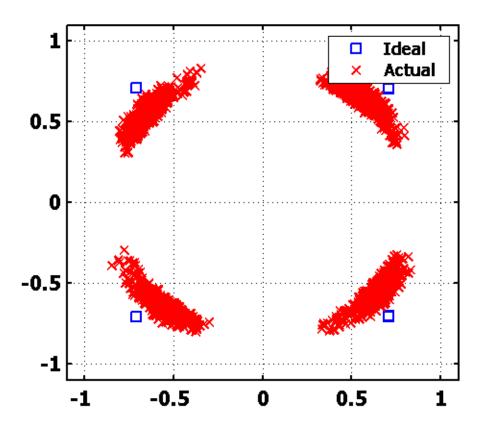

|   | 3.2.1  | QPSK                                                         | 54    |

|---|--------|--------------------------------------------------------------|-------|

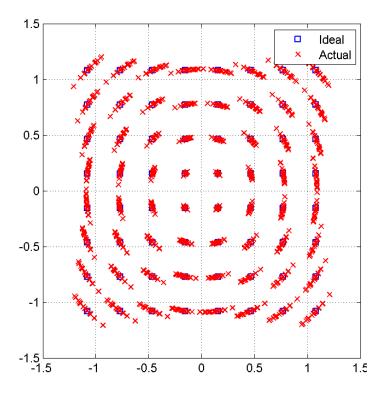

|   | 3.2.2  | Quadrature Amplitude Modulation                              | 56    |

|   | 3.2.3  | OFDM                                                         | 58    |

|   | 3.2.4  | Minimum-Shift Keying                                         | 61    |

|   | 3.2.5  | Comparison                                                   | 64    |

|   | 3.3 B  | aseband Architecture Considerations                          | 65    |

|   | 3.3.1  | Performance Requirements of MSK Baseband Receiver            | 66    |

|   | 3.3.2  | Baseband Architecture Selection                              | 71    |

|   | 3.4 S  | ynchronization Algorithms for Mixed-signal Receivers         | 83    |

|   | 3.4.1  | Feedback Synchronization Algorithms for Mixed-signal Systems | 84    |

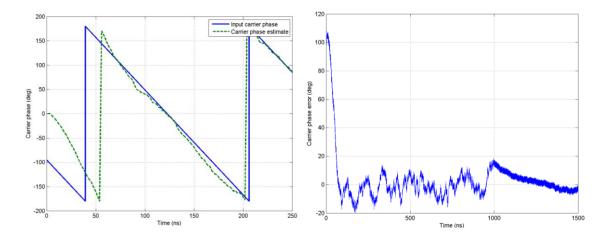

|   | 3.4.2  | Carrier Phase Estimation                                     | 91    |

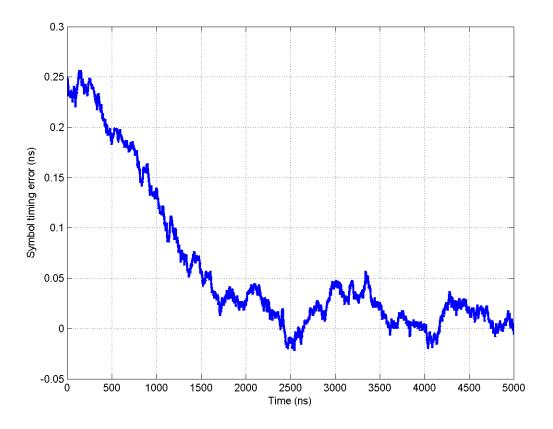

|   | 3.4.3  | Symbol Timing Estimation                                     | 97    |

|   | 3.4.4  | Channel Estimation.                                          | . 100 |

|   | 3.5 S  | ystem Simulations                                            | . 105 |

|   | 3.6 C  | Conclusions                                                  | . 112 |

| 1 | Circui | it Implementation                                            | . 113 |

|   | 4.1 B  | Block-level Architecture                                     | . 114 |

|   | 4.2 C  | Carrier Phase Rotator                                        | . 115 |

|   | 4.2.1  | Gilbert Quad VGA                                             | . 116 |

|   | 4.2.2  | Feedback Tuning Circuit                                      | . 122 |

|   | 4.2.3  | DDFS Current-mode DAC                                        | . 125 |

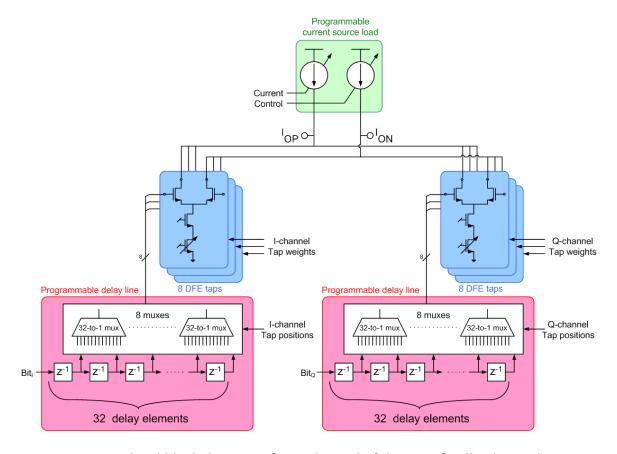

|   | 4.3 D  | Decision-feedback Equalizer                                  | . 128 |

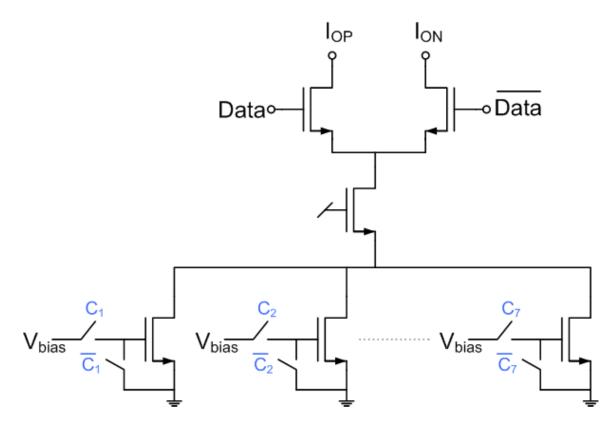

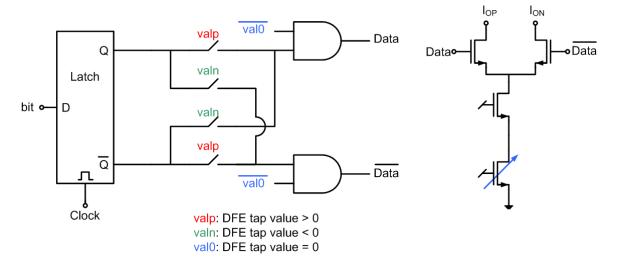

|   | 4.3.1  | DFE Tap Structure with Programmable Current Bias             | . 129 |

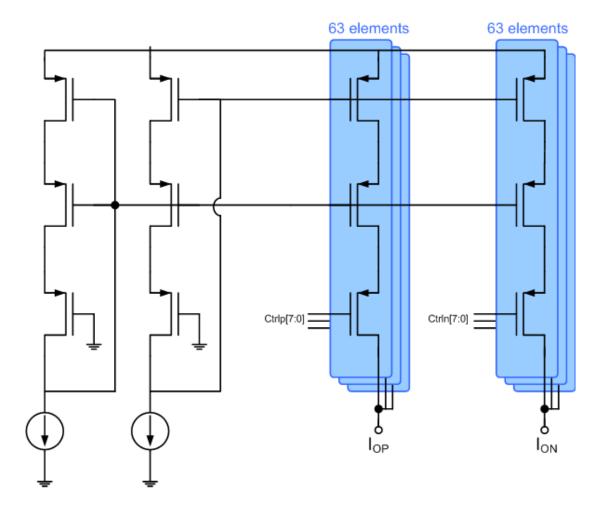

|   | 4.3.2  | Programmable Current Source Load                             | . 131 |

|   | 4.3.3  | Programmable Delay Line                                      | . 132 |

|   | 4.4 S  | umming Current Buffer                                        | . 133 |

|   | 4.5 T  | ransimpedance Track-and-hold Amplifier                       | . 136 |

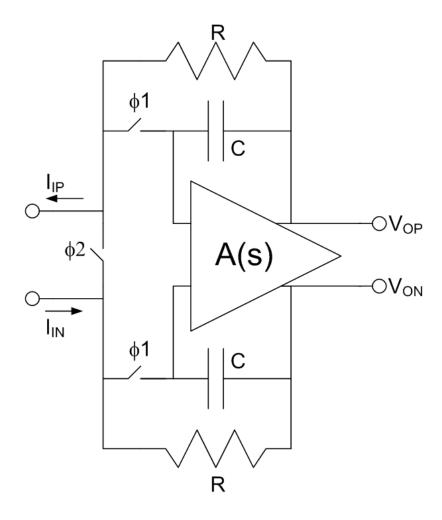

|   | 4.5.1  | THTIA amplifier                                              | . 138 |

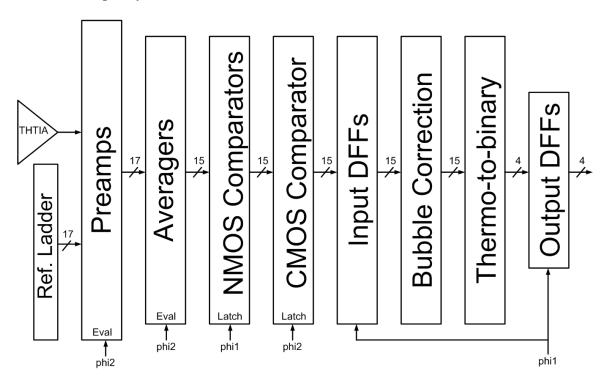

|   | 4.6 F  | lash ADC                                                     | . 140 |

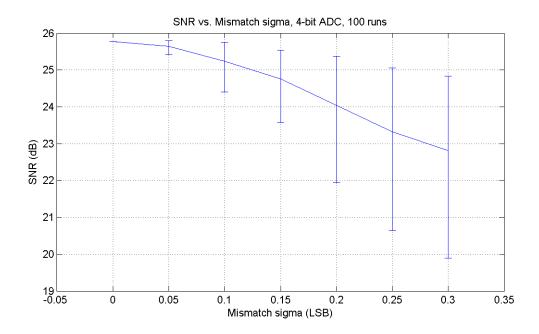

|   | 4.6.1  | ADC Architecture and Mismatch Analysis                       | . 141 |

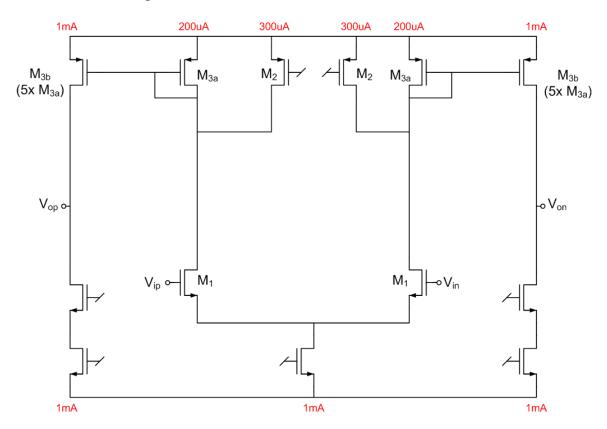

|   | 4.6.2  | Preamplifier                                                 | . 150 |

|   | 4.6.3  | Averager                                                     | . 151 |

|     | 4.6.4            | NMOS Comparator                         | 152 |

|-----|------------------|-----------------------------------------|-----|

|     | 4.6.5            | CMOS Comparator                         | 153 |

|     | 4.6.6            | 5 Digital Logic                         | 154 |

| 5   | Mea              | surement Results                        | 155 |

| :   | 5.1              | ADC Performance                         | 156 |

| :   | 5.2              | Carrier Phase Rotator Performance       | 161 |

| :   | 5.3              | Decision-Feedback Equalizer Performance | 164 |

| :   | 5.4              | Conclusions                             | 172 |

| 6   | Con              | clusion and Future Work                 | 173 |

| Bil | Bibliography 175 |                                         |     |

# **Acknowledgements**

As with any endeavor, this research project could not have been completed without the support and assistance of many others. Foremost, I would like to thank my research advisor, Professor Robert Brodersen for his guidance, his support, and his unfailing ability to steer his students into fascinating and impactful research areas. Also, I would like to thank Professor Jan Rabaey, who along with Professor Brodersen, created the Berkeley Wireless Research Center. I feel truly privileged to have had the opportunity to study in such a rich environment. None of this would have been possible without all of their effort. I would also like to thank Professor Bora Nikolic for providing advice and insight into the area of high-speed serial communications; the course he taught on the topic was directly applicable to many of the techniques I investigated in my research. Thanks is also due to Professor Nikolic and to Professor Paul Wright for reviewing this dissertation and providing helpful feedback.

No department could operate without a support staff, and we were lucky to have such superb people. I must first thank Gary Kelson for his tireless efforts in securing silicon access on my behalf. There was a point in time during my research that I was a "man without a foundry", and were it not for Gary's efforts, I still would be waiting to tape out my chip. Tom Boot deserves special mention for always being willing to go above and beyond the call of duty in order to help the students deal with the vast bureaucracy that is the UC system. I also want to thank Kevin Zimmerman, Brian

Richards, and Brad Krebs for supporting the vast array of computing resources needed at the center.

I would like to thank TSMC for generously donating their foundry access, tools, and technology libraries in support of my work. I would like to particularly thank Dr. Fu-Lung Hsueh for championing our work within TSMC.

An advantage of being a graduate student for as many years as I have been one is that I have had the opportunity to work with and learn from so many brilliant and talented individuals. A disadvantage of being a graduate student for as many years as I have been one is that singling out each person who has had a positive impact on my graduate career would double the length of my dissertation (and perhaps take yet another year to complete!) Therefore, I must offer my apologies to those who go unnamed. However, quite a few of my colleagues deserve mention for their friendship, assistance, and company over these past years. During my first years at Berkeley, I had the good fortune of collaborating with Dennis Yee, Chinh Doan, Sohrab Emami, Johan Vanderhaegen, Brian Limketkai, and Sayf Alalusi. Our discussions—technical and otherwise—were a highlight of my "first tour of duty" at Berkeley. My Ph.D. research was more of a solitary effort, but my experience at Berkeley during those years was by no means solitary, due in large part to the company of many brilliant and friendly colleagues. My years as a Ph.D. student were enriched by many fellow students, most notably Ian O'Donnell, Josie Ammer, Mike Sheets, Tufan Karalar, Nate Pletcher, Simone Gambini, Luca De Nardis, and Danijela Cabric. Whether we were discussing our research, global politics, or the proper pronunciation of Italian vulgarities, your companionship will be missed.

Working part-time at Broadcom throughout much of my Ph.D. research may have added to the duration at my tenure at Berkeley, but it was a decision that greatly added to the quality of my work as a student. When I first joined Broadcom, I told my managers that I intended to eventually return to school to pursue a Ph.D., and I would like to thank them for fully supporting me in that decision. Special thanks are due to Haideh Khorramabadi, Neil Kim, Pieter Vorenkamp, and Tom Kwan for creating a situation where I could simultaneously pursue my academic endeavors while continuing to be a part of the engineering team within the company. I would like to single out my manager, Tom Kwan, to thank him for his support, advice, mentorship, and encouragement during my entire tenure at Broadcom. I would also like to thank all my colleagues in the analog team at Broadcom; I have learned so much from you over these years, and the skills and practices I have gleaned from our interactions have enhanced my work as both a Broadcom employee and a student.

I consider myself lucky to have such a loving and supportive family. I want to thank my parents for encouraging me to pursue my dreams and instilling in me the self-esteem and persistence to keep at it when those dreams feel somewhat out of reach. Your unfailing love and support has been a source of strength to me over the past 32 years. I also want to thank my sister, Heather, for her unconditional kindness. Your smile and your warmth always brightens my day. My brother Eric deserves thanks for simultaneously being my idol, my rival, my tormentor, and my best friend. While you are no longer physically with us, you will always be present in my heart, and I will cherish the 21 years that we shared. I have also been lucky enough to pick up some

wonderful "new" family members along the way. My in-laws, Ed and Glori Chaika, welcomed me into their family with open arms (even if those arms only came up to my waist) and have treated me like a son ever since.

Finally, I want to thank my wife, Melissa. First, I want to thank you for your patience. I know that this whole Ph.D. thing took a little longer than expected, as I know that there is a spreadsheet floating around somewhere that said I'd be graduating sometime in 2006. Thank you for supporting me throughout my entire Ph.D. career and making the countless small (and not-so-small) sacrifices that enabled me to complete this work. Most importantly, thank you for your love. Your presence by my side has enriched my life immeasurably, and I look forward to all of our adventures and misadventures together over the years. I dedicate this work to you with all my love.

## 1 Introduction

### 1.1 Trends in High Data-Rate Wireless Systems

Wireless technology has had a dramatic impact on the way we work, live, and play. Fifteen years ago, it was unthinkable to imagine that an individual could have data connectivity anywhere other than at a terminal or desktop that was tethered to an Ethernet port or a dial-up modem. Today, it is commonplace to assume that, through the use of wireless communications technology, a person can have voice, video, and data access anywhere in his office, his home, or just about any corner of the globe. With the rapid commercialization of wireless local area networking (WLAN) technologies such as 802.11 over the past several years, achievable indoor wireless data rates have scaled from roughly 1Mb/s to over several hundreds of Mb/s. This growth in bandwidth has enabled a host of new technologies and applications, including real-time audio and video streaming. Furthermore, the use of wireless, instead of wired, communications technology has helped spread the overall adoption of the technology in the consumer market, as ease of installation and customer satisfaction is greatly increased by the elimination of unwieldy and unsightly wires and cables [1].

As wireless access has become an increasingly important part of our everyday lives, the demand for wireless bandwidth similarly increases. Applications that were typically run over traditional wired networks—such as web surfing, file and printer sharing, and voice over IP (VOIP)—can now be easily run on 802.11 wireless networks. Similarly, recent developments in ultrawideband (UWB) technologies show promise for

delivering "wireless USB" connectivity between computers and storage-intensive peripherals like digital cameras, camcorders, and external hard disk drives at rates of up to 480Mb/s [2].

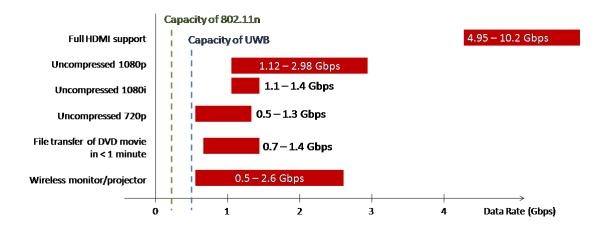

However, there are new wireless applications that demand even greater bandwidth than either 802.11 or UWB can provide. With the widespread adoption of HDTV's and sources of HD content (such as HD set-top boxes, Blu-Ray DVD players, HD camcorders, et al), there is growing demand for real-time wireless streaming between these various HD devices. Similarly, wireless connectivity between a PC (such as a laptop) and a display (either a monitor or an LCD projector) is desirable in many environments. Additionally, the prevalence of mobile personal video players (such as the iPhone, et al) motivates for the capability to "instantaneously" synchronize and transfer large media files between the mobile device and a personal computer over a high-speed wireless link. As shown in Figure 1.1, these applications require throughput exceeding 1 Gb/s, well beyond the capacity of existing wireless systems. Therefore, other technologies must be developed in order to accommodate these new applications. These applications require short-range (on the order of 2-20m) wireless communications capable of handling throughputs of 1Gb/s and above in typical indoor residential and corporate environments. This dissertation presents a study of the key issues involved with enabling this new class of wireless technology and presents the design of a receiver for such a system.

Figure 1.1: New wireless applications and their associated datarate requirements

# 1.2 Recent Developments in the 60GHz Regulatory and Industrial Landscape

In 1995, the FCC allocated the spectrum from 59GHz to 64GHz as an unlicensed, band [3]. Shortly thereafter, the FCC amended their rules to extend this unlicensed band to 57-64GHz, thus providing 7GHz of unlicensed spectrum for general purpose use [4]. The availability of a true multi-GHz band has sparked immense commercial interest in developing 60GHz technology in order to meet the demands of these new high-bandwidth wireless applications. In 2005, IEEE has organized the 802.15.3c task group to develop a standard for a 60GHz wireless personal area network (WPAN) with bandwidths in excess of 1Gb/s [5]. Around that same timeframe, several companies began research and development of 60GHz wireless technology for commercial applications. One of the key technical driving forces behind the commercial interest in 60GHz technology was the demonstration of the feasibility of implementing 60GHz

circuitry in standard, low-cost CMOS [6], [7]. However, due to the limitations of CMOS technology at 60GHz in comparison to other, more expensive materials, new system architectures and techniques must be investigated in order to make a high data-rate, all-CMOS solution feasible. A major aspect of the research described in this dissertation is the analysis and design of a receiver architecture that can accomplish this goal.

### 1.3 Research Goals and Contributions

The goal of the research presented here is to investigate system design issues related to the design of an all-CMOS, 1Gbps, 60GHz wireless receiver and to propose both a system architecture and a baseband receiver implementation that is capable of meeting this high throughput requirement with low power dissipation and implementation complexity. This research is centered around two key theses: first that the overall system design and architecture in inherently linked to the underlying circuit implantation, and that the system must be designed with the strengths and weaknesses of CMOS technology in mind at all times. The second thesis is that the judicious partitioning of the signal processing functions of the receiver baseband between the analog and digital domains is necessary for a truly low-power implementation. Therefore, the scope of this work covers both high-level system design and low-level circuit implementation research, as well as an investigation of the interplay between system and circuit design. In summary, the research contributions include:

An analysis of modulation schemes appropriate for use with a 1Gbps,

60GHz all-CMOS receiver.

- The design of a mixed-signal baseband receiver architecture to reduce overall power dissipation and complexity.

- A full analysis and simulation of the proposed receiver architecture in order to determine necessary system specifications.

- The design and implementation of the proposed receiver in a 90nm digital

CMOS process, including the design of blocks such as:

- o A novel mixed-signal carrier phase correction circuit.

- A high-speed, low-power Gs/s decision-feedback equalizer using a new adaptive tap sizing and positioning scheme.

- A low-power, 4-bit 2Gs/s ADC using a new staggered-averaging technique to minimize the impact of device mismatch.

# 1.4 Organization of the Dissertation

The rest of this dissertation is organized as follows: Chapter 2 examines various issues that are unique to 60GHz communications. The 60GHz indoor channel is analyzed in depth, and key characteristics of this channel are discussed. Also, a review of prior work measuring and characterizing the indoor 60GHz channel is presented. In Chapter 3, system issues related to the design of a baseband receiver architecture are discussed. The impact of CMOS circuit performance at 60GHz is discussed, and modulation schemes and architectures that are amenable to an all-CMOS implementation are investigated. Also, a mixed-signal receiver architecture that promises low power consumption and implementation complexity is proposed and simulated. Chapter 4 details the circuit

implementation of the various blocks within the receiver. Chapter 5 presents measurement results of the fabricated baseband receiver chip, and the dissertation closes with conclusions and suggestions for future research in Chapter 6.

### 2 The 60GHz Communications Channel

The 60GHz communications channel presents several new challenges and opportunities to implement very high bandwidth wireless systems. In many ways, the 60GHz channel has characteristics that are so dramatically different from lower frequency channels, that a wireless transceiver designed for this channel might look quite different from traditional transceiver designs. In this chapter, the 60GHz communications channel is introduced and a qualitative discussion of the key characteristics of the 60GHz channel is presented. This chapter opens with a brief review of directional antenna technology, because—as it will be shown—an approach utilizing directional antenna at 60GHz becomes both feasible and required in order to design a wireless system capable of Gb/s throughput.

As interest in 60GHz communications has grown, there have been numerous studies and measurement campaigns quantifying various parameters of the 60GHz indoor channel and its dependence on other physical parameters such as room size, building materials, and antenna configuration. A survey of these studies is presented in this chapter, with an emphasis on the key channel parameters that impact the system design of a high throughput 60GHz transceiver.

# 2.1 Review of Directional Antenna Technology

In order to understand the challenges and opportunities present in 60GHz wireless communications, a basic understanding on antenna technology is required. In particular, the utilization of directional antenna at 60GHz is a necessity, so a brief discussion of the

basics of directional antenna technology follows. In depth discussions and analyses of antennae, directional antennae, and their applicability to 60GHz wireless communications can be found in [8] and [9].

### 2.1.1 Definition of Terminology

When discussing directional antenna, there are a few basic terms that are frequently used. The first is the notion of an *isotropic antenna*. An isotropic antenna is defined as "a hypothetical lossless antenna having equal radiation in all directions" [8]. A *directional antenna*, by contrast, is defined as an antenna "having the property of radiating or receiving electromagnetic waves more effectively in some directions than in others" [8]. Therefore, all physically realizable antennas are by necessity directional in nature, as even the simple half-wave dipole is a more effective radiator in directions perpendicular to the dipole axis than in directions parallel to it. However, the term *directional antenna* is "usually applied to an antenna whose maximum directivity is significantly greater than that of a half-wave dipole" [8]. An antenna, such as the half-wave dipole, which has directionality in one plane but radiates equally in all directions in the other plane is referred to as an *omnidirectional antenna*.

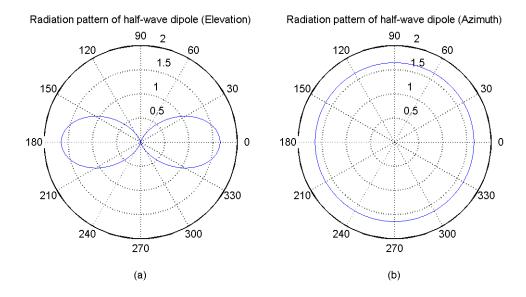

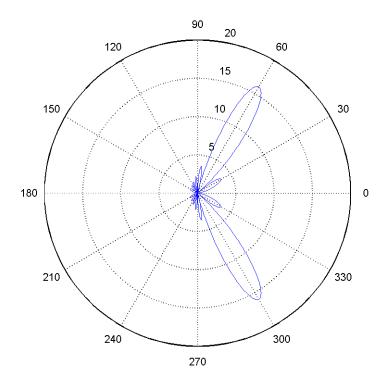

Any directional antenna can be characterized by its *radiation pattern*. The radiation pattern indicates the gain of the antenna in a given plane as a function of the angular offset of the direction of propagation. As an example, the radiation pattern of a half-wave dipole is shown in Figure 2.1 (a) and (b). Assuming the dipole is oriented vertically, the radiation pattern in the azimuth plane is omnidirectional (see Figure 2.1 (b)). The

radiation pattern in the elevation plane (see Figure 2.1 (a)) does show some directionality as discussed above. The maximum directivity of this antenna is 1.64 (linear), or 2.15dBi.

Figure 2.1: Radiation patterns of a half-wave dipole in (a) elevation plane and (b) azimuth plane

The *directivity* of a directional antenna can be derived from its radiation pattern. The directivity is defined as "the ratio of the radiation intensity in a given direction from the antenna to the radiation intensity averaged over all directions" [8]. Therefore, the directivity of an antenna is a function of the angle of observation; however, it is implicitly understood that the direction of interest is the direction of maximum radiation intensity. In this context, directivity can be defined as:

$$D_{max} = \frac{U_{max}}{P_{rad,avg}} = \frac{U_{max}}{P_{rad}/_{\Delta\pi}}$$

(1.1)

where  $U_{max}$  is the maximum radiation intensity (in W/unit solid angle) and  $P_{rad}$  is the total power radiated by the antenna. Therefore, a higher directivity indicates that a higher percentage of the total radiated power is being transmitted in one particular direction.

Closely related to the notion of directivity (and often used interchangeably) is the concept of *antenna gain*. The definition is almost identical, but antenna gain is defined as the ratio of the radiation intensity in a given direction to the power *accepted* by the antenna (normalized by  $4\pi$ ). As with directivity, antenna gain is a function of the angle of observation, but it is also typically assumed to refer to the direction of maximum radiation intensity. In this context, antenna gain can be expressed as:

$$G_{max} = 4\pi \frac{U_{max}}{P_{in}} = 4\pi \frac{U_{max}}{P_{rad}/e_{cd}} = e_{cd} \frac{U_{max}}{P_{rad}/4\pi} = e_{cd} D_{max}$$

(1.2)

where  $e_{cd}$  is the radiation efficiency of the antenna ( $\leq$  1). As can be seen from (1.2), the antenna gain is just the product of the antenna directivity and the antenna efficiency. If the antenna is a perfect, lossless radiator then the two quantities will be equal; in all real cases, however, the gain of an antenna is (somewhat) less than its directivity because of losses internal to the antenna. Typically, the gain of a particular antenna is specified in dBi, which corresponds to the ratio of that antenna's gain to the gain of a lossless isotropic antenna (expressed in dB) [8].

The *half-power beamwidth* (HPBW) is another measure of the directivity of an antenna. The HPBW is the measure of the angle (in radians) over which the radiation intensity of the antenna is at least one-half the value of its maximum value. It follows that

an antenna with a higher directivity by necessity must have a smaller HPBW. In fact, the following lower and upper bounds on HPBW can be intuitively derived:

$$\frac{2\pi}{D_{max}} \le HPBW \le \frac{4\pi}{D_{max}} \tag{1.3}$$

The inverse relationship between antenna directivity and HPBW has significant ramifications when it comes to wireless link design; in particular, a highly directive antenna will require increasingly precise antenna alignment in order to harness the extra gain that such an antenna can provide. Antenna propagation studies have shown that an antenna typically needs alignment to better than 30% of its HPBW in order to be effectively used [10].

### 2.1.2 Types of Directional Antennae

Directional antennae can come in many shapes, sizes, and configurations, but they can be subdivided into two distinct classes: *fixed* and *adaptive*. A *fixed* directive antenna is an antenna that whose radiation pattern is determined solely by its mechanical structure, and hence the basic shape of its radiation pattern can be discerned by merely looking at it. Well-known examples include horn antennae, waveguide aperture antennae, and parabolic reflector antennae, (more commonly known as "dish antennae"). As mentioned above, the pattern of a fixed directive cannot be altered, although the pattern can be redirected by physically moving the antenna. An example of this are the rotating radar dishes typically seen at airports and on military equipment.

An *adaptive* directive antenna is, by contrast, one whose radiation pattern can be altered, typically by electrical means. The most common type—and the one of greatest

applicability to the 60GHz space—is the adaptive antenna array. An antenna array is a set of identical (and typically omnidirectional) antennae that are distributed in space in a particular arrangement and each driven by a unique waveform. The total field of the array is determined by vector addition of the fields radiated by the individual elements [8], and the placement and excitation of the array can be configured so that the net array radiation pattern has a high directivity aimed in the intended direction. Unlike fixed antennae, however, the pattern of an adaptive antenna can be altered by changing the relative excitation of the individual elements.

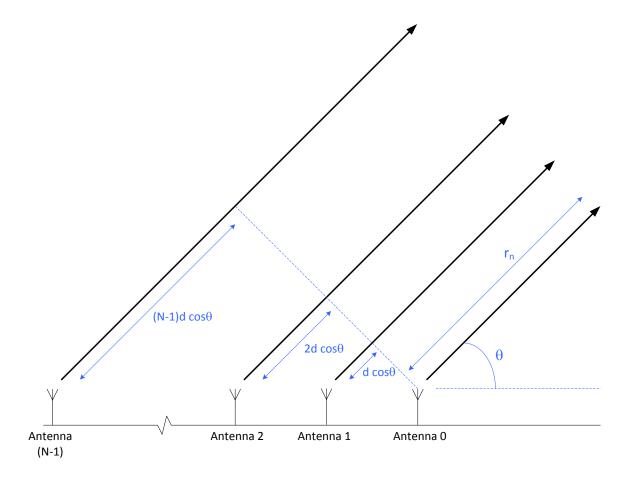

A common example of an adaptive antenna array is the *N-element linear array*. This array is composed of *N* identical omnidirectional antennae that are placed in a linear fashion with an element-to-element spacing of *d*. Figure 2.2 shows an example of this array. For the sake of this example, let us further assume that each element in the array is driven by an equal amplitude excitation, but each element is driven by a progressive phase of  $\phi$ . (i.e. element 1 has a phase of 0, element 2 has a phase of  $\phi$  radians, and so forth, up to element N, which has a phase of  $(N-I)\phi$ . The frequency of excitation is assumed to be fixed, with a wavelength  $\lambda$ , and the *wavenumber*, is defined as the quantity  $k=2\pi/\lambda$  [8]. Lastly, in the far-field, the distance from the observation point to each antenna is almost equal, so that the amplitude of the radiation received from each antenna is equal. For mathematical simplicity, the radiation received from each element is assumed to be 1.

Figure 2.2: N-element linear antenna array (Annotations in blue)

Given these conditions, one can derive the overall antenna pattern as a function of observation angle,  $\theta$ . The total received E-field is the sum of the E-fields received from each individual element.

$$E_{TOT} = \sum_{n=1}^{N} E_n \tag{1.4}$$

The distance from each antenna to the observation point is:

$$r_n = r + (n-1)d \cdot \cos \theta \tag{1.5}$$

The received E-field from each component is:

$$E_n = e^{-j(k \cdot r_n + (n-1) \cdot \phi)} = e^{-jkr} \cdot e^{-j[(n-1)(kd \cos \theta + \phi)]}$$

(1.6)

Plugging (1.6) into (1.4) and simplifying, we get:

$$E_{TOT} = e^{-j\left(kr + \frac{N-1}{2}\psi\right)} \cdot \frac{\sin\frac{N\psi}{2}}{\sin\frac{\psi}{2}}$$

(1.7)

$$\psi = kd\cos\theta + \phi$$

If one ignores the complex phase shift due to the first term in (1.7), the result is termed the *array factor* (AF) of the antenna and describes how the magnitude of the radiation pattern varies based on the observation angle,  $\theta$ . The array factor is:

$$AF = \left[ \frac{\sin\left(\frac{N}{2}\psi\right)}{\sin\left(\frac{1}{2}\psi\right)} \right] \tag{1.8}$$

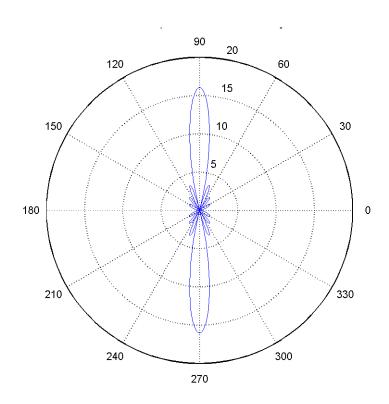

where  $\psi$  is as defined in (1.7). An example of an array pattern is plotted in Figure 2.3. In this example, N=16 antennae are used with a spacing, d, equal to  $\lambda/4$ ;  $\phi$  is set to 0 radians, so  $\psi = \frac{\pi}{2} cos\theta$ .

Figure 2.3: Radiation pattern of linear 16-element array,  $\phi$ =0

The array factor is one of two parameters of an antenna array that determines its overall radiation pattern, and hence its directivity and antenna gain. The other factor is called the *element factor* (or EF), and is the radiation pattern of the individual antenna element used to compose the array. In the linear array mentioned above, the individual antenna are assumed to be 0dBi isotropic radiators. In fact, any antenna type could be used in an array; if a non-isotropic antenna is used, then the overall array radiation pattern is merely a product of the array factor and the element factor [9].

There are two important conclusions to be taken from equations (1.7) and (1.8). The first is that the array pattern is electrically programmable through the choice of the progressive phase,  $\phi$ . In fact, the direction of maximum radiation can be set by enforcing

the condition that  $\psi$ =0. This leads to the condition that:  $\phi_{opt} \triangleq -kd \cdot \cos \theta_{max}$ , where  $\theta_{max}$  is the desired angle of maximum radiation and  $\phi_{opt}$  is the optimal choice for the progressive phasing between antennae. For example, Figure 2.4 shows an antenna pattern where  $\phi$  is set to  $-\pi/4$  and d is  $\lambda/4$  and N=16.

Figure 2.4: Radiation pattern of linear 16-element array,  $\phi = -\pi/4$

As expected, the peak directivity is achieved at  $\theta = +\pi/6$ , or  $60^{\circ}$ . Also, a second directivity peak is achieved at  $\theta = -\pi/6$ , as this is also a solution to the condition stated above. The second important conclusion is that the array factor is limited by the number of antenna used. In fact, solving for  $AF_{max}$  in equation (1.8) yields that the maximum AF achievable is N. Since the array factor is one of two factors that determine antenna gain, the directivity of an array can be increased in one of two ways: either the number of

antennas comprising the array can be increased or the directivity of the individual antenna elements can be increased. The second approach is of limited practicality, as a highly directive antenna element is, by definition, a fixed directive antenna, so its pointing direction cannot be easily modified. Therefore, highly directive antenna arrays that require a reasonable level of control in its pointing angle are typically composed of a large number of low-directionality components. This places a practical limit on the achievable antenna gain that can be implemented, as the complexity of implementing a large number antenna can be difficult. For discussions of techniques to achieve a 60GHz directional antenna array in conventional CMOS technology, see [9].

#### 2.1.3 Performance of a Directional Antenna

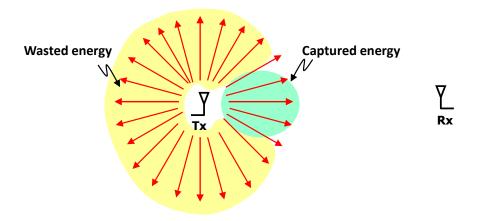

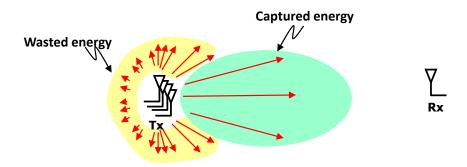

The use of a directional antenna has two significant impacts on the overall characteristics of a wireless link. First, as described in the previous section, the directivity of an antenna (when properly aligned) gives additional gain to the signal over the wireless link. Figure 2.5 and Figure 2.6 give a graphical explanation of the cause of the increased antenna gain.

Figure 2.5: Graphical depiction of energy transmitted using omnidirectional antenna

In Figure 2.5, a wireless link is shown where both the receiver and the transmitter use omnidirectional antennae. Since the transmitter radiates energy equally in all directions, much of the transmitted energy is wasted and a relatively small fraction of the transmitted power reaches the receiver. This can be contrasted to the situation in Figure 2.6, where a directional transmit antenna is used. When properly aligned, the transmit antenna radiates a larger fraction of its total energy in the direction of the receive antenna, thereby increasing the total energy transmitted across the wireless link. The gain in received signal energy is exactly the directivity gain discussed in the previous section.

Figure 2.6: Graphical depiction of energy transmitted using directional antenna

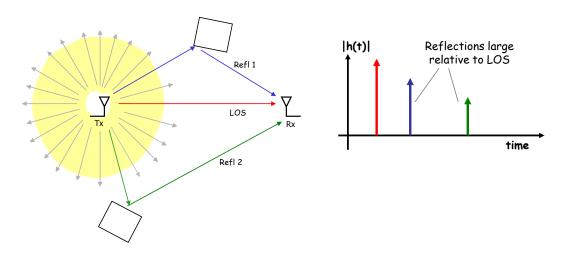

Figure 2.7: Graphical depiction of channel multipath using omnidirectional antenna

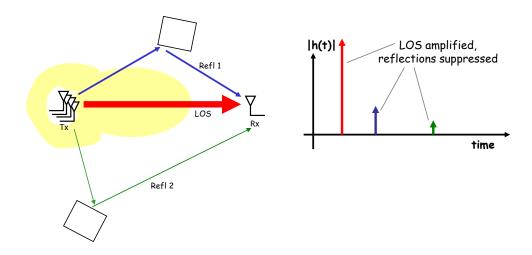

The use of a directional antenna also has significant impact on the nature and severity of the channel multipath. Multipath is caused the by reflection of the transmitted energy of off various objects in the vicinity of the wireless link; in indoor channel, reflections may be caused by walls, surfaces such as tables, floors, or ceilings, and various clutter in the local environment. In the graphical depiction of Figure 2.7, omnidirectional antenna are used; the channel has significant multipath due to the strong reflections off of objects near the transmitter or receiver. In Figure 2.8, a directional antenna is used for the transmitter. The directional antenna limits the spatial extent of the signal to the desired path. The same reflections occur as in the previous case, but now more energy is transmitted in the desired path and less energy in these unwanted reflective paths. As a result, the extent of the multipath can be significantly reduced.

Figure 2.8: Graphical depiction of channel multipath using directional antenna

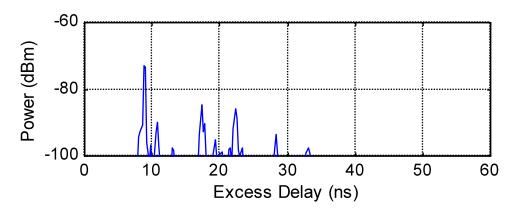

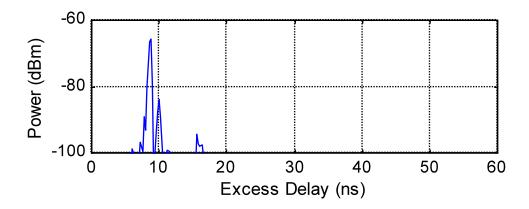

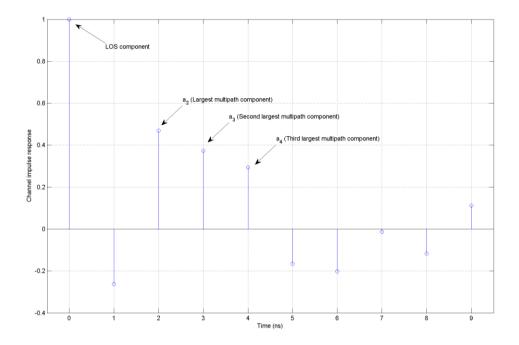

Measurements at HP Labs [11] confirm this behavior. Figure 2.9 shows a sample indoor channel impulse response with a omnidirectional RX antenna, and Figure 2.10 shows the sample impulse response when an RX antenna with moderate directionality (90° HPBW) is used. Comparison of the two plots shows that the LOS path (at about 9ns) is amplified by roughly 5-10dB and the multipath reflections (at 18 and 22ns) are suppressed by over 15dB.

Figure 2.9: Measured channel impulse response with omni RX antenna (from [11])

Figure 2.10: Measured channel response with 90° HPBW RX antenna (from [11])

Several studies have been conducted on the effect of antenna directivity on 60GHz indoor channel multipath. The results of these studies are summarized in section 2.3. Of note is the fact that moderately directive antennae can have a very significant impact on reducing the channel multipath [10], [12], [11], [13]. Therefore, when directive antennae are used, complex techniques for combating multipath—such as OFDM—might no longer be necessary. This opens up the system design to alternative approaches that can enable high data-rate systems to be built without requiring the high-performance RF components that OFDM systems typically require.

# 2.2 Key Characteristics of the 60GHz Channel

The 60GHz channel has some unique characteristics that differ significantly from the characteristics of communications channels in the low-GHz regime. Some of these differences stem from basic electromagnetic or material properties (e.g. oxygen absorption) whereas some of these differences are caused by extrinsic factors such as regulatory issues or practical issues regarding device form factor.

#### 2.2.1 Reduced Performance of CMOS mm-wave Components

In order to enable widespread adoption of 60GHz wireless communications, the transceivers must be fabricated in a low-cost, highly integrable technology such as CMOS. While 60GHz radios have been demonstrated in other technologies such as SiGe [14] and GaAs HBT [15], the goal of the research at the BWRC has been to demonstrate a 60GHz radio entirely in CMOS. Due to the lower electron mobility in silicon, however, CMOS suffers a performance penalty at microwave frequencies when compared to these other semiconductor materials operating at 60GHz or when compared to CMOS operating in the low-GHz regime. Also, the lower breakdown voltage of deep submicron CMOS limits the power handling capabilities the devices; therefore, microwave CMOS power amplifiers (PA's) have reduced output power. Table 2.1 compares reported performance metrics of some key transceiver components for three different cases: CMOS operating at 60GHz, SiGe operating at 60GHz, and CMOS operating at 2.4GHz. The results indicate that the RF components available at 60GHz in CMOS do not match those in SiGe; nor does CMOS performance easily scale from the low-GHz regime up to 60GHz. While continued scaling of CMOS technology will likely enable higher performance 60GHz components, the system design needs to take into account the limited performance of the currently available components. The increased noise figure of the LNA will limit the SNR at the receiver; the limited power handling capability of the PA will limit the received power and may also increase the nonlinear distortion created at the transmitter; the extra phase noise from the VCO can create reciprocal mixing or cause symbol jitter that will impact receiver sensitivity.

| Component | Specification          | CMOS @ 60GHz             | SiGe @ 60-77GHz          | CMOS @ 2-5GHZ             |

|-----------|------------------------|--------------------------|--------------------------|---------------------------|

| LNA       | Noise Figure           | 8.8dB [16]               | 5.7dB [17]               | 4dB [18]                  |

|           | Gain                   | 12dB                     | 23dB                     | N/A                       |

| VCO       | Phase noise            | -85dBc/Hz @<br>1MHz [19] | -95dBc/Hz @<br>1MHz [20] | -116dBc/Hz @<br>1MHz [21] |

| PA        | 1dB<br>compression     | +9dBm [22]               | +14.5dBm [23]            | +24.5dBm [24]             |

|           | Power-added efficiency | 8.8%                     | 12.8%                    | 31%                       |

Table 2.1: Comparison of reported performance of key transceiver components

The focus of the work presented in this dissertation is the baseband system architecture and circuit design, so the poor performance of CMOS at 60GHz does not directly impact the circuits presented herein. However, the system and baseband architecture of a 60GHz receiver must be robust under these limited circuit performance constraints. Therefore, a key challenge that this research addresses in chapter 3 is determining the techniques and approaches to implementing a very high-performance wireless link with limited performance RF components.

## 2.2.2 Oxygen Absorption and Material Penetration

It is known that oxygen molecules interact with microwave frequencies between approximately 50GHz and 70GHz [25]. As a result, atmospheric oxygen absorbs microwave radiation in the 60GHz band, resulting in excess attenuation of the transmitted signal by as much as 15dB/km at sea level [26]. Since this attenuation is in addition to the Friis path loss discussed in section 2.2.3, oxygen absorption severely limits the applicability of 60GHz communications to many long-range applications. However, for indoor, short-range applications such as WLAN or point-to-point media streaming, the O<sub>2</sub>

absorption issue has little significance. For instance, a 100m transmit distance would only suffer from only 1.5dB of O<sub>2</sub> absorption; however, the Friis path loss equation [see equation (1.9)] predicts a path loss of 108dB over a similar distance, assuming 0dB antenna gain.

It is interesting to note that the  $O_2$  absorption issue has actually been embraced by some applications. In high-data rate applications where a low probability of intercept is required,  $O_2$  absorption can help prevent the signal energy from propagating significantly beyond the desired receiver, preventing other unwanted receivers from receiving the signal. An example of this is satellite-to-satellite communications: as the concentration of oxygen rapidly decreases with altitude above sea-level, the signal attenuation due to oxygen absorption in the satellite-to-satellite link is negligibly small. However, the signal energy would be drastically attenuated as it propagated through earth's atmosphere towards sea level; as a result, earth-based eavesdropping on these satellite links would be extremely difficult.

Of more significance to indoor communications are the transmissivity and reflectivity of common indoor building materials with respect to 60GHz radiation. As will be discussed in more depth in section 2.3.1, certain building materials are significantly more opaque to 60GHz radiation than to signals at lower frequencies Measurement campaigns comparing the material transmissivity at 60GHz to that of 2.5GHz [27], 1.7GHz [28], and 5.85GHz [29]all show that many common building materials have higher penetration loss and lower reflectivity at 60GHz than at these lower frequencies.

As a result of the poor material transmission at 60GHz, partitions in an indoor environment act as isolative boundaries between neighboring areas in a single building. As an example, [30] has determined that the material attenuation through a standard wood door would be more than 16dB. Similarly, measurements conducted at the BWRC, showed that typical interior wall and flooring constructions can block 60GHz attenuation by as much as 24dB. Therefore, partitions in indoor structures, such as walls and floors, prevent appreciable signal energy from propagating from one room to adjacent rooms.

The implications of these findings are threefold: First, unlike low-frequency WLAN systems such as 802.11a/b/g/n, a 60GHz wireless system is not well-suited to the typical residential deployment model, where a single basestation is used to serve many mobile clients scattered throughout the house. The attenuation suffered at 60GHz by propagating through one (or more) interior walls or floors is likely to add too much path loss to make high-bandwidth communications feasible. A corporate setting, however, would be more conducive to a 60GHZ WLAN deployment, as a ceiling-mounted basestation could serve several mobile clients without suffering from material penetration issues, provided that the internal structure of the office was more akin to a "cubicle farm" than several distinct office rooms.

A second consequence of the poor material penetration at 60GHz is a corollary of the first: since walls and floors prevent signal energy from spilling out of one room into the next, each room naturally becomes its own microcell. Furthermore, since the structural partitions isolate the adjacent cells from one another, frequency reuse can be aggressively exploited. In other words, each cell can utilize a large fraction (or perhaps

the entirety) of the 7GHz of available spectrum without worrying about intercellular interference. As a result, typical concerns of spectrum efficiency are mitigated, since the opportunities for frequency reuse are significant.

Lastly, the poor material penetration of 60GHz radiation has an effect on the nature of the multipath present in the indoor channel. Most notably, even with omnidirectional antennae, the delay spread of 60GHz indoor channels tends to be smaller than that of lower frequency channels. The path length of multipath reflections are necessarily shorter at 60GHz, since the reflections of sufficient energy can only come from in-room objects [27], [31], [32]. In [31], the delay spread of several different interior structures were measured at both 1.7GHz and 60GHz. In all cases, the delay spread measured at 60GHz was between two to four times smaller than that measured at 1.7GHz.

## 2.2.3 Path Loss and Antenna Directionality

The Friis path loss equation describes the free-space path loss incurred by an electro-magnetic wave as it propagates from a transmitter to a receiver. The Friis path loss equation is:

$$L = \frac{P_{RX}}{P_{TX}} = \frac{G_{TX}G_{RX}c^2}{f_c^2(4\pi d)^2} = \frac{G_{TX}G_{RX}\lambda^2}{(4\pi d)^2}$$

(1.9)

where  $P_{TX}$  and  $P_{RX}$  are the power at the transmitter and receiver, G is the antenna gain,  $f_c$  is the carrier frequency,  $\lambda$  is the carrier wavelength, d is the propagation distance. Note that the convention used here defines L as the ratio of the power received to the power

transmitted. Hence, L is by definition less than or equal to 1 and a smaller value of L indicates a larger amount of path loss..

The Friis path loss equation can be viewed as a power flux equation; the total power exiting a sphere (or any other three-dimensional shape) is independent of the size or position of the sphere but instead must be equal to the total power being radiated by transmitters within that sphere. Therefore, it comes as no surprise that the free-space path loss increases with the square of the propagation distance. Furthermore, it can be shown that the antenna gain, G, is proportional to the antenna area, A, as follows:

$$G \propto \frac{A}{\lambda^2} \tag{1.10}$$

The power flux argument becomes clear if it is assumed that the transmitter is an omnidirectional source (i.e.  $G_{TX}=1$ ) and the expression from (1.10) is used for  $G_{RX}$ . The path loss equation becomes:

$$L \propto \frac{A_{RX}}{(4\pi d)^2} \tag{1.11}$$

where  $A_{RX}$  is the area of the receive antenna. Equation (1.11) shows that the power captured by the receiver is proportional to the surface area of the sphere subtended by receiver antenna; hence the power flux argument becomes obvious.

The Friis equation as shown in (1.9) has led many to conclude that the path loss irrevocably gets worse as the carrier frequency increases [33], [34]. In fact, a direct application of the Friis equation can lead to the conclusion that a 60GHz communications

channel has 22dB more loss than an otherwise identical 5GHz communications channel. This conclusion is somewhat misleading, however, as the additional path loss incurred at higher frequencies is not due to some fundamental effect, but is primarily a consequence of the assumption that antenna gain is a fixed constant independent of frequency. (Typically it is assumed to be 0dB for the case of an omnidirectional antenna.) As indicated by equation (1.10), the area of an antenna *of a fixed gain* scales inversely with frequency. Thus, by the power flux argument of the preceding paragraphs, an antenna of fixed gain will be physically smaller at higher frequencies and will thus capture a smaller fraction of the total radiated power.

The antenna gain, however, is not constrained to be a fixed constant or somehow limited by some a priori fundamental constraint. A more likely constraint is the overall size of the antenna aperture, as physical parameters, such as the size of the wireless device, places an upper-bound on the overall area that can be devoted to the antenna [35]. If it is assumed that the antenna area, *A*, for a given device is fixed, the Friis equation takes the following form:

$$L \propto \frac{A_{TX}A_{RX}}{\lambda^2(4\pi d)^2} \tag{1.12}$$

where  $A_{TX}$  is the area of the transmit antenna. Now it seems as if the path loss gets more benign as frequency increases, in direct contradiction of equation (1.9). From this, one might conclude that the use of higher carrier frequency and higher antenna gain provides a potentially unlimited benefit. In the example comparison between a 60GHz system and a 5GHz system, it now appears that the 60GHz system could achieve an improvement in

channel gain (and hence, SNR) of 22dB! Unfortunately, such an optimistic scenario is not the case either; since an antenna is a passive device, increasing the gain of an antenna can only be achieved by increasing its directionality. As was discussed in section 2.1, directionality can provide many benefits to wireless communications—including the increased antenna gain described here—but it also presents several significant implementation challenges. In particular, the system complexity required to properly produce and align a directional array pattern grows significantly as the antenna gain is increased.

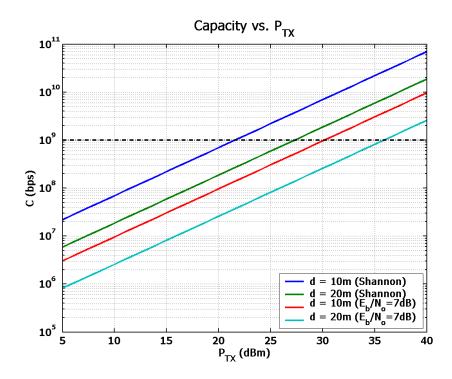

Therefore, it remains to be determined what kind of antenna is suitable for a 60GHz system. The benefit of an omnidirectional antenna is the simplicity of this approach: no additional hardware is necessary in order to create a directional, high-gain antenna pattern, and no scheme to align the pattern is required either. However, the increased path loss suffered at high frequency with an omnidirectional antenna would limit the capacity of the wireless link. An upper-bound of the channel capacity can be approximated using the Shannon capacity calculation for an AWGN channel. The Shannon capacity limit gives the maximum theoretical error-free capacity that can achieved through a channel using arbitrarily complex coding schemes [36]. The Shannon capacity is:

$$C = BW \log_2 \left( 1 + \frac{P_{RX}}{BW N_0} \right) \tag{1.13}$$

where C is the channel capacity in bits/sec, BW is the channel bandwidth is Hz, and  $N_0$  is the input-referred noise level at the receiver in W/Hz. In the case of 60GHz communications, the bandwidth is sufficiently large such that it can be approximated as infinite. Given that approximation, equation (1.13) simplifies to:

$$\lim_{BW \to \infty} C = 1.44 \frac{P_{RX}}{N_0} \tag{1.14}$$

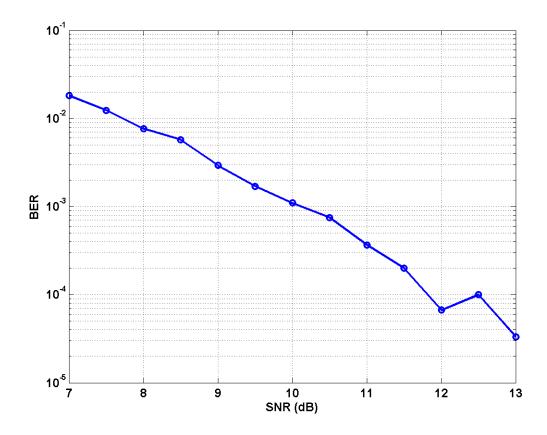

Equation (1.14) can be used to as an upper-bound to determine the theoretically maximum capacity that can be achieved. A more conservative approximation of channel capacity can be based on the observation that common modulation schemes (e.g. BPSK, QPSK, and MSK) require a minimum receiver SNR in order to get a reasonable uncoded error rate. For these modulations schemes, in order to get an uncoded BER on the order of 10<sup>-3</sup>, an SNR at receiver of roughly 7dB is required.

Using the Shannon capacity limit or the 7dB SNR requirement, the capacity of an omnidirectional 60GHz link as a function of transmit power can be determined. Figure 2.11 shows such a plot for a transmit distance of 10m and 20m. In this plot, it is assumed that the receiver has an overall noise figure of 10dB, and there are 10dB of losses from miscellaneous sources such as shadowing loss, board losses, and implementation loss. According to the Shannon capacity limit, the transmitter would require 23dBm (200mW) transmit power to achieve a capacity of 1Gbps at 10m; according to the more realistic 7dB SNR criterion, the transmitter would have to output 30dBm (1W) of power to achieve this capacity! As shown in section 2.2.1, 60GHz power amplifiers with these power levels are simply unrealizable in commercially available CMOS technologies. Therefore, in order to realize a 10m, Gbps link at 60GHz, the path loss dictates that directional antennae are a requirement.

Figure 2.11: Link capacity vs. transmit power for omnidirectional antenna

## 2.2.4 Feasibility of a High Directionality Antenna

The previous sections demonstrate that the increased path loss at 60GHz and the limited performance of 60GHz CMOS circuits necessitate the use of directional antennae. Luckily, at 60GHz the use of directional antennae becomes much more practical than at lower frequencies. As discussed in section 2.2.3, the area required for an antenna of a particular gain is inversely proportional to the square of the carrier frequency. For instance, a rectangular aperture antenna with 12dBi directivity could be synthesized in a 5mm x 5mm area at 60GHz, whereas a similar antenna at 2GHz would be 16.8cm on a side [8]. Therefore, for small form-factor mobile devices where PC board real estate is at

a premium, operating at 60GHz allows for the use of directional antennae that would be prohibitively large at lower frequencies.

## 2.2.5 Regulatory Issues and Spectral Efficiency

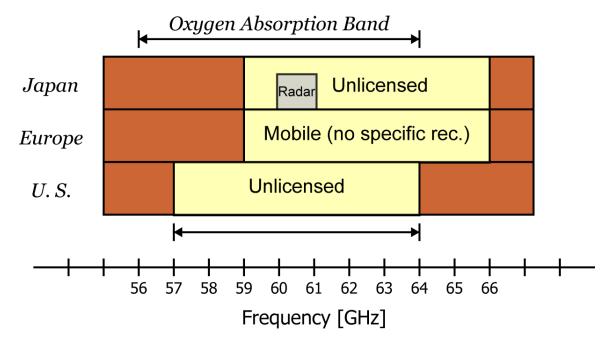

In 1995, the FCC allocated the spectrum from 59GHz to 64GHz as an unlicensed, band [3]. Shortly thereafter, the FCC amended their rules to extend this unlicensed band to 57-64GHz, thus providing 7GHz of unlicensed spectrum for general purpose use [4]. Furthermore, regulatory bodies across the globe have also set aside multi-GHz blocks of spectrum at 60GHz for unlicensed use; Japan has allocated 59-66GHz as an unlicensed band and Europe has allocated 57-66GHz. (See Figure 2.12 for the allocation of unlicensed spectrum in various world-wide regions.)

Figure 2.12: Worldwide allocation of unlicensed spectrum around 60GHz

The presence of a true multi-GHz worldwide band has sparked immense commercial interest in developing 60GHz communications links. Commercial issues aside, the availability of such a large bandwidth at 60GHz also has some profound technical implications as well. With such a wide bandwidth available for communications, bandwidth scarcity is no longer an issue, and spectral efficiency is no longer a parameter of utmost importance. Therefore, the system is free to explore schemes that trade-off circuit or system complexity for spectral efficiency.

In sharp contrast, the evolution of the 802.11 standard from .11b to .11a/g to .11n was driven primarily by the desired to "cram" more throughput through a fixed 20MHz channel bandwidth. As the standard evolved, the spectral efficiency went from roughly 0.5b/sec/Hz for 802.11b to upwards of 10b/sec/Hz for some draft .11n proposals. With this increase in spectral efficiency, however, comes a dramatic increase in the specifications of the analog and RF components. With higher spectral efficiency, higher SNR's are required, which in turn mandates higher performance components: the noise figure on the LNA must be reduced; the phase noise of the oscillator must be improved; and the linearity of all the components—most notably the power amplifier—must be dramatically improved.

However, as discussed in section 2.2.1, the current state of 60GHz CMOS circuits does not display the kind of performance necessary for a system with high spectral efficiency. Therefore, designing a 60GHz system with low spectral efficiency becomes not just a choice, but a *necessity*.

#### 2.3 Literature Review of 60GHz Channel Studies

Recent interest in 60GHz communications has led to a number of studies of the properties indoor 60GHz channel in an effort to both better understand the nature of the 60GHz channel and to characterize it is an accurate, yet compact, manner. The studies published in literature fall into one of two categories: measurement-based campaigns and simulation campaigns based using ray-tracing tools. Each technique has their own set of advantages and complement the other. Measurement-based campaigns generate the required physical data of 60GHz propagation, transmission, and reflection that form the basis of any understanding of the 60GHz channel. However, measurement campaigns are labor-intensive and as a result are limited in their scope and in the diversity of physical environments measured. Simulation-based campaigns can build upon the measurement campaigns by applying the propagation and material properties discerned from these earlier studies and quickly and easily applying them to a variety of physical environments and room geometries. As will be discussed below, these studies indicate that the indoor channel properties are heavily dependent on room geometry and configuration, so a wide variety of environments need to be simulated. As mentioned above, channel simulations generally have used optics-based ray-tracing tools to simulate the wave propagation and generate a deterministic channel model for a particular environment [10]. One limitation for ray-tracing simulators is that they typically do not model diffusion, diffraction or other scattering mechanisms; however, many studies of the 60GHz channel indicate that the these scattering mechanisms typically do not occur in 60GHz indoor channels and

that a ray-traced simulation with only specular reflections will produce valid data [37], [38], [39].

## 2.3.1 Material Properties

Many of the measurement studies characterize the reflectivity and transmissivity of common indoor building materials. The transmissivity of a material is typically specified as the transmission loss (in dB/cm) that 60GHz radiation incurs while propagating through a given distance of that material. The reflectivity of a material is typically specified as the loss incurred by reflecting off the surface of that material. Table 2.2 below summarizes the material property measurements of a few measurement campaigns.

|                   | <b>Ref</b> [37 | ]    | Ref [11] | <b>Ref</b> [30] | Ref [27] | <b>Ref</b> [38] |

|-------------------|----------------|------|----------|-----------------|----------|-----------------|

| Material          | Trans          | Refl | Refl     | Trans           | Trans    | Trans           |

|                   | (dB/cm)        | (dB) | (dB)     | (dB/cm)         | (dB/cm)  | (dB/cm)         |

| Concrete          | >6             | 6.5  | N/A      | 6.67            | N/A      | 6.7             |

| Plasterboard      | 2              | 5.5  | 14.8     | 1.5             | 2.4      | N/A             |

| Wood              | 6.3            | 18   | 14       | 4.2             | N/A      | 4.2             |

| Chipboard         | N/A            | N/A  | N/A      | 5.15            | N/A      | 5.1             |

| Acrylic glass     | 4.2            | 5.5  | 7.3      | 1.03            | N/A      | N/A             |

| Glass             | 5.1            | 12   | N/A      | 5.05            | 11.3     | 6.03            |

| Wire-mesh glass   | >14            | 3    | N/A      | N/A             | 31       | N/A             |

| Office whiteboard | N/A            | N/A  | N/A      | N/A             | 5        | N/A             |

Table 2.2: Transmission and reflection loss of common building materials at 60GHz

A few conclusions can be reached by looking at the table above. First, material transmission at 60GHz is poor, particularly through exterior structural elements such as concrete and wood. Therefore, 60GHz communications is not suitable for short-range building-to-building links where LOS is not guaranteed. Even in indoor environments with most building materials of typical thickness, room-to-room isolation is usually

greater than 20dB [30]. Therefore, 60GHz links seem most suitable to single-room environment, and a microcellular approach utilizing a high degree of frequency reuse is realizable.

Additionally, non-metallic building materials tend to be poor reflectors of incident 60GHz radiation. With the exception of wire-mesh glass and tiles, all of the 32 materials tested in [37] had a reflection loss greater than 5dB, with typical losses exceeding 10dB. As a result, the amplitude of most multipath reflections in 60GHz channels will be relatively small. For example, the extensive measurements in [12] conclude that in the absence of strong reflectors, "the reflected multipath components are at least 10dB below the LOS component." Similarly, in [31], the delay spread of several different interior structures were measured at both 1.7GHz and 60GHz. In all cases, the delay spread measured at 60GHz was between two to four times smaller than that measured at 1.7GHz. Additional measurements of 60GHz indoor channel properties are discussed in the next section.

## 2.3.2 Channel Properties

The aim of the measurement and simulation campaigns summarized here was to extract meaningful properties of the 60GHz channel. While the exact metric extracted differed from study to study, the metrics can be roughly grouped into the following categories:

• Temporal characterization of channel multipath: A variety of metrics were extracted to determine the temporal characteristics of the channel

- multipath. Some metrics included RMS delay spread ([10], [38], [40], [12] [41]) Rician k-factor ([40], [10], [11]) and 90% settling time ([11]).

- Spatial characterization of channel multipath: Some of the studies characterized the spatial nature of the 60GHz channel multipath. For instance, [12] conducted extensive spatial measurement using highly directional antenna to extract angle of arrival information. Other studies ([10], [11], [13], [42], [43]) measured the impact of antenna directivity, alignment, and polarization on the temporal properties of the multipath channel.

- Path loss: Most studies conducted a set of location-specific path loss measurements. For instance, [12] reported the path loss as a function of distance in an interior corridor. This is the simplest metric extracted, and while it provides the least level of detail, the overall path loss in an indoor environment is of crucial importance.

# 2.3.2.1 RMS delay spread and Rician K with Omnidirectional Antennae

The two most relevant temporal metrics of the 60GHz multipath channel are RMS delay spread and Rician k-factor. The RMS delay spread, *R*, is a power-weighted measure of the temporal duration of the multipath reflections and is defined as follows:

$$R = \sqrt{\frac{\sum_{k=1}^{N} (\tau_k - t_a)^2 a_k^2}{\sum_{k=1}^{N} a_k^2}}$$

$$t_a = \frac{\sum_{k=1}^{N} \tau_k a_k^2}{\sum_{k=1}^{N} a_k^2}$$

(1.15)

where N is the number of multipath components,  $\tau_k$  is the arrival time of the kth multipath ray,  $a_k$  is the amplitude of the kth multipath ray, and  $t_a$  is power-weighted average arrival time. High RMS delay spreads indicate channels whose multipath is significant over longer periods of time; hence, channels with low R relative to the symbol period have less intersymbol interference to contend with.

The Rician k-factor, K, is a ratio of the power in the dominant (LOS) signal path versus the total power in all other multipath components. Hence, K, is defined as:

$$K = \frac{a_{\text{max}}^2}{(\sum_{k=1}^N a_k^2) - a_{max}^2}$$

(1.16)

A high K is indicative that most of the received power is contained in the dominant LOS component; hence the eye diagrams of high-K channels are cleaner and "more open". Higher K's are desirable since they indicate a lower probability of degradation from multipath.

Many studies have measured and analyzed the RMS delay spread (RDS) of typical indoor 60GHz channels. [44] measured the delay spread in several typical indoor environments with omnidirectional antenna and found that over all environments (including both LOS and NLOS situations), RDS fell within the range of 15-100ns. Furthermore, the RDS was a strong function of the physical environment; as expected, rooms with highly reflective walls had much higher RDS than rooms with those with less

reflective walls. For example, a "lecture hall" with concrete and wood walls gave RDS measurements in the range of 15-25ns, whereas a "computer room" with smooth metal walls had an RDS between 40 and 50ns. The campaign in [45] expanded this study to measure the impact of room size on RDS. The three rooms mentioned above were considered "small rooms", each with dimensions of roughly 35 x 32 x 10 ft. A larger room, with dimensions of 140 x 133 x 23, had a delay spread between 50 and 70ns. The longer delay spread of larger rooms is expected; since typical wall material is poorly reflective at 60GHz, multipath components will only persist for a few "bounces" before dying out. Therefore, the multipath components in a larger room will have a later arrival time with respect to those in a smaller room.

The ray-tracing campaign in [46] corroborates the results above. Omnidirectional antenna were used and the room size was roughly 80 x 32 ft. Delay spread was about 10-12ns with a transmit distance of 10m and line-of-sight (LOS). Furthermore, the delay spread was proportional to transmit distance; as the transmit distance was decreased to 2m, RDS decreased to about 2-4ns. Once the LOS path was blocked, however, simulated RDS increased to 40-50ns. The Rician K-factor (RKF) was also simulated and was found to decrease with increasing transmit distance; at 2m, K was roughly 10-15dB and at 10m K was 6-8dB under LOS conditions.

Williamson, et al conducted a similar ray-tracing campaign of a typical office environment in [10]. This study included the effect of office partitions causing blockage to the LOS path. The omnidirectional transmitter was in a fixed location in the room, and the omnidirectional receiver was located at various points in the room. Including both

LOS and NLOS configurations, the median delay spread was roughly 23ns and 90% of locations has a delay spread of less than 27ns. The median Rician K-factor was roughly 5dB and 90% of locations had a RKF of 1dB or better.

The author later conducted a channel measurement campaign at Hewlett Packard Laboratories [11]. While the office environment under investigation was different from that studied in his previous work, the measured results were largely in line with those from [10]. In this study, an omnidirectional RX antenna was used, and the TX antenna had a 90° HPBW; also LOS was maintained for all measurements. The median delay spread was 10ns and 90% of locations has a delay spread of less than 15ns. The median Rician K-factor was roughly 4dB and 90% of locations had a RKF of 1dB or better.

# 2.3.2.2 Channel Spatial Characteristics and the Impact of Antenna Directivity on Delay Spread and Rician K

As discussed qualitatively in section 2.1, directive antennae have to potential to reduce channel path loss and to reduce channel multipath. Reducing path loss leads to higher received power, and reducing channel multipath leads to lower delays spread and higher Rician K. As with the studies presented in the previous section, the exact impact of antenna directivity is a strong function of the physical environment under study, but definite trends can be observed across a wide range of measurements.

-

$<sup>^{1}</sup>$  Note that these statistics indicate that 40% of the locations in the room has a delay spread between 23ns and 27ns.

The Williamson report [10] mentioned above also performed the ray-tracing simulations of the same office environment assuming directional antenna at the TX and RX. With both antennae having a 60° HPBW (12 dBi), the median delay spread reduces to roughly 6ns and 90% of locations have an RDS less than 13ns. Similarly, the median Rician K is 18dB and 90% of locations have an RKF better than 7dB. Antenna alignment is shown to be important, but provided that the misalignment is less than 30% of the HPBW, no performance degradation is noticeable. If misalignment is equal to the HPBW, then the delay spread will roughly double and Rician K will plummet by as much as 10-15dB. The measurements later conducted at HP Labs [11] corroborate these simulation results; again, the office environments are different, and different antenna configurations are used, but the results are largely in line. A setup where the TX antenna is omnidirectional and the RX antenna has a 90° HPBW yields a median delay spread of 10ns, and 90% of the RDS values are below 15ns.

Smulders et al [13] also performed ray-tracing simulations with antennas of varying directivity. TX and RX antennas with 10°, 30°, and 60° (corresponding to 25dBi, 16dBi, and 9dBi) were used. In LOS environments, the 7dBi configuration has an RDS of less than 7ns, and the 25dBi configuration has an RDS of less than 1ns. However, 5° misalignment of the 25dBi antenna can cause RDS to increase to roughly 10ns and can cause a reduction in received power by as much as 25 to 30dB.

Xu, Rappaport, et al [12] conducted an extensive study of the spatial characteristics of the 60GHz indoor channel in a typical office/university environment. They used a highly directional RX antenna and, at each location measured, rotated the RX antenna in

a complete circle and measured the channel properties at each rotation angle. They performed the measurement in both intra-room and inter-room scenarios in order to extract LOS and NLOS characteristics, respectively. When the antenna were properly aligned, the RDS in all of their LOS and NLOS measurements ranged from 5ns to 20ns; however, when alignment was not guaranteed, the RDS roughly doubled. Also, they defined a spatial peak-to-average ratio, where the peak power was defined as the maximum power received during a particular spin measurement (i.e. at proper antenna alignment), and the average power was defined as the average power received over all rotation angles in that spin measurement. The PAR reported for most measurements was in the range of 12 to 14dB. This PAR metric can be viewed as the average amount of available RX antenna gain that is lost if the RX antenna is improperly aligned. Therefore, it becomes clear that antenna alignment is critical if the antenna gain is needed to maximize the received power.

## 2.3.3 Summary of Literature Review

A few key points about the 60GHz channel can be culled from the wealth of data available in the literature. They are summarized below:

• Common building materials significantly attenuate 60GHz transmission.

Many indoor building materials are relatively opaque to 60GHz signal radiation, especially when compared to lower frequencies. In the absence of a strong reflective path, the extra path loss incurred in NLOS environments would significantly degrade the overall performance of the wireless link.

- of metallic objects, most other building materials do not reflect 60GHz radiation very well. Also, the reflections tend to be specular in nature, rather than diffuse. As a result, the multipath at 60GHz will be smaller than the multipath at lower frequencies.

- **Configurations with omnidirectional antennae will require additional techniques to mitigate multipath, even in LOS conditions**. Delay spreads with omnidirectional antenna were measured in the range of 15-50ns in LOS conditions. Rician K-factors in the 1 to 5dB range would be common. When compared to the desired data rate of 1GB/s, the delay spread is big enough that significant efforts would be required to compensate the multipath. For instance, an OFDM approach would require over 100 subcarriers, and an equalizer might require over 100 taps.

- Directional antenna can significantly decrease the channel multipath.

Moderately directive antennae (6 to 12dBi) can reduce the delay spread below

10ns and maintain a Rician K above 10dB, even in some NLOS scenarios. Highly

directive antennae (16dBi and above) can further reduce the delay spread to 1 to

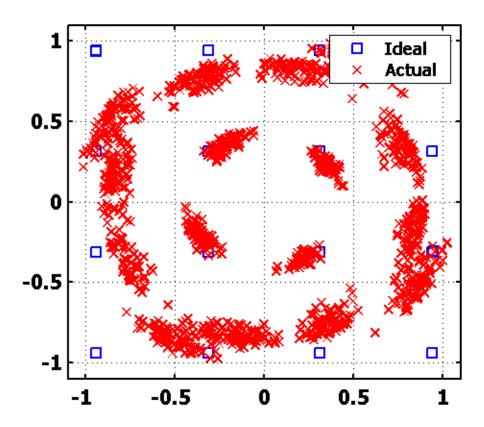

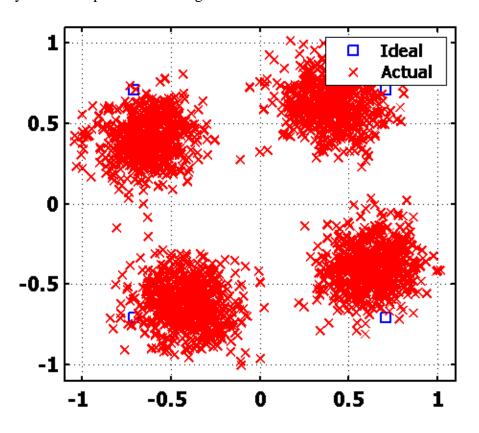

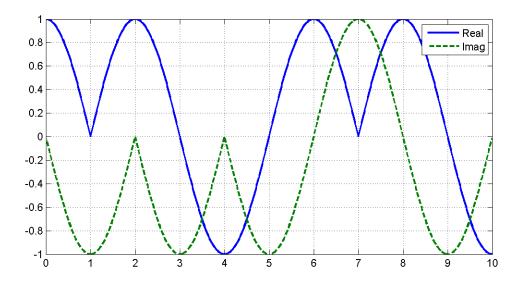

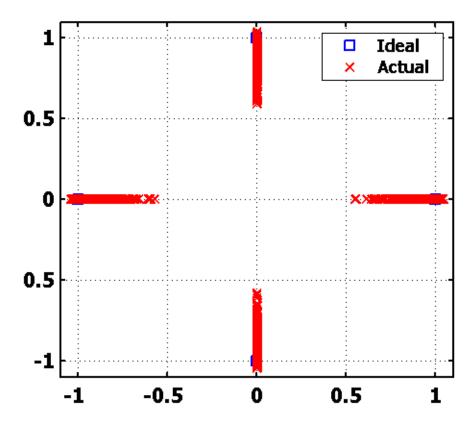

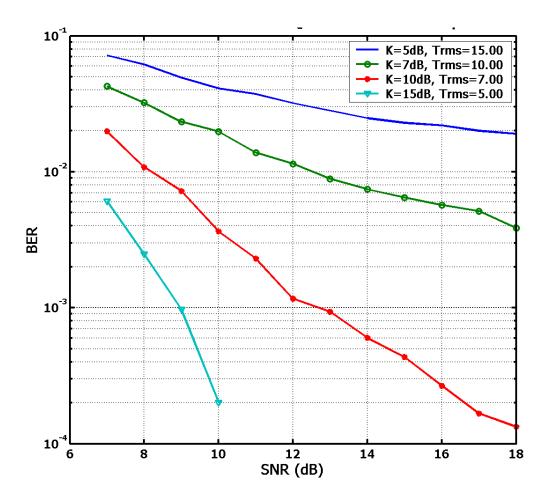

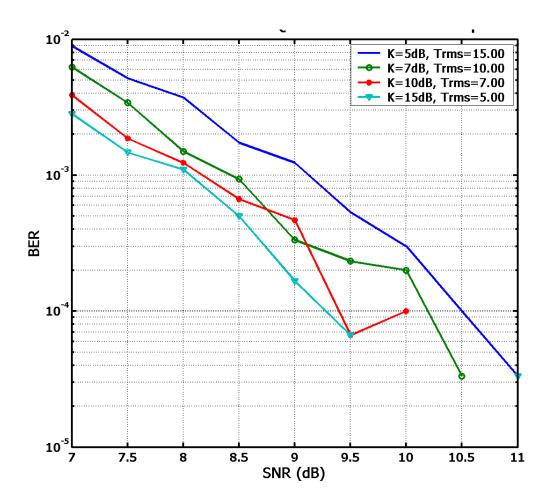

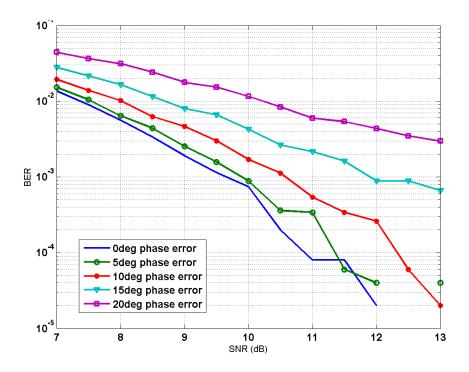

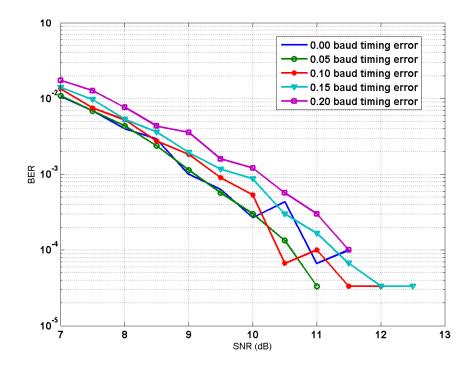

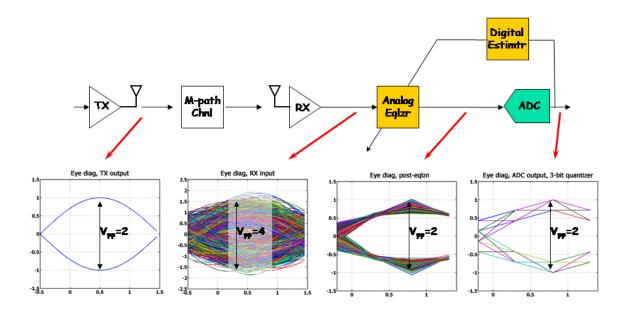

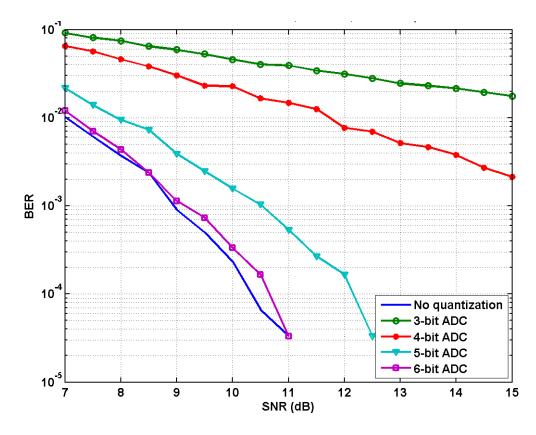

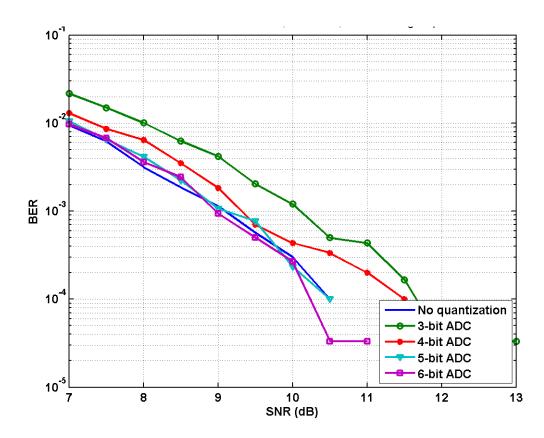

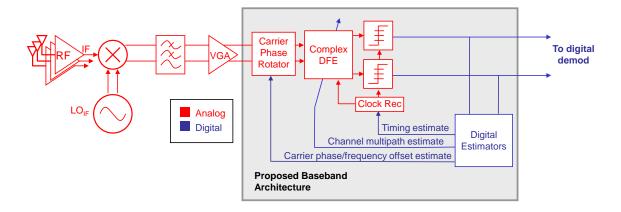

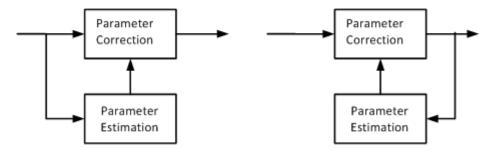

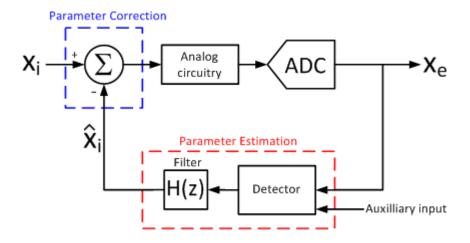

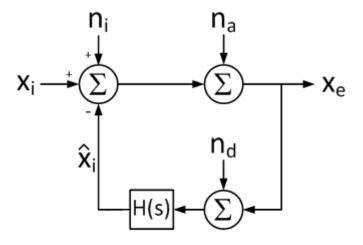

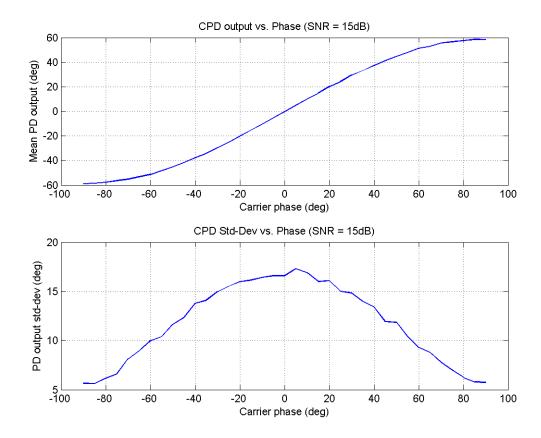

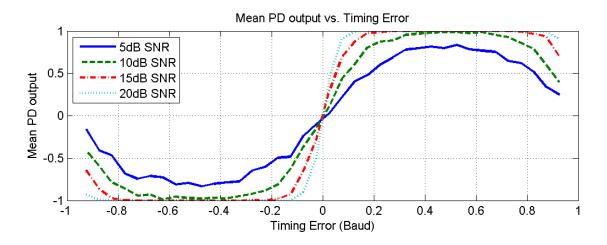

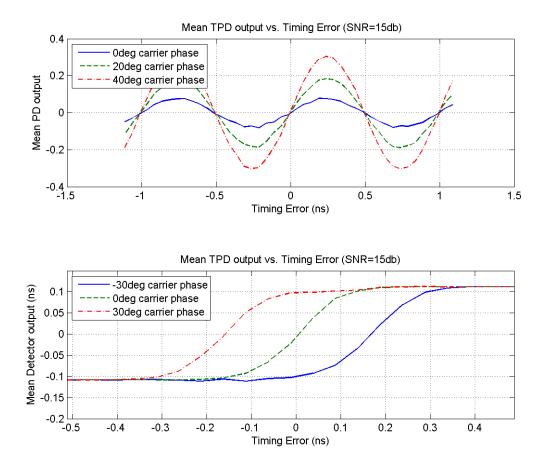

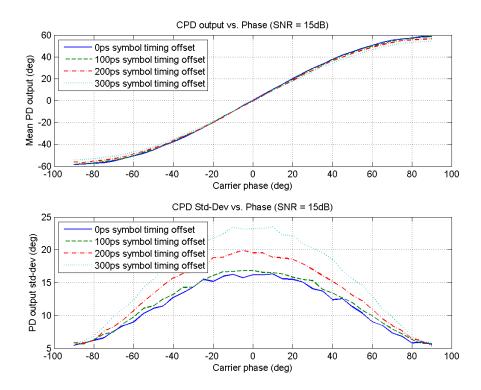

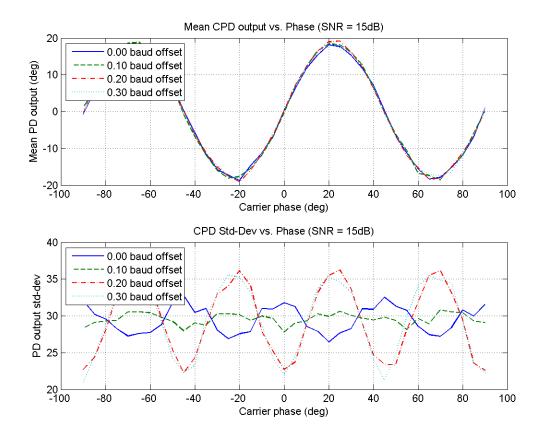

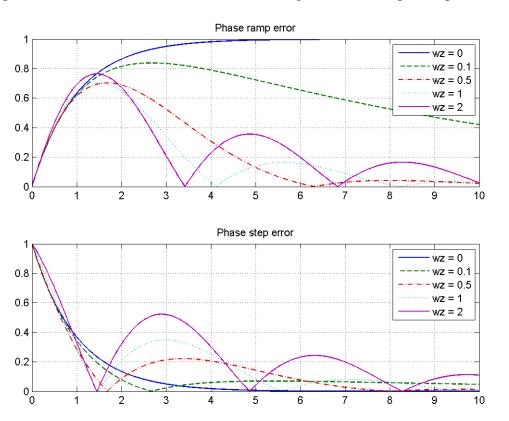

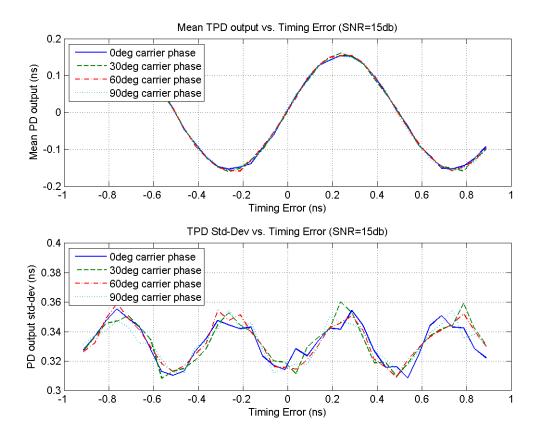

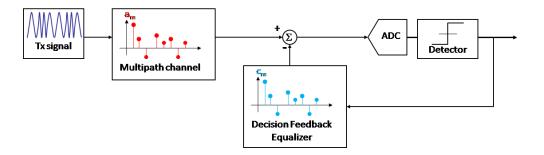

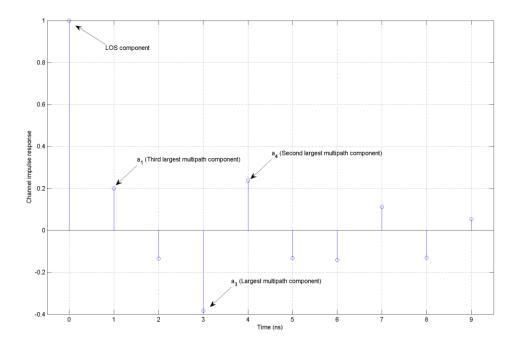

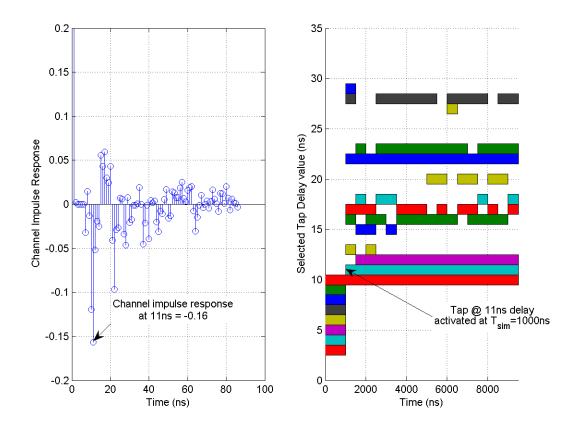

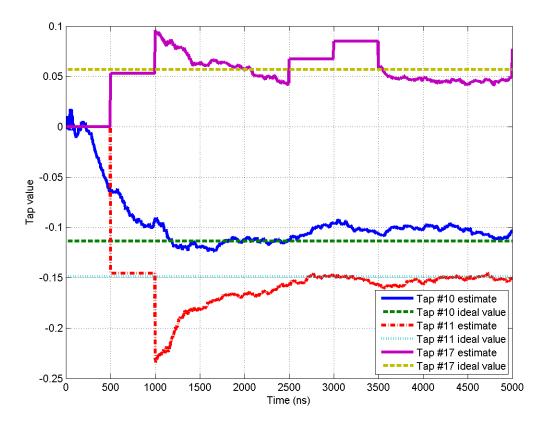

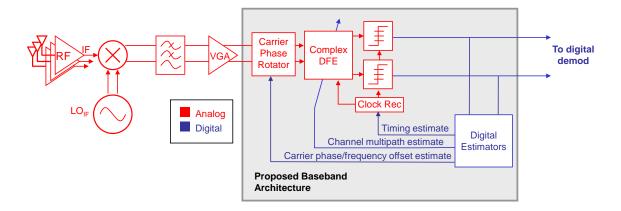

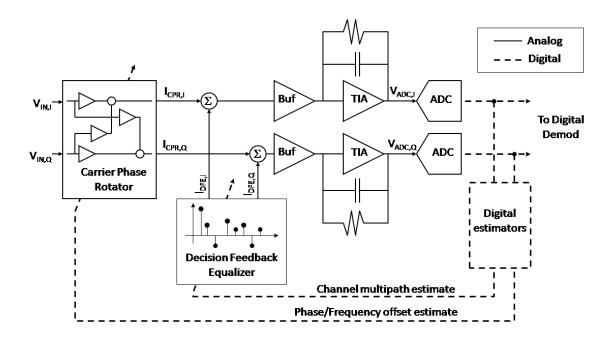

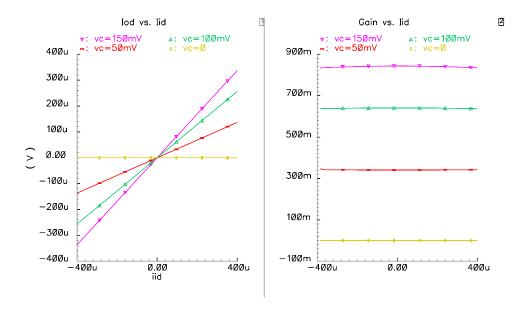

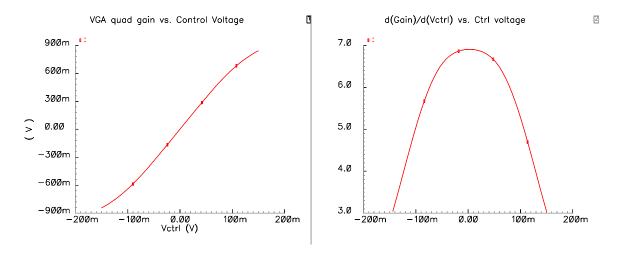

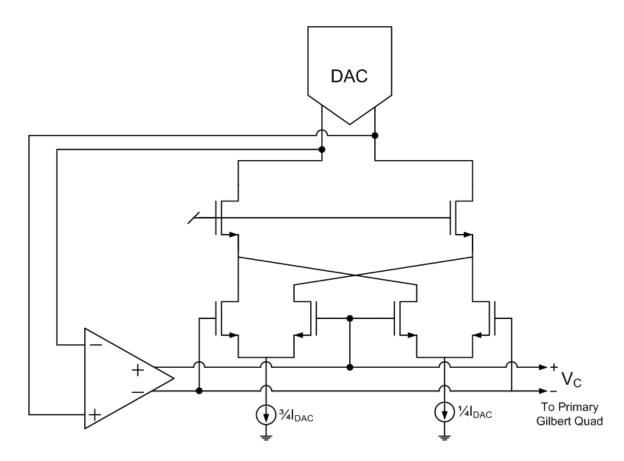

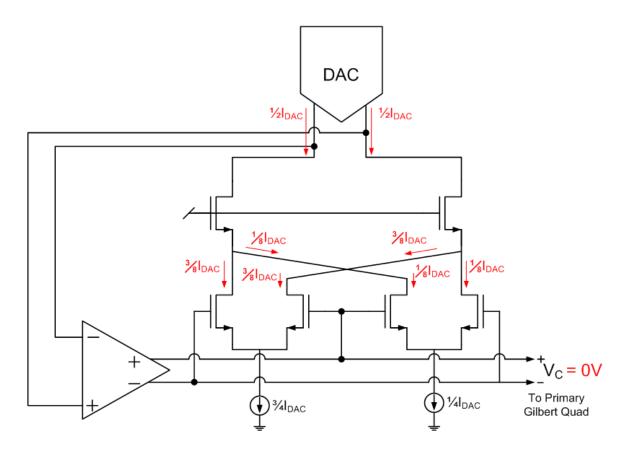

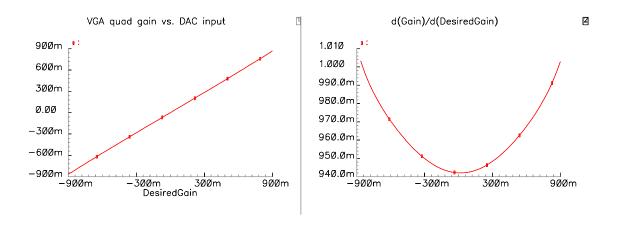

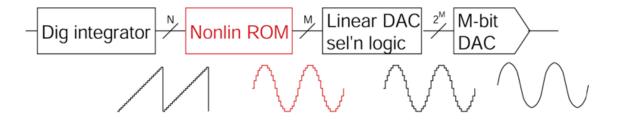

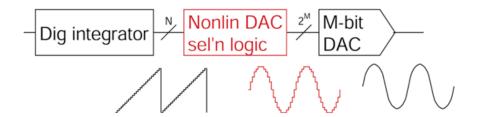

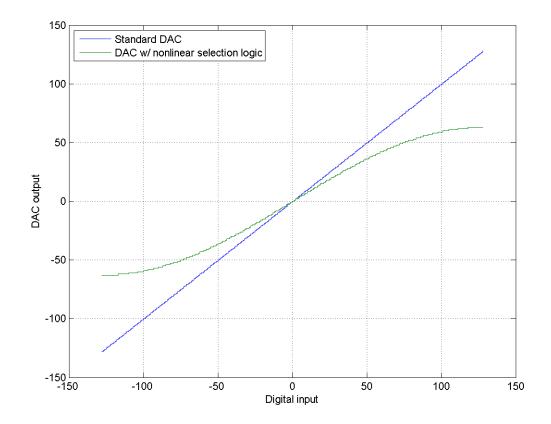

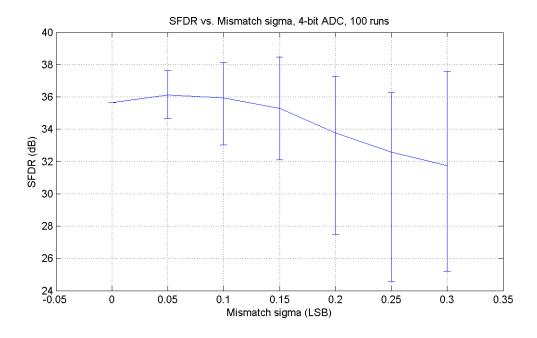

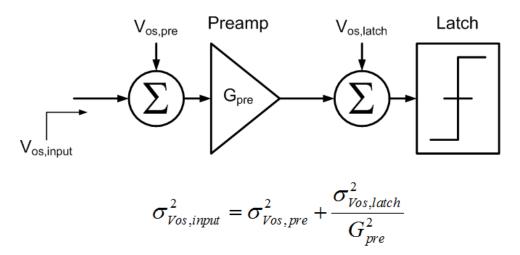

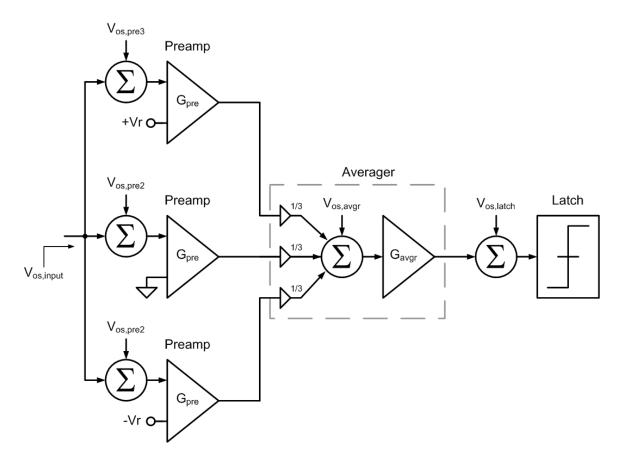

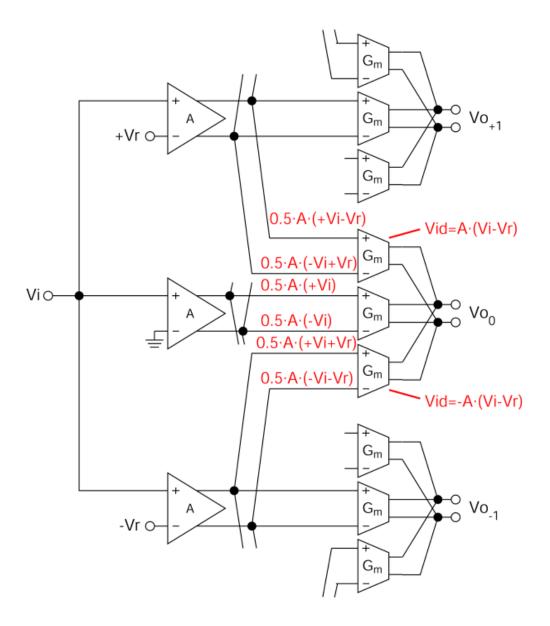

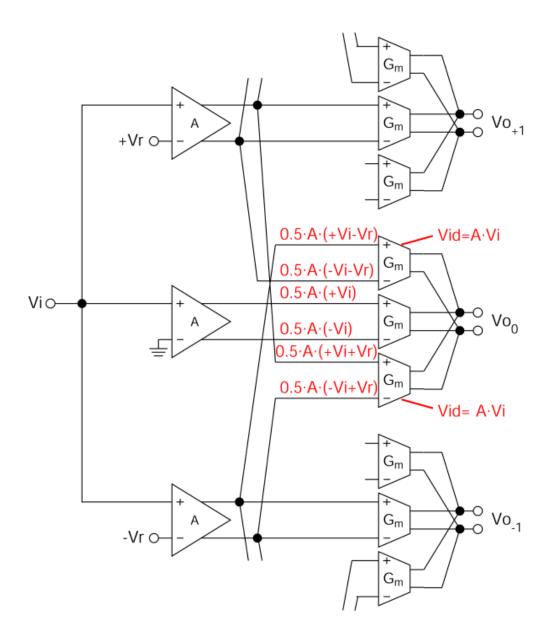

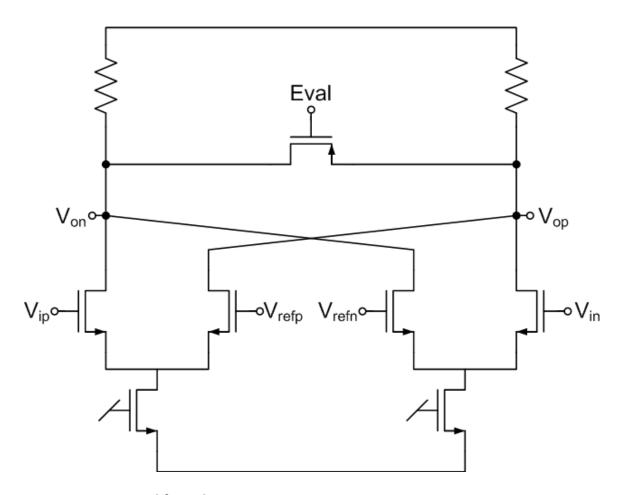

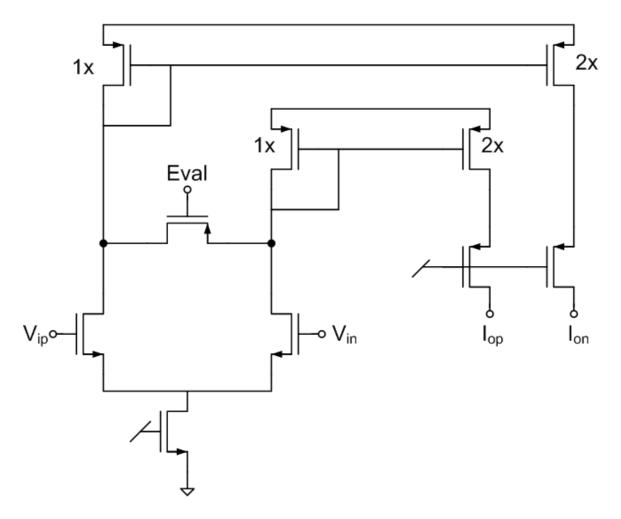

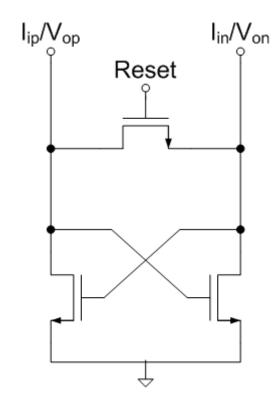

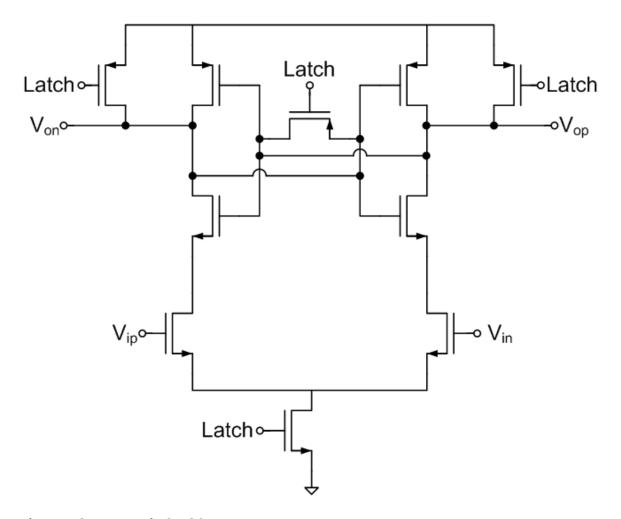

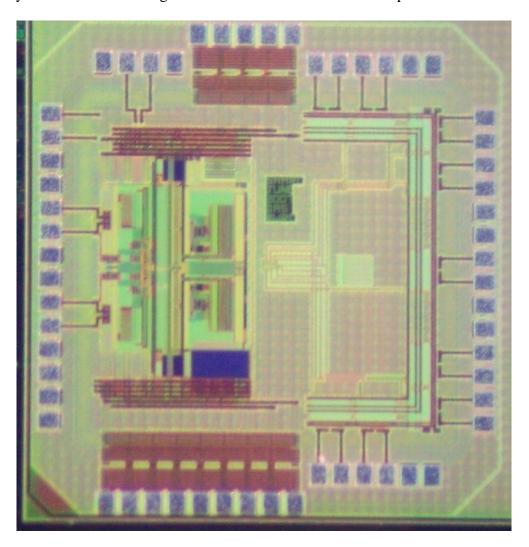

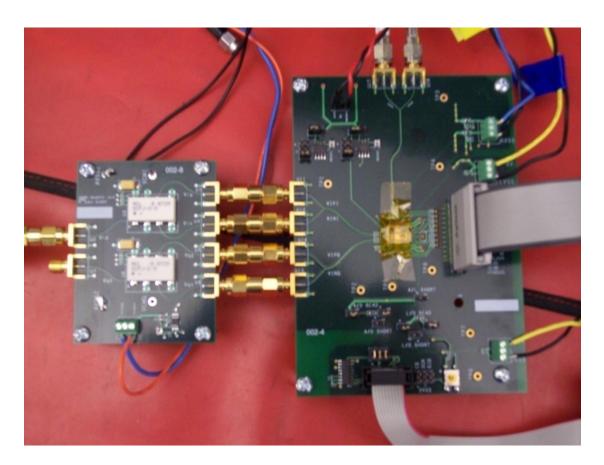

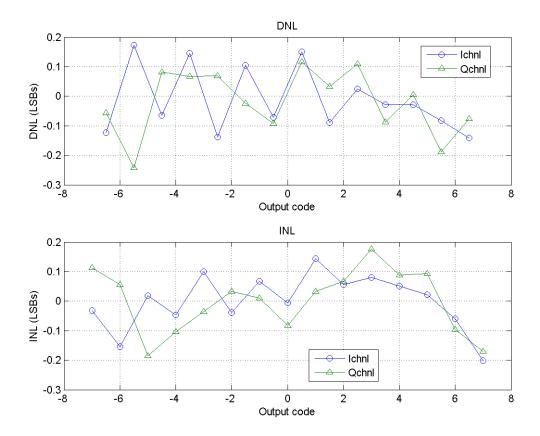

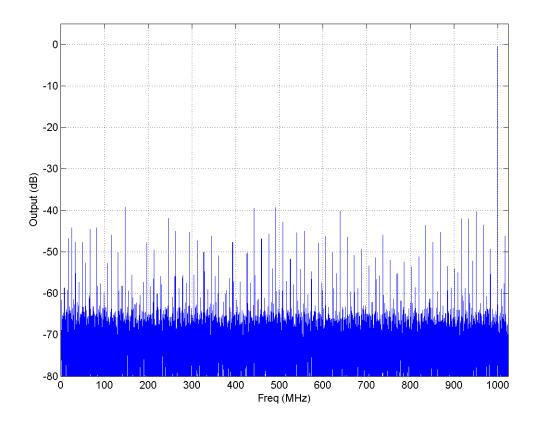

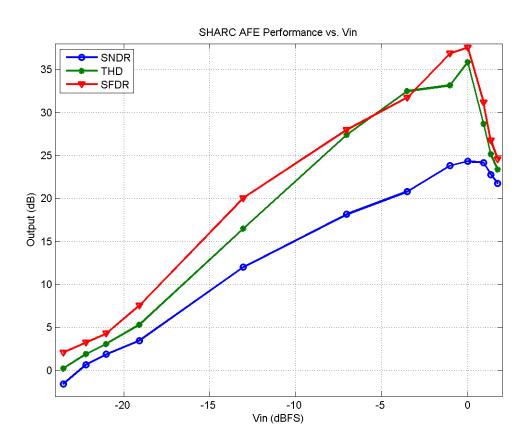

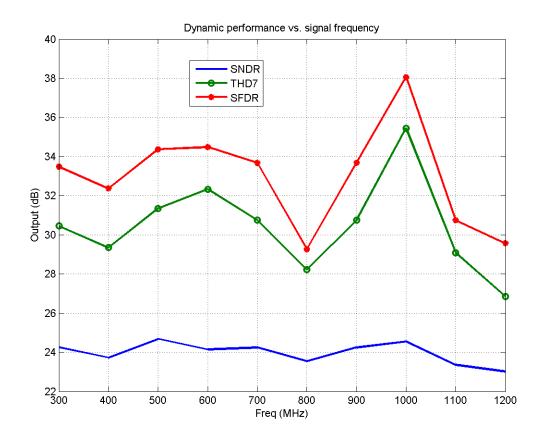

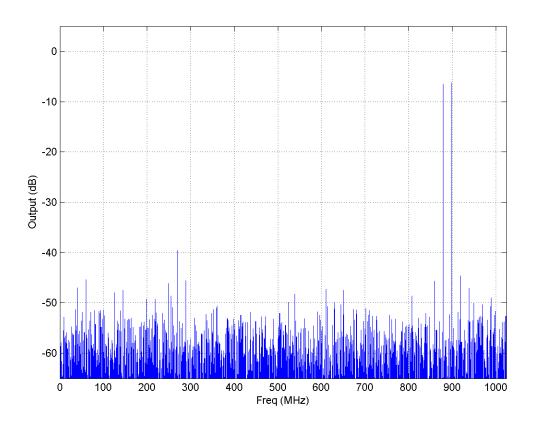

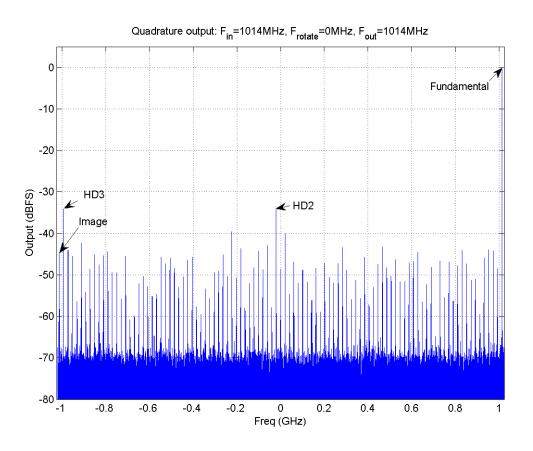

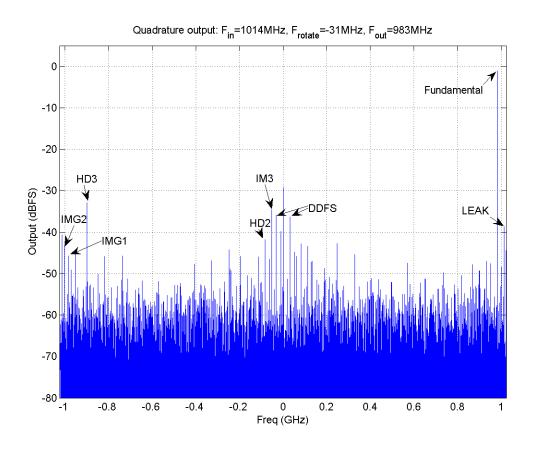

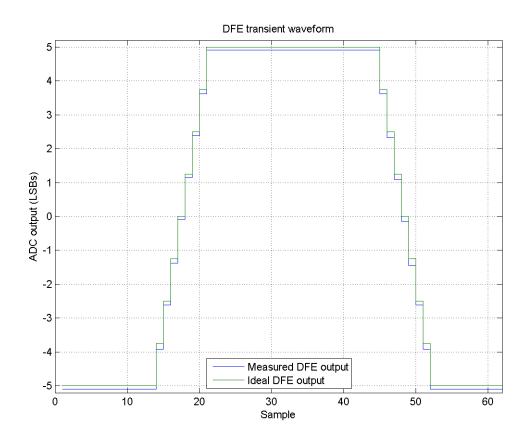

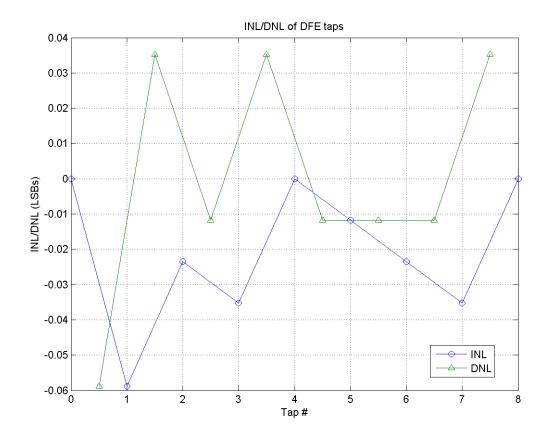

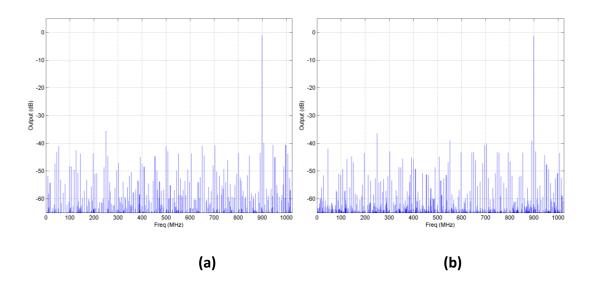

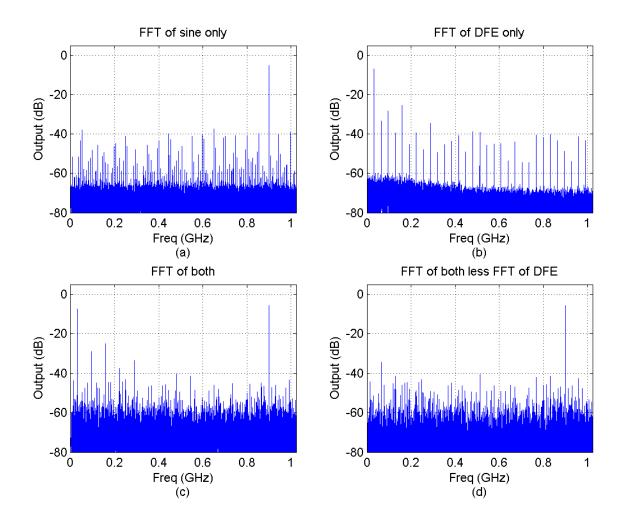

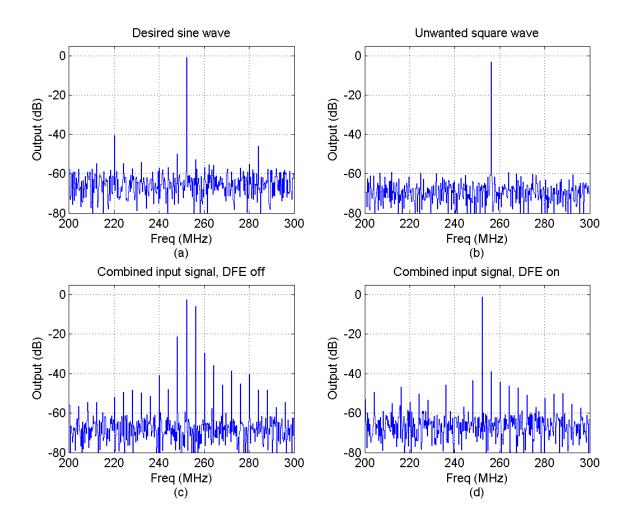

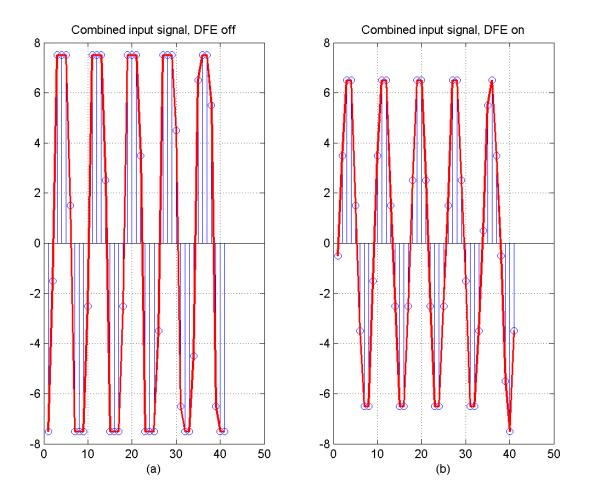

5ns range or below.