# Device and Circuit Techniques for Reducing Variation in Nanoscale SRAM

Andrew Evert Carlson

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-51 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-51.html

May 15, 2008

# Copyright © 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Acknowledgement

The author gratefully acknowledges the support of Profs. Tsu-Jae King Liu and Borivoje Nikolic, Dr. Srinath Krishnan, the UC Berkeley Device Group students, and the staff of the Microlab. The author is also grateful for financial support from AMD and the SRC and silicon support from AMD, ST Microelectronics, and the UC Berkeley Microlab.

#### Device and Circuit Techniques for Reducing Variation in Nanoscale SRAM

by

Andrew Evert Carlson

S.B. (Harvard University) 2003 M.S. (University of California, Berkeley) 2005

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Borivoje Nikolic Professor Robert Leachman

Spring 2008

Device and Circuit Techniques for Reducing Variation in Nanoscale SRAM

Copyright  $\bigcirc$  2008

by

Andrew Evert Carlson

Abstract

Device and Circuit Techniques for Reducing Variation in Nanoscale SRAM

by

Andrew Evert Carlson

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

SRAM scaling, a major driver of microprocessor development, is threatened by increasing variation in transistor parameters such as threshold voltage and gate length. With a target-based model for device I-V characteristics, the effects of these variations on SRAM performance can be well understood and predicted. A robust, iterative algorithm for estimating SRAM cell yield is developed. The analysis is extended to time-dependent

reliability problems, and a statistical methodology for robust cell design is presented.

For future technology nodes, SRAM scaling will require device and circuit innovations to suppress variation. Multi-gate devices and extended spacer lithography processes can be used to reduce random variability at its source. Feedback circuits can be used to reduce systematic SRAM variation after fabrication. Implementation of any one of these techniques is expected to result in a significant yield improvement of several sigma. In combination,

these techniques are expected to enable robust SRAM scaling to the end of the roadmap.

Professor Tsu-Jae King Liu Dissertation Committee Chair

1

To Christina, my light at the end of the tunnel

# Contents

| Contents     |       |                                               | i   |  |

|--------------|-------|-----------------------------------------------|-----|--|

| Li           | st of | Figures                                       | iv  |  |

| Li           | st of | Tables                                        | vii |  |

| $\mathbf{A}$ | ckno  | wledgements                                   | ix  |  |

| 1            | Intr  | roduction: SRAM Scaling                       | 1   |  |

|              | 1.1   | Static Random Access Memory                   | 1   |  |

|              |       | 1.1.1 Cell Architectures                      | 1   |  |

|              |       | 1.1.2 The Drive to Scale                      | 4   |  |

|              | 1.2   | Scaling Issues for Embedded SRAM              | 7   |  |

|              | 1.3   | Studies of Variation                          | 11  |  |

|              |       | 1.3.1 Dopants and patterning                  | 11  |  |

|              |       | 1.3.2 Contemporary work                       | 12  |  |

|              |       | 1.3.3 This work                               | 14  |  |

|              | 1.4   | References                                    | 15  |  |

| 2            | Uno   | derstanding Variation in SRAM                 | 21  |  |

|              | 2.1   | Introduction                                  | 21  |  |

|              | 2.2   | Model Development and Validation              | 25  |  |

|              | 2.3   | Impact of SRAM scaling trends                 | 32  |  |

|              | 2.4   | Yield Modeling and Statistical Design Methods | 40  |  |

|              | 2.5   | NBTI and other reliability issues             | 51  |  |

|              | 2.6   | Conclusion                                    | 58  |  |

|   | 2.7 | References                                     | 59  |

|---|-----|------------------------------------------------|-----|

| 3 | Dev | vice Techniques for Reducing Variation in SRAM | 62  |

|   | 3.1 | Introduction                                   | 62  |

|   | 3.2 | Reducing variation from threshold voltage      | 64  |

|   |     | 3.2.1 Alternative device architectures         | 66  |

|   |     | 3.2.2 Triple Gate Bulk SRAM                    | 71  |

|   | 3.3 | Reducing variation from lithography            | 79  |

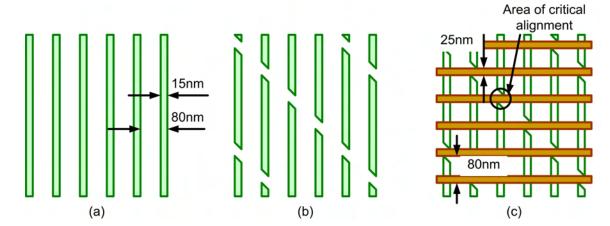

|   |     | 3.3.1 Linear Features                          | 80  |

|   |     | 3.3.2 Negative Spacer Lithography              | 83  |

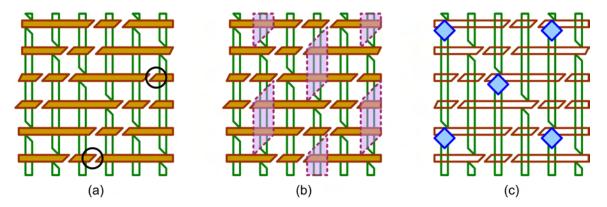

|   |     | 3.3.3 Iterative Spacer Lithography             | 90  |

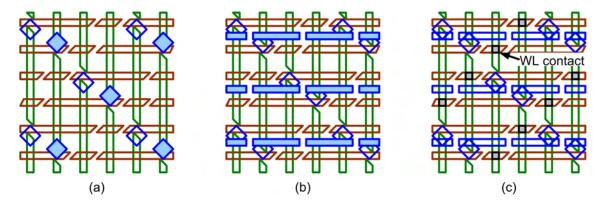

|   | 3.4 | SRAM Design                                    | 95  |

|   |     | 3.4.1 All-Spacer FinFET SRAM                   | 97  |

|   |     | 3.4.2 Other circuit layouts                    | 102 |

|   | 3.5 | Summary                                        | 103 |

|   | 3.6 | References                                     | 105 |

| 4 | Des | signing for Variation in SRAM                  | 108 |

|   | 4.1 | Introduction                                   | 108 |

|   | 4.2 | Systematic Variation Sensing                   | 110 |

|   |     | 4.2.1 Sensor Design                            | 113 |

|   |     | 4.2.2 Experimental Results                     | 117 |

|   | 4.3 | Device Characterization from SRAM Measurements | 121 |

|   | 4.4 | Independently gated FinFET SRAM designs        | 132 |

|   |     | 4.4.1 Pass-gate feedback                       | 133 |

|   |     | 4.4.2 Pull-up write gating                     | 139 |

|   | 4.5 | Summary                                        | 144 |

|   | 4.6 | References                                     | 146 |

| 5 | Con | nclusion                                       | 148 |

|   | 5.1 | Contributions of this work                     | 149 |

|   | 5.2 | Future directions                              | 151 |

|   | 5.3 | Final Thoughts                                 | 152 |

|   | 5 4 | References                                     | 153 |

# List of Figures

| 1.1  | The 6-T SRAM                                          | 2  |

|------|-------------------------------------------------------|----|

| 1.2  | Modes of SRAM Failure                                 | 3  |

| 1.3  | Alternate SRAM Architectures                          | 4  |

| 1.4  | SRAM scaling                                          | 5  |

| 1.5  | SRAM Niche                                            | 6  |

| 1.6  | BFCs                                                  | 7  |

| 1.7  | NP Idsat                                              | 9  |

| 1.8  | Vt Sigma                                              | 11 |

| 1.9  | Lg Sigma                                              | 12 |

| 2.1  | Transistor Modes of Operation                         | 22 |

| 2.2  | I-V modeling with few parameters                      | 25 |

| 2.3  | Key operating biases for SNM modeling                 | 26 |

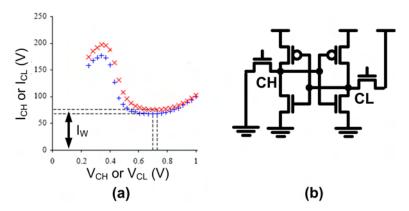

| 2.4  | Write-ability current                                 | 28 |

| 2.5  | I-V validation to mixed-mode device sims              | 29 |

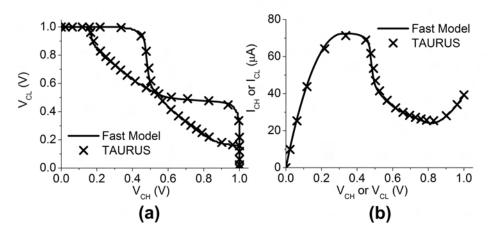

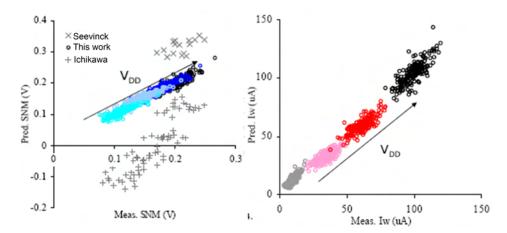

| 2.6  | SRAM validation to mixed-mode device sims             | 30 |

| 2.7  | Validation to 90nm SOI                                | 31 |

| 2.8  | Validation to 90nm SOI (Alternate Processes)          | 31 |

| 2.9  | Validation to 65nm SOI                                | 32 |

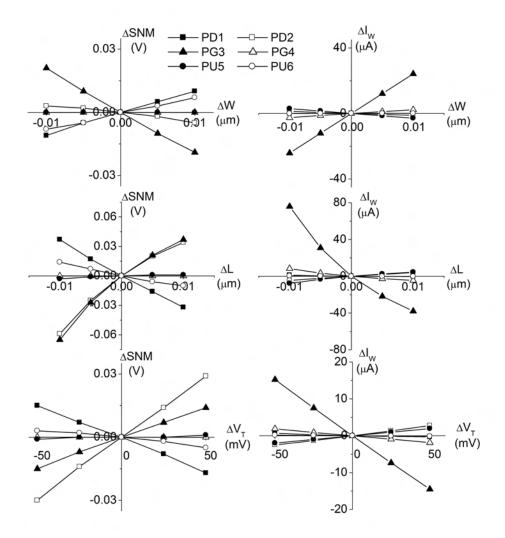

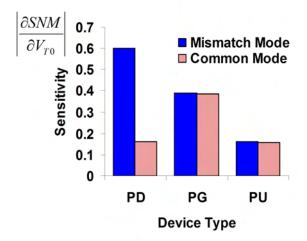

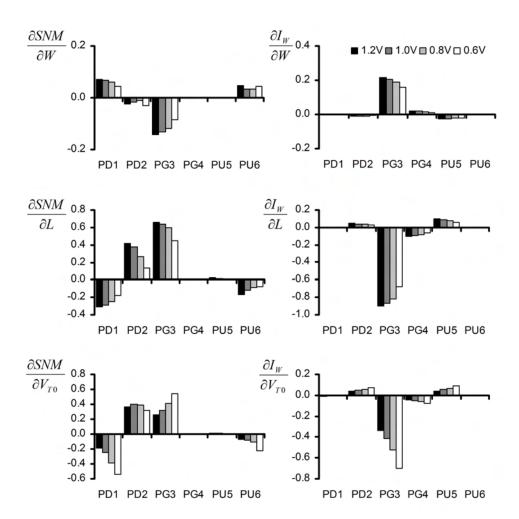

| 2.10 | Sensitivities at $V_{DD} = 1.2 \text{V}$              | 33 |

| 2.11 | Variation and the Butterfly Curves                    | 35 |

| 2.12 | Mismatch vs. common mode Variations                   | 36 |

| 2.13 | Changing sensitivities with $V_{DD}$                  | 37 |

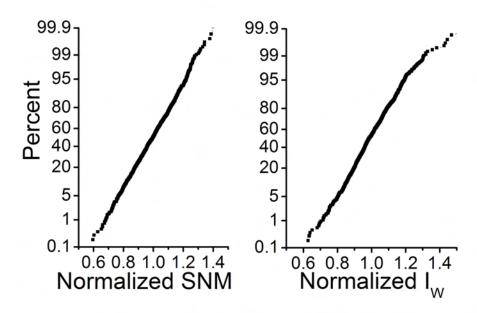

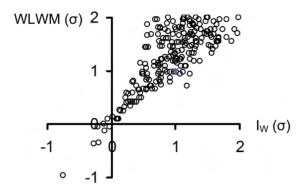

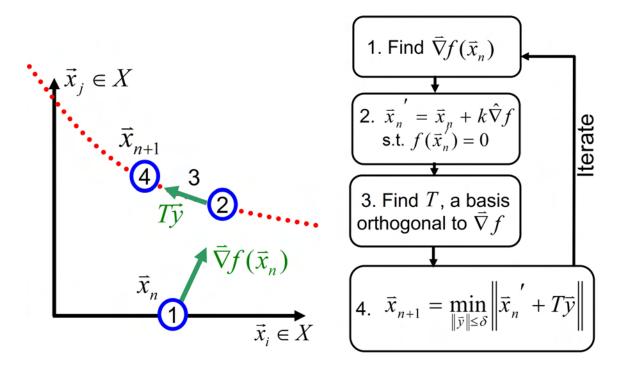

| 2 14 | Cumulative Distribution Plot of Measured SNM and Inc. | 41 |

| 2.15 | Cell sigma and Variation Space                                        | 42 |

|------|-----------------------------------------------------------------------|----|

| 2.16 | Failure Agreement of Write Metrics                                    | 43 |

| 2.17 | Modeling cell sigma                                                   | 44 |

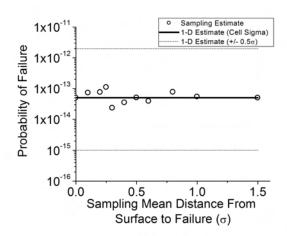

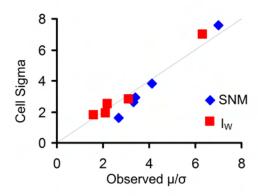

| 2.18 | Importance sampling                                                   | 45 |

| 2.19 | Cell sigma Correlation                                                | 46 |

| 2.20 | Read / Write yield Projections                                        | 48 |

| 2.21 | Read / Write Yield After Optimization                                 | 50 |

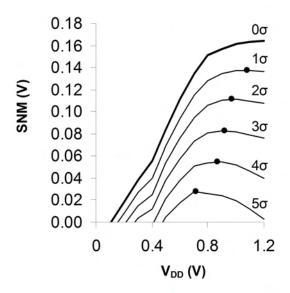

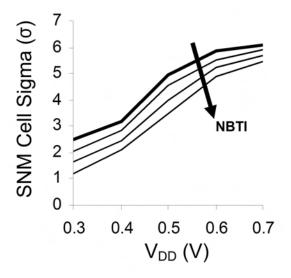

| 2.22 | SNM vs. $V_{DD}$                                                      | 53 |

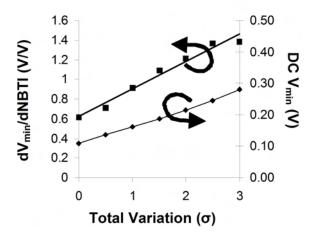

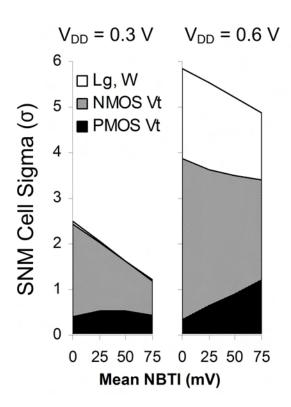

| 2.23 | Sensitivity of $V_{min}$ to NBTI and DC $V_{min}$ vs. total variation | 55 |

| 2.24 | Worst Case Vector Under NBTI                                          | 57 |

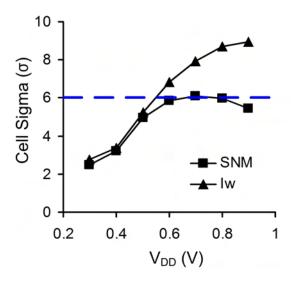

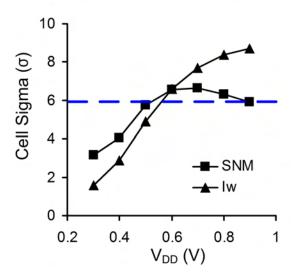

| 2.25 | Cell Sigma vs. $V_{DD}$ Under NBTI                                    | 58 |

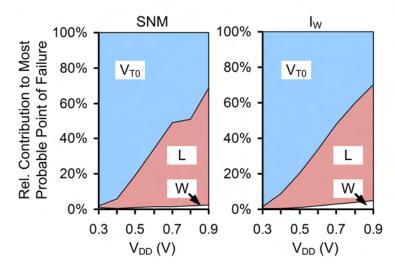

| 3.1  | Parameter-Dependent Variability                                       | 63 |

| 3.2  | Relative Importance of Parameter Variations                           | 64 |

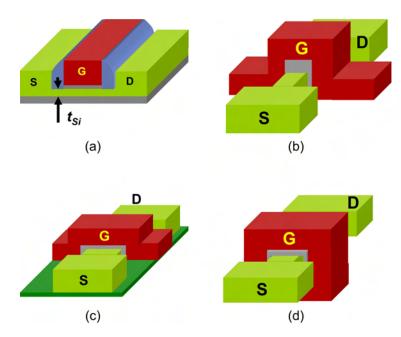

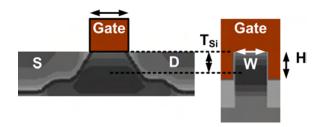

| 3.3  | Alternative device architectures                                      | 67 |

| 3.4  | triple-gate Device                                                    | 72 |

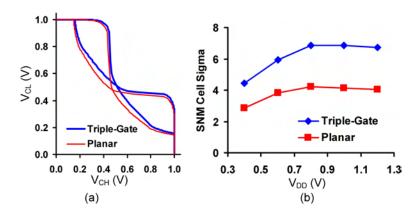

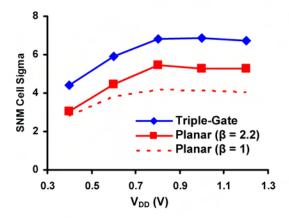

| 3.5  | triple-gate Read Stability                                            | 73 |

| 3.6  | triple-gate Write-ability                                             | 74 |

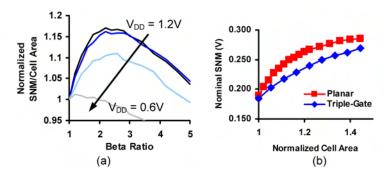

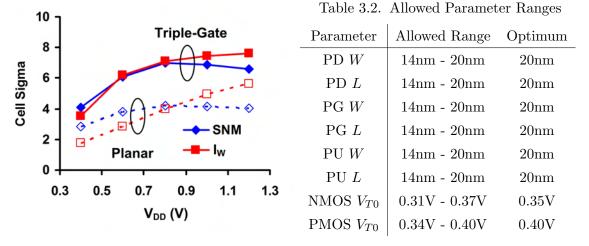

| 3.7  | Optimal sizing                                                        | 75 |

| 3.8  | Optimally sized planar cell                                           | 76 |

| 3.9  | Optimized Triple-gate cell                                            | 77 |

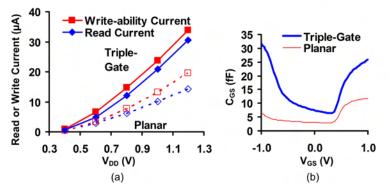

| 3.10 | triple-gate Access Currents and Capacitance                           | 77 |

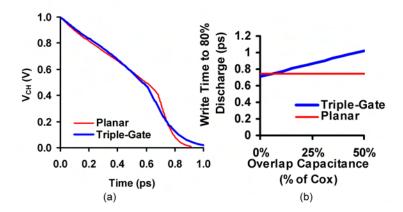

| 3.11 | triple-gate Write Time                                                | 78 |

| 3.12 | Square and linear SRAM layouts                                        | 81 |

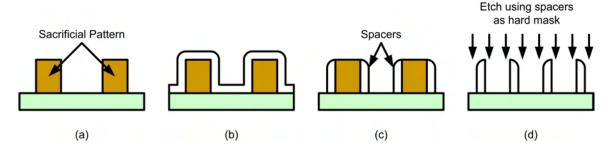

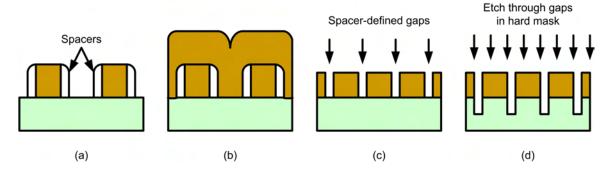

| 3.13 | Conventional spacer lithography                                       | 82 |

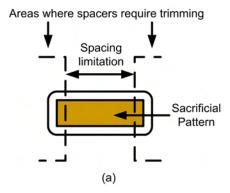

| 3.14 | Challenges in conventional spacer lithography                         | 83 |

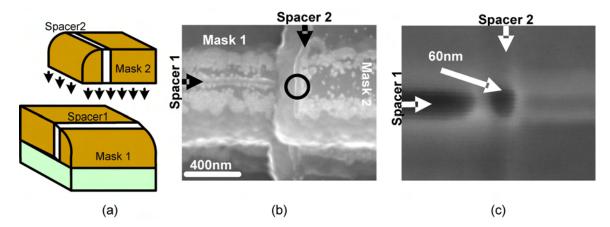

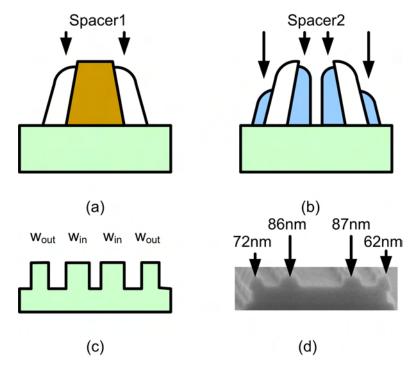

| 3.15 | A negative spacer lithography process                                 | 84 |

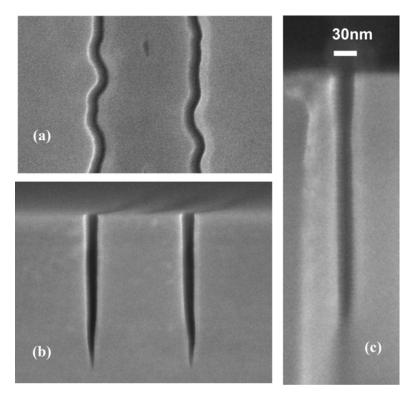

| 3.16 | Negative-spacer defined trenches                                      | 87 |

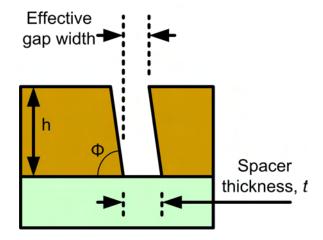

| 3.17 | Gap narrowing                                                         | 87 |

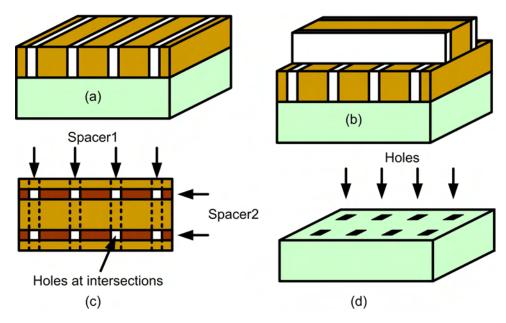

| 3.18 | Contact hole process                                                  | 89 |

| 3.19 | 60nm contact hole                                                     | 89 |

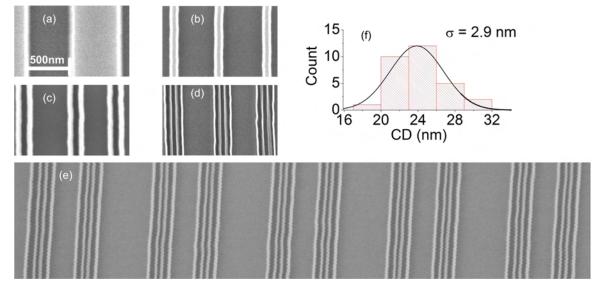

| 3.20 | Systematic Variation in Iterative Spacer Processes                    | 92 |

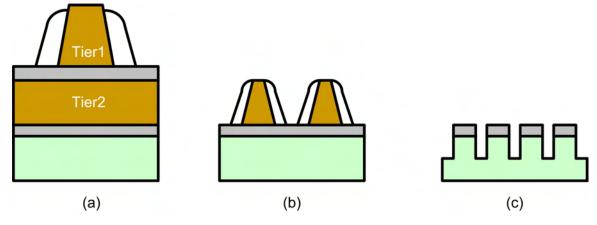

| 2 21 | Multi-tiered hard mask                                                | 0: |

| 3.22 | Iterated spacer process                   | 94  |

|------|-------------------------------------------|-----|

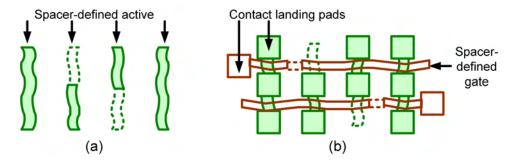

| 3.23 | Spacer-Defined Active                     | 97  |

| 3.24 | All-Spacer SRAM                           | 98  |

| 3.25 | All-Spacer SRAM                           | 96  |

| 3.26 | All-Spacer SRAM                           | 100 |

| 3.27 | All-Spacer SRAM                           | 101 |

| 3.28 | All-Spacer SRAM                           | 102 |

| 3.29 | Spacer-Defined Logic                      | 103 |

| 4.1  | Systematic and random variations          | 111 |

| 4.2  | Correlated variations                     | 112 |

| 4.3  | Systematic variation sensor               | 114 |

| 4.4  | Sensor output correlations                | 115 |

| 4.5  | Optimal $V_{WL}$                          | 116 |

| 4.6  | Sensor response to systematic variations  | 116 |

| 4.7  | Sensor implementation                     | 117 |

| 4.8  | BL sweep                                  | 118 |

| 4.9  | $V_{DD}$ and well bias                    | 119 |

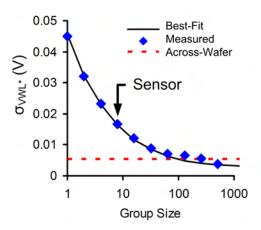

| 4.10 | Systematic and Random Variation           | 120 |

| 4.11 | Die-to-Die Correlation                    | 121 |

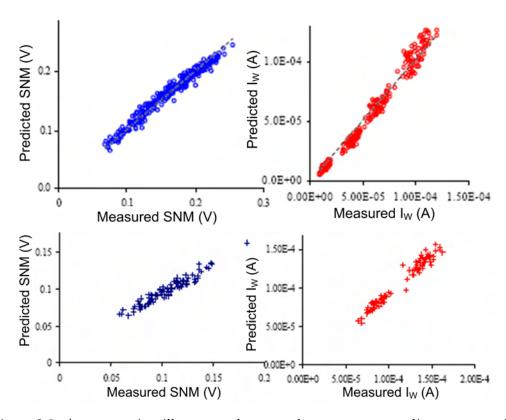

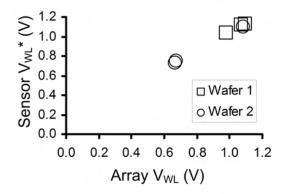

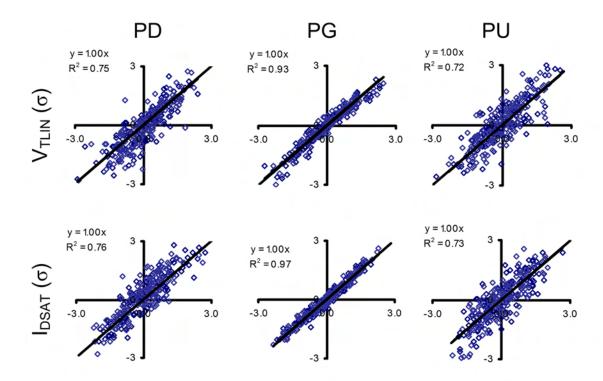

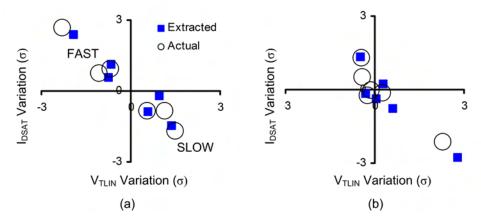

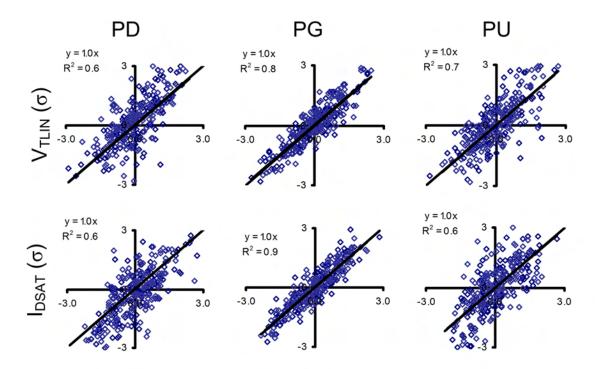

| 4.12 | Linearity of SRAM metrics                 | 124 |

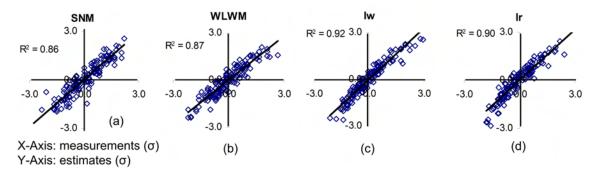

| 4.13 | Sensitivity extraction                    | 125 |

|      | C                                         | 126 |

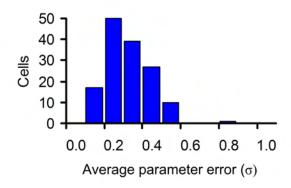

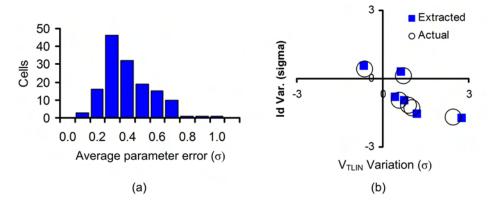

| 4.15 | Average Parameter Error                   | 127 |

| 4.16 | Average Parameter Error and Example Cells | 127 |

| 4.17 | Extraction from Voltage Metrics Only      | 128 |

| 4.18 | Average Parameter Error and Example Cell  | 129 |

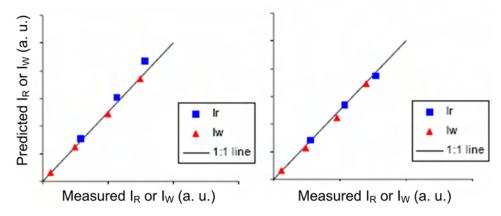

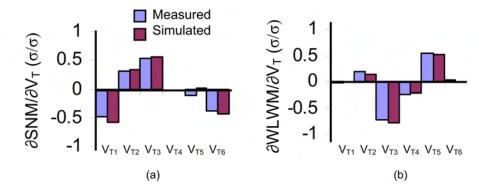

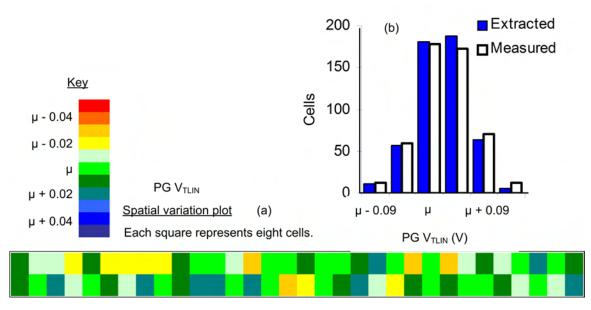

| 4.19 | Measurements from a dense array           | 130 |

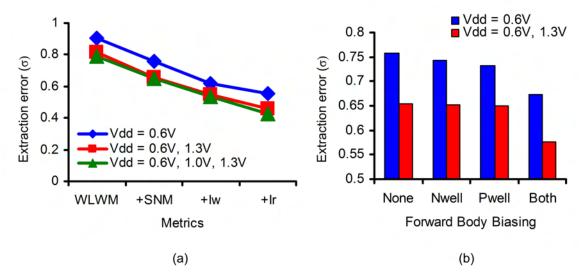

| 4.20 | Choice of metrics                         | 131 |

| 4.21 | Pass-gate feedback                        | 133 |

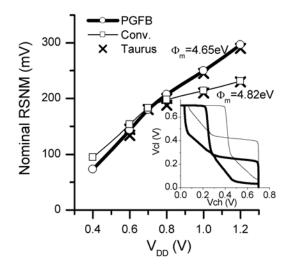

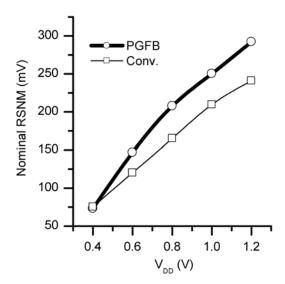

| 4.22 | Nominal Read SNM                          | 135 |

| 4.23 | Nominal $I_W$                             | 136 |

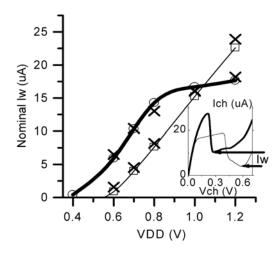

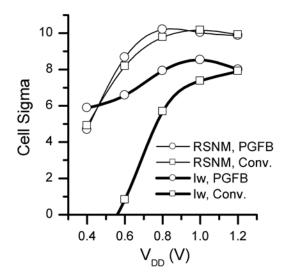

| 4 24 | Read and Write Yields with PGFB           | 137 |

| 4.25 | Read Stability at matched write-ability | 138 |

|------|-----------------------------------------|-----|

| 4.26 | Read Performance of PGFB                | 139 |

| 4.27 | Pull-Up Write-Gating                    | 140 |

| 4.28 | PUWG Write-ability                      | 141 |

| 4.29 | WWL bias effect on read stability       | 141 |

| 4.30 | Optimizing $V_{WWL}$                    | 142 |

| 4.31 | PGFB + PUWG Read Stability              | 143 |

| 4.32 | PGFB + PUWG Yields                      | 144 |

| 5.1  | SRAM tradeoffs                          | 149 |

# List of Tables

| 2.1 | Device Operating Modes                                          | 22  |

|-----|-----------------------------------------------------------------|-----|

| 2.2 | Model I-V Targets                                               | 26  |

| 2.3 | 65nm I-V Targets and Parameter Variations                       | 34  |

| 2.4 | Sensitivity Informed Design                                     | 49  |

| 2.5 | Worst Case Vector for NBTI analysis                             | 54  |

|     |                                                                 |     |

| 3.1 | Alternative Device Architectures for SRAM                       | 71  |

| 3.2 | Allowed Parameter Ranges                                        | 77  |

| 3.3 | Initial Dimensions For Spacer L/S Patterns                      | 91  |

| 3.4 | 1-D Double Patterning and Spacer Lithography Process Comparison | 95  |

|     |                                                                 |     |

| 4.1 | Correlations of Device $V_{TLIN}$ (units of $\sigma_{VT}$ )     | 125 |

| 42  | FinFFT Device Parameters                                        | 135 |

#### Acknowledgements

It is not so much that a Ph. D. is a lot of work (though it is) as it is a lot of time. During my time at Berkeley, several people have guided my work, shaped my career goals, and helped my education. I am grateful for all of their help.

I would like to begin by acknowledging the steadfast support of my advisor, Prof. Tsu-Jae King Liu, who has always been generous in allowing me to pursue my own research interests with my own direction, all the while providing technical guidance, encouragement, and financial support. Research advisors teach the most by example, and there is much about her management style and professional conduct that I hope to bring with me as I go into industry.

I am deeply grateful for all the help of Prof. Borivoje Nikolić, who has been tremendously gracious in unofficially advising my research even though I was not his student. His perspective on SRAM and guidance toward opportunities with a meaningful contribution were exceptionally helpful. Although he was hard for me to read at first, I became profoundly impressed with the sense of fairness and morality he brings to his work.

Dr. Srinath Krishnan provided invaluable opportunities and guidance while and since my internship at AMD, for which I am also very grateful. He encouraged me to develop an SRAM yield model, which has provided a great advantage toward understanding SRAM and all its tradeoffs. I hope to be as informative and impactful with my coworkers as he is with his.

There are several current and former students and staff whom I would like to thank with regards to this work specifically. With Zheng Guo and Liang-Teck Pang I had several helpful SRAM discussions. They also provided invaluable assistance with the logistics of tapeout and testing. Dr. Sriram Balasubramanian was an astute and friendly opponent in many informal debates, who helped me sharpen my technical arguments while he was a student here. Xin Sun and Changhwan Shin provided simulation data for the triple-gate bulk devices and helped me stay sharp on device theory. Xin, Dr. Vidya Varadarajan, Joanna Lai, and

especially Albert Lai helped me debug different processes in the UC Berkeley Microlab. Evan Stateler and Jay Morford also helped me in the lab to get the machines working.

In addition to the above, several others have provided indirect assistance, by helping with my education here at Berkeley. Hideki Takeuchi taught me, among many other things, the technical stubbornness needed to get things done in the lab. Pankaj Kalra provided a much-needed baseline for the Ph. D. experience because he shared my perspective. Donovan Lee, Steve Volkman, Dr. Alvaro Padilla, Dr. Kyoungsub Shin, Dr. Dan Good, Alejandro de la Fuente Vornbrock, Hei Kam, Kinyip Phoa, Yu-Chih Tseng, Noel Arellano, and Prof. Nathan Cheung have also provided technical or educational assistance in some form. Thank you to all.

This work has been funded through several sources. I am first thankful to John Ennals and Bill En of AMD for their help in winning the Semiconductor Research Corporation (SRC)/AMD Mahboob Khan Fellowship. This work has also been supported by the Center for Circuit and System Solutions (C2S2) Focus Center, one of five research centers funded under the Focus Center Research Program, an SRC program. Spacer lithography processing was completed in the UC Berkeley Microlab. Fabrication of a 45nm chip was donated by STMicroelectronics. Data for 65nm and 90nm silicon was provided by AMD.

Finally, I thankfully acknowledge the support of my fiancée, Christina, who with her compassion and understanding helped me through the darkest times, even when she was far away.

"Many complain about their memory, few about their logic."

— Adapted from Benjamin Franklin

## Chapter 1

# Introduction: SRAM Scaling

SRAM scaling represents one of the greatest challenges to decreasing cost per function in microprocessors. On-chip cache size has become increasingly important for high performance applications, and it now presents more of a limit to microprocessor speed than clock rate. The models and methodologies for the design of SRAM, an integral component of microprocessor cache, have changed with time, as new tradeoffs and constraints have emerged. Currently, continued scaling is threatened by variability in SRAM performance and function. This work addresses the emerging threat of variability in three ways: by advancing the understanding of the mechanisms of variation-induced SRAM failure, by developing new devices and processes to address the sources of variation, and by proposing new circuit techniques to compensate for existing variation.

### 1.1 Static Random Access Memory

#### 1.1.1 Cell Architectures

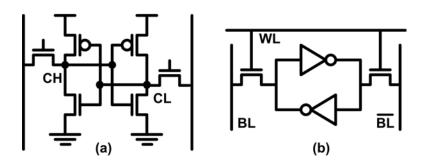

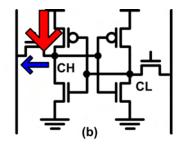

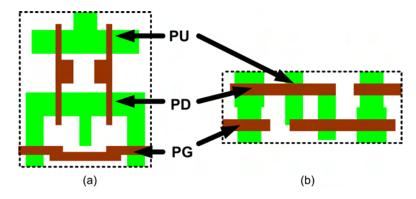

An SRAM array is composed of many identical cells, small circuits that can each store a single bit of information. The most common type of cell, the 6-T SRAM (Fig. 1.1a), is named for the six transistors which comprise it. The cell consists of two cross-coupled

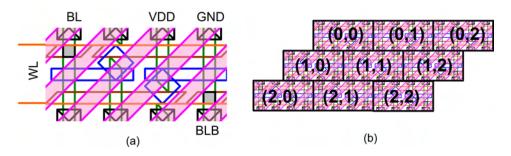

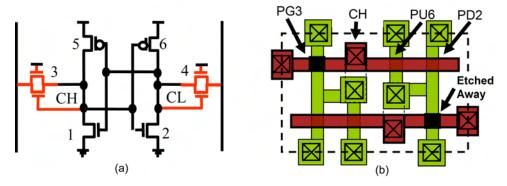

Figure 1.1. The most common SRAM cell architecture, the 6-T SRAM has two pull-up transistors, two-pull-down transistors, and two pass-gate transistors (a). The pull-up and pull-down transistors make up two cross-coupled inverters (b). Cells are accessed by means of orthogonally-routed wordlines,  $\mathbf{WL}$ , and bitlines,  $\mathbf{BL}$  and  $\overline{\mathbf{BL}}$ .

inverters (Fig. 1.1b), made up of the PMOS pull-up devices and the NMOS pull-down devices. The cross-coupled inverters ensure that the internal nodes of the cell always contain complementary values. Two NMOS pass-gate devices connect the internal nodes of the cell to array-level bitlines and provide read and write access to the cell.

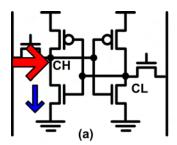

The 6-T SRAM is operated in the following way. To read the cell, the bitlines are precharged to a high bias and the wordline voltage is raised. On the side of the cell storing the logical zero, the bitline is discharged through the access transistor. Depending whether the bitline on the "cell high" (CH) or "cell low" (CL) side is discharged, the cell is read as a logical one or logical zero. To write the cell, the bitlines are driven to complementary values and the wordline voltage is raised. On the side of the cell with the bitline at a low bias, the internal node is discharged through the pass-gate transistor. The cross-coupled inverters raise the bias on the opposite node and latch the new voltages in place.

From this simple description the two basic modes of SRAM failure can be understood. During a read operation, the bias of the low internal node will increase, due to the current through the pass-gate. If the bias rises above the switching point of the inverters, the cell becomes unstable and may switch its state. This event is called a read disturb (Fig. 1.2a). It can be prevented by ensuring the pull-down transistors are much stronger than the pass-gate transistors. This ratio of device strengths is called the *beta ratio* and was an important parameter in early SRAM design.

Figure 1.2. The two basic modes of SRAM failure are a read disturb (a), e.g. in which discharge current through the pass-gate device raises  $V_{CH}$  from a logical zero to a logical one, and a write fail (b), e.g. in which discharge current through the pass-gate is unable to lower  $V_{CH}$  from a logical one to a logical zero.

The other primary mode of SRAM failure is a write failure (Fig. 1.2b). During a write operation, the discharge of the internal node through the pass-gate must overcome a restorative pull-up current through the PMOS device. Write failures can be prevented by ensuring the pass-gate transistors are much stronger than the pull-up transistors. The gamma ratio measures this quantity.

The 6-T cell remains the favorite of SRAM architectures because of these two simple tradeoffs. A design can be virtually guaranteed to work by sizing the devices for high beta and gamma ratios, but at the expense of cell area. In spite of the additional device and processing challenges present in modern SRAM design, these fundamental tradeoffs with area still hold true today.

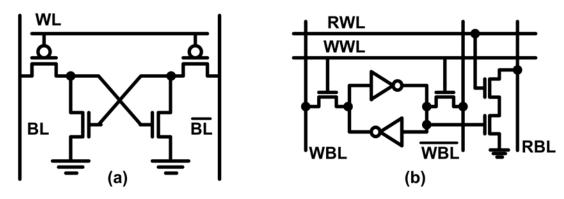

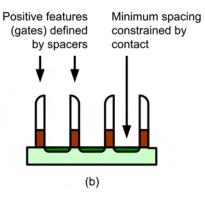

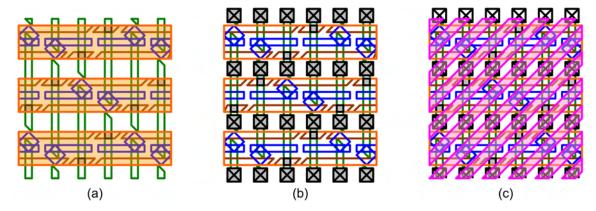

To improve this tradeoff, several alternative SRAM architectures have been investigated. The 4-T SRAM (Fig. 1.3a) removes two transistors from the inverters of the 6-T design [1, 2]. 4-T SRAM has been shown to exhibit better read stability than 6-T for high supply voltages [3] and for low voltages with independently-gated double-gate transistors [4, 5], such as FinFETs [6]. The internal nodes hold complementary values as in the 6-T design; however, the charge on the high bias node is supplied only during the write or through delicate balancing of device off-state currents. It is therefore vulnerable to discharge during a read operation or through leakage paths in the cell and requires periodic refreshing. It is also susceptible to variability [5]. The recently-proposed 8-T SRAM (Fig. 1.3b) adds two transistors to the 6-T cell as a separate read port [7]. It enhances read stability by

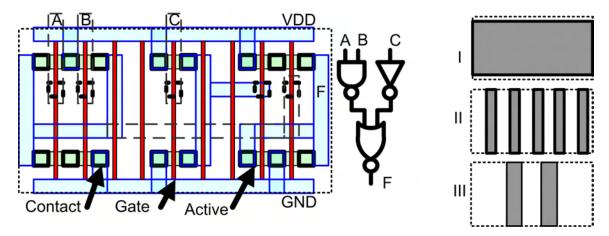

Figure 1.3. The 4-T SRAM has a smaller area but is less robust than the 6-T cell [1, 2] (a). The 8-T SRAM decouples the read and write operations to allow for simultaneous enhancement, but it has a larger cell area and requires separate read and write bitlines and wordlines [7] (b).

eliminating bitline discharge into the internal node, but at the expense of a larger cell. The increase in cell area can be reduced by improvements in array efficiency through specific addressing schemes, but not completely [8]. It is not yet clear how the write yield compares to that of a 6-T design of comparable cell area and array size. Other SRAM architectures, including 9-T [9] and 10-T [10, 11] have been proposed, but also have undesirable tradeoffs in area, reliability, or performance compared to the 6-T design. The analysis presented in this work therefore assumes a 6-T cell; however, the models and methods developed could be easily extended to other cell architectures.

#### 1.1.2 The Drive to Scale

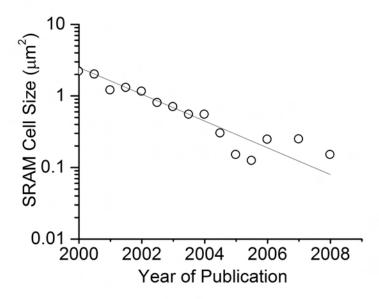

In the design of SRAM, cell area is invariably the metric to optimize. Other metrics, such as read stability or access times, are important insofar as constraints are met, but smaller area is always the primary goal. SRAM scaling has historically followed Moore's Law, with the same economic drivers of speed and cost per function (Fig. 1.4).

SRAM scaling reduces memory access times by allowing more memory to be closer to a logic core. In early microprocessors, before logic and memory were integrated on the same chip, motherboard-based RAM arrays were used as cache memory to reduce the delays associated with hard disk access. Tiny clusters of RAM cells were used as registers

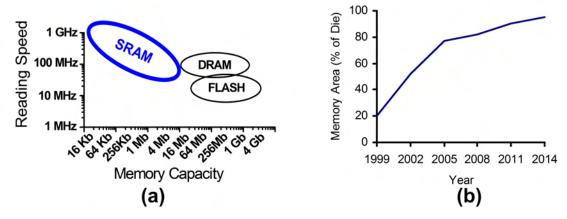

Figure 1.4. Reported SRAM sizes have historically followed Moore's Law, with an area reduction of  $0.5 \times$  every 18 months. Data from [12, 7, 13, 14, 15].

within the core to accelerate program execution further. As transistor dimensions scaled, it became possible to embed a memory cache in the same chip as the logic core, eliminating the I/O and parasitic delays associated with off-chip communication, and memory access times were drastically reduced. In fact, the development of embedded SRAM was instrumental in defining a niche for SRAM among other types of memory, such as dynamic random access memory (DRAM), non-volatile EEPROMs, and magnetic disks. Cache evolved into a multitiered structure, with SRAM making up the fastest access memory (Fig. 1.5a). In modern microprocessors, this trend has continued, such that SRAM cache itself has multiple levels. For example, in recent Intel and AMD microprocessors, L1 (level one) cache contains a small amount of the fastest memory cells. At the next level, L2 cache contains a large amount of cells that are slightly slower, and so on. Memory access time is an emerging constraint on the performance of microprocessors, and is best reduced by increasing the SRAM cache size. Presently, a microprocessor's L2 cache size is a commonly quoted specification, second only to clock speed. Scaling cell area allows for a larger cache in the same area. Yamagata notes that transistor scaling has not led to a commensurate reduction in microprocessor die

Figure 1.5. SRAM is used in relatively small, on-chip cache memories for fastest access (a). With continued scaling, the physical size of a microprocessor remains approximately the same, and the additional area is filled with more memory (b). Figures adapted from [16].

size, but rather more functionality has been integrated into designs of a comparable area [16]. With ever increasing proportion, more functionality means more memory (Fig. 1.5b).

Together with the aforementioned tradeoff between cell area and functionality, the drive to scale resulted in cell designs meeting minimum constraints in read stability. Early SRAM designs could make use of minimum-width devices for the pull-up and pass-gate devices. The gamma ratio for such a device would be a function of the mobilities in the process,  $\gamma \approx \mu_n/\mu_p$ , which ensured sufficient write-ability before the advent of strained silicon technology. The pull-down devices would be sized larger to meet the minimum beta ratio needed to ensure stability. Such a cell design had the benefit of being directly applicable to a new technology node with a simple shrink. A standard dimension reduction of 0.7x results in a cell area of 0.5x. SRAM scaling was therefore automatic with transistor scaling, and advanced models and custom design rules were not necessary.

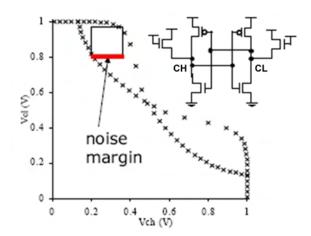

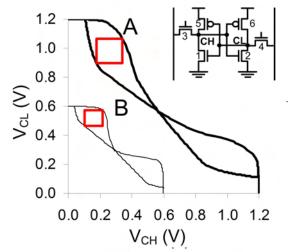

In fact, the only metric of significant concern in early SRAM was that of read stability, since the minimum beta ratio was desired to reduce cell area. Since Seevinck's seminal work in 1987, read stability has been quantified with the static noise margin (SNM), which is defined as the minimum amount of noise needed to upset the state of the cell [17]. It is

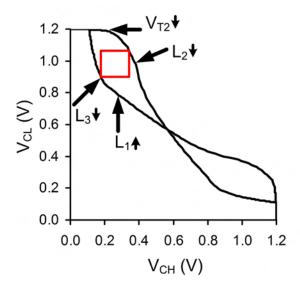

Figure 1.6. Static Noise Margin (SNM), a metric for read stability, can be illustrated with the cell's voltage transfer characteristics (sometimes called the butterfly curves). The curves are generated by sweeping the voltage of one internal node and measuring the voltage of the opposite node with the cell biased as shown. SNM is represented by the side of the largest square that fits within the curves. These curves were generated from measurements of a fabricated cell in an industrial 90nm SOI process.

commonly illustrated with the voltage transfer characteristics (Fig. 1.6, sometimes called the butterfly curves) for the SRAM cell, in which it corresponds to the size of the largest square that fits within the curves. Cells with SNM values of at least 25% of the cell supply voltage,  $V_{DD}$ , are generally considered to have excellent read stability. High SNM cells generally feature a switching voltage near  $V_{DD}/2$  and high inverter gains around this point. SNM remains the most significant SRAM metric today, but it is no longer sufficient to guarantee array functionality.

### 1.2 Scaling Issues for Embedded SRAM

In the past few years, SRAM scaling has faced increasing challenges. Short channel effects and the abandonment of constant field device scaling made existing SNM models obsolete. The development of strained channels, which improve PMOS mobility more than that of NMOS, has decreased cell write-ability to the point where its tradeoff with SNM has become a significant aspect of SRAM design. As dimensions shrink, variations in transistor performance degrade functionality and reduce yield. Devices which leak more in the off-

state limit performance, constrain array architecture, and in extreme cases can cause cell instability. With less capacitance, the internal nodes of a scaled cell are more susceptible to leakage currents and other noise sources.

#### Transistor scaling

Under constant field scaling, all dimensions and voltages for a transistor were scaled down so that the electric fields remained constant between technology nodes. This not only maintained the same beta and gamma ratios for the scaled cell, it allowed SNM to be modeled with closed-form equations [17]. Subthreshold current could be ignored, and long channel equations for drain current  $(I_{DS})$  could satisfactorily model transistor behavior:

$$I_{DS} = \begin{cases} \mu C_{ox} \frac{W}{2L} (V_{GS} - V_T)^2 & V_{GS} > V_T \text{ and } V_{DS} \ge V_{GS} - V_T \\ \mu C_{ox} \frac{W}{L} V_{DS} (V_{GS} - V_T - \frac{V_{DS}}{2}) & V_{GS} > V_T \text{ and } V_{DS} < V_{GS} - V_T \\ 0 & V_{GS} \le V_T \end{cases}$$

(1.1)

where  $\mu$  is the carrier mobility,  $C_{ox}$  is the gate oxide capacitance per unit area, W is the width of the device, L is the gate length,  $V_{GS}$  is the voltage on the gate with respect to the source,  $V_{DS}$  is the voltage on the drain with respect to the source, and  $V_T$  is the threshold voltage of the transistor.

In modern MOSFETs, subthreshold and gate leakage currents inhibit continued scaling of  $V_T$  and  $C_{ox}$ . Weak-inversion currents have become significant in determining the voltage transfer characteristics for modeling SNM. Furthermore, short channel effects such as drain-induced barrier lowering (DIBL), channel length modulation, and velocity saturation complicate the equations and make the old models obsolete. Of these effects, DIBL is particularly deleterious to SNM, since it reduces inverter gain at high supply voltages.

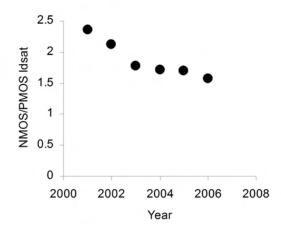

In addition, the ratio between on-currents for NMOS and PMOS has decreased with scaling, due in large part to the development of strained silicon channels (Fig. 1.7). Strain technologies have improved hole mobility  $\mu_p$  more than electron mobility  $\mu_n$ . Although beneficial for speed in logic devices, this can degrade SRAM write-ability. If minimum-

Figure 1.7. Recent advances in high performance CMOS have narrowed the gap between reported NMOS and PMOS drive currents ( $I_{dsat}$ ), measured at  $V_{DD} = 1.0V$  and  $I_{off} = 100nA/\mu m$ . [18, 19, 20, 21, 22, 14] For SRAM cells with minimum-width pull-up and pass-gate devices, this scaling trend results in a decrease in write-ability.

width pull-up and pass-gate devices are retained, the gamma ratio of the cell is reduced. The pass-gate must be made larger to maintain the original gamma ratio, but this requires a proportional increase to the pull-down device to maintain the same beta ratio. It thus becomes more difficult to scale cell area at the historical rate.

#### Variation

The problems caused by transistor scaling are exacerbated by the emergence of process variations. Variations in transistor parameters such as threshold voltage, gate length, or channel width affect the transistor's drive strength. In an SRAM cell, this may affect the SNM, write-ability, or access times. Symmetric circuits like the 6-T SRAM cell are especially vulnerable to mismatches in the strengths of paired transistors. As transistor dimensions scale down, the impact of process variations increases, and the cell yield drops.

The issue is compounded by the increasing SRAM array size. Cache sizes of several tens of million identical cells are common. To achieve high yield for the entire array, the nominal cell design must now have a very large margin for variation of at least five or six standard deviations. As cache sizes increase, the required margin will continue to grow.

Thus with continued SRAM scaling, cell yield will decrease even as arrays require higher yielding cells. This makes variation the greatest challenge to SRAM scaling.

#### Leakage current

In allowing greater subthreshold and gate leakage currents, transistor scaling can curb further SRAM scaling and degrade cell stability. Subthreshold leakage through the passgate transistors of many inactive cells can compete with the current through a single active cell to impair read access times. A constraint on the array column height, the number of cells on each bitline, may be needed to meet access time constraints [23]. Leakage currents through the power supply for several million cells can consume a significant portion of the power budget of a chip [24]. Gate leakage currents within the SRAM cell have been shown to degrade SNM and may also affect write-ability [25, 26]. With continued scaling, the capacitance on the internal nodes of a cell decreases. Thus the amount of charge needed to disturb a cell decreases, while the magnitude of leakage current increases.

#### Soft error rates

The reduction in capacitance is also significant for soft error events, in which the state of an SRAM cell is upset by the introduction of a large impulse of noise to the internal nodes. Soft error rates describe the frequency with which external events such as alpha particle collisions can cause a read disturb. As SRAM scales down, the incidence of soft error rates increases and poses a significant reliability challenge [27, 28].

In summary, there are several major challenges for continued SRAM scaling, and they are all growing worse. Scaled devices obsolete SRAM models and require new cell designs for each technology node. They are more sensitive to process variations, have increased leakage currents, and are more susceptible to external noise. Each of these issues is an area of current research. This work focuses on the most problematic of these, variation.

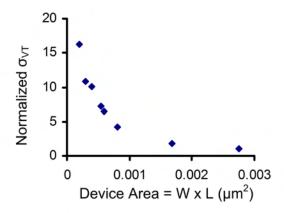

Figure 1.8. The variance of the threshold voltage of a MOSFET increases in inverse proportion to channel area due to random dopant fluctuation. The points in this plot are generated by Monte Carlo simulation, but the effect has been observed experimentally in several technologies [29].

#### 1.3 Studies of Variation

#### 1.3.1 Dopants and patterning

One of the most significant sources of process variations for current VLSI transistors  $(L_G > 20 \text{nm})$  is random dopant fluctuation [29]. To achieve a channel dopant concentration of  $10^{19}$  atoms/cm<sup>3</sup> in a scaled MOSFET with dimensions less than 50 nm, fewer than 100 dopant atoms are required. The displacement or absence of only a few dopants can result in threshold voltage variations. Fig. 1.8 illustrates the increase in the standard deviation of  $V_T$  as a function of channel area  $(W \times L)$  [29]. Threshold voltage variation due to random dopant fluctuation increases proportionally with  $1/\sqrt{WL}$  [30]. With further scaling, discrete effects from displaced source and drain dopants may add to the variation. Recently, experimental studies have shown random dopant fluctuation is responsible for the majority of long channel  $V_T$  variation; however, it does not explain all the variation in NMOS  $V_T$  [31].

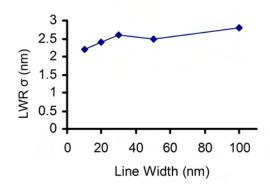

A second source of variation, which is becoming increasingly significant with continued scaling, is patterning. The edge of a printed line exhibits roughness on the scale of 5 nm, primarily due to polymerization effects in the photoresist [32]. This line edge roughness

Figure 1.9. The variance of lithography-defined patterns becomes more significant with continued scaling, due to phenomena such as line edge roughness (LER) (figure adapted from [32]) and proximity effects [33, 34]. The effects are manifest in the gate lengths and channel widths of a  $0.79\mu m^2$  SRAM cell after gate patterning [35].

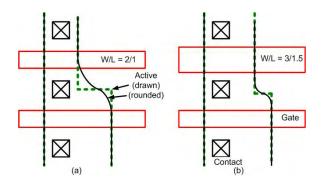

(LER) becomes significant for dimensions smaller than 50 nm, such as gate length or channel width (Fig. 1.9). Although the variance in line width decreases as the nominal width scales down, proportionally its magnitude increases. This is especially significant for undoped multi-gate devices (e.g. FinFETs) in which  $V_T$  is set by the thickness of the active region. In addition to LER, a critical dimension can vary due to image effects from proximity or corner rounding. Printed patterns with sharp corners exhibit a rounding of the feature at spatial frequencies beyond the resolution of the lithography system, affecting the width of the feature near the corner. SRAM gate length has been shown to vary as a function of the layout of the gate and nearby features [33, 34].

Additional sources of variation can be present in strain application or contact resistance; however, these sources are not yet significant for SRAM.

#### 1.3.2 Contemporary work

Variation in SRAM is currently an active area of research, with several yearly reports on measured yield or SNM specifically [36, 37, 38, 39, 21, 22, 40]. Among all types of variations, Venkatraman *et al.* reported that uncorrelated random variations dominate, based on measurements of 90nm node devices [41]. Yamaoka *et al.* reported that the

standard deviation of these variations can depend on systematic variations at the array or wafer level [42]. In some designs, these variations can affect the write-ability of the cell more than SNM [43]. Statistical or "variation-aware" design methodologies are now indispensible [44, 42, 45].

Such methods require fast and accurate models for critical SRAM metrics. Unfortunately, the models with closed-form equations for SNM are no longer accurate for short-channel devices that operate near threshold. Recent models that do achieve a closed-form or semi-analytical expression for SNM make large approximations at the expense of accuracy [46, 47, 48]. They are fast, but not accurate. Other modeling efforts have derived new SRAM metrics [49, 50] or taken a probabilistic approach [51, 52], but lack the tractability or the fundamental basis of SNM. New metrics also take time to be embraced. Although several write-ability metrics have been proposed [49, 43, 53], a consensus has not yet emerged.

A common practice for SRAM modeling is circuit simulation, with a program such as SPICE, using advanced device models and Monte Carlo methods to estimate yield. This approach is accurate, but not fast. Accurate device models must be developed, which can be difficult and time-consuming in a developing technology. For transient simulations, the parasitic resistances and capacitances of a layout must also be modeled, which can require multiple iterations of process characterization. Monte Carlo simulations require many iterations as well. Nevertheless, this approach can yield useful evaluations of the sensitivities and variability of an SRAM design [54].

For process or device technologies where accurate circuit models are not yet available, the mixed-mode capability of a device-simulator such as TAURUS [55] is generally used. Although these simulations require even more computing time, they enable useful observations on the scaling behavior of SRAM. Such simulations have shown that multigate devices will be attractive for SRAM due to improved control of short channel effects and reduced variability [4, 56, 57, 58]. Furthermore, devices with undoped channels are expected to greatly reduce variability by mitigating random dopant fluctuation [59, 60].

Such simulations can influence the development of new devices to reduce variation. Dixit  $et\ al.$  have begun investigating the variability of fabricated FinFET SRAM using a spacer lithography patterning technique to reduce LER [61]. Okayama  $et\ al.$  introduced a fully silicided gate to reduce  $V_T$  variation from dopant penetration [62]. Reducing variation at the device level enables a higher-yielding SRAM cell.

In addition to these efforts, new circuits have been proposed to compensate for increasing variability. By modifying the body bias of blocks of several SRAM cells, yield metrics such as fail counts and minimum operating voltage  $(V_{min})$  can be improved [63, 64]. Wordline biasing can also be used to tradeoff read stability and write-ability [65]. Read stability can be improved by limiting the amount of charge flowing into a cell [66, 67]. The primary tradeoff of these techniques is an array-level increase in area.

#### 1.3.3 This work

This work aims to facilitate continued SRAM scaling in three ways: by furthering the understanding of variation and its sources in an SRAM cell and by developing a new modeling approach to accelerate statistical design methods, by investigating new devices and processes to reduce the sources of variation, and by proposing new SRAM circuits to compensate for increasing variability.

In chapter 2, a new modeling approach is presented that is both fast and accurate for read and write SRAM metrics. Unlike previous closed-form or semi-analytical models, this approach uses several device-specific I-V targets for improved accuracy. Approximations are made to the non-critical parts of the I-V curves, eliminating the need for time-consuming device simulation or model development. This modeling approach is used to investigate cell sensitivities. A statistical design methodology using these sensitivities is proposed as a fast alternative to Monte Carlo iteration. The model is used to provide insights into mechanisms of SRAM failure over time.

In chapter 3, methods to reduce process variation from random dopant fluctuation and

lithography are proposed. Device architectures that do not rely exclusively on dopants to set  $V_T$ , such as undoped FinFETs, are proposed to enhance estimated SRAM yield. SRAM cells with straight active features are shown to have reduced variation due to lithography, and an extended spacer lithography process is developed to enable high-density integration with low variability. Spacer-defined circuit design is demonstrated for a  $0.0512\mu\text{m}^2$  SRAM cell, which could be scaled smaller than any previously-reported SRAM.

In chapter 4, circuit techniques to cope with process variation are presented. A circuit to sense and correct systematic and large-area variations is demonstrated to optimize the read / write tradeoff over a wide range of operating conditions. A technique to estimate process variability from SRAM metrics and probabilities is proposed, enabling SRAM measurements as a form of *in situ* characterization to accelerate process development. FinFET-based SRAM designs with independent gating are introduced and analyzed to enhance read stability and write-ability, allowing six sigma yield for supply voltages as low as 0.4V.

Individually or in combination, it is hoped that these techniques may advance SRAM development through the next several technology nodes. The modeling approach of chapter 2 is already starting to be adopted in industry. Some kind of transition to new devices, processes, or circuits is widely expected for SRAM specifically, and it is the goal of this work to help facilitate such a transition.

#### 1.4 References

- [1] R. F. Lyon and R. R. Schediwy. CMOS static memory with a new four transistor memory cell. *Proceeding of Stanford conference on advanced research in VLSI*, pages 111–131, 1987.

- [2] K. Noda, K. Matsui, K. Imai, K. Inoue, K. Tokashiki, H. Kawamoto, K. Yoshida, K. Takeda, N. Nakamura, T. Kimura, H. Toyoshima, Y. Koishikawa, S. Maruyama, T. Saitoh, , and T. Tanigawa. A 1.9-μm2 loadless CMOS four-transistor SRAM cell in a 0.18-μm logic technology. *IEEE International Electron Devices Meeting*, pages 643–646, 1998.

- [3] O. Semenov, A. Pavlov, and M. Sachdev. Sub-quarter micron SRAM cells stability in low-voltage operation: a comparative analysis. *IEEE International Reliability Workshop*, pages 168–171, 2002.

- [4] Z. Guo, S. Balasubramanian, R. Zlatanovici, T.-J. King, and B. Nikolic. FinFET-based SRAM design. *IEEE International Symposium on Low Power Electronics and Design*, pages 2–7, 2005.

- [5] B. Giraud, A. Amara, and A. Vladimirescu. A comparative study of 6T and 4T SRAM cells in double-gate CMOS with statistical variation. *IEEE International Symposium on Circuits and Systems*, pages 3022–3025, 2007.

- [6] N. Lindert, Y.-K. Choi, L. Chang, E. Anderson, W. Lee, T.-J. King, J. Bokor, and C. Hu. Quasi-planar NMOS FinFETs with sub-100 nm gate lengths. *IEEE Device Research Conference*, pages 26–27, 2001.

- [7] L. Chang, D.M. Fried, J. Hergenrother, J.W. Sleight, R.H. Dennard, R.K. Montoye, L. Sekaric, S.J. McNab, A.W. Topol, C.D. Adams, K.W. Guarini, and W. Haensch. Stable SRAM cell design for the 32 nm node and beyond. *IEEE Symposium on VLSI Technology*, pages 128–129, 2005.

- [8] L. Chang, Y. Nakamura, R.K. Montoye, J. Sawada, A.K. Martin, K. Kinoshita, F.H. Gebara, K.B. Agarwal, D.J. Acharyya, W. Haensch, K. Hosokawa, and D. Jamsek. A 5.3GHz 8T-SRAM with operation down to 0.41V in 65nm CMOS. *IEEE Symposium on VLSI Circuits*, pages 252–253, 2007.

- [9] Z. Liu and V. Kursun. High read stability and low leakage cache memory cell. *IEEE International Symposium on Circuits and Systems*, pages 2774–2777, 2007.

- [10] B. Calhoun and A. Chandrakasan. A 256-kb 65-nm sub-threshold SRAM design for ultra-low-voltage operation. IEEE Journal of Solid-State Circuits, pages 680–688, 2007.

- [11] T.-H. Kim, J. Liu, J. Keane, and C. Kim. A high-density subthreshold SRAM with data-independent bitline leakage and virtual ground replica scheme. *IEEE International Solid-State Circuits Conference*, pages 330–332, 2007.

- [12] D.M. Fried, J.M. Hergenrother, A.W. Topol, L. Chang, L. Sekaric, J.W. Sleight, S.J. McNab, J. Newbury, S.E. Steen, G. Gibson, Y. Zhang, N.C.M. Fuller, J. Bucchignano, C. Lavoie, C. Cabral Jr, D. Canaperi, O. Dokumaci, D.J. Frank, E.A. Duch, I. Babich, K. Wong, J.A. Ott, C.D. Adams, T.J. Dalton, R. Nunes, D.R. Medeiros, R. Viswanathan, M. Ketchen, M. Ieong, W. Haensch, and K.W. Guarini. Aggressively scaled (0.143 /spl mu/m/sup 2/) 6T-SRAM cell for the 32 nm node and beyond. IEEE International Electron Devices Meeting, pages 261 264, 2004.

- [13] M. Okuno, K. Okabe, T. Sakuma, K. Suzuki, T. Miyashita, T. Yao, H. Morioka, M. Terahara, Y. Kojima, H. Watatani, K. Sugimoto, T. Watanabe, Y. Hayami, T. Mori, T. Kubo, Y. Iba, I. Sugiura, H. Fukutome, Y. Morisaki, H. Minakata, K. Ikeda, S. Kishii, N. Shimizo, T. Tanaka, S. Asai, M. Nakaishi, S. Fukuyama, A. Tsukune, M. Yamabe, I. Hanyuu, M. Miyajima, M. Kase, K. Watanabe, S. Satoh, and T. Sugii. 45nm node CMOS integration with a novel STI structure and full-NCS/Cu interlayers for low-operation-power (LOP) applications. *International Electron Devices Meeting*, pages 52–55, 2005.

- [14] H. Nii, T. Sanuki, Y. Okayama, K. Ota, T. Iwamoto, T. Fujimaki, T. Kimura, R. Watanabe, T. Komoda, A. Eiho, K. Aikawa, H. Yamaguchi, R. Morimoto, K. Ohshima, T. Yokoyama, T. Matsumoto, K. Hachimine, Y. Sogo, S. Shino, S. Kanai, T. Yamazaki, S. Takahashi, H. Maeda, T. Iwata, K. Ohno, Y. Takegawa, A. Oishi, M. Togo, K. Fukasaku, Y. Takasu, H. Yamasaki, H. Inokuma, K. Matsuo, T. Sato, M. Nakazawa, T. Katagiri, K. Nakazawa, T. Shinyama, T. Tetsuka, S. Fujita, Y. Kagawa, K. Nagaoka, S. Muramatsu, S. Iwasa, S. Mimotogi, K. Yoshida, K. Sunouchi, M. Iwai, M. Saito, M. Ikeda, Y. Enomoto, H. Naruse, K. Imai, S. Yamada, N. Nagashima, T. Kuwata, and F. Matsuoka. A 45nm high performance bulk logic platform technology (CMOS6) using ultra high NA(1.07) immersion lithography with hybrid dual-damascene structure and porous low-k BEOL. IEEE International Electron Devices Meeting, pages 685–688, 2006.

- [15] S.-Y. Wu, C.W. Chou, C.Y. Lin, M.C. Chiang, C.K. Yang, M.Y. Liu, L.C. Hu, C.H. Chang, P.H. Wu, C.I. Lin, H.F. Chen, S.Y. Chang, S.H. Wang, P.Y. Tong, Y.L. Hsieh, P.Y. Tong, J.J. Liaw, K.H. Pan, C.H. Hsieh, C.H. Chen, J.Y. Cheng, C.H. Yao, W.K. Wan, T.L. Lee, K.T. Huang, C.C Chen, K.C. Lin, L.Y. Yeh, K.C. Ku, S.C. Chen, C.W. Chang, H.J. Lin, S.M. Jang, Y.C. Lu, J.H. Shieh, M.H. Tsai, J.Y. Song, K.S. Chen, V. Chang, S.M. Cheng, S.H. Yang, C.H. Diaz, Y.C. See, and M.S. Liang. A 32nm CMOS low power SoC platform technology for foundry applications with functional high density SRAM. International Electron Devices Meeting, pages 263–266, 2007.

- [16] Y. Yamagata. Embedded memory technology for low power systems. Adapted from IEEE International Electron Devices Meeting, 2005. Short Course Presentation.

- [17] E. Seevinck, F. List, and J. Lohstroh. Static-noise margin analysis of MOS SRAM cells. IEEE Journal of Solid-State Circuits, pages 748–754, 1987.

- [18] S.-F. Huang, C.-Y. Lin, Y.-S. Huang, T. Schafbauer, M. Eller, Y.-C. Cheng, S.-M. Cheng; S. Sportouch, W. Jin, N. Rovedo, A. Grassmann, Y. Huang, J. Brighten, C.H. Liu, B. von Ehrenwall, N. Chen, J. Chen; O.S. Park, M. Commons, A. Thomas, M.-T. Lee, S. Rauch, L. Clevenger, E. Kaltalioglu, P. Leung, J. Chen, T. Schiml, and C. Wann. High performance 50 nm cmos devices for microprocessor and embedded processor core applications. *IEEE International Electron Devices Meeting*, pages 237–240, 2001.

- [19] M. Khare, S. H. Ku, R.A. Donaton, S. Greco, C. Brodsky, X. Chen, A. Chou, R. DellaGuardia, S. Deshpande, B. Doris, S.K.H. Fung, A. Gabor, M. Gribelyuk, S. Holmes, F.F. Jamin, W.L. Lai, W.H. Lee, Y. Li, P. McFarland R. Mo, S. Mittl, S. Narasimha, D. Nielsen, R. Purtell, W. Rausch, S. Sankaran, J. Snare, L. Tsou, A. Vayshenker, T. Wagner, D. Wehella-Gamage, E. Wu, S. Wu, W. Yan, E. Barth, R. Ferguson, P. Gilbert, D. Schepis, A. Sekiguchi, R. Goldblatt, J. Welser, K.P. Muller, and P. Agnello. A high performance 90nm SOI technology with 0.992 μm² 6T-SRAM cell. *IEEE International Electron Devices Meeting*, pages 407–410, 2002.

- [20] T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr. A 90nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors. *IEEE International Electron Devices Meeting*, pages 978–980, 2003.

- [21] P. Bai, C. Auth, S. Balakrishnan, M. Bost, R. Brain, V. Chikarmane, R. Heussner, M. Hussein, J. Hwang, D. Ingerly, R. James, I. Jeong, C. Kenyan, E. Lee, S-H. Lee, N. Lindert, M. Liu, Z. Ma, T. Marieb, A. Murthy, R. Nagisetty, S. Natarajan, J. Neirynck, A. Ott, C. Parker, J. Sebastian, R. Shaheed, S. Sivakumar, J. Steigenvald, S. Tyagi, C. Weber, B. Woolely, A. Yeoh, K. Zhang, and M. Bohr. A 65nm logic technology featuring 35nm gate lengths and enhanced channel strain and 8 Cu interconnect layers and low-k ILD and 0.57 μm² SRAM cell. IEEE International Electron Devices Meeting, pages 657–660, 2004.

- [22] W-H. Lee, A.Waite, H. Nii, H. M. Nayfeh, V. McGahay, H. Nakayama, D. Fried, H. Chen, L. Black, R. Bolam, J. Cheng, D. Chidambarrao, C. Christiansen, M. Cullinan-Scholl, D. R. Davies, A. Domenicucci, P. Fisher, J. Fitzsimmons, J. Gill, M. Gribelyuk, D. Harmon, J. Holt, K. Ida, M. Kiene, J. Kluth, C. Labelle, A. Madan, K. Malone, P. V. McLaughlin, M. Minami, D. Mocuta, R. Murphy, C. Muzzy, M. Newport, S. Panda, I. Peidous, A. Sakamoto, T. Sato, G. Sudo, H. VanMeer, T. Yamashita, H. Zhu, P. Agnello, G. Bronner G. Freeman, S-F Huang, T. Ivers, S. Luning, K. Miyamoto, H. Nye, J. Pellerin, K. Rim, D. Schepis, T. Spooner, X. Chen, and M. Khare. High performance 65 nm SOI technology with enhanced transistor strain and advanced-low-K BEOL. IEEE International Electron Devices Meeting, 2005.

- [23] K. Agawa, H. Hara, T. Takayanagi, and T. Kuroda. A bit-line leakage compensation scheme for low-voltage SRAMs. *IEEE Symposium on VLSI Circuits*, pages 70–71, 2000.

- [24] M. Yoshimoto, K. Anami, H. Shinohara, T. Yoshihara, H. Takagi, S. Nagao, S. Kayano, and T. Nakano. A divided word-line structure in the static RAM and its application to a 64K full CMOS RAM. *IEEE Journal of Solid-State Circuits*, pages 479–485, 1983.

- [25] M. Agostinelli, J. Hicks, J. Xu, B. Woolery, K. Mistry, K. Zhang, S. Jacobs, J. Jopling, W. Yang, B. Lee, T. Raz, M. Mehalel, P. Kolar, Y. Wang, J. Sandford, D. Pivin, C. Peterson, M. DiBattista, S. Pae, M. Jones, S. Johnson, and G. Subramanian. Erratic fluctuations of SRAM cache vmin at the 90nm process technology node. *IEEE International Electron Devices Meeting*, pages 655–658, 2005.

- [26] R. Rodriguez, R. V. Joshi, J. H. Stathis, and C. T. Chuang. Oxide breakdown model and its impact on SRAM cell functionality. *International Conference on Simulation of Semiconductor Processes and Devices*, pages 283–286, 2003.

- [27] H. Kobayashi, K. Shiraishi, H. Tsuchiya, M. Motoyoshi, H. Usuki, Y. Nagai, K. Takahisa, T. Yoshiie, Y. Sakurai, and T. Ishizaki. Soft errors in SRAM devices induced by high energy neutrons and thermal neutrons and alpha particles. *IEEE International Electron Devices Meeting*, pages 337–340, 2002.

- [28] G. Gasiot, D. Giot, and P. Roche. Alpha-induced multiple cell upsets in standard and radiation hardened SRAMs manufactured in a 65nm CMOS technology. *IEEE Transactions on Nuclear Science*, pages 3479–3486, 2006.

- [29] D. Burnett, K. Erington, C. Subramanian, and K. Baker. Implications of fundamental threshold voltage variations for high-density SRAM and logic circuits. *IEEE Symposium on VLSI Technology*, pages 15– 16, 1994.

- [30] M. Pelgrom, A. Duinmaijer, and A. Welbers. Matching properties of MOS transistors. IEEE Journal of Solid-State Circuits, pages 1433–1440, 1989.

- [31] K. Takeuchi, T. Fukai, T. Tsunomura, A. T. Putra, A. Nishida, S. Kamohara, and T. Hiramoto. Understanding random threshold voltage fluctuation by comparing multiple fabs and technologies. *International Electron Devices Meeting*, pages 467–470, 2007.

- [32] T. Yamaguchi, H. Namatsu, M. Nagase, K. Yamazaki, and K. Kurihara. Nanometer-scale linewidth fluctuations caused by polymer aggregates in resist films. Applied Physics Letters, pages 2388–2390, 1997.

- [33] A. Balasinski and D. Coburn. Comparison of mask writing tools and mask simulations for 0.16 μm devices. IEEE/SEMI Advanced Semiconductor Manufacturing Conference and Workshop, pages 372– 377, 1999.

- [34] X. Ouyang, T. Deeter, C.N. Berglund, R.F.W. Pease, J. Lee, and M.A. McCord. High-throughput high-density mapping and spectrum analysis of transistor gate length variations in SRAM circuits. *IEEE Transactions on Semiconductor Manufacturing*, pages 318–329, 2001.

- [35] S.-M. Jung, H. Kwon, J. Jeong, W. Cho, S. Kim, H. Lim, K. Koh, Y. Rah, J. Park, H. Kang, G. Lyu, J. Park, C. Chang, Y. Jang, D. Park, K. Kim, and M.-Y. Lee. A novel 0.79 μm² SRAM cell by KrF lithography and high performance 90 nm CMOS technology for ultra high speed SRAM. *IEEE International Electron Devices Meeting*, pages 419–422, 2002.

- [36] S. Thompson, M. Alavi, R. Arghavani, A. Brand R. Bigwood, J. Brandenburg, B. Crew, V. Dubin, M. Hussein, P. Jacob, C. Kenyon, E. Lee, B. Mcintyre, Z. Ma, P. Moon, P. Nguyen, M. Prince, R. Schweinfurth, S. Sivakumar, P. Smith, M. Stettler, S. Tyagi, M. Wei, J. Xu, S. Yang, and M. Bohr. An enhanced 130nm generation logic technology featuring 60nm transistors optimized for high performance and low power at 0.7 1.4 V. IEEE International Electron Devices Meeting, pages 257–260, 2001.

- [37] Y. Fukaura, K. Kasai, Y. Okayama, H. Kawasaki, K. Isobe, M. Kanda, K. Ishimaru, and H. Ishiuchi. A highly manufacturable high density embedded SRAM technology. *IEEE International Electron Devices Meeting*, pages 415–418, 2002.

- [38] C. B. Oh, H. S. Kang, H. J. Ryu, M. H. Oh, H. S. Jung, Y. S. Kim, J. H. Lee, N. I. Lee, K. H. Cho, D. H. Lee, T. H. Yang, I. S. Cho, H. K. Kang, Y. W. Kim, and K. P. Suh. Manufacturable embedded CMOS 6T-SRAM technology with high-k gate dielectric device for system-on-chip applications. *IEEE International Electron Devices Meeting*, pages 423–426, 2002.

- [39] Y. Hirano, T. Ipposhi, H. Dang, T. Matsumoto, T. Iwamatsu, K. Nii, Y. Tsukamoto, T. Yoshizawa, H. Kato, S. Maegawa, K. Arimoto, Y. Inoue, M. Inuishi, and Y. Ohji. Impact of actively body-bias controlled (ABC) SOI SRAM by using direct body contact technology for low-voltage application. *IEEE International Electron Devices Meeting*, pages 35–38, 2003.

- [40] M. Ball, J. Rosal, R. McKee, WK Loh, T. Houston, R. Garcia, J. Raval, D. Li, R. Hollingsworth, R. Gury, R. Eklund, J. Vaccani, B. Castellano, F. Piacibello, S. Ashburn, A. Tsao, A. Krishnan, J. Ondrusek, and T. Anderson. A screening methodology for vmin drift in SRAM arrays with application to sub-65nm nodes. *IEEE International Electron Devices Meeting*, pages 705–708, 2006.

- [41] R. Venkatraman, R. Castagnetti, and S. Ramesh. The statistics of device variations and its impact on SRAM bitcell performance and leakage and stability. *International Symposium on Quality Electronic Design*, 2006.

- [42] M. Yamaoka and H. Onodera. A detailed Vth-variation analysis for sub-100-nm embedded SRAM design. *International System-on-Chip Conference*, pages 315–318, 2006.

- [43] A. Bhavnagarwala, S. Kosonocky, C. Radens, K. Stawiasz, R. Mann, Q. Ye, and K. Chin. Fluctuation limits and scaling opportunities for CMOS SRAM cells. *IEEE International Electron Devices Meeting*, pages 659–662, 2005.

- [44] R. Heald and P. Wang. Variability in sub-100nm SRAM designs. *International Conference on Computer Aided Design*, pages 347–352, 2004.

- [45] D. Burnett. Statistical design issues of SRAM bitcells and sense amps. IEEE Silicon on Insulator Conference, 2006. Short Course.

- [46] T. Ichikawa and M. Sasaki. A new analytical model of SRAM cell stability in low-voltage operation. IEEE Transactions on Electron Devices, pages 54–61, 1996.

- [47] Q. Chen, A. Guha, and K. Roy. An accurate analytical SNM modeling technique for SRAMs based on butterworth filter function. *IEEE International Conference on VLSI Design*, pages 615–620, 2007.

- [48] B. Calhoun and A. Chandrakasan. Static noise margin variation for sub-threshold SRAM in 65-nm CMOS. *IEEE Journal of Solid-State Circuits*, pages 1673–1679, 2006.

- [49] C. Wann, R. Wong, D. Frankt, R. Mann, S.-B. Ko, P. Croce, D. Lea, D. Hoyniak, Y.-M. Lee, J. Toomey, M. Weybright, and J. Sudijono. SRAM cell design for stability methodology. *IEEE VLSI-TSA International Symposium*, pages 21–22, 2005.

- [50] C.-K. Tsai and M. Marek-Sadowska. Analysis of process variation's effect on SRAM's read stability. International Symposium on Quality Electronic Design, 2006.

- [51] S. Mukhopadhyay, H. Mahmoodi, and K. Roy. Modeling of failure probability and statistical design of SRAM array for yield enhancement in nanoscaled CMOS. *IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems*, pages 1859–1880, 2005.

- [52] K. Agarwal and S. Nassif. Statistical analysis of SRAM cell stability. International Symposium on Quality Electronic Design, 2006.

- [53] K. Takeda, H. Ikeda, Y. Hagihara, M. Nomura, and H. Kobatake. Redefinition of write margin for next-generation SRAM and write-margin monitoring circuit. *International Solid State Circuits Conference*, page 34.5, 2006.

- [54] B. Calhoun and A. Chandrakasan. Analyzing static noise margin for sub-threshold SRAM in 65nm CMOS. European Solid-State Circuits Conference, pages 363–366, 2005.

- [55] TAURUS is a trademark of Synopsys, Inc.

- [56] A. Carlson, Z. Guo, S. Balasubramanian, L.-T. Pang, T.-J. King, and B. Nikolic. FinFET SRAM with enhanced read / write margins. *IEEE Silicon on Insulator Conference*, pages 105–106, 2006.

- [57] H. Ananthan and K. Roy. Technology and circuit design considerations in quasi-planar double-gate SRAM. IEEE Transactions on Electron Devices, pages 242–250, 2006.

- [58] S.-H. Kim and J. Fossum. Design optimization and performance projections of double-gate FinFETs with gatesource/drain underlap for SRAM application. *IEEE Transactions on Electron Devices*, pages 1934–1942, 2007.

- [59] K. Takeuchi, R. Koh, and T. Mogami. A study of the threshold voltage variation for ultra-small bulk and SOI CMOS. IEEE Transactions on Electron Devices, pages 1995–2001, 2001.

- [60] K. Samsudin, B. Cheng, A.R. Brown, S. Roy, and A. Asenov. UTB SOI SRAM cell stability under the influence of intrinsic parameter fluctuation. European Solid State Device Engineering Research Conference, pages 553–556, 2005.

- [61] A. Dixit, K. G. Anil, E. Baravelli, P. Roussel, A. Mercha, C. Gustin, M. Bamal, E. Grossar, R. Rooyackers, E. Augendre, M. Jurczak, S. Biesemans, and K. De Meyer. Impact of stochastic mismatch on measured SRAM performance of FinFETs with resist/spacer-defined fins: Role of line-edge-roughness. *IEEE International Electron Devices Meeting*, pages 709–712, 2006.

- [62] Y. Okayama, T. Saito, K. Nakajima, S. Taniguchi, T. Ono, K. Nakayama, R. Watanabe, A. Oishi, A. Eiho, T. Komoda, T. Kimura, M. Hamaguchi, Y. Takegawa, T. Aoyama, T. Iinuma, K. Fukasaku, R. Morimoto, K. Oshima, K. Oono, M. Saito, M. Iwai, N. Nagashima, and F. Matsuoka. Suppression effects of threshold voltage variation with Ni FUSI gate electrode for 45nm node and beyond LSTP and SRAM devices. IEEE Symposium on VLSI Technology, pages 96–97, 2006.

- [63] S. Mukhopadhyay, K. Kim, H. Mahmoodi, and K. Roy. Design of a process variation tolerant self-repairing SRAM for yield enhancement in nanoscaled CMOS. *IEEE Journal of Solid-State Circuits*, pages 1370–1382, 2007.

- [64] M. Sumita, S. Sakiyama, M. Kinoshita, Y. Araki, Y. Ikeda, and K. Fukuoka. Mixed body bias techniques with fixed Vt and Ids generation circuits. IEEE Journal of Solid-State Circuits, pages 60–66, 2005.

- [65] H. Morimura and N. Shibata. A step-down boosted-wordline scheme for 1-v battery-operated fast SRAM's. *IEEE Journal of Solid-State Circuits*, pages 1220–1227, 1998.

- [66] H. Pilo, J. Barwin, G. Braceras, C. Browning, S. Burns, J. Gabric, S. Lamphier, M. Miller, A. Roberts, and F. Towler. An SRAM design in 65nm and 45nm technology nodes featuring read and write-assist circuits to expand operating voltage. *IEEE Symposium on VLSI Circuits*, pages 15–16, 2006.

- [67] P. Elakkumanan, J. B. Kuang, K. Nowka, R. Sridhar, R. Kanj, and S. Nassif. SRAM local bit line access failure analyses. *International Symposium on Quality Electronic Design*, 2006.

## Chapter 2

# Understanding Variation in SRAM

#### 2.1 Introduction

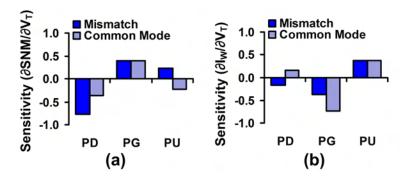

Effective reduction of variation in SRAM metrics requires a thorough understanding of its origins. Although measured SRAM variations have been linked generally to process variations, it is not initially obvious exactly how such variations cause failures. Do all variations matter equally, on all devices? Are correlated variations significant, or do mismatch variations dominate? These kinds of questions require accurate modeling of SRAM metrics down to the device parameters. Understanding the mechanisms of how parameter variation affects these metrics can inform cell and array design and improve SRAM performance and yield.

SRAM variability has become so significant of a concern that it now influences device and technology design. Novel processes have been presented to reduce variation caused by line edge roughness [1] and dopant penetration [2]. Gate length scaling in SRAM has slowed to reduce variability further. To gauge the effectiveness of design options at this level, a model is desired that can estimate SRAM metrics without the need for process development and characterization. To estimate potential yield, it must be able to simulate quickly across a wide range of perturbations. Although the mixed-mode capabilities of a device simulator could provide excellent accuracy across such a range, these simulators

Table 2.1. Device Operating Modes

| Device | $A (V_{DD} = 1.2V)$ | $B (V_{DD} = 0.6V)$           |

|--------|---------------------|-------------------------------|

| PD1    | linear              | linear                        |

| PD2    | saturation          | $\operatorname{subthreshold}$ |

| PG3    | saturation          | weak saturation               |

| PG4    | subthreshold        | $\operatorname{subthreshold}$ |

| PU5    | subthreshold        | $\operatorname{subthreshold}$ |

| PU6    | linear              | linear                        |

Figure 2.1. As  $V_{DD}$  scales down but  $V_T$  stays constant, the operating modes of the SRAM devices change, requiring new equations to represent the voltage transfer curves. Points A and B illustrate the change at two operating points relevant to calculating SNM. In particular, the transition of PD2 into subthreshold requires subthreshold I-V modeling at low  $V_{DD}$ .

provide far more information than what is required and are notoriously slow for it. A better solution is a model that accurately represents SRAM metrics as a function of individual device parameters. For ideal speed, the model equations should be in closed form or at least require only a minimal amount of iteration.

Under constant field scaling, such a model was feasible. Seevinck et al. presented a model derived from the long channel I-V equations of the square law, Eqns. 1.1 [3]. With that model, SNM could be expressed as an equation of basic device widths and lengths by solving for the butterfly curves directly. The model made several approximations, which have since proved obsolete, including ones for the operating modes of the transistors. Fig. 2.1 illustrates how operating modes can change for two points relevant to SNM calculation.

The mode of operation determines which of Eqns. 1.1 is used. A change in modes requires the derivation of a new expression for SNM. Although the algebra is tedious, a closed-form expression can be achieved for many cases; however, the accuracy is significantly degraded when subthreshold current becomes significant. This is the case in Fig. 2.1 for **PD2**, which transitions into subthreshold operation. Assuming a strict cutoff of  $I_{DS} = 0$  in

subthreshold (e.g. as in [4]) distorts the shoulder of the butterfly curves around point  $\mathbf{B}$ , resulting in a 19% overestimation of SNM.

To accurately estimate SNM for this case, two adjustments must be made. Subthreshold or, specifically, weak-inversion current must be modeled around  $V_T$ . This has an exponential dependence, which diminishes the number of cases with a closed-form solution. Secondly, threshold voltage must be treated separately for each device, with dependencies on individual parameter variations. A drain bias dependence must also be included for devices with significant short channel effects.

Recent models have therefore struggled to provide fast and accurate estimates for SNM. Calhoun and Chandrakasan solved SNM for deep subthreshold operation only, and for only minor parameter variations [5]. Chen et al. introduced a model for the butterfly curves using the Butterworth filter function to sidestep the complicated equations; however, the accuracy of the derived SNM is limited and the butterfly curves are divorced from the device parameter dependencies [6]. In spite of this, the authors rightly observe that accurate SNM modeling does not require accuracy in all sections of the butterfly curves. Only four parts of the butterfly curves are important for accurate SNM modeling: the point **A** or **B** from Fig. 2.1, its complement on the lower half of the square, and the corresponding points on the opposite lobe.

## 2.2 Model Development and Validation

This work proposes a semi-analytical model to provide simultaneous fast and accurate estimates for SRAM metrics, including SNM. Rather than generating several equations to approximate SNM in various limited regions or generating approximations of the butterfly curves, this model generates an analytical expression for device I-V behavior. The butterfly curves are generated through iterated, numerical solution. This approach is similar to that employed by circuit simulators such as SPICE; however, the inputs consist of only a few device I-V targets, rather than an advanced deck of hundreds of parameters. It therefore

can be fit to a device technology with less characterization. From these targets, a limited number of parameters for short-channel I-V equations are calculated, such that the model is guaranteed to be accurate at every target.

Short-channel I-V equations are chosen to provide the model with a generic basis on device physics, including effects that correspond to channel length modulation, drain-induced-barrier-lowering (DIBL), velocity saturation, and bulk charge effects (adapted from [7]).

$$I_{DS} = \begin{cases} \mu_{s} C_{ox} \frac{W}{2mL} \frac{(V_{GS} - V_{T})^{2}}{1 + \frac{V_{GS} - V_{T}}{E_{sat}L}} (1 + \lambda V_{DS}) + I_{sub} \left(1 - e^{\frac{V_{DS}}{V_{th}}}\right) & V_{GS} > V_{T} \text{ and} \\ V_{DS} \ge \frac{V_{GS} - V_{T}}{m} & V_{DS} \ge \frac{V_{GS} - V_{T}}{m} \end{cases}$$

$$I_{DS} = \begin{cases} \mu_{l} C_{ox} \frac{W}{L} \frac{V_{DS}(V_{GS} - V_{T} - \frac{mV_{DS}}{V_{0}})}{1 + \frac{V_{GS} - V_{T}}{E_{sat}L}} (1 + \lambda V_{DS}) + I_{sub} \left(1 - e^{\frac{V_{DS}}{V_{th}}}\right) & V_{GS} > V_{T} \text{ and} \\ V_{DS} < \frac{V_{GS} - V_{T}}{m} & V_{DS} \le V_{T} \end{cases}$$

$$I_{sub} \left(1 - e^{\frac{V_{DS}}{V_{th}}}\right) e^{\frac{V_{GS} - V_{T}}{S}} & V_{GS} \le V_{T} \end{cases}$$

$$(2.1)$$

where  $C_{ox}$  is the gate oxide capacitance per unit area, W is the width of the device, L is the gate length,  $V_{GS}$  is the voltage on the gate with respect to the source,  $V_{DS}$  is the voltage on the drain with respect to the source,  $I_{sub}$  is the constant current definition for  $V_T$ , and  $V_T$  is the threshold voltage of the transistor as a function of drain bias:

$$V_T = V_{T0} - DV_{DS} (2.2)$$

The other parameters are used for fitting. Separate carrier mobilities  $\mu_l$  and  $\mu_s$  are used for linear and saturation, respectively, to improve the fit. To ensure continuity between operating modes, a parameter  $V_0$  is introduced such that

$$V_0 = \frac{1}{1 - \frac{\mu_s}{2u_l}} \tag{2.3}$$

$\lambda$  is a fitting parameter corresponding to channel length modulation, D represents DIBL,  $E_{sat}$  determines the amount of velocity saturation, and S represents the subthreshold swing. For ideal MOSFETs, the parameters S and m are equivalent and represent the degree to which the gate has control of the channel. In this work, a separate, global m parameter is

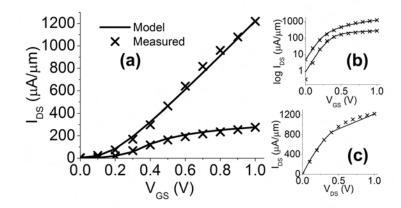

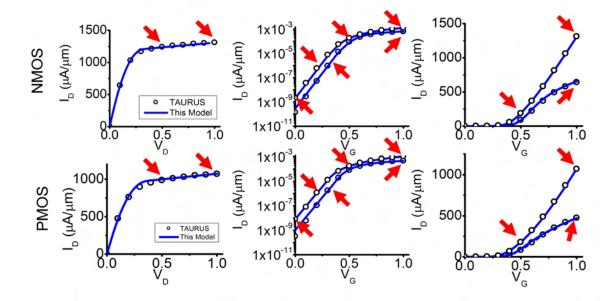

Figure 2.2. The seven parameter model introduced in this work can be used to approximate MOSFET I-V behavior even if the equations are not physically accurate. Model-generated  $I_{DS}-V_{GS}$  curves (a,b) at  $V_{DS}=0.1,1.0\mathrm{V}$  and  $I_{DS}-V_{DS}$  at  $V_{GS}=1.0\mathrm{V}$  (c) exhibit good agreement with the reported I-V of a Schottky source/drain FinFET with 15nm gate length [8]. The accuracy is within 15% at all points with  $I_{DS} \geq 1\mu A/\mu m$  and  $0 \leq V_{DS}, V_{GS} \leq 1\mathrm{V}$ .

used to improve overall I-V agreement, and is not used to fit to individual devices. In all, there are seven independent device-specific parameters,  $\mu_l$ ,  $\mu_s$ ,  $\lambda$ , D,  $E_{sat}$ , S, and  $V_{T0}$ , in addition to device dimensions W and L.

To the extent that a modeled device exhibits short-channel phenomena, the I-V curves are accurate; however, the curves provide a reasonable approximation even in the presence of non-idealities or fundamental differences in carrier transport. As long as the true I-V curves of the device resemble those of a planar MOSFET, the model will be relatively accurate. This enables the model to represent advanced devices such as FinFETs without exact knowledge of the true I-V equations. Fig. 2.2 illustrates better than 15% agreement over  $1\mu A/\mu m$  of this model with the reported I-V from a Schottky source/drain FinFET with 15nm gate length [8].

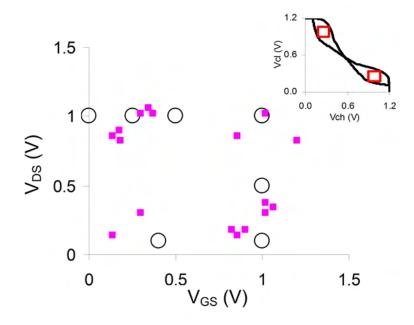

For the purpose of modeling SRAM, accuracy can be improved if the I-V targets around which the model is most accurate correspond to the operating biases most critical for modeling SNM and other metrics. Fig. 2.3 illustrates the biases of interest for NMOS and PMOS devices at key points on the butterfly curves. The most important regions are

Figure 2.3. The drain and gate biases of the six SRAM devices (squares) for the key points for SNM and write-ability at  $V_{DD} = 1.2V$  (inset). The important regions are at high  $V_{GS}$  or high  $V_{DS}$  and suggest locations for I-V targets (circles) to improve model accuracy. By choosing I-V targets near these key biases, the accuracy of the model is improved.

Table 2.2. Model I-V Targets

| Target   | $I_{DLIN}$ | $I_{DSAT}$ | $I_{DLO}$ | $I_{DHI}$ | $I_{OFF}$ | $V_{TLIN}$ | $V_{TSAT}$ |

|----------|------------|------------|-----------|-----------|-----------|------------|------------|

|          |            | 1.0V       |           |           |           |            |            |

| $V_{DS}$ | 0.1V       | 1.0V       | 1.0V      | 0.5V      | 1.0V      | 0.1V       | 1.0V       |

at high  $V_{GS}$  or high  $V_{DS}$ . It is convenient that a number of commonly used I-V targets cover these regions. Table 2.2 lists the seven I-V targets used in this work.

These targets are also chosen such that there exists a one-to-one relation between them and the device parameters of Eqns. 2.1. The device parameters can then be solved as a

function of the I-V targets:

$$\mu_l = \frac{\mu_{l0}}{1 - V_{TLIN} - 0.1 \frac{m}{V_0}} \tag{2.4}$$

where

$$\mu_{l0} = \left[ I_{DLIN} - I_{sub} \left( 1 - e^{-0.1/V_{th}} \right) \right] \frac{1 + \frac{1 - V_{TLIN}}{E_{sat}L}}{0.1 C_{ox} (1 + 0.1\lambda)}$$

(2.5)

and

$$V_0 = \frac{1 - \frac{\mu_s}{2\mu_{l0}} (1 - V_{TLIN})}{1 - \frac{\mu_s}{0.2m\mu_{l0}}}$$

(2.6)

$$\mu_{s} = \frac{2m \left(I_{DSAT} - I_{sub}\right) \left(1 + \frac{1 - V_{TSAT}}{E_{sat}L}\right)}{C_{ox} \left(1 - V_{TSAT}\right)^{2} \left(1 + \lambda\right)}$$

(2.7)

$$\lambda = \frac{\frac{I_{DSAT} - I_{sub}}{I_{DHI} - I_{sub}} - \frac{(1 - V_{TSAT})^2}{(1 + 0.4D - V_{TLIN})^2} \frac{E_{sat}L + 1 + 0.4D - V_{TLIN}}{E_{sat}L + 1 - V_{TSAT}}}{\frac{(1 - V_{TSAT})^2 (E_{sat}L + 1 + 0.4D - V_{TLIN})}{(1 + 0.4D - V_{TLIN})^2 (E_{sat}L + 1 - V_{TSAT})} - \frac{I_{DSAT} - I_{sub}}{2(I_{DHI} - I_{sub})}}$$

(2.8)

$$D = \frac{V_{TLIN} - V_{TSAT}}{0.9} \tag{2.9}$$

$$D = \frac{V_{TLIN} - V_{TSAT}}{0.9}$$

$$E_{sat} = \frac{(0.5 - V_{TSAT})(I_{DLO} - I_{sub}) \left(\frac{1 - V_{TSAT}}{0.5 - V_{TSAT}}\right)^2 - (1 - V_{TSAT})(I_{DSAT} - I_{sub})}{I_{DSAT} - I_{sub} - (I_{DLO} - I_{sub}) \left(\frac{1 - V_{TSAT}}{0.5 - V_{TSAT}}\right)^2}$$

$$S = -\frac{V_{TSAT}}{\ln(\frac{I_{OFF}}{I_{sub}})}$$

(2.11)

$$S = -\frac{V_{TSAT}}{\ln(\frac{I_{OFF}}{I_{cub}})} \tag{2.11}$$

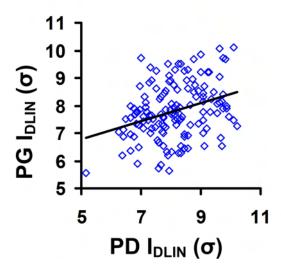

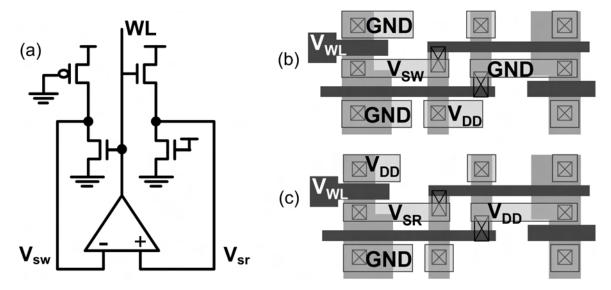

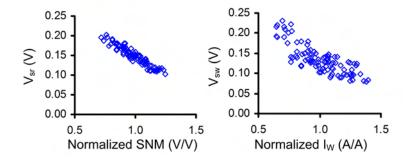

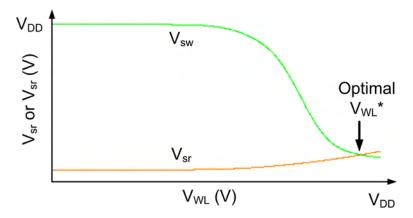

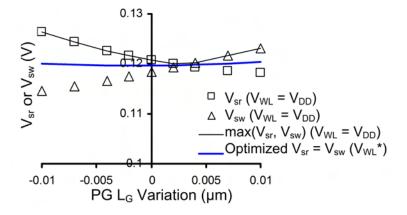

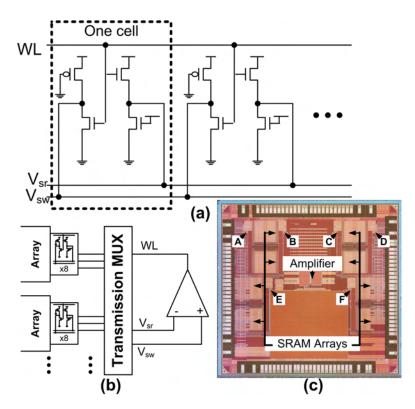

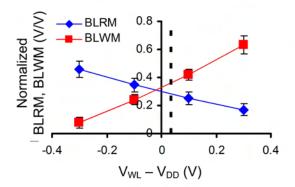

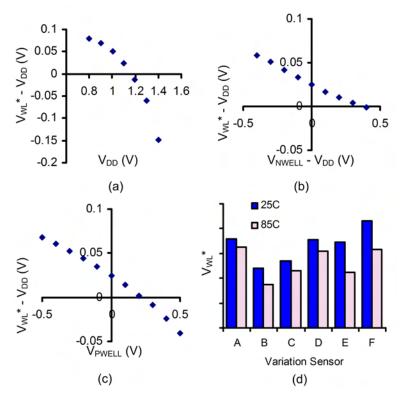

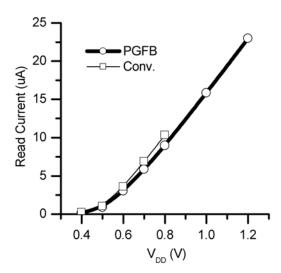

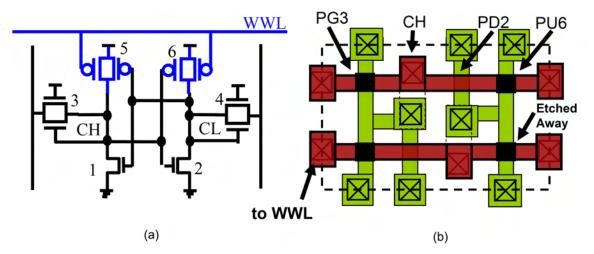

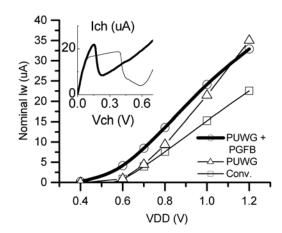

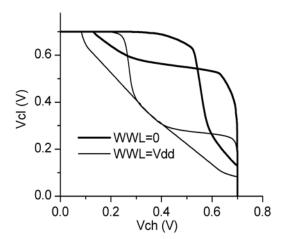

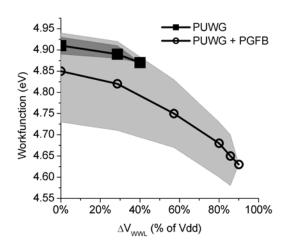

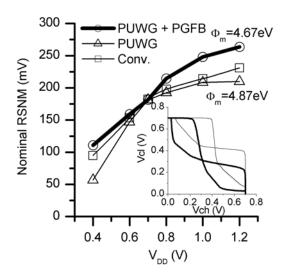

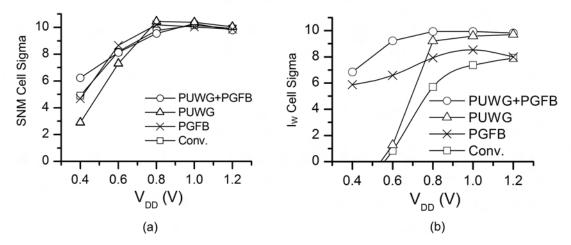

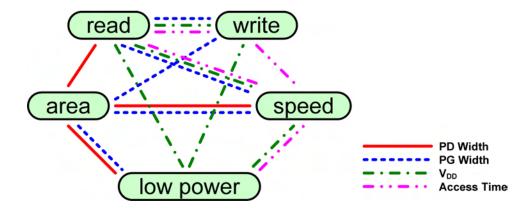

$$V_{T0} = V_{TLIN} + 0.1D (2.12)$$