### A Platform-Based Approach to Communication Synthesis for Embedded Systems

Alessandro Pinto

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-54 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-54.html

May 19, 2008

Copyright © 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### A Platform-Based Approach to Communication Synthesis for Embedded Systems

by

Alessandro Pinto

Laurea (University of Rome "La Sapienza") 1999 M.S. (University of California at Berkeley) 2003

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

### GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge: Professor Alberto L. Sangiovanni Vincentelli, Chair Professor Robert K. Brayton Professor Zuo-Jun Shen

Spring 2008

The dissertation of Alessandro Pinto is approved:

Chair

Date

Date

Date

University of California, Berkeley

Spring 2008

### A Platform-Based Approach to Communication Synthesis for Embedded Systems

Copyright 2008

by

Alessandro Pinto

#### Abstract

### A Platform-Based Approach to Communication Synthesis for Embedded Systems

by

Alessandro Pinto

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Alberto L. Sangiovanni Vincentelli, Chair

As the complexity of electronic systems increases, designers adopt a re-use methodology where new products are assembled out of components. This is a common trend in many application domains. In consumer electronics, Systems-on-Chips (SoCs) integrate many different cores to provide tens of different functions. In automotive, modern cars rely on a distributed, networked embedded system that comprises hundreds of processors to provide comfort, fuel efficiency and entertainment. In large scale systems, such as avionics and building automation, networked distributed controllers are used to provide comfort, safety and energy efficiency.

Since the system behavior depends not only on the components, but also on the way in which they interact, architecting their interconnection is a critical step in the overall design flow. Being subject to tight performance and cost constraints, the design of the interconnection architecture needs to be tailored to the specific system application. This task is too complex to be done by hand, considering also the heterogeneous nature of these systems. Therefore, there is a need for communication synthesis tools that, starting from a characterization of the communication constraints among the components and the library of available communication building blocks, automatically derive an optimal interconnection architecture.

In this thesis I argue that the essence of the communication synthesis problem is invariant to the application domain. I introduce a formal framework to capture the communication constraints, the library of communication building blocks, and the rules to compose them. Using this framework, I formulate a general communication synthesis problem. I show the generality of the approach by formulating and solving the problem in two different domains: system-on-chips and building automation systems.

> Professor Alberto L. Sangiovanni Vincentelli Dissertation Committee Chair

To my mother who raised me and let me go to follow my dreams.

## Contents

| List of Figures |                                                     |    |  |  |

|-----------------|-----------------------------------------------------|----|--|--|

| Li              | List of Tables                                      |    |  |  |

| I               | Introduction                                        | 1  |  |  |

| 1               | Trends in Electronics                               | 2  |  |  |

|                 | 1.1 System Complexity                               | 4  |  |  |

|                 | 1.2 Time-To-Market and Productivity                 | 9  |  |  |

|                 | 1.3 Re-Use                                          | 10 |  |  |

| 2               | Design Methodologies                                | 14 |  |  |

|                 | 2.1 System-Level Design                             | 16 |  |  |

|                 | 2.2 Platform-Based Design                           | 20 |  |  |

|                 | 2.2.1 Formalizing Platform-Based Design             | 22 |  |  |

|                 | 2.2.2 Example                                       | 31 |  |  |

| 3               | Communication Synthesis                             | 38 |  |  |

|                 | 3.1 Flows                                           | 39 |  |  |

|                 | 3.1.1 Maximum Flow                                  | 40 |  |  |

|                 | 3.1.2 Minimum-Cost Flow                             | 41 |  |  |

|                 | 3.1.3 Minimum-Cost Flow with End-To-End Constraints | 43 |  |  |

|                 | 3.2 Optimal Network Design                          | 44 |  |  |

|                 | 3.3 Concluding Remarks on Communication Synthesis   | 46 |  |  |

| II              | I Theoretical Background                            | 48 |  |  |

| 4               | Communication Structures                            | 49 |  |  |

| •               | 4.1 Quantities                                      | 50 |  |  |

|                 | 4.2 Communication Structures                        | 52 |  |  |

|                 |                                                     |    |  |  |

| 5  | Buil   | ling Complex Communication Architectures from Components            |         | 59  |

|----|--------|---------------------------------------------------------------------|---------|-----|

|    | 5.1    | Composition                                                         |         | 60  |

|    | 5.2    | Platforms                                                           | <br>•   | 63  |

| 6  | Com    | munication Synthesis for Networked Systems                          |         | 68  |

|    | 6.1    | Relations Among Communication Structures                            |         | 69  |

|    | 6.2    | A General Optimization Problem                                      | <br>•   | 76  |

| II | [ Aj   | plications                                                          | ;       | 80  |

| 7  | On-    | Chip Communications                                                 |         | 81  |

|    | 7.1    | Design Flow                                                         |         | 84  |

|    | 7.2    | Specification                                                       |         | 92  |

|    | 7.3    | Library and Composition Rules                                       |         | 93  |

|    | 7.4    | Optimization Algorithm                                              |         | 97  |

|    | 7.5    | Results                                                             |         | 04  |

|    |        | 7.5.1 Impact of the Application Characteristics                     |         | 05  |

|    |        | 7.5.2 Effect of Technology Scaling                                  | <br>. 1 | 07  |

|    |        | 7.5.3 Quality of the Solution                                       | <br>. 1 | 09  |

| 8  | Buil   | ling Automation Networks                                            | 1       | 15  |

|    | 8.1    | Specification                                                       | <br>. 1 | 18  |

|    | 8.2    | Capturing the Building Geometry                                     | <br>. 1 | 21  |

|    | 8.3    | Wired Networks                                                      | <br>. 1 | 25  |

|    |        | 8.3.1 Library of Communication Components                           | <br>. 1 | 27  |

|    |        | 8.3.2 Communication Platform and Implementation                     | <br>. 1 | 33  |

|    |        | 8.3.3 Optimization Algorithm                                        | <br>. 1 | 34  |

|    |        | 8.3.4 Results                                                       | <br>. 1 | 41  |

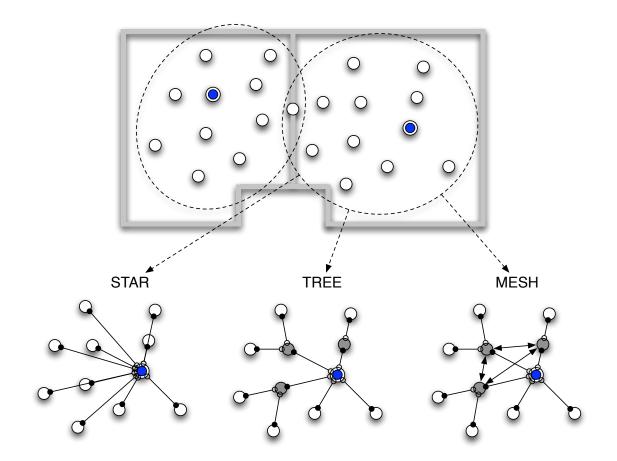

|    | 8.4    | Wireless Networks                                                   | <br>. 1 | 46  |

|    |        | 8.4.1 Library of Communication Components: Modeling ZigBee Networks | <br>. 1 | 47  |

|    |        | 8.4.2 Formulation of the Optimization Problem                       |         | 55  |

|    |        | 8.4.3 Results                                                       | <br>. 1 | 58  |

| 9  | Con    | lusions and Future Work                                             | 1       | 61  |

| Bi | bliogr | aphy                                                                | 1       | .66 |

iii

# **List of Figures**

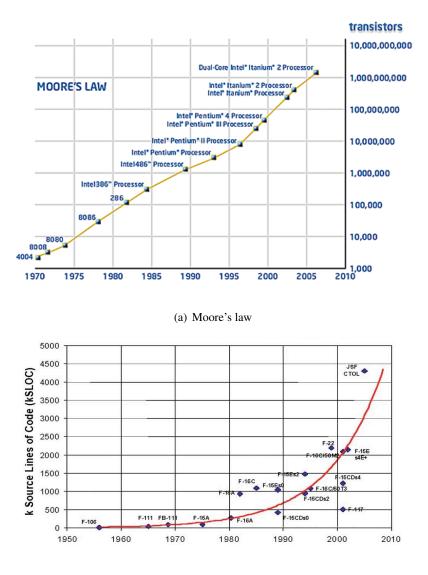

| 1.1        | System complexity: Number or transistors in Intel microprocessors as a function of time, also known as Moore's law (Source: Intel), and number of lines of code for avionic products [111]. | 5        |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

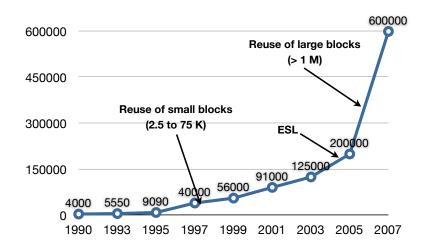

| 1.2        | Hardware design productivity expressed in number of gates per designer per year .                                                                                                           | 11       |

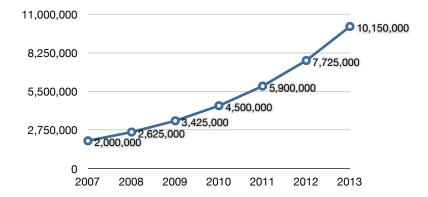

| 2.1        | System-level design flows presented in early papers on this topic.                                                                                                                          | 18       |

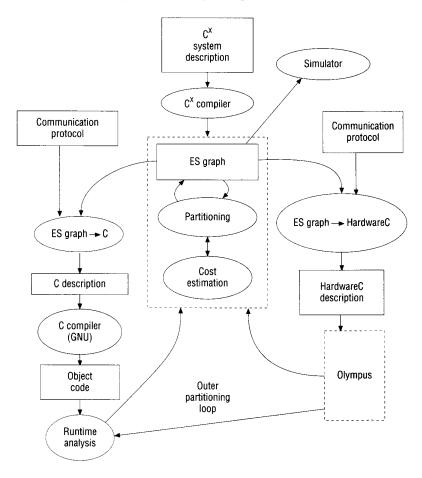

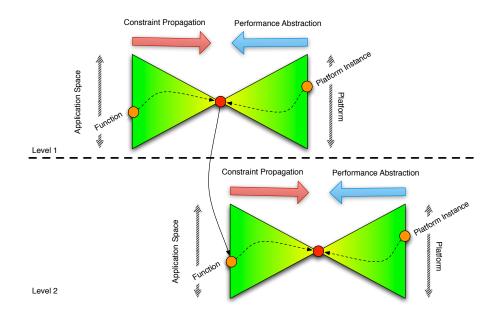

| 2.2        | Pictorial representation of a platform-based design flow.                                                                                                                                   | 21       |

| 2.3        | Architecture and Function Platforms                                                                                                                                                         | 29       |

| 2.4        | Mapping of function and architecture                                                                                                                                                        | 30       |

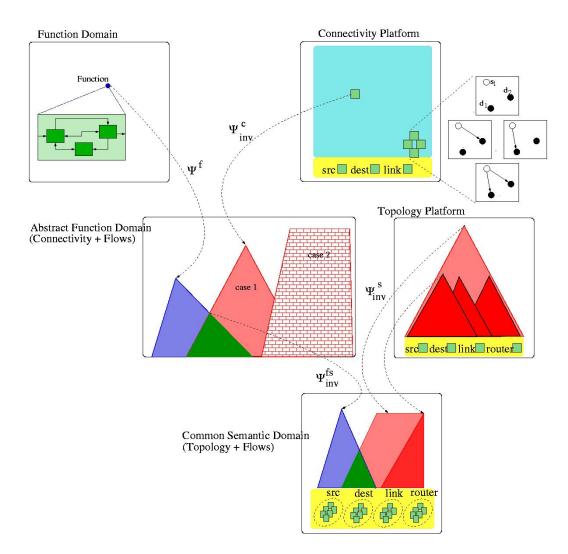

| 2.5        | Platform-based design flow for communication synthesis                                                                                                                                      | 37       |

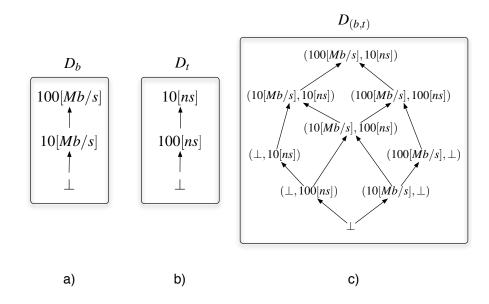

| 4.1        | Hasse diagrams relative to the domains of three quantities: a) bandwidth, b) latency, c) the set containing both bandwidth and latency.                                                     | 51       |

| 4.2        | Hasse diagram of the partial order $\leq_{(b,l)}$ for subset of communication structures                                                                                                    | 55       |

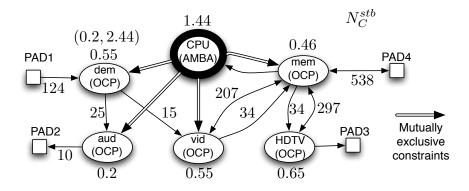

| 4.3        | The system-level specification of a simplified Set-Top Box. Each core in the specification is annotated with and area in $mm^2$ and each arrow is annotated with a                          |          |

|            | bandwidth constraint in <i>MB</i> / <i>s</i>                                                                                                                                                | 56       |

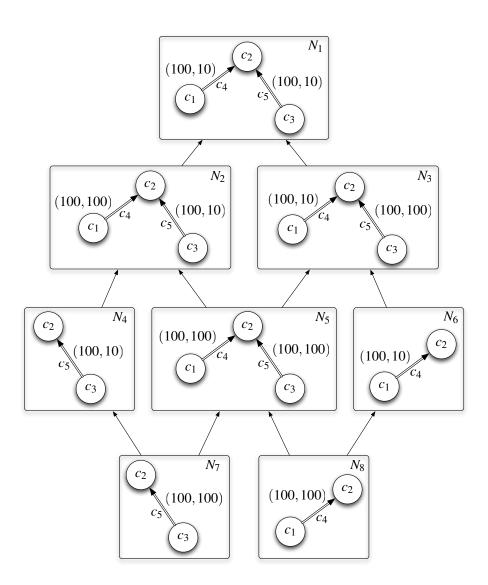

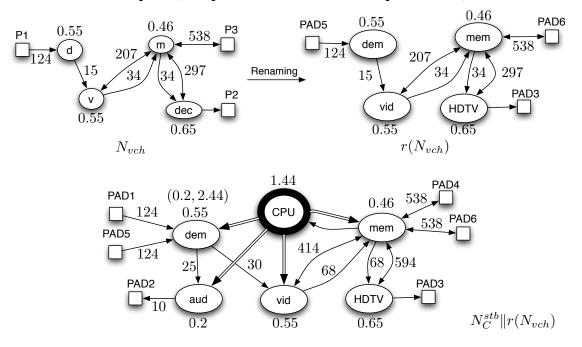

| 5.1        | Example of parallel composition of networks: the set-top box is expanded by adding a video channel and an extra off-chip memory bank.                                                       | 61       |

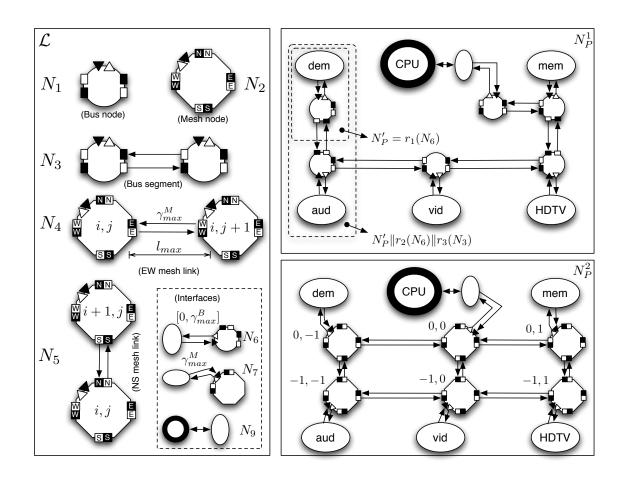

| 5.2        | Example of a library $\mathcal{L}$ for on-chip communication and two alternative implementations for the set-top box example based on composing elements instanced from                     | 01       |

|            | $\mathcal{L}$                                                                                                                                                                               | 66       |

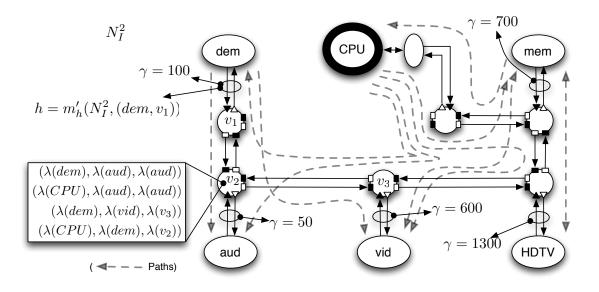

| 6.1        | Example of communication implementation for the set-top box.                                                                                                                                | 71       |

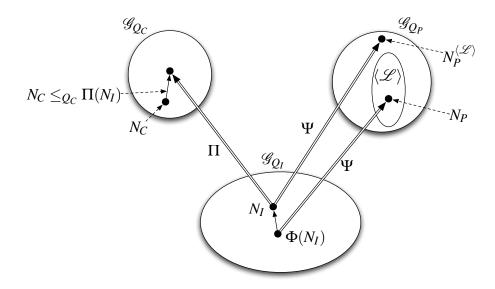

| 6.2        | Summary of the procedure to define problem PR2.                                                                                                                                             | 79       |

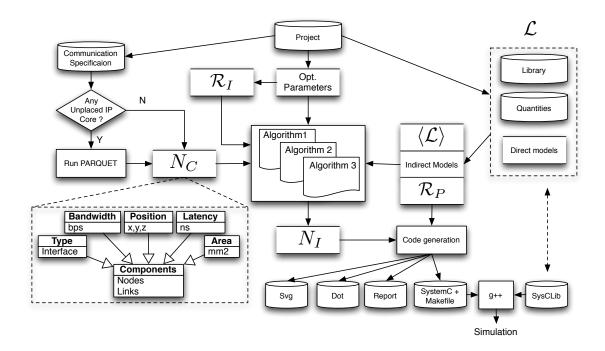

| 7.1        | COSI-OCC open software infrastructure.                                                                                                                                                      | 85       |

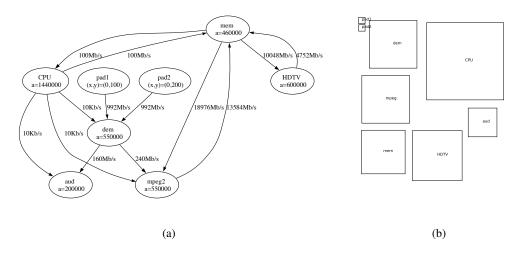

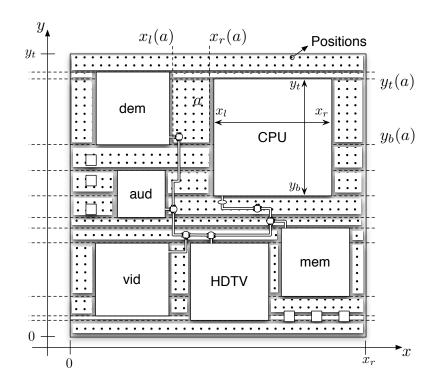

| 7.2        | Specification of the set-top-box example as given to COSI-OCC(a), and, Chip floor-<br>plan after elaboration from PARQUET(b).                                                               | 93       |

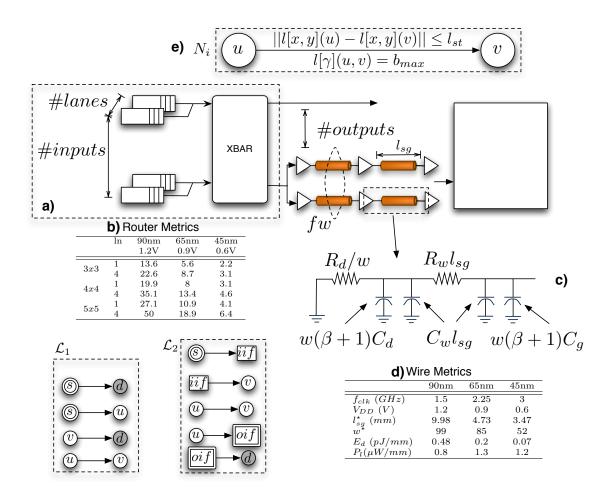

| 7.3        |                                                                                                                                                                                             | 95<br>95 |

| 7.3<br>7.4 | Modeling the NoC components                                                                                                                                                                 | 93<br>97 |

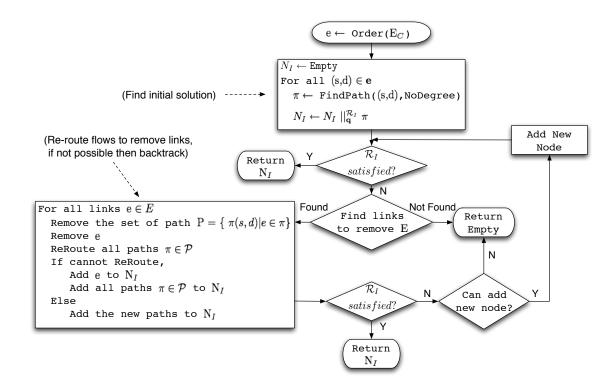

| 7.4<br>7.5 | High-level description of the heuristic algorithm.                                                                                                                                          | 97<br>99 |

|            |                                                                                                                                                                                             |          |

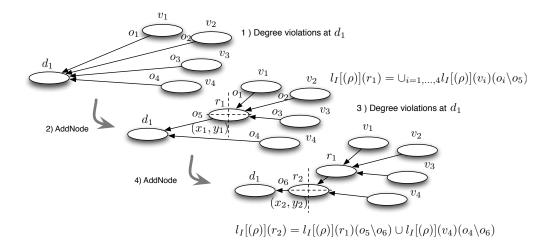

| 7.6        | Procedure for adding a new router to the NoC implementation. For an expression $exp$ , we denote by $exp(x \setminus y)$ the same expression where variable <i>x</i> has been replaced by <i>y</i> .                                                              | 101  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

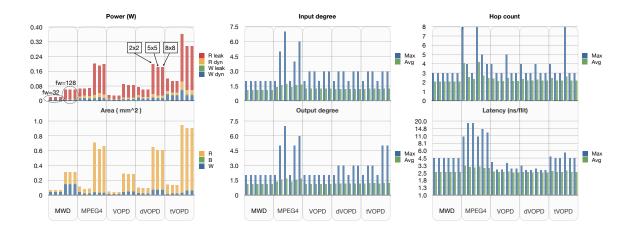

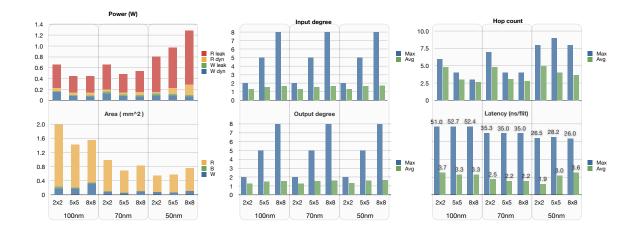

| 7.7        | Properties of the synthesized NoCs for the MWD, MPEG4, VOPD, dVOPD and tVOPD applications. Power is expressed in <i>Watts</i> , area in $mm^2$ and latency in $ns/flit$ . We used the following notation: R for routers, W for wires, B for sequential            |      |

| 7.0        | buffers. Latency is reported on a logarithmic scale.                                                                                                                                                                                                              | 108  |

| 7.8        | Properties of the synthesized NoCs for the VProc applications.                                                                                                                                                                                                    | 110  |

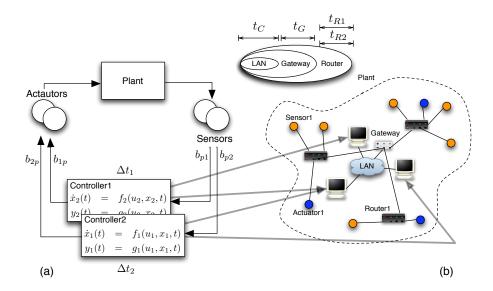

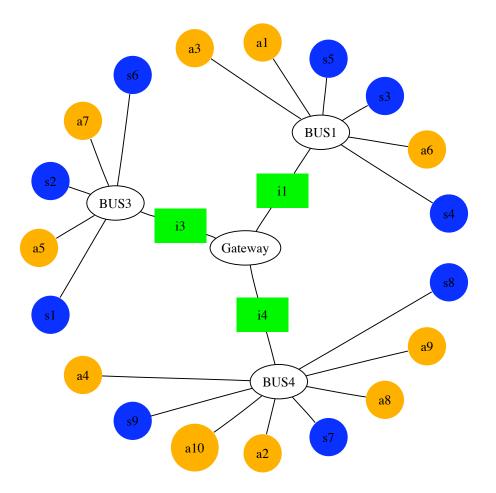

| 8.1        | A distributed embedded control system: (a) controller specification and (b) net-<br>worked execution platform.                                                                                                                                                    | 116  |

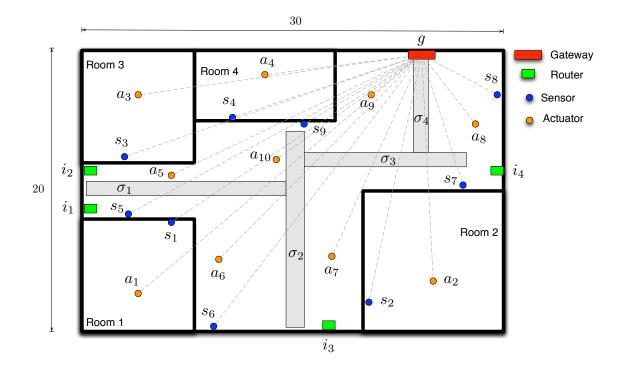

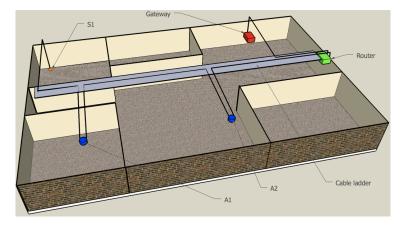

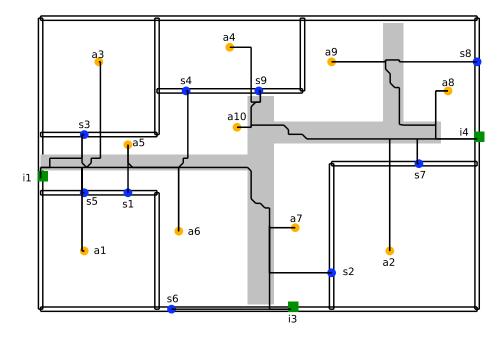

| 8.2        | Example of gateway zone associated to a building floor.                                                                                                                                                                                                           | 121  |

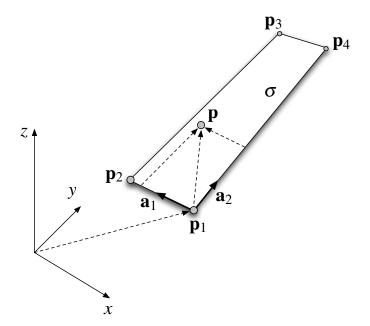

| 8.3        | Representation of a two-dimensional face with four vertexes in the Euclidean space.                                                                                                                                                                               | 122  |

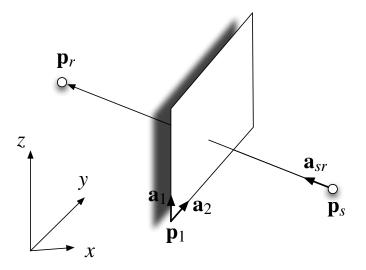

| 8.4        | Intersection of a ray with a face.                                                                                                                                                                                                                                | 123  |

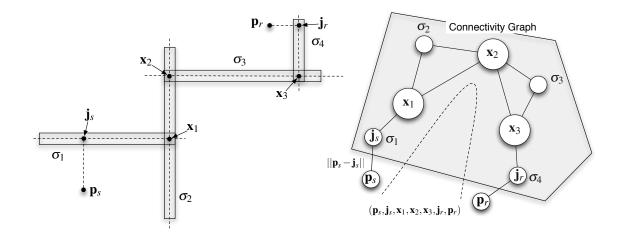

| 8.5        | Construction of the connectivity graph and example of computation of wire layout                                                                                                                                                                                  |      |

|            | for the example of Figure 8.2.                                                                                                                                                                                                                                    | 125  |

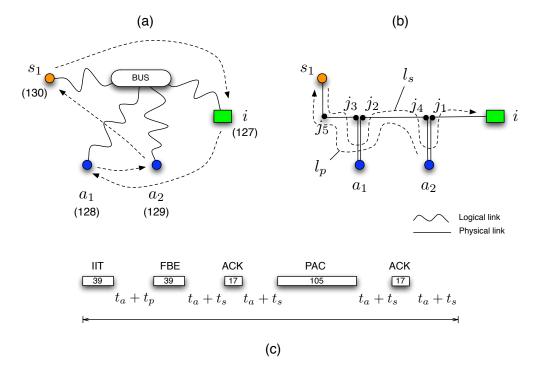

| 8.6<br>8.7 | Example of daisy-chain wiring of a few components in a building automation system<br>Graphical representation of a daisy-chain bus: (a) logical network, (b) physical net-<br>work, (c) sequences of messages generated by the token passing protocol for a short | .127 |

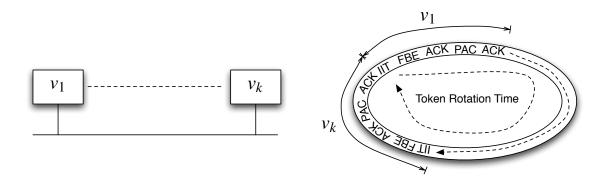

| 8.8        | packet transmission                                                                                                                                                                                                                                               | 128  |

|            | sentation of the token rotation time.                                                                                                                                                                                                                             | 132  |

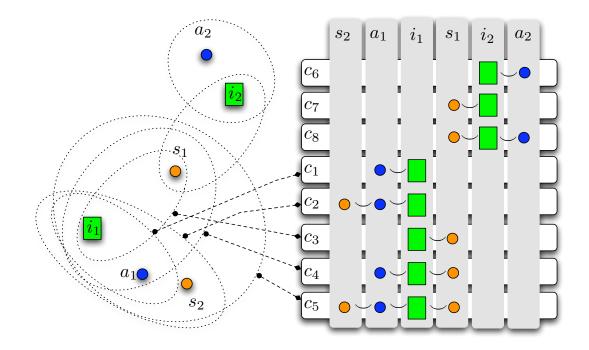

| 8.9        | The chains generated by Algorithm 3 and the resulting covering matrix.                                                                                                                                                                                            | 138  |

|            | Logical components of the synthesized network for the example of Figure 8.2 Physical deployment of the synthesized network implementation for the example of                                                                                                      | 142  |

|            | Figure 8.2.                                                                                                                                                                                                                                                       | 143  |

| 8.12       | Communication specification and building floorplan of a UTRC premise in Hart-                                                                                                                                                                                     |      |

|            | ford, CT.                                                                                                                                                                                                                                                         | 145  |

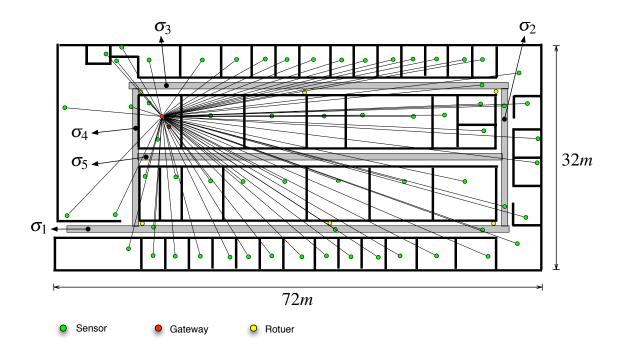

| 8.13       | An area covered by two ZigBee networks (top) and the possible network topologies                                                                                                                                                                                  |      |

|            | for one of them (bottom).                                                                                                                                                                                                                                         | 148  |

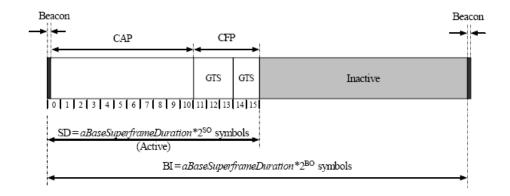

| 8.14       | Structure of a superframe as defined by the ZigBee protocol standard.                                                                                                                                                                                             | 150  |

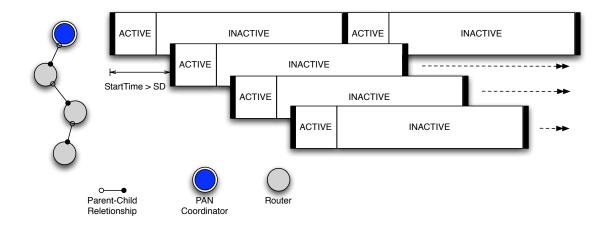

| 8.15       | Relative timing of the superframes in a beacon-enabled ZigBee network                                                                                                                                                                                             | 151  |

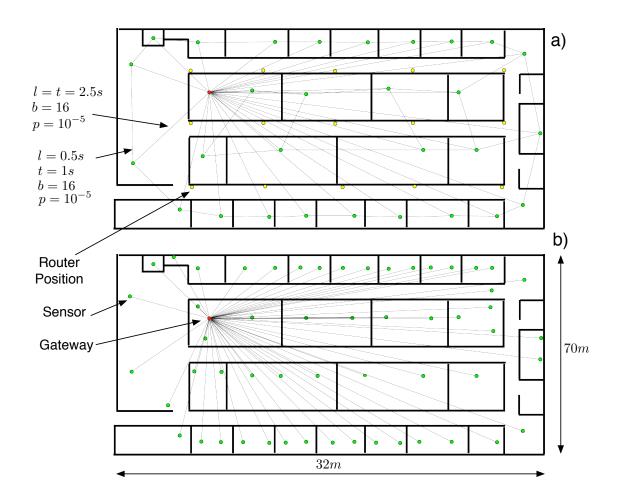

| 8.16       | The two test cases used in our experiments: a) Distributed estimation, b) Centralized                                                                                                                                                                             |      |

|            | estimation                                                                                                                                                                                                                                                        | 159  |

## **List of Tables**

| 7.1 | Tools for component based design.                                                               | 87  |

|-----|-------------------------------------------------------------------------------------------------|-----|

| 7.2 | Characteristics of the selected SoCs applications.                                              | 106 |

| 7.3 | Evaluating the heuristic algorithm of Figure 7.5.                                               | 114 |

| 8.1 | Characterization of the intrinsic performance and cost of a realistic library of com-           |     |

|     | ponents for building automation systems.                                                        | 131 |

| 8.2 | Performance and cost of the synthesis result. The cost is a pair $(n, w)$ where <i>n</i> is the |     |

|     | cost of the nodes including the routers and <i>w</i> is the wiring cost                         | 144 |

| 8.3 | Library parameters and synthesis results for the two L2 building and big box store              |     |

|     | (BB) examples for a new installation. In this table, Bw is the bus speed, $l_{max}$ is          |     |

|     | the maximum allowed bus length, $d_{max}$ is the maximum latency experienced by any             |     |

|     | sensor, and $U_{max}$ is the maximum bus utilization among all instantiated bus.                | 144 |

| 8.4 | Library parameters and synthesis results for the two L2 building and big box store              |     |

|     | (BB) examples for a retrofitting installation. In this table, Bw is the bus speed, $l_{max}$    |     |

|     | is the maximum allowed bus length, $d_{max}$ is the maximum latency experienced by              |     |

|     | any sensor, and $U_{max}$ is the maximum bus utilization among all instantiated bus.            | 145 |

| 8.5 | Results for the centralized estimation case.                                                    |     |

#### Preface

This thesis is divided in three parts: *Introduction*, *Theoretical Background* and *Applications*. The first part is an introduction to the problem of designing complex embedded systems and motivates the necessity for communication centric design flows. In the second part, we provide a formal model on which we built a software infrastructure that allows the development of dedicated communication synthesis tools. The third part focuses on domain specific applications. By applications we do not mean simply case studies. The term "application" refers to the use of the design methodology and software infrastructure on a specific domain like on-chip communication and building automation systems.

Each chapter contained in this thesis starts with a summary of what is presented in the chapter and provides the context to the reader. Each chapter of the last part of this thesis, "Applications", is organized according to the following structure. The communication synthesis problem is first introduced including domain specific details. The specification of the problem is formally defined capturing the main concerns of the design. The library of communication components is described and analytical models used for synthesis are described for realistic components. The optimization algorithms are described as mapping of the specification on a composition of library elements. The chapters end with the results obtained by running the algorithms on a set of case studies.

#### Acknowledgments

This thesis is the result of years of dedication to understanding problems and viable solutions. Its content benefited from the technical contributions of excellent scientists and moral support of relatives and friends. My acknowledgment goes to both.

Many of the original ideas included in this thesis stemmed from inspiring discussions with my advisor Alberto Sangiovanni Vincentelli, by far one of the most energetic and acute people I have ever met. I am truly impressed by the profound meaning and implications of his statements. He has been a guide and role model for research and academic integrity, and a moral support when things seemed to be going in the wrong direction. I would like to thank Luca Carloni that collaborated with me since I came to Berkeley. The discussions with Luca have always been very detailed and passionate, and very helpful in refining rough intuitions into high quality work. Thanks for the time spent in fixing my broken English.

Thanks to my colleagues and friends of the D.O.P. center: Alvise Bonivento, Luca Daniel, Abhijit Davare, Doug Densmore, Trevor Meyerowitz, Roberto Passerone, Claudio Pinello and Alessandra Nardi, Marco Sgroi, Guoqiang Wang, Guang Yang and Yanmei Li, and Qi Zho, and to the research scientists of the Cadence Berkeley Labs, Yosinori Watanabe, Felice Balarin and Luciano Lavagno. I won't forget to thank my friends of the graduate office Ruth Gjerde and Mary Byrnes, for listening to my complaints about politics, women and life in general; and, of course, many thanks to Lorie Mariano for making every GSRC workshop a good time to have fun. Thanks to Prof. Robert K. Brayton and Zuo-Jun Shen for reviewing my thesis.

The amazing journey that from Ericsson Lab Italy brought me to U.C. Berkeley stopped at PARADES, a research lab in Rome where I spent a year and a half. I met great engineers, scientists

and good people. I would like to thank Massimo Baleani, Andrea Balluchi, Luca Benvenuti, Alberto Ferrai and Donatella Santillo, Leonardo Mangeruca and Tiziano Villa for their technical advice, for hosting me during my visits in Rome and for their friendship and support. In the last two years of my Ph.D., I had the luck and pleasure to collaborate with the United Technologies Research Center. I would like to thank Clas Jacobson and Andrzej Banaszuk for their valuable suggestions and insights and for supporting my work on building automation systems.

There are many friends I have to thank for decorating my life outside the walls of Cory Hall. The first semester of my Ph.D. has been cheered up by Alessandro Serra. I met many Italian, European and American friends through the International Italian Student Association. It would be difficult to list them all, but to them I am thankful. Many Thanks to my house-mates and friends Bruno Sinopoli and Massimiliano Fratoni, to my quasi-house-mate and Napolitan friend Massimo Franceschetti who finally got a position and stopped complaining to us, and to uncle Dino Bellugi who, being Roman, reminded me of the old good times in the eternal city. I would like to thank the members of IBERIA (the Berkeley association of Spanish students), in particular Guillermo José Rein Soto Yarritu de la Gonzalera y Pérez del Hierro Martínez de la Cosa y Carvajal de la Apelliduría, also known as Guillermo Rein.

In Berkeley, I met Rebecca Julie Abergel, a devoted chemist and interesting woman who gradually became my beloved life's companion. She poured the last few drops of catalyst into my everyday life to complete this work and step into the future. Thank you Rebechita.

Last, but definitely not least, I thank my family, Gemma, Silvio, Barbara and Daniele. They saw me growing up, they raised me well and gave me everything I needed. Selfishly, I went away to build the future I liked. They let me go, and yet they love me. Part I

# Introduction

### **Chapter 1**

## **Trends in Electronics**

The complexity of electronic systems is *constantly increasing*. A measure of the complexity of an electronic product is the number of functions that it provides to the user. Technology scaling allows an increasing number of transistors to be integrated on the same chip, which enables the convergence of multiple applications on the same platform. The range of devices that can benefit from the integration of multiple functions are numerous: from hand-held consumer devices to large distributed systems for societal scale applications.

On the other hand, time-to-market *keeps shrinking*, posing serious challenges to designers who are required to complete the development of new products within a limited time window. Arriving first on the market is extremely important to fix the price of new products as to maximize revenues. Moreover, a larger market share can be gained if there is no competition initially.

The strategic importance of being able to keep pace with both trends is posing serious challenges to product developers. In fact, design and verification time of electronic systems is directly dependent on the number of hardware and software components that are used to implement them. Thus, it takes longer to bring new complex systems to the market. A traditional solution to this problem has been to increase the size of the engineering and verification teams, in hopes of a corresponding increase in productivity. Unfortunately, communication overhead among team members reduces the potential benefits of larger engineering teams. Moreover, if the design methodology being used is not based on a formal model that supports compositional design, verification must be carried out on the entire system.

An alternative and promising way of increasing productivity is to re-use pre-designed and pre-verified components. Re-use has two advantages. Since a system is built by assembling large components, productivity in terms of number of gates per designer per year increases. Also, since each component has been pre-verified, the verification of the system is reduced to the verification of the interaction among components. However, this is not necessarily easier than verifying the entire system. To reduce, or even eliminate, the verification effort the design flow should be supported by a correct-by-construction methodology that provides the necessary tools to assemble systems automatically. Therefore, the automatic synthesis of communication systems, that we refer to as *communication synthesis*, is of primary importance in a methodology based on re-use. Notice that, whenever components are not available, abstract ones can be used instead, leaving their implementation to the subsequent design steps (at lower abstraction levels). Even in this case, communication synthesis is of great importance.

A communication synthesis tool should allow the description of the properties that a communication system must preserve. A synthesis algorithm should be able to derive the implementation of the communication systems by assembling communication components such that, *by construction*, the properties required by the specification are preserved. In an ideal system design flow, a designer would select a set of components able to implement the system functionality, and then define the properties that their interconnection must satisfy. These properties are then projected onto properties of the communication system and passed to a communication synthesis tool. Verification time is, therefore, completely eliminated because the implementation of the communication system is guaranteed to be correct with respect to the properties imposed by the designer.

### **1.1 System Complexity**

In 1965, Gordon E. Moore observed that, for economical reasons, the number of transistors per chip followed an exponential trend [79]. This trend is known as the Moore's Law. In his original work, Moore predicted that the number of transistor integrated on the same chip would double every year. Even though this trend slowed down in recent years, it remains exponential. Figure 1.1(a) shows the number of transistors per die as a function of time in a logarithmic scale. The data points correspond to successive processor generations starting from the Intel 4004, the first example of an integrated processor on a single chip. The last data point, the Dual Core Intel Itanium, marks the beginning of the Chip-Multi-Processor (CMP) era for Intel. In [22], Borkar *et al.* explains that performance and power consumption are the main reasons to embrace parallelism. Traditionally, the demand for more computational power has been satisfied by increasing the processor clock speed. Unfortunately, memory performance has not been able to keep the same pace. In fact, memory latency is only slowly decreasing, becoming the major bottleneck in terms of computation speed. The second argument in favor of parallelism is power consumption. Having many slower processors instead of a powerful central one gives the flexibility of running part of the chip at full speed while maintaining the rest asleep. Power management becomes less flexible in

(b) Software complexity in Avionics

Figure 1.1: System complexity: Number or transistors in Intel microprocessors as a function of time, also known as Moore's law (Source: Intel), and number of lines of code for avionic products [111].

single processor chips because running a software task, even one of limited complexity, requires the entire chip to be powered-on. Other companies like Sun and AMD have also moved from single to multi-processor platforms. This transition does have many consequences on the hardware and software design flows.

A similar revolution happened in the early 1980's. Computers with a central control unit [18, 86] were not able to satisfy the increasing computational demand coming from the scientific computation community, therefore researchers started to conceive and build parallel computers. The transition from single to multi-processor systems posed many new challenges [61] that are very similar to the ones that we also face today for multi-processor chips. The two major challenges are the programming models used to develop software for multiprocessor system and the communication network that interconnected the processors.

Programmers of multiprocessor systems need a programming model to pass data from one processing element to the other. Given the distributed nature of these systems, and the fact that a central memory would slow down computation due to memory latency, asynchronous models like message passing schemes have been adopted as successful programming models for many recent multiprocessor systems [13, 52]. Programming models (known as Models of Computation) that allow the capturing of application level concurrency have been widely studied and adopted in the design of embedded systems [64, 73]. Using a model of computation that can capture concurrency is essential since the parallelization of sequential specification is an undecidable problem [128].

The other challenge in the design of multi-processor systems is the interconnection network that provides the infrastructure for inter-processor communication. The most important requirements of the interconnection infrastructure are low latency and scalability. Latency depends on network topology and the protocols used and impacts the overall performance of the multiprocessor system. For these reasons several regular interconnection topologies, routing algorithms and switching techniques have been proposed and characterized [33, 35, 88].

Chip Multi-Processor (CMP) systems for general purpose computing are comprised of a number of homogeneous cores. The complexity of these new chips is expected to grow exponentially in the future. An example of this kind of computing platforms is the 80-tile Polaris chip [121] from Intel. This chip features 80 processors interconnected by a mesh network. Depending on the class of applications targeted by a CMP, the number and types of cores can vary. In fact, there are many examples where the platform contains a heterogeneous set of cores like, for instance, the Cell processor [99]. This platform is comprised of 8 processing units and a master processor interconnected by a bidirectional ring network. Heterogeneous platforms are typically used in embedded systems that need to support several applications with different computation requirements and activation semantics.

An explosion in design complexity can be observed also for embedded system software. Figure 1.1(b) shows the number of lines of code of the control software in avionics products [111]. The challenges of real-time software development are related to scheduling, performance and correctness. In fact, software productivity can be as low as six lines of code per designer per day [107] if debugging time is also taken into account.

The challenges posed by complexity are also faced by the systems developer, beyond hardware and software. In consumer electronics, there is a trend to build devices that can perform multiple functions. Apple Inc.'s recent iPhone is a smart-phone offering EDGE connectivity, music and movie play-back, internet navigation, e-mail service, still image and movie capturing, blue-tooth connectivity, calendar and address-book. The user interface is based on a touch screen. This device is battery operated, and therefore its design must be carefully tailored to provide a good customer experience while saving power. To provide all of these functions, Apple relied on third-party components that include: a central processing unit Samsung S5L8900 (which contains an ARM 1176JZF-S and 1 Gbyte of embedded DRAM), an audio codec, an accelerometer from ST Microelectronics, a power management unit, a DMA controller, a light proximity sensor from TAOS, a camera sensor from Micron, an I/O Broadcom device, an EDGE processor from Infineon that provides also the GSM radio frequency module, a display interface from National Instruments, a Marvel WLAN chip, a touch-screen from Balda, and a USB power manager and battery charger from Linear technology [43]. This is not a complete list, but it is long enough to understand that the complexity in building this device resides in assembling the components such that performance is guaranteed and power consumption is minimized.

The component integration problem is also faced by developers of large scale systems such as airplanes and building automation systems. For these systems, the design challenges arise from the scale of the system and the constraints imposed by the control algorithms. Building automation systems are highly distributed and are comprised of a large number of sensors, actuators and local controllers. Moreover, control algorithms of physical quantities, like temperature and pressure, are implemented by tasks that need to run periodically with a period that depends on the time scale of the dynamics of the variables that they control. Until a few years ago, building automation system designers could abstract computation and communication time because the time scales of the variables to control were much longer than the computation and communication delay. A common practice in designing these systems has been to over-provision the communication network leading to solutions that were either grossly inadequate or over-designed and therefore much more expensive than needed. As new functionalities become either mandatory or desirable, the time scale separation property between the control algorithm and the platform does not hold any longer. Consequently the design problem becomes increasingly difficult. For example, ensuring that in case of an emergency, buildings can be evacuated safely and efficiently is an important novel requirement. The movement of people in emergency situations follows a fast dynamics so that egress control requires a sampling period that is comparable to computation and communication delays in the computing platform. In a survey [103] of 60 buildings conducted by the Lawrence Berkeley National Labs, 50% had control problems (including hardware, software and communication).

### **1.2 Time-To-Market and Productivity**

The time-to-market is *the length of time that elapses from when a product is conceived to when it appears on the market*. This time window is a constraint for designers because the revenues generated by selling a new product are higher if the product is the first on the market. Time-to-market for electronic products is domain dependent with a wide variability. However, there is a common trend that is independent of the domain: Time-to-market continues tightening. A few years ago, the time-to-market for consumer electronics products was more than one year and it is today only six months [5]. In automotive, the time-to-market for the electronic equipment was 3 years and it is today one year [5]. Larger systems, like building automation systems, are also facing stringent time-to-market requirements.

Time-to-market is affected primarily by design and verification time. As systems become complex, not only design time necessarily increases, but verification time becomes the major bot-

tleneck. In fact, the productivity of engineers is inversely proportional to the sum of design and verification time together.

In 2004, Synopsys reported the productivity data for hardware designers and predicted the required productivity until 2007. The chart is shown in Figure 1.2(a). Synopsys observed a major improvement in productivity in 1995 when designers started reusing small blocks of pre-designed logic (of the order of 2500 to 75000 gates). Synopsys predicted two other major improvements in productivity: one in 2005 with the introduction of system level design techniques and one in 2007 with the reuse of large blocks of logic (of the order of 1 Milion gates).

Figure 1.2(b) shows the productivity in number of gates per engineer per year predicted by the International Technology Roadmap of Semiconductors (ITRS [4]) until 2013. This chart suggests that productivity should grow exponentially with time. Given that design complexity will keep growing to sustain Moore's law, the exponential growth in productivity can be only achieved by reducing design and verification time. Increasing the size of design teams is not a viable solution to achieve this goal.

### 1.3 Re-Use

In recent years, re-use has been touted as a possible cure to this malaise whereby a design is the result of combining appropriately pre-designed and pre-verified components. In this case, verification amounts to checking the correctness of the interconnection among components. This is not necessarily easier, especially when components are developed by different providers, because their interfaces may be incompatible. Moreover, the communication architecture that interconnects the components affects the quality of the design in terms of performance and correctness. Therefore,

(a) Reported by Synopsys in 2004.

(b) Predicted by the International Technology Roadmap of Semiconductors (ITRS).

Figure 1.2: Hardware design productivity expressed in number of gates per designer per year

the communication architecture must be carefully designed. The verification process is further aided if the composition can be formally proven correct. There has been a flurry of activities in formal verification of interfaces that have clarified the main issues that need to be resolved [108, 97, 36, 114, 25, 96, 26, 27]. One of the key findings is that, if the components are designed with "clean" interfaces, composing the components, i.e., interconnecting them and establishing protocols that guarantee "correct" communication, can be done automatically. We call the automation of the composition of building blocks *communication synthesis*. Communication synthesis has been studied for years and, among the first pioneering work, we list Yen and Wolf [126], Ortega and Borriello [92] and an interesting approach to the synthesis of communication topologies by Gasteie, Munch and Glesner [50].

The major roadblock to effective reuse is the non-orthogonalization of computation and communication. The function implemented by a component and its interface are usually interdependent which makes a component work properly only in some specific contexts<sup>1</sup>. Standardization of the communication interface is one possible solution to this problem. There are currently many standardization efforts in different application domains like the Open Core Protocol (OCP) [89] for on-chip systems, and AUTOSAR [3] for automotive software systems. The building automation industry is still waiting for a definitive answer but there are at least two emerging standard communication protocols, Bacnet [24] for wired systems, and Zigbee [127] for wireless applications. Whenever components do not comply to standard interfaces, protocol adaptors need to be developed to guarantee interoperability.

Standardization does not completely solve the interconnection design problem. This problem can be stated as follows. Given the specification of a system defined by a set of functionalities

<sup>&</sup>lt;sup>1</sup>By context we mean the rest of the system in which the component is used.

and a set of properties to be satisfied<sup>2</sup>, and given a selection of components that implement the functionalities, design a communication system such that the properties are maintained. The communication system is defined by its topology, i.e. the set of links and intermediate nodes used for communication, the routing protocol, the medium access control protocol, the type of interfaces and all other parameters like transmission power and rate.

The design flow proceeds in two steps. In the first step, designers have to project the system properties to properties that the communication infrastructure must satisfy. For instance, at the specification level components communicate over point-to-point channels exchanging abstract data types called tokens. A token can be a real number of an image. The amount of data that is exchanged between them (for instance all the numbers that describe an image) translates to a certain amount of bits per token. After the execution rate of the components has been fixed, it is possible to define a minimum bandwidth requirement between the two components. This requirement is the property that the communication system must guarantee. Then, the communication system is designed by assembling communication components in such a way that all requirements are guaranteed.

Although the first step that may expose some difficulties, we focus on the second step whose complexity is due to the large number of components to be interconnected and the stringent cost and performance requirements. In this thesis we develop a Platform-Based design methodology for communication system design.

$<sup>^{2}</sup>$ Examples of properties are response time, volume of data to be transferred among components, cost and power consumption.

### Chapter 2

### **Design Methodologies**

The problem of designing complex systems can be tackled by raising the level of abstraction at which the design is carried out. Unnecessary information is hidden from the designer who is left with a limited, and therefore manageable, set of choices. Abstraction must be done in a judicious way, so as to preserve the accuracy of those metrics that are used to rank system level design solutions. System-level design means different things to different communities. For System-on-Chip designers, this term commonly refers to the design of systems conducted at a level of abstraction that is higher than RTL (for hardware) and C or assembly language (for software). For automotive companies, system-level design is conducted at even higher abstraction levels, where a system is comprised of several networked Electronic Control Units (ECU) and mechanical parts.

System-level design for SoCs became popular in the research community in the 90's. Many researchers proposed different ways of raising the level of abstraction and bringing a design from concept all the way down to implementation, using different methodologies. A design methodology is a procedure that, when followed, should lead to a design with guaranteed quality. The metrics used to judge the quality depend on the application domain. A design flow that adopts a certain methodology and solves a design problem in a specific application domain has an input and an output. The input consists in the the *problem specification*. The output is an implementable system. Depending on the abstraction gap between the specification and the implementation, the number of free variables that need to be fixed to obtain a deterministic design can be very large. A design methodology helps in exploring the space of the free variables in an intelligent way, such that the complexity can be managed by the designers.

Two generic design methodologies are *top-down* and *bottom up*. In a top-down design methodology, the abstract specification is refined incrementally by fixing a few variables at the time in a predefined order. This methodology is not always effective. In fact, the quality of the design depends on how related are the successive design phases.

An example of top-down design methodology for circuit design is the traditional logic synthesis design flow. In this design flow, a technology independent optimization is followed by technology mapping and place-and-route. This sequence of optimization steps does not yield good results in all cases. Interconnect delay is becoming so important that logic synthesis and place-and-route cannot be completely orthogonal design steps, rather, one may want to consider the impact of routing and wire delay already during technology mapping [98, 109].

In a bottom-up design methodology, an implementation platform is designed to satisfy a class of applications. The platform is constructed mainly by experience from previous designs, relying on predefined architecture templates and selecting the set of components (that includes usually programmable ones). The specification is then satisfied by customizing the implementation. This methodology usually leads to over-designed systems.

In recent years, a novel design methodology called *Platform-Based Design* (PBD) [45, 110, 101] has been proposed and successfully adopted in many application domains. This methodology is a *meet-in-the-middle*, where constraints are propagated top-down and performances bottomup. The implementation of a specification is obtained by a mapping step that matches the constraints and the performance while minimizing a cost function. One of the key elements of PBD is the orthogonalization of function (what a system is supposed to do) and architecture (how the system actually implements the required functionality), and computation and communication that is particularly important to allow the reuse of the same component in different contexts. Given a set of interacting components that have been pre-designed and pre-verified, a desirable feature of a design methodology is that the composition does not introduce undesired behaviors. This can be achieved by allowing the designer to state the properties that the communication system must satisfy, and provide her with a design methodology and a set of tools for communication design (*Communication-Based Design* and *Communication Synthesis*, respectively).

### 2.1 System-Level Design

A design flow starts with the specification of the functionality and constraints that must be satisfied by an implementation. Then, a synthesis process consists of using a set of primitives available to the designer to implement the specification so that the constraints are satisfied and the functionality guaranteed. The higher the level of abstraction, the easier it is to express the functionality and the constraints as well as to catch design errors early. However, quickly reaching a high-quality implementation is more difficult, due to the semantic gap between specification and implementation. Thus, researchers have either chosen to remain at high-levels of abstraction and optimize high-level structures, or to begin with a low-level of abstraction that could reflect the characteristics of the implementation space. This is the case of early work in System-Level Design as in [102, 54, 44] where the specification, captured using a formal model, is partitioned in hardware and software (Hardware/Software Co-Design).

Gupta and De Micheli [54] presented a system-level design flow for hardware/software co-design shown in Figure 2.1(a). The specification is captured in a language called HARDWAREC which extends the standard C language with concurrency and is based on a formal semantics. The HARDWAREC description is then translated into an internal representation that allows verification and synthesis. The synthesis consists in partitioning the specification tasks into hardware and software while also taking into account the overhead of the interface between the two. The partition should minimize implementation cost while satisfying non-functional constraints, like rate of execution and latency, captured in the specification. The design methodology proposed by Ernst *et al.* [44] is shown in Figure 2.1(b). In this case the specification is captured in a formal language called  $C^X$  that is translated into a graph-based internal representation. The specification is partitioned into hardware and software and standard tool chains are used to generate the gate level and the assembly level descriptions, respectively.

The approach presented by Gajski [48] proposed the idea of having two abstraction layers. The specification of the problem is captured by a model called Program-State Machine (PSM) that is based on Statecharts [56] and Communicating Sequential Processes [60]. The input description is then translated into an internal representation that can be used for synthesis. The first step of the synthesis flow consists of allocating resources (processors, memories, busses and hardware) and partitioning the functionality on these resources. The second step is the refinement of the hardware

(a) System-level design flow presented in [54]

(b) System-level design flow presented in [44].

Figure 2.1: System-level design flows presented in early papers on this topic.

and software components. Other important work are related to mapping of applications to architectures taking into account different aspects like communication [106] and memory hierarchy [74].

Similar ideas have been also exploited in the Polis [15] project which already embodies some platform-based design concepts (see Section 2.2). The specification is captured using a particular model of computation called Co-Design Finite State Machine (CFSM) that can efficiently represent software and hardware. Each CFSM can be automatically refined into a software program, or into a hardware description language through synthesis algorithms. The result of the synthesis can be fed into standard refinement and synthesis flow to arrive at the final implementation of the entire system. The interface between hardware and software, as well as the real time operating system, can also be automatically generated. The Polis approach was somehow limited by the expressiveness of the model of computation that was suited for control dominated applications. Its successor, Metropolis [17], covers a broader rage of applications by providing a metamodel that can be used to described several other models of computation. Moreover, the metamodel can be used to capture architectural components, their composition and the quantities characterizing the performance and cost of each component. Mapping of a functional description on an architecture is achieved by synchronizing functional events and architectural events [16] using the Metamodel language features. Given its flexibility, the Metropolis infrastructure can be used to implement application specific design flows [100]. A further evolution of Metropolis is under development [10].

Other languages and tools for system level design exists and are offered by industry and academia. A comprehensive survey is provided by Douglas Densmore *et. al* in [39].

### 2.2 Platform-Based Design

We introduce Platform-Based Design (PBD) with an example. Assume we want to interconnect a set of nodes (e.g., computers) so that every node in the set can access every other node. Initial specifications may include the quality of service that each connection must be able to support, such as the required bandwidth and the maximum latency of the communication. We can solve this problem by constructing a network made of several different components such as routers, hubs, modems, protocol stacks, and links of different nature. The resources must be sized to satisfy the required constraints. However, the gap between our original, high-level, specification, and the implementation is obviously too large to be bridged in a single synthesis step: clearly, enumerating all possible topologies and interconnections is not practical, even for networks of modest complexity. A better way of approaching this problem is to divide this gap in several layers, where each layer focuses on a particular design choice. The question is then whether this division is optimal and, more importantly, how much of the entire design space can be explored. Answering these questions gives us an idea of the quality of the solutions that we obtain. Our approach consists of quantifying the design exploration process by relating the levels of abstraction corresponding to different layers. If two layers are too far apart then performance estimation will likely be poor and will not provide the necessary support for the synthesis algorithms.

In this context, a *platform* consists of a set of library elements, or resources, that can be assembled and interconnected according to predetermined rules to form a platform *instance*. One step in a platform-based design flow involves mapping a function or a specification onto different platform instances, and evaluating their performance. This step is pictorially represented by a bow tie as in Figure 2.2. The left side of the bow tie represents the application space. One particular

Figure 2.2: Pictorial representation of a platform-based design flow.

functional specification is a point in this space and it is called the *function*. The function is the design intent, or better, what the system is supposed to do. The right side of the bow tie is the implementation space and it is called the *platform*. A platform is the set of all valid compositions of library elements. One particular composition is called a *platform instance*. A platform instance can implement many different specification in many different ways. For instance, given a particular network, the same end-to-end constraints can be satisfied by selecting many different paths in the network for each constraint. Indeed, platform instances are characterized by performances that can be computed from the performances of the components and their relations. The mapping of the specification on the platform instance consists in selecting its parameters optimally such that the final cost is minimized and the performance matches the constraints. The result of mapping is a refinement of the original specification and of the platform instance, and plays the role of a new function at the lower level of abstraction.

Similar diagrams can be also found in early work by Gajski and Kuhn in 1987 [47], and Kienhuis *et al.* in 1997 [70]. Both diagrams are called Y-charts but they have very different meanings. The Y-chart presented by Gajski and Kuhn shows three different axes along which a design can be represented: the structural, functional and geometrical representation. For each of these axes, several abstraction levels are presented. This specific type of Y-chart is then used to show the levels of abstractions touched by several design flows. The Y-chart presented by Kienhuis is instead very close to the platform-based design view.

#### 2.2.1 Formalizing Platform-Based Design

In this section we formalize Platform-Based Design (PBD) [45, 28, 123] using a rigorous algebraic framework to provide a methodology where we can conjugate the ease of expressing and verifying designs of high-levels of abstraction with the quality of low-level implementations. In Chapter 4 we use the same concepts developed in this section to formalize a platform-based design methodology for communication systems.

A *platform* consists of a set of library elements, or resources, that can be assembled and interconnected according to predetermined rules to form a platform *instance*.

Our formalization of the platform-based design methodology is based on the framework of Agent Algebra [95]. Informally, an agent algebra  $\mathcal{Q}$  is composed of a domain D that contains the agents under study for the algebra, and of certain operators that formalize the most common operations of the models of computation used in embedded system design. Different models of computation are constructed by providing different definitions for the domain of agents and the operators. The algebra also includes a master alphabet  $\mathcal{A}$  that is used as the universe of "signals" that agents use to communicate with other agents. **Definition 1.** An agent algebra  $\mathcal{Q}$  has a domain  $\mathcal{Q}.D$  of agents, a master alphabet  $\mathcal{Q}.\mathcal{A}$ , and three *operators:* renaming, projection and parallel composition, denoted by rename(r), proj(B) and  $\parallel$ . *Each agent*  $p \in \mathcal{Q}.D$  *is associated with an* alphabet  $A \subseteq \mathcal{A}$ .

The operators of the algebra are partial functions on the domain D and have an intuitive correspondence with those of most models of concurrent systems. The operation of renaming, which takes as argument a renaming function r on the alphabet, corresponds to the instantiation of an agent in a system. The renaming function is required to be a bijection, so that renaming is prevented from altering the structure of the agent interface, by for example "connecting" two signals together. Projection corresponds to hiding a set of signals, and takes the set B of signals to be retained as a parameter. Hence it corresponds to an operation of scoping. Finally, parallel composition corresponds to the concurrent "execution" of two agents. It is possible to define other operators. We prefer to work with a limited set and add operators only when they cannot be derived from existing ones. In particular, we will be mainly concerned with the operator of parallel composition. The operators must satisfy certain axioms that formalize their intuitive behavior and provide some general properties that we want to be true regardless of the model of computation. For example, parallel composition must be associative and commutative. The definitions of the operators is otherwise unspecified, and depends on the particular agent model being considered.

The notion of refinement in each model of computation is represented by adding a preorder (or a partial order) on the agents, denoted by the symbol  $\leq$ . The result is called an *ordered agent algebra*. We require that the operators in an ordered agent algebra be monotonic relative to the ordering. This is essential to apply compositional techniques. However, since these are partial functions, this requires generalizing monotonicity to partial functions. This generalization is however beyond the scope of this thesis. The interested reader is referred to [95] for more details.

It is easy to construct an agent algebra  $\mathscr{Q}$  to represent the interface that components expose to their environment. In this case, the set D consists of the agents of the form p = (I, O) where  $I \subseteq \mathscr{Q}.\mathscr{A}$  is the set of input ports of the components and  $O \subseteq \mathscr{Q}.\mathscr{A}$  the set of output ports. The alphabet of an agent p is simply  $A = I \cup O$ , and we require that the set of inputs and outputs be disjoint, i.e.,  $I \cap O = \emptyset$ . The parallel composition  $p = p_1 \parallel p_2$  is defined only if the sets  $O_1$  and  $O_2$  are disjoint, to ensure that only one agent drives each port. When defined, a port is an output of the parallel composition if it is an output of either agent. Conversely, it is an input if it is an input of either  $p_1$  or  $p_2$ , and it is not concurrently an output of the other agent. Thus  $O = O_1 \cup O_2$ and  $I = (I_1 \cup I_2) - (O_1 \cup O_2)$ . Given the definitions, it is clear that in this example connections are established by name.

The model can be enriched by including type information in the form of a set of possible values for each port. To ensure type consistency, parallel composition is defined only if the type of an output port is contained in the type of the corresponding input port, if one exists. For the refinement relationship, we choose to order agents  $p_1 = (I_1, O_1)$  and  $p_2 = (I_2, O_2)$  so that  $p_1 \leq p_2$  if and only if  $p_1$  and  $p_2$  have the same sets of inputs and outputs. In addition, the type of the inputs of  $p_1$  must contain the type of the inputs of  $p_2$ , while the type of the outputs of  $p_1$  must be contained in the type of the outputs of  $p_2$ . This ensures that  $p_1$  can handle all the inputs that  $p_2$  can, and does not generate outputs that  $p_2$  does not.

The model can be further enriched with information about the nature of the signals used by the agents. For instance, in the case of agents that describe communication topologies, signals can be distinguished between those that belong to a link, denoted by the symbol *l*, and those that belong to a component, denoted by the symbol *n* (non-link). We call this a *typed IO agent algebra*. The sets *I* and *O* of an agent *p* thus become sets of pairs of signals together with their type, i.e.,  $I \subseteq \{(a,t) : a \in \mathcal{Q}. \mathcal{A} \land t \in \{l,n\}\}$  and similarly for the output ports. Parallel composition can also be modified so that the operation is defined only if the ports of the agents being connected are *not* of the same type, i.e., a link must be used to connect two regular ports. Hence,  $p_1 \parallel p_2$  is defined if and only if for all  $i \in I_1$  and for all  $o \in O_2$ , if i.a = o'.a then  $i.t \neq o'.t$ , and viceversa for  $p_2$  and  $p_1$ .

With these definitions, it is in general not possible to derive the components from the composite. Later, we will see how this can be accomplished for a different model that we use to define architectures. There, we will also introduce non-trivial orderings of the agents.

We relate different agent algebras by means of conservative approximations. A conservative approximation from  $\mathscr{Q}$  to  $\mathscr{Q}'$  is a pair  $\Psi = (\Psi_l, \Psi_u)$ , where  $\Psi_l$  and  $\Psi_u$  are functions from  $\mathscr{Q}.D$  to  $\mathscr{Q}'.D$ . The first mapping is an upper bound of the agent relative to the order of the algebra: for instance, the abstract agent in  $\mathscr{Q}'$  represents all of the possible behaviors of the agent in the more detailed domain  $\mathscr{Q}$ , plus possibly some more. The second is a lower bound: the abstract agent represents only possible behaviors of the more detailed one, but possibly not all. Formally, a conservative approximations is an abstraction that maintain a precise relationship between the orders in the two agent algebras.

**Definition 2.** Let  $\mathscr{Q}$  and  $\mathscr{Q}'$  be ordered agent algebras, and let  $\Psi_l$  and  $\Psi_u$  be functions from  $\mathscr{Q}.D$ to  $\mathscr{Q}'.D$ . We say that  $\Psi = (\Psi_l, \Psi_u)$  is a conservative approximation from  $\mathscr{Q}$  to  $\mathscr{Q}'$  if and only if for all agents p and q in  $\mathscr{Q}.D$ ,

$$\Psi_u(p) \preceq \Psi_l(q) \Rightarrow p \preceq q.$$

Thus, when used in combination, the two mappings allow us to relate refinement verifi-

cation results in the abstract domain to results in the more detailed domain. Hence, the verification can be done in  $\mathcal{Q}'$ , where it is presumably more efficient than in  $\mathcal{Q}$ . The conservative approximation guarantees that this will not lead to a false positive result, although false negatives are possible depending on how the approximation is chosen.

To define the inverse  $\Psi_{inv}$  of an approximation, we investigate whether there are agents in  $\mathscr{Q}.D$  that are represented exactly by  $\Psi_u$  and  $\Psi_l$  rather than just being bounded. We do so by only considering those agents p for which  $\Psi_l(p)$  and  $\Psi_u(p)$  have the same value p'. Intuitively, p'represents p exactly in this case, and we therefore define  $\Psi_{inv}(p') = p$ . If  $\Psi_l(p) \neq \Psi_u(p)$ , then p is not represented exactly in  $\mathscr{Q}'$ . In this case, p is not in the image of  $\Psi_{inv}$ .

**Definition 3.** Let  $\Psi = (\Psi_l, \Psi_u)$  be a conservative approximation from  $\mathscr{Q}$  to  $\mathscr{Q}'$ . For  $p' \in \mathscr{Q}'$ .D, the inverse  $\Psi_{inv}(p')$  is defined and is equal to p if and only if  $\Psi_l(p) = \Psi_u(p) = p'$ .

If the algebra  $\mathscr{Q}$  is partially ordered (as opposed to preordered), the inverse of the conservative approximation is uniquely determined. Otherwise, a choice may be possible among order equivalent agents. In all cases, however, because of the defining properties of a conservative approximation,  $\Psi_{inv}$  is one-to-one, monotonic, and inverse of both  $\Psi_l$  and  $\Psi_u$ .

Assume now that for an agent p,  $\Psi_{inv}(\Psi_l(p))$  and  $\Psi_{inv}(\Psi_u(p))$  are both defined, It is easy to show that  $\Psi_{inv}(\Psi_l(p)) \leq p \leq \Psi_{inv}(\Psi_u(p))$ . This fact makes precise the intuition that  $\Psi_l(p)$  and  $\Psi_u(p)$  represent a lower and an upper bound of p, respectively.

We can use agent algebras to describe formally the process of successive refinement in a platform-based design methodology. There, refinement is interpreted as the concretization of a *function* in terms of the elements of a *platform*. The process of design consists of evaluating the performance of different kinds of instances in the platform by mapping the functionality onto its different elements. The implementation is then chosen on the basis of a cost function. We use three distinct domains of agents to characterize the process of mapping and performance evaluation. The first two are used to represent the platform and the function, while the third, called the *common semantic domain*, is an intermediate domain that is used to map the function onto a platform instance.

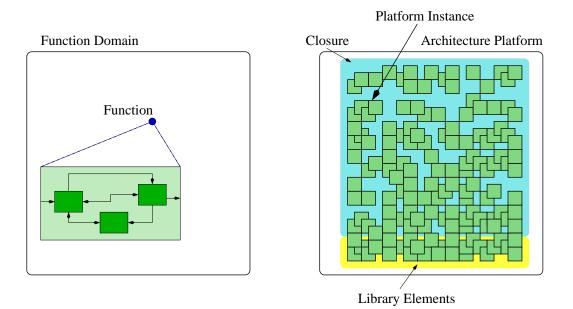

A platform, depicted in Figure 2.3 on the right, corresponds to the implementation search space.

**Definition 4.** A platform consists of a set of elements, called the library elements, and of composition rules that define their admissible topologies of interconnection.

To obtain an appropriate domain of agents to model a platform, we start from the set of library elements  $D_0$ . The domain of agents D is then constructed as the closure of  $D_0$  under the operation of parallel composition. In other words, we construct all the topologies that are admissible by the composition rules, and add them to the set of agents in the algebra. Each element of the architecture platform is called a *platform instance*.

Performance evaluation usually requires that the elements of a platform include information regarding their internal structure. Thus, an algebra such as the typed IO agent algebra described is not suitable for this purpose, since composition does not retain the structure of the agent. The IO agents can, however, be used as library elements  $D_0$ . A new domain of agents D can then be constructed as follows. If  $p_0 \in D_0$  is a library element, we include the *symbol*  $\mathbf{p}_0$  in the set of agents  $\mathscr{Q}.D$ . We then close the set D under the operation of parallel composition. However, we represent a composition  $p = p_1 \parallel p_2$  in  $\mathscr{Q}$  as the *sequence of symbols*  $\mathbf{p}_1 \parallel \mathbf{p}_2$ . By doing so, we retain the *structure* of the composite, since all the previous composition steps are recorded in the representation. We call this process a *platform closure*. **Definition 5.** *Given a set of library elements*  $D_0$  *and a composition operator*  $\parallel$ *, the* platform closure *is the algebra with domain*

$$D = \{\mathbf{p} : p \in D_0\} \cup \{\mathbf{p_1} \parallel \mathbf{p_2} : \mathbf{p_1} \in D \land \mathbf{p_2} \in D\}$$

$$(2.1)$$

#### where $p_1 \parallel p_2$ is defined if and only if it can be obtained as a legal composition of agents in $D_0$ .

The construction outlined above is general, and can be applied to building several different platforms, as will be shown later. The result is similar to a term algebra with the "constants" in  $D_0$  and the operation of composition. Unlike a term algebra, however, our composition is subject to the constraints of the composition rules. For example an "architecture" platform may provide only one instance of a particular processor. In that case, topologies that use two ore more instances are ruled out. In addition, the final algebra must be taken up to the equivalence induced by the required properties of the operators. For example, since parallel composition must be commutative,  $\mathbf{p_1} \parallel \mathbf{p_2}$  should not be distinguished from  $\mathbf{p_2} \parallel \mathbf{p_1}$ . This can be accomplished by taking the appropriate quotient relative to the equivalence relation. The details are outside the scope of this thesis.

On the other hand, the function, depicted in Figure 2.3 on the left, is represented in an agent algebra called the *specification domain*. Here the desired function may be represented denotationally, as the collective behavior of a composition of agents, or may retain its structure in terms of a particular topology of simpler functions. The denotational representation is typically used at the beginning of the platform-based design process, when no information on the structure of the implementation is available. Conversely, after the first mapping, the subsequent refinement steps are started from the mapped platform instance, which is taken as the specification. Thus, a *common semantic domain*, described below, is used as the specification domain. However, contrary to the mapping process that is used to select one particular instance among several, when viewed as a

Figure 2.3: Architecture and Function Platforms

representation of a function the mapped instance is a specification, and it is therefore fixed.

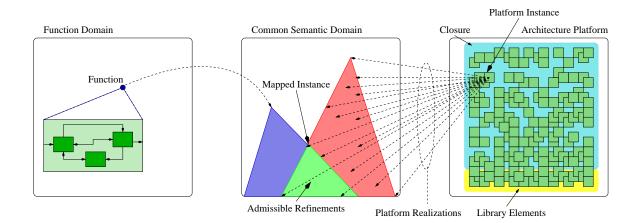

The function and the platform come together in an intermediate representation, called the *common semantic domain*. This domain plays the role of a common refinement and is used to combine the properties of both the platform and the specification domain that are relevant for the mapping process. The domains are related through conservative approximations.

**Definition 6.** Given a platform  $\mathscr{Q}^P$  and specification domain  $\mathscr{Q}^S$ , a common semantic domain is an agent algebra  $\mathscr{Q}^C$  related to  $\mathscr{Q}^P$  and  $\mathscr{Q}^S$  through conservative approximations  $\Psi^P$  and  $\Psi^S$ , respectively.

In particular, we assume that the inverse of the conservative approximation is defined at the function that we wish to evaluate. The function therefore is mapped onto the common semantic domain as shown in Figure 2.4. This mapping also includes all the refinements of the function that are consistent with the performance constraints, which can be interpreted in the semantic domain.

Figure 2.4: Mapping of function and architecture

If the platform includes programmable elements, the correspondence between the platform and the common semantic domain is typically more complex. In that case, each platform instance may be used to implement a variety of functions, or behaviors. Each of these functions is in turn represented as one agent in the common semantic domain. A platform instance is therefore projected onto the common semantic domain by considering the collection of the agents that can be implemented by the particular instance. This projection, represented by the rays that originate from the platform in Figure 2.4, may or may not have a greatest element. If it does, the greatest element represents the non-deterministic choice of any of the functions that are implementable by the instance.