### Digitally Calibrated Analog-to-Digital Converters in Deep Sub-micron CMOS

Cheongyuen (Bill) Tsang

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-67 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-67.html

May 22, 2008

Copyright © 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Digitally Calibrated Analog-to-Digital Converters in Deep Sub-micron CMOS

by

Cheongyuen William Tsang

B.S. (University of Michigan, Ann Arbor) 2000M.S. (University of California, Berkeley) 2003

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY

> Committee in charge: Professor Borivoje Nikolić , Chair Professor Robert Brodersen Professor Paul Wright

> > Spring 2008

The dissertation of Cheongyuen William Tsang is approved:

Chair

Date

Date

Date

University of California, Berkeley

Spring 2008

### Digitally Calibrated Analog-to-Digital Converters in Deep Sub-micron CMOS

Copyright 2008

by

Cheongyuen William Tsang

#### Abstract

#### Digitally Calibrated Analog-to-Digital Converters in Deep Sub-micron CMOS

by

Cheongyuen William Tsang

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

We present and implement an adaptive digital technique to calibrate pipelined analog-todigital converters (ADCs). Rather than achieving linearity by adjustment of analog component values, the new approach infers component errors from conversion results and applies digital postprocessing to correct those results. The scheme proposed here draws close analogy to the channel equalization problem commonly encountered in digital communications. We show that, with the help of a slow but accurate ADC, the proposed code-domain adaptive digital filter is sufficient to remove the effects of component errors including capacitor mismatch, signal-dependent finite op-amp gain, op-amp offset, and sampling-switch-induced offset. The algorithm is all digital, fully adaptive, data-driven, and operates in the background. Strong tradeoffs between accuracy and speed of pipelined ADCs are greatly relaxed in this approach with the aid of digital correction techniques. Analog precision problems are translated into the complexity of digital signal-processing circuits, allowing this approach to benefit from CMOS device scaling in contrast to most conventional correction techniques.

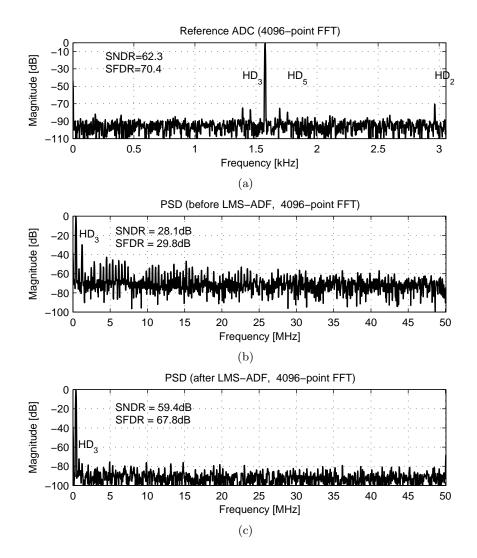

To demonstrate the idea, a prototype has been designed and fabricated in  $0.13\mu$ m with 1.35V power supply. The system mainly consists of a pipelined ADC, a reference ADC, and an adaptive digital filter in FPGA. The measured results show that the SNR improves from 28.1dB before calibration to 59.4dB after calibration at 100MS/s with a 411kHz. The SFDR improves from 29.8dB to 67.8dB. The total power consumption of the chip is 448mW and the estimated power consumption of the adaptive digital filter is 7mW at 100MHz.

Professor Borivoje Nikolić Dissertation Committee Chair To my parents

## Contents

| Li            | st of | Figures                                                                 | vi       |

|---------------|-------|-------------------------------------------------------------------------|----------|

| $\mathbf{Li}$ | st of | Tables                                                                  | x        |

| 1             | Intr  | roduction                                                               | 1        |

|               | 1.1   | Motivation                                                              | 1        |

|               | 1.2   | State-of-the-Art Calibrated ADCs                                        | 2        |

|               | 1.3   | Thesis Organization                                                     | 4        |

| <b>2</b>      | Full  | ly Digital Background Calibration of Pipelined ADCs                     | <b>5</b> |

|               | 2.1   | Introduction                                                            | 5        |

|               | 2.2   | Overview of Pipelined ADCs                                              | 6        |

|               | 2.3   | Review of ADC Calibration Techniques                                    | 7        |

|               | 2.4   | Least-Mean-Square (LMS) Equalization Method                             | 12       |

|               | 2.5   | Code-Domain Filtering Approach                                          | 12       |

|               |       | 2.5.1 Code-Domain Formulation of 1.5-b/Stage Pipelined ADC Architecture | 13       |

|               |       | 2.5.2 Code-Domain Formulation of 2.5-b/Stage Pipelined ADC Architecture | 14       |

|               |       | 2.5.3 Code-Domain Formulation of Residue Amplifier with Nonlinear Am-   |          |

|               |       | plifier Gain                                                            | 17       |

|               |       | 2.5.4 Code-Domain Formulation of a Complete Pipelined ADC $\ldots$      | 18       |

|               |       | 2.5.5 Code-Domain Filtering Technique System Architecture               | 21       |

|               | 2.6   | Behavioral Simulations                                                  | 22       |

|               |       | 2.6.1 Simulation Results                                                | 23       |

|               |       | 2.6.2 Performance Analysis                                              | 27       |

|               | 2.7   | Conclusion                                                              | 31       |

| 3             | Hig   | h-Accuracy Reference ADC                                                | 32       |

|               | 3.1   | Background Calibrated Analog-to-Digital Converter (ADC) System Overview | 32       |

|               | 3.2   | Slow-but-Accurate A/D Converters                                        | 33       |

|               | 3.3   | Integrating A/D Converters                                              | 34       |

|               | 3.4   | Successive Approximation A/D Converters                                 | 35       |

|               | 3.5   | Algorithmic/Cyclic A/D Converters                                       | 36       |

|          | 3.6  | Oversampling A/D Converters                                                                                                                                    |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 3.7  | First-Order Sigma-Delta ( $\Sigma\Delta$ ) A/D Converters                                                                                                      |

|          | 3.8  | Second-Order $\Sigma\Delta$ A/D Converters                                                                                                                     |

|          | 3.9  | Multi-Stage Noise Shaping (MASH) $\Sigma\Delta$ A/D Converters                                                                                                 |

|          |      | 3.9.1 2-1 MASH $\Sigma\Delta$ A/D Converters                                                                                                                   |

|          | 3.10 | Conclusion                                                                                                                                                     |

| <b>4</b> | Des  | ign of $\Sigma\Delta$ A/D Converter 44                                                                                                                         |

|          | 4.1  | Introduction                                                                                                                                                   |

|          | 4.2  | $\Sigma\Delta$ ADC as a DC Voltmeter                                                                                                                           |

|          | 4.3  | Reference ADC Architecture                                                                                                                                     |

|          |      | 4.3.1 Second-Order $\Sigma\Delta$ Architecture                                                                                                                 |

|          |      | 4.3.2 2-1 MASH $\Sigma\Delta$ Architecture                                                                                                                     |

|          | 4.4  | Simulink Models of $\Sigma\Delta$ ADCs                                                                                                                         |

|          |      | 4.4.1 Dynamic Range                                                                                                                                            |

|          |      | 4.4.2 DC Tones and Dithering $\ldots \ldots 49$                                                 |

|          |      | 4.4.3 Power Consumption $\ldots \ldots \ldots$ |

|          |      | 4.4.4 Settling of Finite Impulse Response (FIR) Decimation Filter 53                                                                                           |

|          | 4.5  | Integrator Signal Scaling                                                                                                                                      |

|          | 4.6  | Thermal Noise                                                                                                                                                  |

|          | 4.7  | Flicker Noise    60                                                                                                                                            |

|          | 4.8  | Effects of Circuit Noise                                                                                                                                       |

|          | 4.9  | Matching of $\lambda$ , $\beta$ in 2-1 MASH $\Sigma\Delta$ ADCs                                                                                                |

|          | 4.10 | Amplifier DC Gain    66                                                                                                                                        |

|          |      | Amplifier Settling    67                                                                                                                                       |

|          | 4.12 | Conclusion                                                                                                                                                     |

| <b>5</b> |      |                                                                                                                                                                |

|          | 5.1  | Introduction                                                                                                                                                   |

|          | 5.2  | Switched-Capacitor Integrators                                                                                                                                 |

|          |      | 5.2.1 First Integrator                                                                                                                                         |

|          |      | 5.2.2 Second Integrator                                                                                                                                        |

|          |      | 5.2.3 Third Integrator                                                                                                                                         |

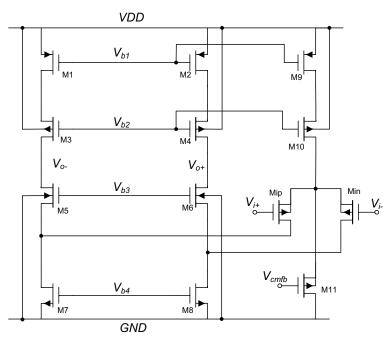

|          | 5.3  | Operational Trans-conductance Amplifiers (OTAs)                                                                                                                |

|          |      | 5.3.1 Main OTAs                                                                                                                                                |

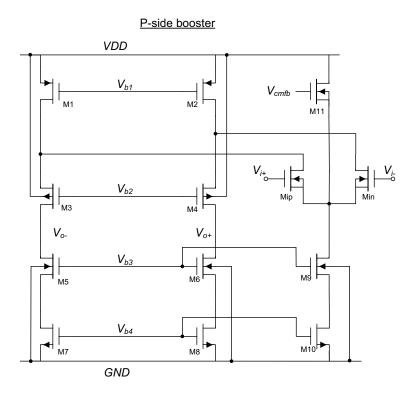

|          |      | 5.3.2 N-side Boosters                                                                                                                                          |

|          |      | 5.3.3 P-side Boosters                                                                                                                                          |

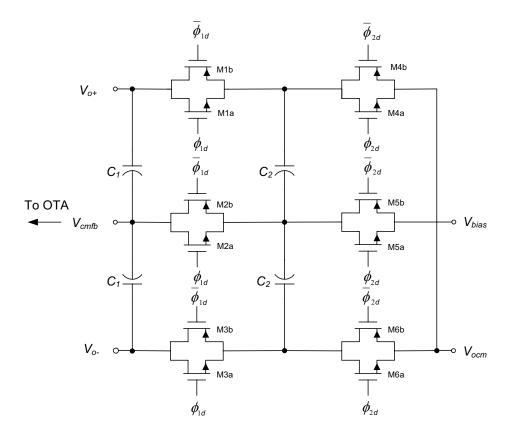

|          |      | 5.3.4 Switched-Capacitor Common-Mode Feedback (CMFB) Circuits 82                                                                                               |

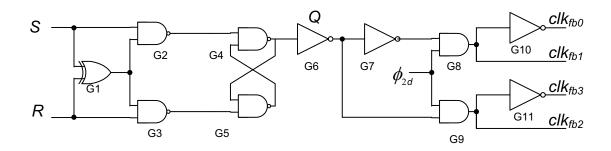

|          | 5.4  | Comparators                                                                                                                                                    |

|          | 5.5  | Latches and DACs                                                                                                                                               |

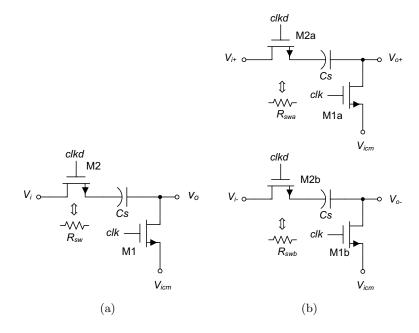

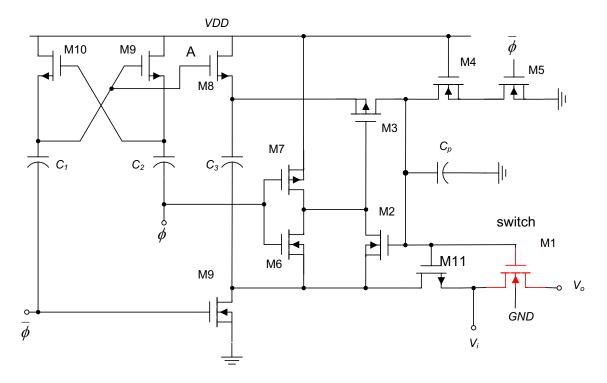

|          | 5.6  | Sampling Switches                                                                                                                                              |

|          | 5.7  | Clock Generation                                                                                                                                               |

|          | 5.8  | Conclusion                                                                                                                                                     |

iv

| 6  |                                                                                                                                                         | 93              |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|    |                                                                                                                                                         | 93              |

|    |                                                                                                                                                         | 95<br>95        |

|    |                                                                                                                                                         | 97              |

|    |                                                                                                                                                         | 98<br>08        |

|    | 6.4 Summary                                                                                                                                             | 98              |

| 7  | Design of High-speed Pipelined A/D Converter 10                                                                                                         |                 |

|    |                                                                                                                                                         | 00              |

|    |                                                                                                                                                         | 01              |

|    | 0 1 0                                                                                                                                                   | 02              |

|    | 0/ 0 <b>i</b>                                                                                                                                           | 02              |

|    |                                                                                                                                                         | 03              |

|    | 0 1 0                                                                                                                                                   | 05              |

|    |                                                                                                                                                         | 06              |

|    | 7.5 Summary $\dots \dots \dots$                         | 08              |

| 8  | Clock Generation Circuit 11                                                                                                                             | 10              |

|    | 8.1 Introduction                                                                                                                                        | 10              |

|    | 8.2 Main Clocks for the Proposed ADC 11                                                                                                                 | 11              |

|    |                                                                                                                                                         | 13              |

|    | 8.4 Low Jitter Clock Buffer (LJCB)                                                                                                                      | 15              |

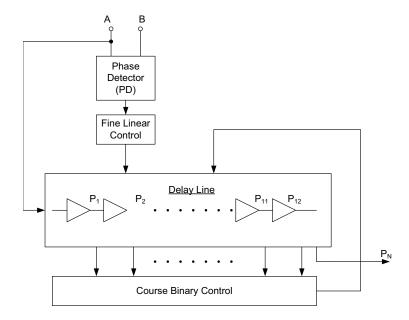

|    | 8.5 All Digital DLL Architecture                                                                                                                        | 15              |

|    | 8.5.1 Delay Line $\ldots \ldots \ldots$ | 17              |

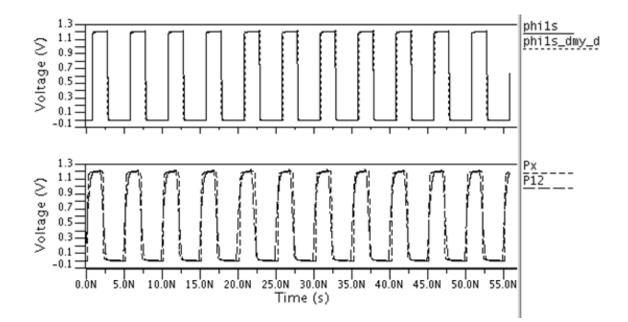

|    | 8.6 Simulations                                                                                                                                         | 17              |

|    | 8.7 Summary                                                                                                                                             | 17              |

| 9  | Full-Chip Integration 11                                                                                                                                | 19              |

| 0  | 1 0                                                                                                                                                     | 19              |

|    |                                                                                                                                                         | $20^{-5}$       |

|    |                                                                                                                                                         | 21              |

| 10 | Dimital Filtons                                                                                                                                         | 25              |

| 10 | 0                                                                                                                                                       | 25<br>25        |

|    |                                                                                                                                                         |                 |

|    | 5 I                                                                                                                                                     | $\frac{25}{26}$ |

|    |                                                                                                                                                         | $\frac{20}{26}$ |

|    |                                                                                                                                                         |                 |

|    | 10.3 Conclusion                                                                                                                                         | 34              |

| 11 | Measured Results 13                                                                                                                                     | 35              |

|    | 11.1 Introduction                                                                                                                                       | 35              |

|    | 11.2 $\Sigma\Delta$ ADC                                                                                                                                 | 35              |

|    | 11.2.1 Packaging and Test Setup                                                                                                                         | 36              |

|    | 11.2.2 Experimental Performance: Stand-alone $\Sigma\Delta$ ADC                                                                                         | 37              |

|    | 11.3 Background Calibrated ADC                                                                                                                          | 39              |

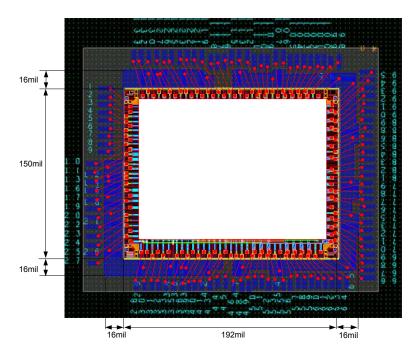

|              | 11.3.1 Chip Layout and Wire Bonding                        | 139 |

|--------------|------------------------------------------------------------|-----|

|              | 11.3.2 Test Setup                                          | 140 |

|              | 11.3.3 Measured Performance                                | 141 |

|              | 11.3.4 Performance Summary                                 | 150 |

| 12           | Conclusion                                                 | 152 |

|              | 12.1 Conclusion                                            | 152 |

|              | 12.2 Key Accomplishments                                   | 153 |

|              | 12.3 Suggestions for Future Work                           | 154 |

| Bi           | bliography                                                 | 155 |

| $\mathbf{A}$ | Prototype Chips Pin-out                                    | 166 |

|              | A.1 Pin-out of the stand-alone 2-1 MASH $\Sigma\Delta$ ADC | 167 |

|              | A.2 Pin-out of the background calibrated ADC               | 167 |

# List of Figures

| 2.1  | Ideal 1-b/stage pipelined ADC.                                                     | 7  |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | Residue amplifier transfer function: (a) ideal, (b) charge injection, (c) com-     |    |

|      | parator offset, (d) capacitor mismatch.                                            | 8  |

| 2.3  | Residue amplifier transfer function with reduced radix and correction idea.        | 9  |

| 2.4  | Residue amplifier of a 1.5-b/stage pipelined ADC and its voltage transfer          |    |

|      | function.                                                                          | 13 |

| 2.5  | (a) Residue amplifier of a 2.5-b/stage pipelined architecture and (b) its volt-    |    |

|      | age transfer function                                                              | 15 |

| 2.6  | Residue amplifier of a 1.5-b/stage pipelined ADC with nonlinear-amplifier          |    |

|      | gain and its voltage transfer function (solid line)                                | 19 |

| 2.7  | Block diagram of a multi-stage 1.5-b/stage pipelined ADC.                          | 20 |

| 2.8  | Error correction of pipelined ADC: code-domain nonlinear channel equalizer.        | 21 |

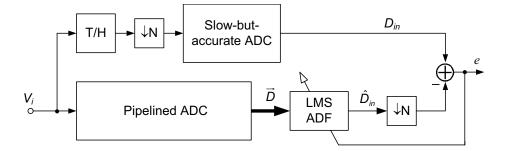

| 2.9  | Error correction of pipelined ADC: code-domain LMS adaptive equalizer.             | 22 |

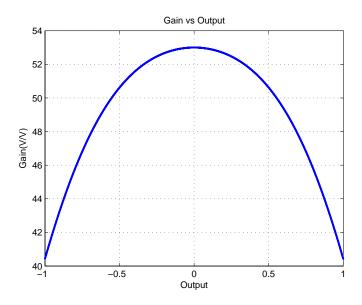

| 2.10 | Gain transfer function of a typical amplifier                                      | 24 |

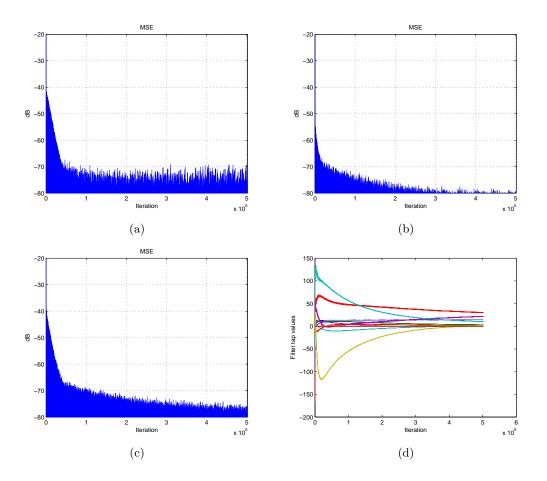

| 2.11 | Learning curve for (a) capacitor mismatch, (b) nonlinear amplifier gain, (c)       |    |

|      | all combined errors, (d) filter tap values                                         | 25 |

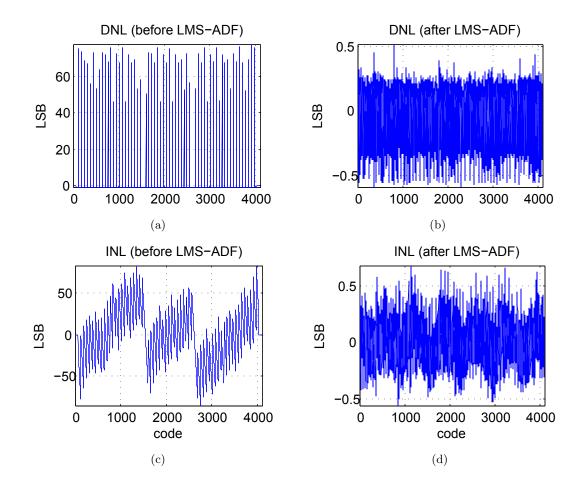

| 2.12 | (a) DNL before calibration, (b) INL after calibration, (c) INL before calibra-     |    |

|      | tion, (d) DNL after calibration                                                    | 26 |

| 2.13 | Learning curve of (a) saw-tooth, (b) random signal                                 | 27 |

| 2.14 | (a) FFT plot before calibration, (b) FFT plot after calibration                    | 27 |

| 2.15 | Calibration with a noisy reference ADC: (a) FFT plot before calibration, (b)       |    |

|      | FFT plot after calibration                                                         | 28 |

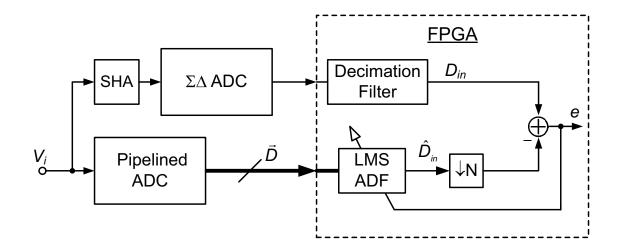

| 3.1  | ADC system block diagram.                                                          | 33 |

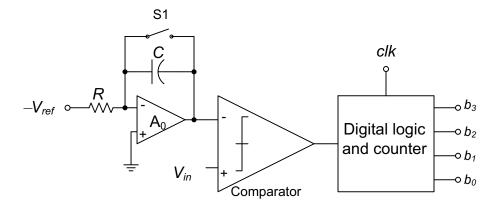

| 3.2  | Block diagram of a single-slope integrating A/D converter                          | 34 |

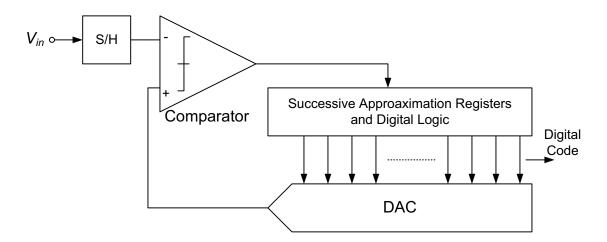

| 3.3  | Block diagram of a successive approximation ADC                                    | 36 |

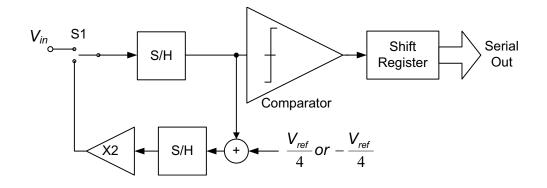

| 3.4  | Block diagram of an algorithmic/cyclic ADC (full-scale input = $\pm 1/2V_{ref}$ ). | 37 |

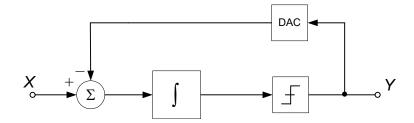

| 3.5  | First-order $\Sigma\Delta$ A/D converter.                                          | 39 |

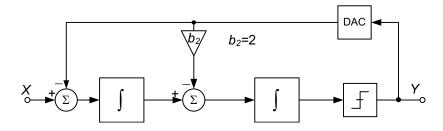

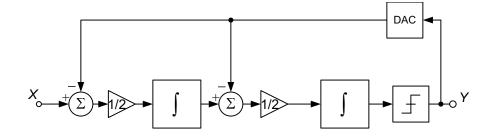

| 3.6  | Second-order $\Sigma \Delta$ A/D converter.                                        | 40 |

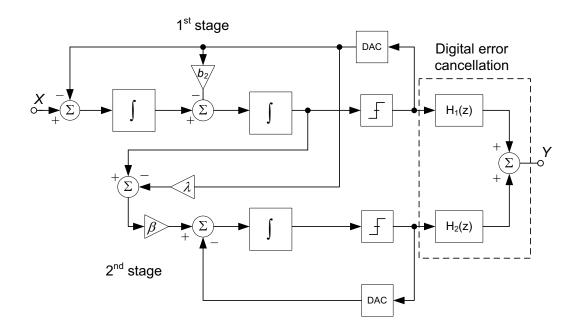

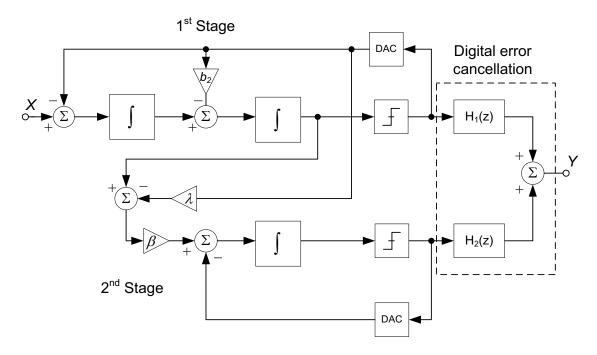

| 3.7  | 2-1 MASH $\Sigma\Delta$ A/D converter.                                             | 41 |

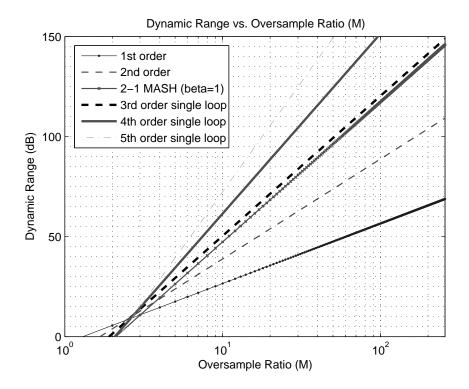

| 3.8  | Dynamic range vs. oversampling ratio $(M)$                                         | 42 |

| 4.1  | Operation of a $\Sigma\Delta$ ADC as a DC voltage                                        |

|------|------------------------------------------------------------------------------------------|

| 4.2  | Second-order $\Sigma\Delta$ with scaled gain coefficients                                |

| 4.3  | Block diagram of 2-1 MASH $\Sigma\Delta$ architecture                                    |

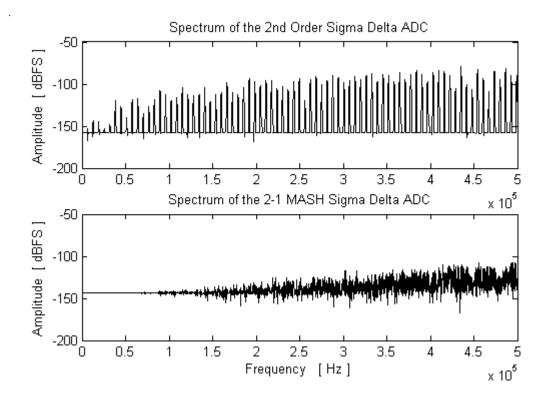

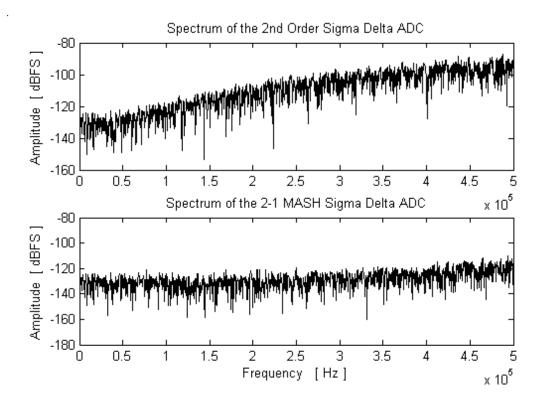

| 4.4  | Output spectra of a 0dBFS 750 kHz sine wave: (a) second-order $\Sigma\Delta$ ADC,        |

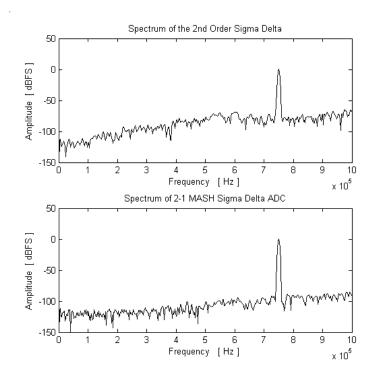

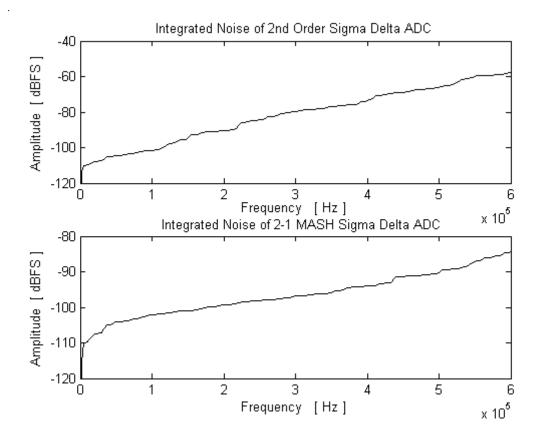

|      | (b) 2-1 MASH $\Sigma\Delta$ ADC                                                          |

| 4.5  | Integrated noise the second-order $\Sigma\Delta$ and the 2-1 MASH $\Sigma\Delta$ ADCs 50 |

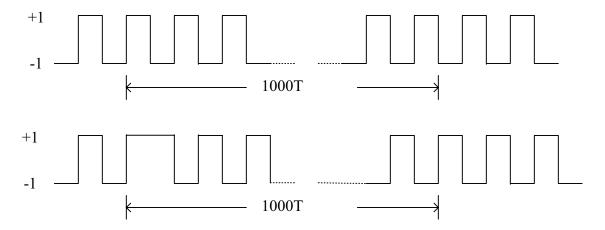

| 4.6  | Output pattern of the comparator: (a) 0 DC input, (b) 0.001 DC input 51                  |

| 4.7  | DC tones without circuit noise (8000-point FFT)                                          |

| 4.8  | 0.001 DC input (8000-point FFT)                                                          |

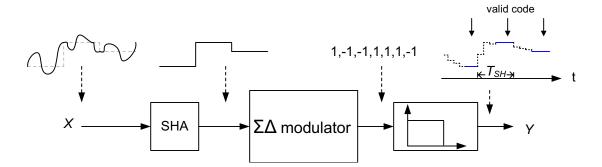

| 4.9  | Sigma-delta A/D converter input waveform                                                 |

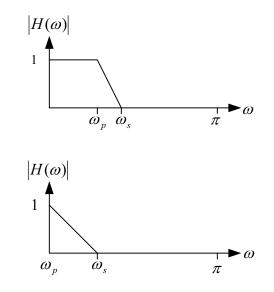

| 4.10 | (a) Traditional decimation filter, (b) proposed decimation filter                        |

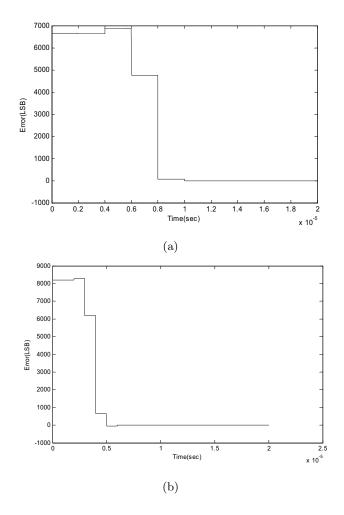

| 4.11 | Transient response of decimation filters: (a) second-order $\Sigma\Delta$ ADC (14-b),    |

|      | (b) 2-1 MASH $\Sigma\Delta$ ADC (14-b)                                                   |

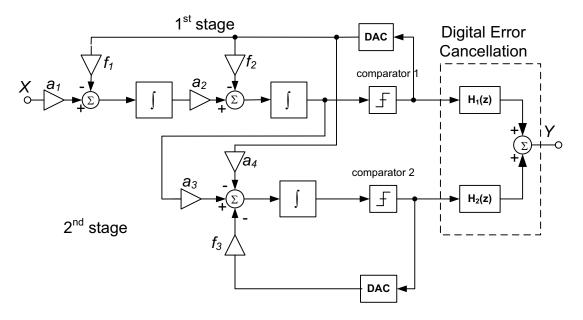

| 4.12 | Block diagram of a 2-1 MASH $\Sigma\Delta$ with scaled gain coefficients                 |

|      | Output swings of integrators                                                             |

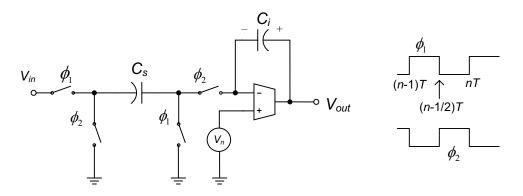

|      | Switched-capacitor integrator                                                            |

|      | Single-ended switched-capacitor integrator with OTA noise                                |

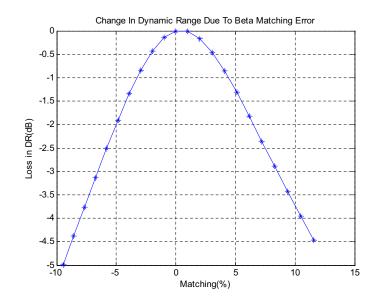

|      | Dynamic range degradation due to $\beta$ mismatch                                        |

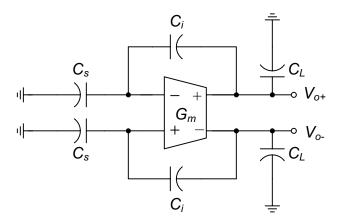

|      | Integrator configuration during integrating phase                                        |

|      |                                                                                          |

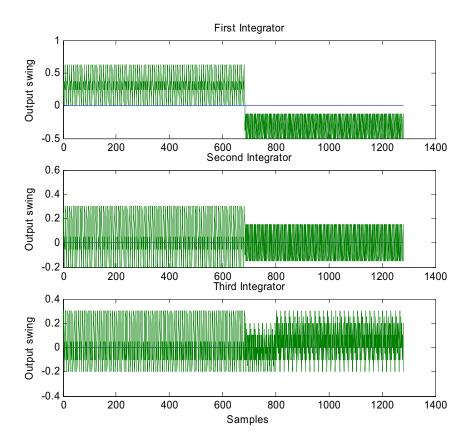

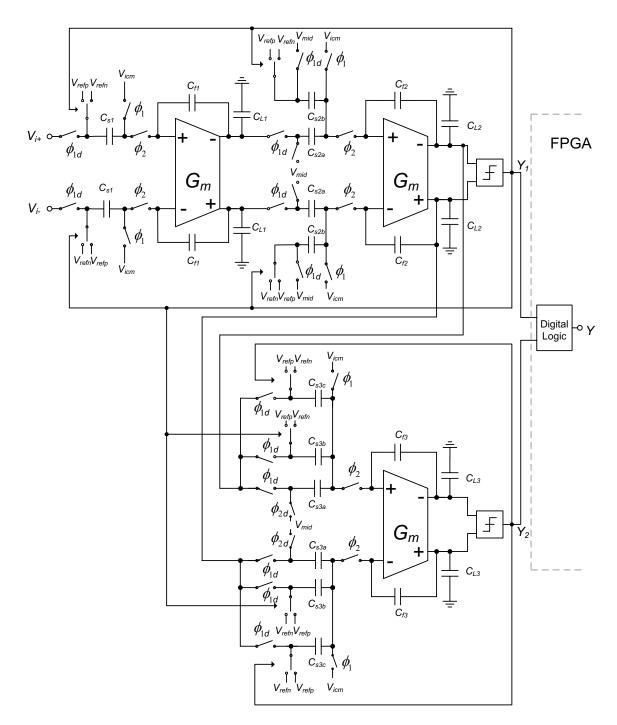

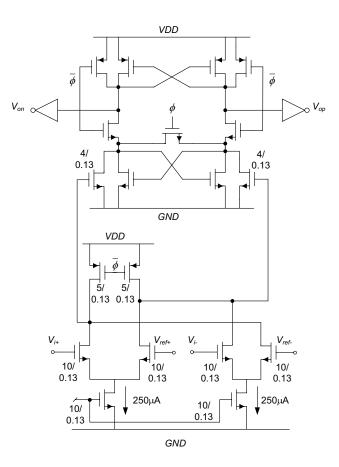

| 5.1  | Schematic of the 2-1 MASH $\Sigma\Delta$ ADC                                             |

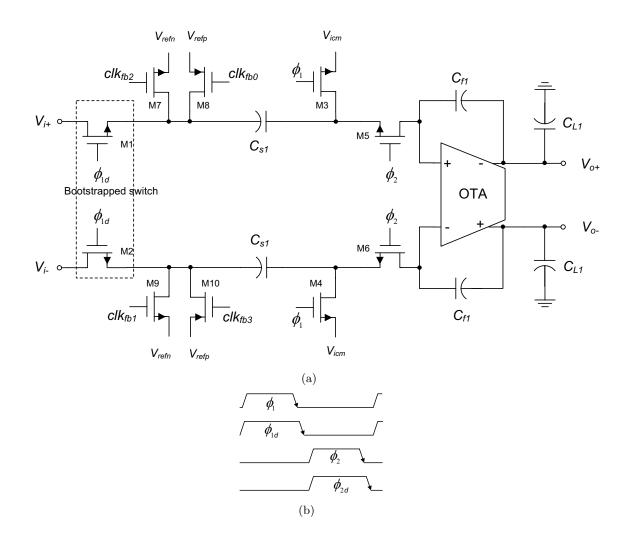

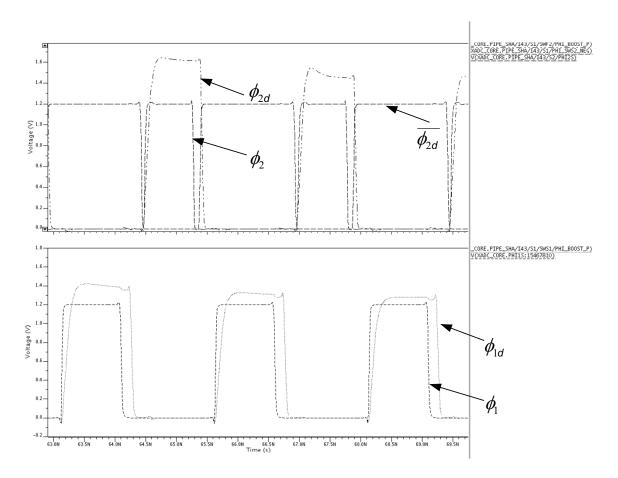

| 5.2  | (a)Schematic of first integrator, (b)its clock waveform                                  |

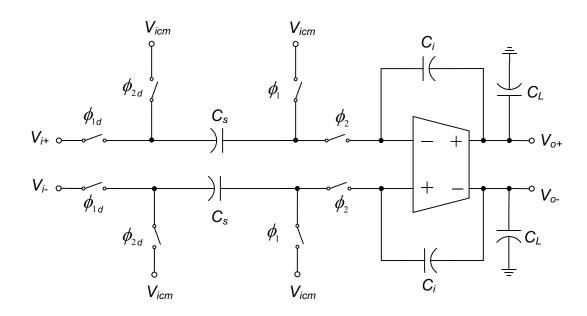

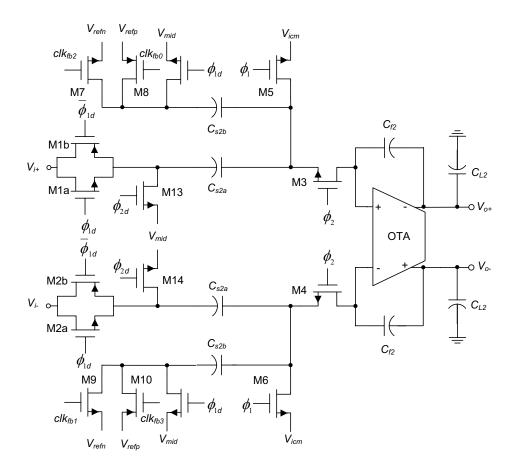

| 5.3  | Schematic of second integrator                                                           |

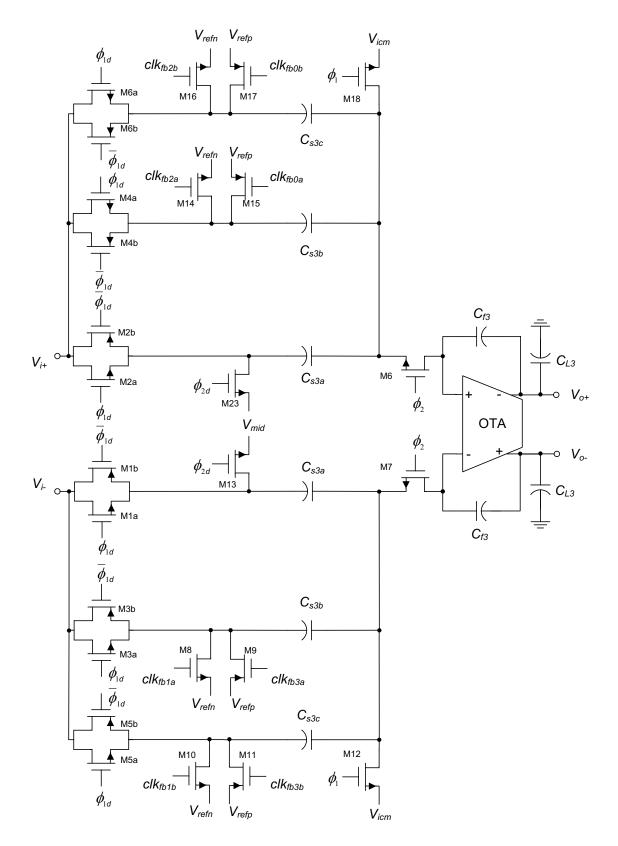

| 5.4  | Schematic of third integrator                                                            |

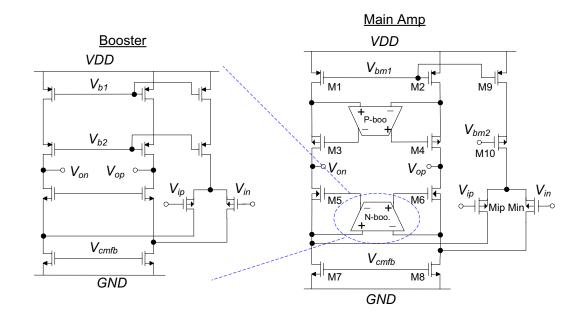

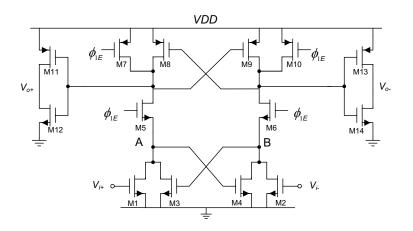

| 5.5  | Folded-cascode OTA with gain-boosting                                                    |

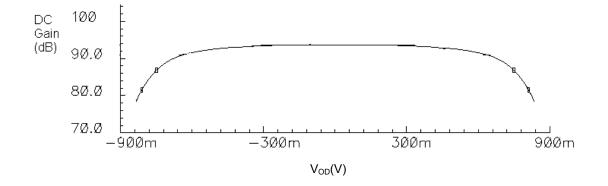

| 5.6  | DC gain of the first amplifier                                                           |

| 5.7  | Schematic of N-side booster                                                              |

| 5.8  | Schematic of P-side booster                                                              |

| 5.9  | Switched-capacitor common-mode feedback                                                  |

| 5.10 | Regenerative comparator                                                                  |

| 5.11 |                                                                                          |

|      | (a) Single-ended sampling network, (b) fully-differential sampling network 87            |

|      | Bootstrapped switch                                                                      |

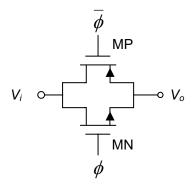

|      | CMOS sampling switch                                                                     |

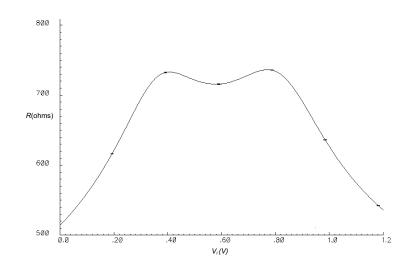

| 5.15 | Equivalent resistance of a CMOS sampling switch with NMOS, PMOS sizes                    |

|      | of $3.42\mu m/0.14\mu m$ and $1\mu/0.14\mu m$ , respectively                             |

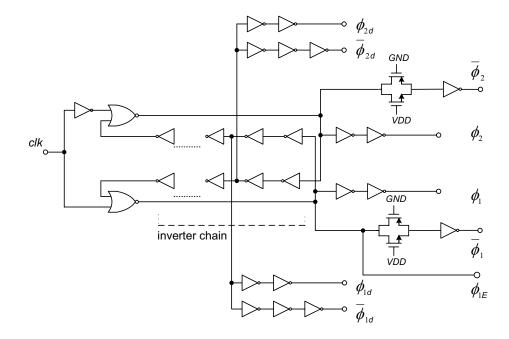

|      | Non-overlapping clock generation circuit                                                 |

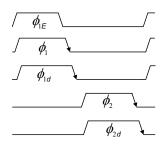

| 5.17 | Non-overlapping clocks                                                                   |

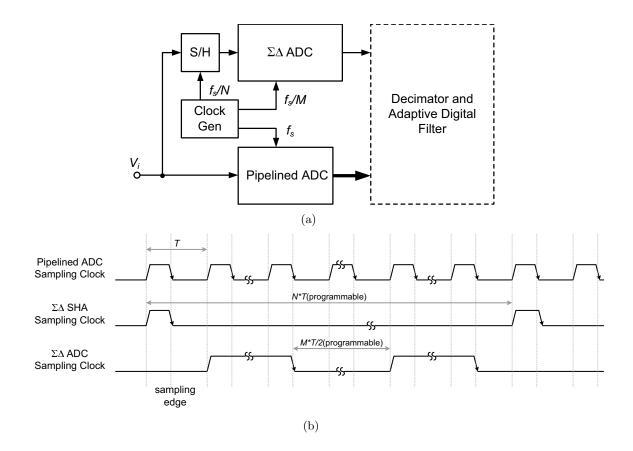

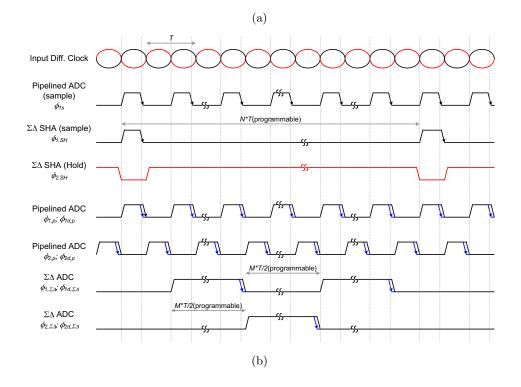

| 61   | (a) ADC sustain block diamam. (b) timin - diamam                                         |

| 6.1  | (a) ADC system block diagram, (b) timing diagram                                         |

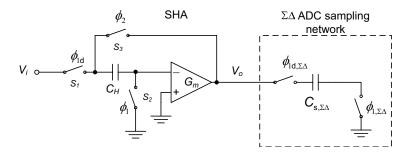

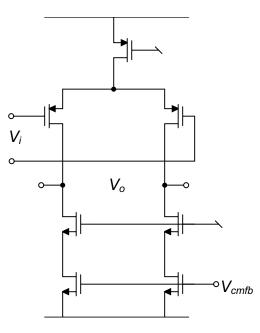

| 6.2  | Flip-over type switched-capacitor SHA                                                    |

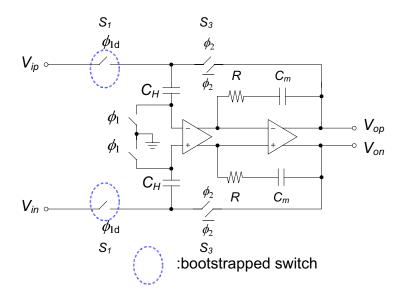

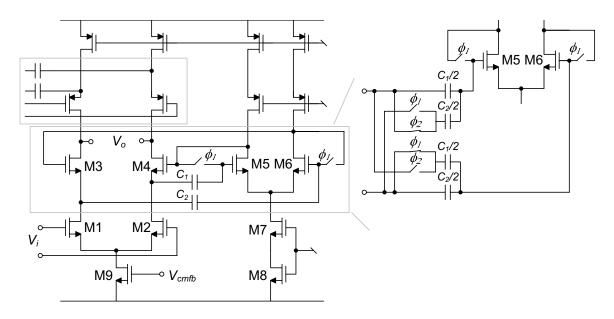

| 6.3  | Two-stage high-gain amplifier in S/H                                                     |

| 6.4  | S/H amplifier: stage 1                                                                   |

| 6.5  | S/H amplifier: stage 2                                                                   |

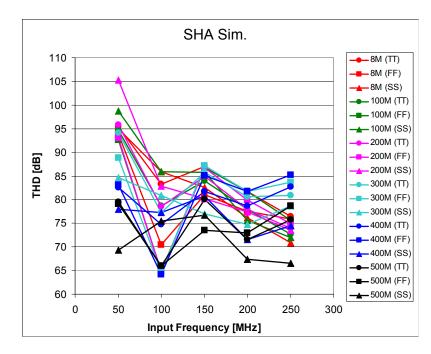

| 6.6  | SHA simulated results                                                                    |

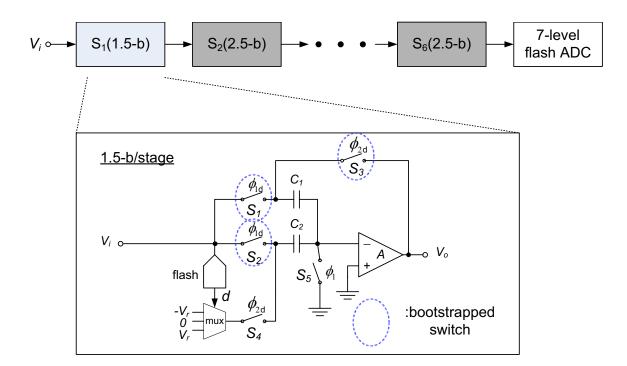

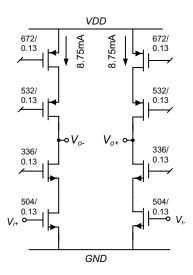

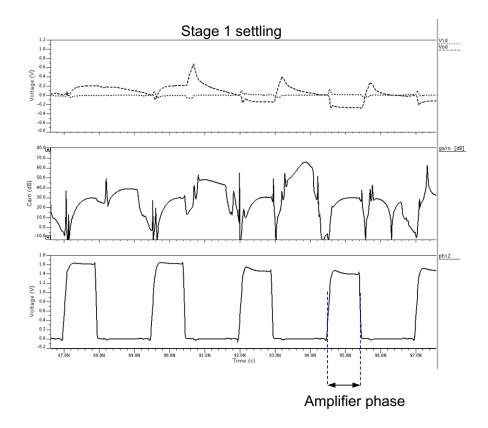

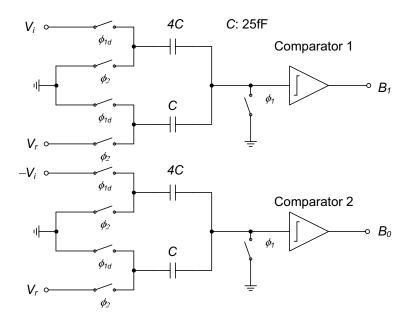

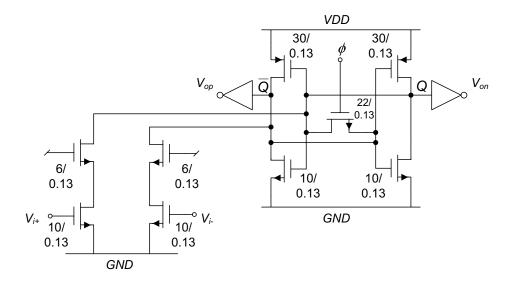

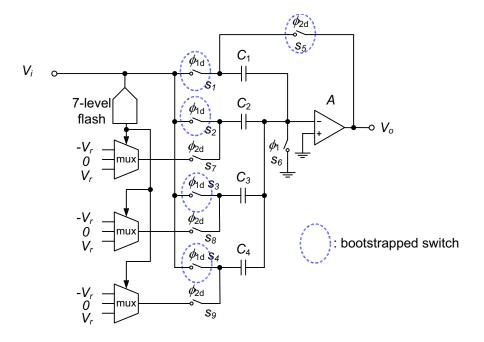

| $7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7 \\ 7.8 \\ 7.9 $ | Block diagram of a pipelined ADC.Amplifier in stage 1.Simulated settling of the first stage residue amplifier (post-layout, 400MS/s).Switched-capacitor flash ADC schematic.Dynamic comparator in stage 1.Schematic of stages 2-6.7-level flash ADC in stages 2-7.Comparator schematic stage 2-7.Comparator offset (50 Monte Carlo simulations). | 101<br>103<br>104<br>105<br>106<br>107<br>108<br>109<br>109 |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

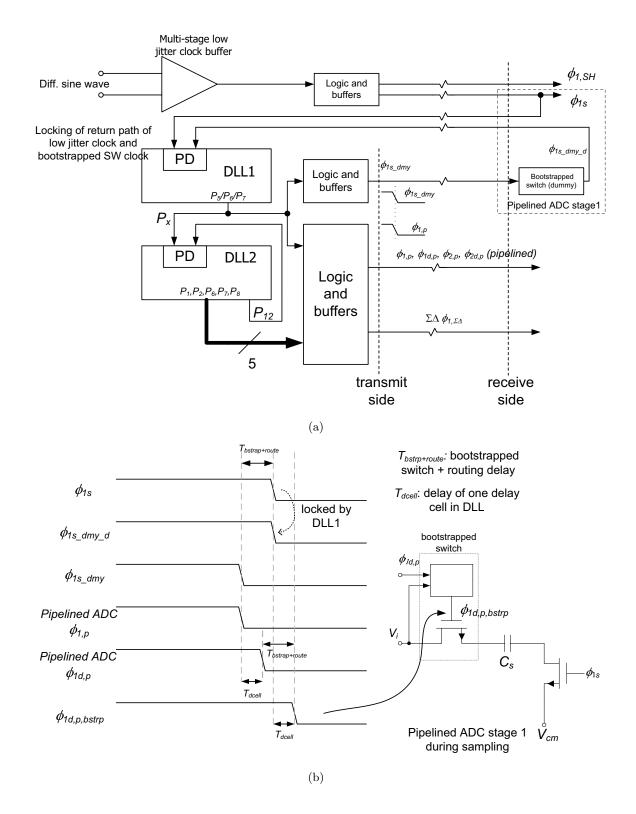

| 8.1<br>8.2                                                     | <ul> <li>(a) ADC front-end with annotated clock signals, (b) timing diagram.</li> <li>(a) Simplified block diagram of the clock generator, (b) locking of different clock phases.</li> </ul>                                                                                                                                                     | 112<br>114                                                  |

| $8.3 \\ 8.4$                                                   | Block diagram of digital DLL architecture.                                                                                                                                                                                                                                                                                                       | $\frac{116}{118}$                                           |

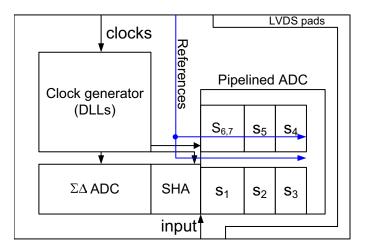

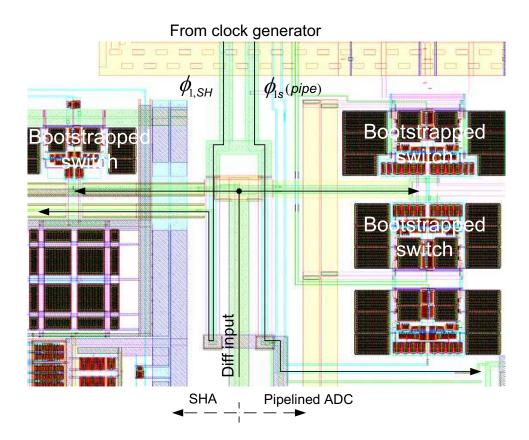

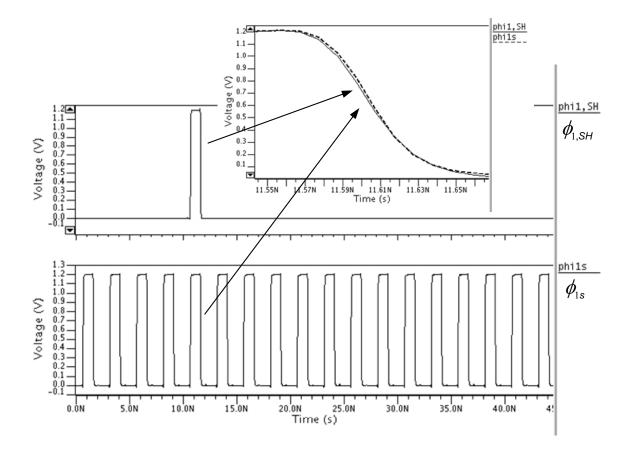

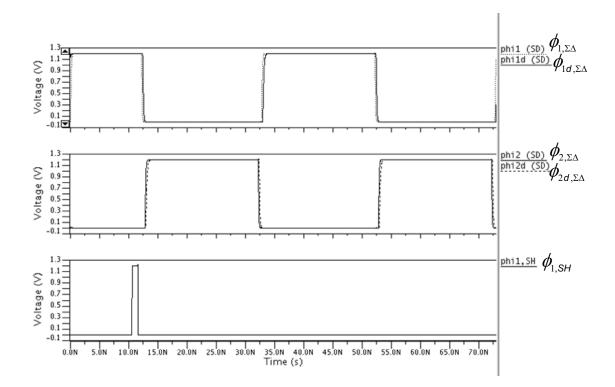

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5                                | Full-chip floor plan                                                                                                                                                                                                                                                                                                                             | . 123                                                       |

|                                                                | stage 1 ( $f_s$ =400MHz)                                                                                                                                                                                                                                                                                                                         | 124                                                         |

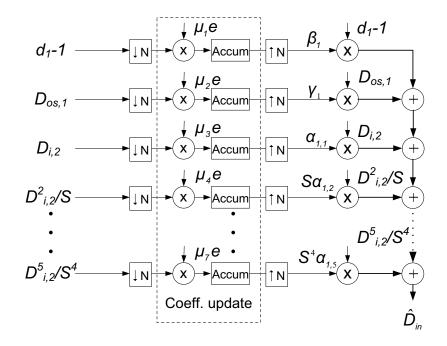

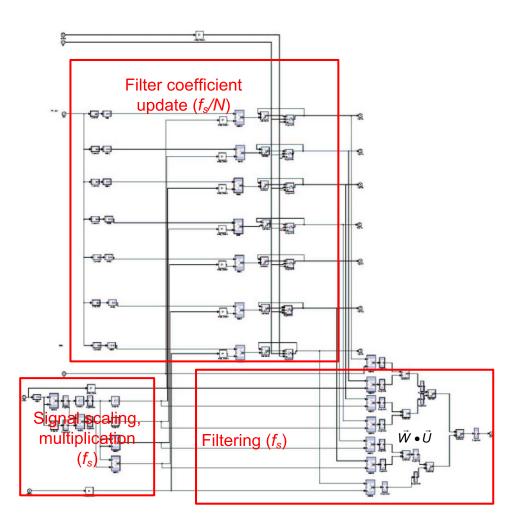

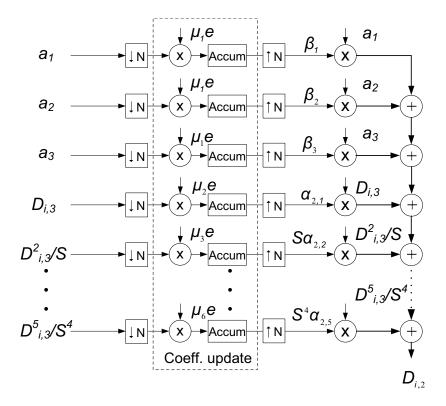

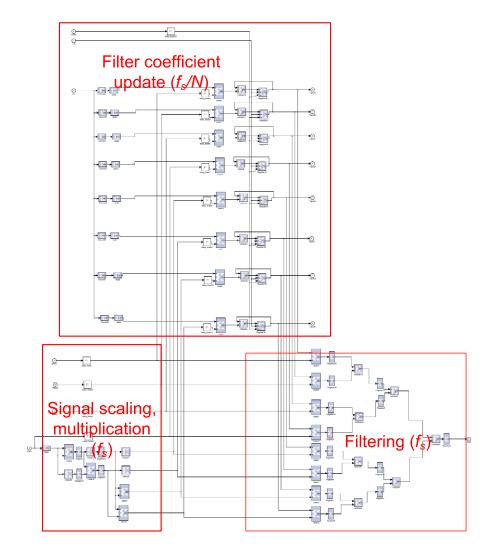

| 10.2                                                           | Nonlinear adaptive digital calibration of pipelined ADCs. $\dots$ Reverse pipelining of multi-stage adaptive digital filter. $\dots$ Simplified coefficient update diagram for the first pipeline stage (1.5-b). Parameter S is a constant scaling factor.                                                                                       | 126<br>127<br>128                                           |

|                                                                | Simulink design for nonlinear ADF for 1.5-b/stage architecture                                                                                                                                                                                                                                                                                   | 128<br>129                                                  |

| 10.6                                                           | Parameter S is a constant scaling factor                                                                                                                                                                                                                                                                                                         | 130<br>132<br>133                                           |

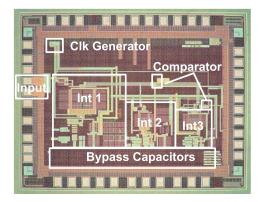

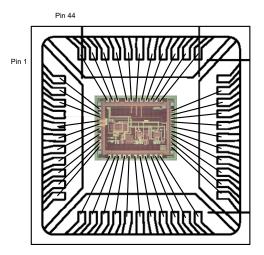

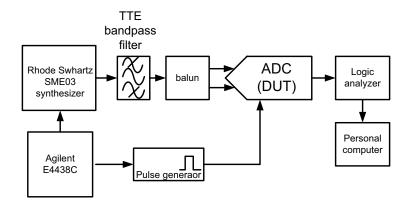

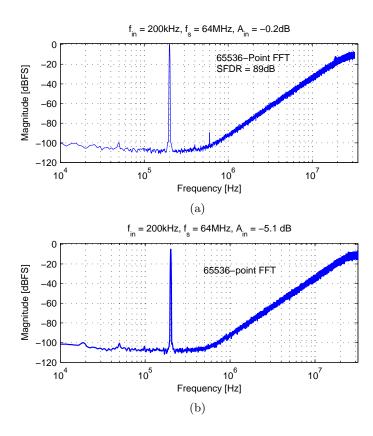

| $\begin{array}{c} 11.2\\ 11.3 \end{array}$                     | Stand-alone $\Sigma\Delta$ ADC die micrograph                                                                                                                                                                                                                                                                                                    | 136<br>137<br>137                                           |

|                                                                | -5.1dBFS input level                                                                                                                                                                                                                                                                                                                             | 138<br>139                                                  |

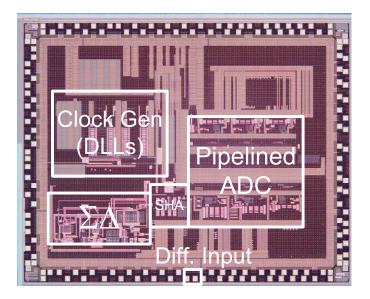

| 11.7                                                           | Background calibrated ADC die micrograph (3.7mm×4.7mm) Background calibrated ADC bonding diagram                                                                                                                                                                                                                                                 | 140<br>141<br>142                                           |

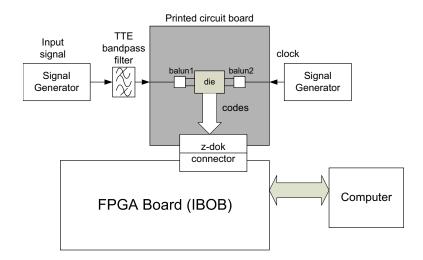

| 118                                                            | Background Calibrated ADC test setup                                                                                                                                                                                                                                                                                                             | 142                                                         |

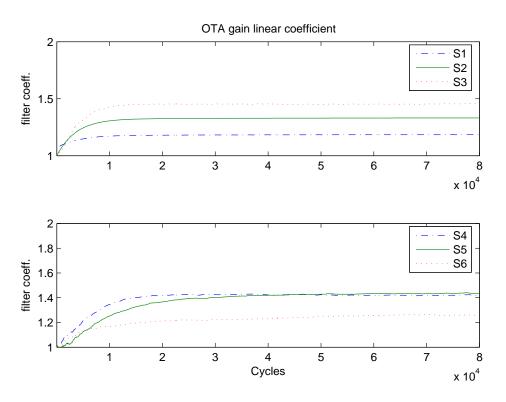

|                                                                | Measured convergence of OTA linear gain filter coefficients (one cycle = $\frac{1}{f_s/2^{14}}$ )                                                                                                                                                                                                                                                | .143                                                        |

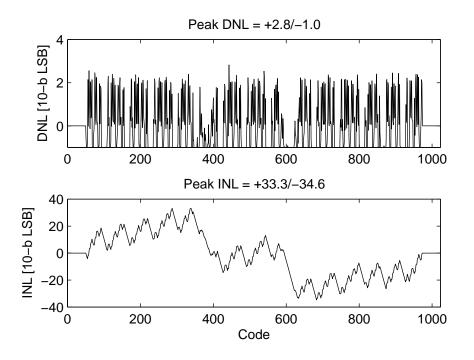

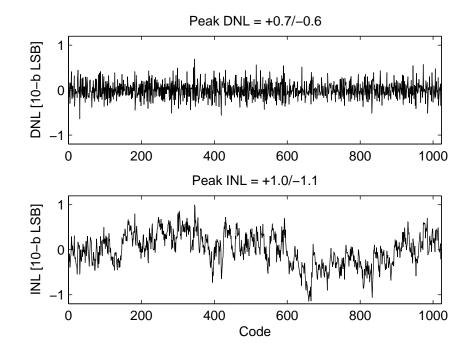

| 11.11Measured DNL and INL after calibration.                                                 | 144 |

|----------------------------------------------------------------------------------------------|-----|

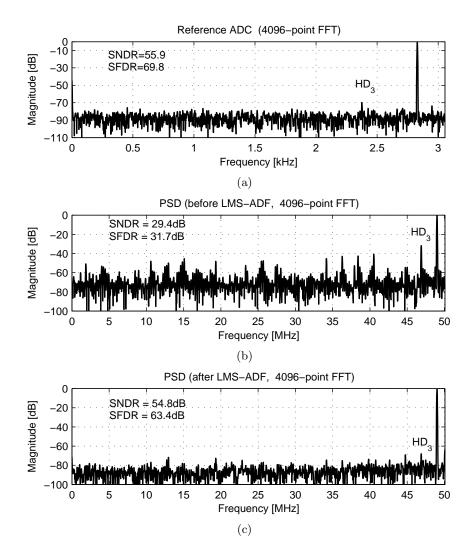

| 11.12<br>Measured ADC spectra for $f_s$ =100MHz, $V_{in}$ =0dBFS, $f_{in}$ =411kHz: (a) Ref- |     |

| erence ADC, (b) before calibration, (c) after calibration                                    | 145 |

| 11.13<br>Measured ADC spectra for $f_s=100$ MHz, $V_{in}=0$ dBFS, $f_{in}=49$ MHz: (a) ref-  |     |

| erence ADC, (b) before calibration, (c) after calibration                                    | 146 |

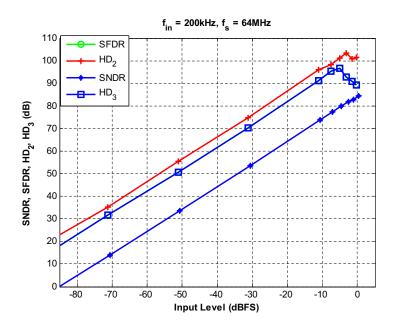

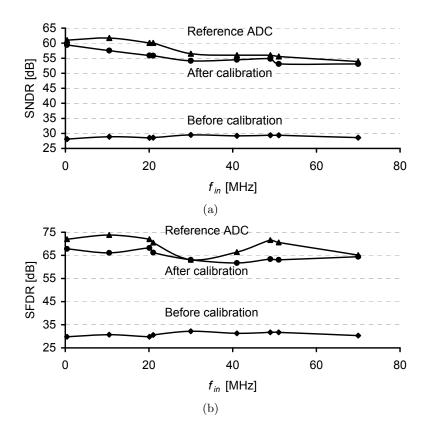

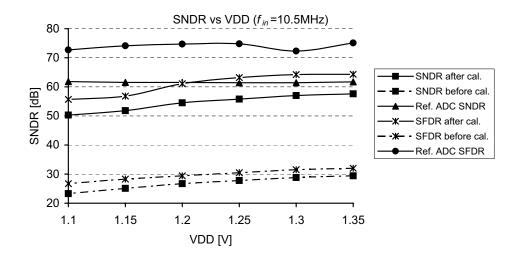

| 11.14Measured performance at 100MS/s: (a) SNDR, (b) SFDR                                     | 147 |

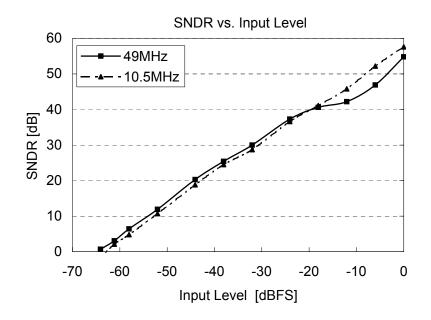

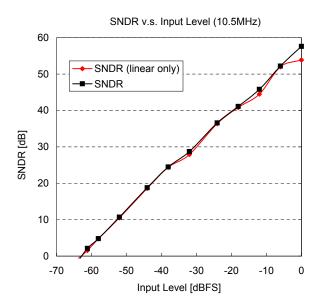

| 11.15Measured SNDR after calibration versus input level at 100MS/s                           | 147 |

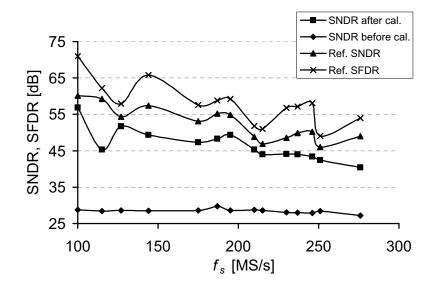

| 11.16 Measured SNDR versus $f_s$ with 10 MHz input                                           | 148 |

| 11.17Measured SNDR after calibration vs. VDD for $f_s=100$ MS/s, $f_{in}=10.5$ MHz.          | 149 |

| 11.18 Measured SNDR with linear and nonlinear calibration vs. input level for                |     |

| $f_s = 100 \text{MS/s}, f_{in} = 10.5 \text{MHz}.$                                           | 150 |

# List of Tables

| $2.1 \\ 2.2$ | 11 0                                                                           | $\frac{15}{24}$ |

|--------------|--------------------------------------------------------------------------------|-----------------|

| 4.1          |                                                                                | 67              |

| 4.2          | Gain coefficients of integrators 5                                             | 68              |

| 5.1          | First integrator transistor sizes                                              | 74              |

| 5.2          | First integrator capacitor values                                              | 74              |

| 5.3          | 0                                                                              | 6               |

| 5.4          |                                                                                | 6               |

| 5.5          | 0                                                                              | 78              |

| 5.6          | 0 1                                                                            | 78              |

| 5.7          |                                                                                | 80              |

| 5.8          |                                                                                | 32              |

| 5.9          | Transistor sizes in P-side boosters                                            | 32              |

| 7.1          | Decision of the 1.5-b flash ADC                                                | )4              |

| 7.2          | Scaling of the pipelines stages                                                | )6              |

| 8.1          | Jitter at different frequencies                                                | .6              |

| 10.1         | Word-length of calibration filter for different stages                         | 31              |

| 10.2         | Error correction of each stage                                                 | 32              |

| 10.3         | Estimated power and area(downsampling ratios $N=2^{14}$ , $M=2^4$ ) 13         | 33              |

| 11.1         | Measured performance summary of the stand-alone 2-1 MASH $\Sigma\Delta$ ADC 13 | 38              |

|              | Experimental Results                                                           | 51              |

| A.1          | Pin-out of the stand-alone 2-1 MASH $\Sigma\Delta$ ADC                         | 57              |

| A.2          | Pin-out of the background calibrated ADC                                       | ;8              |

#### Acknowledgments

It has been a great experience for me to study at the University of California, Berkeley. The knowledge and experience gained at Berkeley are going to benefit me the rest of my life.

I would like to thank my advisor, Professor Borivoje Nikolić for his guidance, patience, and support during my stay at Berkeley. I also want to thank Professor Brodersen, Professor Gray, and Professor Wright for being in my qualifying examination committee and for their comments and feedbacks. I would like to thank Professors Nikolić, Brodersen, and Wright for reading my dissertation.

I am indebted to Yun Chiu for his mentoring and teachings about analog circuits. He provided me with intuition in analog circuits. In addition, I would like to thank Yun Chiu for designing the SHA, Johna Vanderhaegen for help in designing the pipelined ADC, Sebastian Hoyos for designing the clock generation circuits, Dusan Stepanovic for help in testing, Charles Chen for designing the PCB, Henry Chen for help with FPGA and Arnold Feldman for comments on the  $\Sigma\Delta$  ADC. I also want to thank Dr. Haideh Khorramabadi for her comments in our weekly meeting.

I would also like to thank all colleagues at the Berkeley Wireless Research Center and Cory Hall for their help and support. I learned so much from them during my stay at Berkeley. Especially, I would like to thank to students from Professor Nikolić's research group for their help, friendship, and funny jokes in my study. They all made my life at Berkeley easier and happier. Without them, my study would not be as successful. Furthermore, I will like to thank all my friends for their supports. I would like to thank faculty, and sponsors of the Berkeley Wireless Research Center, funding support from the National Science Foundation Infrastructure Grant No. 0403427, wafer fabrication donation of STMicroelectronics, and the support of the Center for Circuit & System Solutions (C2S2) Focus Center, one of the five research centers funded under the Focus Center Research Program, a Semiconductor Research Corporation program.

Finally, I would like to thank my parents for the support in the long journey of perusing a Ph.D. degree at Berkeley. I would also like to thank my love Elisa for her support, encouragement, and patience in the past few years. I am very glad and thankful to have her listening to my complaints in tough moments in my study.

### Chapter 1

### Introduction

#### 1.1 Motivation

With the advent of high performance digital signal processing systems, there is a constant increase in demand for high-resolution, high-speed analog-to-digital converters (ADCs). Besides resolution and speed, power consumption is another key metric in ADC design, especially in mobile applications. Pipelined analog-to-digital converter architecture provides a mean to achieve high-speed and high-precision simultaneously; however, high throughput and high resolution must be realized simultaneously [1]. The 1.5-b/stage architecture [2, 3] is widely used due to its low per stage complexity, large feedback factor for its residue amplifier and tolerance to comparator offset. Prominent analog impairments for ADCs include sampling capacitor mismatch, finite op-amp gain and switch charge injection errors [1–5]. As we are moving towards system-on-a-chip solution, ADCs have to be integrated on a single chip with digital circuits in deep sub-micron CMOS technology. Deep sub-micron CMOS technology poses immense challenge in ADCs design. First, the supply voltage is reduced. This results in reduction in signal swing and thus SNR. Low supply voltage also causes problem in designing high-gain amplifiers because there are small voltage headroom to cascode transistors. In addition, the intrinsic gain of transistor is reduced with scaling. Furthermore, there are no good matched capacitors in scaled digital CMOS as compared to dedicated analog process. A promising ADC architecture in scaled CMOS should be able to utilize faster transistors and abundant digital gates available in CMOS technology to mitigate errors from analog components and to improve ADC performance. In the past, numerous background calibration techniques [6–12] have been proposed to correct errors in pipelined ADCs.

#### 1.2 State-of-the-Art Calibrated ADCs

Calibration in ADCs is to measure errors introduced by analog circuit impairments and errors are compensated in either analog or digital domain. Background calibration performs the measurement and compensation without interrupting the normal operation of ADCs. Some existing background calibration algorithms are skip-and-fill [6, 7], using an extra pipeline stage [8], reference ADC to correct residue error [9], digital calibration with a slow-but-accurate ADC [10], adjusting reference voltages [11], and pseudo random number dithering method [12]. The algorithm used in [6, 7] is based on the concept of skipping conversion cycles randomly but filling in the data later by nonlinear interpolation. In [8], the calibration is done by employing an extra stage that is calibrated outside of the main converter's operation and periodically substituted for a stage within the main converter. [9] uses a slow-but-accurate ADC to correct the pipelined stage residue voltage error. [10] utilizes a slow calibrated algorithmic ADC to calibrate the linear gain error in the multiplying-DAC in the pipelined ADC. In [11], non-linearity caused by inter-stage gain error is compensated by adjusting the reference voltages of calibrated stages during the normal operation of the ADC. [12] relies on applying pseudo random number in the DAC to measure the gain error in the residue amplifier and then compensate the error in digital domain.

We propose a complete digital background calibration technique to achieve high conversion rate and high speed simultaneously without the need of both high-throughput and high-precision analog components. The proposed technique utilizes digital post-processing without tempering with the analog path. It is widely known that accuracy and speed of pipelined ADCs are limited by residue amplifiers. Since the calibration can correct for analog impairments such as analog component mismatch, signal-dependent amplifier finite-gain error, and switch charge injection, the residue amplifiers can be optimized for speed and power only by relaxing the gain requirement. Therefore, the proposed correction technique can be utilized to improve the effective conversion accuracy and conversion speed, and/or to reduce power consumption. Furthermore, the calibration runs in the background so that after the initial acquisition, the calibration algorithm can track temperature drift, supply variation, and device aging. Finally, the calibration is fully digital post-processing; it does not involve any altering of the analog path. Analog precision problems are translated into the complexity of digital signal-processing circuits, allowing this approach to benefit from CMOS device scaling in contrast to most conventional correction techniques.

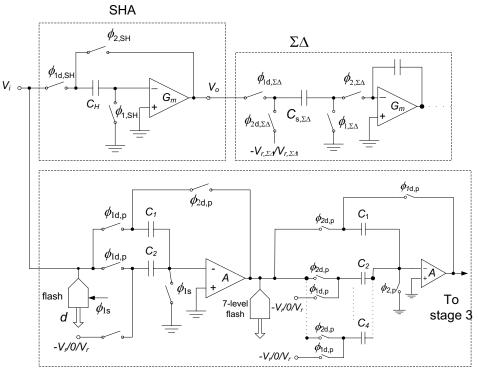

#### 1.3 Thesis Organization

The proposed background calibration algorithm is discussed in detail in Chapter 2. Then, high-resolution ADC techniques are reviewed in Chapter 3. Chapter 4 focuses on the design of sigma-delta ( $\Sigma\Delta$ ) ADC as a reference ADC for the proposed ADC architecture; Chapter 5 presents the circuit design of the sigma-delta ADC. Chapter 6 gives an overview of the dedicated sample-and-hold amplifier (SHA) for  $\Sigma\Delta$  ADC, while Chapter 7 presents the pipelined ADC design. Clock generation circuit is shown in Chapter 8. Layout, floor planning, and full-chip integration issues, are discussed in Chapter 9. Chapter 10 discusses the design and optimization of the least-mean-square (LMS) adaptive digital filter (ADF). Finally, measured results are presented in Chapter 11, and the conclusion is presented at the end.

### Chapter 2

# Fully Digital Background Calibration of Pipelined ADCs

#### 2.1 Introduction

Resolution of pipelined ADCs is limited by the accuracy of the DACs they employ. Traditionally, uncalibrated and untrimmed pipelined ADCs can achieve 10-b accuracy with careful design and layout techniques [4]. In order to achieve accuracy higher than 10-b, trimming or calibration is usually required. This chapter is intended to review some published ADC calibration techniques and to present a new background calibration technique for pipelined A/D converters.

#### 2.2 Overview of Pipelined ADCs

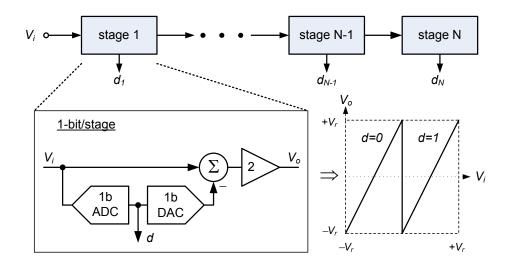

Pipelined ADCs convert analog signals to digital codes stage by stage; each pipeline stage makes a coarse decision and then passes the residue voltage to the subsequence stages for fine conversions. The residue voltage is usually gained to maintain good dynamic range for the subsequent stages. For a given resolution, the number of stages and the gain of the residue signal depend on the number of bits each stage is resolving. Although a complete conversion involves multiple steps, the throughput, with pipelining, is only determined by one stage delay but not the total delay of all stages because pipelining only introduces latency. Figure 2.1 shows a block diagram of a 1-b per stage pipelined ADC. Ideally, the final output code is given by

$$D_o = d_1 \cdot 2^{N-1} + d_2 \cdot 2^{N-2} + d_3 \cdot 2^{N-3} + \dots + d_{N-1} \cdot 2^1 + d_N \cdot 2^0$$

(2.1)

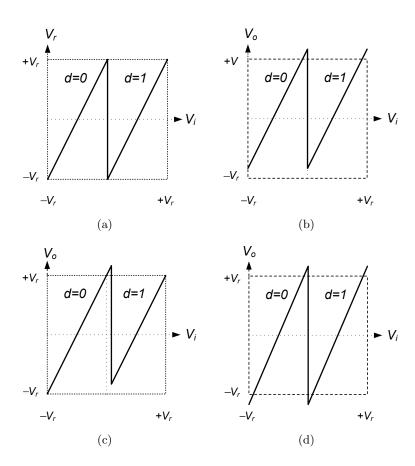

where  $d_N$  is the decision from N-th stage. The figure also illustrates the ideal residue voltage transfer function of a 1-b pipeline stage. However, analog circuit impairments cause the transfer function to differ from the ideal one shown in Figure 2.2 [13]. Figure 2.2(b) plots the residue amplifier transfer function with switch charge injection, while Figure 2.2(c) and (d) plot the transfer functions with comparator offset and capacitor mismatch respectively. Beside resolving one bit per stage, each stage can resolve more than one bit; the 1.5-b/stage architecture [2,3] is widely used due to its low per stage complexity, large feedback factor for its residue amplifier, and tolerance to comparator offset.

Figure 2.1: Ideal 1-b/stage pipelined ADC.

#### 2.3 Review of ADC Calibration Techniques

In addition to the front-end track-and-hold (T/H) bandwidth limitation given by a technology, prominent analog impairments for ADCs include sampling capacitor mismatch, finite op-amp gain, and switch charge injection errors [1–5]. Analog circuit techniques [8, 14–19] have been used to correct these imperfections. However, complicated circuits are typically used to alter the analog path, which in turn lowers the conversion speed. In addition, analog techniques do not benefit from the CMOS device scaling that has improved the performance of digital circuits tremendously in the past three decades and will continue to improve in the coming decade. Digital calibration techniques [6,7,9–13,20–30] have been used to correct ADC errors. Digital calibration can be further grouped into two categories, foreground [13, 20–22, 27] and background [6,7,9–12, 23–26, 28–30].

Digital foreground calibration usually involves measuring and storing the code error at major code transitions at system start-up and compensating afterward in digital domain during normal operation. One early example is [13]. In [13], the nominal gain

Figure 2.2: Residue amplifier transfer function: (a) ideal, (b) charge injection, (c) comparator offset, (d) capacitor mismatch.

of the residue amplifier is set to 1.93 (Figure 2.3) to ensure that the stage output does not over-range the subsequent stage because over-ranging problem cannot be corrected by digital post processing [13]. Assuming that the most significant bit (MSB) stage transfer function resembles that in the left of Figure 2.3, the overall transfer function of the ADC before calibration is the solid curve in the right side of Figure 2.3 provided that later stages are accurate. The missing codes cause the big jump in the ADC transfer function. In order to correct for the transition error,  $D_{\Delta}$  which is  $S_1 - S_2$  in digital form is first measured. If the current stage decision (D) is 0, the final ADC output  $(D_{out})$  is the code from rest of

Figure 2.3: Residue amplifier transfer function with reduced radix and correction idea.

the pipelined stages,  $D_{backend}$ . When D is 1,  $D_{out} = D_{backend} + D_{\Delta}$ . This is equivalent to moving the right section of the original ADC transfer function down as illustrated in dotted line in Figure 2.3. Thus, this method eliminates the big jump in the overall transfer curve. The same measurement technique can be applied to any stage from the least significant bit (LSB) stages to the most significant bit (MSB) stages if necessary. The measured codes are stored in memory and used to compensate for the errors during normal ADC operation. However, foreground calibration lacks tracking capability; therefore, it is sensitive to drift in temperature, voltage supply, and device aging. Background calibration, no matter digital or analog, calibrates ADCs continuously in the background during normal operation [6–12, 23–26, 28–30]; thus, it has the advantages of tracking temperature change, voltage supply variations, and device aging. [6,7] use skip-and-fill algorithm with nonlinear interpolation to allow the possibility of calibrating ADCs in the background synchronously with their normal operation. A conversion cycle is randomly chosen and skipped to free up a time slot for calibration. Then, the skipped conversion is filled in with nonlinear interpolation. The calibration is done by forcing a known reference signal at the ADC input and then the error in the gain stage is measured. The error codes are stored in a memory to be addressed during normal operation. The calibration is done stage by stage, from the LSB stage to the MSB stage. Due to the nature of skipping a conversion, the input signal is limited to below  $f_s/2$  where  $f_s$  is the sampling frequency of the ADC.

Instead of the skip-and-fill technique, [23] demonstrates a background calibration technique using a sample-and-hold queue to obtain time slots for calibration. A sampleand-hold (S/H) queue is placed in front of the ADC. Since the S/H queue is sampling at a slower rate than the ADC, the queue is empty after certain samples. When the queue is empty, the ADC following the queue is available for calibration. After one calibration cycle is completed, the ADC is switched back to convert the actual signal in the S/H. The same procedure repeats when the queue becomes empty again. The digital calibration is done by forcing the major transitions in the ADC transfer function to 1 LSB by an adaptive filter.

Another background calibration method utilizes an accurate-but-slow ADC [9,10] to correct for the errors in the ADC under calibration. [9] proposes using an accurate-butslow ADC to correct the pipelined ADC residue amplifier voltage using LMS adaptive algorithm. The calibration is done stage by stage, from the LSB stages to the MSB stages. [10] employs a LMS adaptive filter to find the weight of each 1.5-b stage simultaneously pipelined stage with the help of a calibrated algorithmic ADC. However, the signal-dependent gain error in the residue amplifier is not calibrated in these techniques.

Dithering based techniques are utilized in [12,24–26,28–31] to calibrate the residue amplifier gain error. The idea is based on injecting a pseudo random signal (PRS) [12,25, 26,28–30] which is uncorrelated to the input signal to the MDAC. The gain of the pseudo random signal through the residue amplifier can be obtained by examining output of the whole ADC with correlation technique. Since the regular signal experiences the same gain as the pseudo random signal, the gain error of the residue amplifier can be found and corrected in digital domain. In [24], the first stage residue amplifier has two transfer voltage functions; either one will allow the correct operation of the ADC. The two transfer functions of the residue amplifier is dithered to find the nonlinear gain error caused by the low gain op-amp.

All these calibration techniques have been proven to be insufficient because analog signal paths are always disturbed during calibration, independent of whether the calibration is performed in the foreground or background. Traditional calibration is performed stage by stage from the LSB stage to the MSB stage. Calibrated less significant stages are used to calibrate the more significant stages until the MSB stage is calibrated. The sequential calibration is very cumbersome to implement, because it often requires switching precision circuits between different stages during calibration. The penalty of such technique is either consumption of higher power or reduction of the conversion speed [6–8,13,20–23]. Dithering based algorithm reduces the usable signal range and the tolerance range of comparator offset error. In addition, it often requires additional technique to correct the capacitor mismatch [12]. Finally, most techniques do not correct for nonlinear op-amp gain error except for those in [24, 27, 31].

#### 2.4 Least-Mean-Square (LMS) Equalization Method

In contrast to traditional calibration techniques, a new calibration technique that treats analog impairments in analogy to distortion in communication channels can be employed to remove errors from all pipeline stages simultaneously using an adaptive digital filter. With this approach, the analog signal path is not disturbed during calibration and thus can maintain maximum conversion speed allowed by a certain technology. This approach is able to correct errors caused by capacitor mismatch, signal-dependent finite op-amp gain, and switch induced offset error. By relaxing requirements on precision matching and high open-loop op-amp gain, the new least-mean-square (LMS) calibration method can improve conversion accuracy and speed and can reduce power consumption.

#### 2.5 Code-Domain Filtering Approach

A description of the calibration technique is discussed in this section. First, we formulate the input-output relationship of a 1.5-b/stage residue amplifier in code-domain filtering form. Second, we show that the same analysis can be applied to a 2.5-b/stage. Third, the effect of signal-dependent op-amp gain in the 1.5-b/stage is also investigated. In the end, we demonstrate that an LMS filter can be used to correct the errors by using an accurate reference signal. This is an extension to the work report in [32].

Figure 2.4: Residue amplifier of a 1.5-b/stage pipelined ADC and its voltage transfer function.

### 2.5.1 Code-Domain Formulation of 1.5-b/Stage Pipelined ADC Architecture

Figure 2.5.1 shows the residue amplifier of a typical switched-capacitor 1.5-b pipeline ADC stage and its voltage transfer function curve. The residue voltage can be derived as [32]

$$V_o = \frac{V_i(C_1 + C_2) - (d - 1)V_rC_2 + V_{os}(C_1 + C_2 + C_x)}{C_1(1 + \frac{C_1 + C_2 + C_x}{AC_1})}.$$

(2.2)

where  $V_r$  is the reference voltage,  $C_x$  is the virtual ground parasitic capacitance,  $V_{os}$  is the offset voltage, A is the op-amp DC gain (constant), and d is the digital decision of the current stage. Specifically, d can either be 0, 1, or 2. The term  $\frac{C_1+C_2+C_x}{AC_1}$  is the error from the finite op-amp DC gain. After some manipulations and dividing the equation by the reference voltage  $V_r$  (given that  $D_i = \frac{V_i}{V_r}$ ,  $D_o = \frac{V_o}{V_r}$ , and  $D_{os} = \frac{V_{os}}{V_r}$ ), a purely digital

representation of (2.2) is obtained,

$$D_i(\frac{C_1+C_2}{C_1}) = D_o(1+\frac{C_1+C_2+C_x}{C_1}\frac{1}{A}) + (d-1)(\frac{C_2}{C_1}) - D_{os}(\frac{C_1+C_2+C_x}{C_1})$$

(2.3)

Equivalently, (2.3) can be rewritten as

$$D_i = D_o \alpha + (d-1)\beta - D_{os}\gamma \tag{2.4}$$

where

$$\begin{split} \alpha &= (\frac{C_1}{C_1+C_2})(1+\frac{C_1+C_2+C_x}{C_1}\frac{1}{A}),\\ \beta &= (\frac{C_2}{C_1+C_2}), \end{split}$$

and

$$\gamma = (\frac{C_1+C_2+C_x}{C_1+C_2}).$$

(2.4) represents a filter with taps  $\alpha$ ,  $\beta$ , and  $\gamma$ . For an ideal pipeline stage, the values of  $\alpha$  and  $\beta$  are 1/2, and the value of  $\gamma$  is 1. In reality, these coefficients are unknown due to capacitor mismatch, finite op-amp gain, and offset error.

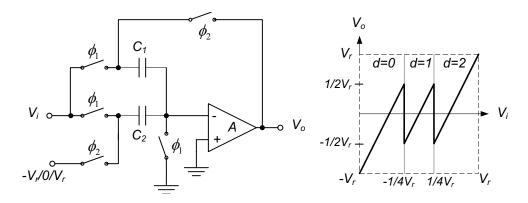

### 2.5.2 Code-Domain Formulation of 2.5-b/Stage Pipelined ADC Architecture

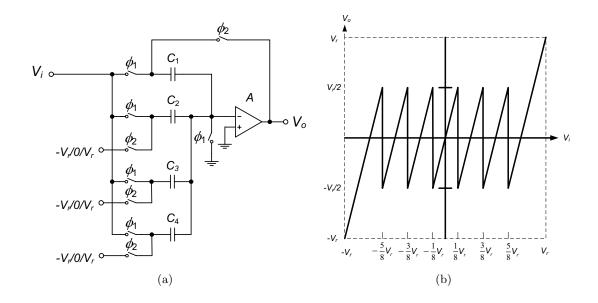

The above code-domain analysis can be further extended to a 2.5-b pipeline stage. Figure 2.5 illustrates the residue amplifier of a 2.5-b pipeline stage and its voltage transfer function. The decision of the stage is listed in Table 2.1. The residue voltage of the 2.5-

Figure 2.5: (a) Residue amplifier of a 2.5-b/stage pipelined architecture and (b) its voltage transfer function.

b/stage architecture can be derived as

$$V_{o} = \frac{1}{C_{1}\left(1 + \frac{C_{1} + C_{2} + C_{3} + C_{4} + C_{x}}{AC_{1}}\right)} \{V_{i}(C_{1} + C_{2} + C_{3} + C_{4}) - V_{r}[C_{2}a_{1} + C_{3}a_{2} + C_{4}a_{3}] + V_{os}(C_{1} + C_{2} + C_{3} + C_{4} + C_{x})\}$$

$$(2.5)$$

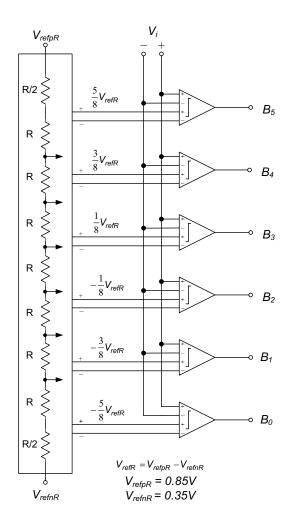

| Table 2.1: Decision of 2.5-b pipelined ADC stage | Table $2.1$ : | Decision | of | 2.5-b | pipelined | ADC | stage |

|--------------------------------------------------|---------------|----------|----|-------|-----------|-----|-------|

|--------------------------------------------------|---------------|----------|----|-------|-----------|-----|-------|

|                             | Stage decision |       |       |  |

|-----------------------------|----------------|-------|-------|--|

| Analog input                | $a_1$          | $a_2$ | $a_3$ |  |

| $-V_r \leq V_i < -5/8V_r$   | -1             | -1    | -1    |  |

| $-5/8V_r \le V_i < -3/8V_r$ | -1             | -1    | 0     |  |

| $-3/8V_r \le V_i < -1/8V_r$ | -1             | 0     | 0     |  |

| $-1/8V_r \le V_i < 1/8V_r$  | 0              | 0     | 0     |  |

| $1/8V_r \le V_i < 3/8V_r$   | 1              | 0     | 0     |  |

| $3/8V_r \le V_i < 5/8V_r$   | 1              | 1     | 0     |  |

| $5/8V_r \le V_i < V_r$      | 1              | 1     | 1     |  |

where  $V_r$  is the reference voltage,  $C_x$  is the virtual ground parasitic capacitance,  $V_{os}$  is the offset voltage, A is the op-amp DC gain (constant), and  $a_1$ ,  $a_2$ ,  $a_3$  are the digital decision of the current stage. Decisions  $a_1$ ,  $a_2$  and  $a_3$  determine whether  $C_2$ ,  $C_3$  and  $C_4$  should be connected to  $-V_r$ , 0 or  $V_r$  when  $\phi_2$  is high (amplifying phase). The term  $\frac{C_1+C_2+C_3+C_4+C_x}{AC_1}$  is the error from the finite op-amp DC gain. Similar to the 1.5-b case, after some manipulations and dividing the equation by  $V_r$  (given that  $D_i = \frac{V_i}{V_r}$ ,  $D_o = \frac{V_o}{V_r}$ , and  $D_{os} = \frac{V_{os}}{V_r}$ ), a purely digital representation of (2.5) is obtained,

$$D_{i}\left(\frac{C_{1}+C_{2}+C_{3}+C_{4}}{C_{1}}\right) = D_{o}\left(1 + \frac{C_{1}+C_{2}+C_{3}+C_{4}+C_{x}}{C_{1}}\frac{1}{A}\right) + a_{1}\left(\frac{C_{2}}{C_{1}}\right) + a_{2}\left(\frac{C_{3}}{C_{1}}\right) + a_{3}\left(\frac{C_{4}}{C_{1}}\right) - D_{os}\left(\frac{C_{1}+C_{2}+C_{3}+C_{4}+C_{x}}{C_{1}}\right)$$

$$(2.6)$$

Equivalently, (2.6) can be written as

$$D_i = D_o \alpha + [a_1 \ a_2 \ a_3] \cdot \vec{\beta} - D_{os} \gamma \tag{2.7}$$

where

$$\alpha = \left(\frac{C_1}{C_1 + C_2 + C_3 + C_4}\right)\left(1 + \frac{C_1 + C_2 + C_3 + C_4 + C_x}{C_1}\frac{1}{A}\right),$$

$$\vec{\beta} = \left[\beta_1 \ \beta_2 \ \beta_3\right] = \left[\frac{C_2}{C_1 + C_2 + C_3 + C_4} \ \frac{C_3}{C_1 + C_2 + C_3 + C_4} \ \frac{C_4}{C_1 + C_2 + C_3 + C_4}\right],$$

and

$$\gamma = (\frac{C_1 + C_2 + C_3 + C_4 + C_x}{C_1 + C_2 + C_3 + C_4}).$$

For an ideal 2.5-b pipeline stage, the values of  $\alpha$  and each entry of  $\vec{\beta}$  are 1/4, and the value of  $\gamma$  is 1. In reality, these coefficients are unknown due to capacitor mismatch, finite op-amp gain, and offset error.

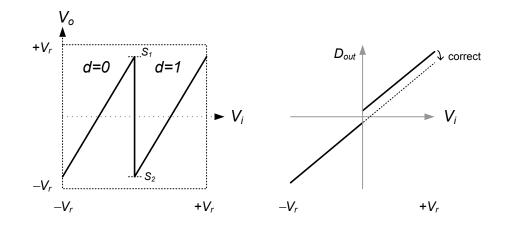

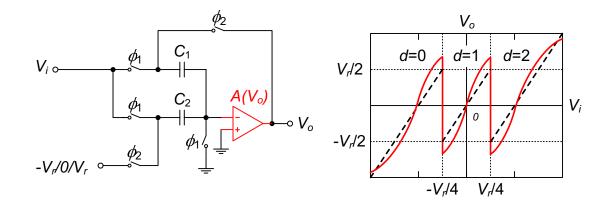

### 2.5.3 Code-Domain Formulation of Residue Amplifier with Nonlinear Amplifier Gain

We have shown the  $\operatorname{input}(D_i)$ - $\operatorname{output}(D_o)$  relationship of a residue amplifier with a linear amplifier DC voltage gain (A). However, the amplifier actual DC gain is nonlinear, i.e., signal dependent. We will show that we can also obtain an  $D_i$ - $D_o$  relationship in code-domain filtering form [33]. For simplicity, a 1.5-b/stage residue amplifier is used to illustrate the idea. Figure 2.6 shows the block diagram of a 1.5-b/stage residue amplifier and its voltage transfer function with nonlinear amplifier gain. Similar to the case with a linear amplifier gain in Section 2.5.1, the residue voltage of a 1.5-b/stage can be expressed as

$$V_o = \frac{V_i(C_1 + C_2) - (d - 1)V_rC_2 + V_{os}(C_1 + C_2 + C_x)}{C_1(1 + \frac{C_1 + C_2 + C_x}{A(V_o)C_1})}$$

(2.8)

where  $V_r$  is the reference voltage,  $C_x$  is the virtual ground parasitic capacitance,  $V_{os}$  is the offset voltage,  $A(V_o)$  is the signal-dependent op-amp DC gain, and d is the digital decision of the current stage. The term  $\frac{C_1+C_2+C_x}{A(V_o)C_1}$  is the error from the finite and nonlinear op-amp DC gain. Compare to (2.2), the only difference is that A is a function of  $V_o$ . After some manipulations and dividing the equation by  $V_r$  (given that  $D_i = \frac{V_i}{V_r}$ , and  $D_{os} = \frac{V_{os}}{V_r}$ ), a

purely digital representation of (2.8) is obtained,

$$D_i(\frac{C_1+C_2}{C_1}) = D_o(1+\frac{C_1+C_2+C_x}{C_1}\frac{1}{A(D_o)}) + (d-1)(\frac{C_2}{C_1}) - D_{os}(\frac{C_1+C_2+C_x}{C_1}).$$

(2.9)

Equivalently, (2.9) can be rewritten as

$$D_{i} = D_{o}\alpha_{1} + D_{o}^{2}\alpha_{2} + D_{o}^{3}\alpha_{3} + D_{o}^{4}\alpha_{4} + D_{o}^{5}\alpha_{5} + \dots$$

$$+ (d-1)\beta - D_{os}\gamma$$

(2.10)

where

$$\alpha_k = f_k(C_1, C_2, C_x, A(D_o)),$$

$$\beta = \left(\frac{C_2}{C_1 + C_2}\right),$$

and

$$\gamma = (\frac{C_1 + C_2 + C_x}{C_1 + C_2}).$$

The same analysis can be applied to 2.5-b/stage residue amplifier to derive the digital representation of the analog input voltage.

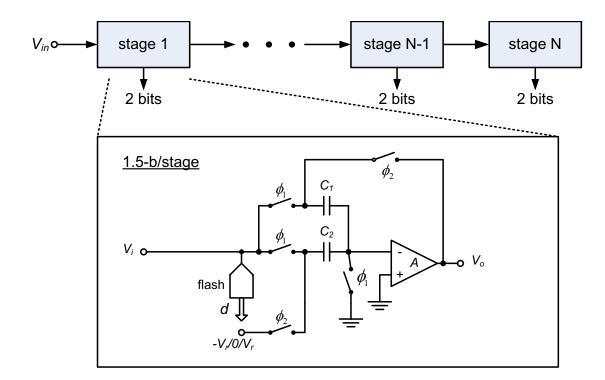

#### 2.5.4 Code-Domain Formulation of a Complete Pipelined ADC

After deriving the input $(D_i)$ -output $(D_o)$  relationship of a single residue amplifier, we are now going to show the input-output relationship of a complete pipelined ADC. A 1.5-b/stage pipelined ADC is shown in Figure 2.7. Using (2.4), we obtain  $D_i$  of each

Figure 2.6: Residue amplifier of a 1.5-b/stage pipelined ADC with nonlinear-amplifier gain and its voltage transfer function (solid line).

stage [32],

$$D_{i,1} = D_{o,1}\alpha_1 + (d_1 - 1)\beta_1 - D_{os,1}\gamma_1$$

(2.11)

$$D_{i,2} = D_{o,2}\alpha_2 + (d_2 - 1)\beta_2 - D_{os,2}\gamma_2$$

(2.12)

$$D_{i,3} = D_{o,3}\alpha_3 + (d_3 - 1)\beta_3 - D_{os,3}\gamma_3 \tag{2.13}$$

$$D_{i,N} = D_{o,N} \alpha_N + (d_N - 1)\beta_N - D_{os,N} \gamma_N.$$

(2.14)

Since  $D_{o,N} = D_{i,N+1}$ , the digital representation of the input signal can be derived recursively as

$$D_{in} = D_{i,1} = [[(..)\alpha_3 + (d_3 - 1)\beta_3 - D_{os,3}\gamma_3)]\alpha_2 + (d_2 - 1)\beta_2 - D_{os,2}\gamma_2]\alpha_1 + (d_1 - 1)\beta_1 - D_{os,1}\gamma_1.$$

(2.15)

Figure 2.7: Block diagram of a multi-stage 1.5-b/stage pipelined ADC.

Equivalently, (2.15) can be written as

$$D_{in} = A + B + \Gamma \tag{2.16}$$

where

$$\begin{split} A &= ((d_1 - 1)\beta_1 + (d_2 - 1)\beta_2\alpha_1 + (d_3 - 1)\beta_3\alpha_2\alpha_1 + \dots + (d_N - 1)\beta_N\alpha_{N-1}\alpha_{N-2}...\alpha_1 \\ &= \sum_{k=1}^N (d_k - 1)f_k \\ B &= D_{o,N}\alpha_N\alpha_{N-1}...\alpha_2\alpha_1 = D_{o,N}\prod_{k=1}^N \alpha_k, \\ \Gamma &= -D_{os,1}\gamma_1 - D_{os,2}\gamma_2\alpha_1 - D_{os,3}\gamma_3\alpha_2\alpha_1 - \dots - D_{os,N}\gamma_N\alpha_{N-1}\alpha_{N-2}...\alpha_1. \end{split}$$

Figure 2.8: Error correction of pipelined ADC: code-domain nonlinear channel equalizer.

(2.16) formulates a filter in code-domain. A, B, and  $\Gamma$  are the weighed sum of digital output of each pipelined stage, quantization error, and the total input-referred offset respectively.  $D_{in}$  with signal-dependent op-amp gain can be derived in the same fashion using (2.10) and the method presented in this subsection. The same method can also be extended to 2.5-b per stage using (2.7).

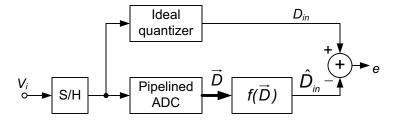

#### 2.5.5 Code-Domain Filtering Technique System Architecture

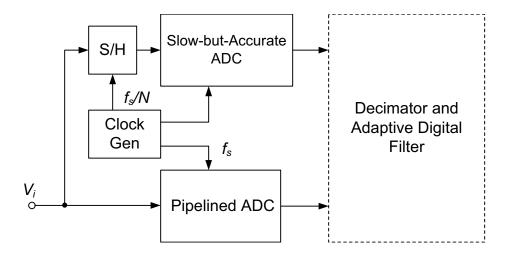

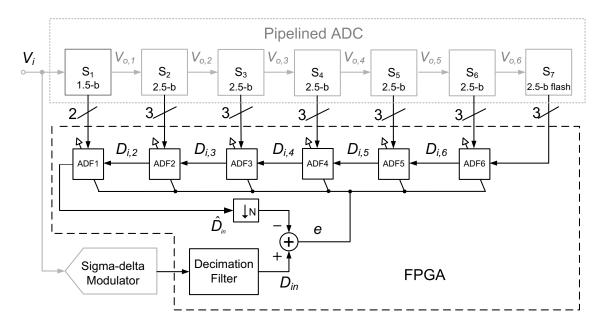

Although, the tap values in (2.16) are, in reality, unknown due to capacitor mismatch, finite op-amp gain, and offset error, an adaptive technique can be applied to obtain the tap values. This problem can be treated similar to a channel equalization problem as illustrated in 2.8. An ideal qualifier is used to train the filter taps in this case. This leads to an adaptive background calibration scheme using the steepest decent gradient method as shown in Figure 2.9. The output vector  $\vec{D}$  of a high-speed, inaccurate pipelined ADC is decimated and applied to the adaptive digital filter, while a slow-but-accurate A/D converter is used to obtain the ideal value of  $D_{in}$ . Least-mean-square (LMS) algorithm is used to update the filter taps at the speed of the slow-but-accurate A/D converter.

Figure 2.9: Error correction of pipelined ADC: code-domain LMS adaptive equalizer.

### 2.6 Behavioral Simulations

To demonstrate the effectiveness of the scheme, a behavioral model (Figure 2.9) is developed to simulate the LMS calibration scheme. Using this technique, the gain requirement of amplifiers can be greatly reduced; thus, simple and inherently fast amplifiers can be used to increase ADC conversion speed. The pipelined ADC, the reference ADC, and the LMS adaptive filter are modeled using Simulink® blocks [34]. To reduce the simulation time, no decimation is performed, i.e., LMS adaption is running at the sampling rate of the pipelined ADC. Since the target accuracy of the calibrated ADC is 12-b, an ideal 14-b ADC is used as the slow-but-accurate reference ADC. The pipelined ADC has (12 + 2) raw output bits; the extra two bits is used for calibration and ensures that the final quantization error(2.15) is below one LSB (12 bits). The pipelined ADC model includes analog circuit non-idealities such as capacitor mismatch, small and nonlinear amplifier gain, comparator offset, and amplifier offset.

#### 2.6.1 Simulation Results

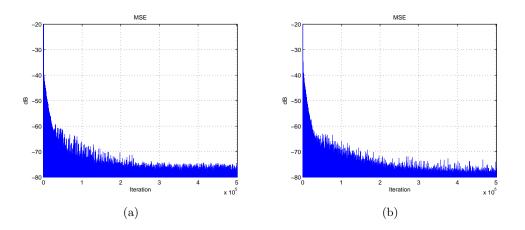

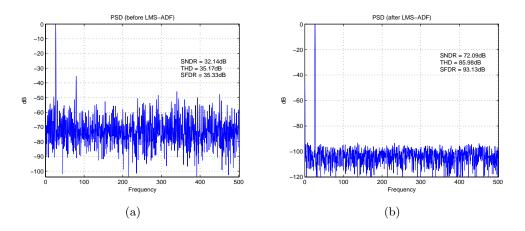

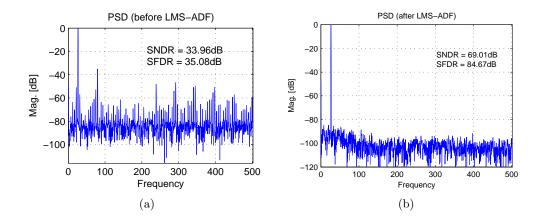

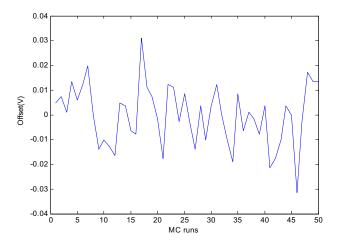

As an example, the first stage of the pipelined ADC employs 1.5-b/stage architecture, while stage 2 to stage 7 employ 2.5-bit/stage architecture. In the LMS filter, additional taps are used to correct signal-dependent op-amp gain up to fifth-order as explained in Section 2.5.3. Despite of the described pipelined ADC architecture is used, the LMS calibration algorithm is valid in any pipelined ADC architecture with inter-stage redundancy. The initial parameter settings are listed in Table 2.2. The op-amp gain for the simulation is also in illustrated in Figure 2.10. The capacitor mismatch errors are first examined. The input signal of the simulation is a sine wave with an amplitude equal to the pipelined ADC reference voltage,  $V_r$ . The sampling capacitors are set as listed in Table 2.2, but all other parameters are ideal. The smallest step size is  $2^{-29}$ . The learning curve is shown in Figure 2.11(a). The mean-square-error (MSE) converges to below -70dB after 500,000 iterations. The amplifier gain effect is the next impairment examined. The nonlinear amplifier gain is modeled as a power series up to fifth order. A typical amplifier gain transfer function shown in Figure 2.10 is used in the behavioral simulations. Again, other parameters are set to ideal values. The learning curve is shown in Figure 2.11(b). Finally, all the static error sources are included in the simulation (Table 2.2 and Figure 2.10). The learning curve and the convergence of filter taps are shown in Figure 2.11(c) and Figure 2.11(d), respectively. Figure 2.12 shows the INL and DNL of the ADC before and after calibration. Although a sine wave input is used in the above simulations, we found in simulation that input signal statistics have little effect on the convergence rate of the adaptive LMS filter. The learning curve with saw-tooth and random inputs are shown in Figure 2.13. Compared to the one

Figure 2.10: Gain transfer function of a typical amplifier.

| Pipelined<br>stage | Sampling Cap<br>mismatch | Op-amp<br>input-referred<br>offset | Comparator<br>offset | Comparator<br>noise | $C_x/C_1$ |

|--------------------|--------------------------|------------------------------------|----------------------|---------------------|-----------|

| 1(1.5-b)           | 5%                       | $10\% V_r(3\sigma)$                | $10\% V_r(3\sigma)$  | $1\% V_r(3\sigma)$  | 30%       |

| 2-7(2.5-b)         | 5%                       | $10\% V_r(3\sigma)$                | $10\% V_r(3\sigma)$  | $1\% V_r(3\sigma)$  | 30%       |

Table 2.2: Circuit parameters of the pipelined ADC used in behavioral simulations.

with sine wave input (Figure 2.11), the difference is very negligible. Figure 2.14 shows the FFT plot of a sine wave input before and after calibration. The SNR improves from 32 dB to 72 dB and the SFDR improves from 35 dB to 93 dB. Although an ideal 14-b reference ADC is used here, simulation shows that random noise at the 14-b reference ADC output has small effect on the effectiveness of the calibration because the random noise is averaged in the LMS filter. Figure 2.15 shows the PSD of the ADC before and after calibration when the reference ADC only has an SNR of 9 bits but more than 16-bit SFDR. We can achieve close to 12-b SNR after calibration; thus, achieving high-linearity of the reference ADC is

Figure 2.11: Learning curve for (a) capacitor mismatch, (b) nonlinear amplifier gain, (c) all combined errors, (d) filter tap values.

Figure 2.12: (a) DNL before calibration, (b) INL after calibration, (c) INL before calibration, (d) DNL after calibration.

Figure 2.13: Learning curve of (a) saw-tooth, (b) random signal

Figure 2.14: (a) FFT plot before calibration, (b) FFT plot after calibration.

most important.

#### 2.6.2 Performance Analysis

In Section 2.5, we formulated a code-domain adaptive filter that compensates linear and nonlinear errors of pipelined ADCs. This code-domain is unique to pipelined ADCs due to the built-in redundancy of the decisions levels. Instead of giving a thorough treatment of performance analysis, a few observations are summarized below [32]:

Figure 2.15: Calibration with a noisy reference ADC: (a) FFT plot before calibration, (b) FFT plot after calibration.

#### Steady-State MSE

When op-amp nonlinearity is excluded, the filtering formulation derived in (2.16) is exact. This indicates that memoryless errors can be fully removed when quantization noise is negligible(noise enhancement will be covered in the next part). This argument is justified by behavioral simulations: steady state MSE close to 12 bits is constantly achieved in spite of the presence of various other errors in the ADC. The MSE is also a function of the step size  $\mu$ ; a gear-shifting algorithm can be used to further reduce MSE in the steady state.

#### Noise Enhancement

It is widely known in communication theory that linear equalization (LE) suffers from a noise enhancement problem when the power spectrum of the input signal is not flat [35]. It is difficult to quantify the noise enhancement effect of the proposed calibration algorithm as the concept "frequency" in code-domain is not well understood. However, we point out the following case where quantization noise is enhanced due to equalization: if many output codes are missing, i.e., all  $\alpha_k$  in (2.16) are substantially larger than 1/2, the second term in (2.16) which is normally the quantization noise will be greatly magnified. This happens when capacitor mismatch or finite op-amp gain effect is severe. A code density test reveals nulls in the statistics (DNL in Figure 2.12). This may serve as an intuition for the non-flatness of the "spectrum". The remedy to this problem is to increase the word length of the raw code, i.e., to add more stages. This occurs with low overhead of power consumption since an optimum pipelined design often employs stage scaling where power consumption is dominated by the MSB stages.

#### Singularity