# **Power-Performance Tradeoffs in ASICs for Next Generation Wireless Communication Datapaths**

Farhana Sheikh

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-93 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-93.html

August 14, 2008

Copyright 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Power-Performance Tradeoffs In ASICs for Next Generation Wireless Communication Datapaths

by

Farhana Sheikh

B.Eng. (Carleton University, Canada) 1993 M.S. (University of California, Berkeley) 1996

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

#### GRADUATE DIVISION

of the

#### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Andreas Kuehlmann Professor Paul Wright

Fall 2008

The dissertation of Farhana Sheikh is approved.

Chair

Date

Date

Date

University of California, Berkeley Fall 2008

### Power-Performance Tradeoffs In ASICs for Next Generation Wireless Communication Datapaths

Copyright © 2008

by

Farhana Sheikh

#### Abstract

### Power-Performance Tradeoffs In ASICs for Next Generation Wireless Communication Datapaths

by

Farhana Sheikh

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

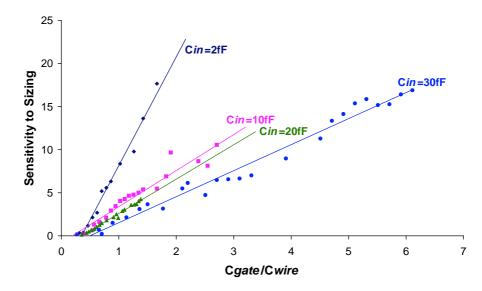

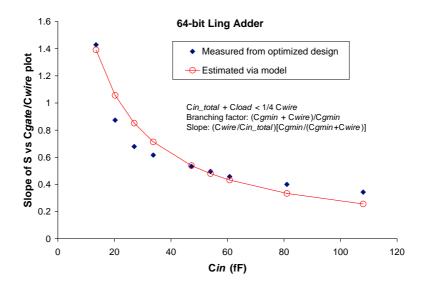

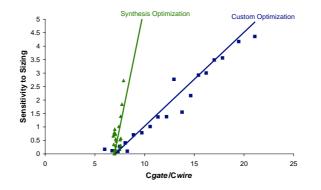

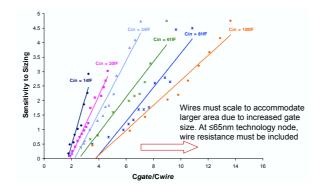

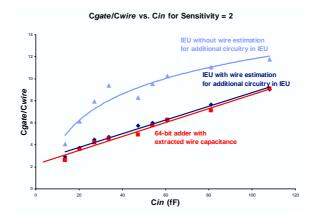

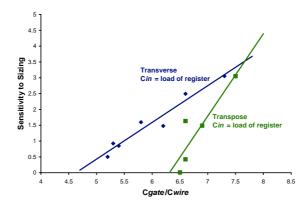

New design methodologies that quickly and systematically explore power-performance tradeoffs between architectures and design variables at each level of design abstraction can enable design innovation and reduce design cost and design time. This dissertation proposes a novel digital design methodology that systematically evaluates power-performance tradeoffs at each level of design hierarchy in the context of constraints from lower levels of design abstraction. It is a holistic approach that uses sensitivity information, which allows designers to systematically and rapidly traverse a vast design tradeoff space, leading to power-performance optimal architectures and enabling short design times. Little formalism has been built around some of the earlier published works that have proposed sensitivitybased design methodologies. This dissertation formalizes the methodology in an optimization framework and algorithm. The framework is conceived using a previously published custom circuit optimizer for power-performance optimization at the leaf cell. The viability of using physical circuit parameters to estimate sensitivity is investigated and shown to be instrumental in reducing design time required to uncover power-performance optimal architectures. A linear relationship between  $C_{gate}/C_{wire}$  and sensitivity to gate sizing is uncovered. This first-order linear estimator mitigates the need to calculate derivatives or run large circuit simulations. The use of composition rules is investigated to enable fast generation of energy-delay curves for larger circuit blocks comprised of smaller leaf cells. Energy-efficiency curves are generated for multiple architectures within short periods of time, allowing rapid evaluation of architectures in the context of lower level design constraints and tuning variables such as circuit sizing. The composition process is formalized into an algorithm that can be implemented as a convex optimization program. This provides an automated mechanism for fast design space exploration at architecture, micro-architecture and circuit levels. A digital FIR kernel for use in multi-mode, multi-standard radio transceiver is optimized using the design methodology.

> Professor Borivoje Nikolić Dissertation Committee Chair

To my parents – Asrar and Parveen; my siblings – Fahim and Samia; and my husband – Iftikhar

## Contents

| C             | onter | ii               |                                              |    |  |  |  |

|---------------|-------|------------------|----------------------------------------------|----|--|--|--|

| Li            | st of | st of Figures vi |                                              |    |  |  |  |

| $\mathbf{Li}$ | st of | t of Tables x    |                                              |    |  |  |  |

| A             | ckno  | wledge           | ements                                       | xi |  |  |  |

| 1             | Intr  | oduct            | ion                                          | 1  |  |  |  |

|               | 1.1   | Next             | Generation Mobile Systems                    | 4  |  |  |  |

|               | 1.2   | Techn            | ology Scaling                                | 7  |  |  |  |

|               | 1.3   | Energ            | y-Efficient System Design                    | 10 |  |  |  |

|               | 1.4   | Sensit           | ivity-Based Circuit Optimization             | 12 |  |  |  |

|               |       | 1.4.1            | Limitations of prior work                    | 13 |  |  |  |

|               | 1.5   | Resea            | rch Scope                                    | 13 |  |  |  |

|               | 1.6   | Disser           | tation Overview                              | 14 |  |  |  |

| <b>2</b>      | Pov   | ver-Pe           | rformance Optimization                       | 16 |  |  |  |

|               | 2.1   | Gradi            | ent-Based Optimization                       | 18 |  |  |  |

|               |       | 2.1.1            | Modeling of Optimization Problems            | 19 |  |  |  |

|               |       | 2.1.2            | Convex Sets and Convex Functions             | 20 |  |  |  |

|               |       | 2.1.3            | Gradients and Iterative Optimization Methods | 22 |  |  |  |

|               |       | 2.1.4            | Lagrangian Theory and Methods                | 24 |  |  |  |

|               |       | 2.1.5            | Convex Optimization                          | 27 |  |  |  |

|               |       | 2.1.6            | Interior Point Iterative Methods             | 28 |  |  |  |

|               |       | 2.1.7            | Geometric Programs                           | 30 |  |  |  |

|   | 2.2 | Discre             | te Optimization                                                                                                           | 1 |

|---|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------|---|

|   |     | 2.2.1              | Branch and Bound                                                                                                          | 2 |

|   |     | 2.2.2              | Approximation Algorithms                                                                                                  | 3 |

|   | 2.3 | Gradie             | ents, Sensitivity, and Optimality 3                                                                                       | 4 |

|   |     | 2.3.1              | Sensitivity and Design Hierarchy                                                                                          | 8 |

|   | 2.4 | Sensiti            | ivity-Based Design Methodology                                                                                            | 4 |

|   | 2.5 | Summ               | ary                                                                                                                       | 6 |

| 3 | Hie | rarchio            | cal Power-Performance Optimization 4                                                                                      | 8 |

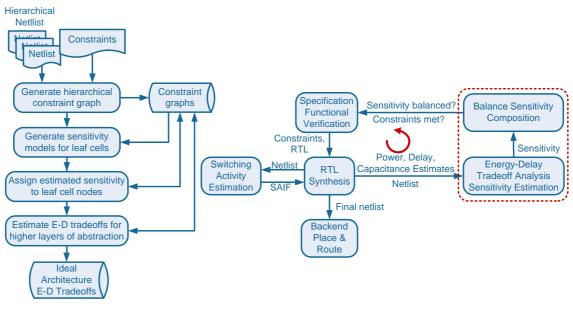

|   | 3.1 | Design             | Methodology Overview                                                                                                      | 3 |

|   | 3.2 | Fast A             | rchitecture Exploration                                                                                                   | 5 |

|   |     | 3.2.1              | Design Composition                                                                                                        | 6 |

|   | 3.3 | Sensiti            | ivity Balancing Across Layers of Hierarchy                                                                                | 1 |

|   | 3.4 | Steps <sup>•</sup> | to Automation                                                                                                             | 2 |

|   |     | 3.4.1              | Data Structures                                                                                                           | 2 |

|   |     | 3.4.2              | Constraint Generation and Propagation                                                                                     | 5 |

|   |     | 3.4.3              | Sensitivity Balancing Formulations                                                                                        | 6 |

|   | 3.5 |                    | ivity Approximation Using Interior Point                                                                                  |   |

|   |     | _                  | thms $\dots \dots \dots$  |   |

|   |     | 3.5.1              | Saturation of Sensitivity and Variable Bounds                                                                             |   |

|   | 3.6 |                    | $tions \dots \dots$ |   |

|   | 3.7 | Summ               | ary                                                                                                                       | 5 |

| 4 | Mo  | dels an            | ad Constraints 7                                                                                                          | 6 |

|   | 4.1 | Analy              | tical Delay, Energy, and Area Models                                                                                      | 7 |

|   |     | 4.1.1              | Delay                                                                                                                     | 7 |

|   |     | 4.1.2              | Energy                                                                                                                    | 8 |

|   |     | 4.1.3              | Area                                                                                                                      | 0 |

|   | 4.2 | Constr             | rained Optimization                                                                                                       | 0 |

|   | 4.3 | Tabula             | ated Models                                                                                                               | 2 |

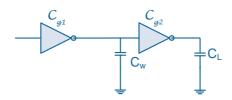

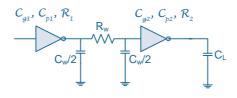

|   | 4.4 | Wire (             | Capacitance and Wire Resistance                                                                                           | 4 |

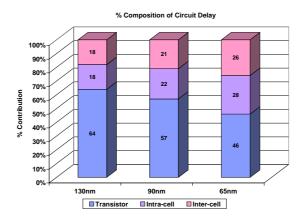

|   |     | 4.4.1              | Effect of Interconnect on Delay                                                                                           | 4 |

|   |     | 4.4.2              | Effect of Interconnect on Energy and Area                                                                                 | 6 |

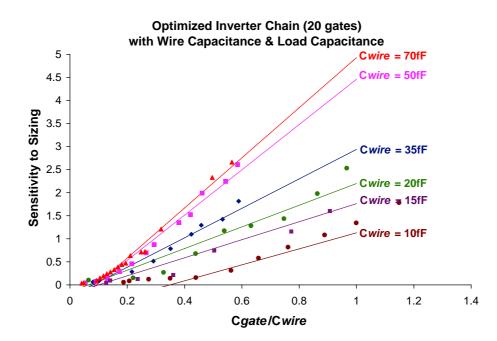

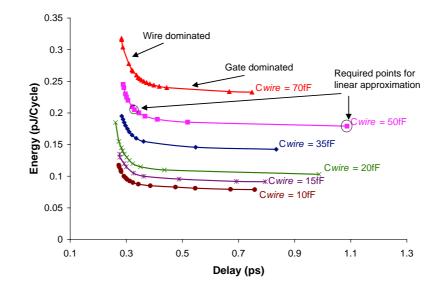

|   |     | 4.4.3              | Effect of Interconnect on Sensitivity and Architecture Selection 8                                                        | 8 |

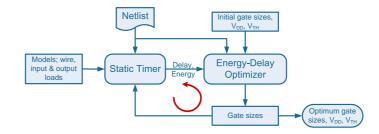

|          | 4.5 | Extension to Supply Voltage and Threshold Voltage<br>Optimization                                                                           | 1 |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|---|

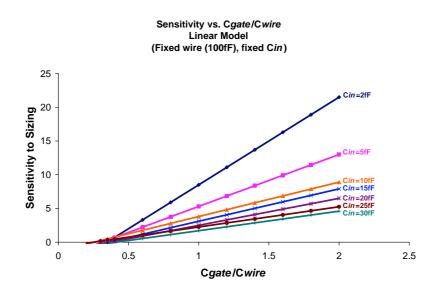

|          | 4.6 | Analytical Models for Sensitivity                                                                                                           | 2 |

|          |     | 4.6.1 Sensitivity to Sizing                                                                                                                 | 3 |

|          |     | 4.6.2 Sensitivity to Supply and Threshold Voltage                                                                                           | 4 |

|          | 4.7 | Design Composition                                                                                                                          | 5 |

|          |     | 4.7.1 Delay                                                                                                                                 | 6 |

|          |     | 4.7.2 Energy                                                                                                                                | 8 |

|          | 4.8 | Summary                                                                                                                                     | 8 |

| <b>5</b> | Sen | sitivity to Sizing 10                                                                                                                       | 0 |

|          | 5.1 | Introduction                                                                                                                                | 0 |

|          |     | 5.1.1 Constrained Circuit Sizing                                                                                                            | 1 |

|          |     | 5.1.2 Chapter Overview $\ldots \ldots 10$ | 3 |

|          | 5.2 | Gradient-Based Circuit Sizing                                                                                                               | 4 |

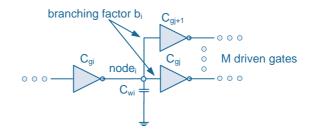

|          | 5.3 | Gate Capacitance, Wire Capacitance, and Sensitivity                                                                                         | 6 |

|          |     | 5.3.1 Analytical Derivation of Sensitivity to Sizing                                                                                        | 7 |

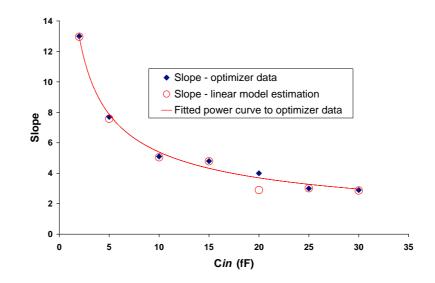

|          |     | 5.3.2 Numerical Approach to Modeling Sensitivity to Sizing                                                                                  | 4 |

|          | 5.4 | Inverter Chain                                                                                                                              | 5 |

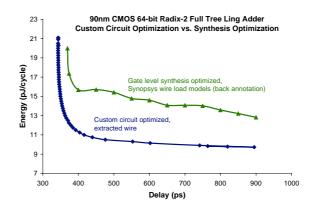

|          | 5.5 | $64-bit Ling Adder \dots \dots$       | 3 |

|          |     | 5.5.1 Synthesis-based Adder Optimization                                                                                                    | 5 |

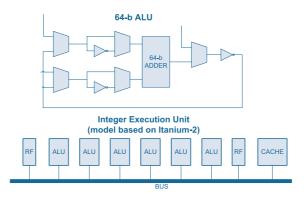

|          | 5.6 | Integer Execution Unit                                                                                                                      | 7 |

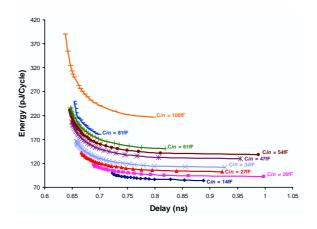

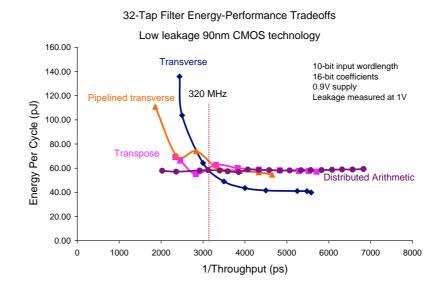

|          | 5.7 | Finite Impulse Response Filter    13                                                                                                        | 0 |

|          | 5.8 | Model Limitations                                                                                                                           | 0 |

|          | 5.9 | Summary                                                                                                                                     | 1 |

| 6        | Arc | chitecture Optimization of Multi-Standard Radio FIR 13                                                                                      | 3 |

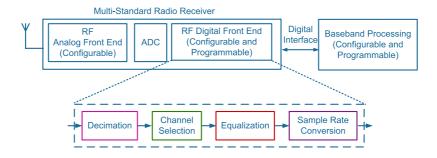

|          | 6.1 | Digital Front-End FIR Requirements                                                                                                          | 5 |

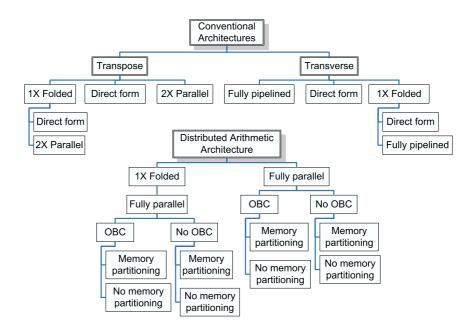

|          | 6.2 | Design Tradeoff Space                                                                                                                       | 6 |

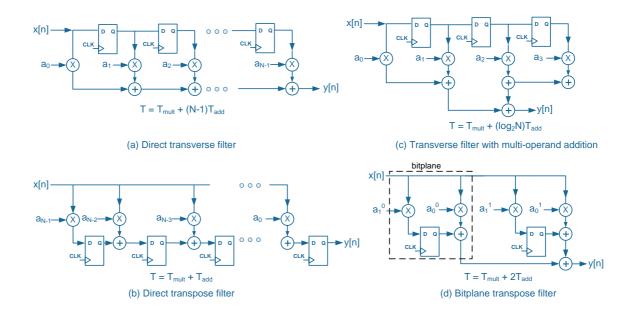

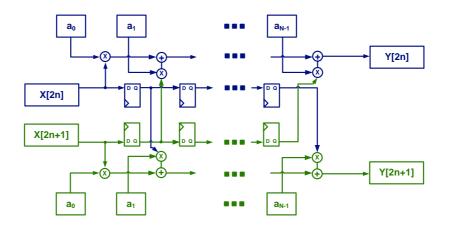

|          |     | 6.2.1 Architecture Tradeoffs                                                                                                                | 7 |

|          |     | 6.2.2 Micro-Architecture Tradeoffs                                                                                                          | 2 |

|          |     | 6.2.3 Logic and Arithmetic Tradeoffs                                                                                                        | 3 |

|          |     | 6.2.4 Circuit and Technology Tradeoffs                                                                                                      | 5 |

|          | 6.3 | Flexible Filter Design Exploration                                                                                                          | 5 |

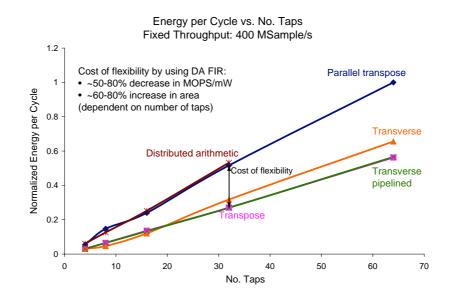

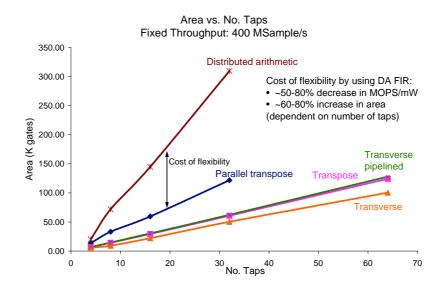

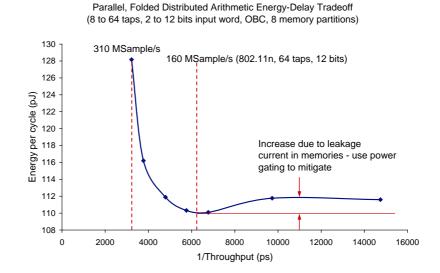

|                | 6.3.1                                                                               | Design Space Exploration                                                                                                                                                                                                                                                                           | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 6.3.2                                                                               | Architectures                                                                                                                                                                                                                                                                                      | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

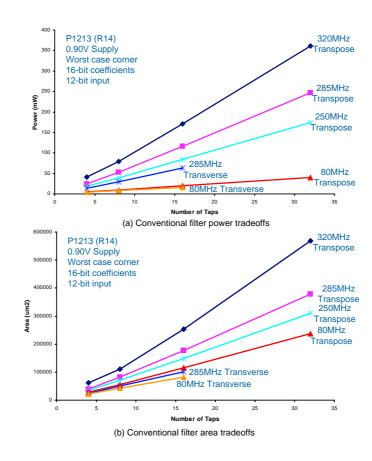

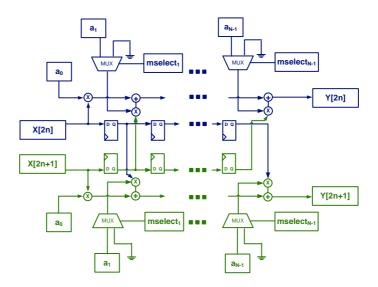

|                | 6.3.3                                                                               | Flexible Conventional Architectures                                                                                                                                                                                                                                                                | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

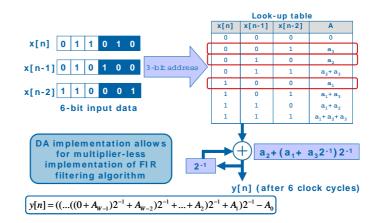

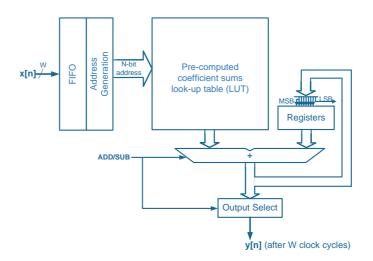

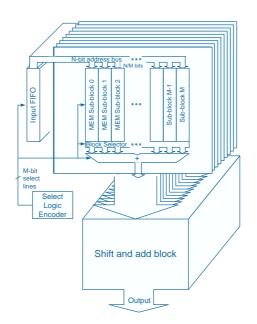

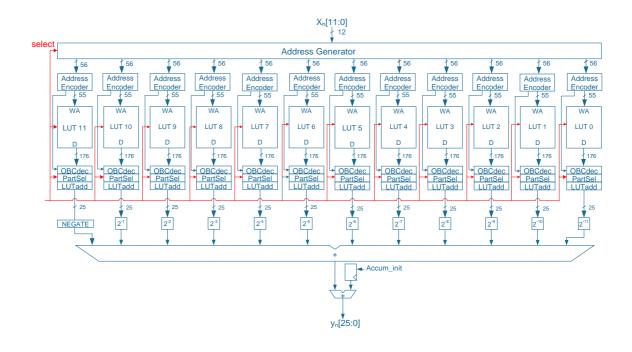

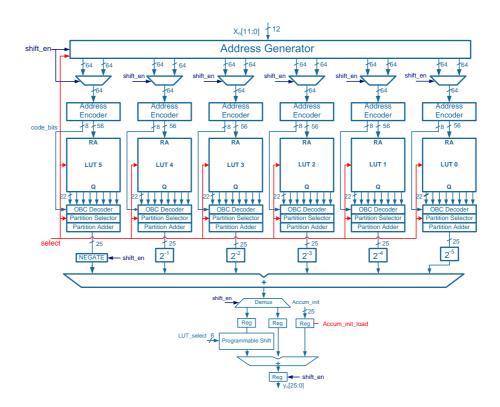

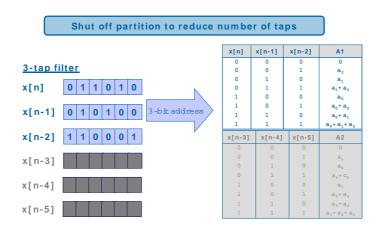

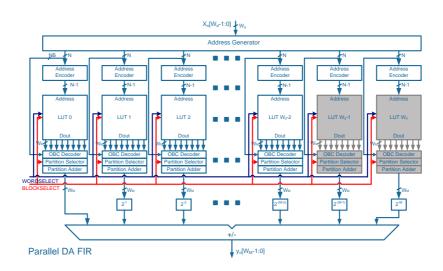

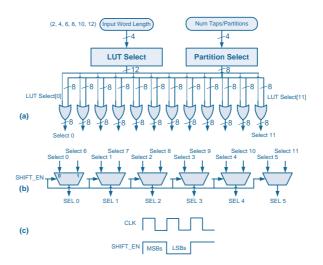

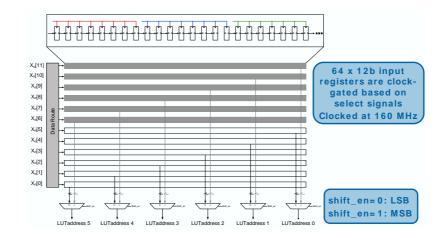

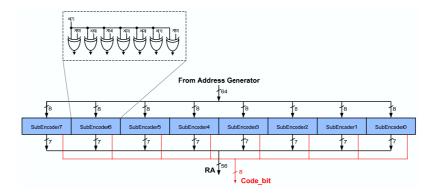

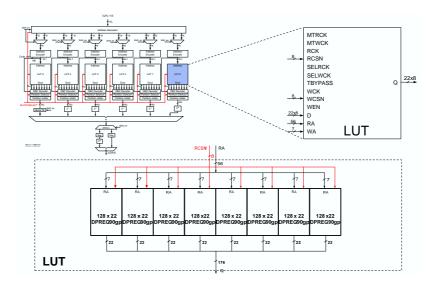

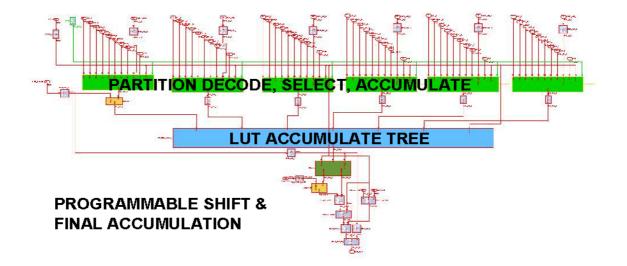

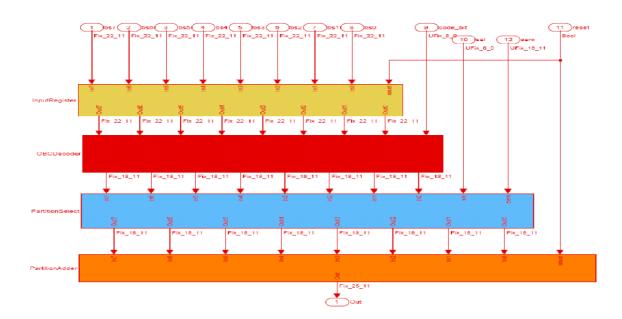

|                | 6.3.4                                                                               | Flexible Distributed Arithmetic Architecture                                                                                                                                                                                                                                                       | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

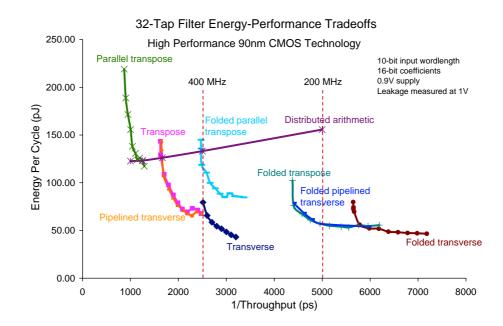

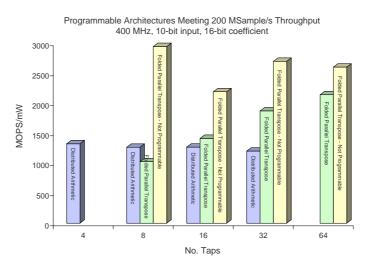

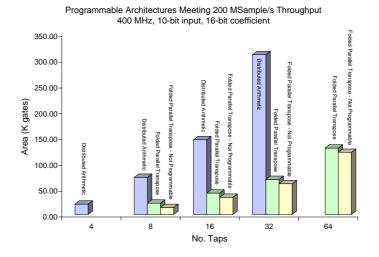

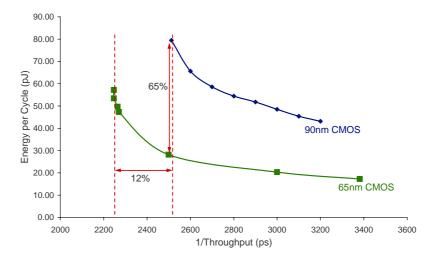

| 6.4            | Flexib                                                                              | ble Digital Filters – High Performance Technologies                                                                                                                                                                                                                                                | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                | 6.4.1                                                                               | Results                                                                                                                                                                                                                                                                                            | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                | 6.4.2                                                                               | Sensitivity Analysis                                                                                                                                                                                                                                                                               | 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                | 6.4.3                                                                               | Optimized Filter Description                                                                                                                                                                                                                                                                       | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                | 6.4.4                                                                               | Cost of Flexibility                                                                                                                                                                                                                                                                                | 168                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.5            | Flexib                                                                              | ole Digital Filters – Low Leakage Technology                                                                                                                                                                                                                                                       | 169                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

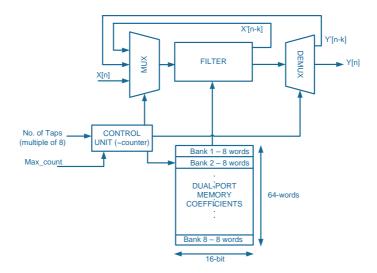

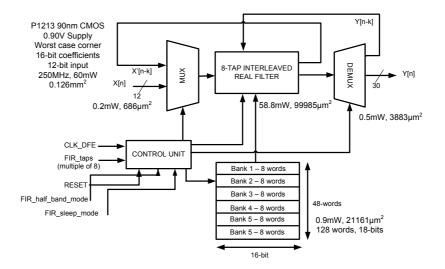

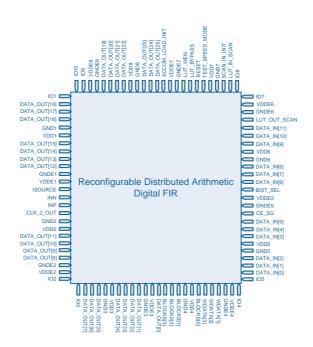

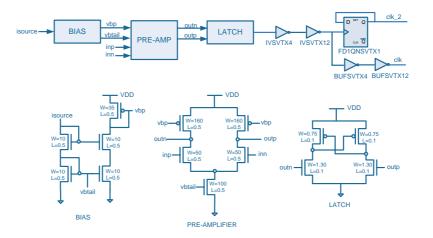

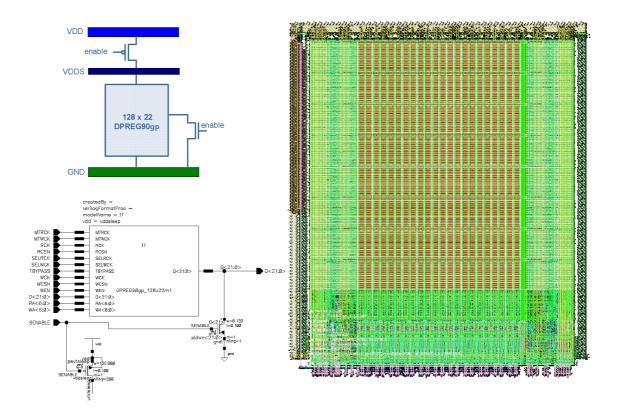

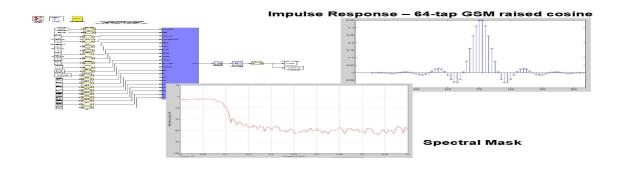

| 6.6            | Distri                                                                              | buted Arithmetic Digital FIR Prototype                                                                                                                                                                                                                                                             | 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

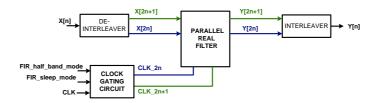

|                | 6.6.1                                                                               | Filter Overview and Specifications                                                                                                                                                                                                                                                                 | 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

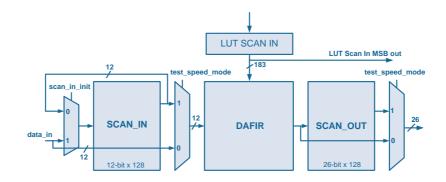

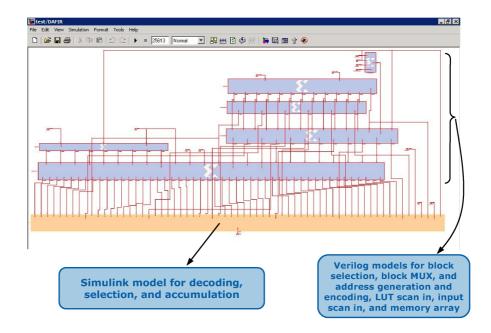

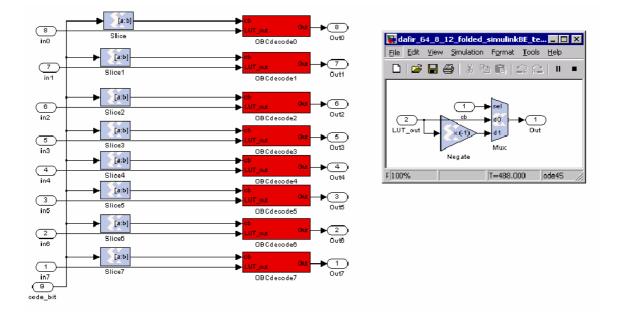

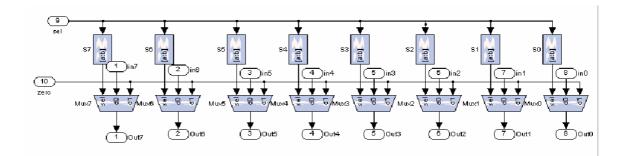

|                | 6.6.2                                                                               | RTL and Simulink Modeling                                                                                                                                                                                                                                                                          | 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

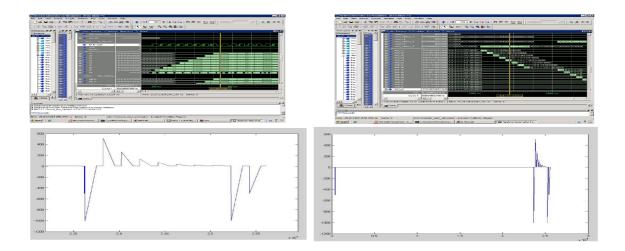

|                | 6.6.3                                                                               | Functional Verification                                                                                                                                                                                                                                                                            | 178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

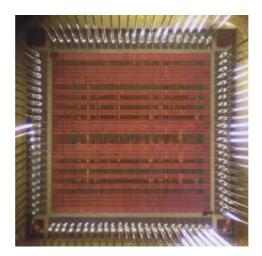

|                | 6.6.4                                                                               | Silicon Implementation and Verification                                                                                                                                                                                                                                                            | 179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

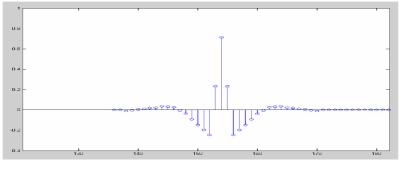

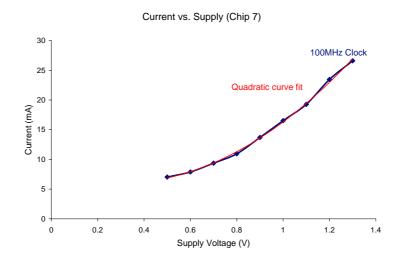

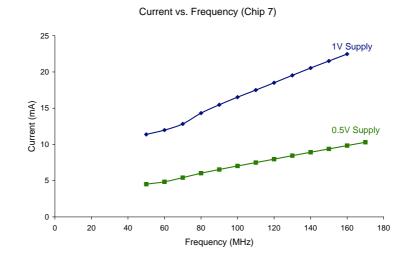

|                | 6.6.5                                                                               | Measured Results                                                                                                                                                                                                                                                                                   | 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.7            | Summ                                                                                | nary                                                                                                                                                                                                                                                                                               | 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Cor            | nclusio                                                                             | on and Future Directions                                                                                                                                                                                                                                                                           | 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.1            | Resea                                                                               | rch Accomplishments                                                                                                                                                                                                                                                                                | 184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.2            | Futur                                                                               | e Directions                                                                                                                                                                                                                                                                                       | 185                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ibliog         | graphy                                                                              | 7                                                                                                                                                                                                                                                                                                  | 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\mathbf{Sim}$ | ulink                                                                               | to ASIC Design Methodology                                                                                                                                                                                                                                                                         | 193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A.1            | Design                                                                              | n Flow                                                                                                                                                                                                                                                                                             | 193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

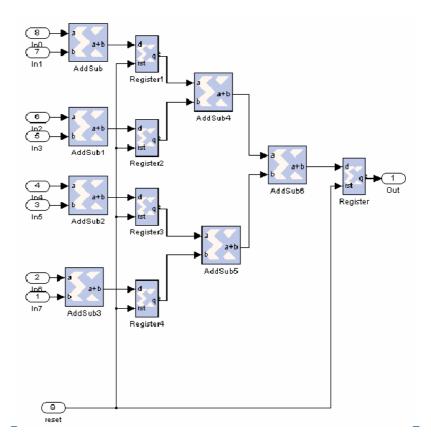

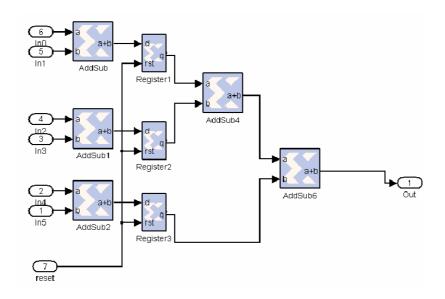

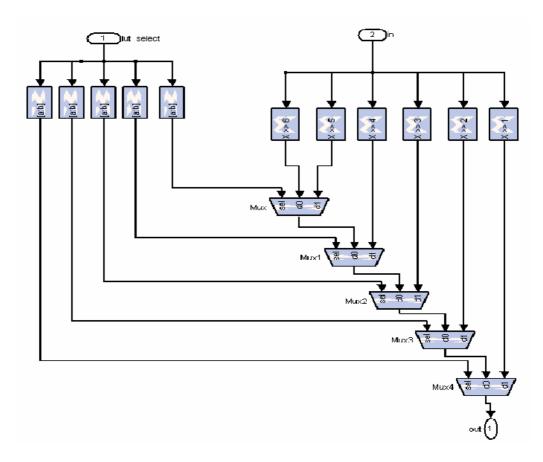

| A.2            | Distri                                                                              | buted Arithmetic FIR Simulink Models                                                                                                                                                                                                                                                               | 193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

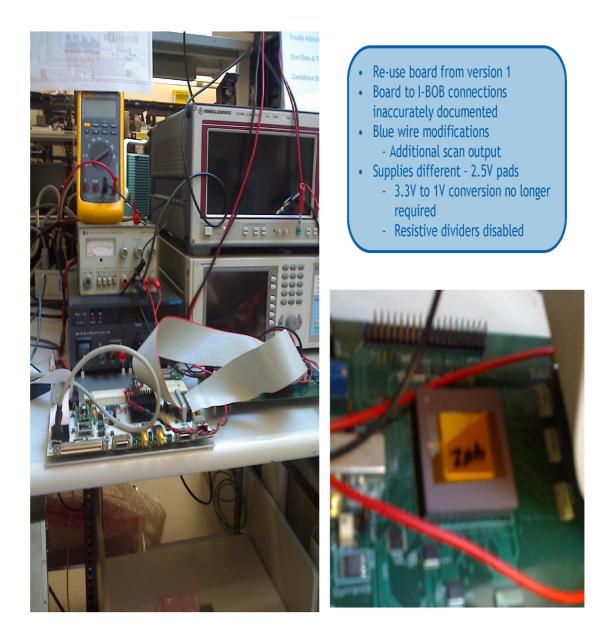

| Tes            | t Setu                                                                              | p for Distributed Arithmetic Prototype                                                                                                                                                                                                                                                             | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B.1            | Test I                                                                              | Methodology                                                                                                                                                                                                                                                                                        | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B.2            | Lab S                                                                               | etup                                                                                                                                                                                                                                                                                               | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                | 6.5<br>6.6<br>6.7<br>Cor<br>7.1<br>7.2<br>ibliog<br>Sim<br>A.1<br>A.2<br>Tes<br>B.1 | 6.3.2<br>6.3.3<br>6.3.4<br>6.4 Flexili<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.5 Flexili<br>6.6 Distri<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.3<br>6.6.4<br>6.6.5<br>6.7 Summ<br>Conclusion<br>7.1 Resea<br>7.2 Futur<br>ibliography<br>Simulink<br>A.1 Desig<br>A.2 Distri<br>Test Setu<br>B.1 Test I | 6.3.2       Architectures         6.3.3       Flexible Conventional Architectures         6.3.4       Flexible Distributed Arithmetic Architecture         6.4       Flexible Digital Filters – High Performance Technologies         6.4.1       Results         6.4.2       Sensitivity Analysis         6.4.3       Optimized Filter Description         6.4.4       Cost of Flexibility         6.5       Flexible Digital Filters – Low Leakage Technology         6.6       Distributed Arithmetic Digital FIR Prototype         6.6.1       Filter Overview and Specifications         6.6.2       RTL and Simulink Modeling         6.6.3       Functional Verification         6.6.4       Silicon Implementation and Verification         6.6.5       Measured Results         6.6.7       Summary         6.6.8       Fluere Directions         7.1       Research Accomplishments         7.2       Future Directions         7.1       Research Accomplishments         7.2       Future Directions         7.1       Design Flow         A.2       Distributed Arithmetic FIR Simulink Models         A.1       Design Flow         A.2       Distributed Arithmetic FIR Simulink Models |

# List of Figures

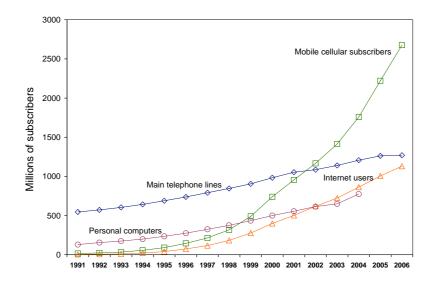

| 1.1  | Mobile vs. Fixed Telephone Line Subscribers (1991–2006)                                                                             | 5  |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

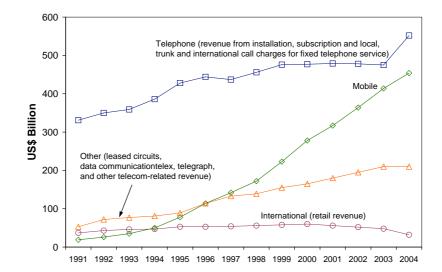

| 1.2  | Telecommunications Revenue (1991–2004) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                    | 6  |

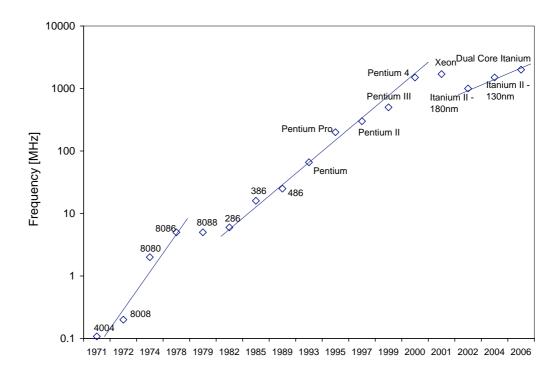

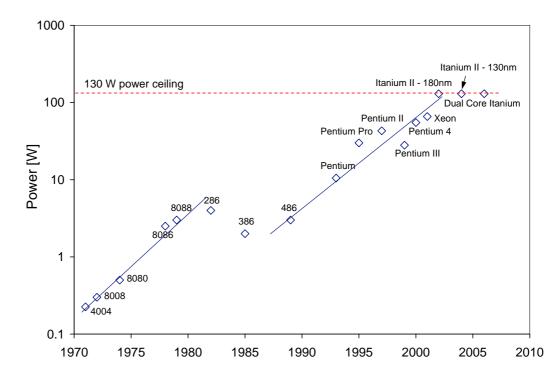

| 1.3  | Exponential increase in frequency for Intel microprocessors (compiled from www.intel.com and www.i-probe.com/i-probe/ip_intel.html) | 9  |

| 1.4  | Power ceiling for Intel microprocessors (compiled from www.intel.com and www.i-probe.com/i-probe/ip_intel.html)                     | 9  |

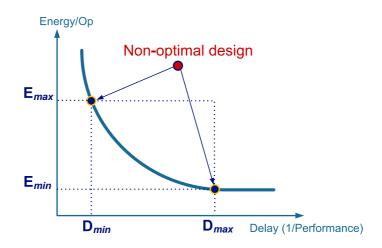

| 1.5  | Energy-efficient system design                                                                                                      | 10 |

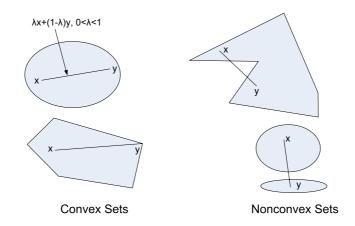

| 2.1  | Convex and non-convex sets                                                                                                          | 20 |

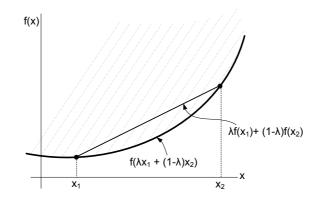

| 2.2  | Epigraph of a convex function and Jensen's inequality                                                                               | 21 |

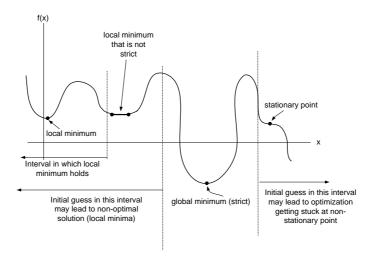

| 2.3  | Optimizations leading to local and global minima, and stationary points                                                             | 24 |

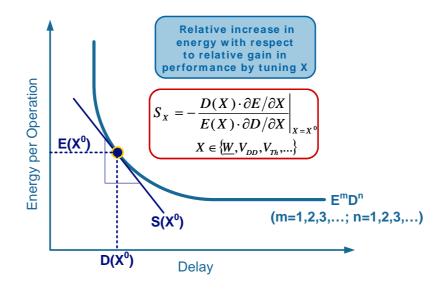

| 2.4  | Definition of sensitivity                                                                                                           | 35 |

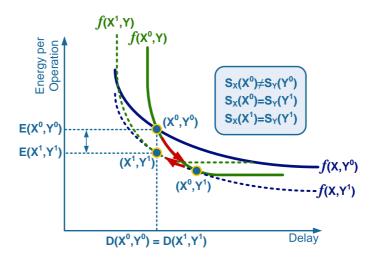

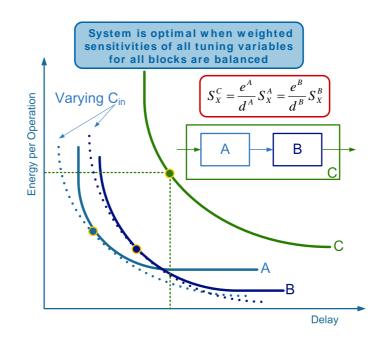

| 2.5  | Circuit optimality using multiple tuning variables                                                                                  | 37 |

| 2.6  | Multi-variable optimization using sensitivity balancing                                                                             | 38 |

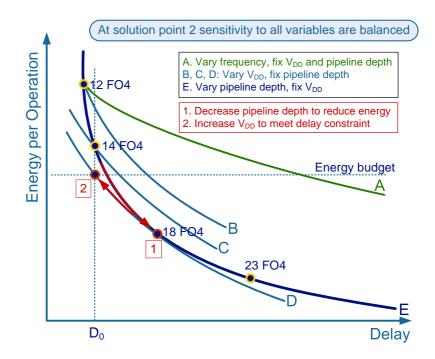

| 2.7  | System optimality                                                                                                                   | 39 |

| 2.8  | Composite pipeline stage                                                                                                            | 41 |

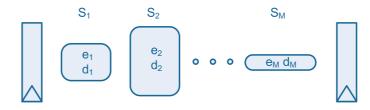

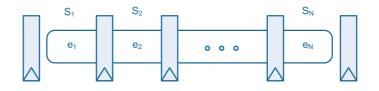

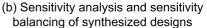

| 2.9  | Multi-stage pipeline                                                                                                                | 42 |

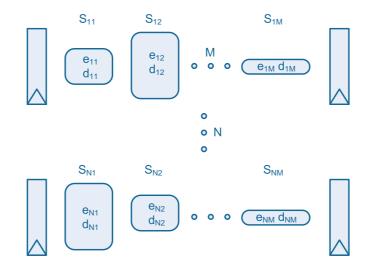

| 2.10 | Multi-stage composite pipeline                                                                                                      | 43 |

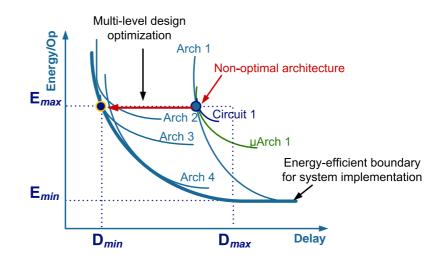

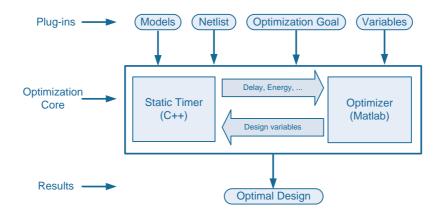

| 3.1  | Energy-delay tradeoffs at multiple levels of design abstraction                                                                     | 49 |

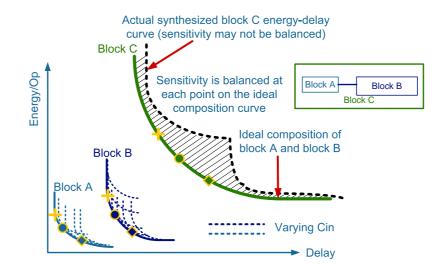

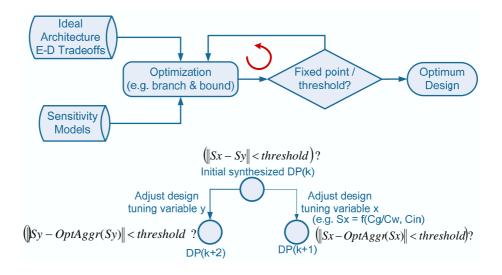

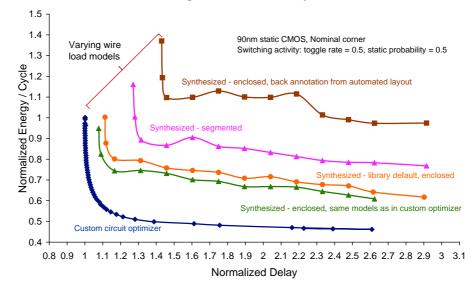

| 3.2  | Gap between ideal and synthesized energy-efficiency boundaries                                                                      | 50 |

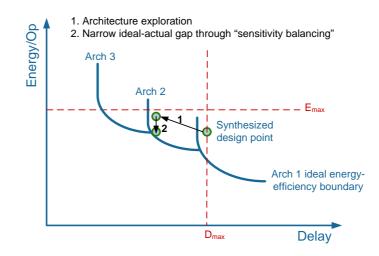

| 3.3  | Two objectives of hierarchical optimization                                                                                         | 51 |

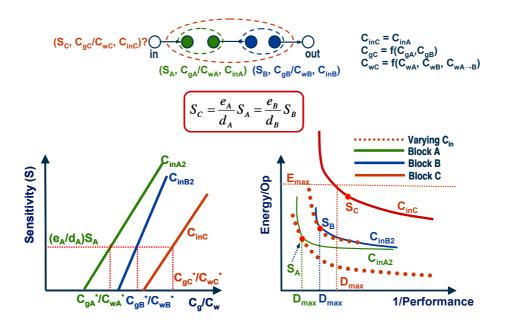

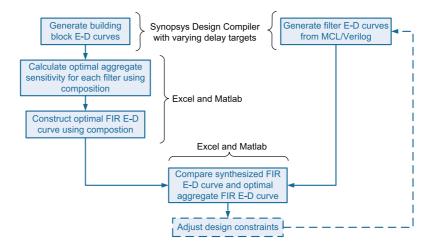

| 3.4  | Fast architecture exploration                                                                                                       | 54 |

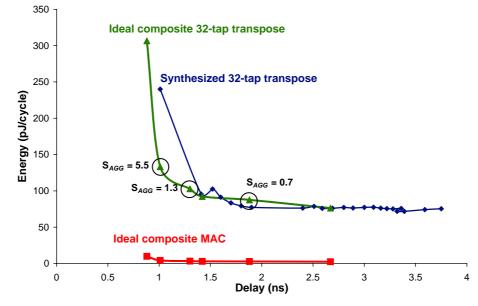

| 3.5  | Relationship between optimal aggregate sensitivity and system energy-<br>efficiency boundary                                        | 56 |

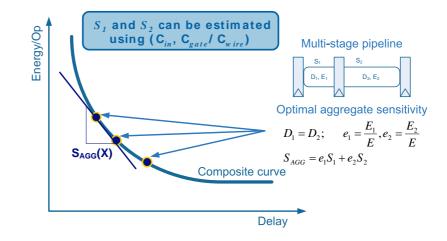

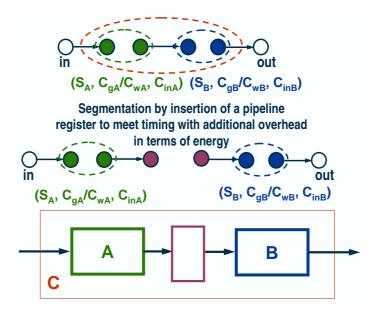

| 3.6  | Design composition of multiply-accumulate (MAC) block                                                                               | 58 |

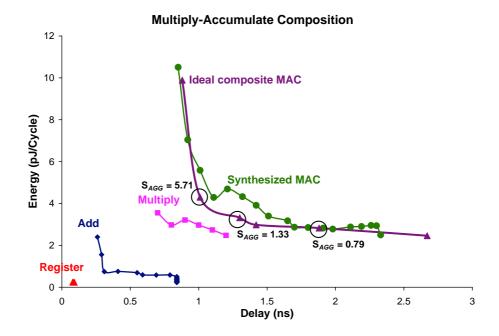

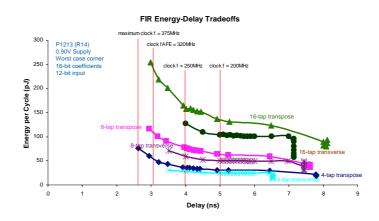

| 3.7  | Design composition of 32-tap transpose filter from MAC composite curve $~$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

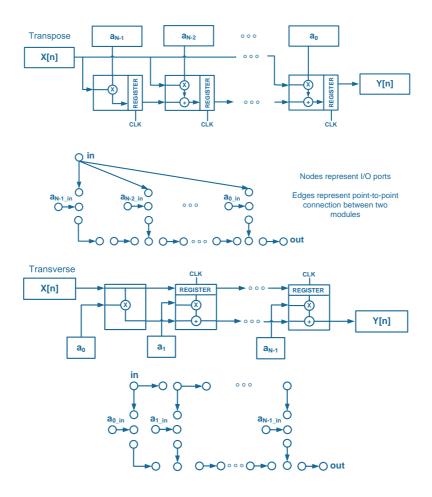

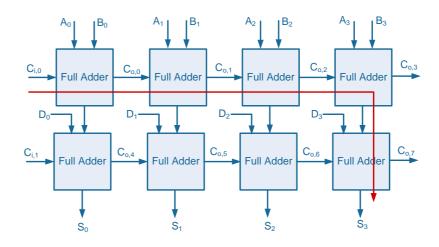

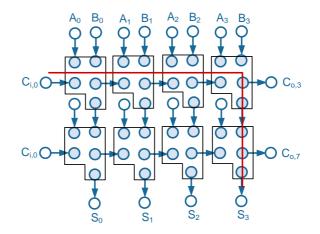

| 3.8  | Interface constraint graphs for transpose and transverse filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63  |

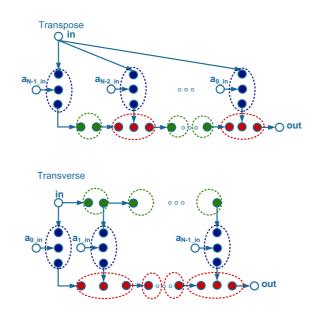

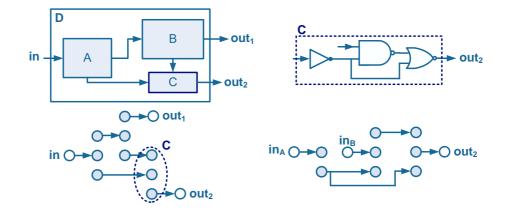

| 3.9  | Examples of embedded netlists in filter constraint graphs $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 64  |