# LNA and Mixer Designs for Multi-Band Receiver Front-Ends

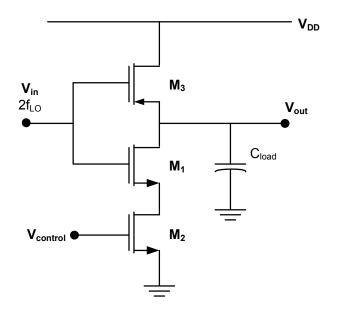

Nuntachai Poobuapheun

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-107 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-107.html

August 1, 2009

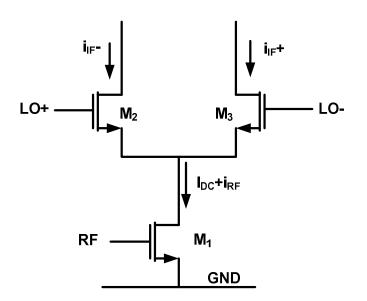

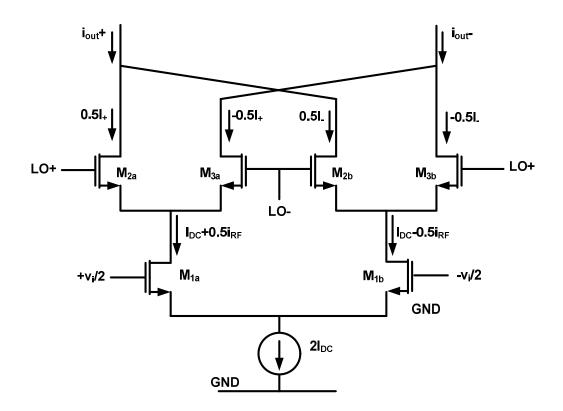

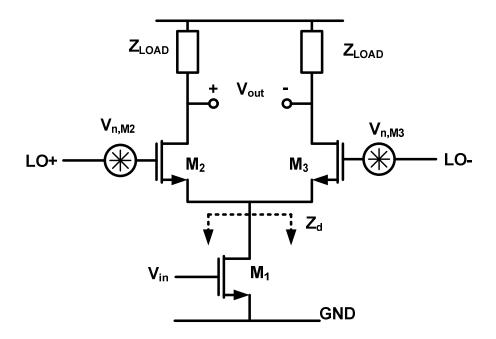

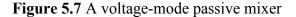

Copyright 2009, by the author(s). All rights reserved.

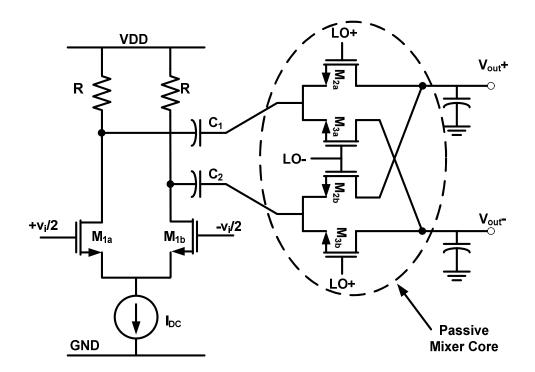

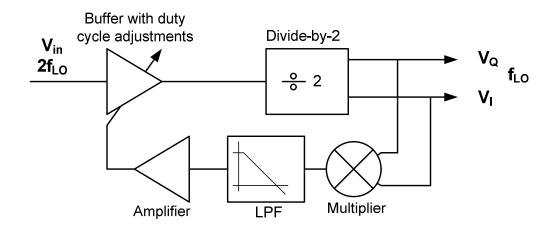

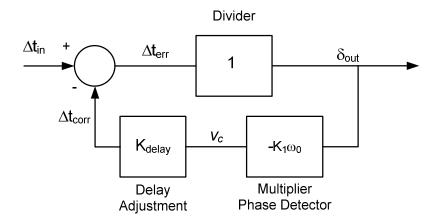

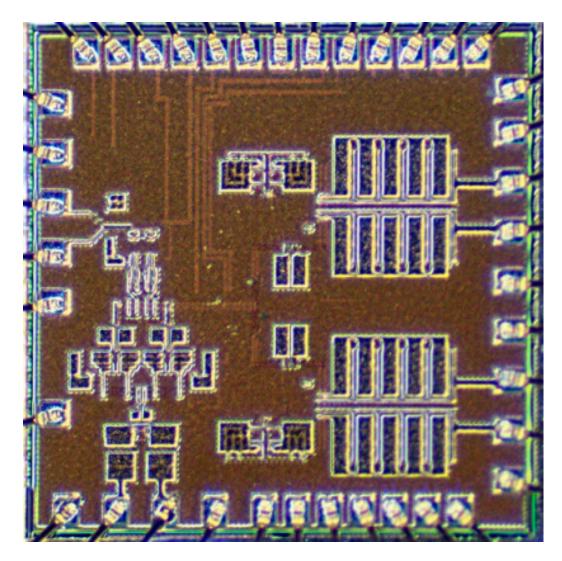

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## LNA and Mixer Designs for Multi-Band Receiver Front-Ends

By

Nuntachai Poobuapheun

B.Eng. (Chulalongkorn University, Thailand) 2002M.S. (University of California, Berkeley) 2005

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Robert G. Meyer Professor Philip B. Stark

Fall 2009

The dissertation of Nuntachai Poobuapheun is approved:

Chair

Date

Date

Date

University of California, Berkeley

## LNA and Mixer Designs for Multi-Band Receiver Front-Ends

Copyright © 2009

By

Nuntachai Poobuapheun

#### Abstract

LNA and Mixer Designs for Multi-Band Receiver Front-Ends

by

Nuntachai Poobuapheun

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences University of California, Berkeley

Professor Ali Niknejad, Chair

With the proliferation of wireless standards and frequency bands, the manufacturers of consumer electronics have tried to integrate many features in a single hand-held device. This has given rise to a need for receivers that are compatible with as many standards and frequency bands as possible. Most current integrated multi-band receivers rely on multiple receiver front-ends to process signals at different bands. The major drawback of this approach is that each front-end must be individually optimized, resulting in longer design-time and higher silicon die areas. This is due to the number of circuit blocks and interface complexity. In addition, this type of implementation is highly standard-specific: thus, it is likely that a major redesign would be required if the same topology were used for different standards.

The primary objective of this research is to investigate efficient ways of implementing such a receiver front-end with minimal cost, power consumption, and design complexity. CMOS will be the targeted process technology for this design, due to the opportunities for analog-digital system integration and cost-reduction. Despite its attractiveness, designing a front-end for multi-band operations in deep-submicron CMOS technology is non-trivial. The main challenge lies in maintaining moderate gain, noise figure, and linearity at minimum current consumption across a wide frequency spectrum with the abating supply voltage.

In this work, we investigate and discuss several receiver front-end building blocks and system designs, with a focus on the issues that arise when designing a multiband receiver front-end. In addition, we propose several circuit building blocks and systems, and implement design prototypes to validate the possibilities. The results suggest that by exploiting high-speed CMOS transistors and innovative low-voltage design techniques, it is possible to design a low-voltage, low-power, wideband receiver front-end path that is capable of processing signals using the proposed architectures.

Professor Ali M Niknejad, Chair

Date

## Acknowledgements

I would like to express my sincere gratitude to my advisor, Professor Ali M. Niknejad, without whom this work would not have been possible. His vast knowledge of several subjects enabled me to be able to advance my work during the years we worked together. Also, he was always supportive of all phases of my work, from the beginning to the end.

I would like to thank Professor Robert G. Meyer, Professor Seth Sanders, and Professor Philip Stark for valuable guidance during the qualifying exam. I also would like to express further gratitude to Professor Meyer and Professor Stark for agreeing to be on the dissertation committee and for providing numerous reviews of and suggestions for my work.

I would like to thank Wei-Hung Chen and Zhimming Deng, my great friends and colleagues, for their time and help with my research during my years at UC Berkeley. I also would like to think Tim Wongkomet, Yuen-Hui Chee, and Stanly Wang for their valuable input into the project and qualifying exam preparation. I would like to thank Ashkan Borna for his time reviewing the dissertation draft. I also would like to thank my all colleagues at BWRC for their supports during the years.

I would like to acknowledge the help of Zdravko Boos for his valuable input and help with the project. Even though we only met once, I have learned many things from our phone conference meetings and discussions, many of which provided me with direction for my work. I also would like to thank Infineon Technologies and IBM for chip fabrications for my research, and all BWRC industrial members for their support and assistance. I especially thank Joel Dunsmore from Agilent Technologies for this time and suggestions for several measurement setups and procedures.

My years at Berkeley not have been as enjoyable without all my friends outside the Department or the University. I would like to thank all the members of the Thai student group for their support, and countless enjoyable moments throughout the years. Also, I have been lucky to have wonderful roommates, Thaisiri Watewai, Pichaya Viwatrujirapong, and Chayut Thanapirom, during my stay at Berkeley.

I would like to thank all my teachers and advisors in Thailand, from my elementary school to college, who gave me such good foundations through giving me knowledge and experience. My project with Professor Wanchalerm Pora brought about my interest in wireless communications, and my courses with Professor Naiyavudhi Wongkoment inspired me to pursue a career in IC design.

My greatest appreciation and my heart go to my wife, Suvimol Ming Sangkatumvong, whom I respect greatly for her love and supports. She has always stood by me in both bad and good times throughout the years, and never questioned my abilities.

Most importantly, I would like to thank my family for their support and their unconditional love. My only brother, Saran, always believes in me and takes care of my parents when I am away from home. My parents, Udom and Chalao Poobuapheun, had to endure many challenges in order for me come to the United States for my graduate studies. My father always supports me and is always there when I need help. My mother always reminds me about the importance of responsibility and integrity, both of which I will always remember. Dedicated to my parents

# **Table of Contents**

## 1. Introduction

|    | 1.1.CMOS Technology and Wireless Systems           | 1  |

|----|----------------------------------------------------|----|

|    | 1.2.Need for Multi-Standard Receivers              | 2  |

|    | 1.3.Research Goals and Contributions               | 4  |

|    | 1.4. Thesis Organization                           | 5  |

|    | 1.5.References                                     | 5  |

| 2. | Wireless Receiver Basics                           |    |

|    | 2.1.Introduction                                   | 7  |

|    | 2.2.Sensitivity                                    | 7  |

|    | 2.3.Selectivity                                    | 11 |

|    | 2.4.Receiver Dynamic Range                         | 19 |

|    | 2.5.Receiver Architecture Reviews                  | 21 |

|    | 2.6.Multi-Band Receivers using Broadband Front-End | 29 |

|    | 2.7.References                                     | 41 |

| 3. | CMOS LNA Fundamentals                              |    |

|    | 3.1.Introduction                                   | 44 |

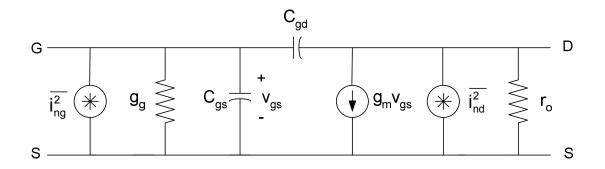

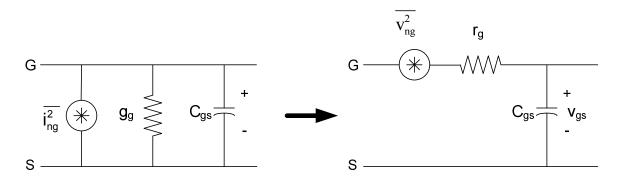

|    | 3.2.Noise Sources in MOS Transistors               | 44 |

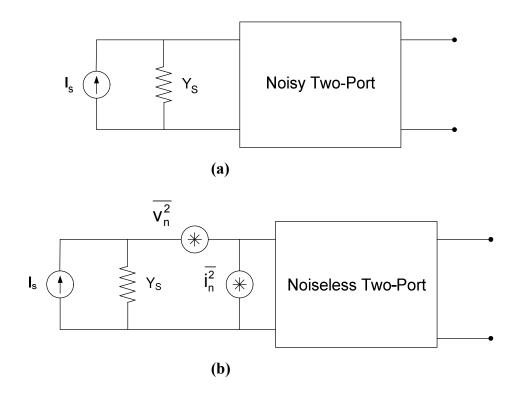

|    | 3.3.Two-Port Noise Theory                          | 50 |

|    | 3.4.Impedance Matching in LNA Designs              | 54 |

|    | 3.5.LNA Input Matching Topologies                  | 55 |

|    | 3.6.References                                     | 68 |

| Broadband CMOS LNA Analysis and Design                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1.Introduction                                      | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2.Multi-Section Input Matching                      | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3.0.8-2.4 GHz Broadband LNA Design Example          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.4.Experimental Results                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.5.References                                        | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CMOS Mixer Fundamentals                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1.Introduction                                      | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2.Mixer Basics                                      | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3.Mixer Performance Metrics                         | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.4.Basic CMOS Mixer Architectures                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.5.Quadrature Signal Generation                      | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.6.CMOS Mixer Architectures for Multi-Band Receivers | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.7.References                                        | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Wideband CMOS Demodulator Analysis and Design         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.1.Introduction                                      | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.2.Quadrature Mixer Architecture                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.3.Building Block Designs                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.4.Experimental Results                              | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.5.References                                        | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Wideband CMOS Front-End Analysis and Design           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.1.Introduction                                      | 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.2.Receiver Front-End Architecture                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                       | Broadband CMOS LNA Analysis and Design         4.1. Introduction         4.2. Multi-Section Input Matching         4.3.0.8-2.4 GHz Broadband LNA Design Example         4.4. Experimental Results         4.5. References         CMOS Mixer Fundamentals         5.1. Introduction         5.2. Mixer Basics         5.3. Mixer Performance Metrics         5.4. Basic CMOS Mixer Architectures         5.5. Quadrature Signal Generation         5.6. CMOS Mixer Architectures for Multi-Band Receivers         5.7. References         Wideband CMOS Demodulator Analysis and Design         6.1. Introduction         6.2. Quadrature Mixer Architecture         6.3. Building Block Designs         6.4. Experimental Results         6.5. References         Wideband CMOS Front-End Analysis and Design         7.1. Introduction         7.2. Receiver Front-End Architecture |

| 7.3.Circuit Implementations       |  |  |  |  |

|-----------------------------------|--|--|--|--|

| 7.4.Experimental Results          |  |  |  |  |

| 7.5.References                    |  |  |  |  |

| 8. Conclusion                     |  |  |  |  |

| 8.1.Introduction                  |  |  |  |  |

| 8.2.Summary and Contributions     |  |  |  |  |

| 8.3.Future Research Opportunities |  |  |  |  |

| 8.4.References                    |  |  |  |  |

# Introduction

## 1.1 CMOS Technology and Wireless Systems

Until the late 1980s, radios were implemented using discrete components such as transistors, capacitors, and inductors. The transistors used in these radios were manufactured using expensive process technologies that were optimized for high-frequency applications [1.1]. As sales of wireless communication handsets have risen, the wireless transceiver market has become increasingly attractive to electronics hardware vendors. This has led to a highly competitive consumer market space, with tremendous pressures in the industry for lowest-cost solutions.

In the early 1990s, the adoption of standards such as GSM, and advances in digital signal processing increased the demand for digital circuits in radio systems. CMOS has been the technology of choice for implementing digital signal processors, since CMOS devices consume less power than competing technologies. This has spurred research efforts to reduce the cost of CMOS transistors and implementations. Given sufficient production volume, the cost of a CMOS chip decreases as the size of a unit transistor decreases, because the same functionality can be provided in a smaller silicon die area. In 1965, Gordon Moore predicted that the number of transistors that could be put in a given space would double approximately every two years [1.2]. His

prediction has proved true: transistor unit size has decreased exponentially for decades [1.3].

As CMOS transistor size shrinks, device parasitic capacitances also become smaller, and the transistor becomes faster [1.4]. Eventually, CMOS transistors become sufficiently fast to be used in radio frequency integrated circuit implementations. From that point, CMOS provides the highest analog-digital on-chip integration and yields the lowest-cost solutions for implementing wireless transceivers. For these reasons, much research on CMOS wireless transceivers has been published, describing increasing levels of digital and analog integration [1.5][1.6][1.7]. Although competing technologies exist, the cost benefits of mixed-signal CMOS technology make it the process of choice for transceivers used in high-volume applications.

#### **1.2 Need for Multi-Standard Receivers**

The limited available frequency spectrums have become overcrowded as wireless network deployments have proliferated. This crowding has stimulated research efforts to increase spectral efficiency through better modulation schemes or advanced system-level techniques (e.g., power control in CDMA systems). In the last 20 years, several new standards have been proposed and implemented; Table 1.1 shows the wireless standards currently in use [1.8]. From the table, it is clear that each standard specifies its own frequency band, modulation scheme, signal power, and data rates. The differences in the defined standards translate into different requirements for receiver front-ends – when a new standard is created, a new receiver front-end must be designed, which is time-consuming. One approach to reducing the system design time is to

| Range               | Long       |              | Medium        | Short      |             |

|---------------------|------------|--------------|---------------|------------|-------------|

| System              | GSM/DCS    | UMTS         | 802.11a       | Bluetooth  | DECT        |

| Frequency           | 0.9/1.8GHz | 2GHz         | 5GHz          | 2.4GHz     | 1.9GHz      |

| Channel spacing     | 200KHz     | 5MHz         | 20MHz         | 1MHz       | 1.728MHz    |

| Access              | TDMA       | CDMA         | CSMA/CA       | CDMA       | TDMA        |

| Modulation          | GMSK       | QPSK         | BPSK/QPSK/QAM | GFSK       | GFSK        |

| Bit rate            | 270K       | 3.84M        | 5.5~54M       | 1M         | 1.152M      |

| Rx sensitivity      | -100dBm    | -117dBm      | -65dBm        | -70dBm     | -83dBm      |

| Signal S/N+I        | 9dB        | 5.2dB        | 28dB          | 21dB       | 10.3dB      |

| Rx NF               | 9dB        | 9dB          | 7.5dB         | 23dB       | 18dB        |

| Rx IIP <sub>3</sub> | -18dBm     | -4dBm        | -20dBm        | -15dBm     | -22dBm      |

| Phase noise         | -141dBc@3M | -150dBc@135M | -102dBc@1M    | -105dBc@1M | -99dBc@2.2M |

| Frequency           | 0.9/1.8GHz | 2GHz         | 5GHz          | 2.4GHz     | 1.9GHz      |

optimize an existing receiver front-end for a different application. However, this methodology results in inferior performance.

**Table 1.1** Comparison of wireless standards (table from [1.8])

Over the past decade, consumer electronics manufacturers have tried to integrate many features in a single hand-held device (e.g., multi-band multi-standards compatibility). This has given rise to a need for receivers that are compatible with as many standards and frequency bands as possible. Most current multi-band receivers rely on multiple receiver front-ends to process signals at different bands [1.6][1.9]. The major drawback of this approach is that each front-end must be individually optimized, resulting in longer design and simulation times, due to the number of circuit blocks, and interface complexity. In addition, this approach can require very large front-end silicon die areas, especially if inductors are used in each receiving path. Finally, this type of implementation is highly standard-specific; thus, a major redesign would likely be required if the same topology were used for different standards – when, for example, there is an immediate need for a front-end that is compatible with the system, but with different requirements from previous front-ends.

### 1.3 Research Goals and Contributions

As indicated in the previous section, there is strong motivation to design a multiband or wideband receiver front-end that is compatible with multiple standards. The primary objective of this research is to investigate efficient ways to implement such a receiver front-end with minimal cost, power consumption, and design complexity. In addition, for the reasons discussed in section 1.1, CMOS will be the targeted process technology for the design, due to the opportunities for system integration and costreduction.

The contributions of this research include the investigation and discussion of several building blocks and system designs, including an analysis of issues in designing a multi-band receiver front-end, and a comparison of various receiver building blocks and system architectures. In addition, we will propose several circuit building blocks and systems, and implement design prototypes to validate the possibilities. The results suggest that by exploiting high-speed CMOS transistors and innovative low-voltage design techniques it is possible to design a low-voltage, low-power, wideband receiver front-end path that is capable of processing signals using the proposed architectures.

## 1.4 Thesis Organization

This thesis is organized as follows: Chapter 2 offers a review of receiver fundamentals, including receiver sensitivity, receiver selectivity, and basic receiver architectures. Also provided are discussions of the universal multi-band receiver frontend in terms of specifications, limitations, and suitable topologies.

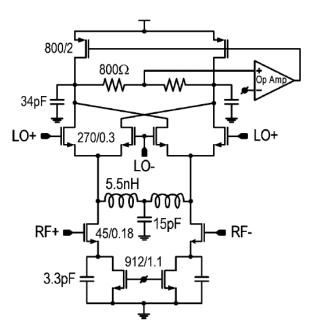

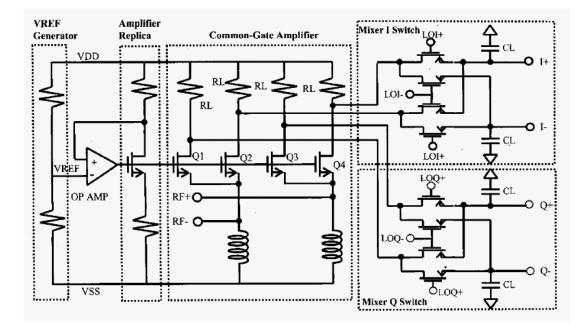

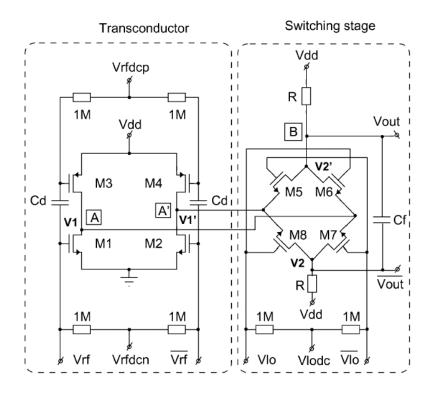

Chapter 3 reviews the fundamentals of CMOS low-noise amplifiers (LNA), including topics ranging from noise sources in MOS transistors to basic CMOS LNA design. Chapter 4 presents the analysis, design, and experimental results of a broadband LNA in a 0.18 µm CMOS process. Chapter 5 reviews mixer fundamentals, with emphasis on CMOS mixers, and covers mixer operations, mixer performance metrics, basic CMOS mixer architectures. Chapter 6 presents analysis, design, and implementation results of a wideband demodulator implemented in a 0.13 µm CMOS technology.

Chapter 7 presents a design for a wideband front-end for a multi-band receiver in 0.13µm CMOS technology, and implementation results.

Chapter 8 presents conclusions and future research possibilities.

## 1.5 References

- [1.1] A. Abidi, "CMOS wireless transceivers: the new wave," *IEEE Communications Magazine*, vol. 37, no. 8, pp. 119-122, Aug. 1999.

- [1.2] Moore, Gordon E., "Cramming more components onto integrated circuits," *Electronics*, Volume 38, Number 8, April 19, 1965.

- [1.3] J. Rabaey, A. Chandrakasan, and B. Nikolic'. *Digital Integrated Circuits: A Design Perspective*, Second Edition, Prentice-Hall, New Jersey, 2002.

- [1.4] P. R. Gray, R.G. Meyer, P. J. Hurst and S. H. Lewis, Analysis and Design of Analog Integrated Circuits, Fourth Edition, Wiley, New York, 2001.

- [1.5] J. C. Rudell, J. Ou, T. B. Cho, G. Chien, F. Brainti, J. A. Weldon, and P. R. Gray, "A 1.9-GHz wide-band IF double conversion CMOS receiver for cordless telephone applications," *IEEE J. Solid-State Circuits*, vol. 32, no. 12, pp. 2071-2088, Dec. 1997.

- [1.6] O. E. Erdogan, et al., "A Single-Chip Quad-Band GSM/GPRS Transceiver in

0.18 µm Standard CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, San Francisco, CA, Feb. 2005, pp. 318-319.

- [1.7] S.S. Mehta, et al., "An 802.11g WLAN SoC," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2483-2491, Dec. 2005.

- [1.8] W. Chen, N. Poobuapheun, and A. Niknejad, "A Broadband High Dynamic Range CMOS Front-End," BWRC Summer Retreat, 2006.

- [1.9] T. Manku, et al., "A single chip direct conversion CMOS transceiver for quadband GSM/GPRS/EDGE and WLAN with integrated VCO's and fractional-N synthesizer," in Proc. *IEEE Radio Frequency Integrated Circuits (RFIC) Symp.*, Jun. 2004, pp. 423-426.

# **Wireless Receiver Basics**

## 2.1 Introduction

This chapter covers two important receiver concepts: selectivity and sensitivity. These parameters are the most comprehensive figures of merit in receiver performance and are influenced by many sub-figures of merit, such as noise performance of the individual building blocks, linearity, gain distribution, and image rejection ratio. The relationships between these sub-figures of merit and selectivity and sensitivity are discussed in sections 2.2, 2.3, and 2.4.

Section 2.5 offers a review of basic receiver architectures characterized by various frequency planning methodologies, including super-heterodyne, zero-IF (direct conversion), and low-IF receivers. Comparisons between several receiver architectures for multi-band receivers are given in section 2.6, along with a discussion on the requirements and estimated performance of a broadband front-end.

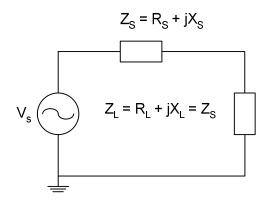

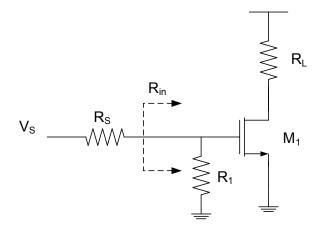

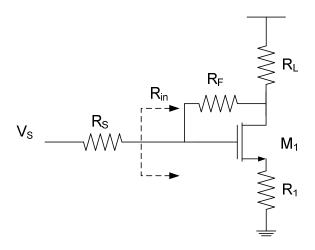

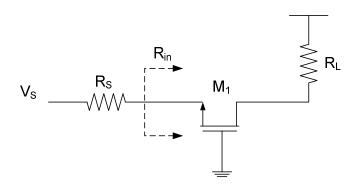

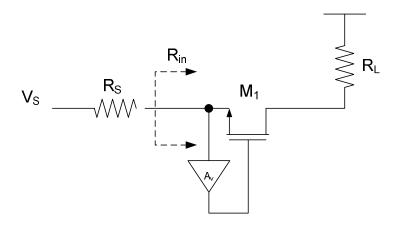

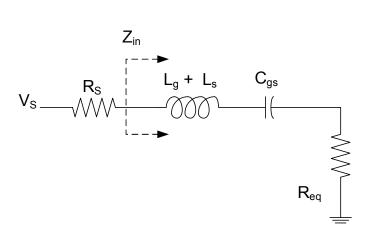

## 2.2 Sensitivity

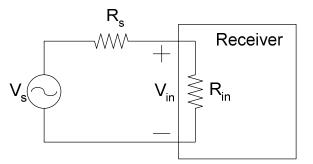

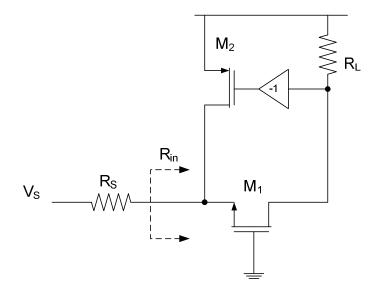

Sensitivity is defined as the minimum signal level at the receiver input such that there is a sufficient signal-to-noise ratio (SNR) at the receiver output for a given application. It can be specified in units of dBm (decibels relative to one milliwatt), along with reference impedance (50  $\Omega$  for most systems), and is typically measured in an interference-free environment. Usually, the input of the receiver is matched to a certain source impedance, simplified as the real impedance  $R_{in} = R_s$ , as shown in figure 2.1.

Figure 2.1 Impedance matching in a receiver

### **2.2.1 Noise Figure Definitions**

The overall sensitivity is directly related to the noise figure of the receiver, which is impacted by noise from individual blocks in the receiver as well as the gain distribution of the receiver chain. The noise figure is defined as a ratio between the SNR at the input and the SNR at the output of the circuit:

$$F = \frac{Input \ SNR}{Output \ SNR}$$

(2.1)

$$NF \equiv 10\log(F) \text{ (dB)}$$

where F is noise factor and NF is the noise figure of the system. Noise figure is calculated in reference to the specified source impedance and the temperature (T). In standard communication systems, the typical values are  $R_s = 50 \ \Omega$  and  $T = 293 \ K$ . For a

circuit building block such as an amplifier, the total noise figure can be calculated in terms of added output noise and the gain of the system. An amplifier with power gain G, input signal power  $P_{in}$ , and input noise power  $N_{in}$  will have the output signal power  $GP_{in}$  and the output noise power  $GN_{in}+N_{add}$ . The noise figure of the amplifier can then be calculated using the definitions in (2.1).

$$F = \frac{\left(\frac{P_{in}}{N_{in}}\right)}{\frac{GP_{in}}{GN_{in} + N_{add}}}$$

(2.3)

$$F = 1 + \frac{N_{add}}{GN_{in}} = 1 + \frac{N_{add,in}}{N_{in}}$$

(2.4)

where  $N_{add,in}$  is the input-referred added noise from the amplifier, defined as  $N_{add,in} = N_{add}/G$ .

#### 2.2.2 Noise Figure Calculations for Cascaded Blocks

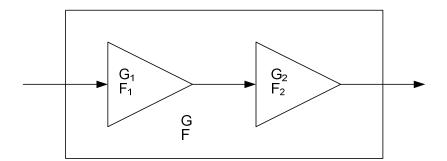

The previous section discussed the definition of the noise figure for a single circuit block. However, for a receiver, we need to calculate the noise figure of cascaded circuit blocks in order to determine the overall system sensitivity. The cascaded noise figure depends strongly on the noise figures of individual blocks, as well as the gain distribution of the receiver chain. If two blocks are cascaded with each other, as shown in figure 2.2, and the impedance matching is done properly (input and output are matched), the total output noise is then given by:

$$P_{noise,out} = F_1 P_{noise,in} G_1 G_2 + (F_2 - 1) P_{noise,in} G_2$$

(2.5)

9

Figure 2.2 Cascaded blocks

$G_1$  and  $G_2$  are the power gains for each block in the given matching condition.  $F_1$  and  $F_2$  are the noise figures for each block. The output SNR of the cascaded blocks is then given by:

$$SNR_{out} = \frac{S_{out}}{P_{noise,out}} = \frac{S_{in}G_1G_2}{F_1P_{noise,in}G_1G_2 + (F_2 - 1)P_{noise,in}G_2} = SNR_{in} \left(\frac{1}{F_1 + \frac{F_2 - 1}{G_1}}\right) (2.6)$$

Finally, the total cascaded noise figure can be calculated as:

$$F = \frac{SNR_{in}}{SNR_{out}} = F_1 + \frac{(F_2 - 1)}{G_1}$$

(2.7)

From (2.7), the overall noise figure depends on the noise figures of both stages and on the gain of the first stage. If  $G_1$  is large, noise from the later stage will have less effect on the overall noise figure. As a result, the first block in the receiver must exhibit low noise and must have at least moderate gain. An amplifier with those characteristics is usually called a low-noise amplifier.

### 2.2.3 Relationship between Noise Figure and Sensitivity

A direct relationship exists between the noise figure of the amplifier and the sensitivity of the receiver. Sensitivity can be calculated in terms of noise floor and the required SNR at the input. Since the required SNR at the output of the receiver is set by top-level specifications such as modulation techniques and bit-error-rate (BER), it is usually fixed for a given application. These numbers determine carrier-to-noise ratio (CNR), which is the ratio between the carrier power and the integrated noise power in the frequency band. Once the CNR is known, the required receiver input SNR can be calculated as:

$$SNR_{in}(dB) = CNR_{out}(dB) + NF(dB)$$

(2.8)

Finally, the expression for the sensitivity is given by:

$$Sensitivity (dBm) = SNR_{in} (dB) + NoiseFloor(dBm) + 10\log(BW) (dB)$$

(2.9)

where BW is the bandwidth of the communication channel.

## 2.3 Selectivity

In the last section, we discussed receiver performance, measured by sensitivity to the desired signal. We did not consider interference from other undesired signals. Receiver selectivity is a performance measure of the ability to separate the desired signal from these unwanted interfering signals. It usually becomes important in the near-far situation where the desired signal is weak and there is a strong adjacentband/channel interfering signal at the receiver input.

There is no clear quantitative measure of selectivity, especially at the circuit level. It is usually specified in the physical layer, such as in blocking masks, which can be used to obtain the filtering, nonlinearity, and phase noise requirements in the circuit. The other test related to selectivity of the receiver is the third-order intermodulation or two-tone test. In this case, a pair of undesired signals is applied to the receiver in such a way that their third-order intermodulation will line up in the same band as the desired signal. We will discuss these specifications and tests in detail in the next sections.

#### **2.3.1 Blocking Performance**

Blocking performance is usually specified with a desired signal being applied to the receiver at a specified power level above the required sensitivity. Simultaneously, an additional signal, called a blocker (sometimes called a jammer) is applied to the receiver at a defined power level and offset from the carrier. Under these conditions, the receiver must maintain the required bit error rate (BER) in the presence of the blocking signal.

A strong blocker can degrade receiver performance in several ways. First, it can cause gain compression, as well as degradation of the noise figure of the receiver. This directly reduces the sensitivity of the receiver for the desired signal [2.1]. The second problem comes from the nonlinearity of the system. When the large blocker goes through second-order nonlinearity in the receiver chain, it can mix with itself down to a very low frequency and so create problems, especially in direct-conversion or low-IF receivers. A detailed analysis of nonlinearity will be given in the next section. Finally, the strong blocker can mix with the local oscillator sidebands resulting from its phase noise, a process known as reciprocal mixing. The mixed signal can be in the same frequency band as the desired signal, effectively decreasing the signal-to-noise ratio. More details about the reciprocal mixing can be found in [2.2].

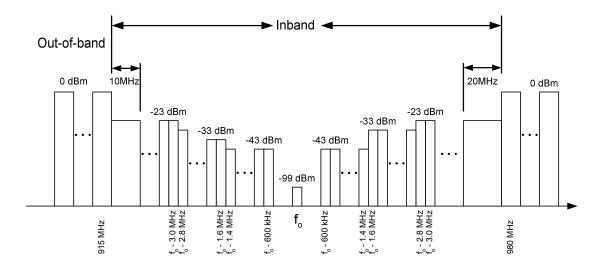

An example of the blocking definition is shown in figure 2.3 for the GSM 900 standard [2.3]. The blocking test is performed by applying a Gaussian Minimum-Shift Keying (GMSK) modulated signal at 3 dB above the required sensitivity, along with the single-tone blocker at the input of the receiver. The blockers are located at increments of 200 kHz away from the desired signal, with the amplitudes shown in figure 2.3. To pass the test, the receiver must maintain the bit-error–rate within a defined limit.

There are two types of blockers: in-band and out-of-band. Usually, the bandselecting filter in front of the receiver will filter out the out-of-band blockers. As a result, those blockers will be highly attenuated before arriving at the real receiver input. However, this is not the case for in-band blockers, where all the signals are in the passband of the filter.

Figure 2.3 GSM 900 blocking definition

### 2.3.2 Second-Order Nonlinearity

Second-order nonlinearity in the receiver blocks causes many problems, especially in direct-conversion or low-IF receivers. This can be understood by examining an expression that relates the input and output signals of the block. First, assuming we have a relationship given by:

$$S_{out}(t) = a_1 S_{in}(t) + a_2 S_{in}^2(t) + a_3 S_{in}^3(t) + \dots$$

(2.10)

where  $S_{in}(t)$  is the input signal and  $S_{out}(t)$  is the output signal. If the input signal (the blocker) is a sine wave, we then have:

$$S_i(t) = S_i \cos(\omega_b t) \tag{2.11}$$

where  $\omega_b$  is the frequency of the blocker. Applying (2.11) to (2.10), the output term created by the second-order nonlinearity is given by:

$$S_{out}(t) = a_2 (S_i \cos(\omega_b t))^2 = a_2 S_i^2 \left(\frac{1}{2} + \frac{\cos(2\omega_b t)}{2}\right)$$

(2.12)

There are two components on the right-hand side of (2.12), one located at DC and the other at the frequency of  $2\omega_b$ . The DC component can superimpose onto the baseband signal at DC and degrade the receiver performance. This becomes problematic in direct conversion receivers with the presence of a strong blocking signal.

Defining second-order harmonic distortion and second-order intermodulation as in [2.4], the expressions for  $HD_2$  and  $IM_2$  are given by:

$$HD_2 = \frac{\frac{a_2}{2}S_i^2}{a_1S_i} = \frac{1}{2}\frac{a_2}{a_1}S_i$$

(2.13)

$$IM_2 \cong HD_2 + 6dB \tag{2.14}$$

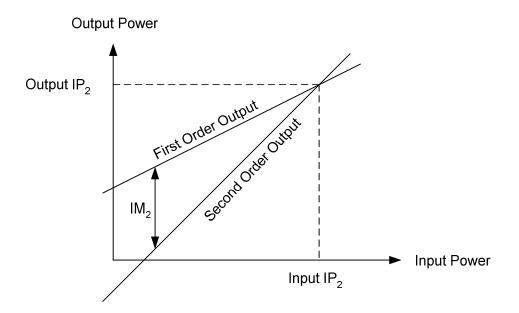

Since IM2 increases linearly with input signal level, there will be a point where the extrapolated IM2 is equal to the extrapolated first-order output signal (figure 2.4). The second-order input intercept point (IIP<sub>2</sub>) is an important figure of merit in receiver designs and is given by:

$$IIP_2 = \frac{a_1}{a_2} \tag{2.15}$$

Given the  $IIP_2$ , one can calculate the output  $IM_2$  for a given input blocker power by the equation:

$$IM_{2}(dB) = P_{bloc\,ker}(dB) - IIP_{2}(dB)$$

(2.16)

Figure 2.4 IM<sub>2</sub> plot and IIP<sub>2</sub> intercept point

## 2.3.4 Third-Order Nonlinearity

Another important type of nonlinearity in receiver systems is third-order nonlinearity. Problems associated with third-order nonlinearity arise from two out-ofchannel signals passing though the nonlinear blocks. Assuming that these two signals are sinusoidal, we can write them in combination as an input signal:

$$S_{i}(t) = S_{1}\cos(\omega_{1}t) + S_{2}\cos(\omega_{2}t)$$

(2.17)

After  $S_i(t)$  passes through the third-order nonlinearity term in (2.10), several unwanted frequencies are generated. After simplification, we get:

$$a_{3}S_{i}^{3} = \frac{a_{3}S_{1}^{3}}{4} (\cos(3\omega_{1}t) + 3\cos(\omega_{1}t)) + \frac{a_{3}S_{2}^{3}}{4} (\cos(3\omega_{2}t) + 3\cos(\omega_{2}t)) + \frac{3}{4}a_{3}S_{1}S_{2}^{2} [2\cos(\omega_{1}t) + \cos((2\omega_{2} - \omega_{1})t) + \cos((2\omega_{2} + \omega_{1})t)] + \frac{3}{4}a_{3}S_{1}^{2}S_{2} [2\cos(\omega_{2}t) + \cos((2\omega_{1} - \omega_{2})t) + \cos((2\omega_{1} + \omega_{2})t)]$$

$$(2.18)$$

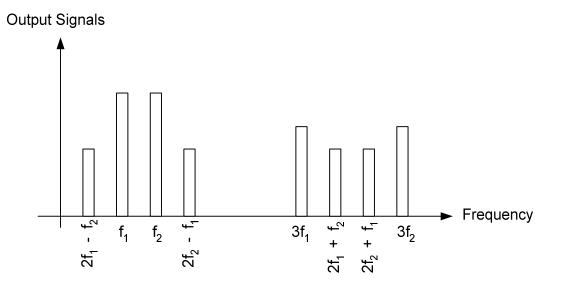

The graphical presentation of (2.18) is shown in figure 2.5. There are linear terms ( $\omega_1$ ,  $\omega_2$ ), third-order harmonics ( $3\omega_1$  and  $3\omega_2$ ), and third-order intermodulation terms ( $2\omega_2-\omega_1$ ,  $2\omega_1-\omega_2$ ,  $2\omega_2+\omega_1$ ,  $2\omega_1+\omega_2$ ).

Figure 2.5 Third–order products in frequency domain

If the two-tones are placed adjacent to each other, some of the IM<sub>3</sub> products will lie just next to  $\omega_1$  and  $\omega_2$ . If the desired channel is located at either  $2\omega_2 - \omega_1$  or  $2\omega_1 - \omega_2$ , it will experience interference due to these components. This is often the most troubling case for receiver applications where there might be alternate channel users present very close in frequency to the receiver's desired channel.

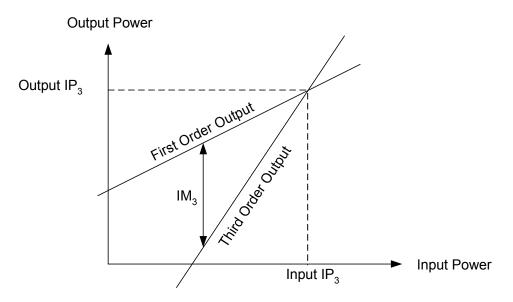

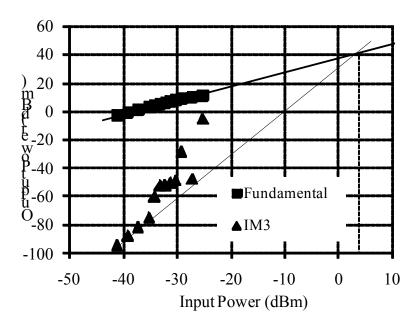

Figure 2.6 Third-order intercept points

Figure 2.6 shows the logarithmic plot between the output and input signals assuming the same power of the two-tones. The third-order intermodulation grows with the input power at three times the rate at which the linear components increase. The third-order intercept point (IP<sub>3</sub>) is defined as the intersection of the two lines. The horizontal coordinate of this point is called the input IP<sub>3</sub> (IIP<sub>3</sub>), and the vertical coordinate is called the output IP<sub>3</sub> (OIP<sub>3</sub>). The IIP<sub>3</sub> can be calculated by equating the linear term and the IM<sub>3</sub> term and is given by:

$$IIP_3 = \sqrt{\frac{4}{3} \left| \frac{a_1}{a_3} \right|} \tag{2.19}$$

Alternately, if the IIP<sub>3</sub> and the power of corresponding two-tone signals are given, the input referred IM<sub>3</sub> can be expressed as (all units are in dB):

$$IM_{3,in} = 2(P_{in} - IIP_3)$$

(2.20)

For cascaded nonlinear stages such as the one in figure 2.2, the overall IIP<sub>3</sub> is affected by the nonlinearity of each block and gain distribution. As shown in [2.5], the overall IIP<sub>3</sub> is given (neglecting second-order interaction) by:

$$\frac{1}{IIP_{3,overall}^2} \approx \frac{1}{IIP_{3,1}^2} + \frac{G_1^2}{IIP_{3,2}^2} + \frac{G_1^2 G_2^2}{IIP_{3,3}^2} + \dots$$

(2.21)

where  $IIP_{3,k}$  and  $G_k$  are the voltage  $IIP_3$  and voltage gain for the block *k*. If one block dominates the overall third-order nonlinearity of the system, the  $IIP_3$  can be estimated as [2.6]:

$$IIP_{3,overall} \approx \min\left[IIP_{3,1}, \left(\frac{IIP_{3,2}}{G_1}\right), \left(\frac{IIP_{3,3}}{G_1G_2}\right), \dots\right]$$

(2.22)

## 2.4 Receiver Dynamic Range

The dynamic Range (DR) of a receiver is defined as the ratio of the maximum input level that the circuit can tolerate, to the minimum input level that is still detectable. The quantitative definitions differ from application to application. In analog circuits such as A/D converters, it can be defined as a ratio between the "full-scale" (FS) input level and the input level for which SNR=1. In RF receivers, however, it is very hard to define FS input level. The commonly used method is to define the upper limit of the input power as the maximum two-tone input level at which the produced output IM<sub>3</sub> is

still below the noise floor. Such a definition is called the "spurious-free dynamic range" (SFDR) [2.5].

By rewriting (2.20), we have:

$$P_{in} = \frac{2IIP_3 + IM_{3,in}}{2}$$

(2.23)

The integrated noise floor over the bandwidth  $(N_{in})$  at the input of a receiver is given by:

$$N_{in}(dBm) = NoiseFloor(dBm) + 10\log(BW)(dB)$$

(2.24)

The *input referred* integrated noise floor at the *output* of the receiver is then given by:

$$N_{out,in}(dBm) = N_{in}(dBm) + NF(dB)$$

(2.25)

The input referred third-order intermodulation product must be equal or less than  $N_{out,in}$ . This gives us:

$$P_{in,\max} = \frac{2IIP_3 + N_{out,in}}{2}$$

(2.26)

Since the lower bound of the input power is the sensitivity or minimum detectable signal (MDS) of the receiver, the spurious-free dynamic range is:

$$DR = P_{in,\max} - Sensitivity \tag{2.27}$$

20

## 2.5 Receiver Architecture Reviews

The previous sections presented the basic requirements of receiver functionalities and figures of merit. We now move our focus to methods for designing receiver systems that meet both selectivity and sensitivity requirements. This section will review the two most popular receiver architectures, heterodyne receivers and homodyne receivers. The contents of this section follow the reviews in [2.7].

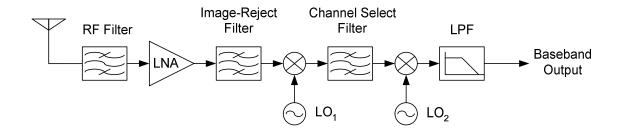

### 2.5.1 Heterodyne Receiver

The heterodyne architecture has been used in wireless receivers for almost a century and provides superior sensitivity and selectivity compared to other architectures [2.8]. The basic block diagram of the receiver is shown in figure 2.7. Immediately after the antenna, there is an RF bandpass filter, used to filter out-of-band signals, followed by a low-noise amplifier (LNA), an image-reject filter, an RF mixer, a channel select filter, an IF mixer, and finally a low-pass filter and baseband processor.

Figure 2.7 Heterodyne receiver architecture

The main concept of this architecture is that the frequency translation process is divided into two steps. The first is the transition of a signal from radio-frequency (RF) to the intermediate frequency (IF). The second is the frequency translation from IF to baseband. The channel filtering takes place at the IF frequency by a bandpass filter with *fixed* center frequency at the IF. This means that the channel selection takes place at the first mixing process by selecting the local oscillator (LO) frequency, such that the RF signal is shifted down by different amounts to locate the desired channel at the fixed IF. Performing channel filtering at the fixed IF frequency greatly relaxes the requirements on the channel-select filter. Channel filtering at the RF frequency would require a tunable RF filter with prohibitively high quality factor (Q).

The RF bandpass filter is a fixed-frequency filter that attenuates out-of-band signals. The low-noise amplifier then provides primary gain for the receiver front-end. As shown in section 2.2, this first block in the receiver chain (besides the bandpass filter) has significant impact on the overall noise in the system. Thus, the main objective of the LNA design is to provide large gain with minimal noise. The other constraint in the LNA design is that its input impedance must match the output impedance of the RF filter, which is usually 50  $\Omega$ .

Since the same frequency components at IF frequencies can be created by RF signals on both sides of the LO, an undesired image signal will be superimposed on the desired signal after the first mixing (figure 2.8). This image signal can be comparable in magnitude to the desired signal, and may obscure all the information if not treated properly. In this case, an image reject filter is used before the first mixing to attenuate the image of the desired RF signal.

Although the RF bandpass filter suppresses the image signal to some extent, it will be amplified by the LNA before mixing. This is why the image-reject mixer is placed immediately before the mixer. This filter also suppresses noise in the image band.

Figure 2.8 Image problem

The heterodyne architecture provides superior selectivity performance due to the benefits from including the IF stage. However, it requires many functional blocks in the system, and many of the blocks are very hard to integrate on-chip. For example, the image-reject and channel-select filters are difficult to implement on-chip due to the relatively low quality factor (Q) of the on-chip inductors. The need for additional off-chip components results in higher passive component costs, chip pin count, and extra board areas.

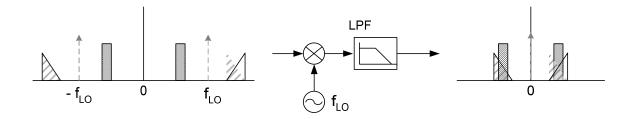

#### 2.5.2 Homodyne Receiver

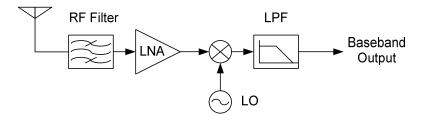

For a homodyne receiver (figure 2.9), the RF signal is downconverted directly to DC (or near-DC) by matching the LO frequency to the center frequency of the RF

passband. In the direct-conversion case, where the signal at RF is converted to baseband directly, the signal is placed on both sides of the LO frequency, as shown in figure 2.10. If complex modulation is used, which is more bandwidth-efficient, there will be garbling due to negative frequency components going to positive frequencies and vice versa, and an image-rejection mechanism will still be required. However, since the image is the mirror of the signal itself, the power level of the image is the same as the level of the desired signal. As a result, the image-rejection requirements can be relaxed and could be achieved with simple image-reject mixer architectures. In addition, since the channel filtering is now done at baseband, it is possible to implement it as a high-order on-chip low-pass filter.

Figure 2.9 Homodyne Receiver

Figure 2.10 Direct-conversion frequency plan

Direct-conversion systems, however, do have some serious problems not present in heterodyne systems. Because the signal is now mixed directly to DC, any DC offset in the receiver path can corrupt the desired signal or saturate the signal path. The unwanted DC offsets can be removed by placing an AC coupling capacitor at the mixer output. However, this may adversely impact the bit-error-rate, since the signal energy at DC will be removed as well. In high-bandwidth systems such as wireless LANs, the use of an on-chip AC coupling capacitor might be acceptable without significant penalties [2.9]. However, in a system with narrower channel bandwidths, the AC coupling capacitors, if used, are of such a size such that they must be placed off-chip [2.10]. Techniques used to reduce the DC content of the signal through coding or redefinition of the baseband signal can be used to alleviate this problem. Another approach to removing the offset is to use the training signal to estimate the existing DC offset. Based on this estimation, the offset can be removed or omitted from the mixer output [2.11]. However, this method does not address dynamic DC offset or 1/f noise problems.

An alternative technique for addressing the DC offset problem in the directconversion receiver is the use of low-IF architecture [2.12]. In this case, the RF signal is down-converted to a very low IF, instead of baseband. In this case, the DC offset problem is relaxed, since the power at DC can be removed by using an on-chip AC coupling capacitor without significantly affecting the desired signal. However, the image becomes a larger problem; in this case, the image power is set by the blocking profile and usually grows stronger as the frequency moves away from the carrier. To minimize the image rejection requirement, the IF frequency is usually not more than one or two channels away from the DC, where the blocker levels are still relatively low. All of the image rejection must be performed with a Weaver-like structure or polyphase filter (see next section) and this strongly depends on the matching between I and Q paths of the receiver. The other drawback of this architecture is that it requires higherbandwidth baseband blocks because the signal is now moved to a higher frequency.

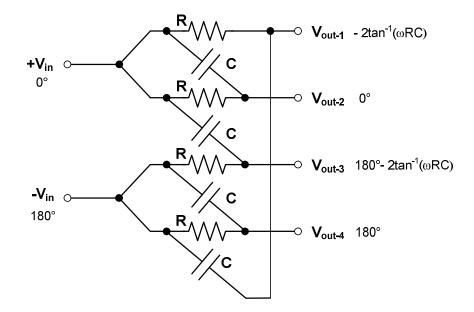

# 2.5.3 Image-Reject Mixers and Complex Filters

Several systems have been proposed to solve image problems in receivers without using an off-chip image-reject filter. These systems are called image-rejected architectures. The most common are Hartley image-reject mixers, Weaver image-reject mixers complex filters are reviewed in this section. More complete descriptions and analysis of these architectures can be found in [2.5], [2.13].

#### 2.5.3.1 Hartley Architecture

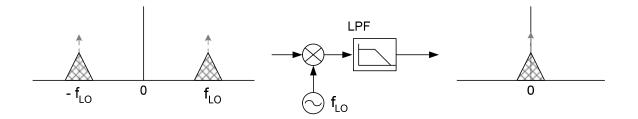

The Hartley architecture is shown in figure 2.11. Note that the 90° phase-shifter is a Hilbert transformer with the transfer function:

$$H(j\omega) = -j\operatorname{sgn}(n) \tag{2.27}$$

The multiplication of the RF signal with the 90° phase-shifted LO followed by the 90° degree phase-shift inverts the signal on one side of the LO, thus distinguishing the signal from the image. Adding this to the signal that is downconverted with nonphase-shifted LO leads to image-rejection. A disadvantage of this architecture is the need for a wideband phase-shifter that provides 90° phase shifts for the entire signal bandwidth.

Figure 2.11 Hartley Architecture

2.5.3.2 Weaver Architecture

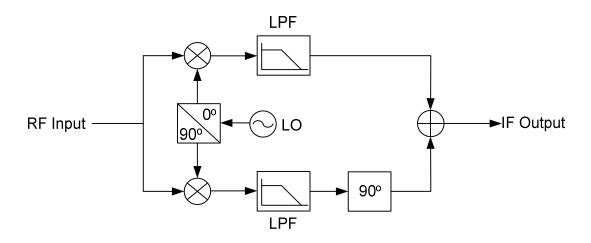

Figurer 2.12 Weaver Architecture

Unlike the Hartley architecture, the Weaver architecture uses two additional mixers placed after the low-pass filters to perform the phase-shifting instead of using a

wideband phase shifter. The RF signal is first downconverted to an intermediate frequency, then downconverted once again to the "final" IF. After the first down conversion, one path is multiplied by the sine wave, which is simply the phase-shifted cosine wave, equivalently downconverting the signal to the output frequency and phase-shifting it by 90° at the same time. The other path, which is multiplied by the cosine wave, is downconverted without the phase shift. As in the Hartley architecture, summing these two paths results in image rejection.

An advantage of using the Weaver architecture is that the wideband phase shifter is no longer needed. Although the 90° phase shifters for the LO quadrature signals are still needed, they are narrowband and easier to design.

#### 2.5.3.3 Complex Filters

Besides image-reject mixers, complex filters are important and are widely used in receiver designs, especially in low-IF architectures [2.14][2.15]. Complex filters use cross-coupling between the real and imaginary signal paths in order to realize filters with transfer functions that do not have the conjugate symmetry (in the frequency domain) of real filters. This implies that their transfer functions have complex coefficients. The filters can be realized using basic operations, i.e., addition, multiplication, and delay operations for discrete-time digital filters, or the integrator operator for continuous-time analog filters. More information on complex mixers is given in [2.13].

## 2.6 Multi-Band Receivers Using Broadband Front-End

A recent trend in the electronics industry has been to integrate many features, including multi-band multi-standards compatibility, in a single handheld device. This has created a need for receivers that are compatible with as many standards as possible. In this section, we will focus on preliminary architectures and issues in designing universal radio front-ends. We will begin by discussing the challenges in designing a broadband receiver. An important issue is that most existing receiver topologies are designed for a fixed single band, or only a few bands [2.16][2.17]. Next, we will investigate the possible implementations for a universal radio receiver using architectures modified from those presented earlier in this chapter. We will compare topologies in terms of their suitability for integration and multi-band capabilities. Finally, we will give a performance estimation of a broadband receiver based on the selected topology.

#### 2.6.1 Possible Front-end Implementations

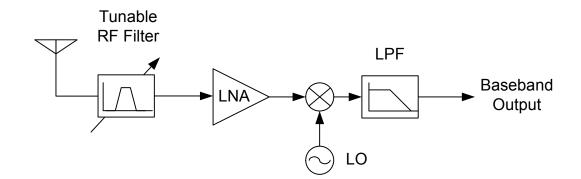

Unlike conventional narrow-band receivers, universal receiver front-ends must be able to detect and process signals at different frequency bands. Since the operations are still narrow-band, one way to implement the receiver is to use a high-*Q* tunable RF bandpass filter for frequency band selection, in conjunction with a broadband LNA and mixer, as shown in figure 2.13. The RF filter is required in order to attenuate any out-ofband jammers and relax the front-end linearity requirements. For example, the out-ofband jammers could be as high as 0 dBm for the GSM standard, as shown in figure 2.3. Such a high-Q tunable RF bandpass filter is difficult if not impossible to implement on a silicon substrate (such as CMOS IC) using current technology [2.5]. However, RF MEMS technology has shown promising results [2.18] and could become a commercially available option in the future.

Figure 2.13 A multi-band multi-mode receiver utilizing a tunable RF bandpass filter

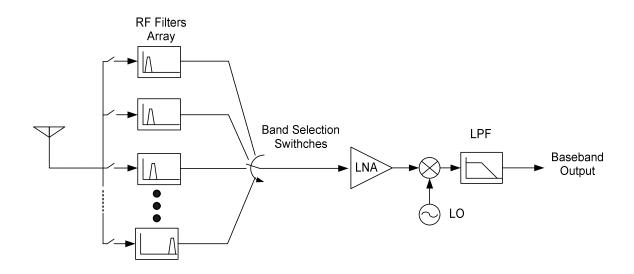

The need for a RF tunable filter can be avoided by implementing the "effective" tunable RF filter with several high-*Q* RF bandpass filters placed in parallel, each covering a frequency band for the intended application. Switches are needed to select which frequency band to use at a given time, as shown in figure 2.14. Although this method is acceptable for implementing a few narrow frequency bands, it would become impractical for generic universal radio or configurable radio, where the receiver must be able to operate in any band in the required frequency range. Moreover, these switches need to have low loss and high linearity at high frequency, both of which are not achievable by CMOS devices.

Figure 2.14 A receiver using multiple RF filters and switches

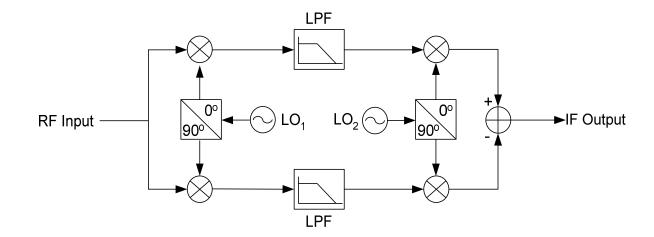

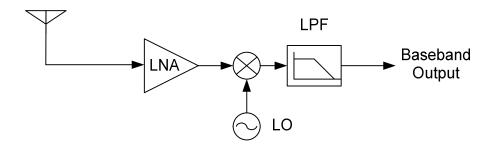

One straightforward solution for the problem of having too many RF bandpass filters is to not to perform any filtering at all. This leaves the broadband receiver with no bandpass filters in the front-ends, as shown in figure 2.15. Because there is no bandpass filtering, any large interfering signals can saturate the signal path or create intermodulation products that overtake the desired signal. For standards with stringent out-of-band jammer requirements (GSM, for example), having no out-of-band attenuation requires an extremely linear receiver front-end, which is very difficult, if not impossible, to implement in modern CMOS technologies. For some standards such as wireless LANs, there is no out-of-band blocking requirement for the standard, and the front-end linearity specifications can be relaxed. However, a high-linearity front-end is still desirable in this case due to possible jamming situations in real-world applications.

Active research has been done on implementing a receiver that can tolerate large out-of-band jammers without using filters. For example, an active filtering technique has been proposed for removing an out-of band blocker without using an extra SAW filter in [2.19]. The circuit employs a feed-forward filter path, and the high-Q characteristic of the filter is realized by using a translinear loop.

Figure 2.15 A broadband receiver with no RF bandpass filtering

If the receiver is broadband, there will be problems with harmonic distortion and harmonic mixing, as well as intermodulation distortion problems that also exist in narrow-band receiver front-ends. For example, if the intended receiving frequency can be anywhere from 0.5 MHz to 5 GHz, a strong signal at 0.8 GHz will create a third-order harmonic distortion at 2.4 GHz and will interrupt any desired signals at that frequency. Likewise, if the desired signal and LO are at 0.8 GHz (narrow channel bandwidth), a strong signal at 2.4 GHz will mix with LO harmonics locating at  $3f_{LO}$  and may corrupt the desired signal. Moreover, signals at 0.9 GHz and 2.4 GHz could mix and create an  $IM_2$  that corrupts any desired signals at 1.5 GHz. The problems of harmonic mixing and wideband harmonic distortion could be alleviated by:

(1) Using harmonic reject mixers that suppress harmonic mixing at near-LO harmonics such as at  $3f_{LO}$  at  $5f_{LO}$ . An example of such a mixer can be found in [2.20] and has been used in [2.21].

- (2) Employing differential circuits in the RF front-end paths to suppress evenorder harmonics or intermodulation.

- (3) Limiting the ratio between the highest and lowest frequency of the intended receiving signals to less than two by using a band-pass filter. In this case, harmonic distortions of an incoming signal will fall out-of-band and will not interfere with the intended receiving signal. In addition, any IM<sub>2</sub> from two strong in-band signals will fall out of band since their channel separation will always be less than the minimum intended receiving frequency. This relaxes the harmonic mixing problems as well.

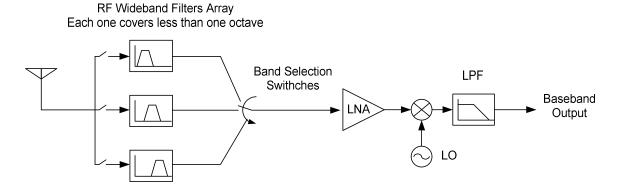

Option (3) could be modified for wider frequency band coverage by using multiple RF bandpass filters, each of which covers a "group" of bands, as shown in figure 2.16. For example, one might use a filter with 0.8 GHz to 1.5 GHz passband responses to avoid any mixing between 0.9 GHz and 2.4 GHz signals falling in-band, and use another filter covering 1.4 GHz to 2.7 GHz to process the signal at 2.4 GHz. Although this might appear similar to the architecture in figure 2.14, the number of required RF bandpass filters could be vastly different. For example, to cover the frequency bands from 0.5 GHz to 5 GHz, the number of filters needed in this topology would be only 4-6, no matter how many standards exist in the range. (The 4-6 variation is due to the amount of overlapping and the chosen frequency ratio.) However, this architecture would likely require out-of-band blocking and linearity requirements similar to those without any bandpass filter. If needed, multiple broadband LNAs can be used for signals from multiple frequency groups as well.

RF Wideband Filters Array Each one covers less than one octave Band Selection Swithches LNA LNA LO

Figure 2.16 A receiver with multiple "wideband" RF bandpass filter

## 2.6.2 Broadband Receiver Prototype Example

From the previous section, we can see that the key components are broadband front-end building blocks regardless of receiver topologies. In this section, we will examine the basic relationships between the receiver and building block specifications in a prototype receiver. As a derivative example, the specification requirements of the prototype will be based on multiple standards presented in Table 1.1. Starting with the architecture of the receiver prototype, we will then discuss system parameters such as noise figure, linearity, and dynamic range, as well as block-level specifications.

#### 2.6.2.1 Prototype Receiver Architecture

The conceptual diagram of the receiver can be simplified as shown in figure 2.17. In the figure, the major receiver building blocks include low-noise amplifiers (LNA), downconversion mixers, a frequency synthesizer (for LO signal generation), low-pass filters, variable-gain amplifiers (VGA), and analog-to-digital data converters (A/D).

Figure 2.17 Conceptual diagram of the receiver

In this lineup, the LNA is broadband, but it could be designed as one broadband LNA or several narrow band LNAs in parallel. The I/Q image-rejection mixers downconvert the incoming signal from RF to IF frequency.<sup>(1)</sup> The LO signal is supplied by the frequency synthesizer. The synthesizer needs a voltage-controlled oscillator (VCO) that has a wide frequency tuning range in order to work with multiple bands and standards [2.22]. Also, it is necessary to have a channel bandwidth adjustment scheme that accommodates different channel bandwidths for different standards. Channel bandwidth adjustments can be implemented using the direct conversion frequency plan with a tunable low-pass IF filter, or a low-IF architecture with a tunable bandpass IF filter. The first approach is simpler but may suffer from the problems with DC offset and 1/f noise, especially if the channel bandwidth is low, as in GSM standards [2.3]. The second approach, on the other hand, does not have low-frequency problems, but the filter design is more complicated and requires good image rejection. If needed, a low-pass filter with DC offset cancellation or AC blocking capacitors could also be used in a low-IF architecture. However, this would result in higher dynamic range requirements for the

(1) It should be noted that the above conceptual diagram shows only one mixer.

VGA and the A/D, since the adjacent channel blocker (located near DC at IF) will not be filtered out.

2.6.2.2 Basic System and Building Block Requirements

As an example, the targeted receiver requirements will be based on multiple standards shown in Table 1.1, and repeated below in Table 2.1 for important receiver requirements.

Table 2.1 Receiver requirements for different wireless standards

| Range               | WAN        |              | LAN        | PAN        | MAN         |

|---------------------|------------|--------------|------------|------------|-------------|

| System              | GSM/DCS    | UMTS         | 802.11a    | Bluetooth  | DECT        |

| Frequency           | 0.9/1.8GHz | 2GHz         | 5GHz       | 2.4GHz     | 1.9GHz      |

| Channel spacing     | 200KHz     | 5MHz         | 20MHz      | 1MHz       | 1.728MHz    |

| Rx NF               | 9dB        | 9dB          | 7.5dB      | 23dB       | 18dB        |

| Rx IIP <sub>3</sub> | -18dBm     | -4dBm        | -20dBm     | -15dBm     | -22dBm      |

| Phase noise         | -141dBc@3M | -150dBc@135M | -102dBc@1M | -105dBc@1M | -99dBc@2.2M |

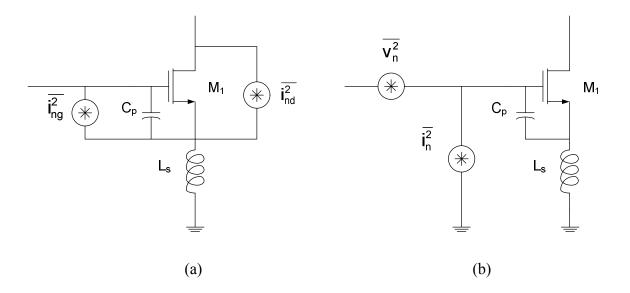

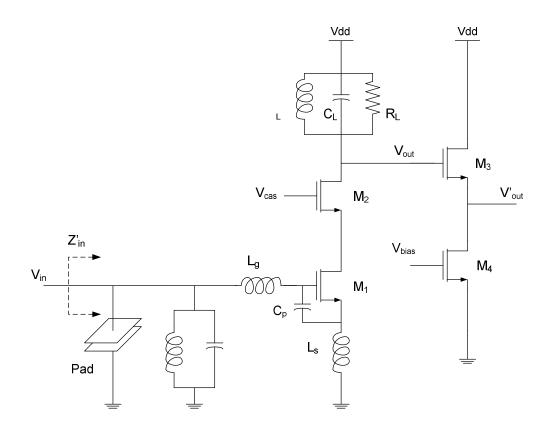

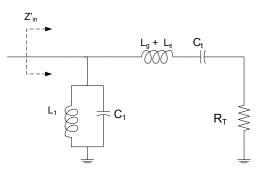

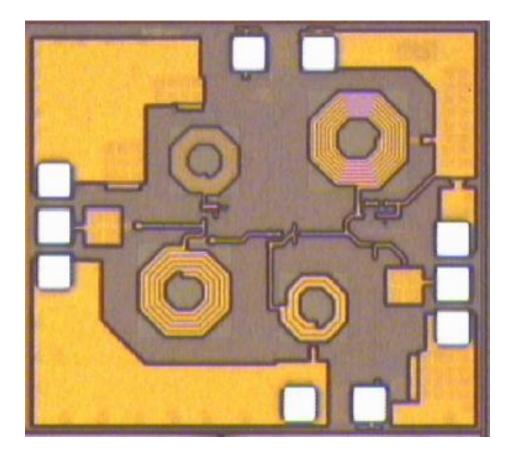

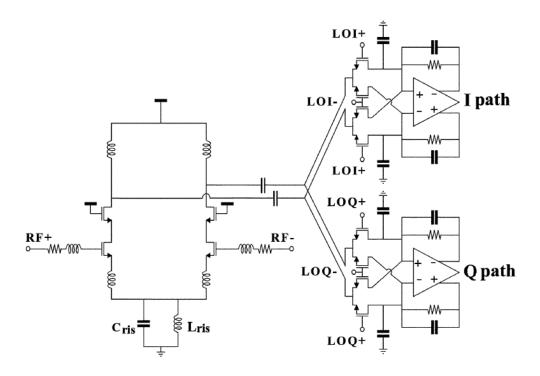

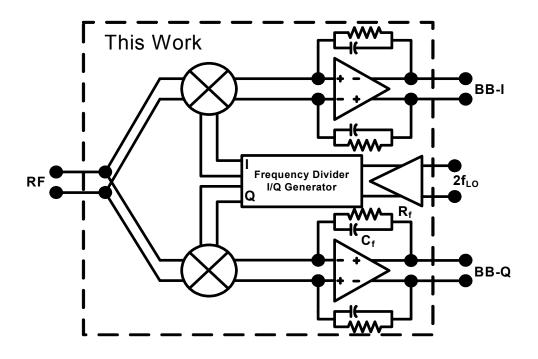

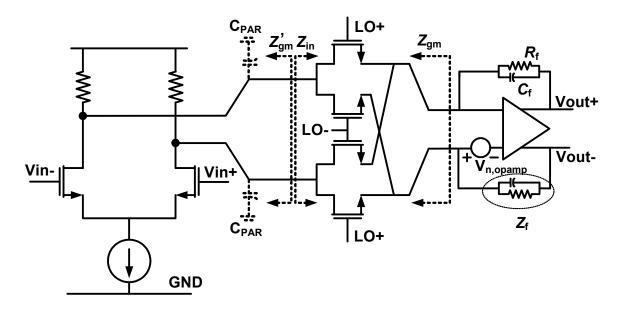

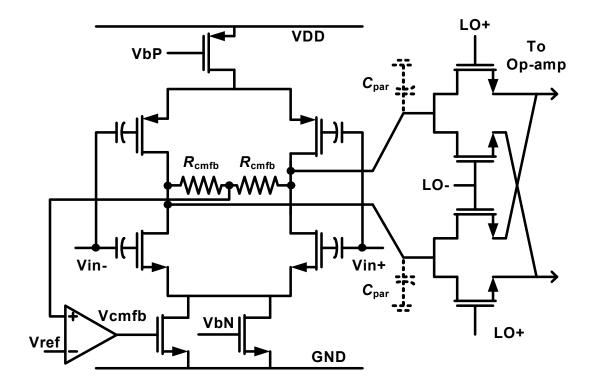

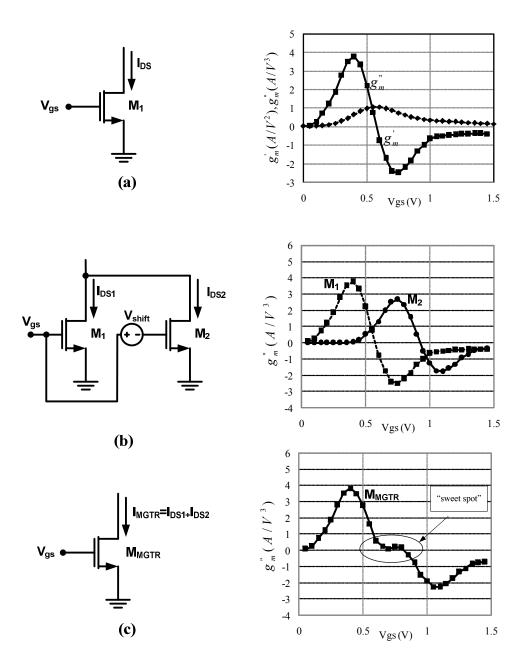

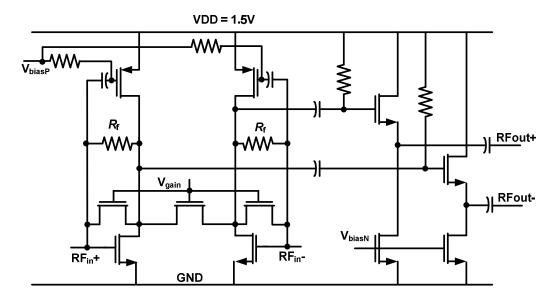

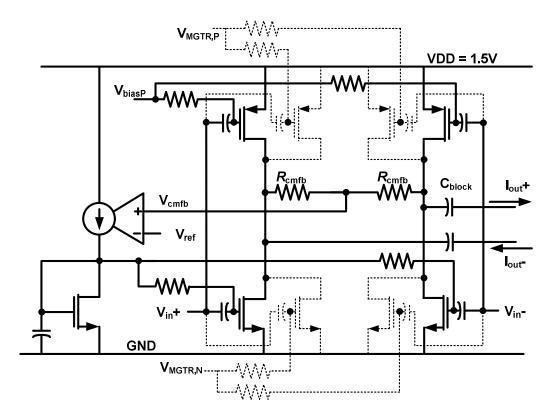

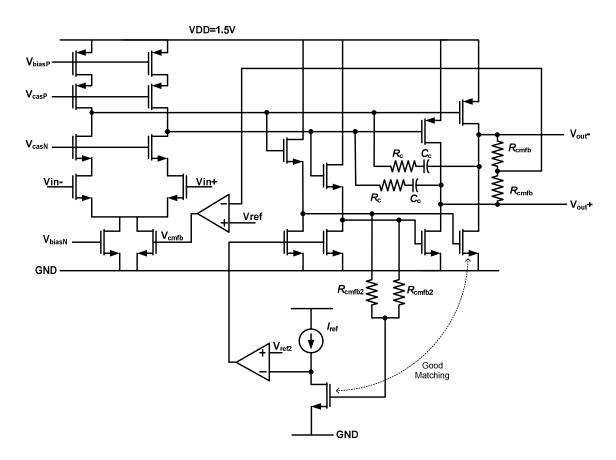

To meet the requirements of all the standards in Table 2.1, the receiver (not just the front-end) needs to have the following specifications: