## **Circuit Symmetries in Synthesis and Verification**

Donald Chai

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-115 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-115.html

August 12, 2009

Copyright 2009, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Circuit Symmetries in Synthesis and Verification

by

Donald Chai

B.S. (Cornell University) 2001 M.S. (University of California at Berkeley) 2004

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering-Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge: Professor Andreas Kuehlmann, Chair Professor Sanjit Seshia Professor Alper Atamtürk

Fall 2009

The dissertation of Donald Chai is approved:

Chair

Date

Date

Date

University of California, Berkeley

Fall 2009

## **Circuit Symmetries in Synthesis and Verification**

Copyright 2009 by Donald Chai

#### Abstract

#### Circuit Symmetries in Synthesis and Verification

by

Donald Chai

Doctor of Philosophy in Engineering–Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Andreas Kuehlmann, Chair

This dissertation explores the application of logical symmetries in the synthesis and verification of digital systems. Given a high-level description of a design, synthesis algorithms are employed to obtain a low-level description which is suitable for manufacture. To make the process computationally feasible, each step assumes a simplified model of the implementation platform. For example, many of the earlier steps disregard the fact that current technologies require that components are laid out in a two-dimensional plane, and therefore that the necessary wiring between components may become problematic. If the cost and performance requirements are not met, then the synthesis process is repeated, backpropagating the current results to refine any estimates for the next iteration.

Rather than forcing designers and tools to make early decisions with incomplete and/or inaccurate information, we propose the use of logical symmetries to defer some decisions until more information is available. For example, instead of assuming a fixed circuit structure, we may use symmetries to permute wires during the final stages of synthesis, when wirelengths are known, to improve the design's performance. In addition, symmetries can be used to eliminate redundant cases during verification. For example, in verifying a traffic light controller, one may often assume that the rules are identical for all four directions and simply check for one of them.

The first part of this dissertation reviews the necessary mathematical underpinnings of group theory, allowing us to efficiently reason about symmetries. With this background, we introduce our approaches to find symmetry in circuits.

The second part presents the application of symmetries in synthesis and verifica-

tion. We show how symmetries may be used in the technology mapping and placement stages, two major steps in synthesis. In technology mapping, we derive alternative representations of the design besides the local minimum obtained from technology independent optimization. In placement, we modify the circuit topology to reduce wirelength. In both cases, symmetries expand the design space with no loss in quality (assuming stable algorithms). Afterwards, we present our approach for improving so-called "symmetry breaking predicates" to speed up Boolean SAT solvers, which are heavily used in verification.

Professor Andreas Kuehlmann Dissertation Committee Chair

500

# Contents

| 1 | Intr                     | Introduction                                 |    |  |  |  |  |  |  |  |

|---|--------------------------|----------------------------------------------|----|--|--|--|--|--|--|--|

|   | 1.1                      | Contemporary Synthesis and Verification Flow | 2  |  |  |  |  |  |  |  |

|   |                          | 1.1.1 Synthesis                              | 3  |  |  |  |  |  |  |  |

|   |                          | 1.1.2 Verification                           | 7  |  |  |  |  |  |  |  |

|   | 1.2                      | Symmetry                                     | 8  |  |  |  |  |  |  |  |

|   | 1.3                      |                                              |    |  |  |  |  |  |  |  |

|   |                          | 1.3.1 Improving Technology Mapping           | 9  |  |  |  |  |  |  |  |

|   |                          | 1.3.2 Improving Placement                    | 10 |  |  |  |  |  |  |  |

|   |                          | 1.3.3 Accelerating SAT                       | 11 |  |  |  |  |  |  |  |

|   | 1.4                      |                                              | 12 |  |  |  |  |  |  |  |

|   | 1.5                      | Contributions of this Dissertation           | 14 |  |  |  |  |  |  |  |

|   | 1.6                      | Organization of this Dissertation            | 14 |  |  |  |  |  |  |  |

|   |                          | 0                                            |    |  |  |  |  |  |  |  |

| 2 | Perr                     | nutation Group Theory                        | 15 |  |  |  |  |  |  |  |

|   | 2.1                      | Basic Definitions                            | 15 |  |  |  |  |  |  |  |

|   |                          | 2.1.1 Groups                                 | 15 |  |  |  |  |  |  |  |

|   |                          |                                              | 18 |  |  |  |  |  |  |  |

|   |                          | 2.1.3 Permutation Groups                     | 19 |  |  |  |  |  |  |  |

|   | 2.2                      |                                              | 20 |  |  |  |  |  |  |  |

|   | 2.3                      |                                              | 22 |  |  |  |  |  |  |  |

|   |                          |                                              | 24 |  |  |  |  |  |  |  |

|   |                          |                                              | 25 |  |  |  |  |  |  |  |

|   | 2.4                      |                                              | 29 |  |  |  |  |  |  |  |

| 3 | Functional Symmetries 30 |                                              |    |  |  |  |  |  |  |  |

|   | 3.1                      |                                              | 33 |  |  |  |  |  |  |  |

|   |                          |                                              | 34 |  |  |  |  |  |  |  |

|   | 3.2 | Improved Graph Formulation for Single Outputs    35 |

|---|-----|-----------------------------------------------------|

|   |     | 3.2.1 Reducing $ V_M $ with Satisfy Counts          |

|   |     | 3.2.2 Reducing $ E $ with Satisfy Counts            |

|   |     | 3.2.3 Reducing $ V_M $ with Unateness               |

|   |     | 3.2.4 Combining Transformations                     |

|   | 3.3 | Multiple-output Functions                           |

|   | 3.4 | Experimental Results                                |

|   | 3.5 | Previous Work                                       |

|   |     | 3.5.1 Spectral Methods                              |

|   |     | 3.5.2 Minterm Comparison 47                         |

|   | 3.6 | Previous Work for Other Types of Symmetry 48        |

|   | 3.7 | Conclusion                                          |

|   |     |                                                     |

| 4 | Sym | metries in Circuits 50                              |

|   | 4.1 | Boolean Networks51                                  |

|   | 4.2 | Structural Symmetries of Boolean Networks           |

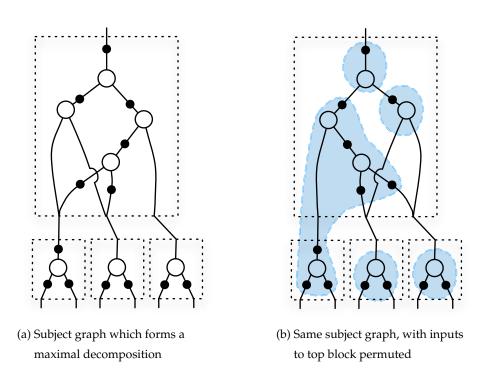

|   | 4.3 | Structural Symmetries of Maximal Decompositions     |

|   |     | 4.3.1 Reduction to Graph Automorphism               |

|   |     | 4.3.2 Polytrees                                     |

|   | 4.4 | Applications in CAD                                 |

|   |     | 4.4.1 Technology Mapping                            |

|   |     | 4.4.2 Placement                                     |

|   |     | 4.4.3 Boolean Satisfiability                        |

|   | 4.5 | Decomposition Heuristic                             |

|   | 4.6 | Conclusion                                          |

|   |     |                                                     |

| 5 |     | nnology Mapping 71                                  |

|   | 5.1 | Introduction                                        |

|   | 5.2 | Previous Improvements in Technology Mapping         |

|   |     | 5.2.1 Cuts, Boolean Matching, and DAG covering      |

|   |     | 5.2.2 Choices and Supergates                        |

|   | 5.3 | Creating Choices Through Symmetry 79                |

|   |     | 5.3.1 AND/XORs                                      |

|   |     | 5.3.2 Prime Functions                               |

|   | 5.4 | Experimental Results                                |

|   |     | 5.4.1 AND Trees                                     |

|   |     | 5.4.2 Prime Functions                               |

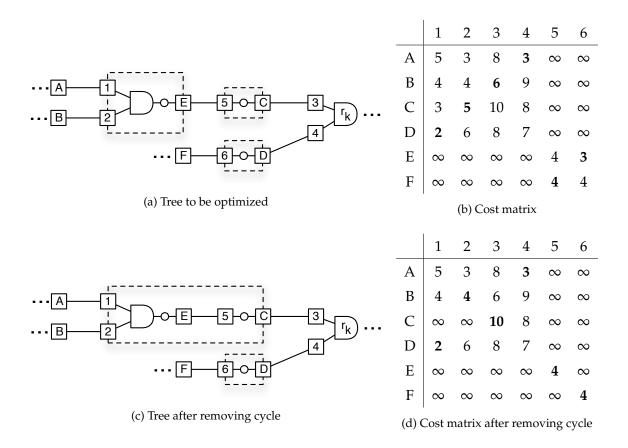

|   | 5.5 | Previous Work with Symmetries                       |

|   | 5.6 | Conclusion                                          |

| 6 | D1- |                                                     |

| 6 |     | 97 Introduction                                     |

|   | 6.1 |                                                     |

|   | 6.2 |                                                     |

|   | 6.3 | Preliminaries                                       |

|   |     | 6.3.1 Circuit Model                                 |

|              | 6.3.2 Assignment Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.4          | Rewiring Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 102 |

|              | 6.4.1 Leaf Rewiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 102 |

|              | 6.4.2 Tree Restructuring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 103 |

| 6.5          | Iterative Placement with Rewiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 6.6          | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 107 |

|              | 6.6.1 Post-placement Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107 |

|              | 6.6.2 Integration into Iterative Placer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108 |

|              | 6.6.3 Timing-driven Rewiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110 |

|              | 6.6.4 Industrial Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 112 |

| 6.7          | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 112 |

| 7 <b>Boo</b> | lean Satisfiability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 116 |

| 7.1          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 116 |

| 7.2          | Preliminaries and Previous Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 120 |

| 7.3          | Strong Symmetry Breaking Predicates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 121 |

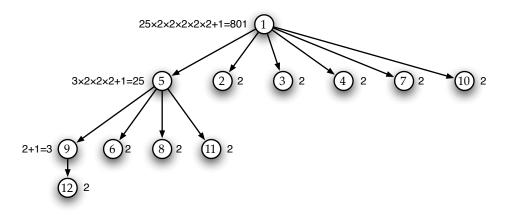

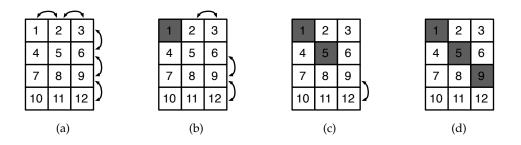

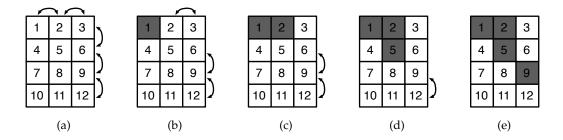

|              | 7.3.1 Motivation for Strengthening                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 122 |

|              | 7.3.2 Desired Traits of SBPs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 124 |

| 7.4          | Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 127 |

|              | 7.4.1 Jerrum Branching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 127 |

|              | 7.4.2 Base Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 128 |

|              | 7.4.3 Permutation Simplification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 131 |

|              | 7.4.4 Variable Reordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 132 |

| 7.5          | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 134 |

| 7.6          | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 138 |

| 8 Cor        | clusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14( |

| 8.1          | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14( |

| 8.2          | Strengths and Weaknesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 141 |

|              | rranhy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 143 |

| Bibliog      | hapity and the second se | TT  |

Two copies of a subregion of the Penrose tiling P3. This tiling is aperiodic, that is, it has no translational symmetry. However any finite subregion appears infinitely often. The overlap between the two copies illustrates this repetition.

#### Acknowledgments

I would like to thank my advisor Andreas Kuehlmann, who showed me all I know about the research process, from the brainstorming of new ideas to the dissemination of findings to the community at large. A large part of my training has been on the crisp formalization of results. To this day, I do not consider an idea well thought out until it has been well exposited.

I would also like to thank the other members of my dissertation committee, Sanjit A. Seshia and Alper Atamtürk. Professor Seshia is a source of inspiration for me, with his boundless enthusiasm for research. Professor Atamtürk has been a wonderful teacher, and his theoretical and practical approaches to optimization have helped greatly in my research.

In addition, I would like to thank Robert K. Brayton, who had served on my qualification exam committee and co-advised me during my first year at Berkeley. His words have inspired some of the work in Chapter 5.

Besides the professors, one of the advantages to attending a world-class university is in the quality of students that one is able to interact with. I am grateful for the opportunity to meet the students in the DOP center and elsewhere in the department; they have helped me grow both as a researcher and as a human.

The administrative staff at Berkeley have always been a great help in filing paperwork. In particular, I would like to thank Jennifer Stone and Ruth Gjerde for going beyond the normal call of duty and keeping me from panicking over deadlines.

Finally, various other researchers have greatly assisted in performing the research in this dissertation. I would like to thank Alan Mishchenko for his aid in the use of his ABC program, and Kai-Hui Chang and Igor Markov for their help with portions of UMpack (i.e., PhySyn). I would also like to thank Philip Chong for his assistance in running our tool on industrial designs.

500

# 1. Introduction

Symmetry, as popularly understood, is the property of self-similarity or invariance under various geometric transformations. A sphere remains the same no matter which way it is rotated. Likewise, a dome remains the same no matter which way it is rotated about the vertical axis. In structural engineering, this property of self-similarity lends strength to a physical system and simplifies design and analysis:

- A basic principle of structural engineering is that all forces and torques in a system must sum to zero to maintain static equilibrium—a nonzero net force implies that the structure is accelerating (i.e. falling). Symmetry guarantees that the top of a dome experience zero net horizontal force.

- Supposing we have a correct design for an arch (a 2-dimensional dome), it is a simple matter to create a dome by superimposing multiple arches which are rotated about the vertical axis.

Exploiting such symmetry is thus one of the reasons why the Roman Pantheon still stands 1900 years after it was built.

Many things in the physical world possess symmetries with respect to one property, but are asymmetric with respect to another. A vase still functions as a vase when rotated about a vertical axis, but one side may be more attractive than another and thus chosen to face the potential viewer. In erecting a building, commodities which are *mostly* interchangeable may be allocated in order to maximize some objective: Miyamoto Musashi's master carpenter assigns material and personnel to best suit the necessary tasks [Miy82]. If Musashi's carpenter faces a new team of workmen, he may first assign them using the information currently available to him, and later reassign the workers as he discovers their specialties. Fortunately for the carpenter, late personnel changes are relatively easy to make.

This dissertation explores the application of logical symmetries in the synthesis and verification of digital systems. As we have just seen, knowledge of symmetries allows us to *enlarge* the design space for various optimization problems (positioning of vase), and to *shrink* the search space for others (analysis of dome).

**Outline of this Introduction.** To motivate for our work, we first briefly review the steps taken in a traditional electronic design and verification flow which uses computed-aided design (CAD) tools. Then we describe the concept of symmetries as used in this dissertation, and provide examples in which symmetries may be exploited in the CAD flow.

### 1.1 Contemporary Synthesis and Verification Flow

Given a high-level description of an electronic system, a variety of algorithms are usually employed to arrive at (or "synthesize") a low-level description which is suitable for manufacture on a target platform. Naturally, the final implementation must satisfy certain constraints and optimize certain objectives over cost and performance.

In the case of the Pantheon, Apollodorus of Damascus was given a description, "temple", and synthesized a set of blueprints which could be communicated to craftsmen and which minimized the amount of granite required for construction. The design needed to be verified to ensure that it indeed correctly implemented "temple", and did not instead implement "pile of rubble".

In a digital design scenario, a designer may write a set of Boolean equations describing the behavior of a traffic light controller, and then use synthesis tools to produce a layout of polygons to be drawn on a silicon wafer. Verification tools are used to ensure that the initial set of equations do not allow traffic flows to intersect, and that the final layout is a valid refinement of the initial set of equations.

To make the synthesis task computationally feasible, the process is divided into a series of smaller steps, each of which assumes a simplified model of the final implementa-

tion platform. For example, many of the earlier steps disregard the fact that current target platforms require components to be laid out in a two-dimensional plane, and therefore that the necessary wiring between components may become problematic. If the desired cost and performance requirements are not met, then the synthesis process is repeated, backpropagating the current results to refine the estimates for the next iteration. Many iterations may be required to achieve so-called "design closure".

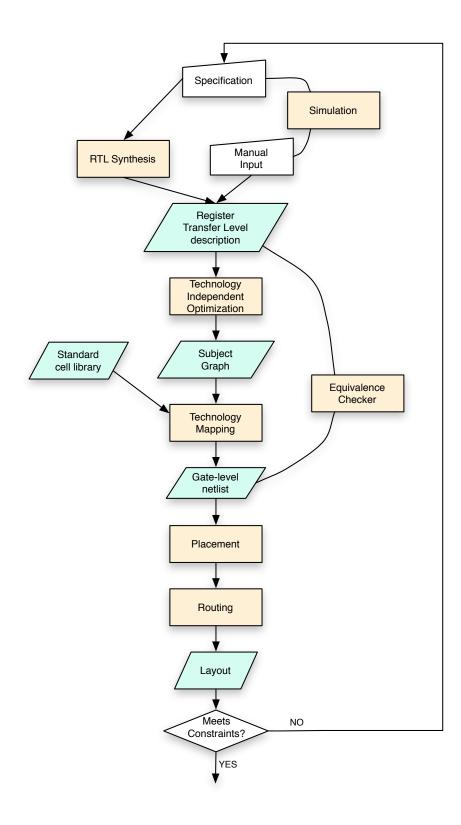

Figure 1.1 shows one possible demarcation of a typical CAD flow for application specific integrated circuits (ASICs), which we will adhere to in the following description. Industrial-scale CAD flows usually consist of many "point tools" which are applied in succession—our description will focus on a few of the major steps. For reference, the introductory chapter of [DGK94] illustrates a similar CAD flow with a different emphasis.

#### 1.1.1 Synthesis

Consider the function *f* that evaluates to true iff two or three of its four inputs *a*, *b*, *c*, *d* are true. The designer provides the following register transfer level (RTL) description:

$$f(a, b, c, d) = \bar{a}\bar{b}cd + \bar{a}b\bar{c}d + \bar{a}bc\bar{d} + \bar{a}bcd + a\bar{b}c\bar{d} + a\bar{b}c\bar{d} + a\bar{b}cd + ab\bar{c}\bar{d} + abc\bar{d} + abc\bar{d}$$

Here  $\bar{a}$  denotes the negation of binary variable *a* (alternatively  $\neg a$ ). The expressions *ab* and a + b denote the Boolean AND ( $a \land b$ ) and OR ( $a \lor b$ ) operations, respectively.

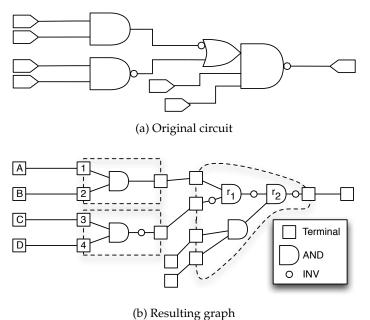

The **technology-independent optimization** stage transforms the above RTL into a **subject graph** consisting of two-input AND and one-input INV (also known as NOT) primitives. As implied by its name, this stage uses a cost model which is independent of target technologies, but shows *some* correlation to the final implementation cost. For our purposes, let the cost of a subject graph be the number of AND primitives in the graph.

Our synthesis tool first simplifies the sum-of-products (SOP) expression we provided by reducing the number of product terms by using an algorithm such as ESPRESSO [BHMSV84]. One possible minimal Boolean expression for f is:

$$f(a, b, c, d) = a\bar{b}c + a\bar{c}d + a\bar{d}b + \bar{a}cd + \bar{a}bd + \bar{a}bc$$

This expression is minimal with respect to the number of sum terms. A different minimal expression might be:

$$f(a, b, c, d) = a\bar{b}d + a\bar{b}c + ab\bar{d} + \bar{a}bc + b\bar{c}d + \bar{b}cd$$

Figure 1.1: Typical CAD flow

The two expressions represent the same function, but are different: the variables appear a different number of times in each. If the values for *a* and *b* arrive at different times, one expression may lead to a faster implementation than the other. However, without further information, the synthesis tool can arbitrarily choose either of these as a minimal representation of the function.

Suppose we choose the first SOP. Let us define a **literal** to be a variable or its negation. We extract common factors from the expression to minimize the total number of literals, and reexpress the function as a **Boolean network**, where each **node** implements a local function:

$$y_1 = c + d$$

$$y_2 = cd + by_1$$

$$y_3 = \bar{b}c + \bar{c}d + \bar{d}b$$

$$f = ay_3 + \bar{a}y_2$$

A number of methods may be applied to minimize the network in terms of literal count or the longest path from inputs to output. We ignore them in this discussion because they are not relevant. In our example, the extraction reduced the literal count from 18 to 16.

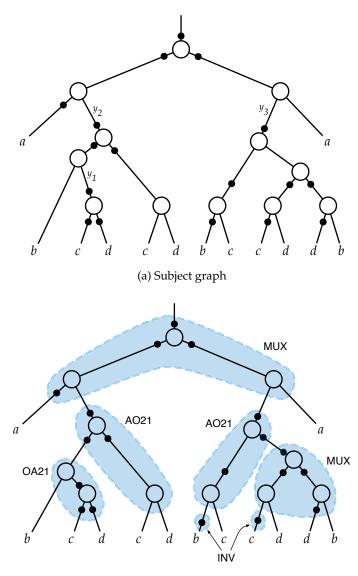

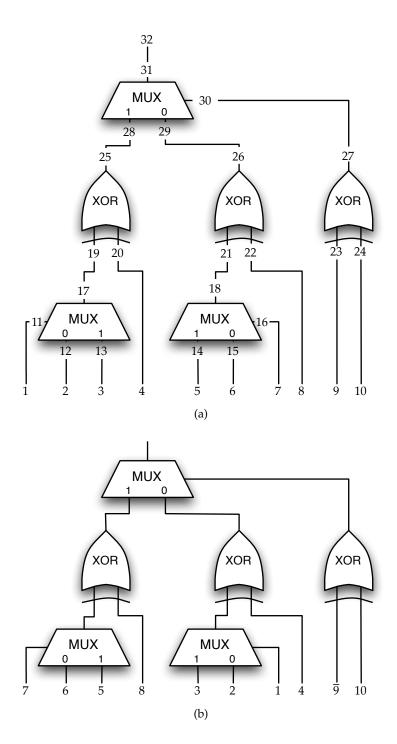

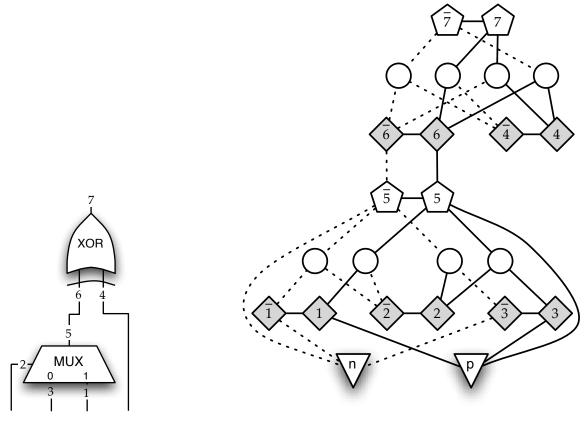

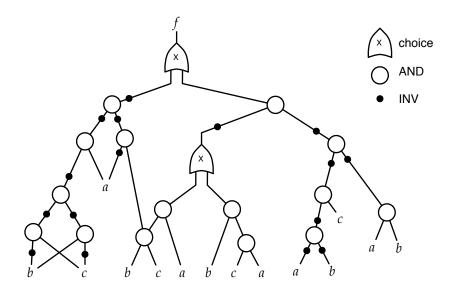

Given a Boolean network, we convert it into a subject graph (shown in Figure 1.2a) by decomposing each of the constituent nodes into AND and INV primitives. Each product (sum) of more than 3 literals (terms) is arbitrarily decomposed into a tree of AND primitives.

From a subject graph, we find an implementation consisting of standard cells. This is called **technology mapping** (or **library binding**). For example, provided a library containing the following five cells

| Cell Name                  | Function                  |

|----------------------------|---------------------------|

| $INV(x_0)$                 | $\bar{x}_0$               |

| $AO22(x_0, x_1, x_2, x_3)$ | $x_0x_1 + x_2x_3$         |

| $AO21(x_0, x_1, x_2)$      | $x_0 x_1 + x_2$           |

| $OA21(x_0, x_1, x_2)$      | $(x_0 + x_1)x_2$          |

| $MUX(x_0, x_1, x_2)$       | $x_0 x_1 + \bar{x}_0 x_2$ |

we may instantiate cells as in the blue (or shaded) blobs in Figure 1.2b. Each instance of a library cell requires some area, and the technology mapper may aim to find a mapping

(b) Mapping to cell library

Figure 1.2: A subject graph and a potential mapping. Black circles are NOT primitives, larger circles are AND primitives. Pairs of NOTs may be added to allow more cells to match. which requires the least total cell area. If the only nodes in the subject graph with outdegree greater than 1 are the input nodes, the technology mapping problem for minimal area is solvable in polynomial time [Keu87]. Otherwise, the problem is  $\mathcal{NP}$ -hard [KR89].

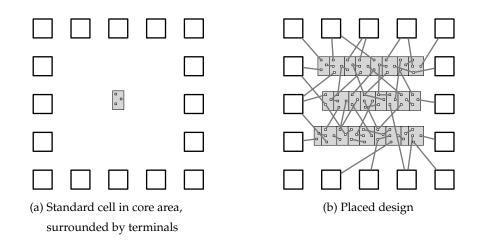

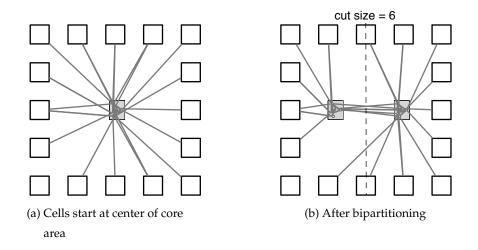

After a Boolean network is mapped into a set of standard cells, the standard cells need to be placed on the plane and wires (interconnect) need to be added to connect the cells. **Placement** and orientation of the cells is a strong factor in determining whether a feasible wiring exists, and if so, the length of the interconnect. Since the delay of a wire is roughly proportional to the square of its length, placement also determines the speed of the final circuit.<sup>1</sup> Thus, placement algorithms typically place the cells so as to minimize the total estimated wirelength. In estimating wirelength, we assume that many wires may pass over the same point, which may not be correct. The actual wirelength is not known until the next stage (**routing**).

At each step of the mapping from Boolean expression to network of standard cells, the synthesis program makes an arbitrary choice, all other things being equal. Rather than forcing designers and tools to make early decisions with incomplete and/or inaccurate information, we propose to use logical symmetries to defer some of the decisions until more information is available. As we will later show, certain symmetries may be analyzed in an efficient manner. Thus, deferring these decisions will not significantly increase the complexity of the synthesis task.

#### 1.1.2 Verification

The results of each step of the synthesis flow must be verified against results from previous steps to guard against errors due to computer bugs or human error. Boolean satisfiability (SAT) forms the cornerstone of many modern verification tools, for example bounded model checkers [BCCZ99] and combinational equivalence checkers [SBSV96]. While the SAT problem is  $\mathcal{NP}$ -complete, recent advances in SAT solving technology make current solvers scalable for many practical problems [MMZ<sup>+</sup>01, ES03]

Regardless, current solvers are based on the Davis-Putman-Logemann-Loveland (DPLL) algorithm [DP60, DLL62], and thus require exponential runtime to solve many problems which are otherwise solvable in polynomial time [Hak85, Urq87].

<sup>&</sup>lt;sup>1</sup>A long wire may be segmented with buffers (also known as repeaters), to improve delay, but this carries with it other costs.

#### 1.2 Symmetry

As we have stated previously, symmetry is the property of invariance under certain transformation. We will also use the term "symmetry" to refer to any such transformation. For a Boolean function, we define symmetry to be invariance of the function under permutation and/or negation of its inputs and/or outputs. This is often referred to as group invariance in the classical literature [McC56], and NPN-equivalence in more recent literature [Mur71, MM90]. For example, the XOR function

$$f = abc\bar{d} + ab\bar{c}d + a\bar{b}cd + a\bar{b}c\bar{d} + \bar{a}bcd + \bar{a}b\bar{c}d + \bar{a}\bar{b}c\bar{d} + \bar{a}\bar{b}c\bar{d}$$

contains a wealth of symmetries. The inputs may be arbitrarily permuted, and any even number from the set of inputs and output may be negated, e.g. inverting *a* and the output does not change the function:

$$f = \bar{a}bc\bar{d} + \bar{a}b\bar{c}d + \bar{a}\bar{b}cd + \bar{a}\bar{b}c\bar{d} + abcd + abc\bar{d} + a\bar{b}c\bar{d} + a\bar{b}c\bar{d}$$

As is the case with other symmetries, **functional symmetries** have the important property that they form a group (in the mathematical sense), that is, any sequence of symmetries may be applied to a function without changing the function. Thus while there are  $n!2^n$  valid transformations of the XOR function, we may efficiently manage and manipulate them using results from group theory. For example, we can represent each valid transformation by a composition of elements drawn from a set of *n* transformations, also known as a generating set.

When reasoning about a logical circuit consisting of multiple levels of logic, the situation is different. Let us refer to the Boolean network for the synthesis example, in which f evaluates to true iff two or three of a, b, c, d are true:

$$y_1 = c + d$$

$$y_2 = cd + by_1$$

$$y_3 = \bar{b}c + \bar{c}d + \bar{d}b$$

$$f = ay_3 + \bar{a}y_2$$

We have already established that the input variables of the function may be arbitrarily permuted without changing the function. In the Boolean network, this might mean, for example replacing every instance of *a* with *b* and every instance of *b* with *a* as follows:

$$y'_1 = c + d$$

$$y'_2 = cd + ay'_1$$

$$y'_3 = \bar{a}c + \bar{c}d + \bar{d}a$$

$$f' = by'_3 + \bar{b}y'_2$$

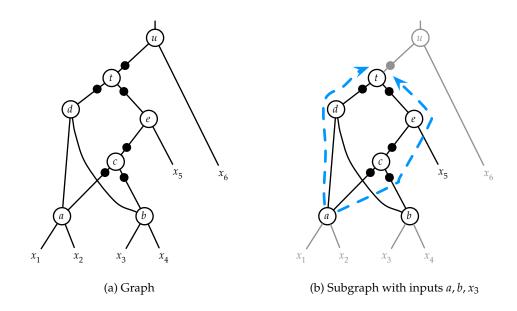

Since there are intermediate variables in a Boolean network, we can do more than simply modify connections to the primary inputs a, b, c, d for the global function. We may also take any subgraph of the Boolean network, find its functional symmetries, and modify the local connections accordingly. For example, the output of the subgraph encompassing nodes  $y'_1$  and  $y'_2$  is true iff one or two of a, c, d are true—any of the 6 permutations of a, c, dare correct. The following shows the result after swapping a with c:

$$y_1'' = a + d$$

$$y_2'' = ad + cy_1''$$

$$y_3'' = \bar{a}c + \bar{c}d + \bar{d}a$$

$$f'' = by_3'' + \bar{b}y_2''$$

The nodes for  $y'_3$  and f' are unchanged.

Since many subgraphs may be drawn from a Boolean network, subject graph, or logical circuit, there are ample opportunities to find symmetry—even if a circuit's global function contains none, many of its local functions contain symmetries.

Having established the notion of symmetry in logical circuits, we now provide examples where synthesis and verification may be improved with its use.

## **1.3 Better CAD through Symmetry**

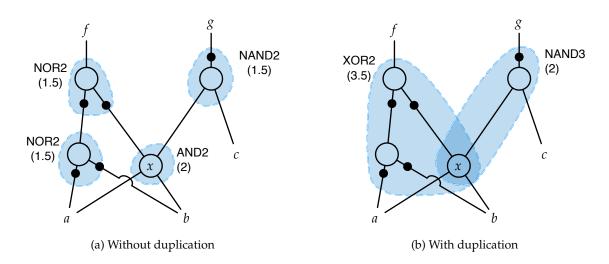

#### 1.3.1 Improving Technology Mapping

The problem with the traditional approach to technology mapping is that the choice of subject graph may cause the resulting mapping to be suboptimal. In the same way that our language shapes our thoughts, the structure of the subject graph has an effect on the final mapping—any instance of a standard cell in the final mapping must correspond to a

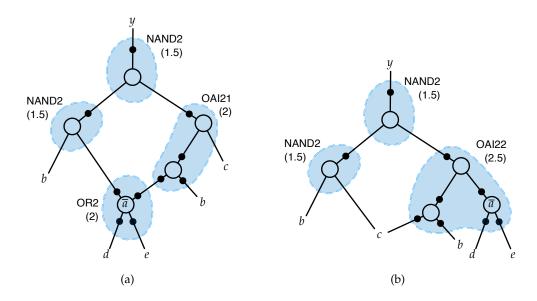

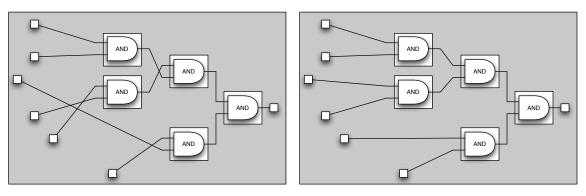

Figure 1.3: Permuting subgraph nodes according to symmetry creates an additional mapping option. Black circles are NOT primitives, larger circles are AND primitives.

subgraph in the subject graph. Thus, any given subject graph allows only a certain set of mappings.

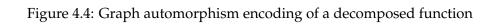

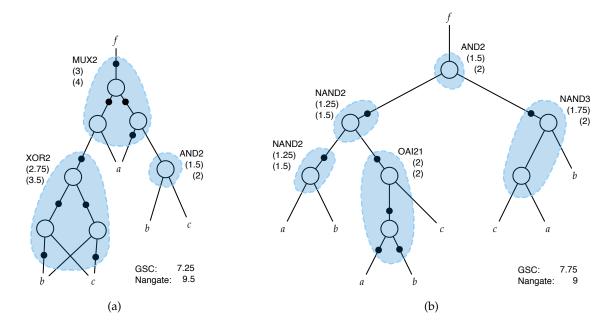

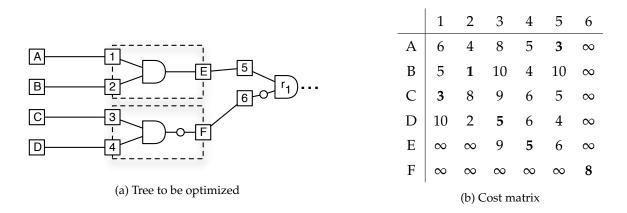

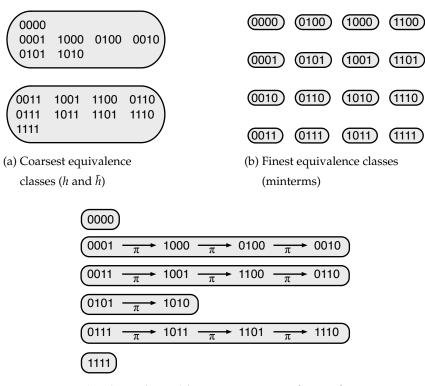

Figure 5.5a shows a subject graph, where the small black circles are INV primitives, the larger circles are AND primitives, and each shaded region represents a subgraph implemented by a standard cell. By analyzing the symmetries of the subject graph, we find that we can swap *a* and *c*, resulting in Figure 5.5b, which leads to a smaller circuit.

Other modifications to the subject graph are clearly possible, and may result in a smaller circuit as well, but may require repeating some of the technology independent optimization steps. However, iteration is precisely what we are trying to avoid. Chapter 5 describes our approach more fully.

#### 1.3.2 Improving Placement

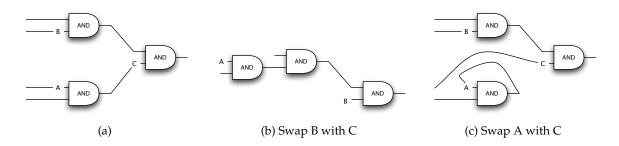

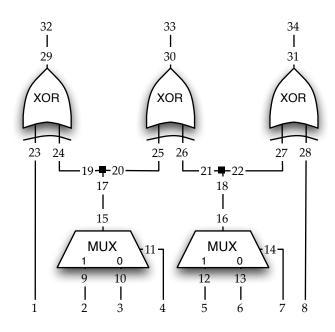

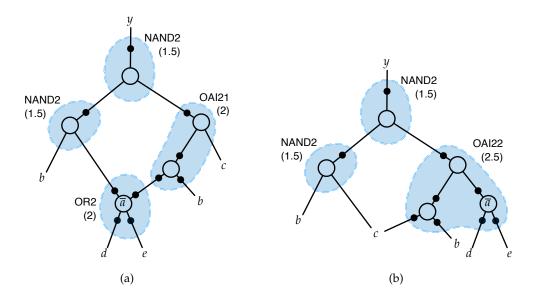

During the placement stage, we take a network of standard cells and assign the cells to non-overlapping locations in the plane so as to minimize the total estimated wirelength. Figure 1.4a shows a placement of five cells which is optimal assuming that the six inputs and output are fixed, and that the gray region is occupied by other (immobile) cells. The

(a) Placed design before restructuring

(b) After restructuring

Figure 1.4: Restructuring a placed design may reduce wirelength.

subcircuit implements a 6-input AND, and we may reassign the connections as long as this functionality is preserved. Figure 1.4b shows the same circuit after having reassigned the connections optimally. Connections to and connections among other cells are not modified, therefore the total estimated wirelength has decreased.

For efficiency, placement algorithms assume that the connectivity of the circuit is fixed. Wirelength may be improved if connections may be modified, either

- after the placement is determined, as in the above example, or

- during the placement step.

Alternatively, a circuit may be modified after placement using **resynthesis** [LESJ98] or **redundancy addition and removal** [JKCMS97]. The difference is that symmetry-based restructuring is more efficient, which allows its use *during* placement. Our restructuring algorithm is described in Chapter 6.

#### 1.3.3 Accelerating SAT

Boolean satisfiability solvers, besides being workhorses in verification, are also increasingly used for various synthesis tasks [NSR99, SVBY06, LJL08] which are in  $\mathcal{NP}$  (or co- $\mathcal{NP}$ ) but for which no polynomial time algorithm is known. Thus any improvements in SAT solving technology would have a great effect on many different stages of the CAD flow. The DPLL algorithm [DP60, DLL62] used in all complete SAT solvers combines a branch-and-bound search with the resolution rule of logic. At each step of the search, a SAT solver assigns a value to some variable which has not already been assigned one. If any of the constraints are not satisfied, modern solvers record a nogood [SS77] using the resolution rule [MSS99] and subsequently backtrack.

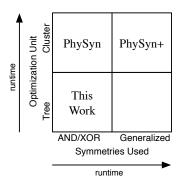

Suppose we are given an instance of the pigeonhole problem with 11 pigeons and 10 holes, and are told to assign each pigeon to a hole without sharing. After we encode the instance as SAT and input the instance to a SAT solver, the solver:

- puts pigeon 1 in hole 1 and fails to assign the remaining 10 pigeons to the remaining 9 holes,

- puts pigeon 1 in hole 2 and fails to assign the remaining 10 pigeons to the remaining 9 holes,

- puts pigeon 1 in hole 3 and fails to assign the remaining 10 pigeons to the remaining 9 holes,

- ...

- puts pigeon 1 in hole 10 and failing to assign the remaining 10 pigeons to the remaining 9 holes, finally quits.

Since the pigeons and holes are identical, we can safely conclude that the problem is unsatisfiable after putting pigeon 1 in hole 1, and not try putting pigeon 1 in any other hole. Then, we assume without loss of generality that pigeon 2 is in hole 2, and so on. Using this reasoning, we can prove unsatisfiability in linear time rather than in exponential time [Hak85].

The general approach which we will follow is that of [CGLR96], which adds **symmetry breaking predicates** to a SAT formula in order to eliminate redundant parts of the search space. Chapter 7 describes our approach to formulate symmetry breaking predicates.

## 1.4 Challenges to Solve

Since our proposed approach of using symmetries is one of many competing solutions for solving the synthesis and verification problems, we must tackle the perennial tradeoffs

Figure 1.5: Symmetries within a circuit do not form a group.

between quality of results and runtime.

- The problem of finding symmetries in Boolean functions has not been completely solved. Current solutions either specialize for the case of functions with one output [AP05, CK06, ABPS07, KK08] or reduce the problem to an instance of graph isomorphism using an exponentially-sized graph [CMB05a].

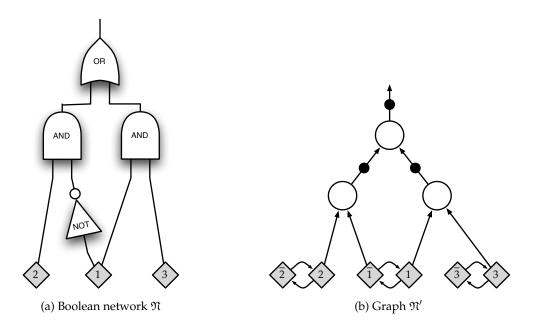

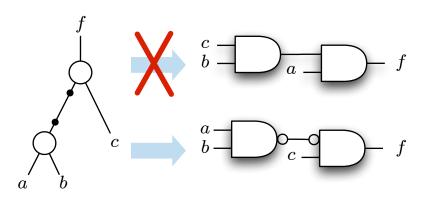

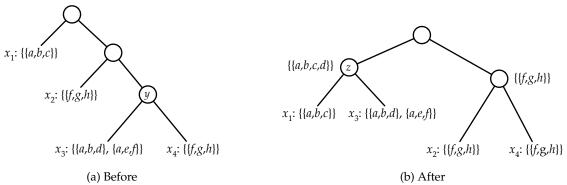

- Symmetries within a circuit do not form a group. In the circuit in Figure 1.5a, connection A may be swapped with connection B, and connection B may be swapped with connection C Figure 1.5b. However, swapping A with C is incorrect, because it creates a cycle (Figure 1.5c). Thus, algorithms to reason about functions cannot be used without modification for circuits.

- A large number of subgraphs can be extracted from any Boolean network, subject graph, or logical circuit for analysis of symmetries. Finding all symmetries may not be practical, and therefore we must isolate those which provide the most potential for optimization.

- After finding symmetries, we must be able to efficiently apply them in synthesis. Explicit enumeration of permutations is not practical.

- The use of symmetries in SAT is purely to reduce the amount of time needed to solve a given SAT formula. It is possible that finding symmetries or generating effective symmetry breaking predicates may take longer than solving the SAT problem directly to begin with. Another possibility is that the augmented SAT problem may be more difficult to solve due to the sheer number of added predicates.

## 1.5 Contributions of this Dissertation

This dissertation presents the following contributions toward the utilization of symmetries for synthesis and verification:

- An efficient method to find symmetries in functions which have multiple outputs. Our method is based on a reduction to *small* instances of graph isomorphism which can be solved for practical functions.

- An approach to finding symmetries in a circuit by analyzing the circuit's structure to locate subgraphs which are likely to contain symmetries that are productive for optimization.

- A general approach for applying symmetries in technology mapping and placement by decomposing a group into orthogonal subgroups, each of which may be explored efficiently using a specialized procedure. Enumeration is thus limited to the number of subgroups, rather than to the total number of symmetries.

- An efficient preprocessor for generating symmetry breaking predicates for SAT formulas. Our preprocessor analyzes the structure of a formula's symmetry group in order to produce a small set of predicates that breaks as many symmetries as practically possible.

## 1.6 Organization of this Dissertation

This dissertation is organized into two parts:

- Part I provides the framework for finding symmetries in circuits. Chapter 2 reviews basic group theory and algorithms for permutation groups. Chapter 3 describes a procedure for finding symmetries of multiple-output functions. Chapter 4 describes our subgraph selection heuristic for finding symmetries in circuits.

- Part II applies the background established in Part I towards three problems in CAD. Chapters 5, 6, and 7 discuss technology mapping, placement, and SAT, respectively.

Finally, the conclusion summarizes our contributions and points out their strengths and weaknesses.

20

## 2. Permutation Group Theory

In this dissertation, the concept of symmetry refers to the ability to permute connections in a circuit without affecting its logical behavior. Permutation group theory is a mature branch of mathematics, and any efficient algorithms which use symmetries will rely on it. Therefore, this chapter serves to provide a sufficient background for the remainder of this dissertation. The reader is referred to [Hal59, Ser02] for a more thorough treatment.

## 2.1 Basic Definitions

#### 2.1.1 Groups

A **group** is a set *G* that together with a binary operation  $\cdot : G \times G \rightarrow G$ , satisfies four group axioms:

- 1. Closure: for any a, b in  $G, a \cdot b \in G$ .

- 2. Associativity: for any  $a, b, c \in G$ ,  $(a \cdot b) \cdot c = a \cdot (b \cdot c)$

- 3. Identity: there exists some  $i \in G$  such that for any  $x \in G$ ,  $i \cdot x = x \cdot i = x$ .

- 4. Inverse: for any element  $a \in G$ , there exists an element  $b \in G$  such that  $a \cdot b = b \cdot a = i$ .

**Example 2.1.** Let us define a binary operation  $\cdot$  over the set  $Z_6 = \{1, 2, 4, 8, 16, 32\}$ , such that  $a \cdot b = 2^{\lg(ab) \mod 6}$ , where lg is the base-2 logarithm. The following "multiplication table" (or **Cayley table**) shows the operation explicitly:

|    | 1                            | 2  | 4  | 8  | 16 | 32 |

|----|------------------------------|----|----|----|----|----|

| 1  | 1                            | 2  | 4  | 8  | 16 | 32 |

| 2  | 2                            | 4  | 8  | 16 | 32 | 1  |

| 4  | 4                            | 8  | 16 | 32 | 1  | 2  |

| 8  | 8                            | 16 | 32 | 1  | 2  | 4  |

| 16 | 16                           | 32 | 1  | 2  | 4  | 8  |

| 32 | 1<br>2<br>4<br>8<br>16<br>32 | 1  | 2  | 4  | 8  | 16 |

The set  $Z_6$  forms a group with  $\cdot$  since it satisfies the four group axioms:

- 1. Closure: from the definition of  $\cdot$ , if *a* and *b* are powers of 2, then  $a \cdot b$  is also a power of 2 between  $2^0$  and  $2^5$ , inclusive.

- 2. Associativity: from the associativity of addition

$2^{\lg(ab) + \lg(c) \mod 6} = 2^{\lg(a) + \lg(bc) \mod 6}$

- 3. Identity:  $x \cdot 1 = x$  for any  $x \in Z_6$ .

- 4. Inverse:  $2 \cdot 32 = 4 \cdot 16 = 8 \cdot 8 = 1$ .

We use multiplicative conventions to refer to the binary operation  $\cdot$ , i.e.  $a \cdot b$  (or simply ab) is the **product** of a and b. Its exact definition will be understood from its context. Since  $\cdot$  is associative, we omit parentheses from algebraic expressions. The group axioms imply that each element has a unique inverse, and the inverse of a is denoted by  $a^{-1}$ .

As a consequence of the group axioms, a group may be described implicitly by a small set of **generators**. A set *K* generates group *G*, i.e.  $\langle K \rangle = G$ , if every  $a \in G$  can be written as a product of elements from *K*, and if every product of elements in *K* is also in *G*.

**Example 2.2.** The group  $Z_6$  from the previous example is generated by the set  $\{2\}$ :

2 = 2  $4 = 2 \cdot 2$   $8 = 2 \cdot 2 \cdot 2$   $16 = 2 \cdot 2 \cdot 2 \cdot 2$   $32 = 2 \cdot 2 \cdot 2 \cdot 2 \cdot 2$   $1 = 2 \cdot 2 \cdot 2 \cdot 2 \cdot 2 \cdot 2$

A **subgroup** *H* of a group *G*, is a subset of *G* that with the same operation, satisfies the four group axioms. This relationship is denoted by  $H \le G$ . For example, the set  $\{1, 8\}$  forms a subgroup of  $Z_6$ .

For groups *G*, *H*, where  $H \le G$ , the **(right)** coset of *H* for some  $x \in G$  is defined as  $\{hx : h \in H\}$  and denoted by *Hx*. The cosets of *H* form equivalence classes. A set consisting of an element from each class is called a **(right)** transversal of *H*, denoted by G : H. The size of the transversal is denoted by |G : H|, and Lagrange's Theorem states that |G| = |G : H||H|. In other words, the cosets form a partition of *G*.

**Example 2.3.** Suppose that  $G = Z_6$  and  $H = \{1, 8\}$ . We enumerate the cosets Hx for each  $x \in G$  as follows:

| Cosets <i>Hx</i>    |   |                                           |  |  |  |

|---------------------|---|-------------------------------------------|--|--|--|

| $\{1, 8\} \cdot 1$  | = | $\{1 \cdot 1, 8 \cdot 1\} = \{1, 8\} = H$ |  |  |  |

| $\{1, 8\} \cdot 2$  | = | $\{1 \cdot 2, 8 \cdot 2\} = \{2, 16\}$    |  |  |  |

| $\{1, 8\} \cdot 4$  | = | $\{1 \cdot 4, 8 \cdot 4\} = \{4, 32\}$    |  |  |  |

| $\{1, 8\} \cdot 8$  | = | {8,1}                                     |  |  |  |

| $\{1, 8\} \cdot 16$ | = | {16,2}                                    |  |  |  |

| $\{1, 8\} \cdot 32$ | = | {32,4}                                    |  |  |  |

The table shows 3 distinct cosets which each appear 2 times. This conforms to Lagrange's Theorem—since |G| = 6 and |H| = 2, |G : H| = 3. Here, the cosets of *H* are *H*, {2, 16}, and {4, 32}; the set {1, 2, 4} forms a transversal. Another way to show this is to represent

each element  $g \in G$  as a product hx of some  $h \in H$  and  $x \in \{1, 2, 4\} = (G : H)$ .

| 8  | = | $h \cdot x$ |

|----|---|-------------|

| 1  | = | $1 \cdot 1$ |

| 2  | = | $1 \cdot 2$ |

| 4  | = | $1 \cdot 4$ |

| 8  | = | $8 \cdot 1$ |

| 16 | = | 8.2         |

| 32 | = | $8 \cdot 4$ |

Left cosets and left transversals are defined similarly, e.g.  $xH = \{xh : h \in H\}$ , with identical properties. We will not be using the "left" variants, but introduce them in order to caution against their inadvertent use. Since a left (right) transversal may be obtained from a right (left) transversal by inverting each element, it is easy to confuse the two. (The difference will be apparent later, when the binary operation is not commutative.)

As we will see, symmetries form a group. These results imply that symmetries may be represented compactly, and that symmetries may be partitioned into a disjoint set of cosets for efficient processing.

#### 2.1.2 Permutations

Let  $\Omega = \{1, 2, ..., n\}$  be a finite set of **points**. A **permutation**  $\pi$  is a bijection from  $\Omega$  to itself. Permutations may be written in cyclic notation, e.g. the permutation (1,3)(2,4,5) swaps 1 with 3 and simultaneously **moves** 2 to 4, 4 to 5, and 5 to 2. The identity permutation is denoted by (). The **image** of a point *i* under  $\pi$  is written  $i^{\pi}$ , e.g.  $5^{(1,3)(2,4,5)} = 2$ . The set of **moved points** of a permutation is the set  $\{i \in \Omega : i^{\pi} \neq i\}$ ; conversely, a permutation **(pointwise) stabilizes** a set if none of the points in the set are moved. For example, the permutation (1,3)(2,4,5) moves  $\{1,2,3,4,5\}$  and stabilizes  $\{6,7,\ldots,n\}$ .

Permutations may also be written in Cartesian notation, which lists the images of each point. For example, (1,3)(2,4,5) may be written as (34152), and () may be written as (12345). Unspecified images are denoted by dashes, e.g. if  $\pi = (53 - -)$  then  $1^{\pi} = 5$ ,  $2^{\pi} = 3$ , and  $3^{\pi}$ ,  $4^{\pi}$ ,  $5^{\pi}$  are unspecified. We will use this notation when permutations are partially specified or when enumerating elements of a permutation group. Otherwise, we

prefer to use cyclic notation because properties such as the set of moved points can be determined by inspection.

#### 2.1.3 Permutation Groups

A **permutation group** is a group consisting of permutations with a binary operation defined as follows. Given permutations  $\pi_1$  and  $\pi_2$ , their product  $\pi_1\pi_2$  is defined such that if  $i^{\pi_1} = j$  and  $j^{\pi_2} = k$ , then  $i^{(\pi_1\pi_2)} = k$ . Since  $i^{(\pi_1\pi_2)} = (i^{\pi_1})^{\pi_2}$  for any point *i*, we may omit the parentheses and simply write  $i^{\pi_1\pi_2}$  with no ambiguity.

**Example 2.4.** Suppose that  $\pi_1 = (1,3)(2,4,5)$  and  $\pi_2 = (1,3)(2,5,4)$ , then  $\pi_1\pi_2 = ()$ , since  $1^{\pi_1} = 3$  and  $3^{\pi_2} = 1$ ,  $2^{\pi_1} = 4$  and  $4^{\pi_2} = 2$ , etc.

The group consisting of all n! permutations over n points is denoted by  $S_n$ , and called the **symmetric group** when n or  $\Omega$  are known from the context.

A permutation group *G* induces a partition of  $\Omega$ , known as the set of **orbits**; for  $x \in \Omega$ ,  $Orbit(x) = \{x^{\pi} : \pi \in G\}$ .

**Example 2.5.** Let n = 11 and  $G = \langle \{(1,3)(2,4,5), (6,7)(9,11), (7,8)\} \rangle$ . The orbits of *G* are  $\{\{1,3\}, \{2,4,5\}, \{6,7,8\}, \{9,11\}, \{10\}\}$ , and can be obtained using a union-find algorithm [CLR89] on the cycles of the generators—the generator (6,7)(9,11) specifies that 6 may move to 7, and (7,8) specifies that 7 may move to 9. By transitivity, 6 may move to 9, therefore 6 and 9 are in the same orbit.

Note that the product operation over permutations is *not* commutative, and the following example illustrates the difference between left and right cosets.

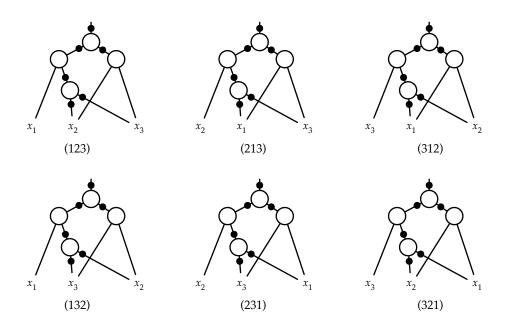

**Example 2.6.** Suppose  $G = S_3$  and  $H = \{(), (2,3)\}$ . A right transversal is  $\{(), (1,2), (1,3,2)\}$ , and a left transversal is  $\{()^{-1}, (1,2)^{-1}, (1,3,2)^{-1}\}$ . The following list shows how *G* may be partitioned into left cosets and right cosets:

| Left cosets $xH$         | G |       |   | Right cosets <i>Hx</i> |

|--------------------------|---|-------|---|------------------------|

| () · ()                  | = | (123) | = | () · ()                |

| () · (2, 3)              | = | (132) | = | (2,3) · ()             |

| (1,2) · ()               | = | (213) | = | () · (1,2)             |

| $(1,2,3) \cdot ()$       | = | (231) | = | $(2,3) \cdot (1,2)$    |

| $(1,2) \cdot (2,3)$      | = | (312) | = | () (1, 3, 2)           |

| $(1, 2, 3) \cdot (2, 3)$ | = | (321) | = | $(2,3) \cdot (1,3,2)$  |

Note that two elements from a right transversal,  $\{(1,2), (1,3,2)\}$  lie in the same left coset (1,2)H.

## 2.2 Stabilizer Chains

Given a permutation group *G*, we would like to formulate efficient algorithms to:

- compute |G|

- enumerate the elements of *G*

- compute a small set of generators

- check whether a permutation  $\pi$  is in *G*

- compute the transversal of any given subgroup

Most efficient algorithms [Ser02] rely on the concept of a stabilizer chain for *G*. This is a successively shrinking series of subgroups which stabilizes a growing corresponding sequence of points. A formal definition is given below.

For a group *G* and set of points *S*, the stabilizer  $G_S$  of *S* in *G* is the largest subgroup of *G* that pointwise stabilizes *S*, that is  $G_S = \{g : g \in G \land \bigwedge_{s \in S} s^g = s\}$ . A **base** *B* is a sequence of points  $\beta_1, \beta_2, \ldots, \beta_k$  such that  $G_B$  contains only the identity permutation. Let  $G^{(i)}$  denote  $G_{\{\beta_1,\beta_2,\ldots,\beta_i\}}$  and let  $G^{(0)} = G$ . *B* induces a **stabilizer chain** as follows:

$$\{()\} = G^{(k)} \le G^{(k-1)} \le \dots \le G^{(2)} \le G^{(1)} \le G^{(0)} = G$$

The base is **reduced** if  $G^{(i)} \neq G^{(j)}$  for  $i \neq j$ . Given a group *G* and base *B*, a **strong generating set**  $T \subseteq G$  is one for which

$$\langle T \cap G^{(i)} \rangle = G^{(i)}$$

for all *i*.

**Example 2.7.** Suppose  $G = S_5$ . The sequence 1,2,3 is *not* a base for *G* because two permutations in *G* stabilize {1,2,3}: () and (4,5).

**Example 2.8.** Suppose  $G = S_5$  and B = 1, 2, 3, 4. The stabilizer chain is as follows:

$G^{(4)} = \{()\}$   $G^{(3)} = \{(), (4,5)\}$   $G^{(2)} = \text{all 6 permutations over } \{3,4,5\}$   $G^{(1)} = \text{all 24 permutations over } \{2,3,4,5\}$   $G^{(0)} = \text{all 120 permutations over } \{1,2,3,4,5\}, \text{ i.e. } S_5$

The permutations {(1,2), (1,2,3,4,5)} generate  $S_5$ , but are not a strong generating set for base *B* since  $G^{(3)} = \{(), (4,5)\}$  but  $\langle \{(1,2), (1,2,3,4,5)\} \cap \{(), (4,5)\} \rangle = \langle \{()\} \rangle =$  $\{()\} \neq G^{(3)}$ . *T*<sub>0</sub>, defined below, is a strong generating set for *S*<sub>n</sub>

> $T_4 = \{()\}$   $T_3 = T_4 \cup \{(4,5)\}$   $T_2 = T_3 \cup \{(3,4,5)\}$   $T_1 = T_2 \cup \{(2,3)\}$  $T_0 = T_1 \cup \{(1,2)\}$

since  $\langle T_i \rangle = G^{(i)}$ .

In the remaining discussion, the base will be assumed to be the sequence of points 1, 2, ..., n for simplicity and for consistency with [Jer86].

Sims [Sim71] presented the first algorithm for finding a strong generating set based on a theorem by Schreier [Hal59]. Efficient variations of the so-called Schreier-Sims method are described in [Jer86] and [Knu91], which present worst-case bounds of  $O(n^5)$  runtime. Asymptotic complexity can be improved by adding Monte Carlo methods [BCF<sup>+</sup>91], at the expense of possibly computing generators for a subgroup of *G*, rather than for the entire group.

Before presenting algorithms to compute |G| or check for membership, we describe the main results of the algorithm proposed by [Jer86]. Compared to other variants of the Schreier-Sims method, this algorithm is more comprehensible for readers who are already familiar with graph theory.

### 2.3 Jerrum's Branching Structure

We focus on the general approach described in [Jer86], which produces a small generating set (|T| < n) in the form of a "labeled branching". The labeled branching decomposes G into transversals:  $G = (G^{(n-2)} : G^{(n-1)}) \cdots (G^{(2)} : G^{(3)})(G^{(1)} : G^{(2)})(G^{(0)} : G^{(1)})$ . Since  $G^{(i)} = G^{(i-1)}(G^{(i)} : G^{(i-1)})$  and  $G^{(n-1)} = ()$ , the transversals form a generating set for each  $G^{(i)}$ , i.e., a strong generating set for G. We now show how Jerrum's branching represents these transversals.

The labeled branching (actually a forest) maintains certain structural properties:

- 1. Nodes are synonymous with points in  $\Omega$ , and are ordered  $1 < 2 < \cdots < n$ .

- 2. Edges are directed and follow the node ordering: an edge connecting nodes i, j where i < j is necessarily from i and to j.

- 3. An edge from *i* to *j* is labeled with a permutation  $\sigma_{i,j} \in T$  where  $i^{\sigma_{i,j}} = j$  and all points less than *i* are stabilized ( $a^{\sigma_{i,j}} = a$  for all a < i).

Thus a path from *i* to *m* ( $i \rightarrow j \rightarrow k \rightarrow \cdots \rightarrow l \rightarrow m$ ) can be construed as a permutation  $\pi$  where  $\pi = \sigma_{i,j}\sigma_{j,k}\cdots\sigma_{l,m}$ ,  $i^{\pi} = m$ , and all points less than *i* are stabilized. A path from *i* to *m* exists if and only if  $m \in \{i^{\pi} : \pi \in G^{(i-1)}\}$ . In other words, the set of points reachable from point *i* (including *i* itself) is equal to the orbit of *i* in subgroup  $G^{(i-1)}$ , and the corresponding paths form the transversal  $G^{(i-1)} : G^{(i)}$ .

As we stated previously, any permutation  $\pi \in G^{(i)}$  can be represented by some product of elements from the transversals:

$$G^{(i)} = (G^{(n-2)}: G^{(n-1)}) \cdots (G^{(i)}: G^{(i+1)})(G^{(i-1)}: G^{(i)})$$

Therefore, the edge labels of the subgraph induced by nodes  $\{i, i + 1, ..., n\}$  generate  $G^{(i-1)}$ , and the edge labels of the entire branching form a strong generating set for *G*.

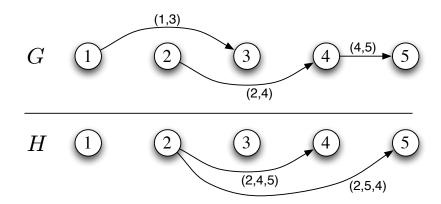

**Example 2.9.** Let  $G = \langle \{(1,2), (1,3)(2,4)\} \rangle$ . This group represents the valid permutations of the variables in the algebraic expression  $x_1x_2 + x_3x_4$ . Assuming that variable  $x_i$  is represented by point i,  $x_2x_1 + x_3x_4$  is an equivalent expression represented by permutation (1, 2). The expression  $x_3x_4 + x_1x_2$  is also equivalent, represented by (1,3)(2,4). Finally,  $x_1x_2 + x_4x_3$  is also equivalent, represented by (3,4).

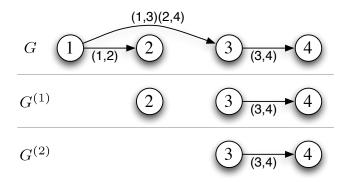

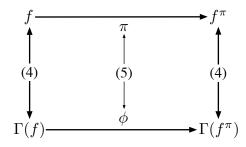

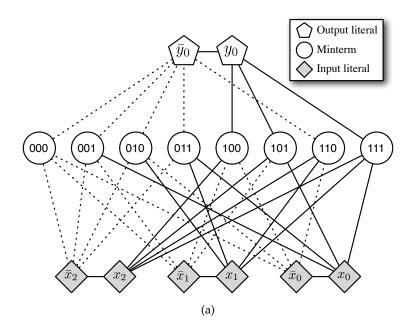

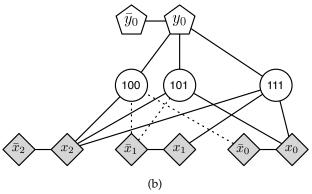

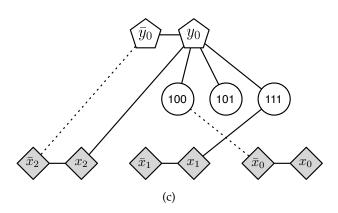

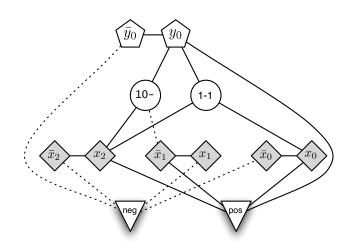

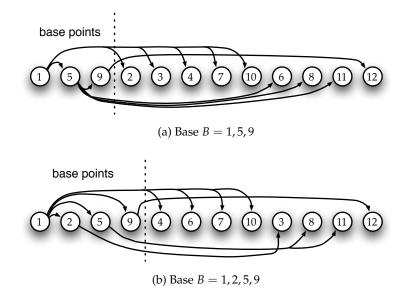

Figure 2.1: Labeled branchings for  $G = \langle \{(1,2), (1,3)(2,4)\} \rangle$  and subgroups  $G^{(1)}$  and  $G^{(2)}$

The stabilizer chain for G is as follows:

$$G^{(3)} = \{()\}$$

$$G^{(2)} = \{(), (3, 4)\}$$

$$G^{(1)} = \{(), (3, 4)\}$$

$$G = G^{(0)} = \{(), (1, 2), (3, 4), (1, 2)(3, 4), (1, 3)(2, 4), (1, 3, 2, 4), (1, 4, 2, 3), (1, 4)(2, 3)\}$$

Figure 2.1 shows the labeled branching for *G*, and the induced subgraphs for  $G^{(1)}$  and  $G^{(2)}$ . From Lagrange's theorem, we know that  $|G^{(0)} : G^{(1)}| = \frac{|G^{(0)}|}{|G^{(1)}|} = 4$ , but do not know the elements of  $G^{(0)} : G^{(1)}$ . The paths from each point *i* form  $G^{(i-1)} : G^{(i)}$  as follows:

$$G^{(2)}: G^{(3)} = \{(), \sigma_{3,4}\} = \{(), (3,4)\}$$

$$G^{(1)}: G^{(2)} = \{()\} \text{ since } G^{(1)} = G^{(2)}$$

$$G^{(0)}: G^{(1)} = \{(), \sigma_{1,2}, \sigma_{1,3}, \sigma_{1,3}\sigma_{3,4}\} = \{(), (1,2), (1,3)(2,4), (1,4,2,3)\}$$

Note that each node in a labeled branching has indegree at most 1. For efficiency, node *j* is labeled with a permutation  $\tau_j$  where  $\tau_j = \tau_i \sigma_{i,j}$  if an edge  $\sigma_{i,j}$  exists, otherwise  $\tau_j = ()$ . Thus for any path  $i \rightsquigarrow m$ , the product  $\sigma_{i,j}\sigma_{j,k} \cdots \sigma_{l,m}$  can be computed in terms of its endpoints:  $\tau_i^{-1}\tau_m$ .

Our discussion centers on how to *use* a labeled branching, and we refer the reader to [Jer86] for details on how to *construct* a labeled branching.

Going further, we can calculate |G| recursively as  $|G^{(i)}| = |G^{(i)} : G^{(i+1)}||G^{(i+1)}|$ . We can also randomly select a permutation from *G* by choosing a random element from

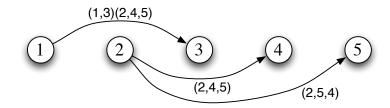

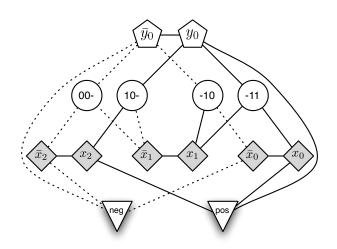

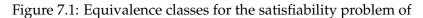

Figure 2.2: Labeled branching for group  $\langle \{(1,3)(2,4,5)\} \rangle$

each  $G^{(i)}$ :  $G^{(i+1)}$  for i = 0, 1, ..., n - 1 and taking their product.

**Example 2.10.** Let  $G = \langle \{(1,3)(2,4,5)\} \rangle$ , and let the graph in Figure 2.2 be a labeled branching for *G*. Point 1 can reach points 1 and 3, and point 2 can reach points 2, 4, and 5, indicating that  $|G| = 2 \cdot 3 = 6$ . We can also enumerate the 6 elements of *G* as products of elements from each transversal:

$$() \cdot () = ()$$

$$(2,4,5) \cdot () = (2,4,5)$$

$$(2,5,4) \cdot () = (2,5,4)$$

$$() \cdot (1,3)(2,4,5) = (1,3)(2,4,5)$$

$$(2,4,5) \cdot (1,3)(2,4,5) = (1,3)(2,5,4)$$

$$(2,5,4) \cdot (1,3)(2,4,5) = (1,3)$$

Note that (1,3) is another valid label for the edge  $\sigma_{1,3}$ . This will be an important point in a chapter 7.

#### 2.3.1 Membership Check

Checking for membership utilizes a "sifting" procedure which resembles algebraic division, or more accurately, the solution of a Rubik's cube. The solution of a Rubik's cube entails restoring one layer at a time until the identity permutation is reached. Similarly, the sifting procedure systematically attempts to "undo" the movement of points 1, 2, 3, etc.

**Example 2.11.** Using the same group and labeled branching from the previous example, let us check whether  $(1,3) \in G$ . Since (1,3) is not the identity, we multiply by  $\tau_3^{-1}\tau_1$ , resulting in (2,5,4). The result is not the identity either, and we multiply it by  $\tau_5^{-1}\tau_2$ , resulting in (). Finally, we conclude that  $(1,3) \in G$ .

**Algorithm 1** IS-MEMBER( $G, \pi$ )

1: while  $\pi \neq ()$  do 2:  $j \leftarrow$  the first moved point of  $\pi$ 3:  $k \leftarrow j^{\pi}$ 4: if there is no path from j to k then 5: return false 6: end if 7:  $\pi \leftarrow \pi \tau_k^{-1} \tau_j$  { undo movement from j to k:  $(\tau_j^{-1} \tau_k)^{-1} = \tau_k^{-1} \tau_j$  } 8: end while 9: return true

**Example 2.12.** Let us now check whether  $(2, 4) \in G$ . The first moved point is 2 and  $2^{(2,4)} = 4$ , so we combine with  $\tau_4^{-1}\tau_2$ , resulting in (4,5). Since there is no path in the graph from 4 to 5, we conclude that  $(2,4) \notin G$ .

#### 2.3.2 Transversal Computation

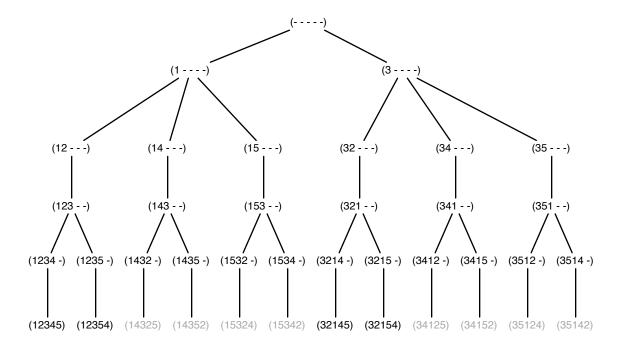

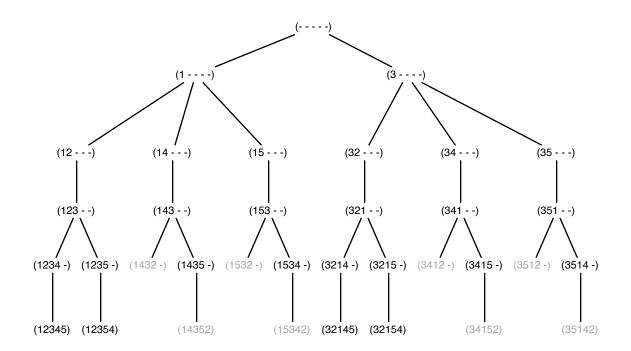

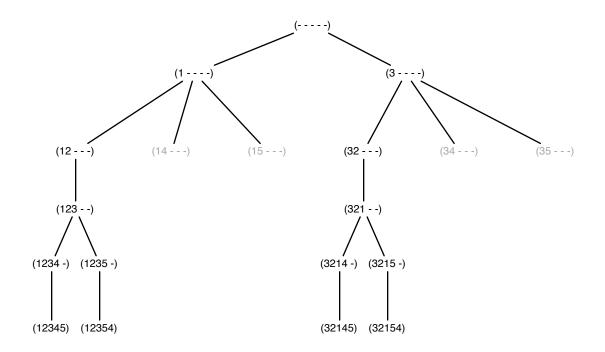

Jerrum described in [Jer86] how to obtain a transversal  $S_n$  : G given a branching structure for G—the set of topological sorts of the branching structure forms a transversal. We can extend this concept for any arbitrary G and H where  $H \le G$ —the set of elements in G consistent with a topological ordering of H's branching structure forms a transversal G : H. Note that the labels for the subgroup's branching structure are not required.

Many group algorithms follow a similar recursive structure. Therefore, for illustrative purposes, we first present a naïve version of the algorithm and add optimizations incrementally. For brevity, the pseudocode equates a group with its respective branching structure.

| Algorithm 2 TRANSVERSAL(G, H)  |  |

|--------------------------------|--|

| 1: $L \leftarrow \{\}$         |  |

| 2: TRANSVERSAL-RECUR(H, 1, ()) |  |

| 3: return L                    |  |

The naïve version enumerates the elements of G, and selects those elements which obey the topological ordering imposed by H's branching structure.

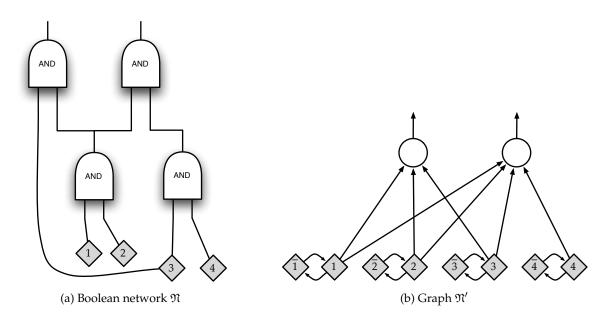

Suppose that  $G = \langle \{(1,3), (2,4), (4,5)\} \rangle$  and  $H = \langle \{(2,4,5)\} \rangle$ . Their corresponding branching structures are shown in Figure 2.3, and indicate that |G| = 12 and |H| = 3. Therefore, we expect that the algorithm produce a set of 12/3 = 4 permutations.

**Algorithm 3** TRANSVERSAL-RECUR( $G, H, j, \pi$ )

| 1: <b>if</b> j | i = n then                                                             |

|----------------|------------------------------------------------------------------------|

| 2:             | if $k^{\pi} < l^{\pi}$ for every edge $(k, l)$ in <i>H</i> then        |

| 3:             | { $\pi$ is consistent with a topological sort of <i>H</i> }            |

| 4:             | $L \leftarrow L \cup \{\pi\}$                                          |

| 5:             | end if                                                                 |

| 6: els         | e                                                                      |

| 7:             | $\tau \leftarrow \text{node labels from } G$                           |

| 8:             | <b>for each</b> <i>k</i> reachable from <i>j</i> in <i>G</i> <b>do</b> |

| 9:             | TRANSVERSAL-RECUR(G, H, $j + 1$ , $\tau_i^{-1}\tau_k\pi$ )             |

| 10:            | end for                                                                |

| 11: <b>en</b>  | d if                                                                   |