# On Invariants to Characterize the State Space for Sequential Logic Synthesis and Formal Verification

Mike Case

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-46 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-46.html

April 2, 2009

Copyright 2009, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Acknowledgement

I would like to thank my adviser, Bob Brayton, for his support and guidance throughout my studies. From our regular meeting to spontaneous coffee shop rendezvous when I wanted to discuss the latest results, Bob was always available, encouraging, and willing to steer me in the right direction.

Alan Mishchenko who served as my unofficial co-advisor. Alan was always willing to hear my latest crazy ideas, and he initially planted into my head many of the seeds that grew into the methods presented in this thesis.

Lastly, my colleagues at IBM. They provided important feedback on my work, and they employed me during my 18 months of study. This gave me

a grounding that 1) motivated the need to explore scalable algorithms, and 2) the ability to evaluate my techniques in a realistic setting.

#### On Invariants to Characterize the State Space for Sequential Logic Synthesis and Formal Verification

by

Michael Lee Case

B.S. (Oregon State University) 2004

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering—Electrical Engineering and Computer Science

in the

#### GRADUATE DIVISION

of the

### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Robert Brayton, Chair Professor Andreas Kuehlmann Professor Lee Schruben

Spring 2009

The dissertation of Michael Lee Case is approved:

Professor Robert Brayton, Chair

Professor Andreas Kuehlmann

Professor Lee Schruben

University of California, Berkeley

Spring 2009

Date

Date

Date

On Invariants to Characterize the State Space for Sequential Logic Synthesis and Formal Verification

Copyright  $\bigodot$  2009

by

Michael Lee Case

#### Abstract

On Invariants to Characterize the State Space for Sequential Logic Synthesis and Formal Verification

by

Michael Lee Case

Doctor of Philosophy in Engineering—Electrical Engineering and Computer Science University of California, Berkeley Professor Robert Brayton, Chair

Because of the large size of industrial designs, modern sequential logic synthesis and formal verification techniques cannot afford to accurately characterize the state space of a design. This limits the ability to both optimize designs and to formally prove the the designs behave as required.

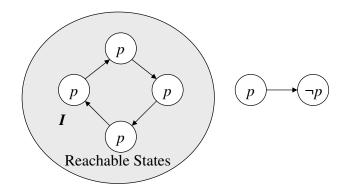

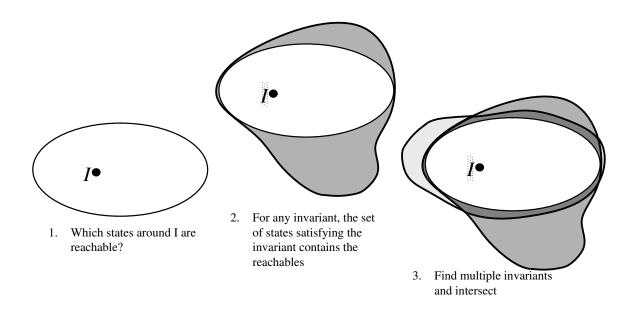

Invariants are properties that hold in all reachable states. They can be generated in an automated manner, and the set of generated invariants provides a characterization of the design's state space. This characterization can be utilized sequential logic synthesis and formal verification.

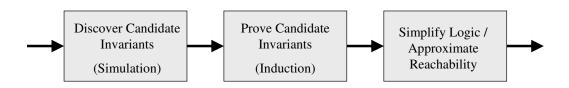

In total, this thesis provides 1) a framework to efficiently generate invariants, 2) extensions to sequential logic synthesis to make it more capable of reducing the size of complex designs, and 3) extensions to formal verification to increase its scalability on complex industrial designs.

Date

#### Acknowledgements

I would like to thank my adviser, Bob Brayton, for his support and guidance throughout my studies. From our regular meeting to the spontaneous coffee shop rendezvous when I wanted to discuss the latest results, Bob was always available, encouraging, and willing to steer me in the right direction.

This work would not have been possible without Alan Mishchenko who served as my unofficial co-advisor. Alan was always willing to hear my latest crazy ideas, and he initially planted into my head many of the seeds that grew into the methods presented in this thesis.

Lastly, my colleagues at IBM were very influential in the later stages of my research. They provided important feedback on my work, and they employed me during my 18 months of study. This gave me a grounding that 1) motivated the need to explore scalable algorithms that actually work on industrial designs, and 2) the ability to evaluate my techniques in a realistic setting. I would like to thank my loving wife Luciena for having the courage to marry a student and for her support and patience through my time at Berkeley.

## Contents

| Table of Contents |                                                                                                                                                                           |                                                    |     |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|--|

| Li                | List of Examples       v         I Introduction       1         1.1 Motivation       1         1.2 Chip Design and CAD Tools       1         1.3 Logic Synthesis       15 | $\mathbf{v}$                                       |     |  |

| 1                 | Intr                                                                                                                                                                      | roduction                                          | 1   |  |

|                   | 1.1                                                                                                                                                                       | Motivation                                         | 1   |  |

|                   | 1.2                                                                                                                                                                       | Chip Design and CAD Tools                          | 1   |  |

|                   | 1.3                                                                                                                                                                       | Logic Synthesis                                    | 15  |  |

|                   | 1.4                                                                                                                                                                       | Formal Verification                                | 28  |  |

|                   | 1.5                                                                                                                                                                       | Synergy Between Synthesis and Verification         | 46  |  |

|                   | 1.6                                                                                                                                                                       | Contributions of This Thesis                       | 48  |  |

| <b>2</b>          | Inva                                                                                                                                                                      | ariants                                            | 50  |  |

|                   | 2.1                                                                                                                                                                       | Motivation and Basic Algorithm                     | 50  |  |

|                   | 2.2                                                                                                                                                                       | Types of Invariants                                | 54  |  |

|                   | 2.3                                                                                                                                                                       | Improving the Quality of Simulation                | 61  |  |

|                   | 2.4                                                                                                                                                                       | Mining Candidate Invariants                        | 67  |  |

|                   | 2.5                                                                                                                                                                       | Efficient Proving of Candidate Invariants          | 73  |  |

|                   | 2.6                                                                                                                                                                       | Efficient Storage of Candidate Invariants          | 86  |  |

|                   | 2.7                                                                                                                                                                       | Orthogonality of Invariant Families                | 99  |  |

|                   | 2.8                                                                                                                                                                       | Alternative Methods For Approximating Reachability | 102 |  |

| 3        | Ap           | plying Invariants to Sequential Synthesis           | 106 |

|----------|--------------|-----------------------------------------------------|-----|

|          | 3.1          | Motivation                                          | 106 |

|          | 3.2          | Direct And Indirect Sequential Synthesis            | 107 |

|          | 3.3          | Case Study: SAT-Based Resubstitution                | 107 |

|          | 3.4          | Case Study: Sequential ODCs                         | 135 |

|          | 3.5          | Conclusions                                         | 160 |

| 4        | Ap           | plying Invariants to Verification                   | 162 |

|          | 4.1          | Motivation                                          | 162 |

|          | 4.2          | Strengthening Interpolation                         | 163 |

|          | 4.3          | Strengthening Induction                             | 174 |

|          | 4.4          | Targeted Invariants                                 | 178 |

|          | 4.5          | Verification of Sequential Synthesis                | 194 |

|          | 4.6          | Conclusion                                          | 195 |

| <b>5</b> | Cor          | nclusion                                            | 196 |

|          | 5.1          | Summary of Ideas Discussed                          | 196 |

|          | 5.2          | Weaknesses of Invariants and Their Solutions        | 197 |

|          | 5.3          | An Ideal Invariant-Strengthened Verification Recipe | 198 |

|          | 5.4          | Future Work                                         | 201 |

| Bi       | Bibliography |                                                     |     |

| Index    |              |                                                     |     |

## List of Examples

| 1.1  | A String-Matching FSM                                                                                                      | 6   |

|------|----------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2  | A Sequential Logic Implementation of Our String-Matching FSM $\ . \ . \ .$                                                 | 9   |

| 1.3  | The Complexity of Product Machines                                                                                         | 11  |

| 1.4  | The Complexity of Datapath and Control Logic                                                                               | 13  |

| 1.5  | Synthesis With Cone of Influence Reduction                                                                                 | 18  |

| 1.6  | Synthesis By Merging Signals                                                                                               | 20  |

| 1.7  | Synthesis With State Re-encoding                                                                                           | 22  |

| 1.8  | Synthesis With Resubstitution                                                                                              | 24  |

| 1.9  | The Cost of a Bug                                                                                                          | 28  |

| 1.10 | Verifying a 64-bit Multiplier With Simulation                                                                              | 30  |

| 1.11 | Sequential Equivalence Checking The Logic Networks of Section 1.3.4 $$                                                     | 32  |

| 1.12 | SEC Specified as Property Checking                                                                                         | 35  |

| 1.13 | Explicit State Model Checking                                                                                              | 38  |

| 1.14 | Induction Based Model Checking                                                                                             | 40  |

| 1.15 | Interpolation Based Model Checking                                                                                         | 42  |

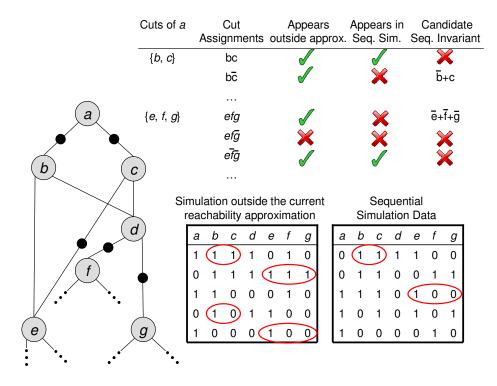

| 2.16 | Mining candidate $k$ -cut invariants $\ldots \ldots \ldots$ | 59  |

| 2.17 | Equivalence Classes                                                                                                        | 86  |

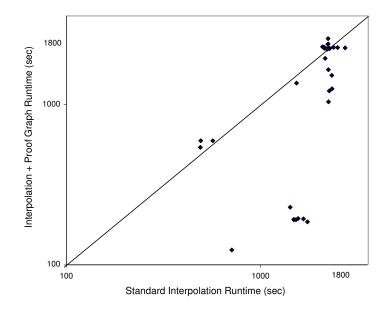

| 2.18 | Reachability by Interpolation: Practical Experience                                                                        | 104 |

| 3.19 | Resubstitution for one-hot encoded registers                                                                               | 117 |

| 3.20 | Expanding a basis set.                                                                                                     | 123 |

| 3.21 Combinational Simplification With ODCs | <br>140 |

|---------------------------------------------|---------|

| 3.22 Extracting Direct ODC Candidates       | <br>147 |

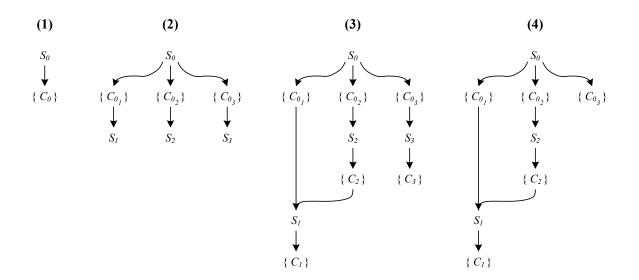

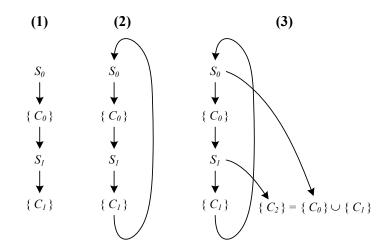

| 4.23 An Example Proof Graph                 | <br>183 |

| 4.24 Cycles in the Proof Graph              | <br>187 |

## Chapter 1

## Introduction

## 1.1 Motivation

This thesis is concerned with building efficient and correct computer chips. Implementing a chip to be smaller, faster, and use less power increases the chip's value to the consumer. Guaranteeing that the chip is designed correctly avoids the need for costly debugging and recalls after the chip has manufactured and shipped.

## 1.2 Chip Design and CAD Tools

Computer chip designs are normally specified in a Hardware Description Language (HDL), as illustrated in Figure 1.1. This is a text-based specification that can be used to derive a circuit implementation which can then be manufactured into a die, the functional part of the computer chip. The process by which the text based specification is translated into a circuit implementation is referred to as Computer Aided Design (CAD).

Chip designs can be roughly classified into two types: **analog** or **digital**. Analog designs are typically specified at the transistor level and thus the designer has much

Detailed Chip Design - Ready for Manufacturing

Figure 1.1: Chip designs normally start with a Hardware Description Language (HDL). CAD tools aid in preparing the HDL design for manufacturing. The pictured die is an Intel Pentium 3 CPU [Intel Corporation, 2001].

more control over the final performance of the chip, but this comes at the cost of a complicated design. In contrast, digital designs are specified at the logic level. This allows the designer to specify the intended logical function of the chip yet ignore the details of how the electronics will implement this logic. This abstraction enables much greater design productivity, and for that reason most designs are specified as **digital logic** designs. This thesis is concerned with such designs.

A chip designer typically employs several different **CAD Tools** in his or her work. Each tool has a different purpose. In this thesis we are concerned with two such families of tools: CAD tools that take an existing design and optimize the logic to produce an equivalent yet better design, known as **synthesis** tools, and tools that check that the chip will function as intended, known as **verification** tools. This thesis introduces techniques that can improve the quality of synthesis and verification tools.

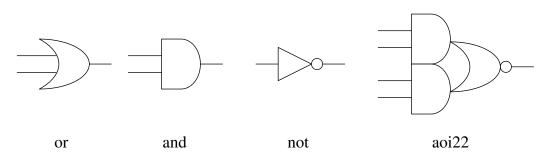

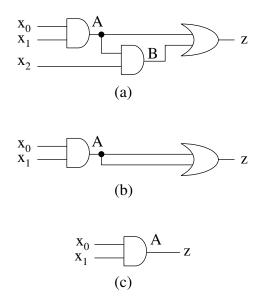

Figure 1.2: Examples of digital logic gates.

### 1.2.1 Digital Logic Components

Digital logic designs can be specified in high-level English-like languages such as VHDL [Wikipedia, 2009], Verilog [IEEE, 2008], or System C [OSCI, 2008]. While convenient for the human user, English-like languages are burdensome to use within CAD software. Instead, a representation that directly discusses the digital logic implementation, known as an **Register-Transfer Level** (**RTL**) design, is used. In high performance chips such as **Central Processing Units** (**CPUs**), a design is often specified directly in terms of RTL because this tends to result in higher-performance chips. Such RTL designs are the focus of this work.

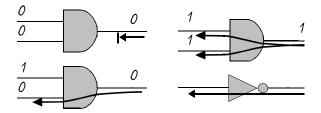

RTL designs are specified in terms of logic gates, and there are several different types of gates that appear in such designs. While dozens of gate types may be found in an RTL design, an example of four such gate types is illustrated in Figure 1.2. An **or gate** takes two inputs and outputs a 1 if either of these inputs is 1. An **and gate** similarly takes two inputs and outputs a 1 if both inputs are 1. A **not gate** takes a single input and outputs a 1 if the input is 0 and is sometimes referred to as an **inverter**. Additionally, there may be more complex gate types present. For example, consider the **aoi22 gate**. This gate takes 4 inputs and outputs a 1 if certain pairs of inputs are not both 1 at the same time.

A family of gate types is known as a **complete logic family** if any compli-

Figure 1.3: Examples of registers that may appear in sequential logic.

cated gate type can be constructed from a combination of gates from the family. The simplest complete logic family has only two members: *and* and *not*. Designs that take gates from only this simple family are known as **And-Inverter Graphs** (**AIGs**) [Kuehlmann and Krohm, 1997]. AIGs have come to be the preferred style for representation of a design inside a CAD tool due to the simplicity of this small logic family.

### 1.2.2 Registers and Sequential Logic

Logic gates can be arranged in a network such that a single gate in the network takes as input either 1) the output of some other gate in the network, or 2) an input to the network as a whole. Such a structure is often referred to as a **logic network** or **netlist**. Such a logic network computes 1 or more signals as a function over a set of inputs. In order that this function be deterministic, we impose the constraint that the logic network be free of cycles. That is, a logic gate should not take its output as one of its inputs, either directly or through a series of intermediate gates.

In addition to logic gates, a logic network commonly includes **registers**. A register is a state holding element, capable of storing a logic value that was computed in the past. Two examples of registers, a realistic one, and a simplified one that will be used in this thesis, are shown in Figure 1.3. The design has one or more signals referred to as **clocks** that control the function of the registers. These clocks control the behavior of the design over time, and we shall refer to **time** j as the j'th time step, or the j'th event that has occurred on the clock signals.

An example of a realistic register can be see in Figure 1.3. The register takes as input an initial value that controls the register's output at time 0. After time 0, the output is controlled by the input signal, the clock signal, and the register's internal **state**. When an event on the clock signal, a transition from 0 to 1 for example, occurs the input signal will be read and the result stored in the internal state. This stored value will be output from the register. Thus the clock signal controls the point(s) in time that the register samples, or **latches**, the input.

A design can have multiple clock signals and multiple different types of registers. Through a technique known as **phase abstraction** [Bjesse and Kukula, 2005], the clocks and registers can be normalized such that a CAD tool only sees one clock signal and one type of register. This dramatically simplifies the implementation of the CAD tool, and we will use this simplified view in this thesis. The simplified latch takes an input that we shall refer to as the **next state function** because it computes the value that the register will have at the next point in time. The output shall be referred to as the **current state** because it is simply a reflection of the register's state at the current time. All registers have an implicit **initial state** which is driven by a designated signal in the design, allowing for a constant initial state, a nondeterministic initial state, or an initial state that is a complex function of initial conditions. All simplified registers take as input the single clock, and because there is no variation across registers, we omit this clock signal from all future discussion of registers. The clock is implicitly part of the design but is customarily not drawn. The terms **latch** and register are used interchangeably in this thesis to refer to this simple register model.

A logic network that is free of registers is known a **combinational logic network**.

Because this type of logic network is free of internal state, it is simpler to understand and to process in CAD tools. Such logic networks have been studied extensively in the past, and there now exist high quality CAD tools to optimize and/or verify these networks.

More complex systems can be constructed from logic networks that also include registers. These logic networks incorporate internal state and are referred to as **sequential logic networks**. Traditionally, sequential logic networks have been handled by removing their registers and processing the remaining combinational logic network in isolation. However, tools that take the registers into consideration can generate significantly more-optimal designs and verify more interesting design properties. Unfortunately, the analysis of sequential logic networks is complex, but the techniques presented in this thesis help to mitigate that complexity.

#### 1.2.3 Finite State Machines

Sequential logic networks can be used to implement **Finite State Machines** (**FSMs**). FSMs form the building blocks of more complex digital logic systems by providing a methodology by which a design has a meaningful internal state that evolves in a chosen manner over time.

**Definition:** A Finite State Machine (FSM) is a 6-tuple  $(\Sigma, \Gamma, S, s_0, \delta, \omega)$  where  $\Sigma$ ,  $\Gamma$  are respectively the sets of inputs and outputs of the FSM. S is the set of state variables in the FSM with  $s_0$  being the FSM's initial state. At any time t, the state at time t + 1 is given by  $\delta(\Sigma, S)$  and the valuations of the outputs  $\Gamma$  are given by  $\omega(\Sigma, S)$ .

Consider the following example of a small yet realistic FSM.

#### Example 1. A String-Matching FSM

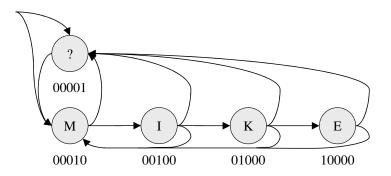

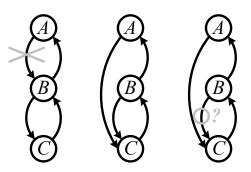

Figure 1.4: State transition graph of a simple FSM.

Suppose we have an FSM that takes as input  $\Sigma$  a sequence of keystrokes and outputs  $\Gamma$  a signal that is 1 whenever the user has typed the string "MIKE". We can define the following states S for this machine:

? Means that the past input is indecipherable.

**M** Means that the user has just typed "M".

**I** Means that the user has just typed "MI".

**K** Means that the user has just typed "MIK".

**E** Means that the user has just typed "MIKE".

The FSM assumes exactly one of these states at any given time, and we can graphically describe the evolution of the FSM's state over time with a **State Transition Graph** (**STG**) as illustrated in Figure 1.4.

Initially, the FSM starts in states  $s_0$  which is either the ? or **M** state, depending on the current input. This is illustrated with a set of arrows from an undefined state in the upper-left of the figure. At any state of the FSM, the state at the next point in time shall be either 1) the next state in the **M-I-K-E** sequence if the appropriate input is given, or 2) the state ? if the current input is not the next key in the sequence, or 3) the state **M** if the current input is wrong but could possibly serve as the starting point for a new M-I-K-E sequence. This defines the state transition function  $\delta$ .

An FSM's internal state allows it to produce more meaningful outputs than is possible in a state-free machine. In this case, we want to output a 1 whenever we have seen "MIKE". In other words, the output function  $\omega$  is simply to output a 1 whenever we are in state **E**.

FSMs can be easily implemented in digital logic. First, label each state in the FSM with a fixed-length unique binary code, as shown in Figure 1.4. Each bit in this code will be stored in a separate register, and so the number of bits in the code define the number of registers in the design. There are many ways to code the states, and some coding styles result in few registers while others trade registers for a higher-performance implementation. This is referred to as the **state encoding problem** and is beyond the scope of this work. The codes in Figure 1.4 were chosen arbitrarily. The valuation of all the registers is referred to as the implementation's **state vector** or simply **state**.

After the states are encoded, the initial values for each register can be derived by simply noting which states (and corresponding codes) are initial states in the state transition graph. The inputs to the registers, called the next state functions, define the value the registers should store at the next point in time. These can be directly translated from the FSM's encoded  $\delta$  function. The set of all next state functions shall be referred to as the **transition relation**.

All that remains is to define the outputs of the sequential logic network. This can be derived easily from the FSM's  $\omega$  function.

It should be noted that the logic implementation of an FSM is not unique. There always exist multiple equivalent implementations, resulting in a spectrum of area, power, and delay trade-offs. This thesis will discuss synthesis and verification, prob-

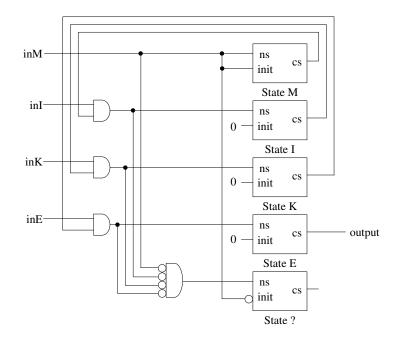

Figure 1.5: Example sequential logic network corresponding to Figure 1.4. Bubbled inputs are a shorthand representation of an inverter feeding the logic gate input.

lems that stem from the non-uniqueness of FSMs. Synthesis is the problem of moving from one implementation to an equivalent but better implementation. Verification involves checking that an implementation is correct or that a pair of implementations are equivalent.

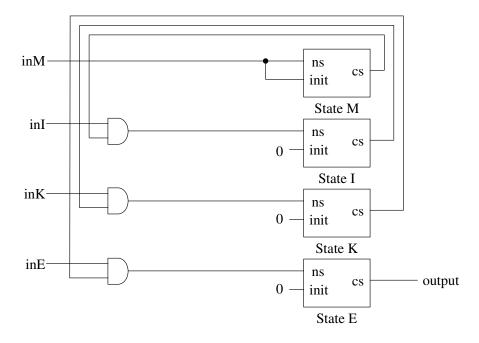

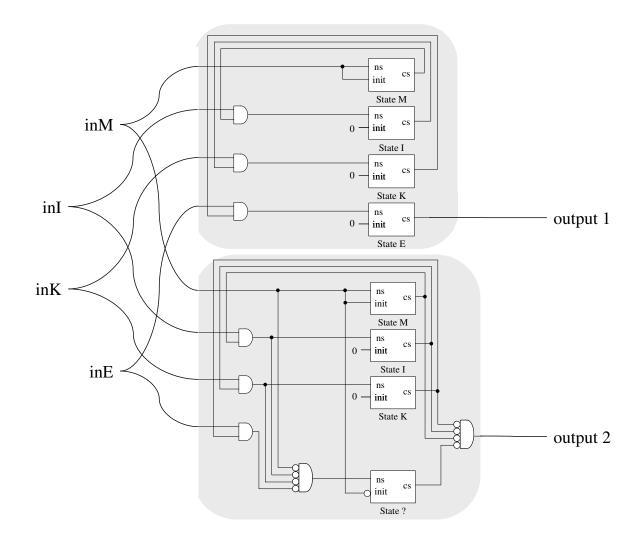

## Example 2. A Sequential Logic Implementation of Our String-Matching FSM

As an example of how to implement an FSM as a sequential logic network, here we implement the FSM of Figure 1.4. The implementation that will be developed is illustrated in Figure 1.5.

Using the state encodings given, there are 5 registers in the sequential logic, and each register corresponds to a single state of the FSM. We label the registers accordingly to get registers "State M" through "State ?". The FSM takes keystrokes as input, and to simplify this suppose we simply consider 4 signals. Input "inM" shall be 1 iff the user typed "M". Inputs "inI", "inK", "inE" are defined similarly.

From Figure 1.4, we can see that the next state is  $\mathbf{M}$  iff in M=1. The next state is  $\mathbf{I}$  if the current state is  $\mathbf{M}$  and in I=1. Similarly, the next state is  $\mathbf{K}$  if the current state is  $\mathbf{I}$  and in I=1 and the next state is  $\mathbf{E}$  if the current state is  $\mathbf{K}$ and in E=1. Otherwise, the next state is ?. This defines the transition relation of the sequential logic network.

The initial states are similarly given by translation from Figure 1.4. The FSM starts in state  $\mathbf{M}$  if in M=1 and in state ? if in M=0. It is illegal to start in any other states, and the initial state functions for the corresponding registers are all constant 0.

The single output is 1 iff the FSM is in state E. This implementation is trivial, just a wire.

Note that this implementation is very inefficient. The state ? is clearly not needed, and the FSM could be implemented with fewer registers. Furthermore, how do we know that this implementation is correct? These questions will be explored below.

#### 1.2.4 The State Space and Design Complexity

The set of states that are possible to represent with an FSM's registers are known as the **state space**. Note that in general the cardinality of this set of states can be much larger than the number of states present in the original state transition diagram. If an FSM is implemented with N registers then the state space has  $2^N$  states. Many synthesis and verification algorithms perform computations over the state space, and the large size of this space makes those computations difficult. A pair of states (a, b) in the state space are connected by a **path** if starting from state a the FSM can assume state b after a fixed number of time steps if provided with suitable input stimulus. A **reachable state** r is any state for which there exists a path from an an initial state i to r. An **unreachable state** is any state for which no such path exists. Note that in a manufactured chip an unreachable state will never be observed during operation.

If the reachable states can be enumerated then this information can be leveraged in two interesting ways:

- Optimizations can be performed such that the behavior of the design is not preserved on the unreachable states. Because the unreachable state will never be observed in the lifetime of the chip, any change in behavior will go undetected. This freedom to change the behavior on a set of states provides flexibility to optimize the design in exotic ways, and such optimizations are known as **sequential synthesis** transformations.

- Verification that the design always behaves in a particular manner can be done by simply checking that this behavior holds on each of the reachable states. Because only these reachable states will be observed when the chip is operating, by checking the behavior on the reachable states the behavior of the chip has been checked for all time. This process is known as **formal verification**.

Clearly, there are advantages in partitioning the state space into reachable and unreachable states. A design with N registers has  $2^N$  states. The FSM in Example 2 has only 5 registers for a total of 32 states, and partitioning these 32 states into reachable and unreachable states is fairly straightforward. However, realistic designs are far more complex.

#### Example 3. The Complexity of Product Machines

While simple FSMs such as seen in Example 2 do exist in practice, complex chip designs can not be constructed manually from a single FSM. Humans have been able to construct complex systems through modularity. By successively partitioning a large design, a designer can limit his focus to a very small window. In this small window an FSM can be used to implement the intended design, and the total design will be composed of the conjunction of several small FSMs from each of these windows. These FSMs often interact with each other in complicated ways.

A product machine is a view of a design that includes two smaller designs. It is an important piece of the hierarchy where two sub-designs come together to form a design that is more complex than either of its constituents. While the size of the total design increases, the complexity of its state space increases as well.

Suppose a product machine is composed of designs  $\alpha$  and  $\beta$ .  $\alpha$  has  $R_{\alpha}$  registers and  $S_{\alpha}$  reachable states ( $S_{\alpha} \leq 2^{R_{\alpha}}$ ). Similarly  $\beta$  has  $R_{\beta}$  registers and  $S_{\beta}$  reachable states. Individually, the two designs have  $2^{R_{\alpha}}$  and  $2^{R_{\beta}}$  states in their state space, respectively. However, the product machine has  $R_{\alpha} + R_{\beta}$  registers and  $2^{R_{\alpha}+R_{\beta}} = 2^{R_{\alpha}} \cdot 2^{R_{\beta}}$  states. The sizes of the state spaces have been multiplied, hence the name product machine.

If the two sub-designs  $\alpha$  and  $\beta$  act independently then the product machine will have  $S_{\alpha} \cdot S_{\beta}$  reachable states. However, often the designs will interact in nontrivial ways. For example,  $\alpha$  may take as input one of the outputs of  $\beta$ . In practice, this limits the reachable state space, and the effective reachable state space will be much smaller than  $S_{\alpha} \cdot S_{\beta}$ .

Because the set of reachable states is not predictable, the partitioning of state space into reachable and unreachable states must be done anew on the product machine. However, the product machine has  $R_{\alpha} + R_{\beta}$  registers, and this increase in the number of registers to process severely complicates this analysis.

#### Example 4. The Complexity of Datapath and Control Logic

Realistic chip designs are not built of FSMs alone. They often contain more complex blocks. For example, an **adder** is a block that inputs two binaryencoded numbers and outputs their sum. This binary encoding could be large. For example, in today's CPUs it is common to see 64-bit encodings, resulting in  $2 \cdot 64 = 128$  inputs and 64 outputs.

Logic blocks such as adders manipulate data as it flows through a chip. Multiple such blocks can be arranged in a network to compute complex functions over the chip's data. For example, by chaining adders and multipliers, polynomials can be computed. Such networks of data-processing blocks are known as a **datapath**.

**Throughput** is a measure of how much computation a chip can complete in a unit of time. In order to increase throughput it is common to **pipeline** the datapath. This process involves cutting signals in the datapath and inserting registers. The combinational logic between two sets of introduced registers is known as a **pipeline stage**. The registers mean that the datapath will require multiple clock cycles to compute a result. In general, a computation will require as many clock cycles as there are pipeline stages, and this cycle requirement is known as the **latency**. However, because the registers partition the design, the data in stage j is independent from all stages i < j. This allows new computations to start before the previous computation completes, resulting in overlapping waves of computation. These waves result in significantly higher throughput.

Registers that carry data as it flows through the design are known as **datapath** registers. For example, the registers that are used for pipelining are datapath registers. They do not store the state of an FSM but instead store intermediate results for a larger data computation. One resultant characteristic is that a set of datapath registers typically have a very high percentage of reachable states.

Arithmetic blocks such as adders and multipliers require a large number of logic gates and correspondingly take a large area on the manufactured die. Additionally, the pipelining can introduce undesirable latency into the design. In order to improve this area and timing, computer architects employ a variety of tricks. The nature of these techniques is beyond the scope of this thesis, but it is sufficient to know that these techniques introduce several inputs to the datapath logic that control its function. These **control inputs** must be configured in a particular way to ensure that the design operates as intended.

FSMs are typically employed to operate the control inputs. An FSM block known as **control logic** is built, and its outputs are tied to the control inputs of the design.

The resulting design is a composition of datapath and control logic. The datapath has a high percentage of reachable states, and the control logic, because of the nature of product machines, typically has a low percentage of reachable states. Characterizing the reachable state space of the composite machine can be complicated because, similar to a product machine, it is not possible to predict the composite reachable state space from the individual spaces of the two components. The composite machine typically contains a large number of registers, further complicating this analysis.

## 1.3 Logic Synthesis

#### 1.3.1 The Synthesis Problem

**Logic synthesis** is the process of optimizing a logic netlist. A **logic synthesis tool** is a CAD tool that inputs a logic netlist, optimizes it in some way, and outputs a netlist with equivalent functionality yet better implementation.

The goal of a logic synthesis tool is to make a logic netlist "better," but the definition of "better" can vary greatly depending on the overall objective. The designer's objective is captured mathematically as a **cost function** inside the synthesis tool, and the synthesis process can be viewed as an optimization problem that is trying to minimize a cost function. Some example cost functions are as follows:

- Often the designer wants to minimize the amount of area that a logic network will take on the die. This reduces the manufacturing cost as more dies can be fit on a single **wafer**. Area can be optimized by implementing the logic network with fewer gates and/or gates that can be arranged more efficiently on the die.

- Power is often another important consideration, and the logic can be optimized to minimize power. **Static power** is related to the area of the logic network and can be optimized with an area-focused cost function. **Dynamic power** can be minimized by re-implementing the logic such that the probability of observing the logic network's signals transitioning is minimized.

- Speed is another common designer objective. Improving the **delay** necessary to propagate logic values through a logic network is important because this enables the network to be run with a higher-frequency clock, improving the speed of the chip. Delay can be optimized by reducing the number of gates that lie on paths from the logic networks input to the outputs.

#### 1.3.2 Technology Independent Synthesis

There are many CAD tools that a designer must use when implementing a chip, and logic synthesis is just one of these tools. Other important tools include **technology mapping**, **placement**, and **routing**. These form a **toolchain** such that the output of logic synthesis is used as the input to technology mapping, technology mapping feeds placement, and placement feeds routing.

Technology independent synthesis is the process of performing logic synthesis in isolation without considering the effects of the logic transforms on the later parts of the toolchain. Technology independent synthesis only considers the logic of the netlist and does not consider factors that affect the later manufacturability of the design. This was the focus of much of the early research in logic synthesis due to its simplicity and limited scope.

Modern CAD tools have shifted focus away from technology independent synthesis and instead invest efforts in **technology dependent synthesis**. This is also known as **physical synthesis**. In a physical synthesis tool, one or more components of the toolchain will be implemented together and performed at the same time. For example, logic synthesis, technology mapping, and placement might be all implemented in the same tool and performed simultaneously. This allows the logic synthesis to see the effect of its transformations on the placed design, allowing it to choose logic transformations that not only satisfy the logic synthesis' cost function but also the cost function in mapping and placement. Such a broader view of the optimization problem results in much more efficient implementations.

Physical synthesis leverages technology independent synthesis algorithms and improves them by integrating other CAD tools. In recent years there has been much research in physical synthesis while technology independent synthesis has been largely ignored. This thesis will discuss technology independent synthesis and will make two key contributions to the field:

- Sequential logic synthesis techniques will be developed, and this type of synthesis is significantly more powerful than conventional methods. These techniques are new and are commonly developed in technology independent synthesis first due to its simplicity. Later they can be applied to physical synthesis.

- Synthesis will be used to simplify verification problems, and in this domain the goal is to verify properties of a design instead of manufacturing a chip. Physical synthesis makes no sense in this domain and therefore the focus should be on technology independent synthesis.

#### 1.3.3 Combinational and Sequential Synthesis

There are several algorithms that have been developed for technology independent synthesis, and these algorithms can be partitioned roughly into two groups: combinational synthesis and sequential synthesis algorithms. Most practical designs incorporate registers, and hence most designs include sequential logic networks. Combinational and sequential algorithms differ in how they handle the design's registers.

**Combinational synthesis** algorithms do not change the number or function of the registers. All synthesis algorithms, both combinational and sequential, are constrained to not change the function of the logic network's outputs. Combinational synthesis takes this a step further by not changing the registers either. This simplifies the analysis because the current state functions can be treated as pseudo-inputs and the next state functions can be treated as pseudo-outputs. After performing this abstraction, combinational synthesis techniques focus on the remaining combinational logic network.

Sequential synthesis algorithms are capable of changing the number and function of the registers. They do not abstract the registers and therefore can optimize the combinational logic and the registers at the same time. This is more complex because it requires the algorithms to understand the state space, but this also enables sequential synthesis to do much more powerful design optimizations that are impossible with combinational synthesis.

### 1.3.4 Important Synthesis Examples

Let us explore a few synthesis algorithms that are important to in this thesis. Note that logic synthesis has enjoyed more than 40 years of active research, and many algorithms have been developed to optimize logic networks. Here we focus on the few algorithms most relevant to this work. Consequently, many of these synthesis algorithms in this section are sequential. All algorithms will be explained through example, and their effects on the logic of Figure 1.5 will be examined.

Example 5. Synthesis With Cone of Influence Reduction

| 1: <b>function</b> findCoi(gate, coiSet)                    |

|-------------------------------------------------------------|

| 2: if $(gate \in coiSet)$ then                              |

| 3: return                                                   |

| 4: else                                                     |

| 5: add gate to coiSet                                       |

| 6:                                                          |

| 7: // Recurse                                               |

| 8: <b>if</b> $(gate is an AND)$ <b>then</b>                 |

| 9: for all inputs in of gate do                             |

| 10: $\operatorname{findCoi}(in,  coiSet)$                   |

| 11: end for                                                 |

| 12: <b>else if</b> ( <i>gate</i> is a register) <b>then</b> |

| 13: findCoi(gate.nextState, coiSet)                         |

| 14: $findCoi(gate.init, coiSet)$                            |

| 15: end if                                                  |

| 16: end if                                                  |

| 17: end function                                            |

Algorithm 1: Recursive Procedure to Find a COI

The **Cone of Influence** (**COI**) of a logic gate is the set of gates and registers in its input or in the input of one of its inputs. Typically the COI of a gate is found in a manner similar to what is shown in Algorithm 1. The procedure starts at the gate and recursively traverses the inputs, adding gates to the set coiSet. The procedure terminates when no new gates can be added to this set. Note that sometimes a COI computation stops at the registers, but this implementation traverses through registers to process both the register's next state function and initial value.

A COI of a gate g is a superset of all the logic necessary to produce the values seen at the output of g. If a gate does not belong to the COI of g then that gate can be removed from the logic network without influencing the values observed at g.<sup>1</sup>

The COI gives rise to a very simple type of logic synthesis optimization: COI Reduction. The outputs of a logic network are more important than any other internal signals. In a COI reduction, the COI of each output is computed, and these COI's are unioned. This gives a set of gates such that if a gate k is not in the set then k can be removed without affecting any of the outputs. Therefore the size of the logic network can be reduced without disturbing any of the outputs.

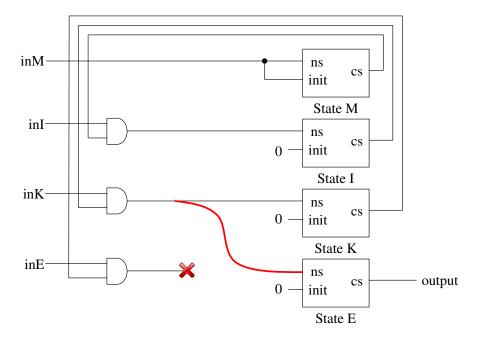

Figure 1.6 shows the effect of COI reduction on the logic network previously examined in Figure 1.5. In Figure 1.5, the register labeled "State ?" and the subset of the logic driving its next state function are not in the COI of the output. Therefore this logic can be removed, yielding a smaller logic network with equivalent output functionality.

COI reduction is a sequential transformation because it can change the number

<sup>&</sup>lt;sup>1</sup>Note that in general there may be gates in the COI of g that can also be removed without changing the values at g. This happens because of logical redundancies that frequently occur in logic networks.

Figure 1.6: Cone of Influence reduction applied to Figure 1.5.

of registers. It is the simplest such sequential transformation, but because of its simplicity it is often used as a subroutine in other synthesis algorithms. It will be used several times throughout this thesis.

#### Example 6. Synthesis By Merging Signals

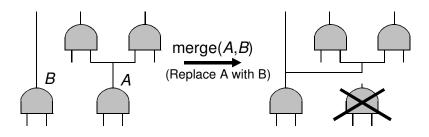

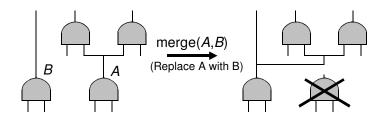

Merging of signals is another simple type of synthesis transformation. The **fanouts** of a gate g are the gates in the logic network that take g's output as one of their inputs. **Merging** is an operation on two gates x and y in a logic network such that the fanouts of x are modified to input the logical value from y instead of x. After the inputs of the fanouts are thus modified, gate x no longer has fanouts and can be removed from the logic network through a subsequent COI reduction<sup>2</sup>.

$<sup>^{2}</sup>$ In general, after x is removed some of its fanins will no longer have outputs and can be removed as well.

Figure 1.7: Merging applied to Figure 1.6.

Figure 1.7 shows an example of merging within the logic network of Figure 1.6. One AND gate fans out to the register denoted "State K," and the another AND gate fans out to the register denoted "State E." If the gates are merged then a single AND gate will be used to drive values into both registers. The other AND gate is now unnecessary because it has no outputs, and a COI reduction can be used to remove this gate.<sup>3</sup>

In general, merging is a symmetric operation in that in the merging of x and y we could use x to replace y or y to replace x. Such a merge is known as an **undirected merge**. There are advantages to each of the two merging directions, and the direction that is used is usually selected depending on the logic network structure. Logic networks must be acyclic, with the exception of cycles that involve registers. Cycles that do not involve registers are known as **combi**-

<sup>&</sup>lt;sup>3</sup>Note that this operation changes the behavior of the output and is therefore not a legal logic synthesis transformation. It is shown here for illustrative purposes only.

national cycles and can be easily avoided by replacing the gate that is furthest from the registers with that which is closest to the registers. More formally, we can define the level of a gate g to be the number of gates on the shortest path from any register to g. If merging always replaces the higher-level gate h with the lower-level gate l then there can be no cycle involving l because the level constraint implies that h cannot fan out to l. Therefore after merging it is impossible for l to fan out to itself, and this is sufficient to guarantee acyclicity of the modified logic network.

In some applications in this thesis it is advantageous to consider **directed merges**. In this type of merge, the directionality is explicitly specified. That is, it is legal to replace gate x with gate y but not vis-a-versa. Directed merges are usually seen in applications where only one merge direction is guaranteed to preserve the functionality of the logic network.

There are many synthesis algorithms that involve merging gates. One of the simplest applications is known as **SAT/BDD Sweeping**. In this algorithm pairs of gates are proved to be equivalent and then they are merged and COI reduction is called. Because the gates are equivalent, the merge direction is not important and undirected merges are used. The merging is guaranteed to preserve the output behavior of the logic network, as is required with all logic synthesis algorithms. Later in this thesis methods will be introduced where strict equivalence between gates is not proved yet merging still preserves the output behavior to enable merging to preserve output behavior.

#### Example 7. Synthesis With State Re-encoding

The algorithms discussed above require little or no knowledge of the state space of the design. For this reason they are highly **scalable**, or fast running and able to handle large design sizes, but they lack the power to dramatically impact the logic network. As an example of a more powerful (and expensive) optimization, we consider state re-encoding here.

State re-encoding is the process of changing the binary state encodings on the STG and then re-expressing the logic network in terms of these changed encodings. The logic network is highly sensitive to these encodings, and small changes in the codes used can have a large impact on the number of gates and the delay of the network. Additionally, the length of the codes used can be varied, resulting in a sequential logic network with a different number of registers.

Logic synthesis tools work on logic networks and not on state transition graphs, making re-encoding of the individual states difficult. While an STG can be extracted from a logic network, often the resultant STG will be too large to manipulate efficiently. Practical re-encoding is therefore limited to only re-encoding the reachable states, but this requires one to exactly know which states are reachable. In large sequential logic networks, computing the exact set of reachable states is computationally infeasible. For all of these reasons, state re-encoding is computationally difficult and therefore rarely used. It is introduced here because later algorithms in this thesis will be compared with state-encoding.

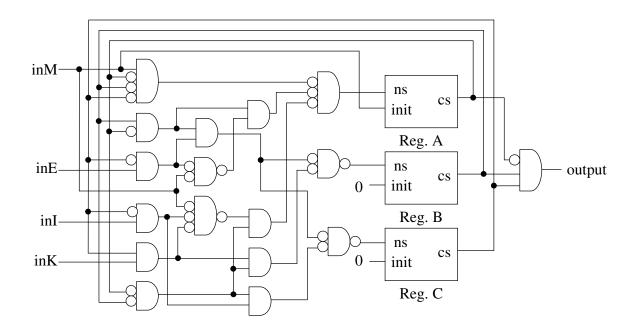

As an example of state encoding, consider changing the state encodings of the sequential logic network shown in Figure 1.6. From Figure 1.4 we know that there are 5 reachable states: "M", "I", "K", "E", and "?". Previously a length-5 encoding was used, resulting in a logic network with 5 registers. For N reachable states, the length of the code words is bounded below by  $\lceil \log_2(N) \rceil$ . Therefore the states in this simple STG can be encoded using only 3 bits. Suppose the 3 bits of the encoding are labeled A, B, C and the encoding is specified like so:

• "M" is denoted as A = 0, B = 0, C = 0.

Figure 1.8: State Re-encoding applied to Figure 1.6.

- "I" is denoted as A = 0, B = 0, C = 1.

- "K" is denoted as A = 0, B = 1, C = 0.

- "E" is denoted as A = 0, B = 1, C = 1.

- "?" is denoted as A = 1, B = 0, C = 0.

With these encodings, a sequential logic network can be derived that has 3 registers: A, B, and C. This logic network is shown in Figure 1.8. Clearly, this logic network has many more gates than the original network, but it has fewer registers. Depending on the objective function of the synthesis tool, such a transformation might be either accepted or rejected.<sup>4</sup>.

#### Example 8. Synthesis With Resubstitution

<sup>&</sup>lt;sup>4</sup>This re-encoding example was done by hand, but due to its complexity such manual analysis can be error prone. The equivalence between Figures 1.6 and 1.8 was formally verified using IBM's SixthSense tool [Baumgartner, 2006]

Often in synthesis reducing the number of registers is critically important. State re-encoding has the potential to dramatically reduce the number of registers but is computationally difficult. Reduction in the number of registers can be accomplished by several methods, state re-encoding being just one. Any method that reduces the number of registers can be viewed as a weak form of state re-encoding because the encodings of all the reachable states will be shortened by at least one bit.

Resubstitution is a algorithm that can be used to re-express a logic function in terms of other logic functions. More formally, if a logic network has gates A, B, and C then resubstitution can be used to find a function F such that A = F(B,C). F(B,C) can then be constructed in the logic network and merged with A. A COI reduction is then used to completely remove A from the logic network.

In this thesis we will focus on resubstitution applied to the registers. In this case, A, B, and C will be registers and the removal of A is equivalent to the removal of a register from the sequential logic network. Removing registers in this way takes advantage of redundancies in the state encodings such that a bit of the code can be removed without changing the functionality of the STG.

The state encoding used in the STG of Figure 1.4 is called **one-hot** because exactly one of the registers will store a 1 at any point in time with the remaining registers storing 0. A one-hot encoding usually results in a small number of logic gates in the logic network but a large number of registers.

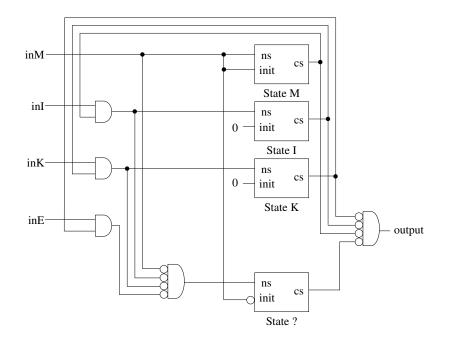

Any one-hot encoding is redundant in that exactly one of the registers can be expressed as a function of the others. Take for example the FSM shown in Figure 1.5. Register E can be expressed as  $E = \overline{M \cdot I \cdot K \cdot ?}$ . Introducing this new logic function into the logic network and doing a merge followed by a COI

Figure 1.9: Resubstitution applied to Figure 1.5.

reduction gives the logic network shown in Figure 1.9. Some of the registerreduction power present in the state re-encoding algorithm is captured here, and resubstitution can be implemented in an efficient and scalable manner.

## 1.3.5 Synthesis Challenges

Physical synthesis has been a great advance in the traditional CAD toolchain, but there remains much research to be done in traditional technology-independent synthesis. Specifically, sequential synthesis provides several ways to optimize a logic network by taking advantage of the state space. There are three main challenges in sequential synthesis:

1. Sequential synthesis is inherently difficult because it usually requires knowledge about the state space. The set of reachable states is very difficult to obtain, and optimizations that utilize this information can be computationally expensive. This thesis will address ways to approximate the set of reachable states and then use this information in an efficient manner to optimize a logic network.

- 2. All software tools are likely to contain bugs, and sequential logic synthesis tools are no different. In order to prevent a logic synthesis bug from causing an error in a manufactured chip, all synthesis results must be checked. A correct logic synthesis tool will not change the behavior of the outputs of the logic network, and so often one wishes to prove that the outputs of the original and optimized logic networks are pairwise equivalent, guaranteeing that sequential synthesis did not alter the design functionality. This verification problem can be quite challenging. This thesis will discuss advances in the field of formal verification, and these advances can be used to verify the results of sequential synthesis. In this way, formal verification enables sequential synthesis algorithms cannot be trusted or used in industrial settings.

- 3. Sequential synthesis changes the number and/or function of the registers in the sequential logic network. The registers today serve as points at which a designer can fully understand the operation of his or her design, and by changing the registers a synthesis tool may optimize a design yet produce something that the original designer is unable to understand. This makes debugging and **Engineering Change Orders (ECOs)** difficult. This is an important obstacle that stands in the way of mass adoption of sequential synthesis. While this obstacle can be overcome, industry leaders often wish to see tangible benefits of sequential synthesis before re-educating their designers. This thesis will advance the field of logic synthesis, laying the foundation for the later effort to change the way chips are understood and designed.

# 1.4 Formal Verification

#### 1.4.1 The Verification Problem

Chip designers not only need efficient ways to construct complex devices, but they also need ways to verify that these devices operate as intended. The cost of a bug in a computer chip can be quite large, and therefore the need to design the chips correctly and fix any problems early in the design flow is great.

Modern chip designs are very complex, and to overcome this complexity chips are designed hierarchically. Errors can be introduced at any level of the hierarchy, but the errors are more costly to fix at higher levels of the hierarchy. This is because higher level fixes have more side-effects and require the coordination of many designers across the project. Typically, if a bug costs X to fix at one level of the hierarchy, it will cost  $10 \cdot X$  to fix at the next higher hierarchy level [Brand, 2007].

#### Example 9. The Cost of a Bug

Modern chips are designed hierarchically, and a logic designer typically works on the lowest-level of the design, called a logic block. Suppose the designer introduces a bug in his or her logic block, and this bug takes the designer 3 days to debug and fix. At a salary of \$100,000 per year, the bug costs the company about \$1000 in just the designer's salary for these 3 days.

Now consider what happens in terms of the hierarchy of the chip:

- Logic block: This is the most basic design unit. Typically only one designer works on a block, and that designer is wholly responsible for fixing bugs in the block. In our example, a bug here may take 3 days to fix at a cost of \$1000.

- **Unit:** A unit is a collection of logic blocks. If a bug in a single block is not fixed, it may manifest itself as a subtle bug in the interaction of the different blocks

that make up the unit. This might take 10 designers 3 days to fix for a total cost of \$10,000.

- **Core:** In a CPU, a core is the smallest block that is capable of executing all of the architecture's instructions. Cores are composed of several units, and many designers are responsible for the logic that ultimately goes into the core. Because of the increased complexity of the design and the increased number of people involved, a \$10,000 bug in a unit may become a \$100,000 bug in the core.

- Chip: Modern chips are composed of several cores that interact independently. Suppose our \$100,000 core-level bug was not fixed but instead manifests itself as a complex inter-core bug at the chip level. The increased complexity will mean that the bug costs \$1,000,000 to find and fix at the chip level.

- System: A system is composed of many chips. Indeed, the system is enormously complex, and all of the designers in a company could be working on one system. The example \$1,000,000 chip bug could take \$10,000,000 to fix at this level.

If a bug is not caught while the system is in development then the costs can be even greater. In 1994, Intel released their first Pentium processor. The CPU had a bug in a block that was responsible for floating-point division, the infamous FDIV bug [Nicely, 2008]. The bug was not detected until after the CPU had shipped and was in the hands of consumers. Intel had to initiate a recall in order to fix the problem, and in total this bug cost Intel \$475,000,000.

Clearly, bugs in a chip design can be very costly. There are efforts underway to allow the designer to specify designs in a way that is less bug-prone [OSCI, 2008], but even with these new design styles bugs will persist because of the simple fact that humans sometimes make mistakes. Verification is the process of detecting bugs or checking that a design is free of bugs. Because a design is not manufactured until late in the design process, it is necessary to verify software models of the design. This is known as **pre-silicon** validation. The goal of verification is to check every level of the design hierarchy and to detect bugs early in the design cycle and in the lowest possible level of the hierarchy in order to minimize costs.

### 1.4.2 Simulation Vs. Formal Techniques

Typically pre-silicon validation is accomplished with simulation. A logic simulator is a CAD tool that can be used to read in a model of the logic design and simulate its logical behavior over time. A designer can provide inputs to the design, and the simulator will compute the output values that will result. By providing a temporal sequence of inputs, a simulator can be made to simulate a sequential logic design over a time interval.

Simulation has long been the workhorse of verification, but it has a major problem that is reducing its usefulness in modern chip designs. Simulators simulate one input vector at a time, and as chips have increased in complexity the number of possible input vectors has increased exponentially. Simulators are simply not able to simulate every possible input vector, and this results in poor design **coverage**, or the percentage of the design's behavior that has been checked.

#### Example 10. Verifying a 64-bit Multiplier With Simulation

A common unit in a modern CPU is a **multiplier**. This unit inputs two binaryencoded numbers and outputs their binary-encoded product. Some modern CPUs use 64-bit encodings for numbers, and therefore the multiplier has  $2 \cdot 64 = 128$ binary inputs and 64 binary outputs. The number of possible inputs is therefore  $2^{128}$ . Suppose a designer wishes to verify a 64-bit multiplier with simulation. To ensure 100% coverage it is necessary to simulate each possible input vector. Suppose the simulator is able to simulate 1,000,000 input vectors per second, extremely fast by today's standards. To simulate all  $2^{128}$  input vectors would therefore take  $1.08 \cdot 10^{25}$  years. In comparison, the universe is only  $1.4 \cdot 10^{10}$ years old [Wikipedia, 2008].

Simulation is handicapped by its ability to process only a single input vector at a time, and formal techniques are the answer to this dilemma. A **formal technique** is any algorithm that is able to process all inputs at the same time. Often this is accomplished by treating the inputs **symbolically** and analyzing the circuit behavior in terms of these symbols. **Formal verification** is the application of formal techniques to verification.

Formal verification is the future of verification. As chips become increasingly complex, the number of input vectors will continue to grow. Today it is impossible to simulate every possible input vector, and in years to come the problem will get even worse. Formal verification arose in the 1980's as a theoretic curiosity, but recently formal verification has become a major focus of research in CAD tools.

This thesis will discuss ways to improve formal verification, and because this thesis is focused on formal verification rather than simulation, the word "verification" should be understood to mean formal verification in the text to follow.

#### 1.4.3 Sequential Equivalence Checking

One compelling use of verification is to check that synthesis did not introduce unintended changes into the design. Synthesis tools by definition will optimize a design while preserving the behavior at the outputs of the logic network, but as with all software there is no guarantee that a synthesis tool is free of bugs. While a design might operate as intended, the possibility that a synthesis tool could introduce a bug into the design means that synthesis results must always be verified.

**Equivalence checking** is the process of driving two similar designs with identical input vectors and then checking that the output vectors are identical. Because logic synthesis tools input a logic network and output an optimized and supposedly equivalent network, to check the correctness of the synthesis tool it is sufficient to check the equivalence of the input and output networks.

Sequential Equivalence Checking (SEC) is the extension of equivalence checking to check the correctness of sequential synthesis. The two logic networks whose equivalence is being checked are fed identical temporal sequences of inputs vectors, and the SEC tool checks that the output vectors are always equivalent. Because every state observed in either of the two designs will always be reachable, SEC allows for sequential synthesis to change the behavior of the design on the unreachable states. Therefore, while sequential synthesis is more powerful than combinational synthesis because it allows more flexibility with respect to the state space, it requires SEC in order to check the equivalence of the input and output logic networks. SEC often involves complex and computationally expensive algorithms, but this thesis will contribute methods to make SEC more scalable.

# Example 11. Sequential Equivalence Checking The Logic Networks of Section 1.3.4

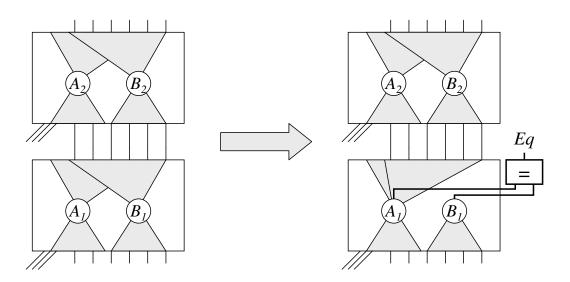

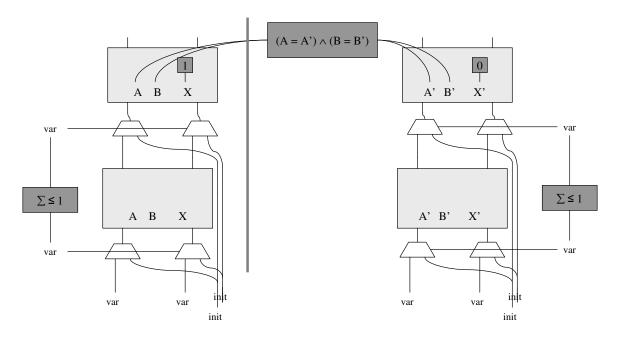

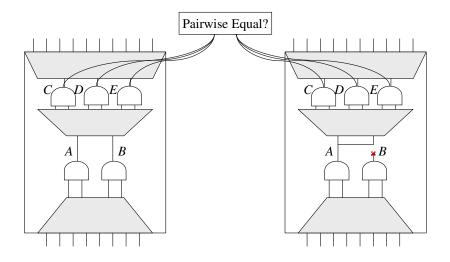

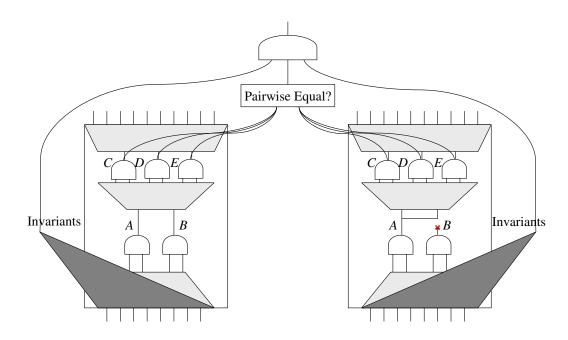

Section 1.3.4 discussed numerous optimizations of the basic sequential logic network in Figure 1.6. SEC can be used to guarantee that this synthesis was correct. As an example, consider the result of resubstitution, shown in Figure 1.9. SEC can be performed on the **product machine** formed from these two simpler logic network. Both logic networks are fed identical outputs, and the resulting composition is shown in Figure 1.10.

Figure 1.10: Checking the sequential equivalence of Figures 1.6 and 1.9.

The product machine has two separate outputs, one for each component logic network. If synthesis operated correctly then these outputs should always be equivalent. SEC is the process of driving this product machine with every possible sequence of input vectors and checking that the outputs are always equivalent.

## 1.4.4 Property Checking

**Property checking** is a more general type of verification. The designer can specify one or more **properties** of the design that should be verified. For example, in programming it is common to use **assertions** to check that your code is operating correctly. Formal verification would treat each assertion as a property and would either 1) prove that for all input sequences it is impossible to violate the assertion or 2) produce a **counterexample trace**, a temporal sequence of inputs that demonstrates how the assertion may be violated.

Many verification tools allow properties to be embedded directly into the designer's HDL, and therefore the designer can specify the properties to be checked as he or she is describing the logic itself. This allows for very intricate properties to be specified, often capturing design assumptions that would otherwise only exist in the designer's head.

Property checking is more general than SEC in that SEC can be expressed as a property checking problem. In SEC, a product machine is constructed and the outputs of the two component designs are proved to be pairwise equivalent. This pairwise equivalence check can be thought of as a property that must be proved on the product machine. In general, for two designs each with n outputs, SEC can be performed by building a product machine and checking n properties on that machine.

Because SEC can be viewed as a special case of property checking, this thesis will focus on the broader field of property checking. Therefore the term verification in the text to follow should be understood to mean formal verification of properties.

#### Example 12. SEC Specified as Property Checking

Consider once more the numerous sequential logic networks presented in Section 1.3.4. The most basic such logic network was presented in Figure 1.5, and the most complex logic network, the result of state re-encoding, was presented in Figure 1.8. The state re-encoding example was complex, and while constructing the example the author used a property checking tool to verify the SEC and thus the correctness of the example.

The IBM verification environment was used to check the correctness of the reencoding. Algorithm 2 shows the VHDL implementation of the product machine used to check the equivalence of Figures 1.5 and 1.8. The two machines each have a single output, output and output2 respectively. A single assertion labeled failo is defined such that failo will be asserted when these two outputs are different. The IBM formal verification tool SixthSense was then used to prove that failo is impossible to assert.

This example also has **constraints**, or conditions that the formal tool must hold to be true. Constraints are often used to model the environment of a circuit, and constraints used in this sense would guarantee that a design is not being stimulated with an illegal input that would never appear in its typical environment. In the case of the two designs examined here, the input signals inM, inI, inK, and inE represent the conditions that the user has pressed the "M", "I", "K", or "E" key, respectively. It is assumed that the user presses at most one key at any point in time, and the constraints labeled c1 through c5 in Algorithm 1.8 are used to model these assumptions. SixthSense is thus disallowed from providing any input stimulus that violates the constraints. This is important because the two designs are actually not equivalent without this environmental

```

1: architecture intro_synth of intro_synth is

signal inM, inI, inK, inE : std_logic;

2:

3:

-- implementation 1: 1 hot

4:

signal cs : std_logic_vector(0 to 3) := "0000";

5:

6:

signal ns : std_logic_vector(0 to 3);

signal m, i, k, e : std_logic;

7:

8:

-- implementation 2: logarithmic encoding

9:

signal cs2 : std_logic_vector(0 to 2) := "100";

10:

signal ns2: std_logic_vector(0 to 2);

11:

signal a, b, c, output2 : std_logic;

12:

13: begin

-- decode everything

14:

in M \ll input(0);

15:

in I <= input(1);

16:

inK \leq = input(2);

17:

in E <= input(3);

18:

19:

--!! [constraint; c0] \leq not in M or not in I;

20:

--!! [constraint; c1] \leq not in M or not in K;

--!! [constraint; c2] \leq not in M or not in E;

21:

--!! [constraint; c3] \leq not in I or not in K;

22:

--!! [constraint; c4] \leq not in I or not in E;

23:

--!! [constraint; c5] \leq not inK or not inE;

24:

25:

26:

...

27:

-- output logic

28:

output \langle = e;

29:

output 2 <= \text{not } A \text{ and } B \text{ and } C;

30:

31:

32:

--!! [fail; fail0; "machines are different" ] <= (output xor output2);

33: end intro_synth;

```

Algorithm 2: Using property checking to check the equivalence of Figures 1.5 and 1.8

constraint. The fact that the in signals are mutually exclusive was used in the state re-encoding, and failing to represent these constraints in verification would result in a **spurious counterexample**, or counterexample that arises simply because of an inadequate verification setup.

To illustrate the importance of SEC, the author checked the correctness of his state re-encoding before drawing the complex circuit of Figure 1.8. In the original state re-encoding derivation, the next state function for register "A" was specified incorrectly, and SixthSense found a counterexample that demonstrated that the designs were legitimately inequivalent. Therefore without SEC, Figure 1.8 would be incorrect.

In the field of property checking, the encountered properties can be classified into two broad types: safety properties and liveness properties. **Safety properties** are properties that express bad design behavior that should be avoided. A counterexample to a safety property is a finite-length sequence of input vectors that can be used to drive the design into a state that violates the property. **Liveness properties** are properties that express good behavior that should always be observed. A counterexample to a liveness property is an infinite length sequence of input vectors that demonstrate that it is possible for the design to always avoid the good behavior specified by the liveness property<sup>5</sup>.

Safety properties have been the focus of much past research because they are conceptually simpler and therefore preferred by logic designers. Therefore a verification tool that is good at checking safety properties is adequate for nearly all logic designers. Recently it has been demonstrated that liveness properties can be transformed into safety properties [Schuppan and Biere, 2006], and therefore the space of liveness properties is contained in the space of safety properties. In this work we study the

<sup>&</sup>lt;sup>5</sup>Because of the finiteness of the state space, all such counterexamples are composed of a tail of states followed by a loop of states.

broader, and conceptually simpler, space of safety properties. In the text to follow, the term property should be understood to mean safety property.

#### **1.4.5** Important Verification Examples

In this section three verification algorithms will be discussed. Similar to synthesis, formal verification has a rich history, and many verification algorithms have been proposed in past research. Many of those algorithms are outside the scope of this thesis, but three algorithms that will be important in future discussions will be explored.

#### Example 13. Explicit State Model Checking

In the formal verification of a safety property, the goal is to demonstrate that the property is satisfied on all reachable states of a finite state machine or to find a temporal sequence of input vectors that can drive the machine from an initial state to a state where the property fails. The most conceptually simple way to do the verification is to simply enumerate all reachable states. If each such state is checked and the property is found to always be true then it is verified. If a reachable state is examined where the property fails to hold then by careful bookkeeping it is possible to produce a sequence of states and corresponding input sequences that form a path from an initial state to the failing state. This is known as **explicit state model checking** or **reachability analysis**.

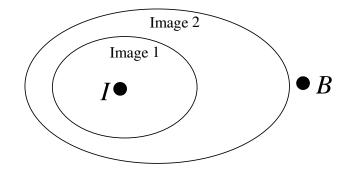

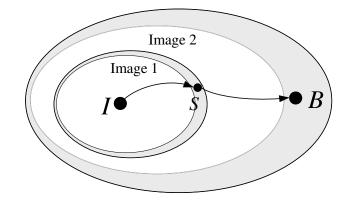

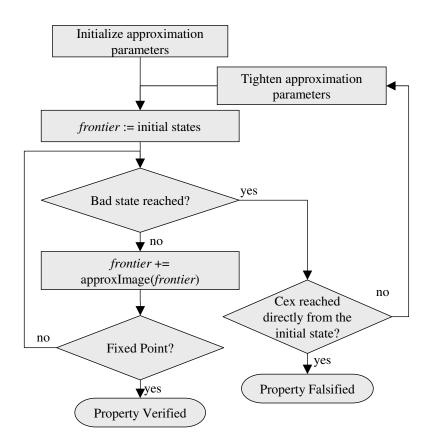

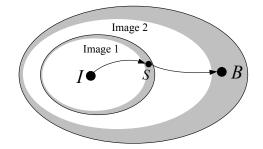

Explicit state model checking proceeds methodically to explore the reachable state space, and to do this it maintains a set of states S that it has examined in the past. This process is illustrated in Figure 1.11 where the state space is gradually explored in a sequence of steps, each step progressing further from the initial states I and looking for states where the property fails B. The steps of the algorithm can be summarized like so:

1. The algorithm examines the initial states, denoted I in Figure 1.11 and

Figure 1.11: Reachability analysis on a state space.

checks that the property holds on these states. The set of examined states is now  $S_1 = \{I\}$ .

- 2. Next, the set of states that are reachable in a single transition from S are examined. This set of states is known as the **image** of S, and the set of examined states is now  $S_2 = S_1 \bigcup image(S_1)$ . If the property fails on any of these states then a counterexample trace can be produced such that the temporal sequence of input vectors defines a path from I through  $S_1$  and terminating in a bad state B in  $S_2$ .

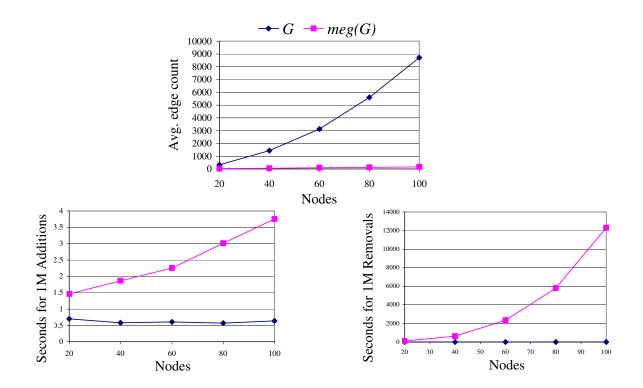

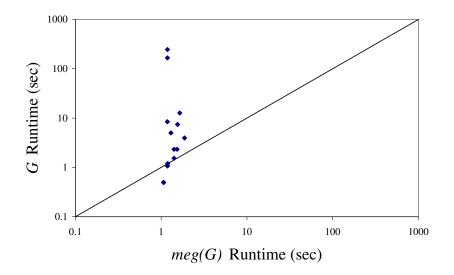

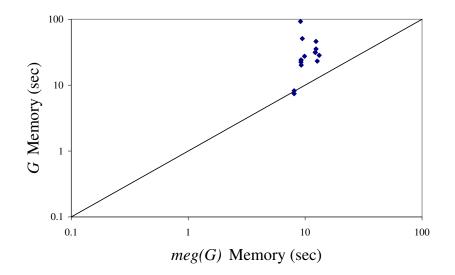

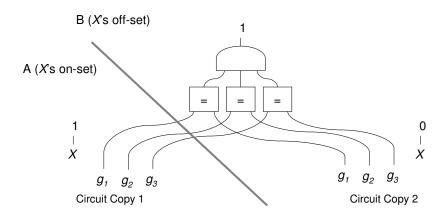

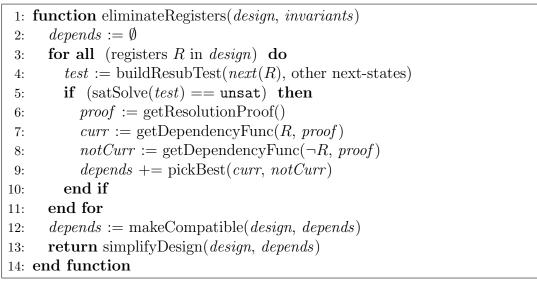

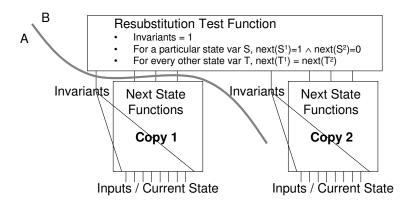

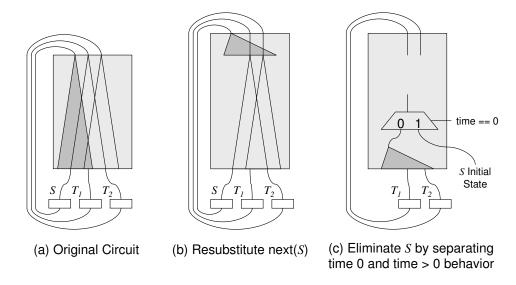

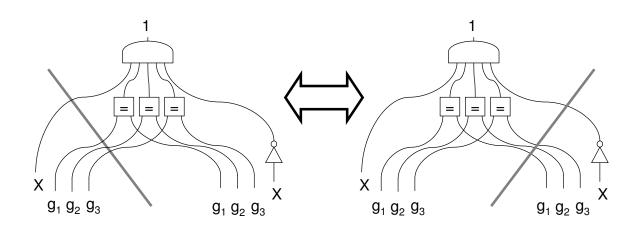

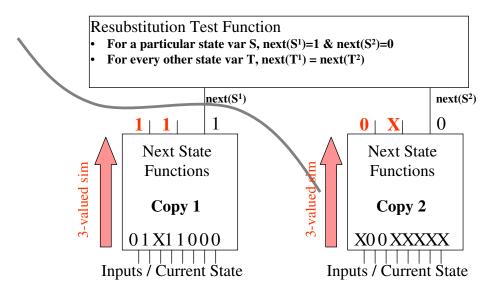

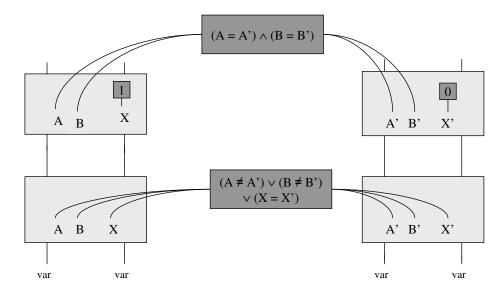

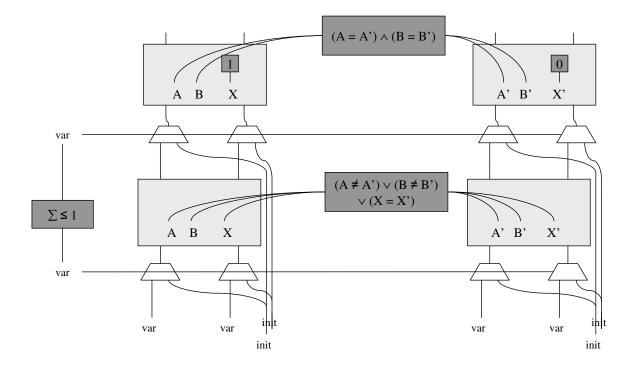

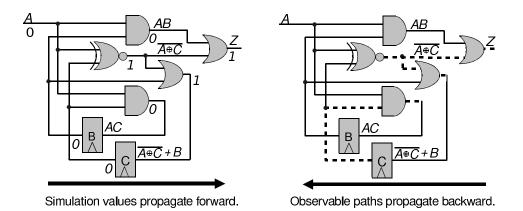

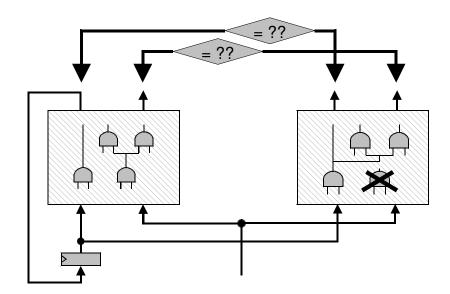

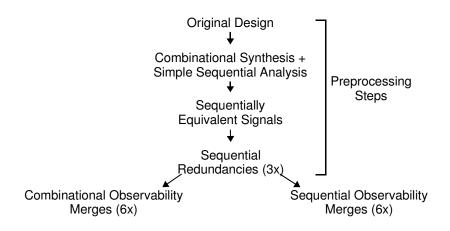

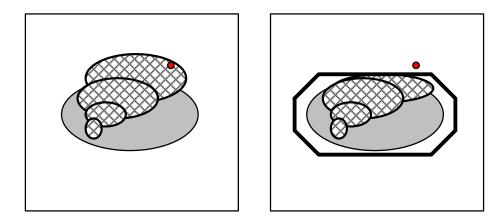

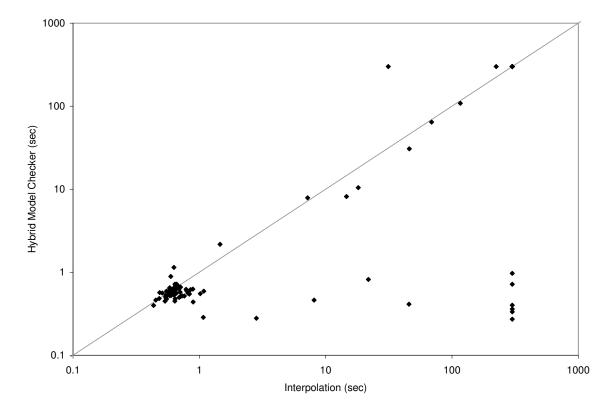

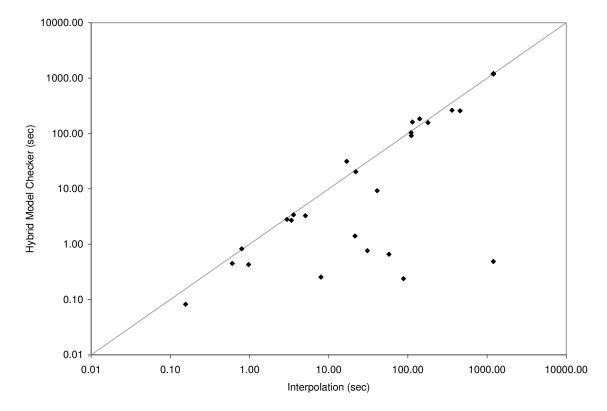

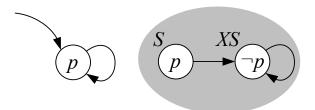

- 3. The sequence of images progresses until either a fixed point is reached, indicating that all reachable states have been explored and the property is verified, or an image operator exposes a bad state B where the property fails to hold.