# Interfaces and Junctions in Nanoscale Bottom-Up Semiconductor Devices

Yu-Chih Tseng

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-65 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-65.html

May 17, 2009

Copyright 2009, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Interfaces and Junctions in Bottom-Up Nanoscale Semiconductor Devices

by

## Yu-Chih Tseng

### B.A.Sc. (University of Toronto) 2002 M.S. (University of California, Berkeley) 2005

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

and the Designated Emphasis

in

Nanoscale Science and Engineering

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Jeffrey Bokor, Chair Professor Vivek Subramanian Professor Steven G. Louie

Spring 2009

The dissertation of Yu-Chih Tseng is approved:

| Chair | Date |  |

|-------|------|--|

|       | Date |  |

|       | Date |  |

University of California, Berkeley

Interfaces and Junctions in Bottom-Up Nanoscale Semiconductor Devices

Copyright 2009

by

Yu-Chih Tseng

#### Abstract

Interfaces and Junctions in Bottom-Up Nanoscale Semiconductor Devices

by

Yu-Chih Tseng

Doctor in Philosophy in Engineering – Electrical Engineering and Computer Sciences University of California, Berkeley

Professor Jeffrey Bokor, Chair

A semiconductor device is a system composed of multiple materials, and its functionality depends on the junctions and interfaces between these materials. This dissertation documents a study of junctions and interfaces in one-dimensional nanoscale semiconductor materials. Examined are the insulator interface and the dopant profile in vapor-liquid-solid (VLS)-grown silicon nanowires, the electronic properties of the native surface of InAs nanowires grown using bottom-up methods, and metal-carbon nanotube (CNT) Schottky contacts. The capacitance-voltage (C-V) measurement is refined to examine these junctions and interfaces. For a Si nanowire, the C-V measurement shows that the density of trap states on its interface with AbO<sub>3</sub> insulator ranges from  $\sim 10^{11}$ /cm<sup>2</sup>·eV in the midgap to  $\sim 10^{13}$ /cm<sup>2</sup>·eV closer to the valence band edge. The boron profile in Si nanowires is found to agree well with predictions from interstitial and vacancy-assisted diffusion model, as in bulk Si. For an InAs nanowire, the C-V technique is used extract the trap density of its native surface, which is  $\sim 3.8 \times 10^{11}$ /cm<sup>2</sup>·eV in the mid-gap and  $\sim 10^{13}$ /cm<sup>2</sup>·eV near the conduction band edge. The trap lifetime in

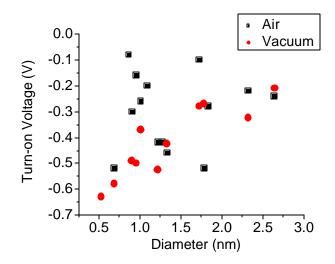

these InAs nanowires is extracted using the C-V method as well. Accurate measurement of the gate capacitance in back-gated InAs nanowires is found to be necessary to determine accurately the electron mobility. The impact of metal-CNT Schottky contacts on the transistor performance and leakage is examined as well. It is found that both the on-state current and off-state leakage depend strongly on the Schottky Barrier Height (SBH) at the contacts. The scaling of the SBH with the CNT diameter shows that the length of the electrical junction is about 25nm. The metal-CNT Schottky junction is also studied using a new instrument capable of measuring rapidly attofarad (10<sup>-18</sup> F)-level capacitances. This study confirms the unpinned nature of the metal-CNT Schottky contacts, and shows a way to directly determine the height of that energy barrier.

The dissertation abstract of Yu-Chih Tseng is approved:

Professor Jeffrey Bokor, Chair

Date

To My Parents

Ming-Ho Tseng and Ai-Chiao Liu

For Their Love

# **Table of Contents**

| Introduction | 1 | Ĺ |

|--------------|---|---|

|--------------|---|---|

## **Chapter 1: Ultra Low-Level Capacitance Measurement**

| 1.1 R  | equirements for the C-V measurement and the usual laboratory apparatus8 |

|--------|-------------------------------------------------------------------------|

| 1.2 TV | ne Cold Bridge11                                                        |

| 1.3 Oj | perating the Cold Bridge13                                              |

| 1.4 Fi | ull Setup16                                                             |

| 1.5 No | pise Performance of the Cold Bridge17                                   |

| 1.6 D  | evice Layout and Design to Minimize Background Capacitance18            |

| 1.7 D  | ealing with Losses22                                                    |

| 1.8 Sı | <i>ummary</i>                                                           |

## **Chapter 2: Diffused Junction in a Silicon Nanowire**

| 2.1 Design of Test Structure and Measurement Scheme | 27 |

|-----------------------------------------------------|----|

| 2.2 Device Fabrication                              | 28 |

| 2.3 The Capacitance Measurement                     | 32 |

| 2.4 The Interface State Density                     | 34 |

| 2.5 Dopant Profile                                  | 37 |

| 2.6 Summary                                         | 41 |

### **Chapter 3: Characterization of Back-Gated InAs Nanowires**

| 3.1 The Interface Between the InAs Nanowire and Its Native Oxide | 46 |

|------------------------------------------------------------------|----|

| 3.2 Capacitance Measurement for Mobility Extraction              | 53 |

| 3.3 Summary and Future Work                                      | 57 |

### **Chapter 4: Metal-Carbon Nanotube Schottky Contacts**

| 4.1 P | rior Work                            | 52 |

|-------|--------------------------------------|----|

| 4.2 A | rray Design, Fabrication and Testing | 53 |

| 4.3 S | tatistical Results                   | 56 |

| 4.4 T | The Geometry of the Pd-CNT contact   | 72 |

| 4.5 C | Other Metals                         | 76 |

| 4.6 C | Conclusions                          | 30 |

# Chapter 5: Capacitance Measurement of Metal-Semiconductor Carbon Nanotube Schottky Contacts

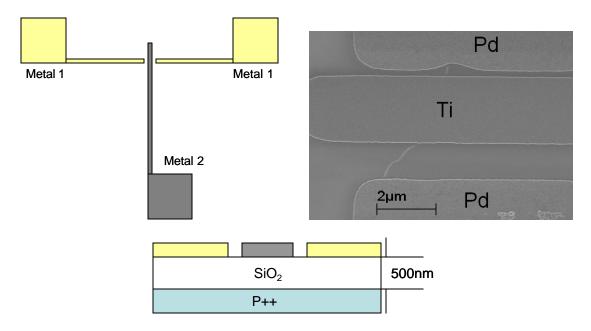

| 5.1 The Test Structure for C-V Measurement and Its Fabrication       | 87  |

|----------------------------------------------------------------------|-----|

| 5.2 Transport Characteristics of Metal-Semiconductor Schottky Diodes | .91 |

| 5.3 Simulation of the C-V Measurements                               | .93 |

| 5.4 Measurement Results                                              | 99  |

| 5.5 Summary and Future Work                                          | 105 |

| <b>Conclusions</b> 10 |

|-----------------------|

|-----------------------|

### Acknowledgements

There are many people who helped me complete this dissertation. First, I would like to thank my thesis advisor, Professor Jeffrey Bokor, for his steady support over the course of 7 years, both in providing the requisite administrative and financial support, but also for his insights and suggestions. I would also like to thank the various collaborators I worked with, whose expertise I was able to benefit from. Professor Ali Javey was very generous is sharing many of his lab equipments, and a pleasure to collaborate with on the InAs nanowire project. I greatly enjoyed the collaboration with students and post-docs in his group, namely Johnny C. Ho, Lexi Ford, Yu-Lun Chueh and Zhiyong Fan. I am grateful to Professor Paul McEuen and Dr. Shahal Ilani for hosting me at Cornell University in the summer of 2006, where I was able to develop the low-level capacitance measurement technique. I would like to thank Erik Garnett, Devesh Khanal, Professor Peidong Yang and Professor Junqiao Wu for their collaboration on the Si nanowire project. In addition, I am grateful for the help provided by Saurabh Sinha and Professor Kevin Cao of Arizona State University on the compact modeling of the carbon nanotube transistors discussed in chapter 4 and to Professor Jing Guo of the University of Florida for providing a Poisson-Schrodinger solver for simulating carbon nanotube devices. As a recognition to the importance of financial support in scientific research, I would like to single out the unique role of the Focused Center Research Program, a subsidiary of the Semiconductor Research Corporation, in providing the funds for supporting my studies.

Lastly, I would like to acknowledge the personal support of my family and close friends, who throughout this long journey never lost faith in me. Your trust is all I needed to persevere.

# Introduction

Any solid-state semiconductor device is a material system. Be it a MOS transistor, bipolar junction transistor, PN diode, Schottky diode, photodiode or solar cell, any functional solid-state device requires the coming together of materials across a large spectrum of electrical conductivity, ranging from oxides for gate insulator to semiconductors for transistor channel, to metals and their alloys for electrical contact. The electrical properties of each constituent of a device influence only partly the overall function. More often than not, the interface between two materials is equally important. The PN junction is the most fundamental example. It is because of the space-charge region at the interface between the two oppositely-doped materials that diodes can rectify, and that electron-hole pairs generated in solar cells can be separated. Another example is the metal-semiconductor contact, which can rectify because of the Schottky

barrier between the metal and the semiconductor. It can also be ohmic if the substrate is sufficiently doped. The oxide-semiconductor interface in a MOSFET is yet another important example. Because the current flowing in a MOSFET is located directly under the gate oxide, a poor interface can strongly degrade the transistor's performance.

| $H^1$    | H <sup>1</sup> Periodic Table of the Elements |          |                                                                                                             |                 |          |            |            |                                                            |                  |          |          |          |                  |                 | 2<br>He         |           |          |

|----------|-----------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------|-----------------|----------|------------|------------|------------------------------------------------------------|------------------|----------|----------|----------|------------------|-----------------|-----------------|-----------|----------|

| 3<br>Li  | Be                                            |          | <ul> <li>hydrogen</li> <li>alkali metals</li> <li>alkali earth metals</li> <li>transition metals</li> </ul> |                 |          |            |            | oor me<br>onmet                                            | als              |          |          | B        | C                | N               | 08              | ۶         | 10<br>Ne |

| 11<br>Na | 12<br>Mg                                      |          |                                                                                                             |                 |          |            |            | <ul> <li>noble gases</li> <li>rare earth metals</li> </ul> |                  |          |          |          | Si <sup>14</sup> | P <sup>16</sup> | S <sup>16</sup> | 17<br>Cl  | 18<br>Ar |

| 19<br>K  | Ca <sup>20</sup>                              | 21<br>Sc | 22<br>Ti                                                                                                    | 23<br>V         | 24<br>Cr | 25<br>Mn   | 26<br>Fe   | 27<br>Co                                                   | 28<br>Ni         | 29<br>Cu | 30<br>Zn | 31<br>Ga | Ge               | 33<br>As        | Se<br>Se        | 35<br>Br  | 36<br>Kr |

| 37<br>Rb | Sr <sup>38</sup>                              | 39<br>Y  | Zr                                                                                                          | 41<br>Nb        | 42<br>Mo | 43<br>Tc   | 44<br>Ru   | 45<br>Rh                                                   | 46<br>Pd         | 47<br>Ag | 48<br>Cd | 49<br>In | 50<br>Sn         | 51<br>Sb        | 52<br>Te        | 53<br>    | Xe<br>Xe |

| Cs       | <b>Ba</b>                                     | 57<br>La | 72<br>Hf                                                                                                    | 73<br><b>Ta</b> | 74<br>W  | 75<br>Re   | 76<br>Os   | 77<br>Ir                                                   | Pt <sup>78</sup> | 79<br>Au | 80<br>Hg | 81<br>Ti | 82<br>Pb         | 83<br>Bi        | 84<br>Po        | 85<br>At  | 86<br>Rn |

| 87<br>Fr | <sup>88</sup><br>Ra                           | 89<br>Ac | 104<br>Unq                                                                                                  | 105<br>Unp      |          | 107<br>Uns | 108<br>Uno |                                                            |                  |          |          |          |                  |                 |                 |           |          |

|          |                                               |          | 58<br>Ce                                                                                                    | 59<br>Pr        | 60<br>Nd | 61<br>Pm   | 62<br>Sm   | 63<br>Eu                                                   | 64<br>Gd         | 65<br>Tb | 66<br>Dy | 67<br>Ho | 68<br>Er         | 69<br>Tm        | 70<br>Yb        | 71<br>Lu  |          |

|          |                                               |          | 90<br>Th                                                                                                    | 91<br>Pa        | 92<br>U  | 93<br>Np   | 94<br>Pu   | 95<br>Am                                                   | 96<br>Cm         | 97<br>Bk | 98<br>Cf | 99<br>Es | 100<br>Fm        | 101<br>Md       | 102<br>No       | 103<br>Lr |          |

**Figure L1:** Elements used in an integrated circuit, compiled from a survey of published literature [1-9]. Red: elements used in first integrated circuits, circa 1970. Blue: new elements incorporated in ICs, circa 2004. Orange: under research.

Early semiconductor devices and circuits involved few materials: silicon and its natural oxide, a few dopant elements, and a few metals to make contacts and interconnects. Today, integrated circuits involve many more elements in the periodic table (figure I1), and more exotic compounds to meet advanced performance and reliability benchmarks, while being ever smaller. Examples include Ge for straining the channel[1], HfO<sub>2</sub> and ZrO<sub>2</sub> for gate dielectric[2,3], Mo and its associated compounds

for gate[4], C in low-k interlayer dielectrics [5], W in vias[6], Co, Ni in silicides [7], and As, Sb for low-diffusivity dopants. Many other elements and compounds, such as PtSi[8], SrTiO[9], are also investigated as well.

As a result of this material "diversification", interface properties are ever more important, and start to impose limits on device design and performance. The requirements for the interface between the gate dielectric and silicon complicate considerably the material choice for high-k dielectric. In highly-scaled transistors, the contact between highly doped source/drain and metal is the largest contributor of parasitic resistance that lowers the drive current. Controlling short-channel effects requires ever shallower and more abrupt junctions that are increasingly difficult to make using existing process technologies.

As individual transistor shrinks in size, there is a growing interest in a new class of one-dimensional semiconductor materials. These, represented by carbon nanotubes and nanowires of various semiconductor materials, are synthesized using chemical and self-assembly methods, and cannot be easily manufactured starting from bulk materials. These nanowires and nanotubes offer new possibilities. In carbon nanotubes, for example, carrier scattering is greatly reduced, leading to high carrier mobility, suitable for high-perfomance transistors[10]. The mere shape of these nanotubes and nanowires makes it easy to fabricate devices with new geometry, such as surround-gate transistors with optimal electrostatic control[11]. The performance of these nanotube and nanowire transistors depends, just like their counterpart in bulk, on proper engineering of their interfaces and junctions with other materials. Semiconductor carbon nanotubes, for example, usually form Schottky contacts with metals, and such a junction can dictate completely the device's behavior [12]. In Si nanowires, it has been shown that the conditions at the surface can alter the carrier mobility considerably[13]. A similar behavior is observed in other type of nanowire devices.

Unlike bulk materials, there are no systematic studies of the interfaces of these bottom-up materials, with the exception of transport across CNT Schottky contacts. The primary reason is the small size of these nano-objects, which precludes the usage of common surface characterization techniques such as XPS, capacitance-voltage, DLTS, admittance spectroscopy, or SIMS. Additionally, these nano-objects generally vary greatly in size, and assembling many of them with a long-range order, in a way that unambiguous information can be obtained, is still a challenge.

This thesis describes the investigation of some basic junctions in these novel one-dimensional semiconductors using capacitance-voltage measurements, extended to very low levels. Conventional instrumentation for this technique requires test capacitors with an area in the order of  $100\mu$  m x  $100\mu$ m. As a result, this technique was only applicable to bulk materials. In this work, this technique is extended to a much higher precision in order to directly characterize an individual junction of small area. The first application is to examine the dopant distribution in a VLS-grown silicon

nanowire and surface trap density at the interface between it and  $A_{\rm b}O_3$  dielectric. Second, the native surface of an InAs nanowire is examined. Third, a widely studied junction, the metal-carbon nanotube Schottky junction, is re-examined to study its impact on the performance of CNT transistors, and we further investigate this junction in detail using the capacitance-voltage technique.

[1] C.-H. Jan et al., International Electron Device Meeting, December 2005,

Washington DC.

[2] M.A. Quevedo-Lopez et al., *International Electron Device Meeting*, December 2005, Washington DC.

[3] G.D. Wilk, R.M. Wallace, J.M. Anthony, J. Appl. Phys., 87, 484-492 (2000)

[4] P. Ranade, H. Takeuchi, T. King, C. Hu, *Electrochemical and Solid State Letters*, 4, G85-G87 (2001)

[5] D. Shamiryan, F. Iacopi, S.H. Brongersma, Z.S. Yanovitskaya, J. Appl. Phys., 93, 8793 (2003)

[6] F. Liu et al, *International Electron Device Meeting*, December 2008, San Francisco.[7] A. Lauwers et al, *International Electron Device Meeting*, December 2005, Washington DC.

[8] J. Kedzierski, P. Xuan, E.H. Anderson, J. Bokor, T.J. King, C. Hu, *International Electron Device Meeting*, December 2000, San Francisco.

[9] R.A. McKee, F.J. Walker, M.F. Chisholm, Phys. Rev. Lett., 81, 3014-3017 (1998)

- [10] A. Javey, J. Guo, Q. Wang, M. Lundstrom, H. Dai, *Nature*, **424**, 654-657 (2003)

- [11] J. Goldberger, A. Hochbaum, R. Fan, P. Yang, Nano Lett., 6, 973-977 (2006)

- [12] S. Heinze, J. Tersoff, R. Martel, V. Derycke, J. Appenzeller, P. Avouris, Phys. Rev.

- Lett., 89, 106801 (2002)

- [13] R. He and P. Yang, Nature Nanotechnology, 1, 42-46 (2006)

# Chapter 1

# **Ultra Low-Level Capacitance Measurement**

There are several related techniques for characterizing the electronic properties of surfaces, interfaces and junctions in semiconductor materials. Probably the most commonly used method is the capacitance-voltage (C-V) measurement. It is a versatile and straightforward way of measuring simple parameters such as the static dielectric constant *e*, and the effective dielectric thickness  $T_{ox}$ . Frequency- and temperaturedependent C-V measurements give information on interface trap density ( $D_{it}$ ), and the lifetime of these traps. When applied to a diffused junction or a Schottky junction, one can extract material parameters such as the spatial distribution of dopants, as well as the Schottky barrier height.

### **1.1 Requirements for the C-V measurement and the usual laboratory apparatus**

The requirements for making good C-V measurements are very straightforward. First, the C-V meter should be able to operate across a wide frequency range and to resolve both capacitive and resistive components. Commercial C-V meters, usually RLC analyzers, do this very well. Second, the test structure must be of sufficient size and quality. A typical on-chip capacitor test structure needs to have an area of about  $100\mu m \times 100\mu m$ , to provide enough area for making contact with probe tips, and to provide enough signal to be resolved by the C-V meter. In addition, the die lectric needs to be insulating and robust enough to ensure low leakage, such that the resistive component does not overwhelm the capacitive component, and that the dielectric does not breakdown too easily during the measurement.

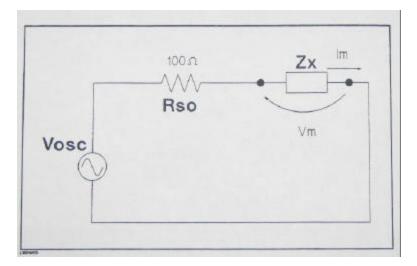

A commonly used RLC analyzer is the HP4284A, which applies an AC voltage across the device under test (DUT) and measures the amplitude and phase of the current through the DUT using a built-in ammeter. A circuit schematic (figure 1.1) from the HP4284A operating manual shows the general working principle. Depending on the chosen circuit model, the R,L,C parameters can be extracted. Unfortunately, the HP4284A is limited by its poor current resolution (1nA) [1]. For an applied AC amplitude of 25mV, the smallest impedance that can be resolved is about 25Mohm, which translates to about 300aF at 20MHz In practice, measurements are often performed at much lower frequencies, and the resolution is significantly worse as a result. Also, to obtain an accurate measurement, the applied AC amplitude can not be

larger than the voltage step size, placing therefore a lower limit to the signal-to-noise ratio.

Figure 1.1: Basic working principle of the HP4824A impedance analyzer.  $I_m$  is measured for known  $V_{osc}$ .

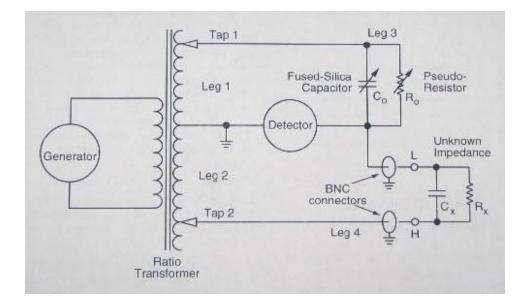

Alternatively, a capacitance bridge such as the Andeen-Hagerling AH2700A can be used to perform the C-V measurements with a much higher precision. This instrument is very similar to a Wheatstone bridge, and owes its precision to low-noise capacitance standard elements and built-in electronics. AH2700A has been employed recently with great success to measure a variety of small capacitances [2,3], and is used in part of the work that follows. When using this instrument, the DUT is connected as shown in figure 1.2 [4]. By adjusting the passive elements  $R_0$  and  $C_0$  in figure 1.2, the bridge can be balanced by nulling the input to the detector. When very long averaging times are used (>24hrs), a resolution of ~2aF can be obtained.

Figure 1.2: Circuit Schematics of the AH2700A capacitance bridge.

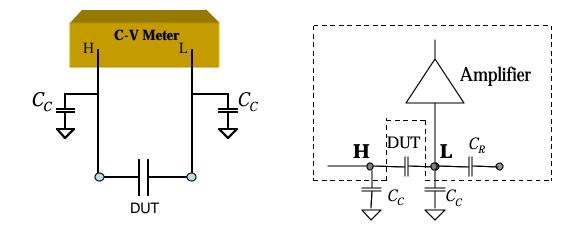

In the capacitance bridge described above, a basic limitation is the parasitic capacitance  $C_c$  associated with the cables connecting the DUT to the meter. The parasitics from the cables can be represented schematically in figure 1.3. In the bridge, the AC signal is supplied from the 'high' node (H). While  $C_c$  at the high node (H) of the DUT causes at most a slight phase rotation of the incoming signal,  $C_c$  at the low node (L) acts as a capacitor divider and shunts the AC signal to ground, especially when the capacitance of the DUT is very small in comparison to  $C_c$ . As a result, the signal reaching the detector is extremely feeble and not obviously different from zero, even when the bridge is not balanced. When this meter is set up in a typical laboratory, cable length in the order of 2m is needed, resulting in a capacitance of 200aF (typical of micron-scale objects), the parasitic  $C_c$  reduces the AC signal reaching the detector to 25nV, which is difficult to resolve unless a long averaging time is used. If an even

smaller energy resolution is needed, especially in a low temperature experiment, then an even smaller AC excitation is required. For smaller capacitances this "brute-force" method would take an impractically long averaging time.

**Figure 1.3:** Schematic representation of the parasitic capacitances from the cables. The dashed line encloses components internal to the C-V bridge. DUT: Device Under Test.  $C_x$ : internal reference capacitor.  $C_c$ : parasitic capacitance between the signal and ground of the BNC cable.

### **1.2 The Cold Bridge**

While the commercial bridge AH2700A is adequate for fairly large capacitances (>100aF), it is less so for much smaller ones because of the cables. A simple solution is to reduce the distance between the DUT and the meter, but the cables can not be shortened very much if a probe station is required to make contact to the DUT. Furthermore, the electronics inside the AH2700A would still operate at room temperature, where the Johnson noise places a lower limit to the input noise of the detector.

However, the basic improvements are clear: shorten the cables and operate at low temperatures. Ashoori pioneered the use of ultra-low capacitance spectroscopy to examine single electron charging in low-dimensional structures[5], by placing the bridge on the same chip as the sample. Subsequent refinement by his group[6] consists of mounting a similar apparatus on the tip of a scanning probe to perform spatiallyresolved capacitance spectroscopy. While impressive, the apparatus they developed lacks the modularity that would allow the measurement of an arbitrary device. The instrument described in this thesis allows one to apply this technique in a much more general and flexible way to an arbitrary device.

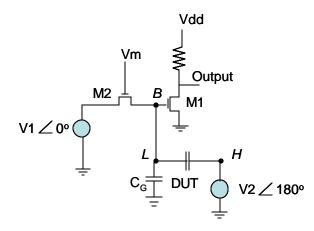

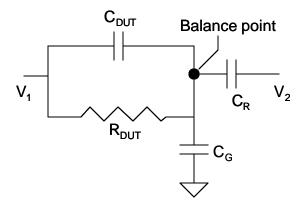

The circuit schematic of the cold bridge is described in figure 1.4, and the photo of the actual apparatus in figure 1.5. By shortening the distance between the low end of the DUT and the detector input to about 0.5cm, the parasitic shunt capacitance to ground is about 6pF, or less than 1/20 of the cable length needed in a typical laboratory setting.

**Figure 1.4:** Circuit schematic of the Cold Bridge. V1, V2 are AC sources  $180^{\circ}$  apart in phase. M1 is a discrete HEMT transistor used to amplify the signal at *B*. M2 is also a discrete HEMT transistor.  $C_G$  represents the total capacitance between *B* and ground. Note that the amplifier M1 is inverting.

Figure 1.5: Photo of the actual Cold Bridge.

### **1.3 Operating the Cold Bridge**

To measure capacitances with the cold bridge, one balances the bridge so that voltage at the balance point '*B*' illustrated in figure 1.4 is minimized (to zero in theory), by varying the amplitude of one of the AC sources ( $V_1$ ,  $V_2$ ). These two AC sources are  $180^{\circ}$  apart in phase so their contribution subtract from each another. The voltage at the balance point *B* is simply:

$$V_{B} = V_{1} \left( \frac{C_{R}}{C_{R} + C_{G} + C_{DUT}} \right) - V_{2} \left( \frac{C_{DUT}}{C_{R} + C_{G} + C_{DUT}} \right)$$

(1.1)

, where the negative sign is due to the out-of-phase  $V_2$ . When balanced,  $V_B=0$ , and the numerical value of the capacitance can then be extracted using this simple formula:

$$V_1 C_R = V_2 C_{DUT} \tag{1.2}$$

, where  $C_R$ ,  $C_G$ ,  $C_{DUT}$  are respectively the capacitor representing the reference, parasitics to ground and device under test. When biased by  $V_M$  to be almost completely off, the discrete HEMT transistor (M2) serves as the reference capacitor  $C_R$ . This scheme has the added advantage that a separate high-resistance DC path to bias the amplifier M1 is unnecessary. In fact, the presence of that high resistance DC path, in the form of a large resistor, would be detrimental to the signal-to-noise ratio since it further reduces the incoming AC signal by shunting it to ground, and acts as a significant noise source for M1. The voltage-adjustable M2 provides a convenient way to bias M1 and acts as a reference capacitor simultaneously. An added bonus is that, by turning on M2, I-V characterization of the DUT can be performed in-situ, without having to remove the device from the setup. The precise value of  $C_R$  can be measured it using the AH2700A commercial bridge, and is 0.37pF in our case.

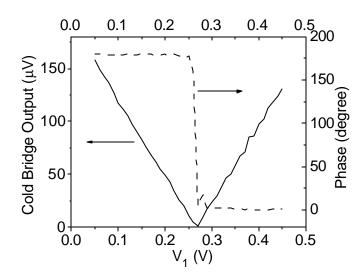

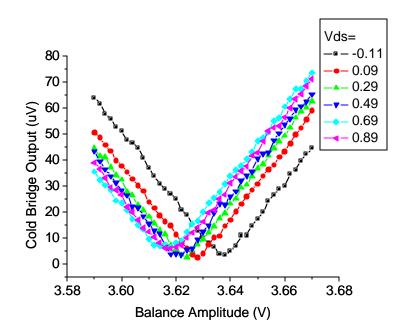

A typical balancing curve is shown in figure 1.6. It is simply the output of the bridge as a function of the amplitude of  $V_I$  (see figure 1.4). As expected, the bridge goes through a minimum (the balance point), accompanied by an abrupt change in the phase from 0 to 180 degree, evidence that contribution from AC source  $V_I$  has become larger. In all devices of interest in this work, the capacitance of the DUT changes with bias applied across it. When this happens, we should expect the balance curve to simply shift horizontally with applied bias, as illustrated in figure 1.7.

**Figure 1.6:** Output of the cold bridge as a function of the amplitude of AC source  $V_1$ . Solid: amplitude. Dashed: phase.

**Figure 1.7:** Output of the cold bridge as a function of the amplitude of AC source  $V_l$ , with varying DC bias applied across the DUT. The DUT is a carbon nanotube Schottky diode.

### 1.4 Full setup

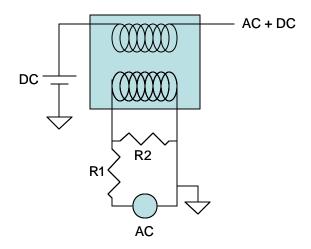

The full measurement setup outside of the cold bridge is described below for future reference. First, the phase between the two AC sources is carefully trimmed to be as close to  $180^{\circ}$  apart as possible. The instruments used for the AC sources are the internal sine generator of the SR830 lock-in amplifier and the HP3312A function generator, whose phase can be adjusted relative to an external trigger. This phase adjustment is necessary to ensure that the bridge output is as small as possible when balanced, and that the simple formula 1.2 can be applied to extract the capacitance of the DUT. Also, as obvious from figure 1.4, the DC bias applied across the DUT for C-V measurement needs to be added to  $V_2$ , and another DC voltage is needed to bias the transistor M1, and should be added to  $V_1$ . The addition of the AC source to the DC source is done passively to avoid introducing additional noises. This is done using an audio-frequency transformer (TRIAD magnetics TF5S1ZZ), as illustrated in figure 1.8. The appropriate AC voltage levels are obtained using resistor-based voltage dividers.

**Figure 1.8:** Adding AC voltage to DC passively using an audio-frequency transformer (TRIAD magnetics TF5S1ZZ). When needed, the AC source is divided resistively using R1 and R2, with typical  $R2/R1 \sim 10^{-4}$ .

### **1.5** Noise Performance of the Cold Bridge

With all components of the bridge optimized and using a lock-in amplifier to reject unwanted noise, the bridge has a noise figure of about 0.3 electrons /  $Hz^{1/2}$  at 77K. Using a typical AC excitation of 20mV and an averaging time of about 120s per data point, the noise figure translates into a capacitance resolution ?*C* of:

$$\Delta C = Noise \ Figure \times \sqrt{Effective \ Bandwidth \times AC \ Voltage}$$

(1.3)

$$\Delta C = 0.3 \frac{e}{\sqrt{Hz}} \times \sqrt{1/120} \times 20mV = 1.4aF \tag{1.4}$$

With a larger AC excitation or greater patience, the bridge can easily resolve capacitances lower than 1 aF.

The capability to measure small capacitances allows for the characterization of individual nanoscale semiconductor devices. As an example, the dimensions of an end-of-the-roadmap silicon MOSFET [7], Lg = W=8.8nm and EOT = 0.5nm, lead to a capacitance of ~5.3 aF, well within the capability of the instrument described above.

### **1.6 Device layout and design to minimize background capacitance**

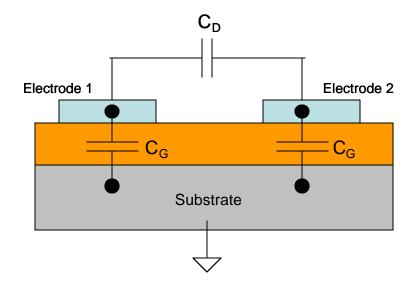

Although the cold bridge is designed to accept an arbitrary device, there are restrictions to the device layout. Illustrated in figure 1.9 are the various parasitic

capacitances. The first restriction is the density of devices. Unfortunately, floating electrodes increase the background capacitance significantly, and resolving a small change in capacitance relative to a large background, even if it stays constant, presents a challenge since the instruments (e.g. lock-in amplifier) have only a resolution of at most 4 decimal places, and can therefore resolve only changes of 1 part in  $10^4$ , and only barely so. A 3mm x 3mm chip (typical size of the sample) densely packed with floating electrodes has about 20 to 30fF of background capacitance. In contrast, when the device density is reduced to one per 5mm x 5mm chip, with no floating electrodes, the stray capacitance diminishes to  $0.2 \sim 0.4$  fF, coming from  $C_D$  in figure 9. Increasing the distance between the electrodes reduces  $C_D$  further, with <0.1 for electrodes 4um apart (figure 1.9).

Figure 1.9: On-chip parasitics between two electrodes and the substrate.  $C_D$  is the capacitance between the metal electrode 1 and 2.  $C_G$  is the capacitance between the substrate and the metal electrodes.

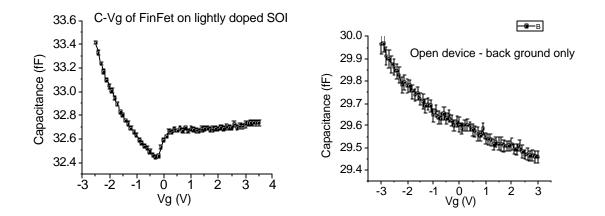

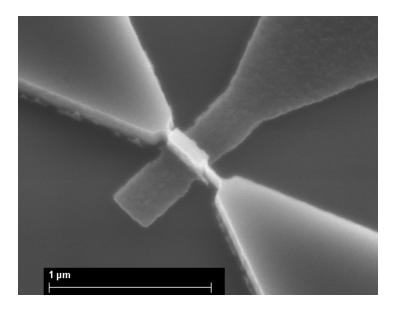

The second design constraint concerns the substrate. The DUT should ideally be on a SOI substrate with a heavily doped handle wafer. The heavy doping is necessary to prevent the substrate from being depleted by voltage applied to the electrodes. If the substrate can be depleted, the background capacitance will not stay constant with applied bias, even if there is no device between the two electrodes. Figure 1.10 illustrates this difficulty when measuring a FinFET fabricated on a lightly doped SOI (figure 1.11). In general, it would also be difficult to subtract the background signal from a control device, since each device has a slightly different background contribution from bonding wires. However, it should be noted that the capacitance step in the left of figure 1.10 is about 160aF, agreeing reasonably with an estimated  $C_{ox} = 220aF$  based on device geometry alone.

**Figure 1.10:** C-V measurement of a FinFET (Lg=150nm, fin width=30nm, fin height=200nm, Tox~10nm). Left: C-V of the device. Right: C-V between two contact pads of the same geometry, but with no transistor between them.

The third design limitation is the size of the bonding pads. Since the substrate is grounded, the bonding pads increase the shunt capacitance to ground  $C_G$ , in parallel with the cables. As discussed previously, a large  $C_G$  leads to low signal-to-noise ratio

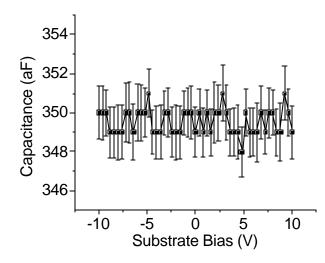

and reduces resolution. A typical bonding pad is a  $75\mu$ m x  $75\mu$ m square on an oxide layer 500nm in thickness, giving a tolerable  $C_G = 0.38$ pF. When these design limitations are satisfied, the background capacitance is constant to better than 2aF, within the error bars, as illustrated in figure 1.12.

**Figure 1.11:** SEM image of the FinFET measured in figure 1.10. Capacitance is measured between the gate (top right), and the source/drain electrodes (upper left and lower right), which are shorted together.

**Figure 1.12:** Capacitance between two metal electrodes  $1\mu$ m apart, as function of the substrate bias. No device exists between the electrodes. The substrate is heavily doped with boron to at least  $10^{19}$ /cm<sup>3</sup>.

### **1.7 Dealing with losses**

When measuring small capacitances, even a seemingly large resistive component in parallel of the capacitor can make the loss unmanageable. Lossy capacitors are encountered in very thin or leaky dielectrics, heavily doped junctions, and Schottky diodes. As an estimate, for C=100aF measured at 10kHz, a resistance of 160 GOhm is sufficient to produce a loss tangent of 1, making the simple formula 1.2 unapplicable. Instead, a more complicated circuit model that includes the resistor in parallel must be used (figure 1.13) and the capacitance extracted using linear circuit analysis.

Figure 1.13: Parallel model for lossy capacitor. The loss is modeled by the resistor  $R_{DUT}$  in parallel with the capacitor.

Linear circuit theory gives the voltage  $V_B$  simply as:

$$V_B = V_1 \left(\frac{Y_{DUT}}{Y_t}\right) - V_2 \left(\frac{Y_R}{Y_t}\right)$$

(1.5)

Where  $Y_x = 1/Z_x$  is the admittance between any node *x* to node *B* in figure 1.13, and  $Y_t$  is the sum of the admittances joining the balance point and the other three nodes. Further simplification gives the real and imaginary parts separately:

$$V_B = \frac{1}{j \mathbf{w} C_G} \left( \frac{V_1}{R_{DUT}} \right) + \frac{j \mathbf{w}}{j \mathbf{w} C_G} \left( C_{DUT} V_1 - C_R V_2 \right)$$

(1.6)

$$\angle V_{B} = \frac{V_{1} / R_{DUT}}{\mathbf{w}(C_{DUT}V_{1} - C_{R}V_{2})}$$

(1.7)

The approximation  $Y_t \sim Y_G$  was employed, since the parasitic  $C_G$  (6pF) is considerably larger than other capacitors. Using equations 1.5 to 1.7, both resistive and capacitive components can be deduced in principle.

### **1.8 Summary**

The above describes the instrument and the methods used to measure very small capacitances. The innovation brought here is the modularity designed into the instrument to enable the measurement of an arbitrary device, provided that it satisfies the design constraints. Methods are also developed to reproduce essentially all the capabilities of a commercial bridge, only with much better capacitance resolution.

### References

- [1] HP4284A Operation Manual

- [2] S. Ilani, L.A.K. Donev, M. Kindermann, P.L. McEuen, *Nature Physics*, 2, 687-691(2006).

- [3] R. Tu, L. Zhang, Y. Nishi, H. Dai, Nano Letters, 7, 1561-1565 (2007).

- [4] AH2700A Operation manual

- [5] R.C. Ashoori, H.L. Stormer, J.S. Weiner, L.N. Pfeiffer, S.J. Pearton, K.W. Baldwin,

- K.W. West, Phys. Rev. Lett., 68, 3088-3091 (1992).

- [6] Gary Steele, Ph.D. Thesis, Massachusetts Institute of Technology (2006).

- [7] ITRS Roadmap 2008, www.itrs.net

# Chapter 2

### Diffused junction in a silicon nanowire

Semiconductor nanowires are useful in several applications, including biochemical sensing, computing and energy harvesting[1,2,3,4,5]. However, important material parameters such as the dopant distribution and surface state density have not been measured in nanowires. Here, C-V method is applied directly to a single silicon nanowire surround gate field effect transistor to extract the radial dopant distribution and interface state density. The methods previously used [6] to determine the dopant density rely on several untested assumptions that can lead to very large uncertainties. For example, the dopant concentration is typically extracted by making nanowire field effect transistors (FETs) and using the conductivity in conjunction with the measured

mobility and threshold voltage[7,8,9]. These methods rely on the calculated gate capacitance and assume a uniform dopant distribution and known surface (or interface) charge density. In planar devices, the above assumptions can be tested using the capacitance-voltage (C-V) technique[10], and the same method is applied here to a nanowire device.

Previous reports on direct C-V measurements on nanowires exist, but these are concerned with measuring the oxide capacitance for the purpose of mobility extraction[11,12]. Accurate mobility measurements are important, and a similar study performed on individual InAs nanowires is presented in the next chapter. A recent study of InAs nanowires addresses the issue of interface trap density, but it was performed on a large ensemble of wires having a large size distribution, and inconsistent electrical contacts[13].

The work presented in this chapter demonstrates the application of C-V measurements on a silicon nanowire transistor, fabricated using a bottom-up method. The interface state density  $D_{it}$  as a function of the energy position inside the bandgap is extracted with the high-low method and the radial dopant profile is determined from high frequency C-V measurement. Finite element modeling (FEM) is used to support the results and to show the limitations in resolving the dopant profile using the C-V method. The results are also compared with those from planar metal oxide semiconductor capacitors.

### 2.1 Design of test structure and measurement scheme

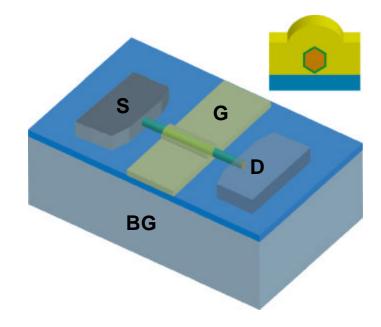

The test structure is similar to that proposed by Ilani et al[14]. Figure 2.1 illustrates the design of the structure. On an SOI wafer, a silicon nanowire bridges two heavily boron-doped silicon pads (S and D), about 4 $\mu$ m apart. A high-k/metal gate stack surrounding the nanowire acts as the top gate. This gate stack, in series with the nanowire, effectively forms a MOS capacitor (MOSCAP). However, 1 $\mu$ m of the nanowire from the source and the drain electrode is not covered by the top gate, and is instead gated by the back gate (BG). The back gate is used to extract the background parasitic capacitances.

**Figure 2.1** Device test structure for CV measurement. S/D: source and drain. G: top gate. BG: back gate. The cross section shows the wire under the top gate. A thin layer of aluminum oxide separates the nanowire channel from the top gate electrode. Credit: E.Garnett.

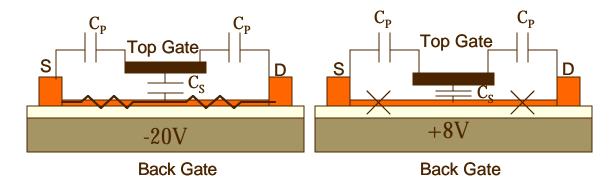

Capacitance is measured between the top gate and the source/drain electrodes, the latter two shorted together. In the first measurement, the back gate is negatively biased to turn on the exposed parts of the nanowire, and both the MOSCAP and the background parasitics contribute to the measured capacitance. In the second measurement, a large positive voltage applied to the back gate turns off the exposed parts of the nanowire, and the nanowire MOSCAP is not measured. The difference between these two measurements yield only the capacitance from the nanowire MOSCAP. The measurement scheme is illustrated in figure 2.2.

**Figure 2.2** Measuring scheme to extract background capacitance. Left: Negatively biased back gate leads to low resistance contact to the MOSCAP. Right: positively biased back gate turns off access the the nanowire MOSCAP.

### **2.2 Device fabrication**

Starting with (110) SOI wafers with heavily doped handle and device layers, standard microfabrication techniques are used to define silicon islands that serve as the source/drain electrodes. Gold nanoparticles with an average diameter of 80nm are then dispersed from solution onto the silicon islands. Vapor-liquid-solid growth of the nanowires at 830°C follows, catalyzed by the gold nanoparticles[15,16]. The silicon

precursor is liquid SiC<sub>4</sub> kept at 0°C, bubbled into the furnace using a mixture of Ar and  $H_2$  (50 and 158sccm, respectively). Since the growth is epitaxial, the long axis of the nanowires are generally perpendicular to the (111) planes of the silicon surface. It should be noted that the islands are aligned such that the direction the nanowires are expected to bridge is parallel to the (111) directions. A (110) wafer is used because it can be patterned such that the (111) surfaces are exposed, and that the (111) directions, to which the nanowires align, are in the plane of the wafer [17].

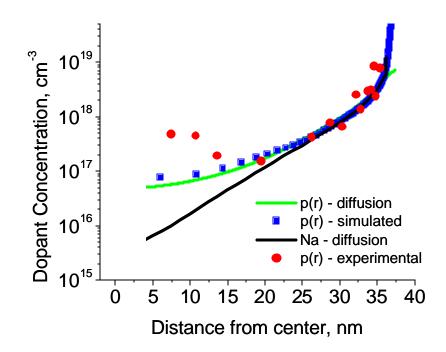

The nanowires are then doped with boron by annealing for 1 hour at 675 °C with 500 sccm of carrier gas and 0.5 sccm of 1% BC<sub>b</sub> in Ar, followed by 15 minutes at the same temperature with the BC<sub>b</sub> line turned off. Using these process conditions, a dopant profile can be simulated using Tsupreme, a commercial semiconductor process simulation tool. The expected dopant profile is shown as the dark solid line in figure 2.9 (Na-diffusion). The Al<sub>2</sub>O<sub>3</sub> gate dielectric is deposited in a ALD chamber using alternating pulses of trimethylaluminum and water precursors. The surround gate metal is patterned via photolithography and chromium sputtering, followed by lift-off.

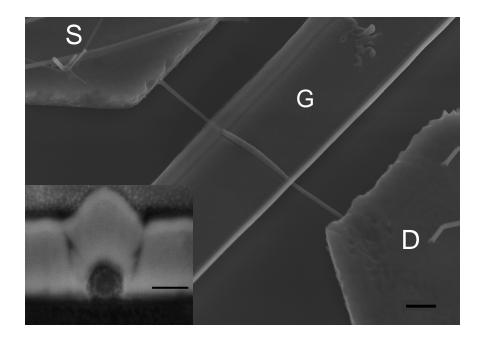

Figure 2.3 shows a completed Si nanowire FET. After all measurements of interest are performed, focused ion beam (FIB) milling is used to expose the buried part of the wire in order to measure the actual diameter. The wire appears to be fully embedded in the surround gate metal and epitaxially integrated into the silicon electrodes. The cross-sectional SEM shows a distinct contrast between the bright Cr surround gate and the dark  $AbO_3$  gate oxide, with a somewhat smaller contrast

difference at the Si/A $bO_3$  interface. The cross-sectional and top view SEM images show a gate length of 2.3 microns, Si nanowire diameter of about 75 nm and A $bO_3$ thickness of about 15 nm. The thickness of the A $bO_3$  is consistent across a large (cm<sup>2</sup>) area, and with a TEM measurement on control samples.

**Figure 2.3** SEM picture of an actual nanowire device. The inset is a cross-sectional view of the device taken after focused ion beam (FIB) milling. The scale bars are 1  $\mu$ m (main panel) and 100 nm (inset). Credit: M. Fardy.

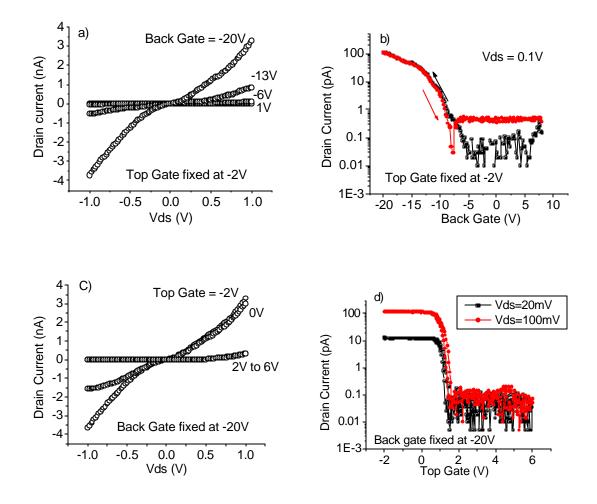

Figure 2.4a-d show the output characteristics (Id-Vd) of the device and transfer characteristics (Id-Vg) relative to the back gate and the top gate. Although the on-state resistance is rather high (~0.3GOhm), it is not important for the purpose of extracting interface state densities and dopant profile. All that is required is a sufficiently low source/drain contact resistance so the MOSCAP can be accessed, and that the back gate can turn off the nanowire sufficiently well to allow the extraction of background capacitance. The slight non-linearity at low *Vds* in figure 2.4a suggests that the source

or drain contact may be a Schottky contact, possibly because of residual oxide on the surface of the trench sidewall. It should also be noted that there is very little hysteresis in figure 2.4b, despite the application of very large voltages. This suggests that the effect of bias-induced stress and charge injection from the gates are very small.

**Figure 2.4** a) Output characteristics (Id-Vd) of the device in figure 2.3 as a function of the back gate. The top gate is fixed at -2V. b) Transfer (Id-Vg) characteristics, vs the back gate, of the Si NW transistor shown in figure 2.3. c) Id-Vd for various top gate voltage. The back gate was -20V. d) Id-Vg characteristics, vs the top gate.

#### **2.3 The capacitance measurement**

Since the furnace for growing the nanowires accommodates only substrates no wider than 1", it is necessary to have a large device density on each chip to obtain a usable number of devices. On a single test chip, there can be more than 100 silicon islands, leading to a large parasitic background capacitance of about 20fF. Nevertheless, the measurement method is precise to less than 10aF, and the large background only presents a minor inconvenience. Electrical contacts are made to the source, drain and gate electrodes by wirebonding from a ceramic package to the degenerately boron-doped silicon source and drain pads and the chromium surround gate. Appropriate ultrasonic power is used to break through the Al<sub>2</sub>O<sub>3</sub> layer covering the source and drain. The series resistances from these wirebonds are negligible compared to that of the nanowire.

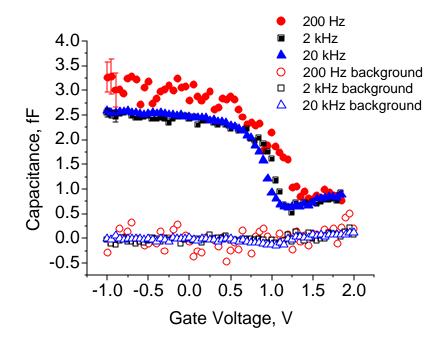

Following the scheme in figure 2.2, the capacitance is measured using the Andeen-Hagerling AH2700A with an AC amplitude of 20 mV at 77K, with sufficiently long averaging times. Figure 2.5 shows the silicon nanowire C-V response at 200 Hz, 2 kHz and 20 kHz with the back gate set at -20 V. The background capacitance is measured with the back gate set at +8 V. Both measurements are repeated at the 3 frequencies. The C-V curves clearly show the expected accumulation and depletion regions. At larger positive gate biases (not shown), inversion does seem to occur, but the data in that regime is not expected to be accurate since the contact to the wire is p-type, and the access resistance to a n-type inversion layer would be a large one.

**Figure 2.5** Capacitance-voltage measurements. Capacitance-voltage curves measured at 77K and 200 Hz (red), 2 kHz (black) and 20 kHz (blue), with the background shown in the corresponding open symbols. The error bars are shown only for the first 3 data points for clarity.

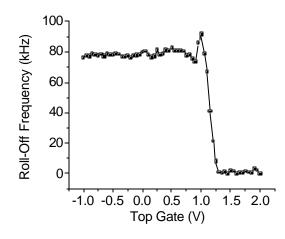

Figure 2.6 The calculated 3dB roll-off frequency using figure 2.4(d) and figure 2.5.

The experimental  $C_{ox}$  of 2.58 fF, taken from the strong accumulation region of the 20 kHz C-V, is within 7% of the calculated  $C_{ox}$  value, using the measured geometrical

dimensions (L=2.3µm, D=75nm), ?=7.3 for Al<sub>2</sub>O<sub>3</sub>, and  $T_{ox} = 15$  nm. If we assume instead that the 15 nm oxide consists of 1 nm native SiO<sub>2</sub> and 14 nm of Al<sub>2</sub>O<sub>3</sub> as would be expected according to a previous TEM study[15], then there is only a 1% deviation between the experiment and the calculation. The agreement also suggests that quantum confinement effect is comparatively unimportant, which is expected for a thick oxide layer. The roll-off frequency, defined as the reciprocal of the product of the measured resistance and capacitance, is shown in figure 2.6, and it is well above the measurement frequencies for the range of top gate voltages of interest (-1 to +1V). The measured changes in the C-V curves are therefore not artifacts of the access resistance.

### 2.4 The interface state density

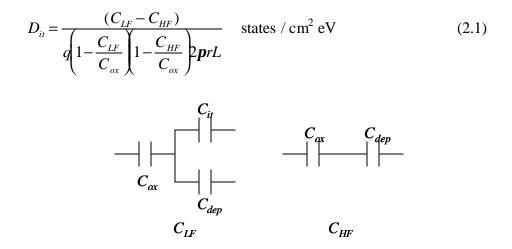

There is significant frequency dispersion in the C-V curves shown in figure 2.5. The dispersion is typically attributed to the finite lifetime of the interface trap states, which cannot respond quickly enough to high frequencies[10]. We can extract the interface state density ( $D_{it}$ ) as a function of position in the band gap by comparing the high and low frequency capacitance curves. Figure 2.7 shows the approximate circuit model in each case. At frequencies much slower than the trap lifetime, contribution from the traps are measured in addition to the depletion and oxide capacitance, whereas at high frequencies the traps effective "freeze out", and do not contribute. A straightforward circuit analysis gives the following expression for  $D_{it}$ :

**Figure 2.7** Circuit model at high and low frequencies. Cox: oxide capacitance. Cdep: capacitance from the depleted region. Cit: capacitance coming from the interface traps.

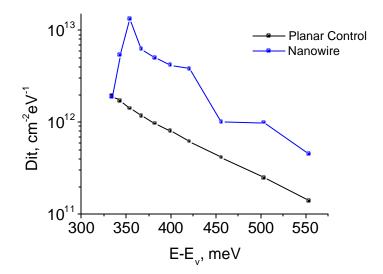

Figure 2.8 shows the resulting  $D_{it}$  versus the energy position relative to the valence band energy.  $D_{it}$  varies from  $4x10^{11}$ /eV·cm<sup>2</sup> at mid-gap to  $1x10^{13}$ /eV·cm<sup>2</sup> closer to the band edge. The trend matches well with the result from on a control MOSCAP fabricated on planar (111) silicon, following the same doping and oxide deposition steps. The mid-gap density is about an order of magnitude above a high quality thermal SiO<sub>2</sub>-Si interface, but similar to both literature and planar control experiment results for A½O<sub>3</sub> on silicon [18,19,20,21].

**Figure 2.8** The interface state density  $D_{it}$  versus position with respect to the valence band, extracted from the C-V curves in figure 2.5.

The shape of the  $D_{it}$  curve and peak position within several hundred meV of the valence band edge are also qualitatively similar to what has been observed in planar Al<sub>2</sub>O<sub>3</sub>silicon interface [10, 17]. Compared to the planar control,  $D_{it}$  is somewhat larger. A possible cause is that the surfaces probed here are not the same as the planar control(111), due to faceting seen in figure 2.3. The faceted surfaces are thought to be (211), since this direction is 30° to the surface normal, as observed in figure 2.3. The observation of the (211) surface was also made previously[22].

Note that our results should be taken as the lower limit of the true  $D_{it}$ , since AH2700A is limited to operate between 50Hz and 20kHz, and it is not possible to access the true high and low frequency characteristics. The high-low method is well-known to underestimate the interface state density due to the difficulties in obtaining

true high and low frequency behavior. However, from previous studies on planar silicon we expect a difference no more than a factor of two from the true profile[10, 23].

### **2.5 Dopant profile**

We have also extracted the dopant profile using the high frequency C-V curve, using depletion approximation. The results are compared to the simulation from a commercial semiconductor process simulator, TSupreme, using the actual device dimensions and process conditions, including the interstitial and vacancy-assisted diffusion models. In addition, we assume that the dopant concentration at the surface is fixed at the solid solubility  $(2 \times 10^{19} / \text{cm}^3 \text{ at } 675^{\circ}\text{C})$ . The depletion approximation is also verified using finite element electrostatic simulations (COMSOL Multiphysics), to include both the ionized dopants and the majority carriers. Figure 2.9 shows the agreement between the simulated diffusion profile and the experimental data. In addition, the FEM simulation shows that the profiles of the ionized dopant and the majority carrier match well, except at low doping levels near the core of the wire. It has been long noted that the C-V technique deduces the dopant concentration accurately only in regions where charge neutrality is exhibited [22,23]. Qualitatively, a gradient in the dopant density leads to a built-in electric field, which is screened out by a redistribution of the majority carriers. The length scale of the re-distribution is simply the Debye screening length ( $L_d$ , equation 2.1), which at low density can be fairly long and is given by [24] :

$$L_d = \sqrt{\frac{\mathbf{k}\mathbf{e}_0 k_B T}{q^2 N_A}} \tag{2.1}$$

37

**Figure 2.9** Radial charge and dopant profile extracted using the C-V measurement. The blue symbols are the majority carrier concentration extracted from a calculated C-V curve fitted to the measured high-frequency C-V curve. The black curve is the dopant profile simulated using TSupreme, using the process conditions. The green curve is the majority carrier concentration expected from the simulated dopant profile.

It has been well established that spatial resolution in C-V dopant profiling is limited to about  $2L_d$ , which at the measurement temperature of 77K should be about 2nm and 13 nm at the surface and core, respectively, due to the different doping levels[10]. Since the C-V method actually measures the free carriers and not the dopant atoms, the experimentally extracted majority carrier profile will only match the dopant profile in regions where the carrier redistribution has a minimal impact, typically around  $1 \times 10^{16} - 1 \times 10^{17}$  cm<sup>-3</sup> or higher[25,26]. Above these resolution limits, we can certainly differentiate between a graded and a uniform dopant distribution (figure 2.10). Using the same FEM 3-D simulations, we can compare the simulated and the experimental C- V curves in order to determine the flat band voltage ( $V_{FB}$ ) and further validate our dopant profiling and  $D_{it}$  extraction techniques.

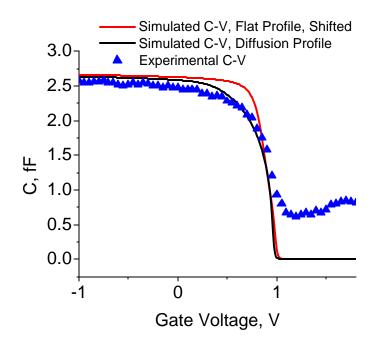

**Figure 2.10** Simulated C-V curves. Experimental high frequency 20 kHz C-V curve (blue) compared to the simulated C-V curves for the boron diffusion profile (black) and the flat profile (red) as shown in Figure 4a and 4b, respectively. Credit: D. Khanal.

Figure 2.10 shows the FEM simulated C-V curves calculated from the graded and the uniform profiles  $(N_a=10^{17}/\text{cm}^3)$ , and the high-frequency (20 kHz) experimental C-V curve. The simulated curves are shifted horizontally so they overlap one another, for the purpose of comparison. Without this shift, V<sub>FB</sub> for the uniform profile would be about 0V. Clearly, the graded dopant profile leads to a C-V curve that matches the experimental C-V curve better than a uniform dopant profile.

The only major deviation comes at full depletion where the simulated capacitance reduces to 0fF, while the experimental curve does not go below 0.5fF. This extra capacitance in the experiment may come from direct coupling between the surround gate and the nanowire leads. The simulation does not account for this since it does not incorporate a back gate and thus allows for the leads (underlapped regions) to become depleted. Since the simulation did not account for interfacial defects, the minor deviation in slope likely stems from interface states, which are known to cause stretch-out even in high frequency C-V measurements[10].

In figure 2.10, it is necessary to shift the simulated C-V curve horizontally to match the measurement. Attributing this flat-band voltage shift to the built-in potential between the metal gate and the substrate and the contribution from fixed charges, we can extract a fixed oxide charge density of  $Q_i$ =-4.6 x10<sup>11</sup> cm<sup>-2</sup>, when a literature value for chromium ( $f_M$ =4.5eV) is used. This value of  $Q_i$  is similar to previous literature reports for Al<sub>2</sub>O<sub>3</sub> deposited using ALD[16].

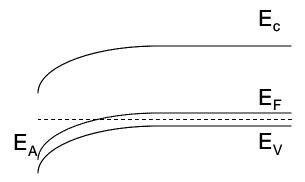

Lastly, it should be noted that although this experiment was conducted at 77K, dopant freeze-out need not to be considered. As illustrated in figure 2.11, dopants are still ionized in the depleted region because the impurity acceptor level  $E_A$  is pulled below the Fermi level, causing it to be filled, and the acceptor impurities to be fully ionized (figure 2.11). Thus, this technique can in principle be extended for even lower dopant densities, if the temperature is lowered further.

**Figure 2.11** Energy band diagram of a p-type semiconductor under freeze-out conditions. Dopants in the flat band (bulk) regions is assumed to be frozen out. Band bending causes the acceptor levels  $E_A$  (dotted) to be pulled below the Fermi level (dashed), causing the acceptor levels to be filled, and the dopant atoms ionized

### 2.6 Summary

The C-V measurement was used to determine all the relevant parameters of a silicon nanowire MOSCAP. Using frequency-dispersion measurement between 200 Hz and 20 kHz, it was demonstrated that the  $D_{it}$  profile as a function of energy position in the band gap is similar to results from bulk silicon. The radial boron dopant profile is also deduced and matches the expected profile from the dopant diffusion simulation with a surface concentration near the boron solid solubility of  $2x10^{19}$  cm<sup>-3</sup>. This is in contrast to a flat dopant profile guessed from measured conductivity, mobility and threshold voltage in previous literature on Si NW transistors. These results unambiguously demonstrate that a quantitative understanding of the surface properties and dopant distribution within semiconductor nanowires will be critical to achieve reproducible high-performance devices.

### References

- [1] Cui, Y., Wei, Q. Q., Park, H. K. and Lieber, C. M. Science 293, 1289-1292 (2001).

- [2] Feng, X. L., He, R. R., Yang, P. D. and Roukes, M. L. Nano Letters 7, 1953-1959(2007).

- [3] Kayes, B. M., Atwater, H. A. and Lewis, N. S. J. Appl. Phys. 97, 114302 (2005).

- [4] Garnett, E. C. and Yang, P. D. J. Am. Chem. Soc. 130, 9224-9225 (2008).

- [5] Hochbaum, A. I. et al. Nature 451, 163-168 (2008).

- [6] Law, M., Goldberger, J. and Yang, P. D. Annual Review of Materials Research 34, 83-122 (2004).

- [7] Goldberger, J., Hochbaum, A. I., Fan, R. and Yang, P. D. *Nano Letters* 6, 973-977 (2006).

- [8] Goldberger, J., Sirbuly, D. J., Law, M. and Yang, P. *J Phys Chem B* 109, 9-14 (2005).

- [9] Cui, Y., Duan, X. F., Hu, J. T. and Lieber, C. M. J Phys Chem B 104, 5213-5216(2000).

- [10] Nicollian, E. H. and Brews, J. R. in *MOS Physics and Technology* 1-903 (Wiley-Interscience, New York, 1982).

- [11] Tu, R., Zhang, L., Nishi, Y. and Dai, H. J. Nano Letters 7, 1561-1565 (2007).

- [12] Gunawan, O. et al. Nano Letters, 8, 1566–1571 (2008).

- [13] S. Roddaro et al, Appl. Phys. Lett., 92, 253509 (2008)

- [14] Ilani, S., Donev, L. A. K., Kindermann, M. and McEuen, P. L. *Nature Physics* 2, 687-691 (2006).

- [15] He, R. R. et al. Adv Mater 17, 2098-2102 (2005).

[16] He, R. and Yang, P. Nat. Nanotech. 1, 42-46 (2006).

[17] A. San Paulo, N. Arellano, J.A. Plaza et al, Nano Lett. 7, 1100-1104 (2007)

[18] Wilk, G. D., Wallace, R. M. and Anthony, J. M. J. Appl. Phys. 89, 5243-5275(2001).

[19] Truong, L., Fedorenko, Y. G., Afanasev, V. V. and Stesmans, A. *Microelectronics Reliability* 45, 823-826 (2005).

[20] Duenas, S. et al. J. Appl. Phys. 99, 054902 (2006).

[21] Kim, T. W. et al. J. Appl. Phys. 74, 760-762 (1993).

[22] R.S. Wagner and W.C. Ellis, Appl. Phys. Lett. 4, 89-90 (1964).

[23] Terman, L. M. Solid-State Electronics 5, 285-299 (1962).

[24] Sze, S. M. in *Physics of Semiconductor Devices* 1-812 (Wiley-Interscience, New York, 1969).

[25] Kennedy, D. P., Murley, P. C. and Kleinfel.W. *IBM Journal of Research and Development* 12, 399-409 (1968).

[26] Kennedy, D. P. and Obrien, R. R. *Ibm Journal of Research and Development* 13, 212-213 (1969).

## **Chapter 3**

### **Characterization of back-gated InAs nanowires**

Transistors have been reducing in size ever since their introduction into integrated circuits. The international technology roadmap predicts that by the completion of this thesis, the gate length of a MOS transistor will be about 32nm. One of the reasons for transistor scaling is to improve switching performance. Even in the velocity-saturation regime, reducing the channel length of the transistor can still improve the drive current[1], as long as the transport is not completely ballistic.

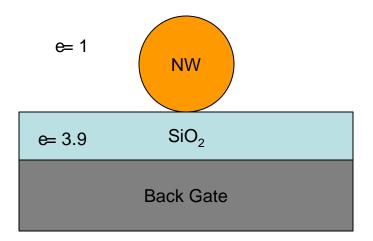

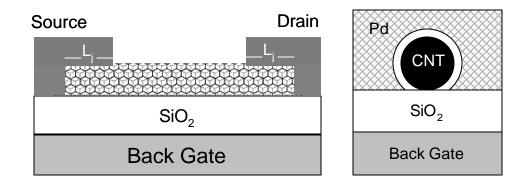

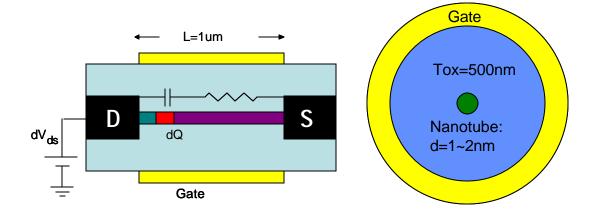

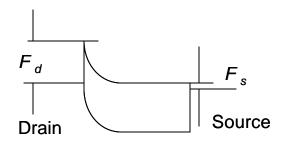

It is well known that carrier mobility is much higher in III-V semiconductors compared to silicon. However, their usage as a channel material in a MOSFET structure is limited by the unavailability of a gate dielectric with sufficiently good 44 interface quality. Transistors based on bottom-up semiconductor materials such as nanowires of Si[2], Ge[3], InAs[4] or carbon nanotubes[5] are shown to have a carrier mobility generally much greater than transistors made in bulk silicon. However, most prior estimates of the mobility were based on rather simple calculation of the gate capacitance[1,2]. In these primitive devices, the channel is often back-gated because that geometry is easy to realize, and one can dispense with gate dielectrics that usually have a deleterious impact on the mobility, although a passivated surface is still necessary. As a result, the dielectric medium surround ing the channel (figure 3.1) is not uniform and the gate capacitance is somewhat difficult to model. A simple alternative is to measure the capacitance directly, and use this information to extract accurate mobility numbers.

In this chapter the C-V technique is used to characterize individual InAs nanowire in its usual back-gated geometry, both to extract the oxide capacitance accurately, and to characterize the interface quality, in terms of usual parameters such as interface trap density and trap life time.

**Figure 3. 1** Cross-section of a commonly used geometry for nanowire devices. The back gate is used to modulate the conductivity of the nanowire channel.

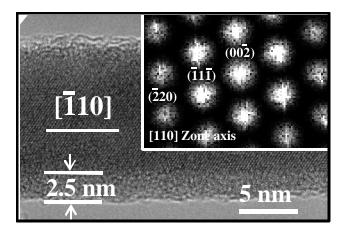

### 3.1 The interface between the InAs nanowire and its native oxide

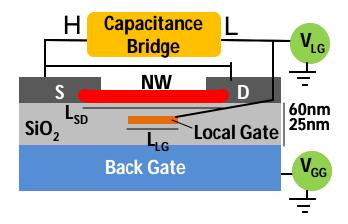

InAs is a small-bandgap and high mobility material. To characterize these InAs nanowires using the capacitance-voltage technique, we use the test structure illustrated in figure 3.2. It is very similar to the structure previously used in chapter 2, with the exception that both gates are buried, so that no mobility-degrading gate dielectric needs to be in contact with the nanowire. Instead, the InAs nanowire is surrounded by its native oxide, about 2.5nm thick as shown in figure 3.3.

**Figure 3.2** Test structure for C-V measurement of InAs nanowires[6]. The underlapped region can be modulated by the back gate for extracting background capacitance. The capacitance is measured between the local gate and the source/drain.

**Figure 3.3** TEM image of an InAs nanowire, showing the crystallinity of the wire as well as the presence of a 2.5nm native oxide[5].

The InAs nanowires are grown using a solid-source CVD technique [3], using nickel nanoparticles as catalyst. The particles are formed directly on the growth substrate by thermally annealing a thin film (10nm~15nm) of nickel, deposited using thermal evaporation. The solid-source InAs, located in the same furnace tube but upstream from the growth substrate, is carried to the catalyst by hydrogen gas. The InAs source is in a powdered form and heated independently of the growth substrate.

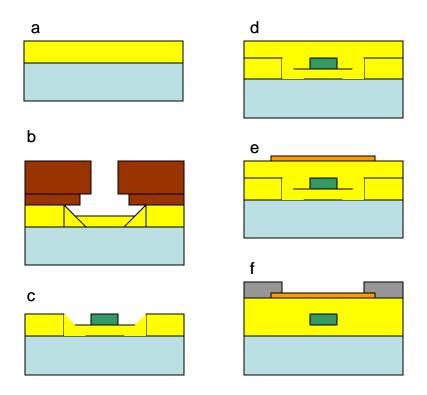

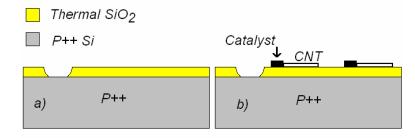

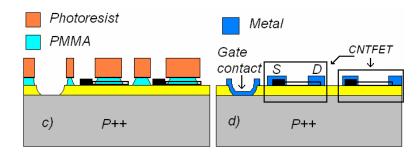

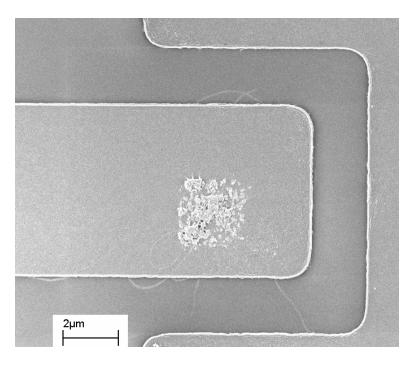

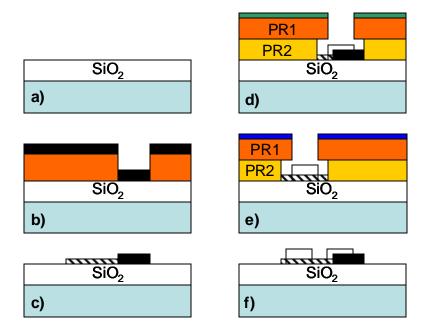

The test structure is fabricated following the process sequence illustrated in figure 3.4. Starting with a heavily doped p-type silicon wafer, a thick layer (200nm) of thermal oxide is grown (3.4a). The buried local gate is fabricated by partially etching away the thick oxide layer using buffered HF, in the area defined lithographically in a photoresist bilayer (3.4b). The drawn length of the gate varies from  $4\mu$ m to  $8\mu$ m. Metal (Pt) is then deposited and lifted off using the same photoresist bilayer. A thin (50nm) layer of CVD oxide is then deposited to insulate the buried local gate from the nanowire.

**Figure 3.4** Fabrication process sequence of the C-V test structure. a) Growth of thermal oxide (yellow). b) Definition of the buried electrode, by etching into the oxide using buffered HF. Pt (green) deposition and lift-off follows, resulting in (c). Lift-off is facilitated by the bilayer resist. d) Deposition of a 50nm silicon dioxide. e) Deposition of InAs nanowires from ethanol suspension onto the entire substrate. f) Definition of the nickel source and drain electrodes. Process designed by J.C.Ho.

The InAs nanowires are then desposited from a suspension in ethanol. The nanowire density is large enough such that about 5 to10 devices with only a single nanowire can be found on each 1"x1" chip. Lastly, nickel source and drain electrodes are defined using a second lift-off step. A brief (~30s) rapid thermal anneal follows to improve the contact resistance.

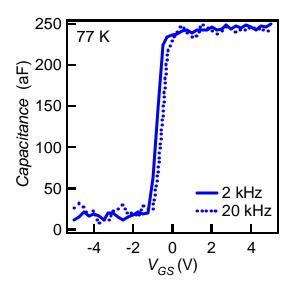

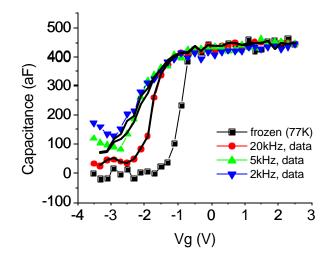

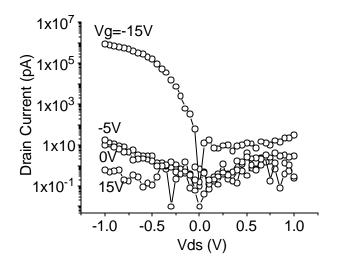

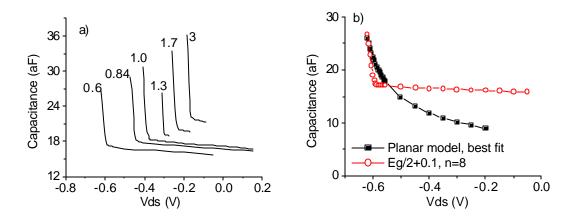

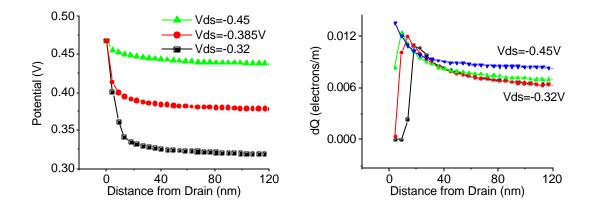

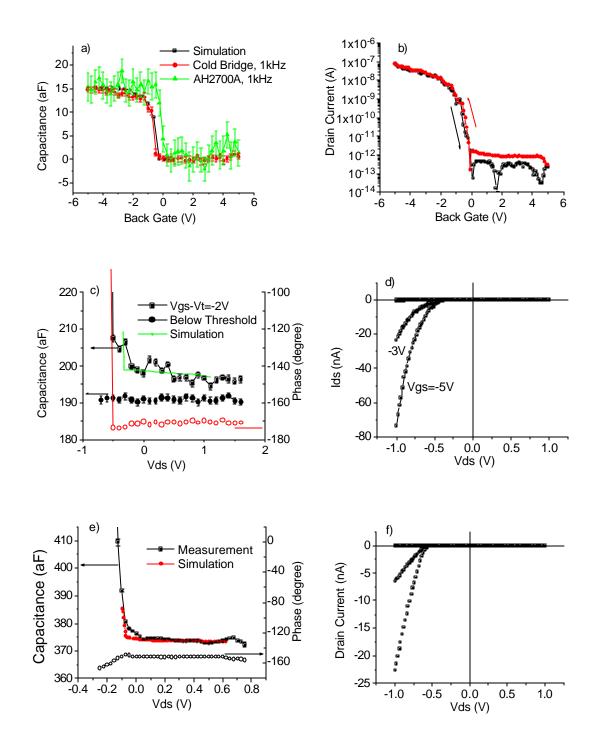

The method for accurate C-V measurement and background extraction follows the description in chapter 2. Figure 3.5 shows a typical C-V curve measured at 77K. At this temperature, the lifetime of the surface states is too long to respond to the applied signal frequency (1-20kHz). At a higher temperature, there is significant frequency dispersion in the C-V curves, as seen in figure 3.6. Above 200K, the lifetime of the traps is short enough to respond to even the highest frequency (20kHz) of the instrument. The capacitance from the traps completely dominates, such that the wire cannot be depleted and an accurate measurement of the background can not be done. Indeed, a recent report[7] shows that frequency as high as 20MHz is necessary at room temperature to stop the traps from responding.

Figure 3.5 Typical C-V curves at 77K for an InAs nanowire. There is a lack of frequency dispersion at such a low temperature.

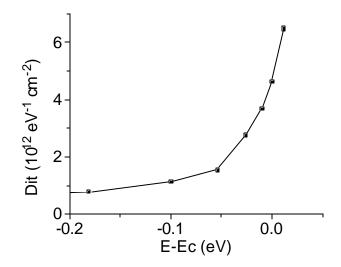

A single time constant model for the trap lifetime successfully reproduces the frequency-dispersion effect in figure 3.6. Based on this model, a surface trap density  $D_{it}$  of ~10<sup>11</sup> to 10<sup>12</sup>/ eV cm<sup>2</sup> can be extracted from the C-V curves (figure 3.7). The capture cross-section  $s_p$  of the trap can also be estimated by using equation 3.1 [8]:

$$\boldsymbol{t} = \frac{1}{v\boldsymbol{s}_p n} \tag{3.1}$$

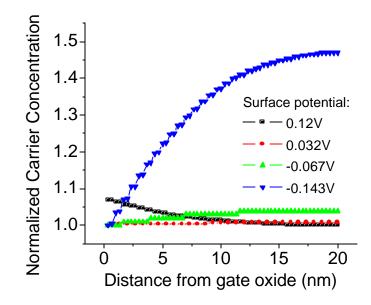

where t, v and n are respectively the trap lifetime, thermal velocity and carrier density. n can be calculated using a commercial three-dimensional device simulator, Taurus 3D, and is remarkably uniform throughout the wire, despite the back-gate geometry (figure 3.8).

**Figure 3.6** C-V curves of an InAs nanowire measured at 200K. The "frozen" curve measured at 77K is assumed to be equivalent to the true high-frequency behavior, where all traps stop to respond.

Figure 3.7 Trap density  $D_{it}$  vs position in the band gap, deduced from single life time fit to figure 3.5.

**Figure 3.8** Normalized carrier density vs distance from gate oxide for several surface potentials. Since the carrier density varies exponentially with the surface potential, it is normalized to the smallest value along the profile for ease of comparison.

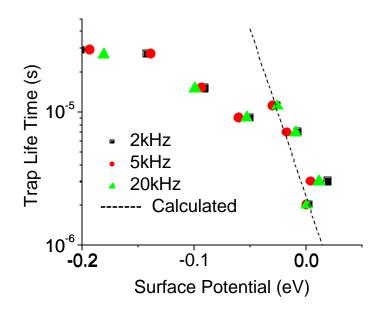

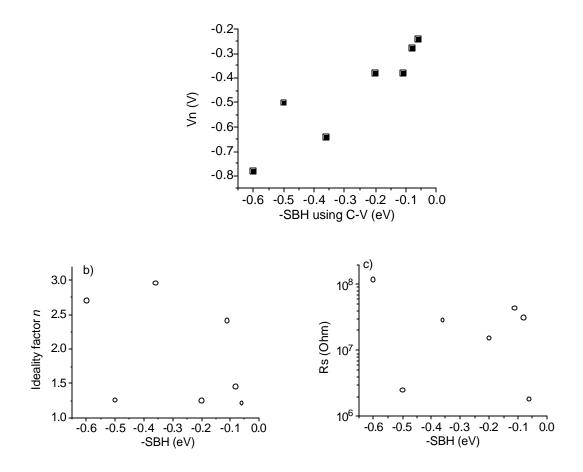

Figure 3.9 shows the trap lifetime deduced from the C-V curves, and its comparison to the expected values calculated from equation 3.1. There is a relatively good agreement for traps near the conduction band, when a capture cross-section of  $2x10^{-15}$  cm<sup>2</sup> is used. This cross-section is significantly larger than traps at the Si-SiO<sub>2</sub> interface (~ $3x10^{-16}$  cm<sup>2</sup>)[7]. Literature search reveals no prior estimates of capture cross-section of traps at the interface of InAs and its native oxide. At a larger surface potential where the lifetime is relatively independent of the surface potential, other processes may cause the frequency dispersion seen in figure 3.9.

**Figure 3.9** Deduced trap lifetime compared to calculated values from equation 3.1. A capture cross section  $s_p = 2 \ge 10^{-15} \text{ cm}^2$  is used.

### **3.2** Capacitance measurement for mobility extraction

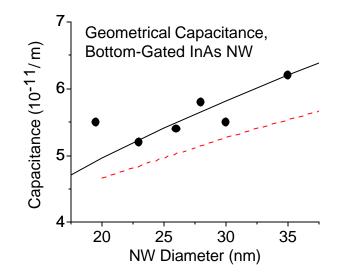

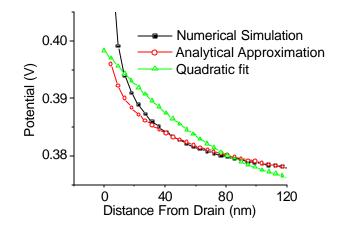

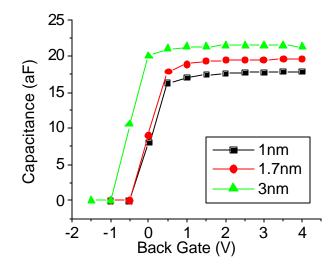

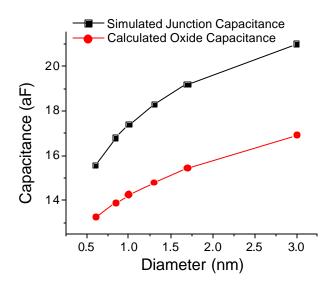

InAs nanowires grown using solid-source CVD can have a diameter ranging from 20nm to 40nm[3]. The measured gate oxide capacitance of back-gated InAs nanowire transistors is shown in figure 3.10. Electrostatic simulation reproduces well but underestimates the capacitance slightly, probably due to an error in the oxide thickness measurement. The oxide at the edge of the buried gate can also be much thinner than expected due to non-conformal step coverage of the CVD process. More importantly, figure 3.10 shows that a simple analytical expression:

$$\frac{C_{ox}}{L} = \frac{2\boldsymbol{p}\boldsymbol{e}_{r}\boldsymbol{e}_{0}}{\cosh^{-1}(\frac{T_{ox} + R_{NW}}{R_{NW}})}$$

(3.2)

**Figure 3.10** Capacitance per unit length for InAs nanowires in a back-gated geometry. The solid line is a fit using equation 3.2, with e=1.77. The dotted line is the result of electrostatic simulation using a commercial tool (Maxwell). The measured oxide thickness is 50nm, which is also used in the simulations.

fits well only when the non-uniform dielectric medium is taken into account. This can be simply done by making the relative permittivity  $e_r$  a fitting parameter, which at 1.77 gives a reasonable fit. This is because the electric field lines go through air as well as the oxide. This result is similar to approximations used for striplines in microwave circuits [9].

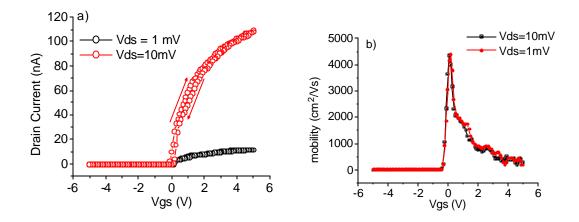

With the gate oxide capacitance accurately known, the low-field mobility can be confidently extracted, and is shown in figure 3.12. The low-field mobility is extracted from the transfer characteristics (figure 3.11) of long-channel devices (Lg >2um) at small drain bias *Vds*, and small values of *Vgs-Vt* such that the effects of velocity saturation and large vertical field can be ignored. More precisely, the Id-Vgs curve is differentiated vs  $V_{gs}$  to yield the conductance  $g_m$ , and the low-field mobility taken as the peak value of the quantity  $g_m L/Cox/Vds$ . At large Vgs-Vt, the mobility is degraded by the vertical field, similar to what is observed in planar Si MOSFETs. At very low Vgs-Vt the device is still not well above the threshold to be modeled correctly by a simple square-law model (eqn 3.3). For long channel, the drain current and the conductance  $g_m$ are simply given by:

$$I_{d} = \mathbf{m} \frac{C_{ox}}{L} (Vgs - Vt - Vds) Vds$$

(3.3)

$$g_m = \frac{dI_d}{dV_{gs}} = \mathbf{m} \frac{C_{ox}}{L} V ds \tag{3.4}$$

Since the device is one-dimensional, the oxide capacitance per nanowire,  $C_{ox}$ , is in the units of (F/m), as opposed to (F/m<sup>2</sup>) for a planar device. The diameter of the nanowire is measured using AFM and  $C_{ox}$  taken from the best analytical fit (figure 3.10) at that diameter.

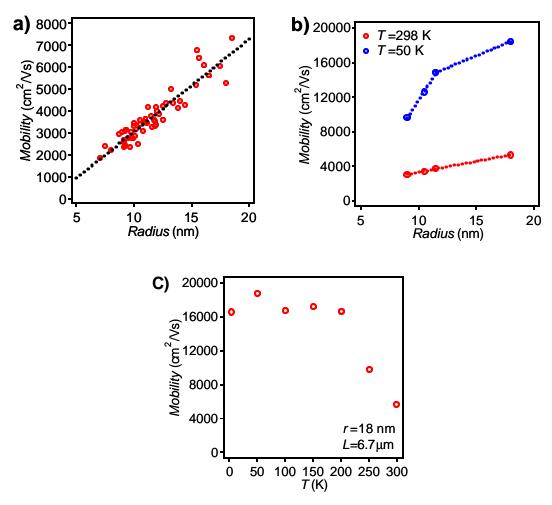

Figure 3.11 a) Transfer characteristics (Id-Vg) and b) mobility of a InAs nanowire transistor

At sufficiently low temperatures, phonon scattering is suppressed, and there is an overall increase in mobility. In a universal mobility model, the surface scatteringlimited mobility does not depend on temperature[10], evident from figure 3.11c. Figure 3.11b indicates that mobility decreases more rapidly for nanowire radius below ~11nm. Since the Bohr radius in InAs, at 34nm, is larger than the nanowire radius, quantum confinement can be important and may explain the stronger dependence of mobility on diameter in small wires, perhaps due to increased effective mass as demonstrated by recent theoretical calculations[11]. Quantum confinement can also modify the bandstructure such that the scattering rate is different from bulk, although this is speculative until a rigorous theoretical treatment is made.

**Figure 3.12** a) Low-field electron mobility vs nanowire radius at room temperature. b) Mobility vs radius at room temperature and 50K. c) Mobility vs temperature for a large diameter wire. The lack of temperature dependence suggests that surface roughness scattering is the dominant scattering mechanism at low temperatures. From [5].

#### **3.3 Summary and Future Work**

In this chapter, low-level C-V measurement and analysis are used to deduce the relevant parameters that describe the surface states of a single InAs nanowire. In addition, it is shown that a simple analytical expression predicts well the geometrical gate oxide capacitance, provided that the non-homogeneous dielectric medium is accounted for. The accurate measurement of the oxide capacitance allows for an accurate determination of the carrier mobility in InAs nanowires. When phonon scattering is suppressed at low temperatures, the dominant mechanism for small-diameter nanowires seems to be surface scattering.

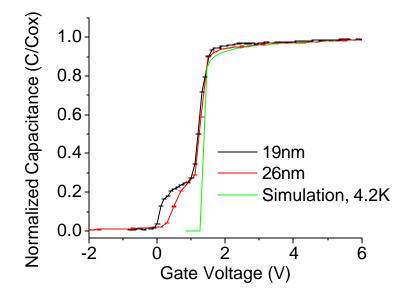

There are other properties of InAs nanowires that can be probed using this technique, one of which is the quantization effect arising from the small diameter. Ilani *et al* used the same technique to probe the density of states in a single carbon nanotube[12]. Figure 3.12 shows much more precise C-V measurements of two small InAs nanowires at liquid helium temperature, and the comparison to simulation. There are small but interesting features that cannot be reproduced by a straightforward electrostatic simulation employing bulk density of states.

**Figure 3.13** Measured C-V curves of two small diameter InAs nanowires at 4K. The measurement frequency is 100kHz. Simulation: diameter=20nm

At the temperature of liquid helium, the traps should have ceased to respond, as implied from the results at liquid nitrogen temperature (figure 3.5). Since the nanowire is undoped, the observed features in the C-V curves cannot be caused by ionized dopants either. The most plausible explanation is that there is a transition of the density of state in the nanowire from bulk-like to that of a one-dimensional quantum wire. At this moment, there is no known method to make much thinner InAs nanowires without increasing significantly the surface roughness. Should a solution be found, the onedimensional band structure of an individual InAs nanowire can be directly probed using this method.

### References

- [1] A. Khakifirooz and D.A.Antoniadis, *IEEE Tran.s on Elec. Dev.* **55**, 1391-1400 (2008)

- [2] Y. Cui, Z. Zhong, D. Wang, W.U. Wang, C.M. Lieber, Nano Lett. 3, 149-152 (2003)

- [3] D. Wang, Q. Wang, A. Javey, R. Tu, H. Dai, H. Kim, P.C. McIntyre, T. Krishnamohan, K.C. Saraswat, *Appl. Phys. Lett.*, 83, 2432-2434 (2003)

- [4] A.C. Ford, J.C. Ho, Z. Fan, O. Ergen, V. Altoe, S. Aloni, H. Razavi, A. Javey, *Nano Research*, **1**, 32-39 (2008)

- [5] A. Javey, J Guo, Q. Wang, M. Lundstrom, H. Dai, Nature, 424, 654-657 (2003)

- [6] A. Ford, J. Ho, Y.L. Chueh, Y.C. Tseng, Z. Fan, J. Guo, J. Bokor and A. Javey, *Nano Letters*, **9**, 360-365 (2009)

- [7] S. Roddaro, K. Nilsson, G. Astromskas, L. Samuelsson, L.E. Wernersson, O. Karlstrom, A. Wacker, *Appl. Phys. Lett.*, **92**, 253509 (2008).

- [8] S. Sze, *Physics of Semiconductor Devices*, 2<sup>nd</sup> edition.

- [9] D.M. Pozar, *Microwave Engineering* 2<sup>nd</sup> edition, Wiley, 1998

- [10] S. Takagi, A. Toriumi, M. Iwase, H. Tango, *IEEE Trans. Elec. Dev.*, 41, 2363-2368 (1994).

- [11] B. Lassen, M. Willatzen, R. Melnik, L.C. Lew Yan Voon, J. Mater. Res., 21, 2927-2935 (2006).

- [12] S. Ilani, L. Donev, F. Kindermann, P. McEuen, *Nature Physics*, 2, 687-691 (2006).

## **Chapter 4**

## **Metal-Carbon Nanotube Schottky Contacts**

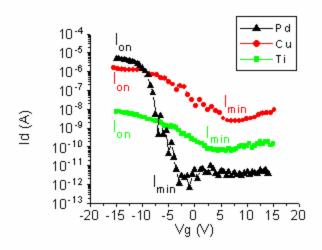

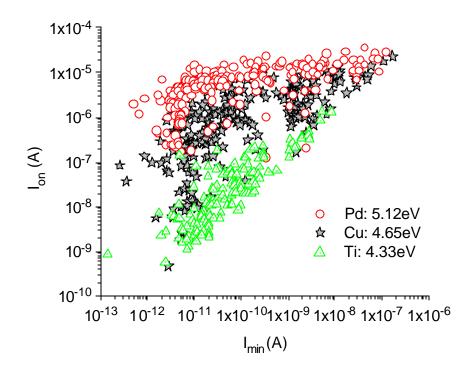

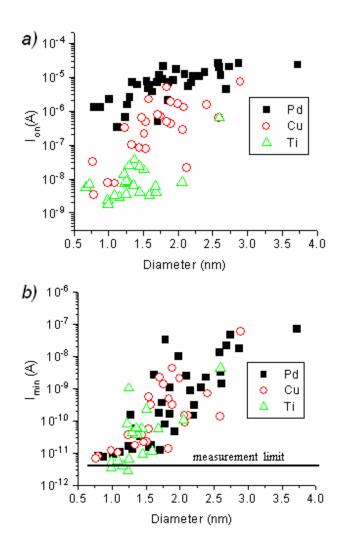

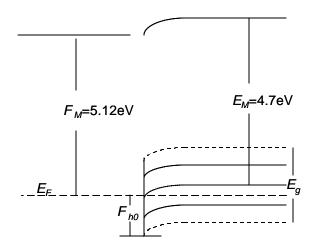

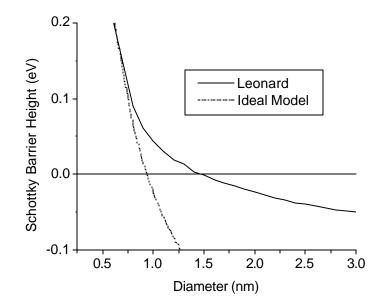

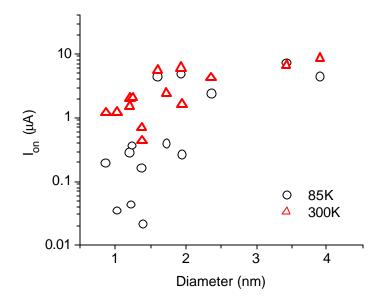

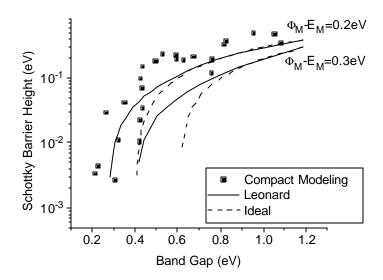

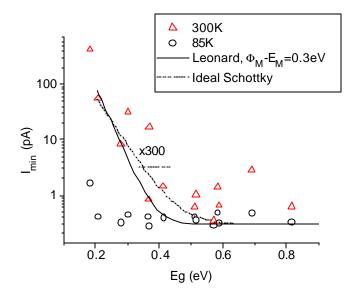

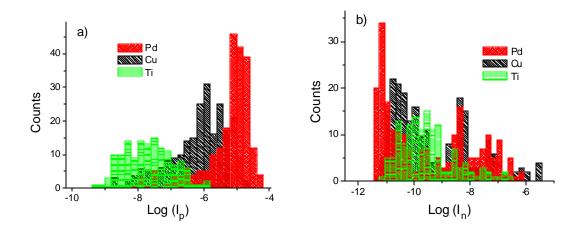

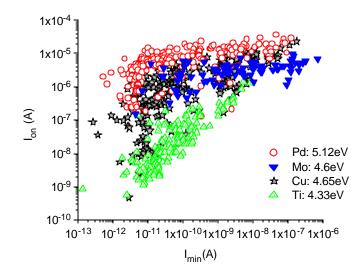

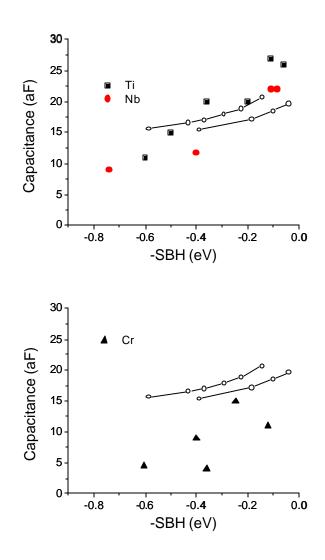

The metal-semiconductor (MS) contact is ubiquitous in semiconductor devices. By itself, a Schottky MS contact, with low substrate doping and large barrier height, can be used as a high-speed rectifier. In other devices such as MOSFETs and BJTs, the MS contact is absolutely necessary for their integration into circuits. These contacts need to have a low specific resistance in order for the devices to function properly. This is usually achieved by doping the contact region heavily to allow tunneling through a thinned Schottky barrier. In the current Si-based MOS technology, the MS contact is a major contributor to serial, parasitic resistances that degrade transistor performance. As the dimensions of MOS transistors diminish further, the resistance of the MS contact can become much more detrimental, since the source/drain junction will need to become even more shallow and abrupt to combat short-channel effects, and the dopant concentration in the source and drain can not go higher, being already limited by the dopants' solid solubility.