### Architectural Synthesis Techniques for Distributed Automotive System

Wei Zheng

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-73 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-73.html

May 20, 2009

Copyright 2009, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Acknowledgement

This research was supported by GSRC, CHESS and GM. I would like to first thank my advisor Alberto Sangiovanni-Vincentelli from Electrical Engineering and Computer Science at UC, Berkeley. He guided me into automotive domain and provided almost unlimited resources and supports for the research. The inspiration of this research comes mainly from the discussion with Marco Di Natale from Computer Science and Computer Engineering Department at Scuola Superiore S. Anna, Pisa. His tremendous guidance, feedback, and support are gratefully appreciated by the author. Finally, I would like to thank my family and friends, especially my wife Jing Yang from BWRC here at Berkeley , for their contributions in making my life in graduate school beautiful. The life in Berkeley will always be good memories.

#### Architectural Synthesis Techniques for Distributed Automotive System

by

Wei Zheng

B.E. (Tsinghua University, Beijing, China) 2000 M.S. (University of California, Berkeley) 2004

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering-Electrical Engineering and Computer Sciences

in the

### GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge: Professor Alberto Sangiovanni-Vincentelli, Chair Professor Sanjit Seshia Professor Robert Leachman

Spring 2009

The dissertation of Wei Zheng is approved:

Chair

Date

Date

Date

University of California, Berkeley

Spring 2009

### Architectural Synthesis Techniques for Distributed Automotive System

Copyright 2009

by

Wei Zheng

#### Abstract

#### Architectural Synthesis Techniques for Distributed Automotive System

by

Wei Zheng

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Alberto Sangiovanni-Vincentelli, Chair

Automotive electronic subsystems support the execution of distributed safety- and time-critical functions on a complex networked system with several buses and tens of ECUs (Electrical Control Units). Complex functions, which are designed as networks of function blocks exchanging signal information, are deployed onto the physical HW and implemented in a SW architecture consisting of a set of tasks and messages. For example, an advanced braking system, implemented on a set of four ECUs, will take responsibility of applying brakes and tightening seat belts within 80 milliseconds when it senses danger.

The objectives of this thesis are to develop analysis and synthesis techniques for vehicle electronic system designers i) to analyze worse case situations, ii) to select appropriate mapping of functionality to architectural elements and iii) to set corresponding design parameters; making sure key functionalities finish before appropriate deadlines for safety-critical applications. The design of communication subsystems is essential in guaranteeing that timing constraints are satisfied. They can be either time-triggered (TimeTriggeredArchitecture (TTA) and FlexRay) or eventtriggered such as CAN. Being able to accommodate incremental design changes while preserving a legacy design may reduce design and verification times substantially. For CAN systems, schedulability theory allows the analysis of the worst case end-to-end latencies and the evaluation of the possible architecture configurations options with respect to timing constraints, but it can also be used in the exploration of the software architecture configurations what can best support the target application. The optimization techniques presented in this thesis are based on ILP (integer linear programming) formulation combined with search algorithms and can derive implementations of both time-triggered and event triggered system that fulfill the design constraints. The techniques proposed are evaluated using industrial examples to prove the effectiveness of the work.

> Professor Alberto Sangiovanni-Vincentelli Dissertation Committee Chair

To my dear parents

# Contents

| Li | st of F | ligures                                                                       | iv |

|----|---------|-------------------------------------------------------------------------------|----|

| Li | st of T | <b>Fables</b>                                                                 | vi |

| 1  | Intro   | oduction                                                                      | 1  |

|    | 1.1     | Research Contribution                                                         | 2  |

|    | 1.2     | Research Motivation                                                           | 3  |

|    |         | 1.2.1 Research motivation from System Level Design methodology                | 3  |

|    |         | 1.2.2 Research motivation from automotive applications                        | 4  |

|    | 1.3     | Modern System and Standard Overview                                           | 6  |

|    |         | 1.3.1 Modern Systems                                                          | 6  |

|    |         | 1.3.2 Automotive Standards                                                    | 9  |

|    | 1.4     | A Real Life Example                                                           | 15 |

| 2  | A De    | esign Methodology and Flow with Emphasis on Scheduling for Automotive Systems | 19 |

|    | 2.1     | Platform Based Design Methodology Introduction                                | 20 |

|    | 2.2     | A Design Flow with Emphasis on Scheduling for Automotive Systems              | 22 |

|    |         | 2.2.1 Functional Models                                                       | 24 |

|    |         | 2.2.2 Architecture Models                                                     | 26 |

|    |         | 2.2.3 System Platform Model                                                   | 27 |

|    |         | 2.2.4 Mapping                                                                 | 28 |

|    |         | 2.2.5 Scheduling                                                              | 30 |

| 3  | Sche    | eduling for Time-Triggered Communication System                               | 33 |

|    | 3.1     | Preliminaries and Definitions for Time-Triggered Communication System         | 34 |

|    |         | 3.1.1 Time-Triggered Protocols Overview                                       | 34 |

|    |         | 3.1.2 Previous Work on Time-Triggered Protocols                               | 39 |

|    |         | 3.1.3 System Modeling                                                         | 41 |

|    | 3.2     | Scheduling Synthesis for a FlexRay based communication network                | 47 |

|    |         | 3.2.1 A Two-Steps Approach and Synchronization Mode                           | 48 |

|    |         | 3.2.2 Synthesis FlexRay Scheduler in An Optimization Framework                | 52 |

|    | 3.3     | Incremental Design for Time-Triggered System                                  | 64 |

| ٠ | ٠ | ٠ |  |

|---|---|---|--|

| 1 |   | 1 |  |

| I | T | т |  |

|   |   |   |  |

|    |       | 3.3.1      | Extensibility and Scalability Design Metrics in a general Time-Triggered Protocol | 66  |

|----|-------|------------|-----------------------------------------------------------------------------------|-----|

|    |       | 3.3.2      | Time-Triggered Incremental Design in an Optimization Framework                    |     |

|    |       | 3.3.3      | Experimental Results                                                              |     |

|    |       |            | •                                                                                 |     |

| 4  |       |            | based Synthesis for Event Triggered Automotive System                             | 92  |

|    | 4.1   |            | inaries and Definitions for Event Triggered System                                |     |

|    |       | 4.1.1      | Controller Area Network Background                                                |     |

|    |       | 4.1.2      | CAN based System Modeling                                                         |     |

|    | 4.2   |            | Analysis of CAN based Communication System                                        |     |

|    |       | 4.2.1      | Response Time for Tasks: Processor Scheduling                                     |     |

|    |       | 4.2.2      | Response Time for Messages: Bus Scheduling                                        | 99  |

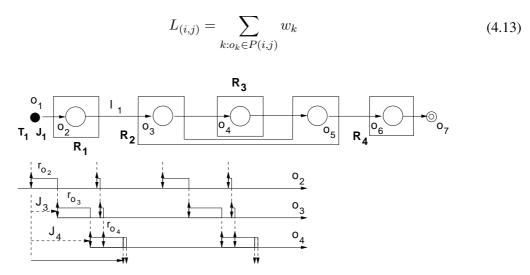

|    |       | 4.2.3      | End to End Latencies                                                              | 100 |

|    | 4.3   | System     | 1 Activation Model                                                                | 101 |

|    |       | 4.3.1      | Periodic Activation Model                                                         | 101 |

|    |       | 4.3.2      | Data-driven Activation Model                                                      | 102 |

|    | 4.4   | Parame     | eter Synthesis of CAN based Communication System                                  | 103 |

|    |       | 4.4.1      | Parameter Synthesis Overview                                                      | 103 |

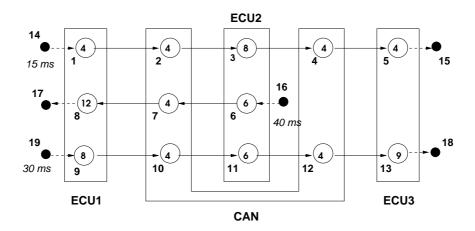

|    |       | 4.4.2      | A Simple Example                                                                  | 105 |

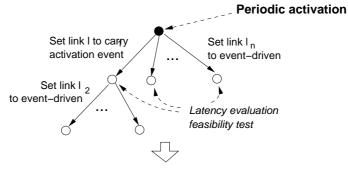

|    |       | 4.4.3      | Optimization Framework for Synthesizing Activation Model                          | 109 |

|    |       | 4.4.4      | Heuristic Framework for Synthesizing Activation Model                             | 114 |

|    |       | 4.4.5      | An Industrial Example                                                             | 122 |

| 5  | Mai   | oping wi   | ith Scheduling for Automotive System                                              | 128 |

|    | 5.1   |            | Plow Revisited                                                                    |     |

|    | 5.2   |            | n Modeling and Notations                                                          |     |

|    | 5.3   |            | ization on Task Placement and Signal Mapping                                      |     |

|    | 0.0   | 5.3.1      | Previous Work                                                                     |     |

|    |       | 5.3.2      | Objective and Formulation                                                         |     |

|    |       | 5.3.3      | Task to ECU mapping                                                               |     |

|    |       | 5.3.4      | Signal to message mapping                                                         |     |

|    |       | 5.3.5      | Two Steps Synthesis Procedure                                                     |     |

|    | 5.4   |            | mental Result                                                                     |     |

| 6  | Cor   | -          | s and Future Work                                                                 | 154 |

| U  | COL   | iciusi0118 |                                                                                   | 134 |

| Bi | bliog | raphy      |                                                                                   | 157 |

| A  | Alp   | habetic    | Notations                                                                         | 167 |

# **List of Figures**

| 1.1  | A Real-life Example: Part of Functionality for EVC                |

|------|-------------------------------------------------------------------|

| 1.2  | A Real-life Example: Part of Architecture for EVC                 |

| 2.1  | Platform Based Design                                             |

| 2.2  | System design flow                                                |

| 3.1  | the four segments in a FlexRay cycle                              |

| 3.2  | FlexRay Timing Hierarchy                                          |

| 3.3  | System model with tasks, links and delays                         |

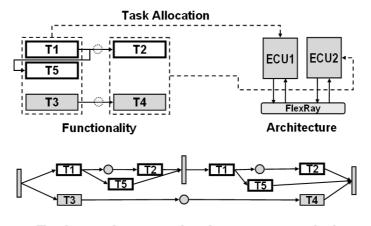

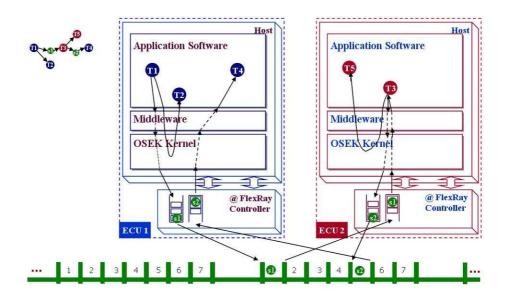

| 3.4  | Mapping and task graph expansion                                  |

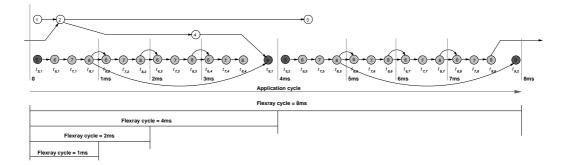

| 3.5  | Instance graph, Application cycle and FlexRay cycle               |

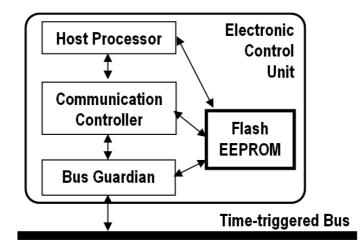

| 3.6  | Time-triggered node architecture                                  |

| 3.7  | FlexRay Message Passing Mechanism                                 |

| 3.8  | Application cycle and FlexRay cycle                               |

| 3.9  | A two-step approach in scheduling FlexRay communication           |

| 3.10 | Schedulers synchronized and not synchronized 51                   |

| 3.11 | Extent and constraints in the definition of the scheduling domain |

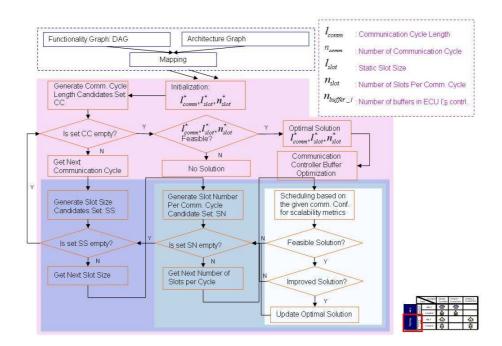

|      | FlexRay Schedule Overall Optimization Flow                        |

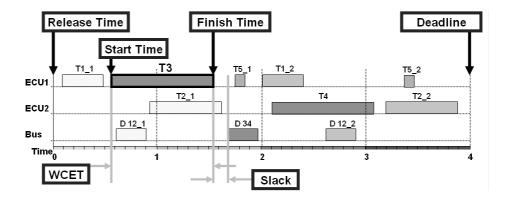

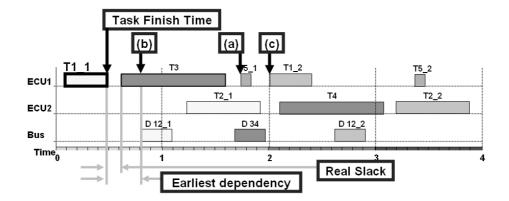

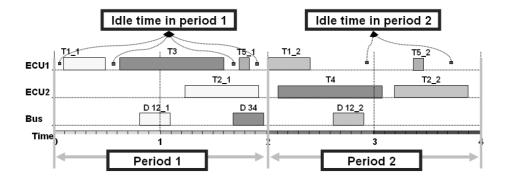

| 3.13 | Properties for Task T3                                            |

| 3.14 | Extensibility metric illustration                                 |

| 3.15 | Scalability metric illustration                                   |

| 3.16 | Case study functionality graph                                    |

|      | Case study architecture graph                                     |

| 3.18 | Extensibility metric evaluation                                   |

|      | Scalability metric evaluation                                     |

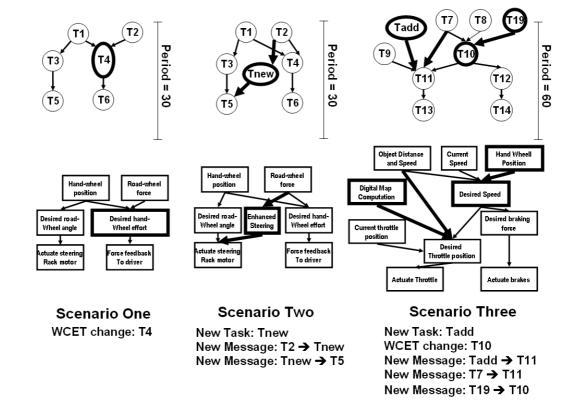

| 3.20 | Incremental design scenarios                                      |

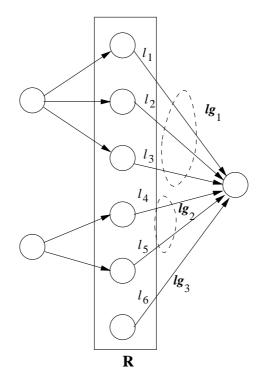

| 4.1  | Example of link groups                                            |

| 4.2  | Periodic activation model                                         |

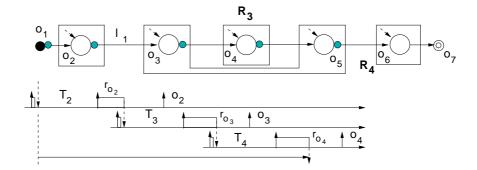

| 4.3  | Data driven activation model                                      |

| 4.4  | Example graph                                                     |

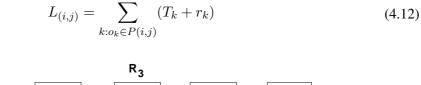

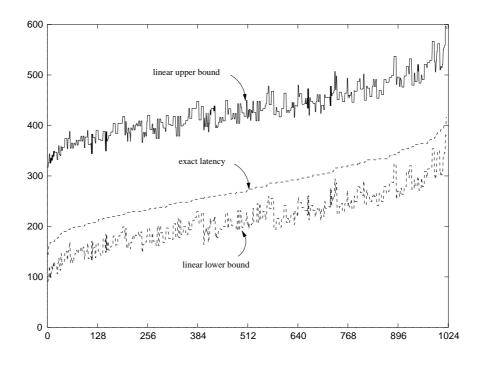

| 4.5  | End-to-end latencies for the lowest priority path of the example  |

| 4.6 | Search tree                                               | 117 |

|-----|-----------------------------------------------------------|-----|

| 4.7 | Steps of the search algorithm for the example             | 122 |

| 4.8 | Activation options for one of the tasks in the case study | 124 |

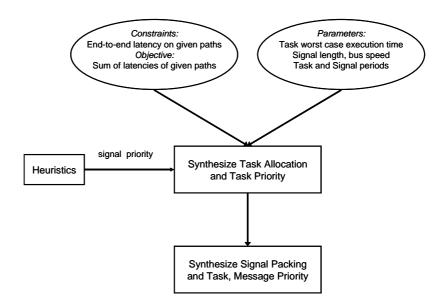

| 5.1 | Design flow stages and optimization objectives (in bold)  | 130 |

| 5.2 | Mapping of tasks to ECUs and signals to messages.         | 132 |

| 5.3 | Periodic activation model.                                | 138 |

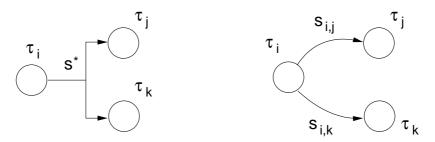

| 5.4 | Multicast signals and their representation.               | 142 |

| 5.5 | Two Step Synthesis Approach                               | 150 |

# **List of Tables**

| 3.1 | Protocol comparison                  | 39  |

|-----|--------------------------------------|-----|

| 3.2 | Tasks for the X-by-wire example      | 64  |

| 3.3 | Signals for X-by-wire example        | 90  |

| 3.4 | Results on the X-by-wire Example     | 91  |

| 3.5 | Incremental design change evaluation | 91  |

| 4.1 | Simple Example Data                  | 107 |

# **List of Algorithms**

| 1 | Search Algorithm |  |  | • | • |  | • |  |  |  |  | • |  |  |  |  | • |  |  |  |  |  |  |  |  |  | • |  |  |  | • |  |  |  |  |  | 1 | 1: | 5 |

|---|------------------|--|--|---|---|--|---|--|--|--|--|---|--|--|--|--|---|--|--|--|--|--|--|--|--|--|---|--|--|--|---|--|--|--|--|--|---|----|---|

|---|------------------|--|--|---|---|--|---|--|--|--|--|---|--|--|--|--|---|--|--|--|--|--|--|--|--|--|---|--|--|--|---|--|--|--|--|--|---|----|---|

#### Acknowledgments

This research was supported by the Gigascale Systems Research Center (GSRC), Center for Hybrid and Embedded Software Systems (CHESS), and General Motors (GM). I would like to first thank my advisor Alberto Sangiovanni-Vincentelli from Electrical Engineering and Computer Science at UC, Berkeley. He guided me into automotive domain and provided almost unlimited resources and supports for the research. The inspiration of this research comes mainly from the discussion with Marco Di Natale from Computer Science and Computer Engineering Department at Scuola Superiore S. Anna, Pisa. His tremendous guidance, feedback, and support are gratefully appreciated by the author. The author would like to thank many researchers and engineers from GM Warren technical center, and GM Bay Area Lab in Palo Alto; more specifically, Paolo Giusto and Thomas Fuhrman, for providing intensive discussion for the industrial case study. The author would also like to appreciate Claudio Pinello from Cadence Berkeley Lab for his guidance and discussion on the project; Haibo Zeng, Jike Chong and Qi Zhu from Department of Electrical Engineering and Computer Sciences, University of California at Berkeley for their discussion and work which help me understand mapping process and design methodology. Professors Shankar Sastry, Sanjit Seshia, Candace Yano and Alberto Sangiovanni-Vincentelli, my advisor, served on the qualifying committee and/or provided invaluable feedback and guidance in the dissertation writing process. Finally, I would like to thank my family and friends, especially my wife Jing Yang from BWRC here at Berkeley, for their contributions in making my life in graduate school beautiful. Without their support, I won't be able to smoothly get to this point and I'd like to owe all of my success here in Berkeley to my wife. The life in Berkeley will always be good memories.

### **Chapter 1**

## Introduction

Function development in Electronics, Controls, and Software-based (ECS) vehicle architectures has traditionally been component or sub-system focused. In recent years, there has been a shift from the single ECU approach towards an increased networking of control modules. The implications are an increased number of distributed time-critical functions and multiple tasks in execution on each ECU.

The starting point for the definition of a car electronic software system is the specification of the set of features that the system is expected to provide. A feature is a very high level description of a system capability (e.g. Cruise Control). Functional models are created from the decomposition of the feature in a hierarchical network of component blocks. The physical architecture model captures the topology of the car network, including the communication buses (e.g. FlexRay or CAN), the CPUs and the management policies (e.g. time-driven scheduling or priority-driven scheduling) that control the shared resources.

Hence, two levels of representation of the system are defined: the functional view and

the physical architecture view. The system designer must find a mapping of the functional architecture onto the physical architecture that satisfies the timing requirements (sensor-actuator deadlines). The mapping is performed at the time the SW implementation is defined, when the functions are implemented by a set of concurrent tasks and the communication signals are transferred in the payload content of messages. To provide design-time guarantees on timing constraints, different design and scheduling methodologies can be used. Avionics controls, for example, are often built based on static, time-driven schedules, examples of standards supporting this scheduling model are the OSEK Time system standard and the FlexRay bus arbitration model. Because of resource efficiency and ultimately price, many automotive controls are designed based on run-time priority-based scheduling of tasks and messages. Examples of standards supporting this scheduling model are the OSEK

This thesis presents an integrated framework for design space exploration that leverages powerful mathematical programming to solve complex scheduling problem in a platform based design context.

This introduction is structured in three parts. In the first part, Section 1.1 presents the research contribution of the thesis. The second part, Section 1.2 describes the motivation of the work. The last part, Section 1.3 contains an overview of modern system followed by a real life automotive system example which will be extensively explained throughout the thesis.

#### **1.1 Research Contribution**

The thesis is performed in the context of the design of distributed software architectures for next-generation automotive controls, where the application performance requirements impose constraints on end-to-end latencies in the execution of the control functions.

The thesis/research goal and effort center around Platform-Based Design (an approach to the new system theory) based system analysis and synthesis for distributed systems, and are embodied in: (1) Modeling of functionality and architecture (2) Mapping from functional model to architectural model (3) Scheduling of the mapped functionality units within the architecture units according to the performance constraints specified by the system designers.

Automated architecture exploration is necessary to improve design productivity for distributed (hard) real time systems especially for Analysis and Synthesis of Design Parameters. The scheduling/schedulability analysis centered system parameter synthesis techniques within a mathematical programming optimization framework could actually solve many problems efficiently where used appropriately. However, the synthesis framework that could facilitates automated architecture exploration applied to automotive systems is the main research contribution of this thesis.

#### **1.2 Research Motivation**

#### 1.2.1 Research motivation from System Level Design methodology

Over the past several decades, embedded systems have evolved to a level of maturity and sophistication and appeared everywhere in our everyday life. The complexity of these systems is, however, reaching levels that were not even conceivable a few years ago: There are more than 80 processors in a new generation car that control its function and implement its entertainment and communication subsystems. The problem is how to systematically conduct the design, analysis and synthesis in this new regime. Stated in another way, is it possible to quickly and effectively provide a new system design methodology with the capability of handling the distributed embedded system

design? Is there a general and flexible design flow embedded in the methodology for a large variety of application domains? Towards this objective, I believe that the recent system level design methodology advances in Platform-Based Design (PBD) offer a unique and attractive solution. The idea for PBD is to call for a successive refinement approach where functionality (what the system is supposed to do) of the design is captured at the highest level of abstraction possible and mapped to a set of predefined solutions. Specifying a design includes identifying constraints such as latency, throughput, reliability, cost, and power consumption. The architecture is an interconnection of elements that are characterized by performance indexes coming from the abstraction of their implementation. The mapping process can be automated if both function and the architecture elements that form the platform are projected to a common semantic domain. The process repeats itself by interpreting the mapped design as a function at the next layer of abstraction and new architectural elements are introduced. Here at the Berkeley Center for Hybrid and Embedded Software Systems (CHESS) and the Gigascale System Research Center (GSRC), I have proposed and developed the common semantic domain for automotive systems with an emphasis on scheduling for PBD, which provides the system designers with the flexibility of performance analysis and parameter synthesis based on the schedulability analysis theory. Furthermore, I have explored the generality and limitations of this methodology, with respect to both bottom up and top down design flows widely used in embedded system design, and provide a practical guidance on meet in the middle design scheme with an emphasis on scheduling.

#### **1.2.2** Research motivation from automotive applications

Platform Based Design was used in a variety of industrial applications: from automotive electronic design to communication systems and semiconductor chips. The promising case stud-

ies in vehicle design demonstrate the effectiveness of PBD in all dimensions. Today's vehicles are becoming increasingly more complex as consumers demand more and better features in their automobiles. Most new features are requiring additional electronic components and control software, constantly pushing the limits of existing architectures and design methodologies. The problems with traditional design methodologies are numerous, resulting in intermittent feature failures, significant testing effort, production delays, increased warranty costs, and consumer dissatisfaction. The solution to all of these problems starts with the adoption of a system level PBD. My research focuses on one of the important system performance, timing, which is impacted by a lot of factors but most in the mapping and scheduling phase during the system design. Based on the system-level PBD, I believe that recent mathematical advances in correlated formulations and solvers offer an attractive solution. The idea is to use a mathematical programming based optimization framework to handle system communication and synchronization models, tasks to Electronic Control Unit (ECU) placement, signals to message mapping and the assignment of priorities to tasks and messages in order to meet end-to-end deadline constraints and minimize latencies. At Berkeley, I collaborated with General Motors Advanced Technology Research Group and I have proposed an ILP based optimization framework to automate the above process: set up the activation model (Synchronous VS. Asynchronous) and leverage the trade-offs between the purely periodic and the data-driven activation models to meet the latency requirements of distributed vehicle functions. Additionally, it is not difficult to find out that the same approach could be leveraged to tasks placement, signals to messages mapping and priorities assignment to expand the automation process of the whole system design. At the same time, the framework is working well for time-triggered protocols which are used by safety critical applications by most of major automotive companies especially in the consideration of incremental design. General Motors has adopted the methodology and the optimization framework for its electronic system design. The effectiveness of all of above approaches has been verified by a real case study from GM.

#### **1.3** Modern System and Standard Overview

#### 1.3.1 Modern Systems

Modern system development is getting more and more complicated and usually goes through phases from system analysis, system design and system implementation to system testing. System analysis (also called system specifications) requires the designer understand application requirements in both functional and non-functional aspects, namely they need to know what the system need to provide to the end users. System design goes through the definition of the design solutions (among all possible ones) that can solve the specifications problem. This part also includes selection of the HW/SW platform, including the operating systems and the resource management policies. The system implementation (coding) phase will focus on translating the design into packages or program modules, developed in a programming language. This part can be manually performed or the result of automatic model translations (provided the design model is formal). Finally the system testing is necessary for checking that the application satisfies all functional and non-functional requirements. The definition of several systems will be introduced to better understand the complication of modern design world.

#### 1.3.1.1 Embedded Systems

According to Wikipedia [2], an embedded system is a special-purpose computer system designed to perform one or a few dedicated functions, often with timing constraints, that means embedded system is usually a real time system. It is often embedded as part of a complete device including hardware and mechanical parts. In contrast, a general-purpose computer, such as a personal computer, can do many different tasks depending on programming. Embedded systems control many of the common devices in use today.

Physically, embedded systems range from portable devices such as digital watches and MP3 players, to large stationary installations like traffic lights, vehicle controllers, or the systems controlling nuclear power plants. Complexity varies from low, with a single micro-controller chip, to very high with multiple units, peripherals and networks mounted inside a large chassis or enclosure.

In general, "embedded system" is not an exactly defined term, as many systems have some element of programmability. For example, hand-held computers share some elements with embedded systems - such as the operating systems and microprocessors which power them - but are not truly embedded systems, because they allow different applications to be loaded and peripherals to be connected. Almost all of the ECUs in cars are embedded systems which usually have special purpose on processing or sensing/actuating.

#### 1.3.1.2 Real Time Systems

There are many definitions for real time systems:

1. A real-time system is an interactive system that maintains an ongoing relationship

with an asynchronous environment i.e. an environment that progresses irrespective of the real time system.

2. (IEEE) Pertaining a system or mode of operation in which computation is performed during the actual time that an external process occurs, in order that the computation results may be used to control, monitor or respond in a timely manner to the external process.

3. A real-time system responds in a (timely) predictable way to (un)predictable external stimuli arrival.

4. Open, Modular, Architecture Control user group - (OMAC) defines a hard real-time system as a system that would fail if its timing requirements were not met, and a soft real-time system can tolerate significant variations in the delivery of operating system services like interrupts, timers, and scheduling.

Overall, a real-time computing correctness depends not only on the correctness of the logical result of the computation but also on the result delivery time. Real-time applications are characterized by timing constraints which are mostly non functional requirements comes from system specification. This applies to almost all the case studies in this thesis.

#### **1.3.1.3 Distributed Systems**

Distributed system or distributed computing deals with hardware and software systems containing more than one processing element (such as ECUs in automotive electronics) or storage element, concurrent processes, or multiple programs, running under a loosely or tightly controlled regime.

In distributed computing a program is split up into parts that run simultaneously on multiple computers communicating over a network. Parallel computing is most commonly used to describe program parts running simultaneously on multiple processors in the same computer. Both types of processing require dividing a program into parts that can run simultaneously, but distributed programs often must deal with heterogeneous environments, network links of varying latencies, and unpredictable failures in the network or the computers. Recent development of automotive electronics has the trend from single ECU application to networked ECU application, for example, automatic windows function in a car could be deployed across as many as four ECUs so that the control signal to the windows won't go through long distance transmission.

#### 1.3.1.4 Modern Automotive System

As mentioned above, the complexity and physical distribution of modern active safety, chassis and powertrain automotive applications requires the use of distributed architectures. Complex functions designed as networks of function blocks exchanging signal information are deployed onto the physical hardware (HW) and implemented in a software (SW) architecture consisting of a set of tasks and messages. ECUs are special purpose computer systems used performing computation of tasks, recent development of safety critical applications addresses stringent timing requirements on the system.

Overall, a complex, safety critical automotive system is an embedded, real-time, distributed system. The thesis will emphasis the design space exploration of such a complicated system.

#### 1.3.2 Automotive Standards

Most applications in automotive electronic designs are getting more and more communication intensive. Design reuse is also being highly considered by major auto-makers. A number of standards are currently addressing the need for reuse of automotive components at different levels of abstraction. The following is a list, far from exhaustive, of the main initiatives. This thesis focuses on two communication protocols in automotive electronic system design: the time- triggered (mainly for the static segment) FlexRay communication system and the event-triggered CAN communication system.

#### 1.3.2.1 AUTOSAR

AUTOSAR [1] has been established by original equipment manufacturers (OEM) and Tier 1 automotive suppliers to develop an open industry standard for automotive electronic architecture which will serve as a basic infrastructure for the management of functions within both future applications and standard software modules. Members include GM, BMW, Bosch, Continental, DaimlerChrysler, Volkswagen, Siemens VDO, Ford, PSA, and Toyota.

The AUTOSAR basic infrastructure objectives are:

- Implementation and standardization of basic system functions as an industry wide "Standard Core" solution

- 2. Scalability to different vehicle and platform variants

- 3. Transferability of functions throughout network

- 4. Integration of functional modules from multiple suppliers

- 5. Consideration of availability and safety requirements

- 6. Redundancy activation

- 7. Maintainability throughout the whole "Product Life Cycle"

- 8. Increased use of "Commercial off the shelf hardware"

- 9. Software updates and upgrades over vehicle lifetime

The AUTOSAR software component implementation is independent from the infrastructure. A fundamental design concept of AUTOSAR is the separation between application and infrastructure. The approach is quite similar to central ideas of the platform based design methodology used throughout the thesis, namely the orthogonalization of functionality with architecture.

#### 1.3.2.2 FlexRay

FLEXRAY [24] is a communication standard created by an industry consortium founded in 2000 by BMW, DaimlerChrysler, General Motors, Motorola, Philips, Volkswagen, and Robert Bosch. FlexRay is a high-speed serial communication system for in-vehicle networks using bus or point-to-point (star topology) links, at 10Mbps over un-shielded Twisted Pair or Shielded Twisted Pair cable. More introduction will be discussed in 3.1.1.1 for FlexRay system.

In FlexRay, the bus time is divided in cycles. Each cycle is partitioned into a static timetriggered portion, and a dynamic event-triggered portion. The communication cycle length is defined by the application up to a maximum of 16ms. The division between the two portions is set at design time and loaded into the controllers and bus guardians. Flexray's intended use is for highly dependable and fast safety critical applications. Protection from timing faults should be provided by the bus guardian that prevents frames sent in the time-triggered segment to overlap in time with each other and with the dynamic segment. The full schedule for the time-triggered portion is not known by each controller. Instead, this segment is divided at compile time into a number of slots of fixed size, and each controller and its bus guardians are informed of which slots are allocated to their transmissions. Nodes requiring greater bandwidth are assigned more slots than those that require less. Each controller learns the full schedule only when the bus starts up. Each node includes its identity in the messages that it sends. During startup, nodes use these identifiers to label their input buffers as the schedule reveals itself.

The Static Segment is typically used for critical messages with the following constraints:

- 1. All static slots are the same length in microticks

- 2. All static slots are repeated in order every communication cycle

- 3. All static slot times are assigned for use in a cycle whether they are actually used or not

- 4. The number of the static slots is configurable but only up to a maximum of 1023 slots

#### 1.3.2.3 CAN

Controller Area Network (CAN) is a multicast shared serial bus standard, originally developed in the 1980s by Robert Bosch GmbH, to connect electronic control units (ECUs). CAN was specifically designed to be robust in electromagnetic noisy environments. Bit rates up to 1 Mbit/s are possible with networks long less than 40 m. Decreasing the bit rate allows longer network distances (e.g. 125 kbit/s at 500 m).

The CAN data link layer protocol is standardized in ISO 11898-1 (2003). The standard describes mainly the data link layer - composed of the Logical Link Control (LLC) and the Media Access Control (MAC) sub-layers - and some aspects of the physical layer of the ISO/OSI Reference Model. All the other protocol layers are left to the network designer's choice. CAN is an attractive solution for embedded control systems because of its low cost, light protocol management and the deterministic resolution of the contention. The protocol adopts a collision detection

and resolution scheme, where the message to be transmitted is chosen according to its identifier. The lowest identifier message is transmitted. This makes possible to encode the message priority into the identifier field and to implement priority-based real-time scheduling of periodic and a-periodic messages. However, its major limitation is in the maximum available bandwidth, which is a consequence of the adoption of a multi-master digital bus. The available bandwidth may easily become scarce given the current trend in the automotive field towards an increased number of interconnected devices, particularly intelligent sensors, and an increased amount of data to be shared. In order to overcome the speed limitation of the CAN bus, other standards are being proposed, like the Flexray. However, because of its low cost and widespread use, the CAN bus is still the dominant communication medium in the automotive industry.

#### 1.3.2.4 OSEK

OSEK [52] stands for Offene Systeme und deren Schnittstellen fr die Elektronik in Kraftfahrzeugen (eng., "Open Systems and their interfaces for the Electronics in Motor vehicles"). The OSEK specifications have been produced for an embedded operating system, a communications stack, and a network management protocol for automotive embedded systems. The most important characteristics of an OSEK-compliant operating system are

- 1. The flexibility on the kernel configuration with increasing service capabilities and memory requirements

- 2. The possibility of configuring the kernel by means of a file in a standard configuration language (OIL)

- 3. The static generation of most operating system and application objects, with a very efficient

implementation and minimum kernel footprint

4. The support for real-time scheduling and resource management algorithms, allowing a predictable timing behavior

OSEK is widely used in automotive electronics today. Understanding the operation system's capability is essential for designers.

#### 1.3.2.5 LIN

Most sensor systems are based on architectures using point to point analog communications from sensors to ECUs. In these cases, signal integrity is at risk in very noisy environments such as that of an automobile. LIN [51] was originally developed for body electronics, however, it has been increasingly used to tackle the integrity issue for sensor interfaces. Its low-cost, bidirectional, single-wire physical-layer implementation reduces wiring and wiring harness requirements. It is possible to build a sensor module that has only three wires (battery, ground and LIN), even if there are multiple sensors inside the module. This reduction in wiring and wiring harness allows for a reduction in the sensor housing size, better sensor placement and less sensitivity to wire placement. This is especially true if more than one sensor is included in the module and all the outputs are multiplexed into a single LIN bus. LIN allows for two-way communication over a single wire so that the master has the capability to request diagnostic information from the sensor, or the sensor can provide system-failure information when needed. The LIN protocol is based on a master/slave architecture - all bus communication is controlled and scheduled by the master node. This feature enables guaranteed latencies for signal transmission, as no arbitration is utilized, which is a necessary property for most sensor signals. The LIN bus architecture is scalable to 16 nodes.

#### **1.4 A Real Life Example**

A real-life case study presented in this part will be used in the following chapters for evaluating the research approaches.

Auto-makers are constantly evaluating and developing new features that bring value to the customer. One important recent example is the integration of active and passive safety features, based on a set of ranging sensors that cover a 360 degree area around the vehicle. Examples are the Virtual Bumper and Anti-theft Systems. Some of these features have been demonstrated on a prototype research vehicle, called V1 in this thesis. The electrical architecture of V1 was developed integrating required sensors, actuators, CAN networks and processing units (ECUs) supporting the execution of the features in a prototype vehicle called mule. The architecture was developed by extension from the mule vehicle in an ad-hoc fashion, without considering extensibility or compatibility with current and future production architectures.

The following version V2 program consisted of the development of a production vehicle where some of the features from V1 and the experience gained in V1 were integrated and extended with new safety-relevant features, some of which coming from Tier-1 suppliers.

In V2, the control engineers provided the deadlines for the end-to-end latencies of selected paths in the architecture. Furthermore, the utilization of the ECUs and the CAN buses of the system had to be controlled to ensure future extensibility.

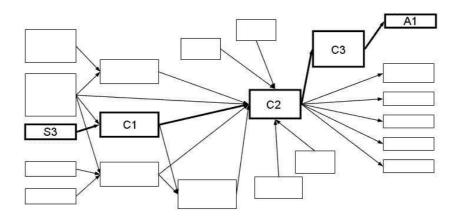

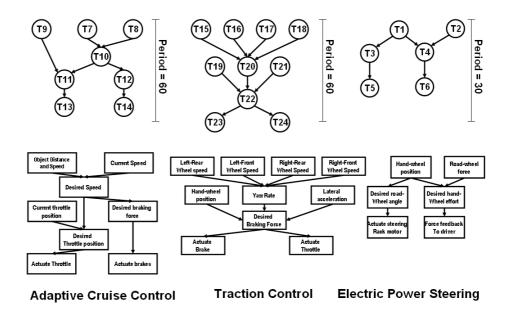

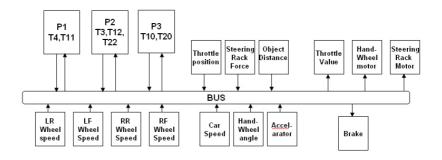

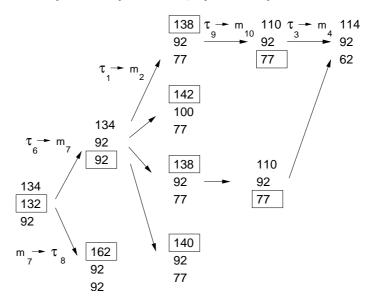

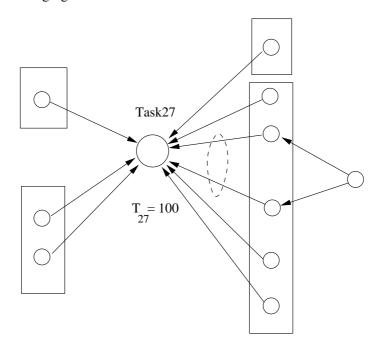

For this thesis, one example modified from a specific version of V2, called Experimental Vehicle (EV), will be used for evaluation purpose. Figure 1.1 shows a part of the entire functionality graph and Figure 1.2 shows a part of the entire architecture graph of the experimented EV.

In Figure 1.1, all the left most rectangles represent sensors, all the right most rectangles

Figure 1.1: A Real-life Example: Part of Functionality for EVC.

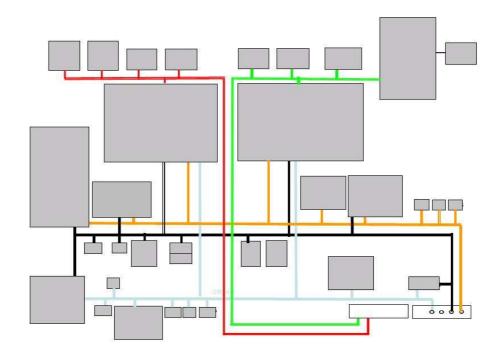

Figure 1.2: A Real-life Example: Part of Architecture for EVC.

represent actuators, and all the remaining ones denote the network of computing blocks decomposed from high level features. There is a timing constraint, required by the feature that the system is expected to provide, associated with one specific path on the functionality graph. This path may start from a sensor module S3 through computing modules C1, C2, C3 and finally reached an actuating module A1. A potential scenario is: sensor S3 runs in a non-stop mode to sense the change of the environment around the vehicle, the signal captured by sensor S3 goes through a series of intermediate computations and then the computed decision is propagated to the actuator A1 which acts on the environment. Consider a safety critical feature: lane keeping. In this example, the series of computation finally makes a decision whether the vehicle should keep the current lane or not, then the functional computation and signal propagation are expected to complete at most in a very short time, say around 100ms. Such an application is typical safety critical and has a high requirement on the path (maybe selected) latencies.

The above network of functionalities will be executed in the physical architecture which can be described in Figure 1.2. It consists of a number of ECUs connected by different types of communication buses, say either FlexRay (for safety critical messages) bus or CAN bus.

Mapping of functionality to architecture as well as scheduling of a set of functionalities to the same architectural unit is a crucial part of the design process. The process, called design space exploration, is the focus of this thesis.

Chapter 2 presents the design methodology combined with a design flow for the automotive domain where scheduling plays a fundamental role. Chapter 3 explains the scheduling synthesis problem in a FlexRay based communication system and then presents a scheduling strategy in an incremental design scenario to reduce design cost. CAN based communication system is discussed in Chapter 4. The trade-off for the periodic activation model and the data-driven model is extensively explored using both a mathematical programming and a heuristic based approach. The effectiveness of the proposed approaches is illustrated by the EV case study. At the end of Chapter 4, the issues of integrated period synthesis is addressed. Chapter 5 investigates mapping policies together with schedulability analysis. The typical configuration features priority based scheduling of tasks and messages and imposes end-to-end deadlines. The proposed approach optimizes task placement and signal-to-message mapping, and automates the assignment of priorities to tasks and messages in order to meet end-to-end deadline constraints and minimize latencies. The effectiveness of the solution is proven again by the EVC example. Chapter 6 is the final chapter of the thesis and presents conclusion and future work.

### Chapter 2

# A Design Methodology and Flow with Emphasis on Scheduling for Automotive Systems

The definition of a car electronic/software system starts from the specification of the set of features, a very high level description of a system capability, that the system is expected to provide.

Functional models are created from the decomposition of the features in a hierarchical network of component blocks. The physical architecture model captures the topology of the car network, including the communication buses, the CPUs and the management policies that control the shared resources.

The design evolution led to the development of a system design methodology, Platform Based Design (PBD) that was proven successful in several automotive industrial problems. Section 2.1 presents the PBD methodology, and then Section 2.2 discusses a design flow under the PBD. In Section 2.2, functional models, architectural models and system models are introduced first, and then a full discussion over mapping and scheduling is conducted.

#### 2.1 Platform Based Design Methodology Introduction

According to the principles of PBD, system-level architecture design is neither a top-down nor a bottom-up design methodology. Rather, it is a meet-in-the-middle approach [35]. In a pure top-down design process, the specification of the application functionality is the starting point for the design process. The sequence of design decisions drives the designer toward a solution that minimizes the cost of the architecture. The design process selects the most attractive solution as defined by a cost function. In a bottom-up approach, a given execution architecture is designed to support a set of different applications and is, in general, developed based on designers intuition and marketing inputs.

The two main concerns of functional and architectural specification are connected by mapping a high level specification, defining an abstract model of the system, to a particular software and hardware architecture or platform. This match between function and architecture is a key aspect of the design of embedded systems and the founding principle of many design methodologies such as the platform-based design [4] and tools such as the former VCC/Sysdesign Sysdesign [54] product by Cadence, the Ptolemy and Metropolis frameworks [5].

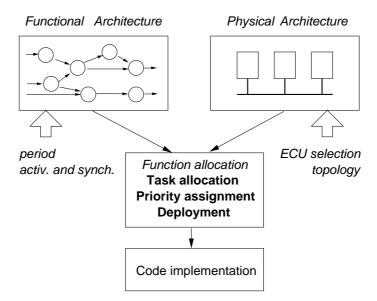

The use of the conceptual framework of the platform-based design methodology and the meet-in-the-middle approach are advocated as key enablers for the exploration of design alternatives and architecture level solutions. Platform-based design requires the identification of clear abstraction layers and a design interface that allows for the separation of concerns between the refine-

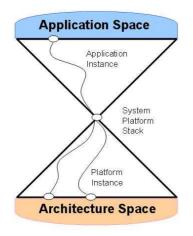

Figure 2.1: Platform Based Design.

ment of the functional architecture specification and the abstractions of possible implementations. Thus in automotive electronic design the application-layer software components are decoupled from changes in micro-controller hardware, ECU hardware, I/O devices, sensors, actuators, communication links, and from the partitioning of the software to the computing nodes. What specific layers should be used depends largely on the application space. For example, in typical automotive electronic applications, it may be sufficient to identify the architecture that one wants to target, then, the source code may be recompiled on various hardware architectures.

The basic idea of the PBD is captured in Figure 2.1. The vertex of the two cones represents the combination of the functional model and the architecture platform. System designers map their applications into the abstract representation that includes a family of architectures that can be chosen to optimize cost, efficiency, energy consumption, reliability and flexibility (timing in this thesis). Decoupling the application-layer logic from dependencies on infrastructure-layer hardware or software enables the application-layer software components to be reused without changes across

multiple vehicle programs over a period of years.

Design space exploration consists of seeking the optimal mapping of the system plat22 form model into the candidate execution platform instances, the mapping must be driven by a set of methods and tools providing an objective and quantitative measure of the fitness of the architecture solutions with respect to a set of constraints and metric functions. The bigger is the gap between two neighboring abstraction levels, the larger is the potential for design optimization and exploration and the greater is the effort that is required to explore the mapping options. Ideally, there could be the possibility for automatic selection of the platform by appropriate software tools. In reality, the technology is not mature for a full synthesis of the mapping and the platform attributes and the approach that is currently viable is a what-if analysis where different options are selected as representatives of the principal platform options and evaluated according to measurable metric functions. Complex automotive systems are also implemented by integrating components provided (implemented) by suppliers. Today, the integration of a subsystem provided by a supplier relies on a black-box specification of the interface messages, including the priorities and possibly the execution rates.

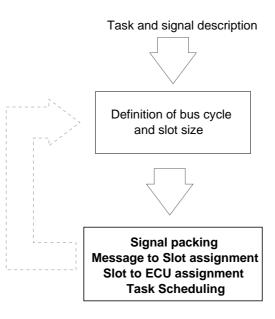

## 2.2 A Design Flow with Emphasis on Scheduling for Automotive Systems

Section 2.1 introduced the concept on design space exploration which is a process of seeking an "optimal" mapping from functionalities to architectures. The mapping is driven by a set of optimization metric functions to evaluate the fitness of the architecture solutions. Through this thesis, the optimization metrics chosen to evaluate the mapping result are timing, in another

word, different timing metrics are used as a guidance to the whole design flow when marrying functionalities to architectures.

Giving the mapping of software modules to hardware components, the design flow turns to focus on the scheduling of functionalities within the chosen architectures. Separating the ideas of mapping and scheduling is a critical assumption as for the cost function that decides the software mapping is orthogonal from the cost function that determines the task and bus message schedule by many auto-designers. [81] describes a methodology that optimizes this mapping by minimizing bus bandwidth and interconnect cost, hence validating this assumption. However, in an idealistic scenario these concerns cannot be separated in order to achieve a global optimal solution and must be accounted for through a multidimensional optimization problem. Nevertheless, in practice the industrial experience is that managing complexity is a key requirement and the approach of orthogonalizing the concern of software to hardware mapping and scheduling is a realistic assumption within the automotive domain. In this thesis, the texts focus on the scheduling part of the whole design flow.

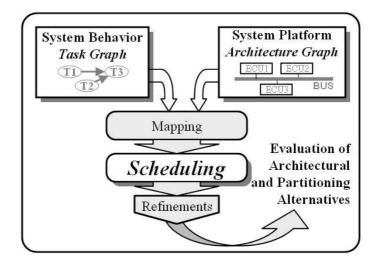

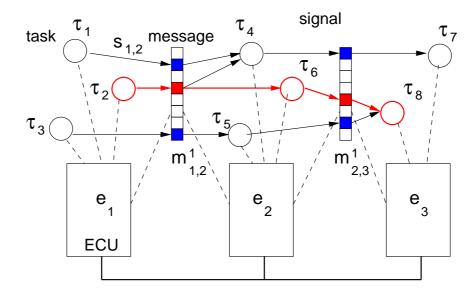

Aside from the orthogonalization of mapping and scheduling, orthogonalizing functions and architectures[36] is also expected by the designers. In such a system development process, a functional description is defined first, then it is mapped onto some set of virtual architectural components. Generally, the above mapping obtains two or three potential solutions. The metrics related to timing such as end-to-end latency, among other performance analysis metrics, are used to obtain an optimized schedule or post-mapping system parameters, and select a potential solution (see figure 2.2).

Functional model, architecture model, system platform model, and the mapping, schedul-

Figure 2.2: System design flow.

ing design phases are introduced one by one in the following sub-sections.

#### 2.2.1 Functional Models

The starting point for the definition of a car electronic system is the specification of the set of features that the system is expected to provide. A feature is a very high level description of a system capability. The brake pedal force emulator in a brake-by-wire system is an example of a feature, consisting of mechanical, electronic and software parts that together emulate the feel of the conventional hydraulic brake pedal.

The software components of each feature are further developed by control engineers who devise control algorithms fulfilling the design goals. Typically, these algorithms consist of complex mathematical operations that are captured by a hierarchical set of block diagrams produced with tools such as Matlab Simulink.

The functional models are created from the decomposition of the feature in a network

of component blocks by abstracting the information that is relevant for the purpose of architecture exploration. The resulting model of the functionality is a hierarchical network of components encapsulating the system behaviors, with provided and required interfaces expressed by a set of ports. In the definition of the vehicle functionality, there is a need to work with a system view that abstracts from the details of the functional behavior and models only the interface and the communication semantics.

To give an example, some of the definitions that apply to the entities of the functional models are: 1. The activation mode of the functional blocks, synchronized on some clock or activated by the arrival event of a signal on one of the incoming ports. 2. The possible precedence constraints in the execution of the functional blocks. Whenever specified, the precedence constraints can be of type AND (all input signals must arrive before a block can execute) or of type OR (the block execution is triggered by the arrival of any of its input signals) 3. The semantics of the signal variables can be of type sticky with overwriting, meaning that the variable preserves the last value that has been written into it and the value of the signal variable is overwritten by a new output, or a signal link can represent a queue of tokens that are produced by the sender block and consumed by the receiver block. An example of the implications of a choice of an activation/communication model, the data communication between any two blocks activated periodically according to local, non synchronized clocks, is assumed to be nondeterministic in time and lossy, meaning that output values may be overwritten before having been read.

Timing constraints are expressed in the context of the functional graph by adding end-toend deadlines to the computation paths, maximum jitter requirements to any signal and time correlation constraints between any signal pair originating from the same functional block or providing input (possibly after further processing) to a common block, that is, having a common ancestor or successor block. A more detailed description of the fundamental concepts of end-to-end latency on a given computation path, and the corresponding deadline is however required for understanding the analysis procedures and the trade-offs in the design.

A path in the functional model is a set of functional blocks. Informally, the end-to-end latency is the largest possible time interval that is required for the change of the environment to be captured as input by the first block and propagated to the end of the chain, whatever is the state of the blocks in the path and regardless of the fact that some intermediate result may be overwritten before it is read. To understand the significance of this definition, please think of a feature like advanced collision preparation (ACP) where the environment variable models the existence of a target object on a collision route and the ending value which is the braking torque that is applied on the brake actuators.

Overall, the functional model considered in this thesis is usually represented by a directed acyclic graph (DAG) which has a network of components/tasks communicating with each other by exchanging messages.

#### 2.2.2 Architecture Models

The model of the architecture is hierarchical and captures the logical topology of the car network, including the communication busses such as CAN and FlexRay links, the number of processors for each ECU and the resource management policies that control the allocation of each ECU and bus, but also the physical and geometric relationships, including abstractions for modeling wiring harnesses and connectors. At this stage, the hardware and software resources that are available for the execution of the application tasks and the resource allocation and scheduling

policies must also be specified. Each RTOS provides a set of services and logical resources and has a set of parameters related to the provided scheduling policy for the ECUs.

The physical model also defines entities of the physical architecture that determine its cost, including connectors and harnesses and their connectivity, ECU and ECU multiplexed buses with the associated controllers and ASICs memory, and the pin-out information for each ECU.

#### 2.2.3 System Platform Model

If specification of functionality aims at producing a logically correct representation of system behavior, the system platform model is where physical concurrency and resource requirements are expressed. At this level, rather than applying the term process or thread - although widely used in the literature - to describe a unit of computation processed concurrently in response to environment stimuli or prompted by an internal clock, the term task will be used in adherence with OSEK. Tasks cooperate by exchanging messages and synchronization or activation signals and contend for use of the execution resources (the processors) as well as for the other resources in the system. The system platform model entities must, on one hand, be the implementation of the functional model entities and are, on the other hand, mapped onto the target hardware.

The system platform models are a synthesis of the mapping process and can be of different types for different analysis purposes, hiding unnecessary details and exporting only the necessary amount of information. Throughout the thesis, two models are investigated:

The first model is simple. In this model, all tasks and messages are activated periodically and communicate according to a semantics where the communication channel holds the last value that is written into it and it is implemented as a shared variable protected against concurrent access. This model, called periodic activation model, has many advantages, including the separation of concerns when evaluating the schedulability of the individual resources and also allows for a very simple specification at the interface of each subsystem or component, thereby simplifying the interaction with the suppliers. The drawback is a non-deterministic time behavior and a possibly very large worst-case end-to-end delay in all computations that are performed according to this model.

The next model includes the possibility of activating messages and tasks based on some event, typically the completion of a task or the change in the value of a signal. The corresponding models, are called on-demand activation and on-event activation. In this case, the completion of a task always results in the immediate enqueuing (or activation) of all the messages that send information produced by the task and the arrival of a message results in the activation of the receiver task.

This model corresponds to an implementation in which, for example, the middleware software layers enqueue a new message whenever a task completes its execution and produced a value for one of its outgoing signals (not necessarily different from the value produced in its previous execution instance) and where the arrival of a message results in the execution of an interrupt handler activating the software task that processes the message data. In the terminology in use among operating system developers and programmers, this model is commonly defined as interrupt driven.

Finally, the most general platform models allow for an arbitrary combination of the previous message and task activation semantics, subject to a few coherency rules. Chapter 4 discusses this in a detailed manner.

#### 2.2.4 Mapping

The mapping of the blocks defined in the functional model into system platform entities and the subsequent placement of those onto the physical architecture objects are the critical design activities. In practice, the blocks defined in the functional part must be executed in the context of one or more system tasks with their attributes. The mapping of the threads and message model into the corresponding architecture model and the selection of resource management policies allows the subsequent validation of the mapped model against functional and non-functional constraints.

The mapping phase consists of allocating each functional block to a software task and each communication signal variable to a virtual communication object. The task activation rates must be entered as parameters of the architectural models and compliance checks are performed with the functional blocks activation rates. If more than one functional block is mapped to a task, the order of the execution must be provided during the mapping phase.

As a result of the mapping of the platform model into the execution architecture, the entities in the functional models are put in relation with timing execution information derived by worst (best) case execution time analysis (not provided directly by the environment) or back-annotations extracted from physical or virtual implementation. In the latter case, several execution timing information are maintained such as best, worst, mean, and distribution.

Given the deployment, it is possible to determine which signals are local (because the source and destination functions are deployed onto the same ECU) and which are remote, hence need to be packed into messages and go over the network. Each communication signal variable is therefore mapped to a communication resource of the implementation, that is, a message, or a tasks private variable or a protected shared variable. Each message, in turn, is mapped to a serial data link, and the mapping relation can be extended by mapping serial data links to harnesses, and harnesses to physical locations in the car.

When mapping a functional model into a platform model, the semantics of the functional

description should be preserved. Therefore, not all the mappings are allowed or should be made legal. For example, a non-deterministic communication among two functional blocks can be made deterministic, and a global execution order for all the functional blocks can be defined, after mapping them into the task set, in accordance with the partial order defined by the semantics of the functional model. However, a mapping of a communication signal with an attached precedence relation to a communication variable shared among two periodic asynchronously activated tasks should not be possible.

#### 2.2.5 Scheduling

When the mapping is done, tasks executing on a computing resource like a ECU with a necessarily finite execution time, additional definitions must be provided, and the same to the messages transmitted on the bus. Each instance of a periodic functional tasks or a message, the release time, start time and finish time associated with each of them are defined. Also the worst case response time for each scheduling entity is needed to calculate clearly.

To obtain a better (less pessimistic) estimate of the timing and reliability properties, the modeling allows the capturing of different configurations in terms of functional, architectural, mapping and timing information of the system: these different configurations are captured as system modes. This analysis only focus on identifying the system modes that result in significant differences in the timing behavior of the system. For example, some engine control functions may be executed at a rate that depends on the engine rotation speed and at high rates, the definition of the function can change (to a simplified implementation) in order to ease the schedulability of the system.

Classification of real time system scheduling could be based on:

#### 1. Input

- 2. Criticality of timing constraints

- 3. The nature of the real time load

Scheduling based on input could be either time-driven or event-driven. If the input is continuous (synchronous), it is time-driven while if the input is discontinuous (asynchronous), then it is event-driven.

Scheduling based on criticality of timing constraints could be hard real time scheduling if the response of the system within the timing constraints is crucial for correct behavior or could be soft real time scheduling if the response of the system within the timing constraints increases the value of the system.

Scheduling based on the nature of the real time load could be static scheduling when the load is predefined, constant and deterministic or could be dynamic when the load is variable (non-deterministic).

A real world system exhibits a combination of these characteristics, for instance, the example in Section 1.4 could be an event-driven, hard real time and static scheduling case.

The scheduling also must be driven by a set of methods and tools providing an objective and quantitative measure of the fitness of the architecture solutions with respect to a set of constraints and metric functions. End to end latencies on selected paths provide us a good metric for evaluating a scheduling result.

Modern automotive architectures support the execution of distributed safety- and timecritical, or at least time-sensitive functions on complex networked systems with several buses and tens of ECUs. Schedulability theory provides support for the analysis of the worst case latencies in distributed computations when the architecture of the system is known and the communication and synchronization mechanisms have been defined. In the design of complex automotive systems, however, a great benefit of schedulability analysis may come from its use as an aid in the exploration of the software architecture configurations that can best support the target application.

The thesis presents several optimization frameworks to select the communication and synchronization model that leverages the trade-offs between the purely periodic and the precedence constrained data-driven activation models in the scheduling phase of the design flow. The problem is amenable to an ILP formulation and to solution based on a standard solver. Formalization of the problem is provided at different levels of approximation and shows what is the result of the optimization on a case study consisting of a complex automotive architecture. The complexity in terms of running time is estimated by evaluating derivatives of the case study with different levels of concurrency and resource utilization.

In addition to the introduction and review for distributed embedded system, this chapter presented the design methodology (Platform Based Design methodology) the thesis based on and discussed the research focus, the scheduling part, within the design flow in automotive electronic system design.

### Chapter 3

# Scheduling for Time-Triggered Communication System

In automotive systems, computation and communication functions can be time- or eventtriggered. In the first case, task activations and message transmissions are bound to happen at predefined points in time. Considering that the development of a modern automotive system is most of time communication intensive, this chapter is dedicated to talking about scheduling synthesis for time-triggered automotive communication system. The structure of this chapter is as follows: all preliminaries and definitions related to **Time-Triggered Communication System** are presented in Section 3.1, followed by Section 3.2 where scheduling synthesis for a FlexRay based communication system in an optimization framework is described, finally scheduling synthesis in an incremental design framework for a general time-triggered system is discussed in Section 3.3.

## 3.1 Preliminaries and Definitions for Time-Triggered Communication System

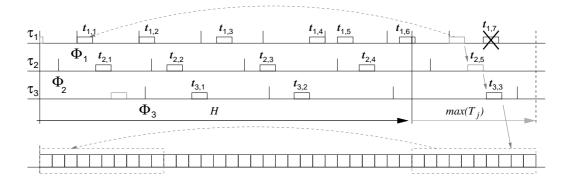

Time-triggered communication system is supported by protocols that schedule the messages statically based on tables that define the time points when messages need to be transmitted. This section gives an overview about time-triggered communication protocols with a focus on FlexRay, Section 3.1.2 then provides previous related work especially on FlexRay. System modeling and description are introduced in Section 3.1.3.

#### 3.1.1 Time-Triggered Protocols Overview

Supporting for time-triggered communication is provided by protocols that schedule the messages statically based on local scheduling tables that define the messages transmission time. SAFEbus [31], SPIDER [61], TTCAN [3], and the Time-Triggered Protocol (TTP) [40] are examples. TTP uses a generalized time-division multiple-access (GTDMA) scheme with variable sized slots, in which each node has only one opportunity to transmit for each cycle. In FlexRay, slots have the same size, but a node can have more than one transmission opportunity for each cycle. Scheduling techniques for the static segment have been developed by extending the work for scheduling messages in a TDMA bus [59] [29]. In [21], the authors consider the case of a hard real-time application implemented on a system with a FlexRay bus. Messages are scheduled in the static segment, and the method in practice reuses scheduling techniques developed for the TDMA bus.

#### 3.1.1.1 FlexRay Introduction

The development of new by-wire functions with stringent requirements for determinism and short latencies, and the upcoming active safety functions, characterized by large volumes of data traffic, generated by 360<sup>0</sup> sensors positioned around the vehicles, are among the motivations for the definition of the FlexRay standard. FlexRay is being developed by a consortium (www.flexray.org) that includes a few core members, namely, BMW, Daimler-Benz, General Motors, Freescale, NXP, Bosch and Volkswagen/Audi, as a new communication standard for highly deterministic and high speed communication. The stated objective is to support cost-effective deployment of distributed by-wire controls.

At the core of the FlexRay system is the FlexRay communications protocol. The protocol provides flexibility and determinism by combining a scalable static and dynamic message transmission, incorporating the advantages of familiar synchronous and asynchronous protocols. The communication channel is a broadcast channel. A message sent to the channel by a ECU is received by all the other ECUs. Application messages are usually scheduled through the static segment of FlexRay bus in order to ensure the timing constraints are satisfied.

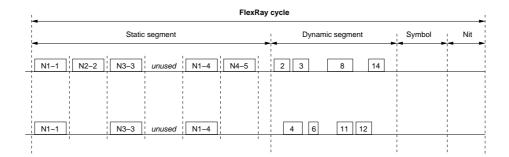

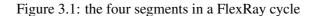

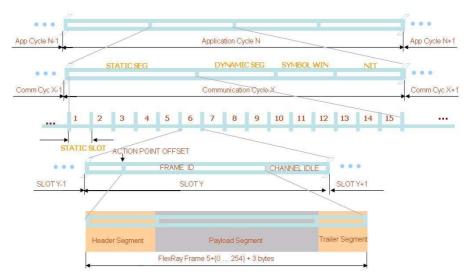

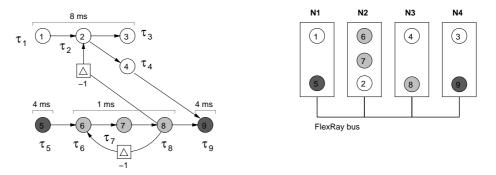

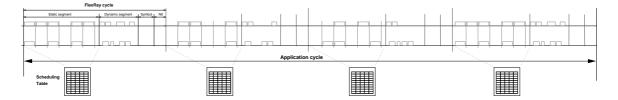

In FlexRay, the communication speed is defined at 10 Mb/s, although determination of the minimum bit-time that is necessary to ensure correct detection of the bit value in spite of delay jitter might suggest additional versions at lower speeds. The bus bandwidth is assigned according to a time-triggered pattern. The available bandwidth is divided into communication cycles and each communication cycle contains up to four segments (Static, Dynamic, Symbol and Network idle time - Nit, as in Figure 3.1). Figure 3.2 shows more details of the timing hierarchy of a FlexRay system. Clock synchronization for the purpose of communication is embedded in the standard

Figure 3.2: FlexRay Timing Hierarchy.

using part of the Nit segment, and therefore comes at no additional cost. This ensures deterministic communications at least from the theoretical standpoint.

The static part of the communication cycle enables the transmission of time critical messages according to a periodic cycle, in which a time slot, of fixed length and in a given position in the cycle, is always reserved to the same node. The dynamic segment allows for flexible communications. Transmission of messages in the dynamic part is arbitrated by identifier priority (the lowest identifier messages are transmitted first, somewhat like in CAN but in a slightly different way). FlexRay includes a dual channel bus specification (for increased reliability) and will include (in its upcoming specification) bus guardians at the node and star level for increased reliability and timing protection. In a dual channel configuration, messages can be replicated on both channels for safety critical communications that leverage the physical redundancy, or the slots can be assigned independently. In the latter case, the communication bandwidth is doubled.

The time-triggered model of FlexRay, not only allows for time determinism, but is also considered as a paradigm for composability and extensibility. Each node only needs to know the time slots for its outgoing and incoming communications. The specification of these time slots is kept in local scheduling tables. No global description exists and each node executes with respect to its own (synchronized) clock. As long as the local tables are kept consistent, no timing conflicts or interferences arise.

Slots that are left free in the (virtual) global table resulting from the composition of the local tables can be used for future extensions. Time protection and isolation from timing faults are guaranteed by the reservation of time slots and guardians that avoid that node transmit outside the allocated time window as stated in the original specification.

The bus cycle time and the transmission slot time are design parameters that should be carefully selected. Fundamental issues related to the composition of subsystems, but also to future extensibility and reuse of components require careful planning and possibly standardization of the approach.

Clock synchronization and time determinism on the communication channel allow the implementation of end-to-end computations in which the data generation, data consumption and communication processes are temporally aligned, avoiding sampling delays, and therefore removing

the worst drawback of composable periodic activation semantics, that is lateness, in exchange of determinism.

Also, system-level time-triggered schedules allow the semantics-preserving implementation of distributed control models (including models with a synchronous reactive semantics, like those produced by popular commercial tools like Simulink from Mathworks [44]).

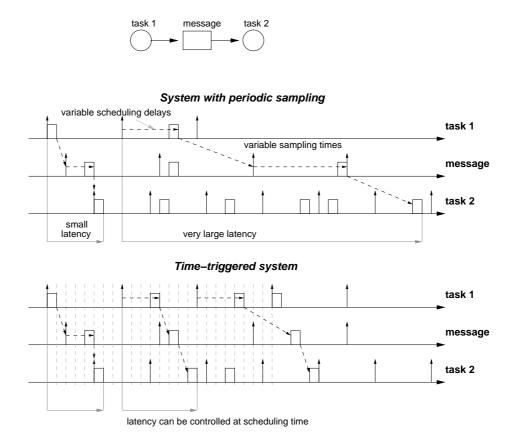

Time determinism requires that the time-triggered model of communication is propagated to the computation layers, using a time-triggered scheduler and a careful coordination of the communication and computation schedules, so that the schedule becomes global. If the schedulers are not coordinated, then not only guaranteeing time determinism is more difficult and probably altogether impossible, but the performance of the system in terms of latency is significantly worse. The synchronization of the communication and RTOS layers is only scantly addressed by current standards.

#### 3.1.1.2 Time-Triggered Protocol (TTP) Introduction

According to [22] TTP is a real-time protocol of the Time-Triggered Architecture (TTA). The protocol uses a Time-Division Multiple Access (TDMA) scheme to enable collision-free bus allocation. TTP focuses on the interconnection of components in order to form a highly dependable realtime system that is sufficient for critical applications such as X-by-wire in the automotive and avionics domains. TTP implements a replicated bus system and a guardian that prevents babbling idiot failures.