# **Practical Fault Tolerance for Quantum Circuits**

Mark Whitney

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-80 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-80.html

May 21, 2009

Copyright 2009, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Practical Fault Tolerance for Quantum Circuits

by

Mark Gregory Whitney

B.S. (University of California, Berkeley) 2000 M.S. (University of California, Berkeley) 2006

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

in the

Graduate Division of the University of California, Berkeley

Committee in charge:

Professor John D. Kubiatowicz, Chair Professor Sanjit A. Seshia Professor K. Birgitta Whaley

Spring 2009

The dissertation of Mark Gregory Whitney is approved:

Chair

Date

Date

Date

University of California, Berkeley

## Practical Fault Tolerance for Quantum Circuits

Copyright 2009 by Mark Gregory Whitney

### Abstract

Practical Fault Tolerance for Quantum Circuits

by

Mark Gregory Whitney Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor John D. Kubiatowicz, Chair

Due to very high projected error rates, large scale quantum computers will require substantial fault tolerance just to maintain a minimum level of reliability. We present tools to better analyze the performance of large, fault tolerant quantum computer designs. We find that current uses of quantum error correction are overly conservative in mitigating the impact of gate errors and negligent of other error sources in quantum data communication and memory.

We have developed circuit layout heuristics to generate detailed designs in trapped ion quantum computing technology. From these designs, we can extract much more accurate error models for a given application, including all gate, movement and idle errors on qubits. Using these extracted models, our flexible error simulation environment determines the overall failure probability of the design. Included in this simulation environment is a bit-parallel Monte Carlo technique that is 10 times faster than previous fault propagation simulations. This allows us to evaluate the reliability of designs that are an order of magnitude larger, in the same amount of time.

Using this analysis framework to verify reliability, we have developed a linear programming-based optimization for error correction which decreases overall circuit resources by an order of magnitude. In some cases, our optimization actually improves overall system reliability by removing error correction. We combine this optimization with judicious quantum error correcting code selection to provide efficient designs for large quantum arithmetic kernels used in Shor's factorization algorithm. We show our optimized designs perform 2x to 100x better than previous works in terms of probabilistic area-delay product. Additionally, the area of our layout of a 1024-bit factoring using Shor's algorithm is  $64cm^2$ , a substantial improvement compared to the  $0.9m^2$  state-of-the-art design from prior work. A design size reduction by this amount will make fabricating such an application feasible much sooner.

Professor John D. Kubiatowicz Dissertation Committee Chair Dedicated to my wife and parents for their patience.

# Contents

| $\mathbf{Li}$ | List of Figures vi |                                                      |    |

|---------------|--------------------|------------------------------------------------------|----|

| Li            | List of Tables xv  |                                                      |    |

| 1             | Intr               | oduction                                             | 1  |

|               | 1.1                | Quantum Circuits                                     | 5  |

|               |                    | 1.1.1 Universal Gates                                | 6  |

|               |                    | 1.1.2 Quantum Decoherence                            | 7  |

|               | 1.2                | Quantum Errors and Error Control                     | 8  |

|               |                    | 1.2.1 Error Correcting Codes                         | 10 |

|               |                    | 1.2.2 Fault Tolerance                                | 16 |

|               |                    | 1.2.3 Noise Threshold Theorems                       | 19 |

|               |                    | 1.2.4 Communication                                  | 20 |

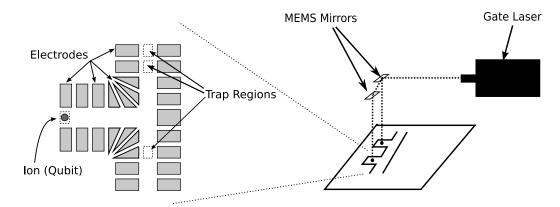

|               | 1.3                | Quantum Computing Technologies                       | 22 |

|               |                    | 1.3.1 Ion Traps at a Glance                          | 22 |

|               |                    | 1.3.2 Trap Electrodes                                | 24 |

|               |                    | 1.3.3 Gate Lasers                                    | 25 |

|               |                    | 1.3.4 Measurement                                    | 26 |

|               |                    | 1.3.5 Noise model                                    | 26 |

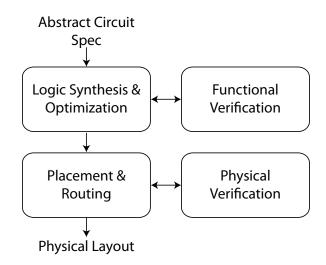

|               | 1.4                | Classical Computer Aided Design Flows                | 27 |

|               |                    | 1.4.1 Logic Synthesis and Optimization               | 28 |

|               |                    | 1.4.2 Functional Verification                        | 29 |

|               |                    | 1.4.3 Placement and Routing                          | 29 |

|               |                    | 1.4.4 Physical Verification                          | 29 |

|               |                    | 1.4.5 Metrics                                        | 29 |

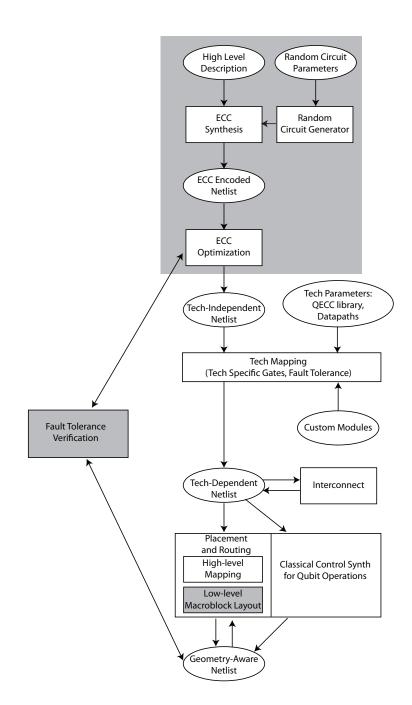

| <b>2</b>      | Ove                | view of Computer Aided Design for Quantum Circuits   | 31 |

|               | 2.1                | Application Circuit Specification and Representation | 34 |

|               | 2.2                | Quantum Logic Synthesis                              | 41 |

|               |                    | 2.2.1 Technology Dependent Gates                     | 42 |

|               |                    | 2.2.2 Fault Tolerant Gate Constructions              | 43 |

|               |                    | 2.2.3 Random Circuit Generation                      | 43 |

|               | 2.3                | Error Correction Circuit Optimization                | 44 |

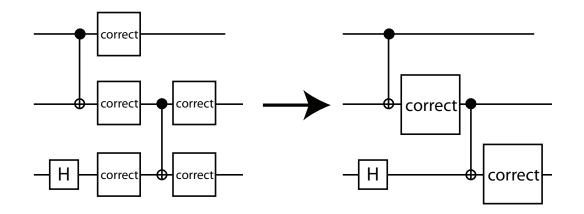

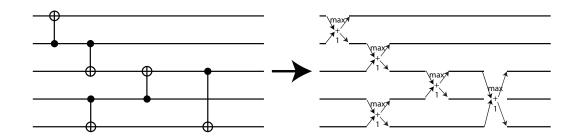

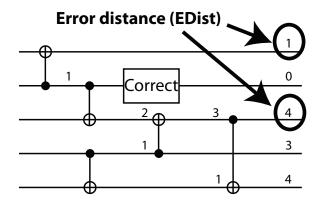

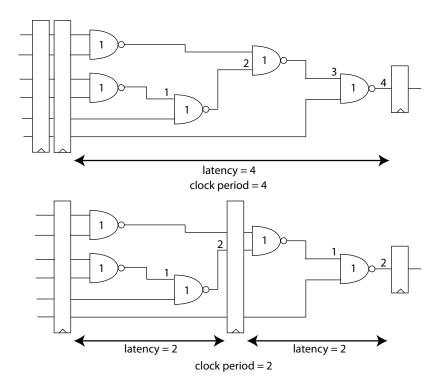

|   |     | 2.3.1 Retiming Based Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.4 | Datapath Microarchitectures 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |     | 2.4.1 Three Major Organizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |     | 2.4.2 An Organizational Zoo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |     | 2.4.3 Coarse-Grained Mapping and Floorplanning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

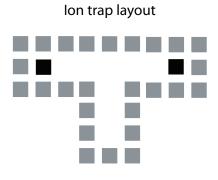

|   | 2.5 | Ion Trap Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | -   | 2.5.1 Fine-Grained Element Place and Route                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

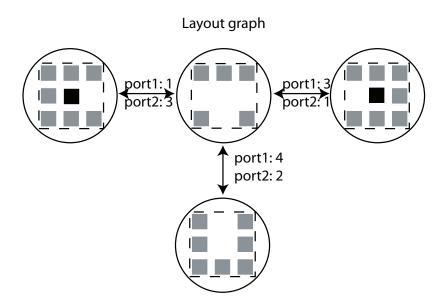

|   |     | 2.5.2 Layout Graph Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

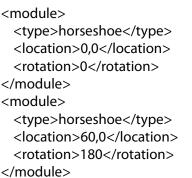

|   |     | 2.5.2         Layout Oraph Representation         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <t< td=""></t<> |

|   | 2.6 | Fault Tolerance Verification   53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 2.0 | 2.6.1 Determining Failure Probability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |     | 2.6.2       Hybrid Fault Point Extraction       53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |     | 2.6.3       Accuracy-Time Tradeoffs       53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |     | 2.6.4       Fault Tolerance Metrics       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |     | 2.6.5       Feedback for Further Optimization       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 2.7 | ADCR: An Aggregate Metric for Probabilistic Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 2.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |     | 2.7.1 ADCR-optimal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3 | Con | nmunication in Quantum Circuits 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| - | 3.1 | Analytical Estimation of Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

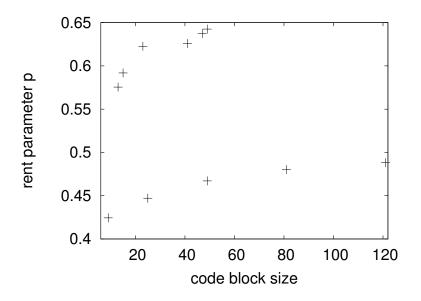

|   | -   | 3.1.1 Rent's Rule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |     | 3.1.2 Donath's Wire Length Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 3.2 | Macroblock Layout Heuristics and Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 0   | 3.2.1 Greedy Place and Route                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |     | 3.2.2 Dataflow-Based Layouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |     | 3.2.3 Simulated Annealing Module Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |     | 3.2.4 Manual Layouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

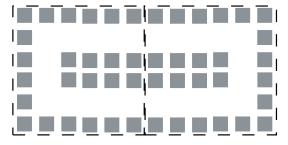

|   |     | 3.2.5 Grid-based Layouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 3.3 | Layout Performance   88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 0.0 | 3.3.1 Latency and Area Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

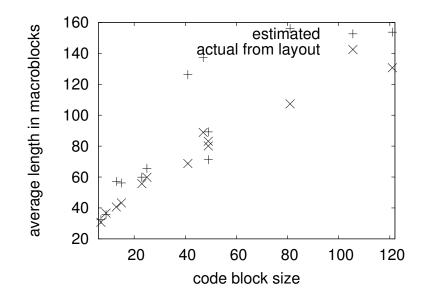

|   |     | 3.3.2 Validating Layouts with Donath's Estimate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 3.4 | Coarse Grained Mapping and Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 0.1 | 3.4.1 Tiled Microarchitectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

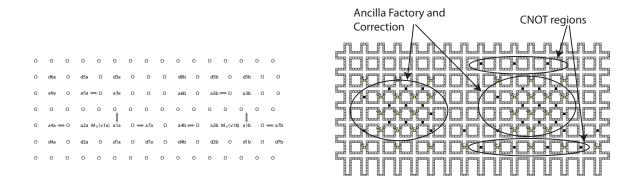

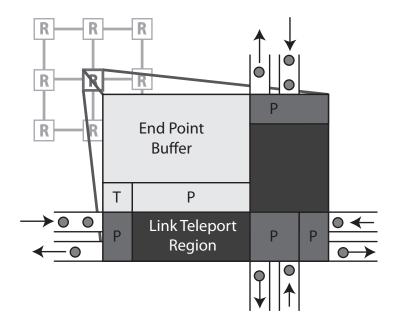

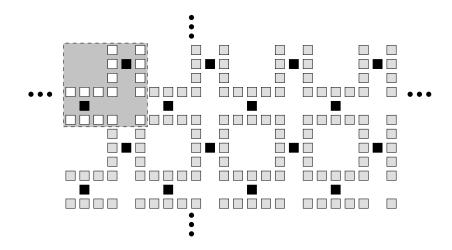

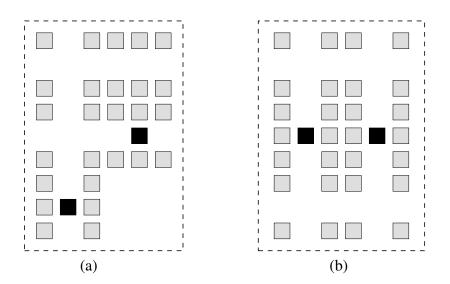

|   |     | 3.4.2 Qalypso and LQLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

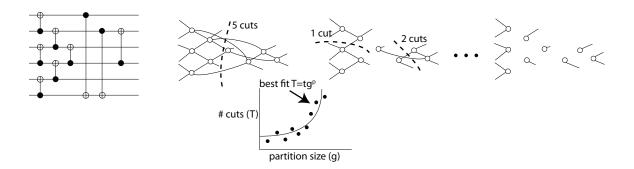

|   |     | 3.4.3 Partitioning the Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |     | <b>5.4.5</b> I at thioning the Oncurt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4 | Fau | It Tolerance Verification 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.1 | Fidelity-Based Error Estimates 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |     | 4.1.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |     | 4.1.2 Communication Fidelity Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 4.2 | General Pauli Error Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |     | 4.2.1 Gate Error Propagation Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

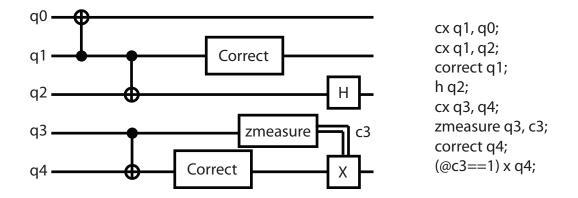

|   | 4.3 | Errors and Classical Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 1.0 | 4.3.1 Qubit Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |     | 4.3.2 Qubit Corrections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |      | 4.3.3 Predicated Quantum Operations                                                                                                     |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------|

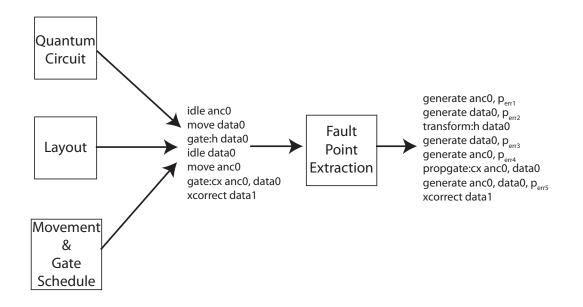

|          | 4.4  | Fault Point Streams    100                                                                                                              |

|          | 4.5  | Joint and Marginal Probabilities of Failure                                                                                             |

|          |      | 4.5.1 Previous Work: QubitSets                                                                                                          |

|          |      | 4.5.2 Joint Probability Evolution                                                                                                       |

|          |      | 4.5.3 Approximating Joint Probability                                                                                                   |

|          | 4.6  | Monte Carlo Simulation                                                                                                                  |

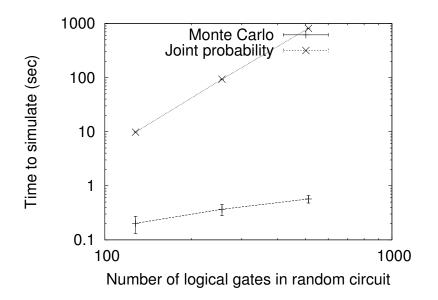

|          |      | 4.6.1 Performance                                                                                                                       |

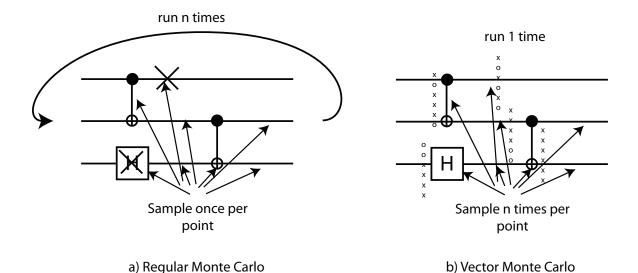

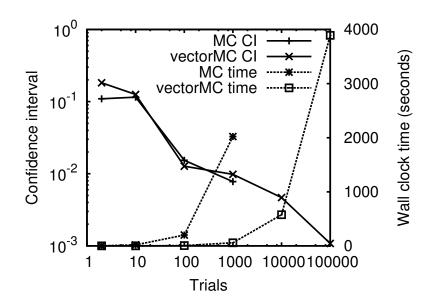

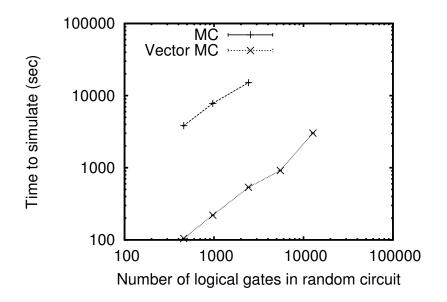

|          | 4.7  | Vectorized Monte Carlo 12                                                                                                               |

|          | 4.8  | Ion Trap Movement and Idle Error Models                                                                                                 |

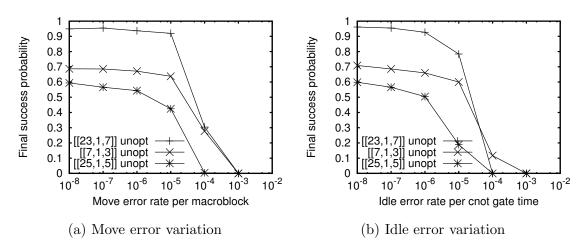

|          |      | 4.8.1 Movement Error                                                                                                                    |

|          |      | 4.8.2 Idle Error                                                                                                                        |

|          |      | 4.8.3 Example Movement/Idle Models                                                                                                      |

|          | 4.9  | Hybrid Error Modeling                                                                                                                   |

|          |      | 4.9.1 Error Streams from Layout Pieces                                                                                                  |

|          |      | 4.9.2 Putting the Pieces Together                                                                                                       |

| <b>5</b> | Erre | or Analysis for Codes and Communication 13                                                                                              |

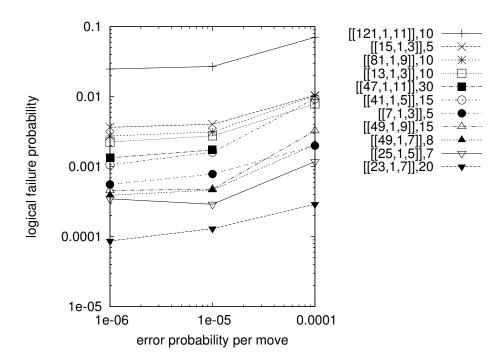

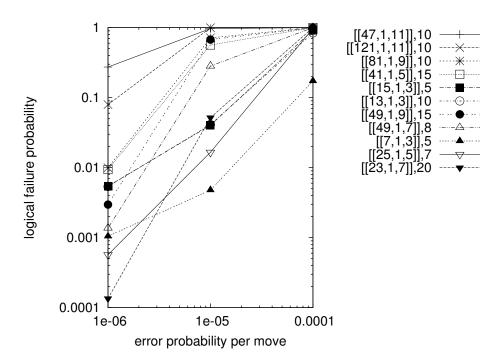

|          | 5.1  | Comparison of Failures in Codes 13                                                                                                      |

|          |      | 5.1.1 QECC Choices and Benchmark Circuits                                                                                               |

|          |      | 5.1.2 Evaluation Flow $\ldots \ldots 14$            |

|          | 5.2  | Comparing Code Pseudo-Thresholds                                                                                                        |

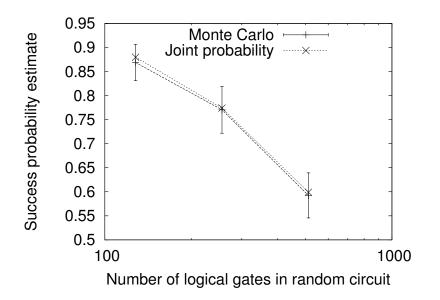

|          |      | 5.2.1 Code Performance on Random Circuits                                                                                               |

|          |      | 5.2.2 Which code is best? $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $14$                                                             |

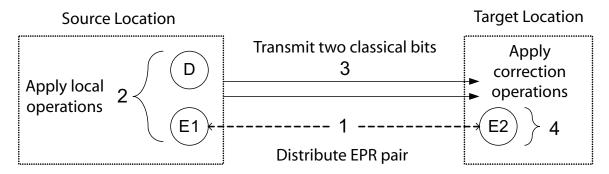

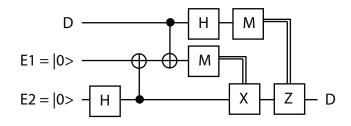

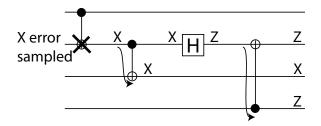

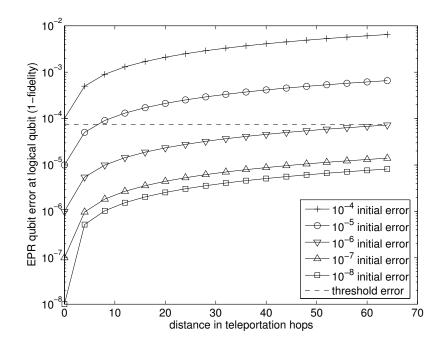

|          | 5.3  | Analysis of Teleportation Interconnect                                                                                                  |

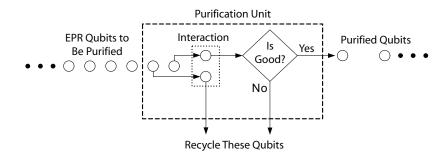

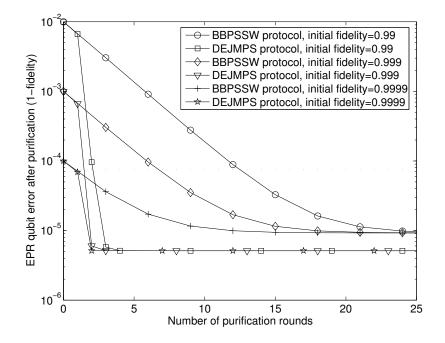

|          | 5.4  | EPR Purification Model                                                                                                                  |

|          | 5.5  | Teleportation Network Fidelity Analysis                                                                                                 |

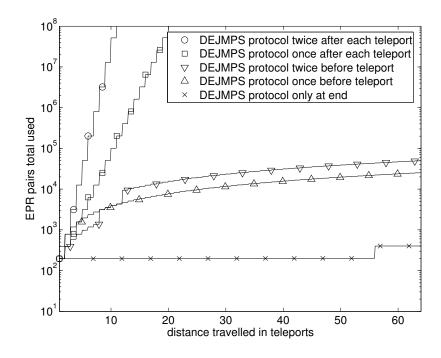

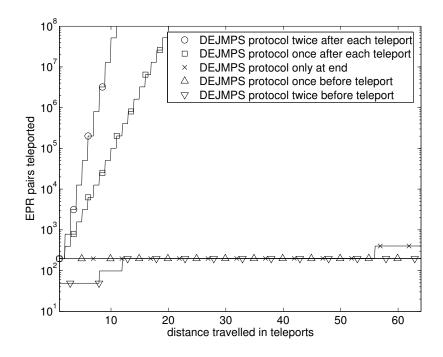

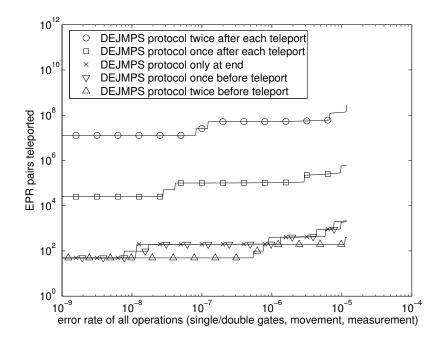

|          |      | 5.5.1 Purification Resources                                                                                                            |

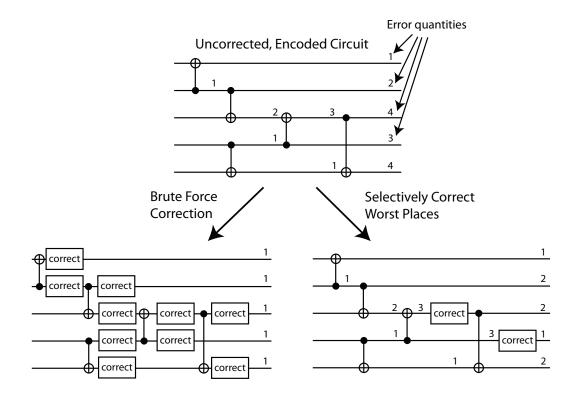

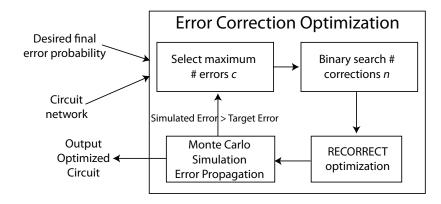

| 6        | Opt  | imization of Fault Tolerant Circuits 150                                                                                                |

|          | 6.1  | Error Correction Placement                                                                                                              |

|          | 6.2  | Fault Counting Model                                                                                                                    |

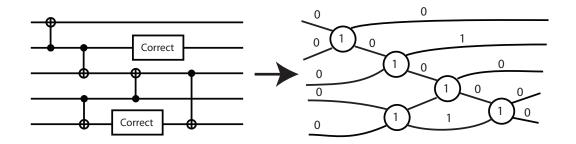

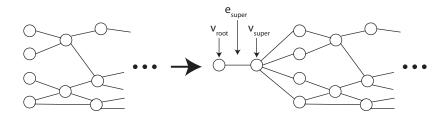

|          | 6.3  | Retiming for EC Placement in Circuits                                                                                                   |

|          |      | 6.3.1 Classical Circuit Retiming                                                                                                        |

|          |      | 6.3.2 Transforming Latency Retiming to Error Recorrecting                                                                               |

|          |      | 6.3.3 Formal Definition of Recorrection                                                                                                 |

|          |      | 6.3.4 Recorrection and Real Error Probability                                                                                           |

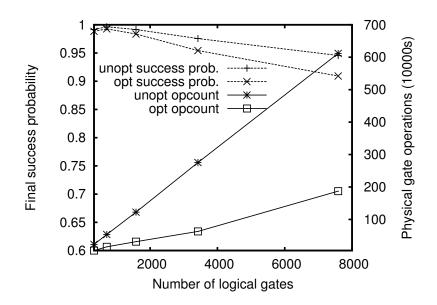

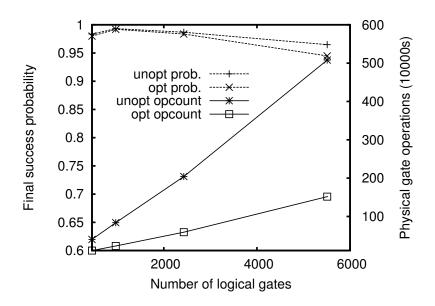

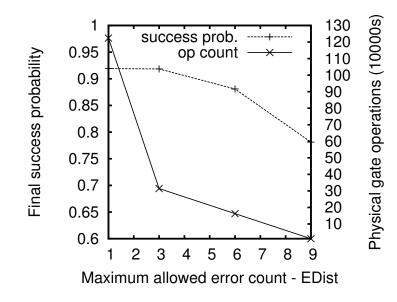

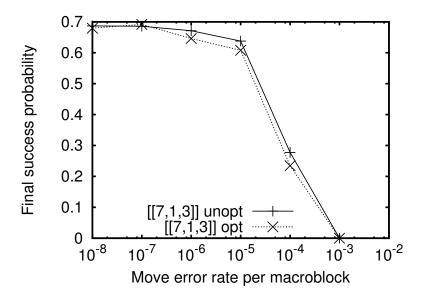

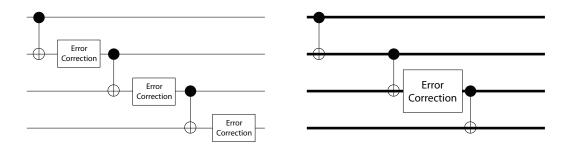

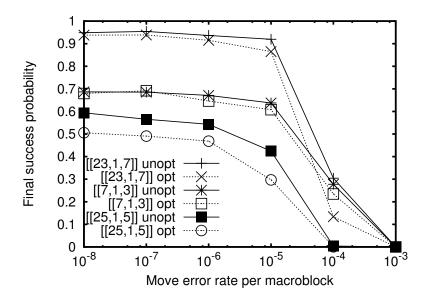

|          |      | 6.3.5 Results for Random Networks                                                                                                       |

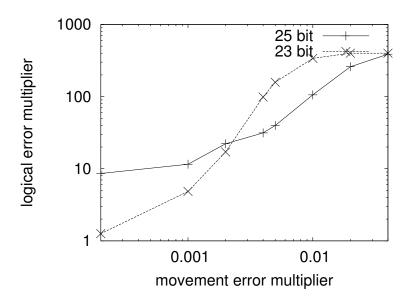

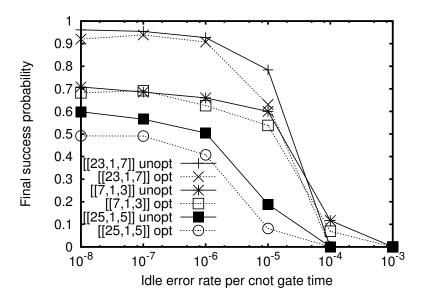

|          |      | 6.3.6 Effect of Non-Gate Errors                                                                                                         |

|          |      | 6.3.7 Limitations $\ldots \ldots 174$ |

|          | 6.4  | Code Selection and Optimization                                                                                                         |

| 7          | Fau  | Tolerant Optimization and Analysis for Large Circuits 18                                                                                                                | 30         |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

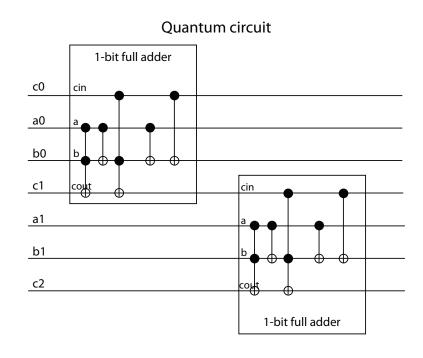

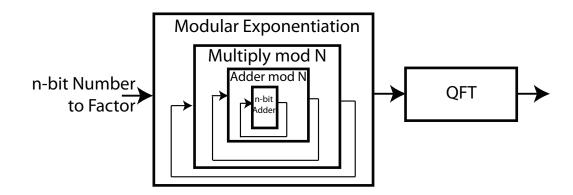

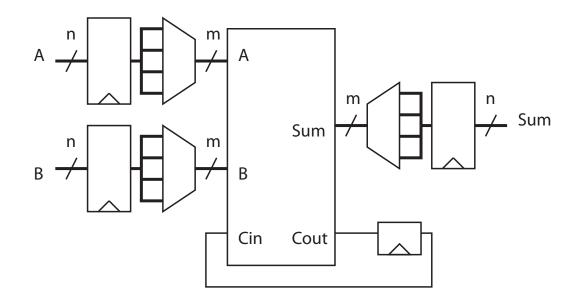

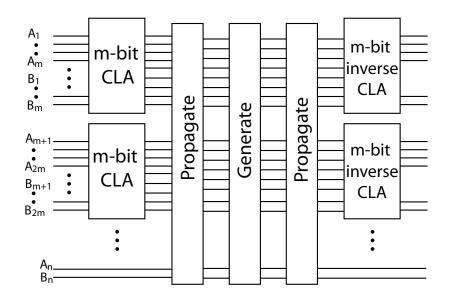

|            | 7.1  | Quantum Addition Circuits                                                                                                                                               | 81         |

|            |      | 7.1.1 Adder Implementation $\ldots$                                                    | 81         |

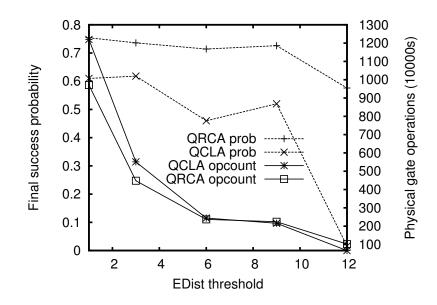

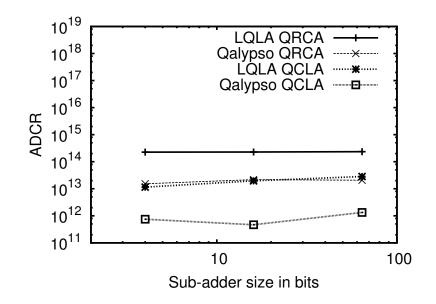

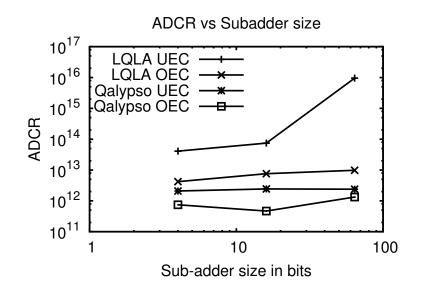

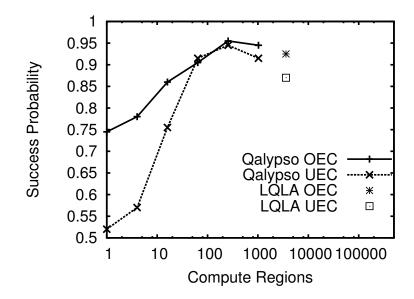

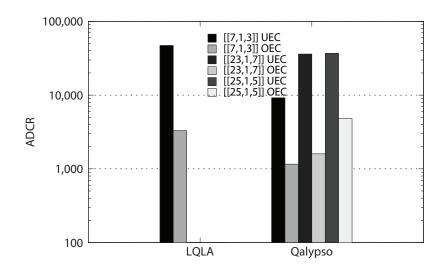

|            |      | 7.1.2 Adder Performance $\ldots \ldots \ldots$          | 82         |

|            |      | 7.1.3 Which adder design to use? $\ldots \ldots \ldots$ | 88         |

|            | 7.2  |                                                                                                                                                                         | 89         |

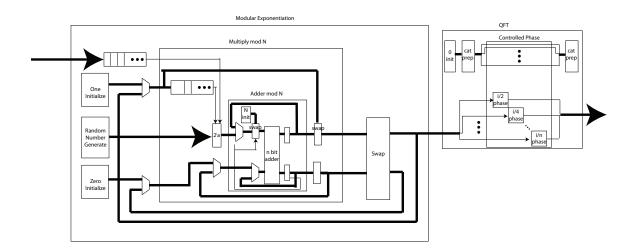

|            |      | 7.2.1 Implementation of Shor's 18                                                                                                                                       | 89         |

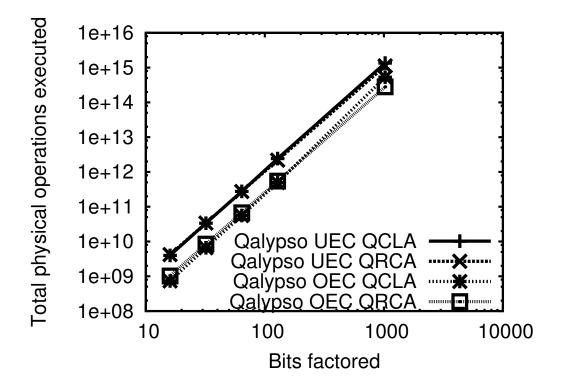

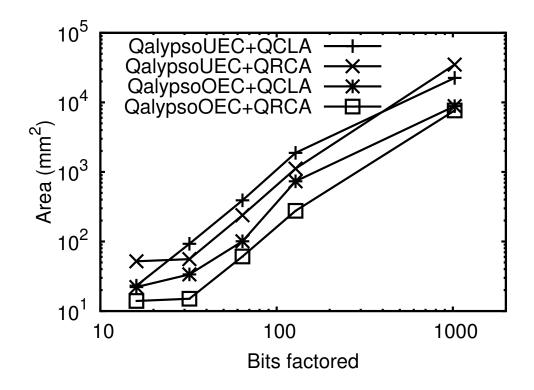

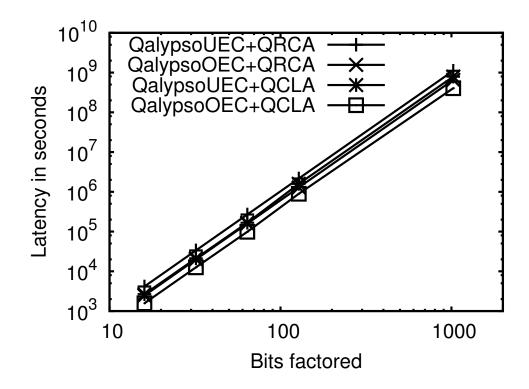

|            |      |                                                                                                                                                                         | 89         |

|            | 7.3  | Future Work                                                                                                                                                             | 90         |

|            |      | 7.3.1 Faster, Bigger Simulations                                                                                                                                        | 91         |

|            |      | 7.3.2 Error Model Refinements                                                                                                                                           | 92         |

|            |      | 7.3.3 Layout and Mapping to Qalypso                                                                                                                                     | 93         |

|            |      | 7.3.4 Expanding Code Comparisons                                                                                                                                        | 93         |

|            |      | 7.3.5 Recorrection Flexibility                                                                                                                                          | 94         |

|            | 7.4  | Conclusion $\ldots \ldots 1$                                                 | 95         |

| <b>л</b> , | 1.1. | 1                                                                                                                                                                       | <b>م</b> ر |

### Bibliography

### 197

# List of Figures

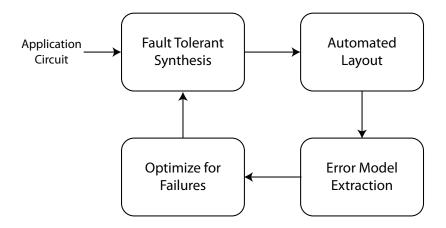

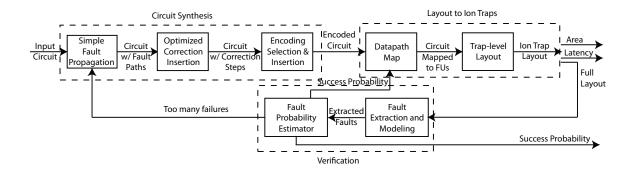

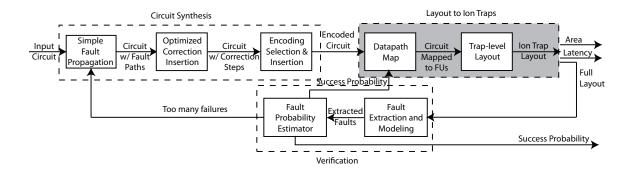

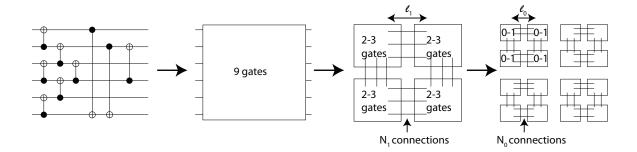

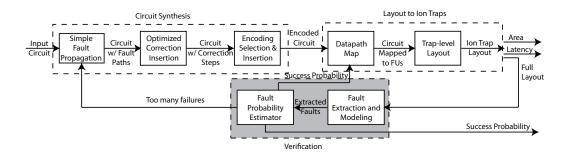

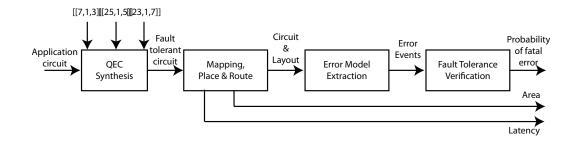

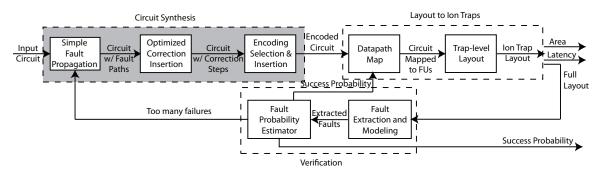

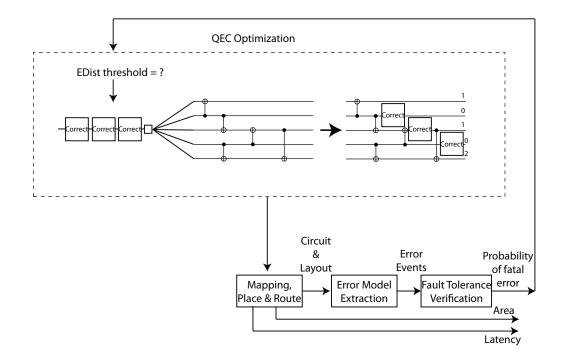

| 1.1 | Evaluating the affect of communication costs on quantum circuit fault tol-<br>erance can be done through an iterative process of fault tolerant synthesis,<br>circuit layout, failure model extraction, and analysis and optimization of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | layout and circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z  |

|     | outputs a layout and various metrics on the layout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3  |

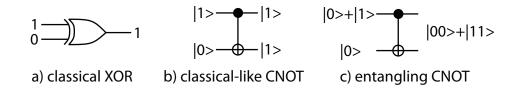

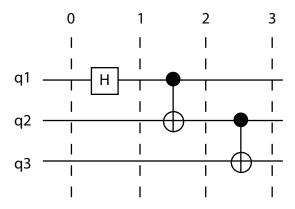

| 1.3 | A comparison between a classical XOR and its quantum analog: the con-<br>trolled not or CNOT. The CNOT gate is reversible, thus the additional out-<br>put. Figure b) outputs the XOR result to the bottom bit. Figure c) shows<br>the same CNOT when the input is a quantum superposition. In this case the<br>output is an <i>entangled</i> qubit state, not representable as independent qubit                                                                                                                                                                                                                                                                                                                                          | ŭ  |

|     | values for the two outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5  |

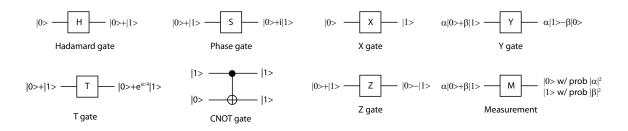

| 1.4 | Basic gates for quantum circuits: this is a set of gates which supports a<br>universal quantum computing model. The Hadamard gate converts bit values<br>to phase values and vice versa. The phase, T and Z gates rotate the phase of<br>the "1" qubit value by different angles. The CNOT gate is the same as shown<br>in Figure 1.3 and performs the XOR functionality. The measurement "gate"<br>measures a quantum state, returning a 1 or 0 and collapses any superposition<br>to that value as well. The X is a bit flip, Z a phase flip, and Y a combination<br>of both. The X, Y, Z, and phase gates can be generated by the other gates<br>shown here but we include them since they are often included as physical<br>primitives | 7  |

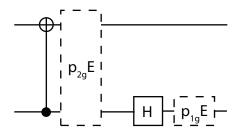

| 1.5 | Above is a simple independent gate error model. After each gate, qubits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1  |

| 1.0 | Above is a simple independent gate error model. After each gate, qubits<br>involved in the gate acquire an error with probability $p_{1q}$ for 1 qubit gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|     | and $p_{2q}$ for 2 qubit gates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8  |

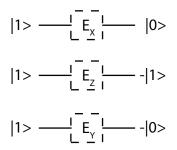

| 1.6 | Types of errors corrected by quantum error correcting codes: The X error $(E_X)$ flips the bit value, the Z error $(E_Z)$ flips the phase difference between 1 and 0 by $\pi$ radians, the Y error does both these things, flipping the bit and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | phase of the qubit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11 |

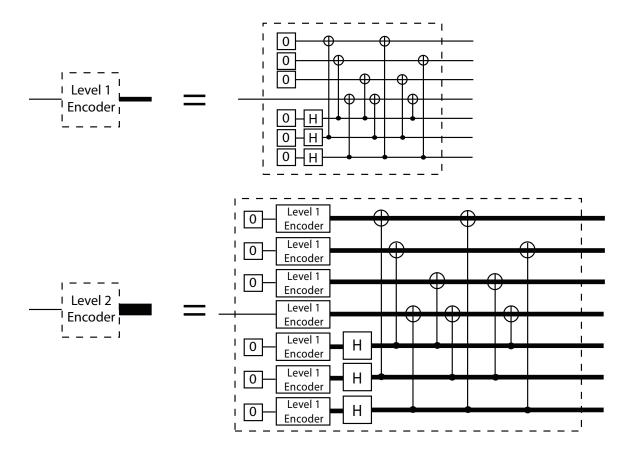

| 1.7   | On the top, we are encoding a single data qubit into a 7 qubit block code (the $[[7,1,3]]$ CSS code). The boxes with zeros indicate a preparation of a   |    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | new qubit in the $ 0\rangle$ state, if the input qubit is a single physical qubit, this                                                                  |    |

|       | is a level 1 encoder, producing a level 1 logical qubit. The bottom figure is                                                                            |    |

|       | a level 2 encoder, using a level one encoder as a building block to produce a                                                                            |    |

|       | level 1 logical zero valued qubit.                                                                                                                       | 12 |

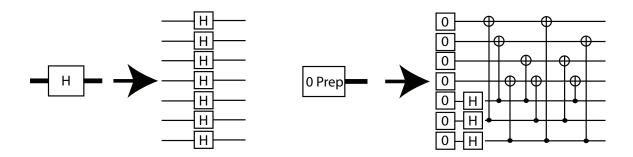

| 1.8   | On the right is a transversal Hadamard gate over an encoded block of qubits,                                                                             |    |

|       | on the left is a non-transversal encoded zero preparation. A transversal gate                                                                            |    |

|       | does not perform any intra-block qubit interactions.                                                                                                     | 13 |

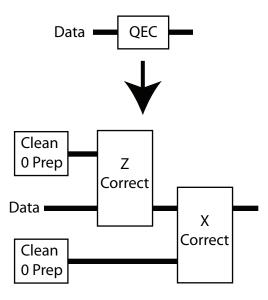

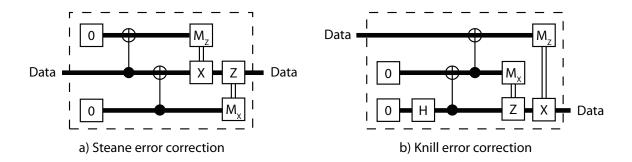

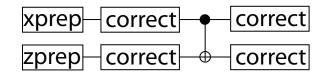

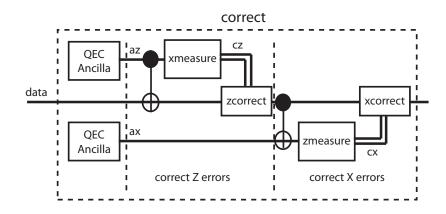

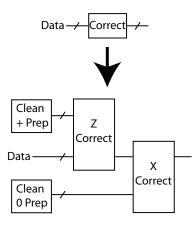

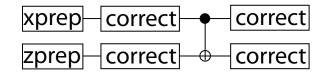

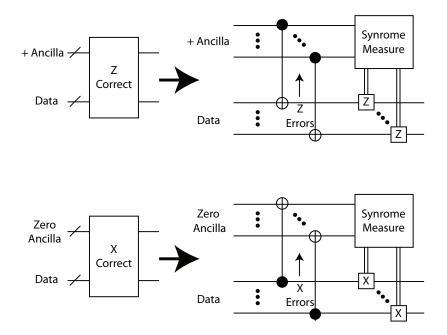

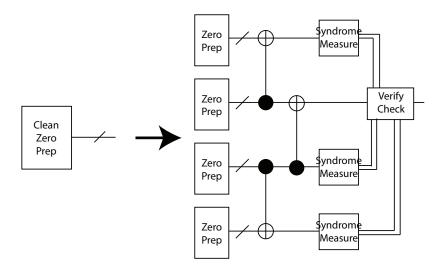

| 1.9   | Steane-style error correction schemes have the following form: generate two                                                                              | 10 |

| 1.5   | encoded zero states then perform sequential Z and X correction operations.                                                                               | 13 |

| 1.10  |                                                                                                                                                          | 10 |

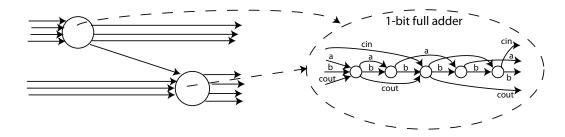

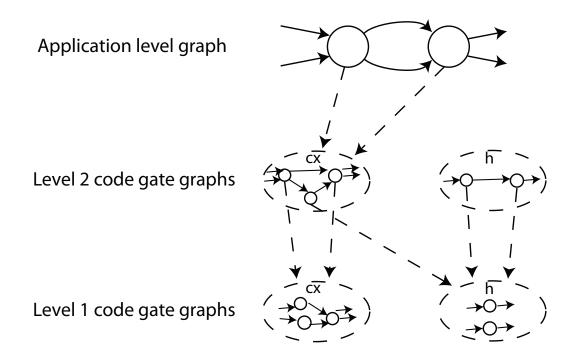

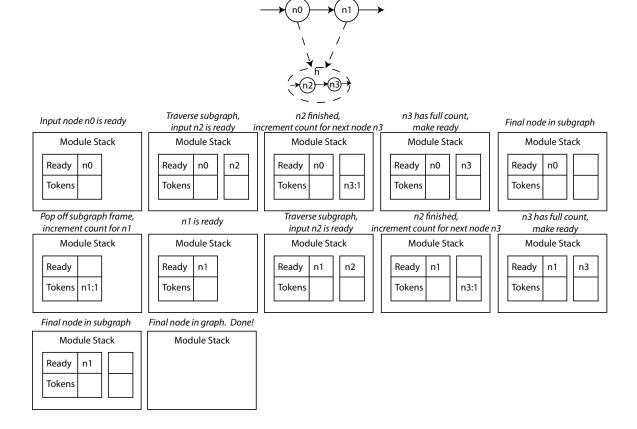

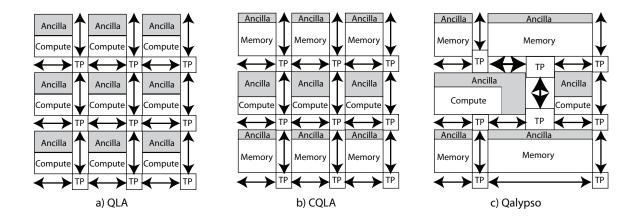

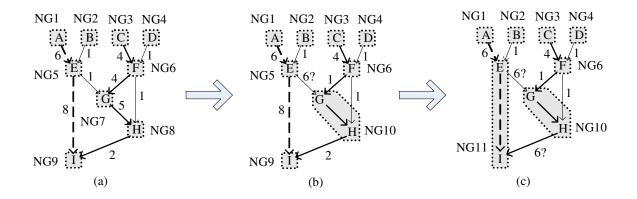

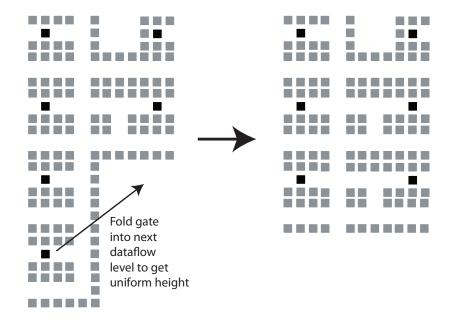

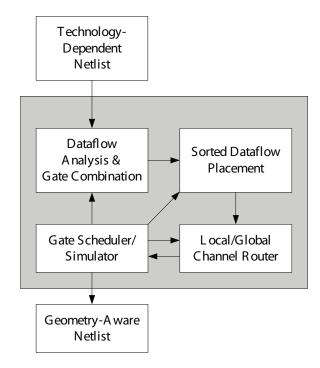

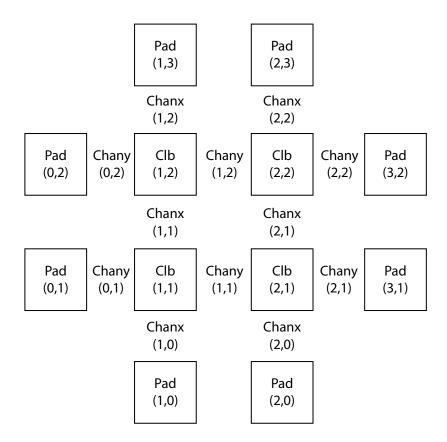

| 1.10  |                                                                                                                                                          |    |