## Downconverting Sigma-Delta A/D Converter for a Reconfigurable RF Receiver

Renaldi Winoto Borivoje Nikolic

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-81 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-81.html

May 21, 2009

Copyright 2009, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Downconverting Sigma-Delta A/D Converter for a Reconfigurable RF Receiver

by

Renaldi Winoto

B.S. (Cornell University) 2003 M.S. (University of California, Berkeley) 2006

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

#### GRADUATE DIVISION

of the

#### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Ali Niknejad Professor Daniel Tataru

Spring 2009

The dissertation of Renaldi Winoto is approved:

Chair

Date

Date

Date

University of California, Berkeley

Downconverting Sigma-Delta A/D Converter for a Reconfigurable RF Receiver

Copyright © 2009

by

Renaldi Winoto

#### Abstract

#### Downconverting Sigma-Delta A/D Converter for a Reconfigurable RF Receiver

by

Renaldi Winoto

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

The proliferation of a multitude of wireless standards as well as the interest in cognitive radios have resulted in the need for a highly reconfigurable radio-frequency (RF) receivers. Reconfigurability in an RF receiver has to be obtained with a negligible degradation in circuit performance, power consumption and silicon area. Digital signal processing offers a degree of flexibility that is perhaps unmatched by analog circuits. Nevertheless, a strategy of processing an RF signal entirely in the digital domain would place an incredible burden in the analog-to-digital converter circuits.

A novel receiver architecture is proposed in this work, where a high performance analogto-digital converter is tightly integrated within the RF circuit. In the proposed architecture, a signal at a radio frequency is directly converted to digital domain using a down-converting sigma-delta ( $\Sigma\Delta$ ) modulator. A  $\Sigma\Delta$  A/D converter is well-suited for an RF receiver. First, it minimizes aliasing due to the high sampling-rate. Second, it enables high-resolution conversion of the desired signal with low-resolution components. A direct-conversion to DC architecture greatly simplifies frequency planning of this flexible receiver, as it eliminates problems related to image frequency bands.

A circuit prototype demonstrating the proposed concept has been designed, fabricated and measured. The test-chip prototype is able to maintain an SNR of greater than +59dB across a 4-MHz bandwidth with a programmable center frequency of 400MHz to 1.7GHz. As illustrated in this work, the tight integration of the  $\Sigma\Delta$  modulator within the RF receiver also enables the receiver to achieve a very good linearity. An IIP3 of +19dBm and an out-of-band 3-dB desensitization level of +6dBm is measured in this test-chip prototype.

Professor Borivoje Nikolić Dissertation Committee Chair

To my dad, for teaching me to be curious.

# Contents

| Contents       |       |                                                                               |      |

|----------------|-------|-------------------------------------------------------------------------------|------|

| $\mathbf{Li}$  | st of | Figures                                                                       | iv   |

| $\mathbf{Li}$  | st of | Tables                                                                        | vii  |

| A              | cknov | vledgements                                                                   | viii |

| 1 Introduction |       |                                                                               |      |

|                | 1.1   | Related Work                                                                  | 4    |

|                | 1.2   | Thesis Organization                                                           | 6    |

| <b>2</b>       | Rac   | io-Frequency Receiver Design                                                  | 7    |

|                | 2.1   | RF Receiver Design: A Mixed-Signal Perspective                                | 7    |

|                | 2.2   | Sigma-Delta A/D Converters                                                    | 17   |

|                |       | 2.2.1 Short Introduction to Sigma-Delta A/D Conversion $\ldots \ldots \ldots$ | 17   |

|                |       | 2.2.2 Sigma-Delta A/D Converters in RF Receivers                              | 21   |

|                | 2.3   | Reconfigurable RF Receiver Specifications                                     | 23   |

|                | 2.4   | Performance Comparison of Integrated Receivers                                | 26   |

|                | 2.5   | Performance Limitations of RF Receivers                                       | 30   |

|                |       | 2.5.1 Linearity Limitation                                                    | 30   |

|                |       | 2.5.2 Frequency-Synthesizer Phase Noise                                       | 34   |

| 3              | Sig   | na-Delta Receiver                                                             | 37   |

|                | 3.1   | System Overview                                                               | 38   |

|                |       | 3.1.1 Scaling of the MOS switch                                               | 42   |

|                | 3.2   | Discrete-Time Processing of RF Signals                                        | 44   |

|          |     | 3.2.1  | Sampling Mixer                                                             | 44  |

|----------|-----|--------|----------------------------------------------------------------------------|-----|

|          |     | 3.2.2  | IIR Filter Synthesis                                                       | 48  |

|          |     | 3.2.3  | Noise in Switched-Capacitor Filters                                        | 53  |

|          |     | 3.2.4  | Circuit Parasitics                                                         | 57  |

|          | 3.3 | System | m Design                                                                   | 61  |

|          |     | 3.3.1  | Sigma-Delta Modulator Design                                               | 62  |

|          |     | 3.3.2  | Capacitor Sizing                                                           | 66  |

|          |     | 3.3.3  | Transconductance Amplifier Design                                          | 68  |

|          | 3.4 | Mixed  | l-Signal Design of the System                                              | 71  |

|          |     | 3.4.1  | Feedback D/A Converter Design Considerations $\ldots \ldots \ldots \ldots$ | 72  |

|          |     | 3.4.2  | Comparator Offset and Noise                                                | 78  |

|          | 3.5 | Summ   | nary of Circuit Parameters                                                 | 80  |

| 4        | Exp | erime  | ntal Prototype                                                             | 82  |

|          | 4.1 | Circui | t Design                                                                   | 82  |

|          |     | 4.1.1  | Transconductance Amplifier                                                 | 84  |

|          |     | 4.1.2  | First Feedback D/A Converter (FB1)                                         | 90  |

|          |     | 4.1.3  | Second Feedback D/A Converter (FB2)                                        | 92  |

|          |     | 4.1.4  | Comparator                                                                 | 93  |

|          |     | 4.1.5  | Gated-Diode Preamplifier                                                   | 101 |

|          |     | 4.1.6  | Clock Generation                                                           | 106 |

|          | 4.2 | Test-C | Chip Prototype                                                             | 110 |

|          | 4.3 | Measu  | rement Results                                                             | 114 |

|          |     | 4.3.1  | Comparative Analysis                                                       | 120 |

|          |     | 4.3.2  | Possible Improvements                                                      | 122 |

| <b>5</b> | Con | clusio | n                                                                          | 125 |

|          | 5.1 | Summ   | nary                                                                       | 125 |

|          | 5.2 | Specif | ic Contributions                                                           | 128 |

|          | 5.3 | Future | e Work                                                                     | 128 |

|          |     |        |                                                                            |     |

# List of Figures

| 1.1  | Cellular telephone supporting multiple wireless standards                                  | 2  |

|------|--------------------------------------------------------------------------------------------|----|

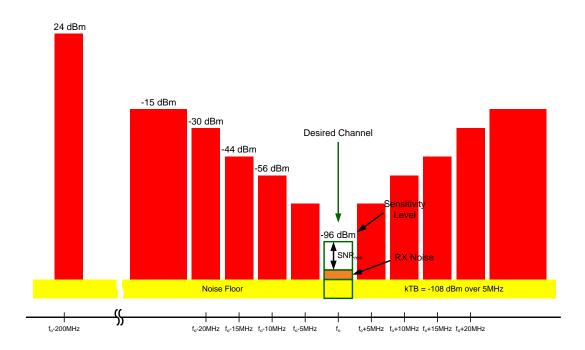

| 2.1  | Near-far problem                                                                           | 8  |

| 2.2  | Blocking mask of a UMTS standard                                                           | 9  |

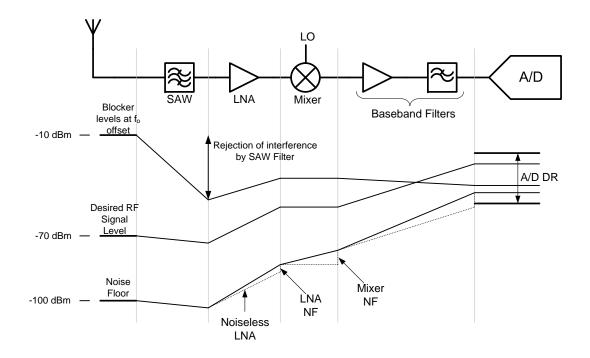

| 2.3  | A direct-conversion receiver                                                               | 11 |

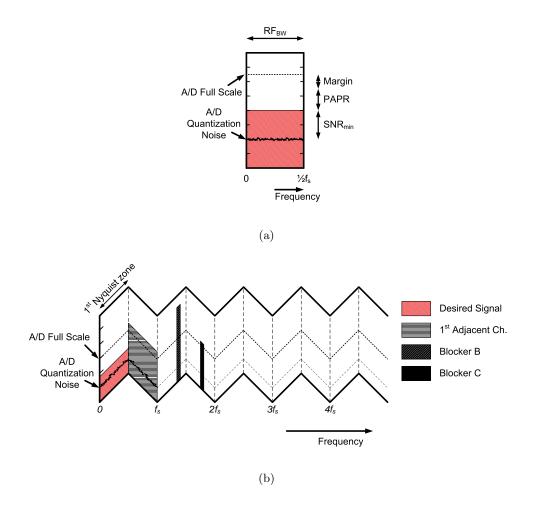

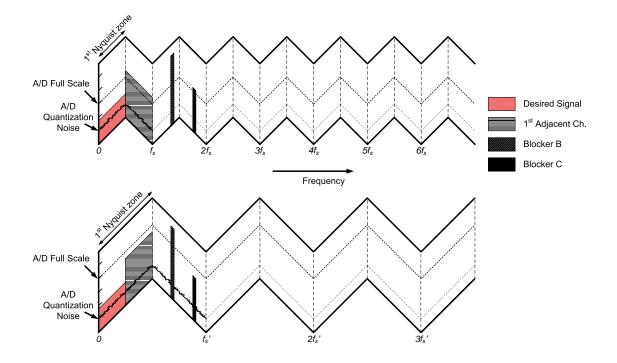

| 2.4  | A/D converter specification: (a) minimum requirements, (b) signal folding due to sampling. | 12 |

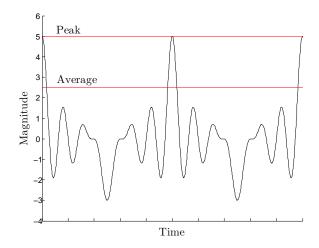

| 2.5  | Illustration of peak-to-average power ratio problem.                                       | 13 |

| 2.6  | Doubling A/D sampling-rate to reduce aliasing                                              | 14 |

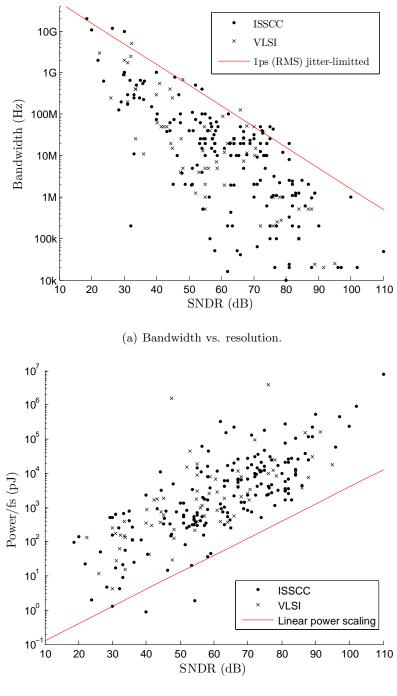

| 2.7  | Survey of A/D converters performance.                                                      | 16 |

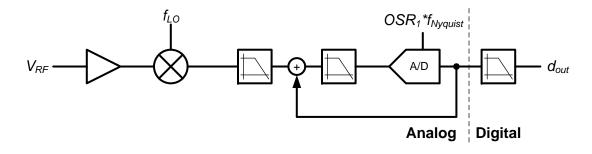

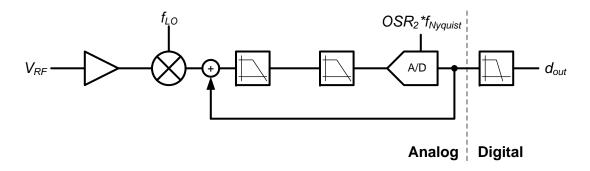

| 2.8  | A low-pass/baseband $\Sigma\Delta$ modulator                                               | 18 |

| 2.9  | Signal and noise transfer functions for a first-order $\Sigma\Delta$ modulator             | 20 |

| 2.10 | Output power spectral density of a simulated first-order $\Sigma\Delta$ modulator          | 21 |

| 2.11 | Comparison between a Nyquist-rate and a $\Sigma\Delta$ A/D converter                       | 22 |

| 2.12 | Comparison of blocker masks between different wireless standards                           | 24 |

| 2.13 | Frequency response of a SAW filter for a UMTS standard                                     | 25 |

| 2.14 | Conceptual diagram of a software-defined radio                                             | 29 |

| 2.15 | MOS transistor voltage-to-current conversion characteristics. $\ldots$                     | 31 |

| 2.16 | Achievable IIP3 from a deep sub-micron transistor                                          | 32 |

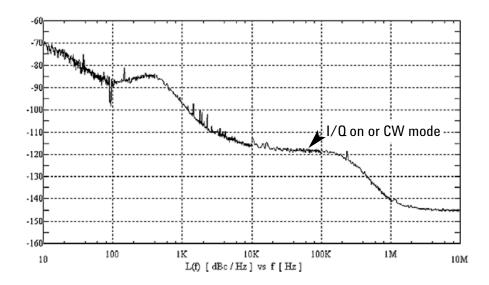

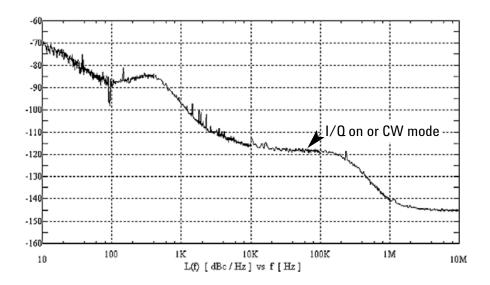

| 2.17 | Phase-noise plot of an Agilent 4438C frequency synthesizer                                 | 35 |

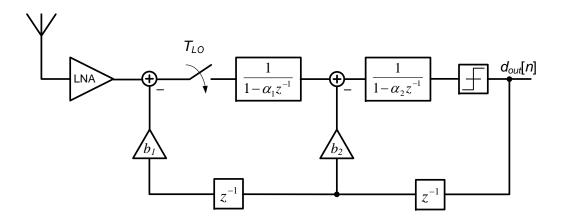

| 3.1  | A $\Sigma\Delta$ receiver block diagram                                                    | 38 |

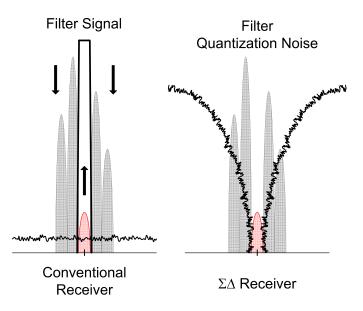

| 3.2  | Comparison between a conventional and a $\Sigma\Delta$ receiver.                           | 39 |

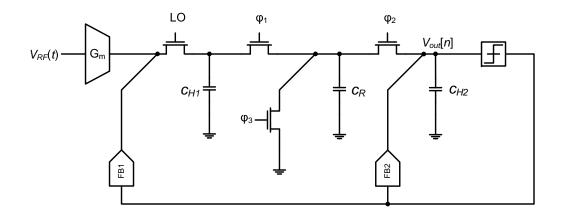

| 3.3  | Simplified circuit diagram of the $\Sigma\Delta$ receiver                                  | 41 |

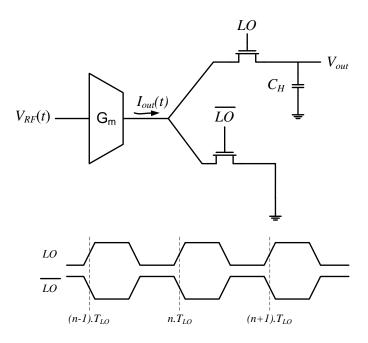

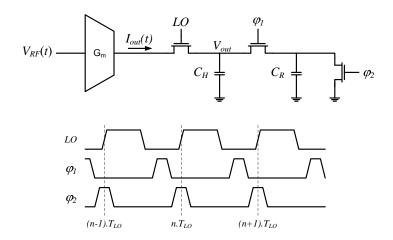

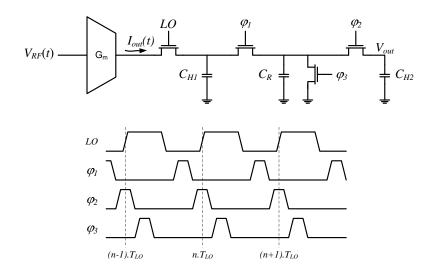

| 3.4  | Single-balanced passive mixer with single-ended output                                     | 45 |

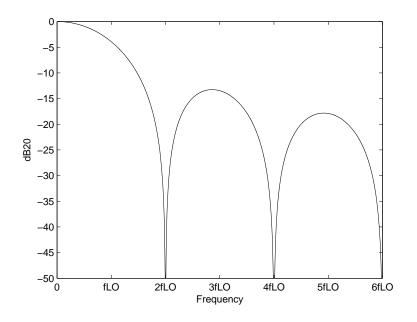

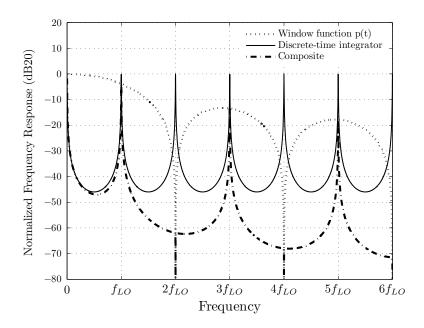

| 3.5  | Frequency response of anti-alias pre-filter $p(t)$                                         | 47 |

| 3.6  | Signal flow-graph diagram of a sampling mixer                                                            | 47 |

|------|----------------------------------------------------------------------------------------------------------|----|

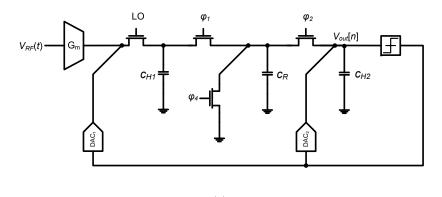

| 3.7  | Lossy discrete-time integrator.                                                                          | 48 |

| 3.8  | A cascade of two lossy discrete-time integrators.                                                        | 50 |

| 3.9  | Signal flow-graph diagram of a cascade of two integrators                                                | 52 |

| 3.10 | Noise on a single switched capacitor                                                                     | 53 |

| 3.11 | Noise on two switched capacitors                                                                         | 54 |

| 3.12 | Noise in a second-order IIR filter: (a) circuit schematic; (b) signal flow-graph diagram.                | 56 |

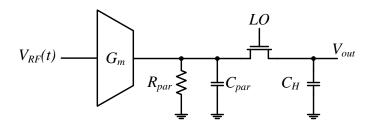

| 3.13 | Input transconductance amplifier with finite output resistance and non-zero output capacitance           | 58 |

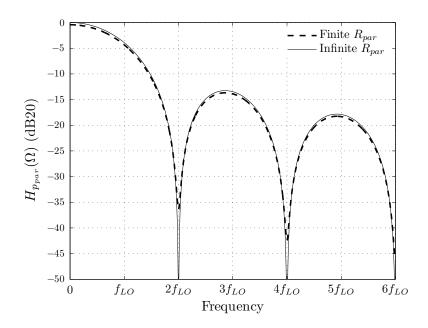

| 3.14 | Impact of transconductance amplifier finite output resistance                                            | 59 |

| 3.15 | Frequency response of passive mixer                                                                      | 61 |

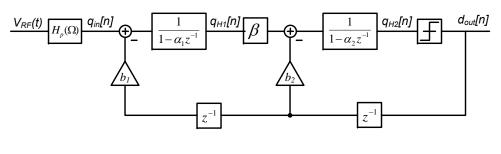

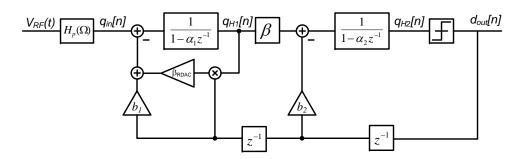

| 3.16 | Second-order $\Sigma\Delta$ modulator: (a) circuit schematic; (b) signal flow-graph diagram              | 62 |

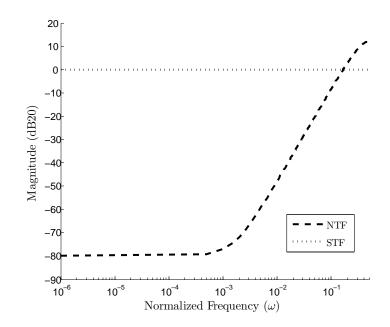

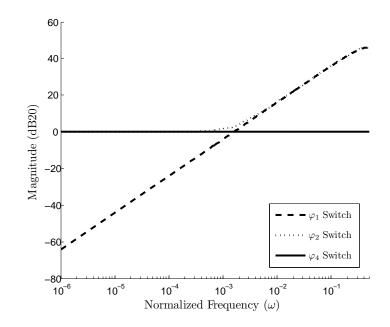

| 3.17 | Signal and noise transfer functions of a passive second-order $\Sigma\Delta$ modulator.                  | 64 |

| 3.18 | Switched capacitor noise in a second-order $\Sigma\Delta$ modulator                                      | 67 |

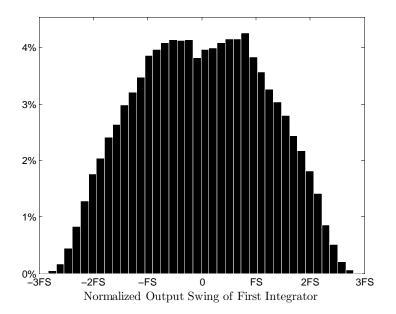

| 3.19 | Normalized histogram of output values of $Q_{H1}$                                                        | 70 |

| 3.20 | Phase-noise plot of a frequency synthesizer.                                                             | 75 |

| 3.21 | Circuit model of the first feedback D/A converter with finite output resistance.                         | 77 |

| 3.22 | System model including the effects of feedback D/A converter finite output resistance.                   | 78 |

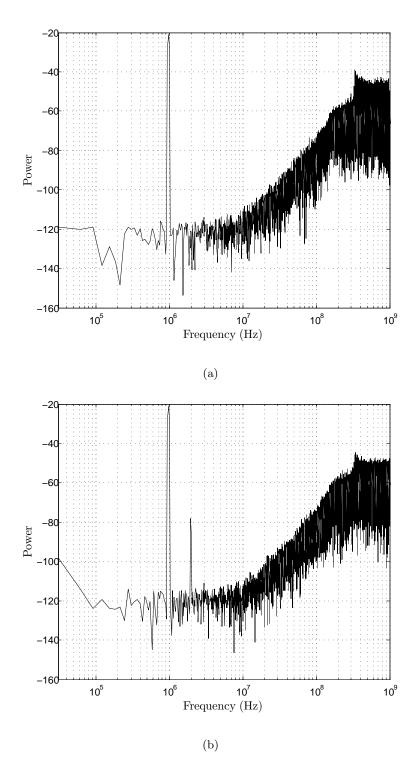

| 3.23 | $\Sigma\Delta$ modulator output spectrum: (a) with an infinite $R_{DAC}$ ; (b) with a finite $R_{DAC}$ . | 79 |

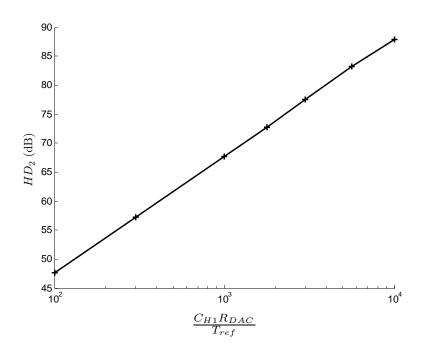

| 3.24 | Second-order distortion due to a finite $R_{DAC}$                                                        | 80 |

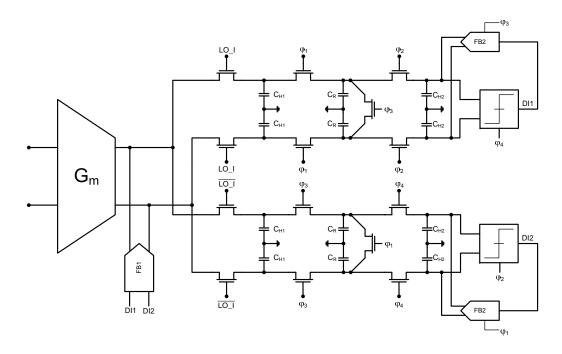

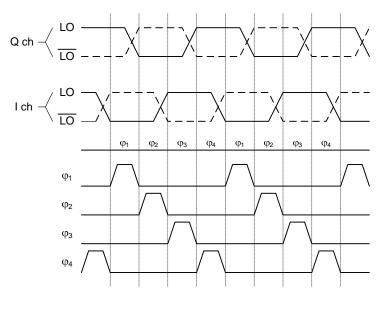

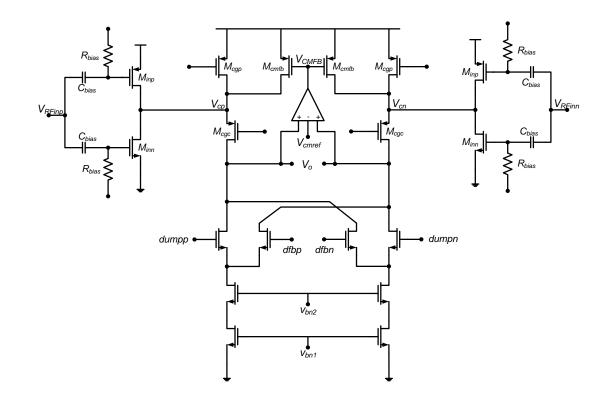

| 4.1  | Detailed system diagram of the $\Sigma\Delta$ receiver.                                                  | 83 |

| 4.2  | Transconductance amplifier circuit.                                                                      | 85 |

| 4.3  | Drain voltage modulation on a MOS transistor                                                             | 86 |

| 4.4  | Common-gate cascode amplifier.                                                                           | 88 |

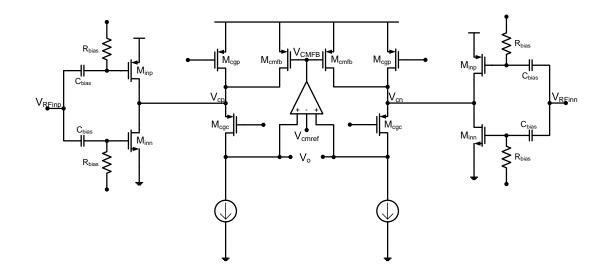

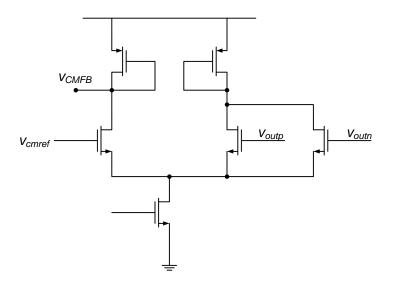

| 4.5  | Common-mode feedback amplifier.                                                                          | 89 |

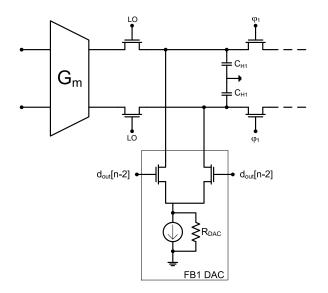

| 4.6  | A combined transconductance amplifier and first feedback D/A converter circuit                           | 91 |

| 4.7  | Second feedback D/A converter circuit.                                                                   | 92 |

| 4.8  | A double-tail latch-type voltage sense-amplifier                                                         | 94 |

| 4.9  | Double-tail latch transient simulation.                                                                  | 95 |

| 4.10 | Buffer and second static latch following double-tail latch.                              | 96  |

|------|------------------------------------------------------------------------------------------|-----|

| 4.11 | Model of a comparator with hysteresis                                                    | 96  |

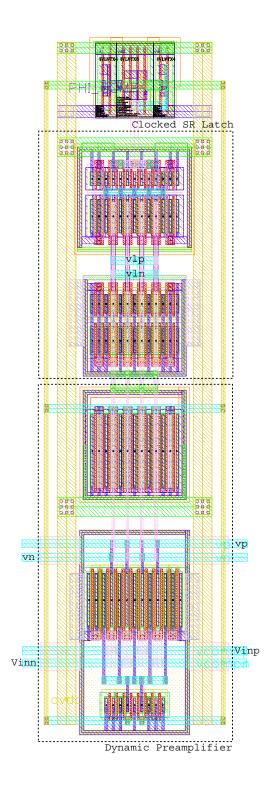

| 4.12 | Layout of the double-tail latch circuit.                                                 | 98  |

| 4.13 | Comparator model with noise source                                                       | 99  |

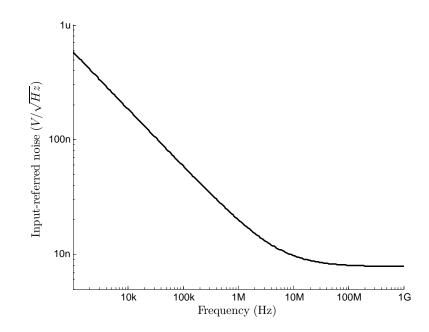

| 4.14 | Input-referred noise of the double-tail latch (PNOISE simulation). $\ldots$ .            | 101 |

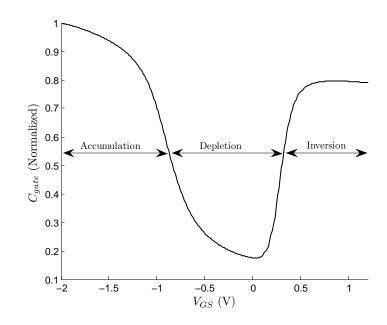

| 4.15 | MOS transistor gate capacitance as a function of applied gate-source bias                | 102 |

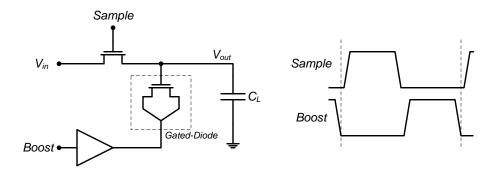

| 4.16 | A gated-diode amplifier                                                                  | 103 |

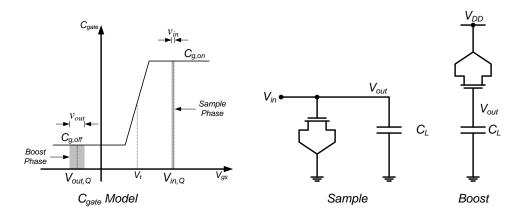

| 4.17 | Operation of a gated-diode amplifier                                                     | 103 |

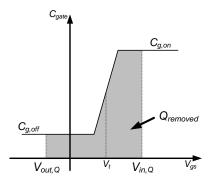

| 4.18 | Charge removed during application of <i>Boost</i> signal                                 | 105 |

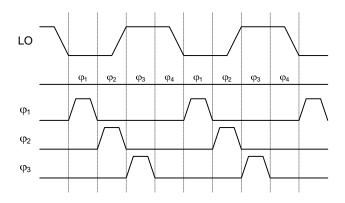

| 4.19 | Non-overlap requirements in timing generation                                            | 106 |

| 4.20 | Clock generation strategy.                                                               | 107 |

| 4.21 | Input clock buffer circuit.                                                              | 108 |

| 4.22 | DCVSL D-latch.                                                                           | 109 |

| 4.23 | Floorplan of test-chip                                                                   | 111 |

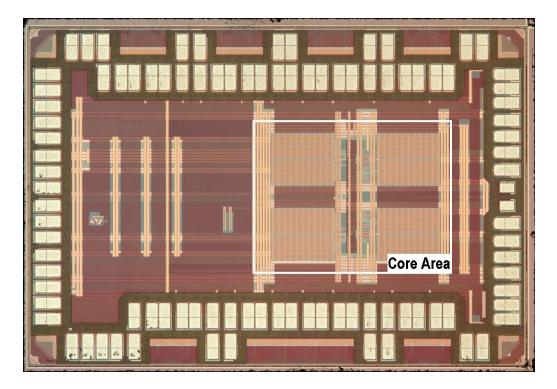

| 4.24 | Microphotograph of test-chip                                                             | 113 |

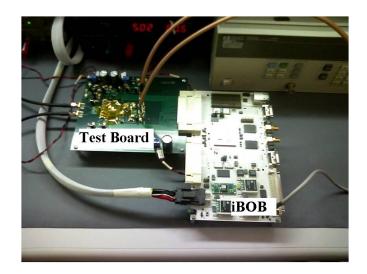

| 4.25 | Test Setup.                                                                              | 113 |

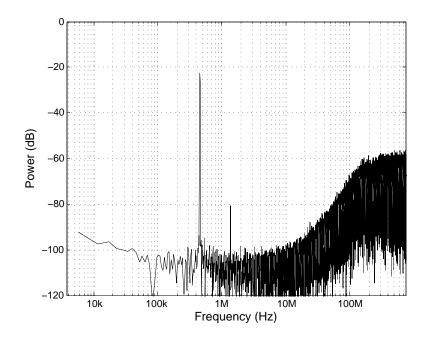

| 4.26 | Power-spectral density of output data at $f_{LO} = 1.5$ GHz                              | 114 |

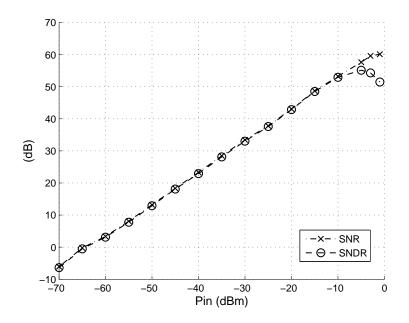

| 4.27 | SNR and SNDR as a function of input power at $f_{LO} = 1.5$ GHz                          | 115 |

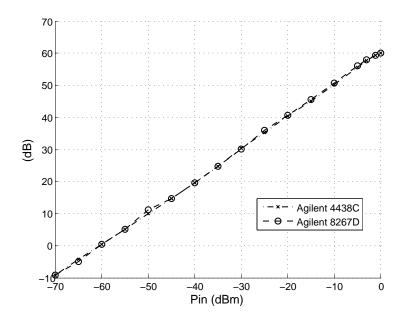

| 4.28 | Performance comparison of the $\Sigma\Delta$ receiver with two different clock sources.  | 115 |

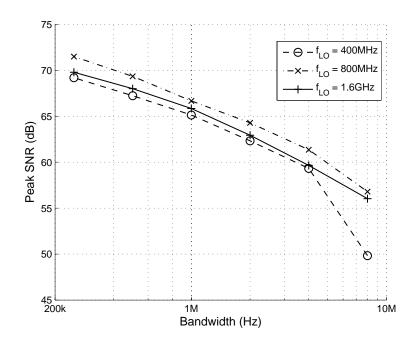

| 4.29 | SNR as a function of signal bandwidth at different $f_{LO}$ frequencies                  | 116 |

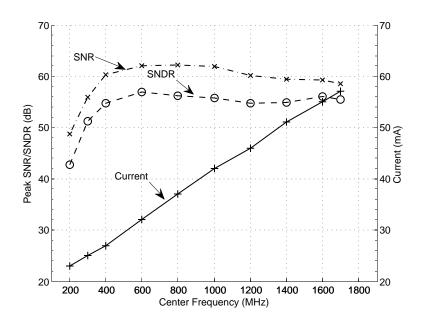

| 4.30 | SNR, SNDR and power consumption at different $f_{LO}$ frequencies for a 4-MHz bandwidth. | 117 |

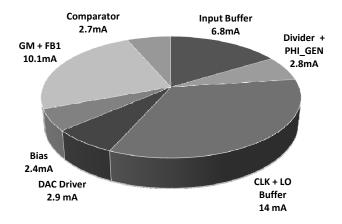

| 4.31 | Breakdown of power consumption at $f_{LO} = 1$ GHz                                       | 118 |

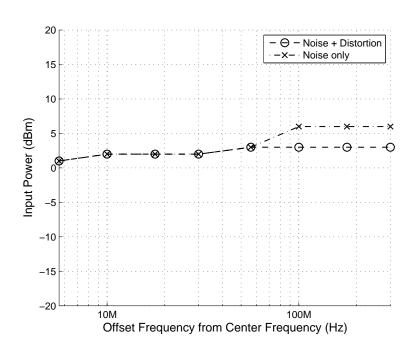

| 4.32 | Out-of-band 3-dB desensitization levels with a 4-MHz bandwidth                           | 118 |

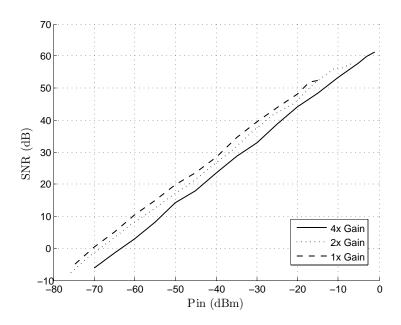

| 4.33 | Gain control and the resulting SNR                                                       | 119 |

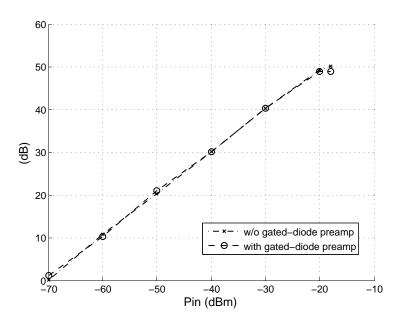

| 4.34 | SNR improvement due to gated-diode amplifier                                             | 120 |

| 5.1  | Comparison of three RF receiver architectures                                            | 126 |

# List of Tables

| 24  |

|-----|

| 25  |

| 27  |

| 28  |

| 29  |

| 33  |

| 36  |

| 40  |

| 65  |

| 76  |

| 81  |

| 119 |

| 121 |

| 122 |

| 123 |

|     |

#### Acknowledgements

It has been a true privilege to spend six years studying in Berkeley, in the course of which I have had the honor to work and interact with a group of very intelligent, resourceful and kind personalities. Surely without them, my stay in Berkeley would not be as memorable.

First and foremost, I would like to express my most sincere gratitude to my advisor, Professor Bora Nikolić, who took me into his group, supported my research and gave me numerous advice in academics, research and career.

I would like to thank Professor Ali Niknejad for his keen interest on my project and for teaching me RF circuit design through the three wonderful classes that he taught. I also thank Professor Bob Brodersen and Professor Daniel Tataru for their evaluation of the initial proposal as well as the final results of my research.

I am indebted to Haideh Khorramabadi and Bogdan Staszewski; both of whom I had many lengthy discussions with during the formative stages of my research. I completed two internships during my graduate studies, at Broadcom and Texas Instruments. Although my assignments at both internships had very little to do with my research, they have enriched my knowledge in many ways. I thank Tom Kwan, Marcel Lugthart, Dirk Leipold and Bogdan Staszewski for those stimulating assignments.

Throughout my stay in Berkeley I have felt very insulated from the administrative bureaucracy, funding uncertainty, computer and lab problems that are often taken as part of being a graduate student. This is a testament to the dedication of a group of people who did a lot of work behind the scene so that students can focus their energy on doing great research. The help of Brian Richards, Sue Mellers, Kevin Zimmerman and Brad Krebs ensured that I have what I need to finish tape-out and to collect measurement results. I would not forget Kevin's help on getting the license server back up on a Sunday morning prior to a tape-out deadline. I thank Jessica Budgin, Jennifer Stone, Jennifer Kim and Brenda Farrell for the administration of my funding. I would also like to thank Tom Boot and Ruth Gjerde, who are not only great at what they do, but are also genuinely kind persons. The friendship of many peers in Berkeley is perhaps one of the best memories that I will take with me of my graduate studies. I have very much enjoyed being part of DCDG/Bora's group. Radu Zlatanovici, Sokratis Vamvakos, Bill Tsang, Liang-Teck Pang, Zhengya Zhang, Zheng Guo, Seng-Oon Toh, Ji-Hoon Park, Dusan Stepanovic, Vinayak Nagpal and Milos Jorgovanovic have made my stay very memorable. I cherish the memories of our lunch conversations, ride to retreats as well as the ski and camping trips that we did together. I appreciate Zhengya's perspective in life, career and in research and most importantly I am thankful for his friendship throughout the years. I thank Simone Gambini for being a good friend and for giving me many constructive and critical feedback on my research; I have learned much from our discussions. I also thank Wei-Hung Chen and Jason Stauth for discussions regarding our common research interests.

Widya has been by my side through the best and the worst days of my graduate studies. I am forever indebted for her unending support and understanding of the demands of my studies. Her love and companion have made my life in grad school so much more meaningful.

I am most fortunate to have my family: my parents, my sister and younger brother. Their constant encouragement has pushed me to be the best that I can be. I value my mom's positive perspective of the world; that there is always lessons to be learned, and that I'll be a better person because of every single life experience, good or bad. Since I was very young, my dad has nurtured my sense of curiosity for science and the physical world by always giving me the complete answer instead of the conveniently oversimplified ones. He is the quintessential engineer and scientist, who needs to understand everything thoroughly. His passion for learning is exemplary, I think having him as a father is perhaps the best preparation I can have for graduate studies. I am certain that the result of this work has been a product of my family's love and support throughout my life.

## Chapter 1

# Introduction

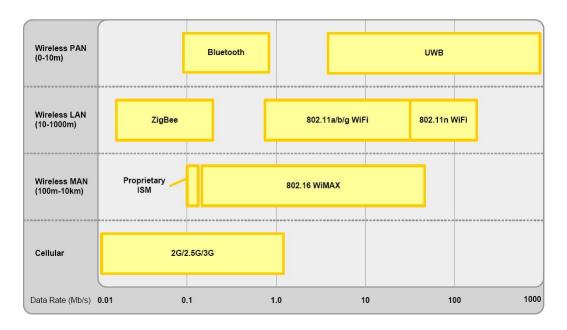

The past decade has witnessed an immense growth of wireless connectivity. This growth has been driven by the continuous reduction of the cost of the underlying hardware as well as the seemingly unending desire to unterher every electronic device. In order to tailor to a specific usage scenario, a multitude of wireless standards have arisen, each categorized by the data rate and the range of communications (Fig. 1.1(a)). Each of these communication standards is optimized for the lowest power and lowest cost.

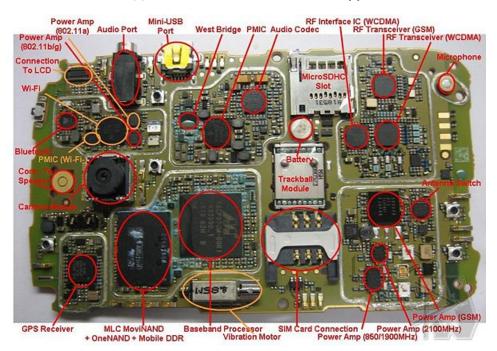

Supporting this multitude of wireless standards has become a significant design challenge in current and future wireless devices. A high-end cellular handset today supports more than five different wireless standards, operating at more than ten frequency bands. Dedicated transceiver ICs along with the necessary peripheral components are typically needed in order to support each wireless standards. Despite the apparent increase in complexity (Fig. 1.1(b)), the continuous cost reduction afforded by the continuous scaling of CMOS technology will only accelerate the demand for these multi-standard capable wireless devices in the future.

Furthermore, looking towards the future, there is a push for a more flexible spectrum allocation. There is a significant amount of allocated spectrum that is poorly utilized [57]. At the same time, the limited spectrum that is unallocated is auctioned off for a very high price. A flexible spectrum allocation holds the promise of a much more efficient, and

(a) Comparison of wireless technologies [4]

(b) PCB of a high-end cellular telephone [7]

therefore cost-effective use of the radio-frequency spectrum. This new paradigm would require RF transmitters and receivers that are sufficiently flexible to communicate in any available frequency band. This is in contrast with contemporary wireless communication schemes, where the communication occurs in limited and very well-defined frequency bands.

For the two reasons mentioned above, a reconfigurable transceiver is desired. The goal is to have a single, but flexible, signal-processing path in order to support all current and future wireless standards. This technology would streamline the design of multi-standard wireless devices as well as enable the deployment and adoption of a flexible spectrum allocation scheme.

This work would particularly be concerned with the development of a highly reconfigurable RF receiver. The focus would be on the 0-2.4-GHz frequency-range where most of today wireless communication standard reside.

Flexibility and reconfigurability in an RF receiver have to be obtained with a negligible decrease in the circuit performance and a minimum increase in power consumption or silicon area. Digital signal processing offers a degree of flexibility that is perhaps unmatched by analog circuits. Nevertheless, a strategy of processing an RF signal entirely in the digital domain would place an incredible burden in the analog-to-digital converter circuits. Since an RF signal is continuous time and continuous amplitude in nature, an analog-to-digital converter is needed in order to translate it to a digital representation.

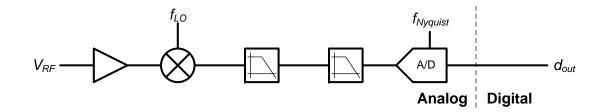

A receiver architecture is proposed in this work, where a high performance analog-todigital converter is tightly integrated with circuitry that is usually categorized as an RF circuit. In the proposed architecture, a signal at a radio frequency is directly converted to digital domain using a down-converting sigma-delta ( $\Sigma\Delta$ ) modulator. A  $\Sigma\Delta$  A/D converter is well-suited for an RF receiver; it minimizes aliasing due to the high sampling-rate and it has a high dynamic-range in the frequency band of interest. Final signal selection is performed in the digital domain, where the signal bandwidth can be easily adjusted through a change of digital filter coefficients. A direct-conversion to DC receiver architecture greatly simplifies frequency planning of this flexible receiver, as it eliminates problems related to image frequency bands.

A circuit prototype demonstrating the proposed concept has been designed, fabricated and measured. The test-chip prototype is able to maintain an SNR of greater than +59dB across a 4-MHz bandwidth with a programmable center frequency spanning from 400MHz to 1.7GHz. As will be illustrated in this work, the tight integration of a  $\Sigma\Delta$  modulator within an RF receiver also enables the receiver to achieve a very good linearity performance. An IIP3 of +19dBm and an out-of-band 3-dB desensitization level of +6dBm is measured in this test-chip prototype.

#### 1.1 Related Work

There are three notable examples of reconfigurable, or software-defined, RF receivers (SDR) [29, 10, 80]. All three use a similar architecture, where a single-conversion mixer is followed by a high-order low-pass filter prior to A/D conversion. Unlike the other two receivers, the one by UCLA [10] contains a passive, discrete-time low-pass filter.

Passive switched-capacitor filter is an old concept that has gained renewed interest, especially for use as a baseband filter in an RF receiver [65, 62, 10, 47]. This technique enables precise control of the filter's critical frequencies, without the stringent amplifier settling-time requirement associated with an active switched-capacitor filter. Furthermore, an all-zero FIR filter, a type of filter that is suitable for an anti-aliasing filter needed in an RF receiver, can be easily implemented using this technique [66]. For example in [65], a simple passive switched-capacitor moving-average filter is used as an anti-aliasing filter prior to sample-rate downconversion in a baseband filter in a Bluetooth receiver.

The resurgence of interest for passive switched-capacitor filters in RF receivers can be partly attributed to the use of a sampling-mixer or charge-sampling circuit. A sampling mixer eliminates the need for a power-hungry sample-and-hold circuit that is needed prior to any discrete-time system. The concept of sampling mixer was first introduced by Yuan [116]. Variations of this concept is used in Texas Instruments' DRP receivers [65, 62], the UCLA software-defined receiver [10] and several other published circuits [40, 41].

In this work, an RF signal is directly sampled at a radio-frequency using a sampling mixer. The output of the sampler is then digitized at the same frequency using a highspeed  $\Sigma\Delta$  modulator. In this manner, much of the signal processing can be performed in the digital domain, where flexibility can be more easily obtained. For example, a change of filter bandwidth can be accomplished simply by loading a different set of filter coefficients.

It has been stipulated that a 'true' software-defined radio would require a highresolution, high-speed A/D converter [60]. A high sampling rate is necessary in order to avoid undesired aliasing of blockers as well as to avoid the problem of noise folding that is prevalent in subsampling receiver architecture [39, 83, 53]. A high resolution conversion is necessary in order to maintain an acceptable SNR for successful demodulation of the desired signal in the presence of large blocker signals. The problem with this approach is that such a high-speed, high-resolution A/D converter is not practically realizable [95].

We circumvent this problem by enclosing a high-speed, but low-resolution, A/D converter inside a  $\Sigma\Delta$  modulator loop. It is important to recognize that an RF signal has a property that is in some ways compatible to an oversampling  $\Sigma\Delta$  A/D converter: the bandwidth of the RF signal is relatively narrow when compared to its center frequency. Sampling the RF signal at a radio frequency would minimize aliasing and undesired folding. However, a high dynamic-range conversion is only needed in a narrow bandwidth relative to the center frequency; it is not necessary to maintain the high dynamic range across all frequencies.

Downconverting  $\Sigma\Delta$  A/D converters have been published previously [14, 103, 70, 17]. The work of Namdar [70] and Tao [103] have a mixer that is enclosed within the  $\Sigma\Delta$  modulator loop. However, the two circuits have limited bandwidths of 40KHz and 200kHz respectively, and center frequencies of less than 400MHz. The other two circuits by Breems [14] and Chen [17] actually consist of a mixer followed by a  $\Sigma\Delta$  A/D converter. As will be seen in chapter 3, putting a mixer inside the  $\Sigma\Delta$  loop has the advantage that the mixer switches only processes the error signal which is much smaller than the desired signal. This subtle difference can result in higher linearity due to reduced signal range in the mixer switches.

### 1.2 Thesis Organization

Chapter 2 of this dissertation presents an in-depth overview of the problem to be addressed by this dissertation. A set of system requirements is derived, a survey of state-of-art solutions is presented and several practical performance limitation is analyzed.

Chapter 3 of this dissertation is concerned with the system design aspect of the proposed architecture. The  $\Sigma\Delta$  receiver architecture is introduced. All pertinent analysis is presented. The chapter ends with a derivation and selection of important circuit parameters for implementation.

Chapter 4 of this dissertation discusses the circuit implementation of the  $\Sigma\Delta$  receiver. Detailed descriptions of the important circuit blocks are discussed. A novel gated-diode preamplifier circuit is presented, along with the pertinent analysis. The chapter concludes with a presentation of measurement results from the test chip.

Chapter 5 of this dissertation summarizes the important contributions of this work.

## Chapter 2

# **Radio-Frequency Receiver Design**

This section provides a brief introduction to RF receiver design. In particular, derivation of an A/D converter specification for an RF receiver is described in detail. A brief introduction to  $\Sigma\Delta$  A/D converter and its relevance to an RF receiver is presented. Specifications for a reconfigurable RF receiver is developed based on a survey of requirements of today's wireless standards. A survey of state-of-art integrated circuit solutions is presented. An effort is made to predict the practical performance limitation of an RF receiver.

### 2.1 RF Receiver Design: A Mixed-Signal Perspective

A wireless communication system differs greatly from its wired counterpart because of the lack of implied control over the type, strength and frequency location of signals that are present in the wireless channel. As a result, RF receivers have to be designed with a much larger tolerance to accommodate the unknown.

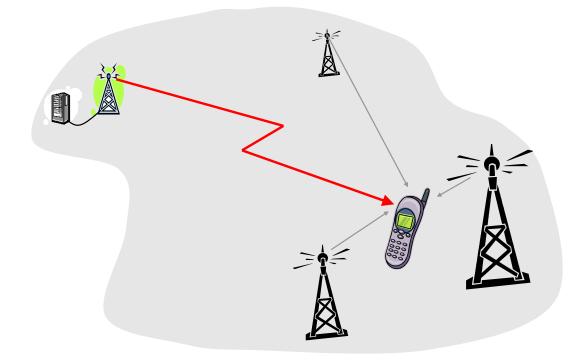

A worst-case scenario is depicted in figure 2.1, which is commonly referred to the nearfar problem. In this scenario, a far away base-station wishes to send a packet of information through the wireless medium. The radio signal is attenuated as it propagates through the medium. When the radio signal reaches the handset, its power level has experienced significant attenuation. On the other hand, other transmitters are present in the surrounding

Figure 2.1. Near-far problem.

environment. Although these transmitters operate at different frequencies compared to the desired signal, they may be at a closer proximity when compared to the desired base station. As a result the power levels of these so-called blocker signals can be orders of magnitude higher than that of the desired signal. The RF receiver has to be sufficiently sensitive in order to be able to demodulate the weak desired signal and it has to be able to do so in the presence of strong undesired blocker signals.

In order for the radio receiver to correctly demodulate the received radio signal, a certain signal SNR,  $SNR_{min}$ , has to be maintained. This SNR is typically in the range of 5-20dB, depending on the wireless standard. The signal power incident at the receiver is determined by: (1) the transmitted power, and (2) the nature of the wireless medium, namely the communication distance and the presence of a line-of-sight path. On the other hand, noise at the RF receiver originates from two sources: (1) thermal noise incident to the receiver antenna and (2) the RF receiver circuit's own noise. Out of all the four factors determining the received signal SNR, the transmitter power and thermal noise incident at

Figure 2.2. Blocking mask of a UMTS standard.

the antenna are not free variables. The remaining two variables are communication distance and the RF receiver's own circuit noise. For a given  $SNR_{min}$ , a lower circuit noise would make the receiver more sensitive, and therefore able to communicate over a longer distance. This is often desired because it can result in a better spectrum usage and more cost-efficient infrastructure deployment. For a particular RF receiver, the minimum signal power incident at the antenna that could result in correct demodulation is called the RF receiver sensitivity level.

The implication of the near-far problem to the resulting specifications of an RF receiver is best illustrated using a figure called a blocking mask (Fig. 2.2). In this representation, the desired signal is shown at the center of the plot and at its sensitivity level. The maximum power levels for signals at adjacent frequencies to the desired signal is also displayed. Other significant blocking signals at some large offset frequencies might also be displayed in this representation. The maximum power levels of adjacent frequencies can be set by either the wireless standard or by government regulations.

The blocking mask shown in figure 2.2 is taken from the UMTS standard. In this stan-

dard, each channel has a 3.84MHz bandwidth, with a 5-MHz channel-to-channel spacing. The standard dictates that the receiver sensitivity level has to be at least -96dBm. The closest four adjacent channels have maximum power levels that are set by the standard. Because the UMTS standard is a frequency-duplex system, it has to be able to receive while simultaneously transmitting signal back to the base station. For this reason, the largest blocker for the UMTS RF receiver is actually its own RF transmitter, which operates at a frequency offset of 200MHz from the receiver.

The ensuing discussion, along with the numerical example from the UMTS standard underlines the challenge of designing a radio-frequency receiver. A radio-frequency receiver has to maintain a very low noise level in order to meet the sensitivity requirements. However, there are blocking signals present in the environment; some of which can be 100dB larger than the desired signal. Therefore, the challenge in the design of an RF receiver is a challenge of *dynamic range*; how to maintain a low noise floor while at the same time having a sufficient full-scale range to avoid saturation due to the presence of very large signals at nearby frequencies.

All modern wireless standards employs complex modulation scheme in order to communicate more bits for a given signal bandwidth (spectral efficiency). Consequently, an equally complex demodulator is necessary in order to retrieve the pertinent information. The drive for spectrum efficiency is somewhat symbiotic with improvements in semiconductor technology (e.g. Moore's law), where, inexpensive, power-efficient digital signal processing capability is abundantly available. As a result, all modern RF receiver consists of a partition of analog and digital signal processing with an A/D converter in between the two domain<sup>1</sup>.

In order to explore the optimal strategy for partitioning the analog and digital signal processing, it is appropriate to review the type of signal operations that are necessary in an RF receiver. A popular RF receiver architecture, commonly referred to a directconversion receiver architecture, is shown in figure 2.3. This architecture consists of a single

<sup>&</sup>lt;sup>1</sup>Unless specified otherwise, the term RF receiver in this dissertation specifically refers to the analog portion of the signal processing path.

Figure 2.3. A direct-conversion receiver.

down-conversion mixer which translates the radio frequency signal down to DC or to a low frequency. Filtering can occur prior, after or both prior and after mixing. In the same figure, the amplitude of the signal of interest, the largest blocking signals and the noise floor level are also shown. Noise power are integrated over the bandwidth of interest, and it comprises of noise originating from preceding blocks as well as noise arising from the current block.

In many respect, modern RF receiver can be considered simply as a circuit to *pre-process* or *pre-condition* radio signals for A/D conversion [8]. A/D converter dynamic-range and sampling-rate limitations dictate the amount of signal processing, in particular the amount of filtering, that needs to occur in the analog domain. Since most A/D converter operates around DC, a mixer is needed to translate the signal from RF to baseband<sup>2</sup>. Recall that a sampling operation in an A/D converter would create aliasing, where signals spaced at integer multiples of the sampling-rate would be frequency-translated to overlap with each

$<sup>^{2}</sup>$ A class of subsampling RF receiver that relies on aliasing to demodulate an RF signal has been previously studied [39, 83, 53]. This type of receivers usually has a higher noise figure due to the problem of noise folding.

Figure 2.4. A/D converter specification: (a) minimum requirements, (b) signal folding due to sampling.

other. Proper anti-aliasing filters have to be designed such that undesired signal aliases are sufficiently attenuated prior to A/D conversion. Sufficient attenuation in this context is defined to be the point where the cumulative power of the undesired aliases is less than the quantization noise floor of the A/D.

In order to derive an A/D converter specification, one could begin by asking the question of what is the *minmum* necessary requirements for an A/D converter. There are only two important parameters in an A/D converter: sampling rate and resolution [108]. The minimum sampling rate necessary is set by Nyquist theorem [78]; sampling the signal at a rate of twice the signal bandwidth should be sufficient in order to digitize the information contained within the radio signal. On the other hand, the minimum resolution for the A/D

Figure 2.5. Illustration of peak-to-average power ratio problem.

converter is simply:

$$Minimum \ Resolution = SNR_{min} + PAPR \tag{2.1}$$

Since  $SNR_{min}$  relates to the *average* signal-to-noise ratio, a certain margin has to be allocated in order to accommodate the *maximum* RF signal level without saturating the A/D converter. This margin amounts to the peak-to-average power ratio (PAPR) of the RF signal (figure 2.5). Signals with large PAPR is often associated with complex, spectrallyefficient modulation schemes. For example, in orthogonal frequency division multiplexing (OFDM) modulation, N sinusoids or subcarriers are used to encode the information [105]. While the signal power of the N tones add in a root-mean-square manner ( $O(\sqrt{N})$ ), the signal maximum is simply a result of the superposition of the N tones (O(N)). This results in an increasing PAPR as N, or the number of subcarriers, is increased.

One strategy for RF receiver design is to use an A/D converter with the minimum specifications set above. For this strategy to succeed, the RF signal has to be isolated from any other signals. After filtering, the total power of all other undesired signals has to be to be smaller than the desired signal by at least a factor of  $SNR_{min}$ . In this manner, the residuals of the undesired signal would be indistinguishable from the quantization noise floor upon folding due to the sampling operation. This strategy puts a demanding requirement on the baseband filters as it would necessitate a very selective filter. For example, the first

Figure 2.6. Doubling A/D sampling-rate to reduce aliasing.

adjacent channel, which could be only tens of kHz away needs to be significantly attenuated prior to A/D conversion. As a result this strategy would result in a high power consumption for the baseband filters.

A different strategy might be taken, where both the sampling-rate and the resolution of the A/D converter is increased. For example, if the sampling-rate of the A/D is doubled, then the first-adjacent-channel signal would not be aliased down to overlap with the desired signal (figure 2.6). Since the first-adjacent channel is at a very small frequency offset with respect to the desired signal, this strategy would significantly relax the filtering requirement prior to the A/D converter and therefore reduce the power consumption of the filter circuits. However, now the resolution of the A/D has to be increased; sufficient margin has to be allocated in order to accommodate the maximum power level of the first-adjacent signal. Whereas the baseband filter requirements are relaxed, a faster, higher resolution and higher power A/D converter is necessary with this strategy.

In the end the partition of analog and digital signal processing or the placement of an A/D converter is an optimization problem in power consumption. On one end of the spectrum, an all-digital radio can be proposed where a minimum amount of filtering occurs prior to a high sampling-rate, high dynamic-range A/D conversion. Signal processing in the digital domain has the added advantages of: (1) it can be easily made programmable and (2) it can be potentially more power efficient, especially in an advanced CMOS process optimized for low-power digital operations. However, the A/D converter needed for such an architecture would consume a lot of power. On the other end of the spectrum, all filtering can be performed in the analog domain, and a power-efficient A/D converter with a Nyquist rate equal to the channel bandwidth can be used. The optimal solution would be somewhere in between these two extremes. Ultimately, the optimal solution is a system that has the lowest power for a given sensitivity level and blocker tolerance.

There are a number of A/D converter architectures, each of which has been shown empirically to be the most optimal at a certain range of conversion rate and resolution. These architectures can be generally classified into three categories: flash, multi-step and oversampled A/D converters [108, 42]. Flash A/D converters digitize the signal through comparing it with  $2^N$  reference levels in parallel, where N is the number of bits in resolution. Flash A/D converters can be operated at a very high frequency, however they consume a lot of power and are limited to low resolution conversions. Multi-step A/D converters performs the comparison in multiple steps, where in each step only  $2^M$  comparisons are made, where M is less than N. Multi-step A/D converters can be implemented iteratively (successive approximation algorithm) or in a pipelined manner. Multi-step converters are generally used for medium resolution, medium sampling-rate applications. Last, oversampling A/D converters, which will be discussed in greater detail in section 2.2.1, is suited for highresolution, low-sampling-rate applications.

We will argue in section 2.2.1 that an oversampled  $\Sigma\Delta$  converters offers a unique solution to the problem of partitioning analog and digital signal processing in an A/D converter. A  $\Sigma\Delta$  A/D converter samples the input signal at a very high rate, which helps in reducing aliasing. However, it only provides a high dynamic-range A/D conversion around a small signal bandwidth where the signal of interest resides.

To end this section, a survey on the performance of contemporary A/D converters

(b) Energy vs. resolution.

Figure 2.7. Survey of A/D converters performance [68].

and the associated power consumption is provided in figure 2.7. There are two important conclusions from this data: what level of performance is possible, and how much does it cost (power) to attain a particular performance level. First, it appears that the bandwidth vs. dynamic-range trade-off is empirically limited by sampling jitter. In this jitter-limited regime, a doubling of the sampling rate would equate to a resolution degradation of 1 bit. This trade-off demonstrates what specifications are attainable from a well-designed A/D converter. Second, this empirical data seems to suggest that there is a linear correlation between power and dynamic-range<sup>3</sup>. A doubling of the A/D dynamic-range (1-bit) would result in a doubling of circuit power. This holds especially true, based on the survey, for low- to medium-resolution converters. From the survey data, it seems that power efficiency is most easily obtained at less than 60dB dynamic range (SNDR).

### 2.2 Sigma-Delta A/D Converters

$\Sigma\Delta$  A/D have been gaining popularity as the A/D converter topology of choice for RF receivers. The increase in popularity of  $\Sigma\Delta$  A/D is attributed to its low power consumption and the relaxed anti-aliasing filter requirements due to oversampling nature of  $\Sigma\Delta$  A/D converters.

Extensive and excellent references on  $\Sigma\Delta$  A/D converters are available elsewhere [75, 81]. However, due to the central nature of  $\Sigma\Delta$  A/D conversion to this work, a brief introduction of  $\Sigma\Delta$  A/D converter along with its relevance to RF receiver design is presented in this section. Relevant notations and terminologies of  $\Sigma\Delta$  modulation is introduced.

#### 2.2.1 Short Introduction to Sigma-Delta A/D Conversion

$\Sigma\Delta$  A/D conversion, or equivalently  $\Sigma\Delta$  modulation, is a technique that enables highresolution A/D conversion using low-resolution quantizer operated at a high speed. There

<sup>&</sup>lt;sup>3</sup>This result is rather surprising, because theoretically a 1-bit increase in dynamic range would *quadruple* the power consumption of the converter [108].

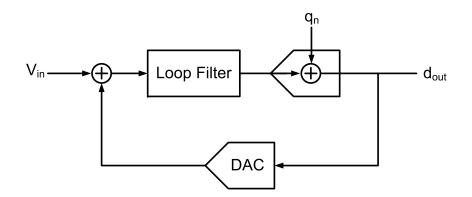

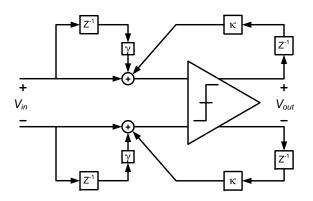

Figure 2.8. A low-pass/baseband  $\Sigma\Delta$  modulator.

are two concepts central to the operation of a  $\Sigma\Delta$  modulation, oversampling and quantization noise shaping.

Oversampling in an A/D converter, enables an increase in SNR simply by spreading the quantization noise over a larger bandwidth. If the signal is fully contained within a limited bandwidth of BW which is less than the Nyquist-rate of the quantizer  $(\frac{f_s}{2})$ , then only the quantization noise within the signal bandwidth of BW should be considered. All other signals, including the quantization noise, that resides at locations other than the frequency band of width BW can be discarded using digital filters. An oversampling ratio (OSR) is defined as the ratio between the Nyquist-rate  $(\frac{f_s}{2})$  of the quantizer and the signal bandwidth (BW):

$$OSR = \frac{f_s}{2 \cdot BW} \tag{2.2}$$

An N-bit quantizer would have an SNR of  $(1.76+6.02 \cdot N)$ dB [108]. This quantization noise is spread over a bandwidth equal to  $\frac{f_s}{2}$ ; i.e., the quantization noise is white<sup>4</sup>. Therefore, the achievable SNR with an oversampling ratio of OSR is:

$$SNR_{oversampled} = 1.76 + 6.02 \cdot N + 10 \cdot \log_{10}(OSR)$$

(2.3)

Thus, every doubling of the OSR would result in a 3dB improvement in SNR.

Quantization-noise shaping can further lower the quantization noise power within the

<sup>&</sup>lt;sup>4</sup>The white-noise assumption does not necessarily hold true for low N, where the quantization noise is highly correlated with the input signal. However, for brevity of exposition of this chapter, a white quantization noise will be assumed. More information about the validity of this assumption can be found in [75, 31].

band of interest. This is achieved by moving the quantization noise away from the band of interest. When combined with oversampling, an improvement of more than 3dB per doubling of the OSR can be achieved.

Quantization-noise shaping can be accomplished by enclosing a (loop) filter around a mixed-signal feedback comprising of a quantizer and a feedback D/A converter (figure 2.8). The loop filter can take one or many poles, and it can have a low-pass or a band-pass frequency response. The frequency-response of the loop filter will determine the frequency characteristics of the loop gain of this feedback system.

For a low-pass type modulator, the large loop gain at DC will force force the feedback D/A converter's output signal to follow the input signal as faithfully as possible. This is only possible if the low-frequency component of the modulator's output  $d_{out}[n]$  tracks the low-frequency component of the input signal. In other words, at low frequency, the quantization error is suppressed by virtue of the large loop gain. As the frequency of the input signal is increased, the loop gain at that frequency will diminish, and as a result the quantization noise will start to increase.

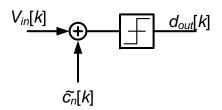

Mathematically, quantization noise can be modeled as an added white noise  $q_n[n]$ , that is introduced within the quantizer block<sup>5</sup>. The output of the modulator  $d_{out}[n]$  is composed of the input signal  $V_{in}[n]$  and the quantization noise q[n]. Because the two inputs are introduced at two different points within the loop, each of them will have a different transfer function to the output. The two different transfer functions, called the signal transfer function (STF) and noise transfer function (NTF), can be designed to have advantageous frequency characteristics.

For example, a first-order, low-pass  $\Sigma\Delta$  modulator can be designed to have a first-order noise shaping. A first-order  $\Sigma\Delta$  modulator consists of a single integrator as the loop filter.

<sup>&</sup>lt;sup>5</sup>Since a  $\Sigma\Delta$  A/D uses a low-resolution quantizer, the white-noise approximation is a rather poor approximation. For more information regarding the conditions on which this approximation is valid, the reader is referred to the work of Gray[31].

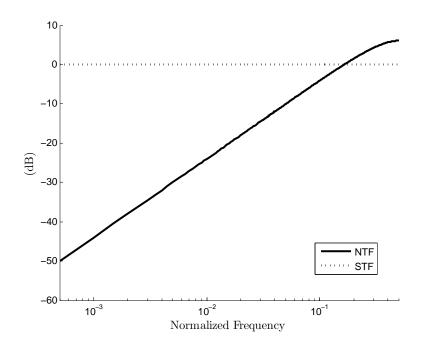

Figure 2.9. Signal and noise transfer functions for a first-order  $\Sigma\Delta$  modulator.

The following STF and NTF can be achieved:

$$STF = 1 \tag{2.4}$$

$$NTF = 1 - z^{-1} (2.5)$$

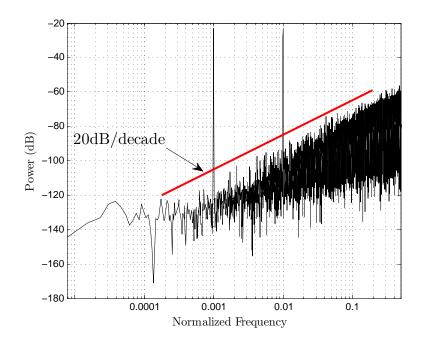

The STF is flat across frequency, while the NTF has a high-pass response (figure 2.9). In this manner, quantization noise is attenuated in the frequency of interest (low frequency), while the signal amplitude is maintained throughout the conversion. The power-spectral density plot of the output is shown in figure 2.10. A 20dB-per-decade rolloff of the quantization noise is observed as a result of a first-order noise shaping. Because the signal is oversampled, only quantization noise that resides at low frequencies matter in the resulting SNR.

Higher-order  $\Sigma\Delta$  modulator can be built by cascading stages of integrators or resonators, for a low-pass and band-pass modulator respectively. However, since there are two or more poles in the loop, stability is no longer guaranteed. The feedback loop would then need to be compensated, either in a feedforward or in a feedback manner. The benefits and drawbacks of these two compensation techniques are discussed in the following references [75, 81].

Figure 2.10. Output power spectral density of a simulated first-order  $\Sigma\Delta$  modulator.

A  $\Sigma\Delta$  A/D converter requires a reconstruction filter in the digital domain. Because the signal is oversampled, a sample-rate down-conversion is necessary in order to isolate and retrieve the signal of interest. The digital decimation filter, as the  $\Sigma\Delta$  A/D reconstruction filter is often called, is usually not a dominant power consumption contributor. Modern CMOS process allows for a very power-efficient digital computation. Moreover, although the throughput of such a filter can be high, the output of a  $\Sigma\Delta$  modulator has only a few bits. Therefore the signal-processing data path can be quite narrow.

### 2.2.2 Sigma-Delta A/D Converters in RF Receivers

As mentioned earlier, an oversampled  $\Sigma\Delta$  A/D converter offers a unique alternative among a selection of A/D converter topologies for an RF receiver. In some ways, a  $\Sigma\Delta$ A/D converter is able to break the trade-off between the need to have a fast, high resolution A/D converter and the need to have a very selective baseband filter in RF receiver.

The reason a  $\Sigma\Delta$  A/D converter is appropriate for an RF signal is precisely because of the two reasons why this type of converter works so well: oversampling and noise-shaping.

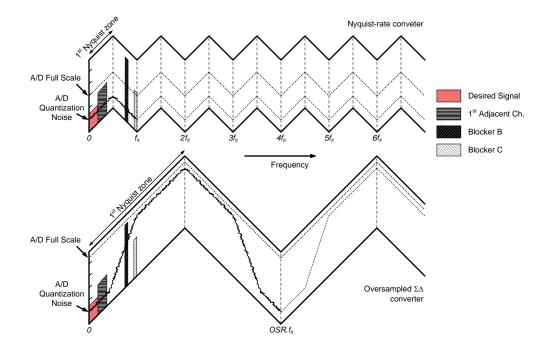

Figure 2.11. Comparison between a Nyquist-rate and a  $\Sigma\Delta$  A/D converter.

Oversampling widens the first Nyquist zones, and therefore it reduces aliasing. In other A/D converter topologies, an increase in sampling-rate would require the converter's low noise floor to be maintained across a wider conversion bandwidth. To make matter worse, since the bandwidth of the input signal is wider, the input signal power is likely to increase. As argued in section 2.1, while the quantization noise floor needs to be kept low, now the full-scale range of the A/D converter has to be increased to accommodate large blocker signals. As a result, an increase in sampling-rate would be accompanied by a necessary increase in resolution as well. Both an increase in sampling rate and resolution would surely result in an increase in power consumption.

Recall that the low quantization noise floor is only needed in the frequency band of interest, for example, near DC for a low-pass modulator. Although the full-scale range of the A/D converter has to be set to accommodate large blocker signal outside the band of interest, the noise floor at those frequencies is not critical. This is where quantization noise shaping feature of a  $\Sigma\Delta$  A/D converter really makes sense, as it provides a low quantization

noise floor *only* where it is needed. The quantization noise floor is not unnecessarily set to be at a very low level outside the band of interest.

For a comparable sampling rate and resolution, it has been shown that a  $\Sigma\Delta$  converter with its associated reconstruction filter can achieve the same power efficiency as a Nyquistrate data converter [61]. For this reason, it can be argued that the virtue of a  $\Sigma\Delta$  A/D converter can be obtained for no additional cost. It is often stated that a  $\Sigma\Delta$  A/D provides a *free* anti-alias filtering. This statement is not entirely correct. Anti-alias filtering in this type of system occurs in the digital domain.

Performing the anti-alias filtering in the digital domain has one additional advantage. In a  $\Sigma\Delta$  converter, the signal bandwidth is not explicitly defined in the analog domain. The final signal selection is done in the digital domain, through the application of digital filters. This creates an opportunity for re-programming the digital filters to accommodate change of signal bandwidths. This feature is very amenable to a concept of reconfigurable RF receiver. It should be noted, however, that if the signal bandwidth is increased, more quantization noise is also integrated. If a high-order  $\Sigma\Delta$  modulator is used, increasing signal bandwidth can come with a significant degradation in resolution as the quantization noise is shaped.

## 2.3 Reconfigurable RF Receiver Specifications

A survey of requirements for different wireless standards will be presented in this section in order to derive a set of requirements for the proposed reconfigurable RF receiver. As argued in section 2.1, the specification of an RF receiver is driven by the characteristics of the signals received at the antenna.

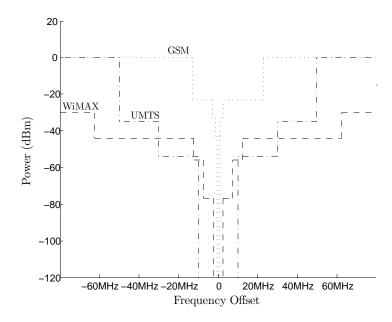

The RF signal characteristics for different standards can be summarized by a blocker mask and a sensitivity requirement. A comparison between blocker masks of three different wireless standards is shown in figure 2.12. A blocker mask provides a good representation as to the largest signals that can be expected at the antenna. Another set of requirements are derived based on the minimum SNR required for successful demodulation and the required

Figure 2.12. Comparison of blocker masks between different wireless standards.

|       | Bandwidth           | Sensitivity Level          | Min. SNR       | Max. NF        |

|-------|---------------------|----------------------------|----------------|----------------|

| GSM   | $200 \mathrm{kHz}$  | $-99 \mathrm{dBm}$         | 9dB            | 12dB           |

| UMTS  | $3.84 \mathrm{MHz}$ | -92dBm*                    | $7\mathrm{dB}$ | $9\mathrm{dB}$ |

| WiMAX | $20 \mathrm{MHz}$   | $-65 \mathrm{dBm}^{\circ}$ | 24 dB          | 11dB           |

Table 2.1. Comparison of sensitivity requirements for different wireless standards.

\* Including 25dB de-spreading gain

$^{\circ}$  Highest data-rate, with 64-QAM and 3/4 coding rate

sensitivity of the particular wireless standard. A comparison of sensitivity levels between various standards are presented in table 2.1.

The three standards illustrated in figure 2.12 and table 2.1 are chosen specifically to illustrate the range of requirements that a reconfigurable RF receiver has to satisfy. On one end, the GSM standard is a narrow-band standard, with a 200kHz signal bandwidth. It is relatively easy to design a high-resolution A/D converter for this standard. However, the GSM standard has some of the most stringent blocker mask requirement; for example, a blocker signal 3MHz away could be more than +76dB larger than the desired signal. On the other end of the spectrum, a WiMAX standard is a high data-rate wireless standard,

| Parameter        | Value                |

|------------------|----------------------|

| Bandwidth        | 200k-20MHz           |

| Max NF           | $9\mathrm{dB}$       |

| Center Frequency | $0-5.2 \mathrm{GHz}$ |

| IIP3             | -5dBm                |

| IIP2             | $65 \mathrm{dBm}$    |

| Max. Signal      | $0 \mathrm{dBm}$     |

Table 2.2. Requirements for a reconfigurable RF receiver.

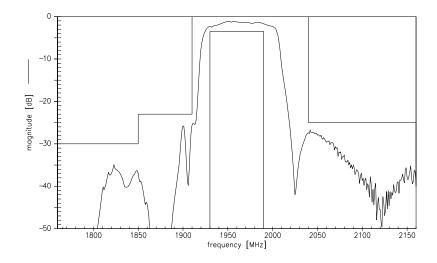

Figure 2.13. Frequency response of a SAW filter for a UMTS standard [26].

with a maximum throughput of more than 75Mbps. In order to achieve this data-rate, a wide signal bandwidth with a complex modulation scheme is used. As a result the WiMAX standard, at its highest data-rate mode, requires a 20MHz bandwidth with a minimum SNR of 24dB for successful decoding. However, the blocker mask requirement of a WiMAX standard is much less stringent than a GSM standard. For example, at greater than 10-MHz offset from the carrier, the maximum signal level of a WiMAX signal is more than 15dB lower than that of a GSM signal.

Based on this survey, a table of requirements for a reconfigurable RF receiver can be derived. These requirements are summarized in table 2.2.

It is important to mention that the high level of performance of today's RF receivers is partly due to the use of external passive filters, such as SAW filters. These passive filters operate at RF, with less than 3dB insertion loss, and can have a rejection ratio of greater than 30dB (figure 2.13). These filters reduces the dynamic-range requirements of the RF receiver, as the filters eliminate much of the largest blockers with minimum degradation in sensitivity. However, the fixed-frequency nature of these filters make them incompatible with the desire for a universally reconfigurable RF receiver. While high-quality tunable RF filters are being researched [72], they are not yet widely available.

### 2.4 Performance Comparison of Integrated Receivers

In the last decade, a significant progress has been made in incorporating a complete RF receiver in a single monolithic die. Initially, short-range standards, such as 802.11 and Bluetooth, with less stringent performance requirements were integrated within a single-die. Today, single-chip solutions exist for most of the long-range cellular standards as well. The performance of these chips is outlined in table 2.3. The different performance metrics, such as noise-figure and input-intercept points, reported for a standard reflects the trade-offs involved in meeting the requirements of the particular standard. The reported performance reflects the design decisions that result in an optimized implementation of a particular standard. For example, the receiver which has the lowest noise figure is a GPS receiver, because in this application, sensitivity is of utmost importance. Similarly, mobile cellular receivers also have to achieve a very low sensitivity while at the same time maintain a low power consumption. On the other hand, in wireless LAN standards, data-rate is the most important metric, while communication range and power consumption is of secondary importance.

In order to maintain backward compatibility with earlier versions of the wireless standards, some of the radios listed in 2.3 are in a way already 'reconfigurable'. For example, the EDGE standard uses the same signal bandwidth as GPRS; however, EDGE uses a more advanced modulation scheme (8-PSK for EDGE, compared to GMSK for GPRS) in order to obtain a higher spectral efficiency. Although both standards occupy the same signal bandwidth, the linearity requirement for EDGE standard is somewhat more stringent than GPRS

|       | Year | Standard                                 | Technology        | Power<br>(mW) | $\frac{\mathrm{NF}}{\mathrm{(dB)}}$ | IIP3<br>(dBm) | IIP2<br>(dBm) |

|-------|------|------------------------------------------|-------------------|---------------|-------------------------------------|---------------|---------------|

| [64]  | 2004 | Bluetooth                                | 130nm             | 60            |                                     |               |               |

| [56]  | 2007 | Bluetooth(EDR)                           | $130 \mathrm{nm}$ | 48            |                                     | -18           |               |

| [59]  | 2005 | 802.11g                                  | 180nm             | 324           | 5.5                                 |               |               |

| [71]  | 2006 | 802.11a/b/g                              | $180 \mathrm{nm}$ | 310           | 5.5                                 |               |               |

| [82]  | 2006 | 802.11n                                  | $90 \mathrm{nm}$  | 170           | 6                                   |               |               |

| [12]  | 2007 | 802.11n                                  | $130 \mathrm{nm}$ | 275           | 4.5                                 | 5             |               |

| [23]  | 2008 | 802.11a/g/n                              | $90 \mathrm{nm}$  | 270           | 4                                   |               |               |

| [102] | 2001 | $\operatorname{GSM}$                     | $350 \mathrm{nm}$ | 75            | 5                                   | -16           |               |

| [63]  | 2006 | $\operatorname{GSM}/\operatorname{GPRS}$ | $90 \mathrm{nm}$  | 84            | 2                                   | -25           | 46            |

| [27]  | 2005 | $\operatorname{GSM}/\operatorname{GPRS}$ | $180 \mathrm{nm}$ | 256           | 2.7                                 | -15           | 40            |

| [48]  | 2005 | GPRS/EDGE                                | BiCMOS            | 202           | 3                                   | -9            |               |

| [21]  | 2008 | GPRS/EDGE                                | $130 \mathrm{nm}$ | 140           | 2.5                                 | -12           | 45            |

| [9]   | 2005 | CDMA                                     | BiCMOS            | 151           | 3                                   |               |               |

| [38]  | 2006 | WCDMA                                    | BiCMOS            | $50^{*}$      | 9                                   | 0             | 55            |

| [104] | 2008 | WCDMA                                    | $180 \mathrm{nm}$ | 105           | 2.8                                 | -2            | 65            |

| [118] | 2007 | CDMA2000                                 | $130 \mathrm{nm}$ | 150           | 9.2                                 | 1             | 51            |

| [51]  | 2007 | TD-SCDMA                                 | BiCMOS            | 95            | 3.5                                 | -14           | 25            |

| [92]  | 2005 | GPS                                      | $90 \mathrm{nm}$  | 84            | 2                                   | 5             |               |

| [24]  | 2006 | GPS                                      | BiCMOS            | 20            | 5                                   |               |               |

Table 2.3. RF receiver performance comparison.

(\* does not include synthesizer power)

|       | Entry               | Supported Standards | Frequency Bands |

|-------|---------------------|---------------------|-----------------|

| [15]  | Broadcom BRCM2075   | Bluetooth (EDR)     | 1               |

|       |                     | GPS                 | 1               |

|       |                     | $\mathbf{FM}$       | 1               |

| [16]  | Broadcom BRCM4329   | 802.11n             | 2               |

|       |                     | Bluetooth (EDR)     | 1               |

|       |                     | $\mathbf{FM}$       | 1               |

| [52]  | Marvell             | 802.11              | 1               |

|       |                     | WiMAX               | 1               |

| [37]  | Freescale           | WCDMA/HSDPA         | 10              |

|       |                     | GSM/GPRS/EDGE       | 4               |

| [11]  | TI/Univ. of Arizona | GSM/GPRS/EDGE       | 3               |

|       |                     | CDMA2000            | 1               |

| [100] | Skyworks            | WCDMA/HSDPA/HSUPA   | 11              |

|       |                     | GSM/GPRS/EDGE       | 4               |

| [32]  | Qualcomm            | WCDMA/HSDPA/HSUPA   | 10              |

|       |                     | GSM/GPRS/EDGE       | 4               |

|       |                     | GPS                 | 1               |

Table 2.4. Comparison of multi-mode radios.

as a result of the more complex modulation scheme. In this case, the RF receiver front-end has to be designed to meet the more stringent EDGE requirement. This is reflected by the fact that EDGE receivers have higher IIP3 and IIP2 when compared to GPRS receivers. This underlines the point made earlier, that for each performance metric, a multi-standard receiver has to meet the most stringent requirement from all of the supported standards.

The initial impetus for a multi-standard receivers is the desire to maintain backward compatibility, as in the case with a GSM/EDGE receiver. From this starting point, several published examples have shown the integration of multiple radios spanning multiple standards on a single die. For the most part, cost reduction through higher integration is the reason behind the development of these multi-standard radios. A summary of multi-mode radios that have been published in the literature is presented in table 2.4.

There is a clear progression from the development of a single-chip radio, to a singlechip, multi-standard radio in the industry. There has also been a lot of research done in the realm of software-defined radio. In theory, a software-defined radio can communicate with any conceivable wireless device. However, in practice, most published examples of

|          |            | IMEC [2       | 9]            |            | UCLA [1       | 0]            | Bit        | twave [80     | , 22]         |

|----------|------------|---------------|---------------|------------|---------------|---------------|------------|---------------|---------------|

| Standard | NF<br>(dB) | IIP3<br>(dBm) | Power<br>(mW) | NF<br>(dB) | IIP3<br>(dBm) | Power<br>(mW) | NF<br>(dB) | IIP3<br>(dBm) | Power<br>(mW) |

| GSM      | 2.8        | -5            | 91            | 5          | -3.5          | 52            | 3.4        | -19           | 142           |

| WCDMA    |            |               |               |            |               |               | 3.2        | -18           | 244           |

| LTE      | 2.4        | -6            | 96            |            |               |               |            |               |               |

| CDMA2000 |            |               |               |            |               |               | 5          | -13           |               |

| 802.11   | 6.5        | -9            | 116           | 5.5        | -3.5          | 57            | 5.6        | -20           |               |

| WiMAX    | 3.8        | -11           | 105           |            |               |               |            | -20           | 183           |

| DVB-H    | 2.3        | -5            | 101           |            |               |               |            |               |               |

Table 2.5. Comparison of published software-defined radios.

Figure 2.14. Conceptual diagram of a software-defined radio.

so-called 'software-defined radios' are simply designed to comply with the requirements of the wireless standards available *today*.

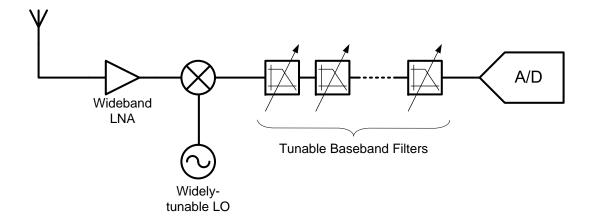

There are a number of examples of these software-defined radios in the literature, which are summarized in table 2.5. All three transceivers employ a common strategy of having a highly reconfigurable signal path. All of them uses a single-conversion receiver architecture followed by a tunable, high-order low-pass filter (figure 2.14). A single-conversion architecture is suitable in such a flexible radio, due to the ease of frequency planning, especially with respect to the location of image signals.

The UCLA receiver uses a wideband, noise-cancelling LNA. A harmonic-rejection mixer [113] is used to downconvert the RF signal to baseband, while avoiding the folding of signals

located at three times the LO frequency. The output of the mixer is filtered by a single, continuous-time RC pole before being sampled using a charge-sampling circuit [116]. A discrete-time system, consisting of a single IIR filter, two FIR filters and two sample-rate downconverters, precedes an A/D converter. The critical frequency of the discrete-time filter can be precisely tuned by changing the clock frequency and by changing the capacitance ratios within the filter. The discrete-time system used in this receiver is similar to the ones implemented in Texas Instruments' DRP receivers [65, 63]. The operation of this discrete-time system will be described in detail in section 3.2.

The IMEC receiver contains a low-band and high-band LNAs that are switched depending on the frequency band of interest. A passive mixer with a square-wave LO is used to downconvert the RF signal to baseband. The load of the passive mixer is implemented as a transimpedance amplifier biquad. The biquad is followed by a third-order low-pass filter, for a total of five poles in the receiver. The location of the five poles are programmable, however there is no discussion on the approach taken to tune the critical frequency of this filter. Finally, a variable-gain amplification (VGA) occurs prior to A/D conversion.

## 2.5 Performance Limitations of RF Receivers

In the preceding sections, a performance comparison of integrated receivers was presented. In an effort to predict an attainable level of performance for current and future RF receivers, several limitations, fundamental, practical or otherwise, will be evaluated in this section.

### 2.5.1 Linearity Limitation

A transistor is not a linear device. It is only approximately linear if operated under a limited operating conditions, namely under a very small input or output signal swing. However, operating with a limited signal range comes with a noise penalty as it limits the acceptable gain of the preceding circuit blocks. Thus this intrinsic transistor limitation

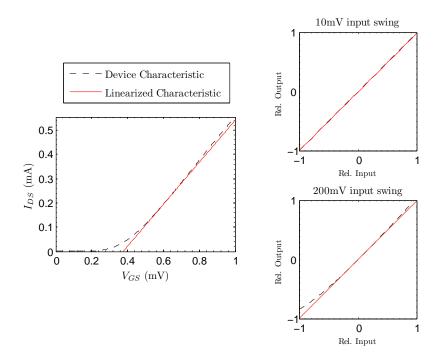

Figure 2.15. MOS transistor voltage-to-current conversion characteristics.

translates again into a dynamic-range limitation. There is an inherent trade-off between signal range, which is limited by distortion, to the resulting circuit noise.

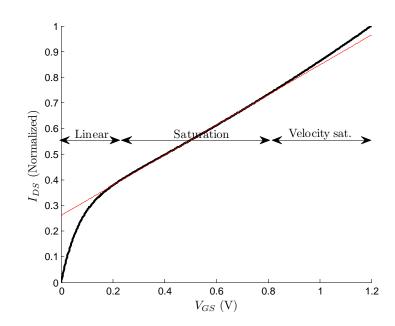

One of the most fundamental operations in any circuit is a voltage-to-current conversion (V-to-I conversion). This is a natural operation for a MOS transistor, where a modulation of the gate voltage would result in a similar modulation of the drain-source current. The voltage-to-current transfer characteristic of a MOS transistor is illustrated in figure 2.15. The two insets in figure 2.15, displays the linearity of the V-to-I conversion under two different input signal ranges (plots are normalized in both axes). It can be clearly seen that operating under a larger input swing generates a larger deviation from a linear transfer characteristic.

Second- and third-order distortions typically dominate in an RF circuit. Distortion in a nonlinear device can be characterized using a polynomial expansion of the device transfer characteristics [73]. In theory, the polynomial expansion can be expanded into very high order; resulting in high-order (e.g. fourth, fifth, sixth, etc) distortion. However, in practice, second- and third-order distortions have much larger amplitude than the higher order terms,

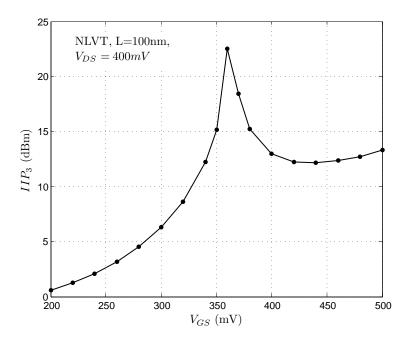

Figure 2.16. Achievable IIP3 from a deep sub-micron transistor.

making them the dominant distortion mechanisms. There are several metrics that can be used to characterize the 'magnitude' of the second- and third-order distortions. Two of the most commonly used are the input-intercept points, namely IIP2 and IIP3 for second- and third-order distortions respectively [49].

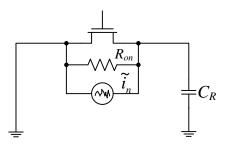

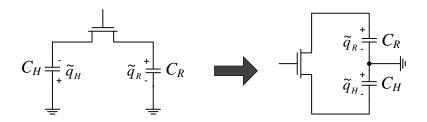

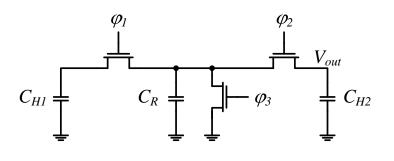

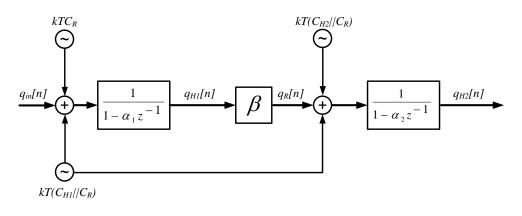

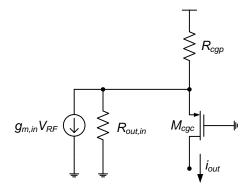

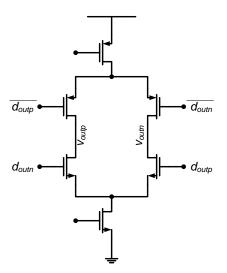

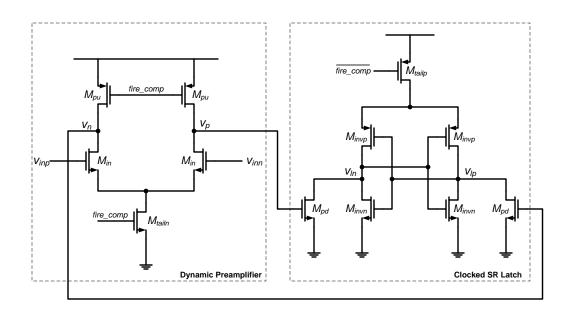

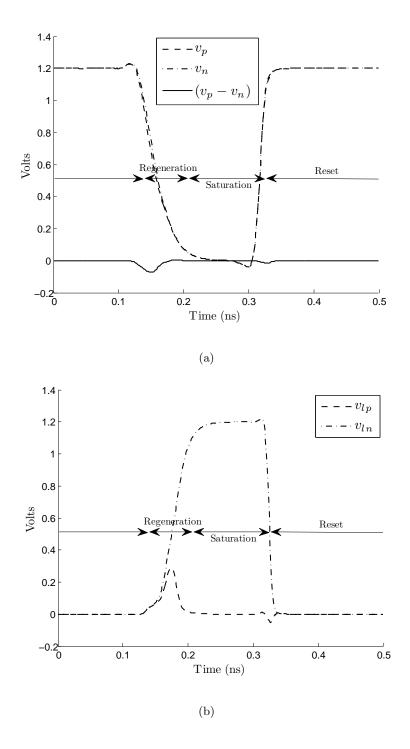

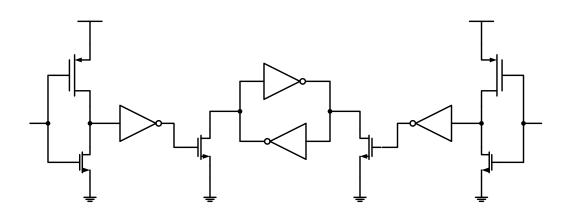

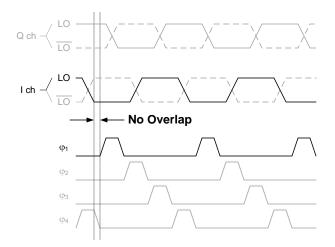

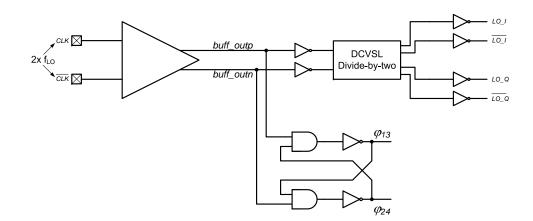

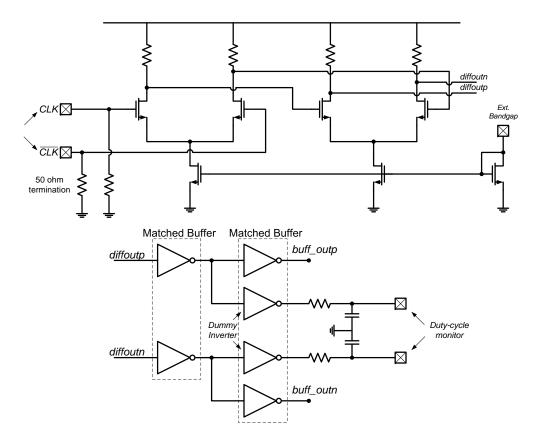

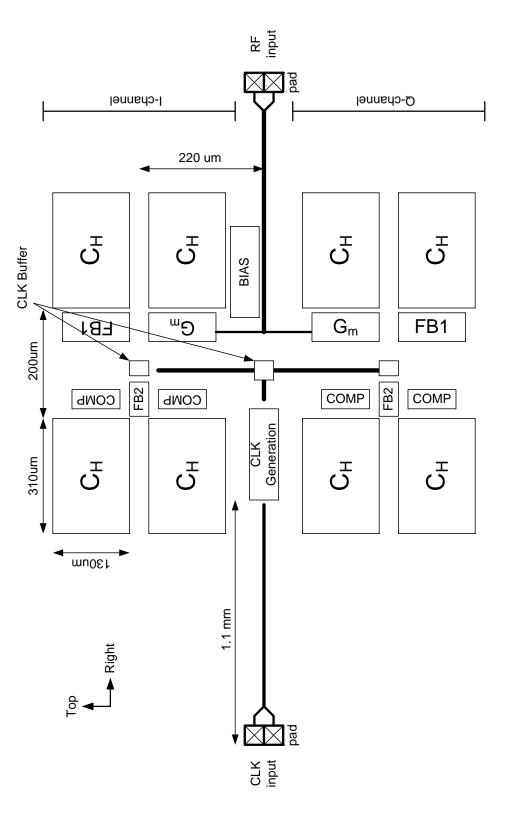

A characterization of the third-order distortion in a MOS V-to-I conversion is shown in figure 2.16. In this figure, an IIP3 resulting from a V-to-I conversion is plotted as a function of gate DC bias. The drain voltage of transistor is connected to an ideal voltage source to decouple the distortion resulting from drain-to-source voltage modulation. Although a peak IIP3 of more than +20dBm is theoretically possible, it is only achievable within a narrow window of DC bias. Such a narrow window would be hard to achieve in a production setting without calibration. From this analysis, one can assume that a realistic IIP3 from modern CMOS transistors would be in the +15dBm range<sup>6</sup>.