### **Low Power Band to Band Tunnel Transistors**

Anupama Bowonder

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2010-154 http://www.eecs.berkeley.edu/Pubs/TechRpts/2010/EECS-2010-154.html

December 15, 2010

Copyright © 2010, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Low Power Band to Band Tunnel Transistors

By

### Anupama Bowonder

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Chenming Hu Professor Sayeef Salahuddin Professor John Morris

Fall 2010

| The dissertation Transistors, is | on of Anupama Bowonder, titled Low Powe sapproved: | r Band to Band Tunnel |

|----------------------------------|----------------------------------------------------|-----------------------|

|                                  |                                                    |                       |

|                                  |                                                    |                       |

| Chair                            |                                                    | Date                  |

| -                                |                                                    | Date                  |

|                                  |                                                    |                       |

| -                                |                                                    | Date                  |

University of California, Berkeley Fall 2010

### **Abstract**

Low Power Band to Band Tunnel Transistors

by

#### Anupama Bowonder

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Chenming Hu, Chair

As scaling continues, the number of transistors per unit area and power density are both on the rise. A reduction in  $V_{dd}$  is highly desirable to reduce power consumption. For MOSFETs however, this would mean scaling the threshold voltage to maintain performance and thereby enhancing the off current and static power consumption since MOSFETs are limited to a swing of 60 mV/decade at best. A low voltage transistor that allows  $V_{dd}$  scaling to 0.5V and below is highly desirable.

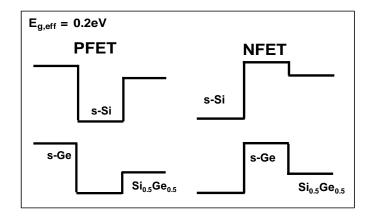

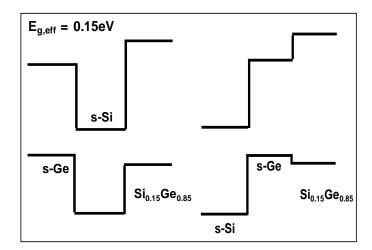

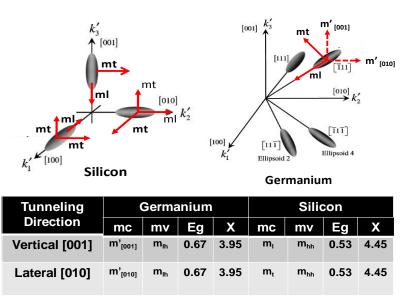

In this thesis, gate induced band-to-band tunneling transistors are explored as a low voltage alternative because of their potential to achieve lower than 60 mV/decade turn-off. Since BTBT is strongly dependant on the band gap of the semiconductor, moving from Silicon to Germanium to lower band gap materials can help scale  $V_{dd}$ . Biaxially strained  $Si_{1-x}Ge_x$  based heterostructures can provide ultra low effective band gaps. Strain is used to engineer complimentary  $Si_{1-x}Ge_x$  heterostructures with low effective band gap for both N and P type transistors. The design and fabrication of heterostructure based tunnel transistors is explored to help scale  $V_{dd}$  to 0.5 V and below. Dopant engineering techniques to enhance the electric field are also explored both with simulations and experiments.

# Table of Contents

| Acknowledgements                                                                          | iv  |

|-------------------------------------------------------------------------------------------|-----|

| Chapter 1 – Introduction                                                                  | 1   |

| •                                                                                         |     |

| 1.1 Scaling and power density                                                             | . 1 |

| 1.2 Limitations of MOSFET voltage scaling 1.3 Passage habitative and discontains autilian |     |

| 1.3 Research objective and dissertation outline 1.4 References                            | 3 4 |

| 1.4 References                                                                            | 4   |

| <b>Chapter 2 - Homojunction PIN Tunnel FETs</b>                                           | 6   |

| 2.1 Structure and operation of BTBT based FETs                                            | 6   |

| 2.2 WKB approximation and tunneling probability                                           | 7   |

| 2.3 TCAD simulations of TFETs                                                             | 10  |

| 2.4 High-K metal gate silicon TFETs                                                       | 12  |

| 2.5 Ultra thin body silicon TFETs                                                         | 20  |

| 2.6 References                                                                            | 25  |

| Chapter 3 – Lateral Pocket TFETs as a Path to Scale $V_{dd}$                              | 27  |

| 3.1 Introduction                                                                          | 27  |

| 3.2 Lateral pocket TFET design                                                            | 27  |

| 3.3 Experimental design                                                                   | 32  |

| 3.4 Experimental results                                                                  | 33  |

| 3.5 Conclusions                                                                           | 39  |

| 3.6 References                                                                            | 39  |

| Chapter 4 – Biaxial Strain Engineering for Sub-0.5V Operation Si/Ge Hetero                |     |

| TFET Design                                                                               | 40  |

| 4.1 Introduction                                                                          | 40  |

| 4.2 Effective tunneling bandgap                                                           | 40  |

| 4.3 Biaxially strained hetero TFET structures                                             | 43  |

| 4.4 Engineering symmetric effective tunneling bandgaps for complimentary TFETs            | 45  |

| 4.5 Heterostructure TFET optimization                                                     | 50  |

| 4.6 Conclusions                                                                           | 56  |

| 4.7 References                                                                            | 57  |

| Chapter 5 – Biaxial Strain Engineering for Sub-0.5V Operation Si/Ge Hetero            |    |

|---------------------------------------------------------------------------------------|----|

| TFET Design                                                                           | 59 |

| 5.1 Introduction                                                                      | 59 |

| 5.2 Strained Si <sub>1-x</sub> Ge <sub>x</sub> on silicon heterostructure MOSFET GIDL | 59 |

| 5.3 Strained silicon on relaxed germanium heterostructure MOSFET GIDL and             |    |

| verification of hetero band to band tunneling concept                                 | 64 |

| 5.4 Impact of mechanical strain on heterostructure MOSFET GIDL                        | 67 |

| 5.5 References                                                                        | 70 |

| Chapter 6 – Bulk Germanium Homojunction and Heterostructure TFET                      |    |

| Processing                                                                            | 71 |

| 6.1 Introduction                                                                      | 71 |

| 6.2 Hetero TFET processing concerns                                                   | 71 |

| 6.3 Gate last hetero-TFET processing                                                  | 73 |

| 6.4 Gate first hetero-TFET processing on bulk germanium substrate                     | 74 |

| 6.5 References                                                                        | 85 |

| Chapter 7 – Conclusion                                                                | 87 |

| 7.1 Summary                                                                           | 87 |

| 7.2 Suggestions for future work                                                       | 88 |

| Appendix A                                                                            | 91 |

| Appendix B                                                                            | 93 |

## Acknowledgements

Firstly I would like to express my deepest gratitude to my advisor Professor Chenming Hu for all his guidance, support and encouragement through my entire graduate career at UC Berkeley. I thank him for helping me become a better researcher and for me helping through my interaction with him in group meetings understand how to question and constantly challenge yourself so no detail is missed. I would also like to thank Professor John Morris for serving both on my qualifying exam committee and my dissertation committee. I would like to thank Professor Sayeef Salahuddin for serving on my dissertation committee and for his valuable insights in our weekly group meetings. I would like to thank Professor Tsu Jae King for her invaluable processing advice and insights during our weekly group meetings and for supporting Microlab related requests. I would like to thank Professor Vivek Subramaniam for serving as the chain on my qualifying exam committee.

I would like to express sincere thanks to all the Microlab staff without whom none of my experiments would have been possible. In particular I would like to thank Sia Parsa and Bob Hamilton for always listening to my complaints and trying to help with keeping the lab MOS clean. I would like to thank Joe Donnelly for all his support with Novellus. I will always remember the wonderful conversations with Joe while running Novellus. I would like to thank Evan Stateler for all his invaluable support of Picosun, ASML and Centura. Only Joe and Evan can keep Novellus and ASML running along and still smile when we make annoying requests.

I would like to thank Dr. Prashant Majhi and Dr. H.H. Tseng for giving me the opportunity to work at SEMATECH and make TFETs when this project was still very young.

I would like to thank all the device group members for making device group so incredibly awesome. In particular I would like to thank Pratik Patel and Cheuk Chi Lo. We started graduate school together in the device group, we studied for our prelims together and we have been through the ups and downs of Microlab and graduate school together. I will forever be thankful for their friendship and support through all the failures and successes of graduate school. I would also like to thank Kanghoon Jeon, Chun Wing Yeung and Jack Yaung for their support, help and friendship and for being great group-mates. I would like to thank Zach Jacobson for being a good friend and for always helping to keep things funny and interesting in my life. I would like to thank all the senior students (Joanna Lai, Sriram Balasubramaniam, Donovan Lee, Vidya Varadarajan, Chung Hsun Lin) who helped welcome me and teach me so much about fabrication in the lab.

I would like to thank DARPA STEEP and MARCO MSD for financial support for this project.

I would like to thank my parents for anything and everything that I am today. Without their love, support and encouragement I would not be who I am today. They always pushed me to do better and push the limit and try and achieve even the hardest goal. I would like to thank my father for supporting me to move from home and come to the US to get an education at an early age. Without his support I would never had made it. My dad has taught me the importance of hard work, sincerity, honesty and not taking anything for granted. I will always remember how incredibly proud he was of me getting a PhD from UC Berkeley and even though he is not with me to see me go through this huge step in life, I know I have made him proud. I would like to thank my mom for being there for me through everything in life and for making me a stronger person. Without their infinite love and support I would never have made it this far.

Lastly I would like to thank Pratik for being so incredible! I can't imagine getting through graduate school without his companionship, support, friendship and love.

# Chapter 1

### Introduction

#### 1.1 SCALING AND POWER DENSITY

Generations of CMOS technologies have thrived from scaling transistor dimensions. While scaling primarily drives cheaper and denser integrated circuits because of the reduced area, it also drives faster circuits. The increase in circuit density and functionality yields higher computing power at the cost of increased power consumption per chip. As the number of transistors per unit area increases the rising power density leads to severe packaging/thermal management concerns. There is also the issue of increased leakage power and its impact on the battery life of electronic equipment.

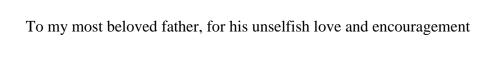

Figure 1.1(a) Active power consumption has been increasing with shrinking technology nodes (b) Standby leakage power also increasing with shrinking technology nodes [1.1]

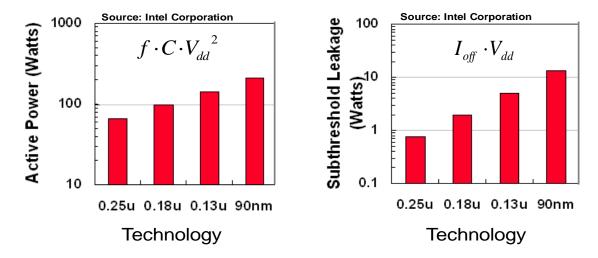

Figure 1.1(a) and 1.1(b) illustrate the increase in active power consumption and standby leakage (subthreshold leakage) power consumption for various CMOS technology nodes [1.1]. The active and standby power is seen to increase steadily with scaling transistor dimensions. As shown by the equations embedded in the figures both active and standby power scale with the operation voltage ( $V_{dd}$ ) and can therefore be reduced by scaling  $V_{dd}$ . Figure 1.2 shows that  $V_{dd}$  scaling has however remained stagnant at  $\sim 1V$  for several technology generations now.

#### 1.2 LIMITATIONS OF MOSFET VOLTAGE SCALING

Figure 1.2  $V_{dd}$  scaling has however remained stagnant at ~ 1V for several technology generations now [1.1]

The primary challenge in scaling  $V_{dd}$  comes from a basic limitation in the MOSFET operation mechanism. A MOSFET relies on the injection of carriers over a potential barrier which is modulated by the gate. Therefore the MOSFET current is exponentially dependant on the gate voltage as seen in 1.1.

$$I_d \propto n_s \propto e^{(rac{q \varphi_s}{kT})} \propto e^{(rac{q V_g}{\eta kT})}$$

1.1

Since  $e^{(\frac{qV_g}{\eta kT})}$  increases by 10 for every  $\eta \times 60 \text{mV}$  of gate voltage, the MOSFET turn on (subthreshold swing, S) is limited to 60 mV/decade increase in current. To maintain high performance,  $V_{dd}$  scaling would require threshold voltage ( $V_t$ ) scaling as seen in 1.2.

$$I_{on} \propto (V_{dd} - V_t)^{\alpha} \tag{1.2}$$

Since the subthreshold swing (S) is 60mV/decade at best, scaling the threshold voltage would lead to an exponential rise in standby leakage current of the transistor.

$$I_{off}(V_g = 0) = I_d(V_g = V_t)e^{-\frac{V_t}{S}}$$

1.3

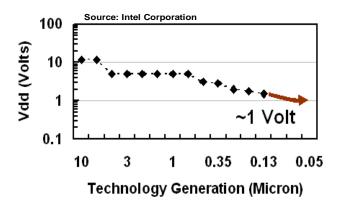

Figure 1.3 demonstrates this increase in leakage power with scaling technology nodes [1.1].

Figure 1.3 Leakage power as a percentage of total power consumption has been on the rise with shrinking technology nodes [1.1].

The most obvious means to enable  $V_{dd}$  scaling without a hit in performance would involve transistors with smaller than 60 mV/decade turn off. Transistors which inject carriers through the potential barrier (quantum mechanical tunneling) instead of over the barrier and mechanical switched could overcome the 60 mV/decade turn off and allow for low voltage operation.

#### 1.3 RESEARCH OBJECTIVES AND DISSERTATION OUTLINE

This dissertation deals with the exploration and design of novel tunneling based transistors (TFET) [1.2-1.7] and the pursuit of the most optimal TFET structure with steepest turn on characteristic and highest  $I_{on}/I_{off}$  at a low operating voltage.

Chapter 2 deals with the structure and operation of the simplest TFET design – a gated PN diode. Through the basics of tunneling physics the key parameters that affect TFET performance are determined – electric field and effective bandgap. This chapter also deals with experimental work on bulk silicon (Si) TFETs with high-k and metal gate and the process development required to tune an existing CMOS baseline process at SEMATECH to fabricate TFETs. Electrical characterization and detailed analysis of the devices is also presented. Finally experimental work on ultra thin body silicon TFETs with raised germanium (Ge) source and drain is also presented.

Chapter 3 deals with the use of dopant engineering to enhance the electric field [1.8,1.9] and therefore TFET performance enabling  $V_{dd}$  scaling to below 0.5V. Dopant pockets are thin regions of dopant opposite in type to the source dopant that can be incorporated in addition to low bandgap materials for even higher performance at ultra low voltages. Simulations are used to understand the operation and optimize a silicon pocket TFET design. Experimental data which confirms the superior behavior of the pocket TFET over a simple PIN TFET is presented. Finally the formation of accidental MOSFETs when creating pocket TFETs is also discussed.

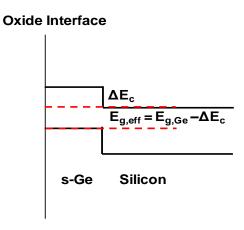

Chapter 4 deals with the use of biaxial strain engineering to obtain the lowest possible effective bandgap for tunneling and therefore enhance TFET performance while still

maintaining a high  $I_{on}/I_{off}$ . Since TFET performance is limited by the BTBT generation rate which is exponentially dependant on the effective tunneling bandgap of the semiconductor, the obvious means to enhance TFET performance and scale  $V_{dd}$  is by scaling this effective tunneling bandgap. While this can be achieved by moving from silicon to ultra low bandgap III-V materials, these materials with issues like poor dielectric interface quality and low density of states[1.10]. Further homo junction TFETs in these ultra low bandgap materials exhibit degraded  $I_{on}/I_{off}$  despite the  $I_{on}$  enhancement because of enhanced  $I_{off}$ . Simulations are used to explore biaxial strain engineering of silicon and germanium based heterostructures to achieve ultra low effective tunneling bandgap without a severe  $I_{off}$  penalty. Further strain engineering is also explored to achieve symmetric N and P hetero TFETs which can enable  $V_{dd}$  scaling to below 0.4V.

Biaxial strain has been researched greatly for enhanced mobility and performance in MOSFETs [1.11-1.13]. Chapter 5 explores electrical measurements of gate induced band to band tunneling (GIDL) from biaxial strained heterostructure MOSFETs as preliminary verification of enhanced tunneling across heterostructures with reduced effective bandgap. The temperature dependence of the GIDL current and impact of mechanical strain on the GIDL current from such biaxial strained heterostructures is also presented.

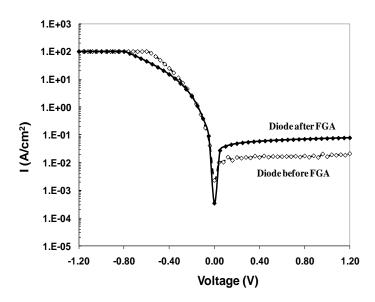

As seen in chapter 5 when working with relaxed germanium layers on a silicon substrate to create heterostructure TFETs, the junction leakage is very high and overshadows the tunneling behavior close to turn on. This high leakage when using relaxed epitaxial layers is largely attributed to the large dislocation density caused during strain relaxation. Bulk germanium substrates could however help solve this problem as long as implant damage is annealed sufficiently. Chapter 6 explores the use of bulk germanium substrates to fabricate homojunction and biaxial strain heterostructure TFETs. Several essential modules required to fabricate hetero TFETs on germanium substrates are implemented and explored in detail. Chapter 7 provides an overall conclusion as well as possibilities for future work.

#### 1.4 REFERENCES

- [1.1] S. Borkar, "Getting gigascale chips: Challenges and opportunities in continuing Moore's law", ACM Queue, 1(7):26–33, Oct. 2003.

- [1.2] T. Y. Chan, J. Chen, P. Ko, C. Hu, "The impact of gate-induced drain leakage current on MOSFET scaling", International Electron Devices Meeting, Vol.33, pp: 718-721, 1987

- [1.3] W. M. Reddick, G. A. Amaratunga, "Silicon surface tunnel transistor," Applied Physics Letters, vol.67, no.4, pp.494-496, Jul 1995

- [1.4] C. Aydin, A. Zaslavsky, S. Luryi, S. Cristoloveanu, D. Mariolle, D. Fraboulet, S. Deleonibus, "Lateral interband tunneling transistor in silicon-on-insulator," Applied Physics Letters, vol.84, no.10, pp.1780-1782, Mar 2004

- [1.5] K. K. Buwalka, M. Born, M. Schindler, M. Schmidt, T. Sulima and I. Eisele, "P-Channel Tunnel Field-Effect Transistors down to Sub-50nm Channel Lengths", Japanese Journal of Applied Physics, 45, pp. 3106 -3109, 2006

- [1.6] Chenming Hu, "Green transistor as a solution to the IC power crisis," Solid-State and Integrated-Circuit Technology, 2008, ICSICT 2008. 9th International Conference on, pp.16-20, 2008

- [1.7] A. Bowonder, P. Patel, K. Jeon, J. Oh, P. Majhi, H. H. Tseng, C. Hu; , "Low-voltage green transistor using ultra shallow junction and hetero-tunneling," Junction Technology, 2008. IWJT '08, pp.93-96, 15-16 May 2008

- [1.8] V. Nagavarapu, R. Jhaveri, J.C.S. Woo, "The Tunnel Source (PNPN) n-MOSFET: A Novel High Performance Transistor," Electron Devices, IEEE Transactions on, vol.55, no.4, pp.1013-1019, April 2008

- [1.9] P, Patel, K. Jeon, A. Bowonder, C. Hu, "A Low Voltage Steep Turn-Off Tunnel Transistor Design", Simulation of Semiconductor Processes and Devices, 2009, SISPAD '09. International Conference on, vol., no., pp.1-4, 9-11 Sept. 2009.

- [1.10] J. A. del Alamo, D. H. Kim, "The prospects for 10 nm III-V CMOS," VLSI Technology Systems and Applications (VLSI-TSA), 2010 International Symposium on, pp.166-167, 26-28 April 2010

- [1.11] K. Uchida, R. Zednik, C. H. Lu, H. Jagannathan, J. McVittie, P. C. McIntyre, Y. Nishi, "Experimental study of biaxial and uniaxial strain effects on carrier mobility in bulk and ultrathin-body SOI MOSFETs", Electron Devices Meeting, 2004. IEDM Technical Digest. IEEE International, pp. 229-232, 13-15 Dec. 2004

- [1.12] M. L. Lee, E. A. Fitzgerald, M. T. Bulsara, M. T. Currie and A. Lochtefeld, "Strained Si, SiGe, and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors", J. Appl. Phys. **97**, pp.011101-011101-28, Jan 2005

- [1.13] J. Welser, J. L. Hoyt, S. Takagi, J. F. Gibbons, "Strain dependence of the performance enhancement in strained-Si n-MOSFETs," Electron Devices Meeting, 1994. IEDM '94. Technical Digest, International, pp.373-376, 11-14 Dec 1994

# Chapter 2

## Homojunction PIN Tunnel FETs

#### 2.1 STRUCTURE AND OPERATION OF BTBT BASED FETS

A low voltage transistor that allows  $V_{dd}$  scaling to below 0.5V is highly desirable for reducing the power consumption of future ICs. Gated PN diode transistors based on band-to-band tunneling (BTBT) [2.1-2.8], are not limited by 60 mV/decade turn-off, and are being heavily researched as a low voltage CMOS alternative.

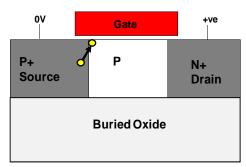

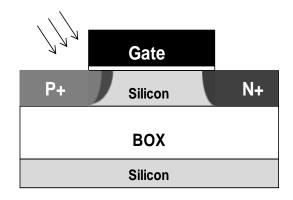

Figure 2.1 Illustration of the simplest PIN N-type Tunnel FET. The TFET is asymmetric and is a three terminal device. In the on-state the drain and gate are biased positive.

Figure 2.1 is an illustration of the simplest N-type BTBT based transistor. It is a three terminal device with a P+ doped source and N+ doped drain. A positive gate bias bends the bands down in the P+ source. With sufficient band bending, overlap occurs between filled valence band states and empty conduction band states. BTBT occurs in the source near the surface generating electron and holes. A positive  $V_{\rm ds}$  reverse biases the source-drain junction and the drain collects the BTBT generated electrons. The arrow in Figure 2.1 indicates the path along which BTBT occurs generating electrons and holes at the ends of the tunnel path.

When the valence band and conduction band extrema of a material are located at the same point in k space, direct BTBT occurs between the two extrema. BTBT can be thought of as an electron penetrating the forbidden gap along the imaginary k axis and making a smooth transition from one band into the other band [2.9]. While in classical mechanics an electron of energy E cannot enter into a region with a potential energy U > E because it would have to possess a negative kinetic energy, in quantum mechanics the negative kinetic energy represents a wave with attenuating amplitude [2.10]. If for example the wave function is

$$\psi = Ae^{(\pm ikx)}$$

k becomes imaginary or  $ik = \alpha$  being real in the potential barrier region. Thus in quantum mechanics even if an electron has E < U the wave function of the electron attenuates as it propagates but is not zero within the barrier and the electron has a finite probability of getting through the barrier region. The transmission probability through the barrier depends on both the width of the barrier and the height of the barrier.

#### 2.2 WKB APPROXIMATION AND TUNNELING PROBABILITY

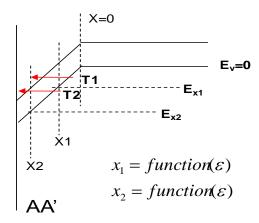

Figure 2.2 Simplified illustration of a band diagram along a cutline in the P+ source when a positive gate voltage causes the bands to bend down. Several different tunneling paths exist with overlap of valence and conduction bands. x1 and x2 are starting and ending points of a tunneling path for a given energy and vary with the specific path.

Figure 2.2 is a simplistic illustration of the band diagram along a cutline in the P+ source bending down with positive gate voltage. The scenario presented shows sufficient overlap of valence and conduction bands and two tunneling paths at two different energies ( $E_{x1}$  and  $E_{x2}$ ) are illustrated.  $x_1$  and  $x_2$  represent the starting and ending points of a tunneling path for a given energy and therefore vary with the specific tunneling path. In order to calculate the number of carriers generated by BTBT along the various tunneling paths, the tunneling probability along each specific tunneling path needs to be computed. The following section explains the details of such a calculation. If the potential varies slowly with distance the WKB (Wentzel-Kramers-Brillouin) approximation can be used to find the solution of the electron wave function [2.10]. When making the WKB approximation, if the change in potential energy over the decay length is smaller than the magnitude of the kinetic energy (E – U) then the transmission probability or tunneling probability through the barrier region

$$T = \exp(-2i\int_{x_1}^{x_2} K dx)$$

2.2

k being the wave vector or dispersion relation within the band gap and x1 and x2 are starting and ending points of the tunneling path.

The dispersion relation within the bandgap can be calculated in many different ways. The simplest dispersion relation, the parabolic one band relation [2.11]

$$k = \frac{i\sqrt{2m_r}}{hbar} \cdot \sqrt{Eg - qFx}$$

2.3

$$\frac{1}{m_r} = \frac{1}{m_c} + \frac{1}{m_v}$$

2.4

is obtained by conservation of energy of the carrier tunneling from the valence band to the conduction band. Momentum conservation is implicit in this assumption.

$$E_{v} - \frac{hbar^{2} \cdot k^{2}}{2m_{v}} + qFx = E_{c} + \frac{hbar^{2} \cdot k^{2}}{2m_{c}}$$

2.5

It is well known that this dispersion relation is most appropriate when the carrier is close to the conduction band edge or valence band edge. For carriers tunneling from the valence band to the conduction band, it is more accurate to use a dispersion relation like *Franz' Symmetric Two Band Relation*. This is a theoretically proven dispersion relation [2.11] which, is applicable to simple two band semiconductors and can take into account unequal effective masses near the conduction and valence band edges.

$$K = \frac{K_c K_v}{\sqrt{K_c^2 + K_v^2}}$$

2.6

$$K_c(x,\varepsilon) = \frac{\sqrt{2.m_c(x)|E_c(x) - \varepsilon|}}{h}$$

$$K_{\nu}(x,\varepsilon) = \frac{\sqrt{2.m_{\nu}(x) |\varepsilon - E_{\nu}(x)|}}{h}$$

2.8

x is the position and  $\varepsilon$  is the energy for a specific tunneling path.

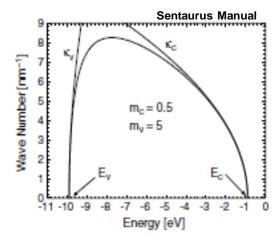

Figure 2.3 is a comparison between single and two band dispersion relations illustrating why the two band relation is more accurate when considering tunneling within the bandgap of the semiconductor from the valence band to the conduction band.

Figure 2.3 A comparison of single and two band dispersion relations illustrating that the two band relation is more accurate when considering tunneling within the bandgap of the semiconductor from the valence band to the conduction band.

Assuming continuity in all 3 directions the tunneling current is a product of 3d density of states and the velocity in the tunneling direction weighted by the transmission probability in the tunneling direction [2.10].

$$J = q \iiint \frac{2}{h^3} T \cdot v_x \cdot (f_v - f_c) \cdot dp_x dp_y dp_z$$

2.9

Assuming that the valence band is fully occupied by carriers and the conduction band states are fully unoccupied and available to receive states,  $f_v - f_c = 1$ .

$$J = q \iiint \frac{2}{h^3} T \cdot v_x \cdot dp_x dp_y dp_z$$

3.0

If

$$E_x = \frac{p_x^2}{2m_r}; \ E_{perpen} = \frac{p_y^2 + p_z^2}{2m_y} = \frac{p_{perpen}^2}{2m_y}$$

3.1

We can do a transformation from momentum space to energy space as shown below

$$dp_{y}dp_{z} = 2 \cdot \pi \cdot p_{perpen} \cdot dp_{perpen}$$

3.2

$$2 \cdot \pi \cdot m_{v} dE_{perpen} = 2 \cdot \pi \cdot p_{perpen} \cdot dp_{perpen}$$

3.3

$$dE_x = v_x \cdot dp \tag{3.4}$$

and the current can be expressed as

$$J_{BTBT} = q \iint \frac{2}{h^3} .2.\pi . m_r . T. dE_x dE_{perpen}$$

3.5

Both  $E_{\text{perpen}}$  and  $E_x$  cannot exceed the total overlap energy (overlap of empty conduction band states with filled valence band states). From this the BTBT generation rate per unit volume can be computed as shown below.

$$G_{rate} = \int_{0}^{E_{\text{max}}} q \cdot \frac{4}{h^3} \cdot \pi \cdot m_r \cdot T \cdot \frac{dE}{dx} dE_{perpen}$$

3.6

This generation rate can be simplified by assuming a constant E field to give a relationship which clearly details the parameters that affect it

$$G_{BTBT} = A_{BTBT} \frac{E^2}{\sqrt{E_g}} \exp(-B_{BTBT} \frac{E_g^{3/2}}{E})$$

3.7

$$A_{BTBT} = \frac{\pi . m_r^{1/2} . q^2}{9h^2} \qquad B_{BTBT} = \frac{\pi^2 m_r^{1/2}}{qh}$$

3.8

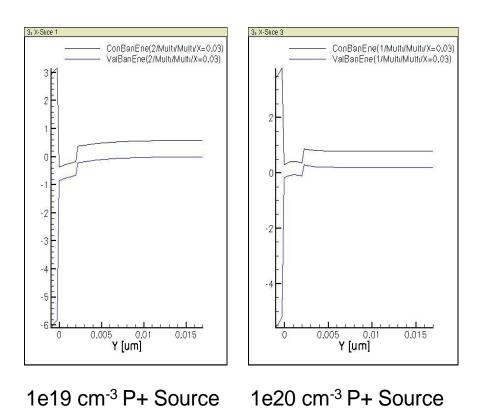

From (3.6) the tunneling design parameters that can be tuned for better tunneling performance are the electric field and the bandgap of the semiconductor. Lower bandgap and larger electric field are desired for enhanced generation rate. The electric field in the source can be enhanced by doping the source heavier

$$E_{Si} = -\frac{q \cdot Na \cdot W_{dep}}{C_{or}}$$

3.9

Thin heavily doped pockets doped opposite to the source and either on top of the source or adjacent to the source can also be used to the enhance the electric field further. Since BTBT is strongly dependant on the bandgap ( $E_g$ ) of the semiconductor, moving from silicon ( $E_g$ =1.12eV) to germanium ( $E_g$ =0.67eV) to InAs ( $E_g$ =0.36eV) and further to heterostructures [2.6] of even lower effective  $E_g$  can help lower  $V_{dd}$  to below 0.5V [2.8, 2.12].

#### 2.3 TCAD SIMULATIONS OF TFETS

TCAD simulators such as Synopsis' Sentaurus are equipped to self consistently compute

BTBT current in TFETs. A specified TFET structure is overlapped with a meshing specification so as to create numerous grid points within the entire structure. When calculating BTBT current, the simulator dynamically searches for overlap between valence and conduction bands and then computes the generation rate along various tunneling paths.

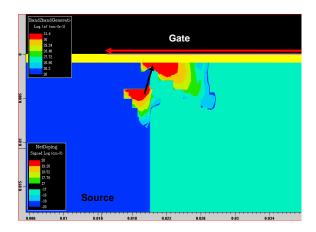

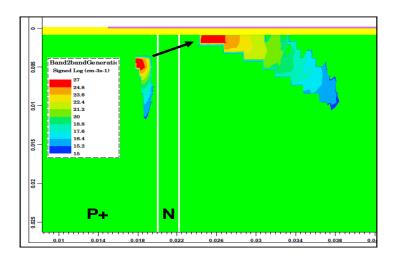

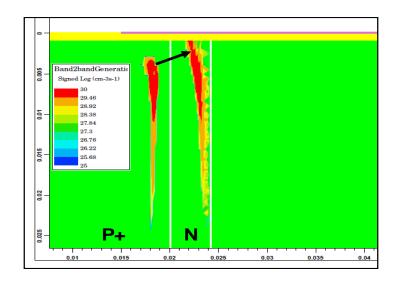

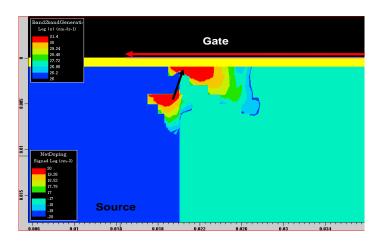

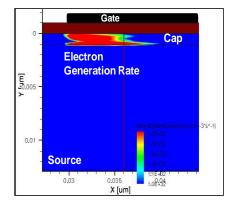

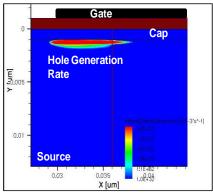

Figure 2.4 TCAD simulation output illustrating contours of BTBT generated holes and electrons. The arrow indicates the direction of tunneling which is not entirely vertical or lateral because both a vertical and lateral field exists. Tunneling originates a few nanometers below the oxide interface entirely within the source of the TFET.

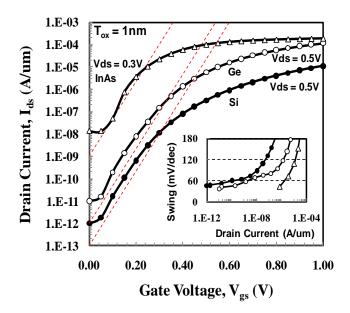

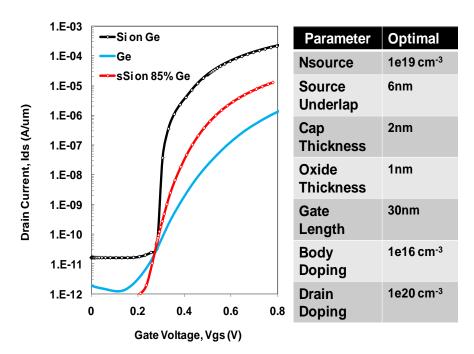

Figure 2.5 Simulations of the  $I_d$ - $V_g$  characteristics of Si, Ge and InAs homojunction TFETs. The  $I_{on}$  increases with lower  $E_g$ , but so does the  $I_{off}$  (junction leakage).

Figure 2.4 is a TCAD simulation output illustrating contours of BTBT generated holes and electrons. The arrow indicates the direction of tunneling which is not entirely vertical or lateral

because both a vertical and lateral field exists. The figure also demonstrates that tunneling originates a few nanometers below the oxide interface entirely within the source of the TFET.

Figure 2.5 summarizes TCAD simulations comparing the  $I_{d}$ - $V_{g}$  characteristics of silicon, germanium and InAs homojunction TFETs. The  $I_{on}$  increases with lower bandgap because of the increased generation rate but so does the  $I_{off}$  (junction leakage). The  $I_{on}/I_{off}$  for a purely InAs TFET is worse than that of a purely silicon or germanium TFET. The dotted lines indicate 60mV/decade. Ideally TFET  $I_{off}$  is entirely due to reverse bias junction leakage. For materials like silicon and germanium TFET  $I_{off}$  is in the 1-10pA current range making these TFETs ideal from a low standby power perspective. Also since the generation rate is exponentially dependant on the electric field, the instantaneous swing of the TFETs is constantly varying and is less than 60mV/decade only over a certain current range. The challenge is in keeping the low  $I_{off}$  and improving the TFET design to increase the  $I_{on}/I_{off}$  at low voltages. Future chapters explore dopant pocket engineering as well as biaxial strained silicon and germanium heterostructures to improve on the simplest homojunction TFET design and enable  $V_{dd}$  scaling to below 0.5V.

#### 2.4 HIGH-K METAL GATE SILICON TFETS

Using an existing High-K metal gate CMOS baseline process flow to fabricate silicon TFETs required the development of a half mask which would align to the gate. This half mask would help with creating asymmetrically doped source and drain regions.

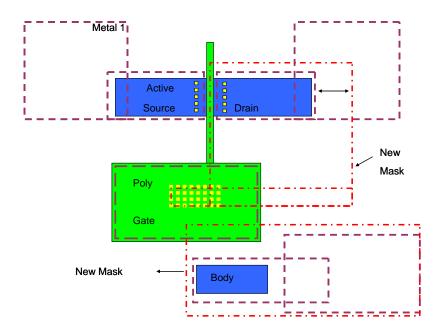

Figure 2.6 Illustration of the new half mask layout designed to be compatible with the existing CMOS mask set at SEMATECH.

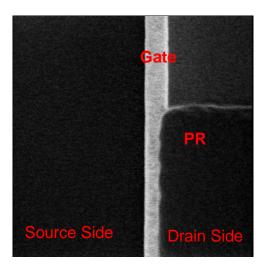

Figure 2.6 is an illustration of the new half mask designed to be compatible with the existing CMOS mask set. This mask was designed to cover the drain while creating the source. Since a reverse half mask was not initially created to minimize cost, the process flow involved a drain implant high enough to create good ohmic contact but low enough to keep compensation of the source dopants minimal. Aligning the half mask to sub 100nm gate lengths required the use of a 193nm DUV stepper with an overlay tolerance specification of +/- 40nm. Figure 2.7 is an SEM image of the half mask aligned to a 50nm gate.

Figure 2.7 Top down SEM image of the half mask aligned to a 50nm gate

The 4000Å thick DUV resist had previously only been used to resolve gates. Using this photoresist to effectively block ion implanted source side dopants from entering the drain side had to be tested. It was also required to test if this resist could after the ion implantation be successfully ashed and cleaned off the wafer. These concerns were tested by a quick experiment shown below in Figure 2.8.

| • | 4K resist spin on + bake |

|---|--------------------------|

| • | Ion implants             |

| • | Resistashed              |

| • | Wafers Inspected         |

| • | SIMS                     |

|   |                          |

| Wafer<br>Split | Species | Implant<br>Dose | Implant<br>Energy |

|----------------|---------|-----------------|-------------------|

| 1              | As      | 4e15            | 35KeV             |

| 2              | В       | 8e15            | 10KeV             |

| 3              | As      | 4e15            | 35KeV             |

|                |         | 2e15            | 10KeV             |

Figure 2.8 Process steps to determine if the resist effectively blocks ion implants. The table shows the various implants tested with the resist.

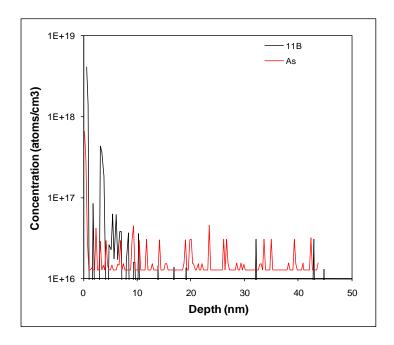

Figure 2.9 shows the concentration of Arsenic and Boron in the silicon substrate from SIMS analysis. The large spike in concentration seen within the first few nanometers at wafer surface is due to an artifact and is well known to be present in all SIMS analysis data. The concentration

deeper in the substrate is negligible indicating that the photoresist does act effectively to block implants from entering the silicon substrate.

Figure 2.9 Concentration of Arsenic and Boron in the silicon substrate from SIMS analysis. The concentration in the substrate is negligible indicating that the photoresist effectively blocks implants from entering the silicon substrate. The large spike in concentration within the first few nanometers of the wafer surface is an artifact well known to be present in all SIMS analysis data.

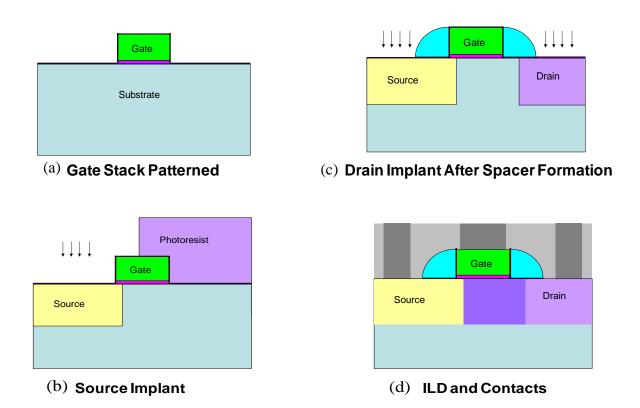

The gate first process flow illustrated in Figure 2.10 involved using the basic MOSFET baseline. The HfSiO<sub>x</sub> high- K dielectric was deposited using ALD at 300 °C and was then subjected to a nitridation anneal to incorporate N and form HfSiON. HfSiON has a higher crystallization temperature [2.13] which is desired to keep the bulk gate leakage low even after a high temperature spike anneal required to activate dopants and remove ion implant induced damage. This is followed by deposition of a 200Å thick TiN layer, a 1000Å thick polysilicon layer and a 600Å thick oxide layer. The oxide layer acts as a hard mask for the gate during gate etching. After the gate stack is patterned and etched, the residual high K dielectric is etched in a buffered HF solution. This is followed by the deposition of a 5nm SiN layer. The SiN is a seal layer which protects the high K dielectric at the gate edges from implant damage. The half mask is then used to protect the drain side with 4000Å of photoresist while the source side is left exposed. For the p-type TFETs a low energy high dose Arsenic implant is carried out to ensure that the source is heavily doped close to the dielectric interface. A 70nm nitride spacer is created and the drain implant is performed with the source exposed. The Bf<sub>2</sub> implant dose is chosen to be high enough to form ohmic contact to the drain with minimal compensation to the source. The activation anneal is performed at 1070 °C for 3s. This is followed by TEOS deposition, contact formation and forming gas anneal.

Figure 2.10 Illustration of a gate first process flow to create silicon homojunction TFETs.

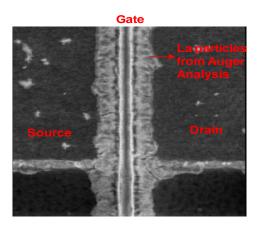

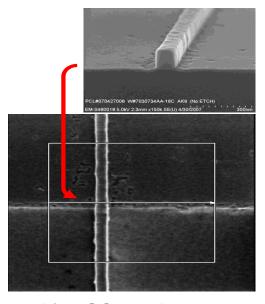

N-type wafer splits were also processed and a Lanthanum capping layer [2.14] was deposited above the  $HfSiO_x$  and before the TiN to achieve N+ band edge work function. Inclusion of the cap however posed a severe problem during the gate etch. As seen from top down SEM shown in Figure 2.11, the standard gate etch cleared the polysilicon and TiN but left La particles close to the gate edges.

After 100A TaN etch 8s (endpoint signal dropped off at 6s)

Figure 2.11 Top down SEM after the gate etch of N-type wafer splits. The Polysilicon and TiN were cleared but La particles were left behind close to the gate edges.

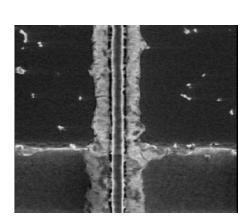

The wafers were soaked in SC1 solution for 5minutes to try and remove the particles since SC1 is used to etch metals gates [2.15]. As seen in Figure 2.12, the SC1 etch was not sufficient. The wafers were then soaked in SC2 solution for 3 minutes and this was found to remove the residual particles as shown in Figure 2.12.

After HF 60s, SC1 5 min (SC1 can etch doped silicon)

After SC2 3min (SC2 does not etch silicon)

Figure 2.12 Top down SEM image after a 5 minute soak in SC1. This etch was not sufficient. The wafers were then soaked in SC2 solution for 3 minutes. This was found to remove the residual particles as shown in the top down SEM image on the right.

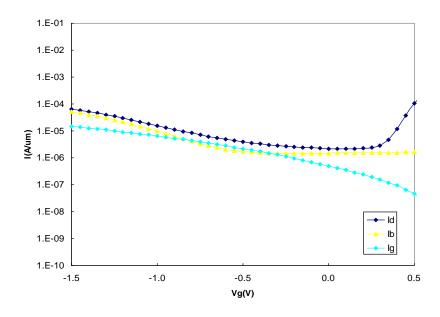

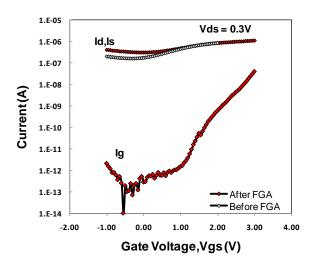

Figure 2.13 The P-type transistor  $I_d$ - $V_g$  shows evidence of BTBT current but the very high junction leakage and gate leakage mask the true nature of tunneling characteristics.

The N-type transistor splits when measured exhibited very high gate leakage current which masked any possible tunneling characteristics. As seen in Figure 2.13, the P-type transistors showed evidence of BTBT current but the very high junction leakage and gate leakage masked the true nature of tunneling characteristics. The sign of the current flowing out of the source, drain and gate is carefully noted and found to indicate that the drain collects holes while the source collects electrons as expected from normal P-type TFET operation.

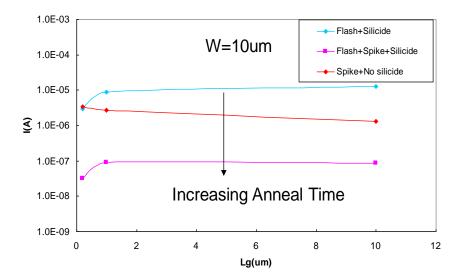

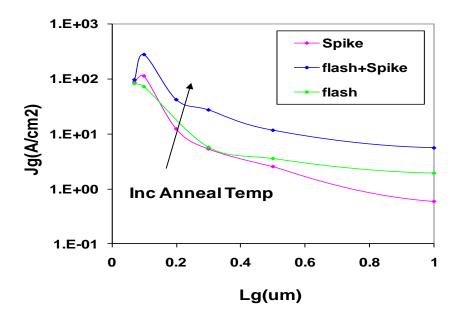

Figure 2.14 TFET  $I_{\text{off}}$  plotted vs. transistor gate length for three different TFET splits. The splits involved different dopant anneals – flash annealing, flash + spike annealing and spike annealing.

The TFET  $I_{\rm off}$  is plotted for various gate length transistors and is found to be fairly independent of gate length. Three different TFET splits are presented in Figure 2.14. The TFET  $I_{\rm off}$  is found to be lowest for the split which received both spike and flash anneal. This seems to indicate that the  $I_{\rm off}$  is due to insufficient damage annealing. The TFET split with flash anneal is found to have larger  $I_{\rm off}$  than the split with spike anneal, again indicating that the high  $I_{\rm off}$  is due to un-annealed damage.

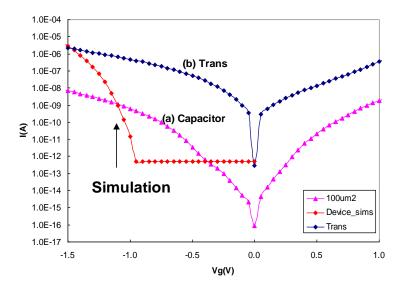

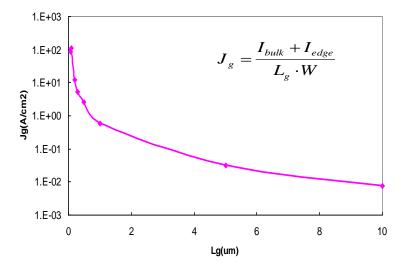

Figure 2.15 combines TCAD simulations of a P-type TFET with measured gate leakage current from a capacitor and a transistor. For the same area, the transistor gate current is much higher than the capacitor gate current. From Figure 2.16 it is clear that the gate leakage current density increases with decreasing gate length indicating that the dominant transistor gate leakage current is from the gate edges rather than the bulk.

Figure 2.15 TCAD simulations of a P-type TFET overlaid with measured gate leakage current from a capacitor and a TFET. For the same area, the transistor gate current is much higher than the capacitor gate current.

Figure 2.16 Gate current density increases with decreasing gate length. This indicates that the dominant transistor gate leakage current is from the gate edges rather than the bulk.

Figure 2.17 indicates that the gate leakage current density increases with decreasing gate length regardless of the activation anneal mechanism.

Figure 2.17 The gate leakage current density vs. transistor gate length for varying anneal mechanisms - spike, flash + spike and flash

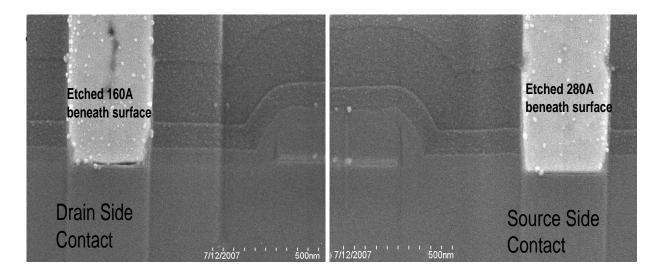

SEM images (Figure 2.18) of the drain side and source side contact indicate that the contact etch etched into the silicon substrate to a deeper extent in the source than in the drain. The etch rate of heavily N-doped silicon is known to be higher and could explain this.

Figure 2.18 SEM images of the drain side and source side contact

In conclusion from the electrical characterization it is clear that in order to see the true tunneling characteristics at the onset of tunneling, the gate leakage current and junction leakage current need to be minimized. The high temperature anneal needs to be optimized for low

junction leakage and the gate etch need needs to be optimized to reduce edge related gate leakage.

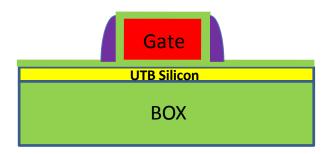

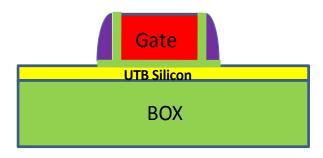

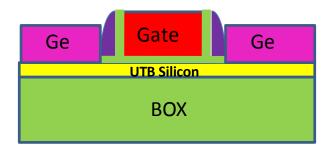

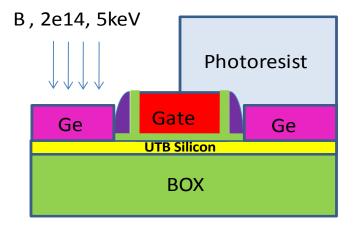

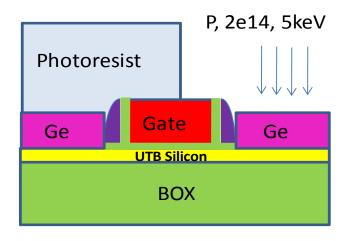

#### 2.5 ULTRA THIN BODY SILICON TFETS

Ultra thin body MOSFETs [2.16, 2.17, 2.18] have been successfully fabricated at UC Berkeley in the past. UTB MOSFETs help achieve better short channel control by eliminating the silicon in the channel which is least effectively modulated by the gate. In UTB MOSFETs the aim is for the potential in the channel to be controlled entirely by the gate rather than by the drain. In TFETs the benefit of the UTB comes from the body being thin enough such that when overlap of conduction and valence bands first occurs, the electric field is large enough that there is a sudden jump in transistor current from the junction leakage (I<sub>off</sub>) to a high tunneling current value. This sudden jump or steep turn on characteristic would occur at a larger voltage than in a thicker body TFET.

UTB MOSFETs do however suffer from large source and drain series resistance because of the thin body. A simple solution to this is using elevated S/D processes. A selectively deposited raised germanium S/D process was used successfully for UTB MOSFET fabrication at UC Berkeley [2.16]. This previously tested process was used to try and fabricate UTB silicon TFETs with raised germanium S/D.

The key steps of the process flow are as shown below

Figure 2.19 (a) Source side dopant implant into UTB silicon after etching the gate stack

Figure 2.19 (b) Bi-layer spacer formation with nitride on top of HTO.

Figure 2.19 (c) Removal of HTO over source and drain region by wet etch

Figure 2.19 (d) Selective deposition of LPCVD Poly germanium on the source and drain

Figure 2.19 (e) Photoresist mask to protect the drain side and source dopant implant into the raised germanium source

Figure 2.19(f) Photoresist mask to protect the source side and drain dopant implant into the raised germanium drain

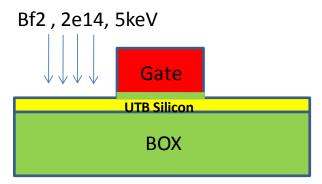

Thinning the silicon on insulator down to 5nm was done in several cycles of dry oxidation followed by wet etch and removal of the oxide. Because of variation in the initial 100nm SOI substrate thickness, the thinned down silicon also had a variation in thickness. The center of the wafer was the thinnest (6.5nm) with rings of thicker silicon (8nm and 11nm) as you move outwards. After gate oxidation the thinnest body measured 5nm in the center of the wafer. Oxidation was followed by in-situ doped polysilicon deposition, gate lithography and etch. This was followed by source implant into the UTB aligned to the source edge. This was a variation from the UTB MOSFET process flow where no ion implantation was performed into the ultra thin body. For TFETs since the source needs to be overlapped by the gate in order to enable gate induced BTBT and therefore it was necessary to introduce dopants close to the gate edge.

A novel process used to fabricate UTB MOSFETs involved a bi-layer spacer consisting of HTO and Nitride. The HTO layer acts as a stopping layer for the nitride spacer etch eliminating the chance of etching into the silicon substrate and disconnecting the channel from the source and drain. In the UTB TFET a bilayer spacer with 20nm of HTO following by 20nm Nitride was used. After the nitride etch the exposed HTO is then cleaned off in HF to leave the silicon substrate exposed in the S/D region. Selective deposition of undoped germanium is then carried out in a LPCVD furnace. The germanium is capped with a LTO layer right away and then half masks are used to implant the source and drain while covering the other electrode. Finally dopant activation and FGA are performed before electrically testing the devices. YK Choi when fabricating UTB MOSFETs had noticed that annealing beyond 900 °C lead to bursting of the channel region. To avoid this and still achieve dopant activation and damage annealing in the silicon the devices were annealed at 800 °C for 30minutes.

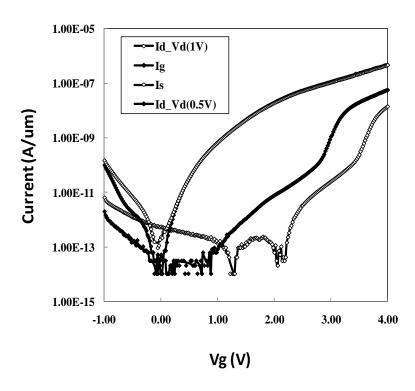

Figure 2.20  $I_d$ - $V_g$  measurements from an N-type UTB TFET. The gate current and source current are identical indicating a gate to source leakage mechanism.

Measurements from an N-type UTB TFET are shown in Figure 2.20. The gate current and source current are identical indicating a gate to source leakage mechanism. Ion implanting source dopants into the ultra thin body aligned to the gate edge is possibly the source of this large leakage current. A very thin ALD layer or LTO layer deposited to protect the gate edges before the ion implant could have possibly eliminated this gate edge damage. Typical MOSFET processing involves a re-oxidation step after the gate etch to heal any etch related damage to the gate edges. YK CHOI found during UTB MOSFET fabrication that the oxidation rate of SOI film less than 10nm was much higher than the normal oxidation rate of bulk silicon. In order to avoid rapid oxidation of the source and drain regions of the UTB TFETs, thermal re-oxidation after the gate etch was avoided which would have left any gate etch related damage un-healed.

In an N-type TFET a positive gate voltage allows for overlap and BTBT to occur in the source. A positive drain voltage reverse biases the PN junction and collects the BTBT generated electrons, while the BTBT generated holes flow to the source contact. Therefore the drain and source currents should be opposite in sign. In the figure shown above, the gate current is positive while both the drain and the source current are negative indicating that both source and drain terminals are collecting the same type of carrier. It appears that the positive gate voltage allows for electrons to be collected by the gate from both the source and the drain presenting no evidence of BTBT in these UTB TFETs. The  $I_d$ - $V_g$  characteristic shown above is representative of most of the devices from the central dies of the wafer.

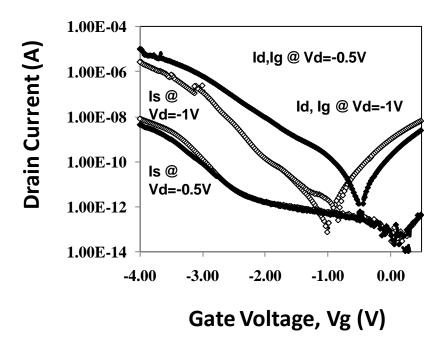

Figure 2.21 Id-Vg measurements from an N-type UTB TFET operated as a P-type TFET by grounding the  $N^+$  terminal and applying a negative bias to the gate and  $P^+$  terminal.

An N-type TFET measurement involves grounding the P+ terminal and applying a positive bias to the gate and N+ terminal to induce BTBT in the P+ source. The same transistor can however also operate as a P-type TFET by grounding the N+ terminal and applying a negative bias to the gate and P+ terminal. Here the N+ region is the source of BTBT while the P<sup>+</sup> acts as the drain.

The  $I_d$ - $V_g$  characteristic from such a measurement is presented in Figure 2.21. The fact that in this measurement setup the drain to gate leakage dominates both at  $V_{ds}$  of -0.5V and -1V, can be explained as follows. The UTB TFET process flow designed to create N-type TFETs involved P+ source implants into the UTB aligned to the gate edge and N+ drain implants aligned to the 20nm bi-layer spacer. For a P-type measurement, the P+ region implanted at the gate edge with gate edge damage now acts as the drain and the N+ region not implanted at the gate edge acts as the source. Since the N+ implant was not aligned to the gate edge, dopant diffusion has to be relied on for overlap of the gate over the N+ region. This would lead to the gate overlapping lighter doped N+ regions which is not the ideal design for a TFET source.

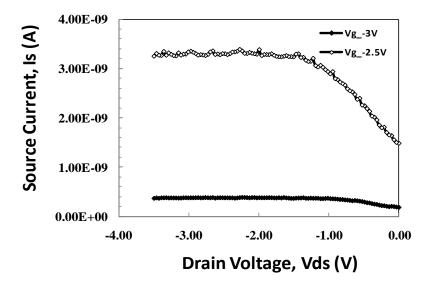

The polarity of the source current in the Id-Vg measurement indicates collection of electrons. The increase in source current with the drain bias seems to indicate that the electrons are not entirely due to tunneling from the negatively biased gate into the source. An alternate generation mechanism of electrons exists, BTBT being a possibility. The  $I_d$ -V $_d$  characteristic of the same P-type biased device is shown in Figure 2.22. For two different negative gate biases, the source current is seen to increase with increasing drain voltage and saturate just as expected from the  $I_d$ -V $_d$  characteristic of a TFET. Again if the source purely collected electrons tunneling from the gate into the source, the source current wouldn't show an increase and saturation with

drain voltage again confirming an alternate generation mechanism for electrons collected by the source.

Figure 2.22  $I_d$ - $V_g$  measurements from an N-type UTB TFET operated as a P-type TFET by grounding the N+ terminal and applying a negative bias to the gate and P+ terminal.

Further annealing of the devices at 800 °C caused even larger increase in gate to drain leakage current, making it difficult to get further meaningful measurements from these devices.

In conclusion use of a protective layer to protect the gate edge before performing the source implant could eliminate or reduce the gate to source/drain leakage allowing us to truly observe and explore UTB TFET behavior. Solid phase epitaxy or annealing the devices at a low temperature like 400 °C for many hours could be explored to achieve better dopant activation in these devices while keeping the thermal budget low. Lastly using solid source diffusion to introduce dopants into the source and drain without damaging the silicon or gate edges could also be a possible direction for improved UTB TFET experiments.

#### 2.6 REFERENCES

[2.1] T. Y. Chan, J. Chen, P. Ko, C. Hu, "The impact of gate-induced drain leakage current on MOSFET scaling", International Electron Devices Meeting, Vol.33, pp: 718-721, 1987

[2.2] W. M. Reddick, G. A. Amaratunga, "Silicon surface tunnel transistor," Applied Physics Letters, vol.67, no.4, pp.494-496, Jul 1995

[2.3] C. Aydin, A. Zaslavsky, S. Luryi, S. Cristoloveanu, D. Mariolle, D. Fraboulet, S. Deleonibus, "Lateral interband tunneling transistor in silicon-on-insulator," Applied Physics Letters, vol.84, no.10, pp.1780-1782, Mar 2004

- [2.4] K. K. Buwalka, M. Born, M. Schindler, M. Schmidt, T. Sulima and I. Eisele, "P-Channel Tunnel Field-Effect Transistors down to Sub-50nm Channel Lengths", Japanese Journal of Applied Physics, 45, pp. 3106-3109, 2006

- [2.5] C. Hu, "Green transistor as a solution to the IC power crisis," Solid-State and Integrated-Circuit Technology, 2008. ICSICT 2008. 9th International Conference on, pp.16-20, 20-23 Oct. 2008

- [2.6] A. Bowonder, P. Patel, K. Jeon, J. Oh, P. Majhi, H. H. Tseng, C. Hu; , "Low-voltage green transistor using ultra shallow junction and hetero-tunneling," Junction Technology, 2008. IWJT '08, pp.93-96, 15-16 May 2008

- [2.7] V. Nagavarapu, R. Jhaveri, J.C.S. Woo, "The Tunnel Source (PNPN) n-MOSFET: A Novel High Performance Transistor," Electron Devices, IEEE Transactions on, vol.55, no.4, pp.1013-1019, April 2008

- [2.8] P, Patel, K. Jeon, A. Bowonder, C. Hu, "A Low Voltage Steep Turn-Off Tunnel Transistor Design," Simulation of Semiconductor Processes and Devices, 2009. SISPAD '09. International Conference on, vol., no., pp.1-4, 9-11 Sept. 2009.

- [2.9] E.O.Kane, "Theory of Tunneling", JAP, Vol. 23, No.1, Jan, 1961

- [2.10] S.Wang, Fundamentals of Semiconductor Theory and Device Physics, 1989

- [2.11] Z.A.Weinberg, "On Tunneling in Metal-Oxide-Silicon Structures", JAP, Vol. 53, No.7, July 1982

- [2.12] C. Hu, D. Chou, P. Patel, A. Bowonder, "Green Transistor A  $V_{DD}$  Scaling Path for Future Low Power ICs", VLSI Technology, Systems and Applications, 2008. VLSI-TSA 2008. International Symposium on. April 2008, pp. 14-15.

- [2.13] H. C. H. Wang, C. W. Tsai, S. Chen, C. T. Chan, H. J. Lin, Y. Jin, H. J. Tao, S. C. Chen, C. H. Diaz, T. Ong, A. S. Oates, M. S. Liang, M. H. Chi, "Reliability of HfSiON as gate dielectric for advanced CMOS technology," VLSI Technology, 2005. Digest of Technical Papers. 2005 Symposium on, pp. 170-171, 14-16 June 2005

- [2.14] C. Y. Kang, C. D. Young, J. Huang, P. Kirsch, D. Heh, P. Sivasubramani, H. K. Park, G. Bersuker, B. H. Lee, H. S. Choi, K. T. Lee, Y. H. Jeong, J. Lichtenwalner, A. I. Kingon, H. H. Tseng, R. Jammy, "The impact of la-doping on the reliability of low  $V_{th}$  high-k/metal gate nMOSFETs under various gate stress conditions," Electron Devices Meeting, 2008. IEDM 2008. IEEE International, vol., no., pp.1-4, 15-17 Dec. 2008

- [2.15] M. M. Hussain, N. Moumen, J. Barnett, J. Saulters, D. Baker and Z. Zhang, "Metal Wet Etch Process Development for Dual Metal Gate CMOS", Electrochem. Solid-State Lett., Volume 8, Issue 12, pp. G333-G336 (2005)

- [2.16] Y. K. Choi, A. K, N. Lindert, V. Subramanian, T. J. King, J. Bokor, C. Hu; , "Ultra-thin body SOI MOSFET for deep-sub-tenth micron era," Electron Devices Meeting, 1999. IEDM Technical Digest. International, pp.919-921, 1999

- [2.17] Y. C. Yeo, V. Subramanian, J. Kedzierski, X. Peiqi, T. J. King, J. Bokor, C. Hu, "Nanoscale ultra-thin-body silicon-on-insulator P-MOSFET with a SiGe/Si heterostructure channel," Electron Device Letters, IEEE, vol.21, no.4, pp.161-163, Apr 2000

- [2.18] P. Xuan, J. Kedzierski, V. Subranmanian, J. Bokor, T. J. King, C. Hu; , "60 nm planarized ultrathin body solid phase epitaxy MOSFETs," Device Research Conference, 2000. Conference Digest. 58th DRC, pp.67-68, 2000

# Chapter 3

# Lateral Pocket TFETs as a Path to Scale V<sub>dd</sub>

## 3.1 INTRODUCTION

The previous chapter explored simple PIN silicon TFET designs. In these PIN transistors, the tunneling current is exponentially dependant on the field set up by the gate and therefore the instantaneous swing constantly varies and gradually increases with current. Since low  $I_{\rm off}$  is required to keep the standby power consumption low, the transistor with lowest  $I_{\rm off}$  and largest  $I_{\rm on}/I_{\rm off}$  at a reduced  $V_{\rm dd}$  is desired for ultra low voltage operation. The simple PIN design (Figure 3.1a) can be further enhanced by using well engineered dopant pockets [3.1, 3.2] to enhance the  $I_{\rm on}/I_{\rm off}$  at ultra low  $V_{\rm dd}$  ( $V_{\rm dd} < 0.3 V$ ). These dopant pockets are thin regions of dopant opposite in type to the source dopant. Dopant pockets can be incorporated in addition to low bandgap materials for even higher performance at ultra low voltages. This chapter presents an overview of the operation and optimization of a silicon pocket TFET design. Further, experimental data which confirms the superior behavior of the pocket TFET over a simple PIN TFET is also presented.

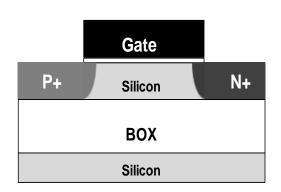

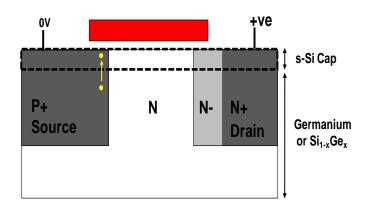

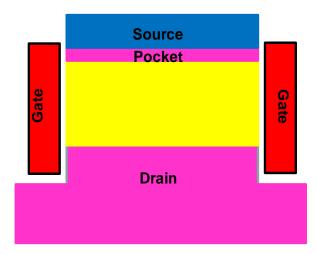

Figure 3.1a. Si PIN TFET with P+ source and N+ drain. The TFETs in this work were fabricated on SOI, 40nm Silicon on 100nm Box.

Figure 3.1b. Si PIN TFET with angled implant to create a lateral N doped pocket adjacent to the P+ source. LPTFETs were also fabricated on 40 nm Silicon on 100nm Box.

### 3.2 LATERAL POCKET TFET DESIGN

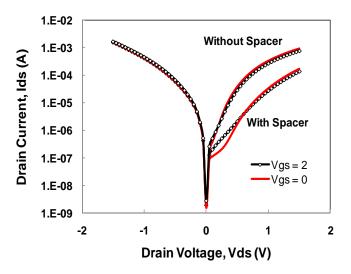

The pocket regions can be either perpendicular to the gate dielectric, adjacent to the source (lateral pocket-LPTFET -Figure 3.1b) [3.1] or parallel to the dielectric interface, above the source (vertical pocket-VPTFET [3.2]). The lateral pocket TFET design (Figure 3.1b) is

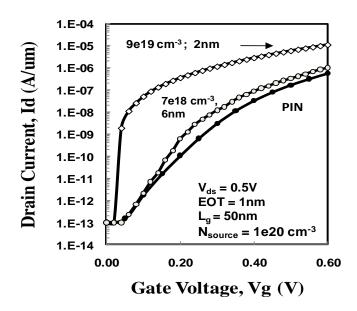

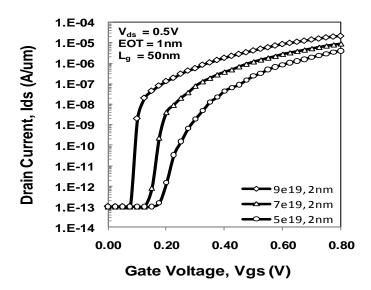

Figure 3.2 TCAD simulations of N-type lateral pocket TFETs and PIN TFET. An ideal heavily doped, fully depleted N type pocket (9e19 cm<sup>-3</sup>, 2nm) adjacent to the source leads to significant enhancement in performance over PIN TFET, while a not so optimal N doped pocket shows minimal enhancement over a PIN TFET.

referred to as tunnel source PNPN MOSFET [3.1] and is explored using SILVACO's device simulator, ATLAS, coupled with analytical tunneling calculations by Nagavarapu et.al. Some experimental data is also shown in [3.1]. In this work we add to the previous study by presenting self consistently done TCAD simulations and very detailed experimental characterization. The simulations were done with Sentaurus' dynamic non local tunneling model with the default silicon tunneling parameters (obtained from calibration with experimental GIDL current of MOSFETs).

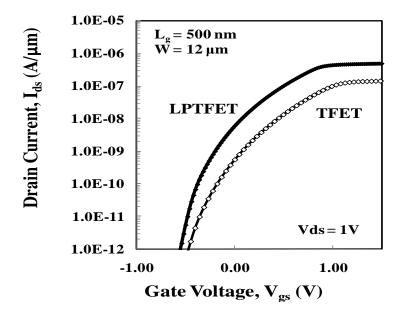

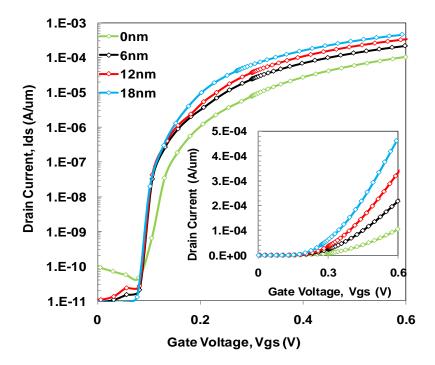

Shown in Figure 3.2 are  $I_d$ - $V_g$  simulations of an ideal lateral pocket TFET and simple PIN TFET. For the same gate WF the LPTFET turns on earlier than the PIN TFET but for a fair comparison (same  $V_{gs}$ - $V_t$ ), it is assumed that WF engineering is used to achieve identical turn on voltage for both transistors. For a PIN TFET, even at 1nm EOT, the sub 60mV/decade swing is only seen up to 10nA of current. The ideal lateral pocket TFET however can show steep switching over a much larger current range (sub 60mV/decade swing up to 5uA). For the same  $I_{off}$  the ideal LPTFET also shows enhanced  $I_{on}/I_{off}$  over that of an ideal MOSFET (60mV/decade swing) at low  $V_{dds}$  below 0.4V. Well implemented pocket TFETs in silicon can therefore help lower  $V_{dd}$  below 0.4V. For larger  $I_{on}$  and enhanced  $I_{on}/I_{off}$  at  $V_{dds}$  below 0.4V, these lateral pockets can further be implemented in Ge, low bandgap III V materials and heterostructures with even smaller effective bandgap.

Figure 3.2 also shows a non optimal lateral pocket design where the enhancement over a PIN TFET is minimal. The ideal pocket is fully depleted and works by enhancing the E field at the source-pocket junction at the point of turn on of BTBT, while suppressing less efficient tunneling paths which would have resulted in a worse swing. This enhanced E field when BTBT first occurs allows for a sudden jump from the off state (junction leakage) to the enhanced BTBT

current value as seen in Figure 3.2. The no. of decades over which the current will jump from off state to on state will depend on the electric field at the point of overlap for band to band tunneling to occur.

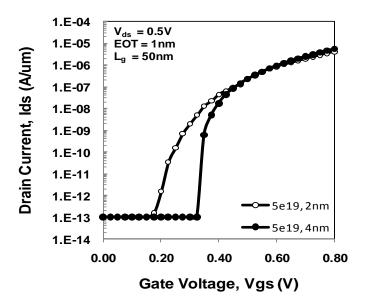

Figure 3.3 LPTFET with varied pocket dose (5e19 cm<sup>-3</sup>, 4nm and 5e19 cm<sup>-3</sup>, 2nm). In the 5e19 cm<sup>-3</sup> N doped, 4nm pocket, the onset of BTBT occurs in the pocket and other less efficient tunneling paths are cut off.

The pocket dose thickness and doping therefore needs to be carefully engineered so that the onset of tunneling occurs within the high field pocket region.

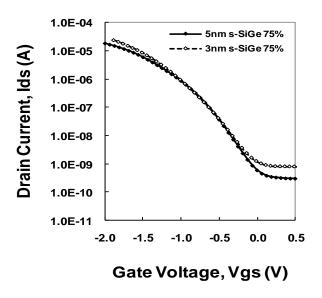

Figure 3.3 and figure 3.5 compare LPTFETs with varied pocket dose. For a steep sudden turn on, the pocket width for a fixed doping concentration needs to be optimized to ensure the pocket is fully depleted and the onset of BTBT is in the high field region. This is also emphasized in [3.1]. Figure 3.3 compares pockets of same doping but varied thickness. In the wider pocket (5e19 cm<sup>-3</sup>, N- doped, 4nm) the onset of BTBT occurs in the high field pocket region and other less efficient tunneling paths are cut off. The wider pocket therefore shows a steeper turn on. This is confirmed in Figure 3.4a and 3.4b, TCAD outputs showing contours of the BTBT generated carriers at the onset of tunneling for the 2nm pocket and 4nm pocket.

Figure 3.5 compares 2nm pockets of varied doping. We see that for a given pocket thickness increasing the doping of the pocket (net dose of the pocket) increases the E field at the source-pocket junction and therefore increases the tunneling current when the conduction and valence bands first overlap. This allows for a sudden jump from off state to a larger current value in the on state and therefore steeper turn on over a larger current range.

In addition to an overview of the optimization and design of the LPTFET, this chapter deals with characterization and analysis of prototype PIN TFETs with and without lateral pocket with 2.5nm EOT. While the use of a conservative dielectric prevents sub 60mV/decade swing and limits the on current of the TFETs, the prototypes demonstrate experimental verification of the enhancement in swing and on current due to lateral pocket design.

Figure 3.4a TCAD output of electrons and holes generated by BTBT for LPTFET with 5e19cm<sup>-3</sup>, N-doped, 2nm pocket. This is the output at 0.05V above turn on. Onset of tunneling does not occur in the high field pocket region. This leads to lower tunneling current at the onset of tunneling.

Figure 3.4b TCAD output of electrons and holes generated by BTBT for LPTFET with 5e19cm<sup>-3</sup> N doped, 4nm pocket. This is the output at 0.05V above turn on (the sudden jump to on current). Onset of tunneling occurs in the high field pocket region. This leads to a sudden jump from off state to a high current in the on state. The higher the field at the onset of tunneling, the higher the jump to on current value will be (shown in Fig. 4).

Figure 3.5 LPTFETs with fixed pocket width and varied pocket dose (5e19 cm<sup>-3</sup>, 2nm; 7e19 cm<sup>-3</sup>, 2nm and 9e19 cm<sup>-3</sup>, 2nm). The E field at the source-pocket junction increases with heavier pocket doping allowing for larger tunneling current at the onset of BTBT and steeper turn on.

Figure 3.6 Comparison of TCAD simulation with experimental data of Si PIN TFET. TCAD simulations involve process simulation emulating fabrication followed by device simulation. Sub 60mV/dec cannot be achieved from a silicon PIN with 2.5nm EOT.

Compared to a Si PIN TFET, the LPTFET presented in this work has 14x larger current at  $V_{ds} = V_{gs}$  -  $V_t = 0.5V$ , 10x larger current at  $V_{ds} = Vgs$  -  $V_t = 1V$  and reduction in minimum swing from 87mV/decade to 63mV/decade. The control TFET's  $I_{on}$  is comparable to simple silicon PIN TFETs from recent literature [3.3]. The experimental data also shows a good fit with TCAD simulations of the PIN TFET (Figure 3.6). Enhancements in the simple PIN TFET  $I_{on}$  by use of lower bandgap materials has already been demonstrated by several groups. LPTFETs can be implemented in these materials to further enhance performance and swing just as in the case of silicon.

The possible formation of a parasitic MOSFET during LPTFET fabrication by angled implant and anneal is also discussed in detail along with experimental results and analysis.

#### 3.3 EXPERIMENTAL DESIGN

Almost all studies of TFETs to date have involved implanted source and drain regions [3.1, 3.3,-3.5], and avoided the integration of selective Epitaxy of the source and drain. Given the significant process complexity of fabricating LPTFETs using selective epitaxial growth of the pocket and source regions, in this initial study, a controlled angled implant aligned to the gate edge followed by a spike anneal is used to create the pocket. The enhancement due to pocket presented here will be greatly enhanced in TFETs with abrupt, epitaxial pocket and source.

PIN TFETs and LPTFETs (inset in Fig3.1b) were fabricated on SOI wafers with 45nm body thickness. The SOI wafers with 100nm box had 100nm body originally and were thinned down to 45nm by consecutive dry oxidation and etch of the oxide grown. Alignment marks are patterned onto the wafer and etched 1200Å deep into the wafer using a CF<sub>4</sub> based dry etch. The gate stack is then created. The 2.5nm gate oxide was grown by dry oxidation at 850 °C for 1min and capped with 1000Å of in situ N+ doped poly-silicon deposited at 615 °C. The drain is covered with a photoresist half mask aligned to the center of the gate and the P+ source is created by a vertical BF<sub>2</sub> implant (5x10<sup>15</sup>cm<sup>-2</sup>, 10keV) aligned to the gate edge. The SEM is used to ensure that the half mask is aligned appropriately and covers the drain. In case of alignment inaccuracies an intrafield offset can be specified in the ASML stepper to help align the mask to the center of the gate. With the source covered by a photoresist half mask the N+ drain is created by a vertical As implant (4x10<sup>15</sup>cm<sup>-2</sup>, 10keV). The wafer splits with lateral N+ pockets received an additional angled As implant (2x10<sup>14</sup>, 20keV, 20°) aligned to the gate edge on the source side. Implant conditions were based on TCAD process simulations, followed by device simulations to ensure optimal TFET design. This was followed by deposition of 1000Å of low temperature oxide deposited at 450 °C. The oxide is deposited before dopant activation to prevent dopant loss during high temperature activation. The silicon PIN control wafer without lateral pocket implant was annealed at 1000 °C for 1s using an RTA tool while the LPTFET splits received dopant activation anneals at 1000 °C for 1s and at 1000 °C for 5s. In the RTA tool the anneal is ramped up to 450 °C and held steady for 30s after which it is ramped up-to 1000 °C in 5s. Contact lithography is followed by a CF<sub>4</sub> and CHF<sub>3</sub> based anisotropic etch with 9:1 selectivity to the silicon substrate. Endpoint detection on a dummy with identical ILD thickness is used to estimate the time for contact etch and a 30% overetch is added in. A quick 3s HF dip is performed before the wafers are put into the sputter tools loadlock. A 10s sputter etch is first performed in the sputter tool followed by deposition of 1000Å of Al/Si 2%. The metal is

patterned and etched with a BCl<sub>3</sub> based anisotropic etch and the wafers receive a FGA at 450 °C for 30minutes before testing.

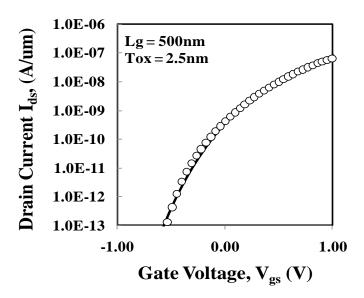

Figure 3.7 Experimental Id-Vg characteristics of a PIN TFET without pocket.

## 3.4 EXPERIMENTAL RESULTS

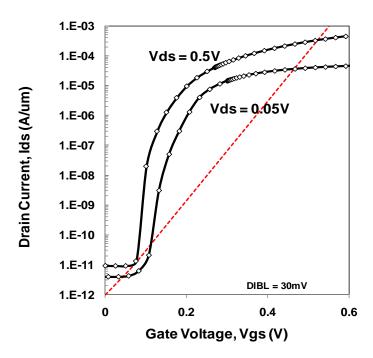

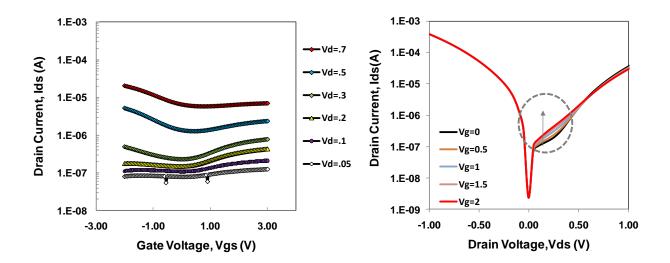

Figure 3.7 shows experimental  $I_d$ - $V_g$  data from the PIN control TFET split without a pocket. The data fits very well to an analytical TFET framework based on the charge sheet model [3.6: to be published elsewhere]. While all the equations of the analytical framework are to be published in detail in [3.6], a very brief summary is provided here. The shape and saturation of the TFET  $I_d$ - $V_g$  data presented in Figure 3.7 are dependent entirely on the electrostatics as follows. The tunneling current is determined by the BTBT generation rate, which is exponentially dependent on the E-field at dielectric-silicon interface (E-field at the interface has a square root dependence on the surface potential). For a given  $V_{ds}$ , the surface potential increases linearly with  $V_{gs}$  at low gate voltages and then saturates with  $V_{gs}$  at high gate voltages [3.6]. The point at which the surface potential saturates with  $V_{gs}$  increases with  $V_{ds}$  [3.6].

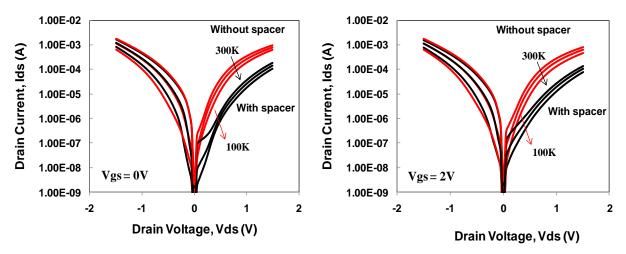

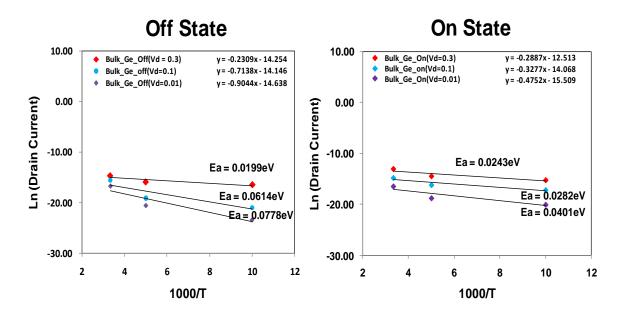

Figure 3.8a and Figure 3.8b show the experimental data from two different LPTFET splits with varied annealing conditions (1s, 1000  $^{\circ}$ C and 5s, 1000  $^{\circ}$ C). The control PIN TFET split without pocket is also shown in both figures. Measured transistor currents are as low as  $1x10^{-14}$  A/µm, but  $1x10^{-12}$ A/µm is assumed as a realistic  $I_{off}$  for all transistors. Also for all transistors the point of onset of tunneling current above this  $I_{off}$  is defined as the turn on voltage (V<sub>t</sub>). From the TCAD simulations (Figure 3.6), Si PIN TFETs with 2.5nm EOT exhibit minimum swing ~ 90mV/decade at pA. A thinner  $T_{ox}$  (~1nm EOT) is required for < 60mV/decade swing but was not used in the prototypes to eliminate potentially enhanced gate leakage after angled pocket

implant. The results and conclusions presented here with a conservative dielectric do however experimentally verify the benefit of and the enhancement in swing and on current with lateral pocket design.

Figure 3.8a Experimental Id-Vg characteristics of a PIN TFET and a LPTFET (angled N implant, 1050  $^{\circ}$ C ,1s anneal) with identical 2.5nm EOT gate stacks. The LPTFET shows improved performance over PIN TFET. The minimum swing is reduced from 89mV/decade for the TFET to 63mV/decade for the LPTFET.

Figure 3.8b Experimental Id-Vg characteristics of a PIN TFET and LPTFETs (angled N implant, 1050 °C 5s anneal) with identical 2.5nm EOT gate stacks. Constant swing over several decades of current seems indicative of accidentally formed MOSFETs rather than LPTFETs.

The LPTFET in Figure 3.8a compared to the Si PIN TFET has 14x larger and 10x larger current at  $V_{ds} = V_{gs}$  -  $V_t = 0.5V$  and 1V respectively. As seen in Figure 3.2, a wide lightly doped pocket, as would be expected after angled implant and anneal, does not show as much enhancement over a PIN TFET as a thin, heavily doped pocket with the optimal pocket dose. Therefore to see this steep turn on a thin, heavily doped pocket formed by epitaxial silicon growth needs to be employed.

The instantaneous swing of the LPTFET in Figure 3.8a is lower than the PIN TFET over all current ranges and the minimum swing is reduced from 89mV/decade to 63mV/decade. Since ellipsometry during fabrication was used to ensure identical  $T_{ox}$  on all splits and all other processing was identical for the two splits, the enhanced swing is attributed to the presence of a lateral pocket. The LPTFET data in Figure 3.8a is characteristic of the devices in that particular wafer split with the minimum swing of the devices in that split varying between 63mV/decade and 69mV/decade.

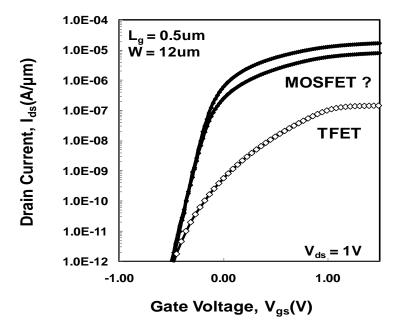

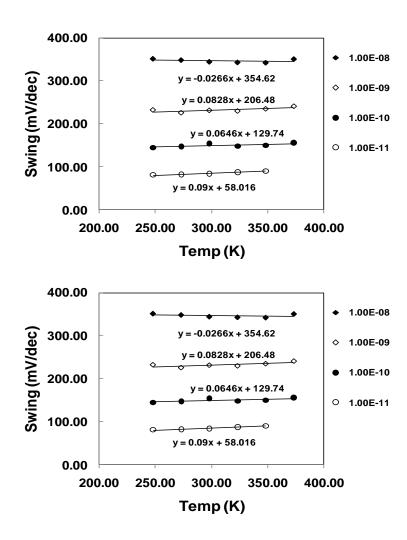

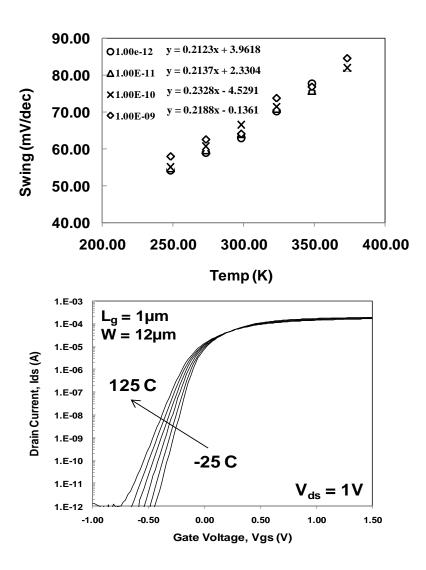

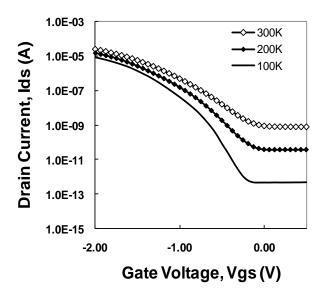

Since the LPTFET if formed by angled implant and anneal it is very challenging to achieve a thin uniformly doped, fully depleted pocket. Figure 3.8b shows the LPTFET split with a longer anneal time (1000 °C, 5s). All working transistors from this split demonstrated constant swing over several decades of current and ~100x greater current than the control PIN TFET split with no pocket. Nagavarapu et.al explained in detail the possible formation of a parasitic MOSFET if the N doped pocket is very wide and not fully depleted [3.1]. In other words instead of creating a thin depleted pocket of charge to enhance the E-field and tunneling at the source-pocket junction you form a parasitic NPN+ transistor and the injection mechanism of carriers into the channel is no longer tunneling from the source but is injection over a barrier. The formation of such a wide un-depleted pocket in the longer anneal split LPTFETs can be confirmed by verifying the carrier injection mechanism. If carriers are injected thermally over a barrier, the swing of these transistors will show a KT dependence. Figure 3.10 and Figure 3.11 explore the temperature dependence of the two LPTFET splits in Figure 3.8a and Figure 3.8b.

Fig. 3.9 Effect of temperature on Id-Vg characteristics of the PIN TFET

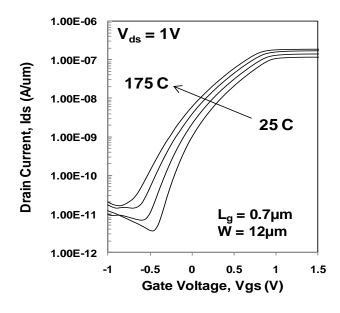

Figure 3.10 Effect of temperature on Id-Vg characteristics of the LPTFET shown in Figure 3.8a for 50 °C steps in temperature. Swing of the LPTFET at various current ranges shows no kT dependence on absolute temperature (slope of the trendline).

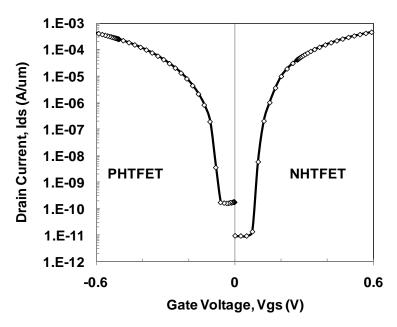

In Figure 3.10, the LPTFET  $I_d$ - $V_g$  exhibits parallel shifts with temperature. As expected from theory, the tunneling  $V_{turn,on}$  decreases with increase in temperature because the bandgap decreases and therefore the  $V_{gs}$  to achieve sufficient band-bending for BTBT decreases with temperature. The swing at various current levels shows no KT dependence with absolute temperature, confirming a tunneling based injection of carriers into the channel. In Figure 3.11, the LPTFET  $I_d$ - $V_g$  exhibits varying slope with temperature. The swing shows a KT dependence on absolute temperature confirming the presence of carrier injection over a barrier. This confirms the hypothesis that the 1000  $^{\circ}$ C, 5s anneal split lead to a very wide pocket and the accidental formation of a NPN+ transistor, while the 1000  $^{\circ}$ C, 1s anneal while not forming the ideal pocket, allowed the formation of a fully depleted N pocket with better performance than the control PIN TFET without pocket.

Figure 3.11 Effect of temperature on Id-Vg characteristics of the accidental MOSFET shown in Figure 3.8b for 25 °C steps in temperature. Swing at various current ranges shows a KT dependence on absolute temperature (slope of the trendlines) confirming the formation of an accidental MOSFET.

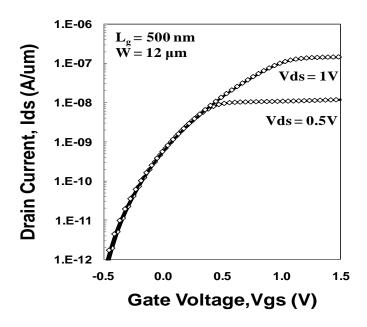

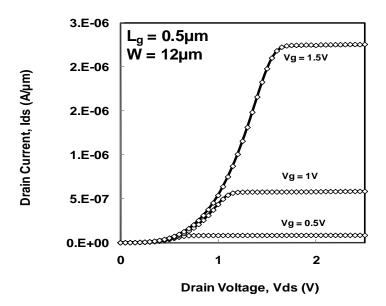

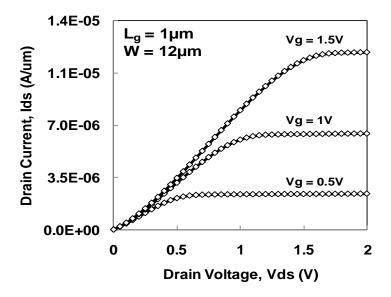

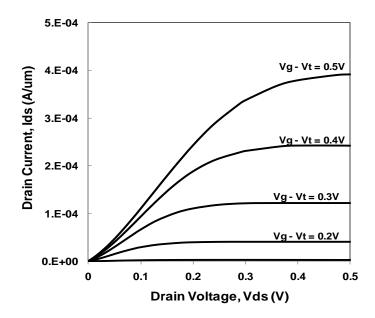

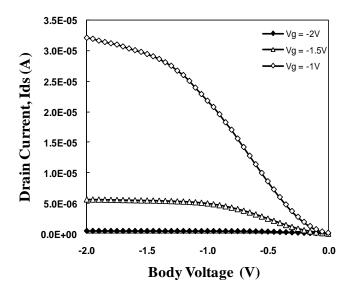

The  $I_d$ - $V_d$  characteristics (Figure 3.12a, 3.12b) of the two LPTFET splits are also presented as further verification. The output characteristics of the LPTFET exhibit non-linearity at low  $V_{ds}$  as expected from analytical theory [3.6]. When tunneling is the carrier injection mechanism, the current (generation rate) is exponentially dependent on E-field (surface potential) at the interface. For a given  $V_{gs}$ , the surface potential increases linearly with  $V_{ds}$  until it finally becomes independent of the  $V_{ds}$  [3.7]. The tunneling current therefore increases exponentially with  $V_{ds}$  and eventually saturates at high drain bias. Complete details and fit of the  $I_d$ - $V_d$  data with theory will be published in [3.6]. When the carriers are injected over a barrier, no such non-linearity is expected in the output characteristics. This is seen in Figure 3.12b, again confirming the hypothesis that the 1000  $^{\circ}$ C, 5s anneal lead to formation of an accidental MOSFET.

Figure 3.12a  $I_d$ - $V_d$  characteristics of the LPTFET shown in Fig.7a. The non-linearity at low  $V_{ds}$  is because  $I_{ds}$  is exponentially dependant on E-field at the surface (the surface potential). For a given  $V_{gs}$  surface potential increases linearly with  $V_{ds}$  until it becomes independent of  $V_{ds}$  [3.6, 3.7].

Figure 3.12b  $I_d\text{-}V_d$  characteristics of the accidental MOSFET split.

### 3.5 CONCLUSIONS

LPTFETs with optimized pocket dose and width can enhance performance of a PIN TFET greatly and enable  $V_{dd}$  scaling to below 0.5V. An angled N pocket implant is used to fabricate LPTFETs in silicon. An optimized anneal condition while not forming an ideal pocket yielded a LPTFET with enhanced performance over the control PIN TFET, while with a longer anneal condition a wide, not fully depleted N pocket formed causing carrier injection over a barrier instead of tunneling from the source. The dependence of swing on absolute temperature was used to confirm carrier injection mechanism in the varied LPTFET splits.

The use of lateral pocket to enhance performance is verified experimentally in this work. Further performance enhancement than demonstrated here can be achieved with better control of the source and lateral pocket profiles and thinner gate dielectric. If implantation is used, flash annealing or other diffusion-less annealing methods can help realize more abrupt source-pocket junctions than possible by RTA. Selective epitaxial growth of source and pocket regions would be ideal to provide maximum enhancement in LPTFET performance and enable  $V_{\rm dd}$  scaling. The Enhancement in swing and on current due to lateral pocket opens up a path to lower TFET operating voltage which can be combined with bandgap scaling to achieve high  $I_{\rm on}$  and high  $I_{\rm on}/I_{\rm off}$  at ultra low  $V_{\rm dd}$ .

### 3.6 REFERENCES

- [3.1] V. Nagavarapu, R. Jhaveri and J. C. S. Woo, "The Tunnel Source (PNPN) n-MOSFET: A Novel High Performance Transistor," IEEE Transaction on Electron Devices, Vol. 55, No.4, April 2008, pp.1013-1019.

- [3.2] P. Patel, K. Jeon, A. Bowonder, C. Hu, "A Low Voltage Steep Turn-off Tunnel Transistor Design," SISPAD Sept 2009.

- [3.3] F. Mayer, C. L. Royer, J. F. Damlencourt, K. Romanjek, F. Andrieu, C. Tabone, B. Previtali and S. Deleonibus, "Impact of SOI, Si<sub>1-x</sub>Ge<sub>x</sub>OI and GeOI substrates on CMOS compatible Tunnel FET performance," IEDM 2008, pp.163

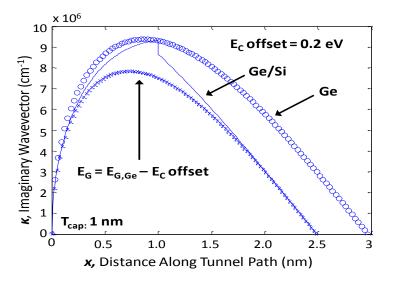

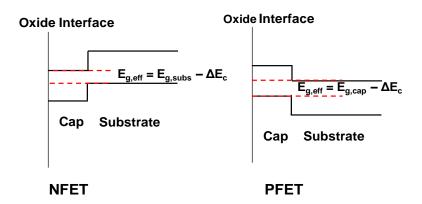

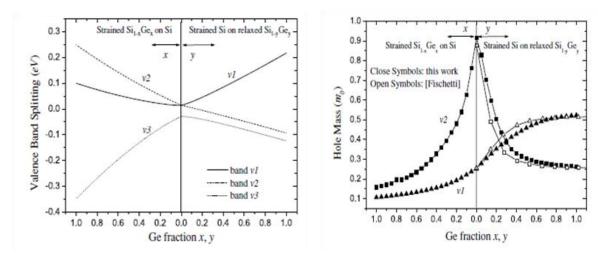

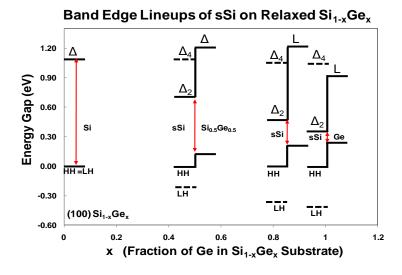

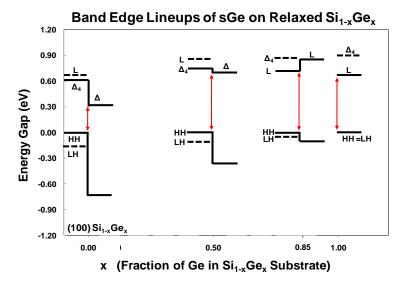

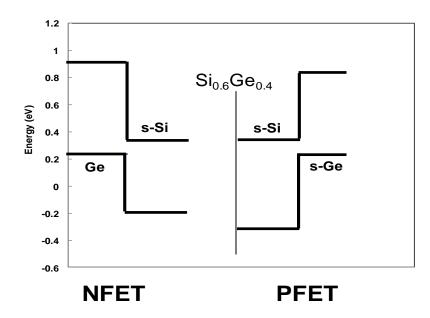

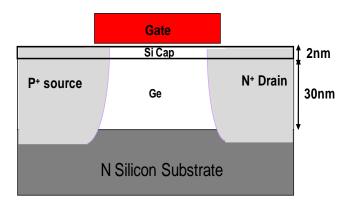

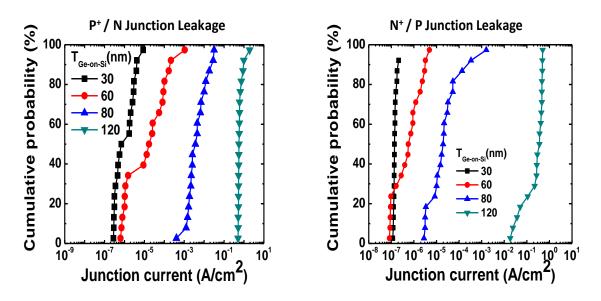

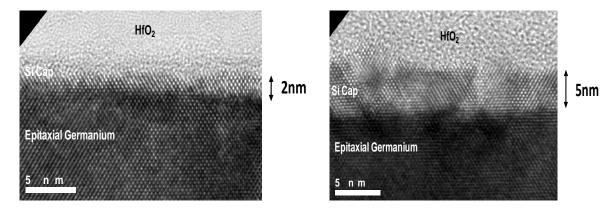

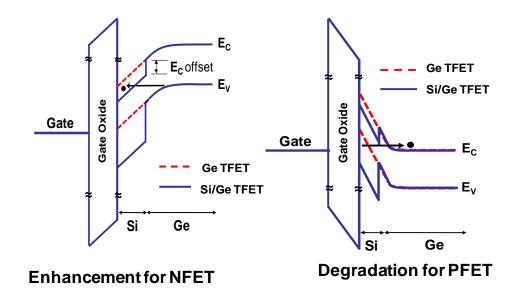

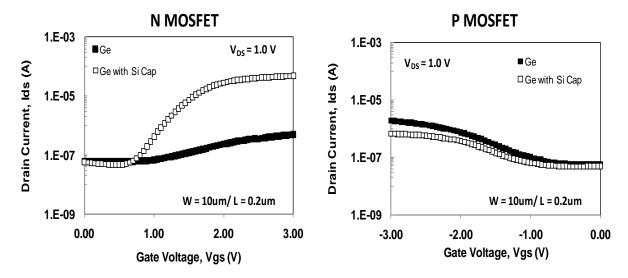

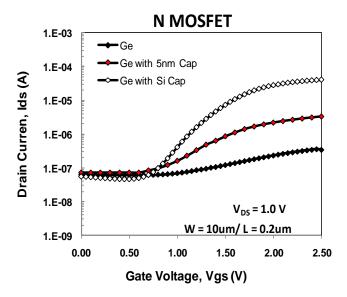

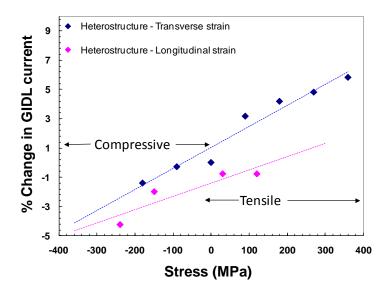

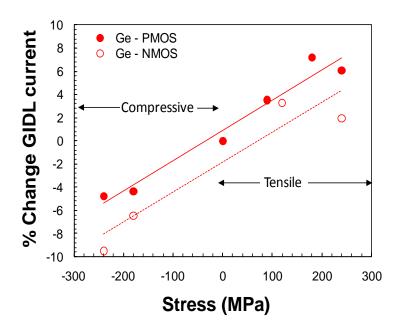

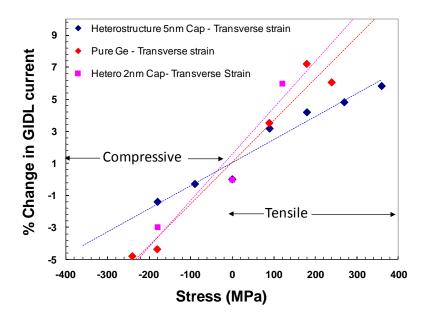

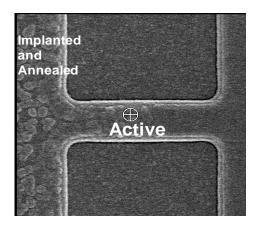

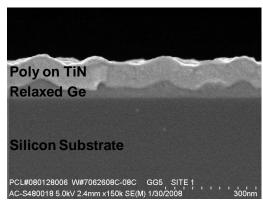

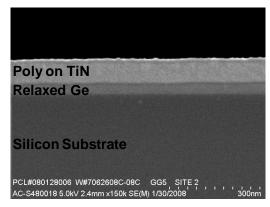

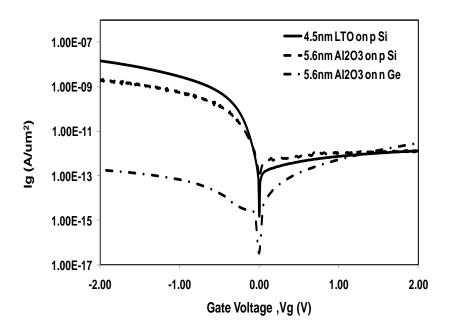

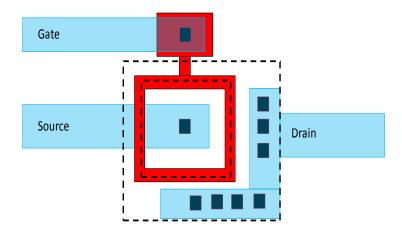

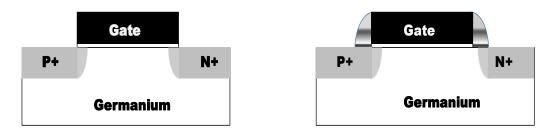

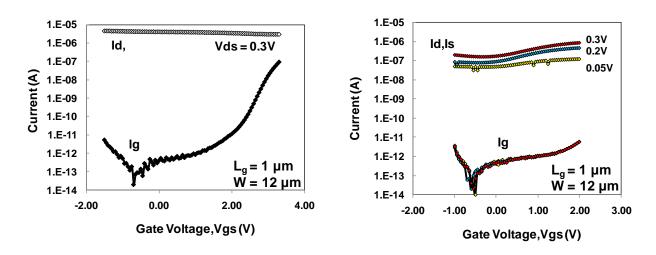

- [3.4] T. Krishnamohan, K. Donghyun, S. Raghunathan, K. Saraswat, "Double-Gate Strained-Ge Heterostructure Tunneling FET (TFET) With record high drive currents and <60mV/dec subthreshold slope," Electron Devices Meeting, 2008. IEDM 2008. IEEE International, vol., no., pp.1-3, 15-17 Dec. 2008