# Design and Measurement of Parameter-Specific Ring Oscillators

Lynn Tao-Ning Wang

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2010-159 http://www.eecs.berkeley.edu/Pubs/TechRpts/2010/EECS-2010-159.html

December 16, 2010

Copyright © 2010, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Design and Measurement of Parameter-Specific Ring Oscillators

by

Lynn Tao-Ning Wang

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Andrew R. Neureuther Professor Tsu-Jae King Liu Professor Elad Alon Professor Fiona M. Doyle

Fall 2010

### Design and Measurement of Parameter-Specific Ring Oscillators

Copyright © 2010

by

Lynn Tao-Ning Wang

All rights reserved

#### Abstract

#### Design and Measurement of Parameter-Specific Ring Oscillators

By

#### Lynn Tao-Ning Wang

#### Doctor of Philosophy in Electrical Engineering and Computer Sciences

#### University of California, Berkeley

#### Professor Andrew R. Neureuther, Chair

Electronic monitoring utilizing process-specific Ring Oscillators (RO) is explored as a means of identifying, quantifying, and modeling sources of variation in circuit performance due to manufacturing and layout design parameters. This approach is motivated by the need to mitigate the increased impact of process variability on circuit performance in the scaling of CMOS. To reduce such impact, there is a need to monitor, analyze, and understand process variation in order to improve current design methodologies. This work contains the first measured silicon results for the utilization of parameter-specific modification of ring oscillator layouts to electronically monitor particular process variation. Design and testing for this work were made possible through the Berkeley Wireless Research Center. The working circuits were fabricated by ST Micro in a 45 nm fabrication process that was under development.

The design was based on a process design kit (PDK) provided by ST Micro. The lithography simulation was carried out using generic models in Mentor Graphics Calibre. Five systematic process effects were considered: etch, focus, misalignment, and capping layer and Shallow Trench Isolation (STI) stress. In all cases, inverter layouts were modified in order to increase sensitivity to a particular parameter within design rule constraints. Due to the dependence of layout geometries on parasitic capacitance, it was also necessary to pre-correct measurements for this effect. A total of 32 different inverter layouts were designed.

For monitoring etch, the presence or absence of adjacent dummy gates and pre-correction for residual lithographic effects were used. For monitoring gate focus, spillover functions and Pattern Matching were used as an initial guide to place added surroundings to the gate; this was followed by systematic optimization via Mentor Graphics Calibre simulations. A bias was added to the gate length, but it was assumed that other Optical Proximity Correction (OPC) methods typically used in production, such as scatter-bar insertion, would not be applied. A focus sensitivity of 1.5 times that of a dense gate was achieved. For monitoring gate-to-active misalignment, a set of 5 pre-programmed offsets on an 'H-shaped diffusion' was designed. The RO frequency versus offset relationship in design showed a parabolic shape with a speed up of 3.2% for 15nm misalignment. The capping layer and lateral STI stress monitors were designed based on changes in the lateral size of the source and drain, including those of asymmetrical source/drain areas.

Each RO monitor consists of 13 inverter stages of one of the aforementioned inverter types. The thirty-two inverter layouts were formed into an instantiation that was then repeated 12 times in a local block. This RO block was instantiated 3 times within the  $2x2 \text{ mm}^2$  chip such that there are 36 instantiations for each RO monitor type per chip. This chip was merged with other chips to form a large overall field size, ensuring that the printed test chips were likely more than 1 cm apart.

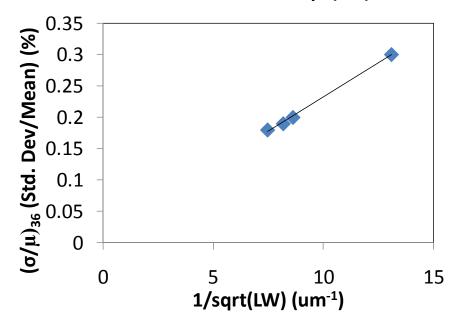

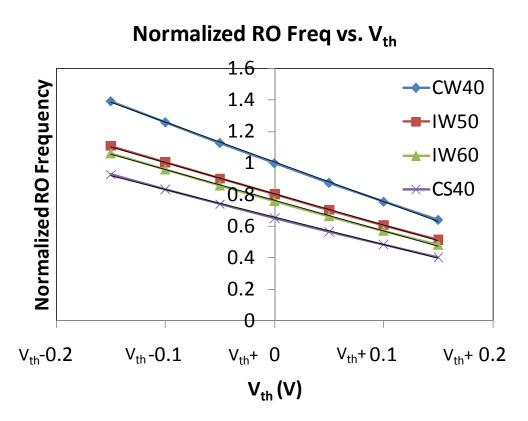

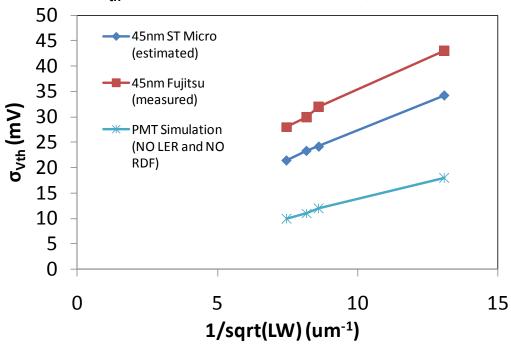

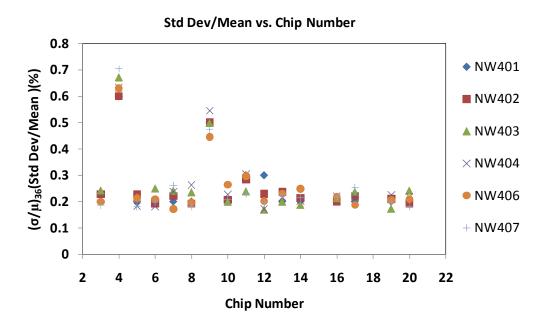

Seventeen chips were received, packaged, and automatically tested. Every ring oscillator worked for every chip. The measured range of the across-wafer variation was 11.1% for control-case RO with minimum sized gate area. Fifteen chips had a small block-to-block variation of  $\sim$ 1.3%. For a given monitor on a typical chip, the variation among the 36 RO instantiations normalized to its mean is 0.2-0.3 %, with the larger value occurring for the smaller gate areas. When these values were multiplied by the square root of the product of 36 instances time 26 transistors per RO, the average threshold slope (AVT) of 2.3mV/um was obtained in an equivalent Pelgrom model.

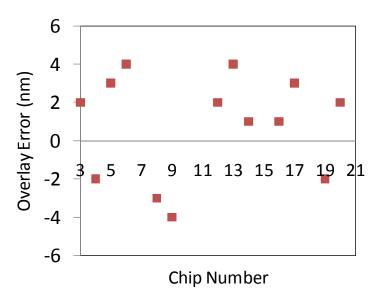

The measured RO frequency sensitivity to gate focus monitors shows that they are about 4% slower than the control ROs. This decrease is attributed to parasitic effects as well as the non-uniform 'hour-glass' shape produced at the top and bottom of the gate from the horizontal extensions used to increase focus sensitivity. The pre-programmed gate-to-active misalignment monitors show a 2-4 nm overlay error for 17 chips. The fact that the experimental measurements are less sensitive than predicted during the design stage is in part attributed to the fact that the wafer was run under unusually good control without any programmed treatments such as defocus. This observation is supported by the fact that the measured range of RO frequency was typically centered and  $1/6-1/4^{th}$  of the SS-FF guard band. The unanticipated requirement to apply strong OPC techniques with scatter-bars to the monitor designs in order to guarantee that they would not impact product yield also resulted in considerable sensitivity loss. This loss not only occurred for the layout monitors with isolated gates, but also for the active 'H-shape' misalignment monitors where process variation of the active layout including its height and curvature at the off-set gate position was reduced.

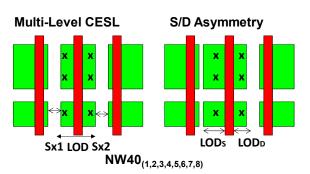

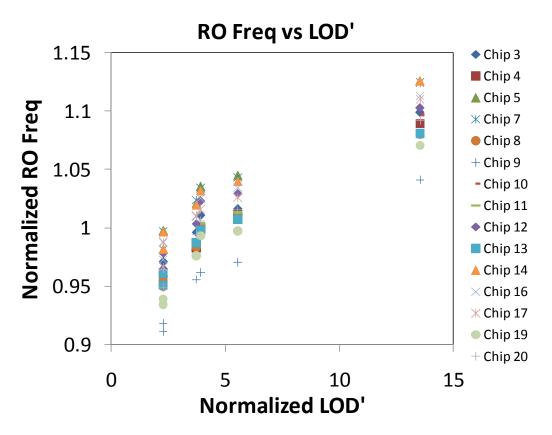

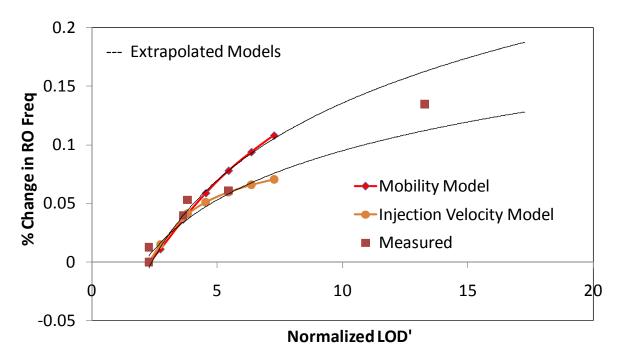

The Nitride Contact Etch Stop Liner (CESL) strain-induced monitors show a ring oscillator frequency increase of 5.3% and 13.9% for 1.8X and long length source/drain diffusion (LOD) respectively as compared to minimum LOD, after the normalization of raw data to simulation data so as to correct for parasitic effects. This increase is due to increased CESL-induced strain for large LOD. For the same LOD, asymmetrical designs show a 3% ring oscillator frequency increase for larger source LOD than that of larger drain LOD, indicating transistor injection velocity as well as mobility is important. These layout geometries are simulated by Nuo Xu in order to model CESL's impact on mobility and injection velocity. The measured RO frequencies show that the 45nm devices operate in a regime between the mobility and velocity injection models.

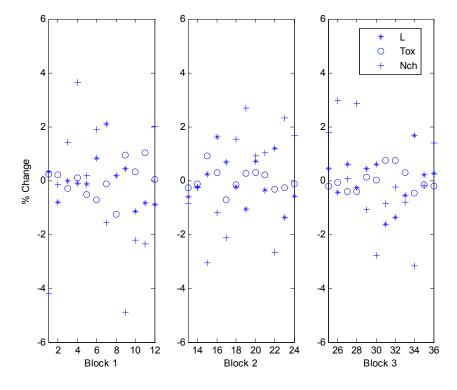

The random variation of RO circuit performance for a given layout monitor within a chip is examined for 3 sources of variations: changes in gate length ( $\Delta L$ ), gate oxide thickness ( $\Delta T_{ox}$ ), and channel doping ( $\Delta N_{ch}$ ). The strategy here is to make a linear approximation of the measured RO frequency sensitivity to these 3 parameters under 5 distinct combinations of operating voltages and temperatures using the 45nm PDK BSIM4/PSP models. The strategy is implemented using least mean square (LMS) analysis. Measured block means were used on one outlier chip that showed 5% slower RO frequency in a third block. For all of the blocks, the LMS results indicate that the source of random within-chip variation is dominated by random dopant fluctuations in comparison with changes in  $\Delta L$  and  $\Delta T_{ox}$ . Since the decrease in RO frequency for the third block was similar for the two focus and control monitor-pairs, the decrease in measured RO frequency is unlikely to be due to a change in focus.

This thesis demonstrates that "parameter-specific ring oscillators" are suitable for multiple critical applications in quantifying systematic and random effects in the co-optimization of process development and circuit design. While parameter-specific RO monitors provide a permanent record of process effect, they are best used during process development and calibration, when less stringent design rules, no-OPC drop-ins, and programmed treatments can be accommodated, yielding inverter layouts with higher as well as directly verifiable sensitivity to process variation. To my family

### Acknowledgements

I am heartily thankful to my research advisor, Professor Andrew R. Neureuther, for his encouragement, supervision, and support from the preliminary work to the concluding chapters of this dissertation. He was always available whenever I needed help, from solving a difficult research problem to rehearsing a conference presentation. I learned a lot from him.

This dissertation is a collaborative effort among the lithography, device, and circuits groups at UC Berkeley. I worked with many professors, and I am grateful for their guidance. Professor Borivoje Nikolic guided me through my first tapeout, provided me with technical feedback on digital circuit designs, and encouraged me to publish at various conferences. Professor Tsu-Jae King Liu gave me technical advice on correlating ring oscillator frequency results to device characteristics and helped me improve upon my technical writing skills. I received a lot of great feedback on my research from Professor Elad Alon. He also taught me how to make better technical presentations. I also appreciated Professor Fiona M. Doyle's comments, which greatly enhanced this dissertation.

I am also very thankful for the help from several colleagues. Liang-Teck Pang taught me about electronic monitoring. Seng-Oon Toh helped and guided me in testing. Nuo Xu and Darsen Lu ingrained in me an immense amount of device knowledge that was necessary for the completion of this dissertation.

This dissertation would not have been possible without the contributions of the students, faculty, and sponsors of the Berkeley Wireless Research Center (BWRC) and the wafer fabrication donation of ST Micro. I would like to make special references to Yorick Trouiller from ST Micro. Without his cooperation, I would not have obtained such relevant data. I really appreciate the sponsors of my research: the UC Discovery Grant ele07-10283 under the IMPACT project and SRC Research Tasks 1443.

I am grateful to my research group members for their friendship and support during the past years: Daniel Ceperley, Eric Chin, Chris Clifford, Marshal Miller, Wojtek Poppe, and Juliet Rubinstein. I thank them for enriching my graduate school life by leading me to get involved with WICSE, PhotoBears, intramural soccer, and rock climbing. In addition, I would like to thank Jae-Seok Yang from Samsung, who changed my life by introducing me to CAD, lithography, and most importantly, Professor Neureuther. I would also like to acknowledge Kenji Yamazoe, a stellar visiting scholar from Canon, who provided me with immense help and support during my qualifying exam as well as the latter part of my graduate school career. His technical advice and encouraging words were invaluable to me.

Lastly, I owe my deepest gratitude to my family for their unconditional love and moral support.

# **Table of Contents**

| Acknowledgements                                                                                        | ii      |

|---------------------------------------------------------------------------------------------------------|---------|

| Table of Contents                                                                                       | iii     |

| Table of Figures                                                                                        | vii     |

| Table of Tables                                                                                         | xii     |

| Chapter 1: Introduction                                                                                 | 1       |

| 1.1 Motivation                                                                                          | 1       |

| 1.2 Dissertation Content and Contributions                                                              | 2       |

| Chapter 2: Characterizing Variability                                                                   | 4       |

| 2.1 Modeling Within-Chip/Across-Chip, Random/Systematic and Dynamic/Static Variab                       | ility 4 |

| 2.2 Sources of Process and Layout-Induced Variation                                                     | 7       |

| 2.2.1 Variations in the Lithography Exposure System                                                     | 8       |

| 2.2.2 Variation in Patterning and Other Manufacturing Steps                                             | 11      |

| 2.3 Process Characterization Methodologies                                                              | 12      |

| 2.3.1 Frequency                                                                                         | 12      |

| 2.3.2 Current: I <sub>d, SAT</sub> and I <sub>d, LEAK</sub>                                             | 13      |

| 2.4 CAD Tools for Monitor Design Enablement                                                             | 13      |

| 2.4.1 Parametric Yield Simulator (PYS)                                                                  | 14      |

| 2.4.2 Pattern Matching Physics                                                                          | 15      |

| 2.5 Design of Gate Lithography Focus Monitors using the Parametric Yield Simulator and Pattern Matching |         |

| 2.6 Summary                                                                                             | 22      |

| Chapter 3: 45nm Ring Oscillator Monitors Experimental Design                                            | 23      |

| 3.1 RO Frequency Sensitivity Analyses for 90nm Test Chip Measurements                                   | 23      |

| 3.1.1 RO Frequency Sensitivity to Gate Length and Electrical Parasitics                                 | 24      |

| 3.1.2 RO Frequency Sensitivity to Gate Lithography Dose and Focus                                       | 25      |

| 3.1.3 Prediction of RO Sensitivity from PYS Lithography Modeling                                        | 27      |

| 3.2 Ring Oscillator Schematics and Floor Plans for 45nm                                                 | 28      |

| 3.3 Summary of the RO Inverter Layouts and the Nomenclature                                                      | 30 |

|------------------------------------------------------------------------------------------------------------------|----|

| 3.4 Pattern Matching Guidance for Design of the RO Monitors for Lithography                                      | 32 |

| 3.4.1 A Strehl Ratio Test for Process Variation (PV) Band Calibration                                            | 32 |

| 3.4.2 Using the Pattern Matcher to Optimize RO Monitor Design                                                    | 33 |

| 3.5 Specific Designs for Etch and Lithography Monitors                                                           | 34 |

| 3.5.1 RO Monitors for Etch Dependence of Poly                                                                    | 34 |

| 3.5.2 RO Monitors for Focus Dependence of Poly                                                                   | 35 |

| 3.5.3 RO Monitors for Gate-to-Active Overlay Using Pre-Programmed Offsets                                        | 36 |

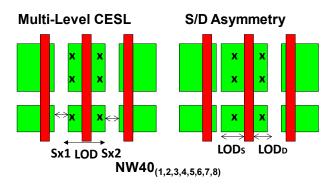

| 3.6 Designing Nitride CESL-Induced Strain and STI-Induced Stress RO Monitors                                     | 39 |

| 3.7 Summary                                                                                                      | 40 |

| Chapter 4: 45nm Ring Oscillator Testing methodologies and Noise Analysis                                         | 41 |

| 4.1 Automated RO Frequency Measurement Setup and Testing Methodologies                                           | 41 |

| 4.1.1 An overview of the RO Frequency Measurement Test Setup                                                     | 41 |

| 4.1.2 Adjustment of Operating Voltages and Temperatures                                                          | 43 |

| 4.1.3 RO Measurement Sequence                                                                                    | 44 |

| 4.2 Measurement System Noise and Drift                                                                           | 45 |

| 4.2.1 RO Measurement Jitter                                                                                      | 45 |

| 4.2.2 RO Measurement Drift                                                                                       | 46 |

| 4.3 Measured Block-to-Block Variation                                                                            | 48 |

| 4.4 Measured Across-Wafer Variation                                                                              | 50 |

| 4.5 Summary                                                                                                      | 55 |

| Chapter 5: Experimental RO Frequency Sensitivity to Gate Etch, Gate Lithography Focus, an Gate-to-Active Overlay |    |

| 5.1 Simulated RO Frequency Variability using Process Corners and Process Variation Band                          | ds |

|                                                                                                                  |    |

| 5.1.1 Simulated Process Corners versus Measured RO Frequencies                                                   |    |

| 5.1.2 PV Bands and SPICE Simulations versus Measured RO Frequency                                                |    |

| 5.2 RO Frequency Sensitivity to Gate Etch                                                                        | 58 |

| 5.2.1 Measured RO Frequency Sensitivity to Gate Etch                                                             | 58 |

| 5.2.2 Simulated RO Frequency Sensitivity to Gate Etch using Process Corners                                      | 60 |

| 5.2.3 Simulated RO Frequency Sensitivity to Gate Etch Monitors using PV Bands and SPICE.                         | 62 |

| 5.3 RO Frequency Sensitivity to Gate Lithography Focus                                               | 62      |

|------------------------------------------------------------------------------------------------------|---------|

| 5.3.1 Measured RO Frequency Sensitivity to Gate Lithography Focus                                    | 63      |

| 5.3.2 Simulated RO Frequency Sensitivity to Gate Lithography Focus using Process<br>Corners          |         |

| 5.3.3 Simulated RO Frequency Sensitivity to Gate Lithography Focus using PV Bar<br>SPICE             |         |

| 5.3.4 Across-Wafer Correlation Plots                                                                 | 67      |

| 5.4 RO Frequency Sensitivity to Gate-to-Active Misalignment                                          | 68      |

| 5.5 Summary                                                                                          | 69      |

| Chapter 6: RO Frequency Sensitivity to Nitride CESL and STI-Induced Stress                           | 71      |

| 6.1 RO Frequency Sensitivity to Nitride CESL-Induced Strain                                          | 71      |

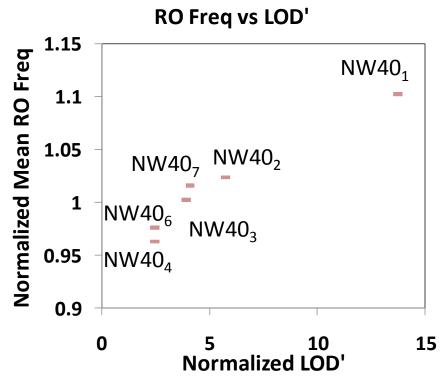

| 6.1.1 RO Frequency Sensitivity versus LOD'                                                           | 72      |

| 6.1.2 Measured RO Frequency Distributions for Two Different 45nm Tapeouts                            | 74      |

| 6.1.3 RO Frequency Sensitivity Averaged Across 15 Typical Chips versus LOD'                          | 75      |

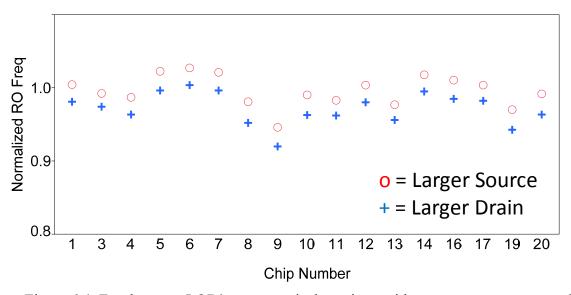

| 6.1.4 RO Frequency Sensitivity to Asymmetrical Source/Drain                                          | 75      |

| 6.1.5 RO Frequency versus Mobility and Injection Velocity Models                                     | 77      |

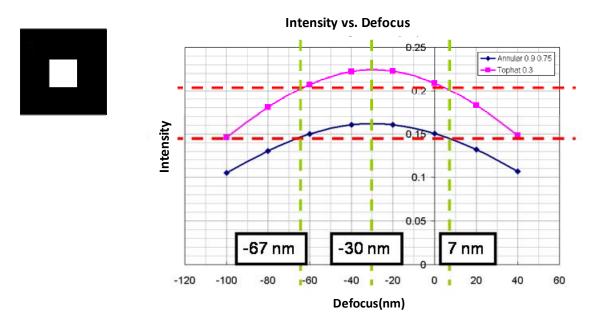

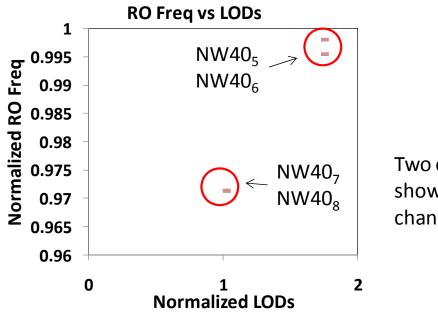

| 6.2 RO Frequency Sensitivity to STI-Induced Stress                                                   |         |

| 6.3 Summary                                                                                          | 79      |

| Chapter 7: Random Noise Analysis: Gate Length, Gate Oxide Thickness, and Doping Va                   |         |

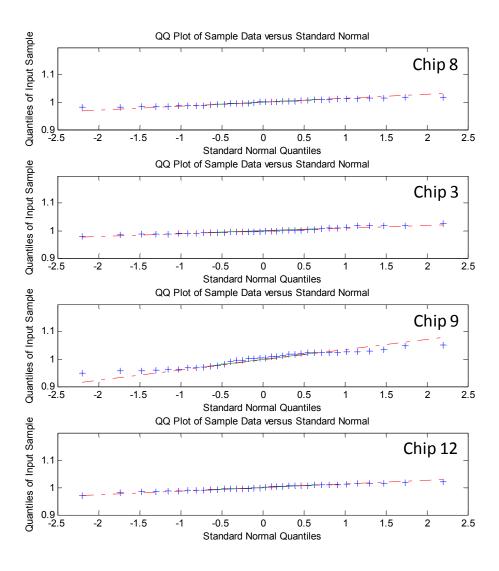

| 7.1 Quantile-Quantile (QQ) and Autocorrelation Plots of RO Frequency Measurement                     |         |

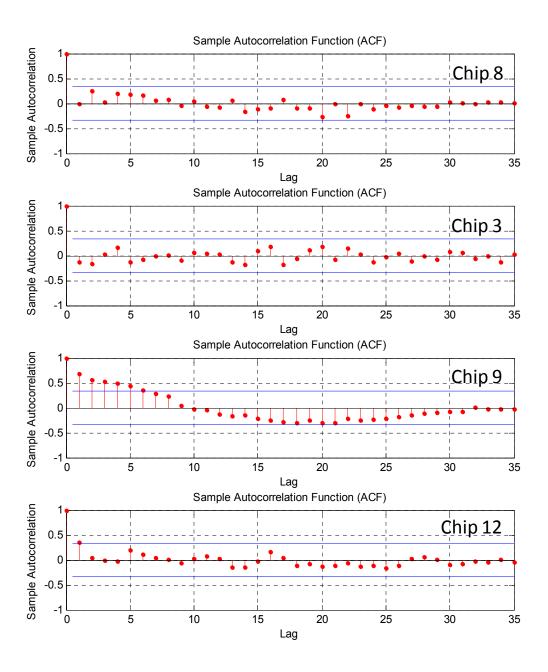

| 7.1.1 QQ Plots                                                                                       | 82      |

| 7.1.2 The Autocorrelation Plots                                                                      | 83      |

| 7.2 Block-to-Block Analysis for Outlier Chips                                                        | 84      |

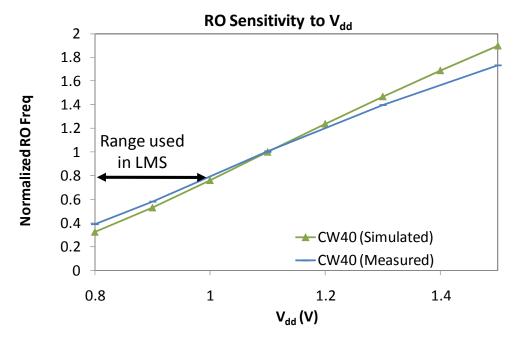

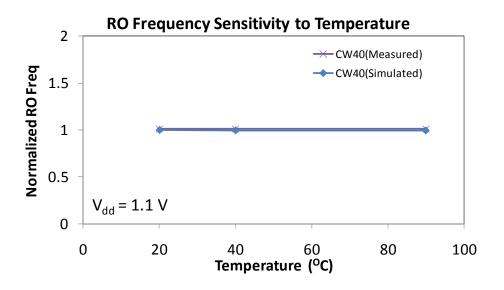

| 7.3 RO Frequency Sensitivity to Operating Voltages (V <sub>dd</sub> ) and Temperature (T)            | 85      |

| 7.4 Inferring Process Parameter from Random Sources of Variability using Least Mea<br>(LMS) Analysis | -       |

| 7.4.1 The Index Definitions                                                                          | 87      |

| 7.4.2 The Variable Definitions and RO Frequency Sensitivity to L, $T_{ox}$ , and $N_{ch}$ Ext        | raction |

|                                                                                                      |         |

| 7.4.3 The Matrix Definitions                                                                         | 88      |

| 7.5 Error Analysis for the LMS Solution                                        | 92  |

|--------------------------------------------------------------------------------|-----|

| 7.6 Summary                                                                    | 94  |

| Chapter 8                                                                      |     |

| 8.1 Design                                                                     | 95  |

| 8.2 Measurement Methodology                                                    |     |

| 8.3 Initial Measurement Results                                                |     |

| 8.4 Monitoring of Gate Etch, Gate Lithography, and Gate-to-Active Misalignment |     |

| 8.5 Monitoring of Nitride CESL and STI-Induced Stress                          | 98  |

| 8.6 Random Noise Analysis using Least Mean Squares                             |     |

| 8.7 Overall Perspective                                                        | 99  |

| Bibliography                                                                   | 102 |

# **Table of Figures**

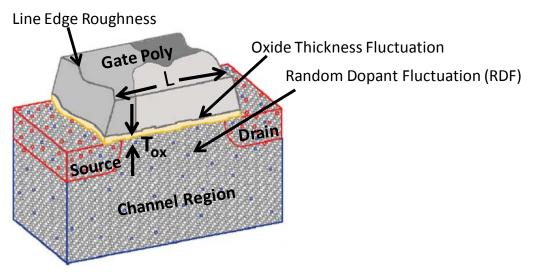

| Figure 2.1: The transistor cross-section and sources of random variability                                |

|-----------------------------------------------------------------------------------------------------------|

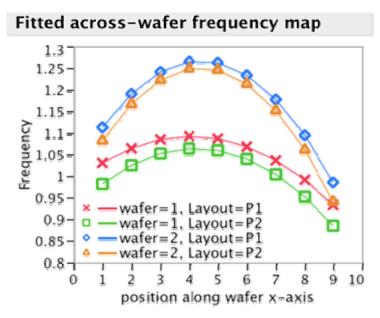

| Figure 2.2: A RO frequency measurement fitted across a wafer shows systematic parabolic                   |

| behavior [13]                                                                                             |

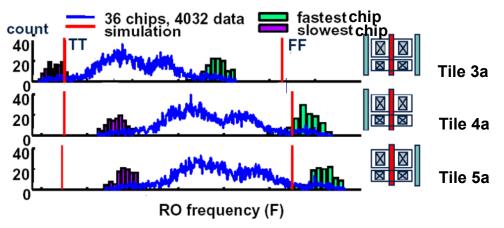

| Figure 2.3: The typical process-corner design methodology is not well-correlated with layout-             |

| induced systematic variation [1]                                                                          |

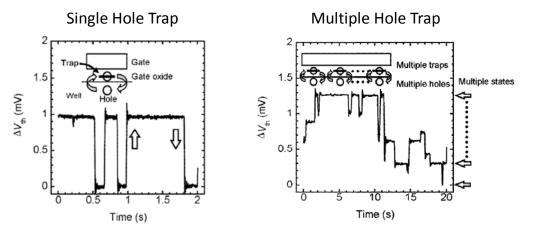

| Figure 2.4: Random telegraph signals (RTS), a dynamic source of variability, cause the threshold          |

| voltage, V <sub>th</sub> , to vary with time [14][15]7                                                    |

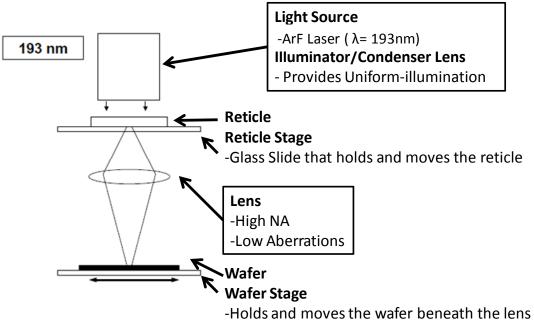

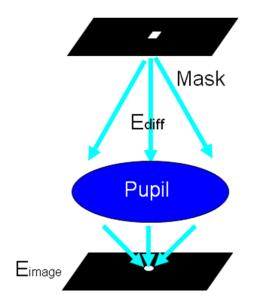

| Figure 2.5: A typical lithography imaging system [18]                                                     |

| Figure 2.6: The DOF concept is a range of lens-wafer distances such that the respective CDs are           |

| maintained within specifications                                                                          |

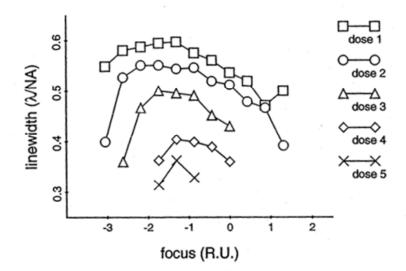

| Figure 2.7: Bossung plot shows that DOF and exposure dose control are quite important in                  |

| maintaining a uniform CD [20]                                                                             |

| Figure 2.8: The fabrication steps of poly-silicon gates show that CDs suffer from etch loading            |

| effects [1] 11                                                                                            |

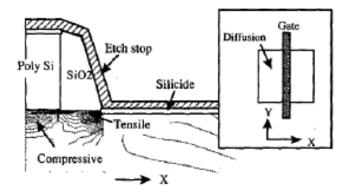

| Figure 2.9: The distribution of mechanical stress beneath the gate that is induced by the contact         |

| etch stop liner, which is also commonly referred to as the capping layer [23] 12                          |

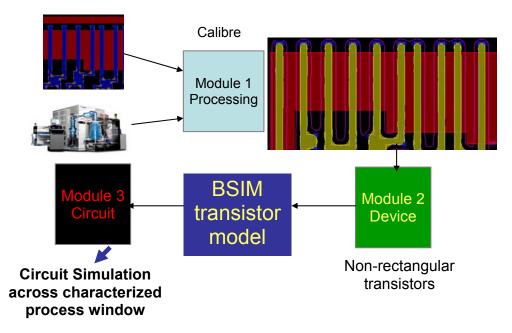

| Figure 2.10: Parametric Yield Simulator (PYS) flow [5]14                                                  |

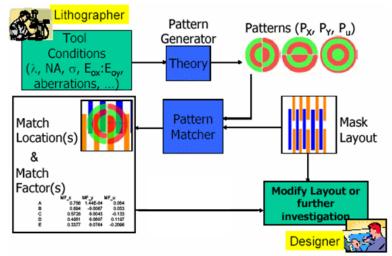

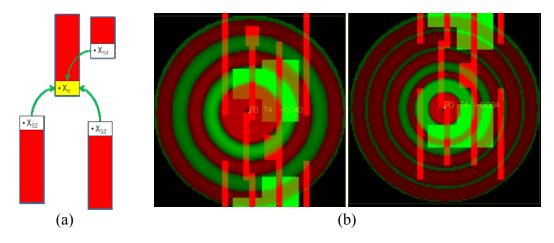

| Figure 2.11: The Pattern Matcher Concept and Flow [34]                                                    |

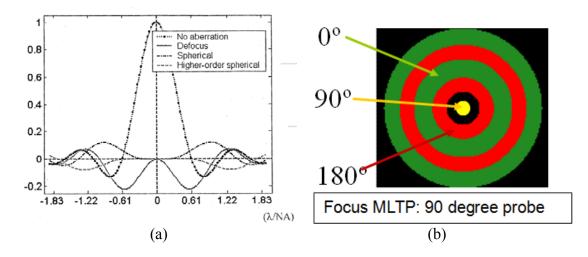

| Figure 2.12: The above kernels in (a) are computed by taking the inverse Fourier Transform of             |

| the corresponding Zernike terms [38], while (b) is an example of a focus monitor16                        |

| Figure 2.13: A typical lithography system                                                                 |

| Figure 2.14: In the Pattern Matcher, electric field spillover is combined onto an observation pixel       |

| $(X_o)$ from surrounding pixels $(X_{Si})$ , as shown in (a) via a convolution computation. In (b),       |

| examples of different kernels matched onto a point on the poly (red) layout are shown                     |

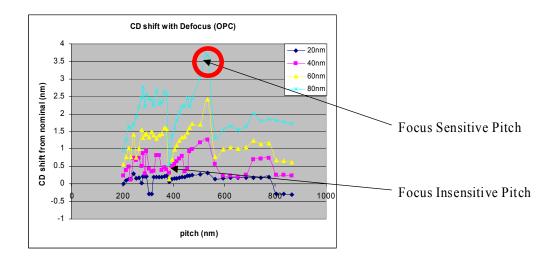

| Figure 2.15: The post-OPC simulated CD shift of 80nm gates for four different levels of defocus           |

| reveals that some pitches exhibit high sensitivity to focus while others are insensitive to focus. 19     |

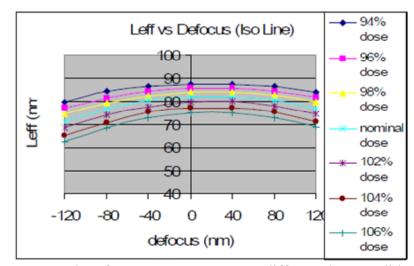

| Figure 2.16: Bossung plot of L <sub>effective</sub> vs. DOF across different dose conditions for an 80nm  |

| isolated line [5]                                                                                         |

| Figure 2.17: A simulated aerial image using PYS for a reticulated monitor is shown in (a), and            |

| the monitor's response through focus and dose is illustrated in (b) [5]20                                 |

| Figure 2.18: A simulated aerial image of a Zernike aberration monitor using PYS is shown in (a),          |

| and the monitor's response through focus and dose is given in (b). Since the center 90 <sup>0</sup> probe |

| region is hyper-sensitive to defocus, the gate CD is expected to change dramatically in response          |

| to the defocus in the scanner [5]                                                                         |

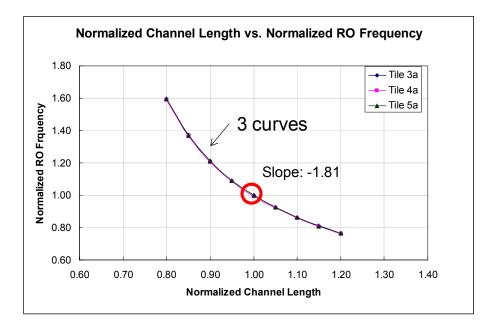

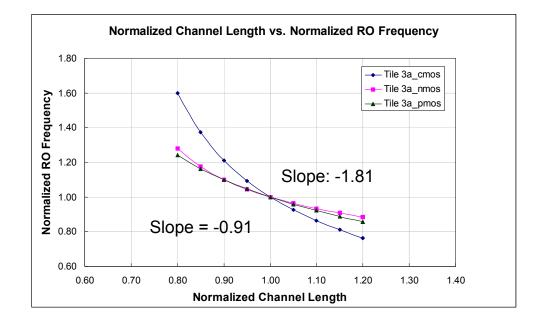

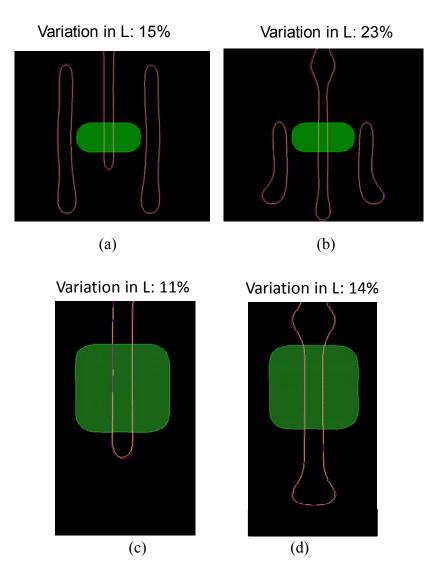

| Figure 3.1: The RO Frequency versus the Channel Length simulations for three monitors show that the presence or the lack of dummy gates has little effect on extracted results for a drawn gate length. The sensitivity at (1,1) is -1.8. 24 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.2: Sensitivity to the individual NMOS or PMOS device is half as big as the sensitivity to both devices                                                                                                                              |

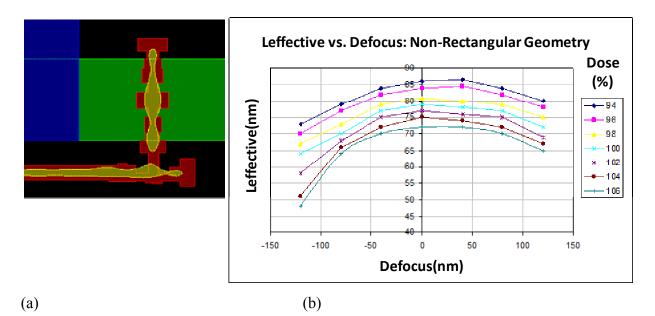

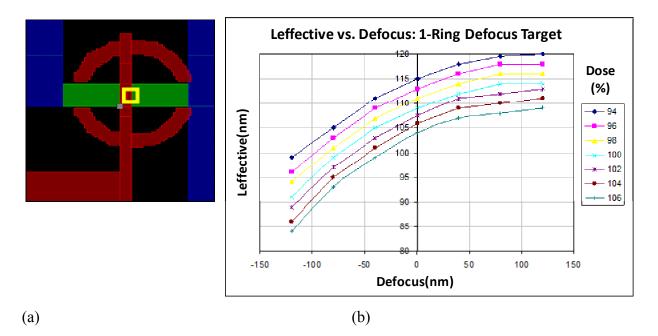

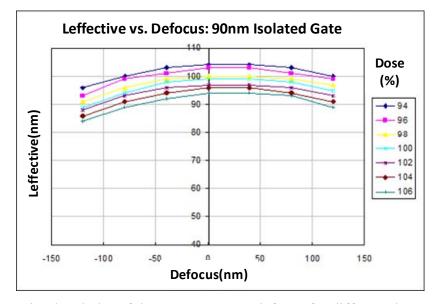

| Figure 3.3: A simulated plot of the L <sub>effective</sub> versus defocus for different dose conditions for an                                                                                                                               |

| <i>isolated</i> 90nm gate shows a $\Delta$ L <sub>effective, focus, NMOS</sub> =5.5%                                                                                                                                                         |

| Figure 3.4: A simulated plot of the L <sub>effective</sub> versus defocus for different dose conditions for a                                                                                                                                |

| dense 90nm gate shows a $\Delta$ L <sub>effective, focus, NMOS</sub> =3.0%. 27                                                                                                                                                               |

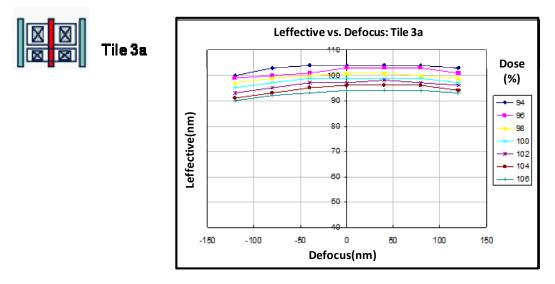

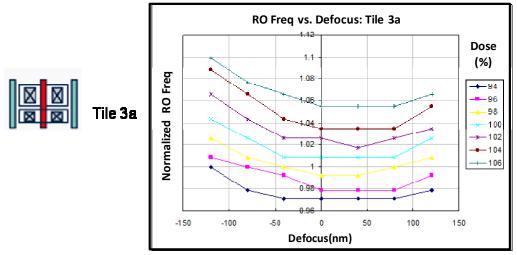

| Figure 3.5: Tile 3a's simulated plot of ring oscillator frequency versus defocus for different dose                                                                                                                                          |

| conditions is used to examine the measured across-wafer RO frequency spread                                                                                                                                                                  |

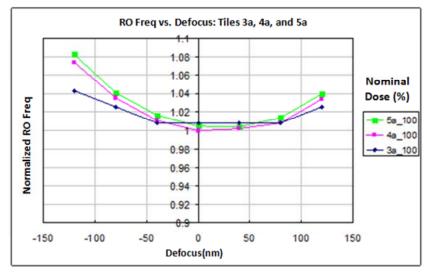

| Figure 3.6: A simulated plot of the RO frequency versus defocus for different dose conditions                                                                                                                                                |

| shows that the pattern dependent shift among monitors Tiles 3a, 4a, and 5a is likely due to a non-                                                                                                                                           |

| lithographic source, such as etch                                                                                                                                                                                                            |

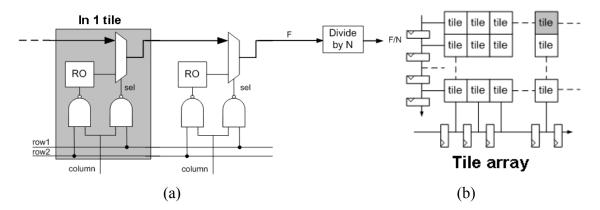

| Figure 3.7: The schematic of a ring oscillator tile arrayed in a row is shown in (a). A 2-D array                                                                                                                                            |

| with a set of vertical and horizontal scan-chains along the perimeter in order to enable row and                                                                                                                                             |

| column select can be seen in (b) [1]                                                                                                                                                                                                         |

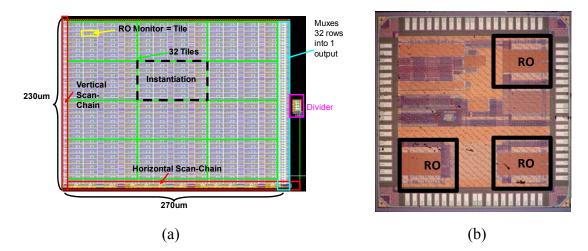

| Figure 3.8: The layout view of the 45nm ring oscillator array is shown in (a). Here, (b) shows the                                                                                                                                           |

| layout in (a) replicated at 3 different locations across the 2x2 mm <sup>2</sup> chip in order to capture the                                                                                                                                |

| variation due to the lithography scanner's slit and scan directions                                                                                                                                                                          |

| Figure 3.9: Summary of inverter layouts                                                                                                                                                                                                      |

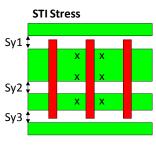

| Figure 3.10: A Strehl ratio test for a light square measuring $(0.4)\lambda$ \NA per side at tophat and                                                                                                                                      |

| annular illumination using Calibre simulation                                                                                                                                                                                                |

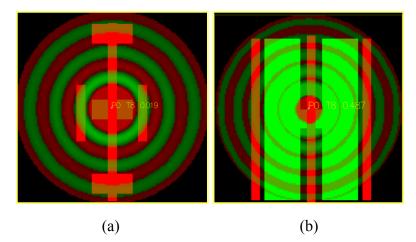

| Figure 3.11: (a) shows a coherent defocus MTLP matched at the poly layer of the layout. (b) shows a defocus MTLP with annular illumination that matches at the diffusion layer of the                                                        |

| layout                                                                                                                                                                                                                                       |

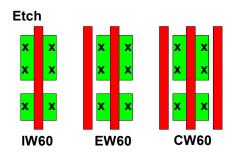

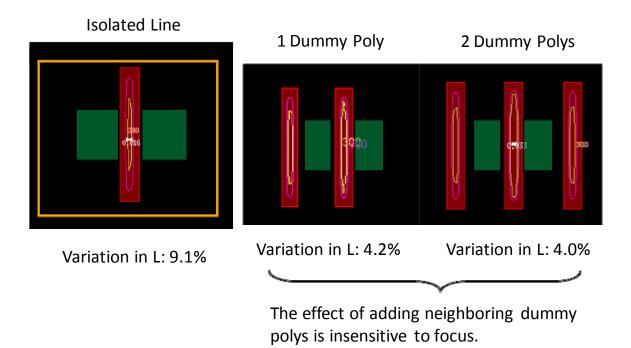

| Figure 3.12: Etch RO monitors are designed to show nearly identical changes in gate length due                                                                                                                                               |

| to defocus                                                                                                                                                                                                                                   |

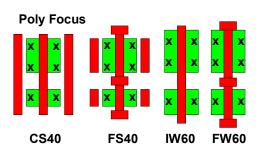

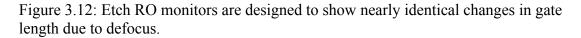

| Figure 3.13: (a) and (c) contain the control RO monitors, and (b) and (d) contain the 1.5x focus                                                                                                                                             |

| sensitive RO monitors at 40nm and 60nm, respectively                                                                                                                                                                                         |

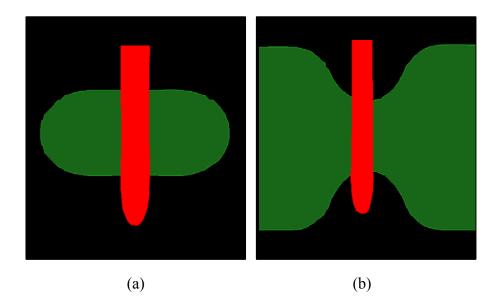

| Figure 3.14: (a) shows the simulation contours for a minimum-sized active area. (b) presents the                                                                                                                                             |

| H-shaped active area gate-to-active misalignment RO monitor                                                                                                                                                                                  |

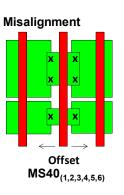

| Figure 3.15: (a) shows the simulation contours for a minimum-sized active area. (b) presents the                                                                                                                                             |

| wedge-shaped active area gate-to-active misalignment RO monitor                                                                                                                                                                              |

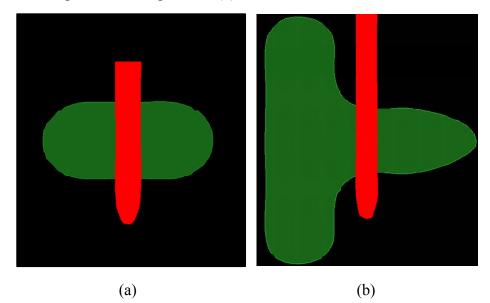

| Figure 3.16: Normalized width versus pre-programmed offsets for the H-shaped monitors at 0nm,                                                                                                                                                |

| +10nm, and +15nm, shown in (a) and for the wedge-shaped monitors at 0nm, +5nm, and +10nm,                                                                                                                                                    |

| shown in (b)                                                                                                                                                                                                                                 |

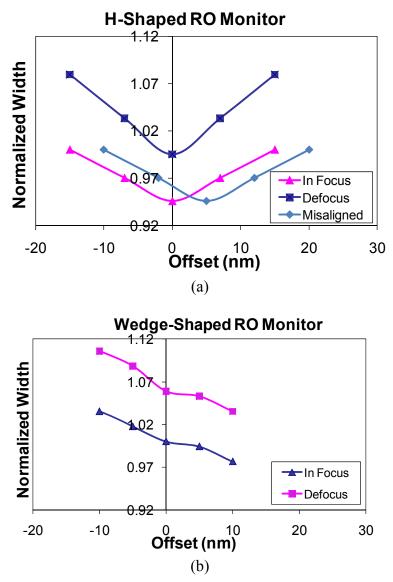

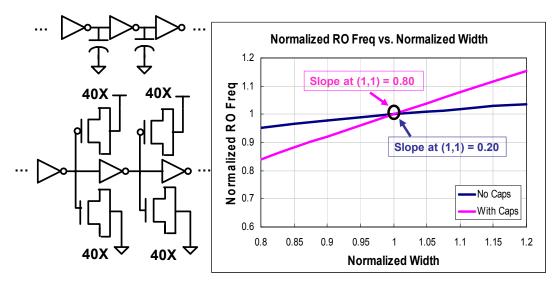

Figure 3.17: This plot of normalized ring oscillator frequency as a function of gate width, with and without capacitive load, shows that added capacitors increase the slope from 0.2 to 0.8. .... 39

### Chapter 4

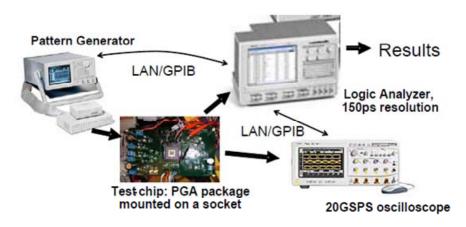

| Figure 4.1: Measurement setup [1]                                                                                                                                             | 42   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

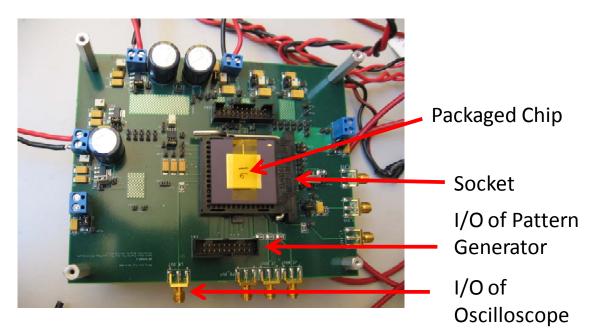

| Figure 4.2: Chip and PCB Photo                                                                                                                                                | 42   |

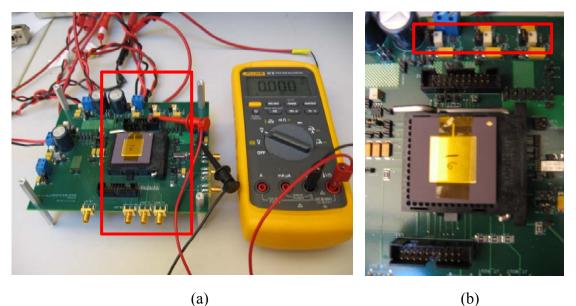

| Figure 4.3: Test setup for operating voltage (V <sub>dd</sub> ) experiments: the on-board regulators in (b)                                                                   | are  |

| adjusted for different voltage settings using a screw driver.                                                                                                                 | 43   |

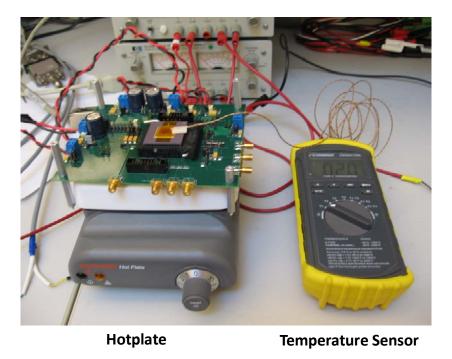

| Figure 4.4: Test setup for temperature experiments                                                                                                                            | 44   |

| Figure 4.5: RO monitors are measured sequentially from 1-36                                                                                                                   | 44   |

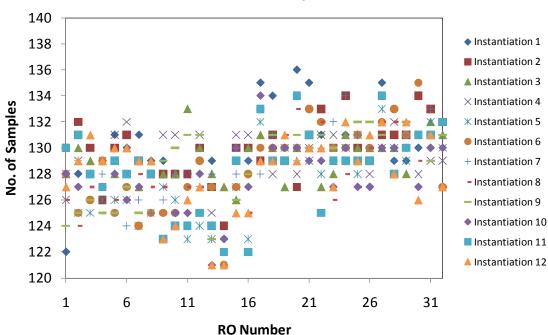

| Figure 4.6: The number of samples per RO in one RO block for a typical chip ranges from 12 140                                                                                |      |

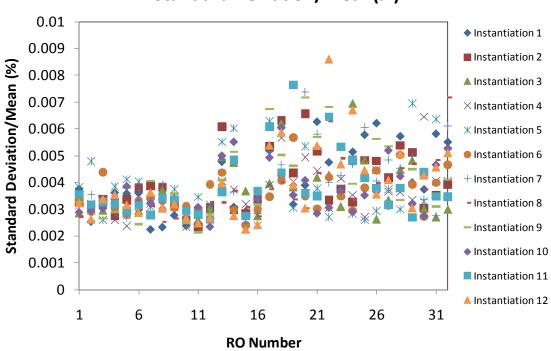

| Figure 4.7: The maximum standard deviation to mean percentage is 0.009%                                                                                                       | 46   |

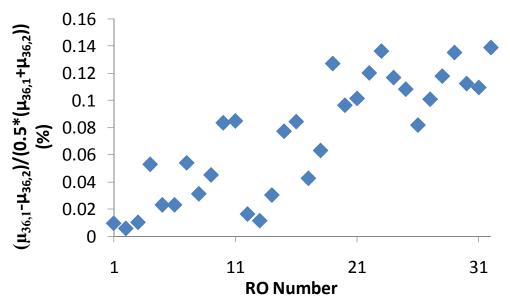

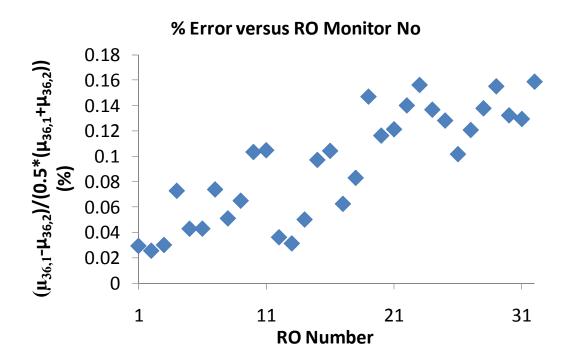

| Figure 4.8: Maximum percentage difference between the measured and re-measured data with                                                                                      | hout |

| intervention for a chip is 0.14%                                                                                                                                              | 47   |

| Figure 4.9: The percentage difference of measured and re-measured data for a chip is greater                                                                                  | if   |

| the test setup is reassembled.                                                                                                                                                | 48   |

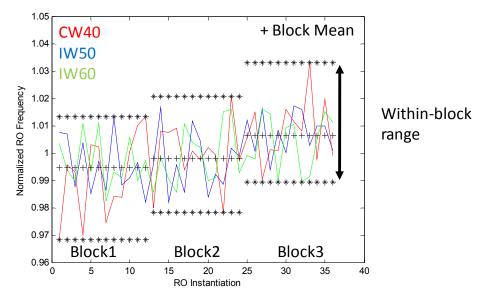

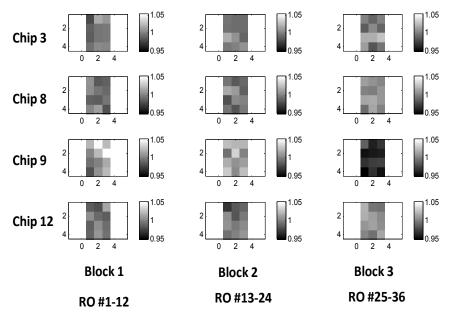

| Figure 4.10: The measured RO frequency for 36 RO instantiations for one typical chip, that o                                                                                  | f    |

| Chip 8                                                                                                                                                                        | 49   |

| Figure 4.11: The measured RO frequency normalized to the mean for that chip shows random within-block variation.                                                              |      |

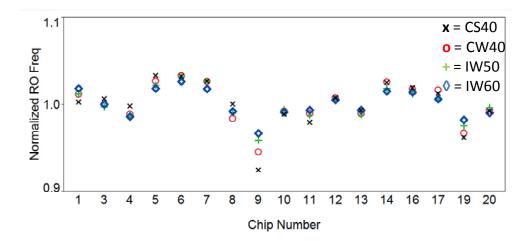

| Figure 4.12: The mean measured RO frequency normalized to the mean for the RO monitor designs CS40, CW40, IW50, and IW60 show an across-wafer variation range of 11.11%, 8.84 |      |

| 7.35%, and 5.99%, respectively                                                                                                                                                | 51   |

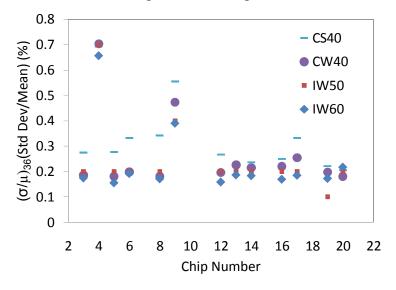

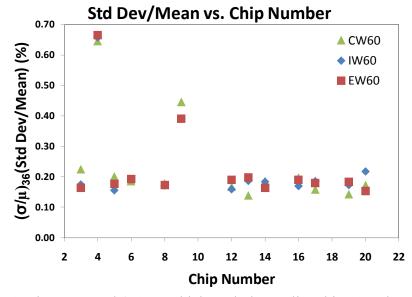

| Figure 4.13: Within-chip $(\sigma/\mu)_{36}$ distribution shows that outlier chips 4 and 9 are noisier when                                                                   | 1    |

| compared to typical chips.                                                                                                                                                    | 51   |

| Figure 4.14: RO monitors employing smaller-area inverters show greater variation in regard t                                                                                  | 0    |

| measured RO frequency                                                                                                                                                         | 52   |

| Figure 4.15: Simulated RO frequency versus threshold voltage for RO monitors CW40, IW50                                                                                       |      |

| IW60, and CS40 show a slope of -2.51/mV, -1.98/mV, -1.94/mV, -1.75/mV, respectively                                                                                           | 53   |

| Figure 4.16: The Pelgrom plots for three 45nm technologies                                                                                                                    | 54   |

| Figure 5.1: The SPICE corner simulations correlate with the mean measured RO frequency  | . 57 |

|-----------------------------------------------------------------------------------------|------|

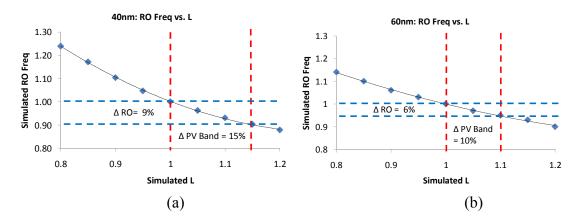

| Figure 5.2: PV band and SPICE simulation results for CW40 (a) and IW60 (b).             | . 58 |

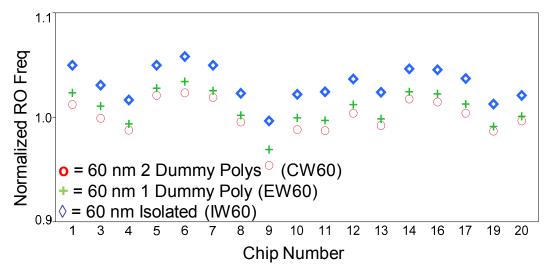

| Figure 5.3: The mean measured RO frequencies reveal that the dummy polys reduce RO      |      |

| frequency by 3%. The across-wafer peak-to-peak variation for IW60, EW60 and CW60 are ~6 | 6-   |

| 7%                                                                                      | . 59 |

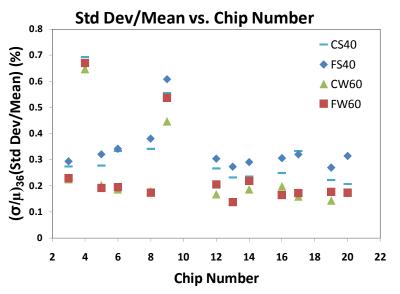

| Figure 5.4: The measured $(\sigma/\mu)_{36}$ which excludes outlier chips 4 and 9 shows that the $(\sigma/\mu)_{36}$ is ~0.2%. |

|--------------------------------------------------------------------------------------------------------------------------------|

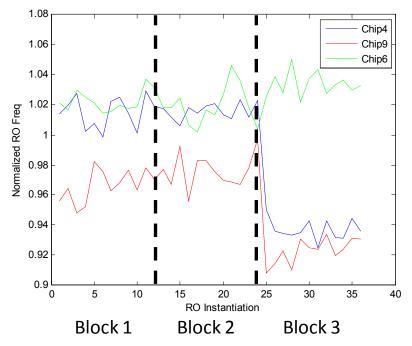

| Figure 5.5: Systematic block-to-block effects are evident in the outlier chips: 6 and 9                                        |

| Figure 5.6: A comparison of measured and process-corner simulated RO frequency for CW60,                                       |

| EW60, and IW60, respectively                                                                                                   |

| Figure 5.7: The mean measured RO frequency for the 40nm drawn gate length shows that the                                       |

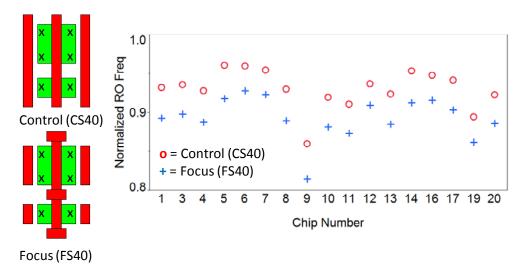

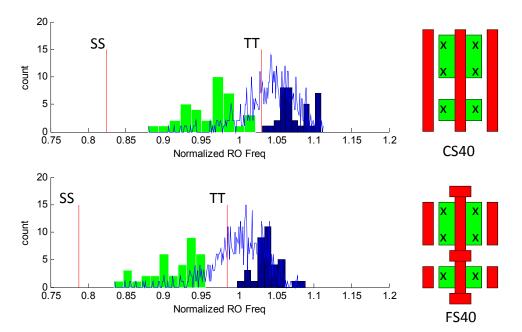

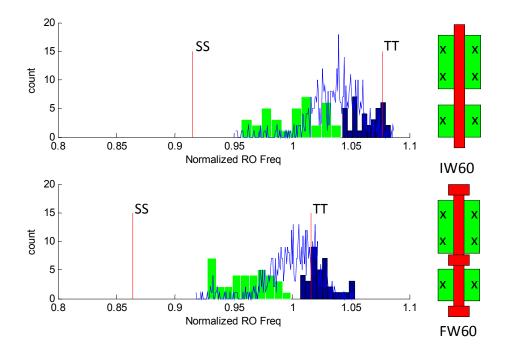

| hammerheads result in about a 4% lower RO frequency. The across-wafer peak-to-peak variation                                   |

| for the control (CS40) and focus monitor (FS40) vary by <1%, when outlier chips 4 and 9 are                                    |

| removed                                                                                                                        |

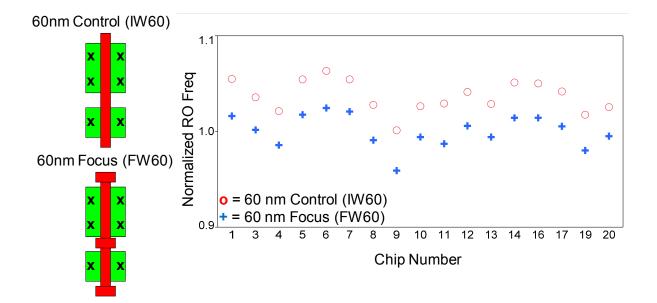

| Figure 5.8: The mean measured RO frequency for 60nm drawn gate length shows that the                                           |

| hammerheads result in a 4% lower RO frequency. The across-wafer peak-to-peak variation for                                     |

| the control (IW60) and focus monitor (FW60) varies by <1%                                                                      |

| Figure 5.9: The measured $(\sigma/\mu)_{36}$ is larger for RO monitors with a smaller gate area. Additional                    |

| hammerheads have negligible impact on $(\sigma/\mu)_{36}$                                                                      |

| Figure 5.10: The measured RO frequency for CS40 and FS40 across 17 chips compared with the                                     |

| simulated RO frequency reveals that the change in RO frequency between layouts is due to                                       |

| mainly parasitic effects from the gate                                                                                         |

| Figure 5.11: The measured RO frequency for IW60 and FW60 across the 17 chips compared                                          |

| with the simulated RO frequency shows that the change in RO frequency between layouts is due                                   |

| to parasitic effects                                                                                                           |

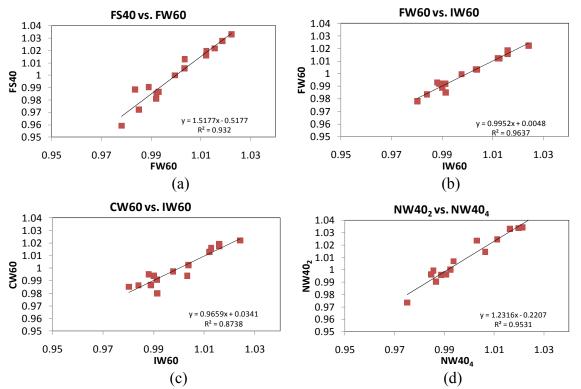

| Figure 5.12: Correlation plots for FS40 versus FW60 (a), FW60 versus IW60 (b), CW60 versus                                     |

| IW60 (c), and NW40 <sub>2</sub> versus NW40 <sub>4</sub> (d) are presented                                                     |

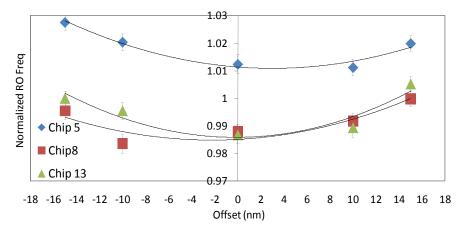

| Figure 5.13: These H-Shaped misalignment RO monitor measurement results for chips 5, 8 and                                     |

| 13, show a 1.5% change in RO frequency                                                                                         |

| Figure 5.14: The deduced overlay error is 2-4nm across the wafer                                                               |

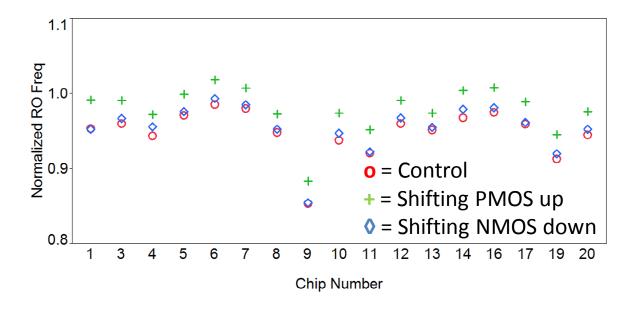

| Figure 6.1: The mean measured RO frequency versus LOD' for 17 chips (excluding                                |

|---------------------------------------------------------------------------------------------------------------|

| asymmetrical monitors)                                                                                        |

| Figure 6.2: The measured $(\sigma/\mu)_{36}$ for NW40 $_{(1,2,3,4,6,7)}$ is 0.2%, excluding the outlier chips |

| Figure 6.3: The mean measured RO frequency of 15 typical chips versus LODs (excluding                         |

| outlier Chips 4 and 9)75                                                                                      |

| Figure 6.4: For the same LOD', asymmetrical monitors with greater sources operate 3% faster                   |

| than monitors with bigger drains                                                                              |

| Figure 6.5: For the same LODs, asymmetrical and symmetrical monitors show minor differences                   |

| in measured RO frequency, indicating that the impact of the drain on device performance is                    |

| small                                                                                                         |

# **Table of Tables**

### Chapter 2

| Table 2.1: Across-chip and within-chip variation for 90nm and 45nm ST Technology [1]        | 4      |

|---------------------------------------------------------------------------------------------|--------|

| Table 2.2: The layout-induced variation reported for 90nm and 45nm technology nodes [1]     | 6      |

| Table 2.3: Design-parameter variation is caused by process-induced or layout-dependent effe | ect. 7 |

| Table 2.4: Relevant layout-induced variations                                               | 8      |

| Table 2.5: A summary of the CAD tools used in this work                                     | 14     |

| Table 2.6: A summary of $\Delta L_{effective}$ for gate lithography monitors                | 22     |

## Chapter 3

| Table 3.1: Nomenclature used for RO monitors                                    |            |

|---------------------------------------------------------------------------------|------------|

| Table 3.2: The block map for the RO monitors—RO monitors in (*) have additional | capacitors |

| inserted between each inverter stage                                            |            |

## Chapter 5

| Table 5.1: A comparison of etch monitors for two technology nodes                     | 62 |

|---------------------------------------------------------------------------------------|----|

| Table 5.2: The comparison of simulated and measured across-wafer variation shows good |    |

| agreement                                                                             | 62 |

| Table 5.3: A comparison of simulated versus measured across-wafer variation           | 67 |

## Chapter 6

| Table 6.1: The normalized layout dimensions for nitride CESL-induced strain RO monitors | 72 |

|-----------------------------------------------------------------------------------------|----|

| Table 6.2: A comparison of RO monitors repeated at the 45nm processes for two tapeouts  | 74 |

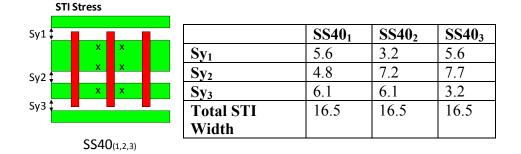

| Table 6.3: The normalized layout dimensions for STI-induced stress monitors             | 78 |

| Table 7.1: A comparison of block-based mean for focus, etch, and stress monitors and their |      |

|--------------------------------------------------------------------------------------------|------|

| respective control ROs for chips 4 and 9.                                                  | . 85 |

| Table 7.2: Chip 9's measurement conditions and its corresponding sensitivity to process    |      |

| parameters for RO monitor CW40                                                             | . 89 |

| Table 7.3: Chip 9's measurement conditions and its corresponding sensitivity to process    |      |

| parameters for RO monitor CW60                                                             | . 90 |

### Chapter 8

Table 8.1: A summary of RO frequency sensitivity for parameter-specific monitors...... 100

# Chapter 1 Introduction

### **1.1 Motivation**

For the past 30 years in the semiconductor industry, advances in CMOS technology have been occurring at an exponential rate, with density doubling as cost per function has been decreasing by approximately 50% every two years. However, variation in electrical performance relative to mean frequency has been increasing with the introduction of smaller feature sizes. For example, the measured 3-standard-deviation-to-mean-ratio has doubled from 90nm to 45nm technology [1]. The introduction of advanced techniques like stress-enhancements, and advanced process treatments, such as laser-assisted annealing, has resulted in the increasing importance of layout-induced variability [2] [3]. Thus, variability has become a challenge to further CMOS scaling and to maintaining high yield.

Monitoring and characterizing variability can have an important practical impact. Circuit designers are concerned about their most vulnerable circuits and the sources that are contributing to their loss of operating margins. A good example is the Static Random Access Memory (SRAM) and the asymmetries observed in the write margins. Understanding the causes of performance variation would allow circuit designers to implement circuit solutions to reduce systematic variation in their designs. Currently, process-induced circuit performance variation is controlled by ensuring that designs obey design rule checks in layout and satisfy process corner models in simulations. In typical design methodologies, obeying these two check points results in a working chip. However, the process corner approach incorporates all manner of variation, including that of across chip, which may be overly pessimistic.

The impact of variability on circuit performance needs to be quantitatively monitored, measured, and characterized in order to reduce its magnitude and negative effect on yield. Since they reflect circuit performance variation caused by systematic and random physical effects, ring oscillators are good monitors of variability [4]. Ring oscillators enable real-time on-chip monitoring with only a few contact pads and are small in terms of area, simple to design, and easy to implement. When used in conjunction with on-chip scan-chains and multiplexers, ring oscillator frequency can be measured easily, rapidly and accurately.

A natural generalization of the ring oscillator automated measurement approach is that of introducing layout modifications of the inverter gates that enhance the sensitivity of the electrical performance to particular process parameters. A suitable starting point for this enhancement is to use the physical understanding of fabrication processes to induce systematic levels of a given process effect through layout design. The understanding of physical effects must be moved up from the wafer to the layout level, where various layout choices can be made to increase sensitivity to a given process parameter while attempting to reduce the response to other parameters. The choice of layout changes can be guided by computer-aided-design (CAD) simulation tools. This strategy has been used to design individual NMOS devices as process defocus monitors [5]. An electronic circuit in the form of ring oscillators designed with this methodology that can be automatically measured is introduced in this thesis and termed "Parameter-Specific Ring Oscillators".

This work is a synergy of device/process, circuits, and computer-aided-design (CAD). Device/process physics and CAD tool simulation are used to design and tune the layouts to be sensitive to a specific process parameter. These layout monitors are then implemented into a 13-stage ring oscillator circuit platform designed by Pang to enable automatic electronic characterization to take place [1]. These designs are taped out through the Berkeley Wireless Research Center (BWRC) and are fabricated at ST Micro. Measured RO frequencies show promising sensitivity to process parameters, correlation with SRAM read-write performance asymmetries and new device models (including stress effects) developed by Xu [6][7].

More specifically, this dissertation explores the feasibility of electronically diagnosing process-induced circuit performance variation that is caused by five physical causes: lithography focus, lithography gate-to-active overlay, gate etch, nitride CESL-induced stress, and STI-induced stress. A set of 32 different layout monitors were designed using ST Micro's 45nm Process Design Kit (PDK) and process simulations using Mentor Graphics Calibre. The layout dimensional changes induced by variation in process conditions are extracted using the process simulator. These extracted changes then serve as inputs into the SPICE simulators in order to predict ring oscillator frequency sensitivity for specific process parameters.

A 45nm test chip was designed and fabricated in collaboration with ST Micro to characterize and quantify the effectiveness of parameter-specific ring oscillator layout monitors. The 36 ring oscillator instantiations were made on a small  $2x2 \text{ mm}^2$  chip in 3 blocks of 12 replications for each of the 32 layout monitor designs. Ring oscillator frequencies for 17 different chips on one wafer were electronically measured and interpreted for parameter specificity. These measurements are used to identify the sources of circuit performance variation as well as to quantify systematic, residual random, within-chip, and across-chip variation.

#### **1.2 Dissertation Content and Contributions**

Chapter 2 details the literature and work most relevant to this dissertational research. It begins by describing components of variability and their impact on circuit performance. It explains the sources of systematic variation in manufacturing processes and layout dependencies. It also discusses why Ring Oscillators (RO) are good process-variation monitors and why fast-CAD tools like Pattern Matching are needed to facilitate the design of parameter-specific inverter layout for ring oscillators. Lastly, this chapter reports on lithography focus layout monitors designed for CDSEM and electric-probe monitoring.

Chapter 3 investigates the challenge of how off-axis illumination likely influences pattern-dependent effects. An extension to Pattern Matching for inclusion of off-axis illumination is developed and applied to the design of defocus inverter layout monitors for ring oscillators. Here defocus sensitivities are confirmed with the aid of Mentor Graphics Calibre process variation (PV) band simulation. This chapter also explores the design challenge of obtaining a 2-4 times focus sensitivity as compared to control-case ROs within design rule checks (DRC). Through an iterative design cycle of DRC, Pattern Matching, and Calibre simulation, RO monitors with 1.5x gate lithography focus sensitivity improvement compared to the control are achieved.

Chapter 4 is devoted to the study of measured noise in ring oscillator frequency caused by the automated testing methodologies and variation due to systematic across-wafer and random within-chip sources for control-case RO monitors. This chapter justifies expedient data analysis assumptions that will be utilized in later chapters. One main challenge delved into in this chapter is that of determining the source of random within-chip variation. Analysis shows that, since measured noised correlates with the inverse of square root of the channel area, within-chip variation is likely due to electrical fluctuations in the devices themselves. Measured RO frequency standard deviation to mean ratio is converted to a Pelgrom plot that shows an average threshold slope (AVT) of 2.3, with respect to the inverse square root of the channel area.

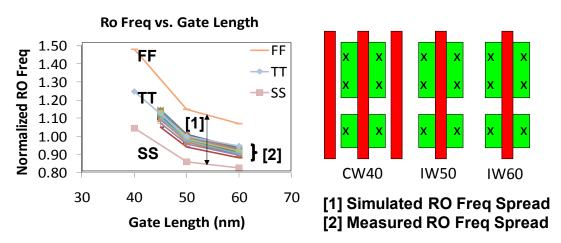

Chapter 5 reports on and analyzes the measured RO frequency sensitivity to gate etch, gate lithography focus, and gate-to-active misalignment. The main challenge here is that of determining the sources of discrepancies between simulations and measured RO frequency sensitivity. For such detective work to occur, various methodologies are used, such as comparing measured RO frequency sensitivity to process corner simulations, comparing the process variation (PV) bands generated by the generic lithography models to those provided by ST Micro, and comparing the measured results with SPICE-simulated RO frequency sensitivities mapped from PV bands. Measured RO frequency sensitivity shows a decrease in gate and active focus effects when compared to that of the generic simulations. This is in part attributed to the fact that the wafer appears to have been run under unusually good control. The measured range of RO frequency is typically centered and 1/6-1/4<sup>th</sup> of that of the SPICE-simulated Slow Slow-Fast Fast (SS-FF) guard band.

Chapter 6 describes the measured ring oscillator sensitivity to Nitride CESL-strain and STI-stress induced variation, including the effect of asymmetrical source/drain active areas. One of the main challenges in determining the impact of stress/strain on RO performance lies in isolating the stress-induced effects from that of the parasitic effects. Measured RO frequencies are thus normalized with that simulated from SPICE using the 45nm PDK provided by ST Micro to extract the parasitic effects. Normalized measured RO frequencies show that a 13.9% increase in RO frequency can be achieved with long source/drain active area as compared to that of the minimum area. RO monitors with larger sources than drains operate 3% faster than the RO with larger drains than sources. This observation indicates that the impact of injection velocity is present in 45nm devices. Measured and simulated RO frequency sensitivities are compared, in which the simulated sensitivities are predicted using a new RO delay model developed by Xu with the inclusion of stress, mobility, and injection velocity effects [7].

While the previous two chapters report on and analyze measured RO frequency sensitivity, Chapter 7 shows the challenge of isolating process parameters that cause random residual effects. Thus, the main contribution of this chapter is the application of the least mean square (LMS) approach to isolate these sources. This methodology assumes that the main sources of variation are likely attributed to changes in 3 parameters: gate length, gate oxide thickness, and doping. Since ring oscillators are expected to show different sensitivity under varying operating conditions, in order to improve the accuracy of this approach, RO monitors are measured under 5 combinations of varying temperatures and operating voltages. Using SPICE simulations, the methodology first linearizes RO frequency with respect to a process parameter. Then, using LMS, the measured RO frequency is related to these parameters, and the relative contribution of each parameter is determined.

Chapter 8 summarizes the contributions of this dissertation and offers perspectives in regard to the future work. A consolidated overall summary of simulated and measured parameter-specificities is presented.

# Chapter 2 Characterizing Variability

Characterizing the impact of variability is quite important in guaranteeing working chip designs. This literature review identifies the current circuit performance issues, describes the techniques for quantifying measured variability, and gives an overview of process-aware computer-aided-design (CAD) simulation tools. This chapter is organized into 6 sections. Section 2.1 describes the components of variability and their impact on circuit performance. Section 2.2 reports on the known sources of variability from the perspective of semiconductor manufacturing. Section 2.3 discusses the various techniques available to monitor variability as well as the circuits developed for monitoring variability. Section 2.4 reports on the CAD tools that enable the design of layout monitors to occur, while Section 2.5 gives examples of single transistor NMOS gate lithography focus monitors that are designed using a combination of the CAD tools that are described in Section 2.4. Finally, Section 2.6 summarizes the chapter.

# 2.1 Modeling Within-Chip/Across-Chip, Random/Systematic and Dynamic/Static Variability

Process variability is categorized based on intra-chip (within-chip) and inter-chip (acrosschip) distinctions. These variations are caused by random or systematic physical sources. Circuit performance variability caused by random variation is non-deterministic, and the performance could change rapidly over small distances (i.e. no correlation length). Circuit performance variability caused by systematic variation induces deterministic shifts, which vary gradually over a wafer and even within a chip. Table 2.1 presents an example of quantitative within-chip and across-chip variation (3 standard deviation,  $\sigma$ , to mean,  $\mu$ , ratio) for 90nm and 45nm ST Micro Technology [1].

|                     | 90nm | 45nm |

|---------------------|------|------|

| Across-Chip (3σ/ μ) | 15%  | 15%  |

| Within-Chip (3σ/ μ) | 3.5% | 6.6% |

Table 2.1: Across-chip and within-chip variation for 90nm and 45nm ST Technology [1]

Both within-chip and across-chip variation are spatially correlated, i.e. circuit performance variability is highly dependent on the location of the circuit with respect to the position of the chip or on the wafer. The length of scale for systematic effects is process dependent here. Lithography variation (other than layout dependencies), is about 1mm, while the length of scale for Chemical Mechanical Polishing (CMP) is about 40-100um [8].

Random variation is unpredictable and is attributed to device parameter fluctuation. Atomic-scale variation causes random non-uniformity in gate length (L), gate oxide thickness ( $T_{ox}$ ), and dopant density in the channel region ( $N_{ch}$ ) [9][10][11]. With scaling and, thus, a decrease in channel area, the number of random dopant atoms decreases, exacerbating the random dopant fluctuation (RDF) impact and causing larger variation in the threshold voltage,  $V_{th}$  [10]. The Pelgrom model, which correlates standard deviation in  $V_{th}$  with the inverse square root of the gate area, is commonly used to characterize random variation [12].

Figure 2.1: The transistor cross-section and sources of random variability

Much of systematic variability is predictable and is attributed to non-uniformity in the following manufacturing steps: lithography/etch, deposition/oxide growth, chemical-mechanical polishing (CMP), and rapid thermal annealing [3]. The evidence of systematic variability is shown in Figure 2.2 by plotting the measured RO frequency versus the position on the wafer for a 45nm technology node [13]. Recently, layout dependent variation from stress-enhancement process technology, such as tensile or compressive Contact Etch Stop Liner (CESL) and Shallow Trench Isolation (STI) have become dominant sources of systematic variations [1].

Figure 2.2: A RO frequency measurement fitted across a wafer shows systematic parabolic behavior [13].

While systematic variation is generally predictable, it is usually unknown at design time or is too complex to be included in circuit simulations in current design methodologies. Thus, current designs are typically created to satisfy worst-case corners, consisting of the total within and across-chip variation. Process-corner design methodology is often too pessimistic and does not correlate well with layout-induced systematic effects. Figure 2.3 illustrates the problematic points associated with the current design methodology.

Figure 2.3: The typical process-corner design methodology is not well-correlated with layout-induced systematic variation [1].

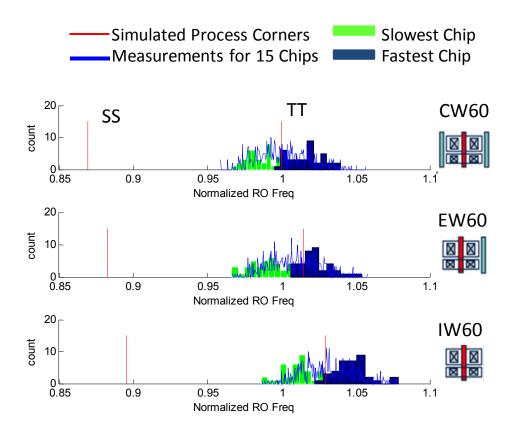

Figure 2.3 reports the results from the 90nm testchip for RO monitors: Tiles 3a, 4a, and 5a [1]. Tile 3a has two dummy polys, while Tiles 4a and 5a have one dummy poly. The SS-TT-FF corner model is rather conservative in suggesting a spread that is twice that of the across wafer measurement. In addition, this model fails to capture the layout-dependent effects. Compared to the measured RO frequency distribution for Tile 3a, as the 10% RO frequency increase is the same for the asymmetric monitor Tiles 4a and 5a, it is unlikely that this result is due to an imaging effect, such as coma. Process variation band simulations of the gate that was imaged through focus shows a change of 4%. This observation is much smaller than the measured 10% shift, indicating that this increase is unlikely to be due to a lithography error (Chapter 3).The measured across-chip RO frequency  $3(\sigma/\mu)$  spread is ~20% and is 5x wider than the fastest/slowest chip. Such a result shows that across-wafer systematic effects dominate over within-chip random distribution.

In addition to the measured RO frequency sensitivities to the three monitors, which is described in Figure 2.3, the systematic results from the screening of the Ring Oscillator (RO) layout monitors developed by Pang for 90nm and 45nm ST Micro Technology are summarized in Table 2.2 [1]. At 90nm, the main source of variation is attributed to etch/lithography, while at 45 nm the dominant source of variation is attributed to a nitride CESL-induced strain.

| Layout               | 90nm                   | 45nm                     |

|----------------------|------------------------|--------------------------|

| Source /Drain Stress | N/A                    | $\Delta f_{RO} \sim 5\%$ |

| STI                  | N/A                    | $\Delta f_{RO} \sim 3\%$ |

| Etch/Lithography     | $\Delta f_{RO} > 10\%$ | $\Delta f_{RO} \sim 2\%$ |

Table 2.2: The layout-induced variation reported for 90nm and 45nm technology nodes [1]

Variability can also be categorized as being dynamic or static. Dynamic variation is timevarying and changes with respect to the utilized operating conditions. Sources that contribute to dynamic variation include: Random Telegraph Signals (Figure 2.4), Negative Bias Temperature Instability (NBTI) [16], temperature, a voltage drop across the wire resistance, or capacitive coupling. Static variation is independent of the time and operating conditions. Static process variation is studied in this research.

Figure 2.4: Random telegraph signals (RTS), a dynamic source of variability, cause the threshold voltage,  $V_{th}$ , to vary with time [14][15].

### 2.2 Sources of Process and Layout-Induced Variation

Circuit design parameters are affected by sources of variation from the manufacturing steps and layout geometries. The design parameters reported in this work are: gate length (L), gate oxide thickness ( $T_{ox}$ ), threshold voltage ( $V_{th}$ ), and mobility/injection velocity ( $\mu$ /  $v_T$ ). Table 2.3 summarizes the systematic sources that induce design parameter variability.

| Circuit Design Parameter                         | Sources of Variability from          |

|--------------------------------------------------|--------------------------------------|

|                                                  | Manufacturing                        |

| Gate length (L) and Gate width (W)               | Lithography, etch, layout-           |

|                                                  | dependent proximity effects,         |

|                                                  | overlay error                        |

| Gate Oxide Thickness (Tox)                       | Oxide growth non-uniformity          |

| Threshold Voltage (V <sub>th</sub> )             | Non-uniformity in anneal             |

|                                                  | temperature, channel area variations |

| Mobility/injection velocity (μ/ ν <sub>T</sub> ) | Layout dependency in the             |

|                                                  | source/drain area, non-uniformity in |

|                                                  | strain/stress distribution from      |

|                                                  | source/drain asymmetries             |

Table 2.3: Design-parameter variation is caused by process-induced or layout-dependent effect

The main sources of process variation that are relevant to this work are described in the following sections. Section 2.2.1 discusses the possible variability sources in lithography, in particular exposure dose, focus, and misalignment. Section 2.2.2 discusses the sources of variability that are induced by other manufacturing steps, such as chemical mechanical polishing, stress engineering, and etch. A summary of the relevant process variation is described in Table 2.4.

| <b>Process Variations</b> | Description                                                         |

|---------------------------|---------------------------------------------------------------------|

| T ( )                     |                                                                     |

| Etch                      | Etch effects refer to the dependence of gate length on etch         |

|                           | loading.                                                            |

| Focus                     | Focus effects refer to the dependence of gate length on lens-       |

|                           | wafer distances.                                                    |

| Misalignment              | Misalignment effects refer to the dependence of gate length and     |

| _                         | gate width due to a gate-to-active overlay error.                   |

| Stress/Strain             | In 45nm, due to non-uniform stress in the silicon substrate, the    |

|                           | use of strained-silicon technology introduces mobility and          |

|                           | injection velocity variation. The stress that is induced is layout- |

|                           | dependent here. Sources of stress include: shallow trench           |

|                           | isolation and a strained capping layer.                             |

Table 2.4: Relevant layout-induced variations

#### 2.2.1 Variations in the Lithography Exposure System

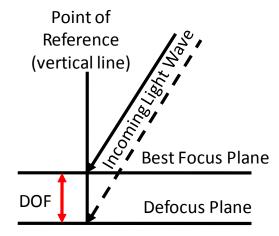

The two key requirements for lithography in manufacturing integrated circuits are critical dimension (CD) and overlay control [17]. Many different feature sizes in layout designs must remain precise within each field, across a wafer, and from wafer to wafer. Maintaining CD and overlay control are quite important to the overall transistor performance. Variability in CD is caused by two main physical sources: (1) the depth of focus (DOF) and (2) the exposure dose. Variability in misalignment is due to the error of aligning a reticle to the features on the wafer during lithography exposure steps.

A typical lithographic imaging system (Figure 2.5) is governed by two fundamental quantities: the resolution and the depth of focus (DOF).

Figure 2.5: A typical lithography imaging system [18]

The smallest resolution achieved, or the smallest printable critical dimension, is defined by the Raleigh criterion and the resist process:

$$CD = k_{\perp} \frac{\lambda}{NA} \tag{2.1}$$

where  $\lambda$  is the wavelength, *NA* is the numerical aperture of the lens, and  $k_1$  is the "k-factor" for a given process. The k-factor changes if a different photoresist process is being used.

The DOF is a range of lens-wafer distances over which the CDs and resist profiles are maintained within specifications.

Figure 2.6: The DOF concept is a range of lens-wafer distances such that the respective CDs are maintained within specifications.

A rigorous derivation of the DOF is defined as:

$$DOF = \frac{1\lambda}{4n} \frac{1}{1 - \sqrt{1 - \left(\frac{NA^2}{n}\right)}}$$

(2.2)

where  $\lambda$  is the wavelength, *n* is the refractive index, and *NA* is the numerical aperture of the lens. If NA << 1, then DOF is approximated as:

$$DOF = \pm 0.5 \frac{\lambda}{NA^2}$$

(2.3)

Currently, lithography stepper systems use a step-and-scan technique: the mask (reticle) and the wafer are simultaneously moved in opposite directions such that a slit of the light scans the entire mask and projects the image onto the wafer [8]. Maintaining the wafer stage, in order that the lens-wafer distance is uniform throughout the step-and-scan procedure, is extremely difficult. Furthermore, in printing smaller feature sizes thus improving the resolution (refer to equation (2.1)), NA is increased in order to capture higher orders of light waves, subsequently decreasing the DOF (refer to equation (2.3)). Thus, the problem of defocus non-uniformity is

particularly difficult in optical lithography, where the DOF has become so small that there is a concern about whether optical steppers are capable of maintaining the image in focus.

In addition to concerns about the DOF control, the lithography system must provide uniform exposure dose illumination to maintain CD control across the exposure field (Figure 2.7) [19][20].

Figure 2.7: Bossung plot shows that DOF and exposure dose control are quite important in maintaining a uniform CD [20].

A uniform dose on the wafer is maintained by controlling the wafer stage scanning speed and the intensity of the laser source. The exposure dose for a given slit width,  $W_s$ , is expressed as:

$$W_s = V_{en} \frac{n}{f} \tag{2.4}$$

where  $V_m$  is the maximum wafer stage scan speed, *n* is the number of pulses required to achieve the specified dose, and *f* is the laser source repetition rate. The exposure dose variation range is typically 1-2% [8].

Alignment of the reticle to the wafer is also an important source of variability. Integrated circuits are manufactured through a series of patterning steps. Each new layer must be placed on top of the preceding layers, and proper alignment of the new layer to the previous circuit pattern, already imaged on the wafer, is essential for correct electrical contact to occur. This alignment error, commonly referred to as an overlay error, must be kept within certain tolerances. Current state-of-the art ArF lithography scanners can maintain overlay errors of 3-4 nm [21].

Other sources of variation in the lithography patterning steps include post-exposure bake (PEB), which causes systematic across-chip variation [22]. The resist here is first spun onto the wafer, exposed, and then baked. After it is exposed through the reticle, a PEB is used to drive additional chemical reactions or the diffusion of components within the resist film. If the temperature is uneven, this non-uniformity will result in critical dimension (CD) variation. This effect is manifested in a parabolic profile across wafers.

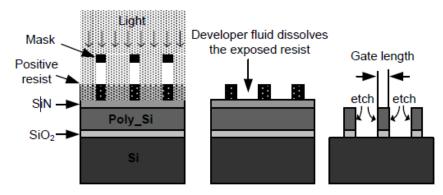

#### **2.2.2Variation in Patterning and Other Manufacturing Steps**

Other patterning and manufacturing steps are important sources of process-induced variation. This section lists and discusses such sources and their potential impact on transistor performance, organized by their respective magnitude of radius of influence.

- Chemical Mechanical Polishing (CMP) causes a difficult challenge for maintaining overlay-error control. The purpose of CMP is to produce planarized surfaces. CMP is helpful to lithography because CMP reduces thin-film effects; however, CMP makes overlay control difficult because it reduces the contrast of alignment targets [8].

- Dry etching is an important step in the patterning of the poly-silicon gates. This process suffers from microscopic loading effects in which densely-spaced gates experience a lower etch rate than isolated ones. This difference causes dense gates to have larger CDs than those of isolated ones.

Figure 2.8: The fabrication steps of poly-silicon gates show that CDs suffer from etch loading effects [1]

• Applying mechanical stress to transistors improves their carrier mobilities. NMOS and PMOS devices respond differently to tensile and compressive stress, depending on the transistor type [23]. To apply mechanical stress to NMOS devices, a nitride contact etch stop liner (CESL) is deposited using Chemical Vapor Deposition (CVD). This capping layer has tensile strain. The discontinuity of the film at the edge of the MOSFET gate/spacer impacts the stress/strain in the channel. Figure 2.9 shows the mechanical stress distribution beneath the channel area. While the additional capping layer enhances NMOS performance, it also increases layout-induced variability due to different diffusion areas.

Figure 2.9: The distribution of mechanical stress beneath the gate that is induced by the contact etch stop liner, which is also commonly referred to as the capping layer [23].

#### 2.3 Process Characterization Methodologies

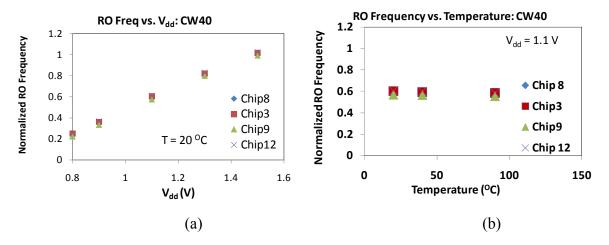

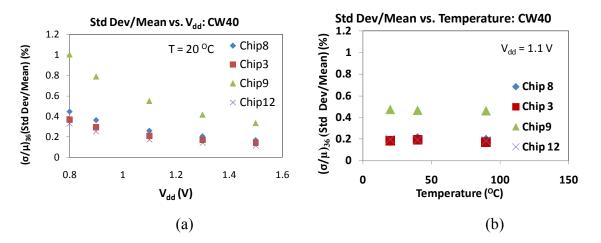

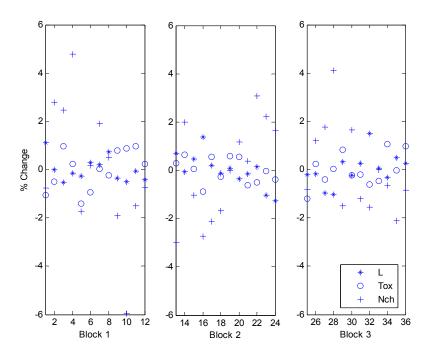

In order to monitor process-induced variation, a variety of process characterization techniques can be employed, such as: optical scatterometry, scanning electron microscopy (SEM), electrical linewidth measurements (ELM), and automated electronic testing. These process characterization methods are used for process control as well as to evaluate process corners.