# Intrinsic and Systematic Variability in Nanometer CMOS Technologies

Kedar Patel

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2010-181 http://www.eecs.berkeley.edu/Pubs/TechRpts/2010/EECS-2010-181.html

December 31, 2010

Copyright © 2010, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Intrinsic and Systematic Variability in Nanometer CMOS Technologies

by

#### Kedar Kantilal Patel

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Costas Spanos, Chair Professor Tsu-Jae King Liu Professor Sandrine Dudoit

Fall 2010

#### Intrinsic and Systematic Variability in Nanometer CMOS Technologies

Copyright © 2010 by Kedar Kantilal Patel

#### Abstract

Intrinsic and Systematic Variability in Nanometer CMOS Technologies

by

#### Kedar Kantilal Patel

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Costas Spanos, Chair

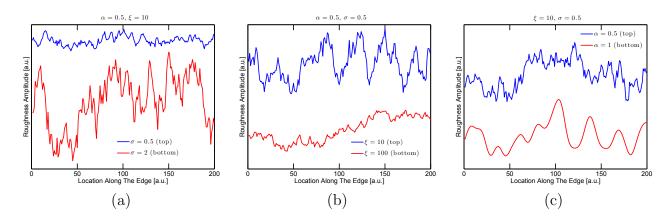

It has been widely recognized that variability is one the most important challenges to scaling of nanoscale CMOS devices. Intrinsic sources of variation such as discretization effect of dopant atoms, metal-gate work-function variation, and line width roughness threaten an end to scaling realized in the past decades. Line width roughness (LWR) is of great importance as it is a significant fraction of the minimum feature size for nanoscale devices, and it does not scale at the same pace as the minimum feature size. According to previous studies, a complete description of LWR can be provided by three parameters: root-mean square (RMS) roughness  $(\sigma)$ , correlation length  $(\xi)$ , and roughness exponent  $(\alpha)$ .

A robust method of estimating line width roughness parameters is presented. Specifically, the proposed method provides a better unbiased estimate of roughness amplitude  $\sigma$  than existing methods. It also provides an estimate of error in LWR parameters. The proposed method also allows for more flexibility in capturing SEM images in that we do not need a special test structure with all lines with same designed CD; any IC layout region with straight lines and arbitrary CDs would suffice. As an application of this method, LWR characteristics of many next-generation lithography processes are explored. LWR parameters are also incorporated in the FinFET device framework, and useful physical insights are provided in regards to its impact on device performance.

Variability can also be systematic in nature. Systematic spatial variation can occur at the wafer- or die-level. Accurate estimation of various variability components is necessary for robust circuit design. To this end, a hierarchical decomposition of semiconductor process variation is performed. A holistic discussion on all components of process variation is provided. Specifically, global (inter-die) variation is modeled in a multivariate normal framework. The same framework is extended to enable wafer-selection for model estimation. Least angle regression and agglomerative hierarchical clustering are proposed for selecting wafers for model estimation. Methodologies to model systematic local (intra-die) variation and spatial correlation are provided. Spatial correlation in intra-die observations is extracted using the variogram, and issues in variogram estimation are discussed in detail.

To my beloved wife, Neha and  ${\rm my \ twin \ bundles \ of \ joy, \ Arav \ and \ Anika}$

## Contents

| Li | st of | Figure  | es e | $\mathbf{v}$ |

|----|-------|---------|------------------------------------------|--------------|

| Li | st of | Tables  |                                          | vii          |

| 1  | Intr  | oductio | on                                       | 1            |

|    | 1.1   | Semico  | onductor Technology                      | 1            |

|    | 1.2   |         | s Variability                            |              |

|    | 1.3   | Role of | f Modeling                               | 3            |

|    | 1.4   | Modeli  | ing Challenges                           | 7            |

|    | 1.5   |         | erview of This Work                      |              |

| 2  | Rob   | ust Es  | timation of LWR Parameters               | 10           |

|    | 2.1   | Introdu | $\operatorname{uction}$                  | 10           |

|    |       | 2.1.1   | Motivation and Background                | 10           |

|    |       | 2.1.2   | Our Work                                 | 12           |

|    | 2.2   | Line V  | Width Roughness Model                    | 13           |

|    |       |         | LWR Parameters                           |              |

|    |       | 2.2.2   | A Variogram Model                        | 14           |

|    | 2.3   | Estim   | ation of Model Parameters                | 16           |

|    |       | 2.3.1   | Estimation of $\xi$ and $\alpha$         | 16           |

|    |       | 2.3.2   | Estimation of $\sigma^2$                 | 19           |

|    | 2.4   | Robus   | st Estimation of LWR Parameters          | 20           |

|    |       | 2.4.1   | Procedure                                | 21           |

|    |       | 2.4.2   | Optimal Block Length                     | 25           |

|    | 2.5   | Result  | ts and Discussion                        | 26           |

|    |       | 2.5.1   | Simulated Data                           | 26           |

|    |       | 2.5.2   | Validation Using Simulated Data          | 26           |

|    |       | 2.5.3   | Experimental Data                        | 30           |

|    | 2.6   | Summe   | arv                                      | 31           |

| 3.2 Estimation of LWR Parameters       3.2.1 SEM Image Acquisition and Processing       3.3.2.2 Estimation Procedure       3.3.3.2.2 Estimation Procedure       3.3.3.3.3.3.3.3.3.3.3.3.1. Double Patterning Lithography (DPL)       3.3.1 Double Patterning Lithography (DPL)       3.3.2 Self-Aligned Double Patterning Lithography (SADP)       3.3.3.2. Self-Aligned Double Patterning Lithography (SADP)       3.3.3.3.3.2. Self-Aligned Double Patterning Lithography (DSA)       3.3.3.3.3.3.3.3.3.3.5. Nano-imprint Lithography (NIL)       3.3.3.5. Nano-imprint Lithography (NIL)       3.3.3.5. Nano-imprint Lithography (NIL)       3.3.3.5. Summary       4.4. Results and Discussion       3.3.5. Summary       4.4. Introduction       4.4. Introduction       4.4. Line Edge Roughness       4.4. 2.1. Background       4.4. 2.2. Spacer vs. Resist Lithography       4.4. 3.3. Simulation Details and Model Formulation       4.4. 3.3. FinFET Structure       4.4. 3.3. Simulation Details       4.3.3. Model Formulation       4.4. Results and Discussion       5.5. Summary       5.5. Summary       6.5. Summary       6.5. Summary       6.5. Summary       6.5. Summary       6.5. Summary       6.6. Summary | 3 | LW  | R in Next-Generation Lithography Processes              | 32 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---------------------------------------------------------|----|

| 3.2.1       SEM Image Acquisition and Processing       3.         3.2.2       Estimation Procedure       3.         3.3       Next-Generation Lithography (NGL) Processes       3.         3.3.1       Double Patterning Lithography (DPL)       3.         3.3.2       Self-Aligned Double Patterning Lithography (SADP)       3.         3.3.3       Extreme Ultraviolet Lithography (EUV)       3.         3.3.4       Directed Self-Assembly Lithography (DSA)       3.         3.3.5       Nano-imprint Lithography (NIL)       3.         3.4       Results and Discussion       3.         3.5       Summary       4.         4       Gate LER Model for FinFET Performance       4.         4.1       Introduction       4.         4.2       Line Edge Roughness       4.         4.2.1       Background       4.         4.2.2       Spacer vs. Resist Lithography       4.         4.3       Simulation Details and Model Formulation       4.         4.3.1       FinFET Structure       4.         4.3.2       Simulation Details       5.         4.3.3       Model Formulation       5.         5.4       Results and Discussion       5.         4.5                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 3.1 | Introduction                                            | 32 |

| 3.2.2 Estimation Procedure       3.         3.3 Next-Generation Lithography (NGL) Processes       3.         3.3.1 Double Patterning Lithography (DPL)       3.         3.3.2 Self-Aligned Double Patterning Lithography (SADP)       3.         3.3.3 Extreme Ultraviolet Lithography (EUV)       3         3.3.4 Directed Self-Assembly Lithography (DSA)       3.         3.3.5 Nano-imprint Lithography (NIL)       3         3.4 Results and Discussion       3         3.5 Summary       4         4 Gate LER Model for FinFET Performance       4         4.1 Introduction       4         4.2 Line Edge Roughness       4         4.2.1 Background       4         4.2.2 Spacer vs. Resist Lithography       4         4.3 Simulation Details and Model Formulation       4         4.3.1 FinFET Structure       4         4.3.2 Simulation Details       5         4.3.3 Model Formulation       5         4.4 Results and Discussion       5         4.5 Summary       6         5 Decomposition of Semiconductor Process Variation       6         5.1 Introduction       6         5.2 Semiconductor Process Variation       6         5.4 Decomposition of Process Variation       7         5.4.1 Nomencl                                                                                                                                                                                                                                                                                                                                                                                        |   | 3.2 | Estimation of LWR Parameters                            | 33 |

| 3.3       Next-Generation Lithography (NGL) Processes       3.3.1       Double Patterning Lithography (PDL)       33         3.3.2       Self-Aligned Double Patterning Lithography (SADP)       33         3.3.3       Extreme Ultraviolet Lithography (EUV)       3         3.3.4       Directed Self-Assembly Lithography (DSA)       3         3.3.5       Nano-imprint Lithography (NIL)       3         3.4       Results and Discussion       3         3.5       Summary       4         4       Cate LER Model for FinFET Performance       44         4.1       Introduction       4         4.2       Line Edge Roughness       4         4.2.1       Background       4         4.2.2       Spacer vs. Resist Lithography       4         4.3       Simulation Details and Model Formulation       4         4.3.1       FinFET Structure       4         4.3.2       Simulation Details       5         4.3.3       Model Formulation       5         4.4       Results and Discussion       5         4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       6         5.1       Introduction       6                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     | 3.2.1 SEM Image Acquisition and Processing              | 33 |

| 3.3.1       Double Patterning Lithography (DPL)       3.3.2       Self-Aligned Double Patterning Lithography (SADP)       3.3.3       3.3.3       Extreme Ultraviolet Lithography (EUV)       3.3.3       3.3.4       Directed Self-Assembly Lithography (DSA)       3.3.5       Nano-imprint Lithography (NIL)       3.3.5       3.3.5       Nano-imprint Lithography (NIL)       3.3.5       3.4       Results and Discussion       3.3.5       Summary       4.4         4       Gate LER Model for FinFET Performance       4.4       4.1       Introduction       4.4       4.2.1       Background       4.2.1       Background       4.2.1       Background       4.2.1       Background       4.3.3       Simulation Details and Model Formulation       4.3.3       Simulation Details and Model Formulation       4.3.1       FinFET Structure       4.4       4.3.2       Simulation Details       5.5       Summary       6         5       Decomposition of Semiconductor Process Variation       5.6       5.5         5.1       Introduction       6.6       5.5         5.2       Semiconductor Process Variation       6         5.3       Spatial Correlation       6         5.4       Decomposition of Process Variation       7         5.4.1       Nomenclature       7         5.4.2       Mo                                                                                                                                                                                                                                                                                            |   |     | 3.2.2 Estimation Procedure                              | 34 |

| 3.3.2       Self-Aligned Double Patterning Lithography (SADP)       3.3.3       Extreme Ultraviolet Lithography (EUV)       3.3.4       Directed Self-Assembly Lithography (DSA)       3.3.5       Nano-imprint Lithography (NIL)       33.3.5       Nano-imprint Lithography (NIL)       33.3.5       Nano-imprint Lithography (NIL)       33.3.5       Summary       44.4         4 Gate LER Model for FinFET Performance       44.1       Introduction       44.4       42.1       Introduction       44.4       42.1       Background       44.4       42.2       Spacer vs. Resist Lithography       44.4       43.3       Simulation Details and Model Formulation       44.4       43.1       FinFET Structure       44.4       43.2       Simulation Details       45.4       43.3       Model Formulation       55.4       43.3       Model Formulation       55.4       43.3       Model Formulation       56.5       55.2       Summary       66       55.3       Spatial Correlation       56.5       56.4       Results and Discussion       66.5       55.3       Spatial Correlation       66.5       55.4       Nomenclature       70.5       54.1       Nomenclature       70.5       54.2       Modeling Choices       77.5       55.4       Nomenclature       77.5       56.4       Nomenclature       77.5       56.4       Nomenclature       77.5 <td></td> <td>3.3</td> <td>Next-Generation Lithography (NGL) Processes</td> <td>34</td>                                                                                                                                               |   | 3.3 | Next-Generation Lithography (NGL) Processes             | 34 |

| 3.3.3       Extreme Ultraviolet Lithography (EUV)       3         3.3.4       Directed Self-Assembly Lithography (DSA)       3         3.3.5       Nano-imprint Lithography (NIL)       3         3.4       Results and Discussion       3         3.5       Summary       4         4       Gate LER Model for FinFET Performance       4         4.1       Introduction       4         4.2       Line Edge Roughness       4         4.2.1       Background       4         4.2.2       Spacer vs. Resist Lithography       4         4.3       Simulation Details and Model Formulation       4         4.3.1       FinFET Structure       4         4.3.2       Simulation Details       5         4.3.3       Model Formulation       5         4.4       Results and Discussion       5         4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       6         5.1       Introduction       6         5.2       Semiconductor Process Variation       6         5.3       Spatial Correlation       6         5.4       Decomposition of Process Variation       7         5.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |     | 3.3.1 Double Patterning Lithography (DPL)               | 35 |

| 3.3.3       Extreme Ultraviolet Lithography (EUV)       3         3.3.4       Directed Self-Assembly Lithography (DSA)       3         3.3.5       Nano-imprint Lithography (NIL)       3         3.4       Results and Discussion       3         3.5       Summary       4         4       Gate LER Model for FinFET Performance       4         4.1       Introduction       4         4.2       Line Edge Roughness       4         4.2.1       Background       4         4.2.2       Spacer vs. Resist Lithography       4         4.3       Simulation Details and Model Formulation       4         4.3.1       FinFET Structure       4         4.3.2       Simulation Details       5         4.3.3       Model Formulation       5         4.4       Results and Discussion       5         4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       6         5.1       Introduction       6         5.2       Semiconductor Process Variation       6         5.3       Spatial Correlation       6         5.4       Decomposition of Process Variation       7         5.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |     | 3.3.2 Self-Aligned Double Patterning Lithography (SADP) | 36 |

| 3.3.4       Directed Self-Assembly Lithography (DSA)       3         3.3.5       Nano-imprint Lithography (NIL)       3         3.4       Results and Discussion       3         3.5       Summary       4         4       Gate LER Model for FinFET Performance       4         4.1       Introduction       4         4.2       Line Edge Roughness       4         4.2.1       Background       4         4.2.2       Spacer vs. Resist Lithography       4         4.3       Simulation Details and Model Formulation       4         4.3.1       FinFET Structure       4         4.3.2       Simulation Details       5         4.3.3       Model Formulation       5         4.4       Results and Discussion       5         4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       6         5.1       Introduction       6         5.2       Semiconductor Process Variation       6         5.3       Spatial Correlation       6         5.4       Decomposition of Process Variation       7         5.4.1       Nomenclature       7         5.4.2       Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |     |                                                         | 37 |

| 3.3.5       Nano-imprint Lithography (NIL)       33         3.4       Results and Discussion       33         3.5       Summary       44         4       Gate LER Model for FinFET Performance       44         4.1       Introduction       44         4.2       Line Edge Roughness       44         4.2.1       Background       44         4.2.2       Spacer vs. Resist Lithography       4         4.3       Simulation Details and Model Formulation       43.1         4.3.1       FinFET Structure       44         4.3.2       Simulation Details       55         4.3.3       Model Formulation       56         4.4       Results and Discussion       56         4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       66         5.1       Introduction       66         5.2       Semiconductor Process Variation       66         5.3       Spatial Correlation       66         5.4       Decomposition of Process Variation       67         5.4.1       Nomenclature       77         5.4.2       Modeling Choices       77         5.5       Wafer-Level Va                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |     |                                                         | 37 |

| 3.4 Results and Discussion       33         3.5 Summary       4         4 Gate LER Model for FinFET Performance       40         4.1 Introduction       44         4.2 Line Edge Roughness       44         4.2.1 Background       44         4.2.2 Spacer vs. Resist Lithography       45         4.3 Simulation Details and Model Formulation       45         4.3.1 FinFET Structure       44         4.3.2 Simulation Details       55         4.3.3 Model Formulation       55         4.4 Results and Discussion       56         4.5 Summary       66         5 Decomposition of Semiconductor Process Variation       66         5.1 Introduction       66         5.2 Semiconductor Process Variation       66         5.3 Spatial Correlation       66         5.4 Decomposition of Process Variation       76         5.4.1 Nomenclature       76         5.4.2 Modeling Choices       77         5.5 Wafer-Level Variation       77         5.5.1 Multivariate Normal Model       77         5.5.2 Normality Test and Outlier Rejection       78         5.6.2 Cluster Analysis       77         5.7 Die-Level Variation       76                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     |                                                         | 38 |

| 3.5       Summary       4         4 Gate LER Model for FinFET Performance       40         4.1       Introduction       41         4.2       Line Edge Roughness       42         4.2.1       Background       42         4.2.2       Spacer vs. Resist Lithography       43         4.3       Simulation Details and Model Formulation       44         4.3.1       FinFET Structure       42         4.3.2       Simulation Details       55         4.3.3       Model Formulation       56         4.4       Results and Discussion       56         4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       66         5.1       Introduction       66         5.2       Semiconductor Process Variation       66         5.3       Spatial Correlation       66         5.4       Decomposition of Process Variation       70         5.4.1       Nomenclature       70         5.4.2       Modeling Choices       70         5.5       Wafer-Level Variation       70         5.5.1       Multivariate Normal Model       70         5.5.2       Normality Test and Outlier Rejectio                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 3.4 |                                                         | 39 |

| 4 Gate LER Model for FinFET Performance 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 3.5 |                                                         | 4  |

| 4.1 Introduction       44         4.2 Line Edge Roughness       4         4.2.1 Background       4         4.2.2 Spacer vs. Resist Lithography       4         4.3 Simulation Details and Model Formulation       4         4.3.1 FinFET Structure       44         4.3.2 Simulation Details       5         4.3.3 Model Formulation       5         4.4 Results and Discussion       5         4.5 Summary       6         5 Decomposition of Semiconductor Process Variation       6         5.1 Introduction       6         5.2 Semiconductor Process Variation       6         5.3 Spatial Correlation       6         5.4 Decomposition of Process Variation       7         5.4.1 Nomenclature       7         5.4.2 Modeling Choices       7         5.5 Wafer-Level Variation       7         5.5.2 Normality Test and Outlier Rejection       7         5.6.1 Least Angle Regression Using PCA Basis Functions       7         5.6.2 Cluster Analysis       7         5.7 Die-Level Variation       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     |                                                         |    |

| 4.2 Line Edge Roughness       4         4.2.1 Background       4         4.2.2 Spacer vs. Resist Lithography       4         4.3 Simulation Details and Model Formulation       4         4.3.1 FinFET Structure       4         4.3.2 Simulation Details       5         4.3.3 Model Formulation       5         4.4 Results and Discussion       5         4.5 Summary       6         5 Decomposition of Semiconductor Process Variation       6         5.1 Introduction       6         5.2 Semiconductor Process Variation       6         5.3 Spatial Correlation       6         5.4 Decomposition of Process Variation       7         5.4.1 Nomenclature       7         5.4.2 Modeling Choices       7         5.5 Wafer-Level Variation       7         5.5.1 Multivariate Normal Model       7         5.5.2 Normality Test and Outlier Rejection       7         5.6.1 Least Angle Regression Using PCA Basis Functions       7         5.6.2 Cluster Analysis       7         5.7 Die-Level Variation       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4 | Gat | te LER Model for FinFET Performance                     | 46 |

| 4.2.1 Background       4         4.2.2 Spacer vs. Resist Lithography       4         4.3 Simulation Details and Model Formulation       4         4.3.1 FinFET Structure       4         4.3.2 Simulation Details       5         4.3.3 Model Formulation       5         4.4 Results and Discussion       5         4.5 Summary       6         5 Decomposition of Semiconductor Process Variation       6         5.1 Introduction       6         5.2 Semiconductor Process Variation       6         5.3 Spatial Correlation       6         5.4 Decomposition of Process Variation       7         5.4.1 Nomenclature       7         5.4.2 Modeling Choices       7         5.5 Wafer-Level Variation       7         5.5.2 Normality Test and Outlier Rejection       7         5.6 Wafer Selection       7         5.6.1 Least Angle Regression Using PCA Basis Functions       7         5.6.2 Cluster Analysis       7         5.7 Die-Level Variation       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 4.1 | Introduction                                            | 46 |

| 4.2.2       Spacer vs. Resist Lithography       44         4.3       Simulation Details and Model Formulation       44         4.3.1       FinFET Structure       44         4.3.2       Simulation Details       55         4.3.3       Model Formulation       56         4.4       Results and Discussion       56         4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       66         5.1       Introduction       66         5.2       Semiconductor Process Variation       66         5.3       Spatial Correlation       66         5.4       Decomposition of Process Variation       76         5.4.1       Nomenclature       76         5.4.2       Modeling Choices       76         5.5       Wafer-Level Variation       77         5.5.1       Multivariate Normal Model       77         5.5.2       Normality Test and Outlier Rejection       77         5.6       Wafer Selection       78         5.6.2       Cluster Analysis       78         5.7       Die-Level Variation       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 4.2 | Line Edge Roughness                                     |    |

| 4.3       Simulation Details and Model Formulation       44         4.3.1       FinFET Structure       44         4.3.2       Simulation Details       55         4.3.3       Model Formulation       56         4.4       Results and Discussion       56         4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       66         5.1       Introduction       66         5.2       Semiconductor Process Variation       66         5.3       Spatial Correlation       66         5.4       Decomposition of Process Variation       76         5.4.1       Nomenclature       76         5.4.2       Modeling Choices       76         5.5       Wafer-Level Variation       77         5.5.1       Multivariate Normal Model       77         5.5.2       Normality Test and Outlier Rejection       77         5.6       Wafer Selection       78         5.6.1       Least Angle Regression Using PCA Basis Functions       78         5.6.2       Cluster Analysis       79         5.7       Die-Level Variation       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     | 4.2.1 Background                                        | 4' |

| 4.3.1       FinFET Structure       44         4.3.2       Simulation Details       55         4.3.3       Model Formulation       55         4.4       Results and Discussion       56         4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       6         5.1       Introduction       6         5.2       Semiconductor Process Variation       6         5.3       Spatial Correlation       6         5.4       Decomposition of Process Variation       7         5.4.1       Nomenclature       7         5.4.2       Modeling Choices       7         5.5       Wafer-Level Variation       7         5.5.1       Multivariate Normal Model       7         5.5.2       Normality Test and Outlier Rejection       7         5.6       Wafer Selection       7         5.6.1       Least Angle Regression Using PCA Basis Functions       7         5.6.2       Cluster Analysis       7         5.7       Die-Level Variation       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |     |                                                         | 48 |

| 4.3.2 Simulation Details       55         4.3.3 Model Formulation       55         4.4 Results and Discussion       56         4.5 Summary       6         5 Decomposition of Semiconductor Process Variation       6         5.1 Introduction       6         5.2 Semiconductor Process Variation       6         5.3 Spatial Correlation       6         5.4 Decomposition of Process Variation       70         5.4.1 Nomenclature       70         5.4.2 Modeling Choices       70         5.5 Wafer-Level Variation       72         5.5.1 Multivariate Normal Model       73         5.5.2 Normality Test and Outlier Rejection       73         5.6 Wafer Selection       73         5.6.1 Least Angle Regression Using PCA Basis Functions       73         5.6.2 Cluster Analysis       74         5.7 Die-Level Variation       74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 4.3 | Simulation Details and Model Formulation                | 49 |

| 4.3.3 Model Formulation       55         4.4 Results and Discussion       56         4.5 Summary       6         5 Decomposition of Semiconductor Process Variation       6         5.1 Introduction       6         5.2 Semiconductor Process Variation       6         5.3 Spatial Correlation       6         5.4 Decomposition of Process Variation       7         5.4.1 Nomenclature       7         5.4.2 Modeling Choices       7         5.5 Wafer-Level Variation       7         5.5.1 Multivariate Normal Model       7         5.5.2 Normality Test and Outlier Rejection       7         5.6 Wafer Selection       7         5.6.1 Least Angle Regression Using PCA Basis Functions       7         5.6.2 Cluster Analysis       7         5.7 Die-Level Variation       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |     | 4.3.1 FinFET Structure                                  | 49 |

| 4.4 Results and Discussion       56         4.5 Summary       6         5 Decomposition of Semiconductor Process Variation       6         5.1 Introduction       6         5.2 Semiconductor Process Variation       6         5.3 Spatial Correlation       6         5.4 Decomposition of Process Variation       7         5.4.1 Nomenclature       7         5.4.2 Modeling Choices       7         5.5 Wafer-Level Variation       7         5.5.1 Multivariate Normal Model       7         5.5.2 Normality Test and Outlier Rejection       7         5.6 Wafer Selection       7         5.6.1 Least Angle Regression Using PCA Basis Functions       7         5.6.2 Cluster Analysis       7         5.7 Die-Level Variation       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     | 4.3.2 Simulation Details                                | 52 |

| 4.5       Summary       6         5       Decomposition of Semiconductor Process Variation       6-         5.1       Introduction       6-         5.2       Semiconductor Process Variation       6-         5.3       Spatial Correlation       6-         5.4       Decomposition of Process Variation       7-         5.4.1       Nomenclature       7-         5.4.2       Modeling Choices       7-         5.5       Wafer-Level Variation       7-         5.5.1       Multivariate Normal Model       7-         5.5.2       Normality Test and Outlier Rejection       7-         5.6       Wafer Selection       7-         5.6.1       Least Angle Regression Using PCA Basis Functions       7-         5.6.2       Cluster Analysis       7-         5.7       Die-Level Variation       7-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |     | 4.3.3 Model Formulation                                 | 5  |

| 5 Decomposition of Semiconductor Process Variation         64           5.1 Introduction         64           5.2 Semiconductor Process Variation         65           5.3 Spatial Correlation         66           5.4 Decomposition of Process Variation         76           5.4.1 Nomenclature         76           5.4.2 Modeling Choices         76           5.5 Wafer-Level Variation         77           5.5.1 Multivariate Normal Model         77           5.5.2 Normality Test and Outlier Rejection         77           5.6.1 Least Angle Regression Using PCA Basis Functions         76           5.6.2 Cluster Analysis         76           5.7 Die-Level Variation         77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 4.4 | Results and Discussion                                  | 50 |

| 5.1 Introduction       6-         5.2 Semiconductor Process Variation       6-         5.3 Spatial Correlation       6-         5.4 Decomposition of Process Variation       7-         5.4.1 Nomenclature       7-         5.4.2 Modeling Choices       7-         5.5 Wafer-Level Variation       7-         5.5.1 Multivariate Normal Model       7-         5.5.2 Normality Test and Outlier Rejection       7-         5.6 Wafer Selection       7-         5.6.1 Least Angle Regression Using PCA Basis Functions       7-         5.6.2 Cluster Analysis       7-         5.7 Die-Level Variation       7-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 4.5 | Summary                                                 | 6  |

| 5.1 Introduction       6-         5.2 Semiconductor Process Variation       6-         5.3 Spatial Correlation       6-         5.4 Decomposition of Process Variation       7-         5.4.1 Nomenclature       7-         5.4.2 Modeling Choices       7-         5.5 Wafer-Level Variation       7-         5.5.1 Multivariate Normal Model       7-         5.5.2 Normality Test and Outlier Rejection       7-         5.6 Wafer Selection       7-         5.6.1 Least Angle Regression Using PCA Basis Functions       7-         5.6.2 Cluster Analysis       7-         5.7 Die-Level Variation       7-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 | Dec | composition of Semiconductor Process Variation          | 64 |

| 5.3Spatial Correlation665.4Decomposition of Process Variation705.4.1Nomenclature705.4.2Modeling Choices705.5Wafer-Level Variation715.5.1Multivariate Normal Model725.5.2Normality Test and Outlier Rejection735.6Wafer Selection735.6.1Least Angle Regression Using PCA Basis Functions735.6.2Cluster Analysis745.7Die-Level Variation73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |     |                                                         | 64 |

| 5.4 Decomposition of Process Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 5.2 | Semiconductor Process Variation                         | 6! |

| 5.4.1 Nomenclature       76         5.4.2 Modeling Choices       76         5.5 Wafer-Level Variation       77         5.5.1 Multivariate Normal Model       77         5.5.2 Normality Test and Outlier Rejection       77         5.6 Wafer Selection       77         5.6.1 Least Angle Regression Using PCA Basis Functions       77         5.6.2 Cluster Analysis       76         5.7 Die-Level Variation       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 5.3 | Spatial Correlation                                     | 68 |

| 5.4.1 Nomenclature       76         5.4.2 Modeling Choices       76         5.5 Wafer-Level Variation       77         5.5.1 Multivariate Normal Model       77         5.5.2 Normality Test and Outlier Rejection       77         5.6 Wafer Selection       77         5.6.1 Least Angle Regression Using PCA Basis Functions       77         5.6.2 Cluster Analysis       76         5.7 Die-Level Variation       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 5.4 | Decomposition of Process Variation                      | 70 |

| 5.4.2 Modeling Choices       70         5.5 Wafer-Level Variation       72         5.5.1 Multivariate Normal Model       73         5.5.2 Normality Test and Outlier Rejection       73         5.6 Wafer Selection       73         5.6.1 Least Angle Regression Using PCA Basis Functions       73         5.6.2 Cluster Analysis       76         5.7 Die-Level Variation       76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |     |                                                         | 70 |

| 5.5       Wafer-Level Variation       73         5.5.1       Multivariate Normal Model       73         5.5.2       Normality Test and Outlier Rejection       73         5.6       Wafer Selection       73         5.6.1       Least Angle Regression Using PCA Basis Functions       73         5.6.2       Cluster Analysis       74         5.7       Die-Level Variation       74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |     |                                                         | 70 |

| 5.5.1       Multivariate Normal Model       73         5.5.2       Normality Test and Outlier Rejection       73         5.6       Wafer Selection       73         5.6.1       Least Angle Regression Using PCA Basis Functions       73         5.6.2       Cluster Analysis       76         5.7       Die-Level Variation       76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 5.5 | Wafer-Level Variation                                   | 72 |

| 5.5.2       Normality Test and Outlier Rejection       73         5.6       Wafer Selection       73         5.6.1       Least Angle Regression Using PCA Basis Functions       73         5.6.2       Cluster Analysis       70         5.7       Die-Level Variation       70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     |                                                         | 72 |

| 5.6       Wafer Selection       73         5.6.1       Least Angle Regression Using PCA Basis Functions       73         5.6.2       Cluster Analysis       76         5.7       Die-Level Variation       77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     | 5.5.2 Normality Test and Outlier Rejection              |    |

| 5.6.1 Least Angle Regression Using PCA Basis Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 5.6 | · · · · · · · · · · · · · · · · · · ·                   | 7: |

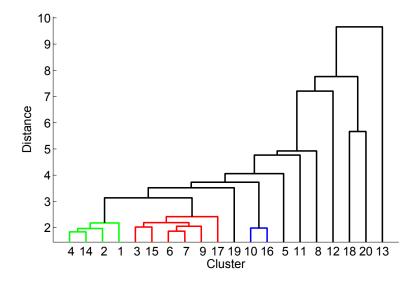

| 5.6.2 Cluster Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | -   |                                                         |    |

| 5.7 Die-Level Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |     |                                                         |    |

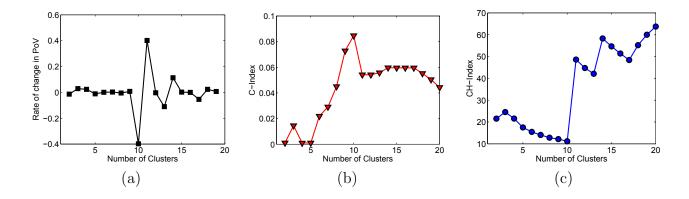

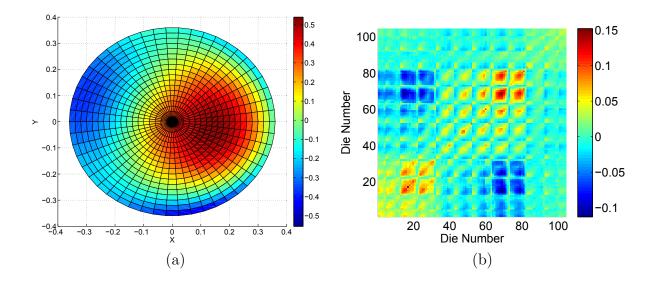

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 5.7 |                                                         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 5.8 | Residual Analysis                                       | 7  |

|    |              |                              | iv |  |

|----|--------------|------------------------------|----|--|

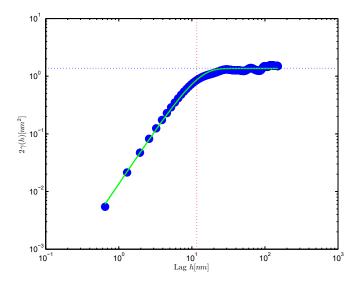

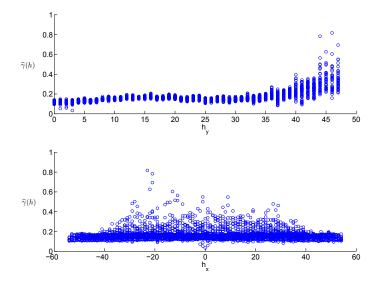

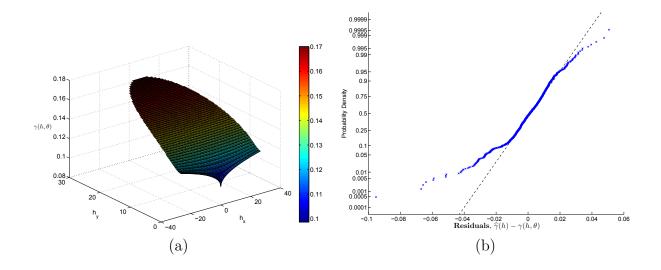

|    |              | 5.8.1 Variogram of Residuals | 78 |  |

|    |              | 5.8.2 Variogram Estimation   | 79 |  |

|    | 5.9          | Results and Discussion       | 82 |  |

|    |              | 5.9.1 Wafer Selection        | 83 |  |

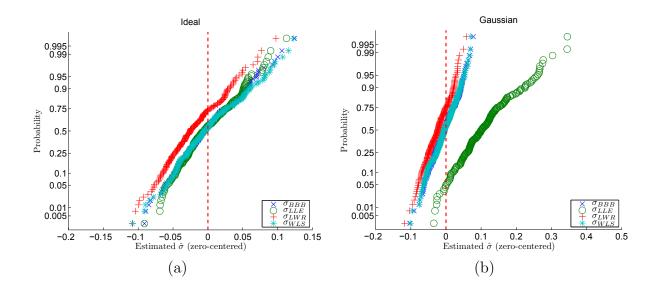

|    |              | 5.9.2 Model Estimators       | 87 |  |

|    | 5.10         | Summary                      | 91 |  |

| 6  | Con          | clusion                      | 92 |  |

|    | 6.1          | Summary of Contributions     | 92 |  |

|    | 6.2          | Suggested Future Work        | 93 |  |

| A  | Bia          | s in Finite Length Variance  | 95 |  |

| В  | Val          | idity of LLE Approach        | 97 |  |

| Bi | Bibliography |                              |    |  |

## List of Figures

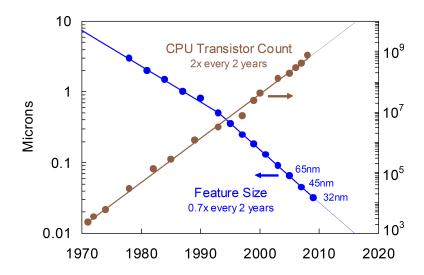

| 1.1  | Moore's Law scaling trend                                                             | 2  |

|------|---------------------------------------------------------------------------------------|----|

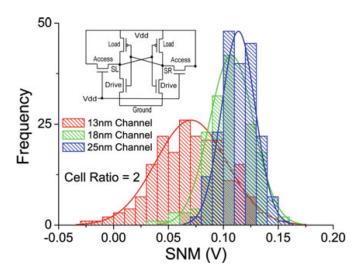

| 1.2  | SNM distribution of 6T SRAM                                                           | 3  |

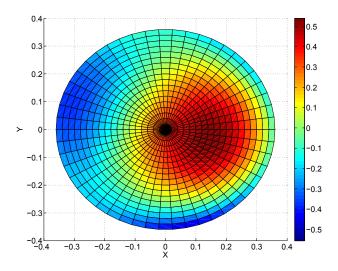

| 1.3  | Example of systematic wafer-level spatial variation                                   | 4  |

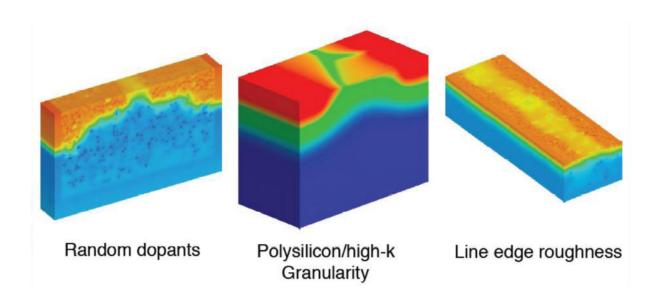

| 1.4  | Sources of intrinsic variation                                                        | 4  |

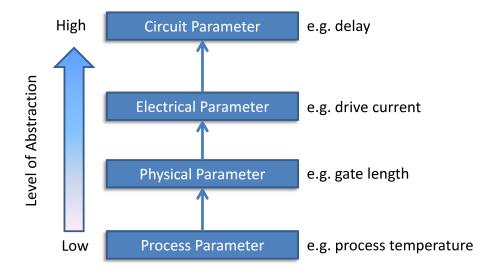

| 1.5  | Levels of abstraction in modeling parameters                                          | 5  |

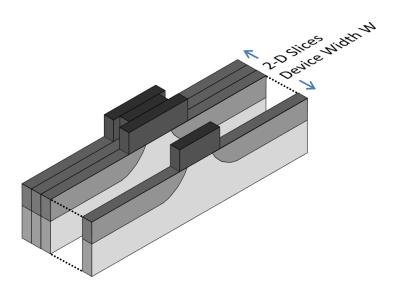

| 1.6  | Schematic view of planar MOSFET shown with 2D slice approximation                     | 6  |

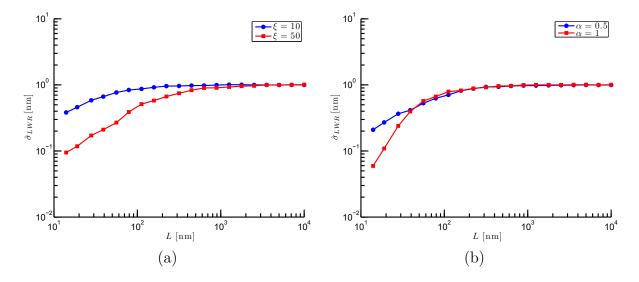

| 2.1  | Biased estimate $\hat{\sigma}_{LWR}$ as a function of length of the line              | 11 |

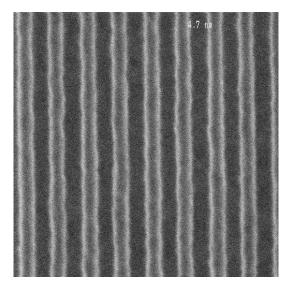

| 2.2  | A sample scanning electron micrograph (SEM) image                                     | 12 |

| 2.3  | Illustration of roughness descriptors                                                 | 13 |

| 2.4  | Generalized framework of simulated and digitized SEM data                             | 17 |

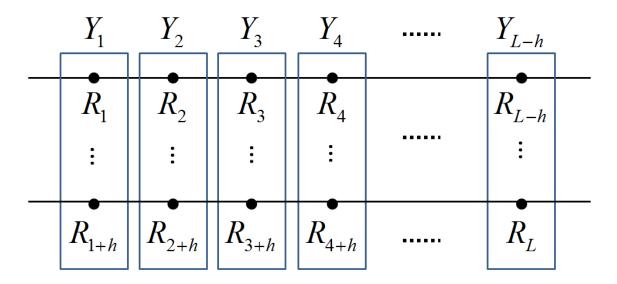

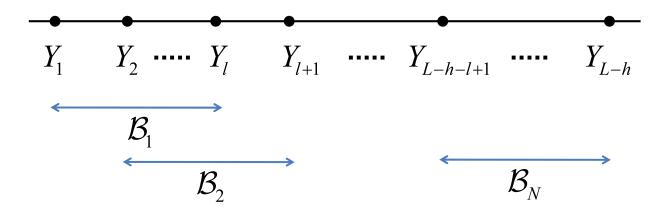

| 2.5  | Graphical illustration of block of blocks bootstrap                                   | 22 |

| 2.6  | Graphical illustration of moving block bootstrap                                      | 23 |

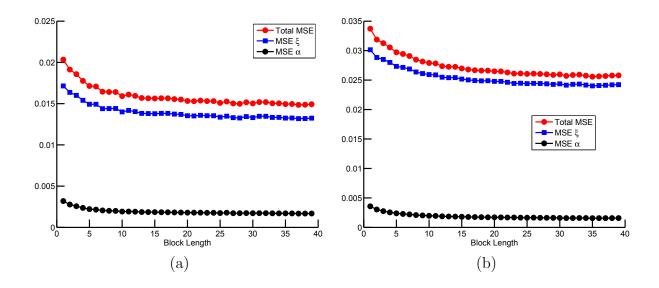

| 2.7  | Mean-squared error (MSE) in $\alpha$ and $\xi$ as a function of the block length      | 27 |

| 2.8  | Optimal block length computed using Politis and White method                          | 27 |

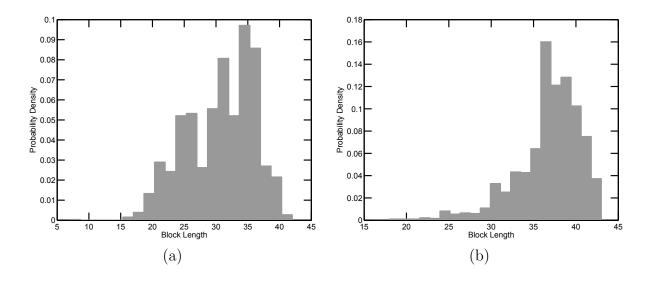

| 2.9  | Comparison of two methods of estimating WLS weights                                   | 28 |

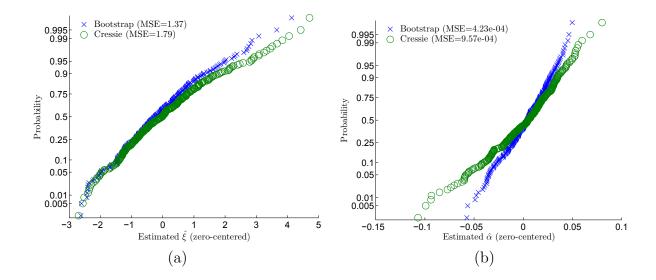

| 2.10 | Comparison of four different estimates of $\sigma$                                    | 29 |

| 2.11 |                                                                                       | 30 |

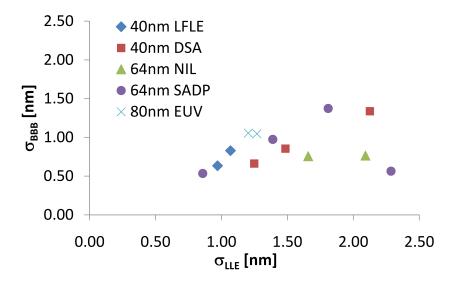

| 2.12 | Comparison of $\hat{\sigma}_{BBB}$ and $\hat{\sigma}_{LLE}$ for various NGL processes | 31 |

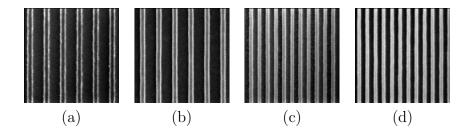

| 3.1  | SEM images at intermediate SADP steps                                                 | 33 |

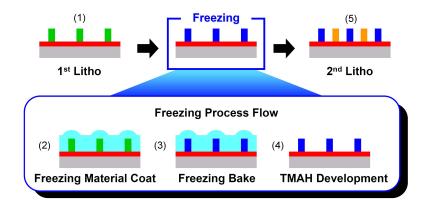

| 3.2  | Litho-freeze-litho-etch (LFLE) process flow                                           | 35 |

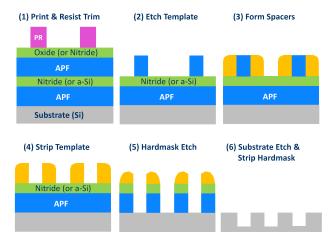

| 3.3  | Self-aligned Double-Patterning process flow                                           | 36 |

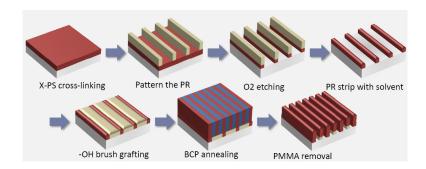

| 3.4  | Directed Self-Assembly process flow                                                   | 37 |

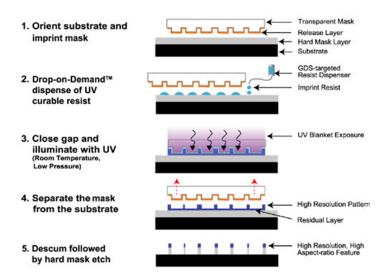

| 3.5  | Nano-imprint lithography process flow                                                 | 38 |

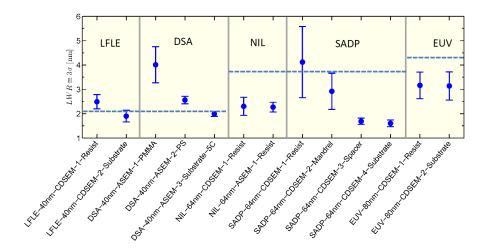

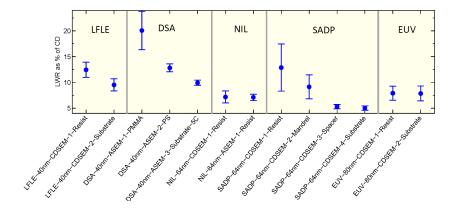

| 3.6  | LWR $(3\sigma)$ in nm for various NGL processes                                       | 40 |

| 3.7  | Normalized LWR for various NGL processes                                              | 41 |

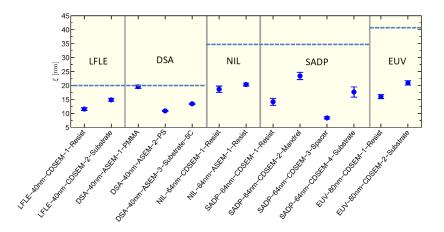

| 3.8  | Correlation length $(\xi)$ for various NGL processes                                  | 42 |

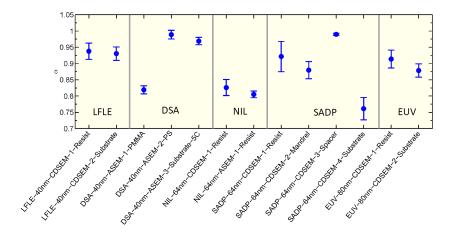

| 3.9  | Roughness exponent $(\alpha)$ for various NGL processes                               | 42 |

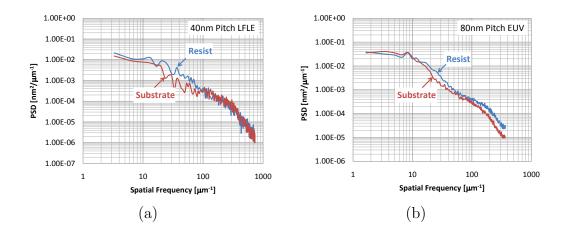

| 3.10 |                                                                                       | 44 |

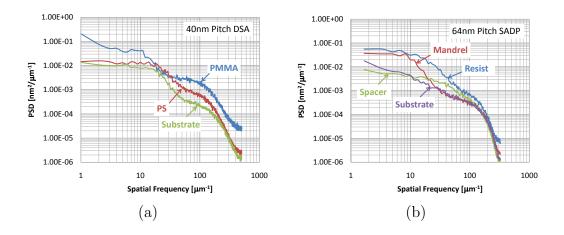

| 3.11 | Power Spectral Density (PSD) for DSA and SADP                                         | 44 |

| 3.12 | Results of process optimization from 64nm pitch EUV                             | 45 |

|------|---------------------------------------------------------------------------------|----|

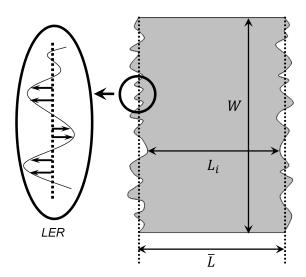

| 4.1  | Comparison of LER and LWR                                                       | 47 |

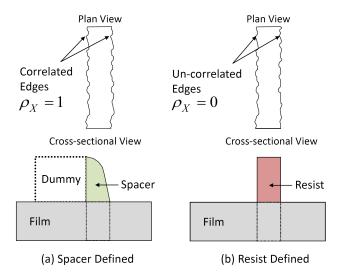

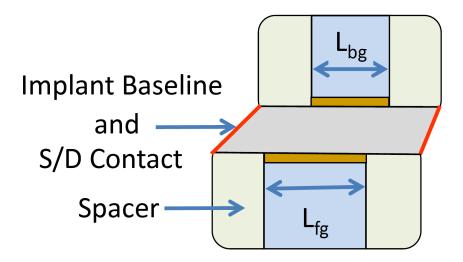

| 4.2  | Illustration of spacer and resist lithography methods                           | 49 |

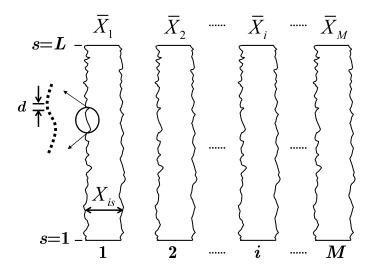

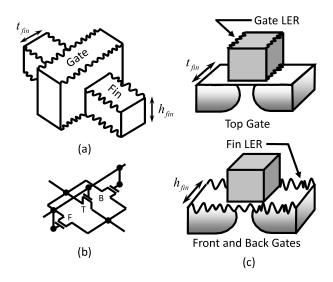

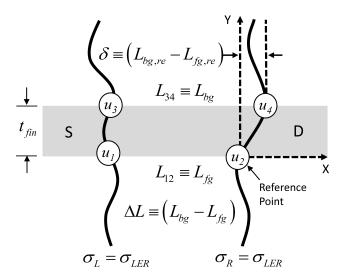

| 4.3  | Illustration of LER components in FinFET                                        | 50 |

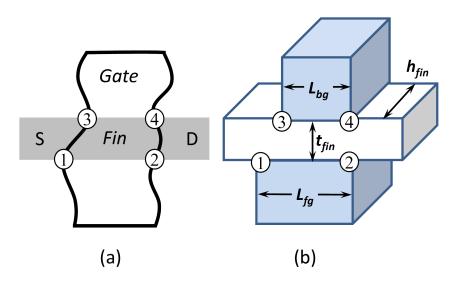

| 4.4  | Schematic views of a DG FinFET                                                  | 51 |

| 4.5  | Non-ideal 2-D DG-FET structure                                                  | 52 |

| 4.6  | Definition of model parameters                                                  | 54 |

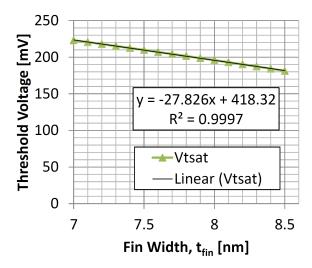

| 4.7  | Fin width dependence of saturation threshold voltage                            | 57 |

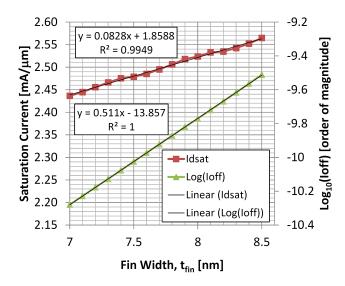

| 4.8  | Fin width dependence of $I_{d,sat}$ and $I_{off}$                               | 57 |

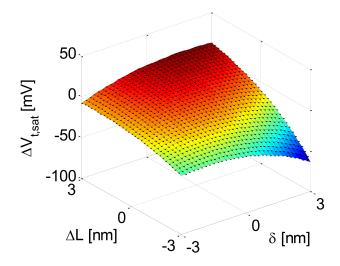

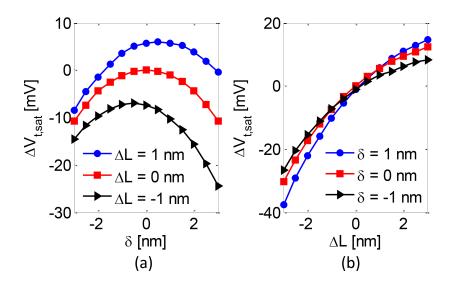

| 4.9  | Threshold voltage variation over $\Delta L$ and $\delta$ space                  | 58 |

| 4.10 | Threshold voltage dependence on $\delta$ and $\Delta L$                         | 58 |

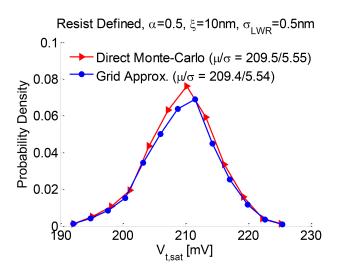

| 4.11 | Monte-Carlo comparison of $V_{t,sat}$ for simulated and experimental grid       | 60 |

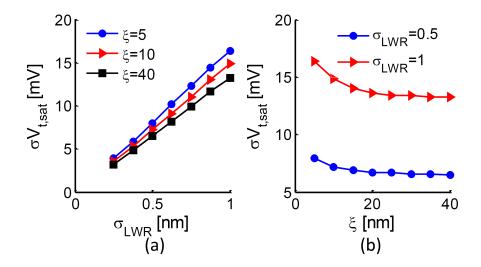

| 4.12 | Variability in saturation threshold voltage $V_{t,sat}$ for resist-defined gate | 61 |

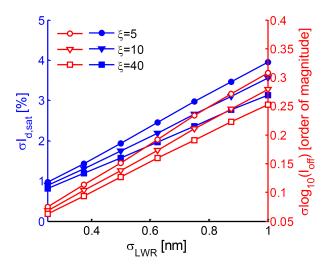

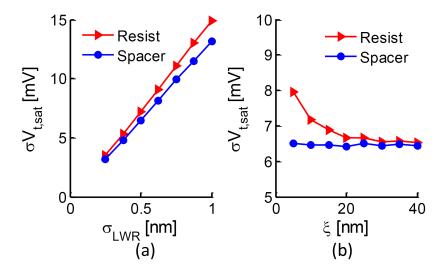

| 4.13 | Variability in drive and off-state current as function of LWR amplitude         | 62 |

| 4.14 | Variability in drive and off-state current as function of correlation length    | 62 |

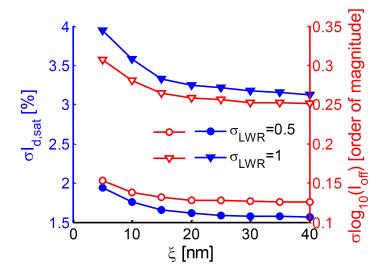

| 4.15 | Variability in saturation threshold voltage $V_{t,sat}$ for resist-defined gate | 63 |

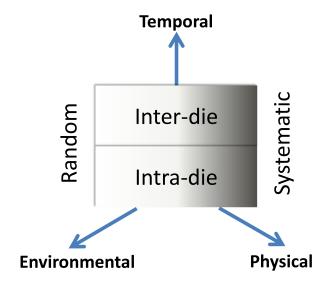

| 5.1  | Overview of variability components and attributes                               | 66 |

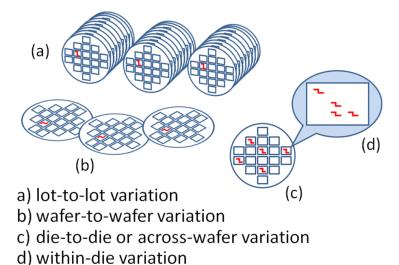

| 5.2  | Illustration of semiconductor process variation hierarchy                       | 67 |

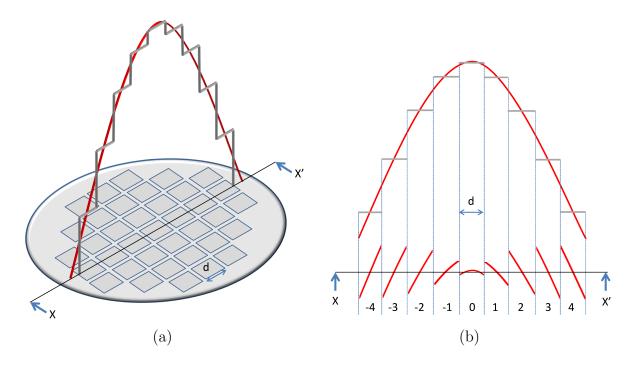

| 5.3  | Source of spatial correlation due to wafer-level variation                      | 68 |

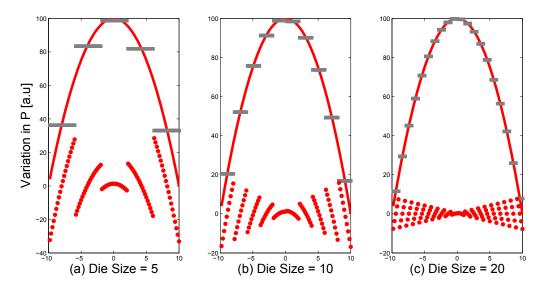

| 5.4  | Factors influencing our ability to estimate spatial correlation                 | 69 |

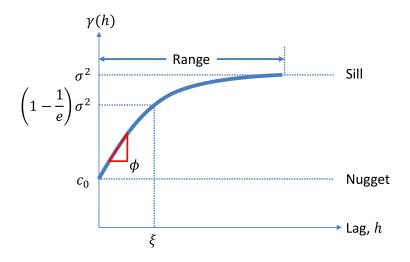

| 5.5  | Graphical illustration of variogram parameters                                  | 81 |

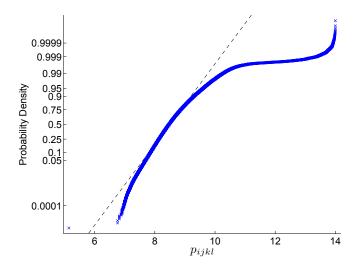

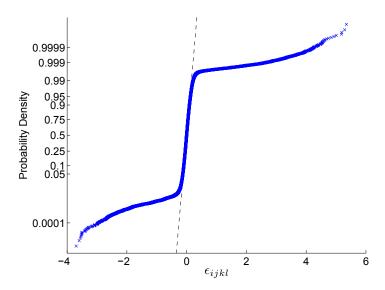

| 5.6  | Probability density plot of raw data                                            | 83 |

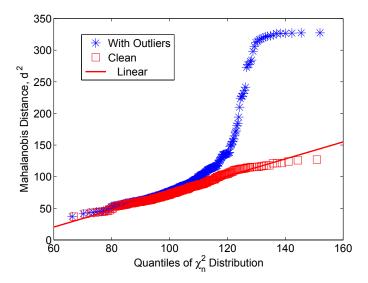

| 5.7  | Mahalanobis distance before and after rejecting outlier wafers                  | 84 |

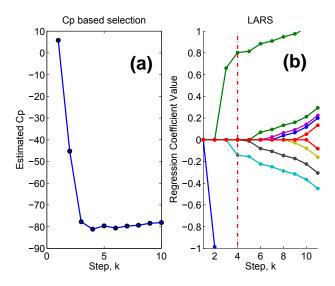

| 5.8  | Example of Least Angle Regression                                               | 85 |