# Time Domain Interference Cancellation for Cognitive Radios and Future Wireless Systems

Jing Yang Robert W. Brodersen

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2010-61 http://www.eecs.berkeley.edu/Pubs/TechRpts/2010/EECS-2010-61.html

May 11, 2010

Copyright © 2010, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# **Time Domain Interference Cancellation for Cognitive Radios and Future Wireless Systems**

By

Jing Yang

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

In

Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Robert W. Brodersen, Chair Professor Borivoje Nikolic Professor Philip M. Kaminsky

Spring 2010

# Time Domain Interference Cancellation for Cognitive Radios and Future Wireless Systems

Copyright 2010

by

Jing Yang

### **Abstract**

The discrepancy between perceived spectrum shortage and the actual availability by measurements motivates the use of cognitive radio concepts. In this approach the radio locates and then transmits in unused or lightly used bands. If a wideband digital approach (on the order of GHz) to channel selection is taken to provide the necessary radio flexibility, there is a stringent dynamic range and speed requirement in the analog to digital conversion process. This arises from the large interfering signals which are effectively in-band since they are not removed by analog pre-filters. Given this extremely challenging wideband dynamic range goal, a fundamentally different mixed signal architecture has been pursued which is based on time domain signal cancellation. The objective of this thesis is therefore to analyze and implement critical aspects of this approach, with particular focus on the power requirements and silicon area.

This approach explores the use of a mixed analog with digital assistance architecture which uses multiple low to medium resolution ADCs with digital adaptive filters. The effective dynamic range of the front-end is enhanced by cancelling the unwanted interference in the time domain.

Interference cancellation performance is improved using oversampling and a digital dual adaptive signal processing technique that provides a low mean squared error for cancellation together with a large processing gain. The system could achieve at least 11 bit equivalent dynamic range for the desired weak signals using two 5-bit ADC's and a 7-bit DAC. In general, the Effective Bits from Dynamic Range Reduction (EBDR) for the system is equal to, or more than N+M bits, where N and M are resolutions of the two ADC's used.

The key components of the system are high speed medium resolution ADC's and they have been implemented to demonstrate the path to a low power small area solution. An asynchronous 1GS/s ADC with a peak SNDR of 31.5dB, ENOB 5.0 bits, is achieved by time interleaving two ADC's based on the binary equivalent successive approximation (SA) algorithm using a series capacitive ladder with input capacitance of 84fF. A simple extension of the SA algorithm essentially removes the ENOB degradation due to metastability from the comparator. The ADC's are fabricated in 65nm CMOS with an active area of 0.11mm<sup>2</sup>, with a total power consumption of 6.7mW.

It is believed that the time domain approach for wideband, high dynamic range applications which has been explored in this thesis is a step towards the goal of a future radio system, in which the A/D conversion process is directly after the front-end low noise amplifiers.

1

To my dear parents

## **Contents**

| List of Figures                                              | v  |

|--------------------------------------------------------------|----|

| List of Tables                                               | ix |

| Chapter 1 Introduction                                       | 1  |

| 1.1 Motivation                                               | 1  |

| 1.1.1 Concept of Cognitive Radio                             | 1  |

| 1.1.1.1 Concept of Cognitive Radio                           | 3  |

| 1.1.1.2 Uniqueness of Cognitive Radio Systems                | 4  |

| 1.1.2 Future Wideband Radio Systems                          | 7  |

| 1.2 Approaches for Interference Cancellation                 | 8  |

| 1.2.1 Frequency Domain Cancellation                          | 8  |

| 1.2.2 Spatial Domain Cancellation                            | 8  |

| 1.2.3 Time Domain Cancellation                               | 10 |

| Chapter 2 Time domain Interference Cancellation Architecture | 11 |

| 2.1 Mixed Signal Architecture                                | 13 |

| 2.1.1 Feedback Architecture                                  | 13 |

| 2.1.2 Feedforward Architecture                               | 15 |

| 2.2 Cancellation Digital Processing                          | 15 |

| 2.2.1 Dual Adaptive Filter (AF)                              | 16 |

| 2.2.2 Processing Gain and Interference Attenuation           | 16 |

| 2.2.3 CR Signal Protection                                   | 18 |

|                                                              |    |

| 2.3 Performance Evaluation and System Design Specification       | 19 |

|------------------------------------------------------------------|----|

| 2.3.1 SINR after Attenuation                                     | 21 |

| 2.3.2 Residue Signal Analysis                                    | 22 |

| 2.3.2.1 Ratio of Signal Peak to Residue Peak                     | 22 |

| 2.3.2.2 Residue Power Analysis                                   | 23 |

| 2.3.3 Overall EBDR for Different SIR                             | 24 |

| 2.3.4 System Specification for Cancellation ADC and DAC          | 26 |

| 2.4 Conclusion                                                   | 26 |

| Chapter 3 Digital Signal Processing In Interference Cancellation | 27 |

| 3.1 System Model                                                 | 28 |

| 3.2 Adaptive Filter Approaches                                   | 30 |

| 3.2.1 Assumptions                                                | 30 |

| 3.2.2 Single Adaptive Filter Approach                            | 30 |

| 3.2.3 Dual adaptive Filter approach                              | 32 |

| 3.2.4 Performance Comparison of the Two Approaches               | 35 |

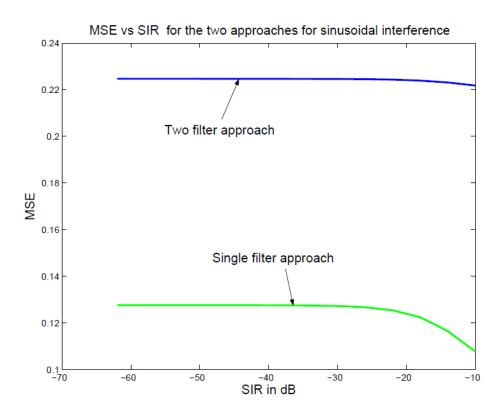

| 3.2.4.1 Variation of MSE with SIR                                | 35 |

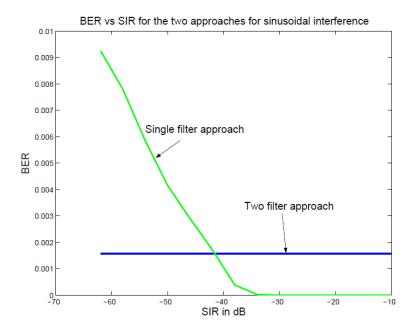

| 3.2.4.2 Variation of BER with SIR                                | 36 |

| 3.2.4.3 Variation of BER with Bandwidth Ratio                    | 37 |

| 3.3 Equalizer                                                    | 37 |

| 3.3.1 Linear Adaptive Equalizer                                  | 38 |

| 3.3.2 Decision feedback equalizer                                | 38 |

| 3.4 Combining Interference Cancellation and Equalizer Blocks     | 40 |

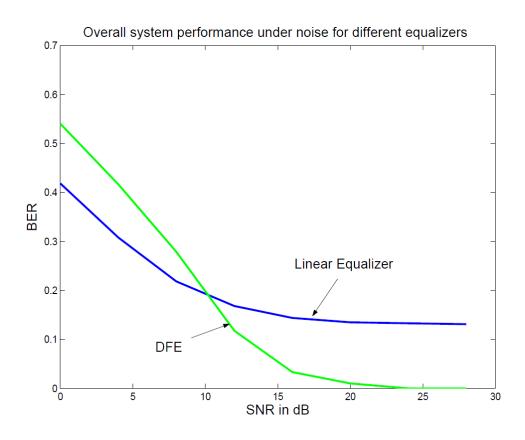

| 3.4.1 Performance in the presence of noise                       | 41 |

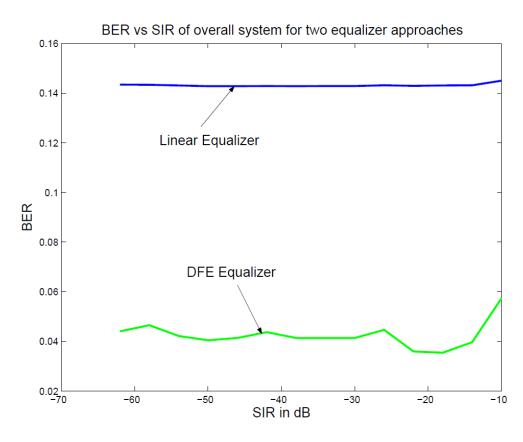

| 3.4.2 Effect of SIR on overall system performance                | 41 |

| 3.5 Conclusion                                                   | 42 |

| Chapter 4 High Speed ADC                                         | 43 |

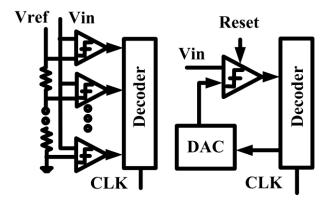

| 4.1 ADC Architecture                                             | 44 |

| 4.1.1 Asynchronous Processing                     | 45 |

|---------------------------------------------------|----|

| 4.1.2 Architecture                                | 46 |

| 4.2 Metastability Issue and Error Correction      | 48 |

| 4.3 Circuit Implementation                        | 50 |

| 4.3.1 Critical Path and Reset Loop                | 51 |

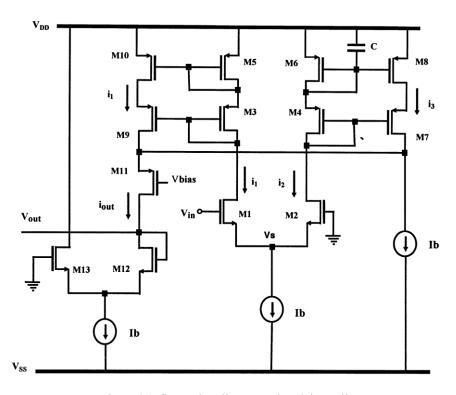

| 4.3.2 Comparator Design                           | 52 |

| 4.3.3 Semi-closed Loop Digital Circuits           | 53 |

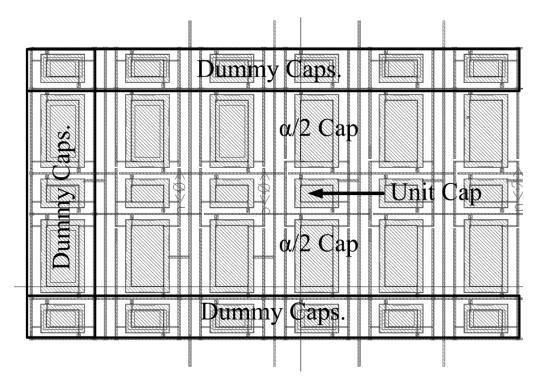

| 4.3.4 DAC Design and Non-Binary Capacitance Array | 55 |

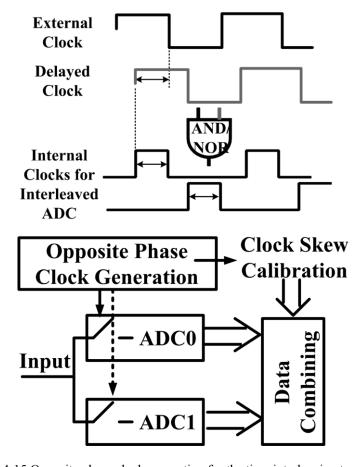

| 4.3.5 Opposite-Phase Clocks for Time Interleaving | 59 |

| 4.4 Measurement Results                           | 59 |

| 4.5 Summary                                       | 65 |

| Chapter 5 System Demonstration.                   | 66 |

| 5.1 Subtractor and Gain Stage                     | 66 |

| 5.2 DAC                                           | 68 |

| 5.3 Analog Delay Line                             | 70 |

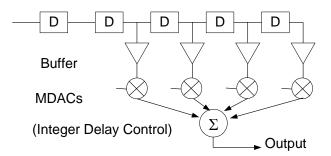

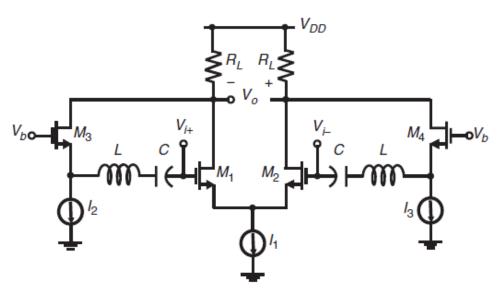

| 5.3.1 First and Second Order Analog Delay Cell    | 71 |

| 5.3.2 Digital Fractional Delay Filters            | 76 |

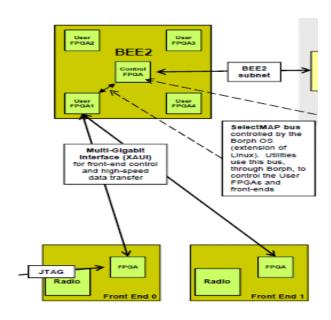

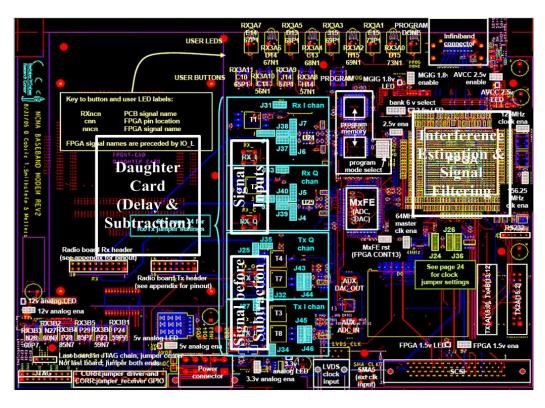

| 5.4 System Test Bed                               | 77 |

| Chapter 6 Conclusions                             | 83 |

| Bibliography                                      | 85 |

# List of Figures

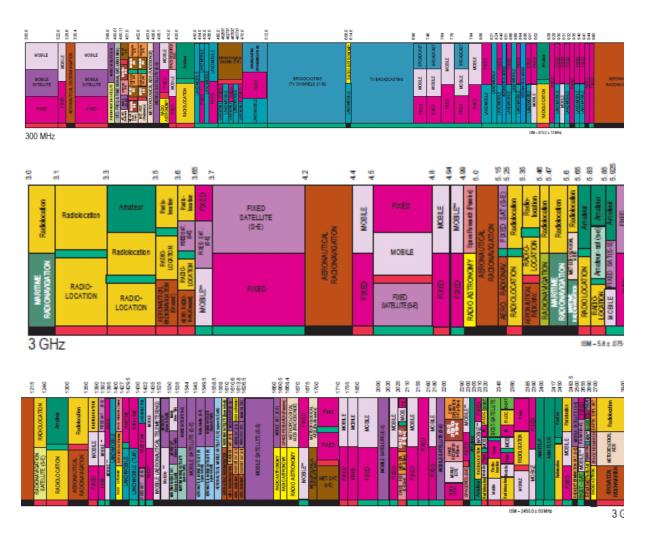

| Fig. 1-1 FCC Allocation Chart. a) 300MHz to 1GHz. b) 1GHz to 3GHz. c) 3GHz to 6                              |    |

|--------------------------------------------------------------------------------------------------------------|----|

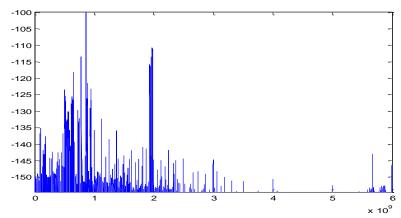

| Fig. 1-2 A snapshot of the spectrum utilization up to 6 GHz in an urban area [1]                             | 2  |

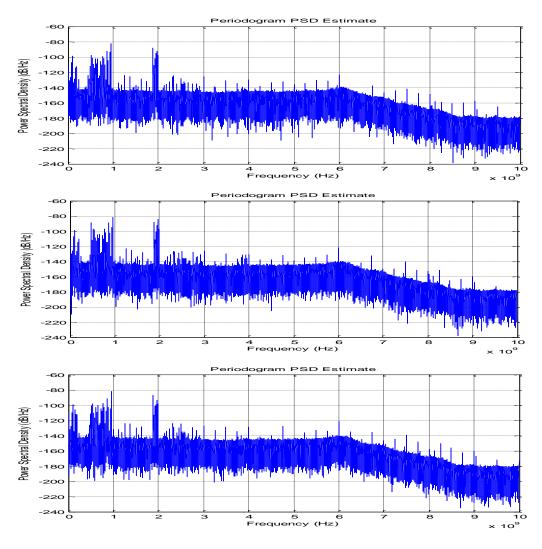

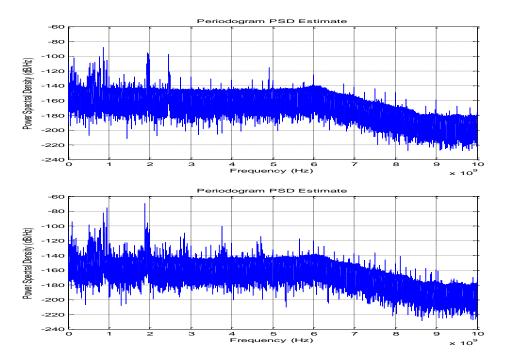

| Fig. 1-3 Dirty Maps of indoor interference at positions with equal probability of inside outside interferers |    |

| Fig. 1-4 Dirty Maps of interference next to a wireless LAN transmitter                                       | 6  |

| Fig. 1-5 Dirty maps of interference in a lab station.                                                        | 6  |

| Fig. 1-6 Traditional radio front-end.                                                                        | 7  |

| Fig. 1-7 Conceptual illustration for future radio front-end.                                                 | 7  |

| Fig. 1-8 Frequency notch filter approach for interference cancellation.                                      | 9  |

| Fig. 1-9 Spatial notch filter approach to reduce the interference of 30dB and 40dB from directions.          |    |

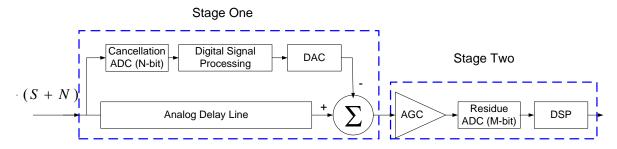

| Fig. 2-1 Time domain interference cancellation approach.                                                     | 12 |

| Fig. 2-2 The interfering and CR signal features.                                                             | 12 |

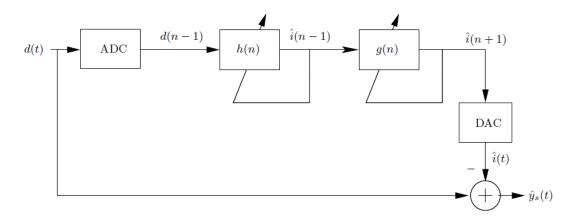

| Fig. 2-3 Feedback architecture for time domain interference cancellation.                                    | 14 |

| Fig. 2-4 Feedforward architecture for time domain interference cancellation.                                 | 14 |

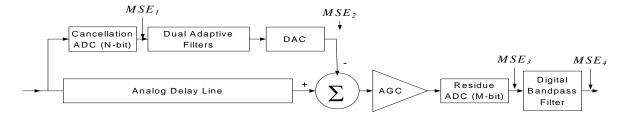

| Fig. 2-5 The system architecture and MSEs interested in the cancellation.                                    | 17 |

| Fig. 2-6 Simulation Setup for the proposed time domain interference cancellation                             | 20 |

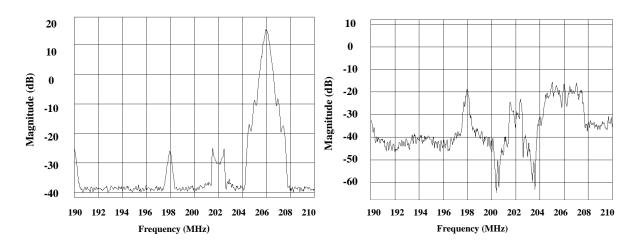

| Fig. 2-7 Simulation showing interference attenuation using the cancellation approach.                        | 20 |

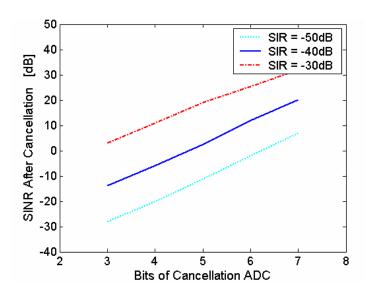

| Fig 2-8 SINR greatly improved using low resolution ADC in difference environments                            | 21 |

| Fig. 2-9 Residue signal break down of the first stage.                                                                                                        | 22   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 2-10 Amplification of the residue signal from the first stage.                                                                                           | 23   |

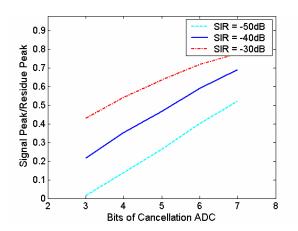

| Fig. 2-11 Time domain peak ratio of the CR signal to the Residue                                                                                              | 23   |

| Fig. 2-12 Residue power analysis.                                                                                                                             | 24   |

| Fig. 2-13 RMS Ratio of signal to Residue versus Bits of Cancellation ADC                                                                                      | 24   |

| Fig. 2-14 Determine the resolution N of the Cancellation ADC and the DAC                                                                                      | 26   |

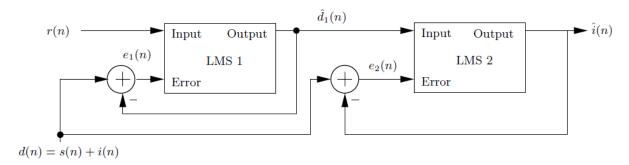

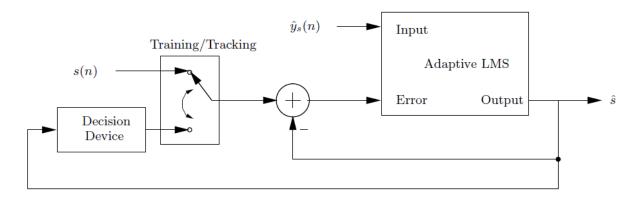

| Fig. 3-1 Signal flow through the channel                                                                                                                      | 28   |

| Fig. 3-2 Illustration of an interference cancellation system in cognitive radio.                                                                              | 28   |

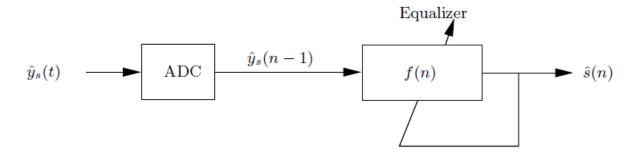

| Fig. 3-3 A system illustrating channel equalization in cognitive radio.                                                                                       | 29   |

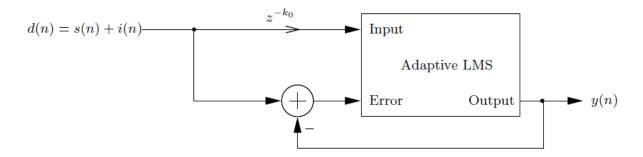

| Fig. 3-4 Single adaptive filter approach for interference cancellation.                                                                                       | 31   |

| Fig. 3-5 The two adaptive filter approach to interference cancellation.                                                                                       | 32   |

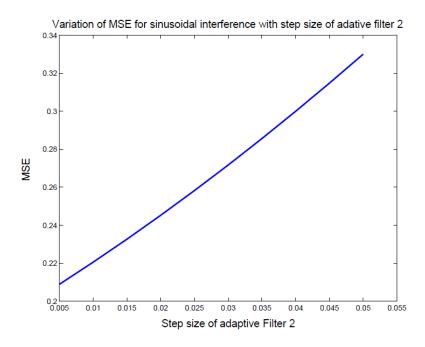

| Fig. 3-6 Effect of step size of second AF on the MSE with sinusoidal interference                                                                             | 34   |

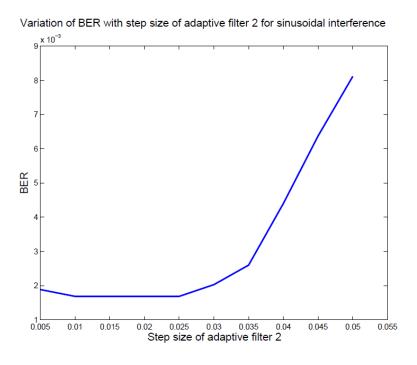

| Fig. 3-7 Effect of step size of second AF on the BER with sinusoidal interference                                                                             | 34   |

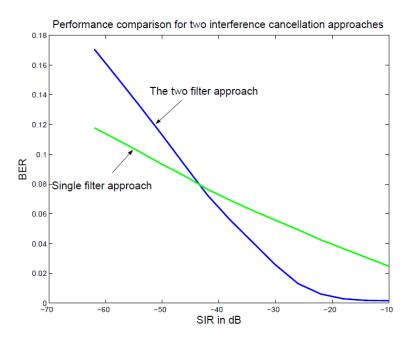

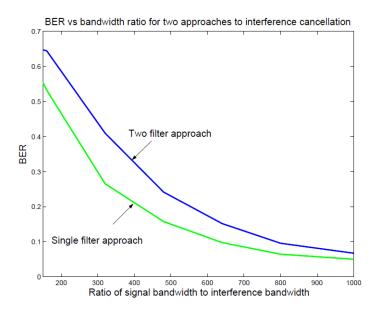

| Fig. 3-8 MSE vs SIR for interference cancellation approaches with sinusoidal interference                                                                     |      |

| Fig. 3-9 BER vs SIR for interference cancellation approaches with sinusoidal interference                                                                     | nce  |

| Fig. 3-10 BER vs SIR for interference cancellation approaches with FSK interference                                                                           |      |

| Fig. 3-11 BER vs ratio of signal bandwidth to interference bandwidth with FSK interference                                                                    |      |

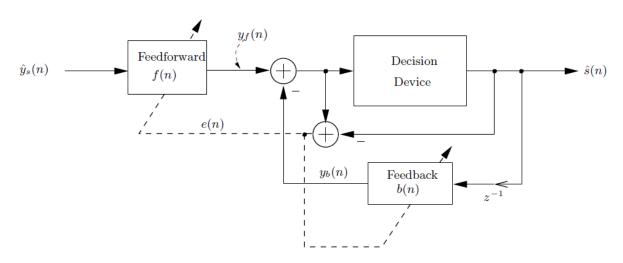

| Fig. 3-12 Structure of a linear LMS adaptive equalizer used to remove ISI.                                                                                    | 38   |

| Fig. 3-13 Structure of an LMS-adapted DFE.                                                                                                                    | 39   |

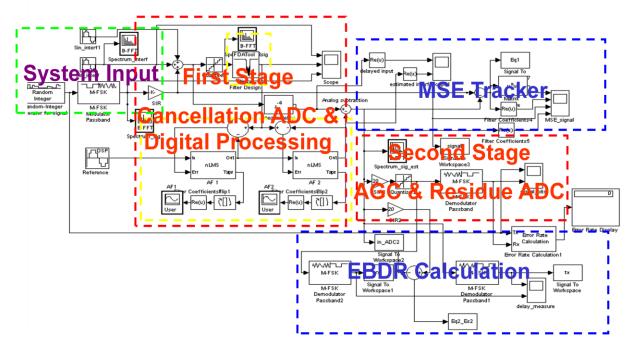

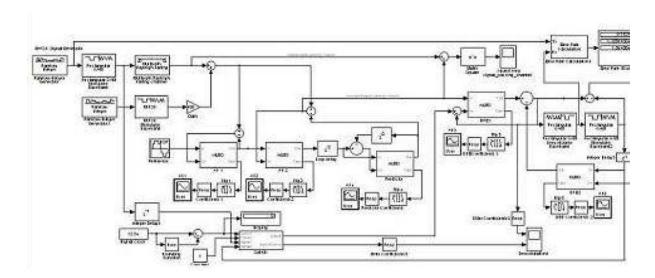

| Fig. 3-14 Snapshot of the implementation (with all the blocks) in Simulink                                                                                    | 39   |

| Fig. 3-15 Overall system performance for two equalization approaches.                                                                                         | 40   |

| Fig. 3-16 Overall system performance for the two approaches of equalization.                                                                                  | 41   |

| Fig. 4-1 High speed ADC architecture. a) Flash ADC, b) SAR ADC                                                                                                | 44   |

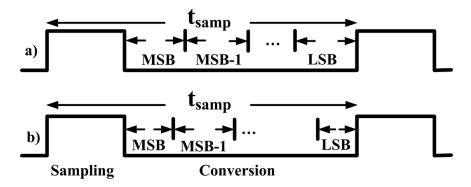

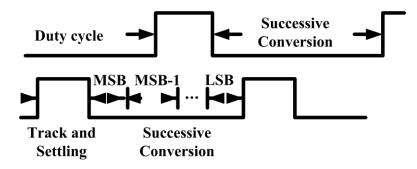

| Fig. 4-2 a) Synchronous processing with equally divided bit comparison time. Synchronous sampling, asynchronous processing conversion with unequal tinterval. | time |

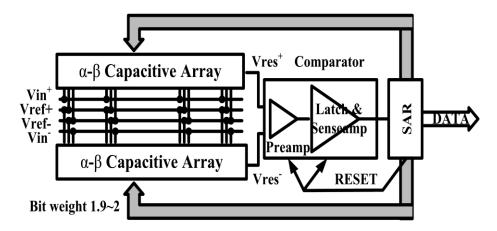

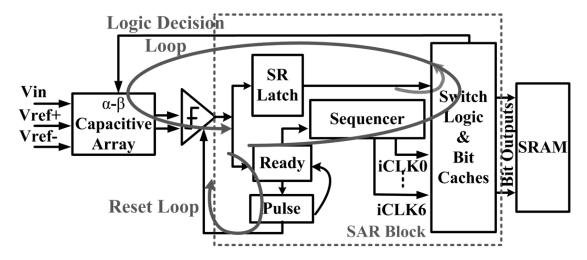

| Fig. 4-3 Time interleaved asynchronous ADC architecture.                                                 | . 46 |

|----------------------------------------------------------------------------------------------------------|------|

| Fig. 4-4 Internal opposite phase clocks.                                                                 | . 47 |

| Fig. 4-5 Single-ended ADC architecture details of SA blocks and data paths                               | . 47 |

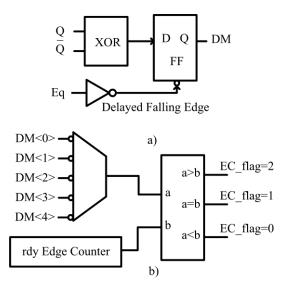

| Fig. 4-6 a) DM register. b) Error correction circuit diagram to solve metastability                      | . 50 |

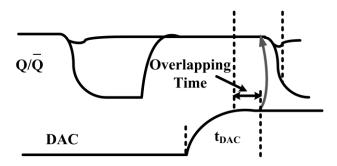

| Fig. 4-7 Time overlapping between the comparator and the DAC.                                            | . 50 |

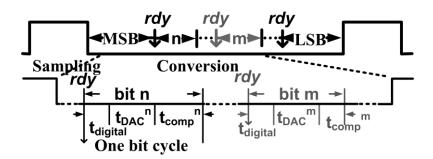

| Fig. 4-8 rdy signals and critical delay in each conversion bit cycle.                                    | . 51 |

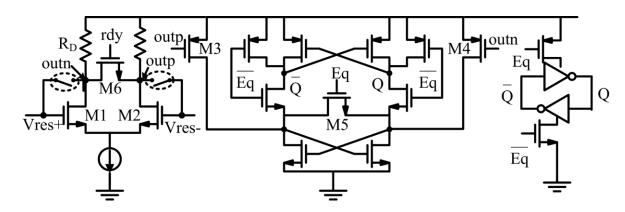

| Fig. 4-9 Dynamic comparator circuit schematic with pre-amplifier, dynamic latch dynamic sense-amplifier. |      |

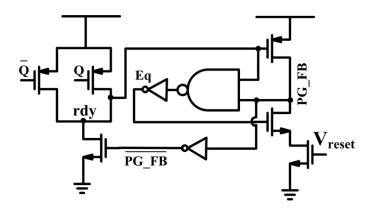

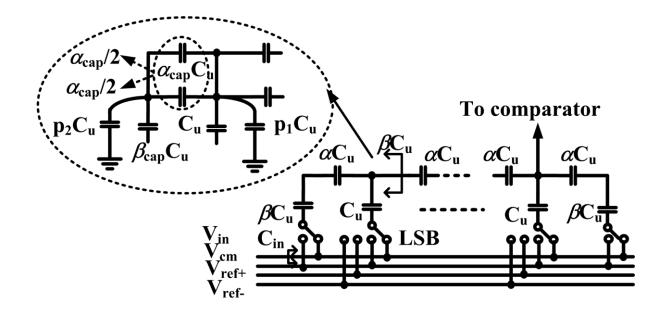

| Fig. 4-10 Dynamic rdy acknowledge signal generator and pulse generator schematics                        | . 54 |

| Fig. 4-11 Semi-closed loop timing diagram with extended reset phase.                                     | . 55 |

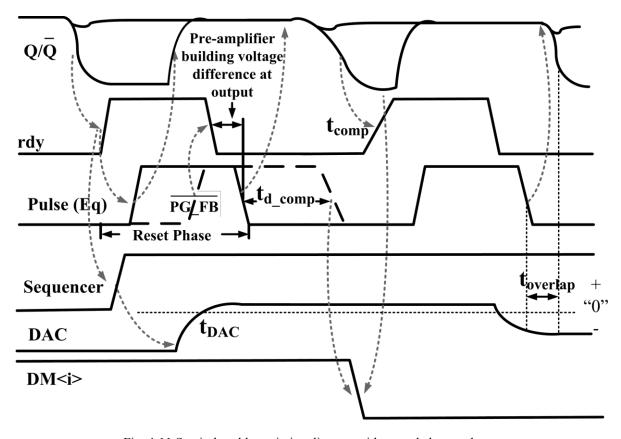

| Fig. 4-12 Fixed DAC settling time by scaling switch sizes as opposed to the targeted svoltages.          | _    |

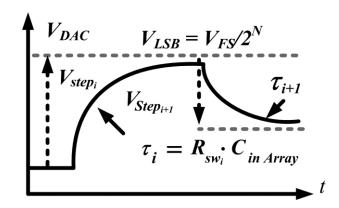

| Fig. 4-13 Non-binary series capacitive ladder network: schematics and parasitic at interconnects.        |      |

| Fig. 4-14 Binary capacitive ladder with improved symmetry.                                               | . 58 |

| Fig. 4-15 Opposite phase clock generation for the time interleaving topology                             | . 59 |

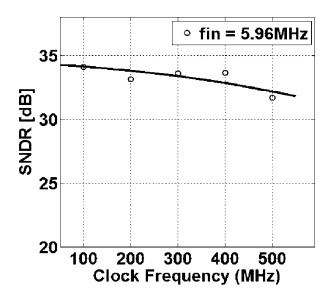

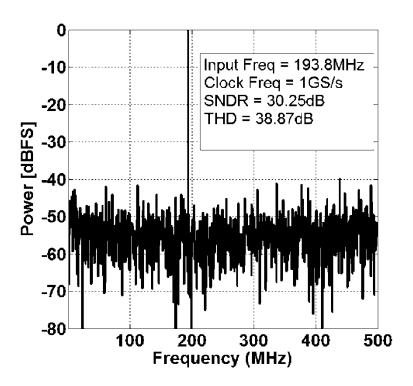

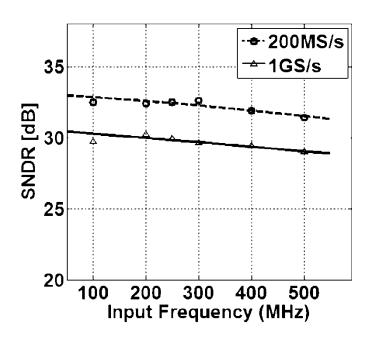

| Fig. 4-16 Measured SNDR versus sampling frequency for one single ADC.                                    | . 60 |

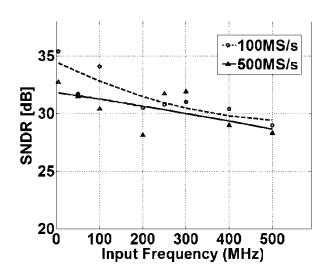

| Fig. 4-17 Measured SNDR versus input frequency for one single ADC                                        | . 60 |

| Fig. 4-18 Measured power spectrum and SNDR versus sampling frequency for interleaved ADC.                |      |

| Fig. 4-19 Measured power spectrum and SNDR versus input frequency for the interlea ADC.                  |      |

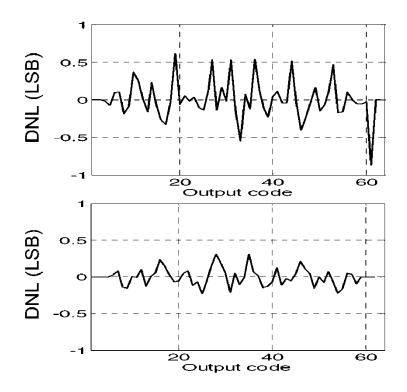

| Fig. 4-20 DNL before and after calibration.                                                              | . 62 |

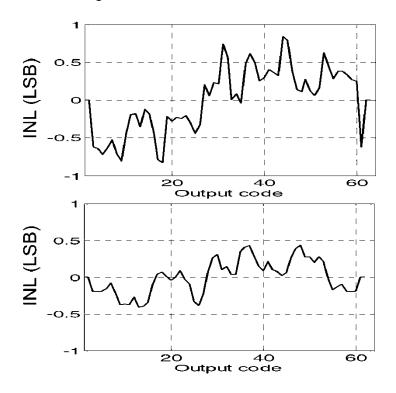

| Fig. 4-21 INL before and after calibration.                                                              | . 62 |

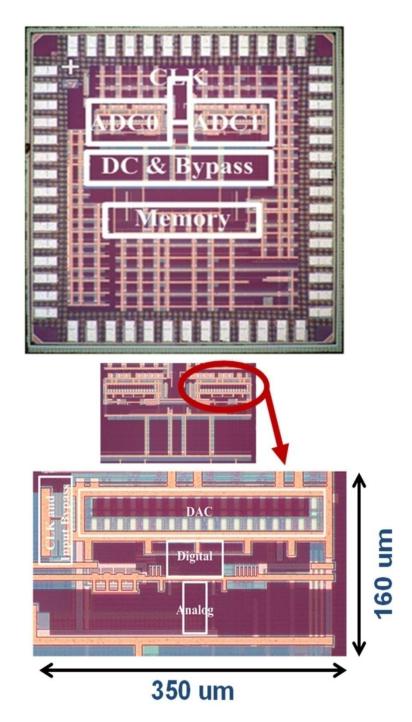

| Fig. 4-22 Chip micrograph.                                                                               | . 63 |

| Fig. 5-1 Conceptual diagram of a conventional gain stage using feedback approach                         | . 67 |

| Fig. 5-2 Open-loop gain stage for residue amplifier with digital correction.                             | . 67 |

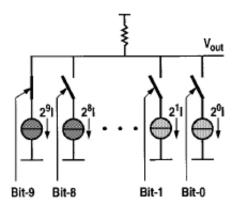

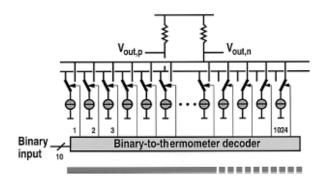

| Fig. 5-3 Binary Weighted DAC                                                                             | . 68 |

| Fig. 5-4 Thermometer-coded DAC                                                                           | . 69 |

| Fig. | 5-5 Block diagram of analog delay line                                                                                                          | 71 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. | 5-6 A first order all pass analog delay cell                                                                                                    | 72 |

| Fig. | 5-7 A second order all pass analog delay line.                                                                                                  | 72 |

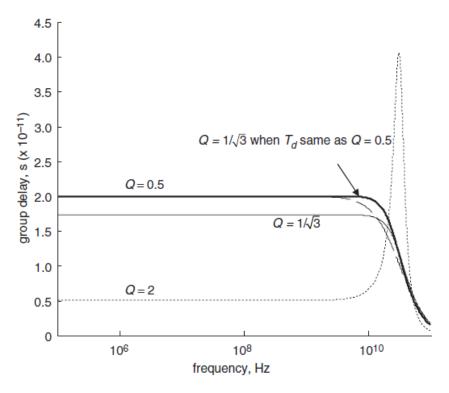

| Fig. | 5-8 Group delay of second order all pass analog delay line with different Q-factor                                                              | 73 |

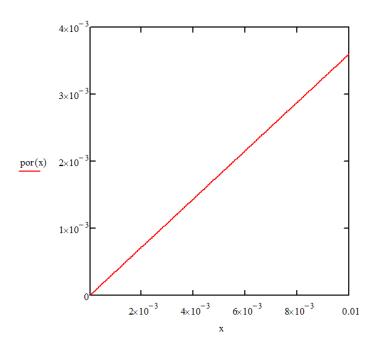

| Fig. | 5-9 Power vs. gm for first order system.                                                                                                        | 73 |

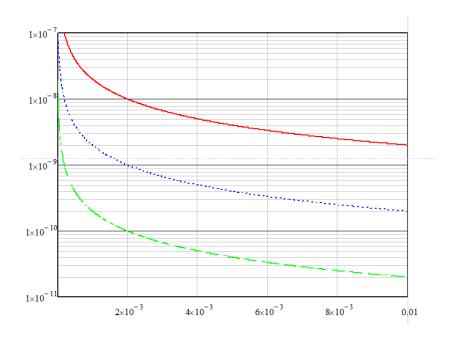

| Fig. | 5-10 Delay vs. gm for first order system given different capacitor values                                                                       | 74 |

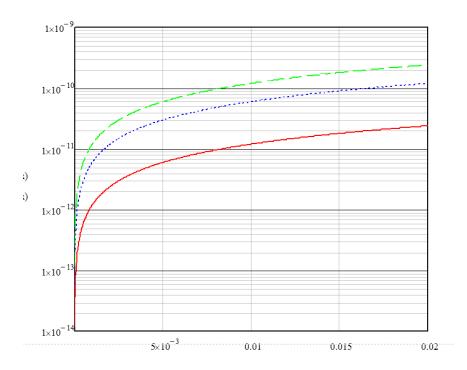

| Fig. | 5-11 Delay vs. gm for second order system given different inductor values                                                                       | 74 |

| Fig. | 5-12 -3dB bandwidth vs. gm for first order system given different capacitor values                                                              | 75 |

| Fig. | 5-13 -3dB bandwidth vs. gm for second order system given different inductor valu                                                                |    |

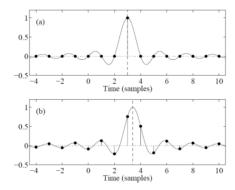

| Fig. | 5-14 Continuous time and sampled impulse response of the ideal fractional delay filt where the delay is $D = 3.0$ samples and $D = 3.4$ samples |    |

| Fig. | 5-15 System test bed interface with BEE2                                                                                                        | 77 |

| Fig. | 5-16 System Prototype for active interference cancellation                                                                                      | 78 |

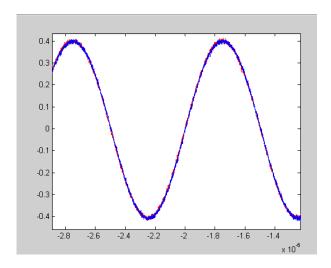

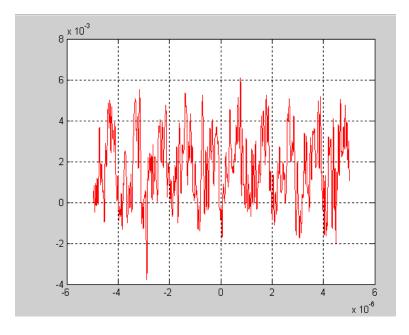

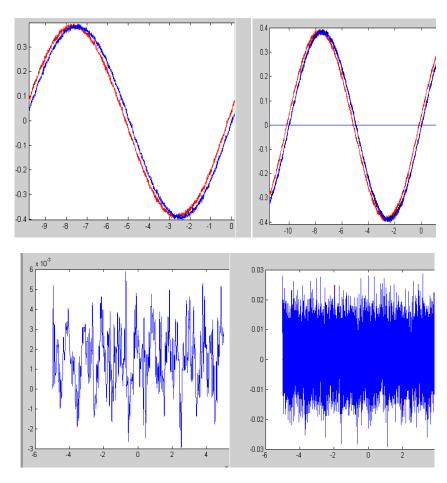

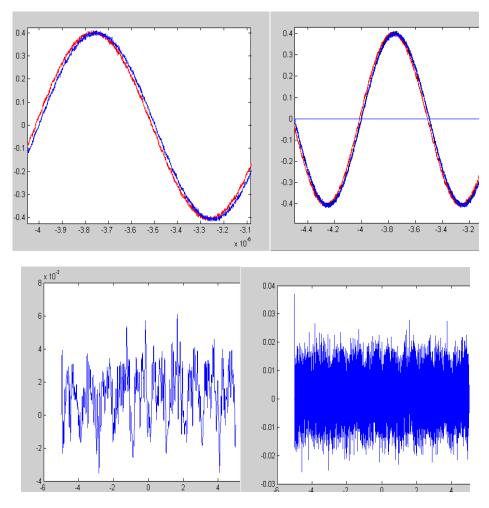

| Fig. | 5-17 Both interference and the desired signal are sine waves with SIR = -30dB                                                                   | 79 |

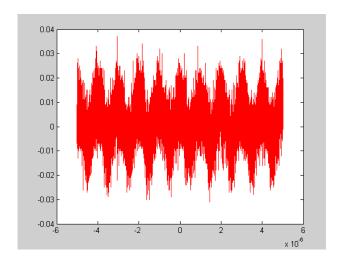

| Fig. | 5-18 Residue signal of the first stage after subtraction.                                                                                       | 79 |

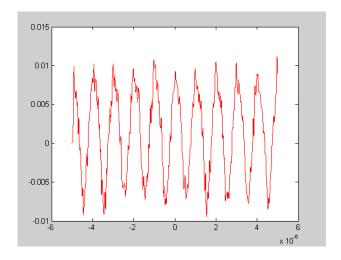

| Fig. | 5-19 Desired signal after filtering.                                                                                                            | 79 |

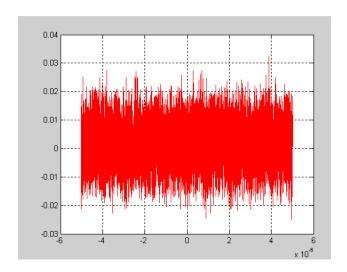

| Fig. | 5-20 Sinusoidal interference with a random-noise-like signal (SIR = -25dB)                                                                      | 80 |

| Fig. | 5-21 Interference estimation error from stage one.                                                                                              | 80 |

| Fig. | 5-22 Recovered CR signal after interference cancellation.                                                                                       | 81 |

| Fig. | 5-23 Estimation error and the recovered CR signal when delay are not match between two path.                                                    |    |

| Fig. | 5-24 The estimation error and the recovered CR signal when delay are better match between the cancellation path and the main path               |    |

## List of Tables

| Tab. 1-1 Usage percentage of spectrum in an urban area.                  | 3  |

|--------------------------------------------------------------------------|----|

| Tab. 2-1 Overall EBDR for different SIRs using different resolution ADCs | 25 |

| Tab. 2-2 System specification summary                                    | 25 |

| Tab. 4-1 Performance summary.                                            | 64 |

## Acknowledgements

This research was supported by the Circuit & System Solutions (C2S2), Berkeley Wireless Research Center (BWRC), and ST Microelectronics (ST). I would like to express my deepest thankfulness to my advisor Bob Brodersen from Electrical Engineering and Computer Sciences at University of California at Berkeley. He guided me into wireless communication and the low power integrated circuit design and provided almost unlimited resources and supports for the research. His tremendous guidance, feedback leads me to successfully finish my project. His personality impacts my whole life.

The author would like to thank professor Bora Nikolic, Jan Rabaey, Paul Gray, Ahmad Bahai from Department of Electrical Engineering and Computer Sciences, University of California at Berkeley for their guidance, discussion and work which help me understand more about the design methodology; professor David Tse from Wireless Foundation, Dr. Ada Poon from Stanford University for providing intensive discussion for the wireless applications; Mike Chen from Atheros for contributing great help on the analog to digital converter design.

The author would also like to appreciate many researchers and engineers from BWRC; more specifically, Thura Lin Naing for his great help with the chip tape-out and lab works, Louis Alarcon for his discussion on the chip design; Sue Mellers, Brian Richard and Fred Burghardt for their supports on the prototype board design of the system. Also, professors Phil Kaminsky from Industrial Engineering and Operation Research at University of California at Berkeley served on my qualifying committee and provided invaluable feedback for the dissertation writing process.

Finally, I would like to thank my family and friends here at Berkeley and Beijing, Shan Li, Wenting Zhou, Yue Liu, Yanmei Li, Yaping Li, Jianhui Zhang, Qingguo Liu, Haibo Zeng, Minghua Chen, Nate Pletcher, Ruth Wang, Brian Otis, Zhigang Yan, and those who loved me and who I loved, for their support and contributions in making my life in graduate school beautiful. Without their support, it will be extremely hard for me to smoothly get to this point. I'd like to owe all of my success here in Berkeley to my dear parents. The life in Berkeley will always be good memories.

## **Chapter 1**

### Introduction

#### 1.1 Motivation

#### 1.1.1 Concept of Cognitive Radio

Through the years, the Federal Communication Commission (FCC) managed the spectrum allocations on a request-by-request basis, usually specifying the applications (TV broadcast, phone service, public safety, etc.) and technology that a licensee could use in its sliver of spectrum. However in the past few years, the FCC has realized that there is a need for change. It basically had no more spectra to allocate, yet the demand for new uses—primarily data—was accelerating.

Action has been set aside to take a continuous 7 gigahertz (GHz) of spectrum between 57 and 64GHz for wireless communications. In addition to frequency re-use, 60GHz band has the unique characteristics that make possible many other benefits, including high-data rates, excellent immunity to interference (due to short transmission distance), narrow antenna beam width and limited use of 60GHz spectrum. Yet the applications in millimeter wave regime typically have severe power and cost constraints.

Fig. 1-1 FCC Allocation Chart. a) 300MHz to 1GHz. b) 1GHz to 3GHz. c) 3GHz to 6GHz.

Fig. 1-2 A snapshot of the spectrum utilization up to 6 GHz in an urban area [1].

In the frequency bands, especially at those that can be economically used for wireless communications (e.g. spectra below 6GHz), there still seems to be a crisis of spectrum availability from the FCC allocation map (Fig. 1-1). However, measurements have shown that much of the spectrum allocated over the years was being grossly underused as seen by the snapshot of spectrum usage in an urban area (Fig. 1-2).

In the figure, there is very little usage at the time, place and direction that this measurement was taken. Analysis of the snapshot in Fig. 1-2 reveals that the actual utilization in the 3-4 GHz frequency band is 0.25% and drops to 0.13% in the 4-5 GHz band. Even in the most crowded bands, such as below 2GHz, the utilization is less than 50% (Tab. 1-1).

| Frequency (Hz) | 0~1G | 1~2G | 2~3G | 3~4G | 4~5G  | 5~6G |

|----------------|------|------|------|------|-------|------|

| Percentage (%) | 54.4 | 35.1 | 7.6  | 0.25 | 0.128 | 4.6  |

Tab. 1-1 Usage percentage of spectrum in an urban area.

#### 1.1.1.1 Concept of Cognitive Radio

It is this discrepancy between FCC allocations and actual usage indicates that a new approach to spectrum licensing is needed. Extensions of the unlicensed usage to other spectral bands, while accommodating the present users who have legacy rights, are desired. With the explosive growth of the wireless services offered in the past few years, the demand for opportunistic sharing of the spectrum becomes stronger each day. With software defined radio a reality today, transition to the more intelligent or "cognitive" counterparts, which can give users the ability to adapt to the real time spectrum conditions, is not a very distant dream.

An approach, which can meet this goal, is to develop a radio that is able to sense the spectral environment over the wide available bands, use the spectrum and transmit only if communication does not interfere with licensed users [2]. According to Institute of Electrical and Electronic Engineers (IEEE), the cognitive radio is a radio transmitter/receiver that is designed to intelligently detect whether a particular segment of the radio spectrum is currently in use and to jump into (or out of) the temporarily-unused spectrum very rapidly without interfering with the transmissions of other existing users. These un-licensed low priority secondary users (SU) using Cognitive Radio (CR) techniques ensure non-interfering coexistence with higher priority users (PU) and thus reduce concerns of a general allocation to unlicensed use [3].

In the environment, where the SU co-existed with the PU, the CR transmitters would have to clear the corresponding band, giving priority to the licensed owner when licensed owner appears in a frequency band. There are two principle possibilities for a licensed owner to access spectrum [4]:

1. It searches for free frequencies within the licensed frequency range. The licensed owner has the right to reclaim frequencies from SU's who are operating within that band. This

- approach requires the licensed owner to be able to detect SU's and probably even to communicate with them. There is an underlying assumption that the licensed owner does not necessarily need to use of all the controlled spectra and is willing to share them under certain constraints.

- 2. In the second approach, the licensed owner has no knowledge about SU's. Consequently it just claims some frequency within its frequency band forcing a SU to change to other unoccupied frequencies.

Based on the first approach, a control channel could be established, using dedicated logical channels for the exchange of control and sensing information. There are two different kinds of envisioned logical control channels, a Universal Control Channel (UCC) and Group Control Channels (GCCs). The UCC is globally unique and has to be known to every CR a priori. Without the knowledge of that control channel, a CR has no communication possibilities. The main purpose of the UCC is to announce existing groups and enable newly arriving users to join a group. In addition to the UCC, each group has one logical GCC for the exchange of group control information. These control channels might be located in some licensed spectrum specifically reserved for this purpose, e.g. in one of the ISM bands or UWB (Ultra Wide Band) [2]. The control channels know information about the PU's as a prior, in term of frequency, modulation, power level and etc.

The second approach usually involves a more dedicated sensing mechanism for the SU's, which facilitates a prompt switching out of the licensed owner band. The control channel will therefore exchange the information between the transmitter and receiver of the SU's for the consecutive operation frequency, modulation, etc. when the PU claim its frequency back. This requires the SU to monitor multiple available frequencies or store information from multi-SU's to enable cooperative operation.

The design of the CR systems involves the mechanism of sensing, transmitting and receiving. The information sharing through the control channel, which is mentioned as a licensed spectrum, is to improve the overall CR throughput and reduce the interfering to the PU's.

#### 1.1.1.2 Uniqueness of Cognitive Radio Systems

To design the CR receiver, it is crucial to understand the special characteristics of the CR systems. First and most important, the sensing and transmission function of CR must be performed over the widest possible bandwidth to provide the maximum flexibility and to give the highest probability of detecting unused spectra. Yet more interfering signals will be present as the bandwidth of interest is extended. The possibility of facing more in-band interferes significantly increases. Due to these strong PU's, the dynamic range requirement of the receiver front-end increases dramatically.

The unique sensing function of Cognitive Radios therefore forces the receiver to provide wideband signal reception, from the antenna to the analog-to-digital converter (ADC) which requires a GHz sample rate if GHz bandwidths are to be exploited.

The new challenges of Cognitive Radios put a stringent requirement on RF sensitivity for received signals and the ability to detect different desired signal types and power levels. Measurements have been taken using a directional antenna (TEM horn) at multiple typical environments (Fig. 1-3, Fig. 1-4, Fig. 1-5). It is observed that, at the CR receivers, even when it is only desired to detect the CR signals at a power level that is a few dB, e.g. with SNR = 10dB, above the noise floor (-158dB/Hz @ 300K), the interference created by the PU's yields signal to interference (SIR) ratios ranging downwards to -70dB. This results in a large dynamic range requirement for the front-ends circuitry and in particular for the ADC which must accommodate the large interfering signals while still provides sufficient quantization performance for the weak CR signals.

Though the interfering signals are in-band, they are not desired. The wideband sensing needs a multi-GHz speed ADC, which together with a high resolution requirement (of 12-bit or more) might make the design infeasible. Therefore, reducing the strong in-band PU signals, which are of no interest to detect, is necessary and important to receive and process the weak signals.

Fig. 1-3 Dirty Maps of indoor interference at positions with equal probability of inside and outside interferers.

Fig. 1-4 Dirty Maps of interference next to a wireless LAN transmitter.

Fig. 1-5 Dirty maps of interference in a lab station.

#### 1.1.2 Future Wideband Radio Systems

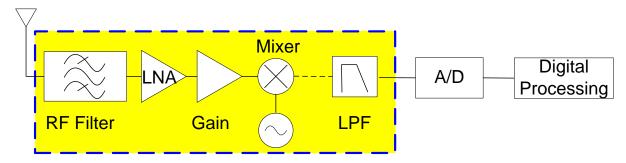

Traditional radio front-end includes multiple analog components. For instance, the receiver generally has a bandpass RF-filter, low noise amplifier (LNA), gain stage, mixer, low pass filter (LPF) and the ADC (Fig. 1-6). The received signal preserves in the presence of analog waveform, until it is been converted by the ADC into digital format.

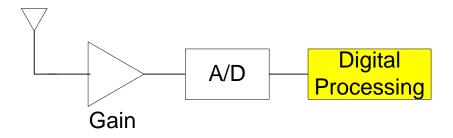

With the technology scaling into ultra-deep-submicron, the cost of the digital logic is significantly lowered, and there is a great incentive to implement high-volume baseband signal processing in the most advanced process technology available. Concurrently, observed that the scaling adversely affects most other parameters relevant to analog designs, there is more incentive to move the lion's share of processing from analog to digital to avoid the difficulties in analog design and achieve the lower-power enhanced-flexibility goal for the wireless systems.

Eventually, an alternative structure needs to be provided that contains fewer portions of analog front-end components (Fig. 1-7). Majority of the filtering, amplification etc. are to be implemented with the lower cost digital circuits. However, achieving high linearity, high sampling speed, high dynamic range, with low supply voltages and low power dissipation in the scaled CMOS technology becomes a major challenge for the ADC's.

Fig. 1-6 Traditional radio front-end.

Fig. 1-7 Conceptual illustration for future radio front-end.

#### 1.2 Approaches for Interference Cancellation

The key problem is how to enhance the dynamic range achievable by the mixed-signal circuits. For high-resolution converters, this inevitably leads to an increase of power consumption to maintain SNR that is set by the non-desirable interferes.

Our approach to resolve the high speed, high dynamic range problem for the CR receiver and future radio system involves active cancellation, because in the situation in which the dynamic range is high (interfering signal is extremely strong), it is possible to provide an active-cancelling signal before the A/D conversion process.

There is an interesting analogy between our approach and the information theoretic analysis of the interference channel [5]. It has been shown that very strong interference is almost innocuous as no interference at all. This comes from the fact that if the interfering signal has a high signal to noise ratio compared to the signal of interest, it can be accurately reconstructed, even treating the signal of interest as noise, and then subtracted off [6].

There are sufficient works to mitigate interference using sophisticated digital processing. But for the challenge presented in Section 1.1, it is obvious that all the interference cancellation are required and limited to be implemented in analog domain, because the signal hasn't been quantized by and converted by ADC yet.

#### 1.2.1 Frequency Domain Cancellation

By more aggressively reusing frequencies within a cluster of radio coverage cells, system operators increase the aggregate number of users that can be supported but such gains come at the expense of increased mutual interference between users, e.g. increased co-channel and adjacent channel interference between users.

As such, adequate cancellation of interference poses challenges for the interference canceling receiver. Because the conventional approaches to interference cancellation, suppression, etc., are based on frequency filters that creates large amount of attenuation over the specified band of frequencies, reducing the unwanted interference to a tolerable level while passing the desired frequency range with minimum attenuation.

High Q factor, wide tuning range (~GHz), fast tuning filter designs (Fig. 1-8) require either high power consumption filter banks, or MEMS designs [7] that are much less flexible.

#### 1.2.2 Spatial Domain Cancellation

Acceptable communication receiver performance depends on more than just the ability to adequately suppress adjacent channel interference. Other phenomena (such as time-varying

Fig. 1-8 Frequency notch filter approach for interference cancellation.

multi-path fading) complicate wireless communications and require special operations to ensure suitable receiver performance. Such operations typically include channel estimation and, particularly with widely dispersive communication channels, signal equalization. Some recent approaches to these signal processing operations are based on antenna array beamforming that senses the parameter of the interference, such as frequency, modulation, power spectrum density, etc. and generates a sharp spatial notch filter at the direction where the interferer is coming (Fig. 1-9). These approaches, however, are complicated. Phase shifter or digital calibration solutions are always involved [8], so as to compensate the non-reciprocity of the antenna array. Therefore, it could fundamentally be expensive. The cancellation performance is limited by the coherence time of the channel with respect to the responding time of the dynamically programmed antenna array. The performance of such operations may be complex and exceed the budget of a low power front-end, for instance, when a fast-changing channel is the dominant cause of a received signal disturbance.

Fig. 1-9 Spatial notch filter approach to reduce the interference of 30dB and 40dB from two directions.

#### 1.2.3 Time Domain Cancellation

The proposed cancellation scheme in Chapter 2, relates to wideband wireless communication systems. Particular focus on the dynamic range enhancement at the receiver is achieved by blind cancellation of strong narrowband interference from a received signal. Interference in the received signal is estimated using a correlation model matched to a few dominant sources of interference at the receiver. Such estimates may also be used to improve channel estimation, signal equalization, or both.

Our proposed RF architecture with digitally-assisted active cancellation through an adaptive linear prediction filter and reconstruction digital-to-analog converter (DAC) operates at high speed, but consumes little power. The key challenge in this approach is to perform analog subtraction with stringent timing constraints. While the active cancellation approach will consume significantly more hardware because of added digital circuitry and is very susceptible to distortions, it offers more flexibility through digital processing.

The mixed analog digital architecture will be illustrated in Chapter 2. Detail of the digital processing adaptive algorithm in the interference cancellation system is described in Chapter 3. A high speed, medium resolution, high performance analog-to-digital converter design is implemented to support the cancellation system. The design methodology and performance will be discussed in Chapter 4. Finally, in Chapter 5, we establish a proof-of-concept prototype to demonstrate the proposed time domain interference cancellation architecture, followed by the conclusions in Chapter 6.

### Chapter 2

# Time domain Interference Cancellation Architecture

As we have seen in the previous chapter, the actual utilization in the 3~4 GHz band is 0.25%, and drops to 0.13% for 4~5 GHz and does not exceed 5% in 5~6GHz. While all the bands have allocations, it is clear from the FCC map that the allocations are not all being utilized. The Cognitive Radio (CR) approach is to treat these allocated users as PU. To provide the maximum flexibility, this sensing and transmission function is performed over the wideband to give the highest probability of detecting unused spectra.

The unique sensing function of Cognitive Radios and the trend for future wireless system force wideband reception at the receiver. Furthermore, it is desirable to detect the weak signal in the presence of much stronger primary interference (low SIR environments). This results in a large dynamic range requirement for the front-end circuitry and in particular for the ADC which must accommodate the large interfering signals while still provides sufficient sensitivity for the CR signal.

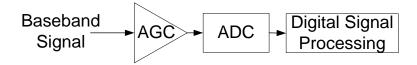

a). Typical baseband radio system.

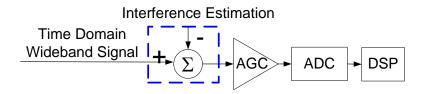

b). An approach to time domain interference cancellation.

Fig. 2-1 Time domain interference cancellation approach.

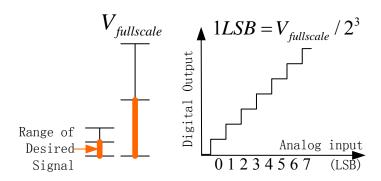

Fig. 2-1a) represents a typical radio system. The automatic gain control (AGC) is designed to present a full scale signal in front of the signal path ADC, so that all bits of the ADC are utilized. However, because the interfering signal is strong, the gain is limited and the CR signal cannot be amplified enough to achieve sufficient quantization accuracy. For example, to achieve a 20dB signal to quantization noise ratio, the required resolution of the ADC would be on the order of 12 bits or greater if there is an SIR of -50dB. This level of accuracy, with GHz sample rate results in an infeasible ADC implementation, under power and cost constraints [9].

To reduce the interfering signals to a level that doesn't result in such difficult dynamic range requirements, we have investigated interference mitigation in the time domain. If we can estimate the interference signal and simply subtract it off from the main signal path on a sample by sample basis (Fig. 2-1 b), we can eliminate the large interfering signals and thus reduce the signal path ADC dynamic range requirements to the level needed for simply decoding the desired signal (e.g., the 20*dB* level in the example mentioned previously).

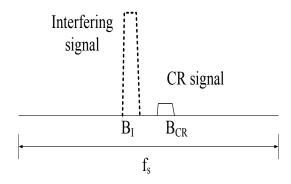

Fig. 2-2 The interfering and CR signal features.

To be able to estimate the interference and separate it out from the signal of interest, there must be some features that distinguish the desired signal from the interference. CR system will be used to illustrate the idea. We exploit two such distinguishing features, summarized in Fig. 2-2. First, we assume the interference is significantly stronger than the desired signal. This allows us to estimate the interference accurately by directly quantizing the wideband signal, with little error caused by the presence of the weak CR signal. Second, we assume that most of the power of the desired signal is outside the bandwidth of the interference. This allows us to filter away the desired signal from our estimate of the interference before subtracting it from the original signal, so that we are left with only the CR signal.

Measurements indicate most of the strong in-band interference can be treated as narrow band with respect to the GHz bandwidth that is focused. Therefore, due to the high over sampling ratio of interfering signal, there exists a high correlation between samples. This correlation provides us with a further gain in estimating the strong interference without actually decoding it.

Section 2.1 develops the mixed signal architecture for a time domain cancellation system and discusses the critical analog design issues including the delay element and mixed signal design requirements. Cancellation digital processing techniques are illustrated and explained in Section 2.2. In Section 2.3, the proposed system is evaluated through simulation under different environments, and results show the effectiveness of the dynamic range reduction and feasibility of circuitry implementation.

#### 2.1 Mixed Signal Architecture

The design of the ADC presents the biggest challenge in a wideband receiver of CR and future radio systems. As an example, let us consider use of a 1 GHz band for the detection of unused spectra. The ADC speed requirements are minimized if the signal is mixed to baseband, resulting in a 500MHz baseband bandwidth. Without assistance from the digital circuits and change in receiver architecture, the analog to digital conversion of such a wideband signal introduces unacceptable system complexity and power consumption.

In this section, two proposed mixed signal architecture will be discussed, the feedforward architecture and the feedback architecture. The former one composes a main signal path and an interfering signal estimate path, operating in an open loop. The latter one executes the estimation of the strong interference in a closed-loop manner, providing much accurate estimates, yet resulting in a requirement of more sophisticated algorithm and extra issues of stability.

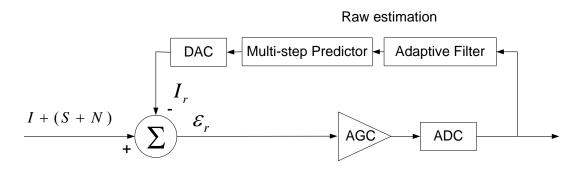

#### 2.1.1 Feedback Architecture

Block diagram in Fig. 2-3 shows the feedback architecture front-end design for active cancellation of interferers. The purpose of the loop is to subtract the interference signal, *I*, caused by the strong (undesired) interference. The feedback path (consisting of the adaptive filter,

predictor, and DAC) extracts the interfering signals for feedback cancellation. Because the ADC, DAC, and adaptive filter each has intrinsic delay, a multistep predictor is needed in order to compensate for this delay. Upon loop convergence, the cancellation signal  $(I_r)$  roughly approximates the incoming interference (I), so that the dynamic range of the residue signal  $(\varepsilon_r)$  is dramatically reduced, enabling the detection of the weak CR signal S. The interfering signals are quantized and extracted to provide an estimate which is used for subtraction.

At initialization,  $I_r = 0$ ,  $\varepsilon_r = I + (S + N)$ , where N is the thermal noise at the front-end. The estimation error,  $\varepsilon_r$ , is dominated by the interference. It is quantized through the high speed low resolution ADC in the loop. The AGC amplifies the error signal such that the full range of the converter could be used. The linear adaptive filter extracts the ADC output to provide a raw estimation, which is further reconstructed by the DAC as  $I_r$ . The estimation of the interference,  $I_r$ , is improved throughout the loop. The accuracy replies on the complexity of the algorithm, and the capability of recovering interference from its subtraction residue. A few samples for training purpose are required.

There are several challenges in this feedback approach. Firstly, the adaptive filter used to regenerate the interference has a time-varying input signal and its estimation accuracy is affected by noise, quantization, prediction errors and speed, therefore limits the performance of the interference cancellation. Secondly, since this is a closed-loop structure, it is difficult to guarantee its stability because of the phase shift accumulation along the loop. Last but not least, the key challenge in this approach is to perform analog subtraction in a closed loop with stringent timing constraints.

Fig. 2-3 Feedback architecture for time domain interference cancellation.

Fig. 2-4 Feedforward architecture for time domain interference cancellation.

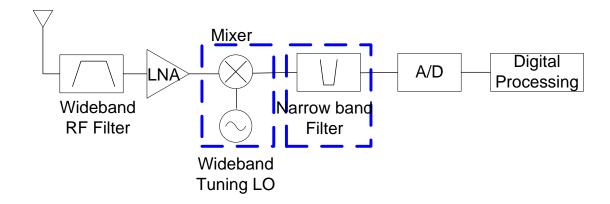

#### 2.1.2 Feedforward Architecture

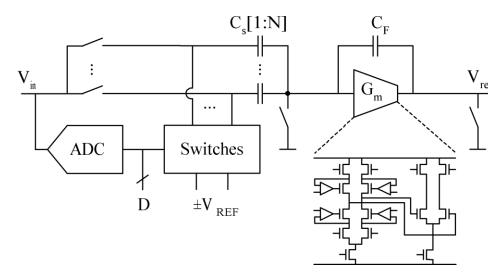

To overcome the limitations of the feedback architecture, alternative feedforward architecture is proposed. Fig. 2-4 illustrates the proposed feedforward radio front-end architecture for active cancellation of strong interferers. An estimation of the interference is created in the cancellation path to be used for subtraction of the strong interference and thus reduces the dynamic range requirements of the ADC in the signal path (the Residue ADC).

We consider an input signal composed of the CR signal of interest, strong in-band interference and thermal noise. The input signal branches into two paths, one of which immediately quantizes through a high speed low resolution ADC (the Cancellation ADC). The active interference cancellation is achieved through the use of an adaptive linear filter and reconstruction DAC in the cancellation path. There might be a notch filter involved in the cancellation path. The purpose is to remove the desired cognitive radio signal from the interference for improved estimation, and to avoid unwanted cancellation/distortion of the desired signals. Since the ADC, digital signal processing (DSP) block and DAC involve a processing delay, t, this same delay must be added to the main signal path to align the signals in the two branches for proper cancellation. The noise level added through the delay line should be sufficiently below the CR signal level to retain high sensitivity for detection.

The whole system can be regarded as a selective AGC which amplifies the CR signal, but not interfering signals. This technique allows two low-resolution ADCs with N and M bits to substitute for a single high-resolution ADC of greater than N+M bits.

The system is composed of two basic mixed signal stages (Fig. 2-4). Stage one involves the interference subtraction, with its output (residue signal) including the CR signal, the cancellation error and noise. Stage two then amplifies this residue to full scale of the Residue ADC, and performs additional digital filtering to pass only the CR signal.

The tradeoff between the number of bits in the cancellation ADC and residue ADC depends on the interference strength, that is, strong interference situations require more bits in cancellation ADC, as will be discussed in Section 2.3.2. While the timing constraints of the feedback loop are avoided by this architecture, it still requires matching of the latency through the two paths using an analog delay line. The challenge of analog delay line is avoided by using a combination of multi-step digital prediction in the cancellation path and a fractional delay through a continuous analog delay line, as will be discussed in Chapter 5.

#### 2.2 Cancellation Digital Processing

The digital signal processing in the cancellation path are required to estimate the interfering signals, while ignoring the desired signal, so that the CR signal is not subtracted off along with the interfering signals.

After the signal is quantized by the relatively low *N*-bit resolution Cancellation ADC, a white quantization noise will be added. As mentioned before, since it is assumed that the interfering signals are narrow band signals, a high oversampling ratio of the interfering signal can be exploited in the estimation.

The more accurately the interfering signal can be estimated, the more effectively can it be cancelled and hence the larger gain could be in the AGC before saturation will occur in the following Residue ADC. The goal is to be able to amplify the desired signal to full scale of the ADC so that the full *M*-bits of the Residue ADC will be available for quantizing the residue signal from the previous stage.

To measure the estimation accuracy, the time domain sample-by-sample difference between the interfering signal and its estimation needs to be tracked. We use the mean squared error (MSE) to estimate the power level attenuation achieved by cancelling the strong interference and reducing the in-band noise.

#### 2.2.1 Dual Adaptive Filter (AF)

To estimate the interfering signal, we use a two stage adaptive filter process [10]. The first stage uses the time varying behavior of the normalized least mean square (NLMS) adaptive filter with a large step size to produce a frequency locked estimation of the interference. The second stage uses NLMS with a small step size as an approximation to the ideal Wiener filter [11] to correct the phase and magnitude of the output from the first stage and produce an interference estimate suitable for cancellation. Details of the adaptive filter approach of the interference cancellation will be discussed in Section 3.2.

Here, two key points are to be noted:

- 1) The first adaptive filter uses a large step size. It enables us to track the time-varying interferer by rapidly adapting to any changes in the interfering signal, such as occurred with data modulation; The second adaptive filter operates more conventionally using a small step size to ensure that the passing band of that filter around the interference frequency is narrow enough to provide the least possible distortion to our CR signal and minimum filtered quantization noise.

- 2) Sampling at high speed yields a high oversampling ratio relative to the narrowband interferer, which results in more correlation between samples and therefore better estimation.

#### 2.2.2 Processing Gain and Interference Attenuation

The high oversampling ratio not only brings the advantage of high correlation between samples, but also allows the implementation of a relatively narrow band pass filter created by the dual AF. It is therefore possible to achieve extra processing gain by filtering out the quantization

Fig. 2-5 The system architecture and MSEs interested in the cancellation.

noise outside of the interference band, which would contribute significant power to the residue after the subtraction of the interfering signal.

We also achieve additional processing gain when the CR signal is narrow band. By using a very narrow band digital filter around the center frequency of the CR signal, the quantization error from the Residue ADC can be significantly reduced by the following digital bandpass filter.

In the following analysis, we measure the processing gain and the interference attenuation by computing the MSE throughout the receiver signal path (Fig. 2-5).

Without loss of generality, we assume the power level of a single existing in-band interference to be  $P_I$ , and that of CR signal to be  $P_{CR}$ . Both are assumed to have a flat spectrum over their own signal bands with  $P_I >> P_{CR}$  (Fig. 2-2). The bandwidth of interest is  $f_s$ , which is assumed to be wide compared to the interfering and the CR signals. The overlap bandwidth between the interfering signal and CR signal is  $B_{OL}$ , with  $B_I$  and  $B_{CR}$  the bandwidths of interfering and CR signals respectively. We assume  $B_{OL} << B_{CR}$  so that most of the energy of the CR signal is outside the bandwidth of the interferer.

In contrast to ADC's, power efficient, high-resolution, and high-speed DAC's are significantly easier to implement [12]. Thus, we assume the DAC's resolution is sufficiently high that no quantization noise is added by the DAC in the cancellation path.

MSE will be dominated by quantization of the interfering signal, which in the case of an *N*-bit low resolution ADC is approximately,

$$MSE_1 = P_I \cdot 2^{-2N} \tag{2.1}$$

When there is little overlap between the interfering signal and the CR signal, namely,  $B_{OL} \ll B_{CR}$ , the dual AF will ideally have a transfer function which is narrow enough to pass only the interfering signals. The stop band attenuation is assumed sufficiently large that the quantization noise outside of the interference band and the CR signal would then be absent from the filtered interference estimation. After reconstruction by DAC, the MSE will be reduced to the following:

$$MSE_2 = MSE_1 \cdot \frac{B_I}{f_s} = P_I \cdot 2^{-2N} \cdot \frac{B_I}{f_s}$$

(2.2)

The thermal noise added by the high resolution delay line element in the main path is significantly below the CR signal level. After subtracting the interference estimate from the

delayed main signal, the residue becomes the CR plus the error in estimating the interference. This residue has the power of  $MSE_2 + P_{CR}$ .

By exploiting the AGC to amplify the residue up to the full scale of the Residue ADC, this low resolution converter would produce an MSE equal to:

$$MSE_3 = (MSE_2 + P_{CR}) \cdot 2^{-2M}$$

(2.3)

After stage one, a sharp narrow band digital filter could be applied to pass only the CR signal band, so that final MSE becomes:

$$MSE_4 = MSE_3 \cdot \frac{B_{CR}}{f_s} \tag{2.4}$$

Substituting (2.2) and (2.3) into (2.4), we get

$$MSE_{4} = (P_{I} \cdot 2^{-2N} \cdot \frac{B_{I}}{f_{s}} + P_{CR}) \cdot 2^{-2M} \cdot \frac{B_{CR}}{f_{s}}$$

$$= P_{I} \cdot 2^{-2(N+M)} \cdot \frac{B_{I} \cdot B_{CR}}{f_{s}^{2}} + P_{CR} \cdot 2^{-2M} \cdot \frac{B_{CR}}{f_{s}}$$

(2.5)

Clearly, it can be seem that the equivalent resolution of interfering signal could eventually become more than N + M bits and there is a processing gain of the product of two oversampling ratios. Furthermore, almost the full resolution of the Residue ADC can be used for subsequent processing of the CR signal.

For comparison, without interference cancellation, a single ADC would lead to an MSE of

$$MSE_{BL} = (P_I + P_{CR}) \cdot 2^{-2M} \cdot \frac{B_{CR}}{f_s}$$

(2.6)

with quantization noise of strong interference dominates. Our approach indicates that it is possible to reduce the interference further by a factor of  $2^{2N} \cdot f_s / B_I$ , so that the MSE caused by interference would be on the order of the quantization noise of the CR signal. Thus, the total MSE is very well reduced.

In an actual implementation, due to the estimation error and limitation of number of taps used in the dual AF, the imperfectness of the digital filter, and the AGC clipping or limited amplification of the residue, the MSE attenuation determined above presents an upper limit.

#### 2.2.3 CR Signal Protection

The requirement to protect the CR signal is of great importance. In our approach, when the CR signal is buried in the quantization noise, the dual AF is less sensitive to it. When it becomes relatively strong, such as in an environment with medium to low interference (ISR below 30dB),

it is no longer possible to distinguish the interfering and the CR signal through magnitude. Although dynamic range is not problematic in those situations, suitable measures have to be taken to protect the CR signal to avoid any distortion due to adaptation to the desired signal on the cancellation path.

One possible method is to use the pre-knowledge from the control channel that includes the possible band(s) of the desired signal, the features, include but not limited to, energy, signal footprint, such as modulation type, symbol rate, and overlapping in power spectrum density [13]. Therefore, digital notch filter in the cancellation path could be added that is aware of the transmitting band of CR. In addition to that, when ISR is below 0dB, it can be seen that the receiver dynamic range is determined by the CR signal. Therefore no interference cancellation is necessary. A pre-knowledge of the power spectrum density of the CR signal, used together with the output from the adaptive filter on the cancellation path, provides an option to turn off the first stage.

Among other degrees of freedom available, spatial domain beamforming [14] can create a notch at the direction that the CR signal is coming. Thus prevents the appearance of the desired signal in the subtractor.

Large stop band attenuation design leads to long delay in digital filters, and is power consuming. To avoid that, a more efficient way could explore a possible solution from a system design perspective. Instead of utilizing a narrow spectrum, when primary user allows for low power spectrum density interferer, it is applicable to choose the transmit CR signal modulation which codes the signal as random noise over a wide bandwidth, such as CDMA, so that dual AF will have no difficulty in ignoring the signal of interest. A demonstration of such modulation will be shown in Chapter 5, which significantly reduces the estimation error of the adaptive filter without extra effort of designing the digital CR-signal-notch filter, thus avoid any extended delay through the main path.

#### 2.3 Performance Evaluation and System Design Specification

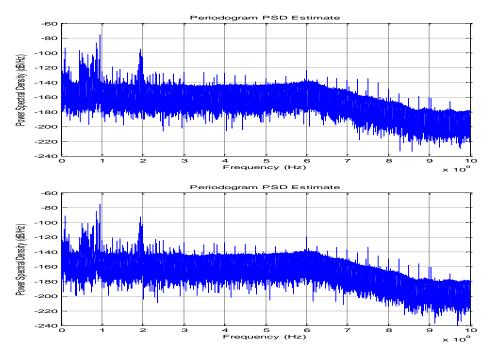

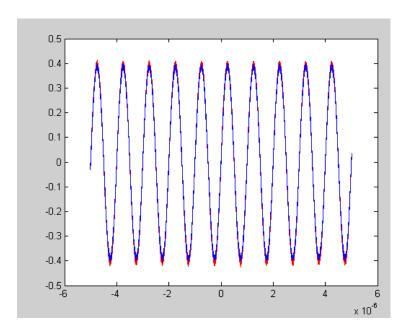

First, we inspect our proposed system by receiving a strong FSK modulated interfering signal and a FSK modulated CR signal. The Simulink model is built as shown in Fig. 2-6. The narrow band FSK signal has strong correlation between samples, which facilitates accurate estimation. FSK modulation inherently has time-varying characteristic, which could display the dynamic behavior of the CR signal. Fig. 2-7 are simulation results which verify the advantage of dynamic range reduction.

By using a 5-bit Cancellation ADC, a first stage 10-tap 1.0 stepsize together with a second stage 10-tap 0.01 stepsize dual AF, an 8-bit resolution DAC, with an appropriate delay for the analog subtraction, we can attenuate the strong interference and reduce the dynamic range to the Residue ADC by almost 35dB, thus extending the effective number of bits for this system by nearly 6 bits.

Fig. 2-6 Simulation Setup for the proposed time domain interference cancellation

a). An incoming of multiple interfering signals (a moderate sinusoidal interferer, a strong FSK modulated interferer) and an FSK modulated CR signal.

b). The power spectrum after interference cancellation with strong interfering signal been attenuated by almost 35*dB* when using 5 bits for the Cancellation ADC and 4 bits for the Residue ADC.

Fig. 2-7 Simulation showing interference attenuation using the cancellation approach.

#### 2.3.1 SINR after Attenuation

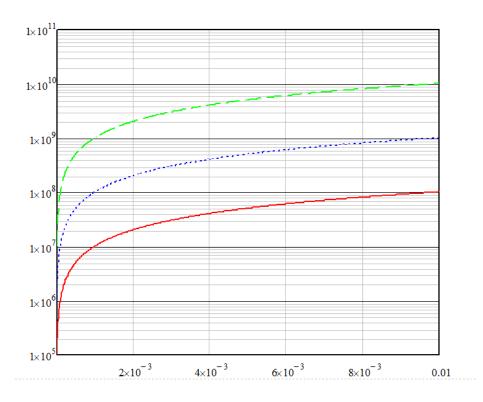

The relationship between attenuated signal to interference ratio (SINR) and number of bits used in the Cancellation ADC is investigated in different environments, i.e. different CR signal to interference signal ratio (SIR). Fig. 2-8 presents, for a single 1MHz wide interfering signal, the SINR improvement as we increase the resolution of the ADC.

The curves' slope in Fig. 2-8 indicates that the incremental of SINR is 39dB when ADC resolution increases by 4 bits, which is 9.75dB per bit of the Cancellation ADC. This is more than a conventional ADC, in which each additional bit gives an SNR improvement of 6dB. The extra 3.75dB comes from the improved ability of the adaptive filter to reject quantization noise as resolution of the Cancellation ADC increases.

This is mainly due to the fact that we are only using 10 taps for the dual AF. The adaptability is limited when resolution of the Cancellation ADC is low, since the passing band bandwidth is relatively wider than that of the interfering signal. As a result, the quantization noise after the subtraction contributes comparably to the error in interference cancellation in the SINR. The more bits the Cancellation ADC has, the more gain we get by exponentially decreasing the in band noise.

The processing gain from oversampling is evident when the slope becomes 6dB/bit, thus, interference error dominates the denominator of the SINR. As an example, when SIR is -30dB, a 6-bit ADC results in a SINR after cancellation of 26dB. The interfering signal has been attenuated by 56dB, which is equivalent to 9.3 bits; the extra 3.3 bits come from the oversampling ratio as a result of the processing gain as explained in Section 2.2. This gain is less than the theoretical gain (oversampling ratio of 500 implies 4.5bits of additional gain). This is mainly because we cannot form a brick-wall filter that strictly passes only the interfering signal, and therefore leads to a decreased attenuation.

Fig. 2-8 SINR greatly improved using low resolution ADC in difference environments.

Another observation is for a given SIR, less resolution in the Cancellation ADC actually simplifies the design. Because, even without filtering, the dual AF is insensitive to the CR signal that are buried under the quantization noise.

As we increase the number of bits, we will finally reach a point where additional bits do not bring any benefits without active reduction of the CR signal in the cancellation path. For instance, when the Cancellation ADC has 6 bits, in an environment with an SIR of -20dB, if we calculate the slope of the curve, the attenuation rate drops to less than 6dB/bit. This comes from the dual AF which begins to consider the desirable CR signal as interference, since we are doing a blind adaptation.

#### 2.3.2 Residue Signal Analysis

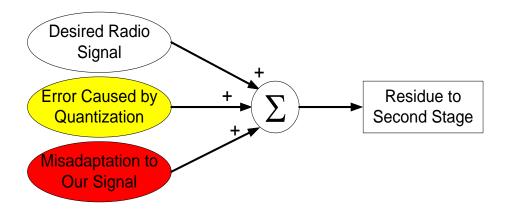

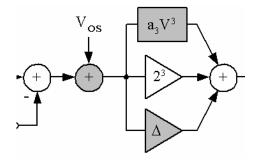

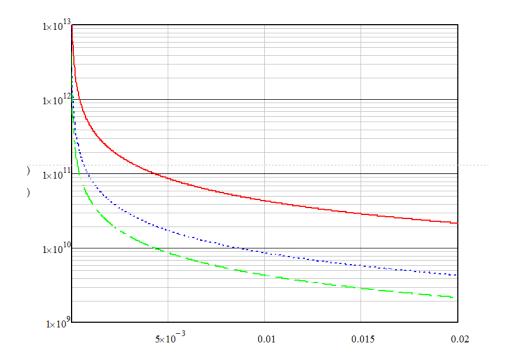

We calculate the residue signal at the input to the AGC of the second stage which includes the CR signal, the cancellation error of the interference and the filtered quantization noise (Fig. 2-9). The resolution for the desired CR signal is determined by the second stage, mainly, the effective gain provided by the gain stage.

#### 2.3.2.1 Ratio of Signal Peak to Residue Peak

The AGC is assumed to amplify this composite signal to full scale of the Residue ADC, indicating that the CR component will still be less than full scale (Fig. 2-10). This fraction will depend on the time domain peak magnitude ratio between the CR signal and the residue as in Fig. 2-11. If the ratio becomes less than one, it will result in a loss of effective bits from the Residue ADC for the CR signal.

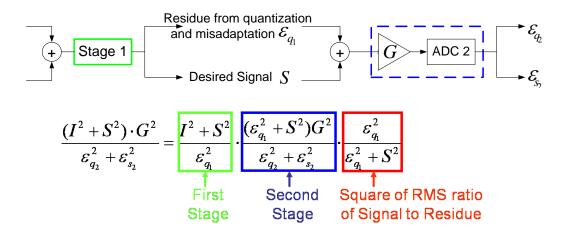

Fig. 2-9 Residue signal break down of the first stage.

Fig. 2-10 Amplification of the residue signal from the first stage.

Fig. 2-11 Time domain peak ratio of the CR signal to the Residue.

We are expecting that as the CR signal becomes weaker, more bits in the Cancellation ADC should be used to attenuate the interference signals. At the same time, this leads to a reasonable peak magnitude ratio for limiting the requirement of the Residue ADC to keep maximum detection sensitivity.

#### 2.3.2.2 Residue Power Analysis

To analyze the sensitivity of the system, we will calculate the input signal to system output noise ratio as is explained Fig. 2-12. The first term depicts the equivalent resolution through the Cancellation ADC and the adaptation. The second term is the effective resolution through the Residue ADC determined by the gain provided from stage two. The third term is dominated by the percentage of RMS of the desired signal power in the total power of the residue.

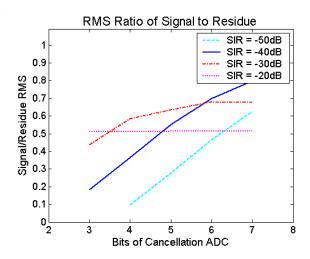

For different environments, this RMS ratio, as plotted in Fig. 2-13 sets a maximum number of bits we want to assign to the Cancellation ADC. The achievable improvement saturates as the Cancellation ADC resolution increases, which indicates overdesign of the converter. To avoid extra power consumption, it is desirable to reduces the Cancellation ADC resolution *N* in high SIR environments.

Fig. 2-12 Residue power analysis.

Fig. 2-13 RMS Ratio of signal to Residue versus Bits of Cancellation ADC

#### 2.3.3 Overall EBDR for Different SIR

By combining two stages, our simulation shows the overall system Effective Bits from the Dynamic Range Reduction (EBDR) is close to N + M, as shown in Tab. 2-1, if the gain of the AGC is set equal to  $2^N$ . Optimizing the resolution in the Cancellation ADC can avoid complex design of the CR signal protection by ensuring that the AF is not able to track that signal.

Also, we observed from the simulation, when using the FSK modulation for the interference, as the frequency of the interfering signal is modulated, there is a transient edge effect at the symbol boundaries. At these random transitions, there will be large error peaks. Therefore the gain of the second stage AGC may be limited by these spikes. If they can be made sufficiently short in duration by fast adaptation of the AF, then it may be possible to simply clip them without significant distortion of the CR signal.

A summary of specifications for a system implemented is given in Tab. 2-2, which uses 6 bits in the Residue ADC in order to accommodate the peak magnitude ratio drop due to spikes and clipping, while providing a worst case effective resolution of 3 bits for the CR signal, which is good enough for most communication systems. The table is based on simulation results with an OSR of at least 50.

Tab. 2-1 Overall EBDR for different SIRs using different resolution ADCs

| SIR = -40dB |

|-------------|

|-------------|

| ADC resolution                    |                         |                      |  |  |

|-----------------------------------|-------------------------|----------------------|--|--|

| Cancellation ADC + Residue<br>ADC | Without Notch<br>Filter | With<br>Notch Filter |  |  |

| 3bits+4bits                       | 8                       | 7.9                  |  |  |

| 4bits+4bits                       | 9                       | 8.8                  |  |  |

| 5bits+4bits                       | 9.9                     | 9.4                  |  |  |

| 7bits+4bits                       | 10.2                    | 9.8                  |  |  |

| SIR=-50dB                         |                         |                      |  |  |

| ADC resolution                    |                         |                      |  |  |

|                                   | Without Notch           |                      |  |  |

| Cancellation ADC + Residue<br>ADC |                         | With<br>Notch Filter |  |  |

|                                   |                         |                      |  |  |

| ADC                               | Filter                  | Notch Filter         |  |  |

Tab. 2-2 System specification summary

| SIR                                | >-50 <i>dB</i> |

|------------------------------------|----------------|

| Cancellation ADC                   | 1GHz / 3~6bits |

| Residue ADC                        | 1GHz / 6bits   |

| DAC                                | 1GHz / 8bits   |

| AGC Gain                           | <40 <i>dB</i>  |

| Maximum Dynamic Range<br>Reduction | >40 <i>dB</i>  |

| Overall EBDR                       | 11.6bits       |

#### 2.3.4 System Specification for Cancellation ADC and DAC

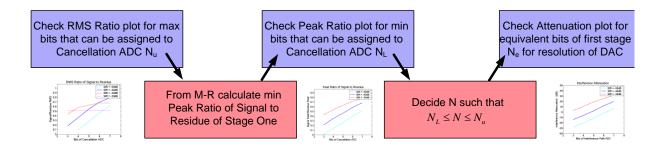

To optimize the system specification with minimum power consumption, an illustration of how to choose the number of bit of the Cancellation ADC, *N*, is shown from the graphs in Fig. 2-14.

For instance, given an approximately known SIR around -40dB, required resolution for signal is 20dB, which is 3bits, maximum bits could be designed to residue ADC is 4bits. The RMS ratio plot provides a power efficient design of the Cancellation, sets the upper bound N to be 6bits. Because for stage two M-3bits=1bit, minimum peak ratio of signal to residue is  $\frac{1}{2}$ . The peak ratio plot in Fig. 2-11 sets the lower bound of N to be 5-bit. Choosing N to be 5-bit, from Fig. 2-8, the SIR improvement is found to be 40+2=42dB, which specifies a DAC resolution of 7bits.

Fig. 2-14 Determine the resolution N of the Cancellation ADC and the DAC

#### 2.4 Conclusion

By using the time domain interference cancellation, it is possible to reduce narrowband interferers so that an in-band signal can be more effectively detected. By using a mixed signal architecture, which contains two low resolution ADC's, it is possible to effectively act as a high-resolution ADC in terms of the ability to resolve a small desired signal in the presence of a large interfering signal.

# **Chapter 3**

# Digital Signal Processing in Interference Cancellation

In this chapter, we analyze the trade-offs, from digital signal processing aspect, among several design-related issues for active cancellation of interference and expand it further, combining equalization of a time-varying channel in a cognitive radio system. The analysis is further demonstrated through simulation.

In order to perform active cancellation of interference, we will have to make some assumptions about how the interference looks in various frequency bands. This a-priori information can be gained while sensing the use of spectrum by neighboring devices before a cognitive radio starts using a chunk of the spectrum. As we mentioned in Chapter 2, the most common form of interference is narrow-band interference. Since, it is assumed, the cognitive radio has found a hole in the spectrum (where there is no primary user), and to find such a preferred band to transit, the bandwidth of both the transmitter and the receiver of the cognitive radio system are required to maintain sufficiently high. Hence, the interference is generally comparably narrow band, and can be of very high power, with SIRs of -50dB occurring frequently.

Another major problem in a cognitive radio system is channel equalization. In fact, in receivers operating in wireless environments, the channel equalizer is the component that requires the most chip area and energy. The simulation of a linear least mean squares (LMS) equalizer and a decision feedback equalizer (DFE) are explicitly compared here.

In this chapter, we will focus on adaptive interference cancellation, channel equalization, and the combining of the above two. Several kinds of interference are considered. The performance of the two adaptive interference cancellation processing algorithms are compared, under two performance metrics, the Bit Error Rate (BER) and the Mean Square Error (MSE). Then, the effect of relative interference bandwidth on the performance of the system is presented to address the flexibility on the first assumption of the —narrow-band" interference. Finally, the equalizer and the test system are included when the channel is a time varying Rayleigh fading channel or an AWGN channel.

# 3.1 System Model

The model used for the system is divided into three stages shown in the Fig. 3-1, Fig. 3-2 and Fig. 3-3 below:

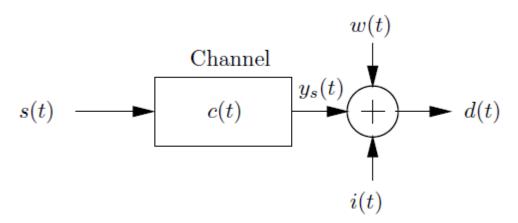

Fig. 3-1 Signal flow through the channel.

Fig. 3-2 Illustration of an interference cancellation system in cognitive radio.

Fig. 3-3 A system illustrating channel equalization in cognitive radio.

In Fig. 3-1, s(t) is the transmitted signal, i(t) is the interference, c(t) is the channel impulse response, and w(t) is a white Gaussian noise process. The sum of  $y_s(t)$ , the interference and the noise is the received signal at the receiver, which has been called the signal d(t).

In Fig. 3-2, the receiver then samples this signal and due to a delay inside the ADC of one sample, it is assumed that the output of the ADC is d(n-1), a delayed version of d(n) which is the ideal sampled version of d(t). The adaptive filter tries to get an estimate of the delayed interference,  $\hat{i}(n-1)$ . This is not good from an interference cancellation point of view, as the current value of interference for cancellation is wanted. So, an adaptive two sample forward predictor, g(n) is built to compensate for the delays in the ADC and DAC. Note that two samples are predicted ahead instead of one to take into account the delay in the DAC that follows the predictor since the DAC is assumed to have a delay which is the same as the ADC. The final output of the interference cancellation block is an analog estimate of interference which can be used for cancellation. Subtracting it from d(t), gives the an estimate of  $y_s(t)$ . Of course, the estimate of the interference is noisy because the filtered signal and AWGN affect on the estimation.

Finally in Fig. 3-3, the estimate,  $\hat{y}_s(t)$  is passed through an ADC which is to be filtered by an adaptive equalizer to remove the effect of the channel on the signal. The estimate of the signal,  $\hat{s}(n)$ , is provided in the discrete time domain.

It is assumed that there are two samplers (ADCs) in the system and the sampler used in interference cancellation can be of comparable resolution to the sampler used in the equalization block. The time alias of the two paths, cancellation and the main path, is realized through the predictor. This model has been used under the observation that two samplers which do not have to be both high resolution and high speed will be cheaper than one sampler which is both high resolution and high speed. The multi-step predictor can be easily implemented in the system. In the simulation that follows, all computations are in discrete time.

The model is hence a baseband model in which timing and carrier synchronization are assumed to be handled perfectly. With these assumptions, in particular, fractionally spaced equalizers or the constant modulus algorithm (CMA) for equalizer adaptation are not considered because these techniques are used to help in the areas which are assumed not to be an issue.

## 3.2 Adaptive Filter Approaches

#### 3.2.1 Assumptions