## **Communication and Control for Quantum Circuits**

Yatish Patel

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2010-77 http://www.eecs.berkeley.edu/Pubs/TechRpts/2010/EECS-2010-77.html

May 14, 2010

Copyright © 2010, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Communication and Control for Quantum Circuits

by

#### Yatish Patel

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

in the

Graduate Division of the University of California, Berkeley

Committee in charge:

Professor John Kubiatowicz, Chair Professor Krste Asanovic Professor John Flannery

Spring 2010

## Communication and Control for Quantum Circuits

Copyright 2010 by Yatish Patel

#### Abstract

Communication and Control for Quantum Circuits

by

Yatish Patel

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor John Kubiatowicz, Chair

Quantum computers will potentially be able to solve certain classes of problems more efficiently than possible on a classical computer. Due to the fragility of quantum data, a large scale quantum computer will require a robust system to enable reliable communication within the datapath. We present a scalable architecture for a quantum computer which specifically addresses communication concerns. Our design minimizes communication error by using a specialized interconnection network to perform long-distance movement.

We developed a set of tools to construct and study quantum datapath designs based on ion trap quantum technology. Our tools automatically synthesize and insert the interconnection network used for long-distance communication into the target datapath. We present a set of greedy heuristics to optimize the routing and scheduling of communication within this network and show that our approach performs as well as an optimal case determined using integer linear programming. We study a number of different quantum circuits including randomly generated circuits, quantum adder circuits, and ultimately Shor's factorization algorithm and show that designs using our optimizations significantly improve upon prior work in terms of a probabilistic area delay metric.

## Contents

| Li            | st of | Figure | res                               | iv   |

|---------------|-------|--------|-----------------------------------|------|

| $\mathbf{Li}$ | st of | Tables | es                                | xii  |

| 1             | Intr  | oducti | ion                               | 1    |

| 2             | Qua   | ntum   | Computing                         | 5    |

|               | 2.1   | Quant  | tum States                        | . 5  |

|               | 2.2   | Quant  | tum Circuit Model                 | . 6  |

|               |       | 2.2.1  | Universal Gates                   | . 8  |

|               |       | 2.2.2  | Quantum Decoherence               | . 8  |

|               |       | 2.2.3  | Fidelity                          | . 8  |

|               | 2.3   | Error  | Correcting Codes                  |      |

|               | 2.4   | Comm   | nunication                        | . 10 |

|               |       | 2.4.1  | Teleportation                     | . 10 |

|               | 2.5   | Quant  | tum Computing Technologies        | . 12 |

|               |       | 2.5.1  | Ion Trap and Qubits               |      |

|               |       | 2.5.2  | Movement                          |      |

|               |       | 2.5.3  | Measurement                       | . 16 |

|               |       | 2.5.4  | Gate Operations                   | . 16 |

|               |       | 2.5.5  | Abstraction                       |      |

|               |       | 2.5.6  | Comparing to Classical CMOS       | . 18 |

| 3             | Qua   | ntum   | CAD Flow                          | 20   |

|               | 3.1   | Applic | cation Circuit Specification      | . 23 |

|               |       | 3.1.1  | Application Dataflow Graph        | . 26 |

|               | 3.2   | Error  | Correction Circuit Optimization   | . 28 |

|               | 3.3   | Quant  | tum Logic Synthesis               | . 28 |

|               |       | 3.3.1  | Technology Dependent Gates        | . 28 |

|               |       | 3.3.2  | Fault Tolerant Gate Constructions | . 29 |

|               | 3.4   | Datap  | oath Microarchitectures           | . 29 |

|               |       | 3.4.1  | Three Major Organizations         | . 29 |

|               |       | 3.4.2  | Network Synthesis                 | . 30 |

|               | 3.5   | Ion Tr | ran Lavout                        | 30   |

|   |      | 3.5.1         | Layout Graph Representation                 | 31 |

|---|------|---------------|---------------------------------------------|----|

|   |      | 3.5.2         | Modular Layouts                             |    |

|   |      | 3.5.3         | Layout Metrics                              | 32 |

|   | 3.6  | High-l        | evel Mapping                                |    |

|   | 3.7  |               | ork Routing and Scheduling                  | 34 |

|   | 3.8  |               | evel Scheduling                             | 34 |

|   | 3.9  |               | Tolerance Verification                      | 34 |

|   | 3.10 | Bench         | marks and Evaluation                        | 36 |

|   |      |               | Adder Circuits and Shor's Algorithm         | 36 |

|   |      |               | Random Circuit Generation                   | 36 |

|   |      |               | ADCR: An Aggregate Metric for Probabilistic |    |

|   |      |               | Computation                                 | 37 |

|   |      |               | •                                           |    |

| 4 | _    |               | g Short-distance Quantum Communication      | 39 |

|   | 4.1  |               | rap Datapath                                | 39 |

|   | 4.2  |               | eath Control                                | 41 |

|   |      | 4.2.1         | Macroblock Abstraction                      | 43 |

|   |      | 4.2.2         | Macroblock Sequencing                       |    |

|   |      | 4.2.3         | Lasers and Measurement                      | 47 |

|   |      | 4.2.4         | Interface to High-level Control             | 47 |

|   |      | 4.2.5         | Scheduling Communication                    | 47 |

|   | 4.3  |               | al Layout of Quantum Circuits               | 48 |

|   | 4.4  |               | nated Grid-Based Layout                     | 50 |

|   |      | 4.4.1         | Regular Tiled Datapaths                     | 50 |

|   |      | 4.4.2         | Optimizing Titled Datapaths                 | 51 |

|   |      | 4.4.3         | Evaluating Grid-Based Datapaths             | 53 |

|   | 4.5  |               | so Compute Regions                          | 55 |

|   |      | 4.5.1         | Ancilla Generator Datapaths                 | 56 |

|   |      | 4.5.2         | Modeling Congestion                         | 57 |

|   | 4.6  | Summ          | nary                                        | 60 |

| 5 | Ont  | imizin        | g Long-distance Quantum Communication       | 61 |

| J | 5.1  |               | nunication Network                          | 62 |

|   | 0.1  | 5.1.1         | Structuring Global Communication            | 63 |

|   |      | 5.1.2         | Terminology                                 | 64 |

|   |      | 5.1.3         | Metrics                                     | 65 |

|   | 5.2  |               | ork Communication Models                    | 66 |

|   | 0.2  | 5.2.1         | Ballistic Transport Model                   | 66 |

|   |      | 5.2.1 $5.2.2$ | Teleportation Transport Model               | 67 |

|   |      | 5.2.3         | EPR Purification Model                      | 67 |

|   |      | 5.2.4         | Communication Model Analysis                | 69 |

|   |      | 5.2.4 $5.2.5$ | Purification Resources                      | 72 |

|   | 5.3  |               | ork Connections and Control                 | 75 |

|   | 5.5  |               | Chain Teleportation                         | 77 |

|    |       | 5.3.2         | Path Reservation                              | 79   |

|----|-------|---------------|-----------------------------------------------|------|

|    |       | 5.3.3         | Link Setup                                    | 79   |

|    |       | 5.3.4         | EPR Teleportation                             |      |

|    |       | 5.3.5         | Data Teleportation                            |      |

|    |       | 5.3.6         | Connection Breakdown                          |      |

|    | 5.4   | Compo         | onent Design                                  | . 81 |

|    |       | 5.4.1         | Purifier                                      | . 81 |

|    |       | 5.4.2         | Router Links                                  | . 82 |

|    |       | 5.4.3         | Routers                                       | . 83 |

|    | ъ     | . •           |                                               | ~~   |

| 6  |       | iting         | C 1 . 1 1.                                    | 85   |

|    | 6.1   |               | Schedule                                      |      |

|    | 6.2   |               |                                               |      |

|    |       | 6.2.1         | Dimension Order                               |      |

|    | 6.3   | 6.2.2         | Adaptive                                      |      |

|    | 0.5   | 6.3.1         | al Routing and Scheduling                     |      |

|    |       | 6.3.2         | Results                                       |      |

|    | 6.4   |               | cal Scheduling and Routing                    |      |

|    | 0.1   | 6.4.1         | On Demand Scheduling                          |      |

|    |       | 6.4.2         | Heuristic Prescheduling                       |      |

|    |       | 6.4.3         | Simulated Annealing                           |      |

|    | 6.5   |               | g Analysis                                    |      |

|    | 0.0   | 6.5.1         | Network Area Impact                           |      |

|    |       | 6.5.2         | Sensitivity to Mapping                        |      |

|    |       | 6.5.3         | Communication Patterns and Circuit Size       |      |

|    | 6.6   | Summa         | ary                                           | 105  |

| _  | _     | 0             |                                               | 100  |

| 7  | `     | •             | <b>ntum Circuits</b><br>um Addition Circuits  | 106  |

|    | 7.1   | •             |                                               |      |

|    |       |               | Ripple-carry Adder                            |      |

|    | 7.2   |               | Factorization Algorithm                       |      |

|    | 1.4   | 7.2.1         | Implementation of Shor's                      |      |

|    |       | 7.2.1 $7.2.2$ | Performance of Shor's Algorithm               |      |

|    | 7.3   |               | Work                                          |      |

|    | 1.0   | 7.3.1         | Alternate Technologies                        |      |

|    |       | 7.3.2         | Early Network Connections                     |      |

|    |       | 7.3.3         | Ballistic Move with Periodic Error Correction |      |

|    | 7.4   |               | sion                                          |      |

| ъ. |       |               |                                               |      |

| Вi | bliog | graphy        |                                               | 114  |

# List of Figures

| 1.1 | Quantum Computer Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Quantum Circuit Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3  |

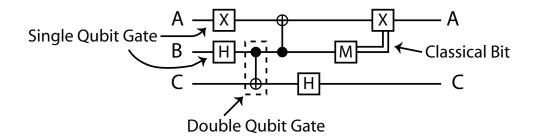

| 2.1 | Quantum Circuit Model. Small example circuit that operates on three qubits. The sequence of operations is read left to right. Quantum bits are represented by single lines and classical bits are represented by double lines. This circuit contains four single qubit gates, two double qubit gates, and a measure gate. In this example, the measure gate generates a classical bit which is used to control the X gate on qubit A                                                                                                                                                                                                                                                    | 6  |

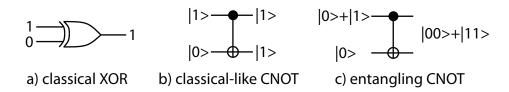

| 2.2 | A comparison between a classical XOR and its quantum analog: the controlled not or CNOT. The CNOT gate is reversible, thus the additional output. Figure b) outputs the XOR result to the bottom bit. Figure c) shows the same CNOT when the input is a quantum superposition. In this case the output is an <i>entangled</i> qubit state, not representable as independent qubit values for the two outputs                                                                                                                                                                                                                                                                            | 7  |

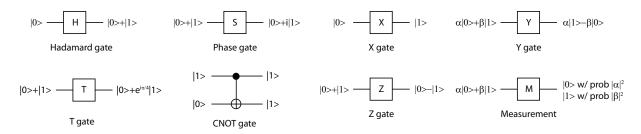

| 2.3 | Basic gates for quantum circuits which supports a universal quantum computing model. The Hadamard gate converts bit values to phase values and vice versa. The phase, T and Z gates rotate the phase of the "1" qubit value by different angles. The CNOT gate is the same as shown in Figure 2.2 and performs the XOR functionality. The measurement "gate" measures a quantum state, returning a 1 or 0 and collapses any superposition to that value as well. The X is a bit flip, Z a phase flip, and Y a combination of both. The X, Y, Z, and phase gates can be generated by the other gates shown here but we include them since they are often included as physical primitives | 7  |

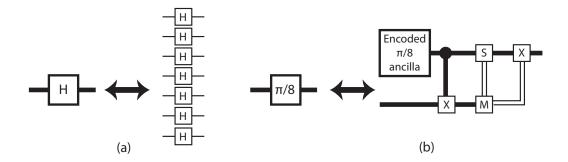

| 2.4 | Example of a transversal and non-transversal gate. Bold lines represent logical qubits where are encoded by a number of physical qubits. In (a) the H gate is performed on an encoded qubit transversally with a single H gate per physical bit. In (b) the $\pi/8$ cannot be performed transversally. Instead we create an encoded $\pi/8$ ancilla and use X, S, and M gates to perform the encoded $\pi/8$                                                                                                                                                                                                                                                                            | 10 |

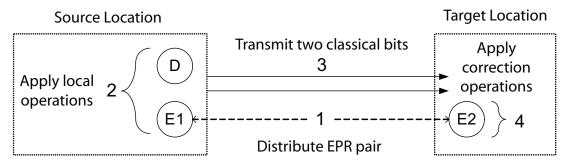

| 2.5  | Teleporting data qubit D to the target location requires (1) a high-fidelity EPR pair (E1/E2), (2) local operations at the source, (3) transmission of classical bits, and (4) correction operations to recreate D from E2 at the target                                                                                                                                                                                                                         | 11 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

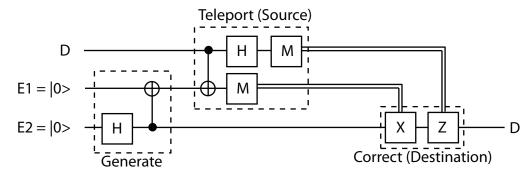

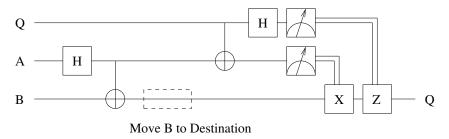

| 2.6  | Circuit representation for the teleportation operation: The first Hadamard and CNOT gates generate the EPR pair E1 and E2. At the source of the teleportation, one half of the EPR pair is CNOTed with the data followed by a Hadamard and measurements. The measurement results (classical information represented by double bit lines) are transmitted to the destination where they are used to apply X and Z gates to correct E2 and recreate the state of D | 11 |

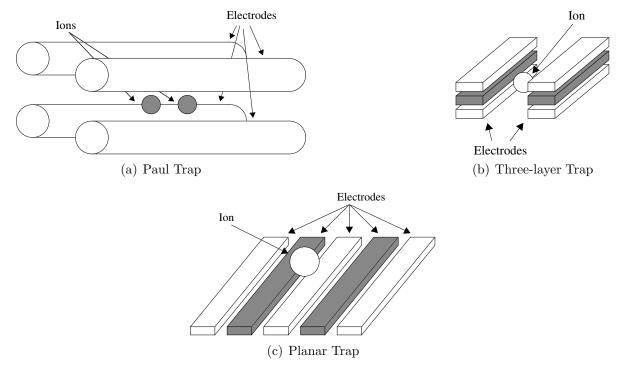

| 2.7  | Various structures used to create an Ion Trap. 2.7(a) Original trap configuration where an ion is trapped between 4 cylindrical rods. 2.7(b) Three-layer structure used in [30]. 2.7(c) Planar trap structure from [50], where ions are trapped above a set of electrodes                                                                                                                                                                                        | 13 |

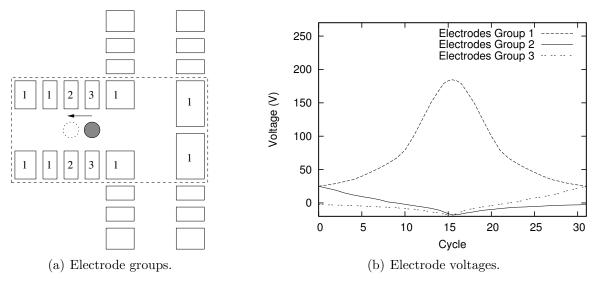

| 2.8  | Electrode groups and voltages used to move a qubit from one trap to another. Each electrode group shares the same voltage level. Electrodes outside the dashed box are not utilized in the movement protocol                                                                                                                                                                                                                                                     | 14 |

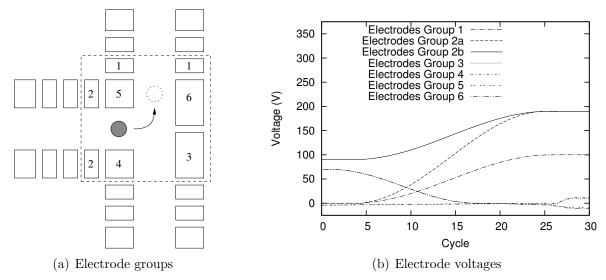

| 2.9  | Electrode groups used to move a qubit around a corner. Electrodes outside the dashed box are not utilized in the movement protocol. All electrodes in a group use the same voltage level. For group 2, 2a is the signal for the top layer, and 2b is the signal for the bottom layer                                                                                                                                                                             | 15 |

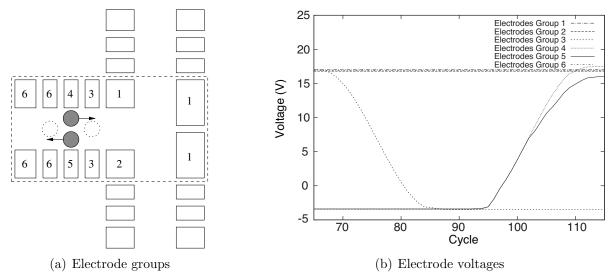

| 2.10 | Electrode groups and voltages used to implement ion splitting and combining. Two ions start in the trap region between electrode groups 4 and 5 and move apart. Electrodes outside the dashed box are not utilized in the movement protocol. Time reversing the protocol will combine two separated ions into the same trap.                                                                                                                                     | 16 |

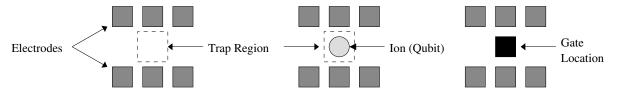

| 2.11 | Ion trap abstraction. The dark gray boxes represent electrodes, and the dashed box is a trap region capable of holding an ion (qubit). The left side of the figure is an unoccupied ion trap, and the right side shows a trap with                                                                                                                                                                                                                               | 10 |

|      | an ion confined in it                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18 |

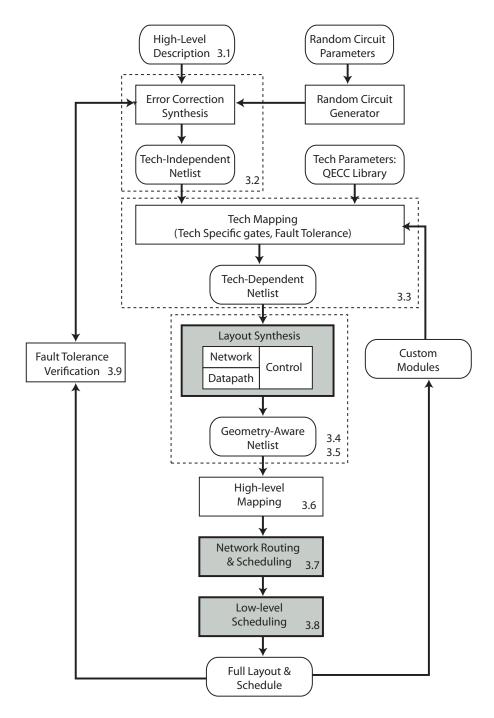

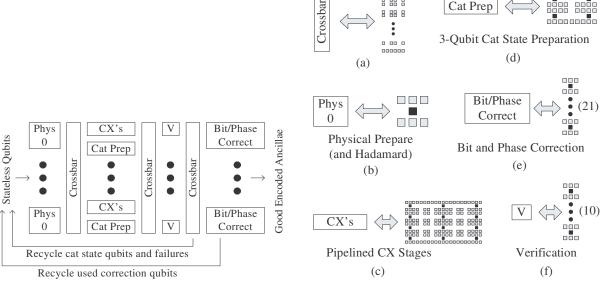

| 3.1  | A high level view of our computer-aided design flow for quantum circuits. The highlighted blocks denote the contributions focused on in this work. Dashed boxes correspond to the indicated section number where details of the stages are explained                                                                                                                                                                                                             | 22 |

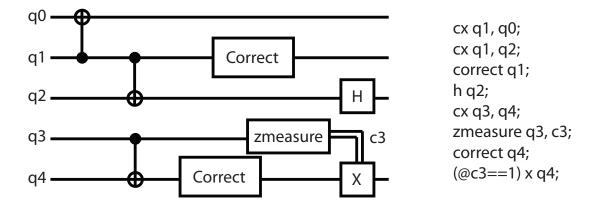

| 3.2  | A quantum circuit and the equivalent QASM instruction stream representing it                                                                                                                                                                                                                                                                                                                                                                                     | 24 |

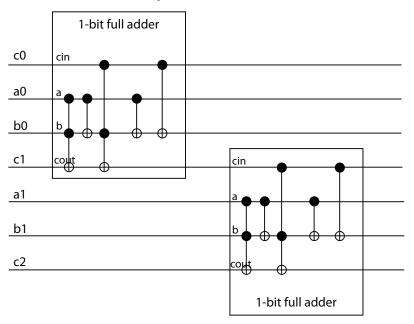

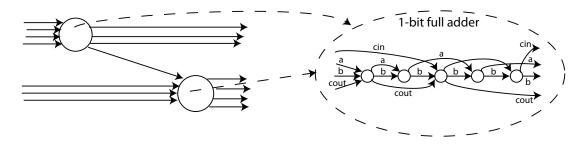

| 3.3  | Gate networks are represented as linked, modular dataflow graphs. In this example, the top level graph consists of two nodes that each correspond to a 1-bit full adder. They both refer to the 1-bit full adder module dataflow                                                                                                                                                                                                                                 | 26 |

|      | graph                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

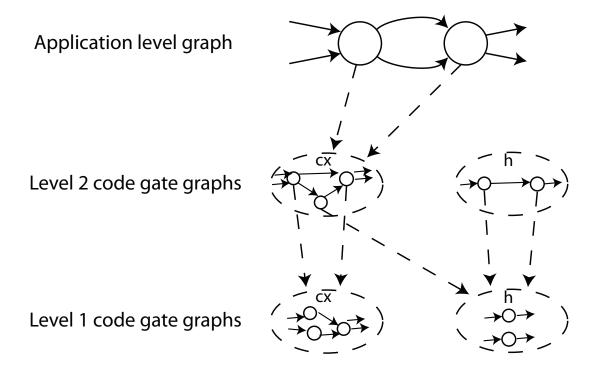

| 3.4 | encodings. In this example we have the 2 gate application circuit encoded in 2 levels of codes. Each code has a library of graphs, each graph implementing an encoded version of one gate type                                                                                                                                                                                                                                               | 27 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

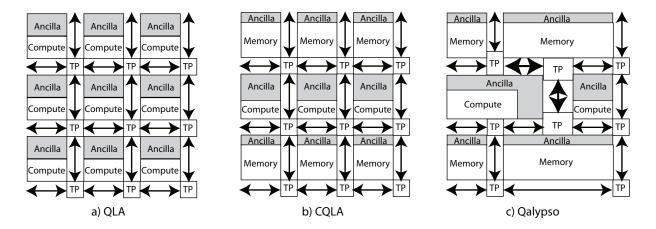

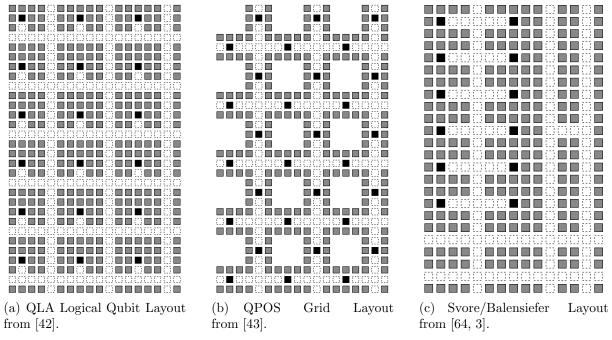

| 3.5 | Quantum Datapath Organizations: a) Quantum Logic Array ( <i>QLA</i> ): An FPGA-style sea of quantum two-bit gates (compute tiles), where each gate has dedicated ancilla resources. b) Compressed QLA ( <i>CQLA</i> ): QLA compute tiles surrounded by denser memory tiles. c) <i>Qalypso</i> : Variable sized compute and memory tiles with shared ancilla resources for each tile; teleportation network can have variable bandwidth links | 30 |

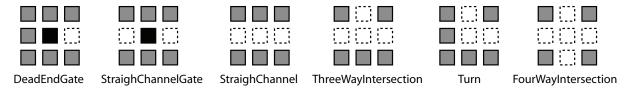

| 3.6 | Library of ion trap macroblocks. Gray boxes represent electrodes and the black box represents a trap region capable of performing a gate operation. Gates are not allowed in the intersection or turn macroblocks as these trap regions are not as stable as a trap region between two electrodes                                                                                                                                            | 31 |

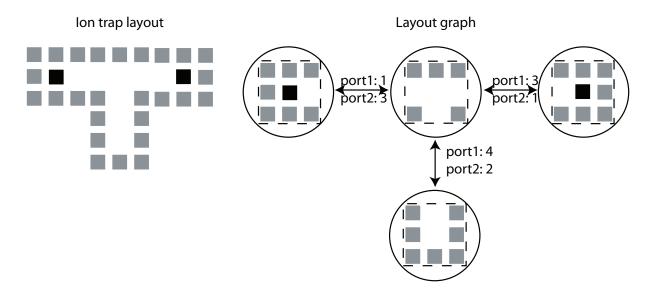

| 3.7 | A layout and its associated graph. The nodes correspond to macroblocks and the edges correspond to "quets" which do not have any associated physical entity but determine how macroblocks are oriented with respect to each other                                                                                                                                                                                                            | 32 |

| 3.8 | Layouts can consist of placements of single macroblocks or definition and then instantiation of larger layout blocks. In this example, we define a larger "horseshoe" block made up of macroblocks and then instantiate two of them in different positions and orientations                                                                                                                                                                  | 33 |

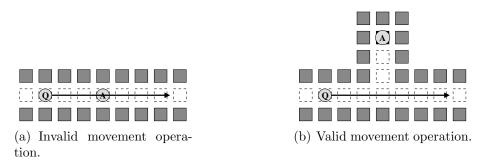

| 4.1 | Example of invalid and valid movement operations. The operation in (a) is not allowed since qubit Q cannot move through the trap occupied by qubit A. The operation in (b) is allowed as qubit A is now far enough away from the path qubit Q wants to take                                                                                                                                                                                  | 40 |

| 4.2 | Circuit used to teleport qubit Q to some destination. Initially qubits A and B are entangled to form an EPR pair. Qubit B is then moved to the destination location. After interacting qubits Q and A, their states are measured and the results are classically transmitted to the destination. Using this classical information B is operated on to recreate Q at the destination                                                          | 40 |

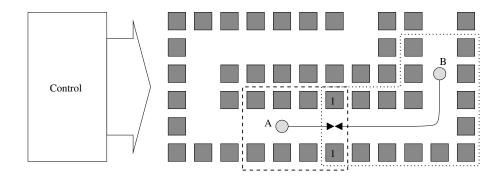

| 4.3 | One possible datapath implementation for the teleportation circuit shown in 4.2. Qubit B is shown in the destination ion trap to where qubit Q will ultimately be teleported. The large dashed box in the middle represents an arbitrary distance.                                                                                                                                                                                           | 41 |

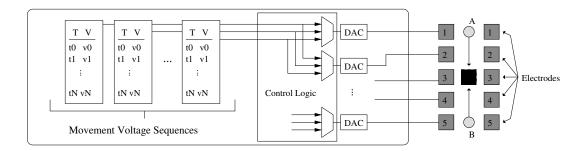

| 4.4 | DACs are used to control the voltages of the ion trap electrodes. Electrodes that share a label receive the same voltage sequence. The control logic programs the DACs to generate the necessary voltage sequences. The voltage sequences corresponding to the various movement operations are                                                                                                                                               |    |

|     | stored in a memory                                                                                                                                                                                                                                                                                                                                                                                                                           | 42 |

| 4.5  | electrodes required to move two qubits to the trap region between the electrodes labeled 1. The movement of qubit A requires all the electrodes within the dashed rectangle. The movement of qubit B requires all the electrodes within the region enclosed by the dotted line                                                                                                                | 42         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

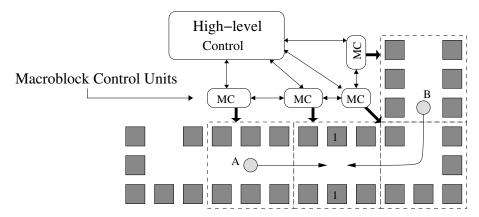

| 4.6  | The same datapath shown in Figure 4.5 redrawn to highlight repetitive operations that can be exploited by a hierarchical control system. The control logic required to perform the straight arrow movement is the same in all cases. Similarly, the control to perform the turn arrows is also the same in each turn case                                                                     | 43         |

| 4.7  | Example library of ion trap macroblocks. Gray boxes represent electrodes and the black box represents a trap region capable of performing a gate operation. Gates are not allowed in the intersection or turn macroblocks as these trap regions are not as stable as a trap region between two electrodes.                                                                                    | 44         |

| 4.8  | The same movement as pictured in Figure 4.5, but with the macroblock abstractions inserted. The macroblock control units are shown along with their interface to high-level control.                                                                                                                                                                                                          | 44         |

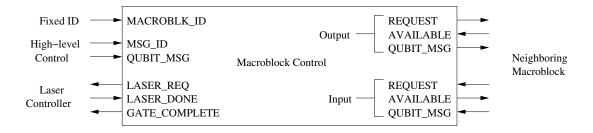

| 4.9  | Macroblock control interface. For each quantum port in the macroblock, there are a set of Input and Output signals that connect to the neighboring macroblock. The macroblock interfaces to higher level controllers through the Instruction Controller and Laser Controller interfaces. Each                                                                                                 |            |

|      | macroblock also has a unique ID for addressing purposes                                                                                                                                                                                                                                                                                                                                       | 45         |

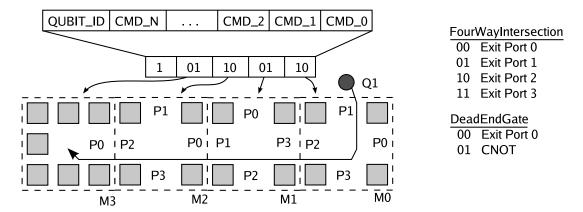

| 4.10 | Example of how a qubit control message is constructed to move a qubit through a series of macroblocks. The layout is constructed from four macroblocks. In this example, M1 happens to be rotated 90 degrees compared to M2 and M0. The qubit enters M0 and travels through M1 and M2, arriving at M3 where it is instructed to perform a CNOT                                                | 46         |

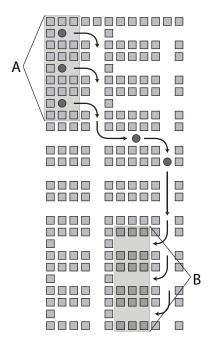

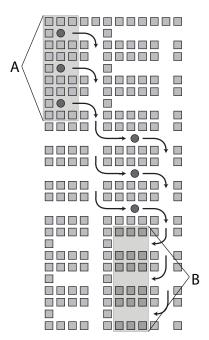

| 4.11 | Inefficient logical qubit move                                                                                                                                                                                                                                                                                                                                                                | 49         |

| 4.12 | Correct logical qubit move                                                                                                                                                                                                                                                                                                                                                                    | 49         |

| 4.13 | Custom designed Layout Tool. The manual layout tool interface allows users to create arbitrary layouts using standard macroblocks or other user-                                                                                                                                                                                                                                              |            |

|      | defined modules                                                                                                                                                                                                                                                                                                                                                                               | 49         |

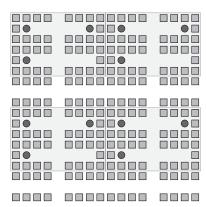

| 4.14 | A sample of physical layouts of Functional Units taken from the literature.                                                                                                                                                                                                                                                                                                                   | 51         |

| 4.15 | Tools used to create and evaluate various grid-based functional unit layouts.                                                                                                                                                                                                                                                                                                                 | 52         |

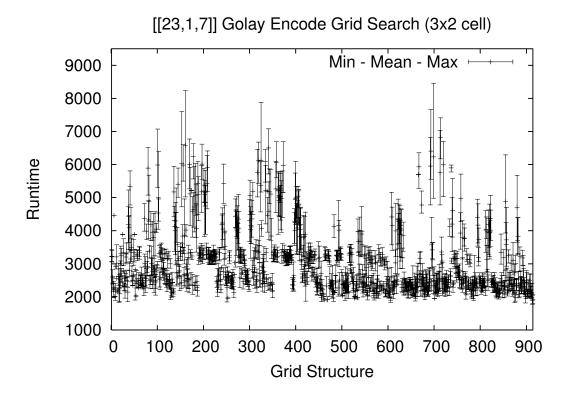

| 4.16 | Variations in runtime of various grid-based physical layouts for $[[23, 1, 7]]$ Golay encode circuit. The datapath is constructed of $3 \times 2$ sized cells tiled to form a total area of 143 macroblocks. The X axis represents the different grid structures tested, only a small subset of the total is shown to demonstrate variability. For each grid structure the minimum, mean, and | <b>-</b> 4 |

| 1 17 | maximum time are plotted                                                                                                                                                                                                                                                                                                                                                                      | 54         |

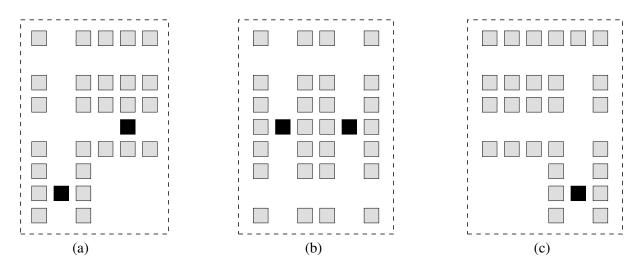

| 4.17 | Comparison of the best $3 \times 2$ cell for two different circuits. (a) The best cell for the [[23, 1, 7]] Golay encode circuit. (b) The best cell for the [[7, 1, 3]] L1 correct circuit. (c) The best cell for the [[7, 1, 3] L2 encode circuit                                                                                                                                            | 54         |

|      | Er correct effects, (c) the best centrer the [[1, 1, 0] L2 effecte effects                                                                                                                                                                                                                                                                                                                    | OH         |

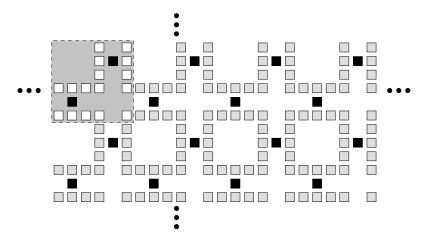

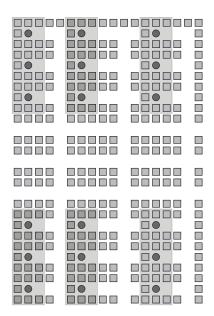

| 4.19<br>4.20<br>4.21<br>4.22<br>4.23 | QPOS grid structure constructed by tiling the highlighted 2×2 macroblock cell. The cells can extend in all directions to create an arbitrarily sized layout. A fully pipelined encoded zero ancilla creation unit                                                                             | 55<br>56<br>56<br>58<br>58<br>59 |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

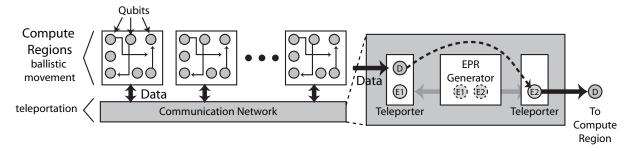

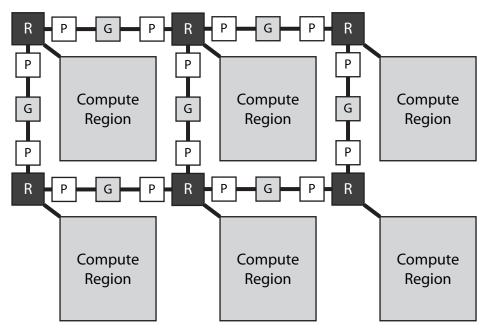

| 5.1                                  | Overview of the Quantum Datapath. A set of Compute Regions are connected via a communication network. Within compute regions data uses ballistic movement. To communication between compute regions, data uses teleportation through the communication network. The right side of the         | 0.4                              |

| 5.2                                  | figure shows a summary of the data teleportation process                                                                                                                                                                                                                                      | 61                               |

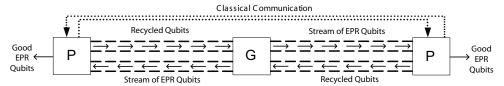

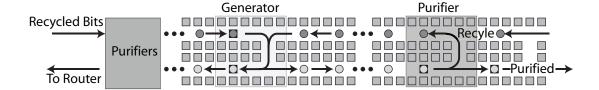

| 5.3                                  | recycled into new EPR pairs                                                                                                                                                                                                                                                                   | 62                               |

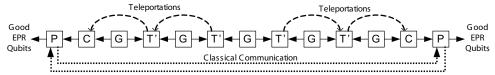

| 5.4                                  | nodes and then purifier nodes                                                                                                                                                                                                                                                                 | 62                               |

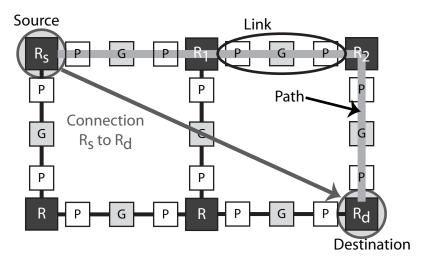

| 5.5                                  | has a local compute region where all the data operations occur                                                                                                                                                                                                                                | 64                               |

| 5.6                                  | Ballistic Movement Model. Communication channels are constructed as a sequence of macroblocks. The fidelity of a qubit and time to move the                                                                                                                                                   |                                  |

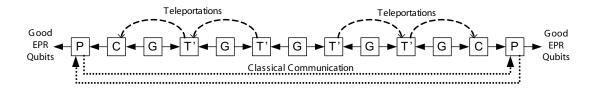

| 5.7                                  | qubit is directly proportional to the distance (in macroblocks) moved Chained Teleportation Distribution Methodology: EPR qubits generated at the midpoint generator are successively teleported until they reach the endpoint teleporter nodes before being ballistically moved to corrector | 66                               |

| 5.8                                  | nodes and then purifier nodes                                                                                                                                                                                                                                                                 | 68                               |

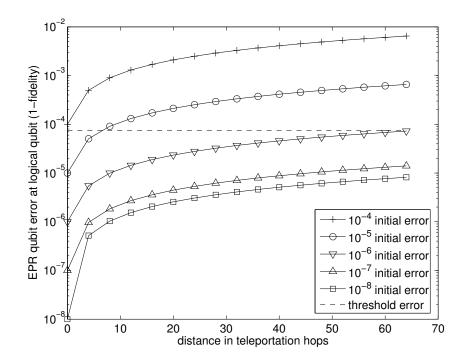

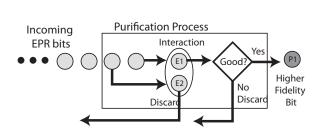

| 5.9                                  | of data qubits, $1-7.5*10^{-5}$                                                                                                                                                                                                                                                               | 68                               |

| 5.10                                 | carded. The remaining bit is retained if good, otherwise it is also discarded. Tree Purification Process. Level 0 qubits are purified to form Level 1 qubits                                                                                                                                  | 69                               |

|                                      | which are then purified to create a Level 2 qubit                                                                                                                                                                                                                                             | 69                               |

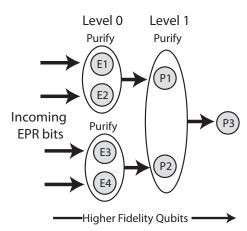

| 5.11 | error rate (1-fidelity) for surviving EPR pairs as a function of the number of purification rounds (tree levels) performed by the DEJMPS or BBPSSW protocol. Lower is better.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

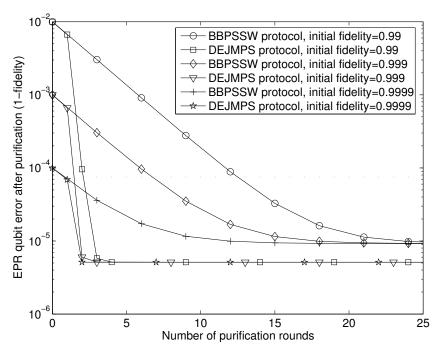

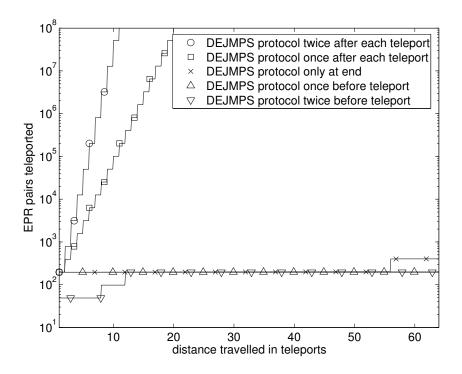

| 5.12 | Total EPR pairs consumed as a function of distance and point at which purification scheme DEJMPS is performed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 73 |

| 5.13 | Total EPR pairs in teleportation channel as a function of distance and point in transport in which purification scheme DEJMPS is performed. The only 2 lines that change from Figure 5.12 are the purify before teleport cases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74 |

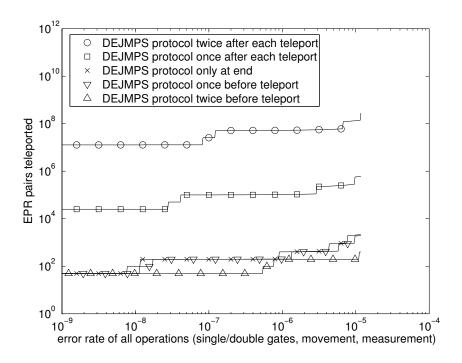

| 5.14 | Number of EPR pairs that need to be teleported to support a data communication within the error threshold. All error rates are set to the rate specified on the x-axis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75 |

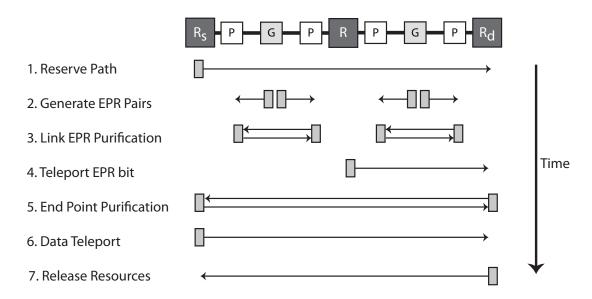

| 5.15 | Classical control messages to setup and use a network connection. Each stage in the process requires the passing of classical control messages to synchronize the operations. The process is described in detail in Section 5.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 76 |

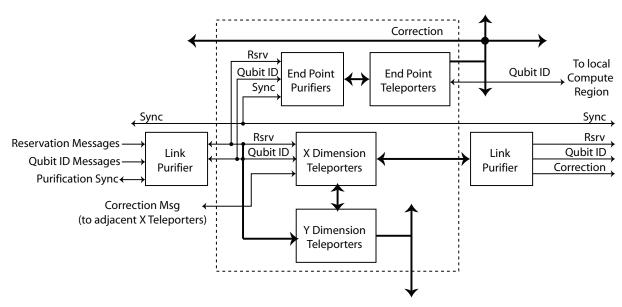

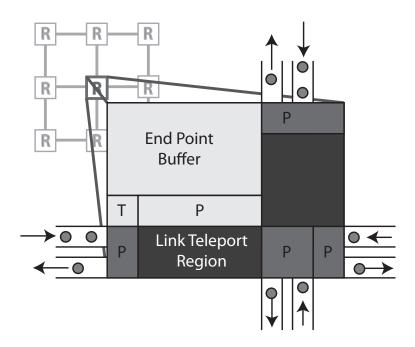

| 5.16 | Control interface for Routers. Routers have control signals connected to the local compute region, link purifiers, and neighboring routers. The signals for the Y teleporters are identical to the X teleporters and are summarized as bold lines. The link purifier modules for the Y dimension are omitted for clarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76 |

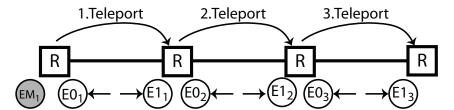

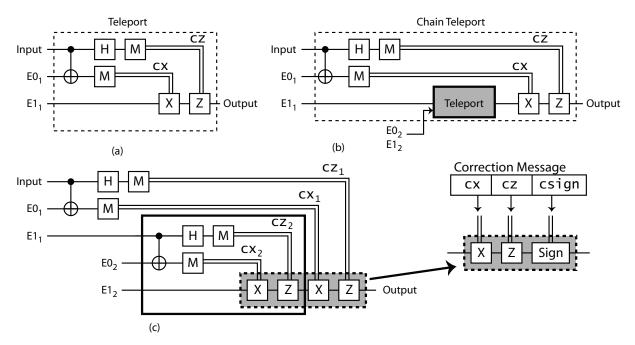

| 5.17 | Chain Teleport Procedure. To get the master EPR bit from the source to the destination router a sequence of chained teleports are performed. $EM_1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77 |

| 5.18 | Chain Teleport Circuits. (a) The standard teleport circuit that uses $E0_1$ and $E1_1$ to teleport Input to Output. Classical bits $cx$ and $cz$ are transmitted to the destination and used to control the $X$ and $Z$ operations. (b) Circuit representation of chain teleportation where an additional teleport operation is inserted to teleport $E1_1$ to the destination (via $E0_2$ and $E1_2$ ). (c) Same as the circuit in (b) with the Teleport box expanded. This figure shows the controlled- $X/Z/X/Z$ correction operations that must occur at the destination to recreate the Input value. Our optimizations remove the multiple correction gates and instead collect the classical bits at each hop in the form of a correction message. At the destination, the correction | 78 |

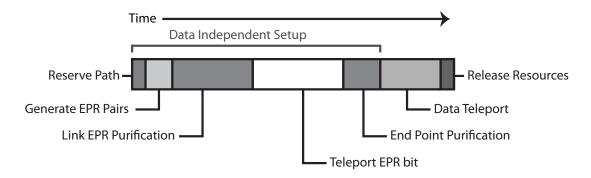

| 5.19 | Breakdown of time to perform a network connection. All the operations that occur before the Data Teleport stage are considered part of the data independent setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81 |

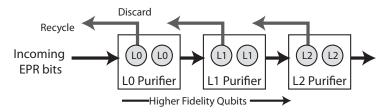

| 5.20 | Queue purification process. Incoming level 0 qubits are purified in the L0 Purifier. Recycled bits exit and return to the generator units. Purified level 1 bits are then moved into the L1 purifier to await the arrival of additional qubits. This process repeats as necessary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82 |

| 5.21 | Router Link Datapath. Links are composed centrally located generators connected to queue purifiers at the end points. The left side purifiers are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83 |

| 5.22 | Datapath layout for a network router. The link purifiers are shown integrated into the router area. Each network dimension has a bank of link teleporters and a separate set of purifiers and teleporters exist for the end point connections                                                                                                                                                    | 83  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

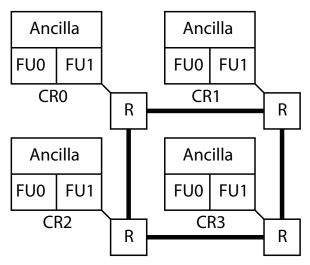

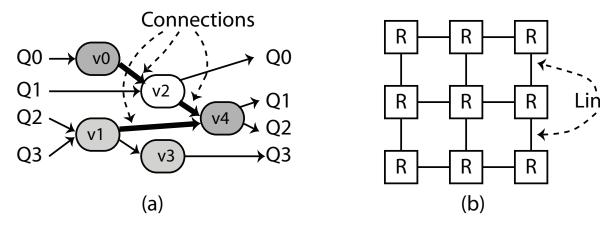

| 6.1  | Example 4 node datapath. This datapath contains four compute regions with their corresponding routers. Each compute region (CR) contains ancilla generators and two functional units. The thicker lines connecting routers are the network links                                                                                                                                                 | 87  |

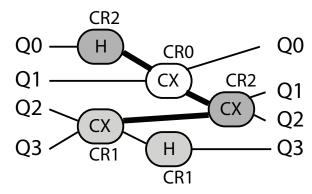

| 6.2  | Example four qubit 5 gate dataflow graph. Each vertex is assigned to execute within a specific compute region. Solid edges between vertices represent long-distance network connections. All other edges are ballistic movement within a compute region                                                                                                                                          | 87  |

| 6.3  | Circuit and Network model used to create a schedule of communication. In (a), the bold lines are communication edges that require the use of the network                                                                                                                                                                                                                                         | 87  |

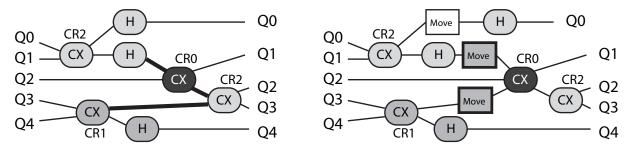

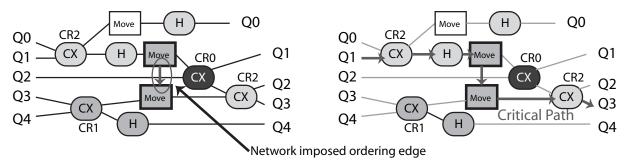

| 6.4  | Adding move event edges to the dataflow graph                                                                                                                                                                                                                                                                                                                                                    | 93  |

| 6.5  | Adding network ordering edges to the graph                                                                                                                                                                                                                                                                                                                                                       | 94  |

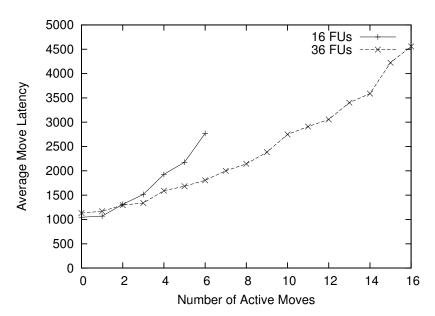

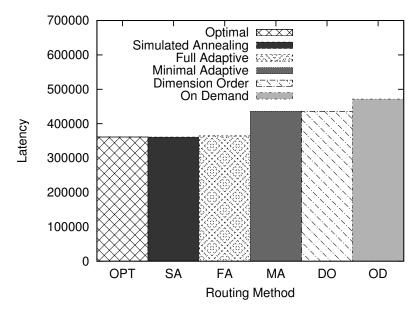

| 6.6  | Circuit Latency for different Routing techniques. For small circuits the Simulated Annealing and Full Adaptive routing techniques come very close to the optimal time as determined by the Linear Program                                                                                                                                                                                        | 99  |

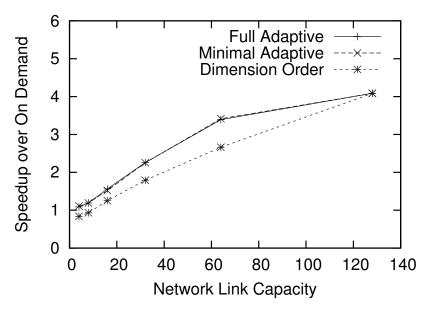

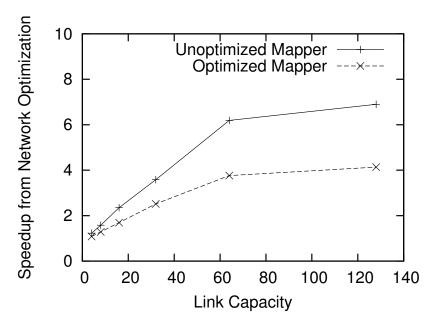

| 6.7  | Network speedup versus link capacity. Each point is normalized to the circuit latency obtained by using On Demand routing. As link capacity is added to the network the adaptive algorithms have more options for routing around congestion and improve over the Dimension Order routing. At the largest network size Dimension Order routing catches up as it no longer encounters congestion.  | 100 |

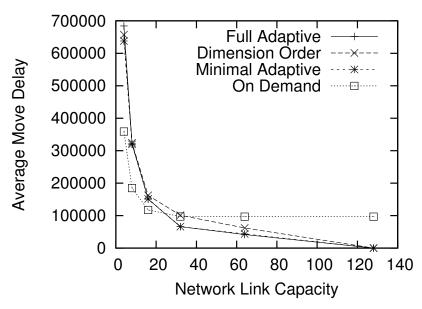

| 6.8  | Average per move delay introduced by the network. For each routing technique, the average amount of delay to move a qubit through the network is plotted against the size of the network links                                                                                                                                                                                                   | 101 |

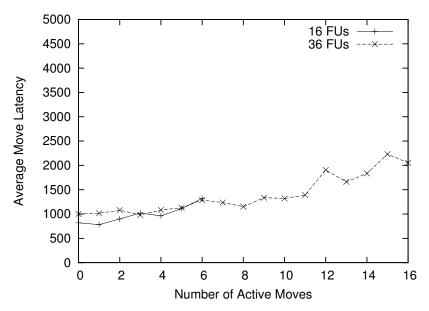

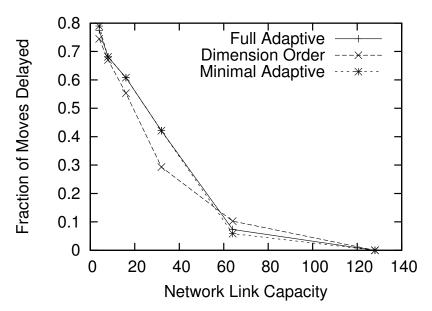

| 6.9  | Fraction of total network connections that are delayed. When a connection encounters congestion it must be delayed until the desired path frees up. As more link capacity is added the number of moves delayed decreases. Dimension Order has fewer delays initially because the communication requests are spread out resulting in a longer total latency when compared to the Adaptive schemes | 102 |

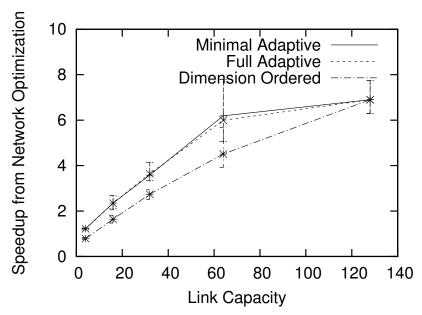

| 6.10 | Network speedup sensitivity to Mapping technique. The circuit is mapped using multiple random Mappers and then routed using the different techniques. For each data point the average speedup is plotted along with the minimum and maximum speedup (over On Demand routing)                                                                                                                     | 102 |

| 6.11 | Network speedup over on-demand given optimized and unoptimized Mappers. The unoptimized mapper generates a poor mapping with less locality allowing the optimized routing techniques to obtain better speedup. The optimized mapper balances computation more effectively reducing speedup |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | (over On Demand routing)                                                                                                                                                                                                                                                                   | 103 |

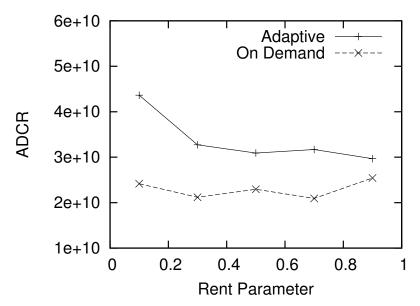

| 6.12 | Routing performance relative to communication density. Random circuits were generated with varying Rent parameters. Lower rent parameters correspond to a larger computation to communication ratio.                                                                                       |     |

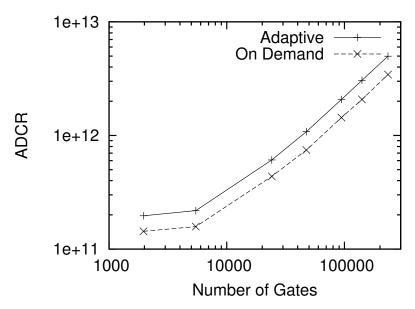

| 6.13 | ADCR versus the number of gates in a circuit. Random circuits were generated with increasing numbers of gates to determine ADCR for Adaptive                                                                                                                                               |     |

|      | and On Demand routing                                                                                                                                                                                                                                                                      | 105 |

| 7.1  | Shor's factoring architecture                                                                                                                                                                                                                                                              | 106 |

| 7.2  | Quantum ripple carry adder with "subadder" serialization                                                                                                                                                                                                                                   |     |

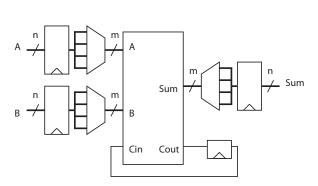

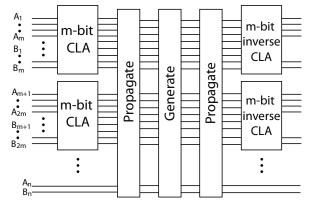

| 7.3  | Quantum carry-lookahead adder                                                                                                                                                                                                                                                              | 107 |

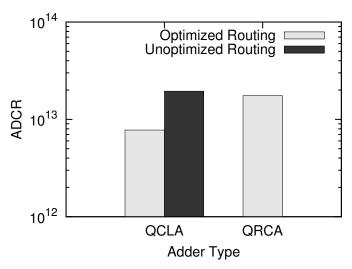

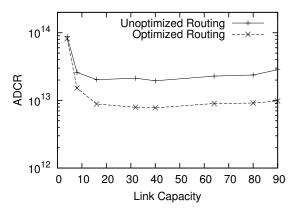

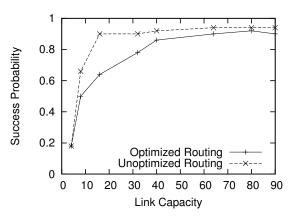

| 7.4  | Optimal ADCR for 1024-bit QCLA and QRCA. For each adder type and router a number of datapaths were searched to obtain the best ADCR                                                                                                                                                        | 100 |

| 7.5  | QRCA ADCR using the best datapath. Unoptimized routing results in a success probability of 0 and therefore isn't plotted. This datapath results in                                                                                                                                         | 108 |

| 7 C  |                                                                                                                                                                                                                                                                                            | 108 |

| 7.6  | Ripple-carry Adder aggregate qubit idle time. The unoptimized router fails due to the large amount of qubit idling in the system                                                                                                                                                           | 108 |

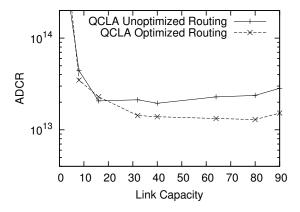

| 7.7  | QCLA ADCR using the best unoptimized routing datapath. This datapath corresponds to the best unoptimized routing ADCR bar in Figure 7.4                                                                                                                                                    | 109 |

| 7.8  | QCLA Success Probability vs Link Capacity for the best unoptimized routing datapath. This datapath corresponds to the unoptimized routing                                                                                                                                                  |     |

|      |                                                                                                                                                                                                                                                                                            | 109 |

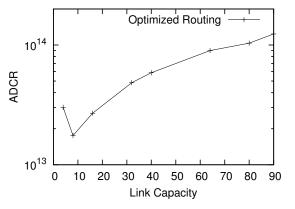

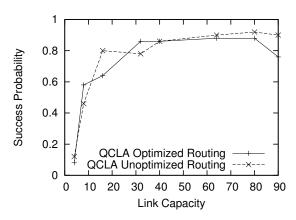

| 7.9  | QCLA ADCR using the best optimized routing datapath. This datapath corresponds to the Optimized Routing ADCR bar in Figure 7.4                                                                                                                                                             | 11( |

| 7.10 |                                                                                                                                                                                                                                                                                            |     |

|      | datapath. This datapath corresponds to the Optimized Routing ADCR bar in Figure 7.4                                                                                                                                                                                                        | 11( |

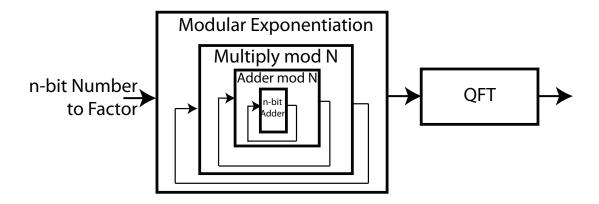

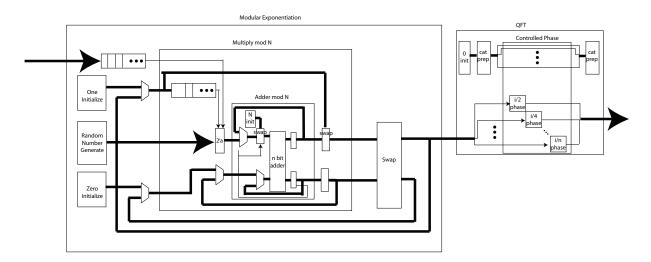

| 7 11 | Shor's factoring architecture. The process consists of two major stages:                                                                                                                                                                                                                   | 11( |

| 1.11 | modular exponentiation and Quantum Fourier Transform. A majority of                                                                                                                                                                                                                        |     |

|      | the complexity is within the modular exponentiation block where the major                                                                                                                                                                                                                  |     |

|      | sub-component is the quantum adder                                                                                                                                                                                                                                                         | 110 |

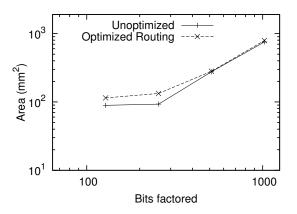

| 7.12 | Total Area used by Shor's factoring algorithm as a function of the number                                                                                                                                                                                                                  |     |

|      | of bits factored.                                                                                                                                                                                                                                                                          | 111 |

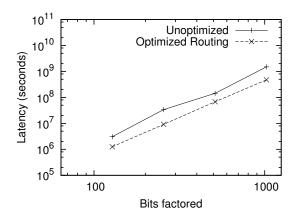

| 7.13 | Total latency used by Shor's factoring algorithm as a function of the number                                                                                                                                                                                                               |     |

|      | of bits factored.                                                                                                                                                                                                                                                                          | 111 |

## List of Tables

| 2.1 | Error probabilities and latency values used by our CAD flow for basic physical operations                                                                                                                                                                                                                                       | 13 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Summary of all the quantum instructions we use. Pure quantum instructions input quantum data and output quantum data. Pure classical instructions manipulate classical data only. Quantum-classical instructions either use classical data to manipulate the quantum data, or measure quantum data to generate classical output | 23 |

| 4.1 | List of our QECC benchmarks, with quantum gate count and number of qubits processed in the circuit                                                                                                                                                                                                                              | 53 |

| 4.2 | Latency results for the three error correction circuits we tested. In each case an exhaustive search for an optimal grid structure yielded a datapath with lower latency. The best grid structure found is shown in Figure 4.17                                                                                                 | 55 |

| 6.1 | Routing and Schoduling Types                                                                                                                                                                                                                                                                                                    | 00 |

#### Acknowledgments

None of this work would have been possible without the support of my advisor, John Kubiatowicz, a.k.a. Kubi. Kubi was patient and supportive during my early years when I was hunting for a thesis proposal and helped guide me towards what interested me most. Kubi was never without ideas and whenever I encountered a stumbling block he would invariably have advice to help me tackle the situation.

The quantum CAD flow presented in this work would not have been possible without the contributions from Mark Whitney and Nemanja Isailovic. The three of us put in countless effort into seeing the CAD flow vision realized. Without this joint effort, it would not have been possible to study quantum circuits in such detail. Aside from our professional relationship, I have developed a very close personal connection with Mark and Nemanja. We have gone on numerous adventures together all around the world, ranging from soccer games in Spain to sipping limoncello in Italy to hiking the Great Wall in China. My graduate student career would not have been the same without them.

I'm thankful to my thesis committee members, Professor Krste Asanovic and Professor John Flannery. Both of whom took time out of their busy schedules to provide help and feedback, without which I would never have been able to complete my work.

I started my graduate career sharing a house with Steve Sinha and Sonesh Surana. The three of us all came from Carnegie Mellon and we all decided to enter the CS Ph.D. program at Berkeley the same year. Consequently, our shared experiences have created a bond between us that will last a lifetime. With my family on the east coast, Steve and Sonesh were my family away from home.

Speaking of family, I would not be in the position I am now without the love and support of my parents, brother and sister-in-law and countless "relatives" in the Rochester community. My parents always encouraged me to strive for the best and made many sacrifices to help me get to where I am today.

Additionally, I'd like to thank all of the graduate students in the department that listened to my ideas and provided insightful feedback. Notably, Yury Markovskiy and Victor Wen were always available and willing to listen to practice talks and provided an "outsiders" perspective into my research.

Finally, I would like to thank my girlfriend, Jen. Jen's love and encouragement made it possible for me get through difficult times throughout my graduate career and enabled me to finally complete my work. You are my sunshine.

## Chapter 1

## Introduction

Quantum computers have the potential to perform certain classes of problems more efficiently than a traditional classical computer. The task that garners the most interest in building a quantum computer is the ability to factor large numbers using Shor's factoring algorithm [57]. In order for a quantum computer to tackle such a complex task, it must contain a large number of quantum bits and must be capable of performing many quantum operations. These requirements force us to address a number of concerns, a fundamental one being how best to manage communication of quantum information within the datapath.

Small quantum computer devices have been experimentally demonstrated using a number of different technologies [25, 35, 41, 15]. Common to all these technologies is the inherent fragility of the quantum bits. Simple tasks such as interacting two qubits together, moving a qubit in the system, or even storing a qubit for long periods of time all expose the quantum data to sources of error. To properly execute a quantum circuit we must carefully schedule how qubits move through the datapath to account for these sources of error. Moving quantum bits more than the shortest of distances can introduce enough error into the system to prevent us from obtaining a valid result.

In a quantum computer a qubit is represented by a physical object, e.g., the nuclear and electronic states of a single ion. To perform a two-qubit operation both qubits must be physically adjacent to each other and must move from one location to another. Therefore, during the execution of a quantum circuit qubits must constantly be shuttling around the system to take part in their various operations. Unfortunately, the simple task of moving a qubit can introduce significant amounts of error into the data stored by the qubit if not managed correctly.

One approach to addressing communication issues is to separate movement into two classes: short-distance and long-distance. Short-distance movement encapsulates all direct physical qubit movement and is limited to distances where we can utilize error correction techniques to reduce the error rates. Long-distance moves are those that would be too costly (in error and time) to perform physically, requiring an alternate method of communication. Fortunately, quantum computers allow us to use the process of teleportation [6] to perform these types of long-distance moves efficiently.

Teleportation utilizes helper qubits to move quantum information over longer dis-

#### **Quantum Computer**

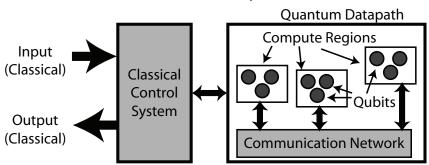

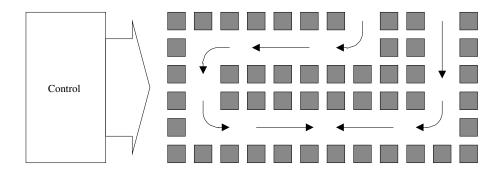

Figure 1.1: High-level view of a quantum computer architecture. The computer ultimately receives and generates classical data, but the main computation is done using qubits in the quantum datapath. The quantum datapath is constructed from a set of compute regions connected via a communication network.

tances. Using this technique we can design an architecture similar to classical multi-core chip with on-chip network: short-distance communication within a "core" (or compute region) occurs ballistically, while long-distance communication (between compute regions) occurs through an interconnection network based on teleportation. Figure 1.1 illustrates this architecture.

The quantum computer is broken up into a classical control portion and a quantum datapath. Both the input data and output data is classical; however, the computation is done internally via quantum operations. The quantum datapath is constructed from a set of compute regions connected via a communication network. The classical control system manages all the operations and orchestrates the full program run.

Variations on this type of architecture have been minimally studied in prior work [42, 66]. The architectures proposed so far however, suffer from a number of limitations:

- The communication networks proposed are high latency. When architectural improvements are made in other parts of the system, network delays start to dramatically impact overall latency.

- The architectural evaluations lacked detail about how various components in the system are constructed. Without these details the architectures cannot be thoroughly evaluated.

- Current research neglects the control system necessary to manage the quantum datapath. The complex support infrastructure and the vast number of qubits contained in the system will require a sophisticated control system that must be addressed.

- General-purpose architectures result in large designs with underutilized regions. In one proposal the authors calculated that a device sized to factor a 1024-bit number would measure approximately  $1m^2$  in area [42]. Without optimizing the designs to the target application it will be difficult to build these types of devices.

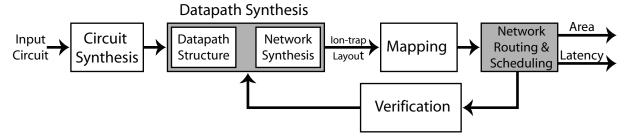

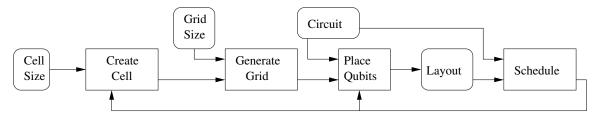

Figure 1.2: Our approach to designing and studying quantum datapaths. The input to the flow is a quantum circuit and the output is a full layout and schedule of operations.

In contrast to a general-purpose architecture, our work is based on using applicationspecific knowledge to optimize the quantum datapath by concentrating on managing the communication needs. A key result of this work is that by analyzing the quantum circuit we can optimize the communication infrastructure to improve overall circuit latency and reduce sources of error.

Our approach to studying the quantum circuit and performing optimization is shown in Figure 1.2, and consists of the following major components:

Circuit Synthesis: Our tools take a quantum circuit specified in a technology independent quantum assembly language combined with technology parameters to synthesize a new circuit with optimized error correction.

**Datapath Synthesis:** We use the synthesized circuit to automatically generate a quantum datapath tailored to the circuits needs. We analyze computation and communication and use this information to determine the best layout of compute regions and network structure.

**Mapping:** The mapping phase maps the circuit operations to the appropriate datapath resources.

**Network Routing & Scheduling:** With a list of operations and locations we generate an optimized routing and scheduling for all the long-distance communication operations that will take place.

**Verification:** The flow outputs a full layout and schedule of operations that are then fed into a verification tool to determine the success probability of the circuit. These results are then used to update the datapath to improve overall area, latency and success probability.

Within this design flow we make the following contributions:

**Short-distance communication:** We develop a method to construct low-level quantum datapaths for arbitrary quantum circuits. We provide tools to schedule gate and movement operations within these datapaths and use them to generate detailed area and communication requirements for our target architecture.

Long-distance communication: We present an architecture to manage long-distance communication within large quantum datapaths using a network built on teleportation. We create a control system to manage the complex interactions within the communication network and design low-level datapaths for all the network components. We use these designs to study detailed communication needs for large quantum circuits.

Routing algorithms for quantum communication networks: We present algorithms that minimize overhead and delay within the long-distance communication network of quantum datapaths. Our algorithms intelligently determine when and how to preschedule connections given available resources with the primary goal of reducing an overall circuit delay-latency to success probability metric. We show that our adaptive routing algorithm with prescheduling can improve on this metric over the on demand case by a factor of 3 to 4.

In Chapter 2 we present an overview of general quantum computing concepts. In Chapter 3 we outline the Quantum CAD flow we developed that allows us to study various quantum circuits and describe where our contributions fit within this flow. Chapter 4 describes how we build ion trap based datapaths and how communication is managed within such datapaths. Chapter 5 presents our teleportation-based long-distance communication network along with designs for the various network components. In Chapter 6, we describe the routing and scheduling algorithms we use within the long-distance communication network. We conclude in Chapter 7 by using our CAD flow to study Shor's factoring algorithm and its major components.

## Chapter 2

## Quantum Computing

Quantum computers differ from classical computers in how they represent a basic data unit. A quantum computer takes advantage of quantum mechanical properties to implement quantum bits, or *qubits*. Similar to classical data bits, a qubit is capable of representing two values such as 0 and 1. Additionally, a qubit may reside in a *superposition*, or mixture of these two values. The power of quantum computers come from this ability to store data in superposition.

In a classical computer a data register can store a single value at a time, e.g., a 4-bit register can be in one of 16 possible states at any given point. If our goal is to run an algorithm on each of the 16 possible inputs in order to determine a single output we generally have to run the algorithm 16 times. Along these lines, every time we add a new bit to the data register we double the amount of computations we must perform.

Using superposition, a quantum computer can potentially outperform a classical computer at this type of task. Rather than only storing a single value in the data register at a time a quantum data register is able to create a superposition of the values, essentially allowing the register to simultaneously be in all possible states at the same time. While we can compute on all of these states simultaneously, the properties of quantum mechanics dictate that when we measure the register's value we will only obtain a single output value. Because of this limitation, quantum algorithms are structured to increase the probability of reading out the correct answer. Using this technique it is possible to run a quantum algorithm a small number of times in order to determine the desired output rather than once for each possible input value as in the classical case.

## 2.1 Quantum States

As we just mentioned, in classical computing the two possible states a bit can be in is 0 or 1. In a quantum computing the equivalent to these base states are  $|0\rangle$  and  $|1\rangle$ . Unlike classical computing, a quantum state can also be in a linear combination (or "superposition") of these base states where the state is described as  $\psi = \alpha |0\rangle + \beta |1\rangle$ . An example of a state in superposition is the state  $\frac{1}{\sqrt{2}}|0\rangle + \frac{1}{\sqrt{2}}|1\rangle$ .

Internally quantum algorithms take advantage of this state information and can ma-

Figure 2.1: Quantum Circuit Model. Small example circuit that operates on three qubits. The sequence of operations is read left to right. Quantum bits are represented by single lines and classical bits are represented by double lines. This circuit contains four single qubit gates, two double qubit gates, and a measure gate. In this example, the measure gate generates a classical bit which is used to control the X gate on qubit A.