# Transistor-Based Ge/SOI Photodetector for Integrated Silicon Photonics

Xi Luo

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2011-41 http://www.eecs.berkeley.edu/Pubs/TechRpts/2011/EECS-2011-41.html

May 8, 2011

Copyright © 2011, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Transistor-Based Ge/SOI Photodetector for Integrated Silicon Photonics

By

Xi Luo

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

In

Engineering-Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Eli Yablonovitch, Chair Professor Ming C. Wu Professor Irfan Siddiqi

Spring 2011

#### Abstract

#### Transistor-Based Ge/SOI Photodetector for Integrated Silicon Photonics

by

#### Xi Luo

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Eli Yablonovitch, Chair

This dissertation describes our effort on developing a technology of photodetectors for application in chip-level optical communication. The photodetector proposed in this thesis work is the Ge/SOI Photo-Hetero-JFET. It is based on a silicon junction-FET in which the traditional electrical gate is replaced by a photo-active germanium mesa. The silicon channel conductance is then modulated by near-infrared light signal incident on the germanium gate.

The limitations of traditional electrical wires which restrict the performance of microelectronic information systems drive researchers to look at optical interconnects as a good alternative for inter-chip data communication. One of the major challenges that the optics solution faces is to achieve as low energy consumption as 100aJ/bit. This in turn sets stringent requirements on the sensitivity of photodetectors, which can only be achieved when the photodetector can be highly integrated and has extremely small device capacitance (<1fF). The Ge/SOI Photo-Hetero-JFET is seamlessly integratable with microelectronic circuitry and also scalable to achieve extremely small capacitance. It was therefore proposed as a promising photodetector design for the application to inter-chip-scale optical links.

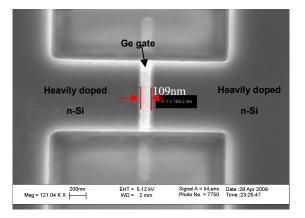

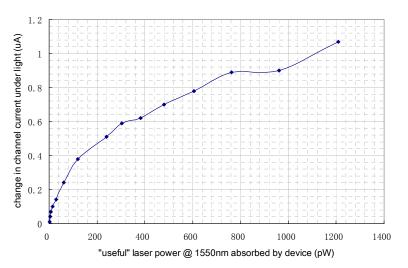

Ge/SOI Photo-Hetero-JFETs with gate length of 100nm are fabricated. They were then characterized as near-infrared photodetectors both under continuous-wave laser and pulsed laser at 1550nm. Geminate recombination together with severe SRH recombination of photocarriers in the germanium gate is found to significantly limit the responsivity of the photodetector. Nonetheless, after correcting for the poor internal quantum efficiency, we found that *one collected photons can lead to the generation of* ~750 *electrons in the silicon channel*, which indicates a DC secondary photoconductive gain of 750 on top of primary responsivity.

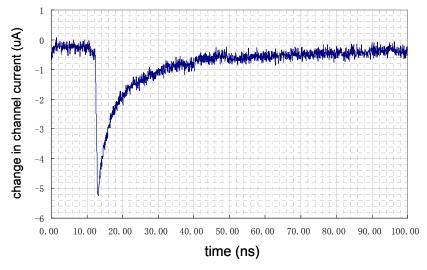

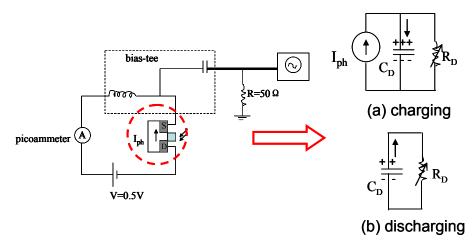

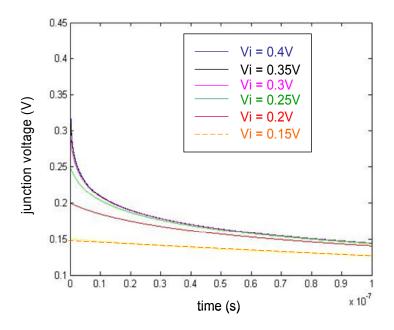

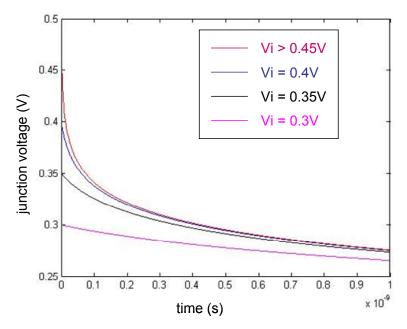

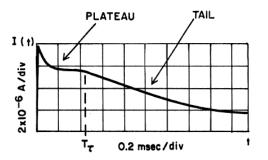

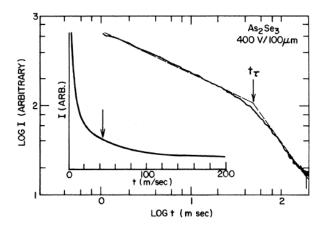

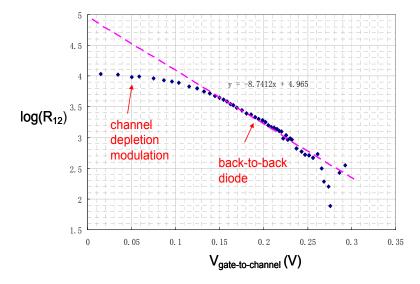

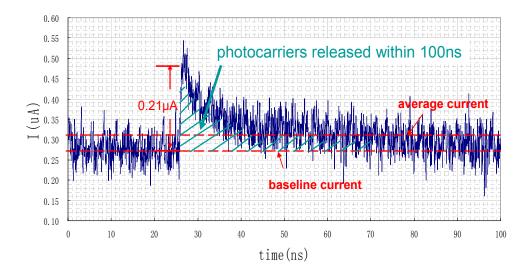

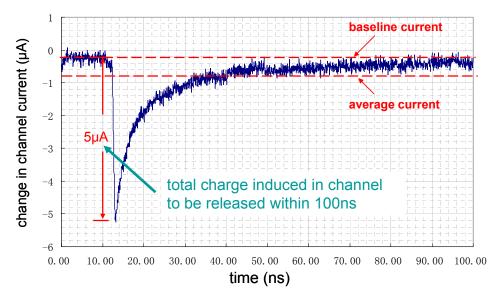

Time-resolved measurement done on the Photo-Hetero-JFET further reveals that the photodetector can respond to laser pulses as short as 4ps. Although the observed risetime of transient photoresponse is 50ps which is currently limited by bandwidth of the measurement circuit, it is believed that when the photodetector is fully-integrated it can achieve its inherent risetime of ~1ps! One caveat regarding the Photo-Hetero-JFET is that its transient photoresponse has a long tail (~26ns fall-time). This was originally attributed to dielectric relaxation process of trapped holes in the gate, but is later found to result from the dispersive nature of photocarrier transport in the defective germanium mesa. In the analysis of peak transient amplitude through JFET model based on trapped charges, we found that with the design of Photo-Hetero-JFET only ~50 photo-holes on the gate/channel junction of  $0.1\mu m^2$  can induce channel current of ~5 $\mu A$ ! This proves that Photo-Hetero-JFETs can also achieve high sensitivity under pulsed illumination.

The attributes of the Photo-Hetero-JFET design that makes the device highly sensitive is its extraordinarily small device capacitance (~52aF) and its seamless integrability with silicon circuitry. Currently, the fabricated Photo-Hetero-JFETs suffer from poor quantum efficiency and slow gain which were brought about by the poor germanium quality. Nonetheless, the device still presents impressive secondary photoresponsivity and great potential in its bandwidth improvement. It is believed that with reasonable germanium film quality, (diffusion length of ~100nm already available in the industry), the Photo-Hetero-JFET is capable of demonstrating great sensitivity and fast speed in the application of chip-level optical communications.

# **Table of Contents**

| Table of C | ontents                                                 | i   |

|------------|---------------------------------------------------------|-----|

| Acknowled  | lgements                                                | iii |

| Dedication |                                                         | v   |

| Chapter 1  | Introduction                                            | 1   |

| 1.1 Mo     | tivation                                                | 1   |

| 1.1.1      | Limitations of electrical wires                         | 1   |

| 1.1.2      | Advantages of optical interconnects                     | 4   |

| 1.1.3      | Challenges for optical interconnects                    |     |

| 1.2 Rev    | view on Ge photodetectors                               |     |

| 1.2.1      | Phototransistors                                        |     |

| 1.3 Pro    | posal of Photo-Hetero-JFETs                             |     |

|            | ganization of this dissertation                         |     |

| Chapter 2  | Design Issues of Photo-Hetero-JFET                      |     |

| 2.1 Fur    | ndamentals of Ge/Si Heterojunction                      |     |

| 2.1.1      | Issues about Ge growth on Si: challenges and approaches |     |

| 2.1.2      | Band Structure of Ge/Si Heterojunction                  |     |

| 2.1.3      | Photocarrier Separation at Ge/Si Heterojunction         |     |

| 2.1.4      | Quantum Efficiency and Diffusion Length                 |     |

| 2.1.5      | Geminate Recombination                                  |     |

| 2.2 Des    | sign of Photo-Hetero-JFET                               |     |

| 2.2.1      | Device structure                                        |     |

| 2.2.2      | Operating Principles of Photo-Hetero-JFET               |     |

| Chapter 3  | Fabrication of the Photo-Hetero-JFET                    |     |

| 3.1 Ma     | terial preparation                                      |     |

| 3.1.1      | Substrate choice and preparation                        |     |

| 3.2 Fab    | prication of heterojunction diode devices               |     |

| 3.3 Fab    | prication of Photo-Hetero-JFET devices                  |     |

| 3.3.1                                             | STEP 1                                                     |    |

|---------------------------------------------------|------------------------------------------------------------|----|

| 3.3.2                                             | STEP 2                                                     |    |

| 3.3.3                                             | STEP 3                                                     |    |

| 3.3.4                                             | STEP 4                                                     |    |

| 3.3.5                                             | STEP 5                                                     |    |

| 3.3.6                                             | STEP 6                                                     |    |

| 3.3.7                                             | STEP 7                                                     |    |

| 3.3.8                                             | STEP 8                                                     |    |

| 3.3.9                                             | STEP 9                                                     |    |

| 3.3.10                                            | STEP 10                                                    | 44 |

| Chapter 4                                         | Device Characterization and Analysis                       | 49 |

| 4.1 Cha                                           | racterization of heterojunction diode device               |    |

| 4.1.1                                             | Responsivity measurements of the heterojunction diode      | 49 |

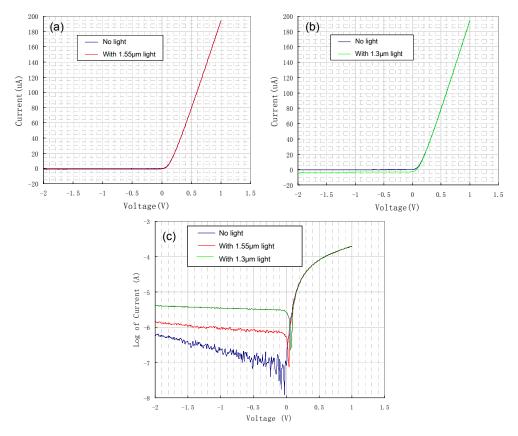

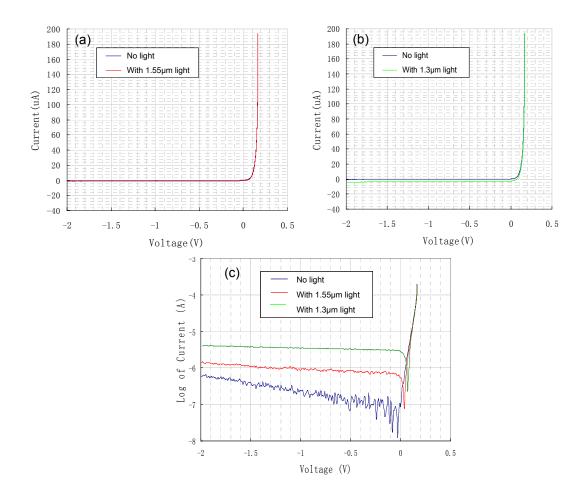

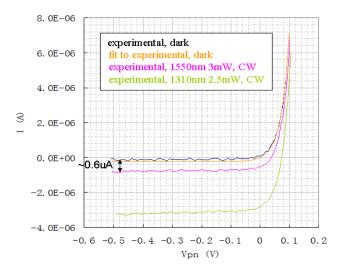

| 4.1.2                                             | Junction I-V curves                                        | 49 |

| 4.1.3                                             | Responsivity and diffusion length                          |    |

| 4.1.4                                             | Estimate of the worst diffusion length                     | 54 |

| 4.1.5                                             | Geminate recombination                                     |    |

| 4.2 Characterization of Photo-Hetero-JFET devices |                                                            |    |

| 4.2.1                                             | Continuous-wave photoresponse                              | 55 |

| 4.2.2                                             | Time-resolved transient response                           | 58 |

| 4.2.3                                             | Rise time of Transient Photoresponse                       | 61 |

| 4.2.4                                             | Fall time of Transient Photoresponse                       |    |

| 4.2.5                                             | Discharging of the heterojunction capacitance              |    |

| 4.3 Furt                                          | her analysis on heterojunction photodiode device           |    |

| 4.3.1                                             | Time resolved transient response of diode devices          | 67 |

| 4.3.2                                             | Dispersive transport                                       |    |

| 4.3.3                                             | Continued discussion of fall-time                          |    |

| 4.4 Moo                                           | deling of the time-resolved response of Photo-Hetero-JFETs | 74 |

| 4.4.1                                             | Physical models for Photo-Hetero-JFETs                     | 74 |

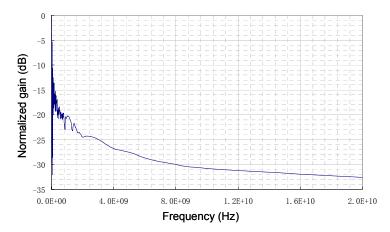

| 4.4.2                                             | Dependence of gain frequency spectrum on Ge film quality   |    |

| 4.5 Con                                           | clusions: Why Photo-Hetero-JFET?                           |    |

| Chapter 5                                         | Conclusion                                                 |    |

| References.                                       |                                                            |    |

## Acknowledgements

During my six-year long journey of PhD, I have been extremely fortunate to work with many nice people. It is their love, encouragement and help that have given me the strength to forge ahead in life. This dissertation would not have been possible without their support. I would like to acknowledge and extend my sincere thanks to all of them.

First and foremost, I would like to thank my research advisor, Prof. Eli Yablonovitch, for giving me the opportunity to work in his group. Prof. Yablonovitch is a truly great advisor and mentor. He is always full of creative ideas, optimism, and had an exceptional ability to communicate his ideas. Without his guidance, encouragement and patience, I would not have been able to go through the struggling moments along and finally finish this work. I enjoyed discussions with Prof. Yablonovitch which were always full of enlightenments and I learned from him how to do research in a really scientific manner. His deep insights and wide visions have definitely changed my research outlook and will keep driving me to pursue the best science in the future career.

I have spent my PhD years in two great universities, first three years at UCLA and the next three at UC Berkeley, and I consider such an experience as a great opportunity since I could get valuable inputs from more people than I could have met if I had stayed in one university throughout. I was very fortunate to have Prof. Chandrashekar Joshi, Prof. Aydogan Ozcan and Prof. Hong-Wen Jiang to serve on my qualifying committee when I was at UCLA, and Prof. Ming C. Wu, Prof. Connie J. Chang-Hasnain and Prof. Ramamoorthy Ramesh on my qualifying committee when I retook the qualifying exam at Berkeley. I greatly appreciate their instructive and helpful advice on my thesis project. I am also thankful to Prof. Ming C. Wu and Prof. Irfan Siddiqi who serves on my dissertation.

This work could not have been done without my coworkers. Subal Sahni started this photodetector project in this group and introduced me into this new field. He was more like a tutor in my first two years in UCLA. Special thanks to him for his training on almost all microfabrication processes and experimental procedures. I would also like to thank my other coworkers, Japeck Tang and Shantha Vedantam at UCLA, all members in the optoelectronics group at UC Berkeley, and all other residents in Cory 258M for their fruitful discussions with me that help me keep this project on the right direction, and for the support and encouragements they gave me during the last six years. The Nanolab at UCLA and the Microlab at Berkeley are where I spent long hours fabricating these photodetector devices. I want to thank all staff and colleagues that I've made friends with there who helped me with various cleanroom situations and keep me companied during the late hours and weekends.

My parents are a constant source of support during the course of my life. All that I have achieved until now would not have been possible without their endless love, support, and guidance. No words are sufficient to thank them here. Last but not the least, I want to thank my boyfriend for his support and help during my struggling days of completing this dissertation, and for his love that has made the last days of my PhD life so beautiful.

# **Dedicated to**

# My parents for their love and guidance

## **Chapter 1** Introduction

This dissertation describes our effort in creating a technology of photodetectors which can accelerate the realization of chip-level optical interconnects. The criteria that are being sought in such photodetectors in alignment with those of optical interconnect technology, are high integration with silicon circuitry and great photo-sensitivity.

This introductory chapter begins with a brief description of the background and motivation for our work. The reasons why optical interconnects are a most promising candidate to replace problematic electrical wiring at the chip-level are summarized. The challenges that chip-level optical links are facing are presented, and the conclusion they lead to, in terms of the receiving end, is that, very sensitive germanium photodetectors with extremely small device capacitance are essential. Then different forms of phototransistors are discussed and reviewed. Finally, the organization of the dissertation is presented.

### 1.1 Motivation

As the microelectronic systems continue to scale down along the projection by Moore's Law, the individual logic elements in the systems have become significantly smaller and faster. Computational speed of the systems is therefore no longer limited by the individual logic elements, but by the communication between them. Indeed, this bottleneck is considered as one of the biggest challenges in the future advancement of integrated electronics [1].

Traditional electrical wiring historically has been an efficient and economic means of communication at various levels of electronic systems, and currently it still dominates the links in and between electronic chips and circuit boards. However, as the volume of chip-to-chip and on-chip communication rockets up, due to the inherent physical properties of electrical wires, it becomes increasingly difficult for them to cope with the growing bandwidth demand. For this reason, optical links have been proposed as a most promising candidate to replace electrical wires and revolutionize the chip-level communications. As a matter of fact, optical fibers have long taken over electrical cables in long-haul telecommunication and optical data links are now extensively employed between cabinets in large systems too. Nonetheless, to use optics at ever shorter distances, all the way down to inter- and even intra- electronic chips, there are technological challenges to solve.

### 1.1.1 Limitations of electrical wires

One of the limitations of electrical wires is that they are inherently lossy [2]. Resistance

of the conductors, together with other factors including dielectric loss, causes electric signal to attenuate. Such attenuation is usually worse for higher frequencies, which leads to distortion of signals. There are techniques such as amplification and equalization that can be used to compensate attenuation and distortion to some extent, and advanced signal formats and signal processing are also used to maximize the information capacity in presence of these imperfections [3]. However, all these techniques increase the complexity of the system and hence increase cost and power dissipation.

It seems that a simple solution to increase information capacity for a given wire is to increase its cross-sectional size, which reduces its resistance. But this increases costs for long lines and also limits the density of wiring in large complex systems. In fact, in these systems, the limited available space tends to be filled with wiring, and equally importantly, to be used to deliver power and remove heat from the system. In this sense, information processing systems tend to be simultaneously limited by wiring density and power [3].

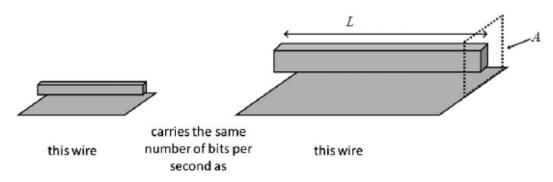

It is found that one cannot increase the information capacity either, by simply scaling down the wires and increasing the wiring density. For bulk-resistance-limited RC lines, scaling down a wire in all three dimensions leaves the RC product the same (Fig.1-1), and if the RC product characterizes the minimum allowable bit time for simple on-off signaling, then such scaling has no effect in changing the number of bits per second that can be transmitted through the wire. For skin-effect-resistance-limited LC lines, the scaling of information capacity for simple on-off signaling follows a similar scaling law. It is actually shown that, at least with a simple model of on-off signaling, the capacity of electrical lines from such resistive limits obeys approximately [2]

$$B \le B_o \frac{A}{L^2},\tag{1.1}$$

where A is the cross-sectional area of the wiring, L is the length of the wires, and  $B_o$  is a constant (~10<sup>16</sup> bits/s for RC-limited lines and a slightly smaller number for LC-limited lines). Equation (1.1) also holds if A is the total cross-sectional area of the wires, not just of one wire. Therefore, by packing smaller wires more densely into a system won't help in increasing the information capacity. It doesn't help either by making the system smaller or bigger once all available space is filled with wiring.

Going beyond simple scaling, there are signal compensation and sophisticated signal processing techniques to expand the information capacity. But as we mentioned previously, these surely raise the costs as one tries to push past the scaling limitation to the information density in electrical wires. The physics of electrical lines also leads to other problems in signal integrity for dense and high speed wiring, including slow effective signal propagation velocities (e.g.,  $\sim 5\%$  of the velocity of light), and cross-talk between adjacent wires. The limited bandwidth of electrical wiring also limits the time

precision for clock distribution.

Fig.1-1 Simple scaling of electrical wiring does not change the RC product. For simple signaling where the RC product would set the shortest pulse to be readily sent on the line, the bit rate capacity of the line is unaffected by the simple scaling (reproduced from ref. [2]).

Apart from wiring density, interconnect energy also limits the performance of modern information processing systems. In fact, among three core operations - logic switching, memory and interconnect, it is the interconnect that accounts for most of the energy dissipation [3], and that energy is almost all associated with charging and discharging the capacitance of electrical wires. For example, in a CMOS gate [4], the capacitance of the transistor is roughly equal to the capacitance of a wire connecting this gate to the adjacent one. So the energy associated with charging or discharging transistor capacitance should be on the same scale of charging or discharging that short interconnect line. For information sent further than the adjacent gate, the energy for charging or discharging the interconnect line can easily exceed that required for the switching of a logic gate. In memory banks, however, the energy dissipation on the interconnect lines is even more severe since memories are usually addressed while whole sets of lines are charged or discharged in reading or writing a single cell. So again the reading and writing energy energy dissipated in interconnect lines - is much larger than that required to retain a bit of information reliably in the memory cell. Other sources of energy dissipations in information processing systems include static dissipations associated with leakage and subthreshold currents. Also, for each unit of energy spent on the core operations, approximately equal or greater energy is to be spent on supplying and conditioning power and sinking thermal dissipation. In fact, information processing systems are increasingly constrained by energy dissipation. Since interconnect energy dominates energy dissipation of the core operations, and can possibly dominate that of the entire signal processing, it is imperative to find ways to reduce the energy dissipated in the interconnect lines.

In short, with electrical interconnects, wiring density and energy are two main issues that hamper the advancement of signal processing systems. The inherent properties of electrical wires, however, determine that one can only minimize these problems to some extent with sophisticated schemes at the expense of system costs. Therefore, a fundamentally different interconnect technique needs to be available to completely solve the existing problems.

#### 1.1.2 Advantages of optical interconnects

Optical interconnects have been proposed as one of the promising candidates to replace traditional electrical wires. In long-haul telecommunication systems, optics has long been the sure choice of communication thanks to extremely low loss and low dispersion of optical fibers. The technical optimization at that system scale is basically designing the fiber system to operate over the longest possible distance with highest possible bandwidth, and thereby the size, power dissipation and even cost of optical transmitters and receivers are of secondary importance. However, when it comes to interconnects at shorter distances, interconnect density and power dissipation are of particular importance [3], neither of which is critical at longer distances.

The use of optics can improve the density of interconnections in the systems with shorter interconnects. The reason behind it is that optical fibers or waveguides do not have the resistive loss physics that limits the capacity of electrical wires [2]. This density advantage is one major reason that has been driving the introduction of optics between cabinets, inside machines and onto chips. For interconnections between backplanes, although electrical cables can carry substantial amount of information over that distance, optical cables however can perform the same job with much smaller cable diameters, and as a result, with greater connection densities. For ever shorter interconnections, especially at chip-level, optical links with the density benefit offer us with a prospect to overcome the notorious scale-invariance of the capacity of electrical wires. In addition, the use of wavelength-division-multiplexing (WDM) further boosts the information capacity of optical channels. In fact, optical fibers themselves are capable of carrying extraordinarily high densities of information. For example, single-mode telecommunication fibers, with a diameter of only 125µm, can carry tens of terabits per second of information [5]. Admittedly, preparing the information in the right form to exploit that bandwidth is never a simple task, and involves many high-speed transmitters and receivers as well as sophisticated wavelength-division multiplexing. Nonetheless, with fiber itself or optical waveguide there is practically no limit to the information capacity for the foreseeable future [3].

Severe power dissipation of electrical wiring is another major constraint on the performance of information processing systems. For optical interconnects or any other technologies to replace copper wires, they must consume much less power than their electrical counterpart. One might argue that this does not seem to be an advantage for

optics at all, since in the long distance optical communication, transmitters and receivers typically consume significant amounts of power, and thus one would not expect that the same technology employed at shorter distance would offer advantage in power dissipation. The reason behind this opinion at first glance is that the main strategy in designing the long distance optical communication is to work with the minimum received optical power, not the *minimum total energy per bit communicated*. But when it comes to interconnects at short distances, the total energy per bit, including the power of both the transmitter and receiver, becomes the primary concern [3].

The remarkable quantum-mechanical nature of optics readily offers the benefit of power efficiency, making optical interconnects fundamentally different from electrical wires. While in electrical systems, the energy required is at least that needed to charge the line (or at least the section of the line that corresponds to the length of the electrical pulse) to the signal voltage. In optical systems, the signal voltage that is generated in a photocell is weakly connected to the power for the light beam. In other words, the voltage can remain constant - numerically equal to the photon energy in electron volts, even if the optical power is tuned down. This eliminates the need to "charge" the optical line fully to the signal voltage. Another aspect of looking at this is "quantum impedance conversion" [6], i.e. the quantum detection in the optical case effectively matches the high impedance of small devices to the low impedance of the electromagnetic propagation (~50 $\Omega$  in cables, ~377 $\Omega$  in free-space propagation).

It has been realized that in optical interconnects at shorter scale, the primary goal of minimizing energy per bit communicated is not the same as optimizing for the minimum received energy, since the energy required to run the receiver amplifier to boost up that minimum signal may well exceed the energy "saved" earlier. For the exact same physics that cell phone batteries go away very fast in weak signal zone, the receiver amplifiers tend to consume much more power if it is operated under weak signals, in fighting with the thermal noise limit. Hence, it is not surprising that in minimizing the total energy dissipated per bit in a short link, the strategy that finally comes out is to deliberately use more received photons to prevent the receiver amplification stages from being noise-limited [7], and requiring more receiver power.

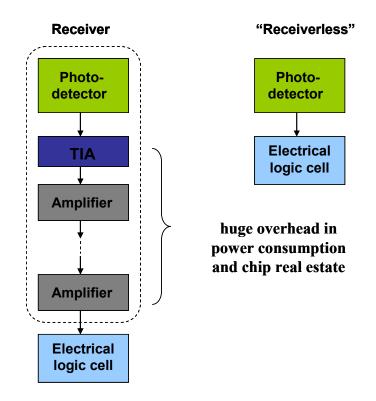

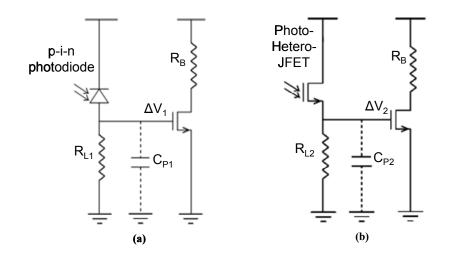

It is even desirable to run the receiving end of an optical link without amplification stages. In a traditional optical receiver, the photodetector converts an optical signal into electrical current which is later converted to electrical voltage by a trans-impedance amplifier. The voltage is then amplified by subsequent amplification stages before it is sent to the logic unit (see Fig.1-2). Obviously, this configuration has huge overhead in power consumption and chip real estate. So in face of energy and density constraints on the interconnect technologies, there's indeed an urge to get rid of all the amplifications in the receiver and operate the photodetector "receiverless" [8]. It is also entirely possible to have input

optical pulse with sufficient energy to swing the photodetector over a full logic range. The key point is that interconnect receivers should have extremely low photodetector capacitance. For instance [3], with total detector and input transistor capacitance of 1fF, a fJ of 1eV photons (~6000 photons) would generate ~1V swing in the photodetector. It should be noted that 1fF of detector capacitance is readily achievable in micrometer-sized detectors integrated beside or within the receiver transistors. The energy benefit of optics from quantum impedance conversion applies to the transmitter side as well, but since this thesis work is devoted to the receiving end of the chip-level optical links, we would not dwell on the discussion of transmitter here.

Fig.1-2 Traditional receiver configuration in comparison with "receiveless" configuration

In addition to density and energy benefits, optics offers improved signal integrity and timing [3]. Low dispersion of optical channels permits the propagation of short pulses over long distances without being substantially broadened, and thereby ensures the precise timing of signals. Another reason for improved timing precision is that the propagation velocity of optical signals is less temperature dependent than that of electrical ones. Optical interconnects should have reduced cross-talk too, and even if there is cross-talk, it is not dependent on bit rate which is always much lower than the carrier frequency.

With all the benefits that optics enjoys, optical interconnect boasts great potential to

replace electrical wiring. However, as the technology of electrical interconnects has evolved to be very advanced and inexpensive, for optics to have more compelling reasons to replace its electrical counterparts, certain technological challenges have to be met.

#### 1.1.3 Challenges for optical interconnects

The technology of optical interconnects at short distances, especially down to chip-levels, is still immature in competition with that of electrical wiring. That's why in spite of all the problems and constraints mentioned above, wires still convey the traffic within and between chips. Admittedly, the technologies associated with long distance optical communication are quite developed, but they cannot be readily transferred to the technology of dense, short-distance optical interconnects, as they were not designed for the same optimization criteria. While optical data links are currently being used extensively between backplanes and boards, at even shorter scale, i.e. chip-level communications, they haven't proven an obvious advantage in power efficiency over electrical wires

The energy dissipation for electrical wiring at different length scales is estimated as follows. The total dissipations of present high-performance electrical interconnects on backplanes are in the scales of a few tens of pJs per bit. For connections on and off chips, energies of several pJs per bit can characterize up-to-date low-energy interconnects. When it comes to the global interconnect lines on chips,  $\sim 1pJ/bit$  is a typical number [9]. Based on these state-of-the-art numbers for electrical wiring, when we seek solutions with optics, we should aim at targeted energies at least one order of magnitude lower, which means  $\sim 1pJ/bit$  for backplane connections, and  $\sim 100fJ/bit$  for intra-chip and global on-chip wiring. The reason to set the target an order of magnitude lower is to leave enough margins to justify serious consideration of replacing electrical wires with optical interconnects.

Now that the total system energy is set to be 100fJ/bit, the estimated received optical energy would be ~1fJ/bit [3]. Note that this estimated value is obtained after taking into considerations of various losses and energies dissipated in performing driver, receiver and etc. As analyzed earlier, to generate substantial voltage (~1V) with 1fJ photons of ~1eV to drive the logic gate, the total photodetector-plus-transistor capacitance should be as low as 1fF. This extremely small capacitance is only possible for photodetectors fully integrated with the circuitry on chip, since a wire of only 10µm length already has capacitance of a few pFs. Therefore the technological challenge for chip-level optical interconnects at the receiving end is to have a photodetector which is *highly-integrated* and has *extremely small device capacitance*. This is exactly how we were led to our design of Ge-on-SOI Photo-Hetero-JFETs.

Similarly, there are technical challenges for optical output devices like lasers and modulators at the transmitter end of the optical link. The energies of these optical output devices need to be in the scale of a few tens of fJ/bit and these devices need to be well-integrated to minimize its capacitance too [3]. Vertical cavity surface emitting lasers are likely to be 1pJ/bit systems, and 100fJ/bit systems would require more radical lasers like nanocavity lasers [9]. But those lasers cannot be easily integrated with silicon. Modulators with an external light source is a feasible strategy. Admittedly, silicon-based modulators suffer from the weak electro-optic effect in Si, and the use of high Q resonators requires precise temperature control. Nonetheless, high-O resonator Si modulator and other CMOS compatible modulators, such as germanium modulators based on Franz-Keldysh effect [10] and germanium quantum wells based on quantum-confined Stark effect (QCSE) [11,12], can still be good candidates for on-chip optical output devices. Since this thesis work is devoted to photodetectors in the application of chip-level optical communications, we will leave the discussion of the transmitter end, and in the following section, we'll review various germanium photodetectors reported from literature.

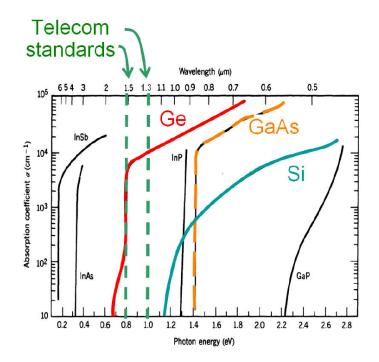

Fig.1-3 Absorption coefficient for various semiconductor vs. photon energy (reproduced from ref. [1])

#### **1.2 Review on Ge photodetectors**

Major advances made in recent years in the field of silicon photonics have a path well aligned with research in chip-level, short distance optical communications.

Germanium-based photodetectors are certainly one of them. The reason for choosing germanium over other semiconductors as a photodetector material is that it can be grown in CMOS compatible processes for ease of integration with silicon and it absorbs well at communication wavelengths (1.3 $\mu$ m and 1.55 $\mu$ m) where attenuation and dispersion in fibers are lowest (Fig.1-3). Other reasons in choosing germanium photodetectors over silicon include higher carrier mobility in Ge which promises faster operation.

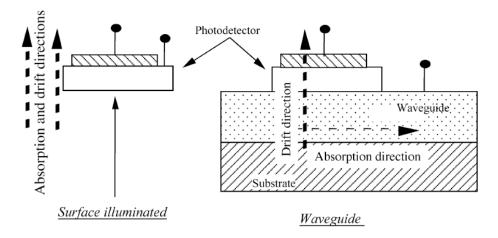

Fig. 1-4 absorption and drift directions are decoupled in a waveguide photodetector allowing for independent optimization of efficiency and speed (reproduced from ref. [16]).

Since chip-level optical interconnects require high-speed and low-capacitance photodetectors, the active regions of photodetectors need to be made very small, i.e. subwavelength. But with a subwavelength active region, the coupling efficiency of light to and hence the absorption efficiency of the active region would be very poor. Nanometallic focusing structures (e.g. C-shaped nanoaperture [35] and dipole antenna [36]) were therefore built around the tiny detectors to enhance the optical near field to significantly improve its responsivity as well as speed. However, p-i-n photodiodes usually have relatively large capacitance which limits high-speed operation and raises energy requirements in the chip-level interconnect systems.

Among photodiode structures, metal-semiconductor-metal (MSM) photodiode is considered one of the most promising candidates for receiver optoelectronic integrated circuits due to its ease of integration with preamplifier circuits, low detector capacitance, and large device bandwidth. But the problem with MSMs made on Ge and Si is high dark current associated with a lower bandgap of the semiconductor, which leads to extra power consumption. The scheme of asymmetric electrode design was introduced and has proved to effectively suppress the leakage in MSM photodetectors [29].

Germanium avalanche photodetectors (APDs) using charge amplification close to

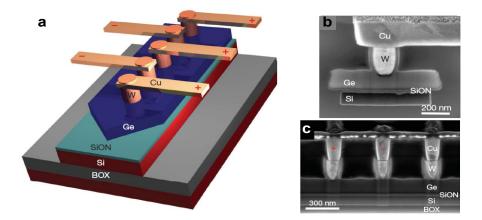

avalanche breakdown, can achieve high gain and detect low-power optical signals, so they can be candidates of the photodetector in chip-scale optical interconnects. But Ge APDs are universally considered to suffer from an intolerably high amplification noise [37]. Although by using separate silicon layer for amplification and germanium layer only for detection of light signal, high gain with low excess noise has been demonstrated [31], the relatively thick semiconductor layers limit APD speeds to about 10GHz and in the meantime require excessively high bias voltage of around 25V. However, researchers at IBM T. J. Watson Research Center recently demonstrated a germanium waveguide-integrated APD [30] (Fig.1-5), in which by shaping the electrical field on nanometer-scale they dramatically reduced the amplification noise by over 70%. With nanophotonic and nanoelectronic engineering, strongly non-uniform electric fields is generated in metal(W)-germanium-metal diodes so that the region of high electrical field for impact ionization in germanium is reduced to just 30nm at the vicinity of the tungsten plug. This extremely small region of avalanche multiplication benefits the device with dramatic reduction of noise, mainly for the reason that the thin gain region favors a "more deterministic statistics of ionization process" and "a narrower ionization-path-length probability distribution function". Furthermore, this Ge APD of very small size only needs a bias voltage of only 1.5V to achieve an avalanche gain of over 10dB with operational speeds greater than 30GHz. The resulting bandwidth-gain product of 300 is among the highest ever reported for APD photodetectors. Although this reinvention of Ge APDs seems to solve some major problems of avalanche photodetector, they still suffer from inherent reliability and thermal issues.

Fig. 1-5 Ge waveguide-integrated APD (a) Schematic; (b) SEM image of lateral cross-section; (c) SEM image of longitudinal cross-section (reproduced from ref. [30]).

#### **1.2.1** Phototransistors

Phototransistors are another form of photodetectors, besides APDs, that have internal

gain added upon primary responsivity. Combining a detector and a transistor into one compact device is an excellent approach towards realizing the "receiverless" photodetector which is desired in chip-level optical interconnects. Such a device should be easily integrated into state-of-the-art transistor chips and can be readily scaled down as a transistor to obtain extremely low device capacitance. The additional gain mechanism, i.e. transistor gain, also helps to relieve the requirement on input light level which would otherwise be quite stringent with only primary photo- responsivity.

The concept of phototransistor was introduced shortly after the demonstration of the first transistor in 1947. However, it was Shockley et al. in their 1951 paper [38] who first proposed the idea of using the bipolar transistor configuration as a phototransistor, and afterwards, even various other types of transistors emerge, when people talk about "phototransistor", unless otherwise specified, by default they mean the bipolar configuration. Shockley also pointed out that in the phototransistor photo-induced hole-electron pair generation replaces carrier injection by the emitter junction. Thus the bipolar configuration was actually realized in germanium [39]. It was a homojunction phototransistor with gain or quantum yield of  $\sim$ 100. The performance of the phototransistor was later found to be improved by using an emitter with wider bandgap than base. This idea of "wide-gap" emitter was first proposed by Shockley [40] and Kroemer [41].

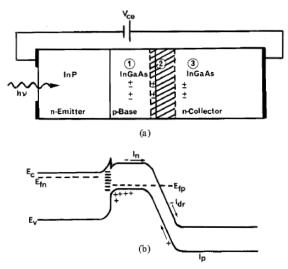

Fig. 1-6 Operation of a floating base HPT: Schematics of (a) cross-section view and (b) energy-band diagram (reproduced from ref. [42])

Fig.1-6 shows the schematics of a heterojunction n-p-n phototransistor (HPT) with a floating gate and its energy-band diagram [42]. The InP emitter has a bandgap energy approximately 0.6 eV greater than that of the InGaAs base and collector. The emitter injection efficiencies close to unity can be achieved in the heterojunction transistor

regardless of the relative base-emitter doping levels. Unlike homojunction transistors which require a lightly doped base and a heavily doped emitter for efficient injection from the emitter to the base, the barrier at emitter-base heterojunction of the HPTs alone can prevent reverse injection from the base. Hence a heavily doped base can be used to reduce the base resistance and a lightly-doped emitter can be utilized to decrease the base emitter capacitance. Light is incident through the transparent InP emitter and is absorbed primarily in the base region, although some absorption also occurs in the base-collector depletion region. The optically generated holes are trapped in the base region and the accumulation of excessive holes causes an increase in the forward bias of the emitter-base junction, or equivalently lowers the barrier for electrons to flow from emitter to base [43]. Current amplification is thus achieved by ordinary transistor action when the base width W<sub>B</sub> is smaller than the electron diffusion length L<sub>D</sub> in the base. The speed of a phototransistor is limited by the charging times of the emitter and collector [1]. So HPTs improve the speed over that of the homojunction ones with both smaller base resistance and less base-emitter capacitance. It was also found [44][45] that by adding a base terminal and with an optimally chosen external bias current, the phototransistor can run faster with enhanced optical gain.

In spite of all these improvements in performance, the gain-bandwidth products achieved of phototransistors were limited and never exceeded that of APDs. Also heterojunction phototransistors were considered too costly to be commercially feasible [1]. The research on phototransistors was then taken over by other photodetector technologies like APDs. However, now that with the ongoing research in chip-scale optical interconnects which asks for well-integrated "receiverless" photodetectors, there should be revived research interests on phototransistor. Furthermore, the improved capabilities of growing germanium on silicon wafers permits the HPTs to be built on Ge/Si hetero-stacks and thus solved problems with compound semiconductor (III-V) technologies which lack the vital cost-effective integration capacity with advanced Si VLSI technology.

Historically, photosensitive transistors with field-effect transistor (FET) configuration have also been the subjects of interest. These photo-FETs include PD-FET [46], MESFET [47] and MOSFET [32]. The advantages of this type of photo-transistors that combine high-impedance amplifiers with built-in photodetectors are believed to have very fast response and high optical gain. However, there have been some debates over the origin of gain observed in these FETs [47][48]. Various experimental evidences indicate that the gain in FETs can actually be a complicated combination of several mechanisms, including photoconductivity gain [47], transconductance gain due to the photovoltaic response of the gate or the substrate-channel junction [48], and the channel conductance modulation due to field screening by the generated photocarriers [46][32].

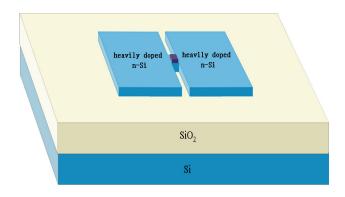

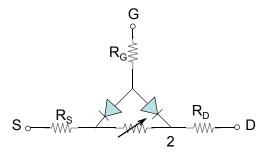

#### **1.3 Proposal of Photo-Hetero-JFETs**

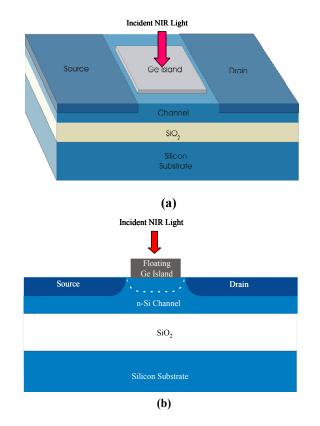

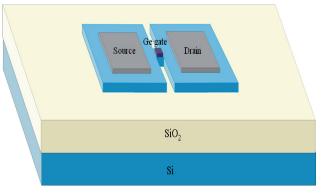

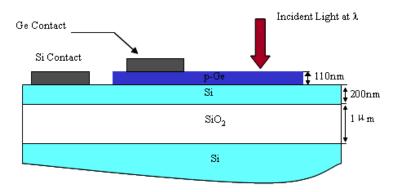

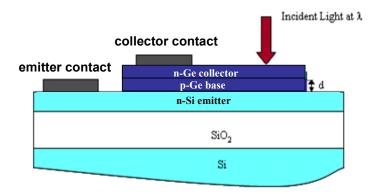

In our effort to create a technology of photodetectors to accelerate the advance of chip-level optical interconnects, we proposed a type of germanium photodetector with the field-effect transistor configuration [49]. The device structure is presented in Fig. 1-7, which integrates a Ge/Si heterojunction photodiode with a field-effect transistor. In other words, it is essentially a junction-field-effect transistor with a floating photosensitive germanium gate. In this photosensitive JFET, incident near-infrared light replaces the traditional electrical gate voltage to modulate channel conductance and thus turn the JFET on. The device is therefore named as Photo-Hetero-JFET.

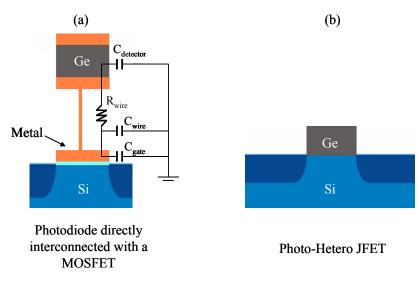

Obviously Photo-Hetero-JFET can be seamlessly integrated onto silicon chips and can be scaled down with the silicon technology to obtain an extremely small capacitance. Secondary gain added to primary photoresponsivity further enhances photosensitivity of the device which helps to relieve the otherwise stringent requirement on the input optical power. Another advantage of this device is that with no electrical wires connecting the gate the photodetector capacitance is not limited by the non-scalable wire capacitance.

Fig.1-7 Device structure of Ge/Si Photo-Hetero-JFET (a) three-dimensional view (b) cross-sectional view

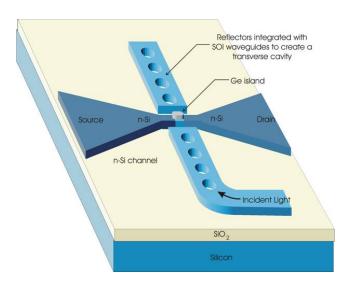

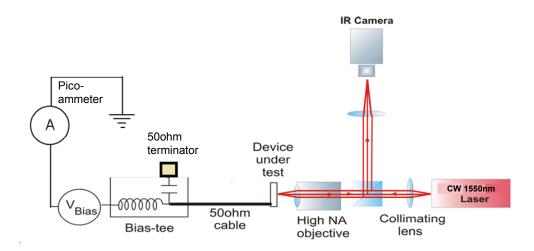

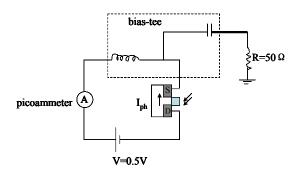

Near-infrared light can be coupled to the photosensitive germanium gate at normal incidence as shown in Fig. 1-7. That's how the Photo-Hetero-JFETs are characterized in our lab setting (you may refer to Chapter 4 for details of the experimental set-up). When the photodetector is built onto chip, light can then be coupled to the germanium mesa through a silicon waveguide. Fig. 1-8 shows a possible configuration of routing light signal through waveguide and sending it to the Photo-Hetero-JFET, with both the waveguide and the photodetector built on an SOI platform. An array of holes with periodic spacing is etched at the end of the waveguide to form one-dimensional photonic crystal reflector. With the same reflector placed on the other side of the photodetector, the light coupling efficiency can be greatly enhanced. This cavity-enhanced configuration is useful in counteractingthe poor coupling efficiency when the germanium gate is scaled to an extremely small size for lowest capacitance.

Fig. 1-8 Photo-Hetero-JFET in waveguide-coupled and cavity-enhanced configuration

#### **1.4 Organization of this dissertation**

This chapter gave the introduction to the background and the motivation of this thesis work. It looked at the limitations of electrical interconnects in chip-to-chip and on-chip communications, and introduced optical links as a most promising candidate for replacement. It then discussed the technological challenges of the chip-scale optical interconnect with a focus on its receiving end. The conclusion is that the photodetectors in the chip-level optical interconnect should be *highly-integrated* and have *extremely small device capacitance*. This chapter reviewed the various types of photodetectors including phototransistors, which finally lead to the proposal of the subject of this thesis work, Ge/Si Photo-Hetero-JFETs.

Chapter 2 looks at design issues and operating mechanisms of Photo-Hetero-JFETs. It starts from the basics of Ge/Si heterojunction by looking at heterogeneous growth of Ge on Si, and mechanism of photovoltaic response in the Ge/Si heterojunction. Based upon that, it then discusses the design of the Photo-Hetero-JFETs including its device structure and operating principles.

Chapter 3 looks at the fabrication of both heterojunction diode devices and Photo-Hetero-JFETs in great details. It describes the challenges in fabricating the nano-gate phototransistor and techniques exploited in tackling them.

Chapter 4 is devoted to the experimental characterization and analysis of the Photo-Hetero-JFETs that has been fabricated. Both steady-state and time-resolved transient response of Photo-Hetero-JFETs are obtained and analyzed. It also looks at the performance of heterojunction diodes both under continuous-wave and pulsed illumination, which provides very important physical insights in understanding the performance of the hetero-JFET device. Different models are attempted in analyzing the device, and it is found that the poor germanium material quality may have severely limited the quantum efficiency and slowed the gain.

Chapter 5 proposes future work in improving the Photo-Hetero-JFETs. It also looks into other possible types of germanium photosensitive transistors with potentially great sensitivity before it concludes this dissertation.

### Chapter 2 Design Issues of Photo-Hetero-JFET

As described in the previous chapter, the Photo-Hetero-JFET is based on a silicon JFET structure, with a germanium floating gate absorbing near-infrared light and hence modulating the silicon channel conductance. Therefore, in this photonic "junction field-effect transistor", the germanium/silicon heterojunction is where all interesting physics of this Photo-Hetero-JFET happens. This chapter will start from the fundamentals of Ge/Si heterojunction, then explore the operating principles, and from there, discuss the design issues of the JFET phototransistor.

#### 2.1 Fundamentals of Ge/Si Heterojunction

#### 2.1.1 Issues about Ge growth on Si: challenges and approaches

The first challenge of integrating Ge with Si is the difficulty of epitaxially growing germanium on silicon, which comes from the 4% mismatch between their lattice parameters. This large difference in their lattice constants severely limits the thickness of the pure defectless germanium film that can be grown on silicon substrate.

During the heteroepitaxy process, the first Ge layer deposited aligns its atoms to those of silicon substrate. This creates compressive strain in Ge along the growth plane and tensile strain along the normal plane. Such strain is accumulated during the following epitaxial growth until the distorted energy is big enough to relax the film through inserting misfit dislocations - usually extra planes of atoms. This occurs when the film reaches the thickness defined as the "critical thickness" [50]. These misfit dislocations are confined to the interface of the epilayer and the substrate, and are energetically stable even after the critical thickness is reached. However, the more detrimental dislocations in the epitaxial film, in terms of their effects on device performance, are threading dislocations. They are the byproduct of the misfit dislocation formation and typically thread from epi-substrate interface to epilayer surface, as dislocations cannot end in a crystal and have to either form a loop or terminate at a free surface [1]. These dislocations are sites for carrier recombination which results in reduced responsivity and large leakage currents in photodetectors. Apart from introducing large density of dislocations in the device film, accumulated strain during growth also energetically favors 3-D island formation at surface [50] instead of layer by layer growth, leading to high surface roughness, which may cause difficulty in process integration.

Owing to the 4% lattice mismatch of the Ge/Si system, the critical thickness of pure Ge epitaxially grown on Si substrate is shown to be only around 10Å [51][52]. Given the absorption length of near infrared light in pure germanium being a few microns [13], any

germanium photodetectors of practical use would have device layer much thicker than the critical thickness and with low density of dislocations.

There have been many reported techniques of obtaining germanium epilayers of good quality on silicon substrate [53-77]. These novel approaches have resulted in threading dislocation densities in the range of  $10^7 - 10^9$  cm<sup>-2</sup>, and have enabled the realization of efficient germanium photodetectors as well as germanium transistors. Some of the important works and techniques are summarized in the following to show the extensive efforts put and successes achieved in this field.

The method of graded buffer layers was demonstrated by Fitzgerald *et al.* [53-55]. They grew SiGe relaxed graded buffer layers on Si at high temperature, and showed that high quality relaxed epilayers with Ge content from 0-100% can be grown. By staying within the low mismatch region with the introduction of each grading layer, they only introduced a small number of new dislocations which prevents massive dislocation nucleation, interaction and multiplication events that would otherwise increase threading dislocation density. In addition, the low mismatched layer grown provides the strain to glide dislocations out of the edge of the substrate. This graded buffer technique, together with an intermediate Chemical Mechanical Polishing (CMP) step, was able to reduce the threading dislocation density in the final Ge film to a record value of  $<2\times10^{6}$  cm<sup>-2</sup>. Instead of relaxed graded buffer layers, Luryi et al. used strained superlattice buffer layers, each within critical thickness, to minimize the insertion of dislocations [56]. It is believed that strain can also act as a barrier to the vertical movement of threading dislocations. With the technique of superlattice buffer layers, they successfully demonstrated p-i-n germanium detectors on silicon with a quantum efficiency of 40% at 1300nm [56]. Researchers also reported the method of low temperature Si buffer layer [57-61]. They demonstrated dramatic reduction of the threading dislocation density in the SiGe layer after the insertion of a low-temperature MBE grown silicon buffer. The suggested mechanism for this improvement is that point defects in the silicon buffer layer can trap the dislocations [62].

A very high temperature MBE process (at 900°C) was utilized by Malta and his co-workers to achieve localized germanium melting and alloying with silicon, thereby confining extensive threading dislocations near the Ge/Si interface [63]. Etch pit density measurements on the germanium films showed that the dislocation density in Ge bulk away from the epi/substrate interface was as low as  $10^5 \text{ cm}^{-2}$ .

Various thermal treatments are also used to anneal out defects and thus reduce dislocation density. After growing a thin germanium buffer layer followed by thick layer at elevated temperature, Kimerling *et al.* subjected the film to **cyclic temperature annealing** treatment. With that, they have built p-i-n photodetectors on 4µm germanium layers on

silicon, which showed responsivity of 0.89A/W at 1300nm [64]. Multiple Hydrogen Annealing for Heteroepitaxy (MHAH) is another thermal treatment technique introduced to grow high quality pure germanium on silicon with low threading dislocation density [65,66]. In this technique, in-situ annealing is carried out at a higher temperature in an H<sub>2</sub> ambient after a thin germanium buffer layer is first grown heteroepitaxially on silicon. Such annealing is shown to reduce the surface roughness by 90% and relieve stress in the first few tens of nanometers. After that, more germanium is then grown homoepitaxially on this virtual germanium lattice with no introduction of defects. Okyay *et al.* have used this technique to grow germanium and fabricated an integrated germanium photodetectors on silicon [1]. They've obtained 50× reduction in threading dislocation density with final density of  $1.5 \times 10^7$  cm<sup>-2</sup>.

**Selective growth** has been shown to effectively reduce the overall threading dislocation density, because small patterned area growth reduces dislocation density and hence dislocation interactions [67,68], as well as reduces the distance the threading dislocations need to travel before they reach the sides of the epilayer [69,70]. **Epitaxial lateral overgrowth** using **nanoscale Ge seeds** even enables germanium growth over SiO<sub>2</sub> film [71]. Those 7-nm-wide seed pads form in the oxide layer when exposed to a germanium molecular beam and they then "touchdown" on the underlying Si. Further exposure to the molecular beam makes germanium selective growth on the seeds which later on coalesce to form an epitaxial lateral overgrowth (ELO) layer. The ELO layer should be free of dislocation except that stacking faults exist at Ge-SiO<sub>2</sub> interface.

One different perspective was put-forward suggesting that instead of trying so hard to reduce the threading dislocation density, one can route the dislocations to thread into the substrate rather than into the epilayer so as to obtain dislocation-free epi-films. By using thin **compliant substrates**, researchers have grown epilayers with very low threading dislocation densities [72-76].

One might have noticed that, most of the techniques reviewed here so far have not paid additional attention to reduce the dislocation density near or at Ge-Si interface. Some of them even sacrifice the material quality at the epi-substrate interface, confining most threading dislocations there, in order to obtain dislocation-free "bulk" part. Unfortunately, in our design of Photo-Hetero-JFET, not only the "bulk" part of the germanium film, but also that near the interface is required to have low dislocation density. In addition, the material quality of the silicon substrate or the silicon layer of SOI substrate where germanium film is grown on should not be compromised either. Therefore, techniques that utilize buffer layers or compliant substrates, or involve localized germanium melting/annoying, are not applicable in the material growth/preparation for our photodetector. One attempt to improve the material quality of the entire heteroepitaxial germanium layer is to **optimize the substrate cleaning/preparation recipe** prior to the epitaxial growth. Subal *et al.* showed that [77] the best epi Ge film is obtained by finishing the silicon substrate cleaning with Piranha, which ensures that the Si surface ends up being terminated by oxide when introduced into the MBE chamber. The oxide is then desorbed using a high temperature in-situ annealing at 800°C. They believed that following this oxide-removal technique results in "the cleanest possible Si surface for epitaxy". Their gauge of the germanium epilayer quality is the minority carrier diffusion length  $L_D$  in the film near epi-substrate interface, which can be estimated by measuring photoresponsivity of the Ge/Si heterojunction. It has been accepted that this minority carrier diffusion length  $L_D$ , independent of the device geometry and experimental methods, is an intrinsic measure of semiconductor material in the applications of electrons or optoelectronics, unless the material is so defective that geminate recombination dominates. The diffusion lengths for their best MBE samples that are subjected to the optimized substrate preparation and growth conditions are ~60nm [77].

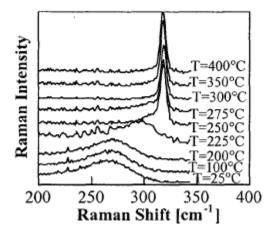

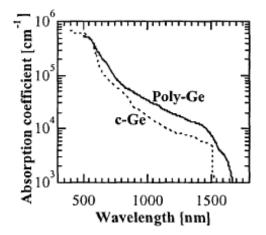

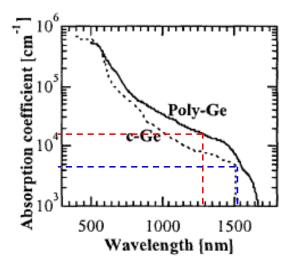

Masini *et al.* showed that they could build Ge/Si heterojunction photodiodes with uncompromised responsivity out of polycrystalline germanium thermally evaporated on silicon [13]. The diffusion length in their poly-Ge film was reported to be in the range of 20-30nm. Their thermal evaporation of germanium is carried out in a vacuum chamber with a background pressure of 1e-6 Torr, using grains of 99.999% pure Ge source, with Si substrate held at 300°C. Prior to evaporation, Si substrate goes through a preclean in HF acid and a rinse in DI water. Raman spectroscopy, shown in Fig. 2-1, demonstrates that Ge films undergo the transition from amorphous to polycrystalline as the substrate temperature exceeds 250°C and the amorphous phase vanishes above 300°C. They also show that the absorption spectrum of polycrystalline Ge is quite similar to that of the crystalline Ge [13] (see Fig. 2-2). However, polycrystalline germanium would obviously have worse carrier mobilities and lifetimes than those in single crystal Ge.

Fig. 2-1 Raman spectra of Ge films evaporated at different temperature [13].

Fig. 2-2 Absorption spectra of poly-Ge (solid line) and crystalline Ge (dashed line) [13].

preliminary results of Photo-Hetero-JFETs was actually Our obtained on proof-of-concept devices fabricated on the single-crystalline Ge films grown on SOI substrates with the same MBE process as the best film with diffusion length of 60nm had gone through. The diffusion length in the germanium film grown on these SOI wafers was not as spectacular, only 8-10nm, which we attributed to the damage of the substrate surface caused by the ion implantation step in the attempt to make the silicon device layer n-type. We later started to cooperate with Masini's group in getting germanium layers grown on SOI wafers. This time we've learned our lesson and avoided the ion implantation step, leaving the top silicon layer as it is, which is p-type or almost intrinsic. The best germanium films that we've obtained showed very small diffusion length values (~1-2nm) through responsivity measurements of the heterojuncton diodes made out of them. We've realized at a much later stage of this thesis work, that diffusion length may no longer be a valid picture; instead, geminate recombination which researchers have studied in amorphous materials for solar cells [79, 80] fits better. Since the thermally-evaporated germanium films were the best accessible material for us at the time, the nano-gate Photo-Hetero-JFET devices and p-n junction photodetector devices that this thesis work discusses on in the remaining chapters are all fabricated out of them. The reason that we go into this length in this chapter reviewing and discussing hetero-growth of germanium on silicon substrate is that the poor material quality turns out to be the most important limiting factor that prevents our photo-JFET detectors to be ultra-sensitive, which will reveal itself in later chapters.

#### 2.1.2 Band Structure of Ge/Si Heterojunction

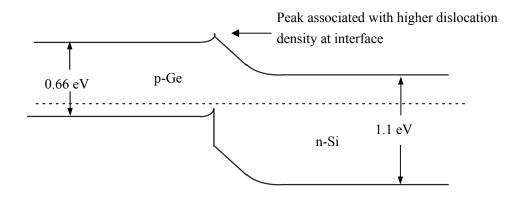

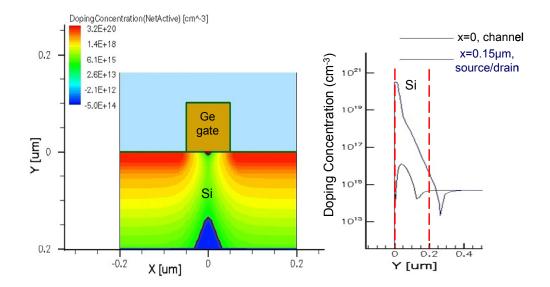

Despite all the efforts that researchers have made in reducing the dislocation density, due to the inherent large lattice mismatch, hetero-grown pure germanium films are usually still quite defective, especially near the Ge/Si interface. Those defects in the germanium film, which take the form of isolated dislocations, introduce deep electronic states in the bandgap, pinning Fermi level close to valence band edge. Furthermore, lattice mismatch between Si and Ge leaves roughly 8% of the Si surface atoms with dangling bonds. Although no dopants are intentionally incorporated during the film growth, Ge film normally exhibits p-type characteristics with peak doping at the interface approaching  $10^{18}$ cm<sup>-3</sup>. According to Di Gaspare *et al.* [78] energy gap difference between Si and Ge are accounted by a valence band discontinuity of 0.36eV and a conduction band discontinuity of 0.1eV. The resultant band alignment for p-Ge/n-Si is shown in Fig. 2-3. Since the doping level in Ge is very high, especially at the interface, and the Si layer is desired to have moderate doping level ( $10^{15} - 10^{16}$  cm<sup>-3</sup>), there is negligible depletion in Ge, and the depletion region is almost all in Si.

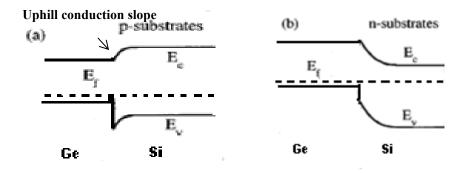

Fig. 2-3 Band structure of p-Ge/n-Si heterojunction

#### 2.1.3 Photocarrier Separation at Ge/Si Heterojunction

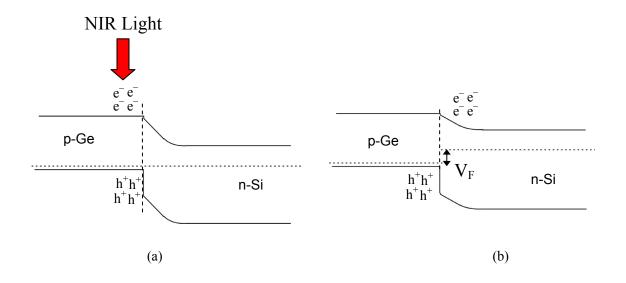

When near-infrared light is incident on the above heterojunction, it only generates electron-hole pairs in Ge because the bandgap of Si is bigger than the incident photon energy. As there is no depletion region in Ge film, there's no built-in electric field there to assist transport of generated photocarriers or to separate them. Hence, the carrier transport in germanium is solely by diffusion. Photocarriers that can survive from recombination and diffuse to the Ge/Si interface can see the built-in electric field in Si and then get separated. In an average sense, only photocarriers generated within one diffusion length near the interface can be collected as useful photocurrents. That's why diffusion length in germanium is associated with responsivity or quantum efficiency of a Ge/Si heterojunciton diode. Although lack of field-assisted carrier transport in germanium is not at all beneficial for carrier collection, the band-alignment of Ge/Si heterojunction conveniently facilitates carrier separation. When electron-hole pairs diffuse to the Ge/Si interface, photo-electrons merrily drift down the potential slope of the conduction band into the silicon side while photo-holes see the potential barrier of the valence band and are left behind in Ge. Charge separation is therefore achieved (See Fig.2-4). The photo-electrons that go to the silicon side neutralize the ionized donors in the depletion region and decrease the depletion width. Or, in a solar-cell model, the separation of photocarriers causes quasi Fermi-level separation as if a forward bias V<sub>F</sub> is applied across the junction. These two physical pictures, depletion-charge model and solar-cell model, should be essentially equivalent. They are the basis on which the proposed Photo-Hetero-JFET is designed and modeled.

It is evident from the heterojunction band-alignment that lightly doped n-type Si is preferred over the lightly doped p-type Si in the Ge/Si heterojunction. Because Si has a bandgap that is inherently larger than Ge, even lightly doped p-type Si, when forming the heterojunction with Ge, will result in an uphill conduction band slope (see Fig. 2-5),

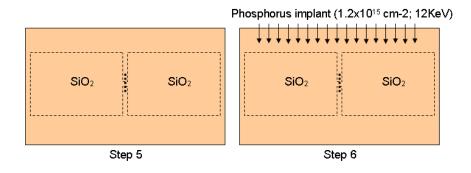

which impedes the photo-electrons to diffusion over. That's the reason, for sample materials used for the proof-of-concept devices, p-SOI wafers were ion implanted into n-type before single-crystalline germanium was grown by MBE.

Fig. 2-4 (a) Incident IR light creates electron-hole pairs in the Germanium (b) The electrons diffuse into the Silicon, creating charge separation. This forward biases the open junction by an amount V<sub>F</sub> that depends on the amount of charge separation (reproduced from ref. [77]).

Fig. 2-5 Band-diagrams of Ge/Si heterojunction with p-Ge on (a) p<sup>-</sup>-Si substrate with resistivity of 13.5-22.5 $\Omega$ ·cm (spec of SOI from SOITEC), and (b) n<sup>-</sup>-Si substrate with n-type dopants of density 2.5×10<sup>16</sup> cm<sup>-3</sup>.

#### 2.1.4 Quantum Efficiency and Diffusion Length

From the discussion of the previous paragraphs, we know that in p-Ge/n-Si heterojunctions subjected to near-infrared light, it is the electron diffusion length in germanium that determines the fraction of photocarriers that can be collected efficiently.

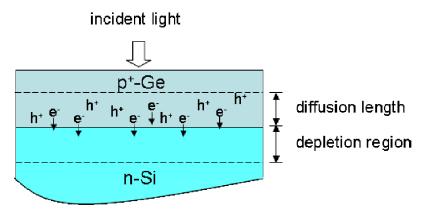

Evidently, the longer the diffusion length is, the larger the percentage of photocarriers collected resulting in better responsivity. Responsivity is heavily structure-dependent and often involves the effects of other external factors including light coupling efficiency. Differently, diffusion length is only material-dependent, and it ultimately limits the responsivity or quantum efficiency that any device structure made out of this material can achieve. This picture presented below shows that photo-electrons within one diffusion length from the junction interface are collected by the built-in electric field in the Si.

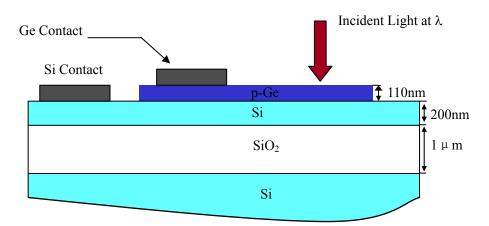

Fig. 2-6 Diffusion length and depletion region in p-Ge/n-Si heterojunction

So, if the incident light power is  $P_0$ , the absorption coefficient of Ge is  $\alpha$ , the minority carrier diffusion length is  $L_D$  and the reflectivity of air/Ge interface is r, for top illumination on the diode structure shown in Fig. 2-6, the responsivity is

$$R = \frac{I}{P_0} = \frac{P_0}{hv} \frac{q(1-r)\alpha L_D}{P_0} = \frac{q}{hv} (1-r)\alpha L_D$$

The quantum efficiency of this diode structure, which describes the ratio of number of photoelectrons that contribute to photocurrent to the number of photons incident, is then

$$\eta = \frac{hv}{q} \cdot R = (1 - r)\alpha L_D$$

Thus, electron diffusion length in p-Ge can be extracted from responsivity measurement done on p-Ge/n-Si heterojunctions as shown in the following equation.

$$L_D = \frac{hv}{q} \cdot \frac{R}{(1-r)\alpha}$$

(2.1)

The material samples that we used to fabricate our devices were characterized in this way. Simple p-Ge/n-Si heterojunction diodes were fabricated similar to the diode structure shown in Fig.2-6. Responsivity measurements were then carried out and diffusion lengths are extracted. The fabrication and characterization of this heterojunction will be discussed in the later chapters. It is evident that heterogeneously-grown germanium films with longer diffusion lengths are desired, for the reason that it results in better responsivity that can be exploited from this device.

### 2.1.5 Geminate Recombination

In most semiconductor material with the quality to make useful optoelectronics devices, the diffusion length picture suffices to indicate the best quantum efficiency that this material can offer. This is due to the common belief that in single crystalline or poly crystalline semiconductor of decent material quality, the initial separation of photoinduced electron-hole pairs is very effective. However, in more disordered material systems, like amorphous semiconductor, this assumption of complete separation of photoelectron-hole pairs at its initial stage after being generated is not valid. One often has to include geminate recombination[79,80], which describes the recombination of an electron-hole pair dissociated from a parent exciton before obvious diffusion occurs, and in some cases one has to include the phenomenon that the "initial charge separation that converts an exciton to a bounded electron-hole pairs" even fails to occur. The possibility of such initial recombination was pointed out by Rutherford long ago [81].

However, the term of geminate recombination was first introduced in chemistry. It refers to the reaction, with each other, of two transient species produced from a common precursor in solution [82]. If reaction occurs before any separation by diffusion has occurred, this is termed primary germinate recombination. If the mutually reactive entities have been separated, and come together by diffusion, this is termed secondary geminate recombination. Later on, researchers working on organic or amorphous semiconductor solar cells borrowed this concept [79,80]. Primary geminate recombination in this context refers to the very initial recombination that prevents the dissociation of an exciton, and secondary geminate recombination corresponds to the recombination of the dissociated electron-hole pairs after some separation by diffusion. Since the recombined electron and hole should be from the same parent exciton, they really haven't diffused much to meet with other electrons or holes excited by different photons, and to recombine with them. Therefore, a bulk diffusion-length model cannot be used to describe geminate recombination in disordered material. Another reason that a diffusion-length model might not apply is that the transport of charged carriers in the semiconductor can be hopping conductance instead of continuous diffusion.

Geminate recombination, if not otherwise specified as primary, often refers to the secondary geminate recombination. Absorption of light leads to creation of excitons, which may dissociate to form geminate, coulombically bound electron-hole pairs. These geminate pairs may in turn recombine, or separate from each other to become free charge carriers. The charge separation probability is determined by the ratio of the "intrinsic recombination" ratio to the sum of the electron and hole mobilities,  $k_0/\mu$  [79]. In organic solar cells people had to assume exceedingly small values of  $k_0$  to explain the poor charge

separation probabilities, although some reported that the mobilities of charge carriers on ultrafast time scales are several orders of magnitude higher than their stationary value, which relaxed  $k_0$  to reasonable values. The theory of geminate recombination [80] and its mathematic models [80][83] are certainly much more complicated and beyond the scope of this thesis work. However, it appears that in disordered material like amorphous semiconductor, geminate electron-hole recombination is one main factor limiting the quantum efficiency of optoelectronic devices that are built on it.

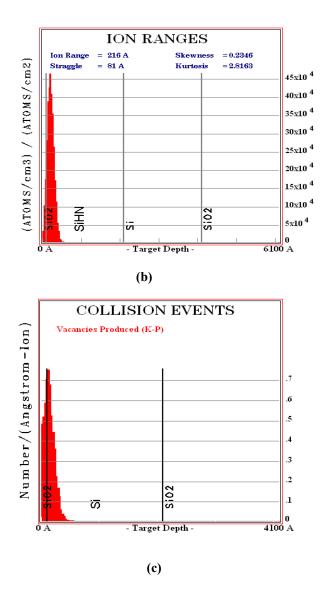

As mentioned in the previous section, the nano-gate Photo-Hetero-JFET devices are fabricated on germanium film thermally evaporated on SOI substrate. The germanium film was assumed to be "polycrystalline", since the films that were grown under the same condition on silicon substrate are shown to be polycrystalline according to Raman Spectra (see Fig.2-1)[13]. However, while the silicon substrates are ensured to be held at 300°C when clamped to the heated holder, the surface temperature of SOI substrates with a buried oxide layer of 1µm can be much lower than the required temperature for the growth to stay in the polycrystalline phase regime. To characterize the material quality of the evaporated germanium film on SOI, responsivity measurements were done on heterojunction diode devices and the diffusion length was extracted to be ~1nm. This diffusion length value is indeed significantly smaller than the reported diffusion length (20-30nm) [34] in the evaporated germanium film on silicon substrate, which suggests that the germanium films on SOI have much poorer quality and could be amorphous. Furthermore, the estimated diffusion length of the germanium film on SOI is too short to be realistic. It will be shown in the later chapter that the worst possible diffusion length is ~1nm. A diffusion length of this extremely small value suggests that physically the carriers simply recombine at where they are generated – there's not really any diffusion Therefore, as we shall also emphasize in the later chapter, the quantum efficiency of photodetectors made on this evaporated germanium films on SOI substrates is better explained by geminate recombination instead of the diffusion length model. Nonetheless, for the previous proof-of-concept devices that are made of single-crystalline MBE-grown germanium films [49,77], their quantum efficiency can still be well-explained in terms of diffusion length.

#### 2.2 Design of Photo-Hetero-JFET

#### 2.2.1 Device structure

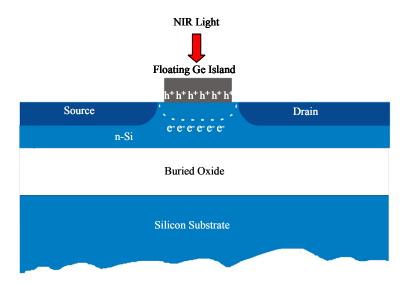

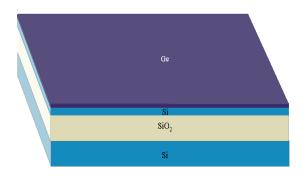

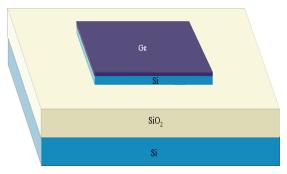

A cross-section view of Photo-Hetero-JFET with charge-separation in the heterojunction shown is presented in Fig. 2-7. It is essentially a junction FET structure. The main idea is to have a three terminal device or a transistor under a Ge/Si heterojunction. This is an attempt to significantly enhance sensitivity by harvesting gain - transistor gain and/or photoconductivity gain - on the photo-signals generated across the heterojunction, from a

decrease in depletion width or a forward photovoltage bias. In this junction FET, intended to work as a photodetector, a germanium island is placed on the channel of a typical Si FET, functioning as a floating gate that controls the conductance of the channel. Note that, being different from traditional p-i-n or p-n junction photodetector design, there's no electrical contact on the Ge.

Fig. 2-7 Cross-sectional diagram of the proposed hetero-JFET detector.

#### 2.2.2 Operating Principles of Photo-Hetero-JFET

In the Photo-Hetero-JFET, instead of having electrical voltage on the gate to modulate the channel conductance, separation of photocarriers effectively forward biases the gate-channel junction; equivalently, photoelectrons that go into silicon neutralize some of the ionized donors and reduce the channel depletion. This bias reduces the depletion in the Si and opens up the channel. This resembles the operation of a regular 'enhancement' mode JFET transistor, in which the channel is initially depleted. The silicon device layers of the SOI substrates that we used are 200nm thick, which should be completely depleted if the self-doping concentration in Ge is  $10^{18}$  cm<sup>-3</sup> and if the doping concentration in Si is  $2.5 \times 10^{16}$  cm<sup>-3</sup>.

Another equivalent operating mechanism in the Photo-Hetero-JFET is often referred to by experts in photoconductors as "secondary photoconductivity" [84]. Photoholes that are left behind and immobile in the germanium gate can attract electrons from source to the channel. With a source-to-drain bias applied across the channel, electrons move and current flows. When the lifetime of holes in the gate ( $\tau_h$ ), or "dwell" time of photo-holes in the context of dispersive transport as we refer to as in Chapter 4, is larger than the transit time of electrons across the channel ( $t_{tr}$ ), a single photo-hole can result in more than one electron flowing into the contacts and collected as photocurrent. Therefore, this photoconductive gain ( $G_{ph}$ ) is proportion to  $\tau_h/t_{tr}$ . One way to increase the photoconductive gain is by reducing  $t_{tr}$ . This is another good reason that drives us to scale down the device, especially in terms of shortening channel length. The transconductance gain of a JFET transistor is also increased with decreased channel length.

Both mechanisms, transconductance gain and photoconductive gain, can exist in the operation of Photo-Hetero-JFETs. Sometimes it's hard to distinguish one from the other. In the framework of a junction-FET, induced electrons from the electrostatic coupling of the "immobile" holes (or holes slowly hopping between traps) in the gate neutralize some of channel depletion and the electric field from the gate charge creates channel "conductance" ("transconductance"). Also, with a bias across the channel, those "immobile" primary holes in the gate can keep attracting secondary electrons to flow from source to drain for photoconductivity ("secondary conductivity). Therefore, as further discussed in Chapter 4, JFET transistor gain and photoconductive gain are referring to the same physics that happens in the operation regime of the Photo-Hetero-JFETs.

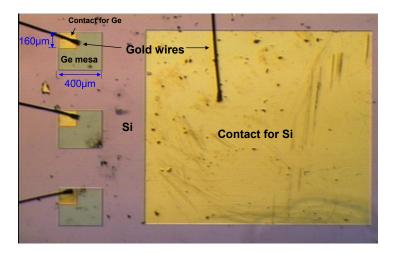

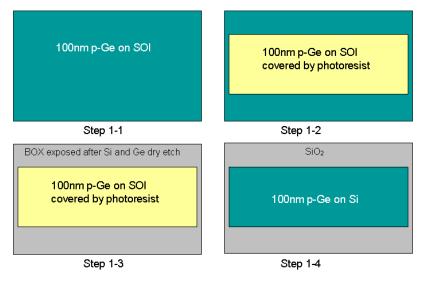

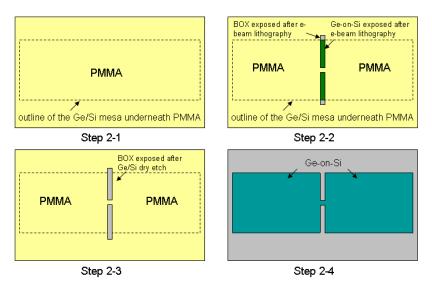

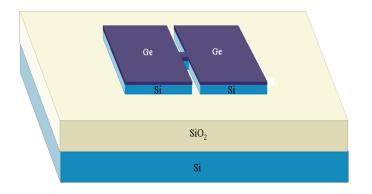

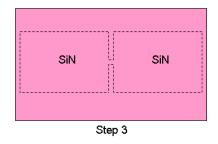

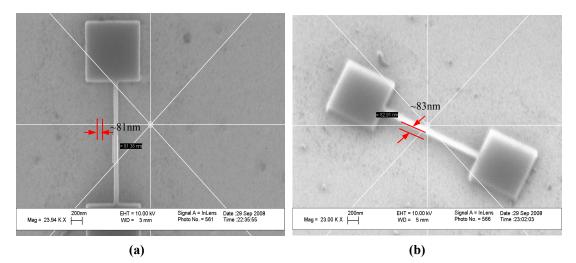

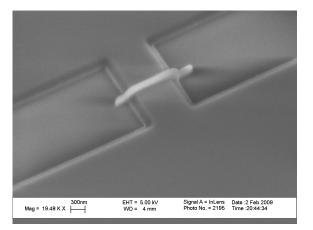

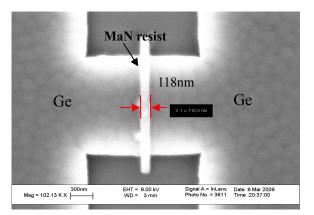

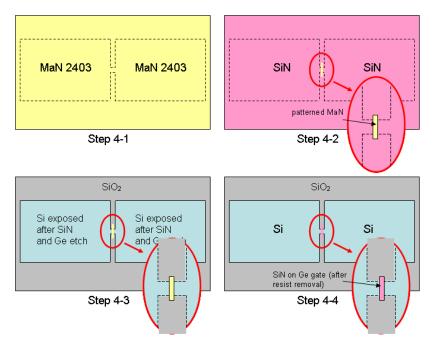

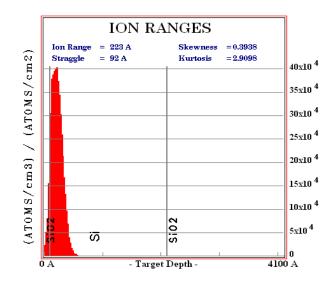

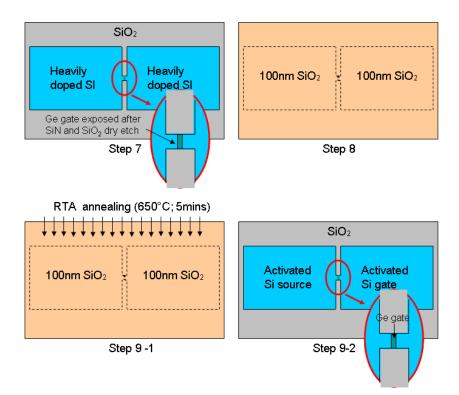

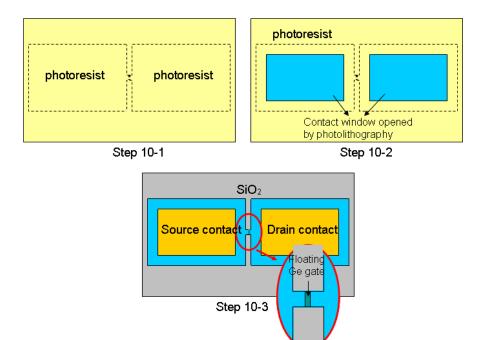

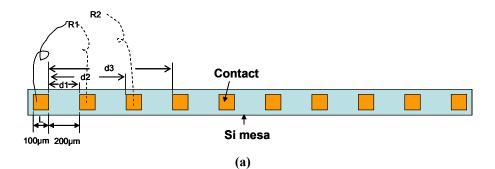

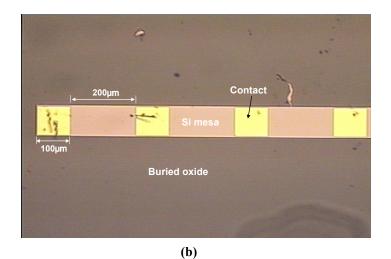

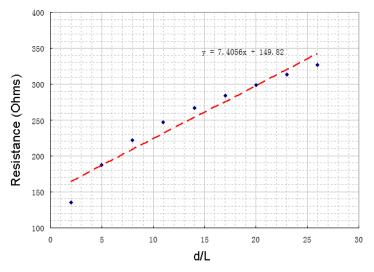

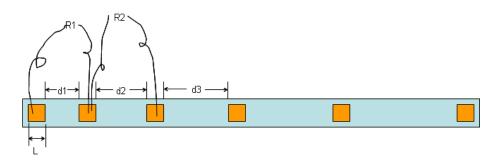

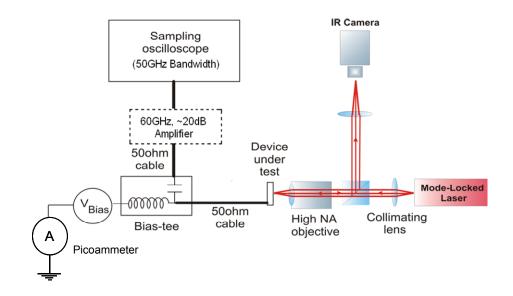

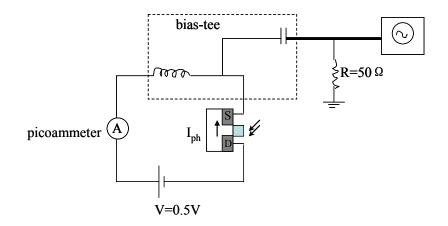

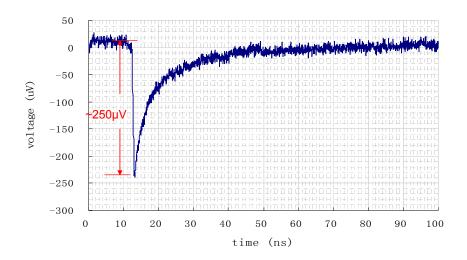

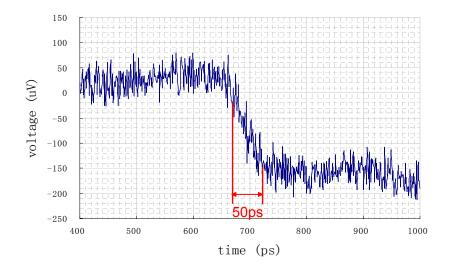

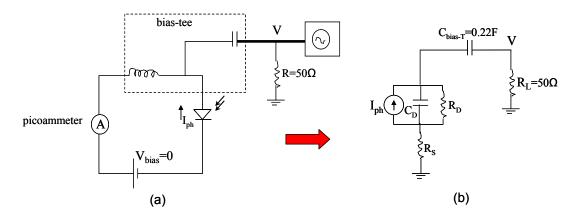

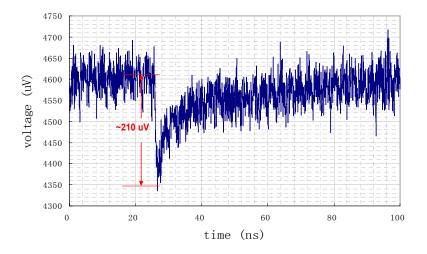

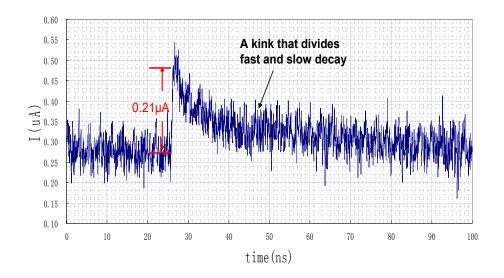

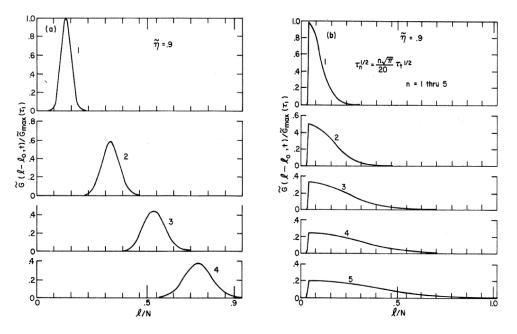

# **Chapter 3** Fabrication of the Photo-Hetero-JFET