#### **Automatic Term-Level Abstraction**

Bryan Brady

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2011-51 http://www.eecs.berkeley.edu/Pubs/TechRpts/2011/EECS-2011-51.html

May 13, 2011

# Copyright © 2011, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Acknowledgement

This research has been supported by Semiconductor Research Corporation contracts 1355.001 and 2045.001.

#### Automatic Term-Level Abstraction

by

#### Bryan Brady

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Sanjit A. Seshia, Chair Professor Robert K. Brayton Professor Alper Atamtürk

Spring 2011

#### Automatic Term-Level Abstraction

Copyright 2011 by Bryan Brady

#### Abstract

#### Automatic Term-Level Abstraction

by

#### Bryan Brady

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Sanjit A. Seshia, Chair

Recent advances in decision procedures for Boolean satisfiability (SAT) and Satisfiability Modulo Theories (SMT) have increased the performance and capacity of formal verification techniques. Even with these advances, formal methods often do not scale to industrial-size designs, due to the gap between the level of abstraction at which designs are described and the level at which SMT solvers can be applied. In order to fully exploit the power of state-of-the-art SMT solvers, abstraction is necessary. However, applying abstraction to industrial-size designs is currently a daunting task, typically requiring major manual efforts. This thesis aims to bridge the gap between the level at which designs are described and the level at which SMT solvers can reason efficiently, referred to as the term level.

This thesis presents automatic term-level abstraction techniques in the context of formal verification applied to hardware designs. The techniques aim to perform abstraction as automatically as possible, while requiring little to no user guidance. Data abstraction and function abstraction are the foci of this work. The abstraction techniques presented herein rely on combining static analysis, random simulation, machine learning, and abstraction-refinement in novel ways, resulting in more intelligent and scalable formal verification methodologies.

The data abstraction procedure presented in this work uses static analysis to identify portions of a hardware design that can be re-encoded in a theory other than the theory of bit vectors, with the goal of creating an easier to reason about verification model. In addition, the data abstraction procedure can provide feedback that can help the designer create hardware designs that are easier to verify.

The function abstraction procedures described in this work rely on static analysis, random simulation, machine learning, and counterexample-guided abstraction-refinement to identify and abstract functional blocks that are hard for formal tools to reason about. Random simulation is used to identify functional blocks that will likely yield substantial performance increases if they were to be abstracted. A static analysis-based technique, ATLAS, and a separate technique, CAL, based on a combination of machine learning and counterexample-guided abstraction-refinement, are then used to compute conditions under which it is precise to abstract. That is, functional blocks are abstracted in a manner that avoids producing spurious counterexamples.

Experimental evidence is presented that proves the efficacy and efficiency of the data and function abstraction procedures. The experimental benchmarks are drawn from a wide range of hardware designs including network-on-chip routers, low-power circuits, and microprocessor designs.

To Mom, Dad, and Ashley

#### Acknowledgments

First, and foremost, I would like to thank my advisor, Sanjit A. Seshia. His contagious enthusiasm, intense motivation and determination, and seemingly infinite patience, have set an example that I can only hope to achieve. His willingness to give feedback, brainstorm, and discuss research ideas late into the night or early hours of the morning, in the office or on the phone, have been invaluable during my tenure as a graduate student. Knowing how hard Sanjit works is enough to motivate me to work harder; he truly leads by example. I am proud to have had the opportunity to work with Sanjit.

I would also like to thank Robert Brayton and Alper Atamtürk for serving on my dissertation committee and qualifying examination committee. Additionally, I would like to thank Ras Bodik for serving on my qualifying examination committee.

Many people have influenced my work in a positive way, through feedback, brainstorming sessions, and sound advice. However, a few deserve special mention. I would like to thank Randy Bryant for his continued collaboration during my graduate career, the critical feedback he provided on the automatic data and function abstraction techniques, and for creating the Y86 processor benchmark that I have used (and become intimately familiar with) over the last several years. I would also like to thank John O'Leary for mentoring me during my internship at Intel and providing me with the opportunity to evaluate my data abstraction tool on a real-world design. His feedback, during and after my internship, helped refine the data abstraction technique and spawn an interest in automatic function abstraction techniques.

Special thanks to Ruth Gjerde and Sandy Weisberg for deciphering departmental policies and procedures, the persistent reminders about paperwork I had forgotten, and, most importantly, the many wonderful conversations.

Thanks to Dan Holcomb, Wenchao Li, Susmit Jha and Rhishikesh Limaye for the intriguing conversations, critical feedback, and all the fun times in the lab. Thanks to the many friends, climbing partners, and roommates for the adventures outside of school that helped keep my sanity intact.

From my days back in Pittsburgh, I would like to thank Steve Jacobs for the solid foundation in digital logic and all of the hard homework and exam questions that kept me up so many nights. Thanks to Steve Levitan for introducing me to verification for the first time and for being my unofficial advisor. Thanks to Rob Santoro, Sam Dickerson, and the many other friends from Pittsburgh who made those late nights in Benedum so enjoyable.

Most importantly, I would like to thank my parents, Mike and Michele, and my sister, Ashley, for your love and support through all these years. I am grateful that you taught me to work hard, to take pride in my work, and to enjoy my work. But, above all, I am grateful that you are my family; I could not have done this without you.

Finally, I would like to thank my girlfriend, Bridget, for making the last year and a half, my best year and a half.

# Contents

| Li | st of                            | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | vi                    |

|----|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Li | st of                            | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | iii                   |

| Li | st of                            | Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ix                    |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4 | Formal Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1<br>2<br>3<br>5<br>5 |

| Ι  | Ba                               | ckground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                     |

| 2  | Mod                              | leling Hardware Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8                     |

|    | 2.1                              | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                     |

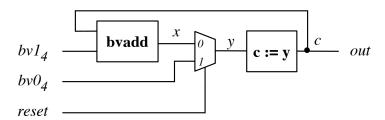

|    |                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10                    |

|    |                                  | O Company of the comp | 12                    |

|    | 2.2                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                    |

|    |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                    |

|    |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17                    |

|    |                                  | $oldsymbol{arphi}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20                    |

|    | 2.3                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22                    |

|    | 2.4                              | 0 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24                    |

|    |                                  | The state of the s | 24                    |

|    | 0.5                              | 8 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                    |

|    | 2.5                              | Correspondence Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28                    |

| 3  | Solv                             | ing Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                    |

|    | 3.1                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30                    |

|    | 3.2                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                    |

|    |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32                    |

|    |                                  | 3.2.2 Disadvantages of Boolean Satisfiability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                    |

|    | 3.3  | Word-Level Reasoning                    | 34        |

|----|------|-----------------------------------------|-----------|

|    |      | 3.3.1 Rewriting                         | 35        |

|    |      | 3.3.2 Abstraction-Refinement            | 36        |

|    |      | 3.3.3 Bit-blasting                      | 37        |

|    |      | 3.3.4 Limitations                       | 37        |

|    | 3.4  | Decision Procedures for EUF             | 38        |

|    |      | 3.4.1 Eliminating Function Applications | 38        |

|    |      | 3.4.2 Small-Domain Encoding             | 39        |

|    | 3.5  | UCLID                                   | 39        |

|    | 3.6  | Challenges                              | 40        |

| II | A    | utomatic Abstraction                    | 42        |

| 4  | Dat  | a-Abstraction                           | 43        |

|    | 4.1  | Type Qualifiers                         | 43        |

|    | 4.2  | Compute Equivalence Classes             | 45        |

|    | 4.3  | Compute Maximal Abstraction             | 46        |

|    | 4.4  | Determine Final Abstraction             | 47        |

|    | 4.5  | Create UCLID Model                      | 48        |

|    | 4.6  | Case Study: CMP Router                  | 49        |

|    |      | 4.6.1 Experimental Setup                | 49        |

|    |      | 4.6.2 Experimental Results              | 50        |

|    | 4.7  | Related Work                            | 50        |

|    | 4.8  | Summary                                 | 53        |

| 5  | Aut  | somatic Function Abstraction            | <b>54</b> |

|    | 5.1  | Identifying Candidate Fblocks           | 54        |

|    | 5.2  | Random Simulation                       | 55        |

|    | 5.3  | Static Analysis                         | 57        |

|    | 5.4  | Illustrative Example                    | 63        |

|    | 5.5  | Benchmarks                              | 66        |

|    |      | 5.5.1 Pipelined Datapath (PIPE)         | 67        |

|    |      | 5.5.2 USB Controller (USB)              | 67        |

|    |      | 5.5.3 Calculator (CALC)                 | 67        |

|    |      | 5.5.4 Y86 Processor (Y86)               | 68        |

|    | 5.6  | Results                                 | 69        |

|    | 5.7  | Related Work                            | 71        |

|    | 5.8  | Summary                                 | 73        |

| 6  | Lea  | rning Conditional Abstractions          | 74        |

| _  | 6.1  | Top-Level CAL Procedure                 | 74        |

|    | 6.2  | Conditional Function Abstraction        | 76        |

|    | 6.3  | Learning Conditional Abstractions       |           |

|    | J. J |                                         |           |

| 6.4 Generating Data |       |                                                        |    |  |  |

|---------------------|-------|--------------------------------------------------------|----|--|--|

|                     |       | 6.4.1 Generating Witnesses                             | 79 |  |  |

|                     |       | 6.4.2 Generating Similar Counterexamples               | 80 |  |  |

|                     | 6.5   | Choosing Features                                      | 81 |  |  |

|                     | 6.6   | Experimental Results                                   | 81 |  |  |

|                     |       | 6.6.1 Processor Fragment                               | 82 |  |  |

|                     |       | 6.6.2 Y86 Processor                                    | 82 |  |  |

|                     |       | 6.6.3 Low-Power Multiplier                             | 85 |  |  |

|                     |       | 6.6.4 Comparison with ATLAS                            | 87 |  |  |

|                     |       | 6.6.5 Remarks                                          | 87 |  |  |

|                     | 6.7   | Related Work                                           | 88 |  |  |

|                     | 6.8   | Summary                                                | 89 |  |  |

| 7                   | Con   | aclusions and Future Work                              | 90 |  |  |

|                     | 7.1   | Summary                                                | 90 |  |  |

|                     | 7.2   | Future Work                                            | 90 |  |  |

|                     |       | 7.2.1 Combining Data and Function Abstraction          | 91 |  |  |

|                     |       | 7.2.2 Constraining the Progress of Learning Algorithms | 91 |  |  |

|                     |       | 7.2.3 Automatic Feature Selection                      | 92 |  |  |

| Bil                 | bliog | graphy                                                 | 93 |  |  |

# List of Figures

| 1.1  | Levels of abstraction                                                   | 3  |

|------|-------------------------------------------------------------------------|----|

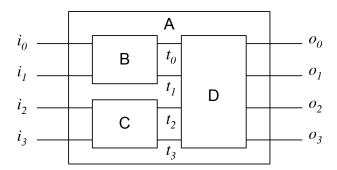

| 2.1  | A hierarchical word-level design                                        | 10 |

| 2.2  | Syntax for Boolean formulas                                             | 11 |

| 2.3  | Boolean operators                                                       | 11 |

| 2.4  |                                                                         | 12 |

| 2.5  |                                                                         | 13 |

| 2.6  | Syntax for bit-vector expressions and formulas                          | 14 |

| 2.7  |                                                                         | 15 |

| 2.8  |                                                                         | 15 |

| 2.9  |                                                                         | 16 |

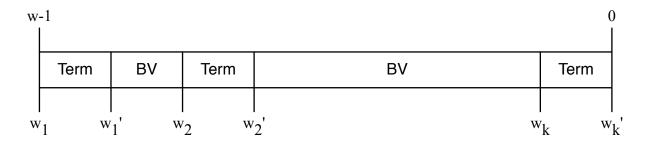

| 2.10 | Comparison between bit-vector and term signals                          | 17 |

| 2.11 | Syntax for expressions and formulas in EUF                              | 18 |

| 2.12 |                                                                         | 18 |

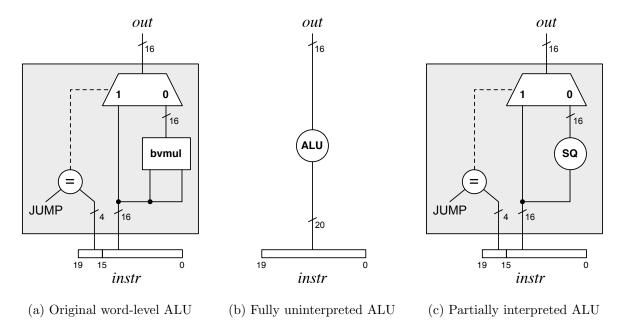

| 2.13 | Three versions of an ALU design with varying levels of abstraction      | 20 |

| 2.14 | Syntax for memory expressions                                           | 22 |

| 2.15 | Syntax for formulas and expressions used in term-level netlists         | 23 |

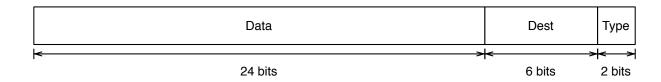

| 2.16 | Anatomy of a flit                                                       | 25 |

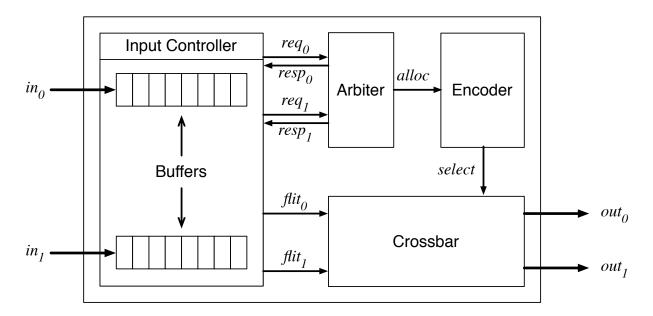

| 2.17 | Chip-Multiprocessor (CMP) Router                                        | 25 |

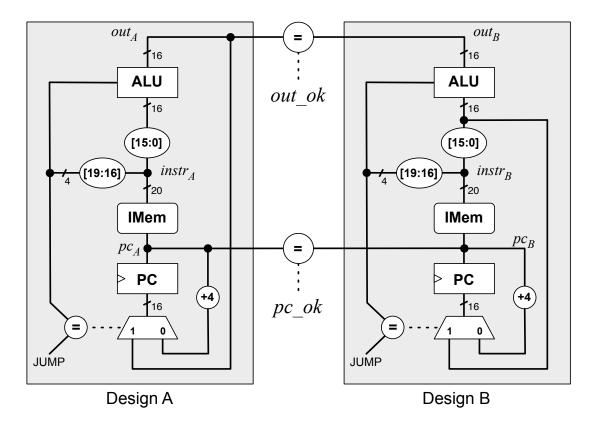

| 2.18 | Equivalence checking of two versions of a portion of a processor design | 27 |

|      |                                                                         | 29 |

| 3.1  | Cone-of-influence (COI) illustration                                    | 31 |

| 3.2  |                                                                         | 32 |

| 3.3  | · · · · · · · · · · · · · · · · · · ·                                   | 35 |

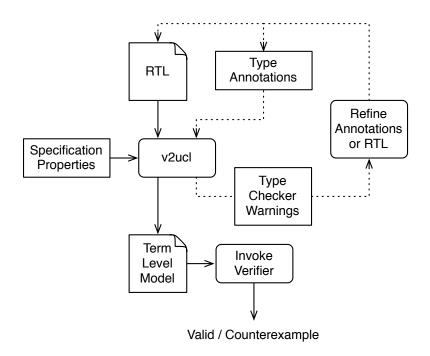

| 4.1  | An overview of V2UCL                                                    | 44 |

| 4.2  |                                                                         | 48 |

| 4.3  |                                                                         | 49 |

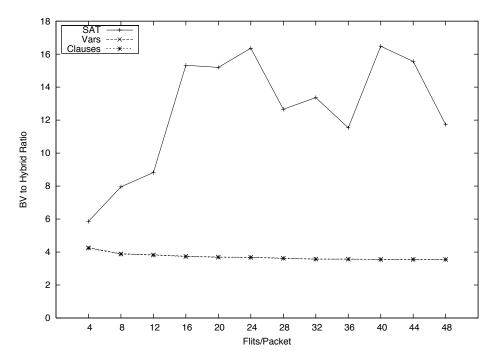

| 4.4  |                                                                         | 51 |

| 4.5  |                                                                         | 52 |

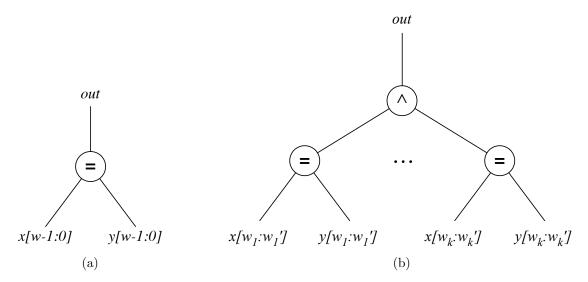

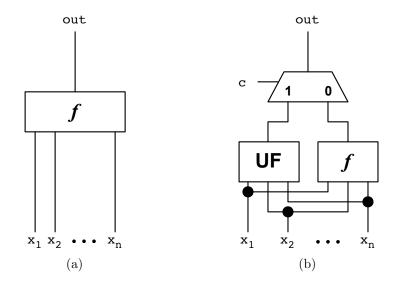

| 5.1  | Conditional abstraction                                                 | 58 |

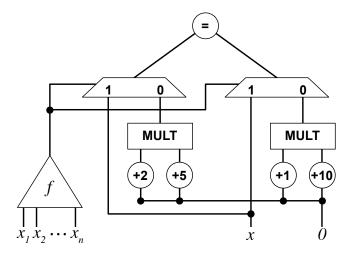

| 5.2  | Circuit for showing NP-hardness of IntCondChk                           | 59 |

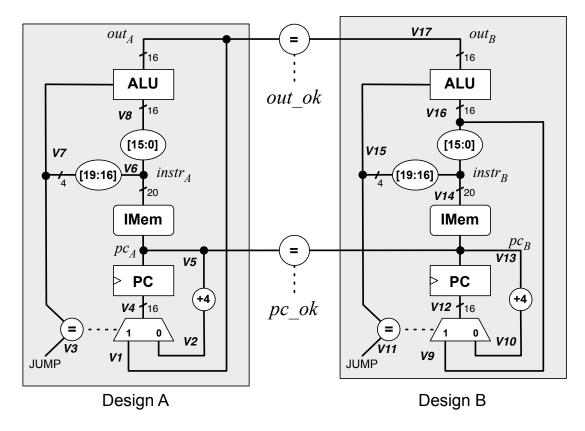

| 5.3 | Equivalence checking of two versions of a portion of a processor design | 66 |

|-----|-------------------------------------------------------------------------|----|

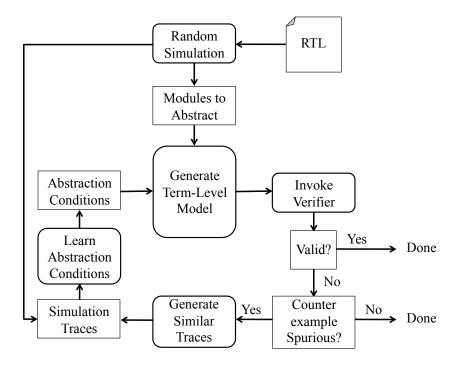

|     | The CAL approach                                                        |    |

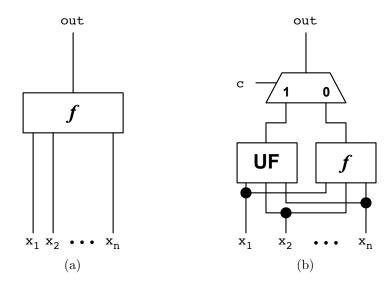

| 6.2 | Conditional abstraction                                                 | 78 |

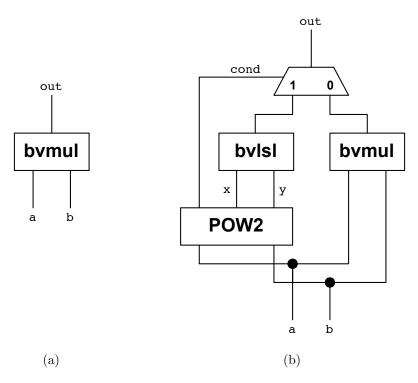

| 6.3 | Low-power design example                                                | 86 |

# List of Tables

| 3.1 | Clauses generated during Tseitin encoding                                         | 32 |

|-----|-----------------------------------------------------------------------------------|----|

| 3.2 | Example of Tseitin encoding.                                                      |    |

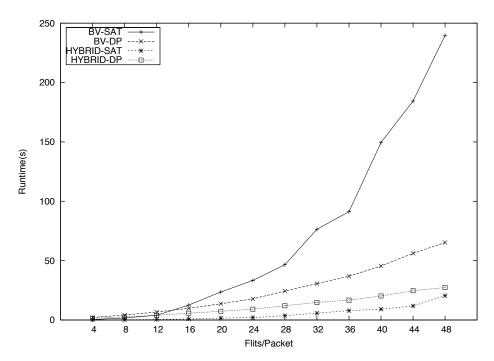

| 3.3 | Runtimes for checking the commutativity of multiplication                         | 34 |

| 3.4 | Simulation runtime of 16-bit multiplier for varying number of simulation vectors. | 34 |

| 4.1 | Rules for merging equivalence classes                                             | 46 |

| 5.1 | Illustration of a random function                                                 | 56 |

| 5.2 | Rules for computing interpretation conditions                                     | 64 |

| 5.3 | Performance Comparison and Benchmark Characteristics                              | 70 |

| 5.4 | Performance Comparison of SAT-based Verification                                  | 72 |

| 6.1 | Performance comparison for Processor Fragment                                     | 82 |

| 6.2 | Performance comparison for Y86-BTFNT processor                                    | 84 |

| 6.3 | Performance comparison for Y86-NT processor                                       | 85 |

| 6.4 | Performance comparison for low-power multiplier                                   | 87 |

# List of Algorithms

| 1 | Procedure ConditionalFuncAbstraction   | 62 |

|---|----------------------------------------|----|

| 2 | Procedure AbstractWithUF               | 63 |

| 3 | Procedure Conditional Abstract With UF | 65 |

| 4 | Procedure VerifyAbs                    | 77 |

| 5 | Procedure CONDABS                      | 77 |

## Chapter 1

### Introduction

Computer systems are ubiquitous in the world today. They are used in a variety of applications from personal communication devices to mission critical systems such as automotive and avionic control systems. Depending on the application, an error could be a minor inconvenience or a major catastrophe, possibly endangering lives. Therefore, there is an ethical and moral obligation to correctly design and implement computer systems.

Design and verification engineers have an arsenal of tools with which they can verify computer systems. These verification tools come in two main flavors: *simulation* and *formal*. Simulation-based verification involves simulating a design with input vectors and comparing the output against known results for those same input vectors. In formal verification, a mathematical model of the design is created along with properties that the design must satisfy and automated reasoning techniques are then used to determine whether the design satisfies the properties in all situations.

Consider the classic example of an elevator design, where the elevator is not supposed to move when the doors are open. To verify this elevator design with simulation-based verification would require simulating the elevator many times and checking in each case if the doors are ever open while the elevator is moving. At the end of this verification process, we know that the elevator never moves when the doors are open for all of the individual test cases that we tested. In small designs, it might be possible to test every possible case. However, in most realistic cases there are far too many combinations of inputs to test the entire input space. Simulation-based techniques can be helpful in finding bugs, but not proving their absence. Various techniques exist that attempt to quantify the amount of the search-space tested by the simulation vectors by computing what is known as a coverage metric. A coverage metric is a measure of confidence that the system is correct.

In situations where absolute guarantees of correctness are required, design and verification engineers turn to formal verification. Formal techniques are able to not only find bugs, but prove the absence of bugs. However, formal methods don't always scale well to large designs and often require hand-crafted abstractions, which can be tedious and error-prone to create. This dissertation focuses on increasing the scalability of formal techniques by automatically applying abstraction to portions of designs that are hard for formal techniques to reason about.

#### 1.1 Formal Verification

Formal verification involves mathematically proving properties about designs. While there are many variations of formal verification, such as model checking and equivalence checking, each variant shares the following three requirements: (i) a mathematical model of the design; (ii) the property to be verified, and (iii) a model of the environment in which the design will be operating. We present below three formal verification techniques that we use in the remainder of this thesis.

Model checking. The goal of model checking is to determine whether a design D satisfies a property P, typically expressible in temporal logic, while operating in environment E. In model checking, the design, property, and environment are modeled symbolically. The model checking algorithm attempts to prove that design D satisfies property P in all states. This is accomplished by computing the set of reachable states  $S_0, S_1, \ldots$  and checking that each state in  $S_i$  satisfies property P. In the absence of a counterexample, the set of reachable states are computed until a fix-point is reached (i.e.,  $S_i = S_{i+1}$ ), at which point it has been proven that design D satisfies property P. Computing the set of reachable states is a major challenge for model checking algorithms. A weaker form of model checking, where it is not necessary to compute the entire set of reachable states, is bounded-model checking (BMC). In BMC, the design is initialized to some known state and is then unrolled for a bounded number of cycles. For a design to pass BMC, it must satisfy the property in each time frame.

Equivalence checking. Equivalence checking involves proving that two designs have equivalent functionality. There are two types of equivalence checking: combinational and sequential. Combinational equivalence checking involves proving that two designs produce the same output for any input. Sequential equivalence checking involves proving that two designs produce the same output for any sequence of inputs. In either case, there are two versions of a design, with the same symbolic inputs connected to both designs, and the goal is to prove that the designs always produce the same output. If two designs are equivalent, they can be used interchangeably. Equivalence checking is a process used frequently throughout the design of hardware systems. Hardware is typically described using a high-level hardware description language (HDL) such as Verilog or VHDL. Next, a variety of logic synthesis algorithms, such as retiming and technology mapping are applied to the high-level HDL. After each synthesis step, it is necessary to ensure that the functionality of the design hasn't changed. Equivalence checking is typically performed after each step of synthesis.

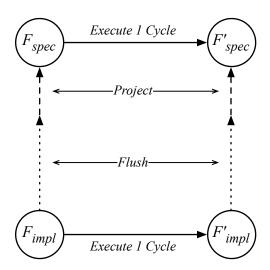

Correspondence checking. Correspondence checking, introduced by Burch and Dill [31], is a formal verification technique used to verify the control logic of pipelined microprocessor designs. In correspondence checking, a pipelined microprocessor is verified against a sequential (meaning that instructions are executed one after another) version of the same processor. The sequential processor is essentially a formal model of the instruction set architecture. The property that correspondence checking aims to verify is that the pipelined processor

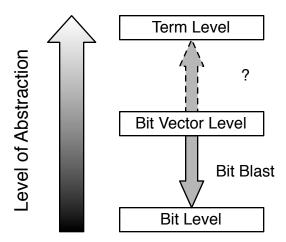

Figure 1.1: **Levels of abstraction.** Bit-level modeling is the lowest level of abstraction. Bit-vector level modeling is one step above bit-level modeling, however, it is precise in the sense that no information is abstracted away. Term-level modeling is the highest level of abstraction, where datapaths and functional blocks can be represented abstractly.

refines the sequential version of the same processor. In other words, the pipelined processor can mimic all of the behaviors present in the sequential version. Since processor designs are some of the main benchmarks used in this dissertation, we describe this technique in more detail in Section 2.5.

#### 1.2 Abstraction Layers in Formal Verification

Regardless of the type of formal verification being applied, the same underlying reasoning mechanisms can be used. The type of reasoning mechanism depends on the level of abstraction used to model the system being verified. While there are many levels of abstraction within which the design and property to be tested can be modeled, this work focuses on three levels: bit-level modeling, bit-vector-level modeling, and term-level modeling. The aforementioned levels of abstraction are listed in increasing levels of abstraction as illustrated in Figure 1.1.

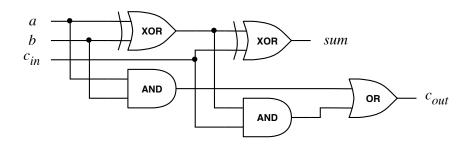

Bit level modeling. At the lowest level, the entire design can be modeled with individual bits, using propositional logic. In this case, higher-level constructs such as addition or multiplication circuits are modeled solely with Boolean logic gates, at the bit level. Solvers that operate at the bit level, such as Boolean satisfiability (SAT) solvers and Binary Decision Diagram (BDD) packages, can be quite powerful and have seen tremendous performance and capacity increases over the last decade.

BDDs, in their current form, were introduced by Bryant in 1986 [25]. He showed how to reduce BDDs into a canonical form by using a series of simplifications that are applied during the creation of a BDD. Further optimizations, such as using a unique table for fast access

to existing nodes and adding complemented edges to represent negation, were presented in [14]. Even the most state-of-the-art BDD packages, such as CUDD, an efficient BDD package created by Somenzi [64], suffer from exponential time and space requirements in the worst case.

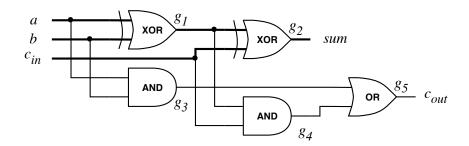

The Boolean satisfiability (SAT) problem, and algorithms to solve SAT problems, have been around for several decades [35, 34]. Even with these early works, the field of SAT solving did not see major advances until the late 1990s and early-to-mid 2000s [55, 57, 39, 40, 38, 67]. SAT solving has since received much attention, and as a result, additional progress has been made [39, 7, 12, 47]. The problem of Boolean satisfiability is NP-complete, thus, it is no surprise that problems exist that exhibit worst-case behavior for even the best SAT solvers. Additionally, certain circuit structures, such as those with many exclusive-or gates, tend to hinder the performance of bit-level solvers. To combat these problems, a higher level of abstraction can be employed.

Satisfiability Modulo Theories. The Satisfiability Modulo Theories (SMT) problem is a decision problem over formulas in first-order logic coupled with decidable first-order background theories. SMT solvers have become the umbrella term for solvers that reason at a level of abstraction above the bit level [9, 10]. There are many background theories supported by SMT solvers, however, they are not all compatible with one another. This work focuses on two background theories, the theory of bit vectors, and logic of equality with uninterpreted functions [10, 9, 33].

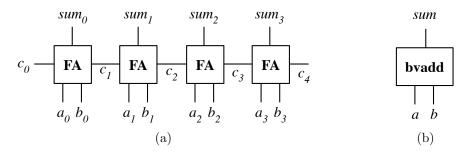

Bit-vector level modeling. The bit-vector level, also referred to as the word level, is the level of abstraction in which most hardware designs are modeled. At the word level, datapath signals are modeled with groups of bits, or bit vectors, and operations are defined over these bit vectors. The most obvious advantage that the bit-vector level has over the bit level is the reduction in model size. For example, the number of gates within a multiplier grows quadratically with the size of the datapath, however, when represented at the bit-vector level, a multiplier has constant size. Another advantage, which can be exploited for major performance increases, is that word-level reasoning procedures take into account properties that are lost at the bit level [48]. One such example is the commutativity of multiplication as we show in Chapter 3. Bit-vector solvers have received a lot of attention over the last several years [27, 28, 44, 43, 21] and there are many efficient solvers available [48, 23, 22, 37]. While bit-vector solvers outperform bit-level solvers in many cases, there are still situations where further abstraction is required. In these situations, term-level abstraction can be employed.

**Term-level modeling.** Term-level abstraction is a modeling technique where datapath signals are represented with symbolic *terms* and precise functionality is abstracted away with *uninterpreted functions*. Term-level abstraction has been found to be especially useful in microprocessor design verification [46, 31, 52, 54]. The precise functionality of units such as instruction decoders and the ALU are abstracted away using *uninterpreted functions*, and decidable fragments of first-order logic are employed in modeling memories, queues, counters,

and other common data structures. While several SMT solvers support some, or all, of the background theories used in term-level abstraction, UCLID [53, 29] and SAL [36, 11] are two of the only full-fledged term-level verification systems available.

A major challenge of any abstraction technique, including term-level abstraction, is in determining what functionality to abstract. On the one hand, constructing these models by hand is a tedious process prone to errors, hence automation is essential. On the other hand, automatically abstracting all bit-vector signals to terms and all operators to uninterpreted functions results in too coarse an abstraction, in which properties of bit-wise and finite-precision arithmetic operators are obscured, leading to a huge number of spurious counterexamples. While such spurious counterexamples can in many cases be eliminated by selectively abstracting only parts of the design to the term level, manual abstraction requires detailed knowledge of the RTL design and the property to be verified. It is difficult for a human to decide what functional blocks or operators to abstract in order to obtain efficiency gains and also avoid spurious counterexamples.

#### 1.3 Thesis Contributions

The problem addressed by this thesis is the automatic application of term-level abstraction to hardware designs with the goal of creating easier to verify models.

The main contributions of this thesis include:

- 1. A data abstraction technique, optionally guided by user-provided type annotations, that re-encodes portions of a bit-vector design at the term-level. While this technique can be fully automated, user-provided type annotations are used to provide feedback to the verification engineer (Chapter 4);

- 2. A random-simulation-based technique used for the identification of abstraction candidates (Chapter 5);

- 3. An automatic approach to function abstraction based on a combination of random simulation and static analysis. Random simulation is used to identify abstraction candidates. Then, static analysis is used to compute conditions under which it is precise to abstract (Chapter 5), and

- 4. An automatic function abstraction technique based on machine-learning, random simulation, and counterexample-guided abstraction-refinement. Abstraction candidates are identified using random simulation. Interpretation conditions are then learned by applying machine learning techniques to the spurious counterexamples that arise (Chapter 6).

#### 1.4 Thesis Overview

This thesis is broken down into two main parts. The first part of this thesis discusses relevant background material. Chapter 2 introduces basic notation, modeling techniques,

and levels of abstraction commonly used in formal methods. This includes the basics of bit-level, word-level, and term-level modeling and examples of term-level abstraction techniques being applied to simple circuits. Chapter 3 discusses the decision procedures used to solve problems at the various levels of abstraction, as well as discussing the strengths and weaknesses of each approach.