# Improving CMOS Speed and Switching Power with Air-gap Structures

Jemin Park

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2011-84 http://www.eecs.berkeley.edu/Pubs/TechRpts/2011/EECS-2011-84.html

July 21, 2011

Copyright © 2011, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Improving CMOS Speed and Switching Power with Air-Gap Structures

By

Je Min Park

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Chenming Hu Professor Tsu-Jae King Liu Professor Eugene E. Haller

Fall 2011

### Improving CMOS Speed and Switching Power with Air-Gap Structures

Copyright © 2011

by

Je Min Park

#### **Abstract**

Improving CMOS Speed and Switching Power with Air-Gap Structures

By

Je Min Park

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Chenming Hu, Chair

Scaling transistors is good for speed but scaling interconnect degrades it due to resistances and parasitic capacitances. Scaling of supply voltage V<sub>DD</sub> has significantly slowed down since the 130 nm node. As a result, integrated circuit (IC) power consumption has been on the rapid rise. Crosstalk noise problem has been also increased as scaling. Reducing capacitance is an excellent solution for these problems; the circuit delay, power consumption, and crosstalk noise. The future transistor and interconnect with lower capacitance should be considered to overcome these problems. An air-gap structure can be attractive solution for both transistor and interconnect. Novel air-gap structures are proposed in this research. In the transistors, the conventional spacer structure is replaced with air-gap spacer structure. This new structure leads for the fringing capacitance to be decreased much. Therefore, the speed and power consumption can be improved. This structure can be compatible with both the conventional gate-first and gatelast process. Other designs involve use of self-aligned contact or linear contact processes to achieve a much more effect. The low-k spacer transistor which is included this air-gap spacer transistor degrades the current performance. Thus, the air-gap spacer technology is very helpful to the high performance devices but it is not much helpful to the low stand-by power devices. The corner spacer transistor with high-k inner spacer and low-k outer spacer is proposed to overcome the degradation of current performance. The high-k material can improve the current performance and the low-k material can improve the capacitance. In the interconnects, the proposed novel air-gap interconnects are compatible with both the subtractive etch interconnect and dual damascene interconnect. These air-gap structures can improve not only the effective dielectric constant but also crosstalk noise problem.

To my wife for her devoted love and support, to my daughters for their affording great pleasure to me, and to my mother for her unbounded love and prayer.

# **Contents**

| Table  | e of Contents                                                               | ii |

|--------|-----------------------------------------------------------------------------|----|

| List o | of Figures                                                                  | vi |

| List o | of Tables                                                                   | X  |

| Ackn   | owledgements                                                                | xi |

| Tab    | ole of Contents                                                             |    |

| Chap   | ter 1: The Needs for Vacuum Gap Structures                                  | 1  |

| 1.1    | Scaling down is no longer the absolute solution for improving circuit speed | 1  |

| 1.2    | CMOS Power density has increased with scaling transistors                   | 2  |

| 1.3    | Crosstalk noise is also a big problem                                       | 4  |

| 1.4    | A possible solution                                                         | 4  |

| 1.5    | Research outline                                                            | 5  |

| 1.6    | References                                                                  | 5  |

| Chap   | ter 2: Vacuum Spacer Transistors                                            | 6  |

| 2.1    | Introduction                                                                | 6  |

| 2.2    | Historical Background                                                       | 8  |

| 2.3    | Process Integration                                                         | 9  |

| 2.     | 3.1 A vacuum spacer transistor with conventional contact process            | 9  |

|        | 2.3.1.1 The comparison structures with simulation                           | 9  |

|        | 2.3.1.2 Structure and Process Concept                                       | 9  |

| 11                                           |

|----------------------------------------------|

|                                              |

| 11                                           |

| 12                                           |

| 13                                           |

| 13                                           |

| 15                                           |

| 16                                           |

| 17                                           |

| 18                                           |

| 18                                           |

| 21                                           |

| 24                                           |

| 25                                           |

| 28                                           |

| <b>2</b> 9                                   |

| = 5                                          |

| 29                                           |

| 29<br>29                                     |

| 29                                           |

| 29<br>31                                     |

| 31<br>32                                     |

| 31<br>32                                     |

| 31<br>32<br>32                               |

| 31<br>32                                     |

| 31<br>32<br>34<br>35                         |

| 31<br>32<br>34<br>35<br>35                   |

| 29<br>31<br>32<br>34<br>35                   |

| 29<br>31<br>32<br>34<br>35<br>35             |

| 29<br>31<br>32<br>34<br>35<br>35<br>35<br>39 |

|                                              |

| Hapter 4: Corner Spacer Transistor  4.1 Introduction  4.2 Historical Background  4.3 Process Integration  4.3.1 The comparison structures by simulation  4.3.2 Structure and Process Concept  4.4 Simulation Results  4.4.1 A corner spacer transistor in high performance devices  4.4.1.1 A simple corner spacer transistor with silicon nitride and oxide  4.4.1.2 Corner spacer transistors with other materials  4.4.2 A corner spacer transistor in low stand-by power devices  4.4.2.1 A simple corner spacer transistor with silicon nitride and oxide  4.4.2.2 Corner spacer transistors with other materials  4.5 Summary  4.6 References  Chapter 5: Vacuum-Gap Interconnect  5.1 Introduction  5.2 Historical Background  5.2.1 Vacuum gap integration in aluminum interconnect  5.2.2 Vacuum gap integration in copper interconnect  5.3 Process Integration  5.3.1 A subtractive etch interconnect with vacuum-sheath structure  5.3.1.1 The comparison structures with simulation  5.3.1.2 Structure and Process Concept  5.3.2 A dual damascene interconnect with vacuum-corridor structure  5.3.2.1 The comparison structures with simulation  5.3.2.2 Structure and Process Concept  5.4 Modeling for Simulation  5.4.1 General Modeling for Interconnect | 54                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

| ~ · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |

| 4.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72                     |

| 4.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

| Chapter 5: Vacuum-Gap Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 74                     |

| Chapter 5: Vacuum-Gap Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7 <b>4</b>             |

| Shapter 5: Vacuum-Gap Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7 <b>4</b><br>74<br>76 |

| Shapter 5: Vacuum-Gap Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 747476                 |

| Shapter 5: Vacuum-Gap Interconnect  5.1 Introduction  5.2 Historical Background  5.2.1 Vacuum gap integration in aluminum interconnect  5.2.2 Vacuum gap integration in copper interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74767677               |

| Shapter 5: Vacuum-Gap Interconnect  5.1 Introduction  5.2 Historical Background  5.2.1 Vacuum gap integration in aluminum interconnect  5.2.2 Vacuum gap integration in copper interconnect  5.3 Process Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74767677               |

| Shapter 5: Vacuum-Gap Interconnect  5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74767777               |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7476777777             |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7476767777             |

| Shapter 5: Vacuum-Gap Interconnect  5.1 Introduction  5.2 Historical Background  5.2.1 Vacuum gap integration in aluminum interconnect  5.2.2 Vacuum gap integration in copper interconnect  5.3 Process Integration  5.3.1 A subtractive etch interconnect with vacuum-sheath structure  5.3.1.1 The comparison structures with simulation  5.3.1.2 Structure and Process Concept  5.3.2 A dual damascene interconnect with vacuum-corridor structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 747677777879           |

| Chapter 5: Vacuum-Gap Interconnect  5.1 Introduction  5.2 Historical Background  5.2.1 Vacuum gap integration in aluminum interconnect  5.2.2 Vacuum gap integration in copper interconnect  5.3 Process Integration  5.3.1 A subtractive etch interconnect with vacuum-sheath structure  5.3.1.1 The comparison structures with simulation  5.3.1.2 Structure and Process Concept  5.3.2 A dual damascene interconnect with vacuum-corridor structure  5.3.2.1 The comparison structures with simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7476777778798080       |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 747677777879808183     |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 747677777879808183     |

| 5.5  | 5.1 A subtractive etch interconnect with vacuum-sheath simulation | 85  |

|------|-------------------------------------------------------------------|-----|

| 4    | 5.5.1.1 Simulation implementation                                 | 85  |

| 4    | 5.5.1.2 Simulation Results                                        | 87  |

| 5.5  | 5.2 A dual damascene interconnect with vacuum-corridor simulation | 91  |

| 4    | 5.5.2.1 Simulation implementation                                 | 91  |

| 4    | 5.5.2.2 Simulation Results                                        | 92  |

| 5.6  | 6 Reasonable Expectation                                          | 96  |

| 5.7  | Summary                                                           | 98  |

| 5.8  | References                                                        | 99  |

| Chap | ter 6: Conclusions                                                | 101 |

| 6.1  | Summary of Work                                                   | 101 |

| 6.2  | Future Directions                                                 | 102 |

# **List of Figures**

| 1.1    | Gate delay and interconnect delay with scaling transistor                               | 1  |

|--------|-----------------------------------------------------------------------------------------|----|

| 1.2    | Doping concentration and junction depth                                                 | 2  |

| 1.3    | The trend of $V_{DS}$ and $V_{TH}$ with each generation                                 | 3  |

| 1.4    | The active and passive power densities                                                  | 3  |

| 1.5 a  | The illustrated mutual capacitance                                                      | 4  |

| 1.5 b  | Worst case interconnect delay due to crosstalk                                          | 4  |

|        |                                                                                         |    |

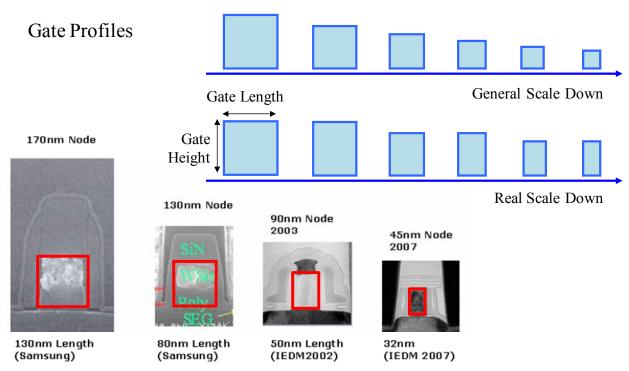

| 2.1    | The trend of vertical scaling down                                                      | 7  |

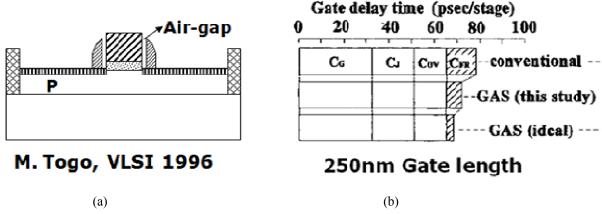

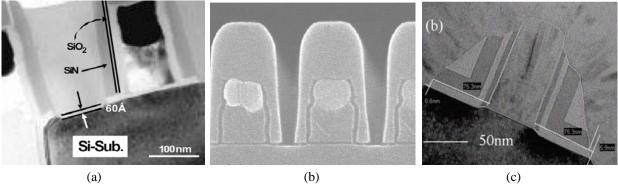

| 2.2 a  | Vertical view of Togo's air-gap transistor                                              | 8  |

| 2.2 b  | Comparison of each capacitance                                                          | 8  |

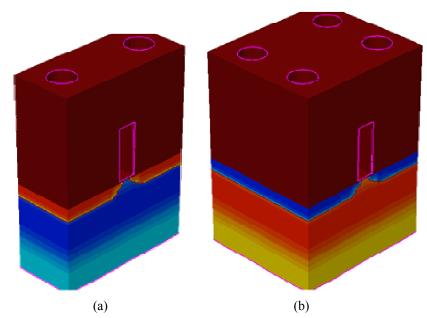

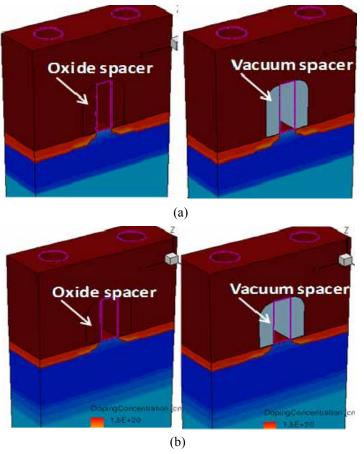

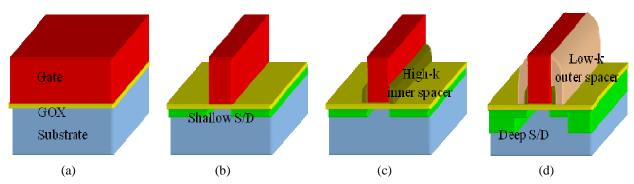

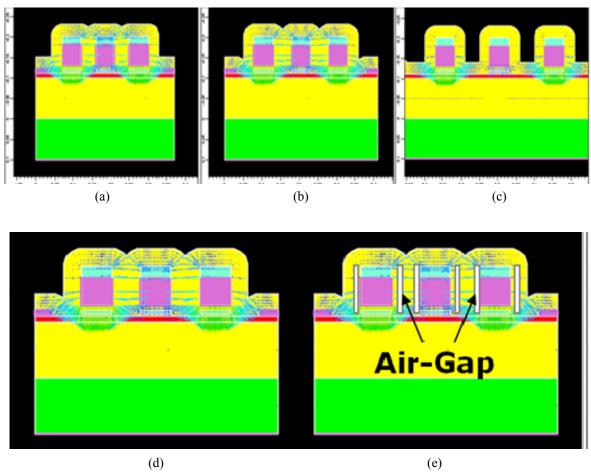

| 2.3    | The final structures of NMOSFETs using TSUPREM4                                         | 10 |

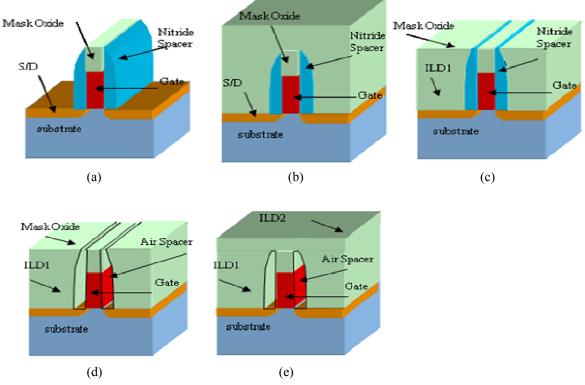

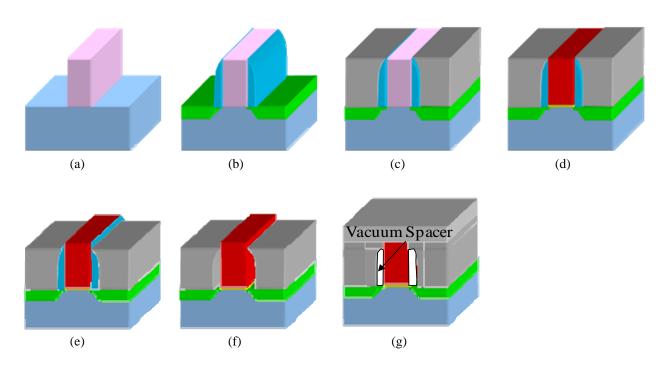

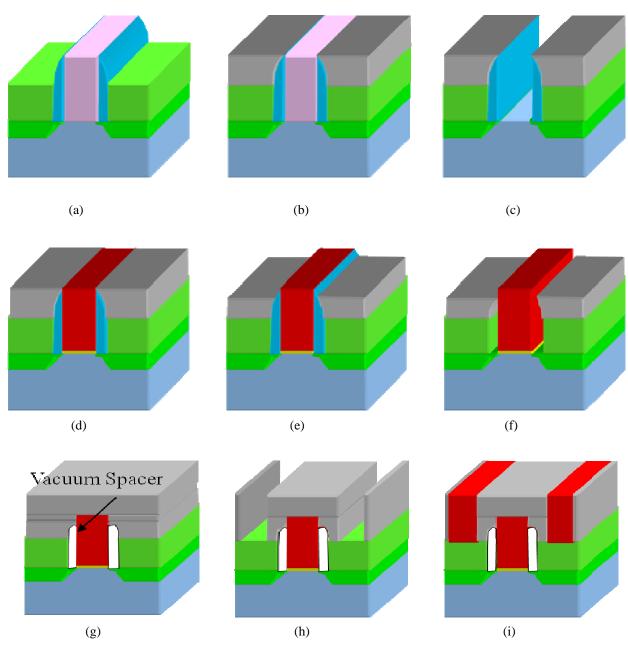

| 2.4    | The proposed process flows for a vacuum spacer transistor                               | 10 |

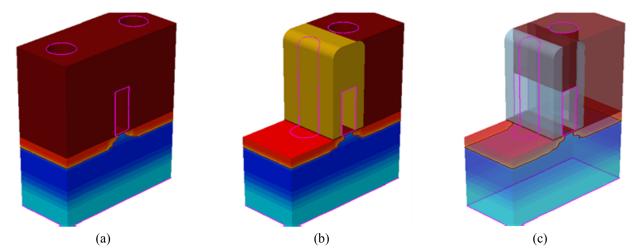

| 2.5    | NMOSFETs constructed with 3D simulator                                                  | 11 |

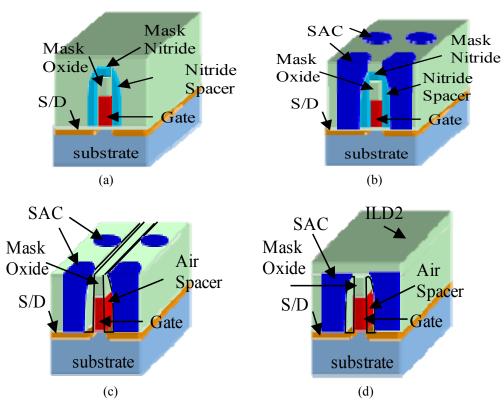

| 2.6    | The proposed process flow of the novel vacuum spacer transistor with SAC process        | 12 |

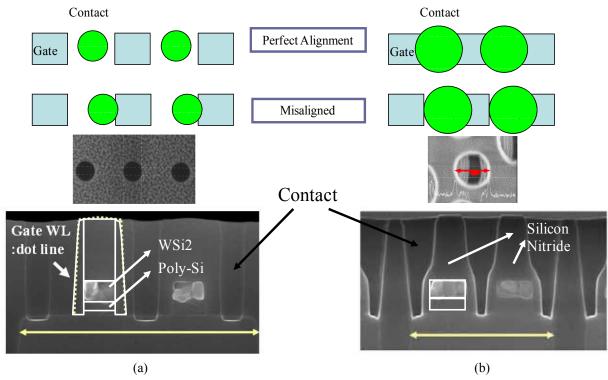

| 2.7 a  | The layout and vertical view of conventional contact process                            | 13 |

| 2.7 b  | The layout and vertical view of SAC process                                             | 13 |

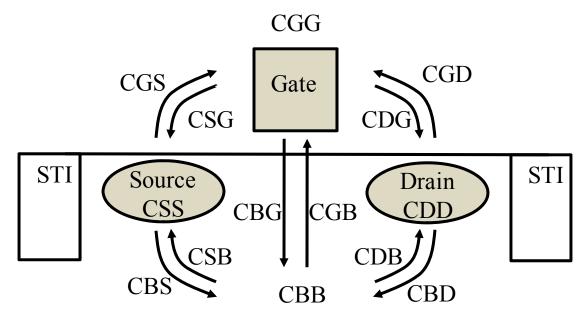

| 2.8    | MOS capacitance parameters                                                              | 14 |

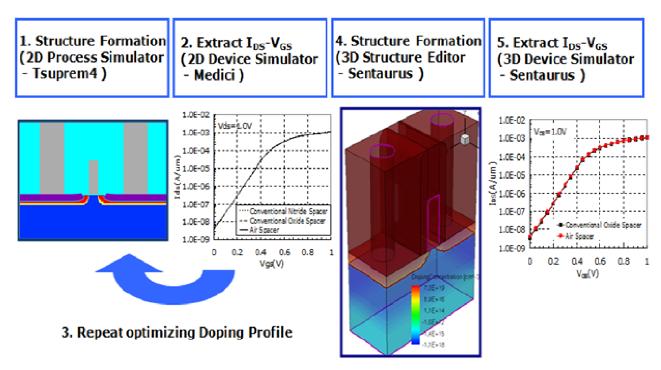

| 2.9    | Simulation Procedures                                                                   | 15 |

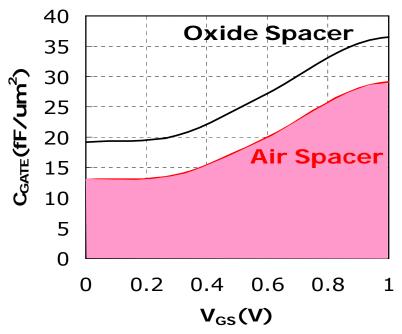

| 2.10   | Gate capacitances and switching energy                                                  | 16 |

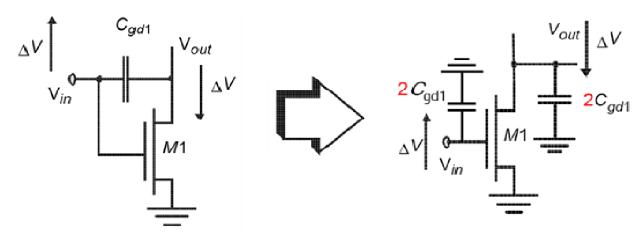

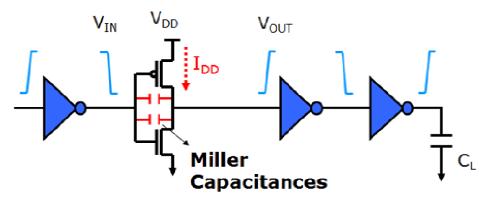

| 2.11   | The Miller capacitances                                                                 | 16 |

| 2.12 a | a 3D NMOSFET structure                                                                  | 17 |

| 2.12 t | o 3D PMOSFET structure                                                                  | 17 |

| 2.13   | The schematic of 4 stages of inverter structures                                        | 17 |

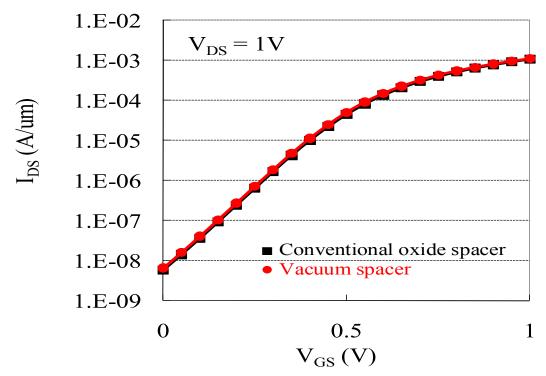

| 2.14   | Simulated I <sub>DS</sub> -V <sub>GS</sub> characteristics                              | 18 |

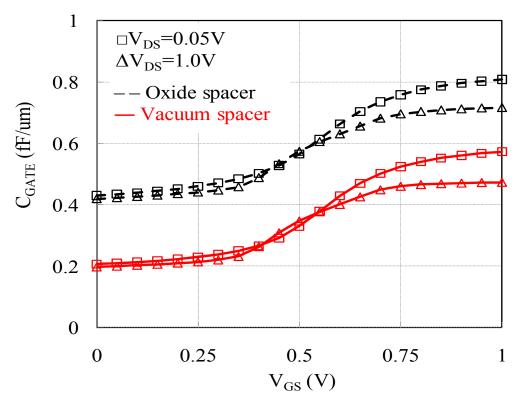

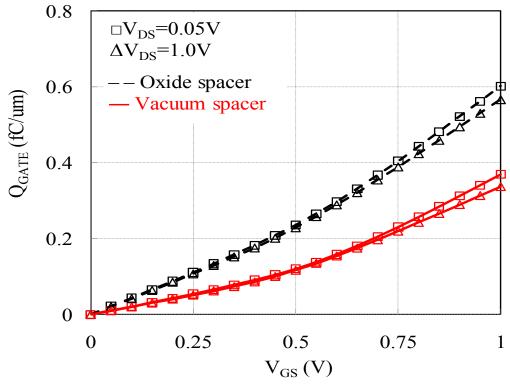

| 2.15   | The gate capacitances of oxide and vacuum spacers                                       | 19 |

| 2.16   | The total gate charge of oxide and vacuum spacers                                       | 19 |

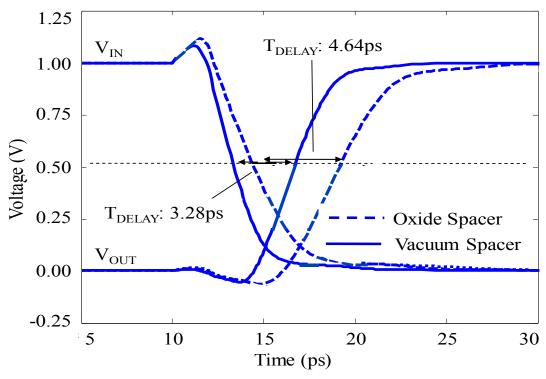

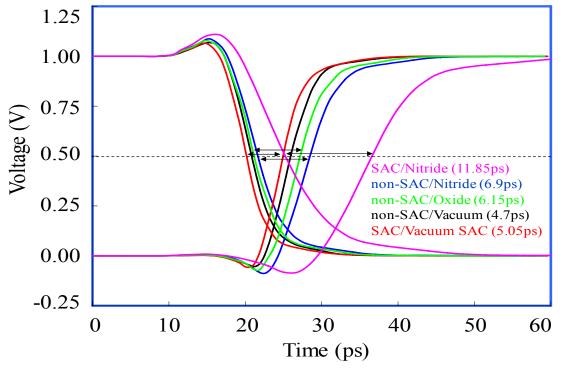

| 2.17   | The mixed-mode simulation of inverter delay                                             | 20 |

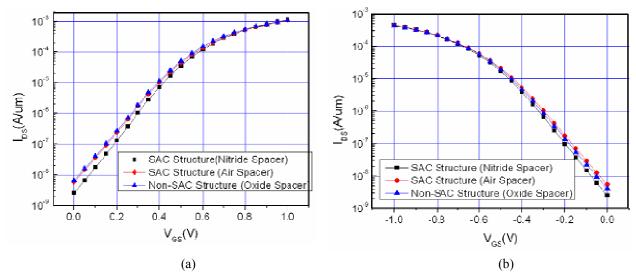

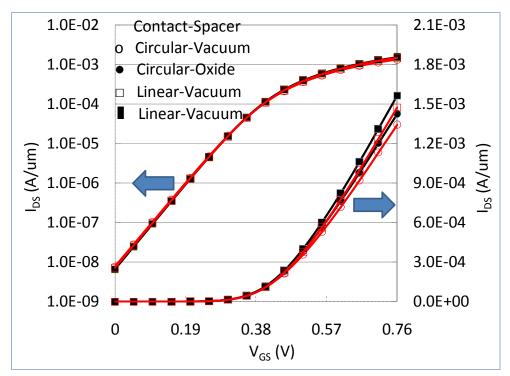

| 2.18 a | a Simulated I <sub>DS</sub> -V <sub>GS</sub> characteristics of three types of NMOSFETs | 21 |

| 2.18 t | Simulated I <sub>DS</sub> -V <sub>GS</sub> characteristics of three types of PMOSFETs   | 21 |

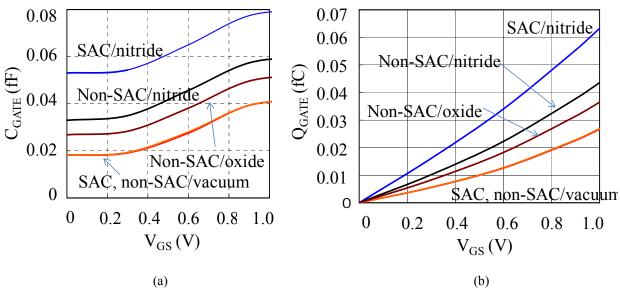

| 2.19 a | The gate capacitances of 5 different types of spacers and contacts                      | 22 |

| 2.19 t | The gate charge of 5 different types of spacers and contacts                            | 22 |

| 2.20   | The mixed-mode simulation of 5 types of inverters                                                                      | 22         |

|--------|------------------------------------------------------------------------------------------------------------------------|------------|

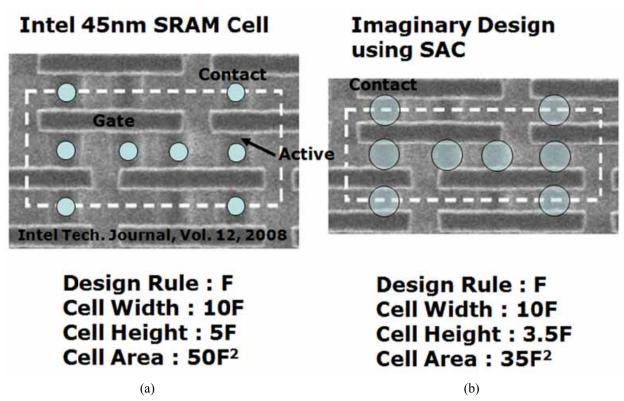

| 2.21 a | a The layout of Intel 45nm SRAM cell                                                                                   | 24         |

| 2.21 1 | b The imaginary layout of SRAM cell with SAC process                                                                   | 24         |

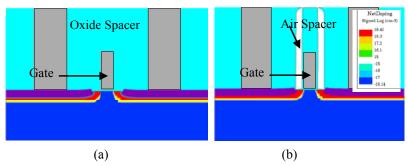

| 3.1    | The final structures of NMOSFETs using Sentaurus                                                                       | 30         |

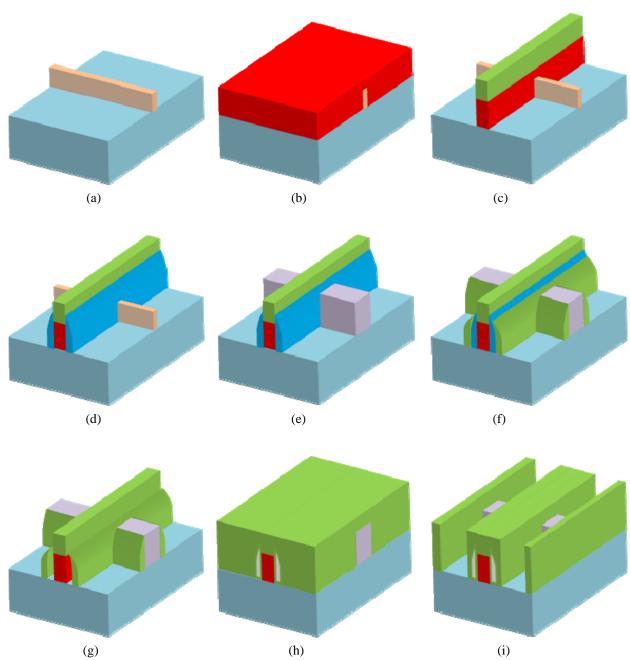

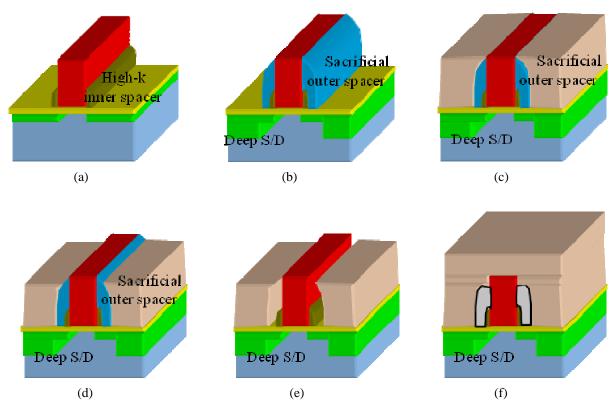

| 3.2    | A proposed process flow of the vacuum spacer transistor with gate last process                                         | 31         |

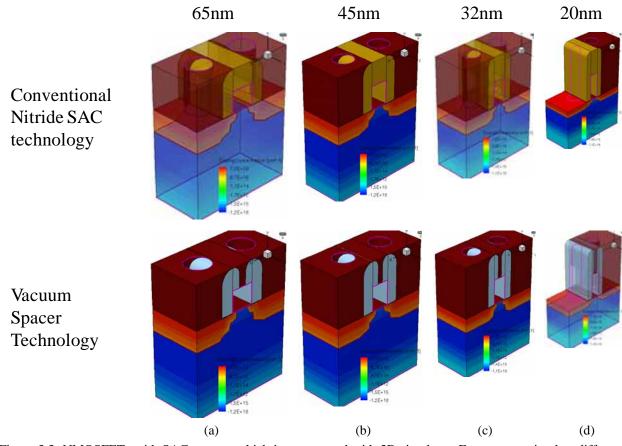

| 3.3    | 3D NMOSFETs with SAC process from 65nm to 20nm of gate length                                                          | 32         |

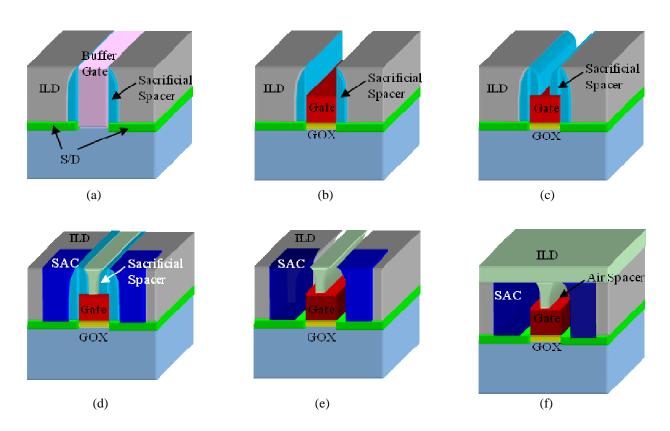

| 3.4    | The proposed process flow of the novel vacuum spacer transistor                                                        | 33         |

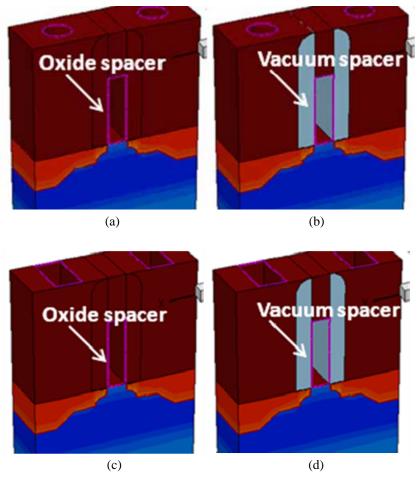

| 3.5    | NMOSFETs constructed with 3D simulator                                                                                 | 34         |

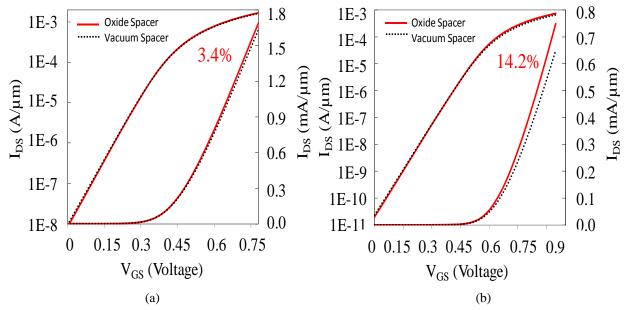

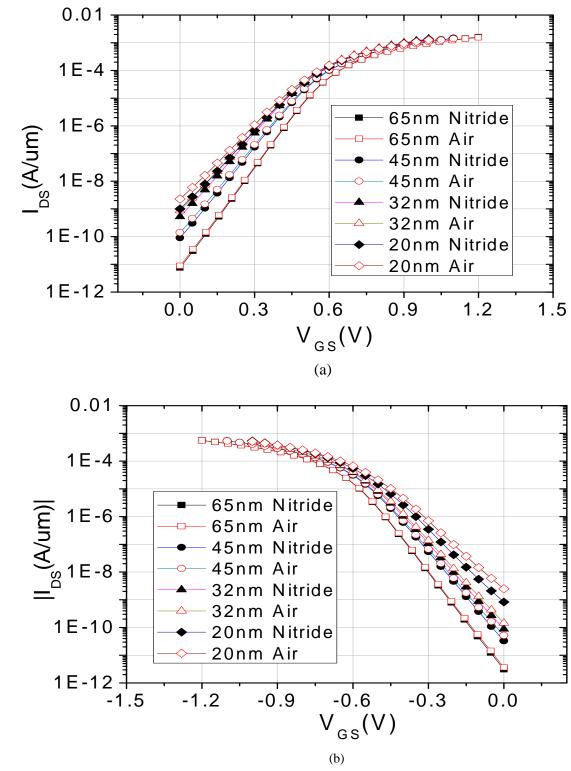

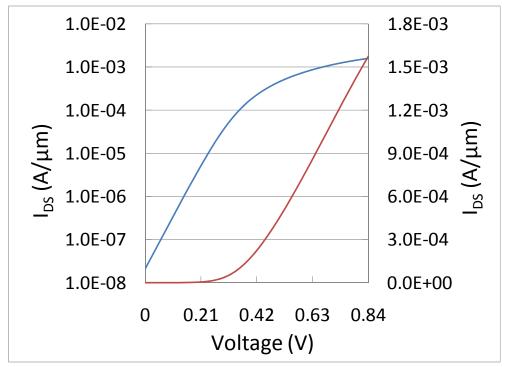

| 3.6    | The simulated I <sub>DS</sub> -V <sub>GS</sub> characteristics of NMOSFETs                                             | 36         |

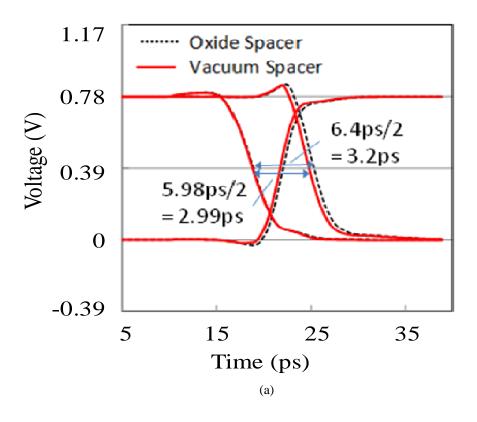

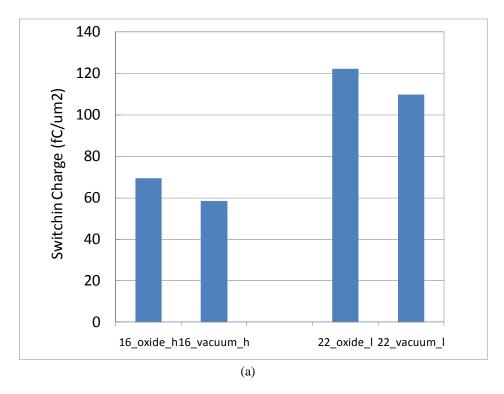

| 3.7 a  | The 3D mixed-mode simulation results for high performance device                                                       | 37         |

| 3.7 b  | The 3D mixed-mode simulation results for low standby power device                                                      | 37         |

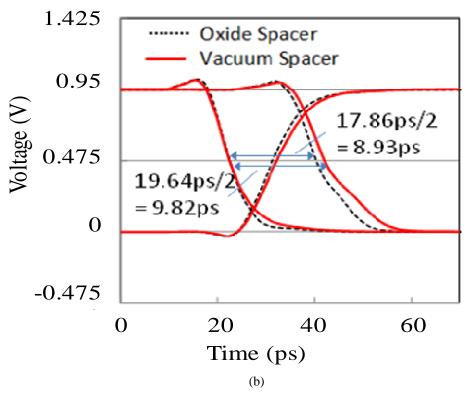

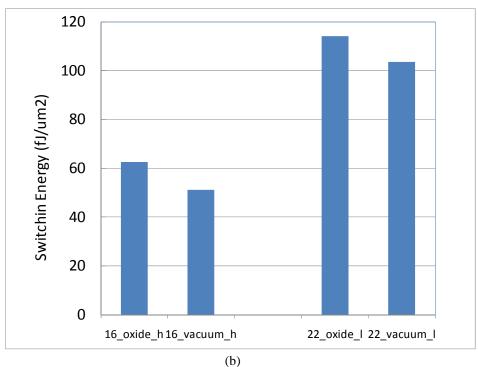

| 3.8 a  | The comparison of switching charges between oxide and vacuum spacer                                                    | 38         |

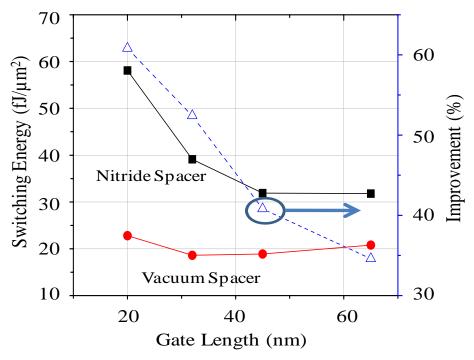

| 3.8 b  | The comparison of switching energies between oxide and vacuum spacer                                                   | 38         |

| 3.9    | The simulated $I_{DS}$ - $V_{GS}$ characteristics of MOSFETs with different gate lengths                               | 40         |

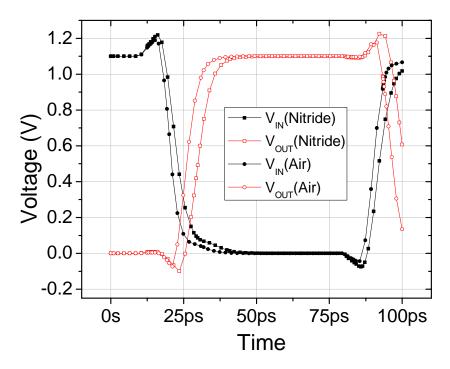

| 3.10   | The 3D mixed-mode simulation results at 45nm gate length                                                               | 41         |

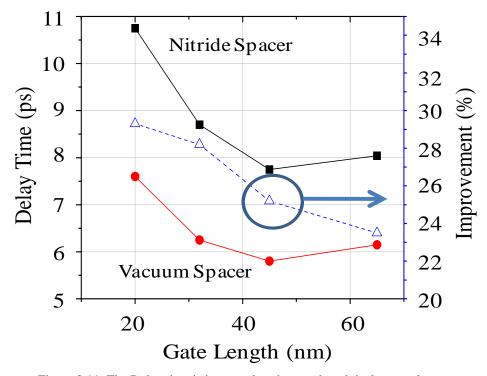

| 3.11   | The simulated delay time results with different gate lengths                                                           | 41         |

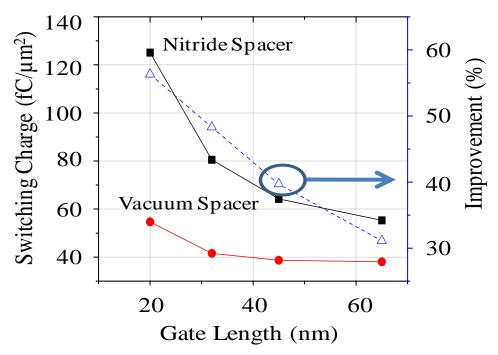

| 3.12   | The simulated switching charge results with different gate lengths                                                     | 42         |

| 3.13   | The simulated switching energy results with different gate lengths                                                     | 42         |

| 3.14   | The simulated $I_{DS}$ - $V_{GS}$ characteristics of the 4 types of NMOSFETs                                           | 44         |

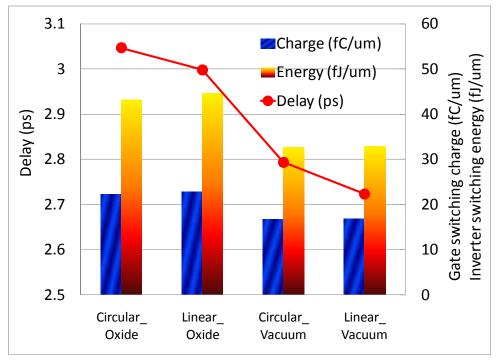

| 3.15   | The mixed-mode simulation results of the 4 stage inverter chains (Fan-out = 1)                                         | 44         |

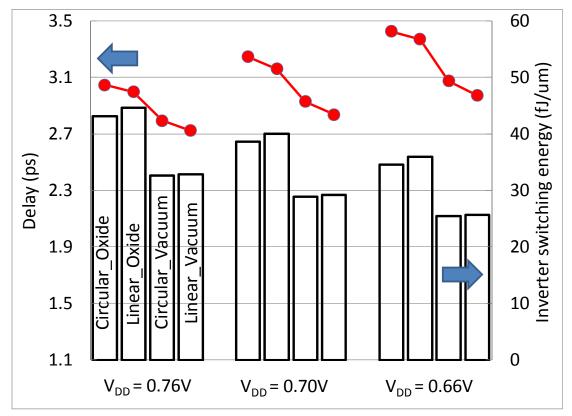

| 3.16   | Simulated inverter delay and the switching energies at three $V_{\text{DD}}$                                           | 45         |

| 3.17   | The proposed process flow of the novel vacuum spacer transistor with gate last and ra S/D and linear contact processes | ised<br>47 |

| 3.18   | The proposed process flow of the novel vacuum spacer transistor with FinFET and lincontact processes                   | nea<br>48  |

| 4.1 a  | Vertical view of Jaegoo's dual spacer transistor                                                                       | 53         |

| 4.1 b  | Vertical view of Jun-Wei's dual spacer transistor with metal gate process                                              | 53         |

| 4.1 c  | Vertical view of Chun-Jen's sidewall spacer transistor                                                                 | 53         |

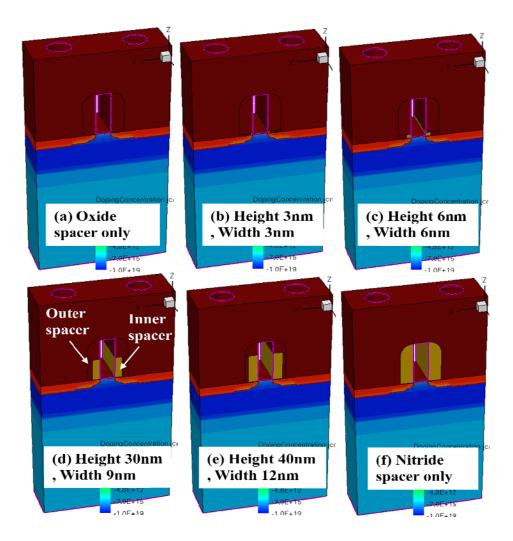

| 4.2    | The final structures of NMOSFETs using Sentaurus simulator                                                             | 54         |

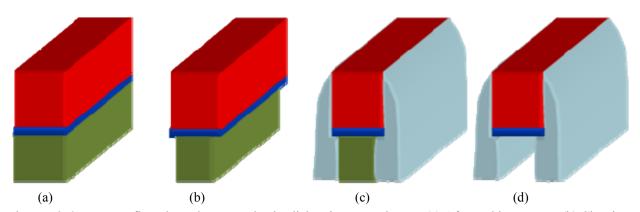

| 4.3    | The proposed process flows for a corner spacer transistor                                                              | 55         |

| 4.4    | The proposed process flows for a corner spacer with vacuum outer spacer transistor                                     | 56         |

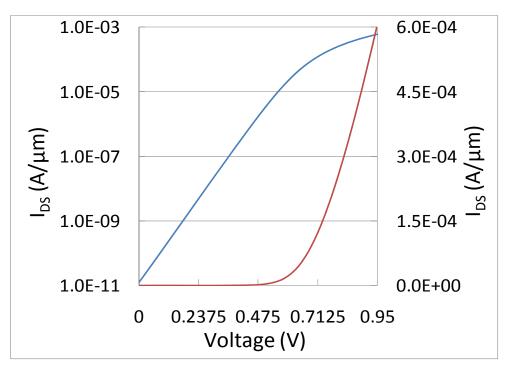

| 4.5   | The simulated $I_{DS}$ - $V_{GS}$ characteristics of the oxide spacer transistor in high performance device      |

|-------|------------------------------------------------------------------------------------------------------------------|

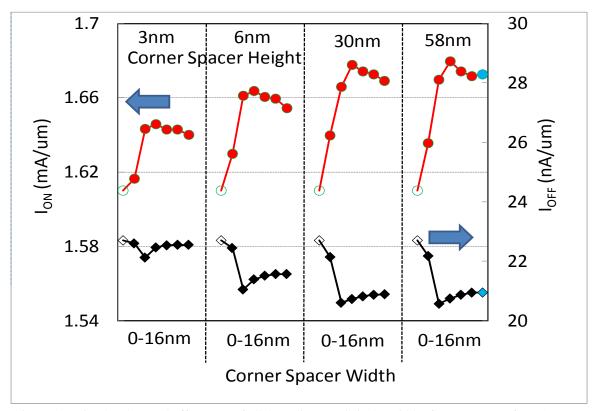

| 4.6   | Simulated on and off current of all the different spacer widths and heights in high performance device 58        |

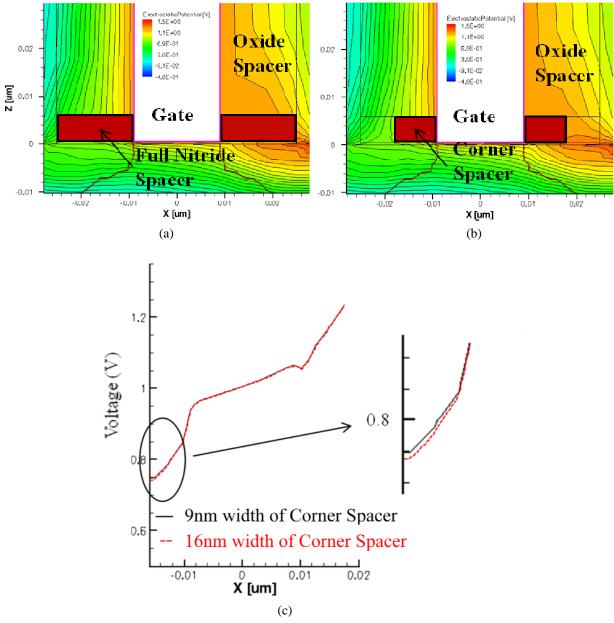

| 4.7 a | Electric potential contour plot of transistor with 16nm all silicon nitride spacer 59                            |

| 4.7 b | Electric potential contour plot of transistor with 9nm silicon nitride spacer 59                                 |

| 4.7 c | The electric potential at the semiconductor/dielectric interfaces of the two transistors 59                      |

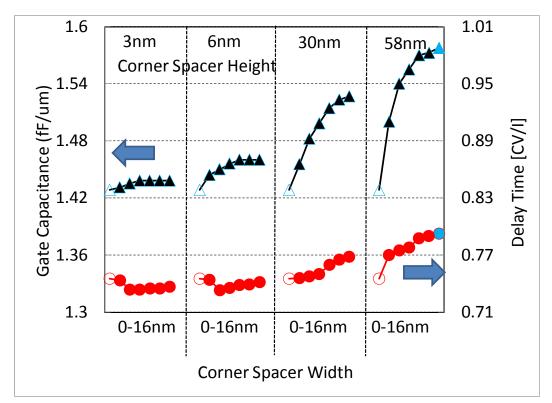

| 4.8   | Simulated gate capacitance and CV/I of all the different spacer widths and heights in high performance device 60 |

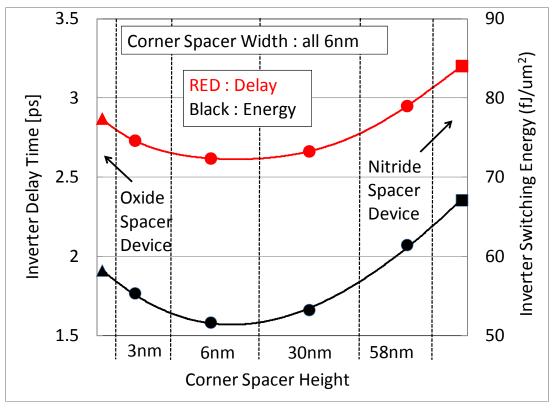

| 4.9   | The 3D mixed-mode simulation results of the different spacer widths and heights in high performance device 61    |

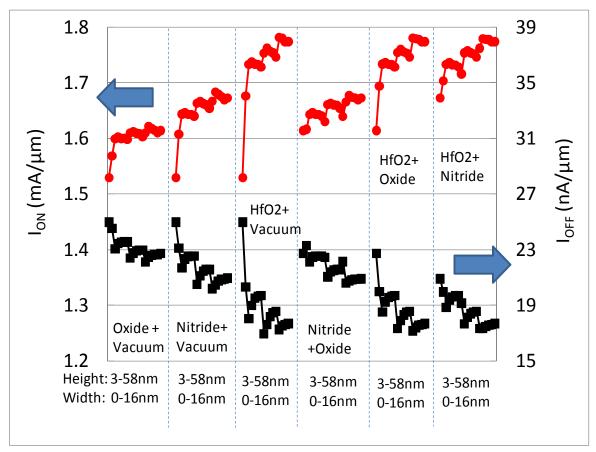

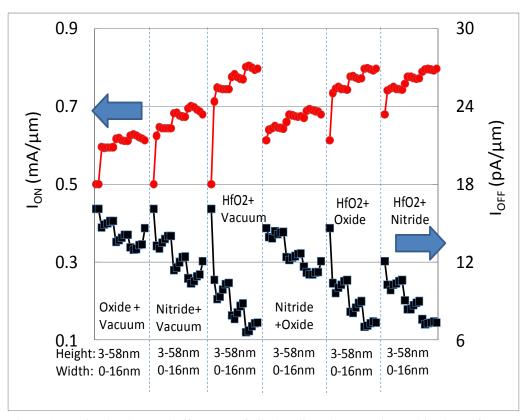

| 4.10  | Simulated on and off current of all the different spacer materials in high performance device                    |

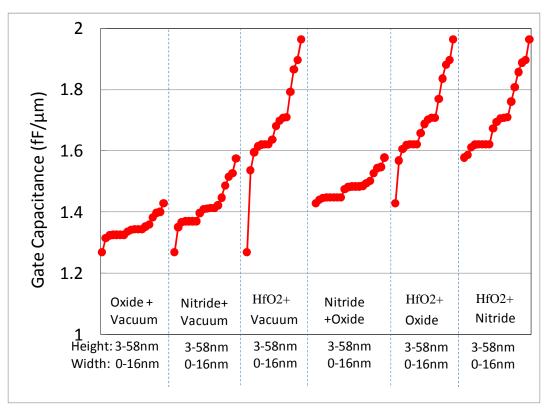

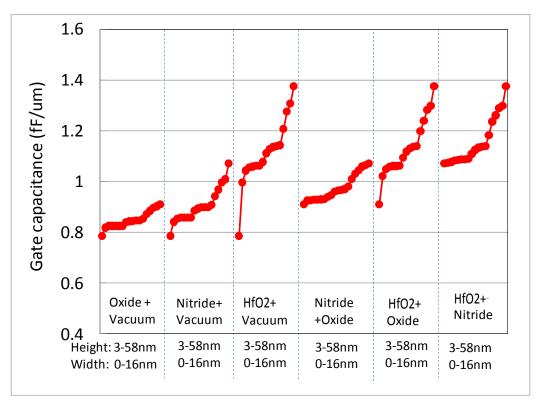

| 4.11  | Simulated gate capacitances of all the different spacer materials in high performance device                     |

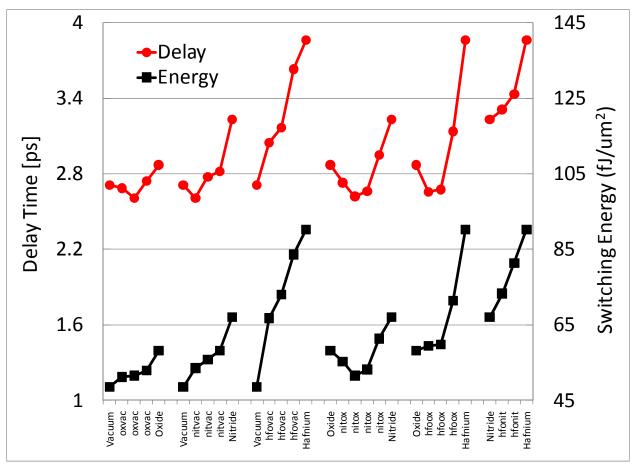

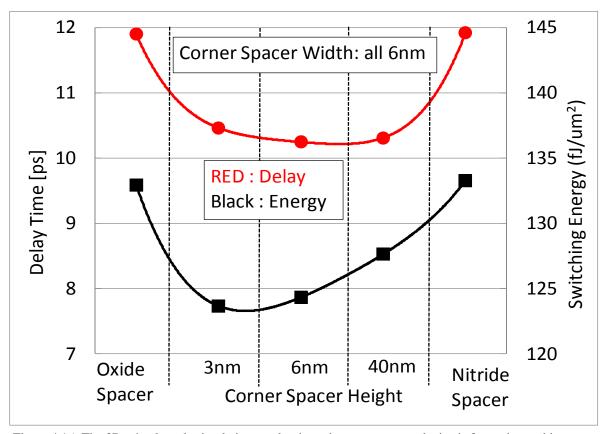

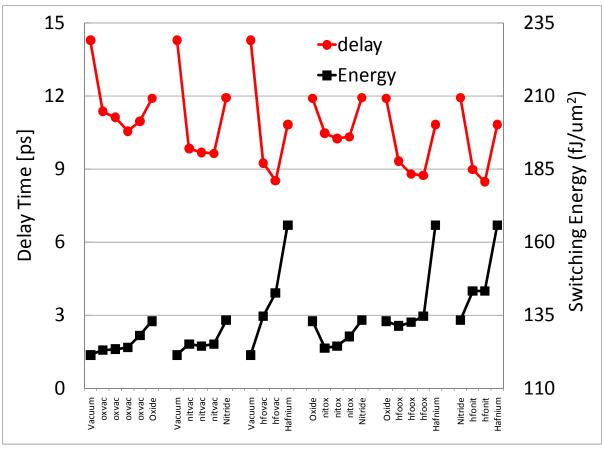

| 4.12  | The 3D mixed-mode simulation results of the different spacer materials in high performance device 64             |

| 4.13  | The simulated $I_{DS}$ - $V_{GS}$ characteristics of the oxide spacer transistor in low stand-by power device    |

| 4.14  | Simulated on and off current of all the different spacer widths and heights in low stand-by power device         |

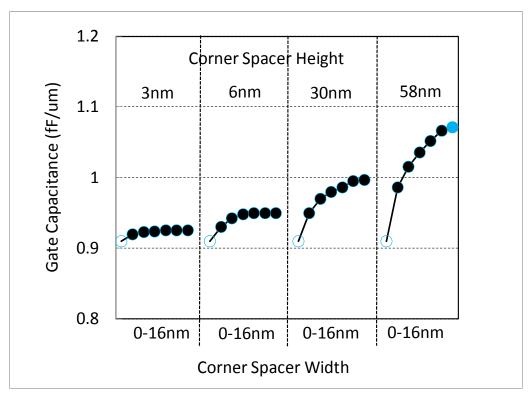

| 4.15  | Simulated gate capacitances of all the different spacer widths and heights in low stand-by power device          |

| 4.16  | The 3D mixed-mode simulation results of the different spacer widths and heights in low stand-by power device 68  |

| 4.17  | Simulated on and off current of all the different spacer materials in low stand-by power device 69               |

| 4.18  | Simulated gate capacitances of all the different spacer materials in low stand-by power device 70                |

| 4.19  | The 3D mixed-mode simulation results of the different spacer materials in low stand-by power device 71           |

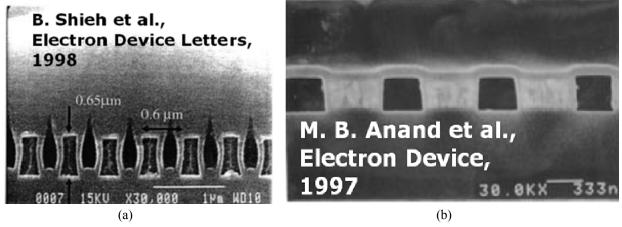

| 5.1a  | Vacuum gap integration profile using non-conformal CVD process in aluminum interconnect 76                       |

| 5.1 b | Vacuum gap integration profile using sacrificial material in aluminum interconnect 76                            |

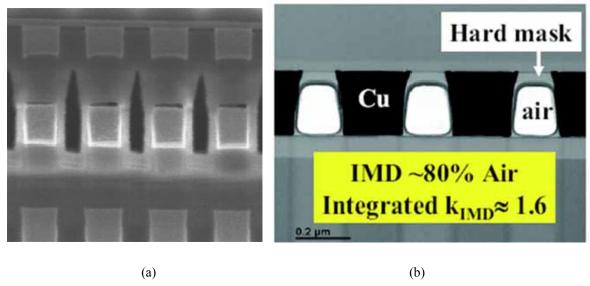

| 5.2 a | Vacuum gap integration profile using non-conformal CVD process in copper interconnect                            |

| 5 2 h | Vacuum van integration profile using sacrificial material in copper interconnect 77                              |

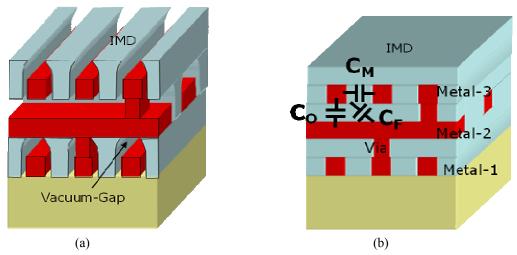

| 5.3  | Comparison between the suggested vacuum-gap interconnect and conventional subtrateth interconnect structures     | ctive<br>78 |  |  |

|------|------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| 5.4  | 3D rendering of the proposed air-sheath interconnect structure                                                   | 78          |  |  |

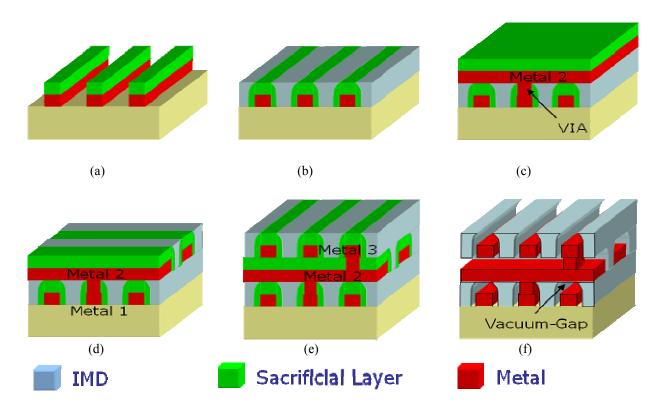

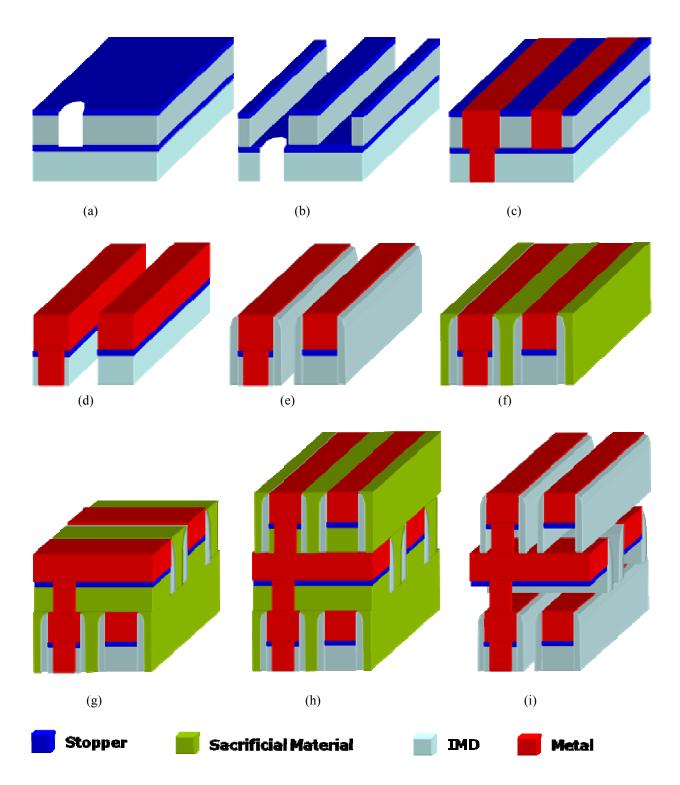

| 5.5  | The proposed process flow of the vacuum-sheath interconnect                                                      |             |  |  |

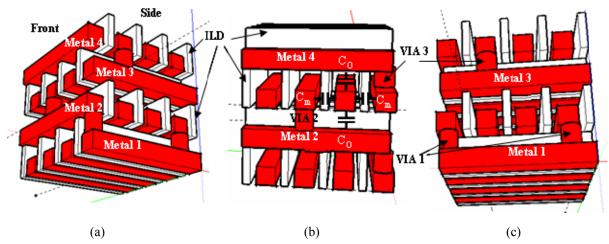

| 5.6  | Comparison between the suggested vacuum-corridor interconnect and conventional damascene interconnect structures | dual<br>80  |  |  |

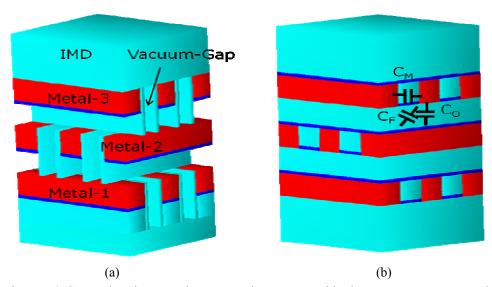

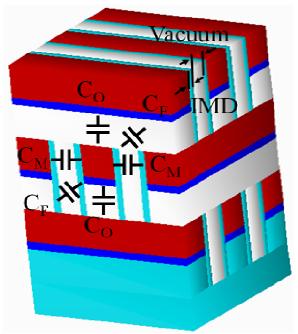

| 5.7  | 3D rendering of the proposed vacuum-corridor interconnect structure                                              | 81          |  |  |

| 5.8  | The proposed process flow of making the dielectric support beams                                                 | 81          |  |  |

| 5.9  | The proposed process flow of the dual damascene interconnect with vacuum-constructure                            | ridor<br>82 |  |  |

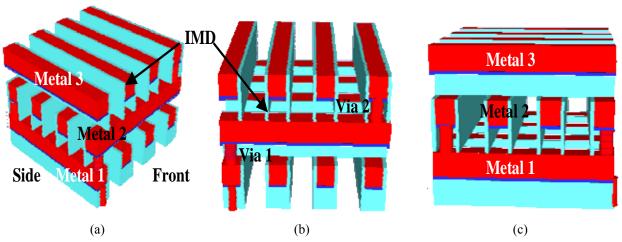

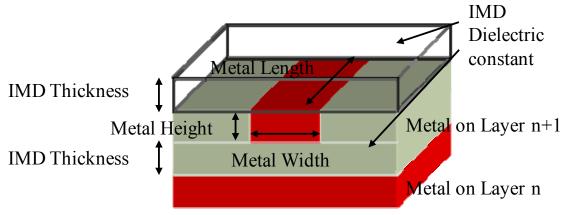

| 5.10 | Interconnect parameters for accurate 3D field solver simulation                                                  | 84          |  |  |

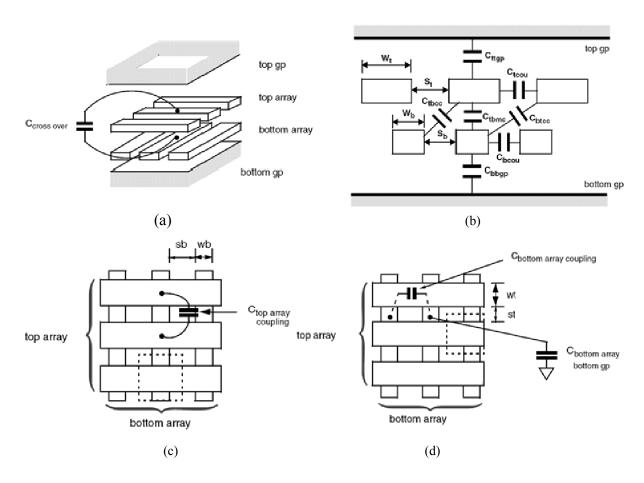

| 5.11 | The represented interconnect capacitances                                                                        | 84          |  |  |

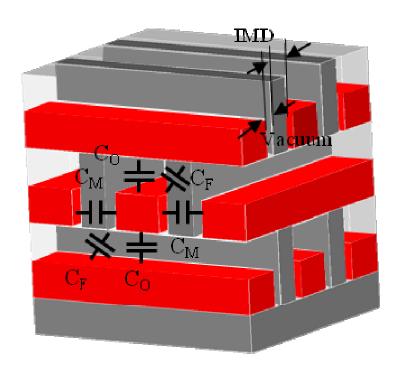

| 5.12 | The simulation structure of vacuum sheath interconnect using RAPHAEL simulator                                   | 86          |  |  |

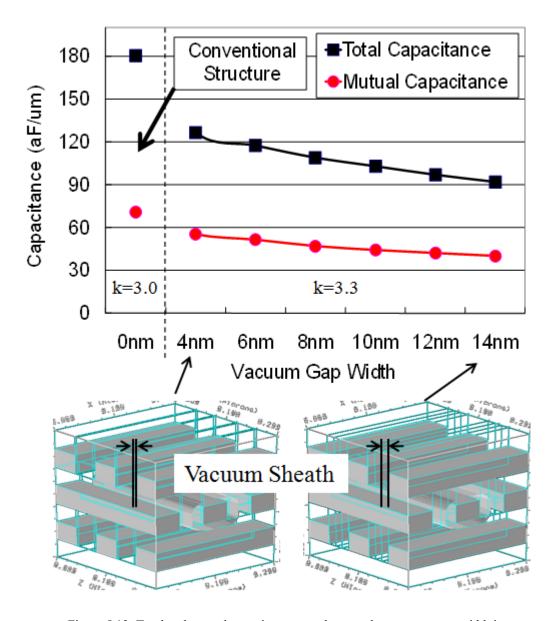

| 5.13 | Total and mutual capacitances vs. different vacuum gap widths                                                    | 87          |  |  |

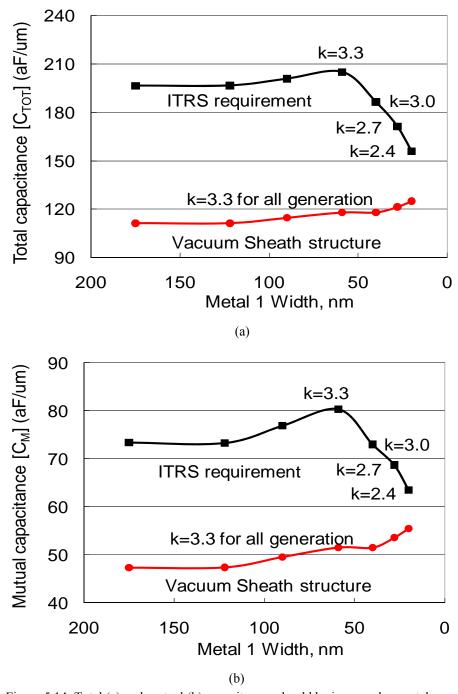

| 5.14 | Total and mutual capacitances vs. different metal widths                                                         | 89          |  |  |

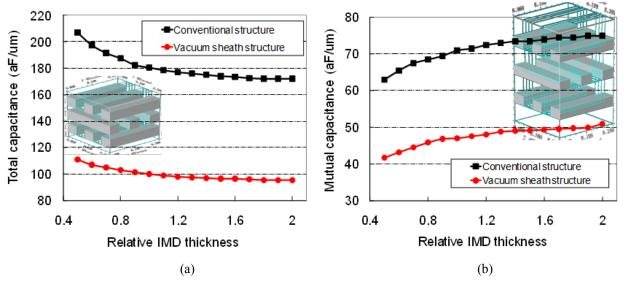

| 5.15 | Total and mutual capacitances vs. different IMD thicknesses                                                      | 90          |  |  |

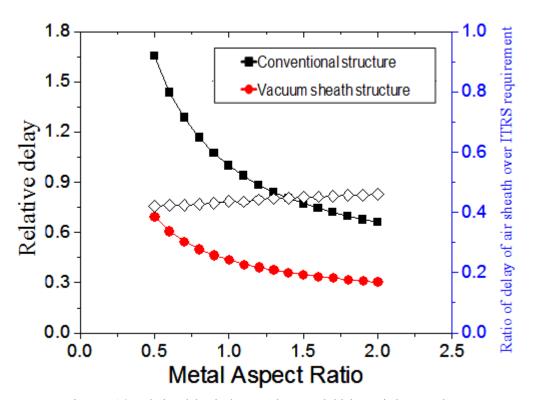

| 5.16 | Relative delay vs. different metal thicknesses                                                                   | 90          |  |  |

| 5.17 | The simulation structure of vacuum corridor dual damascene interconnect RAPHAEL simulator                        | using<br>92 |  |  |

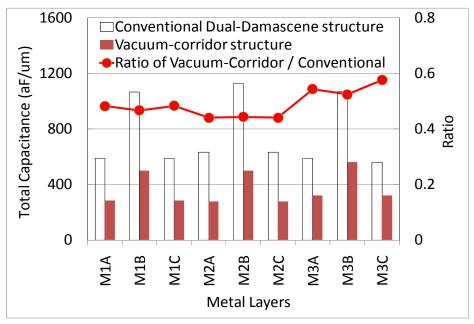

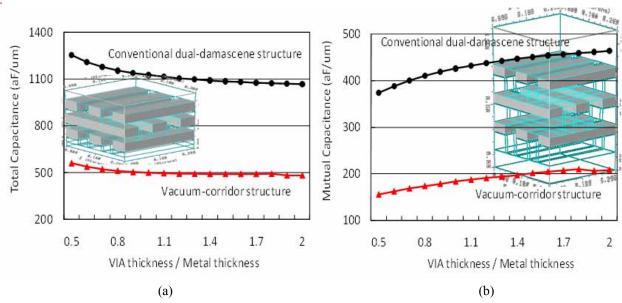

| 5.18 | Total capacitances vs. each metal layer                                                                          | 93          |  |  |

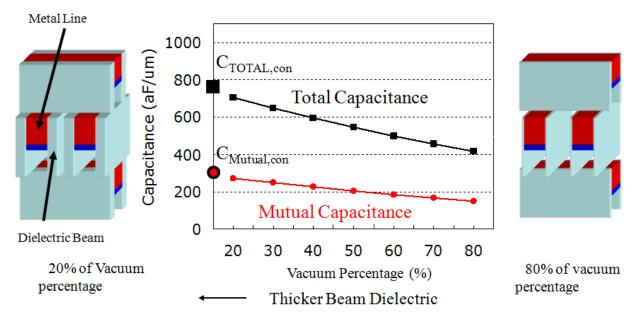

| 5.19 | Total and mutual capacitances vs. vacuum percentages                                                             | 93          |  |  |

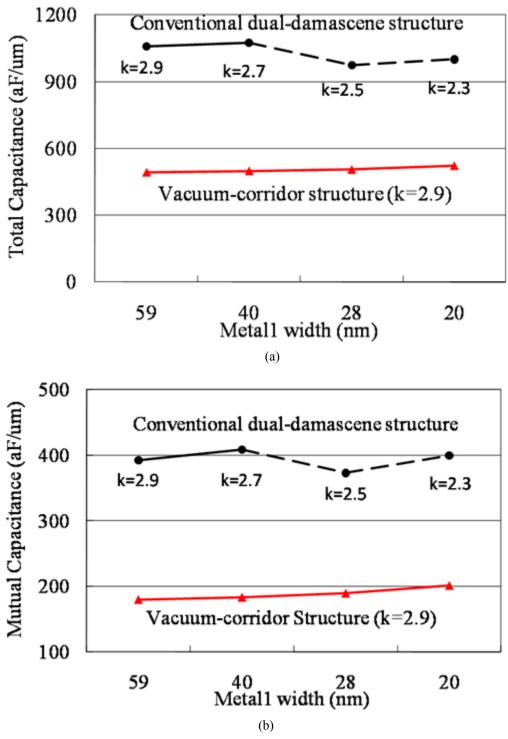

| 5.20 | Total and mutual capacitances vs. different metal widths                                                         | 94          |  |  |

| 5.21 | Total and mutual capacitances vs. different IMD thicknesses                                                      | 95          |  |  |

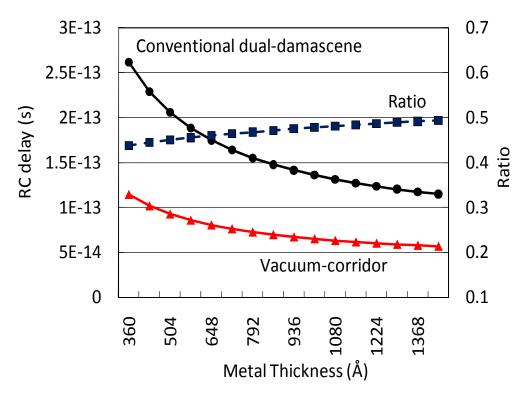

| 5.22 | RC delay vs. different metal thicknesses                                                                         | 96          |  |  |

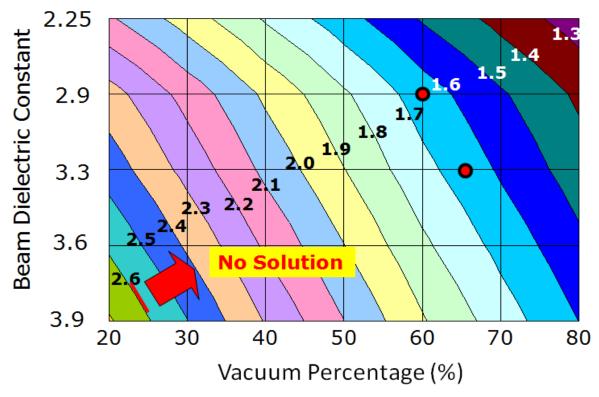

| 5.23 | The effective dielectric constants vs. beam dielectric constants and vacuum percentage                           | es 98       |  |  |

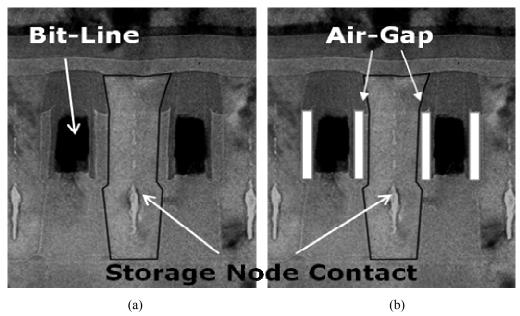

| 6.1  | Vertical view of bit line and storage node contact in DRAM cell                                                  | 102         |  |  |

| 6.2  | Vertical view of NAND flash cell structure                                                                       | 103         |  |  |

|      |                                                                                                                  |             |  |  |

# **List of Tables**

| 2.1 | The equations of six capacitances                                                                                 | 14          |

|-----|-------------------------------------------------------------------------------------------------------------------|-------------|

| 2.2 | The characteristics of oxide and vacuum spacers                                                                   | 20          |

| 2.3 | The characteristics of transistors and inverters                                                                  | 23          |

|     |                                                                                                                   |             |

| 3.1 | ITRS specifications and simulation parameters                                                                     | 30          |

| 3.2 | Several key parameters at each generation                                                                         | 33          |

| 3.3 | The characteristics of transistors and inverters between oxide and vacuum spacers                                 | 39          |

| 3.4 | Characteristics of transistors and inverters between conventional SAC and SAC vacuum spacer structures            | with<br>43  |

| 3.5 | Comparison of four different transistors                                                                          | 46          |

| 5.1 | ITRS 2008 specifications for interconnect and the assumptions for the simulational aluminum interconnect          | on in<br>86 |

| 5.2 | ITRS 2008 specifications for interconnect and the assumptions for the simulation in damascene copper interconnect | dual<br>91  |

| 5.3 | Characteristics summary of vacuum sheath interconnect                                                             | 97          |

| 5.4 | Characteristics summary of vacuum corridor interconnect                                                           | 97          |

### Acknowledgements

Firstly, I would like to thank my research advisor Professor Chenming Hu. His sincere and expert advice led me to find the interesting research topic and keep going to the right way of the research. His unwavering interest in my work have encouraged for me to do my Ph. D. study and research. I have become a better engineer and scholar as result of his ungrudging concern. I would also like to thank Professor Tsu-Jae King Liu for being a member of my committee and for all her advice and feedback. Professor King has been a wonderful source of help with regards to fabrication challenges in Microlab for all device group students. I would like to thank Professor Eugene E. Haller for being a member of my dissertation committee and helping to review my thesis.

I am heartily thankful to my wife, Jeong Hyun Kim for supporting and encouraging me to pursue my Ph.D. degree. Without my wife's encouragement, I would not have finished the degree. I really thank my lovely daughters, Hyein Park and Hyewon Park, for adjusting well to life in America. My mother has prayed to God for my study and health. I really appreciate it.

I would like to acknowledge SAMSUNG, one of the leading semiconductor companies in the world, for funding and supporting me.

Lastly, I would like to thank device group, one of the smartest and friendliest collaborative research groups in the world. I consider it a privilege to be a device group alumnus. I want to thank, in particular, Kanghoon Jeon and Changhwan Shin for being my closest friends. We entered the same year and have been through the worst of times and best of times in graduate school together. They have always been willing help me and more than happy to answer my questions even when I bother him too much. I would also like to thank Jaeseok Jeon, Sunghwan Kim, Pratik Patel, and Anupama Bowonder for their help to my fabrication works. I will miss playing tennis on Wednesday nights. Finally, I had a wonderful time with all my friends in this great school, University of California, Berkeley.

# Chapter 1

# The Needs for Vacuum Gap Structures

# 1.1 Scaling down is no longer the absolute solution for improving circuit speed

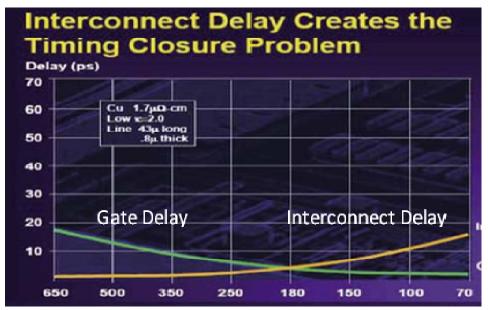

All the modern digital logic devices consist of two major elements: transistors and metal lines for interconnecting them. Scaling the transistor size improves the on-current and reduces the switching time and hence the logic delay. However, this scaling increases the resistance and capacitance of the metal lines, and therefore the overall interconnect delay is increased. Hence, scaling improves the logic delay but degrades the interconnection delay as shown in Figure 1.1.

Figure 1.1: The gate delay is reduced but the interconnect delay is increased as scaling the transistor size. [1.1]

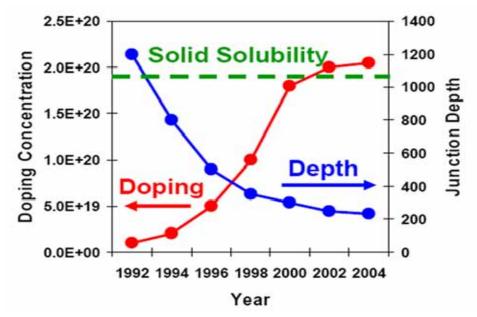

Furthermore, scaling transistors is more and more difficult. Scaling gate oxide is hard to be achieved due to gate leakage current and scaling the gate length is also hard to be demonstrated because of short channel effect (SCE). And scaling source/drain contact induces high contact resistance which drops the voltage a lot so that current is degraded. Junction depths have not scaled at previous historical trends due to inability to increase active dopant concentrations as shown in Figure 1.2. This makes SCE improvements extremely difficult and limits threshold voltage scaling. Thus, the circuit speed cannot be improved much with scaling transistors. Therefore, scaling is no longer the absolute solution for the circuit speed due to the interconnect delay and the difficulty of scaling transistors. In order to improve the circuit speed, reducing capacitance is more and more important.

Figure 1.2: The doping concentration cannot be increased due to the solid solubility so that junction depth is hard to be reduced. [1.2]

#### 1.2 CMOS Power density has increased with scaling transistors

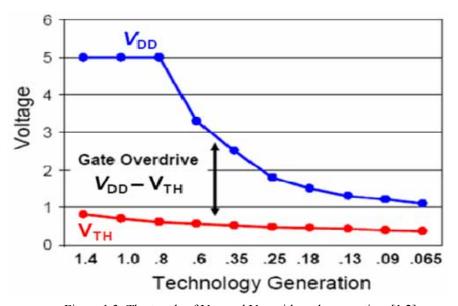

Figure 1.3 shows that the trends of the power-supply voltage  $(V_{DD})$  and the threshold voltage  $(V_{TH})$  with each generation. In order to scale  $V_{DD}$  at the same drive current  $(I_{ON})$ ,  $V_{TH}$  should be reduced as following Eq. (1.1). However, decreasing  $V_{TH}$  increases the off-current exponentially. Thus,  $V_{TH}$  cannot be scaled down aggressively as shown in Figure 1.3. From this reason, scaling  $V_{DD}$  is extremely difficult as the technology node gets small.

$$I_{ON} \propto (V_{DD} - V_{TH})^{\alpha}$$

, where  $\alpha = 1-2$  (1.1)

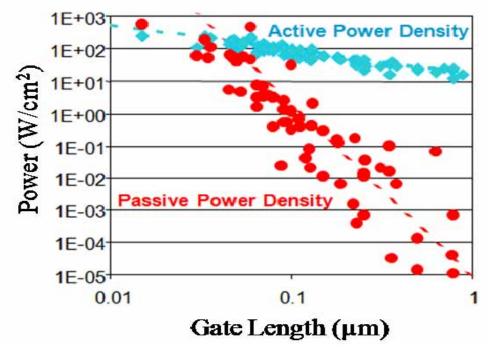

Reducing  $V_{DD}$  is the most effective solution of power consumption in circuit devices. However, CMOS power density has increased with transistor scaling since  $V_{DD}$  has not been scaled down in proportion to the transistor channel length. The active and passive powers are closely related by capacitance and  $V_{DD}$  which are defined as Eq. (1.2). Figure 1.4 shows that

active and passive power densities are increased by 1.3 times /generation and 3 times /generation, respectively. This power crisis will become more severe with increasing device density. Thus, reducing capacitance is a good solution to reduce power consumption.

$$P_{ACTIVE} \propto CV_{DD}^2, P_{PASSIVE} \propto V_{DD}$$

(1.2)

Figure 1.3: The trends of  $V_{DD}$  and  $V_{TH}$  with each generation. [1.2]

Figure 1.4: The active and passive power densities are increased as the gate length is decreased. [1.3]

#### 1.3 Crosstalk noise is also a big problem

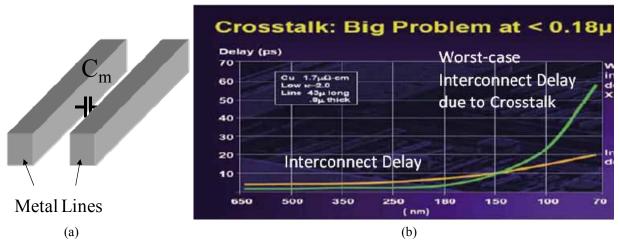

Crosstalk noise is defined as an undesired coupling from one circuit node to another. This noise is closely related the mutual capacitance which is the capacitance between the parallel metal lines as shown in Eq. (1.3). Figure 1.5 (a) illustrates mutual capacitance. As the technology node gets smaller, this crosstalk noise is extremely difficult to solve. James Meindl, director of the Microelectronics Research Center at the Georgia Institute of Technology, said that the tyranny of interconnects is threatening the timing, power, and cost of next-generation chips. For an example, interconnect switching energy is five times that of MOSFET switching energy at 100nm technology but the interconnect energy becomes 30 times greater at 35nm technology [1.4]. Jay McDougal said that signal integrity was really an order of magnitude worse as shown in Figure 1.5 (b) [1.5]. Therefore, crosstalk noise is also a big problem with scaling down. Reducing capacitance is also very helpful to decrease crosstalk noises.

CROSSTALK NOISE

$$\propto C_{\text{MUTUAL}}$$

(1.3)

Figure 1.5: (a) Mutual capacitance is defined by figure . (b) Crosstalk noise becomes a big problem as the technology node gets smaller. [1.1]

#### 1.4 A possible solution

Reducing capacitance is good for speed, power, and crosstalk noise from Section 1.1, 1.2, and 1.3. A lot of research about decreasing capacitance has been studied. Finding low-k material is one option. However, most of low-k materials have porous structure so that the poor structural stability induces reliability problem.

Another option is the combination of conventional material and vacuum. Vacuum is the lowest dielectric material but it cannot be demonstrated by itself. There were lots of patents and papers about this vacuum gap structure. However, most of the research have been focused on interconnect capacitance. The fringing capacitance of transistor is increased at the small gate

length device. Therefore, the vacuum gap structure of transistor will be an attractive structure to overcome delay, power consumption, and crosstalk noise.

#### 1.5 Research outline

The overall focus of this research is to study novel device structures for the purpose of improving complementary metal-oxide semiconductor (CMOS) speed and power consumption. The scaling of CMOS technology has been the driving force for technology advancements in the semiconductor industry over the last few decades. Speed and power are the most important parameters in scaling CMOS devices. These two parameters are closely related to each other. Increasing current is good for speed but this higher current consumes a lot of energy and power. Decreasing drain voltage ( $V_{\rm DD}$ ) leads low power consumption but it makes on-current slower and speed will be decreased. Reducing the device capacitance will be an increasingly important way to enhance the device speed and switching energy and power as the technology node is getting smaller and smaller.

The scope of this work is limited to simulation works of both transistors and interconnects. Chapter 2 reviews the general vacuum spacer transistor which is compared to the conventional spacer transistor. And self-aligned contact (SAC) process with vacuum spacer transistor is proposed for reducing capacitance as well as chip area. In Chapter 3, we propose the gate last process with vacuum gap spacer in both high performance and low stand-by power devices. The linear contact process will be used at the small feature size to overcome the contact resistance. Vacuum spacer transistor with linear contact process becomes more beneficial. In Chapter 4, corner spacer transistor is proposed. A small portion of high-k corner spacer improves the oncurrent and a large portion of low-k outer spacer decreases the capacitance. Chapter 5 introduces novel subtractive etch interconnect and dual damascene interconnect with vacuum gap structures. Chapter 6 summarizes all the works and shows considerable future directions.

#### 1.6 References

- [1.1] Zvi Or-Bach, "Paradigm Shift in ASIC Technology: In-Standard Metal, Out-Standard Cell", eASIC, March 9, 2006. [online] Available:

- $http://camars.kaist.ac.kr/\sim maeng/cs310/micro04/papers/Paradigm\_Shift\_in\_ASIC\_Technology.pdf$

- [1.2] Paul Packan, "Device and Circuit Interactions", International Electron Devices Meeting 2007, Short Course.

- [1.3] B. Meyerson, IBM, semico Conf., Januaruy 2004, Taiwan.

- [1.4] James Meindl, "Beyond Moore's Law: The Interconnect Era", a keynote speech at the International Symposium on Physical Design (ISPD), April 2004

- [1.5] Planet Analog, June 24, 2004, "Bad signals interfere with 90-nm designs", By Richard Goering. [online] Available:

http://www.planetanalog.com/showArticle.jhtml?articleID=19202088

# Chapter 2

### **Vacuum Spacer Transistors**

#### 2.1 Introduction

Speed and power consumption are the most important considerations for developing new transistors. These two parameters are closely related to each other. Increasing on current and decreasing total capacitance should be extremely helpful to develop a high performance transistor. However, higher on current consumes a lot of power. Decreasing  $V_{DD}$  leads to low power consumption but it makes on current lower and speed will be decreased. Thus, designers focus on only one parameter, either speed or power. Higher on current and lower total capacitance are important in high performance technology and  $V_{DD}$  scaling and low on and off current are essential in low power technology.

Capacitance reduction is remarkably useful to both speed and power. As the technology node gets smaller, starting material, gate stack, well/channel doping profile, extension junction, and contact to source/drain (S/D) process have been changed [2.1]. Thus, capacitance has been increased sharply.