# Single Program, Multiple Data Programming for Hierarchical Computations

Amir Ashraf Kamil

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2012-186 http://www.eecs.berkeley.edu/Pubs/TechRpts/2012/EECS-2012-186.html

August 10, 2012

Copyright © 2012, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Single Program, Multiple Data Programming for Hierarchical Computations

by

Amir Ashraf Kamil

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

**Computer Science**

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Katherine Yelick, Chair Senior Lecturer Paul Hilfinger Associate Professor Rastislav Bodik Professor David Wessel

Fall 2012

## Single Program, Multiple Data Programming for Hierarchical Computations

Copyright 2012 by Amir Ashraf Kamil

#### Abstract

#### Single Program, Multiple Data Programming for Hierarchical Computations

by

Amir Ashraf Kamil Doctor of Philosophy in Computer Science University of California, Berkeley Professor Katherine Yelick, Chair

As performance gains in sequential programming have stagnated due to power constraints, parallel computing has become the primary tool for increasing performance. Parallel computing has long been used in scientific computing, and programmers of the future will likely face many of the same challenges that occur in programming large-scale machines. One such challenge is that of hierarchy: machines are built in a hierarchical fashion, with a wide range of communication costs between different parts of a machine, and applications such as divide-and-conquer algorithms often have hierarchical structure.

Large-scale parallel machines are programmed primarily with the single program, multiple data (SPMD) model of parallelism. This model combines independent threads of execution with global collective communication and synchronization operations. Previous work has demonstrated the advantages of SPMD over other models: its simplicity enables productive programming and avoids many classes of parallel errors, and at the same time it is easy to implement and amenable to compiler analysis and optimization. Its local-view execution model allows programmers to take advantage of data locality, resulting in good performance and scalability on large-scale machines. However, it is a flat model that does not fit well with hierarchical machines or algorithms.

In this dissertation, we introduce the recursive single program, multiple data (RSPMD) execution model. This model extends SPMD with hierarchical, structured *teams*, or groupings of threads. We design RSPMD extensions for the Titanium language, including a hierarchical team data structure and lexically-scoped constructs for operating over teams. We demonstrate that these extensions prevent erroneous use of teams that would result in deadlock. In addition, we present a runtime mechanism for ensuring proper use of both global collective operations and collectives over teams, eliminating more potential sources of deadlock.

As analyzable as SPMD is, we demonstrate that RSPMD can also be analyzed precisely and efficiently. We define a hierarchical pointer analysis for determining which data a pointer can reference, as well as on which threads the referenced data may reside. We then present a series of analyses for computing the set of concurrent statements in both SPMD and RSPMD programs. We show that these analyses improve the results of multiple client analyses, including data-locality and sharing inference, race detection, and memory-model enforcement.

Finally, we present application case studies demonstrating the expressiveness and performance of the RSPMD model. We show that the model enables divide-and-conquer algorithms such as sorting to be elegantly expressed, and that team collective operations increase performance of a conjugate gradient benchmark by up to a factor of two. The model also facilitates optimizations for hierarchical machines, improving scalability of a particle in cell application by 8x, performance of sorting by up to 40%, and execution time of a stencil code by as much as 14%.

# Contents

| Co | ontents                                                                                                                                                                                             | i                                 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Li | ist of Figures                                                                                                                                                                                      | iii                               |

| Li | ist of Tables                                                                                                                                                                                       | vi                                |

| Li | ist of Acronyms                                                                                                                                                                                     | vii                               |

| 1  | Introduction         1.1 Thesis Contributions                                                                                                                                                       | 1<br>3                            |

| 2  | Background         2.1       The Single Program, Multiple Data Model         2.2       Titanium         2.3       The Partitioned Global Address Space Model         2.4       Collective Alignment | 5<br>9<br>10<br>11                |

| 3  | Language Extensions3.1 Design Goals3.2 Team Representation3.3 New Language Constructs3.4 Implementation                                                                                             | <b>13</b><br>13<br>14<br>17<br>21 |

| 4  | Alignment of Collectives4.1The Single Type System4.2Dynamic Alignment4.3Alignment of Team Collectives                                                                                               | <b>23</b><br>24<br>29<br>33       |

| 5  | Analysis Background5.1Machine Model5.2Pointer Analysis5.3Concurrency Analysis5.4Sequential Consistency                                                                                              | <b>36</b><br>36<br>37<br>40<br>41 |

|     | 5.5    | Analysis over Teams               | 44  |

|-----|--------|-----------------------------------|-----|

| 6   | Hier   | archical Pointer Analysis         | 47  |

|     | 6.1    | Language                          | 47  |

|     | 6.2    | Concrete Domain                   | 53  |

|     | 6.3    | Abstract Domain                   | 53  |

|     | 6.4    | Abstract Semantics                | 54  |

|     | 6.5    | Soundness                         | 57  |

|     | 6.6    | Algorithm                         | 59  |

|     | 6.7    | Locality Inference                | 60  |

|     | 6.8    | Implementation                    | 61  |

| 7   | Con    | currency Analysis                 | 63  |

|     | 7.1    | Flat Concurrency Analysis         | 63  |

|     | 7.2    | Hierarchical Concurrency Analysis | 73  |

| 8   | Eval   | luation                           | 87  |

|     | 8.1    | Application Case Studies          | 87  |

|     | 8.2    | Dynamic Alignment of Collectives  | 117 |

|     | 8.3    | Pointer Analysis                  | 122 |

|     | 8.4    | Combined Analyses                 | 126 |

| 9   | Rela   | ited Work                         | 132 |

|     | 9.1    | Hierarchical Computation          | 132 |

|     | 9.2    | Collective Alignment              | 134 |

|     | 9.3    | Pointer Analysis                  | 134 |

|     | 9.4    | Concurrency Analysis              | 135 |

|     | 9.5    | Race Detection                    |     |

|     | 9.6    | Sequential Consistency            | 135 |

| 10  | Con    | clusion                           | 137 |

| Bil | oliogi | raphy                             | 139 |

# **List of Figures**

| 1.1                                                                                      | Hierarchical arrangement of a single Cray XE6 compute node                                                                                                                                                    | 2                                |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.1<br>2.2<br>2.3                                                                        | Execution of an RSPMD program.                                                                                                                                                                                | 6<br>9<br>0                      |

| 3.1<br>3.2<br>3.3                                                                        | An example of a team hierarchy                                                                                                                                                                                | 5<br>6<br>8                      |

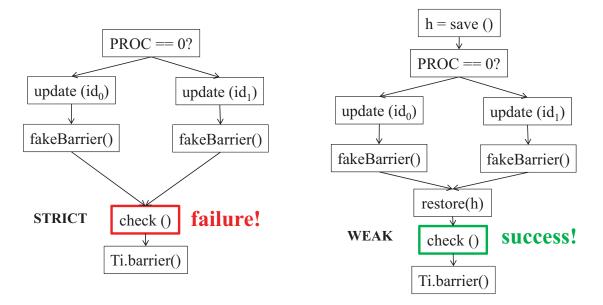

| 4.1                                                                                      | Difference in execution between strict and weak alignment                                                                                                                                                     | 31                               |

| 5.1<br>5.2<br>5.3<br>5.4                                                                 | Example of pointer width with respect to the machine hierarchy team                                                                                                                                           | 87<br>88<br>12<br>16             |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> | Type manipulating functions.4Type checking rules.5Dereferences may require width expansion.5The assignment $y \leftarrow z$ is forbidden.5                                                                    | 19<br>19<br>50<br>50<br>50<br>50 |

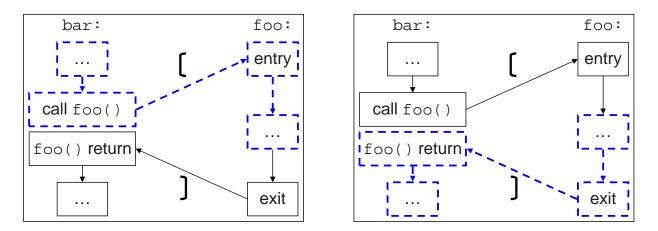

| 7.1<br>7.2<br>7.3<br>7.4                                                                 | Algorithm 7.1.3 computes the concurrency graph of a program                                                                                                                                                   | 54<br>56<br>56                   |

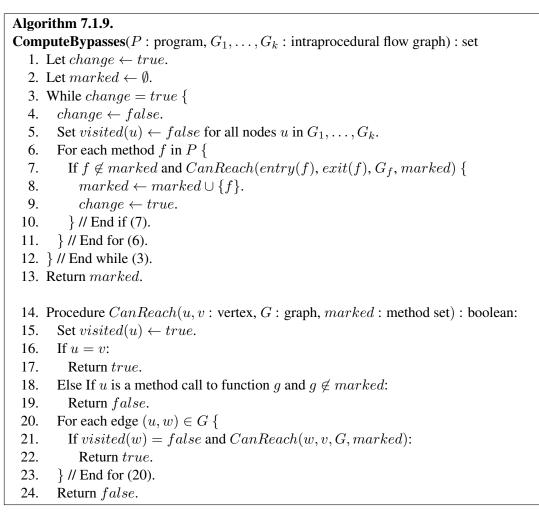

| 7.5<br>7.6<br>7.7                                                                        | Interprocedural control-flow graph for two calls to the same function. $\ldots \ldots \ldots$ | 58<br>58<br>59<br>71             |

| 7.8  | Algorithm 7.1.11 computes the set of nodes reachable from the start node through a feasible path.           | 72  |

|------|-------------------------------------------------------------------------------------------------------------|-----|

| 7.9  | Algorithm 7.1.13 computes the set of all concurrent expressions that can feasibly occur in a given program. | 74  |

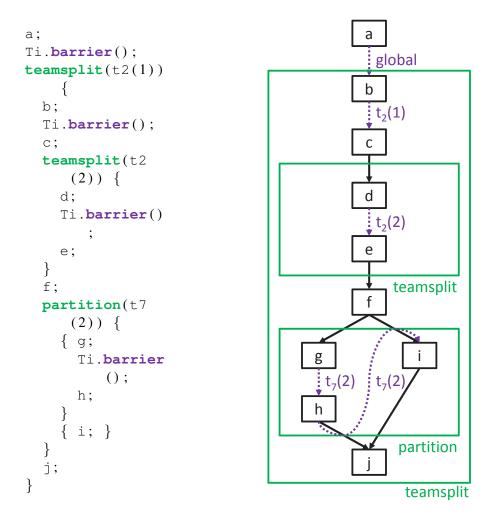

| 7.10 | Example of a concurrency graph.                                                                             | 75  |

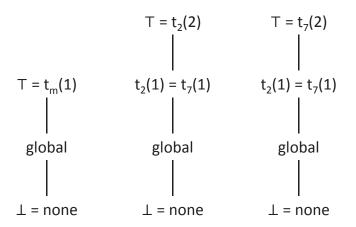

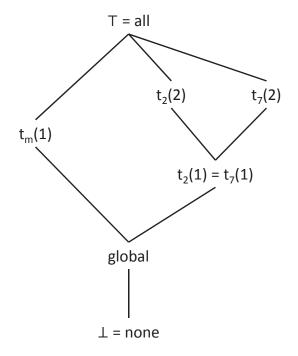

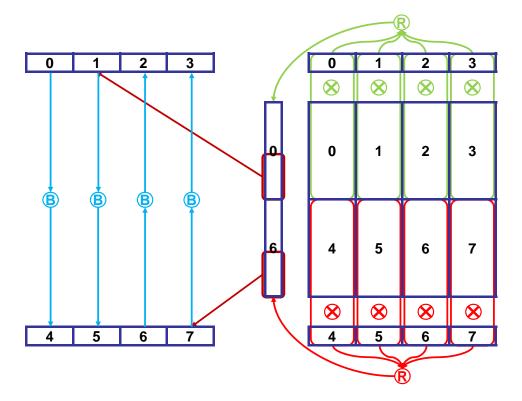

|      | Concurrency-analysis lattices corresponding to the teams in Figure 6.6.                                     | 78  |

|      | Possible hierarchical concurrency-analysis lattice corresponding to the teams in Figure                     |     |

|      | 6.6                                                                                                         | 79  |

| 7.13 | Algorithm 7.2.1 computes the concurrency graph of a program by inserting cross edges                        |     |

|      | into its control-flow graph and replacing barrier nodes with barrier edges                                  | 80  |

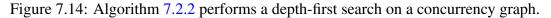

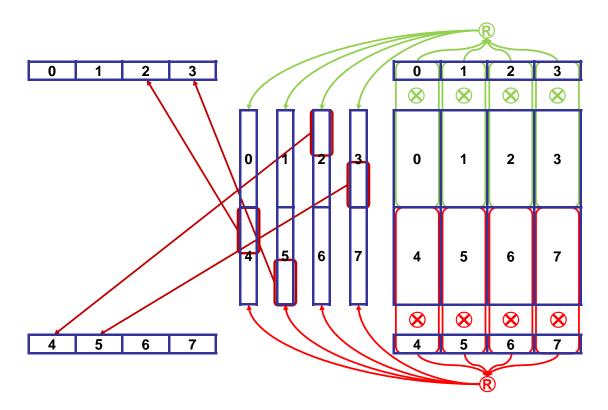

|      | Algorithm 7.2.2 performs a depth-first search on a concurrency graph                                        | 81  |

| 7.15 | Algorithm 7.2.4 uses each method's intraprocedural concurrency graph to determine                           |     |

|      | under which teams its exit is reachable from its entry                                                      | 83  |

| 7.16 | Algorithm 7.2.5 computes the set of teams under which each node is reachable from                           |     |

|      | the start node through a feasible path.                                                                     | 84  |

| 7.17 | Algorithm 7.2.7 computes the set of teams under which any pair of expressions can                           |     |

|      | feasibly and concurrently execute in a given program.                                                       | 86  |

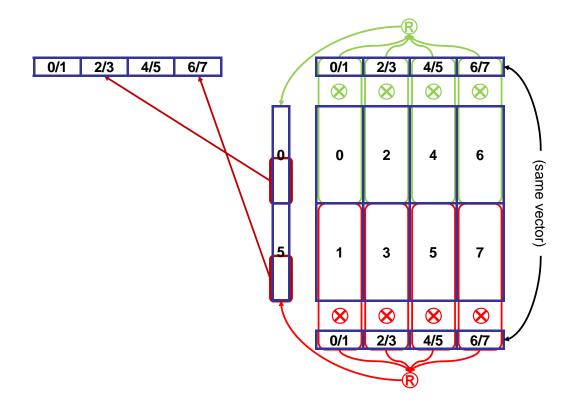

| 8.1  | A single iteration of matrix-vector multiplication in the original and row team versions                    |     |

|      | of CG                                                                                                       | 89  |

| 8.2  | A single iteration of matrix-vector multiplication in the column team version of CG.                        | 90  |

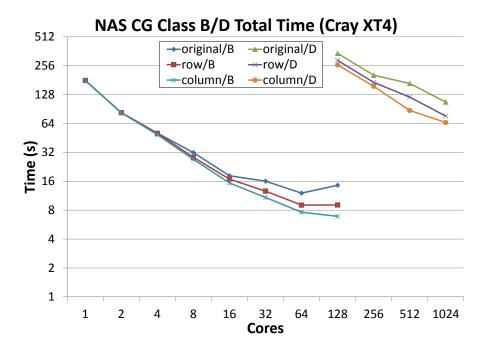

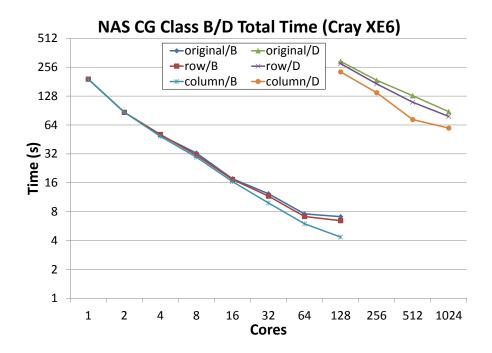

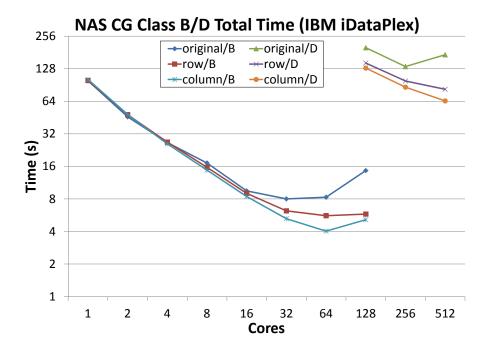

| 8.3  | Strong scaling performance of conjugate gradient on a Cray XT4.                                             | 92  |

| 8.4  | Strong scaling performance of conjugate gradient on a Cray XE6.                                             | 92  |

| 8.5  | Strong scaling performance of conjugate gradient on an IBM iDataPlex.                                       | 93  |

| 8.6  | A single iteration of matrix-vector multiplication in the shared-memory version of CG.                      | 94  |

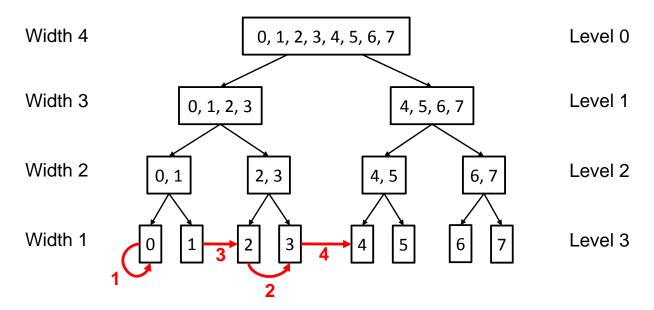

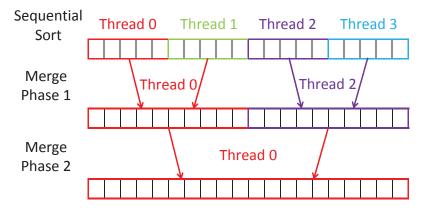

| 8.7  | Shared-memory sorting algorithm on four threads.                                                            | 96  |

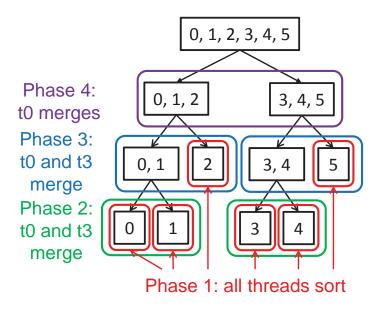

| 8.8  | Shared-memory team hierarchy and execution on six threads                                                   | 97  |

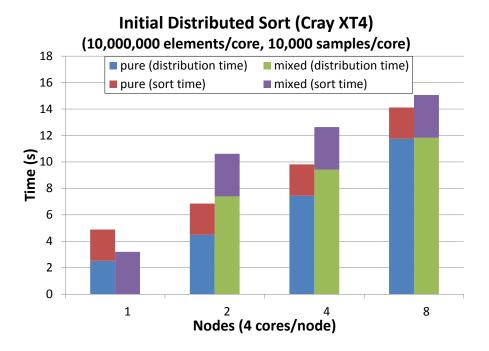

| 8.9  | Performance of initial distributed sort on a Cray XT4                                                       | 98  |

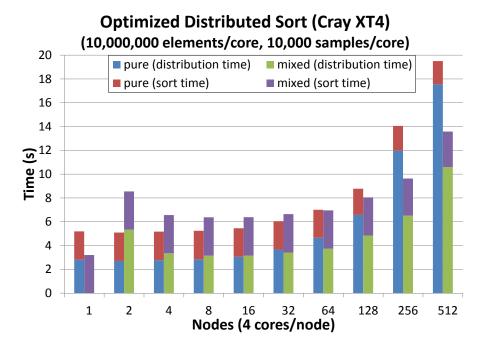

| 8.10 | Performance of optimized distributed sort on a Cray XT4                                                     | 99  |

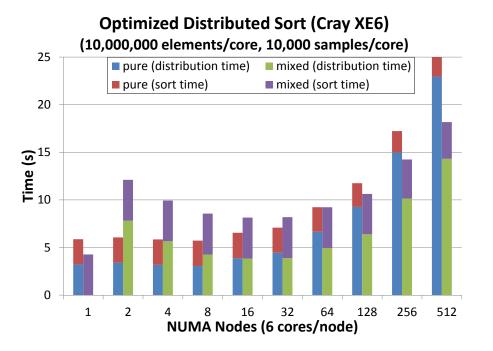

| 8.11 | Performance of optimized distributed sort on a Cray XE6                                                     | 100 |

| 8.12 | Performance of optimized distributed sort on an IBM iDataPlex                                               | 100 |

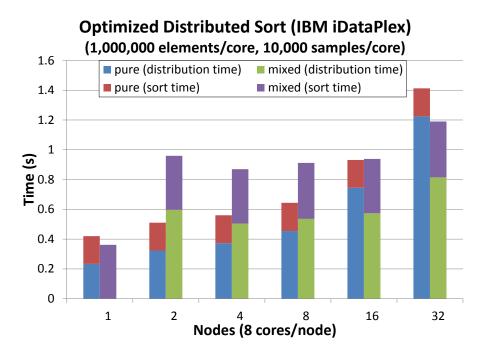

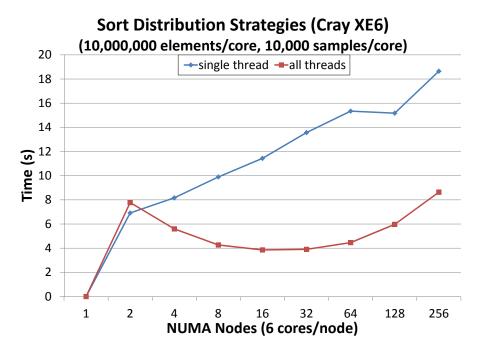

| 8.13 | Distribution time on a Cray XE6 when using a single thread per team for communica-                          |     |

|      | tion versus all threads in a team.                                                                          |     |

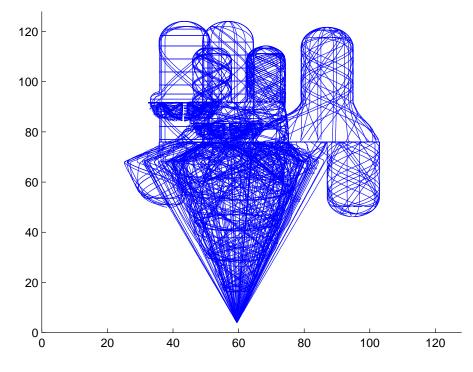

|      | Orthographic projection of the heart model.                                                                 |     |

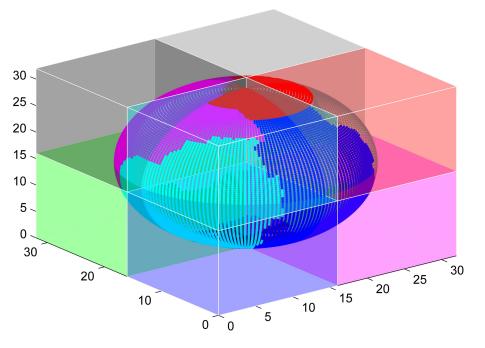

|      | Sample input sphere, distributed across eight threads                                                       |     |

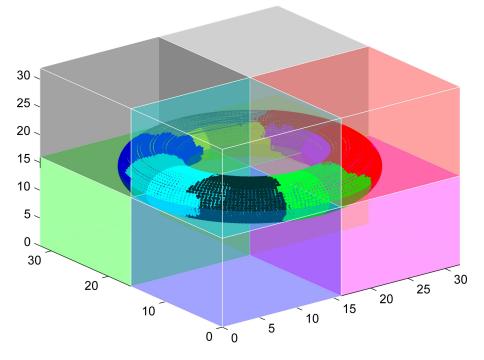

|      | Sample input torus, distributed across eight threads                                                        |     |

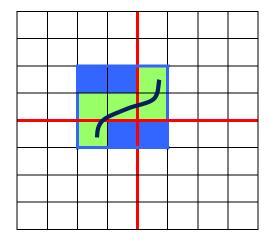

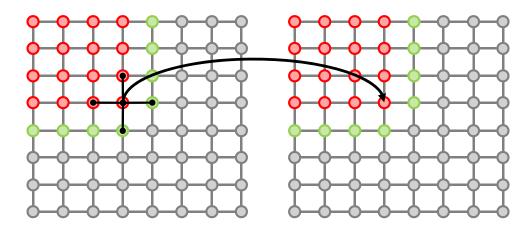

|      | Two-dimensional example of a bounding box containing all of a thread's particles                            | 105 |

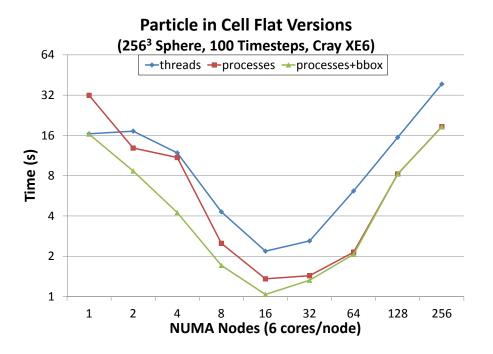

| 8.18 | Performance of flat particle in cell using shared-memory threads on a NUMA node                             |     |

| _    | versus processes that do not share memory.                                                                  |     |

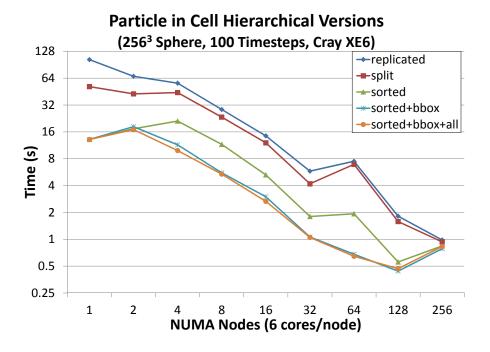

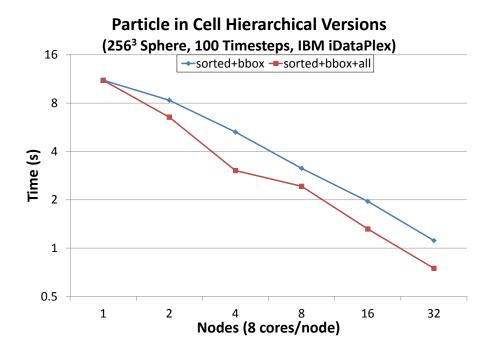

|      | Performance of various hierarchical particle in cell algorithms on a Cray XE6                               |     |

| 8.20 | Performance of various hierarchical particle in cell algorithms on an IBM iDataPlex.                        | 108 |

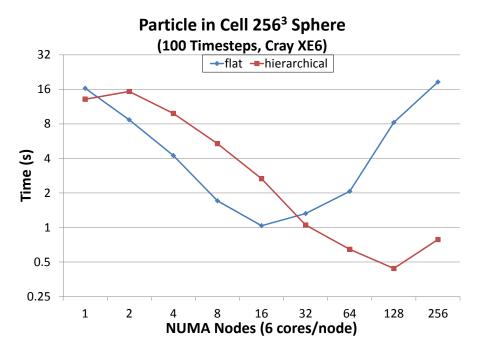

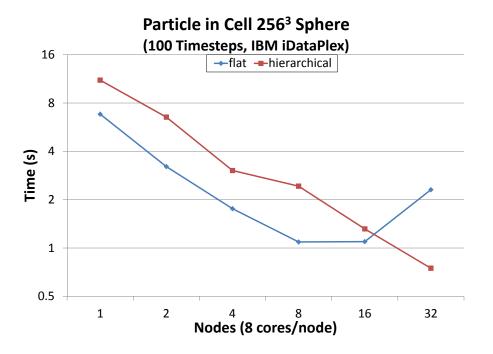

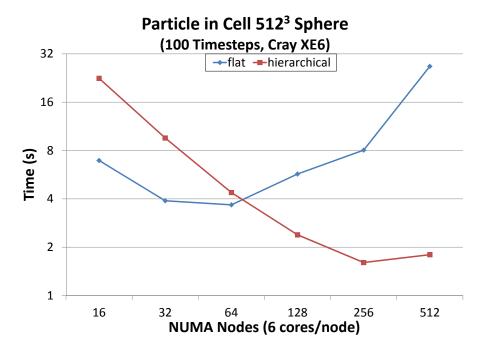

| 8.21 | Performance of a $256^3$ sphere on a Cray XE6 using the best hierarchical particle in cell algorithm versus the best flat algorithm. | 109   |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-------|

| 8 22 | Performance of a 256 <sup>3</sup> sphere on an IBM iDataPlex using the best hierarchical particle                                    | . 107 |

| 0.22 | in cell algorithm versus the best flat algorithm.                                                                                    | . 110 |

| 8.23 | Performance of a $512^3$ torus on a Cray XE6 using the best hierarchical particle in cell                                            |       |

|      | algorithm versus the best flat algorithm.                                                                                            | . 110 |

| 8.24 | Performance of a $512^3$ sphere on a Cray XE6 using the best hierarchical particle in cell                                           |       |

|      | algorithm versus the best flat algorithm.                                                                                            | . 111 |

| 8.25 | A five-point stencil in two dimensions.                                                                                              | . 112 |

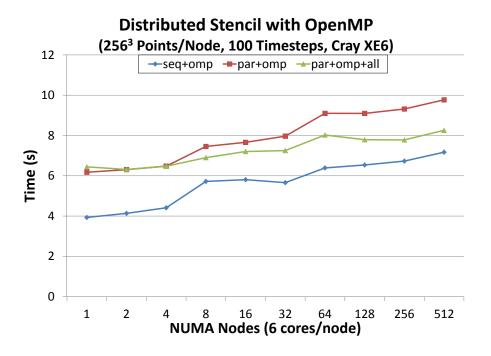

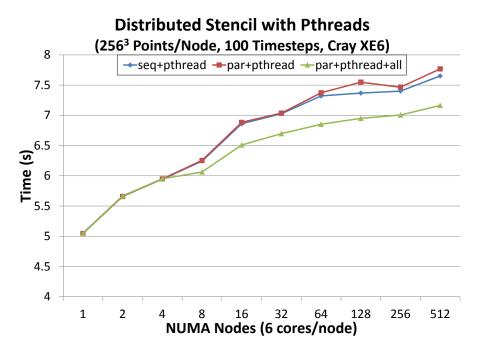

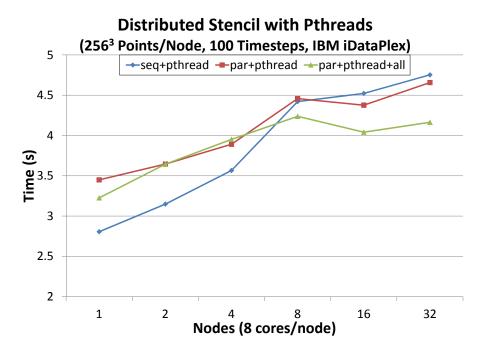

| 8.26 | Weak scaling performance of stencil on a Cray XE6 using OpenMP for shared-memory                                                     |       |

|      | parallelism.                                                                                                                         | . 114 |

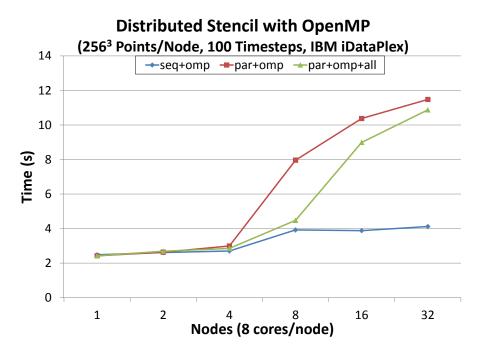

| 8.27 | Weak scaling performance of stencil on an IBM iDataPlex using OpenMP for shared-                                                     |       |

|      | memory parallelism.                                                                                                                  | . 115 |

| 8.28 | Weak scaling performance of stencil on a Cray XE6 using Pthreads for shared-memory                                                   |       |

|      | parallelism.                                                                                                                         | . 116 |

| 8.29 | Weak scaling performance of stencil on an IBM iDataPlex using Pthreads for shared-                                                   | 117   |

| 0.20 | memory parallelism.                                                                                                                  |       |

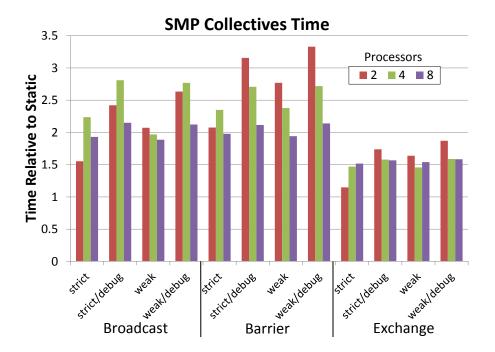

|      | Relative collective performance on the SMP machine.                                                                                  |       |

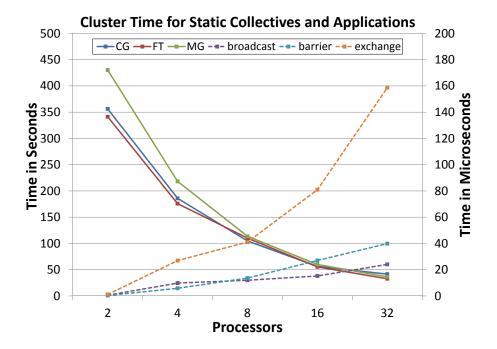

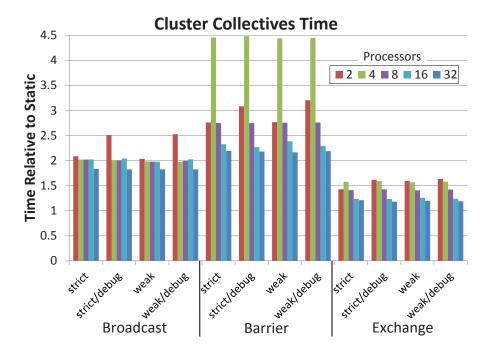

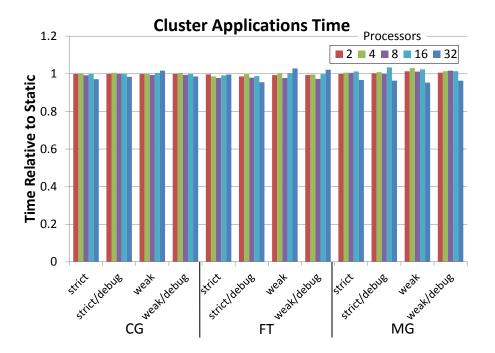

|      | Collective and application performance on the cluster machine in the static case                                                     |       |

|      | Relative collective performance on the cluster machine                                                                               |       |

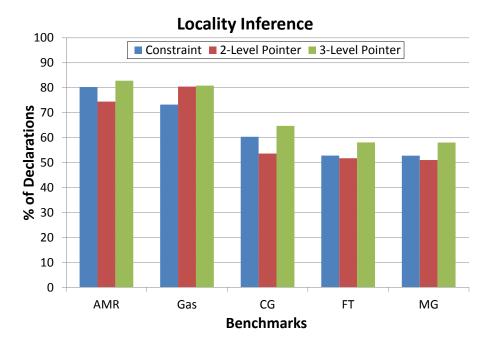

|      | Locality inference results for some Titanium programs.                                                                               |       |

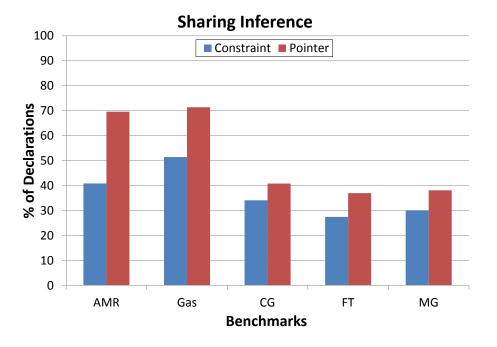

|      | Sharing inference results for some Titanium programs.                                                                                |       |

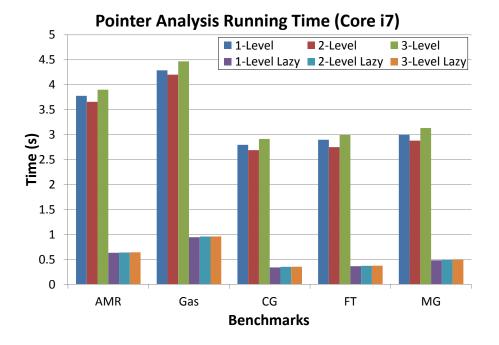

|      | Analysis running time results for some Titanium programs, using various levels of                                                    | . 127 |

| 0.50 | pointer analysis.                                                                                                                    | . 125 |

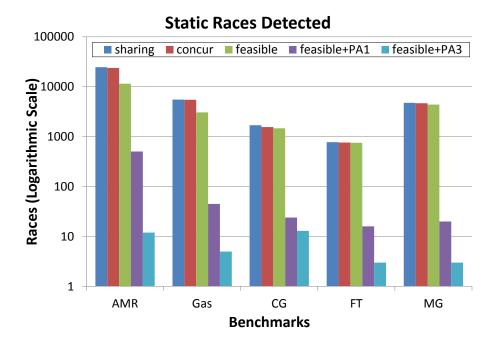

| 8.37 | Number of data races detected at compile-time.                                                                                       |       |

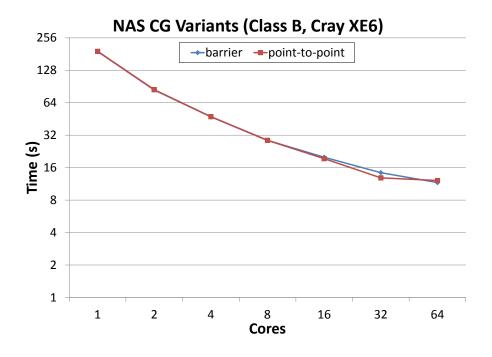

|      | Performance of barrier and point-to-point variants of CG on a Cray XE6                                                               |       |

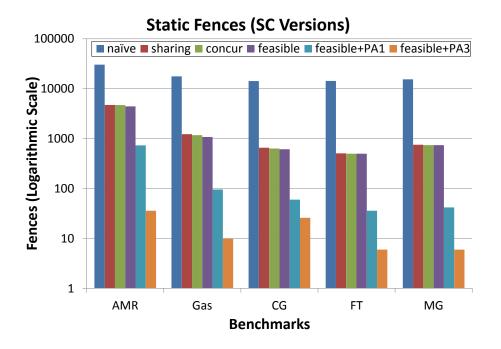

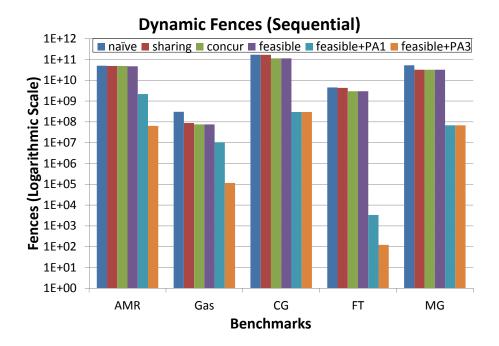

|      | Number of memory barriers generated at compile-time.                                                                                 |       |

|      | Average number of memory barriers executed at runtime.                                                                               |       |

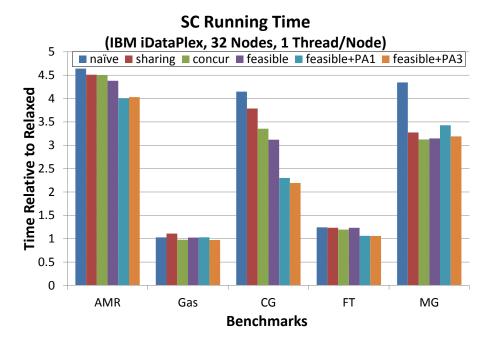

| 8.41 | Execution time on an IBM iDataPlex using 32 processors on 32 nodes, compared to a                                                    |       |

|      | relaxed-consistency version of the code.                                                                                             | . 130 |

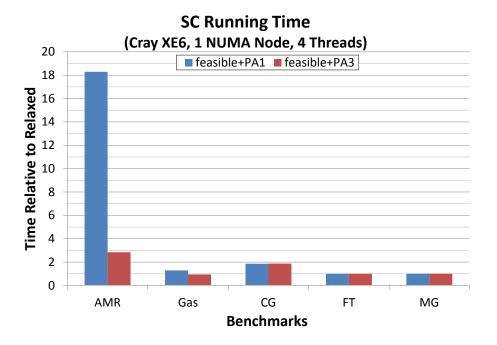

| 8.42 | Execution time on a Cray XE6 using four processors on a single NUMA node, com-                                                       |       |

|      | pared to a relaxed-consistency version of the code                                                                                   | . 131 |

|      |                                                                                                                                      |       |

# **List of Tables**

| 8.1 | Fluid size and number of particles for each particle in cell input. |   |  | 102 |

|-----|---------------------------------------------------------------------|---|--|-----|

| 8.2 | Time for alignment update and check operations on each machine      | • |  | 122 |

| 8.3 | Number of operations and calculated overhead for each benchmark     | • |  | 122 |

# **List of Acronyms**

| AMD   | Advanced Micro Devices                        |

|-------|-----------------------------------------------|

| AMR   | Adaptive mesh refinement                      |

| AST   | Abstract syntax tree                          |

| BSP   | Bulk synchronous parallel                     |

| CFL   | Context-free language                         |

| CG    | Conjugate gradient                            |

| DFS   | Depth-first search                            |

| FT    | Fourier transform                             |

| GHz   | Gigahertz                                     |

| HPCS  | High-productivity computing systems           |

| HPGAS | Hierarchical partitioned global address space |

| НРТ   | Hierarchical place trees                      |

| HSPMD | Hierarchical single program, multiple data    |

| HST   | Hierarchically well-separated tree            |

| НТА   | Hierarchically tiled arrays                   |

| IBM   | International Business Machines Corporation   |

| ID    | Identifier                                    |

| LQI   | Local qualification inference                 |

| MG    | Multigrid                                     |

| MIMD  | Multiple instruction, multiple data           |

|       |                                               |

| MPI               | Message Passing Interface                                                                                              |

|-------------------|------------------------------------------------------------------------------------------------------------------------|

| NAS               | NASA Advanced Supercomputing Division                                                                                  |

| NERSC             | National Energy Research Scientific Computing Center                                                                   |

| NUMA              | Non-uniform memory access                                                                                              |

| PGAS              | Partitioned global address space                                                                                       |

| POSIX             | Portable operating system interface                                                                                    |

| QDR               | Quad data rate                                                                                                         |

|                   |                                                                                                                        |

| RSPMD             | Recursive single program, multiple data                                                                                |

| SC                | Recursive single program, multiple data<br>Sequential consistency                                                      |

|                   |                                                                                                                        |

| SC                | Sequential consistency                                                                                                 |

| SC<br>SMP         | Sequential consistency<br>Symmetric multiprocessor, also shared-memory multiprocessor                                  |

| SC<br>SMP<br>SPMD | Sequential consistency<br>Symmetric multiprocessor, also shared-memory multiprocessor<br>Single program, multiple data |

#### Acknowledgments

I am grateful to Kathy Yelick for all her help over the last nine years. From the first time I worked with her as an undergraduate teaching assistant to the present, she has always been there to guide and encourage me. I would not have been able to finish without her patience and dedication.

I have spent nearly a decade in the Titanium group and am indebted to everyone who has worked on the project. Dan Bonachea and Jimmy Su have helped me in ways impossible to enumerate, and Paul Hilfinger has always provided valuable insight and feedback. I would also like to thank the members of the Berkeley UPC and GASNet teams, especially Rajesh Nishtala and Yili Zheng, for all their help.

The folks in the VLSI Research Group at Sun Labs were gracious hosts during my time there, particularly Ivan Sutherland and Igor Benko. They provided valuable support and guidance as I struggled to narrow down my dissertation topic. And my many office mates over the years have been a source of both inspiration and distraction as needed, Armando Solar-Lezama, Kaushik Datta, Gilad Arnold, Jimmy, and Rajesh foremost among them.

I would like to thank my friends for keeping me sane, especially Munir, Mahil, and Suhaib, and my family for all their love and support. I'm particularly grateful to Shoaib, whose comradeship on this journey was invaluable.

Finally, all praise is to God, without whom nothing is possible.

The work in this dissertation was supported in part by the Department of Energy under Contracts DE-FC03-01ER25509 and FDDE-FC02-07ER25799, by the National Science Foundation under CNS-0325873 and OCI-0749190, by the California State MICRO Program, and by gifts from Sun Microsystems. This research used resources of the National Energy Research Scientific Computing Center (NERSC), which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231.

# Chapter 1 Introduction

In the past few years, parallel computing has entered mainstream use following the introduction of multicore processors. Previously, computing performance was increased primarily through clock speed scaling, resulting in processors that could execute instructions faster. Unfortunately, this also increased power consumption, leading to problems with heat dissipation at high clock speeds. As raising clock speed could no longer be used to increase performance, vendors resorted to increasing the number of processing cores on each chip, allowing more instructions to complete in a given amount of time through parallel execution. Unlike clock speed scaling, which allows existing software to run faster, increasing parallelism requires programs to be rewritten to take advantage of concurrent execution.

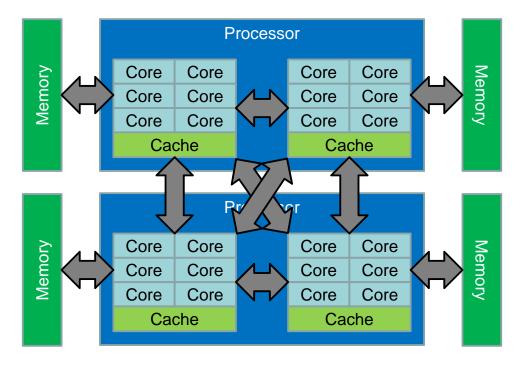

Parallel computing has long been used in scientific computing, where large problem sizes could not be solved on a single processor. As a result, many of the challenges faced in large-scale scientific computing are likely to be encountered in the future by mainstream parallel computing. One specific challenge is that of hierarchical machines. Large scale parallel machines are constructed in a hierarchical fashion, with multiple cores in a processor die, multiple processor dies on a single chip, multiple chips on the same mainboard, multiple boards in a server rack, and multiple server racks in a complete machine. For example, Figure 1.1 diagrams the hierarchical layout of a single compute node in a Cray XE6 machine. This hierarchical organization results in widely varying communication costs between different parts of a machine. Programmers must take into account these costs in order to obtain maximal performance.

Programming large-scale machines is done primarily through the single program, multiple data (SPMD) model. A SPMD program is launched with a fixed number of threads, typically one per core, that execute throughout the program. The SPMD model dominates programming at scale because it encourages "parallel thinking" throughout the program execution, exposing the actual degree of available parallelism. It's local view of execution also naturally leads to good locality and can be implemented by simple, low-overhead runtime systems. The model of communication between threads is orthogonal to choice of control, and both message passing models like the Message Passing Interface (MPI) library [73] and a number of partitioned global address space (PGAS) languages like Unified Parallel C (UPC) [19], Titanium [110], and Co-Array Fortran [77] use the SPMD model by default. Previous work has demonstrated the productivity and performance bene-

Figure 1.1: Hierarchical arrangement of a single Cray XE6 compute node.

fits of languages that combine SPMD and PGAS in general [109] and Titanium in particular [108].

One of the key features of the SPMD model is the ability to define *collective operations*, which are operations that are performed by all threads together. Collectives allow program synchronization and communication to be specified in a simple and elegant manner, making parallel bugs such as race conditions and deadlock less likely. They also allow global-view operations to be specified in a local-view context. Since all threads must participate in each collective, care must be taken to ensure that such operations are *aligned* on all threads to avoid dependencies between collectives. In the case of the Titanium language, alignment guarantees are provided at compile time but may alternatively be enforced at runtime [53]. Finally, collective operations impose a degree of structure on SPMD programs. The combination of this structure and the fact that all threads execute the same code makes SPMD code amenable to program analyses, enabling many optimizations and correctness tools [60, 65, 66, 52, 51, 54].

While SPMD has proven to be a valuable programming model, its restrictiveness does have drawbacks when it comes to implementing hierarchical algorithms on hierarchical machines. Algorithms that divide tasks among threads or that recursively subdivide do not fit well into a model with a fixed number of threads executing the same code. SPMD programming languages also tend to have a relatively flat machine model, with no distinction between threads that are located nearby on a large-scale machine and threads that are further apart. This lack of awareness of the underlying machine hierarchy results in communication costs that are not transparent to the programmer.

In this dissertation, we address the above shortcomings by introducing the recursive single

#### CHAPTER 1. INTRODUCTION

program, multiple data (RSPMD) model, an extension of the SPMD model with user-defined hierarchical *teams*, subsets of threads that cooperatively execute pieces of code. We demonstrate that this model enables productive programming, provides good performance, eliminates entire classes of parallel bugs, and allows precise compiler analysis.

In order to realize the RSPMD model in the context of the Titanium programming language, we introduce a data structure to represent teams, library functions to facilitate team creation, and language constructs that operate on teams. We demonstrate how to ensure textual alignment of collectives, eliminating many forms of deadlock involving teams. We describe multiple program analyses on RSPMD programs including pointer and concurrency analysis.

We evaluate the RSPMD model through case studies on multiple applications. We demonstrate that hierarchical teams are useful for expressing computations that naturally subdivide, without having to create and destroy logical threads, retaining the advantages of parallel thinking. We also show that hierarchical teams can be used to optimize for the varying communication characteristics of modern, hierarchical parallel machines, achieving significant performance improvements over the flat SPMD model. Finally, we show that dynamic checking ensures alignment of collectives with little performance overhead, and we demonstrate that our program analyses produce useful results for locality and data sharing inference, race detection, and sequential consistency.

## **1.1 Thesis Contributions**

The main contributions of this dissertation are as follows:

- We extend the SPMD model of parallelism to support hierarchical computation, resulting in the RSPMD model. We introduce a powerful library for expressing team hierarchies and language constructs for operating over teams. We show that the design of this team mechanism prevents deadlock that may occur in non-hierarchical schemes for grouping threads, and we implement it in the Titanium language.

- We demonstrate how to enforce textual alignment of collectives using runtime checks, eliminating a major class of bugs in parallel programming. We show how to guarantee alignment in programs written with both the flat SPMD model and the hierarchical RSPMD model. We provide experimental evidence that there is low runtime overhead in checking collective alignment.

- We develop a pointer analysis for programs that use the RSPMD execution model and the hierarchical partitioned global address space (HPGAS) memory model. We show that this analysis improves data locality and sharing inference over constraint-based analyses.

- We develop an efficient analysis for determining the set of potentially concurrent statements in SPMD and RSPMD programs.

- We write a race detector using our pointer and concurrency analyses, proving that they improve precision and significantly reduce false positives.

#### CHAPTER 1. INTRODUCTION

- We implement a version of the Titanium compiler that provides a sequentially-consistent memory model, using the pointer and concurrency analyses to minimize the runtime cost of doing so. We demonstrate that applications compiled in such a model can achieve performance that is close to that of a relaxed memory model.

- We implement a set of benchmarks using the RSPMD model and its Titanium implementation. We show that the model enables divide-and-conquer algorithms such as sorting to be expressed elegantly. We demonstrate that team collectives provide better performance and productivity than hand-written communication in a conjugate gradient application. We use RSPMD constructs to perform optimizations for hierarchical machines on sorting, particle in cell, and stencil benchmarks. We show that these optimizations improve scalability of particle in cell and performance of sorting and stencil on multiple contemporary platforms.

# Chapter 2

# Background

In this chapter, we describe the basic language features that we build upon in this dissertation. We start by reviewing the single program, multiple data (SPMD) model of parallelism, one of the most common models used on large-scale machines and the basis for the recursive single program, multiple data (RSPMD) model that we introduce. We then provide a brief overview of the Titanium language that is the vehicle for our work, as well as the partitioned global address space (PGAS) memory model that it uses. Finally, we discuss alignment of collective operations, an important aspect of correctness of large-scale parallel codes.

## 2.1 The Single Program, Multiple Data Model

The single program, multiple data (SPMD) model of parallelism consists of a set of parallel threads that run the same program. Unlike in dynamic task parallelism, the set of threads is fixed throughout the entire program execution. The threads can be executing at different points of the program, though *collective operations* such as barriers can synchronize the processes at a particular point in the program.

As an example of SPMD code, consider the following written in the Titanium language:

```

public static void main(String[] args) {

System.out.println("Hello from thread " + Ti.thisProc());

Ti.barrier();

if (Ti.thisProc() == 0)

System.out.println("Done.");

}

```

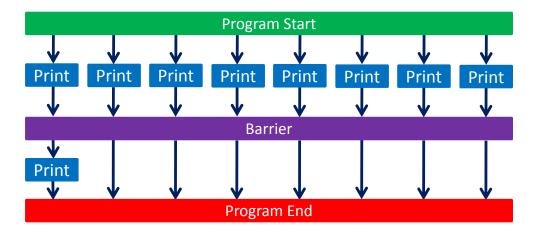

A fixed number of threads, specified by the user on program start, all enter main(). They first print out a message with their thread IDs, or *ranks*, which are unique integers in the range 0 to the number of threads minus one. These messages can appear to the user in any order, since the print statement is not synchronized. Then the threads execute a *barrier*, which prevents them from proceeding until all threads have reached it. Finally, thread 0 prints out another message

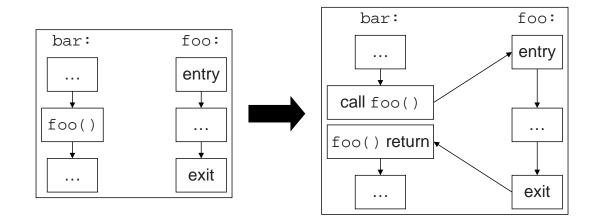

Figure 2.1: Execution of a SPMD program.

that appears to the user after all previous messages due to the barrier synchronization. Figure 2.1 illustrates the execution of this code on eight threads.

Like task-parallel but unlike data-parallel programs, SPMD programs have a *local view* of execution, meaning that each thread is explicitly assigned work. Data parallelism, on the other hand, provides a *global view*, in which there is a single logical thread of control, and the compiler is responsible for distributing work across computational units. In SPMD, collective operations such as a one-to-all *broadcast* or an all-to-all *exchange* provide simple global-view operations in the context of a local-view model and can be used to build larger, more complicated global-view operations.

The set of SPMD languages includes Unified Parallel C (UPC) [19], Co-Array Fortran [77], and Titanium [110]. In addition, though the MPI library [73] supports arbitrary task-parallel code, most MPI programs are written in a SPMD<sup>1</sup> manner, since the added structure of this programming style simplifies the job of the programmer.

SPMD languages occupy a middle ground between task and data parallelism; they are more structured and therefore easier to program and more analyzable than task-parallel languages, but are more flexible than data-parallel languages, allowing expression of irregular applications that is difficult in the data parallel model. Programmer control over work decomposition also generally leads to better performance than the automated decomposition in data parallelism. The following summarizes the advantages of SPMD in more detail:

• Locality. Data locality is essential to achieving good performance on large-scale machines, where communication across the network is very expensive compared to computation and local-memory access. Since SPMD has a local view of execution, it allows programmers to write code that concentrates computation on local data and minimizes communication between threads.

<sup>&</sup>lt;sup>1</sup>SPMD is usually pronounced as "spimdee", so we precede it with the indefinite article "a".

- **Structured parallelism.** The set of threads is fixed throughout computation, exposing the exact degree of parallelism to the programmer. The fact that all threads execute the same program makes it easier to reason about parallel behavior. Global synchronization operations allow programs to be divided into communication and computation phases, reducing the possibility of race conditions, deadlock, and other parallel bugs that are common in the task parallel model. These same features also make it easier for compilers to reason about SPMD code, resulting in more efficient and precise program analyses than in other models.

- Simple runtime implementation. Since SPMD has a local view of execution and parallelism is exposed directly to the user, compilers and runtime systems require much less effort to implement than with data parallelism. The latter can require complicated compiler analysis and runtime mechanisms for data distribution and load balancing. In SPMD, these tasks are handled by the programmer.

- Global operations. Basic collective operations facilitate global synchronization and communication. More complicated global view operations can also be built using the basic collectives, allowing the tasks of data distribution and load balancing to be offloaded to a library, replicating the productivity benefits of data-parallel languages. For example, a distributed matrix library can provide global interfaces for constructing distributed matrices as well as operating over them. These interfaces would appear to the programmer like any other global operations and would be just as easy to use.

As a result of these advantages, large-scale machines are predominantly programmed using a pure SPMD model, combinations of multiple SMPD components, or combinations of SPMD and shared-memory components.

On the other hand, SPMD in its current form does suffer from some drawbacks. The flat model of parallelism, with only global collective operations, makes it difficult to write hierarchical code. This includes codes with application-level hierarchy, such as divide-and-conquer algorithms, as well as programs optimized for hierarchical machines. For the latter, common practice is to write SPMD code for the distributed portion of a machine and then to use a shared-memory parallel library such as OpenMP [80] for the shared-memory part of a machine. Such a strategy does not take full advantage of a machine, since only a single thread in each shared-memory domain is used for communication. In §8.1, we show that better performance can be obtained in many cases by using multiple threads for communication.

As an example of application-level hierarchy, consider a merge sort written in a task parallel manner.

```

1 int[] mergeSort(int[] data) {

2 int len = data.length;

3 if (len < threshold) {

4 return sequentialSort(data);

5 }

6 d1 = fork mergeSort(data[0:len/2-1]);

7 d2 = mergeSort(data[len/2:len-1]);

</pre>

```

#### CHAPTER 2. BACKGROUND

```

8 join d1;

9 return merge(d1, d2);

10 }

```

The code starts with a single thread and then forks off another thread in each divide step, until the data size reaches a threshold where the overhead of using more threads is greater than the gain from any extra parallelism. The join operation in line 8 waits for the sort to be completed on the forked thread before performing each merge step.

Since SPMD does not allow dynamic creation of new threads, the merge sort algorithm needs to be rewritten to make use of the existing set of threads. This can be done as follows.

```

1 int[] mergeSort(int[] data, int[] threadIds) {

int len = data.length;

2

int numThreads = threadIds.length;

3

4

if (numThreads == 1) {

return sequentialSort(data);

5

}

6

if (threadIds[0:numThreads/2-1].contains(myId)) {

7

d1 = mergeSort(data[0:len/2-1], threadIds[0:numThreads/2-1]);

8

9

} else {

d2 = mergeSort(data[len/2:len-1],

10

threadIds[numThreads/2:numThreads-1]);

11

}

12

barrier(threadIds);

13

if (myId == threadIds[0]) {

14

return merge(d1, d2);

15

}

16

17 }

```

Here, the code starts with all threads, repeatedly dividing the data and set of threads in half until only one thread remains. Each thread sequentially sorts its data, after which threads recombine to perform the merge step, until all threads reach the top level. The barrier in line 13 performs the same function as the join in the task parallel algorithm, waiting for all relevant threads to finish sorting before the merge operation can occur. Unlike in flat SPMD, however, it should act only on a subset of threads, not all the threads in the program. We refer to such subsets of threads as *teams*. Teams are represented by arrays of thread IDs above; in  $\S3.2$ , we define a more complex data structure for teams.

Another common example of application-level hierarchy is to divide the initial set of threads among multiple distinct tasks. For example, a climate modeling code may use separate threads to model the ocean, land, and the atmosphere. Each such task may be written independently, requiring them to be composed in a single application. This composition is difficult in flat SPMD, and thread teams can be used to facilitate the process.

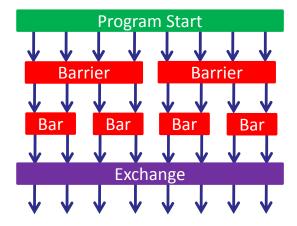

Despite the fact that teams are represented by flat vectors in the merge sort algorithm above, there is a hierarchical relationship between teams: starting from the global team, each team is recursively subdivided into two smaller teams. We thus define the recursive single program, multiple

Figure 2.2: Execution of an RSPMD program.

data (RSPMD) model of parallelism as an extension of SPMD that provides hierarchical teams. Figure 2.2 illustrates the execution of an RSPMD program.

In this thesis, we extend the Titanium language to support the RSPMD execution model. Other languages such as UPC are moving towards an execution model based on teams [5], and the GAS-Net [17] runtime layer used in Titanium now has experimental support for teams and team collectives. Unlike the teams in our work, teams in both UPC and GASNet are non-hierarchical groupings of threads. As we demonstrate throughout this thesis, hierarchical teams provide safety and analyzability advantages over flat teams.

## 2.2 Titanium

The work in this thesis is done in the context of the Titanium language [110]. Titanium is an explicitly parallel dialect of Java that uses the SPMD model of parallelism and the PGAS memory model described in §2.3. In addition, it provides language features for parallel and scientific programming. These include multidimensional arrays and index spaces, immutable classes, region-based memory allocation [2, 40], C++-style templates, operator overloading, and barrier synchronization. In this report, we discuss only those features that are relevant to our analyses.

The Titanium compiler does not use the Java Virtual Machine model. Instead, the end target is assembly code. For portability, Titanium is first translated into C and then compiled into an executable. In addition to generating C code to run on each processor, the compiler generates calls to a runtime layer based on GASNet [17], a lightweight communication layer that exploits hardware support for direct remote reads and writes when possible. Titanium runs on a wide range of platforms including uniprocessors, shared-memory machines, distributed-memory clusters of uniprocessors or SMPs, and a number of historical supercomputer architectures.

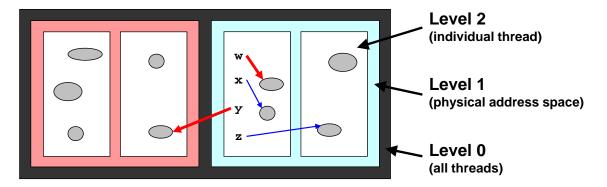

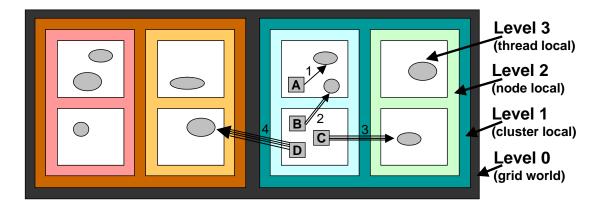

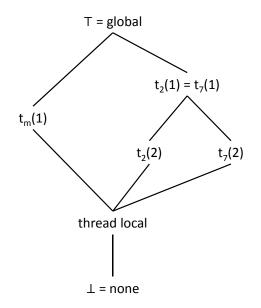

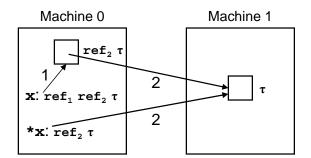

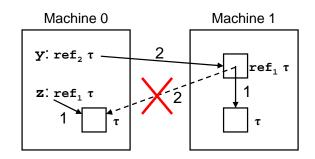

Figure 2.3: The Titanium thread hierarchy. The thin, blue arrows signify node-local and thread-local pointers, while the thick, red arrows designate global pointers. Global pointers may point to local data. Levels are numbered by increasing degree of locality.

## 2.3 The Partitioned Global Address Space Model

The SPMD execution model specifies the mechanism of *control* in a parallel program; the mechanism of *communication* is orthogonal to that of control. One important communication mechanism is the *partitioned global address space* (PGAS) model, which allows any thread to directly access memory on other threads. At runtime, two threads may share the same physical address space, in which case such an access is done directly using load and store instructions, or they may be in distinct address spaces, in which case the global access must be translated into communication using a library such as GASNet.

As an example, consider the following Titanium code:

```

int[] local mydata = { ... };

int[] data0 = broadcast mydata from 0;

for (int i = 0; i < data0.length; i++)

... data0[i] ...

```

In this code, each thread creates an integer array in its own memory space. Thread 0 then broadcasts a pointer to its array to the other threads, which can then access elements of thread 0's array, albeit with a possible performance penalty.

As can be seen in the example above, PGAS languages expose some degree of memory hierarchy to the programmer by virtue of the partitioned address space. In Titanium, pointers can be *thread local*, corresponding to level 2 in Figure 2.3, *node local*, corresponding to level 1, or *global*, corresponding to level 0. Thread-local pointers can only address data on the same thread<sup>2</sup>, node-local pointers can only reference data in the same physical address space, and global pointers can point to any object in the program. By default, pointers in Titanium are global, and the **local** qualifier specifies that a pointer is node local. There is no specific qualifier for thread-local point-

<sup>&</sup>lt;sup>2</sup>Thread-local pointers in Titanium are actually only used by program analysis and are not exposed in the type system.

#### CHAPTER 2. BACKGROUND

ers, though pointers qualified by the **nonshared** keyword are guaranteed to be thread local. Other PGAS languages such as UPC only have two levels of hierarchy.

The hierarchical partitioned global address space model (HPGAS) is an extension of PGAS to an arbitrary machine structure with an arbitrary number of levels. It can be used to represent the memory hierarchy on a single thread, as well as hierarchical network communication costs. Previously, we used the HPGAS model to construct a pointer analysis for Titanium [54]. In §6, we extend the pointer analysis to work on hierarchical teams.

Instead of a partitioned global address space, a unified global address space can be provided to the programmer. Such a memory model, however, does not expose any locality to the user. A global pointer in the PGAS model provides a hint to the programmer that communication may be required; a unified model would not provide such a hint, making performance more opaque to the user. This in turn could make it more difficult to write code that performs well.

Another alternative to PGAS is message passing, in which communication is done by exchanging messages between threads, as is used in the Message Passing Interface (MPI) [73]. Both sender and receiver explicitly participate in communication, requiring significant programmer effort to align the two participants and avoid deadlock. The PGAS model, on the other hand, requires the explicit participation of only the initiator of communication, and thus is simpler to program than message passing.

Previous work has shown that PGAS languages in general [109] and Titanium specifically [108] provide an excellent combination of application performance and programmer productivity, justifying our decision to pursue hierarchical extensions to parallel programming in the context of the Titanium language.

#### 2.4 Collective Alignment

One of the key features of the Titanium language is that it guarantees proper usage of collective operations through textual alignment. Collectives are *textually aligned* if all threads execute the same textual sequence of collective operations, and they agree on all control-flow decisions that affect execution of collectives. For example, the code below violates textual alignment, since different threads take different branches; not only do they not agree on control flow affecting collectives, they reach different textual instances of a collective.

```

if (Ti.thisProc() % 2 == 0) // even threads

Ti.barrier();

else // odd threads

Ti.barrier();

```

Discussions with parallel application experts indicate that most applications do not contain unaligned collectives, and most of those that do can be modified to do without them. Our own survey of eight NAS Parallel Benchmarks [9] using MPI demonstrated that all of their collectives are textually aligned.

Misalignment of collectives can result in deadlock, such as in the following code:

```

1 if (Ti.thisProc() % 2 == 0) // even threads

2 Ti.barrier();

3 else // odd threads

4 y = broadcast x from 0;

```

In this code, threads with even ID wait at the barrier in line 2, while threads with odd ID wait at the broadcast in line 4. Neither operation can complete until all threads have reached it, resulting in deadlock. While this example may be contrived, more complicated cases can occur in practice with much more subtle errors.

Titanium's type system statically ensures that global collective operations are textually aligned by making use of *single-valued* expressions that are semantically the same on all threads [1]. We describe this type system in detail in §4. Unfortunately, the type system requires significant programmer burden and is difficult to extend to collectives over teams. Instead, we introduce in §4 a dynamic scheme that guarantees textual alignment at runtime.

# Chapter 3

# **Language Extensions**

The recursive single program, multiple data (RSPMD) model of parallelism consists of a fixed set of cooperating threads that can be recursively subdivided into smaller groups of threads. In this chapter, we define language extensions for Titanium to implement the RSPMD model. We start be discussing the primary design goals for the language extensions. We then present new data structures and language constructs for RSPMD. Lastly, we provide an overview of how the extensions are implemented in the Titanium compiler and runtime.

## 3.1 Design Goals

In designing the new additions to the Titanium language, we had a few goals in mind for the extensions to satisfy: safety, flexibility, composability, support for collectives, performance, and analyzability.

1. **Safety.** Team implementations in other SMPD languages and frameworks do not generally impose any restrictions on their use. This can lead to circular dependencies in team operations, resulting in deadlock. For example, a set of threads may attempt to perform a collective operation on one team, while other threads attempt to perform a collective operation on a different team; if the two teams overlap, then this situation results in deadlock. The following code illustrates this problem:

```

1 Team t1 = new Team(0:7);

2 Team t2 = new Team(0:3);

3 if (myId == 0) {

4    barrier(t1);

5 } else {

6    barrier(t2);

7 }

```

In this code, barrier(t) executes a barrier operation over team t. Since threads 0 through 3 are in both t1 and t2, thread 0 waits for threads 1 through 3 to arrive at the barrier in line 4, while they in turn wait for thread 1 to arrive at the barrier in line 6. Deadlock is the result.

While the problem is easy to spot in the code above, more complicated examples can be constructed that contain less obvious circular dependencies. The Titanium team extensions should prevent such dependencies, as well as ensure that team collectives are textually aligned on all threads in the relevant team, as is done for existing global collectives.

- 2. Flexibility. A trivial solution to the safety problem would be to restrict each thread to be a member of a single, fixed team throughout program execution, preventing circular dependencies between teams. However, many applications make use of different thread groupings at different points in the program, such as a matrix-vector multiplication that requires both row and column teams. The team mechanism should be flexible enough to support such cases while still providing safety guarantees.

- 3. **Composability.** Existing code running in the context of a particular team should behave as if the entire world consisted of just the threads in that team, with thread ranks as specified by the team. This is to facilitate composition of different tasks, so that a subset of threads can be assigned to each of them. At the same time, the team mechanism should make it possible to interact with threads outside of an assigned team if necessary.

- 4. **Support for collectives.** One of the key features of the SPMD programming model is the ability of threads to communicate and synchronize through collective operations, such as reductions and barriers. Without support for collective operations over teams, users would have to hand-write their own implementations, requiring extensive development time and resulting in suboptimal performance. We describe such an example in §8.1.2.

- 5. **Performance.** Team operations should not adversely affect application performance. This requires that team usage operations, which may be invoked many times throughout an application run, be as lightweight as possible, even at the expense of team creation operations that are called much less frequently.

- 6. Analyzability. The structure of SPMD code makes it more amenable to analysis than other models of parallelism, enabling optimizations and correctness tools that take advantage of analysis results. RSPMD code should similarly be easy to analyze, and the team extensions should avoid making it harder to reason about RSPMD programs.

## 3.2 Team Representation

In order to represent a team hierarchy, we introduce a new Team object, as shown in Figure 3.1. A Team represents a group of threads and contains references to parent and child teams, resulting in a hierarchy of teams. Like MPI or GASNet groups, Team objects specify team structures separately from their usage; this is useful when a program uses multiple different team structures or repeatedly

```

public class Team {

/** Create team with all threads in currently executing team. */

public Team();

/** Returns the ith child of this team. */

public Team child(int i);

/** Number of child teams. */

public int numChildren();

/** Rank of this team in its parent. */

public int teamRank();

/** Number of threads in this team. */

public int size();

/** The child team containing the calling thread. */

public Team myChildTeam();

/** Split team into n equally-sized subteams, with threads retaining

*

relative ranks. */

public void splitTeam(int n);

/** Split team into n child teams, with threads assigned to subteams

* in block cyclic order. */

public void splitTeamBlockCyclic(int n, int sz);

/** Split team into the given subteams, with ranks specified

relative to this team. */

*

public void splitTeamRelative(int[][] teams);

/** Collective split operation. Assigns threads to subteams

according to color and the given rank relative to other threads.

*

*/

public single void splitTeamAll(int color, int relrank);

/** Collective split operation. Divides threads into subteams of

* threads that share memory, with the given relative rank. */

public single void splitTeamSharedMem(int rel);

/** Collective operation. Constructs a new team in which each

* subteam consists of a single thread from each subteam of this

team. */

*

public single Team single makeTransposeTeam();

/** Initialize runtime structures required by this team and run

* consistency checks. */

public single void initialize(boolean check);

}

```

Figure 3.1: Relevant functions from the Titanium Team class.

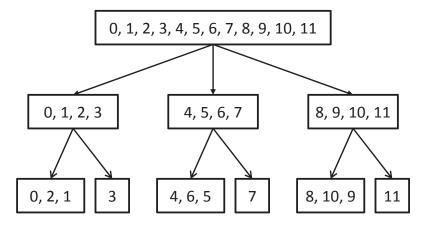

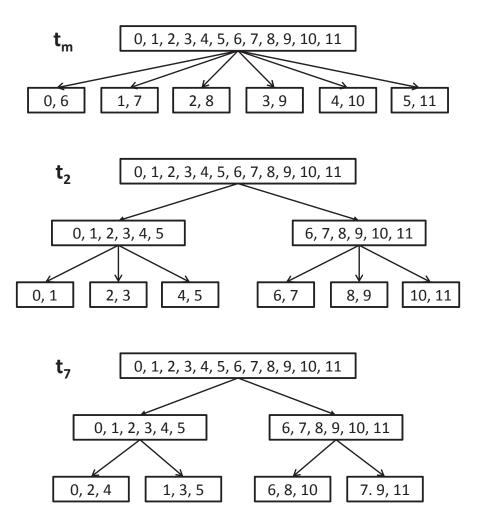

Figure 3.2: An example of a team hierarchy.

uses the same structure, as in  $\S$ 8.1.2, and also allows team data structures to be manipulated as firstclass objects.

Knowledge of the physical layout of threads in a program allows a programmer to minimize communication costs, so a new method Ti.defaultTeam() returns a special team that corresponds to the mapping of threads to the machine hierarchy. Currently, it merely divides threads into groups that share memory, though future use of the *hwloc* library [84] can provide a more representative layout. The invocation Ti.currentTeam() returns the current team in which the calling thread is participating.

Figure 3.2 shows the team hierarchy created by the following code, when there are a total of twelve threads:

```

Team t = new Team();

t.splitTeam(3);

int[][] ids = new int[][] {{0, 2, 1}, {3}};

for (int i = 0; i < t.numChildren(); i++)

t.child(i).splitTeamRelative(ids);

```

Each box in the diagram corresponds to a node in the team tree, and the entries in each box refer to member threads by their global ranks.

The code above first creates a team consisting of all the threads and then calls the **splitTeam** function to divide it into three equally-sized subteams of four threads each. It then divides each of those subteams into two uneven, smaller teams. The **splitTeamRelative** call divides a team into subteams using IDs relative to the parent team. In this case, each child u of team t is split into two smaller teams, with threads 0, 2, and 1 of u assigned to the first subteam and thread 3 of u assigned to the second. This behavior allows the same code to be used to divide each of the three children of t, which would not be the case if **splitTeamRelative** used global IDs.

The Team class provides a few other ways of generating subteams, as shown in Figure 3.1. In addition, it includes numerous functions to query team properties, a sample of which are also

shown in Figure 3.1. For example, the teamRank() function returns the rank of a team in its parent, which can be used to write code that is conditional on a team's rank.

Once a team has been created, the programmer must call the initialize method before using the team in the constructs introduced below. It is a collective operation that performs the runtime setup needed by a team and checks team consistency across threads. In our current implementation, this initialization is separate from team creation, allowing a user to construct a team on a single thread and then broadcast it to the others. Those threads then must create local copies since Team objects contain thread-specific state. So far, we have not found this to be a useful feature, and we may remove this functionality in order to combine team creation and initialization.

## **3.3** New Language Constructs

In designing new language constructs that make use of teams, we identified two common usage patterns for grouping threads: sets of threads that perform different tasks and sets of threads that perform the same operation on different pieces of data. We introduce a new construct for each of these two patterns.

#### 3.3.1 Task Decomposition

In task parallel programming, it is common for different components of an algorithm to be assigned to different threads. For example, a climate simulation may assign a subset of all the threads to model the atmosphere, another subset to model the oceans, and so on. Each of these components can in turn be decomposed into separate parts, such as one piece that performs a Fourier transform and another that executes a stencil. Such a decomposition does not directly depend on the structure of the underlying machine, though threads can be assigned based on machine hierarchy.

Task decomposition can be expressed through the following *partition* statement that divides the current team of threads into subteams:

```

partition(T) { B_0 \ B_1 \ \dots \ B_{n-1} }

```

A Team object (corresponding to the current team at the top level) is required as an argument. The first child team executes block  $B_0$ , the second block  $B_1$ , and so on. It is an error if there are fewer child teams than partition branches, or if the given team arguments on each thread in the current team do not have the same description of child teams. If the provided team has more than n subteams, the remaining subteams do not participate in the partition construct. Once the partition is complete, threads rejoin the previous team.

As a concrete example, consider a climate application that uses the team structure in Figure 3.2 to separately model the ocean, the land, and the atmosphere. The following code would be used to divide the program:

```

partition(t) {

{ model_ocean(); }

{ model_land(); }

```

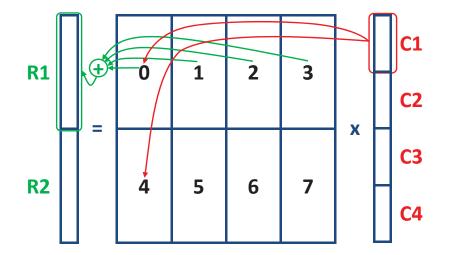

Figure 3.3: Blocked matrix-vector multiplication.

```

{ model_atmosphere(); }

}

```

Threads 0 to 3 would then execute model\_ocean(), threads 4 to 7 would run model\_land(), and threads 8 through 11 would model the atmosphere.

Since partition is a syntactic construct, task structure can be inferred directly from program structure. This simplifies program analysis and improves understandability of the code.

#### 3.3.2 Data Decomposition

In addition to a hierarchy of distinct tasks, a programmer may wish to divide threads into teams according to algorithmic or locality considerations, but where each team executes the same code on different sets of data. Such a data decomposition can be either machine dependent or required by an algorithm, and both the height and width of the hierarchy may differ according to the machine or algorithm.

Consider the matrix-vector multiplication depicted in Figure 3.3, where the matrix is divided in both dimensions. In order to compute the output vector, threads 0 to 3 must cooperate in a reduction to compute the first half of the vector, while threads 4 to 7 must cooperate to compute the second half. Both sets of threads perform the same operation but on different pieces of data.

A new *teamsplit* statement with the following syntax allows such a data-driven decomposition to be created:

```

teamsplit(T) B

```

The parameter T must be a Team object (corresponding to the current team at the top level), and as with partition, all threads must agree on the set of subteams. The construct causes each thread to execute block B with its current team set to the thread's subteam specified in T, so that thread ranks and collective operations in B are with respect to that subteam. As mentioned above, each subteam also has a rank, which can be used to determine the set of data that the subteam is to operate on.

As an example, consider a reduction over the rows of a matrix, as in the following code:

```

teamsplit(t) {

Reduce.add(data[t.myChildTeam().rank()], myData);

}

```

The reduction executes over the current team inside the teamsplit on each thread, which is its associated child team of t. As a result, data from threads 0 to 3 are reduced to produce a result for team 0, and data from threads 4 to 7 are combined into a result for team 1.

#### 3.3.3 Common Features

Both the partition and teamsplit constructs are lexically scoped, changing the team in which a thread is executing within that scope. This implies that at any point in time, a thread is executing in the context of exactly one team (which may be a subteam of another team and have child teams of its own). Given a particular team hierarchy, entering a teamsplit or partition statement moves one level down in the hierarchy, and exiting a statement moves one level up. Statements can be nested to make use of multi-level hierarchies, and recursion can be used to operate on hierarchies that do not have a pre-determined depth. Consider the following code, for example:

```

public void descendAndWork(Team t) {

if (t.numChildren() != 0)

teamsplit(t) {

descendAndWork(t.myChildTeam());

}

else

work();

}

```

This code descends to the bottom of an arbitrary team hierarchy before performing work. A concrete example that uses this paradigm is the merge sort in  $\S8.1.3.2$ .

In order to meet the composability goal of §3.1, the thread IDs returned by Ti.thisProc() are now relative to the team in which a thread is executing, and the number of threads returned by Ti.numProcs() is equal to the size of the current team. Thus, a thread ID is always between 0 and Ti.currentTeam().size()-1, inclusive. A new function Ti.globalNumProcs() returns the number of threads in the entire program, and Ti.globalThisProc() returns a thread's global rank.

Collective communication and synchronization now operate over the current team. Both the partition and the teamsplit construct are also considered collective operations, so they must be textually aligned in the program. The combination of the requirement that all threads must agree on the set of subteams when entering a partition or teamsplit construct, lexical scoping of the

constructs, and textual collective alignment ensure that no circular dependencies exist between different collective operations. In  $\S4.3$ , we describe how the first and last properties are enforced.

## 3.3.4 Discussion

It may be apparent that the partition statement can be implemented in terms of teamsplit, such as the following:

```

teamsplit(t) {

switch(t.myChildTeam().teamRank()) {

case 0:

model_ocean();

break;

case 1:

model_land();

break;

case 2:

model_atmosphere();

}

}

```

While this is true, we decided that an explicit construct for task decomposition is cleaner and more readable than the combination of teamsplit and branching. The two constructs also differ with respect to the superset operations described below.

## 3.3.5 Superset Operations

By design, the partition and teamsplit constructs require a user to exit or enter a construct to move up or down a team hierarchy or to use multiple team hierarchies. We suspect that it may be useful, however, to be able to temporarily move up one or more levels in a team hierarchy without exiting a partition or teamsplit, though we have yet to find concrete examples where this is the case. Nevertheless, our implementation contains a *superset* statement that ascends the team hierarchy within a specified lexical scope:

superset (i) B

This results in execution of block B in the context of the team that is i levels up from the enclosing team, i.e. that team's ith ancestor. As an example, consider the following code:

```

teamsplit(t) {

Reduce.add(data[t.myChildTeam().rank()], myData);

superset(1) {

Ti.barrier();

}

...

}

```

#### CHAPTER 3. LANGUAGE EXTENSIONS

Inside the teamsplit, threads execute as members of their respective subteams of t, so the reduction is over these teams. If threads read data from another team later in the teamsplit, then a global synchronization is necessary to ensure that the reductions have completed on all threads. The superset operation accomplishes this by walking up one level to the global team and performing a barrier.

A superset operation is considered to be a collective operation in the enclosing team as well as its i ancestors. Since teams in a partition execute different code, the i enclosing team statements must all be teamsplits in order to conform to textual collective alignment. It is an error if all threads do not execute the superset in any of the i ancestral teams, if they differ on the value of i, or if the enclosing team has fewer than i ancestors. Superset statements may be nested, but they may not contain any teamsplit or partition statements.

We anticipate that the most likely use of a superset operation will be to perform a collective, such as a barrier, at a higher level in the team hierarchy. As such, we have implemented versions of many collective operations that operate at higher levels without requiring an explicit superset construct. For example, the call Ti.barrier(1) executes a barrier on the parent team. Of course, such operations must meet the same requirements as the superset construct itself.

#### **3.4 Implementation**

We have implemented hierarchical team constructs on top of GASNet teams, which are flat groupings of threads. Each node in a team hierarchy is associated with a separate GASNet team, which is created when a team is initialized. We avoid creating unnecessary duplicate GASNet teams by caching them at the Titanium level and checking whether or not there is an existing GASNet team corresponding to a particular Titanium subteam.

The lexical teamsplit, partition, and superset operations are implemented in the compiler as calls to the following library functions:

single static TeamHandle checkedSplit(Team t, boolean isTeamsplit); single static TeamHandle split(Team t, boolean isTeamsplit); single static void unsplit(TeamHandle th);

Upon entering a new team context, checkedSplit or split is called, depending on whether or not the user has enabled error checking. (See §4.2.3 for more details on error checking.) This returns a TeamHandle immutable object that encodes the previous team before entering the new context. When exiting that context, the handle is passed to unsplit, restoring the previous team context.

As with any lexical construct, such as the **synchronized** statement of Java, the compiler must ensure that the previous context is restored even when exiting the construct through an abrupt termination. An *abrupt termination* is a termination that exits a statement at any point other then its syntactic exit point and includes return statements and thrown exceptions. The Titanium compiler instruments abrupt terminations to restore the previous team context, if necessary.

Finally, when entering a new team context, the Titanium runtime sets the current GASNet team on each thread accordingly and updates a handful of variables to reflect the properties of

the new team. As a result, there is very low overhead to switching team contexts, satisfying the performance goal of  $\S3.1$ . In order to execute a collective, the Titanium runtime passes the current GASNet team to the GASNet collectives library, resulting in the desired behavior that collectives only execute over the current team.

# Chapter 4

# **Alignment of Collectives**

Many scientific applications are written in a bulk-synchronous style that alternates between communication and computation phases, or between different phases of physical simulations such as the ocean and atmospheric models in a climate simulation. These applications frequently require all threads to synchronize and communicate together. Like other SPMD languages, Titanium provides *collective operations* to support this. The four primitive collective operations in Titanium are barriers, broadcasts, exchanges, and reductions. A *barrier* forces threads to wait until all threads have reached it. A *broadcast* is a one-to-all communication construct that sends a value from one thread to the others. An *exchange* is an all-to-all communication construct that copies one value from each thread to all threads. A *reduction* combines values from each thread into a single value on one thread or an all threads. More complicated collectives can be built using these primitives, including global view operations like those in the data parallel model

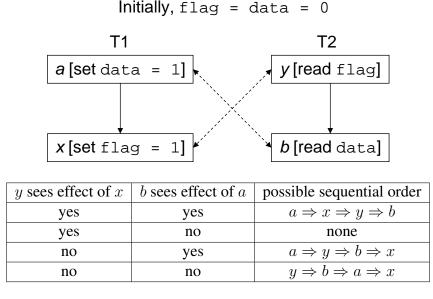

Collective operations introduce the possibility of deadlock if not all threads execute the same sequence of collectives. The collectives are *aligned* if all threads do execute the same sequence.

Most SPMD languages do not attempt to guarantee alignment of collectives. Some languages such as UPC have *named* collectives. These collectives take an integer value as an argument. When the collective executes, it compares the value on all threads and generates an error if they differ. However, different collective operations in a program can have the same value under this scheme. Even if each collective in a program has its own unique value, as soon as the collective is wrapped inside a function, the alignment scheme can be defeated. For example, a call to the following function acts like an unnamed barrier:

```

void barrier2() {

upc_barrier 315415431;

}

```

More complicated and less malicious examples of this can occur in practice. A further flaw with named collectives is that they can result in late error messages: the actual program statement<sup>1</sup> that causes misalignment can be far from the affected collective and is not detected or reported to the user.

<sup>&</sup>lt;sup>1</sup>In this chapter, we use the term *statement* to refer to both statements and expressions in a program.

Aiken and Gay introduced the concept of *structural correctness* to enforce alignment of collectives and developed a static analysis that determines whether or not a program is structurally correct [1, 39]. The following code is not structurally correct:

```

if (Ti.thisProc() % 2 == 0)

Ti.barrier(); // even ID threads

else

; // odd ID threads

```

Titanium provides a stronger guarantee of *textually-aligned collectives*: not only do all threads execute the same number of collectives, they also execute the same *textual* sequence of collectives. In addition, all control-flow decisions affecting execution of collectives must match on all threads, avoiding the problem with named collectives above. Thus, both the above structurally incorrect code and the following structurally correct code are erroneous in Titanium:

```

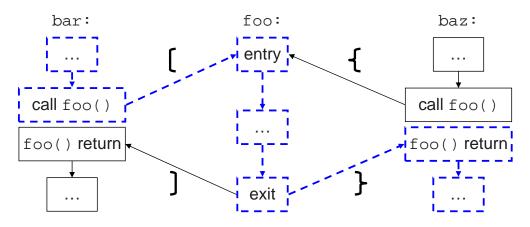

if (Ti.thisProc() % 2 == 0)