# **Experimental and Simulation Study of Resistive Switches for Memory Applications**

Feng Pan

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2012-192 http://www.eecs.berkeley.edu/Pubs/TechRpts/2012/EECS-2012-192.html

September 4, 2012

Copyright © 2012, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Ву

Feng Pan

A dissertation submitted in partial satisfaction of the

requirements for the degree of

**Doctor of Philosophy**

in

Engineering - Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Vivek Subramanian, Chair

Professor Tsu-Jae King Liu

**Professor Ronald Gronsky**

Fall 2012

#### Abstract

Experimental and Simulation Study of Resistive Switches for Memory Applications

By

# Feng Pan

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vivek Subramanian, Chair

In recent years, resistive random access memory (RRAM) has gained significant attention as one of the promising candidates for next generation memory applications. This is due to its anticipated advantages versus Flash technology with respect to high density, low power and fast read and write speed. The main operation mechanism of these devices is a resistance change induced by filament formation through metal-cations or oxygen vacancies.

In the first part of this work, a Kinetic Monte Carlo (KMC) simulator is built to study the filament formation process in an electrochemical metallization (ECM) RRAM. This simulator takes into account most important physical and chemical processes such as oxidation, reduction, metal crystallization, adsorption, desorption and ionic transportation. The characteristics of the forming voltage, forming time and switching speed are investigated. In addition, studies on filament overgrowth and on-state resistance distribution are presented. Further, filament topography, which strongly influences device properties, is studied under different device operation conditions. The simulator also predicts that depending on the strength of lateral electric field, the conductive filament can break at various locations during the RESET process. The simulation results are verified by experiments conducted on Ag/Ag<sub>2</sub>S/W and Cu/H<sub>2</sub>O/Cu systems.

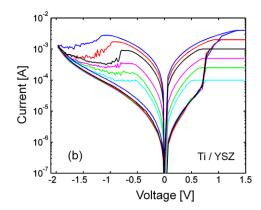

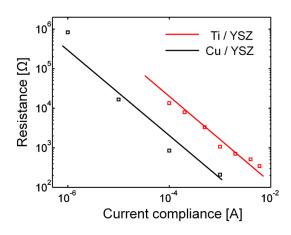

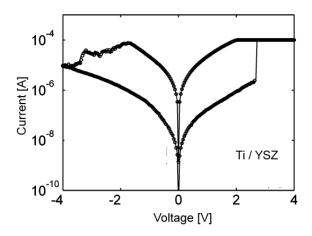

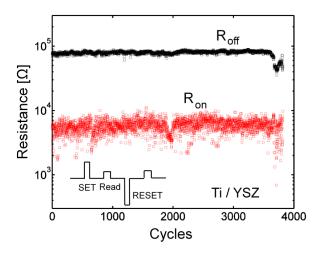

In the second part of this work, RRAM memory devices based on amorphous Yttria stabilized Zirconia (YSZ) are systematically studied. The effects of different top electrodes of Au, Cu, Ni, Al and Ti are investigated. And the characteristics and the mechanisms of Ti/YSZ and Cu/YSZ are studied in details. It is found that Ti/YSZ has much better endurance, retention and reliability than Cu/YSZ. The underlining physics driving this behavior is investigated. In addition, it is found that Ti/YSZ has very smooth transition in the RESET stage and the off state resistance exponentially increases with an increase of erase voltage. Based on those properties, a multilevel programming (MLP) cell is realized that shows good endurance. The underlying physics that makes the MLP possible for Ti/YSZ is investigated. Finally, it is shown that an incremental step pulse programming (ISPP) technique can significantly increase the device endurance and reliability. Furthermore, it can optimize the tradeoff between resistance programming window and device lifetime.

# Acknowledgements

Pursuing PhD in UC Berkeley is an extraordinary experience for me that I have never had before. It is a journey not only to drink in knowledge from book but also to learn from others and realize the weakness of my own and subsequently find a way to improve. Throughout this process there are many people I feel thankful to. And without their support, this work would not have been possible.

I feel deeply indebted and thankful to my parents. I would like thank my Dad and Mom for raising me up and thank for their enormous love and sacrifice for me throughout my life. Without their boundless love and support, I would not achieve what I have today. I would especially thank my father. I would never forget the hardships he had in his life for the family. Furthermore, I would like thank my wife. She is such a nice person and has almost perfect personality and character. Coming across with her is my greatest fortune in my life. I also want to sincerely thank my Dad in law and Mom in law for their selfless support for taking care my daughter and my family. They sacrificed their time and even health in order to let my wife and I focus on research and study. I also would like thank my daughter. She is my hope and my joy source and moreover, she motivates me to work harder.

I would like heartily to thank my advisor Vivek Subramanian for his enormous support and guidance from the very beginning I joined the group. He is one of the greatest advisors I have ever encountered. He gives me the freedom to do the research topic I like. And he never gives students excessive pressure. Life is always balanced in our group. In addition, from him I am not only learning how to systematically conduct scientific research but also learning how to be an integrate, optimistic, mature person which is utmost important for my future career and personal life.

Next, I would like thank my colleague Dr. Shong Yin. I have continued his previous work on non volatile memory which I enjoy and perhaps will further continue on this topic after I graduate. Shong is such a nice people that he is willing to help me any time I need help. And he helps me go through my toughest time at the beginning of my graduate life.

I am also thankful to Kyle Braam, Jaewon Jang, Teymur Bakhishev, Huangyuan Tseng, Hongki Kang, Steven Volkman, Dan Soltman, Lakshmi Jagannathan and all the rest friends in organic group. Thanks for being friends and thanks for the help and encouragement given to me throughout years. I also feel very grateful to Dr. Nuo Xu for his inspiring ideas and great help.

In addition, I would like thank my qualifying exam and dissertation committee members: Prof Tsu-Jae King Liu, Prof Ronald Gronsky and Prof Sayeef Salahuddin.

Last but not least, I would like to thank all the people throughout my life who once loved me and cared about me. Thank you very much!

# **Table of Contents**

| Chapter 1: Introduction to Nonvolatile Memory Devices                           | 1  |

|---------------------------------------------------------------------------------|----|

| 1.1 Memory background                                                           | 1  |

| 1.2: FLASH                                                                      | 8  |

| 1.2.1: Floating Gate Device Operation Mechanism                                 | 9  |

| 1.2.2: NAND and NOR FLASH                                                       | 11 |

| 1.2.3: The Application and Scaling Limitations for FLASH                        | 15 |

| 1.3: Introduction to Resistive Random Access Memory                             | 16 |

| 1.3.1 RRAM Background                                                           | 17 |

| 1.3.2 Classification of RRAM Devices                                            | 18 |

| 1.3.3: Introduction to Electrochemical Metallization RRAM                       | 19 |

| 1.3.3: Introduction to Oxygen Vacancies Based RRAM                              | 25 |

| 1.3.4: The Equivalence Between ECM and VO Based RRAM                            | 31 |

| 1.4: Performance and Scaling Perspective of RRAM                                | 32 |

| 1.4.1: RRAM Performance                                                         | 32 |

| 1.4.1: RRAM Scaling                                                             | 33 |

| 1.5: This Work                                                                  | 38 |

| 1.6: References                                                                 | 39 |

| Chapter 2: Kinetic Monte Carlo Simulation on Electrochemical Metallization RRAM | 43 |

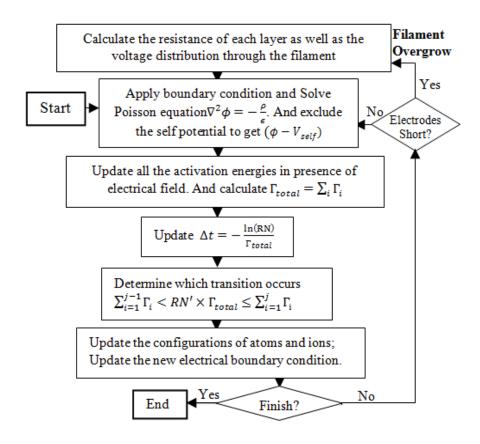

| 2.1: Introduction to Kinetic Monte Carlo Method                                 | 43 |

| 2.2: Establishment of a KMC simulator for ECM RRAM                              | 47 |

| 2.2.1: Basic Chemical and Physical Processes and Assumptions                    | 47 |

| 2.2.2: Simulation Procedures                                                    | 50 |

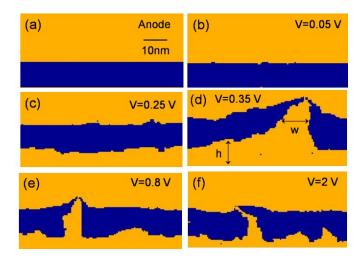

| 2.3: Simulation Results and Discussion                                          | 52 |

| 2.3.1: Filament Formation Study                                                 | 52 |

| 2.3.2: Relationship Between Forming Voltage and Device Size                     | 57 |

| 2.3.3: I-V Characteristics and SET Switching Properties                         | 59 |

| 2.3.4. RESET Stage Characteristics                                              | 62 |

| 2     | 2.3.5: | The Effect of Material Properties                                         | 65  |

|-------|--------|---------------------------------------------------------------------------|-----|

| 2.4   | : Su   | mmary                                                                     | 66  |

| 2.5   | : Re   | ferences                                                                  | 67  |

| Chap  | ter 3  | : Yttria Stabilized Zirconia Based RRAM                                   | 69  |

| 3.1   | .: Int | troduction to Yttria Stabilized Zirconia                                  | 69  |

| 3.2   | : Ex   | perimental Procedures                                                     | 72  |

| 3.3   | : Eff  | fect of Different Top Electrodes and Switching Mechanisms                 | 75  |

| 3.4   | : Ti   | YSZ and Cu/YSZ Devices                                                    | 77  |

| 3     | 3.4.1: | I-V Characteristics for Ti/YSZ and Cu/YSZ                                 | 77  |

| 3     | 3.4.2: | Endurance, Retention and Uniformity of Ti/YSZ and Cu/YSZ                  | 83  |

| 3     | 3.4.3: | Noise Analysis for Ti/YSZ and Cu/YSZ                                      | 87  |

| 3.5   | : Su   | mmary                                                                     | 92  |

| 3.6   | i: Re  | ferences                                                                  | 92  |

| Chap  | ter 4  | : Multi-level Programming and Impact of Programming Methodology on Device |     |

| Relia | bility |                                                                           | 95  |

| 4.1   | .: Int | troduction                                                                | 95  |

| 4.2   | 2: M   | ulti-level Programming of Ti/YSZ in RESET Stage                           | 96  |

| 4.3   | 3: Im  | pact of Programming Methodology on Device Reliability                     | 99  |

| 4.4   | : Su   | mmary                                                                     | 102 |

| 4.5   | : Re   | ferences                                                                  | 103 |

| Chap  | ter 5  | Conclusions and Future Work                                               | 105 |

| 5.1   | .: Co  | nclusion                                                                  | 105 |

| Į.    | 5.1.1  | KMC Simulation for ECM based RRAM                                         | 105 |

| ŗ     | 5.1.2  | YSZ based RRAM                                                            | 106 |

| į     | 5.1.3  | Multi-level Programming of Ti/YSZ based RRAM                              | 107 |

| į     | 5.1.4  | Impact of Programming Methodology on Device Reliability                   | 108 |

| 5.2   | : Fu   | ture Work                                                                 | 109 |

|       |        | forences                                                                  | 100 |

# **Chapter 1: Introduction to Nonvolatile Memory Devices**

# 1.1 Memory background

Electronic memory devices have vast applications in almost every area of modern life. Essentially, all modern electronic devices have memories either embedded or externally attached. In addition, the emerging of the personal electronics such as laptop computers, digital cameras, smart phones, tablets and other entertainment devices in the past two decades have resulted in a dramatic increase in the demand for such memory devices. Consumers' consistent desire to have better and cheaper memory has motivated researchers to pursue the continued advancement of memory technology. In the following paragraphs, the properties that a good memory device should have are described.

First, the density of a memory should be as large as possible such that it can store a large amount of data in a given die area. This means the cost per bit of information stored can be minimized. This significantly benefits the consumers in that they can satisfy their storage needs at a cheaper price. In fact, it is hard to imagine that in the year 1966, it would incredibly cost \$8×10<sup>12</sup> to have a one gigabyte DRAM, whereas today it is only around \$2 [1]. This shows the tremendous importance of high density memory.

Second, a memory device should have good endurance. Endurance determines how many cycles the device can sustain during write and erase operations. A device with large endurance can be repeatedly used without encountering operational failures. Clearly, this is critical because consumers don't need to replace the memory device frequently.

Third, a good memory device should have long retention. Retention defines how long data can be stored inside the memory devices without being lost inadvertently. A good memory should have as long a retention time as possible, so that once the memory is written, the system doesn't need to periodically back up or refresh the data.

Next, it is also good for the memory device to have fast programming and access speed so that the time spent on reading data from and writing data into the memory can be minimized. This is especially important when the speed is the primary concern. For example, in the computational arena, there is a trend towards replacing traditional hard disk drives (HDD) with solid state drives (SSD), which are based on FLASH technology. One of the reasons for doing so is that SSD has a faster access time. Thus, it can significantly increase computation speed and hence improves the computer efficiency.

Finally, the power consumption of the memory should be as low as possible. This is especially important for mobile devices such as smartphones, tablets and digital cameras. A low

power device reduces the need for battery charging and brings a significant convenience to customers.

In reality, it is very difficult for a memory device to have all the merits listed above. Depending on the application, every type of memory always has a particular focus. However, the merits mentioned above serve as guidelines motivating people to do research and try to come up with new memory devices that can have as many of the aforementioned properties as possible. In the following paragraphs, the classification of memory devices is discussed. In addition, special attention is paid to phase change memory, which is one of the emerging memory devices with which people hope to replace the current floating gate memory device technology. Finally, due to the extreme importance of floating gate memory devices in current technology, they are discussed comprehensively in the next section.

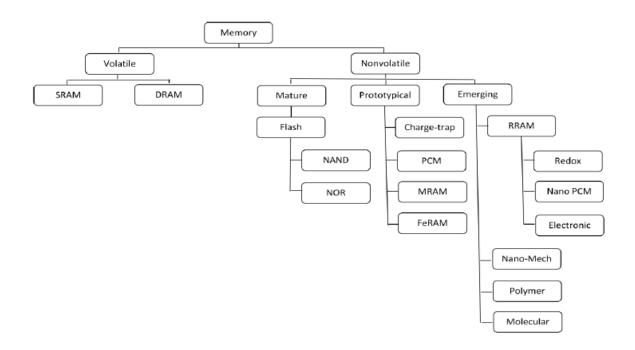

Figure 1.1. Memory classifications (An Chen – GLOBAL FOUNDRIES) [2]

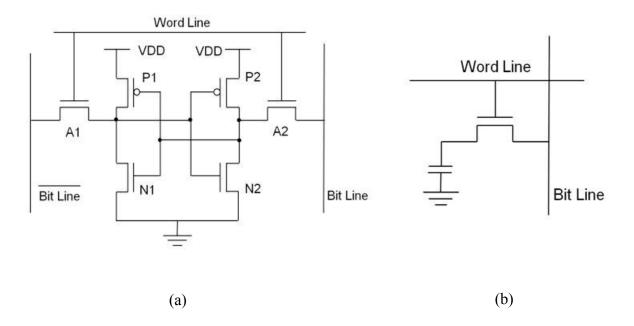

Generally memory devices can be classified into two categories based on their operational behavior as shown in Fig. 1.1 [2]. One class is volatile memory and the other type is non-volatile memory (NWM). Volatile memory, by definition, has to be connected to a power supply during the entire operation period. It will lose all the stored information (bit stored in each memory element) once the power is turned off. One of the most important volatile memories is static random access memory (SRAM), which consists of six transistors for each memory element as shown in Fig. 1.2 (a). Essentially, it is two inverters connecting in series with two access transistors attached to each input of the two inverters. As can be seen, due to the complicated

structure involving six transistors per bit, the density of SRAM is poor. Dynamic random access memory (DRAM) on the other hand has a much simpler structure as shown in Fig. 1.2 (b). It consists of a transistor in series with a capacitor which can naturally give rise to two memory states. The first state is the one when the capacitor is charged and the other one is when the capacitor is empty. Ideally, if there was no leakage current passing through the capacitor when it is in charged state, DRAM can hold the charge forever and information will remain even if the power is off. In reality, however, due to the leakage current present all the time, charges stored on the capacitor can only stay for several milliseconds. Therefore, periodic refreshment is needed to keep the information. The leakage current could come from several factors. First of all, the leakage path could be due to the non-ideal insulating properties of the dielectric between the two capacitor metal plates, where a finite current can always flow through the capacitor. The second leakage source is the subthreshold conduction of the transistor which results a finite a leakage current even if the world line is unselected. As can be seen due to its simple structure, DRAM has a much larger density than SRAM. Because of this advantage, the main memory in personal computer is DRAM.

Figure 1.2. (a) Structure of SRAM (b) Structure of DRAM

NWM, on the other hand, does not require power to sustain information. Today, the main commercial NVM technology is Flash, which is short for "flash electrically erasable programmable read-only memory". The word "read-only" is a bit confusing since nowadays those memories can be erased and programmed many times. The details of Flash will be discussed in the next section. Now, a question may naturally arise. Since NWM can sustain data

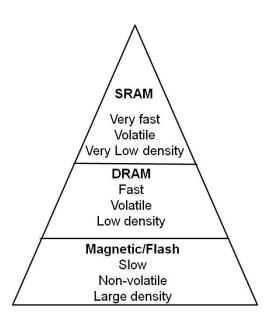

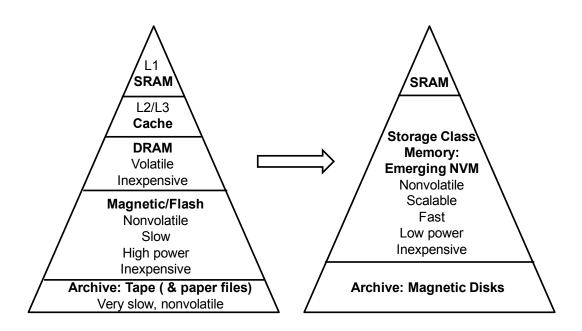

even without power supply, why do people still use volatile memory? The answer to this question is related to memory hierarchy as shown in Fig. 1.3 [3]. SRAM, even though it is volatile with very low density, has very fast program, erase and access time. Thus, it is used inside the processor chip and acts as cache. DRAM which has larger density than SRAM but slower speed is used as RAM for a computer. Traditional NVM such as Flash, even though it has much larger density than both SRAM and DRAM, is much slower than both of them. Thus, Flash is typically used for external storage of data instead of storing programming code inside a computer chip.

Figure 1.3. Memory Hierarchy

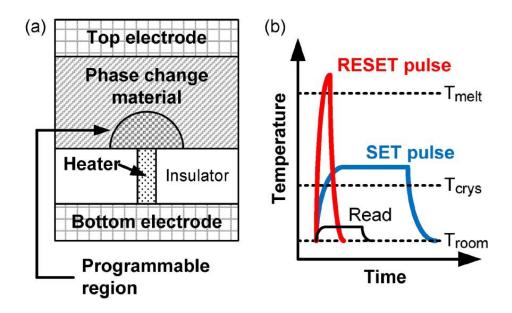

The initial motivation for people to study other types of NVM is to further improve the memory density such that people can store more information on a given size chip. Flash technology, as will be discussed soon in the next section, faces serious downscaling bottlenecks for device feature sizes less than 20nm [4]. Currently, lots of research has been done on phase change memory (PCM) [5, 6]. At a fundamental level, phase change memory utilizes joule heating to induce a phase change inside the material (germanium-antimony-tellurium (GST) as an example [7, 8]), so that the resistance of the material will change accordingly. Typically, it involves physical transitions between amorphous and crystalline states. Fig. 1.4 (a) shows the schematic of a conventional PCM cell. As can be seen the unit cell consists of both top and bottom electrodes with a phase change material sandwiched in between. One unique feature for the archetypal PCM cell is that there is a heater embedded in the insulator layer between the phase change material and the bottom electrode. The purpose of this heater is to increase the programming efficiency and reduce the programming power, as will be discussed soon.

Figure 1.4. (a) A schematic of a conventional PCM cell. (b) The temperature evolution inside the PCM device under different operation regimes [5]

As fabricated, the phase change material is in a crystalline state, because the processing temperature of the metal interconnect layer is high enough to crystallize the phase change material [5]. The crystalline structure generally shows a low resistivity property (memory at a low resistivity state is commonly described as being in the on state). In order to switch the device from the on state to the off state (high resistance state), which is defined as a RESET process, a large and fast voltage/current pulse has to be applied across the top and bottom electrodes such that the temperature inside the PCM material can rapidly rise up to the melting temperature,  $T_{melt}$  as shown in Fig. 1.4 (b) due to the joule heating effect. temperature will randomize the atomic order inside the PCM material, causing the material to transition from a crystalline structure to an amorphous state. One important note is that the falling edge of the applied pulse has to be very sharp as shown in Fig. 1.4(b). This means the device has to be quenched rapidly from T<sub>melt</sub> to a lower temperature below the crystallization temperature T<sub>crvs</sub>, in order to prevent crystallization from occurring. In this process, a heater can be added to localize the current and thus enhance the temperature in the local programmable region as shown in Fig. 1.4 (a). In this case only part of the PCM material is converted to the amorphous state. However, since this portion of material is in series with the crystalline material on the top, it effectively determines the overall resistance of the cell [5]. By adoption of the heater, due geometry effects, the current density at the heater and PCM material interface is much higher than the current density at other locations. Thus the temperature at the interface region reaches  $T_{\text{melt}}$  first, which make the PCM material become amorphous. Subsequently, the boundary of the amorphous region starts to grow and a droplet shape region, defined as a programmable region, is formed inside the PCM material as shown in Fig. 1.4 (a). The significant advantage of this approach is a reduction in the programming current and power due to the current localization effect.

Next, in order to switch the PCM cell from an amorphous to a crystalline state, defined as a SET process, an annealing process is applied. During this process, a moderate voltage/current pulse with longer duration is applied. The temperature of the PCM cell rises up to  $T_{crys}$ , but stays below  $T_{melt}$ .  $T_{crys}$  refers to the temperature at which the PCM material can crystallize. Generally, the crystallization of the material takes time, thus it is very important that the pulse be long enough that the temperature inside the PCM material is held high for sufficient time such that the crystallization process can be completed. After this process, the device transitions from the high resistive state to a low resistive state.

The reading process is relative straightforward compared with the SET and RESET processes. During the reading process, a small voltage/current detection pulse is applied across the electrodes. The resultant temperature inside the PCM material is well below  $T_{crys}$  so that the memory state of the device is not disturbed.

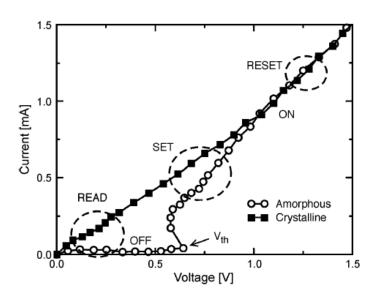

Figure 1.5. The I-V characteristics of a typical PCM cell under different operation regimes [5]

Fig 1.5 shows the typical current-voltage characteristics of a PCM device [5]. Assuming the device is initially at the off state, since the the resistivity of the amorphous material is large, there is little current flowing through the device. The device is turned on when the voltage reaches a threadhold value ( $V_{th}$ ). This is accompanied by a large increase in current. This is indicated by SET process as shown in the figure, and the device reaches the on state. In the RESET stage, an even higher voltage is applied. If the pulse drops rapidly, the device will reach the off state. However, if the voltage is ramped down gradually, there is enough time for the

material to crystallize and the device will stay at the on state. In addition, it is interesing to see that there is snap-back behavior in the I-V characteritics shown in Fig. 1.5 and resulting in a negative resistance. F. Buscemi and colleagues [9] conducted a Monte Carlo simulation and conclude that when the electron hopping process inside the PCM material is not fast enough, charge is accumulated close to the contact regions, which generates a counter electric field. The net effect is a decrease of voltage as the current increases which results in the snap-back phenomenon. Thus, the snap-back behavior is a non-equilibrium behavior.

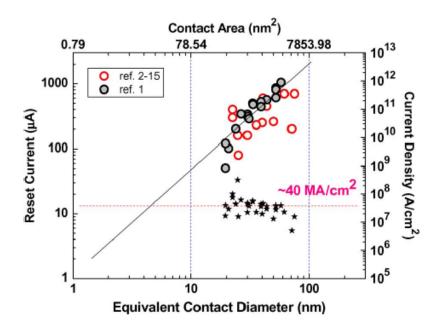

One problem associated with PCM is the power consumption. In order to change the crystal structure of the film, a large amount of current has to be applied to the device to make sure that enough heat is generated. Fig. 1.6 shows the relationship between the RESET current and effective device contact area. As can be seen, even though the RESET current decreases as the device contact area decreases, the required current density is more or less constant around  $40\text{MA/cm}^2$ . It is estimated that even for a PCM with size reduced to 15nm on a side,  $40\mu\text{A}$  RESET current is still needed [2]. This limits the applications of PCM, particularly with respect to today's low-power electronic devices such as laptops and mobile devices.

Figure 1.6. The relationship between RESET current and equivalent device contact diameter [5]

It will be ideal if people can find a kind of universal memory device which is non-volatile like FLASH, offers fast programming and access time like SRAM, and at the same time has the combined advantages of high density and low power consumption [10]. If such a universal memory exists, it can not only replace FLASH but also possible replace DRAM such that it could

be directly integrated into computer chips and thus can significantly improve computational performance. Resistive random access memory (RRAM) is such a candidate memory.

## **1.2:** FLASH

Flash memory has had a dramatic market growth in the past two decades. Table 1 shows the rise of the Flash memory market in the past 20 years [11]. As can be seen within only fifteen years, the share of Flash memory in total memory market increased from 0.3% to 34.4% and by year 2006 Flash alone had occupied 8.1% of entire semiconductor market. The rapid growth of Flash memory is attributed to two of its major properties which ideally suit the consumer electronics market [11]. The first one is that Flash is small and reliable. The second feature is its non-volatile property. Due to those features, Flash has become an ideal candidate for electronics requiring mobility and miniaturization. It is typically used in USB flash drives, solid-state drives and memory cards which can be found in various modern electronic products such as smartphones, digital cameras, tablets, laptops and personal computers.

Table 1.1. The rise of the Flash memory market [11]

|      | Flash memory<br>market<br>(USD Million) | Flash memory<br>market annual<br>percentage growth | Flash memory as<br>percentage of total<br>semiconductor<br>market | Flash memory as<br>percentage of total<br>memory market |

|------|-----------------------------------------|----------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------|

| 1990 | 35                                      |                                                    | 0.1                                                               | 0.3                                                     |

| 1991 | 135                                     | 286                                                | 0.3                                                               | 1.0                                                     |

| 1992 | 270                                     | 130                                                | 0.5                                                               | 1.8                                                     |

| 1993 | 640                                     | 106                                                | 0.8                                                               | 3.0                                                     |

| 1994 | 865                                     | 35                                                 | 0.9                                                               | 2.7                                                     |

| 1995 | 1,860                                   | 115                                                | 1.3                                                               | 3.5                                                     |

| 1996 | 2,611                                   | 40                                                 | 2.0                                                               | 7.2                                                     |

| 1997 | 2,702                                   | 3                                                  | 2.0                                                               | 9.2                                                     |

| 1998 | 2,493                                   | -8                                                 | 2.0                                                               | 10.8                                                    |

| 1999 | 4,561                                   | 83                                                 | 3.1                                                               | 14.1                                                    |

| 2000 | 10,637                                  | 133                                                | 5.2                                                               | 21.6                                                    |

| 2001 | 7,595                                   | -29                                                | 5.5                                                               | 30.5                                                    |

| 2002 | 7,767                                   | 2                                                  | 5.5                                                               | 28.7                                                    |

| 2003 | 11,739                                  | 51                                                 | 7.1                                                               | 36.1                                                    |

| 2004 | 15,611                                  | 33                                                 | 7.3                                                               | 33.1                                                    |

| 2005 | 18,569                                  | 19                                                 | 8.2                                                               | 38.3                                                    |

| 2006 | 20,275                                  | 9                                                  | 8.1                                                               | 34.4                                                    |

In this section, the operation principle of Flash and its limitations are discussed. First of all, the basic physics of its building block floating gate device is described. Next, NAND and NOR, two types of Flash structures, are discussed in detail. The discussion includes their programming and erases mechanisms as well as physical properties like endurance, retention

and reliability. Finally, the limitations affecting the future development of Flash are emphasized.

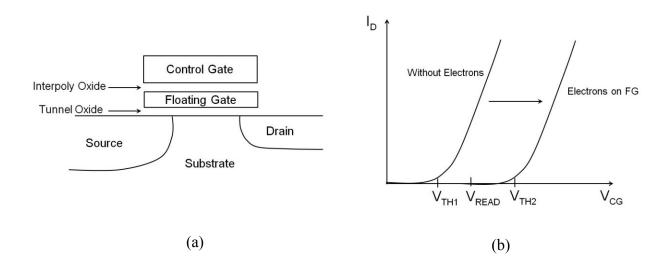

#### 1.2.1: Floating Gate Device Operation Mechanism

The basic building block of FLASH is a special type of metal oxide semiconductor field effect transistor (MOSFET) as shown in Fig. 1.7 (a) [12]. The major difference compared with a normal MOSFET is that a second gate named "floating gate (FG)" is inserted between the control gate (CG) and silicon substrate. The purpose of this floating gate is to modulate the device threshold voltage ( $V_{TH}$ ). If there are electrons trapped inside the FG,  $V_{TH}$  will shift towards the positive direction as shown in Fig. 1.7 (b) by an amount of:

Figure 1.7. (a) The structure of floating gate device. (b) Typical I-V characteristics of a floating gate device with and without electron on the floating gate.

$$\Delta V_{TH} = \frac{-\Delta Q_{FG}}{C_{FC}} \tag{1}$$

Where  $\Delta Q_{FG}$  is the electron charges trapped on the FG and  $C_{FC}$  is the coupling capacitance between CG and FG. Thus, if a read voltage (V<sub>READ</sub> shown in Fig. 1.7 (b)) is applied, there will be no current flowing for devices which have electrons trapped on their FGs, yet a significant amount of current flowing for devices which don't have electrons on their FGs. Therefore, by doing so, two memory states are created.

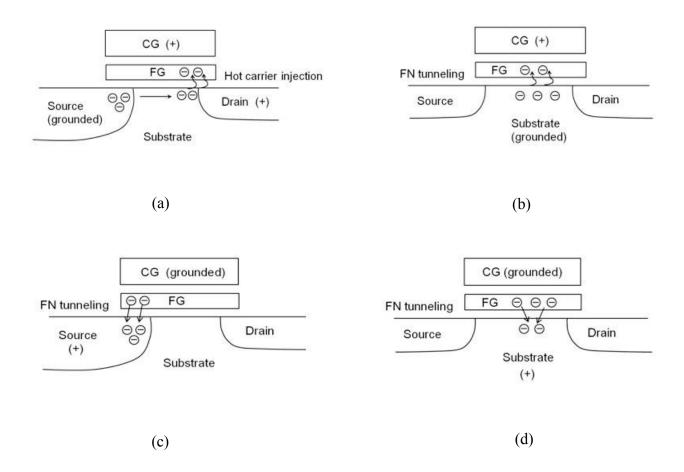

There are two ways to inject electrons (program) into the FG as shown in Fig. 1.8 (a). The first one is to use hot carrier injection (HCI) and the second method is by adopting Fowler-Nordheim (FN) tunneling shown in Fig. 1.8 (b). HCI is done by applying a large positive voltage above 10V to both the CG and the drain electrode, which drives the transistor into saturation

mode. A very large electric field is therefore created near the junction of the drain and substrate corner. Electrons in this region gains significant kinetic energy and subsequently become "hot". Once electrons have enough energy, they can overcome the potential barrier represented by the tunnel oxide, and traverse through the tunneling oxide and get trapped inside the floating gate. One obvious disadvantage of this method is power consumption. In order to create enough hot carriers, a large drain current has to flow though the device which results in very poor power efficiency.

Figure 1.8. To program the Floating gate device by (a) hot carrier injection method and (b) by FN tunneling. and to erase the device by (c) FN tunneling at source side and (d) FN tunneling at channel.

Another type of programming method is based on FN tunneling as shown in Fig. 1.8 (b). In this case, the CG is positively biased and the substrate is grounded while the source and drain are kept floating. The strong transverse electric field between the channel and the CG enable electrons to tunnel from the inversion layer formed in the substrate directly into FG. The major advantage of this method is that FN tunneling consumes much less power than that of HCI. The approximate mathematical formula to describe FN tunneling can be achieved by using the Wentzel-Kramers-Brillouin (WKB) approximation [13]

$$J = \frac{q^3 F^2}{16\pi^2 h^2 \Phi_B} \exp \left[ -\frac{4(2m_{ox}^*)^{1/2} \Phi_B^{3/2}}{3\hbar q F} \right]$$

(2)

Where  $\Phi_B$  is the barrier height and  $m_{ox}^*$  is the effective mass in the dielectric and F is the electric field through the oxide. As can be seen, the current density is very sensitive to electric field and this can cause a variation problem with respect to the  $V_{TH}$  as will be discussed later.

There are two methods to erase the electrons on the FG. Both of them are based on FN tunneling as shown in Fig. 1.8 (c) and (d). The first method is to apply a positive voltage at source side and leave the CG grounded. The electrons can then tunnel through the oxide and reach the source region. Since a large positive voltage is present on the source side, the junction between the source and substrate is highly reversely biased. Therefore, to prevent junction breakdown, the doping concentration of the source cannot be too high. Practically, the source depth is designed deeper than the drain side with less doping concentration to prevent breakdown [12]. A second problem associated with this erase operation is that as device size keeps scaling down, the overlap region between the FG and the source side become smaller and smaller. Thus the erase process gradually becomes less efficient. To overcome this problem, a second erase methodology has been adopted as shown in Fig. 1.8 (d). In this case, the substrate instead of the source is positively biased and the CG is grounded. The electrons can directly tunnel into the channel region. Furthermore, a symmetric source and drain configuration can be utilized.

Finally, even though FN tunneling is power efficient, the exponential dependence of tunnel current causes critical problems of process control. Any small variation in oxide thickness can cause significant variation in  $V_{TH}$  during the programming and erase steps. Thus, good process control is needed to minimize the oxide surface roughness [12].

#### 1.2.2: NAND and NOR FLASH

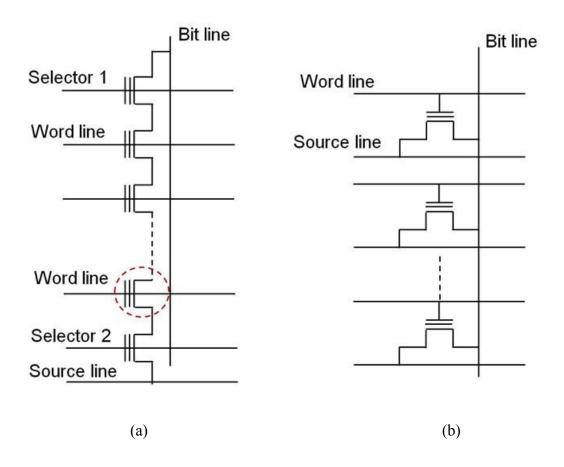

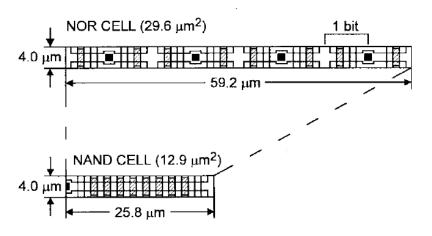

A typical FLASH memory is based on one of the array structures shown in Fig. 1.9. The NAND module contains a series of floating gate devices connecting in series while the NOR module has them connecting in parallel. Fig. 1.10 [12] shows the layouts of those two structures. The layout is drawn based on one micron technology design rules, for convenience, but is generally applicable across all technology nodes. In the example, each memory array consists of eight single cells. As can be seen, the average cell area occupied by NOR Flash is 29.6  $\mu$ m<sup>2</sup>, whereas only 12.9  $\mu$ m<sup>2</sup> is needed for NAND Flash. It is obvious that the density of NAND FLASH is higher than that of NOR, particularly since every transistor in the string does not require its own source and drain contact. This is one of the major advantages of NAND over a NOR structure. In fact, if *F* represents the smallest feature size at any given technology node, the individual cell size in NAND structure is  $2F \times 2F = 4F^2$ , and it is at least  $5F \times 2F = 10 F^2$  for NOR.

Figure 1.9. (a) The NAND array structure of FLASH (b) the NOR array structure.

Fig. 1.10. Layout comparisons between NAND and NOR Flash [12].

The read operation of NAND FLASH is done as follows. First, the BL is pre-charged to ~1V and the select gates of the block are enabled. Next, the selected WL is held at 0V and all the other deselected WL are biased at a voltage which is higher than the highest  $V_{TH}$  such that the information can go through. If the selected cell has a  $V_{TH}$  smaller than 0V, the BL will discharge and a page buffer circuit will read the data as "1". If the selected cell has a  $V_{TH}$  larger than 0V, there is no current flowing through and the BL stays at 1V and the page buffer reads the data as 0 [14]. Because of the NAND structure one obvious disadvantage is the slow read speed. For example, in order to read a cell at the bottom of the chain as shown in Fig. 1.9(a), circled by dash line, signal has to pass through all the other cells on top of it, which generates significant amount of parasitic resistance and capacitance and therefore the RC time delay is large. On the other hand, such problem does not exist in NOR FLASH structure which offers the random access to every memory cell inside the array. Because of access time difference, together with the difference in density, NOR FLASH is more attractive for applications such as program-code storage, while NAND is more suitable for video or audio storage which do not need fast random access but need large storage density [15].

To program and erase the memory array is much more complicated than the read operation. Generally before the programming step, all the cells in both NAND and NOR array have to be erased first [16]. It is straightforward to do the erase operation for NAND architecture, in which all cells in the module are erased at same time and this is achieved by applying large positive voltage to the substrate and OV to the word line while keeps the source line and bit line floated so that the electrons can tunnel back to the channel. For NOR array, OV is applied to CG and a large positive voltage to the source side so that electrons can tunnel into the source region.

To program a cell inside a NAND array, the selector 1 is enabled such that the bit line is connected to ground while selector 2 is disabled so that the source line is kept floating. Then a high voltage (~20V) is applied to the CG and electrons can subsequently tunnel into the FG by the FN tunneling mechanism. To program a NOR device, a high voltage is applied to both word line and bit line of the selected devices, based on HCI, electrons can overcome the barrier of oxide and get trapped in the FG. Because of the difference in the programming methodology, NAND FLASH is much more power efficient than NOR array.

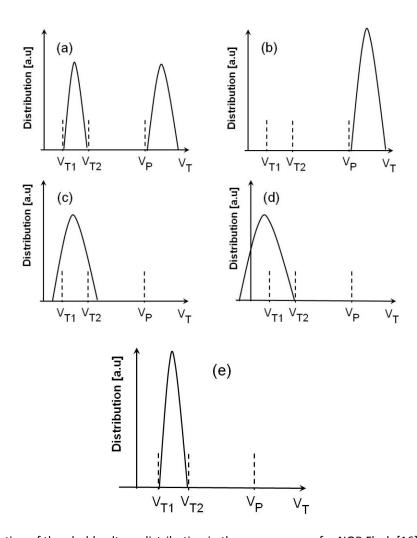

It has to be mentioned that because of its parallel array structure, leakage path problems have to be avoided in NOR memory array and in practice a program "0" step has to be applied during the erase process of NOR Flash. Fig. 1.11 illustrates the entire erase procedure of a NOR device [16]. Before the erase operation, the  $V_{TH}$  distribution throughout the memory array is illustrated in Fig. 1.11 (a). After that, a "program 0" step has to be performed shown in (b) such that the  $V_{TH}$  of all the devices is raised, which reduces the over-erase problem in the following steps. Next, an erase step is performed as shown in (c). As can be seen, this erase step causes a large distribution of  $V_{TH}$  which can go beyond the acceptable range of  $V_{T1}$  and  $V_{T2}$  respectively. Therefore additional steps have to be performed to squeeze all the individual  $V_{TH}$  values into this allowable range. Thus, an erase verification procedure has to be applied and this is shown in (d). However, at this moment some devices are over-erased as shown in (d) and  $V_{TH}$  of some devices are less than  $V_{T1}$  and even go negative. This should be absolutely avoided in the NOR array since cells with negative  $V_{TH}$  cause significant leakage current when the device is

unaddressed (e.g. the word line voltage is 0). Therefore, as a final step, a "soft programming" has to be done to shift all the  $V_{TH}$  within the range.

Figure 1.11. Illustration of threshold voltage distribution in the erase process for NOR Flash [16] (a) before erase (b) after a "program 0" step (c) after a single erase pulse (d) after the erase verify procedure (e) after soft-programming.

Table 1.2 Performance comparison between NAND and NOR Flash

|      | Density | Read            | Erase        | Program | Access Method |

|------|---------|-----------------|--------------|---------|---------------|

| NAND | High    | slightly slower | Milliseconds | Fast    | sequential    |

| NOR  | Low     | Fast            | Seconds      | Slow    | Random        |

Due to the complicated erase procedure, NOR takes a much longer time to erase than does NAND. Table 1.2 compares the performance of NAND and NOR. Due to the differences in their performances, NOR is more suitable for code storage and NAND is more suitable for data storage.

# 1.2.3: The Application and Scaling Limitations for FLASH

Based on the fundamental operation mechanism of FLASH, there are several limitations from both application and scaling perspectives. First, as discussed above it is impossible to achieve properties like fast programming, access and high density together with random access at same time. NAND Flash offers the advantages of faster programming and high density yet it doesn't have the random access capability and the read speed is slow. NOR Flash, on the other hand, has random access capability; however, it is inferior to NAND in all the other aspects. Thus, it is desirable to have kind of device which has all the merits as a memory device.

There is another fundamental challenge for Flash for future NVM application. In fact, scaling will become the eventual bottleneck for all such devices. Even though NAND Flash has higher density than NOR, it faces lots of difficulties to continue scaling down. People generally believe that the feature size of traditional Flash is impossible to scale down to below 20nm [17]. Those limitations generally are related to its fundamental operation principle. First of all, the interpoly dielectric thickness must scale with tunnel oxide to maintain adequate coupling of the applied voltage to the tunnel dielectric [17]. To ensure sufficient voltage can be passed to the floating gate during program and erase operations, the gate coupling ratio (the capacitance ratio of the CG to FG capacitor to the total FG capacitance) has to be greater than 0.6 [17]. As devices scale down, the CG needs to wrap around the FG to provide enough capacitance. However, it is very difficult to achieve such a structure when the bit line spacing becomes 20nm or less. In addition, there is also a limitation on the thickness of the tunneling oxide. If the tunneling oxide is too thin, electrons can, even without any external electric field, easily tunnel back to the channel. Therefore, the device retention properties could be severely degraded. The same principle is also true for interpoly oxide. Furthermore, because of the difficulties in scaling down the thickness of oxides, the reduction of the operating voltage also becomes difficult.

In addition, there are additional factors that set a fundamental scaling limitation on the device channel length. For devices that are programmed by HCI and erased by electrons tunneling from the FG to the source side, a minimum overlap between drain and FG as well as between source and FG is needed. This sets a limitation on how small the channel length can be. In addition, even for device based on FN tunneling between the FG and the channel, the channel length cannot be too small in order to prevent leakage current caused by various short channel effects. Finally, as the size of device goes smaller, the number of electrons stored in the FG will be very small and cause severe random telegraph noise [17] and furthermore, result in associated reliability problems.

# 1.3: Introduction to Resistive Random Access Memory

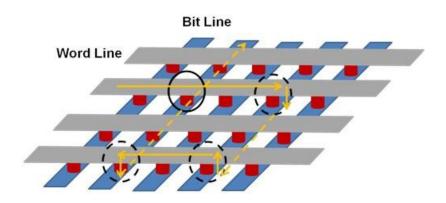

As stated in the previous section, due to the scaling limitations of current Flash technology, it is desirable to discover new technologies such that the scaling can be continued further. More than that, it is very attractive to find one kind of memory which has the combinational advantages of both SRAM and Flash such that it not only has fast program, erase and access time but also has good non-volatility as well as high density characteristics. This type of memory can be called universal memory or storage class memory [18]. If this type of memory is realized, the memory hierarchy will be fundamentally changed as shown in Fig. 1.12.

As shown from bottom to top, currently we have tape, magnetic/Flash, DRAM and Cache as well as SRAM. Along this direction, the speed of the memory goes up while the density decreases. If a universal memory can be realized, such a memory could replace the Flash, the DRAM and part of the Caches. The magnetic disk is only used for archive purpose due to its extremely high density while the SRAM is only adopted when extremely fast speed is required. As a result, the memory hierarchy becomes much simplified.

Figure 1.12. The modification of memory hierarchy upon realization of a universal memory (storage class memory) [18]

The requirements of such universal memory will be nonvolatile, scalable, fast, low power and inexpensive. People are trying various technologies and developing new physical concepts to make this type of memory possible. One of most promising candidates the so called Resistive Random Access Memories (RRAM) will be introduced in this chapter.

# 1.3.1 RRAM Background

The history of the resistive change effect in RRAM can be traced back to the 1960s. In 1964, P.H. Nielsen [19] and colleagues first found the resistive switching effect in an Au/SiO/Au structure. They further suggested that such an element could be used as a memory device which could be accessed nondestructively. Several years later, several researchers also found similar phenomena in an Al/SiOx/Au system [20, 21]. Due to stability problems and the emergence and successful development of Si based memories [22], the resistive switching memories never developed until quite recently. In 2002, W.W. Zhuang and colleagues [23] demonstrated an RRAM device based on PCMO. They first showed that such a device is capable of providing memory characteristics that are potentially more favorable than that of traditional FLASH devices. After that, in 2004, Samsung Electronics [24] demonstrated resistive switching behavior in various transition metal oxides (TMO) such as NiO, TiO2, HfO2 and ZrO2. The devices delivered operating voltage below 3V, programming current around 2mA with 10<sup>6</sup> cycles of endurance. Ever since, RRAM has become one of the hottest research topics in both academia and industry. The main motivation for people to investigate RRAM is due to its anticipated advantages, which almost cover all the merits of an ideal memory such as large endurance, long retention, fast access speed, low power and most importantly high density.

Similar to PCM, the operation of RRAM, through applying voltage/current pulses, induces a resistance change in the device system. In addition, the RRAM device can be repeatedly switched between high and low resistance states. Unlike PCM, however, in which the resistance change is achieved by modification of the crystal structure of the resistive layer, the operation of RRAM generally involves electrochemical processes together with the physical migration of metal cations or oxygen anions.

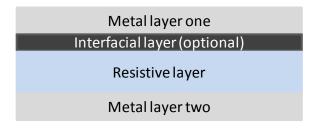

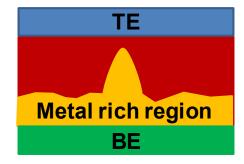

Figure 1.13. basic structure of RRAM

Fig. 1.13 shows the typical structure of a RRAM device. Generally, the structure is simple and consists of several layers. Two of them are top electrode and bottom electrode with a resistive layer sandwiched in between. And there is another optional interfacial layer which sometimes is used to improve the RRAM device performance. It is worthy to note that the basic structure is very similar to that of a PCM cell. One major difference between them is that in RRAM, the additional heater structure is eliminated. This greatly simplifies the fabrication process flow. As will be discussed later, even though there is no heater structure, RRAM is much more power efficient when compared with PCM.

#### 1.3.2 Classification of RRAM Devices

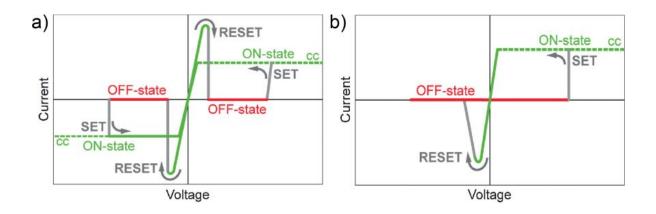

Figure 1.14. Two operation schemes for RRAM (a) unipolar device (b) bipolar device [25]

There are many ways to classify the various kinds of RRAM devices. Two approaches are particularly important and will be discussed here. The first approach is to classify RRAM devices based on the symmetry of I-V characteristics during the SET and RESET operation as shown in Fig. 1.14 [25]. Fig. 1.14 (a) illustrates one type of RRAM device, in which both the SET and RESET operation can be achieved by applying either positive or negative voltage. In other words, there is no polarity dependence of the device I-V characteristics. This type of device is called a unipolar device. It is worthwhile to point out that for such device, a current compliance (CC) has to be applied during the SET operation to avoid excessive heat generation and thus protect the filaments created as part of the SET process. On the other hand, in the RESET process, no CC is applied and a large current is intentionally generated to break the conductive filament and switch the device back to a high resistance state. Thus, for unipolar devices, the RESET current is generally larger than the SET current. Fig. 1.14(b) demonstrates the other type of RRAM devices where a stable SET operation is only possible when a positive voltage is applied across the device. On the other hand, the voltage needed for the RESET operation is always opposite to that used in the SET process. In this particular example, the RESET is only achievable when the voltage is negative. This type of device operation mode is called bipolar. As will be discussed in the following sections, the RESET current in bipolar devices is much less than that of unipolar

devices, and thus it is more power efficient. The current mainstream technology of RRAMs is based on the bipolar type of devices.

Next, based on the operation principle and device physics, RRAMs can be classified into two types of devices. One is metal cation based electrochemical metallization (ECM) RRAM. The other type is oxygen vacancies based (VO) RRAM. For ECM RRAM, metal cation generally is much more diffusive than oxygen anion or it easily precipitates such that in the on state, a conductive metallic bridge is formed. On the other hand, for VO based RRAM, oxygen anion have a significant role which is much more diffusive than metal cation. And the nature of the conductive filament in the on state is attributed to the traps formed by the VOs.

In the following sections, the ECM RRAM will be discussed first and then a description of VO based RRAM is presented. Finally, as will be shown, there are no fundamentally physical differences between those two type devices. Ergo, a unified theory can exist.

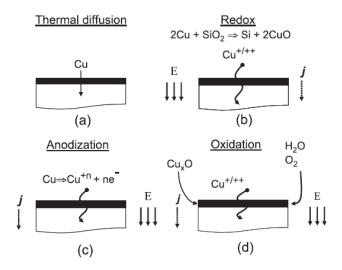

#### 1.3.3: Introduction to Electrochemical Metallization RRAM

## 1.3.3.1 I-V Characteristics and Switching Mechanisms for Three Types of ECM RRAM

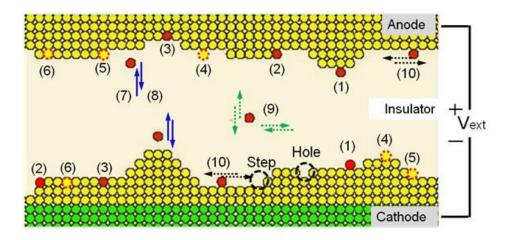

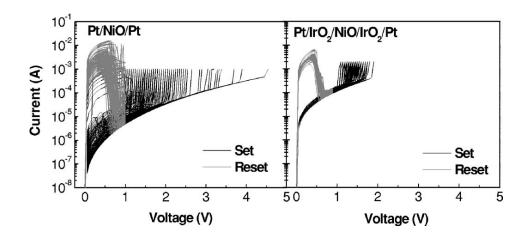

By definition, the operation of ECM based RRAMs typically involves the diffusion and redox electrochemical reaction of metal cations. In the on state, a metallic-like conductive filament is formed which brings the device from a high resistance state (HRS) to a low resistance state (LRS). Lots of materials have been explored for RRAM applications and even for ECM based RRAM, and thus, the material choice for each layer is not limited. Depending on origin of the metal cations, ECM RRAM can be further classified into three groups. In the first group, the metal cations are supplied only from the electrode. For examples, for system like  $Cu/SiO_2/Pt$  [26] and  $Cu/Ta_2O_5/Pt$  [27], Cu cations are from the Cu electrode. For the second group, the cations are supplied purely from the resistive layer. For example, for system like Pt/NiO/Pt [28], the Pt/NiO/Pt [28], the

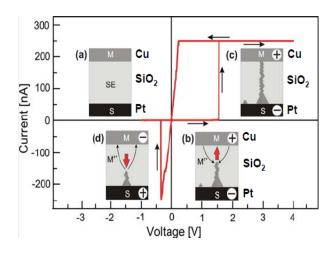

#### 1.3.3.1.1 I-V Characteristics of Cu/SiO2/Pt

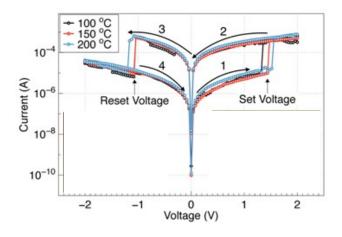

Fig. 1.15 shows the I-V characteristics of Cu/SiO2/Pt [26]. The system starts from the initial state (a). After a positive voltage ramp is applied on the Cu electrode, Cu atoms on the Cu electrode start to get oxidized and become Cu<sup>+</sup>/Cu<sup>2+</sup> ions. Those cations, under the applied electric field, subsequently diffuse through the SiO<sub>2</sub> layer and get accumulated on the Pt electrode where the crystallization process occurs. This process continues until a narrow Cu filament eventually is formed. At the moment when the filament shorts the top and bottom electrode as shown (b), a significant current flows through the device and the device goes from HRS to LRS. As can be seen, generally a current compliance (CC) is imposed in this process to avoid too much current flowing through the device. Excessive current will generate significant joule heating which can damage the metallic filament. Opposite to the SET process, in the

RESET process a negative voltage is applied on the Cu electrode. Therefore, the Cu filament gets oxidized and starts to dissolve. The oxidized  $Cu^+/Cu^{2+}$  from the filament migrates back to the Cu electrode and gets precipitated there. As long as the filament no longer connects the top electrode, there is a sharp decrease in the current as shown in (d) and the device goes from LRS to HRS. In addition, it is noted that in this particular case the I-V shows bipolar characteristics, where the SET voltage ( $V_{SET}$ ) is positive whereas the RESET voltage ( $V_{RESET}$ ) is negative. Further, it is shown that the RESET current ( $I_{RESET}$ ) is more or less same as the SET current ( $I_{SET}$ ), i.e., around 250nA. As will be discussed later, as a general experimental observation,  $I_{RESET} \approx I_{SET}$  is valid for most bipolar devices regardless of their chemical compositions and switching mechanisms.

Figure 1.15. I-V characteristics of Cu/SiO2/Pt [26]

There are two major advantages of bipolar devices. First of all, since  $V_{\text{SET}}$  and  $V_{\text{RESET}}$  have different polarity, there is a larger margin between them and therefore the device reliability is typically significantly improved. Second, as mentioned above, the RESET process in bipolar devices is a combinational effect of both chemical and thermal processes, and therefore the  $I_{\text{RESET}}$  is reduced which in turn minimizes the device power consumption.

#### 1.3.3.1.2 I-V Characteristics of Pt/NiO/Pt

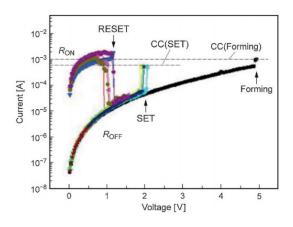

Fig. 1.16 shows the I-V characteristics of a Pt/NiO/Pt device [28], which belongs to the second type of ECM devices in that the metal cations all comes from the NiO layer. In this example, inert Pt is used for both top and bottom electrodes. When electrons are injected into the NiO resistive layer by applying a voltage across the two electrodes, Ni cations can capture the electrons and thereby reduce to a metallic state. The resulting small metallic precipitate will enhance local electric field distribution and more and more precipitates will be formed; eventually a metallic filament is created which shorts both top and bottom electrodes. Therefore, the device switches from HRS to a low resistance state LRS. This process is called a forming process as indicated inside Fig. 1.16 (a). The forming process is the first cycle of the

device operation in which the device is driven to LRS from its pristine HRS state. The voltage at which the device goes to LRS is called the forming voltage ( $V_{Form}$ ). For Pt/NiO/Pt, the RESET process is done mainly by thermal joule heating effect (with the help of chemical oxidation). In this operation, there is no CC limit applied on the device, and therefore a large current can flow through the metallic filament. A large current in turn can generate large heat flow which can melt the filament and make the device go to HRS again.

Figure 1.16. I-V characteristic of a Pt/NiO/Pt stack [28]

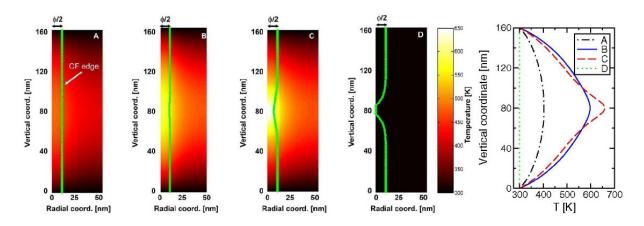

Russo [30] gives a detailed description of the RESET process as shown in Fig. 1.17. First of all, due to the poor thermal conductivity of the dielectric layer, the middle part of the Ni metallic filament is more likely to have higher temperature when a current is flowing. Therefore, it has a larger dissolution rate which in turn makes the filament thinner and resistance higher. The change of resistance modifies the distribution of voltage and current and a positive feedback loop is formed. The filament will eventually break and cause a sharp transition in the RESET stage. In addition, it is interesting to note that the voltage needed to turn on the device again in the following cycle is less the than  $V_{Form}$ . The reason is that unlike the first forming cycle, in the following cycles only part of filament is broken and therefore a smaller voltage is enough to turn on the device. Thus, as a general rule the  $V_{SET}$  typically is less than  $V_{Form}$  for all RRAM cells.

Figure 1.17. The metallic Ni filament dissolution process by joule heating in Pt/NiO/Pt stack [30].

# 1.3.3.1.3 I-V Characteristics of Ag/Ag<sub>2</sub>Se/Pt

Figure 1.18. I-V characteristic Ag/Ag₂Se/Pt stack [29]

Finally, Fig. 1.18 shows I-V characteristics of an Ag/Ag<sub>2</sub>Se/Pt stack, which belongs to the third group of ECM RRAMs, where the metal cation can be supplied both from the Ag electrode and from the Ag<sub>2</sub>Se resistive layer. Such systems also include Ag/Ag<sub>2</sub>S/Pt [31] and Ag/Ag<sub>33</sub>Ge<sub>20</sub>Se<sub>47</sub>/Ni [32]. As can be seen, the I-V characteristic of Ag/Ag<sub>2</sub>Se/Pt is almost identical to that of the aforementioned Cu/SiO<sub>2</sub>/Pt stack. Both show bipolar switching characteristics. This is expected, since all the physical and chemical processes involved in the Ag/Ag<sub>2</sub>Se/Pt stack are almost identical to the processes involved in the Cu/SiO<sub>2</sub>/Pt stack. The only difference is that Ag<sub>2</sub>Se can supply the Ag<sup>+</sup> ions that participate in the metallization process, whereas SiO<sub>2</sub> only serves as an ionic transportation medium for metal cations. Because of this Ag<sub>2</sub>Se has a very large ionic conductivity and this causes a voltage distribution which is different from SiO<sub>2</sub> devices. This will be discussed more in details in section 1.3.3.3.

#### 1.3.3.2 Comparisons Between Unipolar and Bipolar Switching Modes

As already been shown in the previous section, ECM devices can have both unipolar and bipolar operational modes. Generally, bipolar devices have two advantages over unipolar devices. The first one is that bipolar devices are more power efficient. During the RESET process, because of the combination of the thermal and electrochemical effects in bipolar devices, less  $I_{RESET}$  is needed whereas only a thermal effect is involved for unipolar devices, necessitating a larger  $I_{RESET}$ . Second, because the  $V_{SET}$  and  $V_{RESET}$  in bipolar devices have different polarity, bipolar devices have larger voltage margin, which makes their operation more reliable.

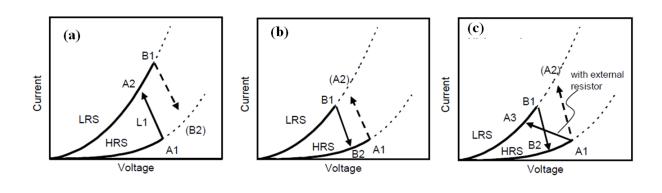

In addition, for unipolar devices, the SET-RESET competition [33] has to be avoided as shown in Fig. 1.19 [33], whereas no such problems present for bipolar devices. The SET-RESET competition is a phenomenon where either the SET or RESET processes are not stable. For example, if the SET process is not stable, once the device is driven to the SET stage it can automatically go to the RESET stage. The SET-RESET competition can be avoided by connecting a lager series resistor in the SET stage, whereas a smaller resistor is connected in the RESET operation. The details are shown in Fig. 1. 19 and are discussed below.

Figure 1.19. Several switching modes in unipolar RRAM (a) stable SET (b) stable RESET (c) both stable SET and RESET [33]

Fig 1.19(a) shows a situation where an identical series resistor (or no external resistor) is connected to a unipolar device in both SET and RESET stage. Its resistance is small and can be viewed as system parasitic resistance. Starting from the HRS, the device switches to LRS at point A; after that, due to the voltage drop on the parasitic resistance, the voltage on the resistive layer reduce to A2. In order to RESET the device, a larger voltage and current has to be applied and at point B1 the device switches back to HRS and stays at position B2. However, voltage at B2 is larger than SET voltage A1, and thus, the SET-RESET competition occurs. The device most likely will not stay at HRS but will switch back to LRS. This corresponds to the unstable RESET. A similar situation can occur in the SET stage as well, as shown in Fig. 1.19(b) where the RESET

process is stable and the SET stage is not stable. For a reliable operation, both SET and RESET have to be stable. The only way to achieve this goal is to connect a large series resistor (equivalent to a lower CC) during the SET stage operation and a small resistor (equivalent to a larger CC) in the RESET stage operation as shown in Fig 1.19(c). In this mode, after RESET, the voltage across the device is less than  $V_{\text{SET}}$  (as indicated by point B2 and A1) such that the RESET is stable. On the other hand, after the SET operation, the voltage across the device is less than  $V_{\text{RESET}}$  (as shown by point B1) and therefore accidental RESET is also prevented so that the SET operation is also stable. Even though adopting a smaller series resistor for RESET can stabilize the unipolar device operation, it makes the device operation more complicated.

In summary, because of the power, voltage margin and the SET-RESET competition issue, the current main technology of RRAM is based on bipolar devices.

## 1.3.3.3 Voltage distribution inside ECM devices

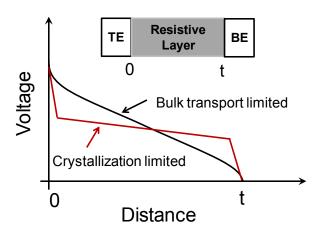

In the above discussion, it is shown that in the  $Cu/SiO_2/Pt$  stack, the  $SiO_2$  just serves as a transportation layer for oxidized anode ions passing through from the anode to the cathode [34]. However, for the  $Ag/Ag_2Se/Pt$  stack,  $Ag_2Se$  itself consists of a large number of Ag cations that can participate in the crystallization process. They can then get replenished from the Ag electrode. In this case, the  $Ag_2Se$  layer serves as an electrolyte that has large ionic conductivity. Due to the ionic conductivity difference, the voltage distribution in  $Ag/Ag_2Se/Pt$  can be significantly different from the voltage distribution in a  $Cu/SiO_2/Pt$  stack. For  $Cu/SiO_2/Pt$ , it is possible that most of the applied voltage is dropped across the  $SiO_2$  layer, whereas only a very small voltage is dropped across the  $Ag_2Se/Pt$  stack.

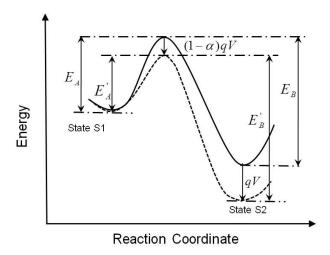

In fact, depending on the conductivity of the dielectric layer and the ability of the metal cations to precipitate, the voltage distribution across the resistive layer can be classified into bulk transport limited and crystallization limited operating regimes as shown in Fig. 1.20. In the bulk transport limited regime, most of the voltage drops across the dielectric (system like Cu/SiO<sub>2</sub>/Pt). Thus, for this type of system, it is almost impossible to get the resistive switching effect when the device thickness significantly increases (for example in the micron range). On the other hand, for systems like Ag/Ag<sub>2</sub>S/Pt, most of the voltage drops across the electrode and dielectric interface where the electron charge transfer process occurs, and only a very small portion of voltage drops across the resistive layer. For such systems, metallic formation can be directly observed even when the dielectric becomes extremely thick (for example beyond the millimeter range).

Figure 1.20. The voltage distribution across the resistive layer in bulk transport limited and crystallization limited cases

## 1.3.3: Introduction to Oxygen Vacancies Based RRAM

For ECM based RRAMs, metal cation has an important role in the formation of conductive bridge. On the other hand, when metal cations are less diffusive or very difficult to precipitate, O<sup>2-</sup> anions may have the dominant effects on device performance. Unlike ECM based RRAM, the physics of VO based devices are quite complicated and there are still lots of unknowns. Despite the vagueness, several basic mechanisms and theories still exist which can at least explain part of the device behaviors.

#### 1.3.3.1: The Switching Mechanisms and Models for Oxygen Vacancies Based RRAM

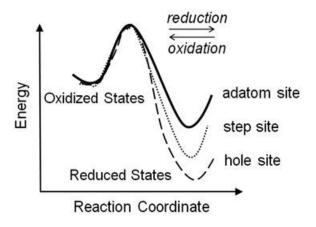

For VO based RRAMs, VO has an important impact on the conductive bridge formation process inside the memory cell. In these systems, VO is typically more diffusive than metal cations. In addition, the SET and RESET operations typically involve VO generation and annihilation. When the VO concentration is large, the cell has low resistance. On the other hand, when the VO concentration is low, the cell resistance increases. Thus, the key to understand VO based RRAMs is to understand how the VO affects the conductivity of the memory cell and how the VO concentration can be modulated by applied voltage.

For low and moderate bandgap materials like  $TiO_2$  and  $Ta_2O_5$ , VO typically acts as an n-type dopant [35]. Thus, when the VO concentration increases, the electron concentration also increases. On the other hand, for large bandgap materials like  $HfO_2$  and  $ZrO_2$ , VO typically acts as traps. In this case, electron hopping conduction becomes important. In the following sections both conduction mechanisms are discussed.

# 1.3.3.1.1: Oxygen Vacancies Act as Dopants

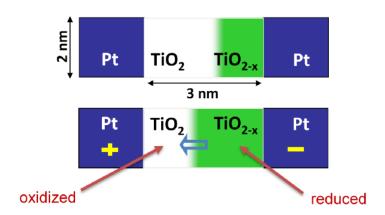

Figure 1.21. switch mechanism of Pt/TiO<sub>2</sub>/Pt cell [2]

Figure 1.22. The VO distribution and the band diagram for Pt/TiO<sub>2</sub>/Pt system [25]

$TiO_2$  is one of the most commonly studied materials for VO based RRAMs. Fig. 1.21 shows the evolution of the chemical composition inside the  $TiO_2$  layer when a voltage is applied on a  $Pt/TiO_2/Pt$  stack [2]. Fig. 1.22 shows the distribution of VO and the band diagram for such a system. As can be seen, when a positive voltage is applied on the left side at the Pt electrode,  $O^{2-}$  ions migrate towards the left under the electric field, as indicated by the arrow and leave the VOs behind. Hence  $TiO_2$  becomes  $TiO_{2-x}$  (green region in Fig. 1.21). Since VOs are n-type dopants for materials having moderate bandgap such as  $TiO_2$  [35], the increase of VO

concentration can make the dielectric more electronically conductive. This is demonstrated in Fig.1.22. As shown when the VO concentration increases, the energy difference between the Fermi level and the conduction band decreases, which indicates an increase in the electron concentration. For this reason, the region containing  $TiO_{2-x}$  is also called a virtual electrode. As this process continues, the width of the tunneling barrier formed between the left Pt electrode and the virtual electrode decreases. When the tunnel barrier becomes thin enough; there will be a significant current flowing through the device. As a result, the device switches from HRS to LRS.

During the RESET process, a negative voltage is applied on the left electrode which pushes  $O^{2-}$  ions back into the  $TiO_x$  film and subsequently recombines them with VOs. Thus, the VO concentration decreases at the interface between the left Pt electrode and the  $TiO_x$  layer. Therefore, the width of the tunneling barrier increases, which leads to a significant increase in the cell resistance.

## 1.3.3.1.2: Oxygen Vacancies act as traps

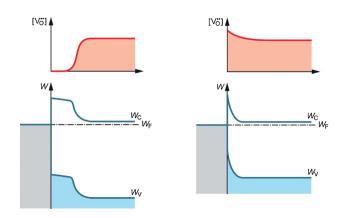

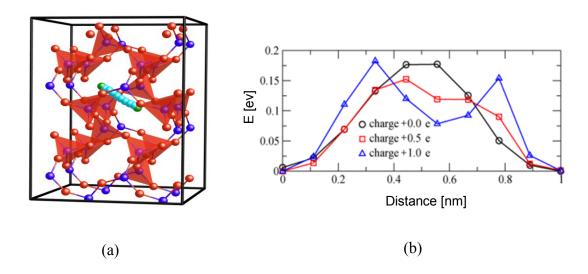

The above theory works well for a dielectric with moderate bandgap. However, for large bandgap dielectric material such like HfO<sub>2</sub> and ZrO<sub>2</sub>, VO doesn't act as a dopant but rather behaviors like trap. In this case other theories are developed [36, 37]. One of the frequently used models is so called Ion-Transport-Recombination model [37] shown in Fig. 1.23.

Figure.1.23. (Left) Illustration of electron transport in LRS and HRS (right) illustration of electron occupation probability at different VO sites in HRS [37].

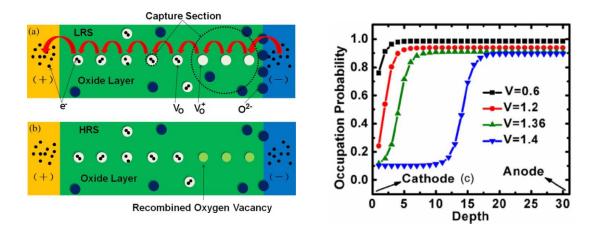

In this model, the LRS is represented by the percolation through a series of VOs denoted by the white circles in the left figure. The conduction current is due to the electron hopping through those VO sites. In addition, during the forming and SET process a positive voltage is applied on the electrode (shown in blue) which causes a large amount of O<sup>2-</sup> anions to flow

towards the electrode and subsequently get adsorbed there. During the RESET process, the electron occupation probability will significantly decrease at the anode side assuming that the electron hopping rate between VO sites are much faster than the hopping rate between VO and electrode. As a result, the VO carries net positive charge which can then combine with the O<sup>2-</sup> ions released from the cathode (shown in blue). Therefore, the original dielectric structure is restored and a gap is created between the filament and electrode which leads a significant current reduction. As a result, the device switches from LRS to HRS.

This model is simple yet very effective in explaining certain phenomena. The key process in this model involves the flow  $O^{2^-}$  ions in and out from the blue colored electrode such that the electrode can temporarily store the  $O^{2^-}$  during SET process yet release the  $O^{2^-}$  in the RESET process. In the other words, the electrode serves as an oxygen reservoir. In reality, both Ti and TiN are good  $O^{2^-}$  reservoirs [38, 39].

Figure 1.24. The I-V characteristics of a Ti/HfO<sub>2</sub>/TiN stack [40]

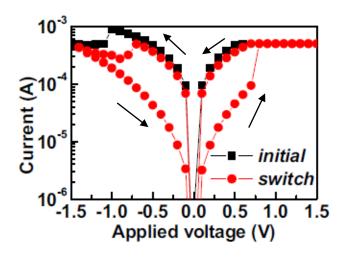

As an example, Fig. 1.24 [40] shows the I-V characteristics of a Ti/HfO<sub>2</sub>/TiN stack. During the measurement, the TiN electrode is always grounded. When a positive voltage is applied on the Ti electrode, O<sup>2-</sup> ions migrate towards the Ti electrode and get adsorbed there, leaving the VO behind. The VO concentration inside the HfO<sub>2</sub> continues to increase as the voltage increases until a percolation threshold reaches. At around 0.7V there is a sharp increase of current and at this moment, the device is turned on. In the RESET process, a negative voltage is applied on the Ti electrode. Due to the combined effects of joule heating and the presence of the electric field, the adsorbed O<sup>2-</sup> ions on the Ti electrode start to diffuse back into HfO<sub>2</sub> layer, where they recombine with VOs. Therefore, the trap density inside the HfO<sub>2</sub> decreases. The current gradually decreases and the device switches from LRS to HRS again. It is worthwhile to note that in this case, the device shows bipolar switching characteristics and in addition, the RESET process is a gradual process, which means the conductance of the cell decreases slowly as the

V<sub>RESET</sub> increases. This is quite different from the ECM cells, which RESET rapidly. This gradual RESET process has important impacts on the multilevel-programming capability of the device as will be discussed in the following chapters.

#### 1.3.3.2: The Atomic Filament Structure of VO Based RRAMs

In the above discussion, the essence of resistive switching is attributed to the modulation of the O<sup>2-</sup> flow inside the oxide. This picture gives an effective way to describe the overall behavior of the device. However, in reality the migration of O<sup>2-</sup> typically triggers a phase transition inside the metal oxide such that a transition between an insulating phase and a more conductive phase usually occurs. The model described above is oversimplified and cannot describe the real physical processes happening inside the metal oxide in a mesoscopic scale.

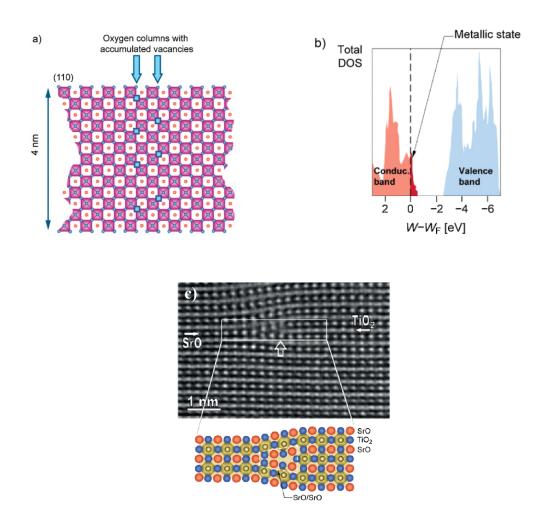

Figure 1.25. (a) The VO accumulation along lines in SrTiO3 [25] [41] (b) Calculated density of states close to the defect region [18] (c) Illustration of lattice structure close to the core of edge dislocations in SrTiO3[25] [42].

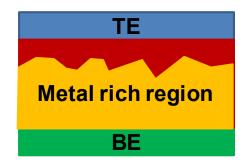

As stated above, VOs typically act as n-type dopants in a moderate bandgap metal oxide. As the VO concentration exceeds the equilibrium value, point defects start to interact with each other and form extended defects such as vacancy chains [25]. They can also get accumulated at the cores of edge or screw dislocations [25]. Regardless of the detailed structures of those extended defects, one of the common features is that at the region close to the extended defects a metal rich region is formed and metal cations get reduced. At the same time the band gap shrinks and the Fermi level increases, which lead to an increase of the local electronic conductivity.

Fig. 1.25 illustrates several possible crystal extended defects. In Fig. 1.25 (a) [25, 41] VOs are accumulated along lines in a confined region. Through first principles simulation, it is found that along this defect region, the electrons around Ti ions get delocalized, resulting in a local insulator to metal transition [25]. Fig. 1.25 (c) shows another possibility that VOs are trapped in the core of the edge dislocation in  $SrTiO_3$  [25, 42]. In addition, researchers [43] found that compared with the bulk region, VOs can have a dramatic increase of diffusivity along those dislocations. As a result, those dislocations can act as fast transport paths for  $O^{2-}$  anions [25] and can form a percolation path which shorts two electrodes to create a LRS inside RRAM cell.

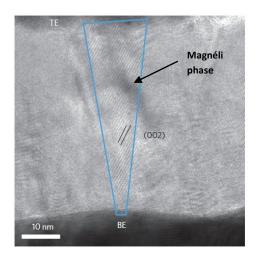

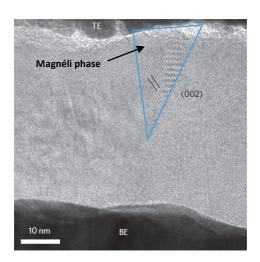

Besides the extended defects, it is reasonable to believe that as VO concentration further increases, with the help of the joule heating during the forming or SET processes, metal oxides can transfer to other more conductive and metal rich phases or suboxides. Researchers [44] have found that  $Ti_4O_7$  is formed in LRS inside the  $TiO_2$  layer for a Pt/TiO2/Pt RRAM cell as shown in Fig. 1.26, by using high resolution TEM. The transition between LRS and HRS is attributed to the creation and rupture of this conductive phase. The observed diameter of those filaments is around 5nm to 10nm. Similarly, in the SET stage, a more conductive  $TaO_2$  phase is observed for RRAMs based on  $Ta_2O_5$  [45].

Figure 1.26. TEM image of Magnéli phase after the forming process inside of Pt/TiO<sub>2</sub>/Pt cell (Left) and a discontinued Magnéli phase (Right) [44]

## 1.3.4: The Equivalence Between ECM and VO Based RRAM

Even though in the above sections, RRAM devices are intentionally classified into metal cations based ECM and VO based devices, there are really no essential differences between them. Rather, they are two different ways to describe the same physical and chemical processes inside the metal oxide cells:

- In the SET stage, this is a locally increasing metal element concentration and at same time reducing metal cations process such that metal rich region (or suboxide) can be formed.

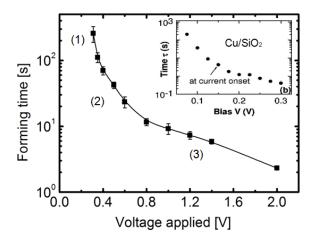

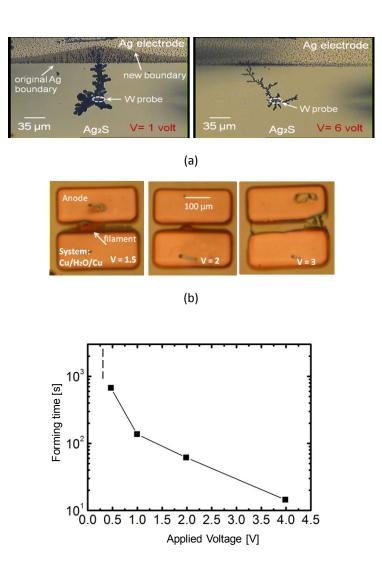

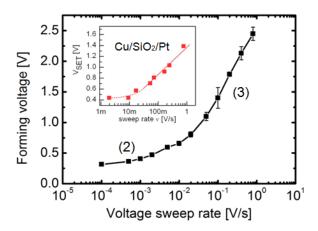

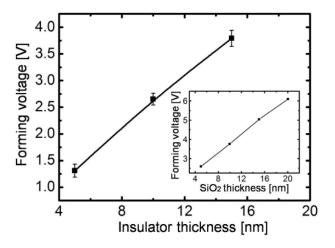

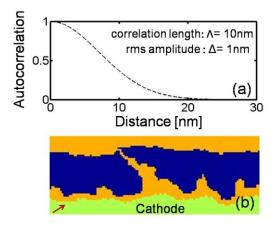

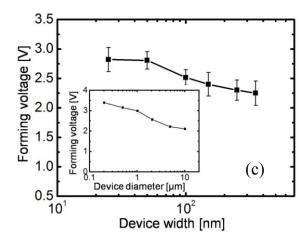

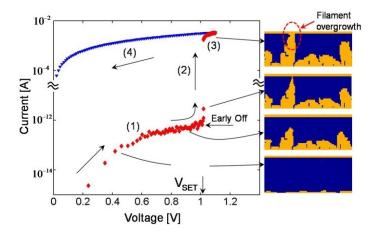

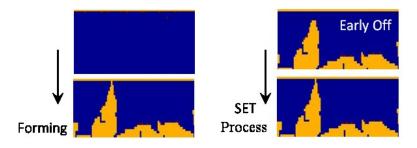

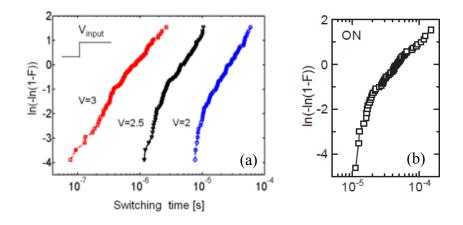

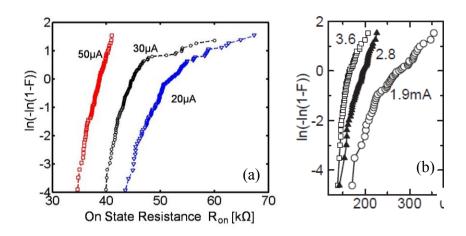

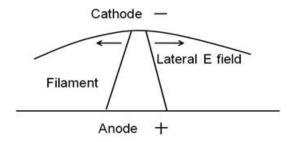

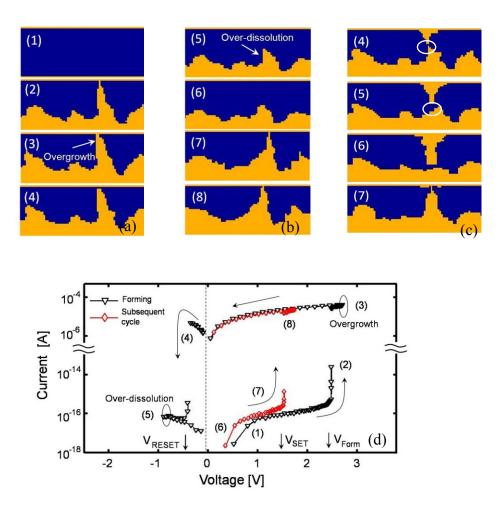

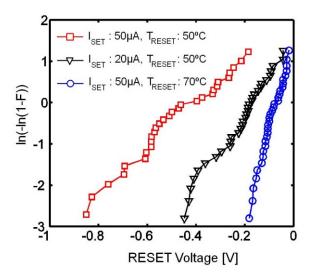

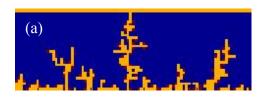

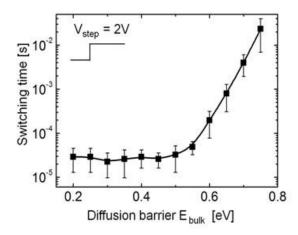

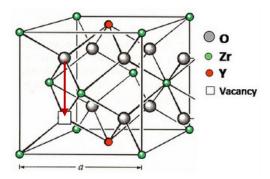

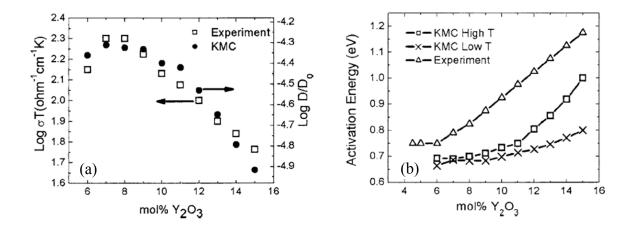

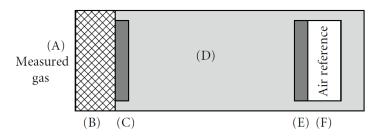

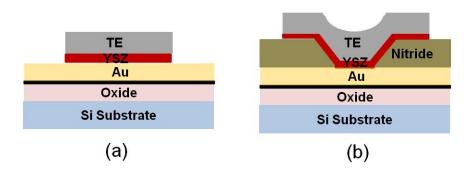

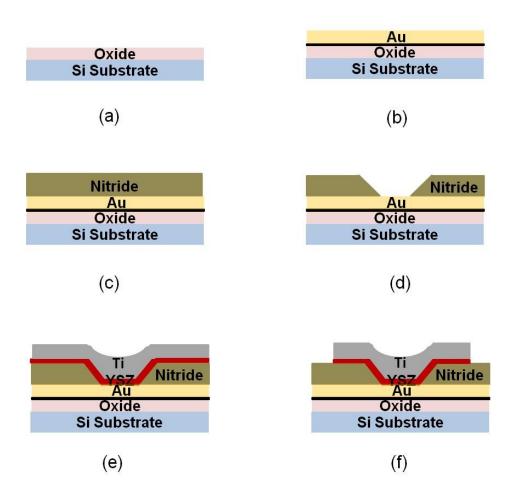

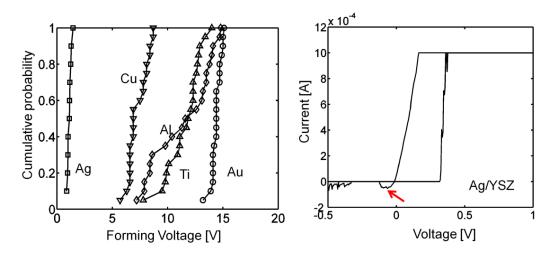

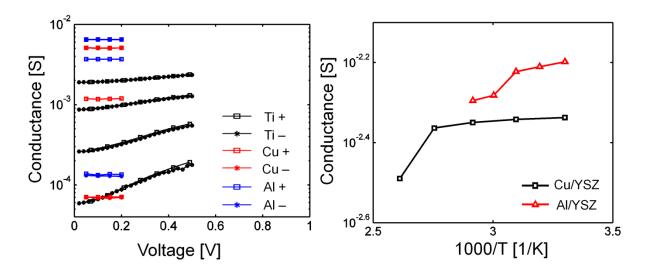

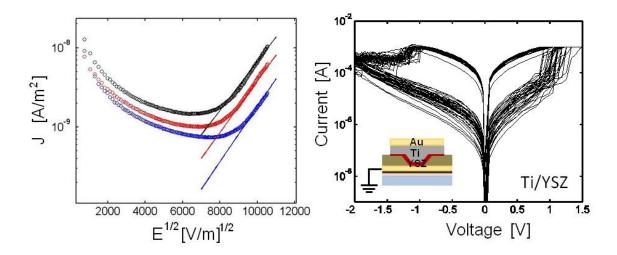

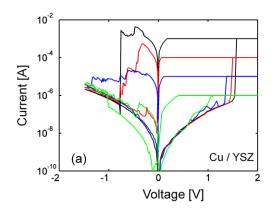

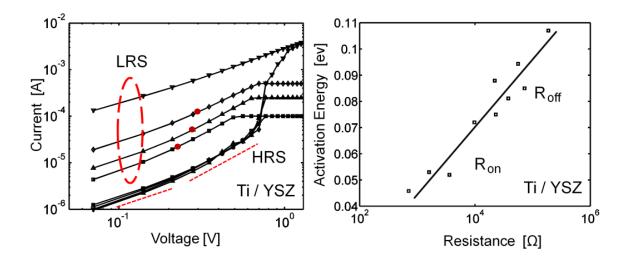

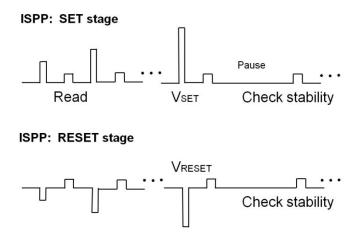

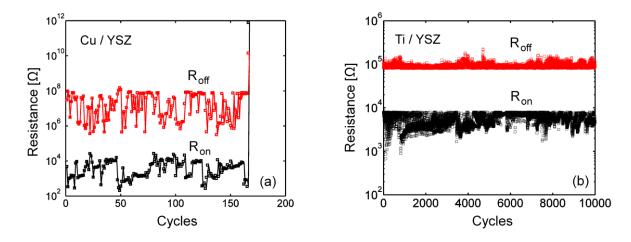

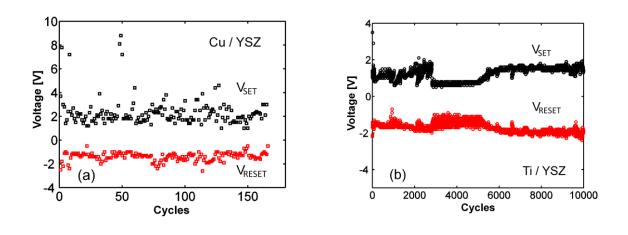

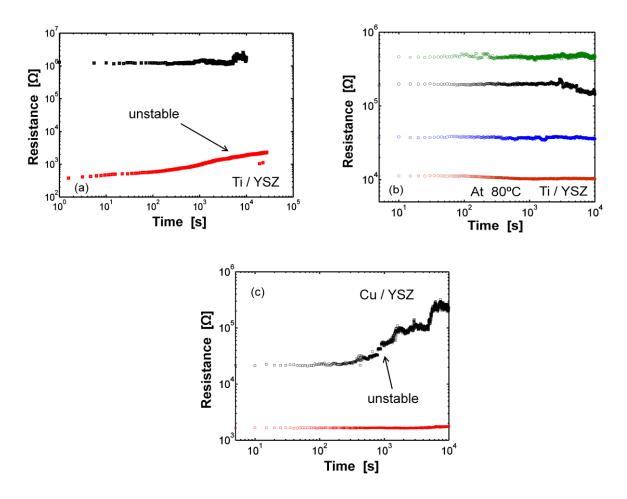

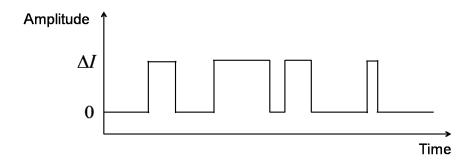

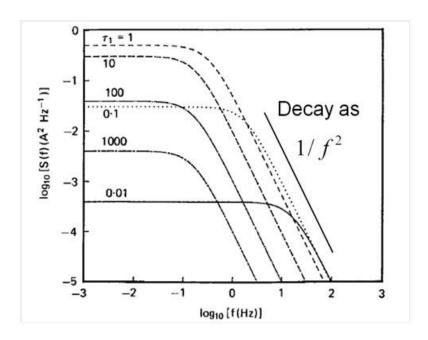

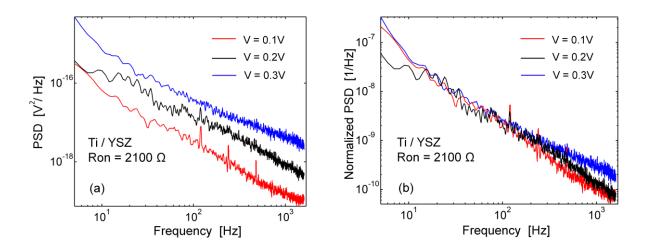

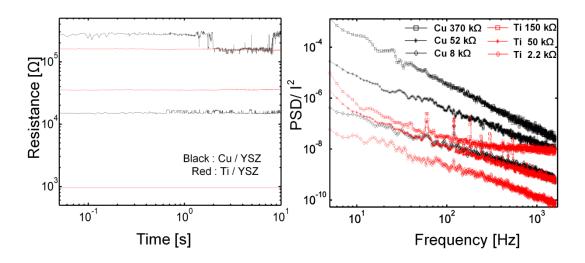

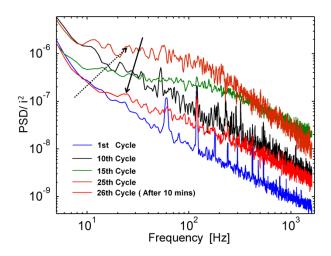

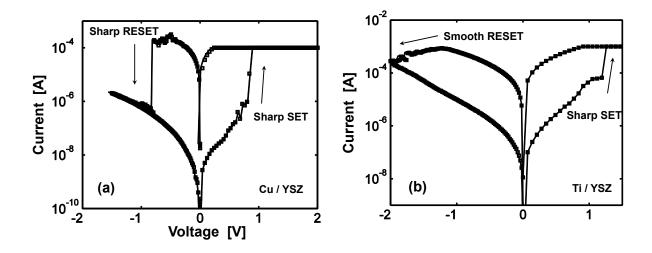

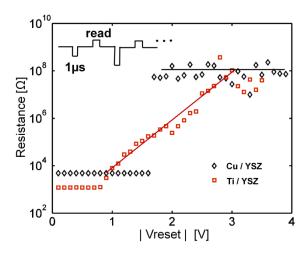

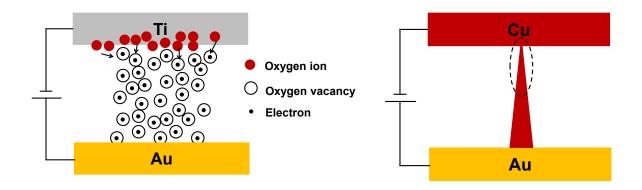

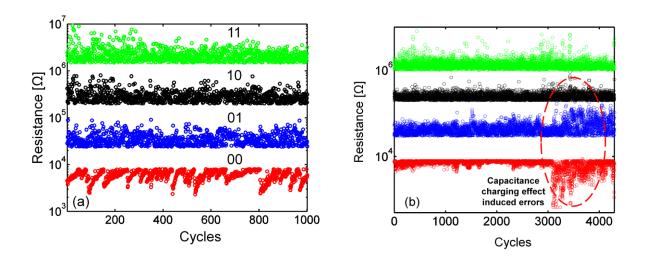

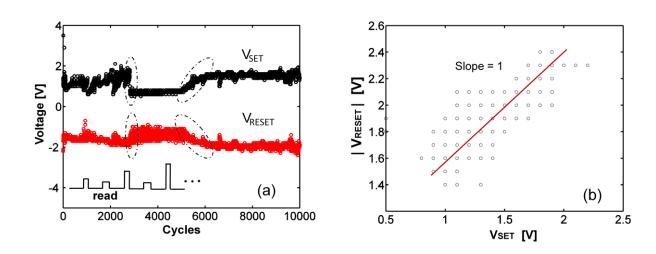

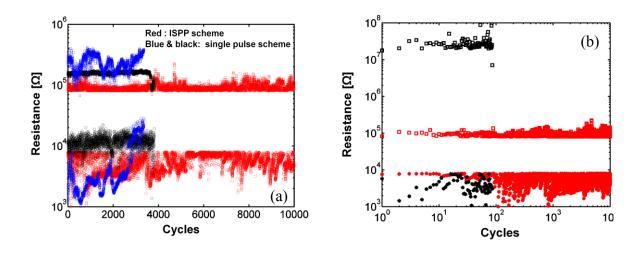

- In the RESET stage, this is a locally decreasing metal element concentration and oxidizing the metallic species or cations such that more insulating oxide can be formed locally.