# Nanomaterials processing toward large-scale flexible/stretchable electronics

Toshitake Takahashi

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-144 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-144.html

August 13, 2013

Copyright © 2013, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Nanomaterials processing toward large-scale flexible/stretchable electronics

by

#### Toshitake Takahashi

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Ali Javey, Chair Professor Tsu-Jae King Liu Professor Liwei Lin

Fall 2013

# Nanomaterials processing toward large-scale flexible/stretchable electronics

Copyright 2013 by Toshitake Takahashi

#### Abstract

## Nanomaterials processing toward large-scale flexible/stretchable electronics

by

#### Toshitake Takahashi

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali Javey, Chair

In recent years, there has been tremendous progress in large-scale mechanically flexible electronics, where electrical components are fabricated on non-crystalline substrates such as plastics and glass. These devices are currently serving as the basis for various applications such as flat-panel displays, smart cards, and wearable electronics.

In this thesis, a promising approach using chemically synthesized nanomaterials is explored to overcome various obstacles current technology faces in this field. Here, we use chemically synthesized semiconducting nanowires (NWs) including group IV (Si, Ge), III-V (InAs) and II-IV (CdS, CdSe) NWs, and semiconductor-enriched SWNTs (99 % purity), and developed reliable, controllable, and more importantly uniform assembly methods on 4-inch wafer-scale flexible substrates in the form of either parallel NW arrays or SWNT random networks, which act as the active components in thin film transistors (TFTs).

Thusly obtained TFTs composed of nanomaterials show respectable electrical and optical properties such as 1) cut-off frequency,  $f_t \sim 1$  GHz and maximum frequency of oscillation,  $f_{max} \sim 1.8$  GHz from InAs parallel NW array TFTs with channel length of  $\sim 1.5$  µm, 2) photodetectors covering visible wavelengths (500-700 nm) using compositionally graded CdS<sub>x</sub>Se<sub>1-x</sub> (0 < x < 1) parallel NW arrays, and 3) carrier mobility of  $\sim 20$  cm<sup>2</sup>/Vs, which is an order of magnitude larger than conventional TFT materials such as a-Si and organic semiconductors, without sacrificing current on/off ratio ( $I_{on}/I_{off} \sim 10^4$ ) from SWNT network TFTs.

The capability to uniformly assemble nanomaterials over large-scale flexible substrates enables us to use them for more sophisticated applications. Artificial electronic skin (e-skin) is demonstrated by laminating pressure sensitive rubber on top of nanomaterial-based active matrix backplanes. Furthermore, an x-ray imaging device is also achieved by combining organic photodiodes with this backplane technology.

| To my family and everyone else whom I've had the privilege of running into from birth to present day. |

|-------------------------------------------------------------------------------------------------------|

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

### Acknowledgement

Throughout my graduate life, I have truly enjoyed working with many wonderful people. This PhD thesis cannot be completed without any single help from those people.

First of all, I would like to acknowledge my advisor, Professor Ali Javey, for accepting me in his laboratory five years ago, sharing his continuous enthusiastic passion to science and technology, and being a great mentor throughout my PhD life. I have had a truly invaluable experience working in his group, especially his lab's dynamic and fast-moving early days. These experiences have made me feel prepared for the next phase of my career.

I also would like to thank Professor Tsu-Jae King Liu, Professor Ronald Fearing, and Professor Liwei Lin for being on my Qualification and Dissertation committees and providing me valuable feedback to improve my research.

None of my work detailed in this thesis cannot be completed by myself. Special acknowledgement needs to be given to flexible subgroup members in Javey's group, Prof. Zhiyong Fan, Prof. Kuniharu Takei, Prof. Hyunhyub Ko, Prof. Johnny Ho, Dr. Chuan Wang for their guidance, their insights and stimulating discussions. I was also fortunate to have many opportunities to work with many collaborators outside the group. I would like to give a special thanks to Professor Ali M. Niknejad, Dr. Ehsan Adabi, Prof. Amin Arbabian for the help in InAs RF project, to Professor Ming C. Wu, Dr. Arash Jamshidi for the help in CdSSe phtodetector project, and to Professor Ronald Fearing, Mr. Andrew Gillies for stretchable SWNT e-skin project. I also want to thank past and current members of Javey's group who have helped me to learn all the skills I have: Prof. Yu-Lun Chueh, Dr. Alexandra Ford, Dr. Zachery Jacobson, Prof. Paul Leu, Prof. Morten Madsen, Prof. Cary Pint, Prof. Min Hyung Lee, Prof. Junghyo Nah, Prof. Ha Sul Kim, Dr. Zhibin Yu, Dr. Daisuke Kiriya, Dr. Corsin Battaglia, Dr. Yuping Zeng, Dr. Chien I Kuo, Dr. Yongjing Lin, Mr. Rehan Kapadia, Mr. Onur Ergen, Mr. Hui Fang, Mr. Xiaobo Zhang, Mr. Steven Chuang, Mr. Daniel Ruebusch, Mr. Maxwell Zheng, Mr. Peter Lobaccaro, Mr. Kevin Chen, Mr. Thomas Rembert, Mr. Mahmut Tosun, Mr. Hank Wang, Mr. Jerry Chang, Mr. Hiroshi Shiraki, Mr. Mark Hettick, Mr. Shuai Xu, Mr. Pak Heng Lau, Mr. Jingsan Xu, Mr. Xingian Yin, Mr. Justin Zhang, Ms. Junjun Zhang, Ms. Haleh Razavi, Mr. Jae Won Do, Ms. Aimee Moriwaki, Mr. Ali Rathore. Among them, I would like to especially thank Dr. Kiriya and Dr. Yu for their mental and physical support outside the group.

Finally, I have to acknowledge the constant support of my family throughout my PhD life. They have always encouraged me to push forward with my work and maintain confidence especially when the research stuck.

Toshitake Takahashi Berkeley, California May, 2013

## **Table of Contents**

| Acknowledg   | gements                              |                                                           | ii       |  |  |

|--------------|--------------------------------------|-----------------------------------------------------------|----------|--|--|

| Table of Co  | ntents                               |                                                           | iv       |  |  |

| List of Figu | res                                  |                                                           | vi       |  |  |

| List of Tabl | es                                   |                                                           | xiii     |  |  |

| Chapter 1    | Intro                                | duction                                                   | 1        |  |  |

| 1.1          | Introduction to flexible electronics |                                                           |          |  |  |

| 1.2          | Mater                                | Materials system used as TFT active components            |          |  |  |

|              | a)                                   | Organic materials                                         |          |  |  |

|              | b)                                   | a-Si/poly-Si                                              |          |  |  |

|              | c)                                   | Oxide semiconductor/ layer transferred semiconductor      |          |  |  |

|              | d)                                   | Semiconductor nanowires (NWs)                             |          |  |  |

|              | e)                                   | Single-walled carbon nanotubes (SWNTs)                    |          |  |  |

| 1.3          | Manu                                 | Manufacturing processing                                  |          |  |  |

|              | a)                                   | Printing technique                                        |          |  |  |

|              | b)                                   | Lithographic technique                                    |          |  |  |

| 1.4          | Overv                                | Overview of this thesis                                   |          |  |  |

| 1.5          | References                           |                                                           |          |  |  |

| Chapter 2    | Scala                                | ble and low-temperature assembly process for nanomate     | rials 10 |  |  |

| 2.1          | Large-scale assembly of NWs          |                                                           |          |  |  |

|              | 2.1.1                                | Introduction                                              |          |  |  |

|              | 2.1.2                                | NWs contact printing methodology                          |          |  |  |

|              | 2.1.3                                | Monolayer resist patterned contact printing               |          |  |  |

| 2.2          | Large                                | Large-scale assembly of single-walled carbon nanotubes    |          |  |  |

|              | 2.2.1                                | Introduction                                              |          |  |  |

|              | 2.2.2                                | Solution-based process using high purity semiconducting S | SWNTs    |  |  |

| 2.3          | Summary                              |                                                           |          |  |  |

| 2.4          | References                           |                                                           |          |  |  |

| Chapter 3                  | Assembled semiconductor NWs device component                                                   | 29 |

|----------------------------|------------------------------------------------------------------------------------------------|----|

| 3.1                        | Introduction                                                                                   |    |

| 3.2                        | Parallel Array InAs Nanowire Transistors for Mechanically Bendable,                            |    |

|                            | Ultrahigh Frequency Electronics                                                                |    |

| 3.3                        | Compositionally graded CdS <sub>x</sub> Se <sub>1-x</sub> nanowire parallel arrays for tunable |    |

|                            | photodetectors                                                                                 |    |

| 3.4                        | Summary                                                                                        |    |

| 3.5                        | References                                                                                     |    |

|                            |                                                                                                |    |

| Chapter 4                  | System integration on large-scale flexible substrate                                           | 49 |

| 4.1                        | Introduction                                                                                   |    |

| 4.2                        | Large-scale Carbon Nanotube Active Matrix Circuitry for Conformal                              |    |

|                            | Electronics and Sensors                                                                        |    |

| 4.3                        | Light Interactive Electronic Skin for Visible Photon and X-ray Imaging                         |    |

| Chapter 5                  | Summary and Future Work                                                                        | 72 |

| 5.1                        | Summary                                                                                        |    |

| 5.2                        | Contribution of this work                                                                      |    |

| 5.3                        | Future directions                                                                              |    |

| Appendix A: printing" (2.1 | Supporting information of "monolayer resist for patterned contact 1.3)                         | 75 |

| Appendix B: frequency de   | Supporting information of "InAs nanowire parallel arrays radio vices" (3.3)                    | 78 |

| Appendix C:                | Supporting information of "Artificial electronic skin (E-skin)" (4.2)                          | 86 |

## **List of Figures**

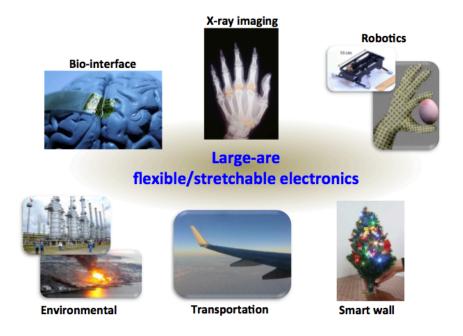

- **Figure 1-1.** Envisioned applications enabled by large-scale mechanically flexible/stretchable electronics.

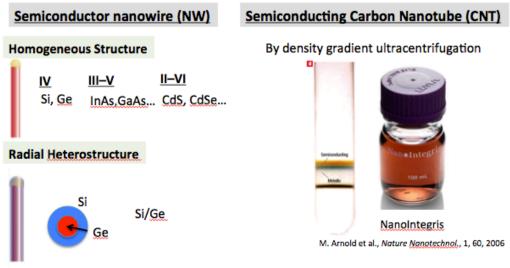

- **Figure 1-2.** (left) various types of nanowires grown by Vapour-liquid-solid (VLS) method, (right) Commercially available semiconductor enriched single-walled carbon nanotube solutions (from NanoIntegris).

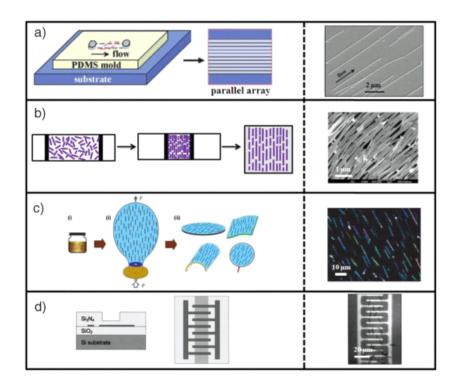

- **Figure 2-1.** Nanowire-assembly techniques (image from reference 1). (a) Schematic and the result of flow-assisted NW-assembly method, (b) Schematic of LB NW assembly method, (c) Schematic of blown-bubble NW assembly method, (d) Schematic (left) and optical image (right) of electric field alignment of NWs.

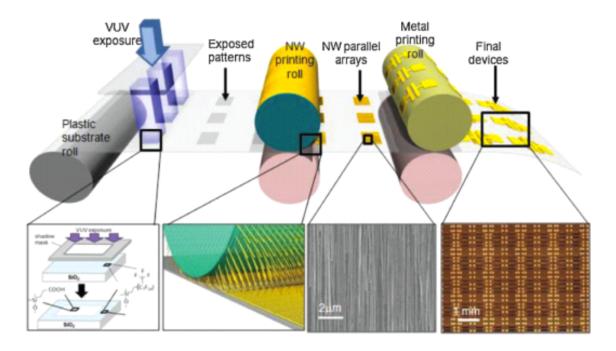

- **Figure 2-2.** Schematic of an envisioned roll-to-roll printing set-up for NW electronics and sensors fabrication. The process involves fluorinated monolayer patterning of the receiver substrate to define "sticky" and "non-sticky" regions for the subsequent patterned transfer and assembly of NWs by contact printing. Following the printing of NW active components, devices are fabricated by defining the source/drain and gate electrodes.

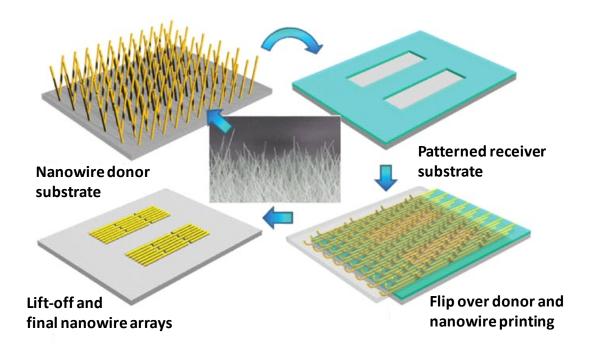

- **Figure 2-3.** Schematic of NW contact printing process. The SEM image in the inset shows the grown Ge NWs are randomly oriented on the growth substrate. The NWs are then aligned and transferred to the receiver substrate by application of a directional shear force, resulting in the printing of sub-monolayer NW parallel arrays on the receiver substrate.

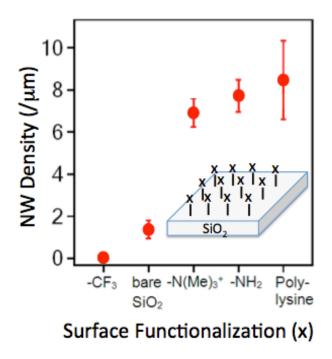

- **Figure 2-4.** The density control of printed Ge NW by contact printing through the surface modification of Si substrate. Bare  $SiO_2$  corresponds to the untreated  $SiO_2$  surface, while CF3 [(heptadecafluoro-1,1,2,2-tetrahydrodecyl) dimethylchlorosilane), -N(Me)3 (Ntrimethoxysilylpropyl-N,N,N-trimethylammonium chloride], and -NH2 (3 triethoxysilylpropylamine) correspond to the surface-modified functional groups. Note that, as expected, poly(L-lysine) functionalization results in a larger standard deviation due to the less uniform coverage of the surface by the polymeric thin film, as compared to the molecular monolayers.

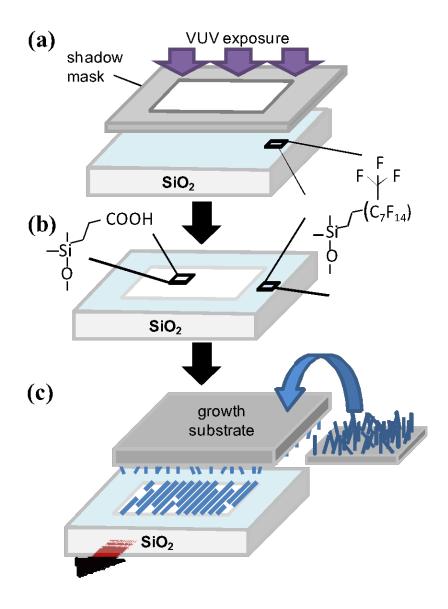

- **Figure 2-5**. Schematic of the patterned contact printing process with monolayer resist. (a) Patterning of fluorinated  $SiO_2$  surface is carried out by VUV irradiation in the presence of  $O_2$ . (b) C-F bonds in the exposed regions are cleaved and replaced with -COOH or -CHO functional groups. (c) Contact printing results in the aligned transfer of NWs on the VUV exposed regions.

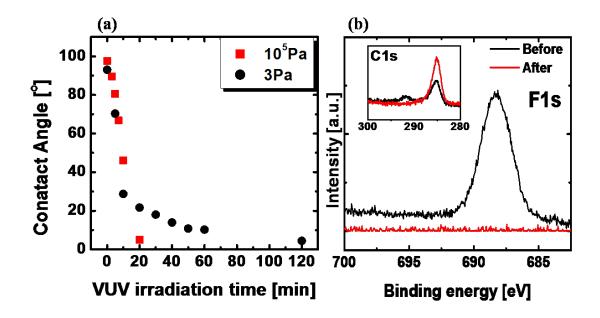

- **Figure 2-6.** (a) Water contact angle as a function of VUV irradiation time. Irradiation is carried out at  $10^5$  Pa and 3 Pa, corresponding to  $2 \times 10^4$  Pa and 0.6 Pa of oxygen partial

- pressure, respectively. **(b)** F1s and C1s (inset) XPS spectra of fluorinated surfaces before (black curve) and after (red curve) VUV irradiation for 30min at 10<sup>5</sup> Pa.

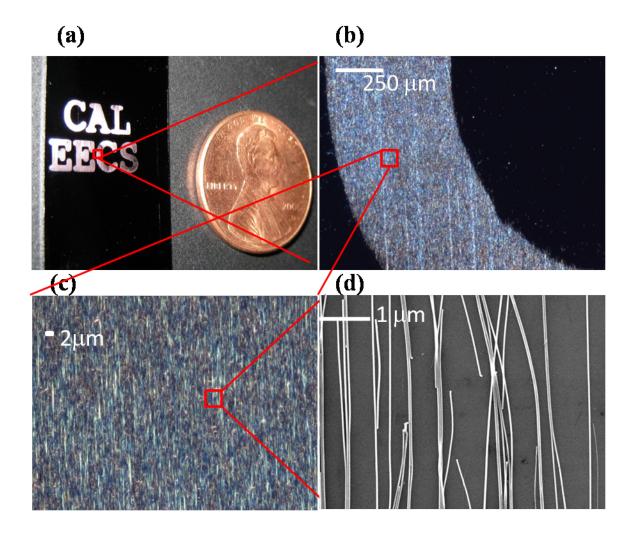

- Figure 2-7. (a), (b), (c) Optical dark field and (d) SEM images of Ge NWs ( $d \sim 30 \text{ nm}$ ) printed on the VUV patterned SAM-resist.

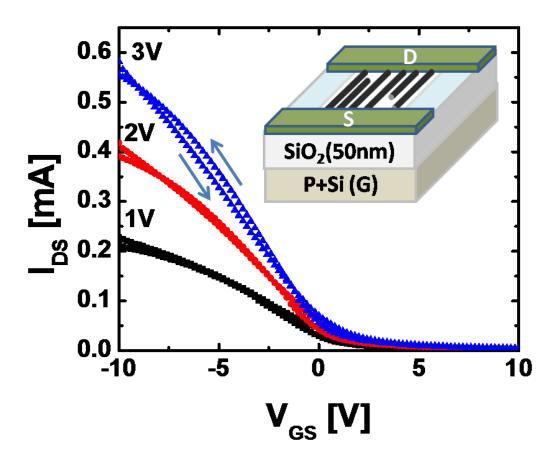

- **Figure 2-8.** Transfer characteristics of a parallel-array Si NW FET with  $W\sim200$  mm and  $L\sim3$  mm, for various values of  $V_{DS}$ .

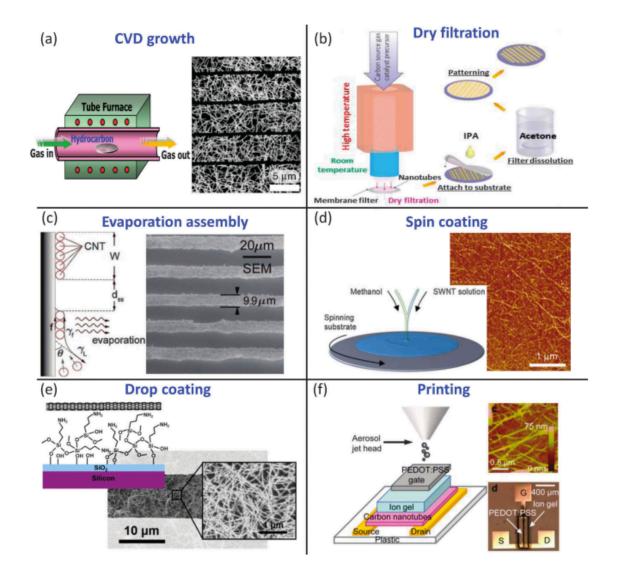

- **Figure 2-9.** Different methods used for assembly of SWNT networks. (a) CVD growth, (b) Dry filtration, (c) Evaporation assembly, (d) Spin coating, (e) Drop casting, (f) Printing.

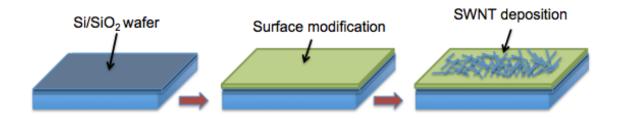

- **Figure 2-10.** Schematic of SWNT deposition process. Surface is modified with either poly-L-lysine or aminopropyltriethyoxysilane (APTES) in this study.

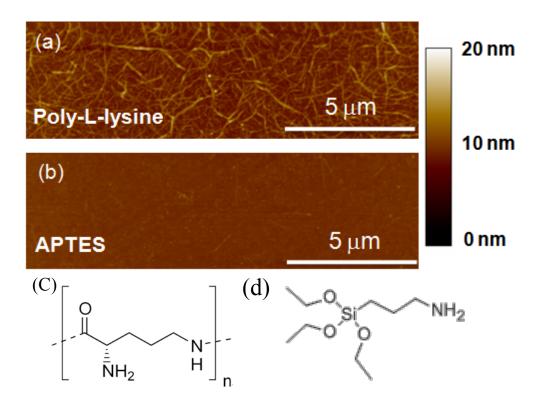

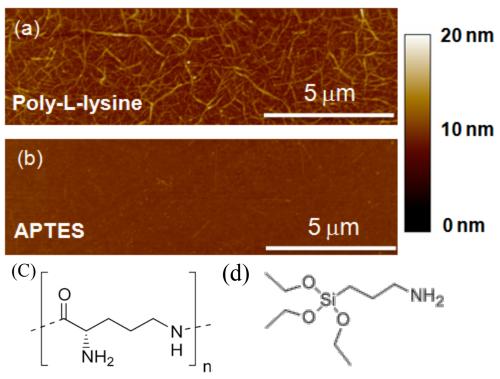

- **Figure 2-11**. The effect of surface treatment on the deposited nanotube density. The surface is treated with **(a)** poly-L-lysine for 5min and **(b)** aminopropyltriethyoxy silane (APTES) for 30min. SWNT deposition time is 20min. Chemical structure of **(c)** poly-Llysine and **(d)** APTES.

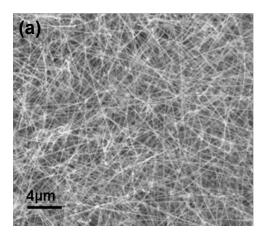

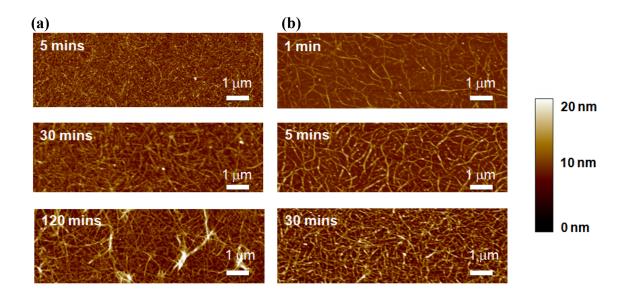

- **Figure 2-12.** AFM images taken from different SWNT deposition time on (a) evaporated  $SiO_2$  and (b) thermally grown  $SiO_2$ . For (a), 5min, 30 min, and 120 min are used, and for (b) 1 min, 5 min, and 30min are used as SWNT deposition time. The density increases as the deposition time increases, and eventually it forms nanotube bundles, degrading the device  $I_{ON}/I_{OFF}$  ratio.

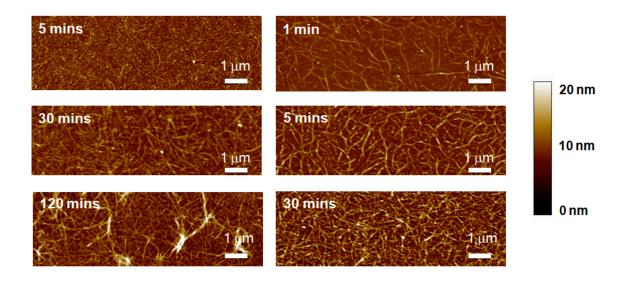

- **Figure 3-1**. The schematic and optical images of a printed InAs NW array FET fabricated on a flexible PI substrate for GHz operation. (a) The schematic illustration of the NW parallel array FET, illustrating the various layers of the device. The cross-sectional image is shown in the top. (b) A photograph image of the fabricated NW device array on a bendable PI substrate. (c) A bright-field optical image of a NW-array FET with ground-signal-ground configuration for the RF measurements. (d) A dark-field optical image, showing the printed InAs NW region.

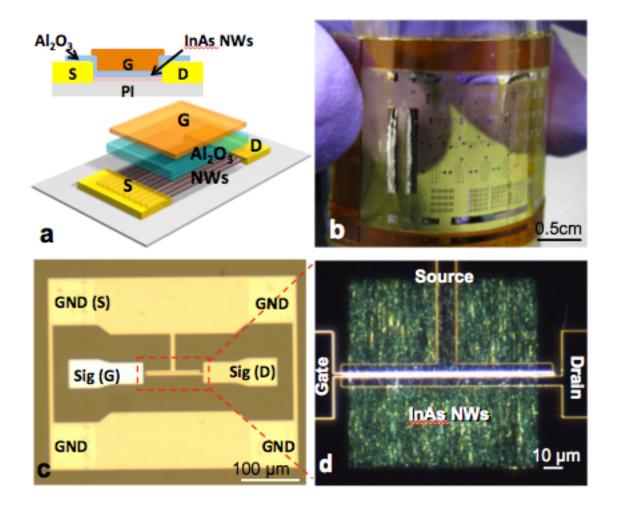

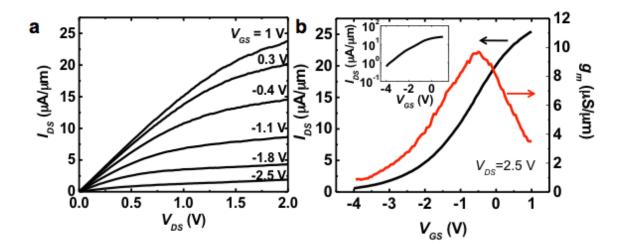

- **Figure 3-2.** DC characteristics of an InAs NW-array FET. (a) The normalized output characteristics of a NW-array FET with a channel width,  $W\sim100~\mu m$  and gate length,  $L_{\rm G}\sim1.5~\mu m$ . (b) Linear-scale transfer characteristic and the corresponding transconductance as a function of gate bias at  $V_{\rm DS}=2.5{\rm V}$ . The log-scale  $I_{\rm DS}$ - $V_{\rm GS}$  at  $V_{\rm DS}=2.5{\rm V}$  is shown in the inset.

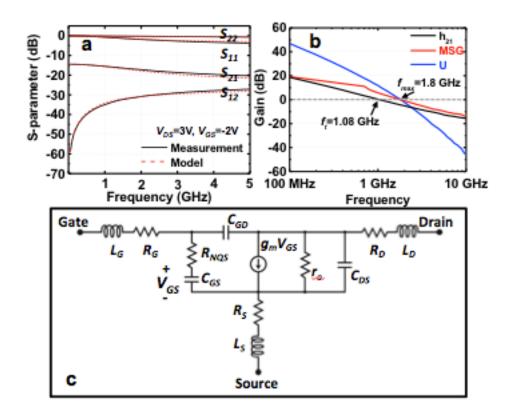

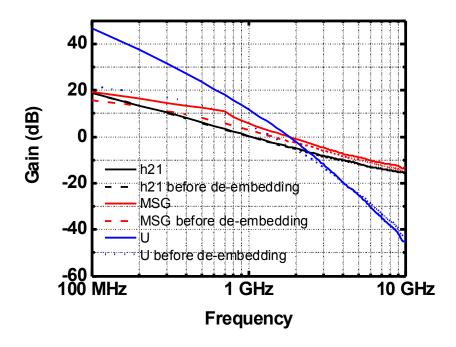

- **Figure 3-3**. RF characterization of an InAs NW-array FET. (*a*) The measured (black solid line) and modeled (red dashed line) scattering parameters,  $S_{11}$ ,  $S_{12}$ ,  $S_{21}$  and  $S_{22}$  of an InAs NW array FET with  $W\sim200~\mu m$  after de-embedding for frequencies between 40 MHz and 5 GHz. (*b*) The current gain ( $h_{21}$ ), maximum stable gain (MSG), and unilateral power gain (U) extracted from measured S-parameters as a function of frequency. The

unity current gain frequency,  $f_t$ , and unity power gain frequency,  $f_{max}$ , are ~1.08 and 1.8 GHz, respectively. (c) Small signal equivalent circuit model and (d) device schematic, illustrating the various circuit components.  $R_S$ ,  $R_D$ , and  $R_G$  are composed of metal sheet resistance and contact resistance.

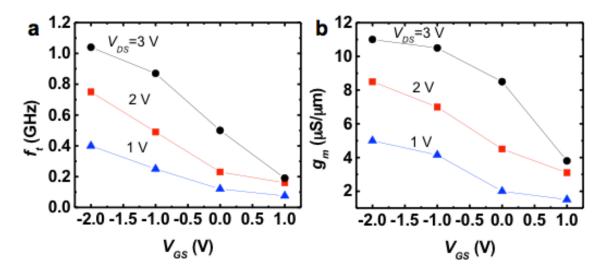

- **Figure 3-4**. Bias dependence of the RF response. (a), (b) The measured unity current gain frequency and transconductance as a function of  $V_{\rm GS}$  and  $V_{\rm DS}$  for a NW-array FET with  $W = 200~\mu \rm m$ .

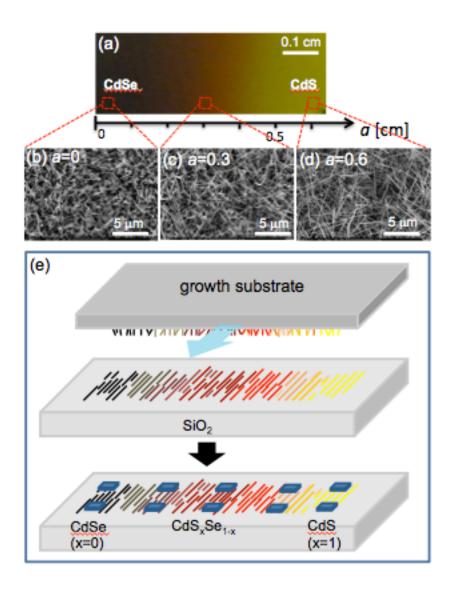

- **Figure 3-5.** Compositionally graded  $CdS_xSe_{1-x}$  NWs. (a) Real-color photograph of asgrown spatially composition-graded  $CdS_xSe_{1-x}$  NWs. SEM images taken from three different locations, (b) Se-rich, (c) middle, and (d) S-rich region. (e) Schematic of contact printing method, and final device configuration for CdS/Se-based photodetectors.

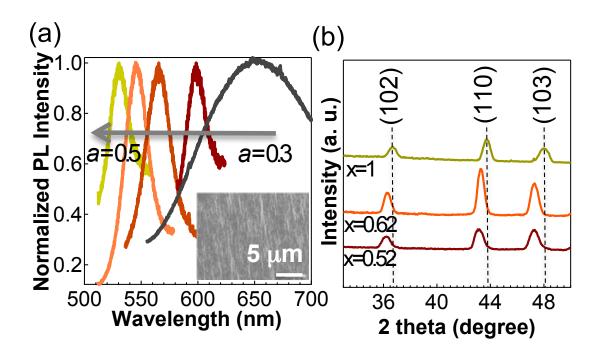

- **Figure 3-6.** (a) Micro photoluminescence spectra of contact-printed compositionally-graded NW-arrays (0.3 < a < 0.5). SEM image of printed NWs from a = 0.4 region is shown in the inset. (b) The normalized X-ray diffraction patterns (XRD) of three different printed NW regions. The dash lines correspond to (102), (110), and (103), respectively (CdS: JCPDS 41-1049).

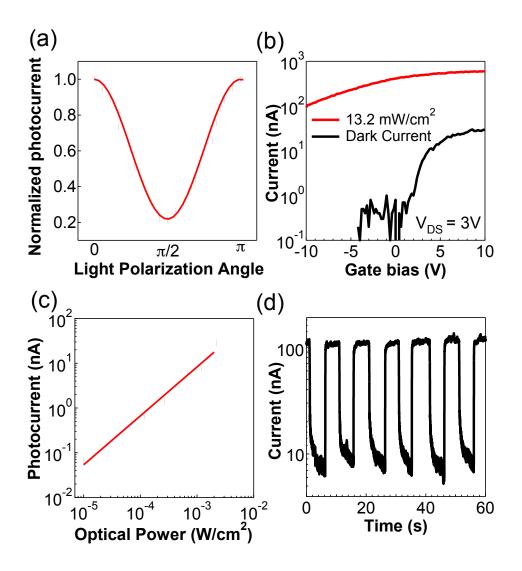

- **Figure 3-7.** (a) Normalized photocurrent of  $CdS_{0.5}Se_{0.5}$  NWs as a function of the angle of light polarization. Photocurrent is measured with  $V_{GS} = 0$  V and  $V_{DS} = 3$  V, and normalized with the current at  $\theta = 0^{\circ}$ . (b) Transfer characteristics of a  $CdS_{0.5}Se_{0.5}$  NW-array device as a function of the back-gate voltage at  $V_{DS} = 3$  V under dark (black line) and white light illumination at 13.2 mW/cm<sup>2</sup> (red line). (c) Photocurrent with  $V_{GS} = 0$  V and  $V_{DS} = 3$  V as a function of optical power intensity. (d) Time response under illumination at 2 mW/cm<sup>2</sup> with  $V_{GS} = 0$  V and  $V_{DS} = 3$  V.

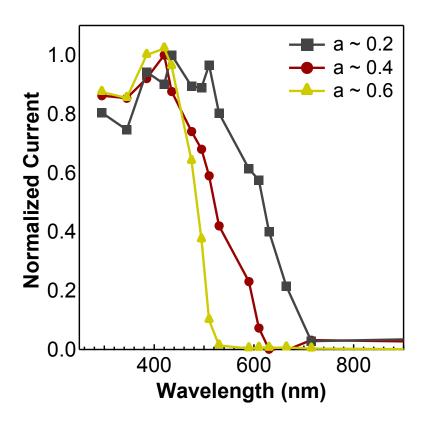

- **Figure 3-8.** Spectral response of photocurrent obtained from three different NW-array devices corresponding to S-rich, middle and Se-rich regions.

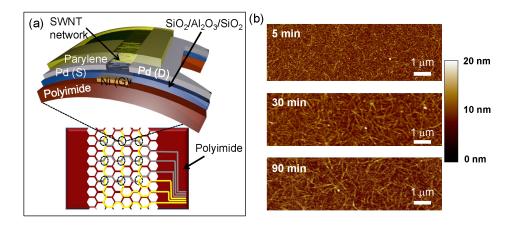

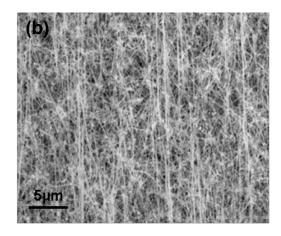

- **Figure 4-1.** Semiconductor-enriched SWNT-TFTs on flexible substrates. (a) Schematic of a mechanically flexible/stretchable active-matrix back-plane ( $6\times4$  cm<sup>2</sup> with  $12\times18$  pixel array) based on SWNT-TFTs, and an expanded schematic of a single TFT. (b) Atomic force microscopy images of SWNT networks on a PI substrate, showing that the density can be controlled by the nanotube deposition time (5, 30, and 90 min; top to bottom, respectively). Average length of nanotubes is  $\sim 0.8 \mu m$ .

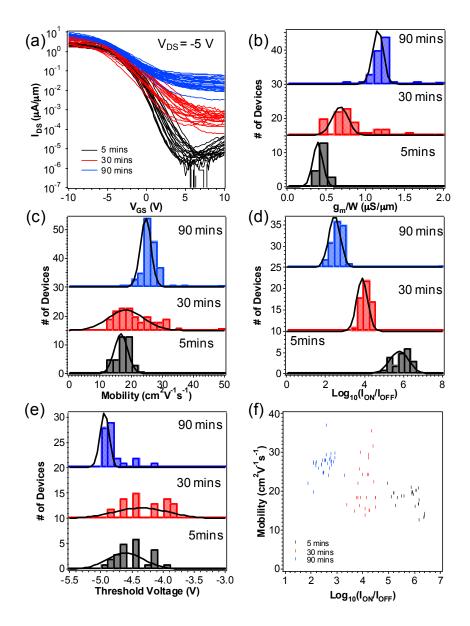

- Figure 4-2. Statistical variation of the electrical properties over a 4-inch PI substrate. (a) Transfer characteristics of SWNT-TFTs at  $V_{DS} = -5$  V for three different SWNT deposition times of 5, 30, and 90 min, corresponding to different nanotube densities. (b)-(e) Histograms of width-normalized transconductance, peak field-effect mobility, log-scale of  $I_{ON}/I_{OFF}$ , and threshold voltage for each deposition condition. In (b) and (d), the devices are measured at  $V_{DS} = -5$ V, and in (c) and (e) the devices are measured at  $V_{DS} = -5$ U mV. (d) Peak field-effective mobility as a function of  $I_{ON}/I_{OFF}$  for various measured devices. Here, the channel length is ~3 µm and width is 250 µm.

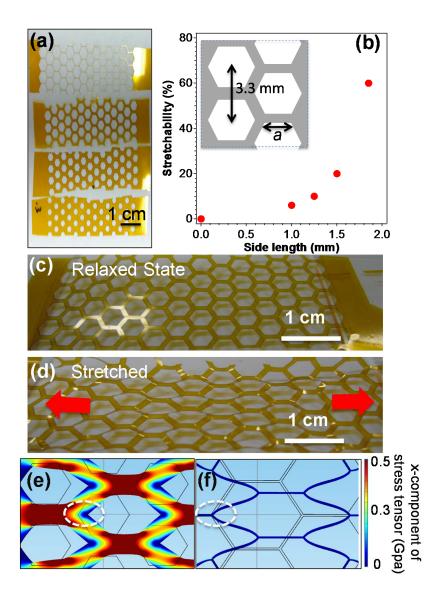

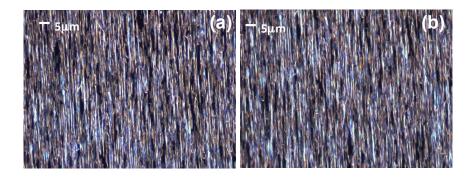

- **Figure 4-3.** Stretchable PI substrates. (a) PI mesh substrate with four different side length of hexagonal holes (a=1, 1.25, 1.5 and 1.85 mm, from bottom to top). (b) Stretchability as a function of the side length, a, of the hexagonal holes. Here, the period of holes is fixed at 3.3 mm as shown in the inset. Optical images of (c) relaxed and (d) stretched state of the PI substrate with a=1.25 mm. Mechanical simulation of (e) a=1.25 mm and (f) a=1.85 mm mesh, when the substrate is stretched by 2 mm in the horizontal direction. The location where the active devices are placed is marked with the white circle.

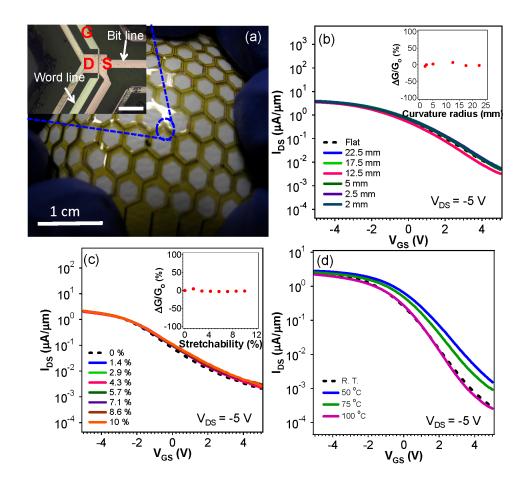

- **Figure 4-4.** Mechanical robustness of SWNT-TFTs on honeycomb patterned PI substrates. (*a*) Optical images of a stretchable device array, showing conformal coverage on a baseball. Expanded image of an active device area (corresponding to the TFT for a single pixel) is shown in the inset (scale bar is 200 μm). Channel length and width are 5 μm and 200 μm, respectively. (*b*) Transfer characteristics at  $V_{DS} = -5$  V measured at various bending radius. The inset depicts  $\Delta G/G_0$  as a function of bending radius, showing minimal performance change even when bent down to 2 mm of bending radius. (*c*) Transfer characteristic at  $V_{DS} = -5$  V as a function of stretchability. The inset shows  $\Delta G/G_0$  as a function of stretchability. (*d*) Transfer characteristics at  $V_{DS} = -5$  V as a function of temperature.

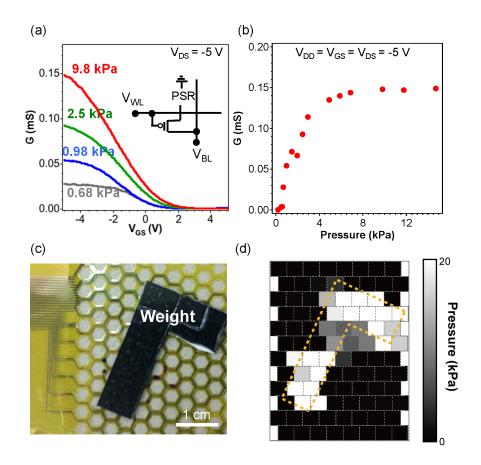

- **Figure 4-5.** Artificial electronic-skin using SWNT-TFT active matrix back-plane. (a) Transfer characteristics as a function of the normal applied pressure for a representative pixel. (b) Output conductance at  $V_{DD} = V_{GS} = V_{DS} = -5$  V as a function of the applied normal pressure. (c) Optical image of a fully fabricated electrical skin sensor. An "L"-shaped object is placed on top. (d) The two-dimensional pressure mapping obtained from the 'L'-shaped object in (c).

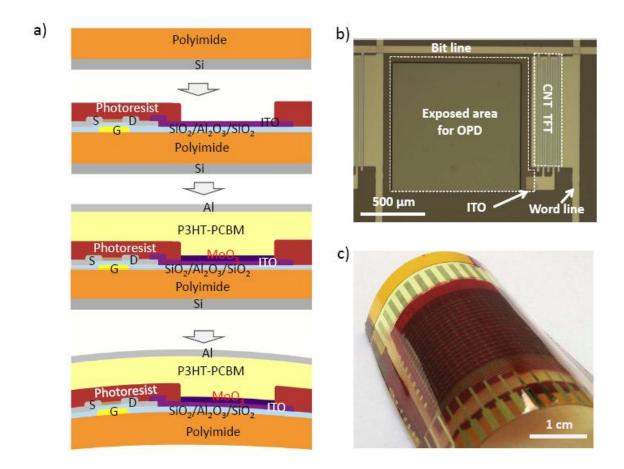

- **Figure 4-6.** Fabrication of mechanically flexible imagers. (a) Step-by-step fabrication process flow. (b) Optical image of a single pixel after the completion of the nanotube TFT process. (c) Optical image of a fully fabricated imager bent to a curvature of radius of ~5 mm.

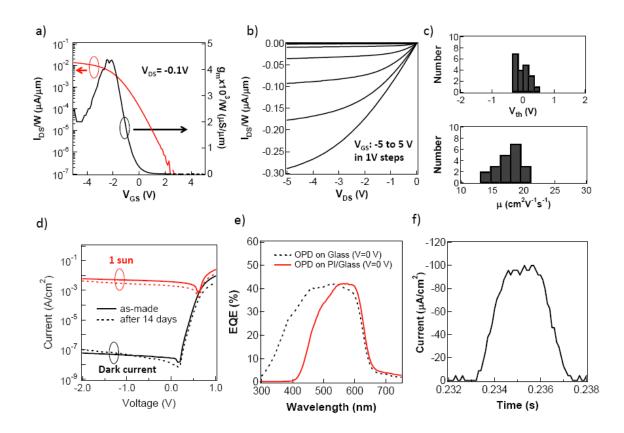

- Figure 4-7. Electrical and optical characteristics of stand-alone TFTs and OPDs. (a) Channel width normalized drain current vs. gate voltage characteristic at a drain voltage of -0.1 V. The corresponding transconductance as a function of gate voltage is also shown. Channel length and width are 30 μm and 2000 μm, respectively. (b)  $I_D$ - $V_{DS}$  characteristics for applied gate voltages of -5 V to 5V in 1V steps. (c) Histograms of mobility and threshold voltage for 20 randomly chosen TFTs across the substrate. (d) Current voltage characteristics of an organic photodiode measured under 1-sun and dark condition (solid lines). Same device is measured again after exposure to ambient atmosphere for 14 days (dashed lines). (e) External quantum efficiency between 300 nm and 750 nm for an organic photodiode on PI (red line) and glass (black dashed line) substrates. (f) Time response of the photocurrent at a reverse bias of 2V for an incident light with  $\lambda$ =535 nm and intensity of 500 μW/cm<sup>2</sup>. The light is chopped at 42 Hz.

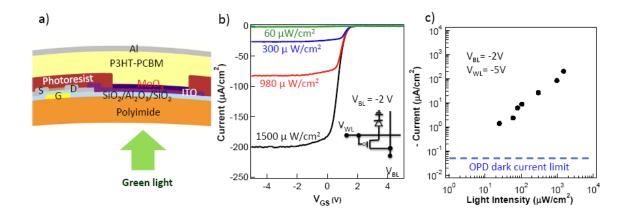

- **Figure 4-8.** Characterization of individual pixels. (a) Cross-sectional schematic of a single pixel. Light is exposed from the PI side. (b) Transfer characteristics of one pixel under various light intensities ( $\lambda$ =535 nm). The inset shows the circuit schematic of a pixel. (c) Photocurrent response of a pixel at  $V_{GS}$ =-5V and  $V_{BL}$ =-2V as a function of incident light intensity.

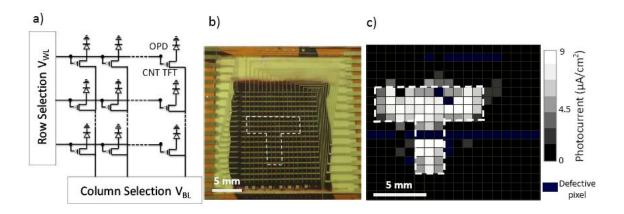

- **Figure 4-9.** Flexible visible light imagers. **(a)** Circuit schematic of the imager. **(b)** Optical photograph of a fully-fabricated imager (18 by 18 pixels). The imager is exposed to light with an intensity of  $100 \,\mu\text{W/cm}^2$  and  $\lambda$ =535 nm through a "T"-shaped shadow mask (shadow mask is not shown here). **(c)** The corresponding two-dimensional intensity profile obtained by measuring the photocurrent of the pixels. The character "T" is readily imaged by the device.

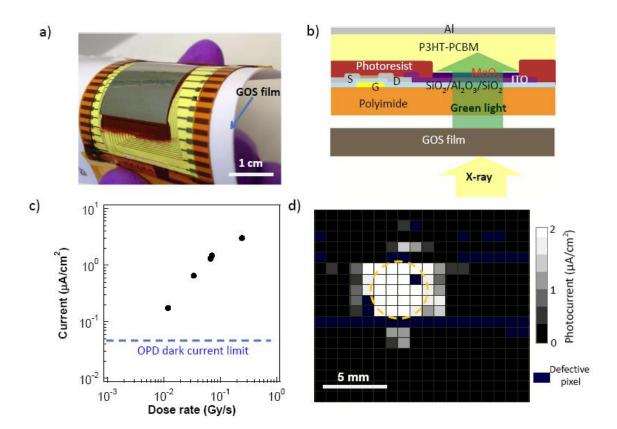

- **Figure 4-10.** Flexible X-ray imagers. (a) Optical photograph of an imager placed on top of a GOS film used for X-ray detection. (b) Cross-sectional schematic of one pixel. X-rays are irradiated onto the GOS film, and emitted green light is detected by the OPDs of each pixel. (c) Measured current from one pixel at a reverse bias of 2V as a function of X-ray dose rate. (d) Spatial mapping when a circle-shaped (diameter of 2 mm) X-ray source is projected with a dose rate of 100 mGy/s.

- **Figure A-1.** Top-view SEM images of the Ge NWs on the donor substrate (a) prior and (b) after the contact printing process.

- **Figure A-2.** Dark-field optical images of the assembled GeNW arrays (a) before and (b) after the Scotch tape test, showing no noticeable change in the density of the assembled NWs.

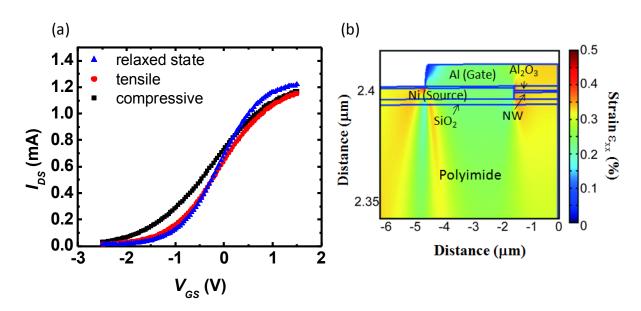

- **Figure B-1.** Mechanical bendability of NW-array FETs. (a) Transfer characteristics of an InAs NW-array FET with  $W = 200 \, \mu m$  measured at  $V_{\rm DS} = 1 \, \rm V$  as a function of the imposed bending condition. The device is first measured at the relaxed state, (bending radius,  $r = \inf(r)$ ), and under a tensile and compressive strain ( $r = 18 \, \rm mm$ ) conditions. (b) Mechanical simulation of the strain for a NW device when bent to 18 mm curvature radius. Only half of the device is shown, depicting the various layers and their strain.

- **Figure B-2**. The effect of de-embedding on the measured current gain  $(h_{21})$ , Maximum stable gain (MSG), and maximum unilateral gain (U).

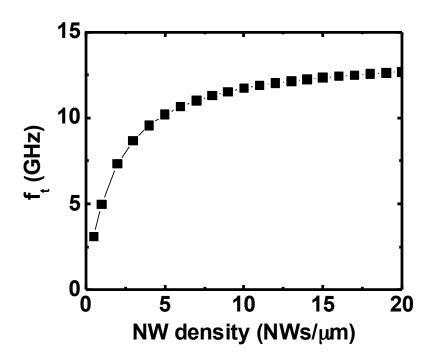

- **Figure B-3.** The calculated cutoff frequency as a function of NW density for  $Lg=1.5 \mu m$ . Note that the parasitic capacitances are assumed to be the same as the experimental devices (Table 1). The dominant effect of increase the NW density is to reduce the  $C_{p,GS}/C_{ox}$  ratio per unit width, thereby increasing the cutoff frequency.

- **Figure C-1.** The effect of surface treatment on the deposited nanotube density. The surface is treated with **(a)** poly-L-lysine for 5min and **(b)** aminopropyltriethyoxy silane (APTES) for 30min. SWNT deposition time is 20min. Chemical structure of **(c)** poly-L-lysine and **(d)** APTES.

- **Figure C-2.** AFM images taken from different SWNT deposition time on (*a*) evaporated SiO<sub>2</sub> and thermally grown SiO<sub>2</sub>. (*b*). For (*a*), 5min, 30 min, and 120 min are used, and for (*b*) 1 min, 5 min, and 30min are used as SWNT deposition time. The density increases as deposition time increases, and eventually it forms nanotube bundles, which degrade the device  $I_{ON}/I_{OFF}$  ratio.

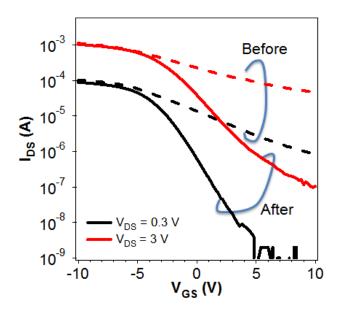

- **Figure C-3.** The effect of vacuum annealing on the device properties. Transfer characteristics of a representative SWNT-network TFT before and after vacuum annealing at 200 °C for 1h.

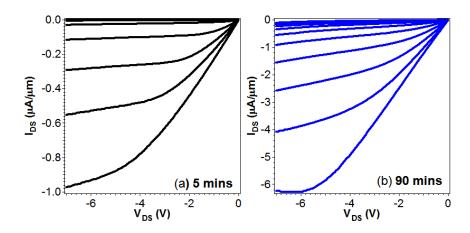

- **Figure C-4.** Output characteristics of flexible SWNT-TFTs with two different SWNT densities. CNT deposition time of (a) 5 min and (b) 90 min. Applied  $V_g$  is from -10 V to 0 V with 1 V step from bottom to top.

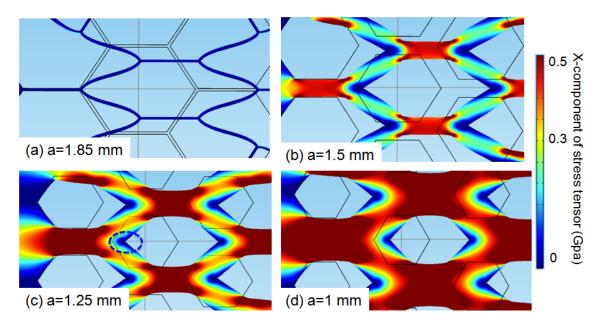

- **Figure C-5.** Mechanical simulation results for honeycomb patterned PI substrates with a side length of the hexagon holes being (a) a = 1.85 mm, (b) a = 1.5 mm, (c) a = 1.25 mm, (d) a = 1 mm. Here, the substrate is stretched by 2 mm in the x-direction.

## **List of Tables**

**Table 3-1**. The extracted and fitted parameters from small signal RF modeling for a NW-array FET with W = 200  $\mu$ m and L = 1.5  $\mu$ m.

# **Chapter 1 Introduction**

#### 1.1 Introduction to flexible electronics

Historically, the continuous miniaturization of the conventional metal-oxidesemiconductor field effect transistor (MOSFET) has been the main driving force for the current high performance microelectronics. The number of transistors in an integrated circuit doubles every two years according to Moore's law, resulting in improvements in energy efficiency and operating speed as well as dramatic reduction in the cost per transistor. On the other hand, there is another trend in the electronics industry, which deals with large amount of electronic devices spread over a large surface area on the order of meters on mechanically bendable and stretchable substrates. Figure 1-1 shows some of the envisioned applications enabled by so-called large-area flexible electronics. Owing to its mechanical flexibility as well as the large size, this sheet-type device on which various electrical/ sensor components are distributed can be used as artificial skin for robots, dynamic monitoring of mechanical fatigue in transportation systems, and even biological interfaces with the human brain as one example. The problem to realize the applications mentioned above, however, is that the cost per unit area of current silicon (Si) transistor is still too expensive, although the cost per transistor is drastically reduced by scaling. In addition, bulk Si is not mechanically robust enough to deal with mechanical bending or stretching. Therefore, alternative materials system which not only possess desirable electrical and mechanical characteristics, but also can be processed in cost effective way, need to be explored. More specifically noted, for the use as the active channel material in thin-film transistors (TFTs), we are interested in the materials which satisfy following three properties. First of all, the materials have to be compatible with a large-scale, low temperature, and cheap fabrication process. Secondly, the materials need to be robust enough against mechanical strain such as bending and stretching. Lastly, the electrical performance of the explored materials has to be superior in order to expand the limit of the applications.

**Figure 1-1.** Envisioned applications enabled by large-scale mechanically flexible/stretchable electronics.

#### 1.2 Materials system used as TFT active components

Firstly, the materials system commonly used in flexible electronics is briefly reviewed. These materials are amorphous silicon/poly-crystalline silicon, organic semiconductors, amorphous oxide semiconductors, and layer transferred semiconductor. Next, the opportunities of two kinds of nanomaterials; semiconductor nanowire and single-walled carbon nanotubes, which are the focus of this thesis, are discussed.

#### a) Amorphous silicon (a-Si)/ poly-crystalline silicon (poly-Si)

A-Si/poly-Si TFTs on rigid silicon and glass substrates have been widely used as a switching element to control the gray level in a liquid crystal display (LCD)<sup>1, 2</sup> and to drive an organic light-emitting diode (OLED)<sup>3, 4</sup>. A-Si has been also intensively explored in x-ray imaging applications<sup>5</sup>, where a-Si is used for both TFT components and photodetectors. While deposition of a-Si:H is achievable at relatively low temperature (~150 °C) in order to make the process compatible with plastic substrate, the quality of the material is inferior to that achieved with a high temperature process (typically

mobility of  $\sim 1 \text{ cm}^2/\text{Vs}$  is obtained). Furthermore, the inorganic a-Si is brittle, so it is limited for the use in flexible electronics.

On the other hand, poly-Si has been used as the channel material for the applications where high mobility TFTs are required. Previously, Wagner *et al.* reported poly-Si TFTs on metal foil substrate with the mobility of 64 cm²/Vs for electrons and 22 cm²/Vs for holes<sup>6</sup>. Serikawa et al. fabricated the poly-Si TFTs on flexible steel foil using KrF excimer laser annealing of a-Si, and the mobility is 103 cm²/Vs and 122 cm²/Vs for n- and p-channel, respectively <sup>7</sup>. The disadvantage of poly-Si, however, is high temperature thermal process is required to crystallize a-Si using either from post-annealing (~900 °C) or local laser irradiation, which prohibit this approach from being used on a plastic substrate. Additionally, large poly-Si grain size causes poor device-to-device uniformity, which is obviously problematic when we consider this for large-scale use.

#### b) Organic semiconductors

Organic semiconductors have been considered as a promising candidate to replace a-Si in the applications where large-area coverage, mechanical flexibility, and low cost fabrication are required<sup>8</sup>. Once formulated into inks, organic semiconductors are readily applicable to solution-based printing processing. Small molecules frequently used in TFTs such as pentacene and its derivatives (the deposition is not by solution based process but by evaporation method) show mobilities of up to 1.5 cm<sup>2</sup>/Vs under optimized condition<sup>9</sup>, but the mobility of polymer organic molecule semiconductors such as regioregular (RR) poly(3-hexylthiophene) (P3HT)<sup>10</sup> and a-w-dihexyl-quinquethiophene<sup>11</sup>, typically used with solution based printing process is around 0.1 cm<sup>2</sup>/Vs.

So far, many groups have reported numerous applications using organic TFTs such as backplanes in active matrix displays <sup>12, 13</sup> and radio frequency identification (RFID) tags <sup>14</sup>. In display applications, for example, organic TFTs act as individual pixel switches in the active matrix backplane circuit. The mobility in the range of ~ 0.01 cm²/Vs is good enough for small-sized devices with low resolution and low refresh rate, while organic TFTs are not a desirable candidate for medium- to large-sized liquid crystal displays (LCDs) used for monitor and television displays, where much higher ON current (i.e. higher mobility) is necessary for better resolution and faster refresh rate. Furthermore, the uncertain long-term reliability issue and difficulty of controlled doping techniques for these materials remained to be addressed.

#### c) Amorphous oxide semiconductors

Oxide semiconductors, especially amorphous ones, have attracted tremendous interest for the use as TFT active components because of exceptional optical transparency, air-stability and superior carrier mobility<sup>15</sup>. Various materials by solution

based process have been reported, including  $In_2O_3^{16}$ ,  $InGaO_3(ZnO)_5^{17}$ ,  $InGaZnO^{18}$ ,  $InZnO^{19}$ ,  $ZnO^{20}$ ,  $ZnMgO^{21}$ . Decent electrical properties (mobility up to ~120 cm²/Vs as well as large  $I_{on}/I_{off}$  ratio of Iofo) have been reported²²². But these properties are only achieved after high temperature (up to 400-500 °C) post-deposition annealing is done, which is not compatible with plastic substrate with low glass transition temperature (Glass transition temperature: Iofo °C for polyethylene terephthalate:PET and Iofo 400 °C for polyimide). The typical carrier mobility of solution-processed oxide semiconductor with modest annealing temperature (~ 150 °C) is in the range of 1-10 cm²/Vs²³, which is still lower than that of poly-silicon TFT (~ 100 cm²/Vs).

#### d) Layer transferred semiconductor

To achieve high quality materials, high temperature annealing process is desirable. But the use of plastic substrate imposes the upper limit of process temperature. To solve this dilemma, Roger *et al.* reported a new approach, where they fabricated nanometer- or micrometer-scale structures such as ribbons and membranes from high-quality, bulk wafers, and then transferred these with simple PDMS stamp onto plastic substrates at room temperature<sup>24, 25, 26</sup>. Significant advancement has been achieved using this technique, but there still remain challenges to be addressed such as fabrication cost and large-scale fabrication.

#### e) Semiconductor nanowires (NWs)

NWs have been intensively studied due to their size-related intriguing properties, and have been expected to be a promising potential as building blocks for nanoscale electronics <sup>27</sup>, optoelectronics <sup>28, 29</sup>, chemical/biological sensing <sup>30, 31, 32</sup>, and energy conversion/harvesting <sup>33, 34</sup>. With a vapour-liquid-solid (VLSI) process, various types of semiconductor NWs such as group IV, II-VI, III-V and even heterostructures can be grown (left in Fig. 1-2). To fully extend this potential for practical large-scale electronics, the use of aligned NW parallel arrays as the TFT channel materials has been explored. Numerous approaches have been reported so far (see more details in Chapter 2). The approach used in this thesis is based on contact printing methodology developed in our group <sup>35, 36, 37</sup>. The biggest advantage of this approach is that chemically synthesized inorganic NWs are transferred on receiver substrate at room temperature, thereby preserving high quality single crystal NWs on arbitrary any substrate such as paper and plastic. In this thesis, the potential of the aligned NW parallel arrays for large scale flexible electronics using contact printing will be discussed.

#### f) Single-walled carbon nanotubes (SWNTs)

SWNTs have been considered as a promising material for a wide range of applications in solid-state devices owing to their superb electrical properties such as scattering-free ballistic transport of carriers at low electric fields, higher carrier mobility (>10,000 cm<sup>2</sup>/Vs), and great gate control. Despite recent technological advancement in individual nanotube transistors, there still remains many challenges to be addressed, including reliable accurate assembly on a handling substrate, device-to-device fluctuation, just to name a few. On the other hand, the use of carbon nanotubes networks as the channel material in TFTs presents a new promising path for large-scale rigid/flexible electronics. Although electrical property of random network SWNT film is not comparable to that of single carbon nanotube due to considerable amount of contact resistance between each nanotube junctions, the SWNT network film not only holds many desirable characteristics such as superior carrier mobility (two orders of magnitude higher than a-Si or organic semiconductors), mechanical flexibility and optical transparency, but it can also be readily processed over large scale substrates with solution-based printing at room temperature. Various techniques have been reported for this purpose (summarized in Chapter 2). Though some advancement has been reported using SWNTs network film for macro-scale electronics<sup>38, 39</sup>, additional treatments such as electrical breakdown and channel width control are inevitably required to obtain better I<sub>on</sub>/I<sub>off</sub> ratio due to the coexistence of metallic and semiconducting nanotubes. Therefore, highly purified semiconducting SWNTs have been desired for device applications since those significantly simplified device fabrications. To address this issue, Hersam et al., successfully demonstrated the use of density gradient ultracentrifugation (DGU) to achieve electronic type separation<sup>40</sup>. By now, 99.9 % semiconductor-enriched SWNTs are commercially available (right in Fig. 1-2). In this thesis, we focused on this purified SWNTs and investigate the potential of purified SWNTs network film for the use in large-scale flexible electronics applications.

W. Lu and C.M. Lieber, J. Phys. D: Appl. Phys. 39, R387-R406 (2006).

**Figure 1-2.** (left) various types of nanowires grown by Vapour-liquid-solid (VLS) method, (right) Commercially available semiconductor enriched single-walled carbon nanotube solutions (from NanoIntegris).

#### 1.3 Manufacturing processing

#### a) Printing technique

Conventionally, electronics system has been fabricated with lithographic technique, where a series of subtractive steps are involved and each step is associated with expensive fabrication tool. In addition, the throughput is also limited by the use of each tool. In contrast to these drawbacks associated with conventional lithographic techniques, printing techniques hold several advantages. With the additive processing, the processing steps are drastically reduced, resulting in alleviated process complexity and less amount of tools required. Although total processing cost still depends on the process throughput and materials cost, this process reduction greatly simplifies the fabrication process. Several printing techniques have been studied for electronics applications. including screen printing, gravure/flexographic/offset printing, inkjet printing. Despite recent advancement in printing techniques, the linewidth and functional transistor density achieved with printing techniques, however, are still not yet comparable to those achieved by the state-of-the-art lithographic tools. Therefore, the use for printed electronics should be restricted to the applications that are area-constrained, but not function-constrained<sup>41</sup>. It should be also noted that reliable printing of high-k dielectric layers remains to be solved.

#### b) Conventional lithographic technique

The use of conventional lithography for flexible electronics is favorable since the issues associated with printing technology such as linewidth and line-edge roughness can be avoided. The process approach we developed<sup>42</sup>, in which the handling wafer on which polymer is spin-casted, is used for device fabrication and then polymer layer is peeled off after the fabrication is completed, can be combined with the conventional lithographic technique, enabling us to fabricate complicated and sophisticated device structure on flexible substrate.

The work detailed in this thesis to achieve flexible electronics relies on the conventional lithographic approach, rather than printing technique.

#### 1.4 Overview of this thesis

This dissertation focuses on the scalable assembly process of nanomaterials and its application to large-scale flexible and stretchable electronics. Chapter 2 describes the low temperature assembly process for semiconducting NWs and SWNTs. Thin film transistors (TFTs) composed of thus assembled nanomaterials are characterized, as detailed in Chapter 3. In this chapter, radio frequency characteristics are investigated to study the performance limit of InAs NWs parallel array TFTs. Furthermore, compositionally graded CdS<sub>x</sub>Se<sub>1-x</sub> NWs are assembled in similar fashion for tunable photodetector, and its optical responses are characterized. Chapter 4 describes the integrated device characteristics of SWNT TFTs, especially for artificial electronic skin and x-ray imager applications. Chapter 5 summarizes the contributions of this thesis and offers suggestions for future work.

#### 1.5 References

1

<sup>&</sup>lt;sup>1</sup> H. Yamamoto, H. Matsumaru, K. Shirahashi, M. Nakatani, A. Sasano, N. Konishi, K. Tsutsui, and T. Tsukada, "A new a-Si TFT with Al<sub>2</sub>O<sub>3</sub>/SiN double-layered gate insulator for 10.4-inch diagonal multicolor display," in *IEDM Tech. Dig.*, 1990, 851.

<sup>&</sup>lt;sup>2</sup> G. Kawachi, E. Kimura, Y. Wakui, N. Konishi, H. Yamamoto, Y. Matsukawa, and A. Sasano, "A novel technology for a-Si TFT-LCDs with buried ITO electrode structure," *IEEE Trans. Electron Devices*, 1994, 41, 1120.

<sup>&</sup>lt;sup>3</sup> J. A. Nichols, T. N. Jackson, M. H. Lu, and M. Hack, "a-Si:H TFT active-matrix phosphorescent OLED pixel," in *SID Tech. Dig.*, 2002, 1368.

<sup>&</sup>lt;sup>4</sup> T. Tsujimura, Y. Kobayashi, K. Murayama, A. Tanaka, M. Morooka, E. Fukumoto, H. Fujimoto, J. Sekine, K. Kanoh, K. Takeda, K. Miwa, M. Asano, N. Ikeda, S. Kohara, and S. Ono, "A 20-inch OLED display driven by super-amorphous-silicon technology," in *SID Tech. Dig.*, 2003, 6.

<sup>&</sup>lt;sup>5</sup> Larry E. Antonuk, John Boudry, Weidong Huang, Daniel L. McShan, Edward J. Morton, John Yorkston, Michael J. Longo, Robert A. Street, *Med. Phys.* 1992, 19, 1455.

<sup>&</sup>lt;sup>6</sup> M. Wu, X. Z. Bo, J. C. Sturm, and S. Wagner *Appl. Phys. Lett.*, 1997, 70, 342.

<sup>&</sup>lt;sup>7</sup> T. Serikawa and F. Omata, *IEEE Trans. Electron Devices*, 2002, 49, 820.

<sup>&</sup>lt;sup>8</sup> C. D. Dimitrakopoulos and D. J. Mascaro, *IBM J. Res. Dev.*, 2001, 45, 11.

<sup>&</sup>lt;sup>9</sup> Y.-Y. Lin, D. J. Gundlach, S. Nelson, and T. N. Jackson, "Stacked Pentacene Layer Organic Thin-Film Transistors with Improved Characteristics," *IEEE Electron Device Lett.* 1997, 18, 606.

<sup>&</sup>lt;sup>10</sup> H. Sirringhaus, P. J. Brown, R. H. Friend, M. M. Nielsen, K. Bechgaard, B. M. W. Langeveld-Voss, A. J. H. Spiering, R. A. J. Janssen, E. W. Meijer, P. Herwig, D. M. de Leeuw, *Nature*, 1999, 401, 685.

<sup>&</sup>lt;sup>11</sup> H. E. Katz, A. J. Lovinger, J. Johnson, C. Kloc, T. Siergist, W. Li, Y.-Y. Lin, and A. Dodabalapur, "A Soluble and Air-Stable Organic Semiconductor with High Electron Mobility," *Nature* 2000, 404, 478.

<sup>&</sup>lt;sup>12</sup> T. Someya, et al., "A large-area, flexible pressure sensor matrix with organic field-effect transistors for artificial skin applications" *Proc. Natl Acad. Sci. USA* 2004, 101, 9966.

<sup>&</sup>lt;sup>13</sup> T. Sekitani, *et al.*, A large-area wireless power-transmission sheet using printed organic transistors and plastic MEMS switches. *Nat. Mater.* 2007, 6, 413.

<sup>&</sup>lt;sup>14</sup> V. Subramanian, J. M. Frechet, P. C. Chang, D. Huang, J. B. Lee, S. E. Moleasa, A. R. Murphy, D. R. Redinger, S. K. Volkman, *Proceedings of the IEEE*, 2005, 93, 1330.

<sup>&</sup>lt;sup>15</sup> E. Fortunato, P. Barquinha, and R. Martins, *Advanced Materials* 2012, 24, 2945.

<sup>&</sup>lt;sup>16</sup> H. S. Kim, P. D. Byrne, A. Facchetti, T. J. Marks, *J. Am. Chem. Soc.*, 2008, 130, 12580.

<sup>&</sup>lt;sup>17</sup> K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, H. Hosono, H.; *Science* 2003, 300, 1269.

<sup>&</sup>lt;sup>18</sup> J. H. Lim, J. H. Shim, J. H. Choi, J. Joo, K. Park, H. Jeon, M. R. Moon, D. Jung, H. Kim, H. J. Lee, *Appl. Phys. Lett.*, 2009, 95, 012108.

<sup>&</sup>lt;sup>19</sup> D. H. Lee, Y. J. Chang, G. S. Herman, C. H. Chang, *Adv. Mater.*, 2007, 19, 843.

<sup>&</sup>lt;sup>20</sup> R. Chen, W. Zhou, M. Zhang, H. S. Kwok, Thin Solid Films, 2012, 520, 6681.

<sup>&</sup>lt;sup>21</sup> W. S. Choi, J. G. Yoon, Solid State Commun. 2011, 152, 345.

<sup>23</sup> R. A. Lujan and R. A. Street, *IEEE Electron Device Letters*, 2012, 33 688.

- <sup>24</sup> E. Menard, K. J. Lee, D.-Y. Khang, R. G. Nuzzo, J. A. Rogers, *Appl. Phys. Lett.* 2004, 84, 5398.

- <sup>25</sup> J.-H. Ahn, H.-S. Kim, K. J. Lee, Z. Zhu, E. Menard, R. G. Nuzzo, J. A. Rogers, *IEEE* Electron Device Lett. 2006, 27, 460.

- <sup>26</sup> Y. Sun, S. Kim, I. Adesida, J. A. Rogers, *Appl. Phys. Lett.* 2005, 87, 083501.

<sup>27</sup> J. Xiang, W. Lu, Y. Hu, Y. Wu, H. Yan, C. M. Lieber, *Nature* 2006, 441.

- <sup>28</sup> M. H. Huang, S. Mao, H. Feick, H. Q. Yan, Y. Y. Wu, H. Kind, E. Weber, R. Russo, P. D. Yang, Science 2001, 292, 1897.

- <sup>29</sup> H. G. Park, C. J. Barrelet, Y. Wu, B. Tian, F. Oian, C. M. Lieber, *Nat. Phot.* 2008, 2. 622.

- <sup>30</sup> Z. Y. Fan, D. W. Wang, P. C. Chang, W. Y. Tseng, J. G. Lu, *Appl. Phys. Lett.* 2004, 85, 5923.

- <sup>31</sup> Y. Cui, Q. Q. Wei, H. K. Park, C. M. Lieber, *Science* 2001, 293, 1289.

- <sup>32</sup> F. Patolsky, G. F. Zheng, O. Hayden, M. Lakadamyali, X. W. Zhuang, C. M. Lieber, Proc. Natl. Acad. Sci. USA 2004, 101, 14017.

- <sup>33</sup> X. D. Wang, J. H. Song, J. Liu, Z. L. Wang, *Science* 2007, *316*, 102.

- <sup>34</sup> J. Law, J. E. Greene, J. C. Johnson, R. Saykally, P. D. Yang, *Nat. Mater.* 2005, *4*, 455.

- <sup>35</sup> Z. Fan, J. C. Ho, Z. A. Jacobson, R. Yerushalmi, R. L. Alley, H. Razavi. A. Javev. Nano Lett. 2008, 8, 25.

- <sup>36</sup> R. Yerushalmi, Z. A. Jacobson, J. C. Ho, Z. Fan, A. Javey, *Appl. Phys. Lett.* 2007, 91, 203104.

- <sup>37</sup> Z. Fan, J. C. Ho, Z. A. Jacobson, H. Razavi, A. Javey, *Proc. Natl. Acad. Sci. U.S.A.* 2008, 105, 11066.

<sup>38</sup> P. G. Collins, M. S. Arnold, P. Avouris *Science*, 2001, 292, 706.

- <sup>39</sup> Q. Cao, H. S. Kim, N. Pimparkar, J. P. Kulkarni, C. Wang, M. Shim, K. Roy, M. A. Alam, J. A. Rogers, *Nature* 2008, 454, 495.

- <sup>40</sup> M. S. Arnold, A. A. Green, J. F. Hulvat, S. I. Stupp, M. C. Hersam, *Nat. Nanotech.* 2006, 1, 60.

- <sup>41</sup> H. Klauk, Wiley-VCH, "Organic electronics II: More Materials and Applications", 2012, 235.

- <sup>42</sup> K. Takei, T. Takahashi, J. C. Ho, H. Ko, A. G. Gillies, P. W. Leu, R. S. Fearing, A. Javev. Nat. Mater. 2010, 9, 821.

<sup>&</sup>lt;sup>22</sup> M. G. Kim, H. S. Kim, Y. G. Ha, J. Q. He, M. G. Kanatzidis, A. Facchetti, T. J. Marks , J. Am. Chem. Soc. 2010, 132, 10352.

# Chapter 2 Scalable and low-temperature assembly process for nanomaterials

#### 2.1 Large-scale assembly of NWs

#### 2.1.1 Introduction

To utilize NWs for practical large-scale flexible electronics, a controllable yet reliable assembly method needs to be established. For this purpose, various assembly approaches have been reported (Fig. 2-1 from ref. 1) including flow-assisted alignment<sup>2, 3, 4, 5</sup>, Langmuir-Blodgett (LB)<sup>6, 7, 8</sup>, bubble-blown techniques<sup>9</sup>, and electric-field-directed assembly 10, 11, 12, 13. Each approach has a unique advantage and demonstrated the feasibility of parallel-arrayed assembly, but suffers from certain limitations, mainly the scalability, uniformity, and/or the complexity of the process for use in macro-scale applications. To address this point for large-scale and controllable assembly of highly aligned NW parallel arrays, our lab has developed contact printing technology 14, 15, 16, where as-grown NWs are mechanically transferred on the receiver substrate with appropriate surface modification. During this printing process, shear force is utilized to effectively align the NWs. With this simple but versatile approach, parallel arrays of NWs are readily formed on literally any substrate including paper, glass and plastic substrate. This NWs contact printing technology could be an important advancement to realize fully printed flexible electronic devices (Fig. 2-2), which exhibit both low cost and high performance. The approach described in Fig. 2-2 is divided into three components; 1) patterning of the receiver substrate to define 'sticky' and 'non-sticky' regions for selective NWs transfer, 2) contact printing of NWs array as the active channel region, and 3) metal contact and insulator deposition to complete the device. Since the step 3 is an intensively explored research field in organic electronics community, this topic won't be discussed here. Rather our effort is focused on steps 1 and 2 as described in following chapter.

**Figure 2-1.** Nanowire-assembly techniques (image from reference 1.) (a) Schematic and the result of flow-assisted NW-assembly method<sup>2-5</sup>, (b) Schematic of LB NW assembly method<sup>6-8</sup>, (c) Schematic of blown-bubble NW assembly method<sup>9</sup>, (d) Schematic (left) and optical image (right) of electric field alignment of NWs<sup>10-13</sup>.

**Figure 2-2.** Schematic of an envisioned roll-to-roll printing set-up for NW electronics and sensors fabrication (image from reference 1). The process involves fluorinated monolayer patterning of the receiver substrate to define "sticky" and "non-sticky" regions for the subsequent patterned transfer and assembly of NWs by contact printing. Following the printing of NW active components, devices are fabricated by defining the source/drain and gate electrodes.

#### 2.1.2 NWs contact printing methodology

The overview of contact printing process is shown in Fig. 2-3 (image from ref. 1). Here the NWs used in this process are grown by CVD (chemical vapor deposition). The NWs are typically grown on the growth substrate with random orientation, as shown in the SEM image in the inset of Fig. 2-3. Contact printing enables these as-grown NWs to be transferred on the pre-patterned receiver substrate. During this process, NWs are effectively combed by the directional shear force, and are eventually detached from the growth substrate as they are anchored by the chemically modified surface on the receiver substrate. After lift-off process, highly aligned arrays are readily obtained. This simple process can be readily applicable to the large-scale (4" wafer) assembly. The density of printed NWs is controlled by using different surface modification of the receiver substrate. Figure 2-4 shows the density of printed Ge NWs on various chemically modified surfaces. For the receiver substrates functionalized with –CF3 terminal groups, which are well known to be highly hydrophobic and 'non-sticky', almost no NWs are transferred. On the other hand, highly dense NW assembly are observed on –NH2 and –

N(Me)3+ terminated monolayers due to the strong surface bonding interactions. To extend this, in the next subsection, a self-assembled monolayer (SAM) is used to define 'sticky' and 'non-sticky' surface regions, followed by NW contact printing. This approach enables us to realize lithography-free fully printable electronics (Fig. 2-2).

**Figure 2-3.** Schematic of NW contact printing process. The SEM image in the inset shows the grown Ge NWs are randomly oriented on the growth substrate. The NWs are then aligned and transferred to the receiver substrate by application of a directional shear force, resulting in the printing of sub-monolayer NW parallel arrays on the receiver substrate (Ref. 1).

**Figure 2-4.** The density control of printed Ge NW by contact printing through the surface modification of Si substrate. Bare SiO<sub>2</sub> corresponds to the untreated SiO<sub>2</sub> surface, while –CF3 [(heptadecafluoro-1,1,2,2-tetrahydrodecyl) dimethylchlorosilane), -N(Me)3 (Ntrimethoxysilylpropyl-N,N,N-trimethylammonium chloride], and -NH2 (3 triethoxysilylpropylamine) correspond to the surface-modified functional groups. Note that, as expected, poly(L-lysine) functionalization results in a larger standard deviation due to the less uniform coverage of the surface by the polymeric thin film, as compared to the molecular monolayers (Ref. 1).

#### 2.1.3 Monolayer resist for patterned contact printing $\Diamond$

In recent years, single crystalline, semiconductor nanowires (NWs) have been widely explored as the potential building blocks for various technological applications, such as electronics<sup>17</sup>, photonics<sup>18, 19</sup>, sensors<sup>20, 21</sup>, and energy conversions<sup>22, 23</sup>. To fully extend the potential, however, the development of generic assembly methods is required<sup>24, 25</sup>. Recently, we demonstrated a simple contact printing approach for the largescale assembly of parallel arrays of NWs on rigid substrates as well as mechanically flexible substrates<sup>26, 27, 28</sup>. During this process, the direct and aligned transfer of NWs from the growth (i.e., donor) substrate to the receiver substrate is attained. This highly versatile approach is attractive for large-area printable electronics with the printed NW parallel arrays being configured as the channel or active material for transistors and sensors. Previously, the NW patterning was achieved by photolithographically patterning a polymeric resist layer on the receiver substrate prior to the printing process<sup>6</sup>. Following the printing process, the resist layer covered with the printed NWs is dissolved in a solvent, leaving behind only the NWs assembled at predefined locations. To further demonstrate the versatility of the contact printing process, here, we report patterned printing of NWs by using fluorinated self-assembled monolayers (SAMs) as the resist layer. By projecting a light pattern on the surface of the SAM-resist in an oxygen rich environment, sticky and non-sticky regions on the surface are directly defined in a singlestep process which then enables the highly specific and patterned transfer of the NWs by the printing process, without the need for a subsequent lift-off step. This work demonstrates a novel route toward scalable, patterned printing of NWs on substrates by utilizing very ultraviolet (VUV) tunable, nanoscale chemical interactions.

The process flow for the patterned NW printing with SAM-resist is illustrated in Figure 2-5. Firstly, a Si/SiO<sub>2</sub> (50 nm, thermally grown) substrate is chemically reacted with (heptadecafluoro-1,1,2,2-tetrahydrodecyl) dimethylchlorosilane (HDF) to form a highly stable, fluorinated SAM on the surface of the substrate. A light pattern is then projected on the SAM-resist by using an excimer light source (172 nm. ~25 mW/cm<sup>2</sup>) and a shadow mask (Fig. 2-5a). The VUV light exposure in the presence of O<sub>2</sub> results in the chemical cleavage of the F-C bonds and the formation of -COOH and -CHO functional end groups (Fig. 2-5b)<sup>29, 30</sup>. While the original fluorinated SAM is highly non-sticky to the NWs, the VUV-modified monolayer exhibits strong binding interactions with the NWs, most likely through hydrogen bonding. Following the patterned exposure of the SAM-resist, the NW printing is conducted by directionally sliding a growth substrate consisting of a dense forest of Ge or Si NWs (grown non-epitaxially by vapor-liquid-solid process) on top of the receiver substrate. A lubricant (octane: mineral oil, 2:1 v:v) is applied between the two substrates in order to minimize the mechanical interactions, therefore, enhancing the dominant role of the well-controlled chemical interactions in guiding the NW transfer process. During the printing process, NWs are dragged on the receiver substrate, resulting in their alignment in the direction of the shear force (Supp.

<sup>&</sup>lt;sup>⋄</sup> The work presented here has been published in a similar form to the following reference; T. Takahashi, K. Takei, J. C. Ho, Y. –L. Chueh, Z. Fan, A. Javey, *Journal of the American Chemical Society*, 131 (6), 2102-2103, 2009.

Info.). Once anchored to the surface of the receiver substrate by chemical binding interactions, NWs are detached from the growth substrate. As a result, highly aligned NW arrays are assembled on the exposed SAM regions of the receiver substrate while no NWs are assembled on the unexposed, fluorinated SAM regions (Fig. 2-5c).

To characterize the properties of the VUV exposed SAMs, contact angle, XPS, and ellipsometry measurements were performed as a function of the exposure time. As shown in Fig. 2-6a, the contact angle of the HDF treated surface is ~100°, showing a highly hydrophobic surface property. As the monolayer is exposed to VUV, however, the contact angle decreases and the surface changes to possess a hydrophilic property. Specifically, the contact angle is reduced to ~10° after 60 min exposure in 3 Pa  $O_2/N_2$  (21, 79 %) ambient. On the other hand, when irradiation is carried out at  $10^5$  Pa, it takes <20 min to achieve a similar contact angle. This accelerated chemical transformation of the monolayer by increasing the pressure depicts the important role of  $O_2$  in the VUV enabled surface chemical modification  $^{29,30}$ .

From XPS measurements (Fig. 2-6b), the VUV-induced, chemical modification of the monolayer is directly confirmed. While the F 1s peak at 688 eV, originating from C-F bonds, is clearly observed for the unexposed SAM, it is completely diminished after the VUV irradiation. This is also seen from the C 1s spectrum, where the C-F peak at 292 eV disappears upon VUV irradiation. On the hand, the C 1s peak at ~285 eV which corresponds to the C-C bond remains intact, even after the VUV exposure. The results suggest that the alkyl backbone of the monolayer remains intact with only the C-F bonds being oxidized upon VUV irradiation and replaced with polar –COOH and -CHO species. This is also confirmed from ellipsometry measurements where a SAM thickness of ~1.1 and 0.9 nm are observed for the unexposed and exposed SAMs, respectively. The observed results are consistent with the previously reported VUV modification of fluorinated SAMs on SiO<sub>2</sub> surfaces in the presence of molecular oxygen<sup>29, 30</sup>. In those studies, it was proposed that molecular oxygen forms highly active species upon VUV irradiation which then readily oxidize and cleave the C-F bonds. A similar surface chemical reaction is expected in our fluorinated SAMs.

Optical and scanning electron microscopy images of printed Ge NWs (d  $\sim$ 30 nm) on VUV-patterned fluorinated SiO<sub>2</sub>/Si substrate are shown in Fig. 2-7. Fluorinated regions possess highly non-sticky surface properties; therefore, preventing NW transfer during the contact printing process. On the other hand, NW parallel arrays are readily assembled on the hydrophilic regions, enabled by the VUV exposure. The transferred NWs are found to be relatively dense (2-5 NW/ $\mu$ m) and well aligned (Fig. 2-7*d*). The density may be further enhanced in the future by using complementary surface modification of VUV-irradiated regions, which was not incorporated in this work. As clearly evident, this simple process enables a high degree of selectivity in the assembly of the NWs in well defined locations on surfaces, especially for applications that do not require nm-scale positioning, such as for large-area electronics with the device dimensions on the order of 10's of microns. In our current set-up, a resolution limit of ~5  $\mu$ m is obtained which is limited by the non-ideal contact between the shadow mask and the substrate.

To further investigate the feasibility of this printing approach for electronic applications, we fabricated back-gated (gate oxide thickness ~ 50 nm SiO<sub>2</sub>), field-effect-transistors (FETs) with channel width ~200  $\mu$ m and source/drain (S/D) spacing ~3  $\mu$ m by using *p*-type Si NWs (d~30 nm, B doped). Notably, the assembled NWs do not detach from the substrate during the standard microfabrication processing steps used here (Supp. Info.). Fig. 2-8 shows a representative transfer characteristic of such a proof-of-concept device structure. The transistor delivers a modest ON current of ~0.6 mA at V<sub>DS</sub>=3V with I<sub>ON</sub>/I<sub>OFF</sub> >100. This ON current corresponds to ~1  $\mu$ A/NW assuming a NW density of 3 NW/ $\mu$ m, which is consistent with the observed I<sub>ON</sub> for a typical single Si NW FET configured in similar device geometry.

In summary, well-defined and highly specific NW assembly is achieved by combining the contact printing with direct SAM patterning on SiO<sub>2</sub> surfaces. Here, the SAM is effectively used as the resist for NW transfer process, enabling a highly versatile, one-step process for achieving patterned assembly of parallel arrays of NWs on substrates.

**Figure 2-5**. Schematic of the patterned contact printing process with monolayer resist. (a) Patterning of fluorinated  $SiO_2$  surface is carried out by VUV irradiation in the presence of  $O_2$ . (b) C-F bonds in the exposed regions are cleaved and replaced with – COOH or -CHO functional groups. (c) Contact printing results in the aligned transfer of NWs on the VUV exposed regions.

**Figure 2-6**. (a) Water contact angle as a function of VUV irradiation time. Irradiation is carried out at  $10^5$  Pa and 3 Pa, corresponding to  $2 \times 10^4$  Pa and 0.6 Pa of oxygen partial pressure, respectively. (b) F1s and C1s (inset) XPS spectra of fluorinated surfaces before (black curve) and after (red curve) VUV irradiation for 30min at  $10^5$  Pa.

**Figure 2-7.** (a), (b), (c) Optical dark field and (d) SEM images of Ge NWs (d ~30 nm) printed on the VUV patterned SAM-resist.

**Figure 2-8.** Transfer characteristics of a parallel-array Si NW FET with  $W\sim200$  μm and  $L\sim3$  μm, for various values of  $V_{DS}$ .

#### 2.2 Large-scale assembly of single-walled carbon nanotubes

#### 2.2.1 Introduction

Various assembly methods for random single-walled carbon nanotubes (SWNTs) network have been reported, including direct CVD growth <sup>31, 32</sup>, dry filtration <sup>33</sup>, evaporation assembly <sup>34</sup>, spin coating <sup>35, 36, 37</sup>, drop coating <sup>38, 39, 40, 41</sup>, and printing <sup>42, 43, 44, 45</sup>, <sup>46</sup> (Figure 2-9 from reference 47). Each of the methods has unique opportunities and challenges (see detailed info in ref. 47). In this study, we decided to focus on solution-based deposition of pre-separated single-walled carbon nanotubes (SWNTs) on macro scale substrate. In this experiment, as-received 99 % semiconductor enriched SWNT solution (IsoNanotubes-S from NanoIntegris, Inc.) is used without any densification.

# 2.2.2 Solution-based process using high purity semiconducting SWNTs

Figure 2-10 shows the solution-based process of high purity semiconducting SWNTs deposition. First, the surface of SiO<sub>2</sub> is functionalized with either poly-L-lysine (PLL) for 5 min or aminopropyltriethoxysilane (APTES) for 30 min after mild O<sub>2</sub> plasma treatment (30W, 1min). Then, semiconductor-enriched SWNTs solution (99 %) is casted with pipet on the surface for certain amount of time, followed by a rinse with DI water. AFM images of deposited SWNTs network from PLL- and APTES-functionalized surfaces are shown in Fig 2-11a, b. Each molecular structure used for surface functionalization is also shown on Fig. 2-11c, d. APTES is reported as commonly used polymer for SWNTs deposition<sup>31,35</sup>, but it didn't work for us for unknown reasons. On the other hand, PLL reliably works better as SWNT deposition, so we use this polymer for the rest of our work. It should be also noted that the density of SWNTs as a function of time is highly dependent on the particular surface being explored. Figure 2-12 shows AFM images of deposited SWNTs with different deposition time on two different surfaces; one is thermally grown SiO<sub>2</sub> and the other is evaporated SiO<sub>2</sub>. Higher densities of SWNTs with higher bundling probability are observed for similar deposition times on thermally grown SiO<sub>2</sub> layers. Furthermore, we observed that the density depends on the nanotube solution, in part because different semiconductor-enriched products utilize different surfactants. The electrical properties of thusly deposited SWNTs will be discussed in Chapter 4.2.

**Figure 2-9.** Different methods used for assembly of SWNT networks. (a) CVD growth<sup>25, 26</sup>, (b) Dry filtration<sup>27</sup>, (c) Evaporation assembly<sup>28</sup>, (d) Spin coating<sup>29-31</sup>, (e) Drop casting<sup>32-35</sup>, (f) Printing<sup>36-39</sup> (from reference 47).

**Figure 2-10.** Schematic of SWNT deposition process. Surface is modified with either poly-L-lysine or aminopropyltriethyoxysilane (APTES) in this study.

**Figure 2-11**. The effect of surface treatment on the deposited nanotube density. The surface is treated with **(a)** poly-L-lysine for 5min and **(b)** aminopropyltriethyoxy silane (APTES) for 30min. SWNT deposition time is 20min. Chemical structure of **(c)** poly-Llysine and **(d)** APTES.

**Figure 2-12.** AFM images taken from different SWNT deposition time on (a) evaporated  $SiO_2$  and (b) thermally grown  $SiO_2$ . For (a), 5min, 30 min, and 120 min are used, and for (b) 1 min, 5 min, and 30min are used as SWNT deposition time. The density increases as the deposition time increases, and eventually it forms nanotube bundles, degrading the device  $I_{ON}/I_{OFF}$  ratio.

# 2.3 Summary

In this chapter, simple but versatile assembly methods for parallel NWs array and random network SWNTs are discussed. Parallel NW arrays are readily printed on arbitrary substrate at room temperature with contact printing technique combined with monolayer resist, while SWNT random network is controllably deposited with proper surface modification. By using these NW arrays or SWNT networks as the active components of TFTs, the stochastic device-to-device variation is drastically reduced, thereby, presenting a viable route towards the utilization of functional nanoscale materials for practical applications.

#### References 2.4

<sup>&</sup>lt;sup>1</sup> Z. Fan, J. C. Ho, T. Takahahsi, R. Yerushalmi, K. Takei, A. C. Ford, Y. L. Chueh, A. Javey, Adv. Mater. 2009, 21, 3730.

<sup>&</sup>lt;sup>2</sup> X. F. Duan, C. M. Niu, V. Sahi, J. Chen, J. W. Parce, S. Empedocles, J. L. Goldman, Nature 2003, 425, 274.

<sup>&</sup>lt;sup>3</sup> Y. Huang, X. F. Duan, Q. Q. Wei, C. M. Lieber, *Science* 2001, 291, 630.

<sup>4</sup> C. Yan, T. Zhang, P. S. Lee, *Appl. Phys. A: Mater. Sci. Process.* 2009, 94, 763

<sup>&</sup>lt;sup>5</sup> C. Y. Geng, Y. Jiang, Y. Yao, X. M. Meng, J. A. Zapien, C. S. Lee, Y. Lifshitz, S. T. Lee, Adv. Funct. Mater. 2004, 14, 589.

<sup>&</sup>lt;sup>6</sup> S. Jin, D. M. Whang, M. C. McAlpine, R. S. Friedman, Y. Wu, C. M. Lieber, *Nano* Lett. 2004, 4, 915.

A. Tao, F. Kim, C. Hess, J. Goldberger, R. R. He, Y. G. Sun, Y. N. Xia, P. D. Yang, Nano Lett. 2003, 3, 1229.

<sup>&</sup>lt;sup>8</sup> X. L. Li, L. Zhang, X. R. Wang, I. Shimoyama, X. M. Sun, W. S. Seo, H. J. Dai, *J. Am.* Chem. Soc. 2007, 129, 4890.

<sup>&</sup>lt;sup>9</sup> G. Yu, A. Cao, C. M. Lieber, *Nat. Nanotechnol.* 2007, 2, 372.

<sup>&</sup>lt;sup>10</sup> P. A. Smith, C. D. Nordquist, T. N. Jackson, T. S. Mayer, B. R. Martin, J. Mbindyo, T. E. Mallouk, Appl. Phys. Lett. 2000, 77, 1399.

<sup>&</sup>lt;sup>11</sup> L. F. Dong, J. Bush, V. Chirayos, R. Solanki, J. Jiao, *Nano Lett.* 2005, 5, 2112.

<sup>12</sup> Y. Cao, W. Liu, J. L. Sun, Y. P. Han, J. H. Zhang, S. Liu, H. S. Sun, J. H. Guo, Nanotechnology 2006, 17, 2378.

<sup>&</sup>lt;sup>13</sup> O. Englander, D. Christensen, J. Kim, L. W. Lin, S. J. S. Morris, *Nano Lett.* 2005, 5, 705.

<sup>&</sup>lt;sup>14</sup> Z. Fan, J. C. Ho, Z. A. Jacobson, R. Yerushalmi, R. L. Alley, H. Razavi, A. Javey, Nano Lett. 2008, 8, 25.

<sup>&</sup>lt;sup>15</sup> R. Yerushalmi, Z. A. Jacobson, J. C. Ho, Z. Fan, A. Javev, *Appl. Phys. Lett.* 2007, 91. 203104.

<sup>&</sup>lt;sup>16</sup> Z. Fan, J. C. Ho, Z. A. Jacobson, H. Razavi, A. Javey, *Proc. Natl. Acad. Sci. U.S.A.* 2008, 105, 11066.

<sup>&</sup>lt;sup>17</sup> J. Xiang, W. Lu, Y. Hu, Y. Wu, H. Yan, C. M. Lieber, *Nature* 2006, 441.

<sup>&</sup>lt;sup>18</sup> M. H. Huang, S. Mao, H. Feick, H. Q. Yan, Y. Y. Wu, H. Kind, E. Weber, R. Russo, P. D. Yang, *Science* 2001, 292, 1897.

<sup>&</sup>lt;sup>19</sup> H. G. Park, C. J. Barrelet, Y. Wu, B. Tian, F. Qian, C. M. Lieber, *Nat. Phot.* 2008, 2, 622.

<sup>&</sup>lt;sup>20</sup> F. Patolsky, G. Zheng, C. M. Lieber, *Anal. Chem.* 2006, 78, 4260.

<sup>&</sup>lt;sup>21</sup> M. C. McAlpine, H. Ahmad, D. Wang, J. R. Heath, *Nat. Mater.* 2007, 6, 379.

<sup>&</sup>lt;sup>22</sup> X. D. Wang, J. H. Song, J. Liu, Z. L. Wang, Science 2007, 316, 102.

<sup>&</sup>lt;sup>23</sup> M. Law, L. E. Greene, J. C. Johnson, R. Saykally, P. D. Yang, *Nat. Mater.* 2005, 4,

<sup>&</sup>lt;sup>24</sup> G. Yu, A. Cao, C. M. Lieber, *Nat. Nanotech.* 2007, 2, 372.

<sup>&</sup>lt;sup>25</sup> P. Pauzauskie, A. Radenovic, E. Trepagnier, H. Shroff, P. D. Yang, J. Liphardt, *Nat*. Mater. 2006, 5, 97.

<sup>&</sup>lt;sup>26</sup> Z. Fan, J. C. Ho, Z. A. Jacobson, R. Yerushalmi, R. L. Alley, H. Razavi, A. Javey, Nano Lett. 2008, 8, 25.

- <sup>28</sup> Z. Fan, J. C. Ho, Z. A. Jacobson, H. Razavi, A. Javey, *Proc. Natl. Acad. Sci. U.S.A.* 2008, 105, 11066.

- <sup>29</sup> S. L. Brandow, M. S. Chen, R. Aggarwal, C. S. Dulcey, J. M. Calvert, W. J. Dressick, *Langmuir* 1999, 15, 5429.

- <sup>30</sup> Y. J. Kim, K. H. Lee, H. Sano, J. Han, T. Ichii, K. Murase, H. Sugimura, *Jpn. J. Appl. Phys.* 2008, 47, 307.

- <sup>31</sup> Q. Cao, H. S. Kim, N. Pimparkar, J. P. Kulkarni, C. Wang, M. Shim, K. Roy, M. A. Alam and J. A. Rogers, *Nature*, 2008, 454, 495.

- <sup>32</sup> E. S. Snow, J. P. Novak, P. M. Campbell and D. Park, *Appl. Phys. Lett.*, 2003, 82, 2145.

- <sup>33</sup> D. Sun, M. Y. Timmermans, Y. Tian, A. G. Nasibulin, E. I. Kauppinen, S. Kishimoto, T. Mizutani and Y. Ohno, *Nat. Nanotechnol.*, 2011, 6, 156.

- <sup>34</sup> M. Engel, J. P. Small, M. Steiner, M. Freitag, A. A. Green, M. C. Hersam and Ph. Avouris, *ACS Nano*, 2008, 2, 2445.

- <sup>35</sup> M. A. Meitl, Y. X. Zhou, A. Gaur, S. Jeon, M. L. Usrey, M. S. Strano and J. A. Rogers, *Nano Lett.*, 2004, 4, 1643.

- <sup>36</sup> M. C. LeMieux, M. Roberts, S. Barman, Y. W. Jin, J. M. Kim and Z. Bao, *Science*, 2008, 321, 101.

- <sup>37</sup> M. Vosgueritchain, M. C. LeMieux, D. Dodge and Z. Bao, *ACS Nano*, 2010, 4, 6137.

- <sup>38</sup> E. S. Snow, P. M. Campbell, M. G. Ancona and J. P. Novak, *Appl. Phys. Lett.*, 2005, 86, 033105.

- <sup>39</sup>C. Wang, J. Zhang, K. Ryu, A. Badmaev, L. Gomez and C. Zhou, *Nano Lett.*, 2009, 9, 4285.

- <sup>40</sup> C. Wang, J. Zhang and C. Zhou, *ACS Nano*, 2010, 4, 7123.

- <sup>41</sup> N. Rouhi, D. Jain, K. Zand and P. J. Burke, *Adv. Mater.*, 2011, 23, 94.

- <sup>42</sup>M. Ha, Y. Xia, A. A. Green, W. Zhang, M. J. Renn, C. H. Kim, M. C. Hersam and C. D. Frisbie, *ACS Nano*, 2010, 4, 4388.

- <sup>43</sup> P. Chen, Y. Fu, R. Aminirad, C. Wang, J. Zhang, K. Wang, K. Galatsis and C. Zhou, *Nano Lett.*, 2011, 11, 5301.

- <sup>44</sup> M. Jung, J. Kim, J. Noh, N. Lim, C. Lim, G. Lee, J. Kim, H. Kang, K. Jung, A. D. Leonard, J. M. Tour and G. Cho, *IEEE Trans. Electron Devices*, 2010, 57, 571.

- <sup>45</sup> J. Noh, M. Jung, K. Jung, G. Lee, J. Kim, S. Lim, D. Kim, Y. Choi, Y. Kim, V. Subramanian and G. Cho, *IEEE Electron Device Lett.*, 2011, 32, 638.

- <sup>46</sup> J. Noh, S. Kim, K. Jung, J. Kim, S. Cho and G. Cho, *IEEE Electron Device Lett.*, 2011, 32, 1555.

- <sup>47</sup> C. Wang, K. Takei, T. Takahashi, A. Javey, *Chem. Soc. Rev.* 2013, 42, 2592.

<sup>&</sup>lt;sup>27</sup> R. Yerushalmi, Z. A. Jacobson, J. C. Ho, Z. Fan, A. Javey, *Appl. Phys. Lett.* 2007, 91, 203104.

# Chapter 3 Assembled semiconductor NWs device component

#### 3.1 Introduction

In this chapter, electrical and optical properties of discrete parallel array NW TFTs assembled by contact printing are characterized.

Firstly, in section 3.2, the electrical properties of InAs NW parallel array TFTs are investigated, especially in the radio frequency regime. Previously, the electrical properties of single InAs NW grown by CVD has been systematically studied<sup>44</sup>, showing a respectable field-effect electron mobility of 2500 cm<sup>2</sup>/Vs for radius of 25 nm, with  $I_{on}/I_{off}$  ratio of  $10^4$ . In this study, we assemble InAs NWs into parallel arrays with contact printing, and investigate the performance limit of InAs NW parallel array TFTs.

Secondly, the electrical and optical properties of spatially composition graded  $CdS_xSe_{1-x}$  (x=0 to 1) NWs are discussed in section 3.3. Due to the lattice mismatch required for epitaxial growth, bandgap control by alloying crystalline semiconductors with different bandgaps has been challenging. To address this issue, in this study we utilize CVD-grown compositionally graded  $CdS_xSe_{1-x}$  NW alloy, and transfer them into parallels array by contact printing to realize tunable-wavelength photodetectors.

#### 3.2 Parallel Array InAs Nanowire Transistors for Mechanically Bendable, Ultra

# **High Frequency Electronics**<sup>♦</sup>