# Tunneling in low-power device-design: A bottom-up view of issues, challenges, and opportunities

Kartik Ganapathi

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-164 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-164.html

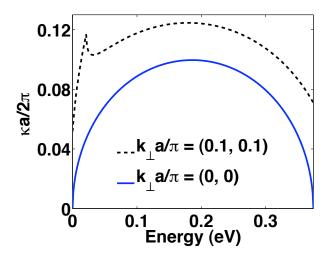

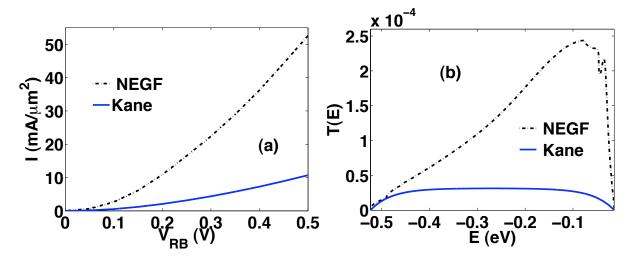

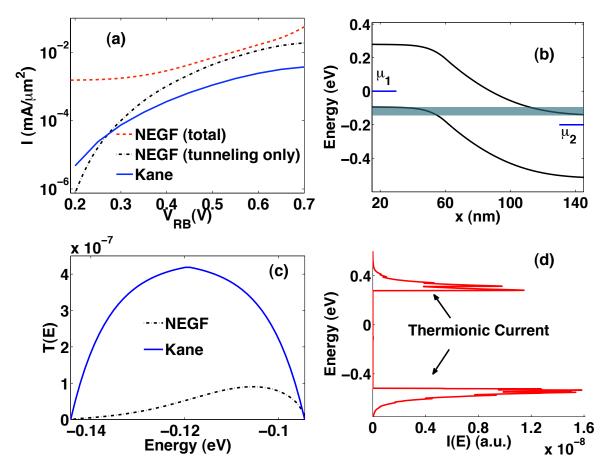

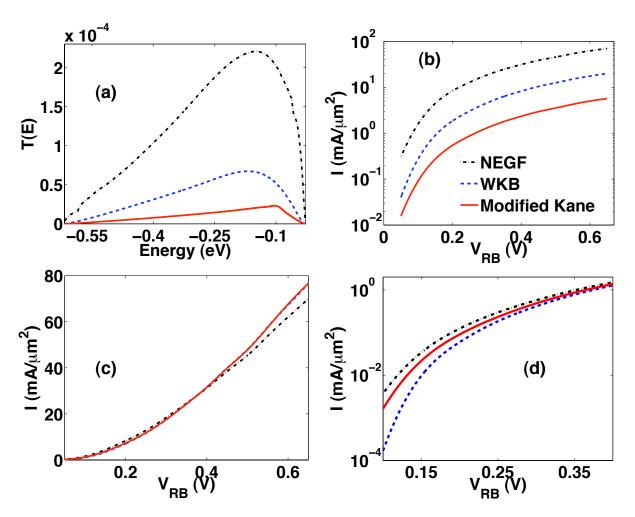

October 3, 2013

Copyright © 2013, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Tunneling in low-power device-design: A bottom-up view of issues, challenges, and opportunities

By

#### Kartik Ganapathi

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California Berkeley

Committee in charge:

Professor Sayeef Salahuddin, Chair Professor Ali Javey Professor Chenming Hu Professor Junqiao Wu Tunneling in low-power device-design: A bottom-up view of issues, challenges, and opportunities

Copyright © 2013 by Kartik Ganapathi

#### Abstract

Tunneling in low-power device-design: A bottom-up view of issues, challenges, and opportunities

by

#### Kartik Ganapathi

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Sayeef Salahuddin, Chair

Simulation of electronic transport in nanoscale devices plays a pivotal role in shedding light on underlying physics, and in guiding device-design and optimization. The length scale of the problem and the physical mechanism of device operation guide the choice of formalism. In the sub-20 nanometer regime, semi-classical approaches start breaking down, thus necessitating a quantum-mechanical treatment of the electronic transport problem. Non-equilibrium Green's function (NEGF) is a theoretical framework for investigating quantum-mechanical systems – interacting with surroundings through exchange of quasiparticles – far from equilibrium. Although hugely computation-intensive with a realistic device-representation, it provides a rigorous way to include particle-particle interactions and to model phenomena that are inherently quantum-mechanical.

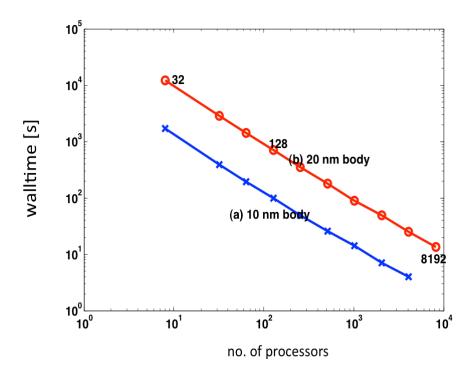

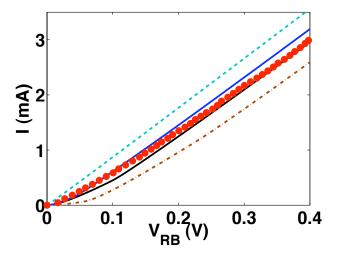

We build the Berkeley Quantum Transport Simulator (BQTS) – a massively parallel, generic, NEGF-based numerical simulator – to explore low-power device-design opportunities. Demonstrating scalability and benchmarking results with experimental tunnel diode data, we set out to understand tunneling in devices and to leverage it for both digital and analog applications.

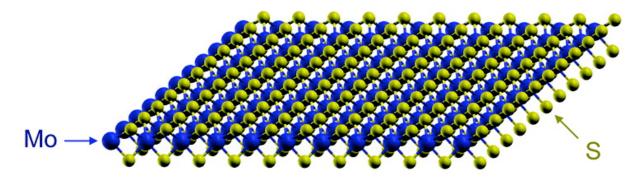

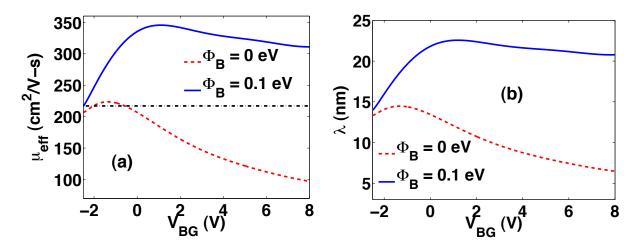

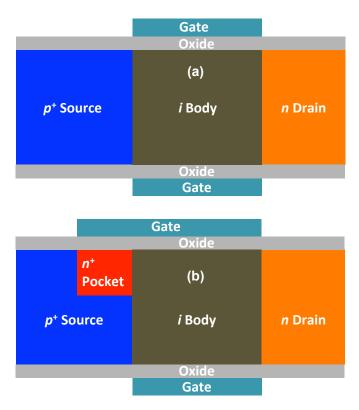

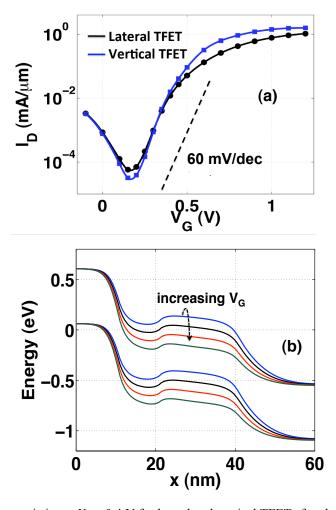

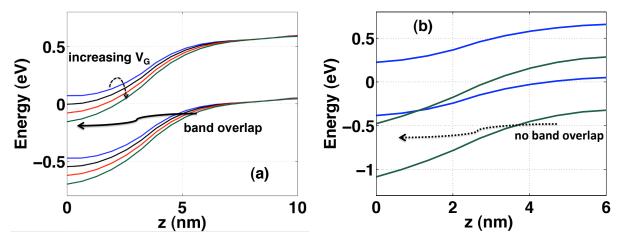

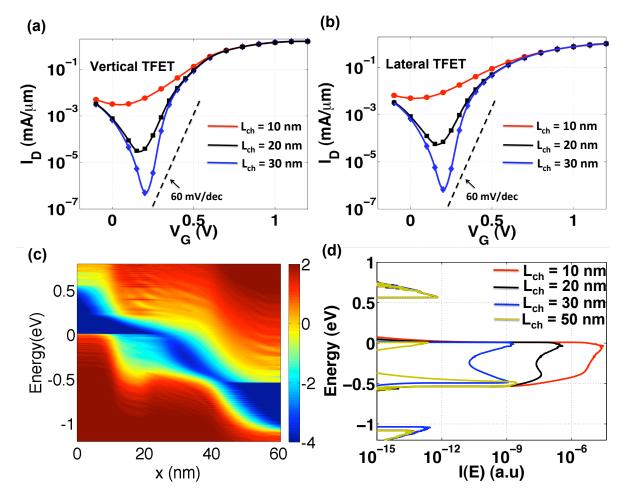

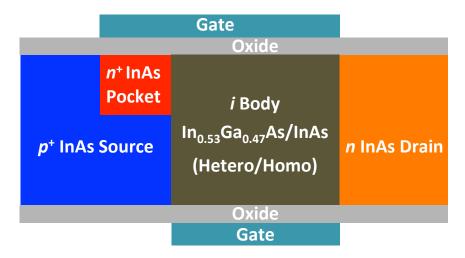

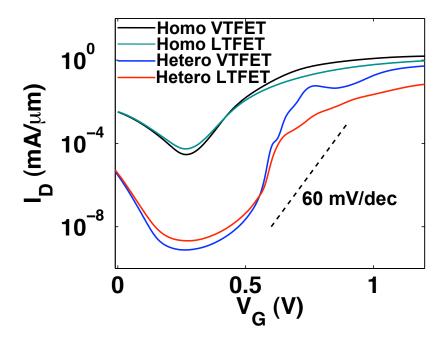

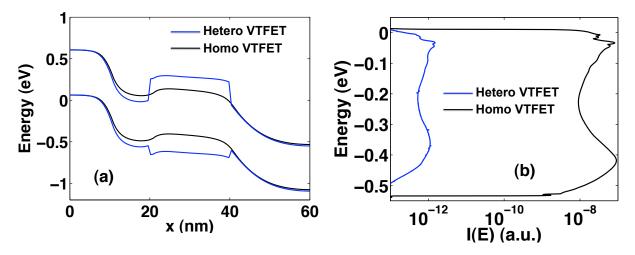

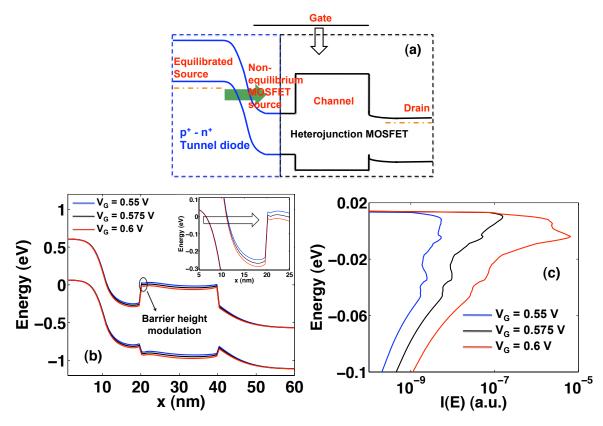

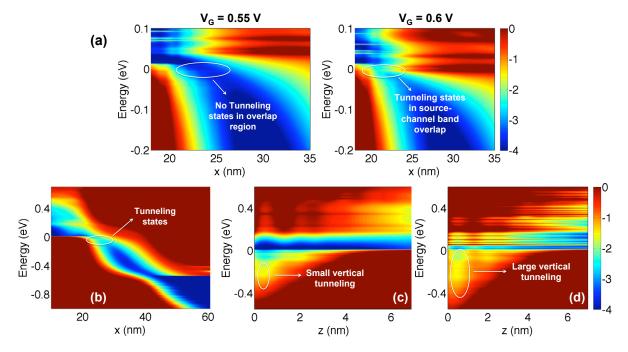

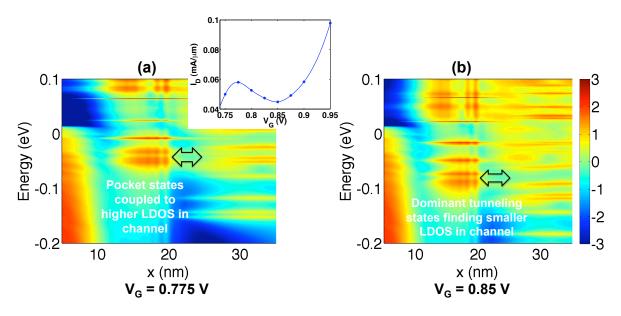

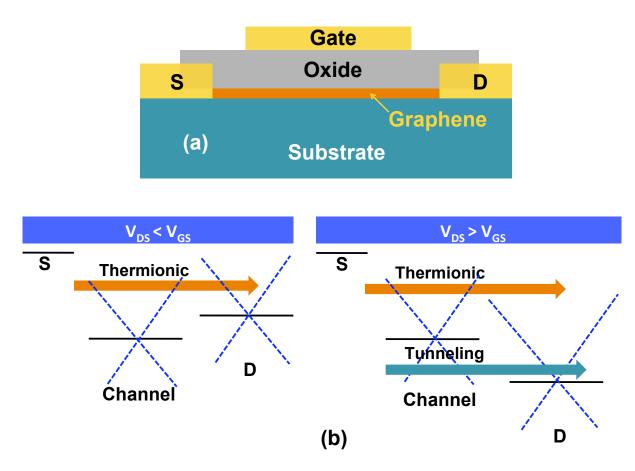

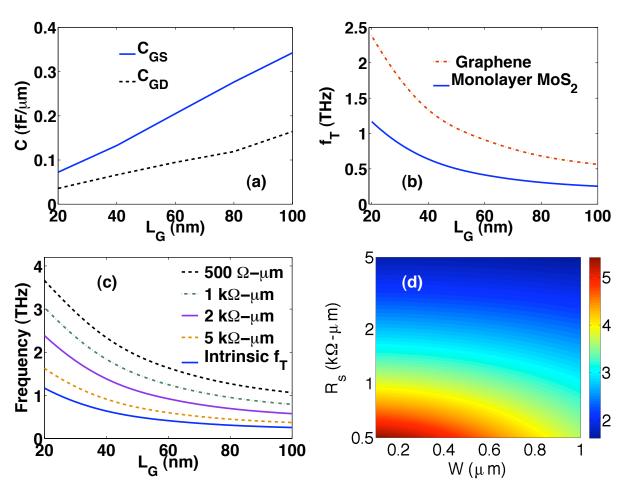

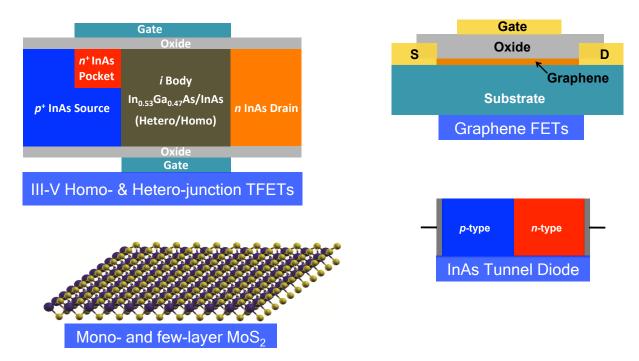

Investigating InAs short-channel band-to-band tunneling transistors (TFETs), we show that direct source-to-drain tunneling sets the leakage-floor in such devices, thereby limiting the minimum subthreshold swing (SS) in spite of excellent electrostatics. A heterojunction TFET with a halo doping in the source-channel overlap region is proposed and is shown to achieve steep SS as well as large ON current. We discover that by band-offset engineering, the steepness therein could be controlled primarily by the modulation of heterojunction-barrier. Subsequently, exploring layered materials for analog applications, we demonstrate that doping the drain underlap region in graphene FETs prolongs the onset of tunneling in their output characteristics, and hence significantly increases their output resistance  $(r_0)$  and intrinsic gain  $(g_m r_0)$ . Due to large bandgap, and consequently, large  $r_0$ , monolayer-MoS<sub>2</sub> FETs exhibit a significant enhancement in maximum oscillation frequency  $(f_{max})$  over their graphene counterparts.

### **TABLE OF CONTENTS**

| Chapter 1: Introduction                                                |    |

|------------------------------------------------------------------------|----|

| 1.1 Overview.                                                          | 1  |

| 1.2 Simulation of modern-day semiconductor devices                     |    |

| 1.3 Non-equilibrium Green's function based quantum transport           | 5  |

| 1.4 Quantum-mechanical tunneling.                                      | 7  |

| 1.5 Some relevant questions.                                           | 9  |

| 1.6 References.                                                        | 10 |

| Chapter 2: Berkeley Quantum Transport Simulator                        | 15 |

| 2.1 Overview.                                                          | 15 |

| 2.2 Device structures.                                                 | 16 |

| 2.3 Electronic structure capabilities.                                 | 16 |

| 2.3.1 The <i>k.p</i> method.                                           | 17 |

| 2.3.2 The semi-empirical tight-binding method.                         | 19 |

| 2.4 Self-consistent solution of Pöisson's and ballistic NEGF equations | 21 |

| 2.4.1 Pöisson's equation.                                              | 22 |

| 2.4.2 Ballistic NEGF equations.                                        | 23 |

| 2.5 Parallelization and Scaling.                                       | 25 |

| 2.6 References                                                         | 27 |

| Chapter 3: MOSFET simulations – Monolayer Molybdenum disulfide transis |    |

| exemplars                                                              |    |

| 3.1 Molybdenum disulfide                                               |    |

| 3.1.1 Material properties.                                             |    |

| 3.1.2 Transistors of monolayers                                        |    |

| 3.2 Short-channel MOSFET simulations                                   |    |

| 3.2.1 Extraction of parameters from experiments                        |    |

| 3.2.2 Simulation approach                                              | 33 |

| 3.3 Results and discussion.                                            | 34 |

| 3.3.1 Transfer characteristics                                         | 34 |

| 3.3.2 Output characteristics.                                          | 35 |

| 3.3.3 Extrapolation to diffusive regime                                | 35 |

| 3.3.4 Capacitance and density-of-states                                | 36 |

| 3.3.5 Gate oxide and contacts                                                                 | 38   |

|-----------------------------------------------------------------------------------------------|------|

| 3.4 Putting it all in perspective                                                             | 39   |

| 3.5 Summary                                                                                   | 40   |

| 3.6 References                                                                                | 40   |

| Chapter 4: Zener tunneling – Congruence between semi-classical and quantum ballist formalisms |      |

| 4.1 Semi-classical or quantum?                                                                |      |

| 4.2 Simulation approach                                                                       | 44   |

| 4.3 Results and discussion                                                                    | 45   |

| 4.3.1 Heavily doped junctions                                                                 | 45   |

| 4.3.2 Lightly doped junctions                                                                 | 46   |

| 4.3.3 Capturing non-uniformity using tight-binding WKB and modified Kane's model              | s 46 |

| 4.3.4 Comparison with tunnel diode data                                                       | 48   |

| 4.4 Summary                                                                                   | 49   |

| 4.5 References                                                                                | 49   |

| Chapter 5: Indium Arsenide lateral and vertical band-to-band tunneling transistors            | 52   |

| 5.1 Motivation                                                                                | 52   |

| 5.2 Geometry and simulation details                                                           | 52   |

| 5.3 Results and discussion                                                                    | 54   |

| 5.3.1 Transfer characteristics                                                                | 54   |

| 5.3.2 No vertical tunneling in ultra-thin films                                               | 55   |

| 5.3.3 Gate length scaling trends                                                              | 56   |

| 5.4 Summary                                                                                   | 57   |

| 5.5. References.                                                                              | 57   |

| Chapter 6: Heterojunction vertical tunneling transistors – Steep subthreshold swing v         |      |

| 6.1 Motivation.                                                                               |      |

| 6.2 Heterojunction VTFET – Simulation details.                                                |      |

| 6.3 Results and discussion.                                                                   |      |

| 6.3.1 Transfer characteristics                                                                |      |

| 6.3.2 OFF state behavior                                                                      |      |

| 6.3.3 Turn-on mechanism                                                                       |      |

| 6.3.4 Factors affecting steepness                                                             | 63   |

| 6.3.5 Negative transconductance.                                                  | 64       |

|-----------------------------------------------------------------------------------|----------|

| 6.4 Summary                                                                       | 65       |

| 6.5 References                                                                    | 65       |

| Chapter 7: Graphene transistors – Engineering tunneling to improve output resi    | stance67 |

| 7.1 Graphene transistors for non-digital applications                             | 67       |

| 7.2 Simulation approach                                                           | 68       |

| 7.3 Results and discussion                                                        | 69       |

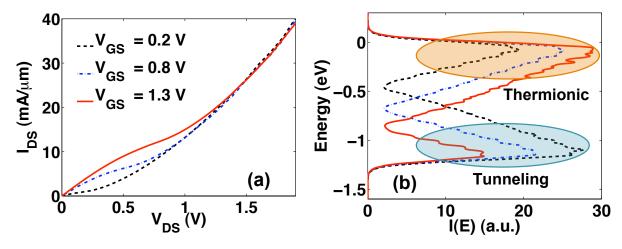

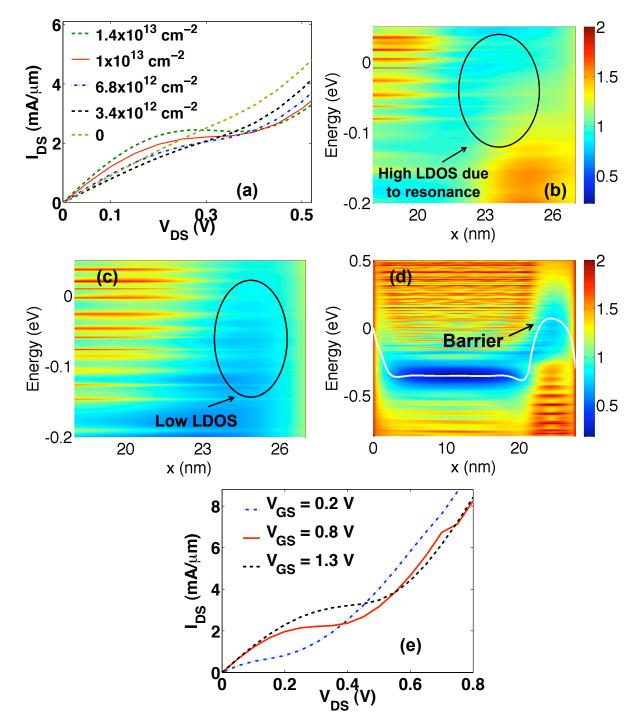

| 7.3.1 GFET output characteristics                                                 | 69       |

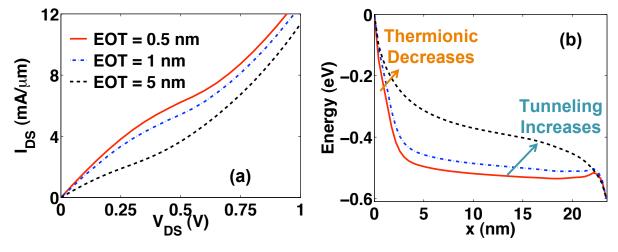

| 7.3.2 Effect of EOT                                                               | 70       |

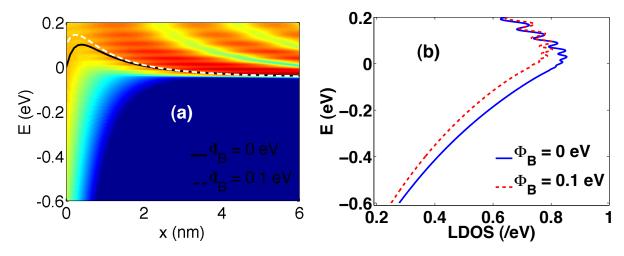

| 7.3.3 Effect of Schottky barrier height at the drain contact                      | 70       |

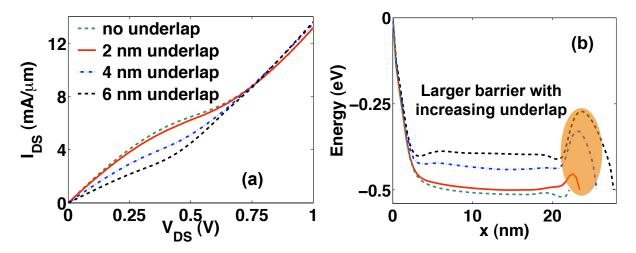

| 7.3.4 Effect of drain underlap length.                                            | 70       |

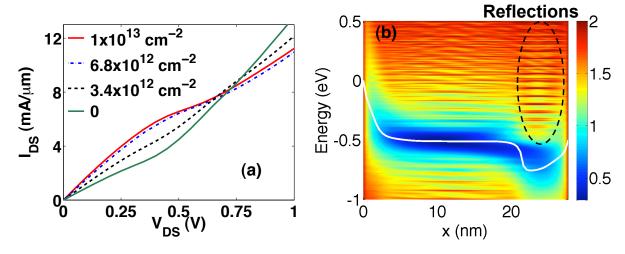

| 7.3.5 Effect of <i>n</i> -type doping in the drain underlap region                | 72       |

| 7.3.6 Effect of <i>p</i> -type doping in the drain underlap region                | 72       |

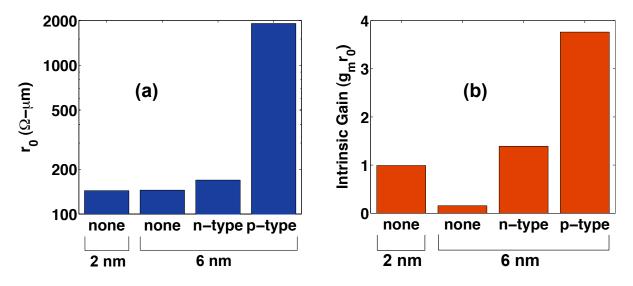

| 7.3.7 Output resistance and intrinsic gain                                        | 74       |

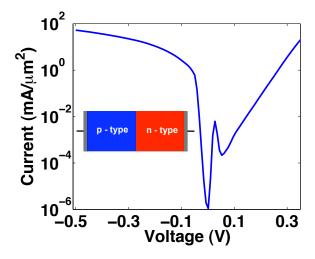

| 7.3.8 Are quasi-saturation and three-terminal NDR related?                        | 75       |

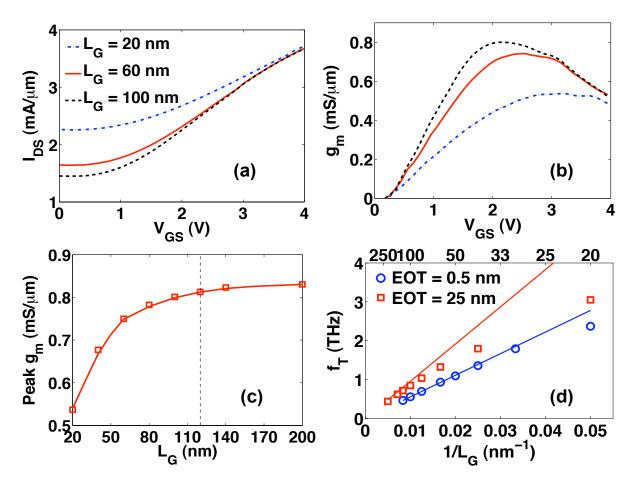

| 7.3.9 Effect of $L_G$ scaling on $f_T$                                            | 75       |

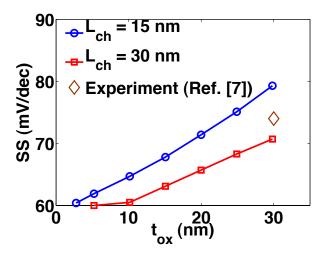

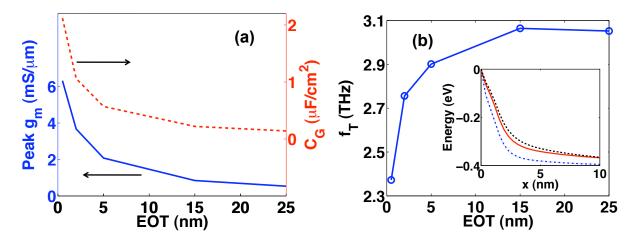

| 7.3.10 Effect of EOT scaling on $f_T$                                             | 77       |

| 7.3.11 Estimation of maximum oscillation frequency                                | 77       |

| 7.4 Summary                                                                       | 78       |

| 7.5 References                                                                    | 78       |

| Chapter 8: Monolayer MoS <sub>2</sub> transistors – Applications beyond switching | 81       |

| 8.1 Motivation and scope                                                          | 81       |

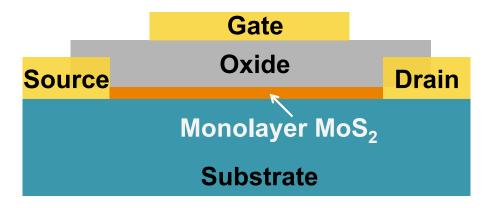

| 8.2 Simulation approach                                                           | 82       |

| 8.2.1 A two-band <i>k.p</i> Hamiltonian description of monolayer MoS <sub>2</sub> | 82       |

| 8.2.2 Geometry and other parameters                                               | 83       |

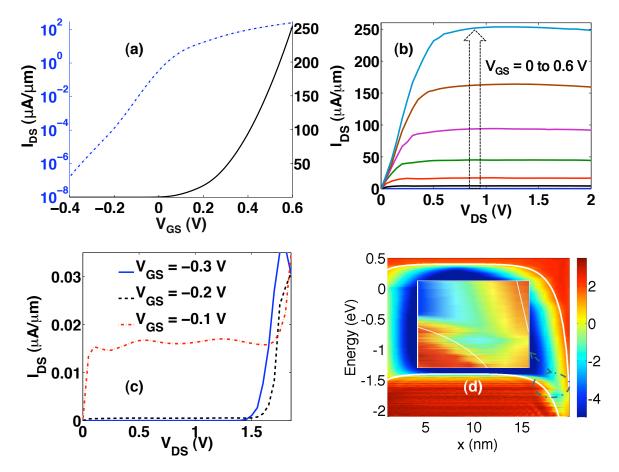

| 8.3 Results and discussion                                                        | 84       |

| 8.3.1 Transfer characteristics                                                    | 84       |

| 8.3.2 Output characteristics                                                      | 84       |

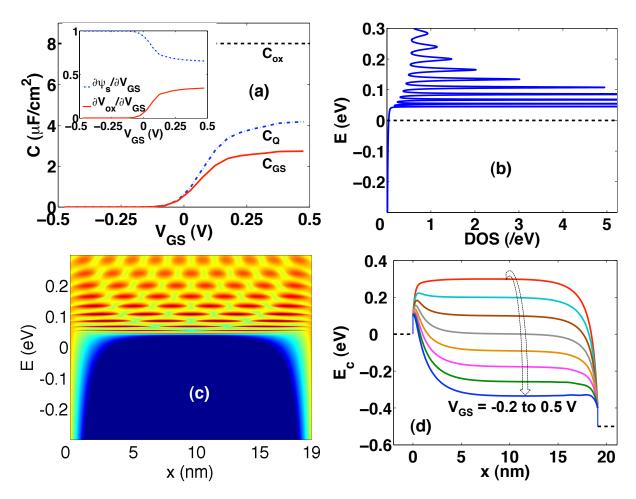

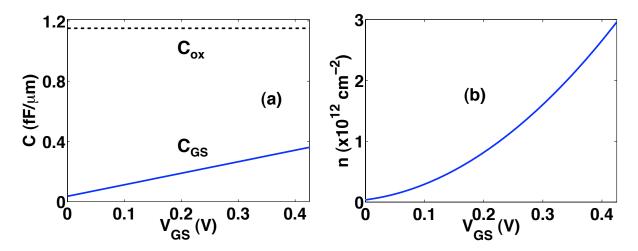

| 8.3.3 Capacitance characteristics                                                 | 84       |

| 8.3.4 Non-self-consistent calculations from bandstructure                         | 85       |

| 8.3.5 Scaling trends of $f_T$ and $f_{max}$                                       | 87       |

| 8 4 Summary                                                                       | 88       |

| 8.5 References                                                 | 88 |

|----------------------------------------------------------------|----|

| Chapter 9: Conclusions and future work                         | 91 |

| 9.1 Consolidating what we have learned so far                  | 91 |

| 9.1.1 Comparison between semi-classical and quantum formalisms | 91 |

| 9.1.2 Confinement effects                                      | 92 |

| 9.1.3 Level broadening effects                                 | 92 |

| 9.1.4 Insights in tunnel-FET design                            | 92 |

| 9.1.5 Tunneling insights in MOSFET-design                      | 93 |

| 9.2 Future directions                                          | 93 |

| 9.2.1 Dissipative transport                                    | 93 |

| 9.2.2 Density functional theory                                | 94 |

| 9.2.3 Incorporating gate tunneling and strain                  | 95 |

| 9.3 Epilogue                                                   | 95 |

| 9.4 References                                                 | 95 |

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to express my deepest sense of gratitude to my advisor, Professor Sayeef Salahuddin. It has been a great privilege to work with him and observe from close quarters the myriad ways in which he attacks a scientific problem. It would not be an overstatement to say that if it were not for his careful grooming during my formative years as a researcher, his constant encouragement to keep setting higher and higher standards for myself, his probing and insightful questions and suggestions, and his eye for new problems, this thesis would not have taken the shape it has today. I will forever remain grateful to him for all the learning experiences interactions with him and working in his group have offered me over the course of my Berkeley years.

I would like to thank Professors Ali Javey, Chenming Hu and Junqiao Wu for gladly accepting to be on my qualifying exam and dissertation committees, and for providing invaluable suggestions and comments during this course. Also, I would like to express my sincerest thanks to Professor Javey for all the help from time to time – often going out of his way – in addition to the learning opportunities I had as a research collaborator, and as a GSI for his class. I am also thankful to Professor Hu for all the interesting and stimulating discussions we had during the DARPA STEEP days, which is when my interest in tunneling phenomenon started blooming.

I am indebted to Professor Youngki Yoon, my long time collaborator, with whom I had the chance to work on a variety of research projects and to share my excitement about several small-but-pleasing discoveries along the way. I would also like to thank Professor Mark Lundstrom for some intriguing discussions we had during our collaboration on graphene transistors.

I am grateful to SRC Education Alliance and GlobalFoundries for the internship opportunity during the summer of 2012. I would like to thank Drs. Ajey Jacob and Bhagawan Sahu for mentoring me and providing a glimpse of industrial research, in addition to hosting me in Albany, NY and helping during the entire period in ways more than one. My sincere thanks are also due to Drs. Zoran Krivokapic and Steven Bentley for many a thought-provoking technical discussion on III-V transistors.

I am very thankful to Intel Corporation for the PhD Fellowship they offered me during 2012-13. In this context, I would like to thank Dr. Ian Young and my fellowship mentor, Dr. Uygar Avci, for opportunities they provided to present my research to their group both in person and via teleconferences. I am hugely indebted to Dr. Dmitri Nikonov for his very generous help in recommending me to the fellowship.

I have had the good fortune of interacting with some very bright and talented colleagues from LEED and Device groups in Berkeley, and of learning a great deal from them. In particular, I would like to express my thanks to Asif I. Khan, Khalid Ashraf, Debanjan Bhowmik, Samuel Smith, Varun Mishra, Rumi Karim, Nattapol Damrongplasit, Sriramkumar Venugopalan, Rehan Kapadia, Sapan Agarwal, Sung Hwan Kim and Peter Matheu for several interesting conversations at workplace, technical or otherwise.

Also, outside workplace, I was lucky enough to make some very good friends at Berkeley and in the bay area, all of who, in some way or the other, have helped me endure difficult times and have been instrumental in helping me gain a broad perspective on various aspects of life. I would like to express my heartfelt gratitude to Kaustubh Joshi, Pranav Shah, Sudeep Kamath, Pavan Hosur, Sudeep Juvekar, Rutooj Deshpande, Dhawal Mujumdar, Mangesh Bangar, Anuj Tewari, Shaama M. S., Sarika Goel, Sameer Agarwal, Deepan Raj Prabakar, Debanjan Mukherjee, Sharanya Prasad, Aditya Medury, Ankit Jain, Avinash Bharadwaj, Chintan Thakkar, Vivek Ramamurthy, Nitesh Jain, Arunanshu Roy, Venkatesan Ekambaram, Ashwin Kashyap, and Abhinav Gaikwad for being the wonderfully warm and genuine people they are.

And last but not the least, words fail me in conveying indebtedness to my parents – Ganapati Ramakrishna Bhat and Saraswati Bhat – whose love, affection, encouragement, and unflinching confidence in my abilities forever motivate me to keep striving for excellence in every endeavor. This work is a dedication to all their sacrifices that have brought me to where I am today.

#### CHAPTER 1

#### INTRODUCTION

In this chapter, we begin with a brief overview of the challenges and opportunities associated with low-power device-design. Subsequently, we examine the necessary considerations in choosing the electronic transport formalism to investigate next-generation of energy-efficient transistors. We then provide a summary of the non-equilibrium Green's function based quantum transport formalism, which is the approach we use during the course of this study. Finally, after examining various efforts reported in the literature on using tunneling as a means to achieving lower power consumption, we outline the questions that we hope to answer in the subsequent chapters.

#### 1.1 OVERVIEW

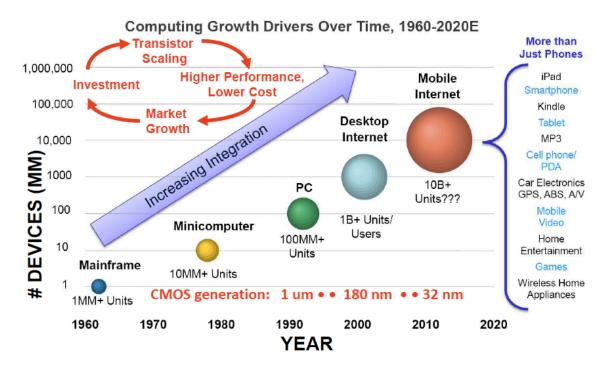

Over the past 40 years or so, microelectronics industry has seen an exponential growth. In accordance with Gordon Moore's observation in his 1965 paper, we have seen several cycles of transistor-scaling resulting in higher performance at lower cost, consequent fueling of market growth, and subsequent capital reinvestment in further research [1] (Fig.1.1). Today, we are seeing an *explosion* in two important respects - 1) the total number of mobile devices – smartphones, tablet PCs, gaming consoles to name a few – has been increasing rapidly; 2) the static power consumption – a negligible fraction of the total power consumed in earlier CMOS generations – is reaching alarming levels in the ultra-scaled, sub-100 nanometer technology nodes due to short-channel effects [2].

Figure 1.1. Evolution of computing market over the last five decades showing an exponential increase in number of electronic devices. Source: ITU, Mark Lipacis, Morgan Stanley Research.

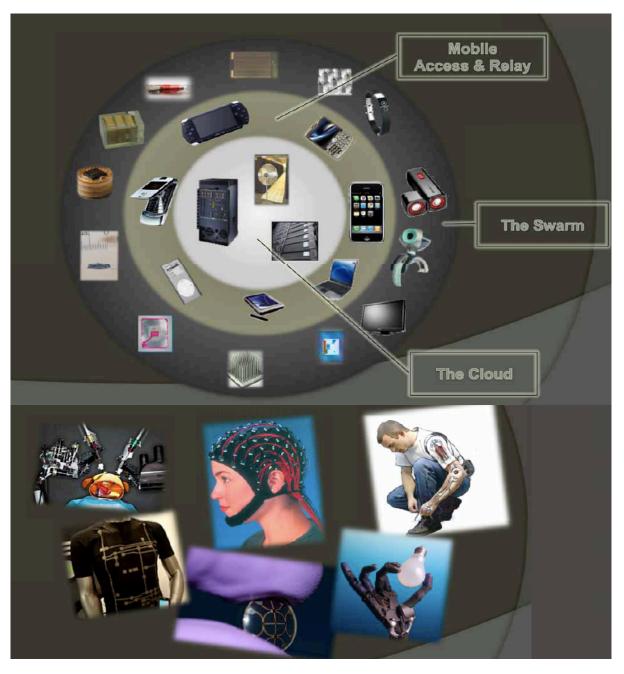

With the proliferation of technology and increase in people's computing needs, it can be expected that in future, demands on cloud computing, which fuels most of the high-performance computing today, would increase. Additionally, it is envisioned that we would reach an era of immersive computing where a large number of physically standalone devices (e.g., wireless sensor networks, wearable electronics) would augment our sensory perceptions of physical reality [3](Fig.1.2).

Thus, the motivation to investigate design of energy-efficient, low-power electronic devices and systems is threefold – (a) the global non-renewable, fossil fuel reserves are anticipated to deplete

Figure 1.2. A speculative view of the future of low-power electronics – a swarm of physically standalone devices increasing the number of ways in which we interact with our surroundings (top); a huge number of wearable devices (bottom), necessitating energy-efficient computing (adapted from Ref. [3]).

to discomfortingly low levels in the coming few decades; (b) the share of electronics in people's energy consumption requirements is increasing, and (c) the battery life of devices, particularly in cases such as medical implants (cochlear implant, artificial cardiac pacemaker etc.), wireless sensors deployed in remote areas to name a few, is critical. Hence it is unsurprising that, in addition to finding renewable, clean and sustainable ways of electric power generation as a means to address some of the above concerns, a great volume of research is directed towards designing next-generation of power-parsimonious electronics through innovations not only at the transistor level, but also at circuit and system levels [4]-[6].

In this thesis, however, our focus will be on underlining issues and challenges at the former level and on investigating opportunities that a combination of low-dimensional material-systems and non-conventional switching mechanisms provides in achieving that goal. The following explanatory points are in order here –

Firstly, in appreciating the underlying bottlenecks in any engineering design problem, it is imperative that we make the following distinction between two loosely defined classes of challenges. The first class is categorized by issues that are either fundamental to the physical mechanism of interest or are due to some intrinsic, difficult-to-tune properties of the materials under consideration – e.g., Boltzmann tyranny in conventional metal-oxide-semiconductor fieldeffect transistors (MOSFETs), leakage current limitations due to absence of bandgap in graphene etc. [7]. The second category is those of challenges that are more closely associable with translation of a proof-of-concept or theoretical demonstration to a commercially viable technology - e.g., CMOS process compatibility, lithography-related scaling issues etc. While we do not undermine the importance of addressing the second class of problems, our motivation to focus on the first category is guided by the following heuristics – (a) in identifying challenges and opportunities for technologies distantly away on the roadmap, it is of practical significance to focus on this class so that the vast exploration-space is sufficiently narrowed, and (b) our experience - gained as a community over the past decades in driving Moore's law - gives reasons to be optimistic of overcoming challenges of second kind, provided the promised gains of a given scientific idea command its technologization.

Secondly, guided by the same spirit, this work – barring occasions when we either compare with or provide explanations to experimental observations – draws heavily upon simulation, which has emerged as the third pillar of scientific enquiry – theory and experiment being the other two – enabling headways in problems considered resistive to latter approaches [8]. While there exist several interesting physical problems – the celebrated spin-glass problem and computation of the universal functional in density functional theory being the classic exemplars – which have been shown to be computationally intractable (with increasing degrees of freedom) using classical computers, most problems of interest to us in electronic transport simulation – which involve low-energy excitations of a quantum many-body system – do not fall into this category and are amenable to perturbative methods with certain approximations [9]-[11]. The theoretical framework for our simulation will be described in greater detail in subsequent sections.

#### 1.2 SIMULATION OF MODERN-DAY SEMICONDUCTOR DEVICES

The need to accurately predict device performance via simulations has, perhaps, never been as important as it is today, with fabrication complexity of modern-day semiconductor devices continuously increasing, resulting in several challenges relating to yield and variability.

However, even in the simulation domain, there exist considerable issues concerning computation time and memory requirements.

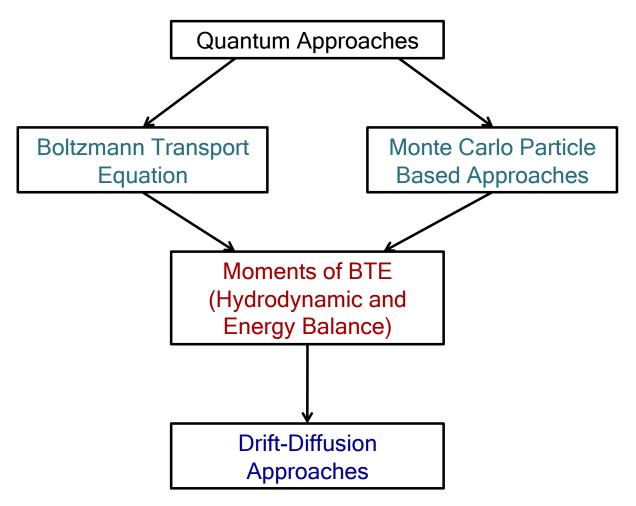

The choice of theoretical formalism for electronic transport simulation is governed by two factors – a) the critical spatial dimension of the problem; this could be, among other things, the channel length of a bulk metal-oxide-semiconductor field-effect transistor (MOSFET) or the body thickness of an ultra-thin body device, and b) the physical mechanism of device operation e.g., tunneling, thermionic injection etc. Figure 1.3 depicts the commonly used transport formalisms in a hierarchical manner. For an overview and detailed exposition on various simulation approaches, the readers are urged to refer to resources such as Refs. [13]-[15]; here, however, we highlight some key considerations that guide our choice of quantum transport approach.

From a computational viewpoint, the drift-diffusion approach – obtained using first moment of the Boltzmann transport equation (BTE) – is the simplest and hence, has been the workhorse of various commercial technology computer aided design (TCAD) packages [16]-[18]. While this provides a fairly accurate description of carrier transport in long-channel, scattering-dominated

Figure 1.3. Hierarchical overview of the prominent electronic transport formalisms, with the most rigorous and computationally intensive quantum approaches at the top and the most scalable drift-diffusion methods at the bottom (adapted from Ref. [12]).

(diffusive) devices wherein the electric fields are small, it fails to capture hot-carrier effects like velocity overshoot, that affect the device performance considerably in the sub-100 nm channel-length regime [19]. In order to account for these, one needs to move to hydrodynamic and energy-balance models, which happen to be higher moments of BTE. However, moment-based solutions to BTE lose their validity with increase in electric field strength and could result in spurious velocity peaks due to truncation of moments – which, in theory, are infinite in number – to a finite number [20].

The resolution of issues arising due to these continuum models of transport is achieved by solving the full-blown BTE itself, wherein the most common approach is using particle-based Monte Carlo methods – discussed extensively in literature viz. Refs. [21], [22]. While these techniques provide a reliable and accurate way to understand transport behavior in ultra-scaled transistors, including phenomenon like self-heating – common in silicon-on-insulator (SOI) devices – their correctness is still limited to the semi-classical regime i.e., when the electrostatic potential within the device is varying smoothly on the order of the quasi-particle De Broglie wavelength. With device dimensions continuously shrinking, present-generation transistors are already at a stage where, in certain non-silicon material-systems like III-V semiconductors with much smaller carrier effective mass, the semi-classical approximation is breaking down. This, coupled with our interest in leveraging tunneling – a phenomenon with no classical analogue – for low-power device design, motivates us to adopt the most computation-intensive quantum transport approaches. We describe one such formalism – non-equilibrium Green's function (NEGF) in the subsequent section, which we use throughout the rest of the report for simulation purposes.

#### 1.3 NON-EQUILIBRIUM GREEN'S FUNCTION BASED QUANTUM TRANSPORT

Non-equilibrium Green's function (NEGF) approach is a generic theoretical framework for investigating quantum-mechanical systems far from equilibrium. With device dimensions believed to enter the sub-10 nm regime in the near future, it has emerged as the most acceptably rigorous way to understand carrier transport mechanisms at such length-scales [23]. A detailed introduction to the fundamentals of the formalism – developed through the seminal works on quantum many-body physics of Martin and Schwinger [24], Kadanoff and Baym [25], Keldysh [26] – can be found in Refs. [23] and [27]. Here we only provide a brief overview of the formalism for the sake of completeness.

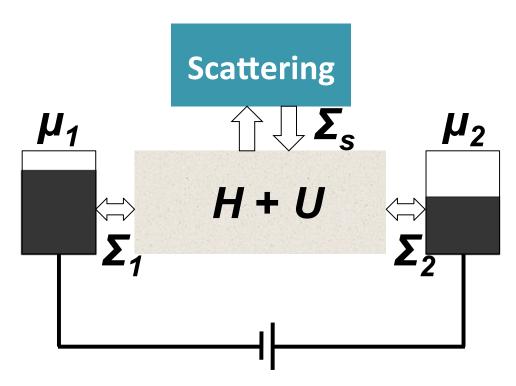

In a nutshell, NEGF is a compact scheme for determining the response of an open system – typically driven outside equilibrium – which couples to external reservoirs with which it can exchange quasi-particles like electrons (e.g., in case of an electrochemical cell), photons (a light source), phonons (crystal lattice) etc. While esoteric scenarios involving reservoirs themselves being driven out of equilibrium could, in principle, be handled within the framework, in cases of our interest, the equilibrium assumption on reservoirs suffices. This implies we can assign equilibrium ensemble-measures such as electrochemical potential ( $\mu$ ) and temperature (T) to them. However, such assignments are not made for the system (device), which is assumed to be *small* enough so that similar statistics do not hold.

Figure 1.4 shows the schematic representation of a nanoscale electronic device whose transport properties we are interested in modeling. The device region is modeled using its Hamiltonian (H), represented in some basis of choice. The word *bottom-up* in the title of this dissertation

refers to the fact that, in this formalism, we could build up a description of the entire device from that of the constituent atoms and/or molecules. This gives us a straightforward way to incorporate particle-particle interactions. In contrast, *top-down* approaches rely primarily on a continuum approximation and hence the handling of such phenomena therein becomes ad-hoc.

For interesting cases, the device is coupled to at least a pair of electron reservoirs (contacts) and, in some cases, also to a phonon bath resulting in scattering at finite temperatures. For every such coupling, there is an associated self-energy ( $\Sigma$ ), which describes the potential felt by a carrier due to interaction with the reservoir. More rigorously, from a quantum-field-theoretic perspective, self-energy represents the first-order perturbative electron-electron interaction and the renormalization of electronic states in the device due to this. This is expressed succinctly by the Dyson's equation, given by  $-G = G_0 + G_0 \Sigma G$ , where G and  $G_0$  are respectively the Green's function of the open and isolated (device-only) systems [28]. Consequently, each of the stationary states (eigenvalues of the isolated system), which are sharply defined discrete levels, gets broadened out due to coupling with contacts. The broadening (whose extent in energy is denoted by  $\Gamma$ ) is due to the finiteness of lifetime of carriers (since they can *escape* to contacts after a certain period), which is proportional to the imaginary part of  $\Sigma$ . The Green's function equations involving the retarded Green's function (G) and the electron correlation function (G<sup>n</sup>) are most commonly solved in the frequency (equivalently, energy) domain thus implicitly accounting for two-point correlations in time. The quantities of interest such as charge density and total current are obtained by suitable integration over energy and other variables.

Figure 1.4. Schematic of the nanoscale device system whose electronic transport properties we are interested in modeling. The electronic reservoirs – denoted by their respective electrochemical potentials – and phonon bath, which contributes to some of the dominant scattering mechanisms in the channel, are depicted. Their effects are captured through respective self-energies.

The electrostatic potential (U) is another important piece of the puzzle due to our interest far away from equilibrium where its effect is non-negligible. As long as device dimensions are not extremely small, to the extent of rendering the single-electron charging energy  $(U_0)$  to be larger than contact-induced broadening  $(\Gamma)$  and thermal broadening  $(k_BT)$ , with  $k_B$  being the Boltzmann constant) – the well-known self-consistent field (SCF) regime – we can include U in the Green's function calculations through self-consistent solutions of NEGF and Poisson's equations. We shall turn to discussion of equations and the associated computational challenges in a detailed manner in Chapter 2. However, for the remainder of this chapter, we will focus our discussion on yet another key topic in the title, tunneling, which happens to be the common thread across several pieces of this work.

#### 1.4 QUANTUM-MECHANICAL TUNNELING

Tunneling is, arguably, one of most extensively studied quantum-mechanical phenomena ever since the advent of quantum mechanics in earlier part of the previous century. Experimental evidence of tunneling – a manifestation of the wave-particle duality, with particle having a decaying-but-finite probability in the classically forbidden region – has been observed in a plethora of physical systems – from condensed-matter to high-energy. Needless to say, a large number of practical applications have been built leveraging tunneling, some of which we shall discuss briefly in the remainder of this section and hence motivate the readers towards the role of tunneling in recent low-power device-design efforts.

In solids, tunneling comes about in various flavors depending on -a) the quasi-particle under consideration – electron- and hole-tunneling in semiconductors, tunneling of Cooper pairs in superconducting Josephson junctions; b) the initial and final states of the carriers – band-to-band tunneling, intra-band tunneling; c) shape of the potential barrier through which tunneling occurs - Fowler-Nordheim tunneling, direct tunneling (most commonly in tunneling through gate-oxide of modern-day MOSFETs); d) the mediator for tunneling – trap-, impurity- and phonon-assisted tunneling; e) the number of tunnel-barriers – resonant tunneling, second and higher-order cotunneling effects in cascaded tunnel junctions (commonly in quantum-dots and single-electron transistors (SETs)) [29]-[32]. Each of these mechanisms is interesting in its own right and has ramifications in real-world applications – e.g., gate-oxide tunneling is one of the major leakage and oxide-degradation mechanisms posing OFF-state current and reliability concerns in ultrascaled FETs, the negative-differential resistance (NDR) in current-voltage characteristics of III-V resonant tunneling diodes could be used for electrical gain in optoelectronic devices, cotunneling is a source of errors in SETs, among others [33]-[35]. However, our primary focus in this report will be on band-to-band tunneling i.e., carrier tunneling from valence to conduction band of a semiconductor, which has emerged as a mechanism to design low-power transistors in recent times.

The first theoretical investigation of tunneling in solids (for 1-D case) was done by Clarence Zener, where he calculated the probability of transition of carriers into excited bands under high electric fields [36]. Subsequently, Keldysh and Kane calculated the tunneling rate for the case of constant electric field across a *p-n* junction, with the inclusion of transverse crystal momenta – conserved during tunneling – in their treatments [37], [38]. In addition, their calculations involved greater rigor in terms evaluating the action integral near the branch point – where conduction and valence bands merge for some imaginary wavevector – thereby accurately

computing the transition rates. However, the closed-form, analytical expressions derived by them in case of direct bandgap semiconductors hold only under the approximations of semiclassicality and of parabolic dispersion in both conduction and valence bands. In a later paper, Kane extended his treatment to the case of indirect tunneling – where the transitions occur across the indirect bandgap with the emission or absorption of phonons – resulting in an expression similar to the direct tunneling case [39]. This, together with his discussion on extension of these arguments to include effects such as variable field, non-parabolicity of electronic structure, presence of bandgap states etc. formed the mainstay of our understanding of tunneling and its modeling, in various forms, in TCAD device simulators until fairly recently when we could investigate the phenomenon in the full quantum-mechanical sense, in realistic device dimensions with a sufficiently elaborate electronic structure description.

On the experimental front, the one of the first demonstrations of tunneling was by Esaki in forward-biased, heavily doped, narrow germanium *p-n* junctions [40]. Since then, the robustness of tunneling phenomenon in two-terminal devices as been comprehensively established with its observation in a wide range of ranging from III-V homo- and hetero-junctions (Refs. [41]-[43]), graphene and its nanostructures (Refs. [44], [45]), oxides of rare earth metals (Ref. [46]), superlattices (Ref. [47]) to name a few. Consequently, the effect has been used for various applications – both in forward- (NDR region) and reverse-bias regimes – such as in voltage regulators, high-speed microwave circuits, multi-junction solar cells, lasers etc [48], [49].

One of the earliest proposals to leverage tunneling in a three-terminal device is due to Chang and Esaki, who put forth the idea of a tunneling-base transistor wherein the relatively short tunneling time in the base was expected to increase the current gain [50]. However, requirements of right heterostructure band-offsets and device dimensions imposed severe restrictions on fabrication. Later, Quinn et al. suggested voltage-controlled modulation of tunneling probability by replacing the doping of a MOSFET source from  $n^+$ - to  $p^+$ -type – a structure investigated widely in subsequent years in the context of low subthreshold swing (SS) devices – as spectroscopic tool to probe 2-D channel states [51]. The experimental demonstrations of field-effect-dependent tunneling behavior were done by Baba in GaAs-based  $p^+$ -p- $n^+$  devices [52] and later by Koga and Toriumi in a Si system [53], who showed, along the lines of the bipolar tunnel FET proposed by Leburton et al. [54], a modulation of the NDR region with changing gate voltage.

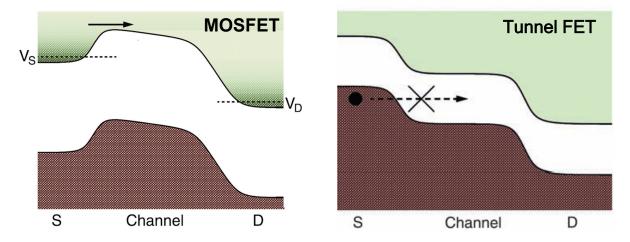

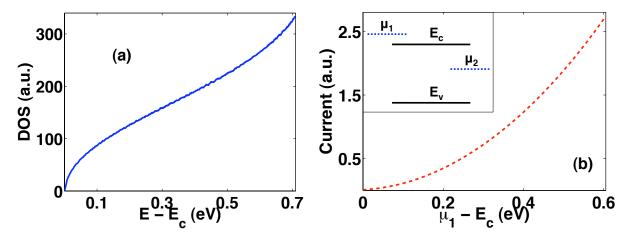

The idea behind using band-to-band tunneling transistors, the discussion of which will form a significant portion of this study, is that the crossing and uncrossing of conduction and valence bands in close spatial proximity – the same phenomenon that gives rise to NDR in two-terminal junctions – can be effectively modulated using gate-induced vertical field in an MOS structure. The ability of such devices to circumvent *Boltzmann tyranny* arises from the fact that the carrier concentration on the source side (e.g., degenerately doped p-type material) follows a non-Boltzmann-like (and hence non-equilibrium) distribution due to clipping of part of the Fermi-tail due to the semiconductor bandgap (Fig. 1.5). Appenzeller et al. provided the first experimental confirmation of using this concept to achieve less than 60 mV/decade of SS at room temperature through carbon nanotube tunneling field-effect transistors (TFETs) that exhibited 40 mV/decade swing [56]. Some of the earliest results showing less than 60 mV/decade SS in other material systems have been by Choi et al. in Si TFETs [57], by Krishnamohan et al. in Ge [58], and by Kim et al. in  $p^+$  Ge/ $n^+$  Si devices [59]. For a more comprehensive overview on the status of TFET research until circa 2010, the readers are suggested to refer to the review article by

Seabaugh and Zhang [60] and the references therein. However, here we present a summary of the major challenges in order to motivate our studies in the upcoming chapters.

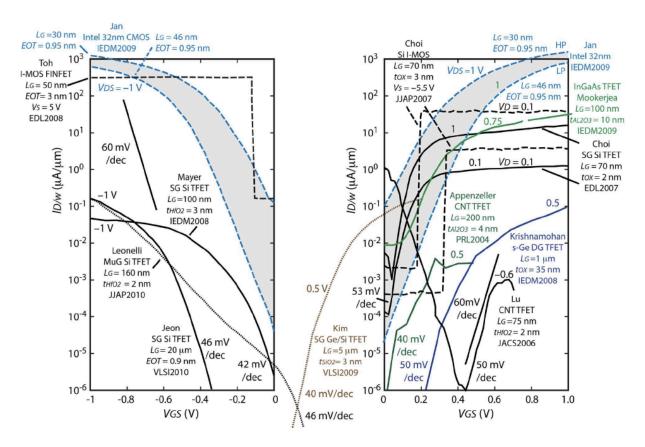

Figure 1.6 (Fig. 2 of Ref. [60]) shows the experimental switching characteristics of both *p*- and *n*-channel TFETs reported in various studies compared against those of the state-of-the-art 32-nm conventional CMOS technology. It is imperative to infer that on the experimental front, the TFETs are at a fairly nascent stage in becoming a viable alternative for next-generation low-power technologies – a) reliable, reproducible results exhibiting less than 60 mV/decade have been few; b) due to the very nature of TFETs – huge tunneling resistance in ON state – the ON current is significantly less; c) the ON-OFF ratios in devices with large ON current – III-V-based TFETs in particular – are severely degraded; d) the SS, even in cases where they are than 60 mV/dec, have been mostly in the range of 40-50 mV/decade. However, simulation studies on TFETs (e.g. Refs. [61]-[64]), primarily the ones using semi-classical formalisms – WKB, Kane and their variants to name a few – have been overly optimistic in their projections of device performance in general and SS, ON current and ON-OFF ratios in particular (refer to Fig. 3 of Ref. [60] for an overview of various TFET-simulation reports).

#### 1.5 SOME RELEVANT QUESTIONS

Given this context, it becomes pertinent to answer the following questions – a) with a rigorous representation of the atomistic properties of the system, what kind of device performance could be expected? b) Are there any fundamental bottlenecks or design trade-offs that are not manifestly apparent through simpler models? c) Under what conditions/ length-scales does the correspondence between semi-classical and quantum formalisms of tunneling hold? d) How do the effects of confinement and level broadening affect TFET design considerations? e) Can the insights on tunneling, gleaned from understanding TFETs, be used to design better MOSFETs for non-switching applications in certain novel material-systems? The quest for answers to these questions guides our discussion in the remainder of this report. Before we jump into the specific device physics aspects, we shall take a detour in Chapter 2 to detail the development of a

Figure 1.5. Schematic showing the physical mechanisms of operation of MOSFET (left) and Tunnel FET (right) (adapted from Ref. [55]). MOSFETs operate through thermionic emission over the barrier in the channel and thus have a fundamental limit in the steepness of switching. TFETs cut-off part of the Fermi-Dirac distribution of carriers in the source through the bandgap and hence overcome this limitation.

Figure 1.6. Experimental switching characteristics of *p*-type (left) and *n*-type (right) TFETs from various studies that have reported SS of less than 60 mV/decade (from Ref. [60]). The characteristics for state-of-the-art 32-nm node CMOS technology are also shown for the purposes of comparison.

massively parallel, NEGF-based quantum transport simulator that we use to address the above questions.

#### 1.6 REFERENCES

- [1] G. E. Moore, "Cramming more components onto integrated circuits," *Electronics Magazine*, vol. 38, no. 8, 1965.

- [2] N. S. Kim, T. Austin, D. Baauw, T. Mudge, K. Flautner, J. S. Hu, and V. Narayanan, "Leakage current: Moore's law meets static power," *Computer*, vol. 36, no. 12, pp. 68-75, 2003.

- [3] J. M. Rabaey, "The swarm at the edge of the cloud-A new perspective on wireless," *IEEE Symp. on VLSI circuits (VLSIC)*, pp. 6-8, 2011.

- [4] E. A. Vittoz, "Low-power design: ways to approach the limits," *International Solid-State Circuits Conference (ISSCC) Tech. Dig.*, pp. 14-18, 1994.

- [5] J. M. Rabaey, "Low power design essentials," Springer, 2009.

- [6] D. Markovic, C. C. Wang, L. P. Alarcon, T. -T. Liu, and J. M. Rabaey "Ultralow-power design in near-threshold region," *Proc. IEEE*, vol. 98, no. 2, pp. 237-252, 2010.

- [7] S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," *Nano Lett.*, vol. 8, no. 2, pp. 405-410, 2008.

- [8] L. P. Kadanoff, "Excellence in computer simulation," *Comput. Sci. Eng.*, vol. 6, no. 2, pp. 57-67, 2004.

- [9] R. B. Laughlin, "The physical basis of computability," *Comput. Sci. Eng.*, vol. 4, no. 3, pp. 27-30, 2002.

- [10] S. Aaronson, "Computational complexity: Why quantum chemistry is hard," *Nat. Phys.*, vol. 5, no. 10, pp. 707-708, 2009.

- [11] M. M. Wolf, "Quantum many-body theory: Divide, perturb and conquer," *Nat. Phys.*, vol. 4, no. 11, pp. 834-835, 2008.

- [12] D. Vasileska (2001, Spring), "Introduction to Modeling," [Online]. Available: http://www.eas.asu.edu/~vasilesk/EEE533/lecture2.ppt

- [13] D. Vasileska, D. Mamaluy, H. R. Khan, K. Raleva and S. M. Goodnick, "Semiconductor Device Modeling," *J. Comput. Theor. Nanos.*, vol. 5, no. 6, p. 999, 2008.

- [14] M. Lundstrom, "Fundamentals of carrier transport," Cambridge University Press, 2009.

- [15] S. Datta, "Electronic transport in mesoscopic systems," Cambridge University Press, 1997.

- [16] S. Selberherr, H. Stappel and E. Strasser, "Simulation of Semiconductor Devices and Processes," *Springer*, vol. 5, 1993.

- [17] Taurus Medici: Medici User Guide, Version A-2007.12, Mountain View, California: Synopsys, Inc., 2007.

- [18] Sentaurus Device User Guide, Version Z-2007.03, Mountain View, California: Synopsys, Inc., 2007.

- [19] K. Raleva, D. Vasileska, S. M. Goodnick and T. Dzekov, "Modeling thermal effects in nano-devices," *IEEE Trans. Electron Devices*, vol. 55, no. 6, pp. 1306-1316, 2008.

- [20] T. Grasser and S. Selberherr, "Limitations of hydrodynamic and energy-transport models," *Proc. SPIE*, vol. 1, pp. 584-591, 2002.

- [21] C. Jacoboni and L. Reggiani, "The Monte Carlo method for the solution of charge transport in semiconductors with applications to covalent materials," *Rev. Mod. Phys.*, vol. 55, no. 3, p. 645, 1983.

- [22] K. Hess, "Monte Carlo Device Simulation: Full Band and Beyond," *Kluwer Academic Publishing*, Boston, 1991.

- [23] M. P. Anantram, M. S. Lundstrom and D. Nikonov, "Modeling of Nanoscale Devices," *Proc. IEEE*, vol. 96, no. 9, pp. 1511-1550, 2009.

- [24] P. C. Martin and J. Schwinger, "Theory of many-particle systems I," *Phys. Rev.*, vol. 115, no. 6, pp. 1342-1373, 1959.

- [25] L. P. Kadanoff and G. Baym, "Quantum statistical mechanics: Green's functionmethods in equilibrium and nonequilibrium problems," *Benjamin*, New York, 1962.

- [26] L. V. Keldysh, "Diagram technique for nonequilibrium processes," *Sov. Phys.– JETP*, vol. 20, no. 4, pp. 1018-1026, 1965.

- [27] S. Datta, "Quantum transport: atom to transistor," Cambridge University Press, 2005.

- [28] F. J. Dyson, "The S Matrix in Quantum Electrodynamics," *Phys. Rev.*, vol. 75, no. 11, pp. 1736-1755, 1949.

- [29] B. D. Josephson, "Possible new effects in superconductive tunneling," *Phys. Lett.*, vol. 1, no. 7, pp. 251-253, 1962.

- [30] R. H. Fowler and L. Nordheim, "Electron Emission in Intense Electric Fields," *Proc. R. Soc. Lond. A*, vol. 119, no. 781, pp. 173-181, 1928.

- [31] W. Schattke and G. K. Birkner, "Theory for Impurity Assisted Tunneling," *Z. Physik*, vol. 252, no. 1, pp. 12-24, 1972.

- [32] D. V. Averin and Y. V. Nazarov, "Virtual electron diffusion during quantum tunneling of the electric charge," *Phys. Rev. Lett.*, vol. 65, no. 19, pp. 2446-2449, 1990.

- [33] W. -C. Lee and C. Hu, "Modeling CMOS Tunneling Currents Through Ultrathin Gate Oxide Due to Conduction- and Valence-Band Electron and Hole Tunneling," *IEEE Trans. Electron Devices*, vol. 48, no. 7, pp. 1366-1373, 2001.

- [34] T. J. Slight and C. N. Ironside, "Investigation Into the Integration of a Resonant Tunnelling Diode and an Optical Communications Laser: Model and Experiment," *IEEE J. Quantum Elect.*, vol. 43, no. 7, pp. 580-587, 2007.

- [35] T. A. Fulton and G. J. Dolan, "Observation of single-electron charging effects in small tunnel junctions," *Phys. Rev. Lett.*, vol. 59, no. 1, pp. 109-112, 1987.

- [36] C. Zener, "A Theory of the Electrical Breakdown of Solid Dielectrics," *Proc. R. Soc. Lond. A*, vol. 145, no. 855, pp. 523-529, 1934.

- [37] L. V. Keldysh, "Behavior of Non-Metallic Crystals in Strong Electric Fields," *Soviet Phys. JETP*, vol. 6, no. 33, pp. 763-770, 1958.

- [38] E. O. Kane, "Zener Tunneling in Semiconductors," J. Phys. Chem. Solids, vol. 12, no. 2, pp. 181-188, 1960.

- [39] E. O. Kane, "Theory of Tunneling," J. Appl. Phys., vol. 32, no. 1, pp. 83-91, 1961.

- [40] L. Esaki, "New Phenomenon in Narrow Germanium *p-n* Junctions," *Phys. Rev.*, vol. 109, no. 2, pp. 603-604, 1958.

- [41] C. A. Burrus, "Gallium Arsenide Esaki Diodes for High-Frequency Applications," *J. Appl. Phys.*, vol. 32, no. 6, pp. 1031-1036, 1960.

- [42] D. A. Collins, D. Z. -Y. Ting, E. T. Yu, D. H. Chow, J. R. Söderström, Y. Rajakarunanayake, T. C. McGill, "Interband tunneling in InAs/GaSb/AlSb heterostructures," *J. Cryst. Growth*, vol. 111, no.1-4, pp. 664-668, 1991.

- [43] J. Zimon, Z. Zhang, K. Goodman, H. Xing, T. Kosel, P. Fay and D. Jena, "Polarization-Induced Zener Tunnel Junctions in Wide-Band-Gap Heterostructures," *Phys. Rev. Lett.*, vol 103, no. 2, pp. 026801-04, 2009.

- [44] V. H. Nguyen, A. Bournel, and P. Dollfus, "Large peak-to-valley ratio of negative-differential-conductance in graphene *p-n* junctions," *J. Appl. Phys.*, vol. 109, no. 9, pp. 093706-10, 2011.

- [45] H. Cheraghchi, and K. Esfarjani, "Negative differential resistance in molecular junctions: Application to graphene ribbon junctions," *Phys. Rev. B*, vol. 78, no. 8, pp. 085123-30, 2008.

- [46] Y. F. Guo, L. M. Chen, M. Lei, X. Guo, P. G. Li, J. Q. Shen and W. H. Tang, "Tunnelling current in YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7-8</sub>/Nb-doped SrTiO<sub>3</sub> heterojunctions," *J. Phys. D: Appl. Phys.* vol. 40, no. 15, pp. 4578-81, 2007.

- [47] E. F. Schubert, J. E. Cunningham, and W. T. Tsang, "Perpendicular electronic transport in doping superlattices," *Appl. Phys. Lett.*, vol. 51, no. 11, pp. 817-819, 1987.

- [48] M. Baudrit and C. Algora, "Tunnel Diode Modeling, Including Nonlocal Trap-Assisted Tunneling: A Focus on III–V Multijunction Solar Cell Simulation," *IEEE Trans. Electron Devices*, vol. 57, no. 10, pp. 2564-71, 2010.

- [49] T. Knodl, M. Golling, A. Straub, R. Jager, R. Michalzik, K. J. Ebeling, "Multistage bipolar cascade vertical-cavity surface-emitting lasers: theory and experiment," *IEEE J. Quantum Elect.*, vol. 9, no. 5, pp. 1406-1414, 2003.

- [50] L. L. Chang and L. Esaki, "Tunnel triode-a tunneling base transistor," *J. Appl. Phys.*, vol. 31, no. 10, pp. 687-689, 1977.

- [51] J. J. Quinn, G. Kawamoto and B. D. McCombe, "Subband Spectroscopy by Surface Channel Tunneling," *Surf. Sci.*, vol. 73, no. 1, pp. 190-196, 1978.

- [52] T. Baba, "Proposal for Surface Tunnel Transistors," *Jpn. J. Appl. Phys.*, vol. 31, no. 4B, pp. L455-L457, 1992.

- [53] J. Koga and A. Toriumi, "Negative differential conductance in three-terminal silicon tunneling device," *App. Phys. Lett.*, vol. 69, no. 10, pp. 1435-37, 1996.

- [54] J. P. Leburton, J. Kolodzey, and S. Briggs, "Bipolar tunneling field-effect transistor: A three-terminal negative differential resistance device for high-speed applications," *J. Appl. Phys.*, vol. 52, no. 19, pp. 1608-1610, 1988.

- [55] T. N. Theis and P. M. Solomon, "It's Time to Reinvent the Transistor!" *Science*, vol. 327, no. 5973, pp. 1600-1601, 2010.

- [56] J. Appenzeller, Y.-M. Lin, J. Knoch, and Ph. Avouris, "Band-to-Band Tunneling in Carbon Nanotube Field-Effect Transistors," *Phys. Rev. Lett.*, vol. 93, no. 19, pp. 196805-196809, 2004.

- [57] W. Y. Choi, B. -G. Park, J. D. Lee, and T. -J. K. Liu, "Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec," *IEEE Electron Dev. Lett.*, vol. 28, no. 8, pp. 743-745, 2007.

- [58] T. Krishnamohan, D. Kim, S. Raghunathan, and K. Saraswat, "Double-gated strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and < 60 mV/dec subthreshold slope," *IEDM Tech. Digest*, pp. 947-949, 2008.

- [59] S. H. Kim, H. Kam, C. Hu, and T. -J. K. Liu, "Germanium-source tunnel field effect transistors with record high  $I_{ON}/I_{OFF}$ ," *VLSI Technol. Symp.*, pp. 178-179, 2009.

- [60] A. Seabaugh and Q. Zhang, "Low-Voltage Tunnel Transistors for Beyond CMOS Logic," *Proc. IEEE*, vol. 98, no. 12, pp. 2095-2110, 2010.

- [61] K. K. Bhuwalka, J. Schluze, and I. Eisele, "Performance enhancement of vertical tunnel field-effect transistor with SiGe in the  $\delta p^+$  layer," *Jpn. J. Appl. Phys.*, vol. 43, pp. 4073-4078, 2004.

- [62] A. Bowonder, P. Patel, K. Jeon, J. Oh, P. Majhi, H.-H. Tseng, and C. Hu, "Low-voltage green transistor using ultra shallow junction and hetero-tunneling," in *Proc. Int. Workshop Junction Technol.*, 2009, pp. 93–96.

- [63] O. Nayfeh, C. N. Chleirigh, J. Hennessy, L. Gomez, J. L. Hoyt, and D. A. Antoniadis, "Design of tunneling field-effect transistors using strained-silicon/strained germanium type-II staggered heterojunctions," *IEEE Electron Device Lett.*, vol. 29, no. 9, pp. 1074–1077, 2008.

- [64] V. Nagavarapu, R. Jhaveri, and J. C. S. Woo, "The tunnel source (pnpn) n-MOSFET: A novel high performance transistor," *IEEE Trans. Electron Devices*, vol. 55, no. 4, pp. 1013–1019, Apr. 2008.

#### **CHAPTER 2**

#### BERKELEY QUANTUM TRANSPORT SIMULATOR

In this chapter, we describe the features of Berkeley Quantum Transport Simulator (BQTS) – a massively parallel, NEGF-based numerical simulator, which we use during the course of our answering the questions raised at the end of Chapter 1. We begin with an overview of the organization of the simulator, followed by a detailed discussion of its capabilities in terms of device geometries and electronic structures. We then turn to the implementation of self-consistent solution of Pöisson's and NEGF equations, which forms the core of the simulator. Subsequently, we present our results demonstrating scalability on large-scale distributed systems. Our primary focus here would be on laying out the core formalism and its implementation; however, the discussion on benchmarking simulation results with experimental data – in tunneling devices where our interests primarily lie – would be taken up in Chapter 4.

#### 2.1 OVERVIEW

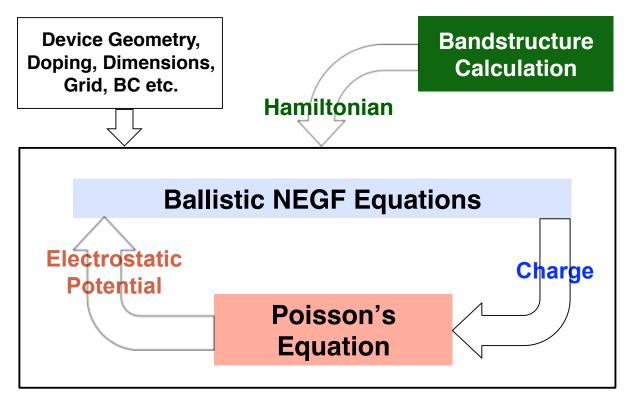

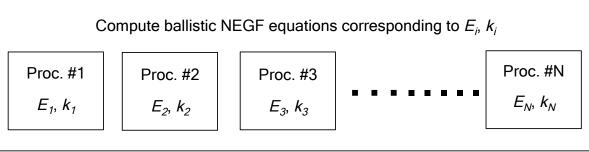

In this section, we outline the broad contours of the organization of BQTS. Figure 2.1 provides a schematic framework of the simulator. At the core of it is a self-consistent solver of Pöisson's and ballistic NEGF equations. We turn to a detailed examination of the equations involved herein in Section 2.4 but a couple of explanatory points are in order – (a) all our discussions are

Figure 2.1: Schematic framework of the organization of various components of the Berkeley Quantum Transport Simulator.

confined to the SCF regime and the dimensions under consideration are large enough to ignore Coulomb blockade effects; (b) although even in short-channel-length devices there invariably exists some amount of scattering, we primarily focus on ballistic simulations due to the following reasons – (i) inclusion of scattering effects in a strict sense renders the calculations greatly computationally expensive by destroying the inherent parallelism present otherwise [1]; (ii) the best-case performance is a fairly good indicator of feasibility in case of several tunneling-related problems of our interest.

The Hamiltonian description of the system – an input to the core solver described above – comes through the band structure calculation module of the simulator. While the simulator can, in principle, handle any Hamiltonian represented in an orthogonal basis, we have been focusing on semi-empirical tight binding, k.p and effective mass descriptions so far – the details of which shall be described in section 2.3. In addition, various geometry-related parameters including grid-size, doping concentrations in different regions, electrical boundary conditions (BC) at the edges of the simulation domain etc. act as inputs to the simulator.

#### 2.2 DEVICE STRUCTURES

This section will focus on describing the flexibility that BQTS provides in terms of incorporating various device structures and geometries. An important feature of the core-solver is its agnosticism to material-specific details. This means that the core of the simulator can be used to investigate electronic transport behavior in a wide range of materials - Si, Ge, InAs, GaN, graphene to name a few - without any modification. The dimensionality of the systems under investigation – from 1-D (e.g., nanowires, nanoribbons etc.) to 3-D (bulk semiconductors) – is also handled in a fairly generic manner. This requires a brief explanation – in order to accurately represent the device behavior, depending on the spatial variation of electrostatic potential, certain dimensions (along which the changes are rapid) need to be resolved in real-space while in some others (where the variation is slow or negligible) a periodic boundary condition could be imposed and hence a momentum-space representation suffices therein. The generality of the simulator implies that with a Hamiltonian with some of its dimensions represented in real-space and some others in momentum-space as input, the simulator can compute physical quantities of interest in a straightforward manner. We shall return to the discussion on the trade-offs of using real- and momentum-space representations in a later section. Another characteristic of the simulator is that in addition to being able to capture spatial variation in doping profiles, fixed charges arising due to traps and impurities, and dielectric interfaces, it can include, with the knowledge of each of the materials' electronic structure- and electrostatics-related parameters. hetero-structures in the transport calculations. We also note that BQTS can handle both reflectionless, Ohmic (e.g., heavily doped semiconductors) and Schottky type of contacts in the self-consistent calculations thereby providing significant flexibility in exploring several of the novel material-systems wherein contacts are mainly of latter kind and where the issue of designing low-resistance contacts is an area of active research [2], [3].

#### 2.3 ELECTRONIC STRUCTURE CAPABILITIES

In this section, we discuss the flexibilities offered by BQTS in terms of types of electronic structures that can be incorporated. The choice of right method to describe band structure depends on the specific problem at hand – computation-time and accuracy being the trade-off variables. While from a formalism viewpoint, NEGF can, in principle, work with a Hamiltonian

described in non-orthogonal bases as well, we confine ourselves to the orthogonal basis representations [4]. Specifically, we discuss, in some detail, our efforts in working with k.p and semi-empirical tight binding methods in our studies.

#### **2.3.1 THE** *k.p* **METHOD**

The *k.p* method for calculating the electronic structures has been used extensively over the last few decades in case of a wide range of semiconductors – most prominently in investigating optical properties of direct-bandgap semiconductors, heterostructures and quantum wells [5]. For a comprehensive elucidation of the approach, the readers are urged to peruse Refs. [6]-[8]. Here, however, we outline some key ideas for the purposes of completeness. The main advantage of this approach is fourfold – (a) it provides a reasonable compromise in terms of both time and model-complexity between simpler approaches like effective-mass Hamiltonian and more elaborate descriptions such as tight-binding and *ab-initio* methods; (b) the model parameters such as bandgap, effective mass, optical matrix elements etc. can be inferred easily from experiments and hence the method becomes an attractive option in case of new materials, for exploring their potential in initial feasibility studies before a more rigorous description could be used; (c) it provides a way to include effects of strain and spin-orbit interactions in a relatively straightforward manner; (d) it provides analytical expressions for band dispersions close to high-symmetry points in the Brillouin zone (BZ).

At the core of it, k.p method relies on perturbative expansion of the Bloch functions around certain point in the BZ (e.g., most commonly, zone center in case of zinc-blende III-V semiconductors). In terms of notations, denoting the wavefunction of a certain band indexed by n at a point  $\vec{k}$  in the BZ by  $\Psi_{n\vec{k}}(\vec{r}) (= e^{i\vec{k}.\vec{r}} u_{n\vec{k}}(\vec{r}))$ , where  $u_{n\vec{k}}(\vec{r})$  denotes the periodic part of the wavefunction), the single-particle Hamiltonian equation  $(H\Psi_{n\vec{k}}(\vec{r}) = E_n(\vec{k})\Psi_{n\vec{k}}(\vec{r}))$  could be written in terms of  $u_{n\vec{k}}(\vec{r})$  as –

$$(H_0 + H_k + H_{k,p}) u_{n\vec{k}}(\vec{r}) = E_n(\vec{k}) u_{n\vec{k}}(\vec{r})$$

(1)

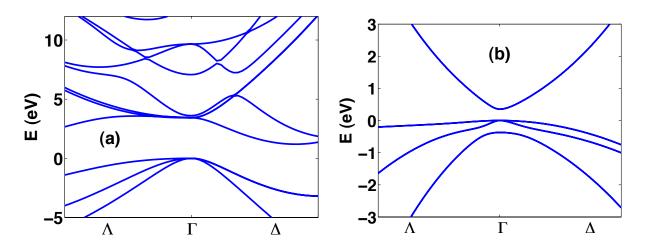

Figure 2.2: k.p bandstructures for (a) bulk Si (parameters from Ref. [9]), and (b) bulk InAs (parameters from Ref. [5]) along two important high-symmetry directions of the BZ ( $\Lambda$  and  $\Delta$ ).

where  $H_0$  is the unperturbed Hamiltonian (i.e., at  $\vec{k}=0$ ),  $H_k=\frac{\hbar^2|\vec{k}|^2}{2m}$ , and  $H_{k,p}=\frac{\hbar}{m}\vec{k}\cdot p$  (with  $\hbar$ , m and p being the reduced Planck's constant, free electron mass and momentum operator respectively). Now,  $u_{n\vec{k}}(\vec{r})$  can be expanded in an orthonormal basis of Bloch functions at a high-symmetry point, e.g., for expansion around  $\vec{k}=\Gamma$ ,

$$u_{n\vec{k}}(\vec{r}) = \sum_{j=1}^{N} a_j(\vec{k}) u_{j0}(\vec{r})$$

(2)

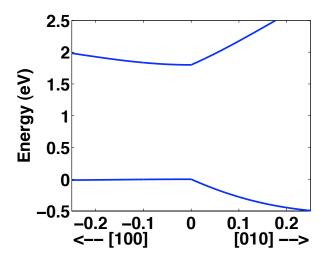

The total number of bands, N, generally used depends both on the material in question and the problem at hand – 6 bands are sufficient to describe the valence bands of zinc-blende (ZB) III-Vs with the inclusion of spin-orbit interaction, 2 more bands for incorporating conduction band description; 15 bands to describe the indirect bandgap in case of Si, Ge etc [5], [9]. The number of parameters required to uniquely determine the bandstructure is governed by the inherent symmetries of the BZ. We note that the accuracy of the resulting eigenfunctions and eigenvalues progressively decreases as  $|\vec{k}|$  increases. Non-parabolic effects like valence-band warping can be taken care of by increasing the order of perturbation. Of particular interest are the commonly used Luttinger-Kohn (LK) and Dresselhaus-Kip-Kittel (DKK) Hamiltonians in the description of valence bands of ZB semiconductors whose second-order-perturbation model-parameters depend on Luttinger parameters that are very well-known for most materials of interest [10], [11]. The said parameters are fitted, in most cases, to obtain an accurate electronic structure description in bulk semiconductors. The illustration of the method in calculating dispersion relations in InAs and silicon – two of the most common semiconductors – along a couple of high-symmetry directions is shown in Fig. 2.2.

A couple of important points must be noted here - (a) as discussed in Section 2.2, in most transport calculations, some directions require a real-space representation of the electronic

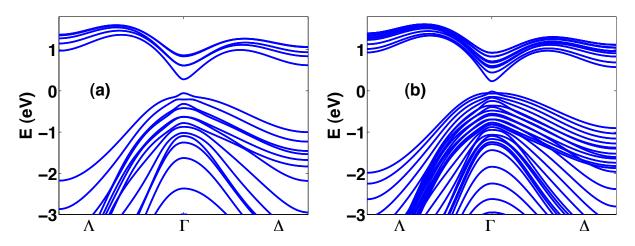

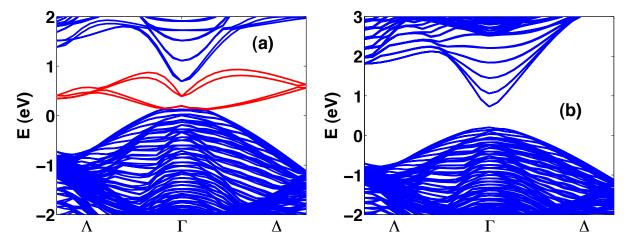

Figure 2.3: Dispersion relations in InSb along  $\Lambda$  and  $\Delta$  for the case where one of the dimensions is geometrically confined along [100]. The plots are for (a) 3.2 nm and (b) 6.4 nm thick InSb films, after elimination of spurious mid-gap states using the prescription in Ref. [12].

structure. A straightforward prescription of translating to such a representation from the momentum-space representation is by noting that the projection of  $\vec{k}$  in position-space is given by  $-\vec{k} \leftrightarrow -i\nabla$ , the gradient operator, and projecting this onto a finite-difference grid. The gridspacing herein should be chosen such that with a finite N-band representation there should exist appropriate density-of-states (DOS) within the energy range of interest while simultaneously ensuring that it is not too small as to reach large values of  $|\vec{k}|$  where the accuracy of the method reduces; (b) in certain nanostructures, there exists geometrical confinement along certain dimensions and abruptly terminating the real-space Hamiltonian in the simulation domain in such cases leads to incorrect imposing of boundary conditions and hence spurious eigenvalue solutions in the bandgap. Hence care must be taken in order to ensure elimination of such artifacts through modification of model-parameters. In this regard, a subtle point is in order: the abovementioned spurious states might be manifested in certain non-symmetric direction and hence examining the bandstructure along high-symmetry lines of BZ will not suffice. A robust test is to plot the transmission probability (discussed later in Section 2.4.2), where contributions from eigenstates corresponding to all momenta at a given energy are accounted for. We use the solution proposed by Foreman by analyzing the roots of secular equation to get rid of incorrect solutions [12] (Fig. 2.3). In the next subsection, we discuss in detail the semi-empirical tightbinding method for describing electronic structure.

#### 2.3.2 THE SEMI-EMPIRICAL TIGHT-BINDING METHOD

In this section, we would like to discuss briefly certain aspects related to using tight-binding based Hamiltonians in our simulations. Tight-binding (TB) methods provide more elaborate descriptions of electronic structure in solids than the *k.p*-based methods. Hence their accuracy is better, albeit at the expense of increased computational burden. However, they are less accurate than the more comprehensive but computation-intensive density-functional theory, from which the former can be derived under certain approximations [13]. While TB approach comes in both orthogonal- and non-orthogonal-bases flavors, we confine our discussions herein to the former due to their simplicity of incorporation in electronic transport calculations.

Unlike in case of *k.p* method where the basis functions were defined on a unit cell (or a finite-difference grid), TB method relies on expansion of the electronic wavefunction as a linear combination of atomic orbitals (LCAO) that constitute the crystal. This emanates from the assumption that the single-particle, time-independent Hamiltonian of the crystal could be written as a sum of isolated atomic Hamiltonian and some overlapping potential due to the presence of neighboring atoms in the crystal lattice, i.e.,

$$H(\vec{r}) = \sum_{\vec{R}} H_{atom}(\vec{r} - \vec{R}_n) + V(\vec{r})$$

(3)

where the summation extends over all atomic sites in the lattice  $\vec{R}_n$  and  $V(\vec{r})$  is the correction to the isolated atomic potential. Assuming that the effect of  $V(\vec{r})$  is only in altering the isolated atom electronic wavefunction only in a perturbative sense, the eigenfunctions of  $H(\vec{r})$  could be written as a linear combination of the former, i.e.,

$$\psi(\vec{r}) = \sum_{m, \vec{R}_n} a_m(\vec{R}_n) \psi_m(\vec{r} - \vec{R}_n) \tag{4}$$

where  $\psi_m$  denotes the wavefunction corresponding to *m*-th atomic orbital. Imposing the translational symmetry of the crystal through the Bloch's theorem, the coefficients  $a_m$  satisfy the family of equations –

$$a_m(\vec{R}_n - \vec{R}_t) = e^{i\vec{k}.(\vec{R}_n - \vec{R}_t)} a_m(\vec{0})$$

(5)

for all translational vectors of the lattice  $\vec{R}_t$ . In orthogonal TB, one uses modified orbitals – obtained by Löwdin orthonormalization of atomic orbitals – such that wavefunctions corresponding to different atomic sites are orthogonal [14]. In such a case, the wavefunction could be written, in terms of orthogonalized Löwdin orbitals,  $\Psi_m$ , as –

$$\psi(\vec{r}) = \frac{1}{\sqrt{N}} \sum_{m,\vec{R}_n} e^{i\vec{k}\cdot\vec{R}_n} \Psi_m(\vec{r} - \vec{R}_n)$$

(6)

where N is the number of atoms in the lattice. It is easy to notice that with (6) as an eigenfunction, finding the eigenvalues of  $H(\vec{r})$  involves computation of overlap integrals of  $V(\vec{r})$ , typically for large number of  $\vec{R}_n$ , thus making them difficult to evaluate. However, Slater and Koster noted that although analytical evaluation of those terms is practically infeasible, since the wavefunctions and eigenvalues have the correct symmetry properties, it is possible to get accurate bandstructure description at any point in the BZ as long as the approximations preserve the symmetry dictated by the crystal structure [15]. In particular, they suggested using some of the integrals as fitting parameters, which are to be chosen such that the energies thus calculated agree well with those determined either through experiments or through more precise electronic structure calculation methods at certain high symmetry points in the BZ. Also, another simplifying assumption is the neglecting of three-center integrals – arising in calculation of matrix elements of  $H(\vec{r})$ due periodic atomic potential to i.e.,  $\int \Psi_m^*(\vec{r} - \vec{R}_i) V_{atom}(\vec{r} - \vec{R}_k) \Psi_n(\vec{r} - \vec{R}_i) dv - \text{in comparison to two-center integrals (i.e., } k = i \text{ or } k = i$ j). Slater and Koster, noting that this approach necessitates the use of only few nearest-neighbor

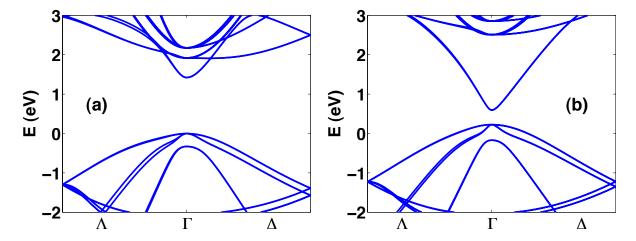

Figure 2.4: Semi-empirical TB bandstructures of (a) bulk GaAs and (b) bulk InAs using an  $sp^3s*d^5$  set of basis functions. The parameters used herein are obtained from Ref. [17].

Figure 2.5:  $sp^3s^*d^5$  TB bandstructures of geometrically-confined (along [100]), 6 nm thick InAs film (a) before and (b) after the elimination of erroneous eigenstates in the bandgap (denoted by red lines in (a)), arising due to incorrect BC, using the technique outlined in Ref. [18].

interactions, also calculated the general form of matrix elements – in terms of the abovementioned fitting parameters and direction cosines of the displacement vector between atoms – for s, p and d atomic orbitals, which are sufficient to describe the electronic structure in majority of the common semiconductors. Vogl determined the nearest-neighbor TB parameters in an  $sp^3s^*$  model for a wide range of frequently encountered semiconductors and showed the corresponding electronic structure to be in good agreement with experiments [16]. More recently, Klimeck et al. have determined, through stochastic optimization algorithms, TB parameters by incorporating split-off bands and fitting more accurately the effective masses along certain directions [17]. Figure 2.4 shows the dispersion relations along some high-symmetry directions in bulk InAs and GaAs.

Quite like in case of *k.p*, TB Hamiltonians, when used to represent geometrical confinement and hence finite simulation domain, require correct imposing of boundary conditions, in the absence of which one encounters spurious mid-gap eigenstates as an artifact. However, the prescription to remove such states in different herein. We adopt the approach by Lee et al. wherein one passivates the dangling bonds at the edge of the simulation domain by adding a large potential energy to missing bonds, thereby forcing the wavefunction to go to zero [18]. Figure 2.5 shows the effect of such a treatment in case of ultrathin body films where there exists structural confinement in one of the dimensions.

### 2.4 SELF-CONSISTENT SOLUTION OF PÖISSON'S AND BALLISTIC NEGF EQUATIONS

In this section, we look at some of the important aspects in the self-consistent solution of Pöisson's and NEGF equations by examining them in greater detail. In a nutshell, the solution involves, as shown in Fig. 2.1, a) evaluating the non-equilibrium charge density using NEGF equations, b) computing the electrostatic potential for this charge from Pöisson's equation, and c) in the SCF regime, using this potential to recompute charge density until convergence. For a detailed exposition on the basic formalism, the readers are suggested to consult Refs. [1], [19].

We focus herein on some of the factors that govern the computational effort in arriving at numerical convergence. We begin with the analysis of Pöisson's equation.

#### 2.4.1 PÖISSON'S EQUATION

The numerical solution of Pöisson's equation is an extremely well-studied problem [20], [21]. While there exist several standalone programs as well as libraries in high-level languages in the public domain for highly optimized, fast solutions to Pöisson's equation, we choose to have our own implementation, albeit not comparably optimized, because i) in most of our simulations, the scalability bottleneck, even with massive parallelization happens come from the NEGF part of the solver, and ii) the maintenance of the software becomes greatly simplified due to homogeneity. The keys steps in the approach are outlined herein. We start with the Pöisson's equation –

$$\vec{\nabla}.\ \varepsilon \nabla U = q(n - p + N_A^- - N_D^+) \tag{7}$$

(8)

where U is the electrostatic potential,  $\varepsilon$  the dielectric constant, n and p the electron densities, and  $N_A^-$  and  $N_D^+$  the ionized donor and acceptor concentrations respectively. We note that (7) is the more general form of the equation, wherein the spatial variations in dielectric constant are implicitly handled (through the  $\nabla \varepsilon$ .  $\nabla U$  term). We discretize (7) by projecting it on to a rectangular, finite-difference grid with 7 (3-D), 5 (2-D) and 3 (1-D) point stencils. The discretized version looks like –

$$\begin{split} &\varepsilon(x_{i},y_{j},z_{k})\times\Big(\frac{U(x_{i+1},y_{j},z_{k})+U(x_{i-1},y_{j},z_{k})-2U(x_{i},y_{j},z_{k})}{h_{x}^{2}}+\frac{U(x_{i},y_{j+1},z_{k})+U(x_{i},y_{j-1},z_{k})-2U(x_{i},y_{j},z_{k})}{h_{y}^{2}}\\ &+\frac{U(x_{i},y_{j},z_{k+1})+U(x_{i},y_{j},z_{k-1})-2U(x_{i},y_{j},z_{k})}{h_{z}^{2}}\Big)+\Big(\frac{(\varepsilon(x_{i+1},y_{j},z_{k})-\varepsilon(x_{i-1},y_{j},z_{k}))\times(U(x_{i+1},y_{j},z_{k})-U(x_{i-1},y_{j},z_{k}))}{4h_{x}^{2}}\\ &+\frac{(\varepsilon(x_{i},y_{j+1},z_{k})-\varepsilon(x_{i},y_{j-1},z_{k}))\times(U(x_{i},y_{j+1},z_{k})-U(x_{i},y_{j-1},z_{k}))}{4h_{y}^{2}}+\frac{(\varepsilon(x_{i},y_{j},z_{k+1})-\varepsilon(x_{i},y_{j},z_{k+1}))\times(U(x_{i},y_{j},z_{k+1})-U(x_{i},y_{j},z_{k-1}))}{4h_{z}^{2}}\Big)\end{split}$$

where

$$i$$

,  $j$  and  $k$  denote the indices along  $x$ ,  $y$  and  $z$  axes of the grid, and  $h_x$ ,  $h_y$  and  $h_z$  the corresponding spacing. It is a well-known result that (7), with Dirichlet (i.e.,  $U(x_i, y_j, z_k) = U_0$ , a constant), Neumann ( $\nabla U \cdot \hat{\boldsymbol{n}} = 0$ , where  $\hat{\boldsymbol{n}}$  denotes the normal to the surface at  $(x_i, y_j, z_k)$ ) or mixed (combination of Dirichlet and Neumann) boundary conditions (BC) specified along the

$= q(n(x_i, y_i, z_k) - p(x_i, y_i, z_k) + N_A^-(x_i, y_i, z_k) - N_D^+(x_i, y_i, z_k))$

mixed (combination of Dirichlet and Neumann) boundary conditions (BC) specified along the surface (3-D), edge (2-D) and endpoints (1-D) of the simulation domain, has a unique solution. The imposition of BC is fairly straightforward in the finite-difference method. It is easy to see that (8), with BC put together, results in a system of linear equations of the form -Ax = B, which can be solved using any iterative scheme such as Newton's method. The choice of BC to be used at a given node at the periphery of the domain is governed by the specific details of the problem; e.g., at grid points corresponding to gate electrode(s) in an MOS structure where the potential is governed by the external circuitry it is convenient to use a Dirichlet BC, while in case of doped source and drain contacts where the metallic contact pads are far outside the simulation domain, Neumann BC – implying conservation of flux – is more appropriate. In order to increase the rate of convergence to self-consistency, we use a non-linear transformation on the charge density using the semi-classical, effective-mass approximation –

$$n = N_c F_{1/2} \left( \frac{F_n - E_{c,old}}{k_B T} \right) \tag{9}$$

$$p = N_{\nu} F_{1/2} \left( \frac{E_{\nu,old} - F_p}{k_B T} \right) \tag{10}$$

where  $E_{c,old}$  and  $E_{v,old}$  are the conduction and valence band energies from the previous iteration of self-consistency inferred from  $U_{old}$ ,  $N_c$  and  $N_v$  the corresponding effective density-of-states (DOS),  $F_{1/2}$  the Fermi-Dirac integral of order  $\frac{1}{2}$ ,  $k_B$  the Boltzmann constant and T the temperature. We have dropped the arguments  $(x_i, y_j, z_k)$  in (9) and (10) for clarity. We note that the above equations are only to improve the convergence rate and the assumptions therein have no bearing on the resulting self-consistent charge densities and electrostatic potential profiles as the former quantities are calculated solely from NEGF equations. A weighted average of electrostatic potential from the previous iteration and new solution from Pöisson's equation as the new potential ensures that the convergence to self-consistency is smooth. The weights could be tuned based on the difference between new and old values.

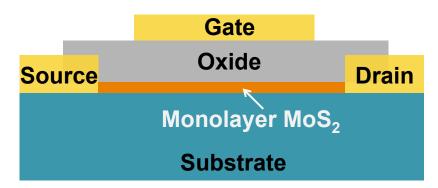

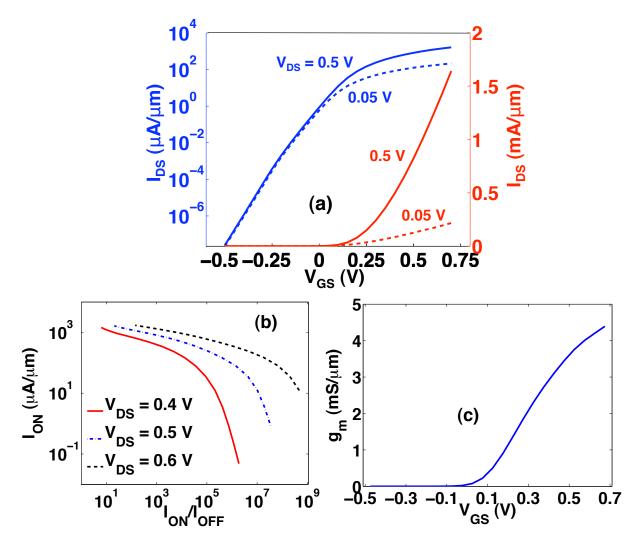

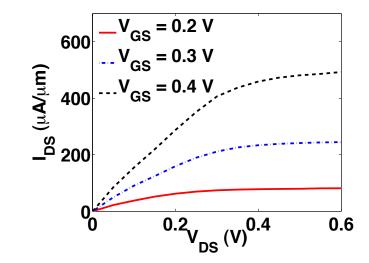

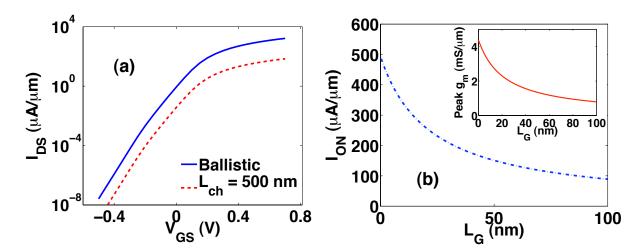

#### 2.4.2 BALLISTIC NEGF EQUATIONS