# Time-Domain Ultra-Wideband Synthetic Imager in Silicon

Amin Arbabian

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-188 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-188.html

December 1, 2013

Copyright © 2013, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Time-Domain Ultra-Wideband Synthetic Imager in Silicon

by

#### Mohammad Amin Arbabian

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering–Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Jan M. Rabaey Professor Eli Yablonovitch Professor Steven Conolly

Fall 2011

# Time-Domain Ultra-Wideband Synthetic Imager in Silicon

Copyright 2011 by Mohammad Amin Arbabian

#### Abstract

Time-Domain Ultra-Wideband Synthetic Imager in Silicon

by

Mohammad Amin Arbabian

Doctor of Philosophy in Engineering–Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali M. Niknejad, Chair

Low-cost and portable medical devices will play a more significant role in wellness, healthcare and medicine. While consumer electronics have become ubiquitous and inexpensive, medical devices, by contrast, are still primarily found only in hospitals. There is a great potential benefit in using techniques developed in the consumer electronic industry and applying them to the healthcare market. To do this, substantial innovation is required to develop new sensors and devices that are fundamentally less invasive and use profoundly different physical phenomena to address medical applications.

This research aims at designing a non-invasive, low-cost, and portable imaging device for cancer screening. Detection in early stages has proven to be essential for reducing the mortality rate in cancer. This requires pursuit of modalities that could be widespread and are safe to be used for more frequent screening. This research uses the available contrast in microwave frequencies to detect abnormalities.

Conceptualization, architectural and system-level design, and finally implementation of the system called TUSI, Time-Domain Ultra-Wideband Synthetic Imager, are addressed. Using an array of closely controlled radiating silicon chips, acting as transceivers in microwave /mm-wave frequencies, this device transmits short "beam-steered" pulses and picks up reflections from tissue abnormalities (e.g. cancerous tissue). By processing the data from multiple transceivers, a larger aperture is synthesized. In essence, this imager probes the "electrical" properties of the tissue. Various challenges related to generating, controlling, transmitting, and detecting these coherent ultra-short pulses are examined and new solutions proposed. A pixel-scalable integrated transceiver consisting of elements from antennato-antenna is designed and implemented in a SiGe BiCMOS process.

# Contents

| Li       | ist of | Figures                                       | iv   |

|----------|--------|-----------------------------------------------|------|

| Li       | ist of | Tables                                        | viii |

| 1        | Intr   | oduction                                      | 1    |

|          | 1.1    | Silicon-Based Medical Imager                  | 1    |

|          | 1.2    | Low-Cost Breast Cancer Screening              | 2    |

|          | 1.3    | Skin Cancer Detection                         | 3    |

|          | 1.4    | Other Applications                            | 4    |

|          | 1.5    | Organization of the Dissertation              | 4    |

| <b>2</b> | Bac    | kground and System Design                     | 5    |

|          | 2.1    | Radar Imager                                  | 5    |

|          | 2.2    | Contrast                                      | 6    |

|          | 2.3    | Resolution Basics                             | 8    |

|          |        | 2.3.1 Depth Resolution                        | 8    |

|          |        | 2.3.2 Lateral Resolution                      | 9    |

|          | 2.4    | Pulsed-Based Antenna Arrays                   | 10   |

|          | 2.5    | Signal-to-Noise Ratio                         | 11   |

|          | 2.6    | Resolution Limits                             | 12   |

|          | 2.7    | TUSI Imager                                   | 15   |

|          | 2.8    | Undesirable Coupling of SNR with Resolution   | 16   |

|          | 2.9    | Limits of Integration for Closing the SNR Gap | 18   |

|          |        | 2.9.1 Stability of the Imaging Setup          | 19   |

|          |        | 2.9.2 Limitations on Increasing the PRF       | 19   |

|          |        | 2.9.3 Accurate Delay Generation               | 19   |

|          | 2.10   | Coherent Radar Phase Information              | 22   |

|          | 2.11   | Spatial Coding to Suppress Spatial Leakage    | 24   |

|          | 2.12   | TUSI in the Large-Scale                       | 24   |

|          |        | 2.12.1 TUSI for Intelligent Surfaces          | 25   |

| 3 | Ant | enna Design                                              | 28  |

|---|-----|----------------------------------------------------------|-----|

|   | 3.1 | Integrated Antennas                                      | 28  |

|   |     | 3.1.1 Slot and Dipole Antennas                           | 30  |

|   | 3.2 | Antentronics                                             | 34  |

|   |     | 3.2.1 Folded Slot Dipole Antentronic Structure           | 34  |

|   |     | 3.2.2 Dual-Loop Antentronic Structure                    | 37  |

|   | 3.3 | Wideband Antennas                                        | 43  |

| 4 | TU  | I Transmitters                                           | 45  |

|   | 4.1 | Process Overview                                         | 45  |

|   | 4.2 | Transmitter Architecture                                 | 47  |

|   |     | 4.2.1 Pulse Modulating the RF Carrier                    | 47  |

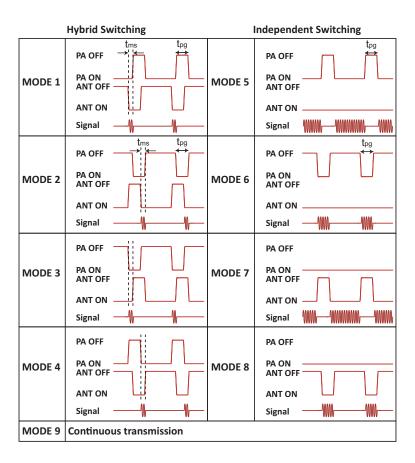

|   |     | 4.2.2 Hybrid Switching                                   | 47  |

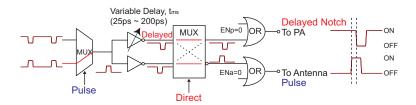

|   | 4.3 | High-Speed Timing Circuitry                              | 50  |

|   |     | 4.3.1 Mode Selection Circuitry                           | 51  |

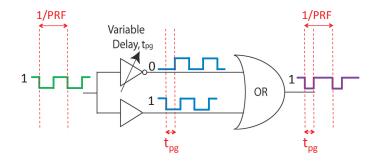

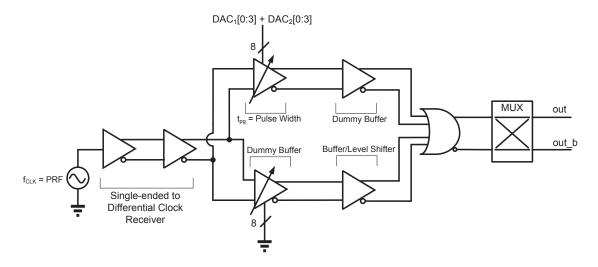

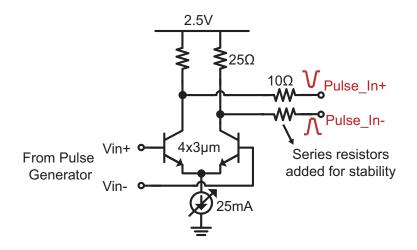

|   |     | 4.3.2 Pulse Generator                                    | 54  |

|   |     | 4.3.3 Programmable Delay                                 | 55  |

|   |     | 4.3.4 Impact of Jitter in Pulse Generation               | 57  |

|   |     | 4.3.5 High-Speed Output Buffer                           | 58  |

|   | 4.4 | Quadrature Voltage Controlled Oscillator (QVCO)          | 62  |

|   | 4.5 | Switched Power Amplifier                                 | 65  |

|   | 4.6 | Voltage Switching Transmitter                            | 68  |

|   |     | 4.6.1 Voltage Switching Antentronic Network              | 68  |

|   |     | 4.6.2 Experimental Results                               | 69  |

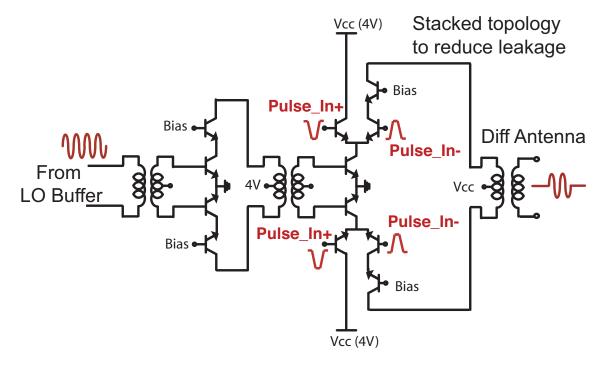

|   | 4.7 | Current Switching Transmitter                            | 76  |

|   |     | 4.7.1 Power Tuning Capability                            | 76  |

|   |     | 4.7.2 Current Switching Scheme                           | 77  |

|   |     | 4.7.3 Experimental Results                               | 77  |

| 5 | Rec | eiver                                                    | 84  |

|   | 5.1 | 94GHz Receiver Overview                                  | 84  |

|   |     | 5.1.1 Distortion                                         | 84  |

|   | 5.2 | Wideband Amplification                                   | 86  |

|   |     | 5.2.1 Distributed Amplifiers                             | 86  |

|   |     | 5.2.2 Passive Design                                     | 88  |

|   |     | 5.2.3 Active Element Design                              | 94  |

|   |     | 5.2.4 Distributed Amplifier with Internal Feedback       | 97  |

|   |     | 5.2.5 Tapered-Cascaded Multi-Stage Distributed Amplifier | 112 |

|   |     | · · · · · · · · · · · · · · · · · · ·                    | 120 |

|   | 5.3 | 1                                                        | 127 |

|   | 5.4 | Mixer Design                                             |     |

|                           |                 | 5.4.1   | Overview of Challenges                | 130 |

|---------------------------|-----------------|---------|---------------------------------------|-----|

|                           |                 | 5.4.2   | Mixer Core Design                     | 132 |

|                           |                 | 5.4.3   | LO Buffer                             | 133 |

|                           | 5.5             | Baseb   | and Amplification                     | 134 |

| 6                         | Inte            | egrated | l 94GHz Radar Transceiver             | 137 |

|                           | 6.1             | System  | n Overview                            | 137 |

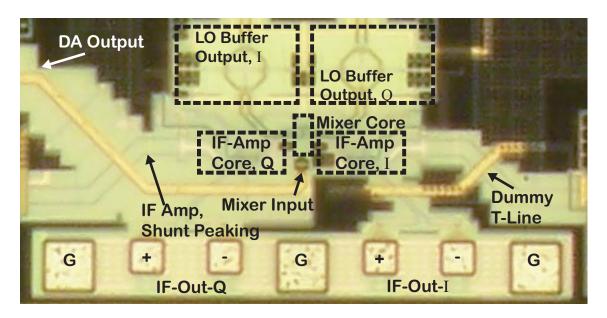

|                           |                 | 6.1.1   | Receiver Architecture                 | 137 |

|                           |                 | 6.1.2   | Transmitter Architecture              | 139 |

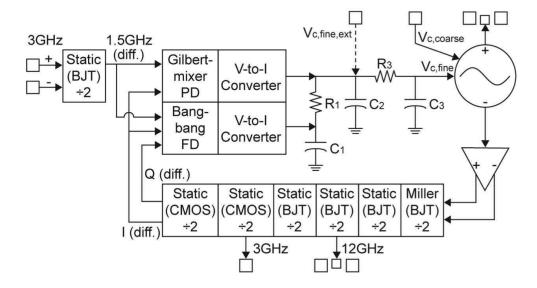

|                           |                 | 6.1.3   | Frequency Generation and Distribution | 140 |

|                           |                 | 6.1.4   | Pulse Position and Width Programming  |     |

|                           | 6.2             | End-to  | o-End Measurement Results             | 144 |

| 7                         | Cor             | clusio  | n I                                   | 152 |

| $\mathbf{B}^{\mathbf{i}}$ | Sibliography 15 |         |                                       |     |

# List of Figures

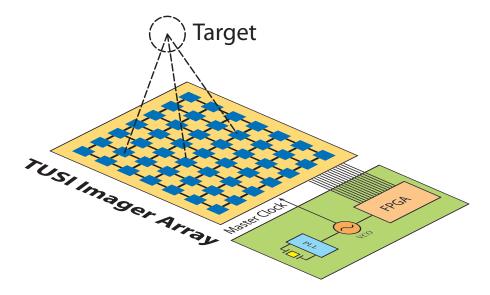

| 2.1  | TUSI imager concept                                                           | 7  |

|------|-------------------------------------------------------------------------------|----|

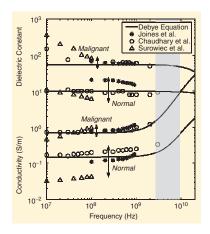

| 2.2  | Dielectric-properties data for normal and malignant breast tissue (from [1]). | 8  |

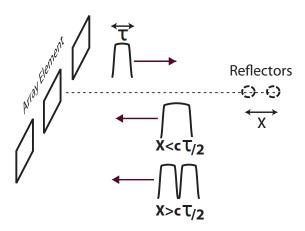

| 2.3  | Depth resolution in pulsed radar                                              | Ö  |

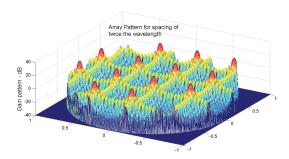

| 2.4  | Frequency-domain array with grating lobes                                     | 10 |

| 2.5  | Comparison of pulsed and frequency-domain arrays                              | 11 |

| 2.6  | Penetration depth and resolution                                              | 12 |

| 2.7  | Resolution reduction effect from large variations in amplitude                | 13 |

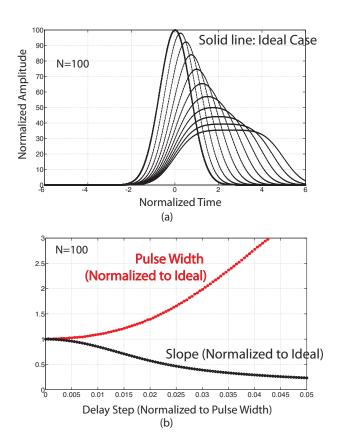

| 2.8  | Effect of pulse integrity on performance                                      | 13 |

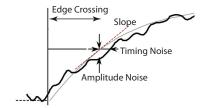

| 2.9  | Received pulsed edge with noise                                               | 14 |

| 2.10 | TUSI array imager on flexible substrate                                       | 15 |

| 2.11 | Proposed array architecture and system block diagram                          | 17 |

| 2.12 | Delay-Locked Loop architecture for generating fine time steps                 | 17 |

| 2.13 | System simulations of the transmit/receive chain                              | 18 |

| 2.14 | Range and position ambiguity from high PRF                                    | 20 |

| 2.15 | Linear antenna array model                                                    | 20 |

| 2.16 | Effect of delay step quantization                                             | 23 |

| 2.17 | Spatial sectorization in the TUSI Imager                                      | 24 |

| 2.18 | Large-scale TUSI array for intelligent surfaces                               | 26 |

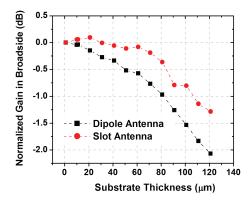

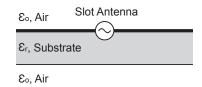

| 3.1  | Elementary slot and dipole antennas on silicon substrate                      | 29 |

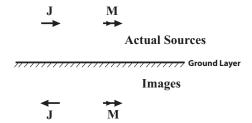

| 3.2  | Electric and magnetic sources close to a ground plane                         | 30 |

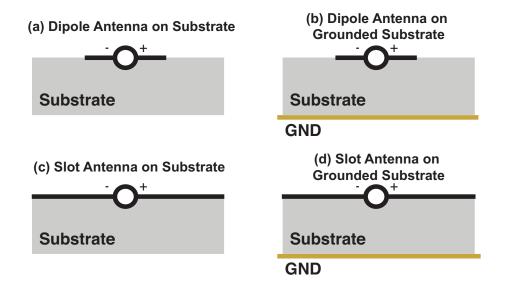

| 3.3  | Various forms of integrated antennas on dielectric substrates                 | 31 |

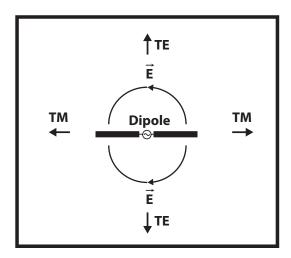

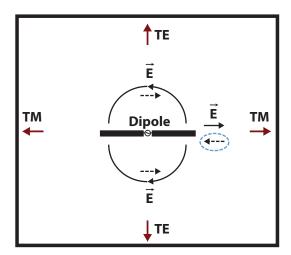

| 3.4  | Directions of propagation of surface-waves for a dipole antenna               | 32 |

| 3.5  | Direction of reflected E-fields in the dipole on grounded substrate           | 32 |

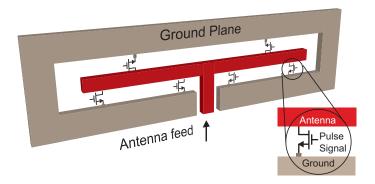

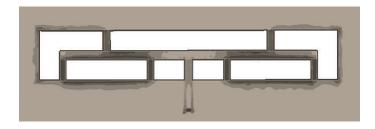

| 3.6  | Antentronic Structure with folded slot dipole antenna                         | 35 |

| 3.7  | Non-radiating mode current distribution                                       | 35 |

| 3.8  | Simulated input impedance of the antenna in transmit mode                     | 36 |

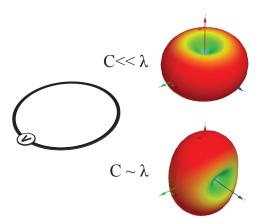

| 3.9  | Loop antenna together with radiation pattern in cases of small loop           | 37 |

| 3.10 | Resonant loop antenna equivalent to two half-wavelength dipoles               | 38 |

| 3.11 | Loop antenna on ground plane                                                  | 38 |

| 3 12 | Radiation efficiency broadside gain and input resistance of loop antenna      | 30 |

| 3.13 | Simulated E and H-plane pattern of the loop antenna                         | 39 |

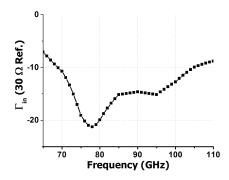

|------|-----------------------------------------------------------------------------|----|

| 3.14 | Slot antenna on a dielectric substrate                                      | 40 |

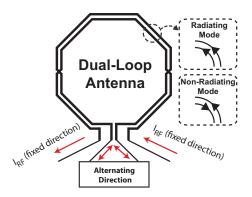

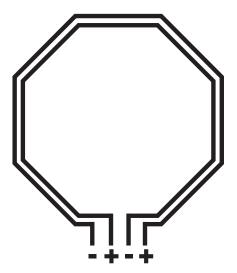

| 3.15 | Dual-loop antentronic structure                                             | 41 |

| 3.16 | Dual loop antenna under non-radiating drive conditions                      | 42 |

| 3.17 | Some wideband antenna designs                                               | 43 |

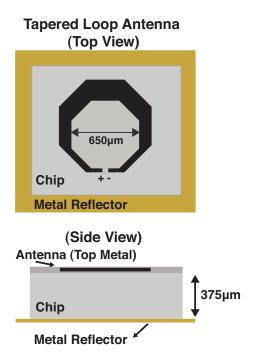

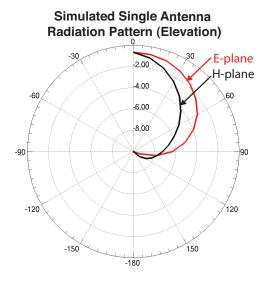

| 3.18 | Tapered loop antenna on silicon substrate                                   | 44 |

| 3.19 | Single-element tapered loop antenna pattern                                 | 44 |

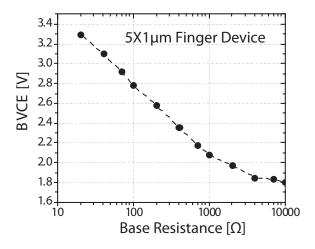

| 4.1  | Collector-Emitter breakdown voltage of a $5\mu m$ device                    | 46 |

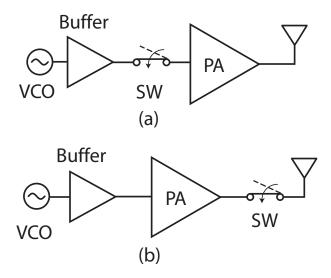

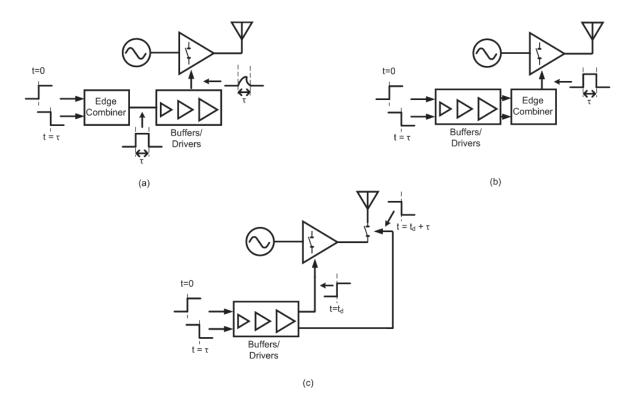

| 4.2  | Conceptual switching options for pulse modulating the carrier               | 48 |

| 4.3  | Pulse generation options                                                    | 49 |

| 4.4  | Input equivalent circuit of the pulse driver load                           | 50 |

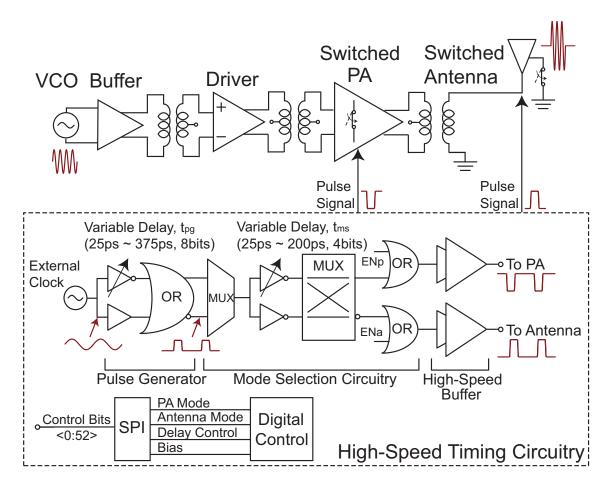

| 4.5  | System block diagram of the TUSI transmitter                                | 51 |

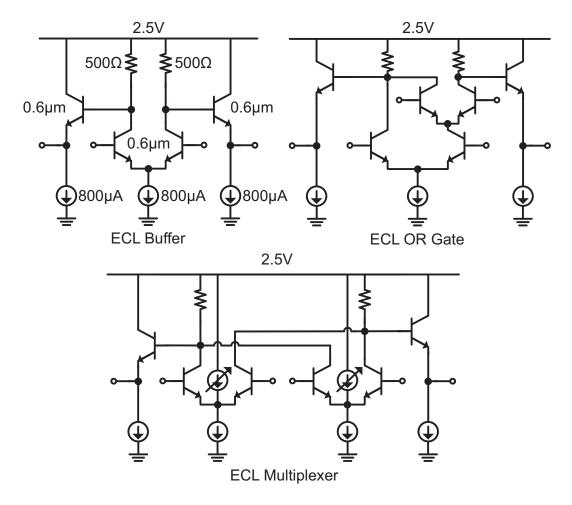

| 4.6  | Schematic of ECL logic gates used in design of High-Speed Timing Circuitry. | 52 |

| 4.7  | Operation modes of TUSI transmitter                                         | 53 |

| 4.8  | Block diagram of Mode Selection circuitry (programmed for Mode 1)           | 53 |

| 4.9  | Simplified schematic of pulse generator                                     | 54 |

| 4.10 | Detailed block diagram of pulse generator                                   | 54 |

| 4.11 | Plot of simulated pulse widths at the output of PA driver                   | 56 |

|      | Transient simulation comparing pulse generator output to PA driver output.  | 56 |

|      | Illustration of timing uncertainty in hybrid mode                           | 57 |

|      | Simulated period jitter (rms) of variable delay buffer                      | 58 |

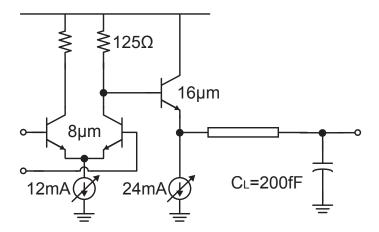

| 4.15 | Circuit schematic of the high-speed buffer                                  | 59 |

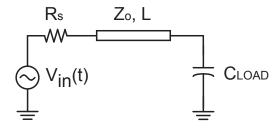

| 4.16 | Simplified circuit model for buffer circuit including the trace             | 60 |

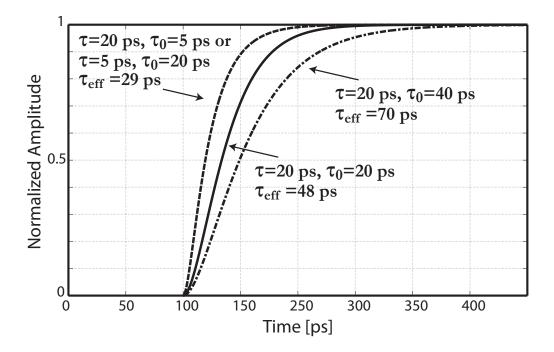

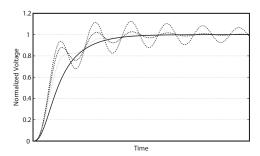

| 4.17 | Response of a capacitively terminated transmission line                     | 61 |

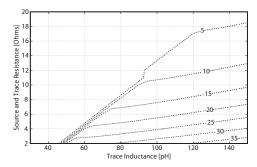

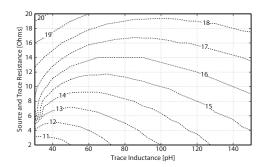

|      | Design curves for pulse driver circuit parameters                           | 63 |

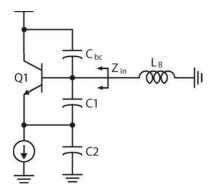

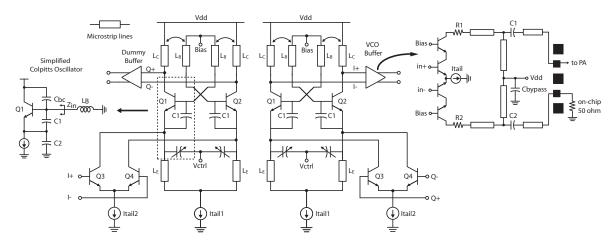

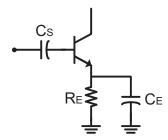

|      | Simplified schematic of the Colpitts oscillator                             | 64 |

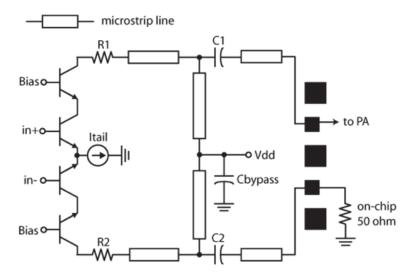

|      | Complete schematic of QVCO                                                  | 64 |

| 4.21 | Schematic of the output buffer                                              | 65 |

|      | Measured VCO tuning range as well as the measured spectrum at 74 GHz.       | 66 |

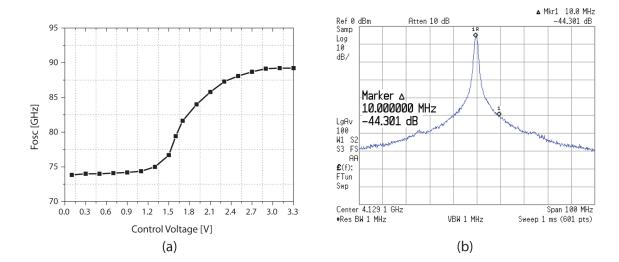

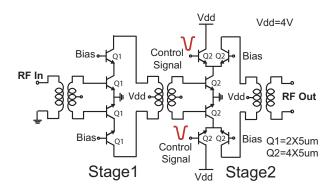

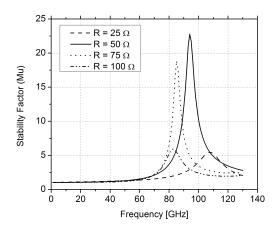

|      | Two-stage transformer-coupled power amplifier                               | 67 |

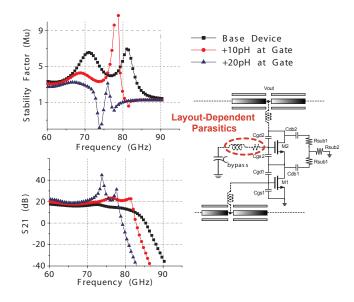

| 4.24 | Stability factor of the PA under different presented loads to the output    | 68 |

| 4.25 | Chip micrograph of the TUSI VS transmitter                                  | 69 |

|      | Transmitter measurement setup                                               | 70 |

|      | Ideal unlocked RF pulse response in BW limited regime                       | 71 |

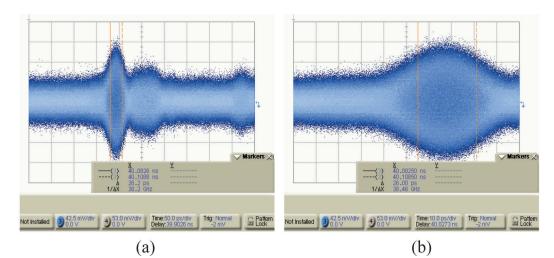

|      | Measured pulse in mode 6 with (a) 50ps/div and (b) 10ps/div                 | 71 |

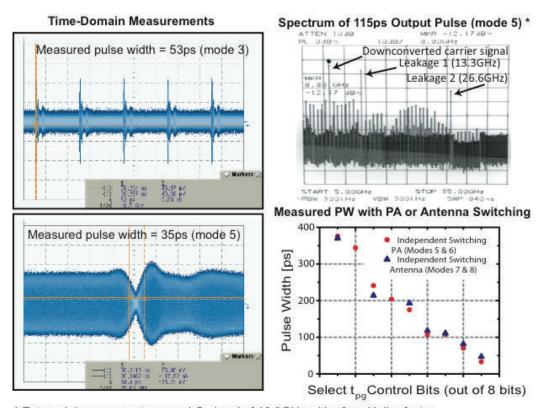

|      | Time domain measurements of mode 3 (53ps) and mode5 (35ps)                  | 72 |

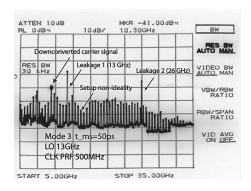

|      | Spectrum measurements of positive pulse in mode 3 (hybrid)                  | 72 |

|      | Time domain measurements from Mode 1 (hybrid)                               | 73 |

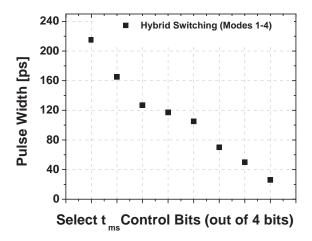

|      | Hybrid mode measurements/                                                   | 73 |

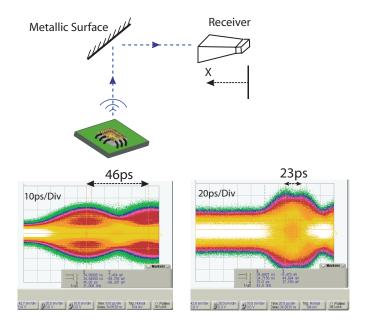

| 4.33 | Measurements with a metallic reflector and infinite setting on oscilloscope | 74 |

| 4.34 | System level block diagram of the current-switched transmitter            | 76  |

|------|---------------------------------------------------------------------------|-----|

| 4.35 | Circuit schematics of the current switching scheme transmitter            | 78  |

| 4.36 | TUSI CS chip micrograph.                                                  | 79  |

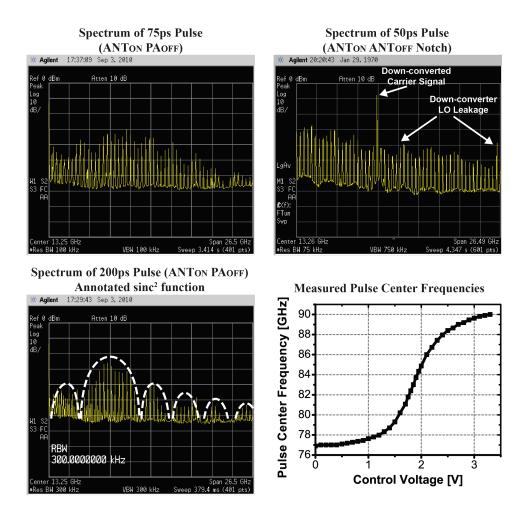

| 4.37 | Measured PSD of various pulses                                            | 80  |

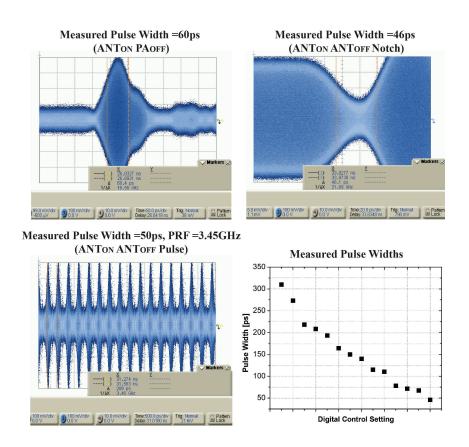

|      | Time-domain measurements for different settings                           | 81  |

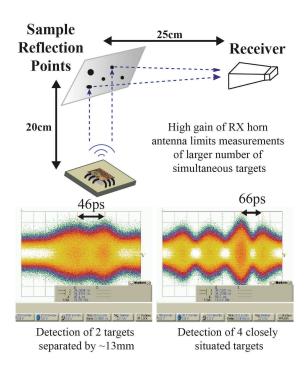

|      | Bistatic reflection measurements                                          | 82  |

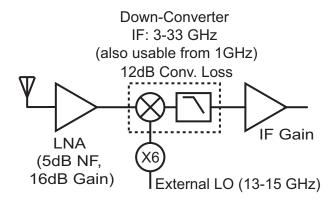

| 5.1  | Block diagram of the direct-conversion TUSI receiver chain                | 84  |

| 5.2  | Block diagram of the external down-converter                              | 85  |

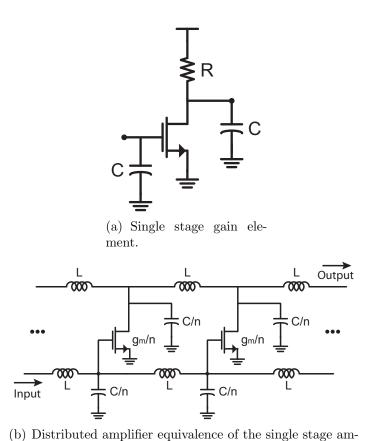

| 5.3  | Comparing a single stage common-source to a distributed amplifier         | 87  |

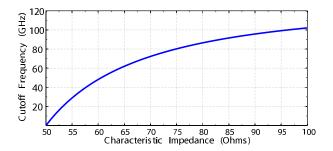

| 5.4  | Line bandwidth limitation due to the initial $Z_0$ of transmission line   | 90  |

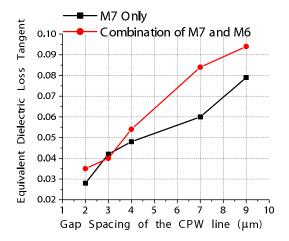

| 5.5  | Equivalent loss tangent of CPW transmission lines                         | 90  |

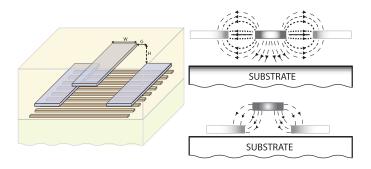

| 5.6  | Conceptual layout of shielded elevated line with current flow             | 90  |

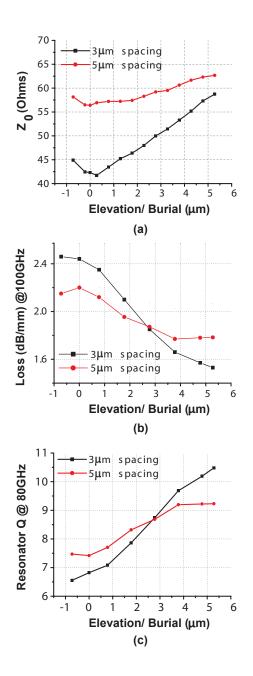

| 5.7  | HFSS simulation of elevated line characteristics                          | 91  |

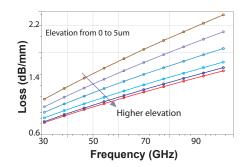

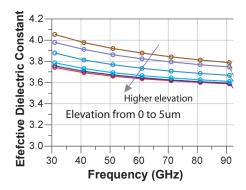

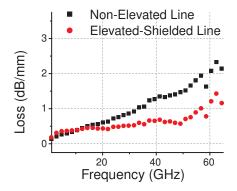

| 5.8  | HFSS simulations of loss for various elevations with respect to frequency | 92  |

| 5.9  | Effective dielectric constant of the transmission line                    | 92  |

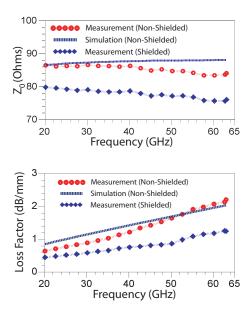

| 5.10 | E-CPW line measurements                                                   | 94  |

| 5.11 | Measurements of a shielded elevated CPW with M1 and poly as filaments     | 94  |

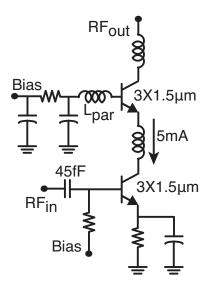

| 5.12 | Schematic diagram of cascode device with important parasitic elements     | 95  |

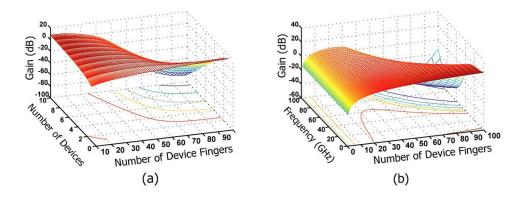

| 5.13 | Simulated DA gain under varying device size and number of devices         | 96  |

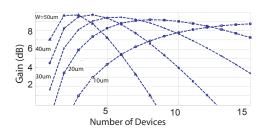

| 5.14 | Simulated DA gain vs. number of devices for various number of fingers     | 96  |

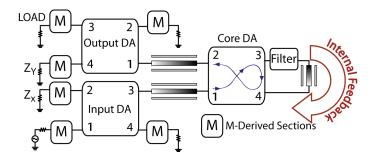

| 5.15 | Proposed DA architecture for improved gain-bandwidth product              | 97  |

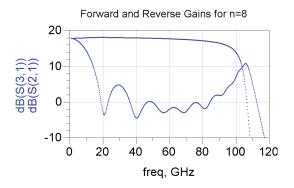

| 5.16 | MATLAB simulations of reverse gain in hypothetical 3 and 10 stage DAs     | 96  |

| 5.17 | Simulations for forward and reverse gain of 8-stage DA                    | 96  |

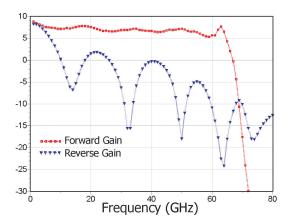

| 5.18 | DA forward and reverse gain simulations                                   | 100 |

| 5.19 | Calculated normalized gain for a conceptual feedback DA                   | 102 |

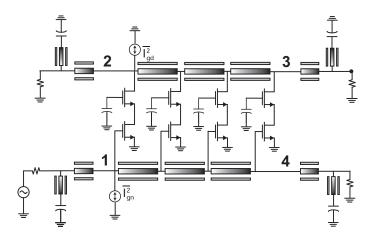

| 5.20 | Theoretical NF of DA in terms of frequency for different $n$              | 104 |

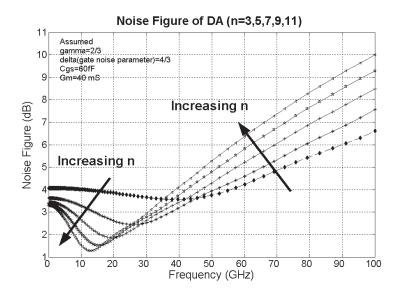

| 5.21 | Simulated gain and NF of a 16 stage DA in level 1 MOS models              | 107 |

| 5.22 | Simulated gain and NF of a FBDA with the same number of stages            | 108 |

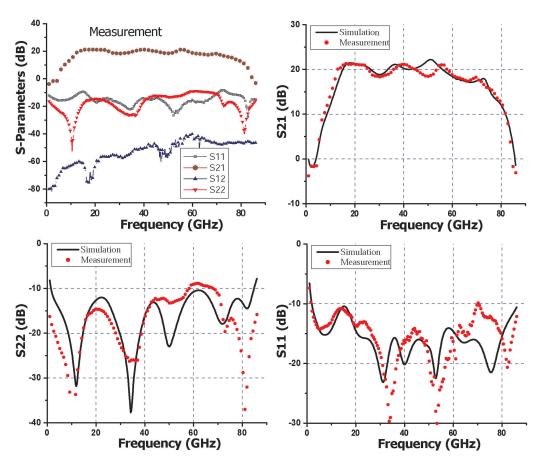

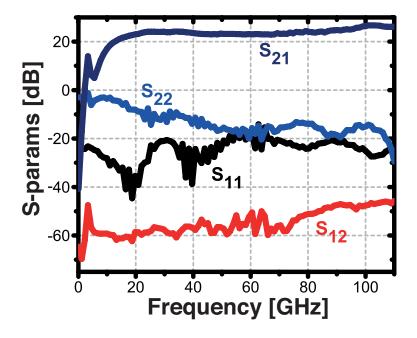

| 5.23 | Measured s-parameters of the FBDA                                         | 109 |

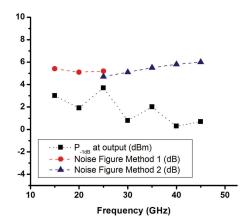

| 5.24 | Measured noise and $P_{1dB}$ of the FBDA                                  | 110 |

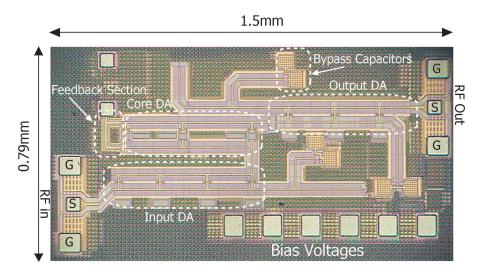

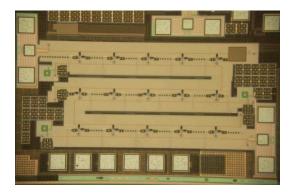

| 5.25 | Chip micrograph of the FBDA                                               | 110 |

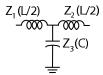

| 5.26 | T-section of a synthesized transmission line                              | 114 |

| 5.27 | Schematic diagram of a tapered distributed amplifier                      | 114 |

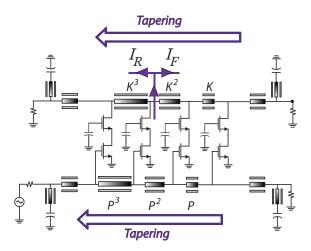

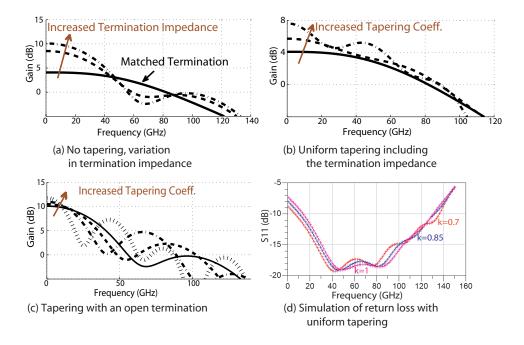

| 5.28 | Simulated gain with different tapering strategies                         | 115 |

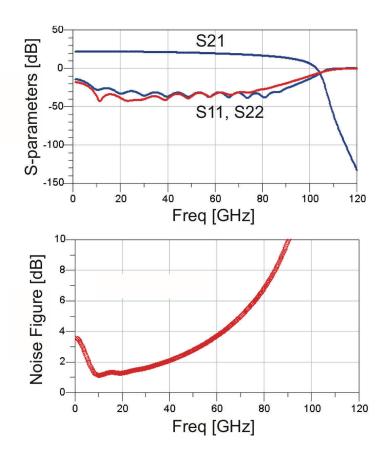

|      | Schematics of the T-CMSDA                                                 |     |

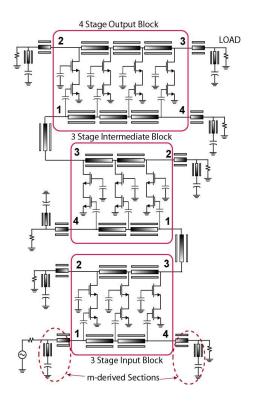

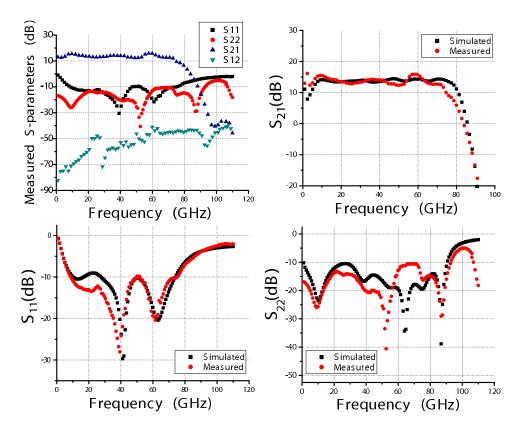

| 5.30 | S-parameter simulation and measurements of the T-CMSDA                    | 117 |

|      | Chip micrograph of the of the T-CMSDA                                     |     |

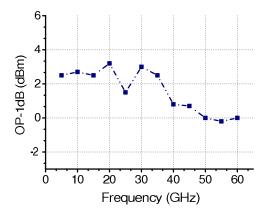

| 5.32 | Output compression point measurements of the T-CMSDA                      | 118 |

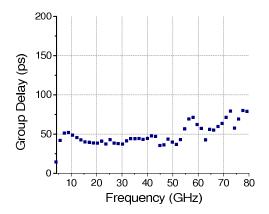

| 5.33 | Measured group delay of the amplifier in frequency band of interest       | 118 |

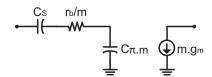

| 5.34 | Single gain stage equivalent circuit                                      | 122 |

| 5.35 | Common emitter stage with degeneration and series capacitor                   | 122 |

|------|-------------------------------------------------------------------------------|-----|

| 5.36 | DA cascode gain element                                                       | 124 |

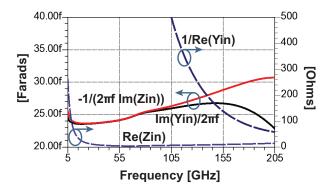

| 5.37 | Input loading from the DA gain element                                        | 125 |

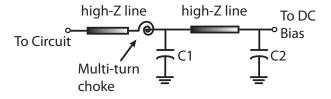

| 5.38 | Cascaded choke architecture                                                   | 125 |

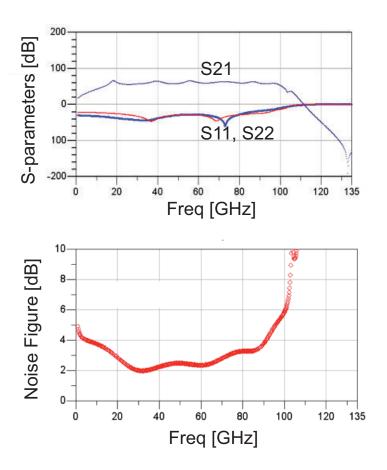

| 5.39 | Chip micrograph of the SiGe distributed amplifier                             | 126 |

| 5.40 | S-parameter measurements of the SiGe DA                                       | 126 |

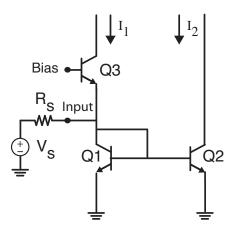

| 5.41 | Active balun circuit schematic                                                | 127 |

| 5.42 | Circuit schematic of the active balun with degeneration and base resistances. | 128 |

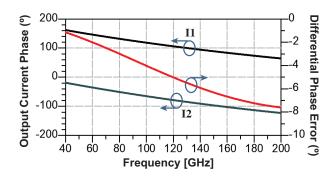

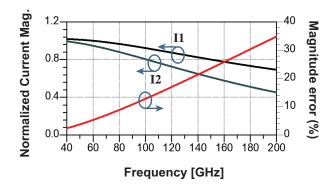

| 5.43 | Phase response of the active balun                                            | 129 |

| 5.44 | Magnitude response of the active balun                                        | 129 |

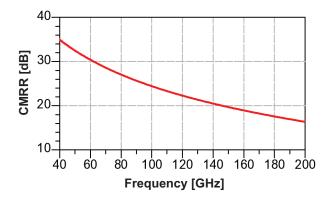

| 5.45 | CMRR of the core active balun circuit                                         | 129 |

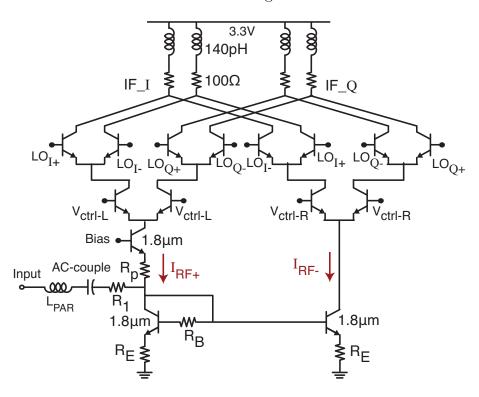

| 5.46 | Schematic of the quadrature mixer                                             | 130 |

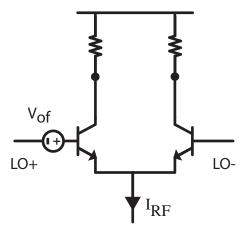

| 5.47 | Mixer core with input offset voltage                                          | 132 |

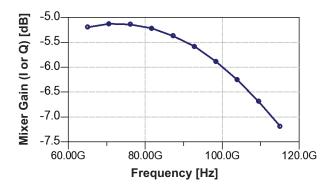

|      | Mixer gain                                                                    |     |

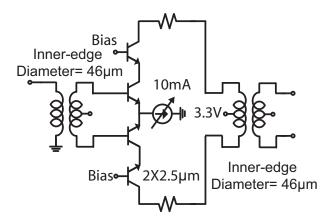

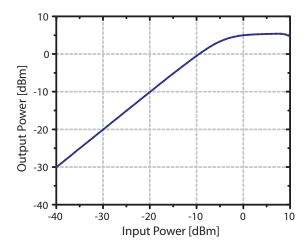

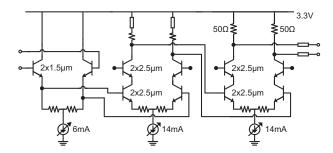

| 5.49 | The schematic of the single-ended to differential LO buffer                   | 134 |

| 5.50 | LO buffer output power                                                        | 135 |

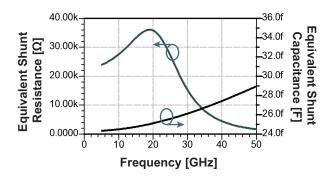

|      | Input impedance at the input of the mixer                                     |     |

| 5.52 | The schematic of the baseband buffer                                          | 136 |

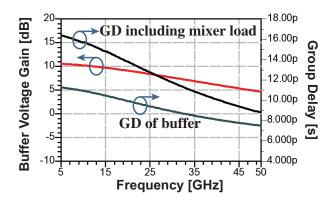

| 5.53 | Baseband buffer voltage gain and group delay simulations                      | 136 |

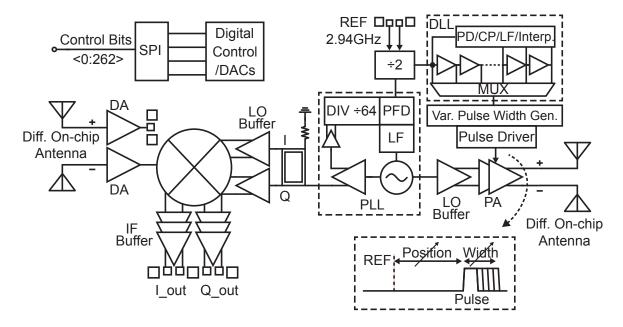

| 6.1  | Block-level schematics of a pulsed-based radar transceiver                    | 138 |

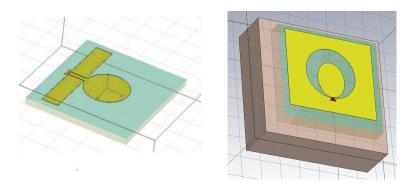

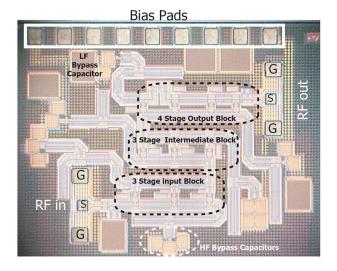

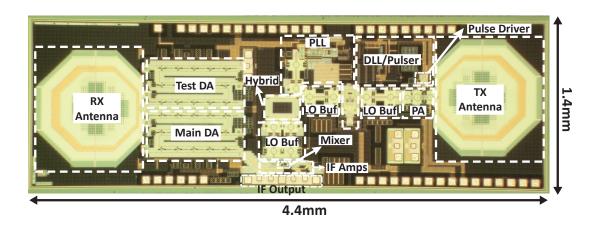

| 6.2  | Chip micrograph of the radar transceiver                                      |     |

| 6.3  | Layout of the baseband section                                                | 140 |

| 6.4  | Two-stage transformer-coupled power amplifier                                 | 141 |

| 6.5  | PA pulse driver schematics                                                    | 141 |

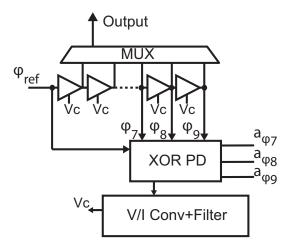

| 6.6  | PLL architecture implemented in TUSI transceiver                              | 142 |

| 6.7  | Conceptual schematics of delay-locked loop (DLL)                              | 143 |

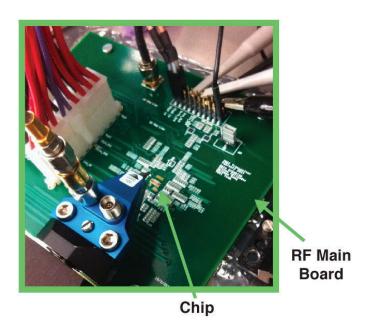

| 6.8  | Picture of the RF board in the measurement setup                              | 144 |

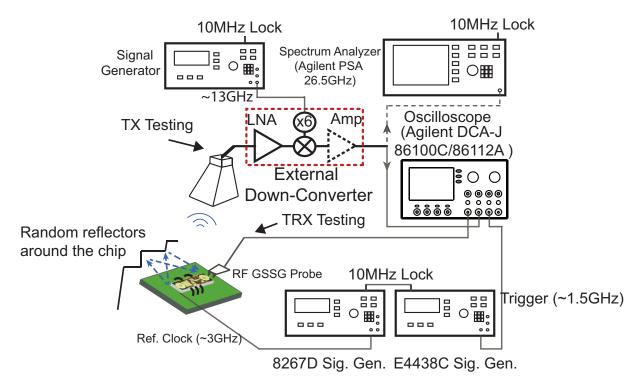

| 6.9  | Measurement setup for testing the radar transceiver                           | 145 |

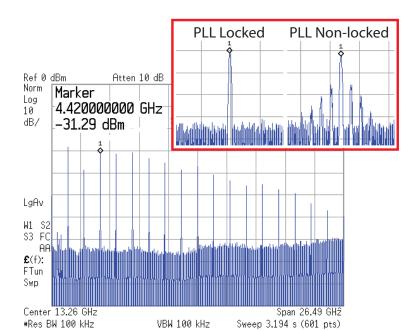

| 6.10 | Frequency domain measurements of the transceiver                              | 146 |

| 6.11 | Time-domain measurements with a non-locked PLL                                | 147 |

| 6.12 | PLL locking range based on various VCO frequency bands                        | 148 |

| 6.13 | Measurements of TRX pulse output waveform                                     | 148 |

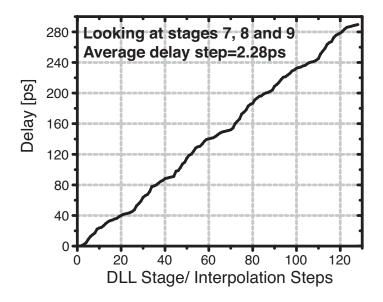

| 6.14 | Pulse delay profile in coarse setting                                         | 150 |

| 6.15 | Measured pulse delay (referenced to initial setting)                          | 151 |

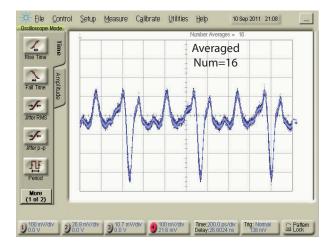

| 6.16 | Intercepted pulse from the transmitter                                        | 151 |

# List of Tables

| 4.1 | Measurements Summary for TUSI VS                                 | 75  |

|-----|------------------------------------------------------------------|-----|

| 4.2 | Measurements Summary for TUSI CS                                 | 83  |

| 5.1 | Performance comparison of the FBDA to the prior state of the art | 111 |

| 5.2 | Comparison table for the tapered DA                              | 119 |

| 5.3 | Transmission line parameters                                     | 121 |

| 6.1 | Summary of radar transceiver performance                         | 149 |

#### Acknowledgments

It is difficult for me to believe that my time at Berkeley has come to an end. My Cal experience has been an amazing journey- one that has shaped my life in many different ways. I was never planning on spending my whole life as a Cal grad student but this has been enjoyable and fulfilling and it is definitely strange for me not to be a Cal student anymore! The past few years would not have been what they were without the help and support of many people. Thank you to all!

First, I would like to thank my partner both in school and in life, Sahar. For the past six and a half years that we have been married (and nearly a decade of being together) she has enriched my life in many many different ways. We have grown up together and experienced the toughest transitions and periods side by side. She has always been a constant source of inspiration and encouragement. Words cannot express how grateful I am. My research and my thesis would not have been possible without her support at different levels; emotionally and intellectually. In research, she is the first person to hear my (at times crazy and dumb) ideas and that has been an amazing experience. Thank you for everything!

I could not have asked for a better adviser in supporting my ambitions and goals. Ali has been a great friend, mentor and teacher as well as academic adviser and has provided constant and generous support. I think he has a close to ideal balance in guiding graduate students. Initially, he provided substantial help to get me started. After that, he not only played a big role in technical guidance but also helped me learn how to learn. He has never "over-advised" me if a term like that exists. I have been given freedom to pursue different paths and I thank him for trusting me. I have learned many things from Ali both in science and engineering as well as the academic path in general. I also want to thank him for his excellent teaching of EE142, EE240, and EE242. He is knowledgeable, thoughtful, extremely intelligent and original and at the same time great-hearted, high-minded and considerate. It is not very common to find these characteristics in one person.

I would like to thank Professor Eli Yablonovitch for being on my qualifying exam and dissertation committees and also for his advice and support on many occasions during the past few years. I have always enjoyed our discussions and have learned a great deal from them. His unique and powerful way of approaching problems amazed me during classes and research discussions. Taking Eli's EE290B and EE236 courses were life-changing experiences. These were among the best courses I have ever taken and have had lasting effects on my education.

I would also like to thank Jan Rabaey and Steven Conolly for being on my PhD qualifying exam and dissertation committees. I have learned a lot from discussing various technologies and future wireless trends with Jan. He has been extremely supportive of my research. I also thank him for developing a collaborative and positive research environment at BWRC. Brainstorm meetings with Steve have been very interesting and intellectually fulfilling. His insight and experience in biomedical imaging and MRI have been a great source of information. I would also like to thank him for his excellent teaching of the medical imaging and

MRI courses at Berkeley.

My warmest gratitude goes to Haideh Khorramabadi, a great teacher and mentor. She has supported us in many different ways and has always been there for help and advice. She is one of the kindest and most respectable people I have come to know here at Berkeley. Thank you Haideh!

An important part of my Berkeley experience was the magnificent courses that are offered across campus. In this regard, in addition to the people mentioned previously, my sincere gratitude goes to professors Khorramabadi, Markovic, Rabaey, Bokor, Bahai, Carmena and Kuroda in the EECS department, professors Ganor and Cummings in the Physics department, professors Wu and Gronsky in the MSE department and professor S. Lee in the Bioengineering department.

My gratitude goes to all the people who helped me in this project. I owe thanks to Bagher (Ali) Afshar for his help in the design of power amplifiers. I would also like to thank the "Junior" graduate students Jun-Chau Chien, Steven Callender, and Shinwon Kang as well as the undergraduate students (Alex Pai, Alan Wu, Yasin Alipour) who helped me in various designs and were all at some point part of the "TUSI team". It was a privilege working with such smart and talented students.

Words can hardly do justice in showing the extent of my gratitude to many friends that I have been blessed with knowing at Berkeley or before. My warmest thanks go to Ashkan Borna, Ehsan Adabi, Ali Afshar and Arash Parsa for great discussions and being awesome friends at BWRC and beyond! I learned a great deal from Ehsan and Ali when I joined BWRC. My first tapeout would not have gone anywhere without their help. I also enjoyed the random but interesting discussions with Omar Bakr. One day our thoughts might actually converge to something great! I would also like to thank other members of Ali's group: Mounir Bohsali, Babak Heydari, Cristian Marcu, Debopriyo Chowdhury, Mohan Dunga, Wei-Hung Chen, Stefano Dal Toso, Peter Haldi, Patrick Reynaert, and Jiashu Chen. Many thanks to Matthew Spencer and Siva Thyagarajan for being outstanding TAs for the EE142 course.

I am also thankful to many BWRC students and friends including Simone Gambini, Louis Alarcon, Jesse Richmond, David Chen, Michael Mark, Tsung-Te Liu, Vahid Majidzadeh, Rikky Muller, Mervin John, Lingkai Kong, Chintan Thakkar, Antoine Frappe, and many others. I owe many thanks to BWRC and EECS faculty and staff including Tom Budinger, Elad Alon, Gary Kelson, Tom Boot, Sue Mellers, Brian Richards, Kevin Zimmerman, Brad Krebs, Bira Coelho, Mary Byrnes, Ruth Gjerde, Dana Jantz, and Patrick Hernan. My special thanks goes to my older friends Ashkan, Alireza, Hooman, Kia, Ehsan (Roosta), and Aria (the great!). It is amazing to see how we are all slowly converging to the same geographical location after so long.

I would like to thank Ali Tassoudji, Bo Sun, and Jorge Garcia, my mentors from Qualcomm CRD during the fellowship and the internship. I learned a great deal from my discussions with Ali on different antenna issues. Bo was just a wealth of knowledge and experience in every aspect of IC design. I also enjoyed my other internships at Tagarray Inc. and would like to thank Farokh Eskafi and Kourosh Pahlavan for the exciting opportunities.

I would like to acknowledge and thank professors Sharif-Bakhtiar, Bastani and Jahan-bagloo from my undergraduate at Sharif University. They helped shape my understanding of engineering as well as what it would take to continue down the academic path to PhD. I learned much of what I know of electronic and communication systems from them and I am very grateful for their great advice and teaching.

My greatest thanks and gratitude go to my parents Homayoun and Nasrin and also my brothers Iman and Alireza. This work is the result of their endless love and constant support. They must have seen something in me which I am yet to find myself!

# Chapter 1

# Introduction

### 1.1 Silicon-Based Medical Imager

Scaling has allowed silicon technology to enter exciting areas of research such as high-speed data communications, radar and imaging [2, 3, 4, 5, 6, 7, 8]. Due to its higher yield and reliability, silicon has outperformed III-V semiconductors in many millimeter-wave applications and is establishing itself as a market standard for high performance reliable systems. Moore's law is pushing silicon towards yet another application: bio-medical devices. Starting from 1970-80's, silicon technology has successfully transformed different areas from measurement instrumentation to personal computers, communication devices and more recently consumer electronics and ubiquitous computation/communication devices. The next big impact is thought to be in the field of bio-medical devices.

Information technology and medical devices will play a more significant role in wellness, healthcare and medicine. While consumer electronics have become ubiquitous and inexpensive, medical devices, by contrast, are still primarily found only in hospitals. There is a great potential benefit in using techniques developed in the consumer electronic industry and applying them to the healthcare market. To do this, substantial innovation is required to develop new sensors and devices that are fundamentally less invasive and use profoundly different physical phenomena to address medical applications. These devices will provide better service to a rapidly aging population at a fraction of the cost of todays technologies.

Some of the efforts are concentrated on designing new instruments and functionalities that have been made possible largely due to the effectiveness and miniaturization of electronics (e.g. brain-machine interfaces and large array neural-sensors). There is also an effort to tackle more conventional medical problems. Imaging is one such problem that can greatly benefit from cost-reduction and/or miniaturization. Today, imaging devices are largely confined to health-centers and some only in large hospitals. The dynamics of patient health-provider (doctors or emergency care units) interaction will radically change if these diagnostic tools are available at the local clinics rather than at long distances. Ultimately,

some of these tools will be available at homes and much closer to the patients.

The path to better utilization of silicon capabilities in medical imaging may well take us towards less conventional sensing and detection schemes. Devices and modalities that have the potential to benefit the most from the silicon advances are to be examined. Here, we focus on using the dielectric properties of tissue for imaging. Although with great potential, electrical properties and polarization characteristics in the microwave/mm-wave spectrum have not yet received much attention for diagnostic and screening applications. There are many specific cases where electrical properties can greatly enhance image quality or provide alternative contrast to conventional techniques. Electromagnetic signatures have been used for medical imaging applications [9] [10] [11]. Breast cancer screening technology is an example that has been pursued by various researchers in the past one or two decades [1] [10] [12]. One of the main limitations with this modality has been obtaining adequate signal to noise levels as well as sufficient cost/size reduction to be appealing compared to conventional modalities. These are areas where there is a great potential improvement to be made in using the techniques developed in consumer electronics and by leveraging Moore's law.

The goal of a dielectric imager is to detect boundaries with different electrical properties. This could be achieved by various signaling schemes, such as frequency chirp methods or pulse based techniques [13] [14] [7]. The focus of this work is on Time-Domain Ultra-wideband Synthetic Imaging (TUSI) where short pulses are transmitted and the reflections are recorded from multiple sites. The final imaging device is portable and battery operated and can be used to address a variety of applications.

We aim to realize an RF to millimeter-wave fully integrated radar transceiver with close to 25 ps modulated pulse in silicon technology [15] [16] [11]. To obtain short pulses, a new hybrid technique is employed in the transmitter that allows for independent control of start/stop time of the pulse in addition to potentially enabling finer tuning of pulse width without compromising the pulse amplitude. In addition, the concept of antentronics is introduced, where integrated circuits and antennas are intelligently combined to enhance desired antenna performance.

Extremely wideband signal amplification is another challenge for a pulsed-based radar. A large gain-bandwidth (GBW) product as well as minimal distortion in terms of amplitude ripple or group-delay variations are desirable. Various techniques to achieve wideband amplification in CMOS are described and the design and measurements of three different distributed amplifiers discussed.

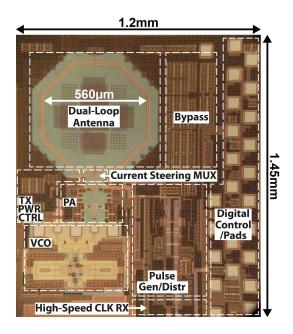

In the end, a single-chip pulsed-based coherent radar imager implemented in SiGe BiC-MOS process will be described.

### 1.2 Low-Cost Breast Cancer Screening

Worldwide, breast cancer is the second most common type of cancer after lung cancer. Women in the United Stated have the highest incidence of breast cancer in the world and

among them this is the most common cancer and the second most common cause of death [17] [18].

Currently, mammography (X-ray imaging of compressed breast) is the dominant modality in early detection schemes. The mammogram essentially is a map of breast density. The resolution of the obtained image could be high, however, the contrast is low. It is difficult, even impossible in many cases, to localize a tumorous structure of few milliliters in size or to distinguish between benign and malignant tumors. According to [17] [18], some of the limitations of mammography are missing up to 15% of breast cancers, difficulty with women with dense breasts, and large false positives (as high as 10-15%). 10% of mammograms result in inconclusive data, only 10% of which turns out to be malignancies. The technique causes discomfort, is not widely available, and due to the ionizing radiation, poses health risks. Ionizing radiation limits the frequency of test to 18-24 months and is only performed for the specific age bracket of +40 years old. These are major obstacles in detecting fast-growing invasive cancers.

Using microwaves to detect cancerous tissue relies on the difference in dielectric properties of malignant and normal tissue. There is evidence that tumors have higher water content than the normal tissue and for certain types of tumor, such as breast carcinoma surrounded by fatty tissue, the difference could be considerable. The obtained data available in the literature [1] [12] [10] [19] show the existence of contrast between cancerous tissue in the breast and the surrounding normal tissue. The contrast is considerably larger for adipose-dominated tissue in which the conductivity is much lower. This allows for a reliable detection scheme. The characteristic difference in the dielectric parameters (permittivity and conductivity) is mainly due to to increased water content from increased protein hydration and vascularization of the tumorous tissue.

### 1.3 Skin Cancer Detection

Another application of this imaging modality is in the detection of skin cancer. Around 160,000 new cases of melanoma are diagnosed worldwide each year with 48,000 melanoma-related deaths [17]. Malignant melanomas account for 75% of all deaths associated with skin cancer. Visual examination is often used to detect melanomas in the initial stage. Diagnosis is made using factors such as size, shape, color, border irregularities, presence of ulcer, tendency to bleed and other factors. Skin biopsy under local anesthesia is used on suspicious sites to determine the characteristics of the mole. However, there are multiple problems with the current methods in practice. Visual examination is generally prone to human errors. The accuracy of detection is somewhere between 55% and 82% [20, 21, 22, 23]. It may result in many suspicious sites especially in older patients and this often leads to waiting for the progress of the moles. This increases the risk of metastases or other complications. Also, the biopsy procedure is often inconvenient and produces many false alarm cases. Increasing the threshold for requiring a biopsy on the other hand increases the

risks of late detection. Other melanomas are amelonatic (colorless or flesh-colored) and this complicates the procedures.

Other skin cancer types are sometimes even more difficult to detect visually (e.g. Merkel cell carcinoma). This and the uncertainty in diagnosis and the issues involved with multiple biopsies leads to a significant requirement for an alternative method. The method needs to be simple, non-invasive, conclusive, easy to interpret, low-cost and able to be widespread. Millimeter-wave imaging is a good candidate since the tumor is close to the skin and hence the losses are low. Also, use of the higher frequency band in TUSI allows for improved depth and lateral resolution and could significantly reduce the number of biopsies. Patients with multiple suspicious sites (not rare in older patients) are able to be diagnosed at early stages.

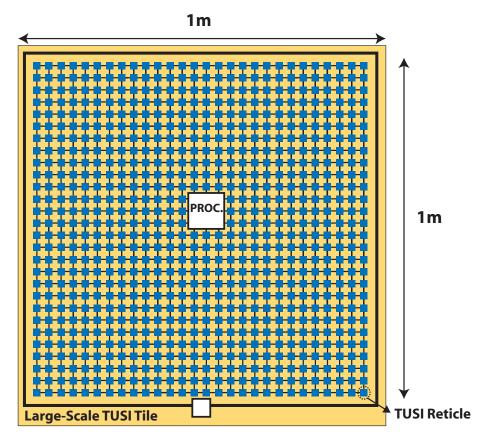

# 1.4 Other Applications

The TUSI array is designed to be pixel-scalable. This means that the single transceiver is design to be as agnostic as possible to the size of the array. Some of the other applications for this large and scalable array imager are in security imaging (e.g. airports) and for smart surfaces. The TUSI array can be used in large-scale smart and interactive surface that can detect 3D position of objects and by that facilitate various applications in human-computer interfaces. More details are provided in the next chapter.

### 1.5 Organization of the Dissertation

The rest of the dissertation is organized as follows. Chapter 2 presents an overview of the time-domain pulsed-based imager. Design concepts as well as the main challenges are described. System level simulations are provided. Chapter 3 discusses the design of various antenna elements for the 90 GHz transceiver. Antentronics is introduced as a technique to synthesize the impulse response of the antenna for desired radiation characteristics. Chapter 4 discusses the design and implementation of transmitter blocks that are capable of generating sub-50ps pulses from the antenna. Two different transmitter topologies together with the measurement results are presented. Chapter 5 reviews the design of the receiver circuits for the detection of the wideband pulse. Various amplifier topologies that provide large gain-bandwidth product are analyzed and compared to the state of the art. In the end, a 1.5 THz gain-bandwidth SiGe amplifier is presented for the final transceiver. In Chapter 6 we present the design, implementation, and measurements of a single chip radar transceiver in a SiGe BiCMOS process. Finally, the dissertation concludes with a summary of the key results and a discussion of future research in Chapter 7.

# Chapter 2

# Background and System Design

In this section some of the system-level challenges associated with the design of an array imager are briefly discussed.

A silicon-based imaging array for remote measurements of complex permittivity of tissue is introduced. Using a coherent pulsed measurement approach, this time-frequency resolved technique recovers the three dimensional mapping of electrical properties of the subject in the microwave/millimeter-wave frequency spectrum. Some of the major challenges in the design of the system will be examined.

In any imaging modality, a specific property of the tissue is mapped to the final image (e.g. tissue denisty/atomic number for X-ray or water content for MRI). We target electrical properties of tissue in the RF to mm-wave spectrum for cancer detection. These are the tissue responses to relatively weak electromagnetic fields dominated by electric properties of ensemble of cells. Charge asymmetry and rotational mobilities cause electric dipole moments that respond to the external electric field differently based on the properties of tissue.

The main obstacle in measurement of dielectric properties has been the low penetration depth of microwave fields in human body. Higher frequencies that yield better resolution have even higher losses. The dynamic range for obtaining such images has not been attainable with standard measurement instruments. With the accelerated pace of growth in silicon and electronic devices, reaching the required dynamic range is becoming a possibility.

# 2.1 Radar Imager

A high-resolution, phase-coherent, miniature-radar is designed for the detection of dielectric boundaries in various tissue structures. Historically, high-resolution radar came about primarily with the ability to control and detect the phase of the radar signal. Coherent sources facilitated this control over phase. Early on, after the realization of phase-coherent radar, concepts like synthetic aperture radar (SAR) came about. SAR uses the motion of radar antenna to synthesize a larger effective aperture [24].

A pulsed radar transmits short pulses and measures the reflections to determine the objects located in the vicinity. Pulses are sent periodically with a period of PRI (pulse repetition interval). In addition, these pulses are often sent in bursts depending on the exact radar application. As an example a burst might consist of 1,000 pulse intervals. In general we could describe the transmitted pulse train by:

$$P_{TX}(t) = \sum_{i=1}^{K} \sum_{j=1}^{N} x(t - iT_B - jT_p)$$

(2.1)

where

$$x(t) = A(t)\cos(2\pi f_0 t + \phi_{ii})$$

(2.2)

Here  $T_p$  is the PRI and  $T_B$  is the burst period. The pulses are sent, will get to the target and reflect back to the receiver. The received waveform will consist of a combination of pulses within the PRI depending on the shape and position of reflectors. If the center frequency of the pulse is locked to the PRI, then the phase of the received pulses are preserved and the phase information could be used to improve resolution.

In the array, in addition to the pulse arriving to the point from which it was transmitted, it will also arrive in all of the receivers in the array. From the time position of the pulses arriving to various array receivers, we can identify the dominant reflection points. For the processing, if sufficient SNR exists after averaging, delay-sum or other array processing algorithms could be used to construct the image. In addition, with the system architecture providing control over frequency, pulse width and position, one could also perform time-reversal or diffraction tomography algorithms [25] [26].

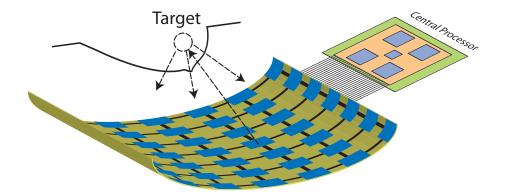

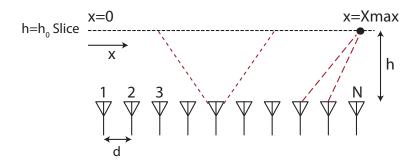

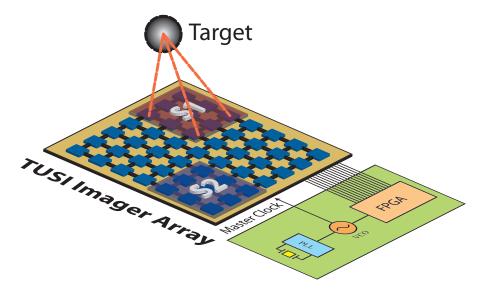

Fig. 2.1 shows the general concept of the array imager. Four physical elements provide the resolution for this imager: Large instantaneous bandwidth (short pulse), wide frequency tuning in frequency generation, large synthesized aperture, and phase coherency of the array. In this figure, each square represents a single element of the array which is implemented as a transceiver in silicon technology. This could be thought of as a single "pixel" of the imager. These pixels are then integrated on a common board to form the imager (Fig. 2.1). The single element is designed for scalability. Depending on the specific application, different array sizes or number of elements may be required. The element is designed to be as agnostic as possible to the size of the overall array.

### 2.2 Contrast

Contrast is the observable and detectable difference in the resulting image of two different tissue types. Higher contrast images are better in distinguishing different objects.

In an imaging system, contrast depends upon the physical mechanism used for imaging. As an example, in X-ray imaging, the tissue density and attenuation are mapped to the image. It does not provide a good soft tissue contrast and is mainly suitable for imaging

Figure 2.1: TUSI imager concept.

skeletal properties. In MRI, the system measures the spin density and this allows for a much better soft tissue contrast. Given the dominance of water in the body and the spin associated with hydrogen, MRI maps the water content in the body.

Dielectric properties of tissue can also be used for direct reflection imaging. These properties have been studied in the literature [27, 28, 29, 30]. Water is an important part for determining the tissue response at RF to mm-wave frequencies. In biological materials, water is a solvent for salts, protein, nucleic acids, and smaller molecules. Water's response can be modeled by a single-pole Debye relaxation equation with a primary dispersion in the GHz range ( $\tau \simeq 10 \mathrm{ps}$ ). At higher frequencies, another dispersion at approximately 670 GHz is observable. Besides water, the majority of biological macromolecules (e.g. proteins) act as polar molecules with permanent or induced dipole moment. The molecular structure, configuration, and size of these molecules determine the size of the dipole moments.

Measurements of tissue properties show several broad dispersions (e.g.  $\alpha$ ,  $\beta$  and  $\gamma$  dispersions) [27, 28, 29, 30]. The  $\alpha$  dispersion is at low frequency and is characterized by very high permittivity values. The  $\beta$  dispersion occurs at intermediate frequencies (radio frequencies) and originates mostly from the capacitive charging of the cellular membranes. At higher frequencies where the water response is dominant, the  $\gamma$  dispersion due to the dipolar polarization of tissue water takes place. The data for various tissue types is available from [27, 28, 29, 30].

For screening and diagnostic imaging applications, response contrast between normal and cancerous tissue is important. Various studies have shown this contrast for different tissues. For example, previous studies [1] [12] [10] have shown normal and malignant breast cancer tissue to have considerable contrast in the microwave frequency range. The char-

acteristic difference in the dielectric parameters (permittivity and conductivity) is mainly due to increased water content from increased protein hydration and vascularization of the tumorous tissue [31]. It can also be affected by other factors such as membrane potential differences, changes to cell connectivity, and sodium concentration. Necrosis in tumorous tissue leads to breakdown of cell membrane and affects low-frequency conductivity.

Fig. 2.2 shows the available dielectric contrast for normal breast tissue and cancerous tissue (from [1]). Based on the conductivity levels reported for normal tissue, the shown contrast is mainly between cancerous tissue and fat-dominated tissue. For connective and gland tissue in the breast, the contrast is smaller than what is reported here. Larger variability of dielectric properties for normal breast tissue has been reported in [32].

Figure 2.2: Dielectric-properties data for normal and malignant breast tissue (from [1]).

### 2.3 Resolution Basics

### 2.3.1 Depth Resolution

Resolution is a measure of the ability to distinguish two small objects that are close to each other. Spatial resolution is often described in terms of the point spread function or PSF. PSF describes the response of an imaging system to a point source or point object. The PSF can be thought of as the system's spatial impulse response [33].

Here, we will analyze resolution in radar terms. Ultimately, the goal is to define the general resolution in the sense of detecting two close by targets. Pulse-based radar sends out short time-domain pulses and detects the echoes/reflections from nearby scattering points. The depth/range resolution is given by [13]:

$$\delta R = \frac{c\tau}{2} \tag{2.3}$$

where c is the speed of light and  $\tau$  is the pulse width (Fig. 2.3).

Figure 2.3: Depth resolution in pulsed radar.

It is clear that a large BW is required to achieve mm-range resolution level. The wave velocity being lower in tissue helps reduce this requirement but this is often negated by the increase in dispersion and pulse-spread. For applications such as tumor diagnostic scans, detection of mm-size tumors is desirable. As will be discussed later, in this system a pulse width close to 25 ps is targeted. This will provide resolution close to 1- 2 mm in tissue. Generating, controlling, transmitting, and detecting narrow pulses down to 25 ps poses many circuit and system design challenges that will be described in future chapters.

#### 2.3.2 Lateral Resolution

Lateral or cross resolution is set by antenna parameters and more specifically the aperture of the imager. In order for the waves from two lateral points to be distinguishable, the received wave from the two points has to have some phase-shift across the antenna aperture. If the phase-shift is too small, the two points will be indistinguishable. Assuming this phase shift to be 180 degrees, we can derive a relationship between the lateral resolution,  $\delta x$ , the range, R, the aperture, D, and the wavelength,  $\lambda$  [13]

$$\delta x = \frac{\lambda R}{D} \tag{2.4}$$

One can also derive a similar relationship by taking into account an approximation for the beamwidth,  $\theta = \frac{\lambda}{D}$ , and multiplying that by the range to get the lateral resolution,  $\delta x = R\theta$ .

The end result is that for an antenna to have a lateral resolution close to the wavelength, the overall aperture and the distance to the image need to be of the same order. It has to

Figure 2.4: Frequency-domain array with grating lobes. Array uses a  $2\lambda$  element spacing. Grating lobes are visible.

be pointed out that for time-based pulsed radar with a large aperture the pulse-width as well as delay/phase resolution will also play a role and the equations only serve as a first order approximation for lateral resolution.

In our system, the high-frequency band (94 GHz) is designed for the best resolution level. For example, with an aperture of 3 cm and maximum range of 3-5 cm, we need an effective wavelength of close to 1.5 mm in tissue to obtain a preprocessed resolution of 2-3 mm. With these numbers and an effective dielectric constant of 4, a 94 GHz carrier can provide the required cross-resolution. Post-processing can further enhance the resolution to obtain closer to 1 mm voxels.

### 2.4 Pulsed-Based Antenna Arrays

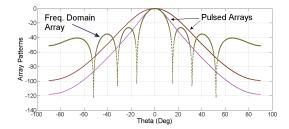

In conventional antenna arrays, as previously discussed, the broadside beam-width or resolution improves with array aperture [34]. This shows that to improve resolution we need to increase the number of elements or effectively the size of the array. To avoid increasing total system cost or complexity, we can use spatial sub-sampling and increase the spacing between array elements so that the same aperture will use less number of elements. However, in a conventional frequency domain array, this leads to grating lobes which are essentially secondary main-lobes that produce ambiguity in the direction of arrival [34]. An example of this is shown in Fig. 2.4.

Pulsed based arrays use pulses to send and receive data from various array elements [35, 36]. In contrast to sine-based systems, these arrays do not posses side-lobes and have a side-level that is dependent on how well the space is sampled. The main-lobe width of these arrays is dependent on how many samples are taken. Qualitatively, this could be described as follows: In a sine based array, the signals have sidelobes since they are extended in time and can interfere (constructively) at an angle that is off-center. If the antenna spacing meets the Nyquist criteria then this interference only shows a sidelobe (as compared to a

Figure 2.5: Comparison of pulsed and frequency-domain arrays.

grating lobe). In pulse arrays, however, the signals are so short in time so that the result is either addition of all (in the main beam) or just a sum of signals added incoherently. An example of response of a pulsed array with only side-levels is shown in Fig. 2.5.

In pulsed based-systems instead of frequency and wavelength, pulse width and observation window are well defined. Therefore, comparisons of array element spacing need to compare to quantities such as vT in which v is the wave velocity and T is the observation time. Later in the chapter we will describe the issue of false illumination points in a pulsed array.

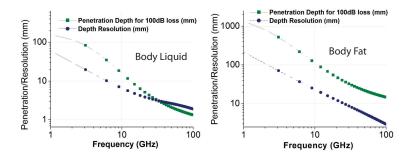

# 2.5 Signal-to-Noise Ratio

Another challenge in obtaining effective images through reflections in the microwave and mm-wave regime is the large signal loss in human body. Given that unlike other modalities these losses are the main contrast mechanisms, the system should work with very small SNR levels. Fig. 2.6 shows simulated signal penetration and raw resolution in body fat and fluid based on published models [30]. Penetration depth is plotted for 100 dB of tolerated total loss and resolution is based on signals with 30% relative BW to carrier. This is a first-order approximation for the preprocessed resolution obtainable for each frequency. It is clear that, especially for images involving body fluids, the obtainable resolution becomes smaller than penetration depth for higher frequencies and therefore the low frequency regime has to be simultaneously leveraged. Also, depending on the cross section of the target, the actual loss may be more by 20-30 dB.

For the mentioned 100 dB loss, frequency BW close to 30-40 GHz, and transmit peak power close to 20 dBm, the obtained SNR is close to -30 to -40 dB. There is a need for large number of array elements as well as long integration windows to improve the SNR levels. Synchronized arrays can generate an increase in transmitted signal power by a maximum of  $N^2$ . However, array losses due to lack of perfect synchronization or quantization in delay generation techniques, could result in both power losses as well as pulse widening or "spatial dispersion" (described in section 2.9.3). Beamforming will also require a wideband delay element to shift the modulated pulse signal in time domain. Narrowband approximations to

Figure 2.6: Penetration depth and resolution for body fat and body liquid assuming 30% relative BW and 100dB two-way loss.

this delay (fixed phase shifts) will encounter unacceptable errors for larger arrays occupying a wide frequency bandwidth. In this imager, the transmitter uses a delay-locked-loop to move the envelope of the pulse before it is multiplied by the carrier. The carrier phase need to also be shifted by a narrowband phase shifter. After combining (multiplying) the carrier and the envelope, a delayed version of the modulated pulse is obtained and the need for a wideband phase shifter is eliminated.

### 2.6 Resolution Limits

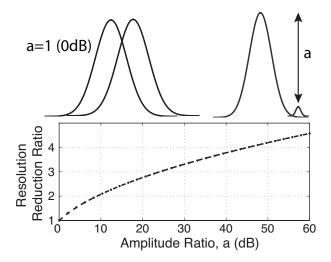

In the case of reflection measurements for medical applications, the resolution limit is tighter than the classical two-point radar resolution. This is due to the large dynamic range of signal levels at the receiver. Distinguishing multiple targets with largely different amplitudes is more difficult than when the amplitude levels cover a smaller range.

Resolution limits generally address two issues: ability to distinguish close objects (with same or different amplitudes) and the ability to pinpoint the position of an object in the presence of noise. It will be shown that both resolution limits improve with enhancing the signal bandwidth (BW).

As previously discussed, for two equi-amplitude signals, the resolution will be  $\frac{c\tau}{2}$  (for pulsewidth of  $\tau$ ) or equivalently  $\frac{c}{2BW}$  (where BW is the signal bandwidth for an alternatively modulated radar signal) [13].

If the two signals have different amplitudes, especially in the case where one completely dominates the other, this becomes more restricting. Fig. 2.7 shows the effect of obtaining lower resolution with larger amplitude ratios. For example, if a target is 20 dB lower than a main reflector (deeper in a lossy medium or smaller cross-section), the resolution decreases by approximately a factor of 3. Therefore, we can conclude that resolution in a lossy medium is also a function of depth due to the differences in signal amplitudes.

In order to counter this effect, we need to either push for narrower pulse generation

Figure 2.7: Resolution reduction effect from large variations in amplitude. Here, the resolution reduction ratio is shown normalized to the case of a = 0dB.

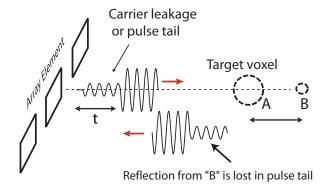

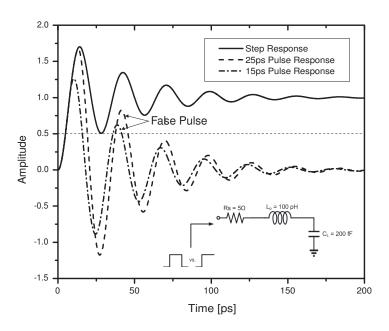

Figure 2.8: Effect of pulse integrity on performance (echo effect shown here).

(more BW) or compensate the effect with assumed prior knowledge of pulse shape and time-gated post-processing. The former is difficult especially that this puts a limit on pulse fidelity and pulse amplitude roll-off in time domain. The latter requires better knowledge of dispersion characteristics. With that knowledge, one could also apply pre-processing to the transmit waveform to improve resolution. In all cases, it is necessary for this system to utilize calibration/compensation algorithms to achieve the resolution limit.

Pulse fidelity is also important for resolution. Fig. 2.8 illustrates the effect of a pulse tail on detection. A large leakage or pulse tail manifests as a false echo that can completely overwhelm a reflection from a smaller object.

Resolution is also restricted from accurately identifying a pulse edge position. We can calculate the Cramer-Rao lower bound (CRLB) for the estimation of the pulse arrival time

Figure 2.9: Received pulsed edge with noise.

(and from that the position through  $R_0 = vt_0/2$  where v is the wave propagation velocity). We will assume a white noise or equivalently colored noise with sampling at nulls of the auto-correlation function. The lower bound on the timing uncertainty can be derived as [37]:

$$\overline{(t_0)^2} = \frac{1}{\beta^2 \frac{E}{N_0/2}} \tag{2.5}$$

where E is the pulse energy,  $N_0$  the noise spectral density and  $\beta$  is an effective bandwidth [37]. Once again, a sharper and narrower pulse results in a better decision on the pulse arrival time.

This result can be explained by Fig. 2.9. An edge from a pulse of width  $\tau$  and rise time  $t_r$  is shown together with additive noise. The quantity to be estimated is the arrival edge of the pulse. The amplitude noise gets "translated" to timing uncertainty through the slope of the pulse edge and hence:

$$\overline{t_0^2} = \frac{\overline{n^2}}{slope^2} = \frac{\overline{n^2}}{A^2/t_r^2} = \frac{t_r^2}{SNR}$$

(2.6)

where A is the pulse amplitude and  $\overline{n^2}$  is the noise variance  $(N_0B)$ . Given that signal power (S) is  $\frac{E}{\tau}$  and noise BW is B, equation (2.6) can be rewritten as:

$$\overline{t_0}^2 = \frac{t_r^2 B \tau}{\frac{E}{N_0}} = \frac{1}{B_{eff}^2 \frac{E}{N_0}}$$

(2.7)

where the last part is due to the relationship between  $\tau$ ,  $t_r$  and noise BW (B) resulting in an effective bandwidth  $(B_{eff})$  dependent on the specific pulse shape. Thermal noise is not the only limiting factor in obtaining the resolution. Direct timing jitter from the transmitter  $(\sigma_{TX})$ , receiver  $(\sigma_{RX})$  or from phase noise on reference oscillators  $(\sigma_{PN})$  could also add to the final variance.

$$\overline{t_0^2} = \frac{1}{\beta^2 \frac{E}{N_0}} + \sigma_{TX}^2 + \sigma_{RX}^2 + \sigma_{PN}^2$$

(2.8)

Figure 2.10: TUSI array imager on flexible substrate.

# 2.7 TUSI Imager

This dissertation describes the design of a Time-Domain Ultra-Wideband Synthetic Imager or TUSI. TUSI implements a synchronized time-domain array with a two-tier integration scheme. In the first tier it integrates single coherent transceiver elements on a chip. This is a bi-static setup (separate TX and RX) to reduce direct leakage effects. Time-gating eliminates "delayed" leakage from TX.

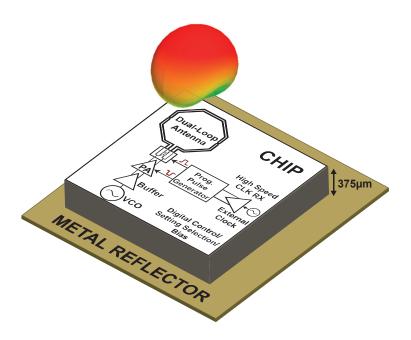

In the second tier, which enables a scalable array, single-element chips are integrated on daughterboards, multiples of which are then mounted on a common motherboard. The motherboard also integrates clock and power distribution circuits as well as the central processor (Fig. 2.1). Distributed sampling with partial local computation reduces the aggregate data rate provided to the central processor to a few hundred Mbps.

Depending on the specific application, the array may use a flexible substrate. In that case, the processing unit will have a remote connection to the array itself. The flexible-substrate imager will reside on the body separated by a matching layer. The conceptual shape of the imager on the flexible substrate is shown in Fig. 2.10.

Using the individual transceivers in the array, the TUSI system is capable of imaging in both coherent multi-static and coherent MIMO modes. Several techniques are used to improve the resolution beyond the raw pulse-width limited region. A high pulse repetition frequency (PRF) results in better averaging gain in a given window. TUSI uses frequencies spanning from low microwave to mm-waves to provide flexibility in face of diverse loss mechanisms in different tissue types. In addition, at each of the spectral bands, the center frequency is swept on a batch-by-batch basis to cover the frequency spaces (in the output comb) caused by the high PRF.

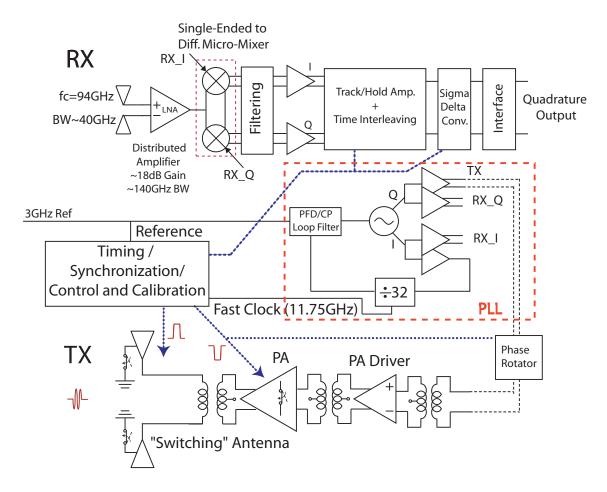

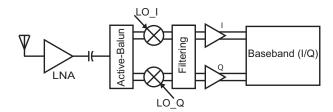

The block diagram of the system is shown in Fig. 2.11. This is the block diagram of the high-frequency channel that has both of the antennas integrated on the chip. On the receiver the signal goes through a wideband antenna system. The final antenna is designed

as a wideband but resonant tapered loop antenna. The non-idealities of the receiver antenna can be partially compensated for in the processing. The signal then goes through a wideband gain stage. This is the common gain element that is shared between various frequency bands. For the 94 GHz band, the amplifier is followed by a micro-mixer. In the baseband, the quadrature signals go through 10 dB gain and buffering. Signal conditioning, filtering, and digitization happens on the chip. Partial analog/digital integration reduces the interface data-rate to about 1-10Mbps.

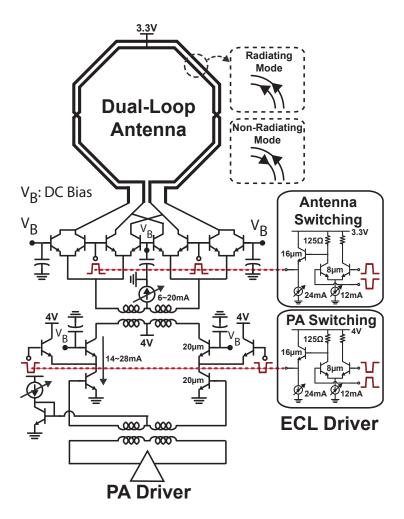

In the transmitter the carrier signal from the PLL goes through a narrow-band phase shifter followed by buffer and power amplifier. The carrier is multiplied by the envelope both in the PA as well as the antenna element. As will be described in future chapters, switching happens either in each of the PA or antenna or through a hybrid switching technique. The antenna element in the transmitter, therefore, must incorporate switching functionality. This is the topic of chapter 3.

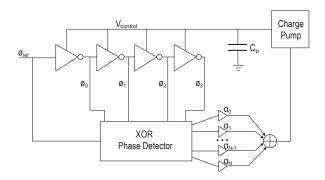

A 3 GHz reference clock is distributed to each of the transceivers. The reference clock is used to drive central timing circuits, the DLL and acts as the reference clock for the PLL. The DLL sets the PRF and adjusts the position of the pulse. An interpolation scheme is utilized in the DLL architecture (Fig. 2.12). A pulser generates activation signals that drive the PA or the antenna as well as the sampling circuits. In one implementation, an additional "fast clock" is extracted from the PLL chain and is used for further fine-tune synchronization. To reduce the signal dynamic range incident upon the electronic elements, a time-stretched gating circuit is employed. During the averaging period, each "path" will work with a fixed signal level and this reduces the dynamic range.

To enhance the SNR level at the receiver, extensive signal averaging is performed. A sigma-delta modulator is used for data conversion. In the averaging scheme, the quantization noise is shaped through the filter while the white input noise from the receiver sees a "brickwall" filter (no shaping). For the averaging window of larger than 1 ms, as targeted here, the quantization component of noise will be extensively suppressed. The thermal input noise provides dithering to the sigma-delta converter and this reduces the tones from the limit-cycle oscillations.

### 2.8 Undesirable Coupling of SNR with Resolution

In many imaging systems the resolution and SNR are tightly coupled through change of signal energy with pixel size. Improving the resolution often requires better SNR levels. This is also true for super-resolution techniques that leverage prior knowledge of the waveform. In this imaging modality, jitter limits the number of averaging cycles for a specific target resolution. Sampling and accumulating with a non-ideal clock signal is equivalent to convolving the signal with the probability distribution function (p.d.f.) of the clock arrival edge (in the limit) [38]. For a gaussian p.d.f. of timing jitter with variance of  $\sigma^2$ , the signal is effectively low-pass filtered by a gaussian filter of an equivalent bandwidth ( $\propto \frac{1}{\sigma}$ ).

Figure 2.11: Proposed array architecture and the block diagram of the TUSI transceiver for the high frequency band.

Figure 2.12: Delay-Locked Loop architecture for generating fine time steps.

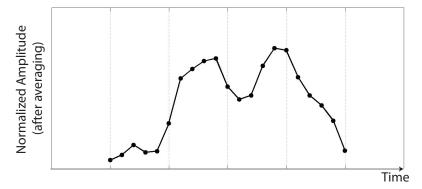

Detection with rms jitter of 1ps. Two pulses are distinguishable.

Detection with rms jitter of 10ps. Two pulses are not distinguishable.

Figure 2.13: System simulations of the transmit/receive chain. LO phase noise, transmit and receive jitter, thermal noise and quantization noise effects are included. Two pulses are 25ps wide and are separated by 60ps. The averaging window is assumed to be 1ms with PRF=1GHz. In one case the system has a total rms jitter of 1ps and in the other 10ps.

Therefore, for long integration times, the image resolution is reduced. This limits the total jitter budget of the transmitter and the receiver to 0.5-5ps depending on range resolution required. Fig. 2.13 shows this effect through transmit/receive system simulations. Averaging has been performed to bring the signal out of noise.

# 2.9 Limits of Integration for Closing the SNR Gap

The SNR is improved by 10log(N) with having N pulses integrated coherently. The receiver does not use an RF phased-array architecture due to lack of scalability for large apertures. Phase/amplitude errors (from narrow-band approximation as well as from other sources) will limit the resolution in case of RF phase-shifters. Since processing is performed

in the digital domain, extensive averaging is performed on the RX to compensate for the low SNR. However, there are limitations in increasing the averaging window indefinitely.

#### 2.9.1 Stability of the Imaging Setup

Similar to microscopic vibrations that limit optical resolution, macroscopic vibrations lead to spatial filtering of the object and limit the obtainable resolution. Without stabilization techniques, averaging windows are limited to about 10ms-1s, especially for a hand-held imager that is the target of this study.

#### 2.9.2 Limitations on Increasing the PRF

A repetitive pulse transmission approach is being utilized in which short pulses of width  $\tau$  are transmitted with a repetition frequency of PRF. Here, given a fixed total integration window, we can increase the number of pulses being averaged by increasing the PRF. However, there are multiple limitations for this approach. First of all, the maximum unambiguous range can limit high PRF as it does in classical radar [13]. In a time-based array system, as proposed here, another limitation is due to the cross-range ambiguity from high PRF. Intuitively, this is related to the fact that for large arrays and beam angles, the delay spread between first and last element can be quite large. For a far-field array this difference is  $(N-1)d\sin(\theta)/v$  where N is the number of elements in array, d is the elements spacing and  $\theta$  the beam angle from broadside. As an example, with an aperture of 10 cm, 45 degrees angle, and  $v = 1.5 \times 10^8$ , we need 466 ps delays. With the PRF approaching a few GHz this will potentially cause ambiguity in angle of incidence. If, for example, the PRI is set to 466 ps, the signal from element at the near point of the array to the desired direction combines with the second PRF signal of the element at the far end for a sidelobe in  $\theta = 0^\circ$  direction.

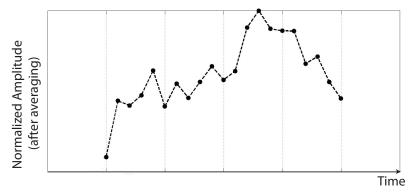

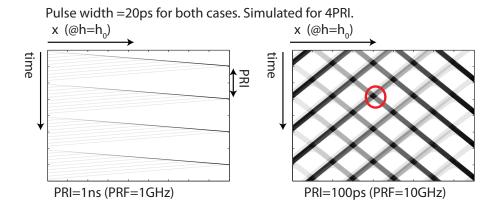

If the object resides in the near-field of the array, this relationship will be different but in essence one can assume that the delay gets larger with array size. Once this delay difference becomes comparable to the pulse repetition interval (PRI or 1/PRF), secondary "illumination" points will appear and cause ambiguity. Fig. 2.14 shows this effect. This is a gray scale coding of the received amplitude versus horizontal position and time. The arrays are focused to x=Xmax (Fig. 2.15). In one case (left) the period is chosen to avoid range ambiguity. The second case is for a much higher PRF (same pulse width and distance). Multiple focused points are observed. For illustration purposes a sparse array (large antenna spacing) is chosen to exaggerate secondary focus point amplitudes. In conventional arrays the actual peaks will be smaller.

### 2.9.3 Accurate Delay Generation

The spatial resolution is a function of the pulse width as well as the delay steps that perform beamforming. The time-step quantization smears multiple reflection points and

Figure 2.14: Received signal (gray-scale coded, dark=large amplitude) at a fixed vertical distance from a 10-element linear sparse-array (at  $h = h_0$ ). The X-axis is the horizontal position (x) and the y axis is time. The array is focused at x=Xmax and simulations are done for 4PRI periods. The circle shows one of the ambiguous points.

Figure 2.15: Linear antenna array with element spacing d. Here, a slice at vertical distance  $h_0$  from the array is being analyzed.

knocks down or distorts high spatial-frequency components of the image. To calculate the required time-steps, we will first assume a full 180° field-of-view (FOV) for individual antenna elements. With this, we can identify two timing-step requirements. One is related to the relative delay required on two antenna elements when they are focusing on a single point  $(\overrightarrow{r} = \overrightarrow{r_0})$ . The second is for one antenna element focusing on two adjacent resolution pixels. It could be seen that these problems are geometrically equivalent as long as the array spacing and the pixel sizes are approximately the same dimension. We will analyze the case of adjacent antennas focusing on a single point.

To find the time step we will take the case where we are focusing at a slice with vertical distance h from the array and at x = 0 (Fig. 2.15). For  $h \gg d$  the worst case will be the delay difference between the first two elements (directly beneath the object). We can

approximate this as:

$$\Delta \tau_{min} \simeq \frac{d}{2v} \times \frac{d}{h} = \frac{\frac{d}{2v}}{\alpha}$$

(2.9)

where d is the antenna spacing. The other extreme case is where  $h \ll (N-1)d$  in which the delay difference approaches d/v in the limit. Obviously (2.9) is the limiting factor in this case. Assuming PRF = T and center frequency of  $f_0$ , the  $\alpha$  factor with an antenna spacing of half-wavelength (material wavelength or  $\lambda_g$ ) is going to be:

$$\alpha = \frac{h_{max}}{d} = \frac{h_{max}}{\lambda/2} = \frac{vT/2}{v/2f_0} = f_0 \times T$$

(2.10)

Here, the maximum range is replaced with a function of PRF. Intuitively, larger T dictates longer distances which leads to a smaller observation angle. This leads to a finer delay step requirement (larger  $\alpha$ ). In addition to that, a larger center frequency will also lead to smaller antenna spacing and hence a smaller observation angles. As an example, for PRF = 1GHz and  $f_0 = 90GHz$  we have  $\alpha = 90$ , and we need a delay step of:

$$\Delta \tau_{min} \simeq \frac{\frac{\lambda/2}{2v}}{\alpha} = \frac{1}{4f_0 \alpha} \tag{2.11}$$

This will translate to a raw delay step requirement of 30fs which of course is beyond reach. In the calculated scenario, under worst range/cross-range conditions this delay resolution results in no quantization noise. However, numerous frequency/time domain signal processing techniques can mitigate the error from non-ideal steps.

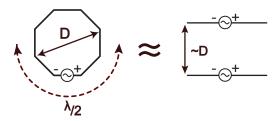

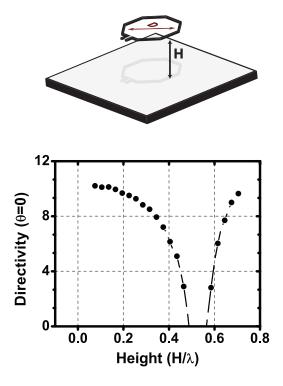

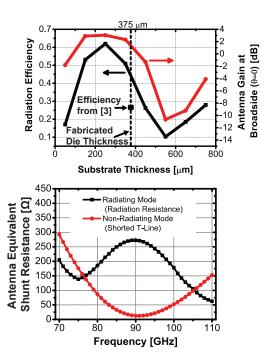

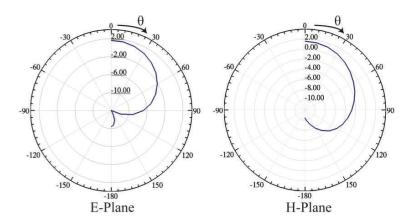

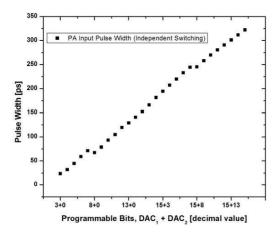

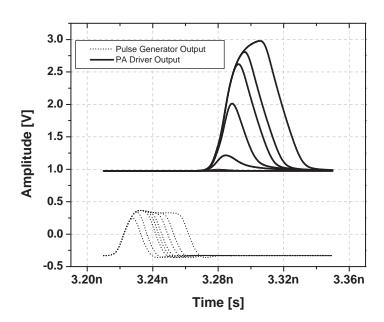

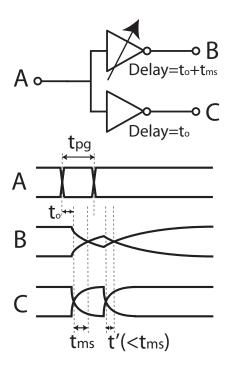

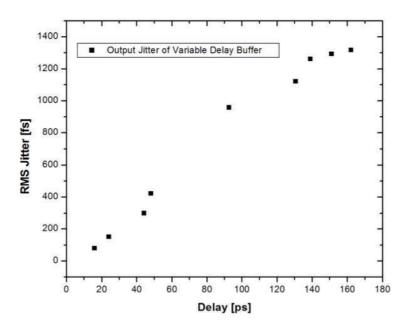

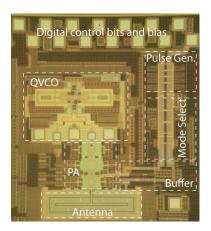

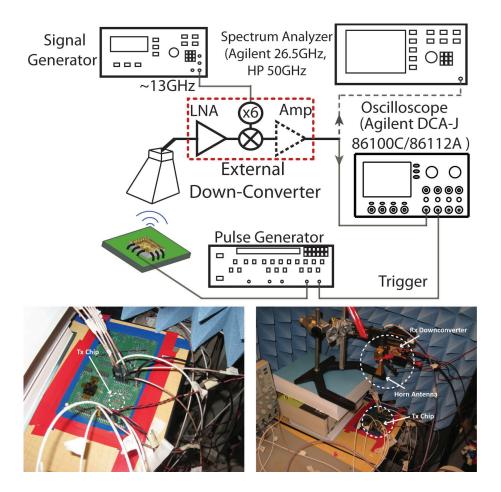

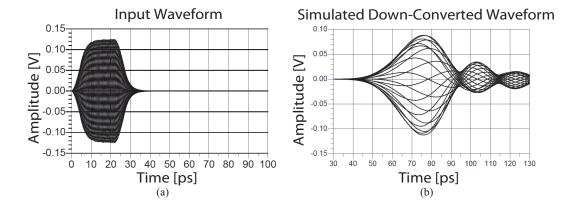

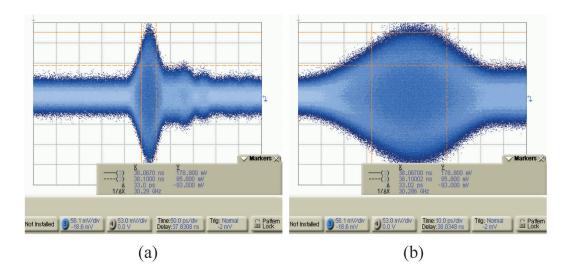

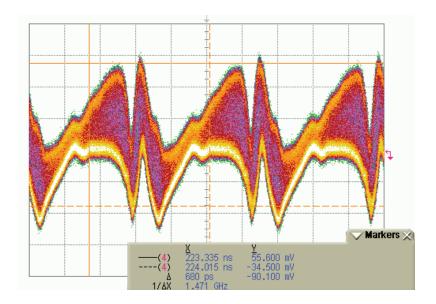

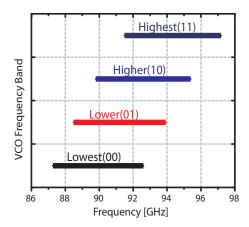

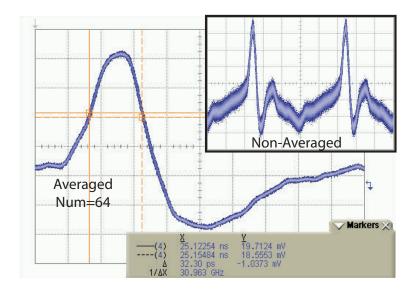

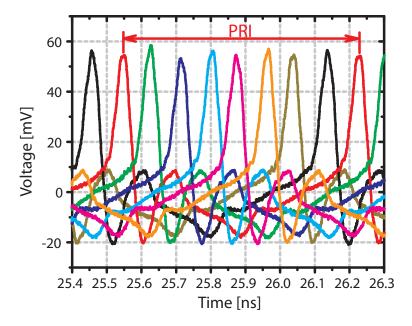

We can also see this through computing the range inaccuracy incurred if there is a quantization noise in delay step. This is yet another way through which resolution (range accuracy) and SNR (ability to energy-combine sources coherently) are coupled. Trading off resolution for SNR is needed especially in cases where deeper signal penetration in tissue is required.