## Formal Verification and Synthesis for Quality-of-Service in On-Chip Networks

Daniel Holcomb

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-228 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-228.html

December 19, 2013

Copyright © 2013, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Formal Verification and Synthesis for Quality-of-Service in On-Chip Networks

by

#### Daniel Edward Holcomb

B.S. (University of Massachusetts Amherst) 2005 M.S. (University of Massachusetts Amherst) 2007

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge: Professor Sanjit A. Seshia, Chair Professor Andreas Kuehlmann Professor Lee Schruben

Fall 2013

| The dissertation of Daniel Edward Holcon | nb is approved: |

|------------------------------------------|-----------------|

| Chair                                    | Date            |

|                                          | Date            |

|                                          | Date            |

University of California, Berkeley

### Formal Verification and Synthesis for Quality-of-Service in On-Chip Networks

Copyright 2013

by

Daniel Edward Holcomb

#### **Abstract**

Formal Verification and Synthesis for Quality-of-Service in On-Chip Networks

by

#### Daniel Edward Holcomb

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Sanjit A. Seshia, Chair

Quality-of-service (QoS) in on-chip communication networks has a tremendous impact on overall system performance in today's era of ever-increasing core counts. Yet, Networks-on-Chip (NoCs) are still designed and analyzed using RTL simulation, or analysis of highly abstracted models. The formal techniques that are used in core components do not find use in QoS verification due to the scale of the problems of interest, such as verifying latency bounds of hundreds of cycles.

This dissertation presents my recent work toward leveraging formal methods for NoC design and QoS verification. In particular, it addresses the problems of (1) verifying end-to-end latency bounds in a mesh network using abstraction; (2) scalable latency verification using compositional inductive proofs; and (3) optimal buffer sizing based on bounded model checking.

Professor Sanjit A. Seshia Dissertation Committee Chair

## **Contents**

| Li | st of l | Figures       |                                | v    |

|----|---------|---------------|--------------------------------|------|

| Li | st of ' | <b>Fables</b> |                                | vii  |

| 1  | Intr    | oduction      | ı                              | 1    |

|    | 1.1     | Thesis        | Statement                      | . 1  |

|    | 1.2     | Thesis        | Contributions                  | . 2  |

|    | 1.3     | Thesis        | Overview                       | . 3  |

| Ι  | Ba      | ckgrou        | nd                             | 4    |

| 2  | On-     | chip Cor      | nmunication Networks           | 5    |

|    | 2.1     | Motiva        | tion for NoCs                  | . 5  |

|    | 2.2     | Definin       | g Characteristics of an NoC    | . 6  |

|    |         | 2.2.1         | Topology                       | . 7  |

|    |         | 2.2.2         | Flow Control                   | . 7  |

|    |         | 2.2.3         | Routing                        | . 8  |

|    |         | 2.2.4         | Architectural Parameters       | . 8  |

|    | 2.3     | Quality       | of Service                     | . 9  |

|    | 2.4     | Modeli        | ng NoC                         | . 9  |

|    |         | 2.4.1         | Hardware Description Languages | . 10 |

|    |         | 2.4.2         | Analytical Models              | . 11 |

|    |         | 2.4.3         | Preview of xMAS Formalism      | . 12 |

| 3  | For     | nal Veri      | fication                       | 13   |

|    | 3.1     | Linear '      | Temporal Logic (LTL)           | . 13 |

|    |         | 3.1.1         | Safety and Liveness Properties | . 14 |

|    |         | 3.1.2         | Bounded Liveness Properties    | . 14 |

|    | 3 2     | Model         | Charling                       | 15   |

|    |      | 3.2.1    | Boolean Satisfiability Problem                           | 16 |

|----|------|----------|----------------------------------------------------------|----|

|    |      | 3.2.2    | Bounded Model Checking                                   | 16 |

|    |      | 3.2.3    | Induction                                                | 17 |

|    |      | 3.2.4    | IC3 / Property-Directed Reachability                     | 18 |

|    |      | 3.2.5    | Model Checking using Satisfiability Modulo Theories      | 18 |

| 4  | Fori | mal No(  | C Modeling                                               | 20 |

|    | 4.1  | Execut   | table Microarchitectural Specifications (xMAS)           | 20 |

|    |      | 4.1.1    | Communication over Channels                              | 21 |

|    |      | 4.1.2    | Data Types in xMAS                                       | 22 |

|    |      | 4.1.3    | xMAS Primitives                                          | 23 |

|    | 4.2  | Impler   | mentation of Queues                                      | 27 |

|    |      | 4.2.1    | Queues as Circular Buffers                               | 27 |

|    |      | 4.2.2    | Queues as Records                                        | 29 |

|    | 4.3  | Model    | of Router Core                                           | 29 |

|    | 4.4  | Check    | ing Latency Bound Properties on Network Model            | 32 |

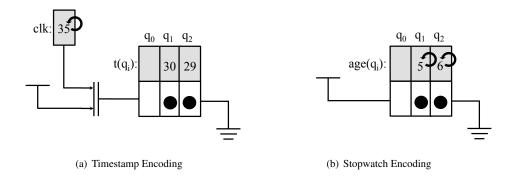

|    |      | 4.4.1    | Timestamp Encoding                                       | 33 |

|    |      | 4.4.2    | Stopwatch Encoding                                       | 34 |

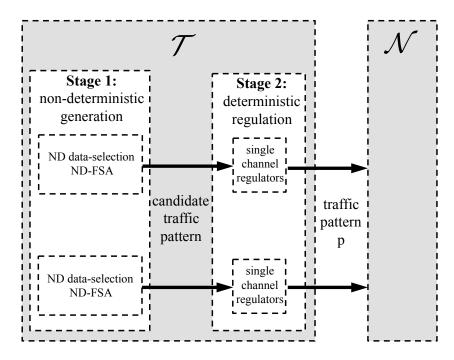

|    | 4.5  | Forma    | l Traffic Model                                          | 34 |

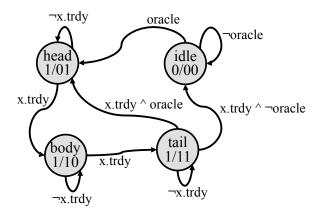

|    |      | 4.5.1    | Stage 1 of Traffic Model: Generating Candidate Patterns  | 36 |

|    |      | 4.5.2    | Stage 2 of Traffic Model: Deterministic Rate Constraints | 37 |

|    |      |          |                                                          |    |

| II | Sc   | alable   | Latency Verification                                     | 40 |

| 5  | Con  | npositio | nal Reasoning using Traffic Abstraction                  | 42 |

|    | 5.1  | Introdu  | uction                                                   | 42 |

|    | 5.2  | Prelim   | inaries                                                  | 44 |

|    |      | 5.2.1    | Basic Definitions                                        | 44 |

|    |      | 5.2.2    | Smallest Verifiable Latency Bound                        | 45 |

|    | 5.3  | Traffic  | Model Inference                                          | 45 |

|    |      | 5.3.1    | Form of Traffic Model                                    | 46 |

|    |      | 5.3.2    | Inferring Traffic Model Parameters from RTL Simulations  | 48 |

|    |      | 5.3.3    | Creating Traffic Model from Constraints                  | 48 |

|    | 5.4  | Experi   | mental Results                                           | 49 |

|    |      | 5.4.1    | Convergence of Traffic Model Inference                   | 50 |

|    |      | 5.4.2    | Latency Verification using Inferred Models               | 50 |

|    | 5.5  | Relate   | d Work                                                   | 54 |

|    | 5.6  | Concli   | usion and Discussion                                     | 55 |

|    |      | 5.6.1     | BMC Depth and Completeness                                        | 55 |

|----|------|-----------|-------------------------------------------------------------------|----|

|    |      | 5.6.2     | Limitations of Proposed Approach                                  | 56 |

|    |      | 5.6.3     | Lessons From this Chapter that Shaped Chapter 6                   | 57 |

| 6  | Con  | positio   | onal Proofs using Induction                                       | 59 |

|    | 6.1  | Introdu   | uction                                                            | 59 |

|    | 6.2  | Prelim    | inaries                                                           | 61 |

|    |      | 6.2.1     | Modeling Conventions in this Chapter                              | 61 |

|    |      | 6.2.2     | Sketch of Latency Lemmas                                          | 62 |

|    | 6.3  | Forma     | lism                                                              | 64 |

|    |      | 6.3.1     | Checking Cumulative Latencies as Age Bounds                       | 65 |

|    |      | 6.3.2     | Auxiliary Invariants ( $\Psi$ )                                   | 66 |

|    |      | 6.3.3     | Proving a Latency Bound                                           | 66 |

|    | 6.4  | Latence   | cy Lemmas                                                         | 66 |

|    |      | 6.4.1     | Generating Age Lemmas ( $\Phi^L$ ) using Stage Graph $\mathscr G$ | 66 |

|    |      | 6.4.2     | Deriving Channel Blocking Bounds and Progress Lemmas ( $\Theta$ ) | 68 |

|    | 6.5  | Experi    | imental Methodology                                               | 76 |

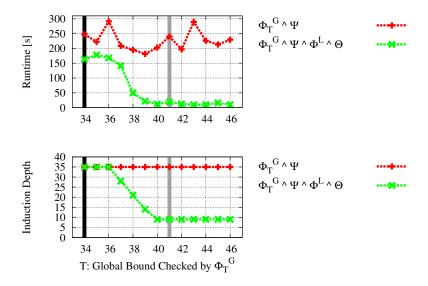

|    |      | 6.5.1     | Evaluating Looseness of $T_L$ with Bounded Model Checking         | 76 |

|    |      | 6.5.2     | Efficient Encoding of Packet Ages                                 | 77 |

|    | 6.6  | Illustra  | ative Examples                                                    | 78 |

|    |      | 6.6.1     | Single Queue                                                      | 78 |

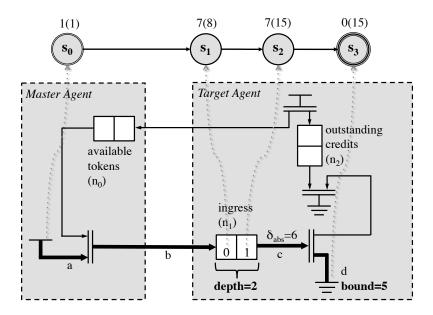

|    |      | 6.6.2     | Credit Loop                                                       | 78 |

|    |      | 6.6.3     | Virtual Channel                                                   | 80 |

|    |      | 6.6.4     | Token Bucket Regulator                                            | 84 |

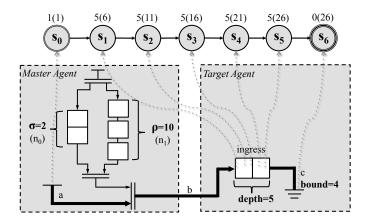

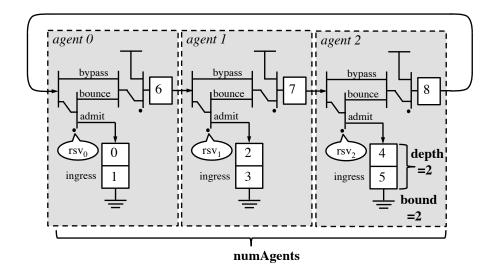

|    | 6.7  | Non-S     | tallable Ring Interconnect                                        | 86 |

|    |      | 6.7.1     | Implementation of a Ring Agent                                    | 86 |

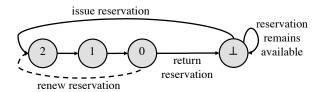

|    |      | 6.7.2     | Receive Reservation Logic                                         | 87 |

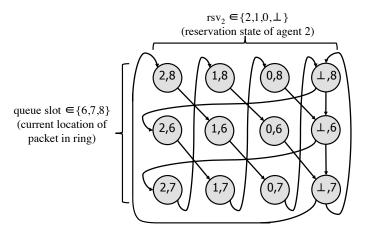

|    |      | 6.7.3     | Creating Age Lemmas using Stage Graph $\mathscr{G}$               | 88 |

|    |      | 6.7.4     | Latency Verification Results for Ring Interconnect                | 90 |

|    | 6.8  | Relate    | d Work                                                            | 91 |

|    | 6.9  | Conclu    | usion                                                             | 92 |

| II | I N  | loC Pa    | nrameter Synthesis                                                | 93 |

| 7  | Buff | fer Sizir | ng                                                                | 94 |

|    | 7.1  |           | uction                                                            | 94 |

|    | 7.2  | Forma     | ll Model and Problem Definition                                   | 95 |

|    |      | 7.2.1     | Modeling Symbolic-Sized FIFOs                                     | 96 |

| Bil | bliogr | aphy     |                              | 112 |

|-----|--------|----------|------------------------------|-----|

| 8   | Cone   | clusions | and Future Work              | 110 |

|     | 7.6    | Conclu   | sion                         | 109 |

|     | 7.5    | Related  | 1 Work                       | 106 |

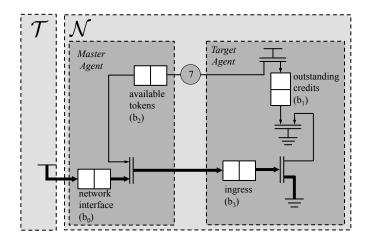

|     |        | 7.4.2    | Chip Multiprocessor Router   | 103 |

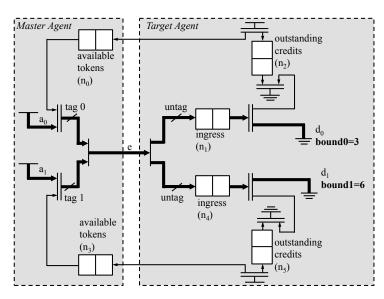

|     |        | 7.4.1    | Credit Logic                 | 101 |

|     | 7.4    | Experi   | mental Buffer Sizing Results | 100 |

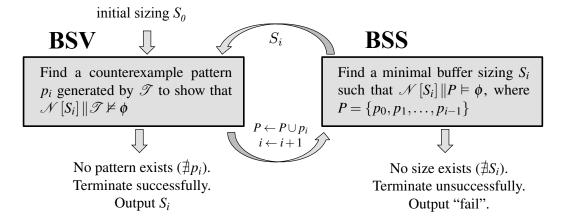

|     |        | 7.3.3    | Optimal Buffer Sizing        | 100 |

|     |        | 7.3.2    | Buffer Size Verification     | 100 |

|     |        | 7.3.1    | Buffer Size Synthesis        | 98  |

|     | 7.3    | The CE   | EBUS Approach                | 98  |

|     |        | 7.2.4    | SMT-based Buffer Sizing      | 97  |

|     |        | 7.2.3    | QoS Performance Properties   | 97  |

|     |        | 7.2.2    | Traffic Model Specification  | 96  |

# **List of Figures**

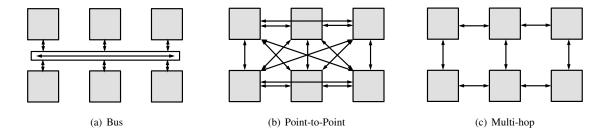

| 2.1  | Types of Interconnection Networks.                                | 6  |

|------|-------------------------------------------------------------------|----|

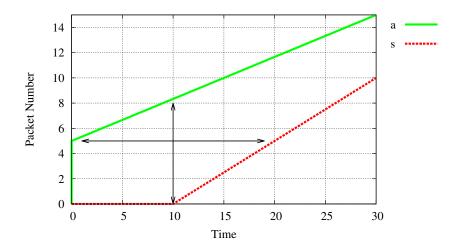

| 2.2  | Arrival and Service Curves in Network Calculus                    | 12 |

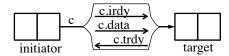

| 4.1  | The Signals Comprising an xMAS Channel                            | 21 |

| 4.2  | The xMAS Kernel Primitives                                        | 23 |

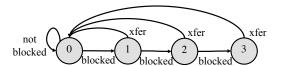

| 4.3  | State Machine for Bounded Non-deterministic Sink Primitive        | 25 |

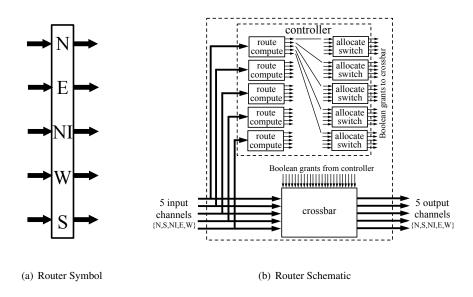

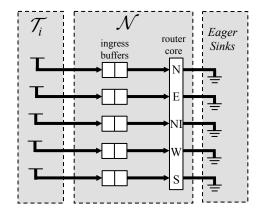

| 4.4  | Router Core                                                       | 30 |

| 4.5  | Two Encodings of Flit Ages.                                       | 33 |

| 4.6  | Block Diagram for a Traffic Model $\mathscr{T}$                   | 35 |

| 4.7  | Non-deterministic FSA for Generating Consistent Flit Sequences.   | 37 |

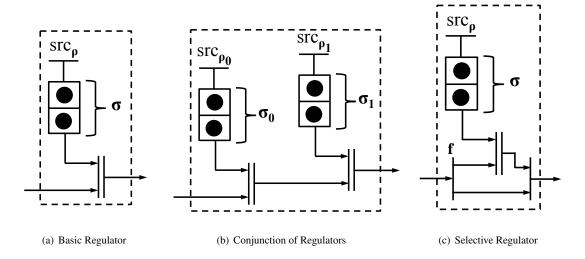

| 4.8  | Traffic Regulators.                                               | 39 |

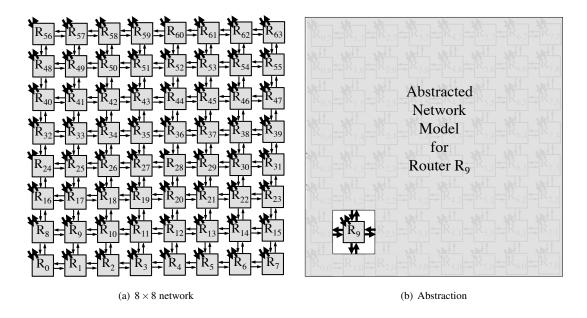

| 5.1  | Challenge of Performance Verification                             | 43 |

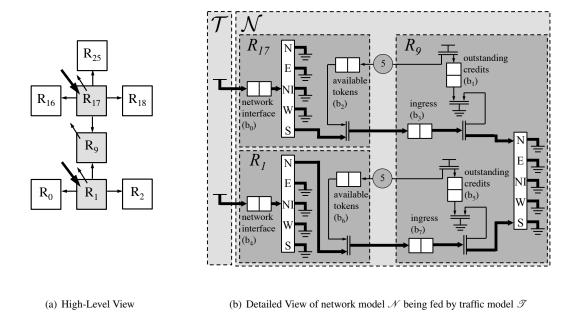

| 5.2  | Traffic Model and Router Model to Verify                          | 47 |

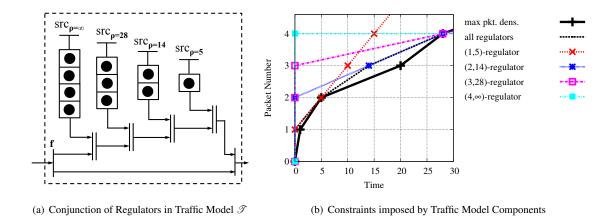

| 5.3  | Rate Constraints Imposed by Regulator                             | 50 |

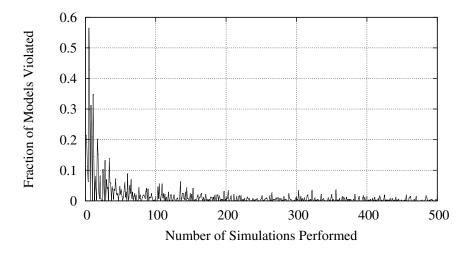

| 5.4  | Convergence of Inferred Traffic Models                            | 51 |

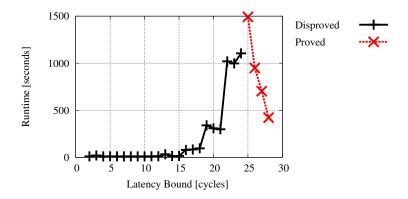

| 5.5  | SMT Solver Runtime versus Checked Latency Bound                   | 54 |

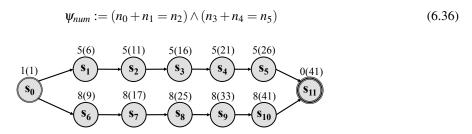

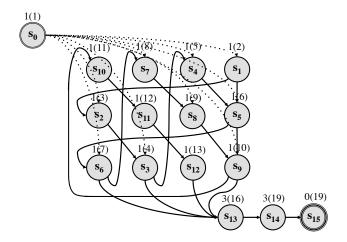

| 6.1  | Credit Loop Model ${\mathscr N}$ with Stage Graph ${\mathscr G}$  | 63 |

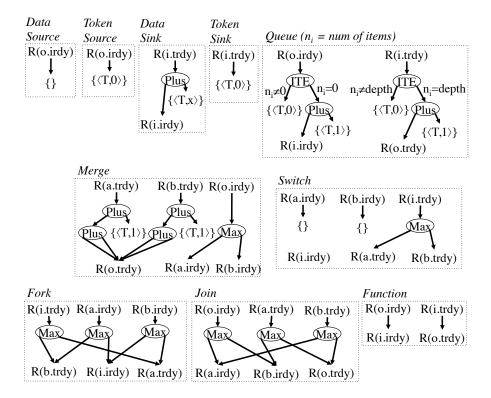

| 6.2  | Recurrence Relations for Future Readiness of xMAS Primitives      | 71 |

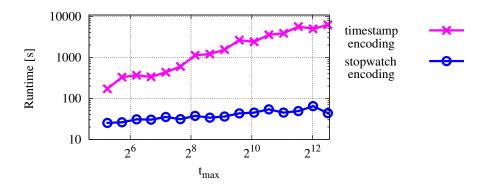

| 6.3  | Comparison of Stopwatch Age Encoding and Timestamp Age Encoding   | 77 |

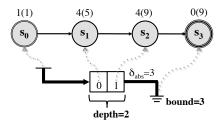

| 6.4  | Queue network with Stage Graph ${\mathscr G}$ Shown Above         | 78 |

| 6.5  | Runtime versus Problem Size in Queue                              | 79 |

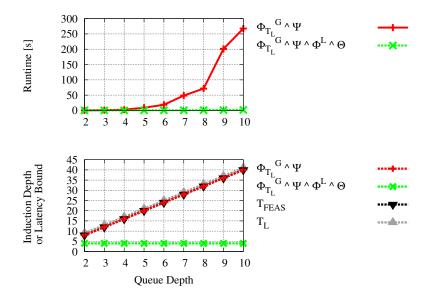

| 6.6  | Runtime versus Problem Size in Credit Loop.                       | 80 |

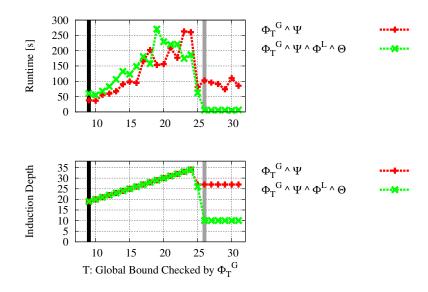

| 6.7  | Verification Runtime versus Proved Latency Bound in Credit Loop.  | 81 |

| 6.8  | Virtual Channel Network $\mathcal N$ and Stage Graph $\mathcal G$ | 82 |

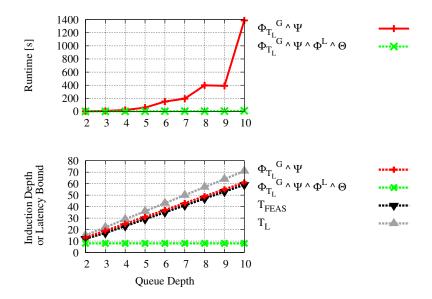

| 6.9  | Runtime versus Proved Latency Bound in Virtual Channel            | 83 |

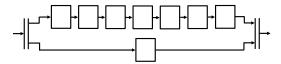

| 6.10 | Token Bucket Traffic Metering Circuit                             | 85 |

| 6.11 | Verification Runtime versus Proved Latency Bound in Token Bucket  | 85 |

| 6.12 | Parameterized Ring Network                                      | 87  |

|------|-----------------------------------------------------------------|-----|

| 6.13 | Receive Reservation State Machine.                              | 88  |

| 6.14 | Product Automaton of Receive Reservation and Occupied Ring Slot | 88  |

| 6.15 | Stage Graph ${\mathscr G}$ for the 3-agent Ring Network         | 89  |

| 7.1  | CEBUS Procedure for Optimal Buffer Size Synthesis               | 98  |

| 7.2  | Modeling Element for Non-pipelined Delay                        | 101 |

| 7.3  | Credit Logic Model for Buffer Sizing Experiment                 | 102 |

| 7.4  | CMP Network Model for Buffer Sizing Experiment                  | 104 |

## **List of Tables**

| 3.1 | LTL operators                                                       | 14  |

|-----|---------------------------------------------------------------------|-----|

| 4.1 | Data Fields of a Typical Flit                                       | 22  |

| 5.1 | Allowed Turns in XY-routing.                                        | 46  |

| 5.2 | Example of a Simulation Trace                                       | 48  |

| 5.3 | Maximum Packet Density Constraints                                  | 48  |

| 5.4 | Proving Latency Bounds using TITAN Models with UCLID                | 52  |

| 5.5 | Proving latency bounds using TITAN models and 30-cycle BMC          | 53  |

| 6.1 | Comparing Verification Engines on Credit Loop.                      | 81  |

| 6.2 | Comparing Verification Engines on Virtual Channel                   | 83  |

| 6.3 | Age Lemmas for 3-agent Ring                                         | 90  |

| 6.4 | Latency Verification Runtimes for 3-agent Ring                      | 91  |

| 6.5 | Latency Verification Runtimes for 8-agent Ring                      | 91  |

| 7.1 | Credit Loop Buffer Sizing Results using Circular Buffer Queue Style | 103 |

| 7.2 | Credit Loop Buffer Sizing Results using Record-based Queue Style    | 104 |

| 7.3 | CMP Buffer Sizing Results using Circular Buffer Queue Style         | 106 |

| 7.4 | CMP Buffer Sizing Results using Record-based Queue Style            | 107 |

| 7.5 | Counterexample Traffic Patterns from BSV in CEBUS on CMP Design     | 108 |

| 7.6 | Buffer Sizes Produced by BSS in CERUS for CMP Design                | 109 |

#### Acknowledgments

I wish to thank my family, and especially my Mom and Dad. It would have been impossible to write this dissertation without their love and their procreation. I am lucky to have shared lunches and holidays with my sister Christine during our four common years in Berkeley, and fortunate for Julie being so gracious and understanding about deadlines. I also wish to thank my uncle William Valentine for his encouragement.

I am indebted to the many people who have taught me, and helped me to learn. Professor Sanjit A. Seshia has always been a great source of knowledge, wisdom, inspiration, and encouragement; working in his lab has been a wonderful experience. I am thankful to my dissertation committee members Professor Lee Schruben and Professor Andreas Kuehlmann for their input and support.

Many people outside of our immediate lab have helped and supported my research. The research group of Professor Li-Shiuan Peh provided the PARSEC benchmark traces that are used in Chapter 5. Professor Bob Brayton and his research group provided much assistance with tools; in particular, Alan Mishchenko for supporting ABC, and Jiang Long for supporting VeriABC. I am also indebted to many friends at Intel Strategic CAD Labs for their contributions to my research and for two immensely fun internships in Hillsboro Oregon.

I am thankful to all of my friends in the lab; to Bryan Brady, Susmit Jha, Jonathan Kotker, Alexandre Donze, Indranil Saha, and Rhishikesh Limaye for leading the way; Wenchao Li for taking the journey with me, and Daniel Fremont, Garvit Juniwal, Dorsa Sadigh, Rohit Sinha, Wei Yang Tan, Nishant Totla, and Zach Wasson for chasing me out.

I appreciate the financial support that made this work possible. This work was partially supported by the NSF Expeditions in Computing project ExCAPE: Expeditions in Computer Augmented Program Engineering (grant CCF-1139138). Additionally, this research was supported in part by the Gigascale Systems Research Center, one of six research centers funded under the Focus Center Research Program (FCRP), a Semiconductor Research Corporation entity.

## **Chapter 1**

### Introduction

Multi-processor systems historically meant multi-chip systems with high-performance links connecting them, but that has changed in the last 15 years. Technology scaling continues to enable the fulfillment of Moore's Law, with ever-increasing numbers of components integrated onto a die. This thesis topic was chosen when 45nm CMOS technology was being rolled out, and industry is now on the cusp of 14nm. Personal computers now routinely contain 8 high-performance processing cores integrated onto a single chip, and much higher core counts are found elsewhere. Inter-processor communication is no longer occurring over high-performance inter-chip links, but now occurs on-die.

While a great deal of research has gone into automated design methodologies for on-chip communication networks to connect specialized IP blocks, the design methodologies for multiprocessor networks has not kept pace. This thesis aims to advance the state-of-the art in design methodologies for on-chip communication networks in multiprocessor systems. The two specific problems that this dissertation addresses are performance verification, and synthesis of buffer sizes that guarantee performance goals are met; both of these problems are addressed using state-of-the-art formal techniques. Addressing these problems in a formal way requires work toward finding and applying appropriate models for networks and traffic, and choosing appropriate verification techniques for the chosen models.

#### 1.1 Thesis Statement

The thesis explored in this dissertation is:

Scalable formal methods based on abstraction and compositionality, adapted to the domain of communication networks, allow performance properties to be addressed using model checking.

The formal techniques that are used in core components have not traditionally found use in performance verification due to the scale of the problems of interest, such as verifying latency bounds of hundreds of cycles.

In this dissertation, scalable model checking of communication networks is achieved using techniques such as abstraction and invariant strengthening, but applied in a way that is well suited to the problems that arise in networks. Bringing model checking into performance analysis avoids the use of highly abstracted models, the creation of which is inherently error prone. Through the application of model checking, performance properties can be proved with the same highest level of assurance as formally verified functional properties are today.

#### 1.2 Thesis Contributions

The contributions of this work are in devising domain-specific techniques that allow formal verification to scale up to the problems arising in NoC performance verification. The novelty comes not from the techniques, but instead from their adaptation to the problems at hand. Experimental data is provided to evaluate each approach, and to highlight promising future directions and apparent dead ends. Among performance properties verified, latency bounds play a role in all contributions of the dissertation.

The verification of NoC latency bounds is an important problem to solve because network latency can be a bottleneck for overall system performance. For example, consider the performance impact of traffic sent from a processing core to a memory controller and back. A computation on the processor may be stalled while waiting for data from memory, and the NoC is responsible for delivering the request to the memory controller and returning data to the core. A large latency for this traffic significantly degrades overall performance. Proving a worst-case bound on latency enables designers to decide whether the bound is acceptable or whether the design must be modified for a smaller latency. However, the myriad types of traffic in a CMP make it challenging to identify the conditions that induce worst-case latency, and this limits the confidence of any bound determined through simulation alone. Formal verification addresses this problem by providing guaranteed worst-case latency bounds.

Latency bounds are verified in this dissertation using model checking. Unfortunately, current model checking engines are unable to scale up to handle problems as large as those arising in naïve formulations of latency verification. Two factors challenge scalability of model checking latency properties. Firstly, in a SAT-based model checker, the number of variables generally scales as the product of the number of unrollings and the number of state bits in the model. Secondly, the number of unrollings is proportional to the worst-case latency, and this is unacceptably large. Chapter 5 addresses these challenges using abstraction, while Chapter 6 uses invariant strengthening for inductive verification, and demonstrates that the technique reduces verification runtime by 2 orders-of-magnitude. An additional contribution of this dissertation is the use of model checking for synthesizing latency-guaranteeing buffer sizes in Chapter 7.

#### 1.3 Thesis Overview

This dissertation is split into two parts: Part I gives motivation and background material about techniques and models used; Part II gives two approaches for latency verification; Part III gives an approach for synthesis, and more specifically for buffer sizing. The chapter topics are sketched here, with a description of how myself and collaborators contributed to the novel material presented in Chapters 5, 6, and 7:

- Part 1 (Background)

- Chapter 2: introduces networks-on-chip, why they are of interest, the need for quality of service, and typical approaches for modeling and analysis.

- Chapter 3: presents an overview of the current state-of-the art in formal verification.

- Chapter 4: introduces the modeling approach that is employed for the novel contributions of the subsequent chapters.

- Part 2 (Scalable Latency Verification)

- Chapter 5: presents work on traffic abstraction for latency verification. This work was done

in collaboration with Bryan Brady and Sanjit Seshia at UC Berkeley, and published at the 2011

Design Automation Conference (DAC) [50].

- Chapter 6: presents work on compositional verification using invariant strengthening. This work was a collaboration with Sanjit, myself, and many people at Intel Strategic CAD Lab including Alexander Gotmanov, Mike Kishinevsky, Satrajit Chatterjee, and Yuriy Viktorov. An early version of this chapter was published in the 2012 Formal Methods and Models for Codesign Conference (MEMOCODE) [51] with Alexander, Mike, and Sanjit as co-authors. While the ideas in this chapter were developed both at Berkeley and during an internship at Intel, the published data and that appearing in this dissertation are from my implementation of the work while at UC Berkeley. The work appearing in Chapter 6 is extended and improved relative to the version that appeared at MEMOCODE, and is currently under review as a journal paper.

- Part 3 (NoC parameter synthesis)

- Chapter 7: presents work on buffer sizing done in collaboration with Bryan Brady and Sanjit Seshia; this work was originally published at the 2011 Design Automation and Test in Europe Conference (DATE) [14]. Bryan did early work on the implementation, and I later reimplemented it; Bryan and I were joint first authors on the paper.

## Part I

# Background

## **Chapter 2**

## **On-chip Communication Networks**

According to Moore's law, technology scaling enables an integration of an ever-increasing number of components onto each chip. With the increasing number of functional blocks on a chip, the importance of the communication infrastructure that connects them rivals that of the individual blocks themselves. On chip networks emerged in the early 2000s as an efficient mechanism for communication between a large number of components. Network-on-chip (NoC) is a term introduced by Dally and Towles [37] to describe this paradigm for communication within large many-core, system-on-a-chip designs.

#### 2.1 Motivation for NoCs

Different types of communication fabrics can be used to interconnect a number of processing elements, where each element is a processor core, memory controller, or other functional block found in a modern VLSI design. The appropriate choice of communication fabric for a given design depends on a variety of factors including bandwidth and latency requirements. The advantages and disadvantages of various interconnection schemes are outlined in the following paragraphs. Whereas buses or point-to-point links were used historically, the dominant paradigm is now multi-hop communication using a series of on chip routers. A detailed quantitative comparison of these interconnection schemes is given by Lee *et al.* [65].

**Bus:** as shown in Fig.2.1(a), a bus is a communication network one in which all agents communicate over a single shared resource (the bus). Each agent has a interface to the bus, and through this interface it can inject and receive traffic. Area cost in a bus is linear in the number of connected agents n. The significant drawback of a bus interconnect is performance. Due to the global sharing of the bus resource, only two agents can communicate concurrently. Bus variants exists which can support multiple concurrent communicating agents, but such schemes are essentially just multiple redundant buses and do not avoid the problem of shared global resources which make buses undesirable for a system with a large number of agents.

**Point-to-point:** as shown in Fig.2.1(b), a point-to-point network, has a dedicated link between every pair of communicating agents. Each of the n agents arbitrates among n inputs. Area cost in a point-to-point network is quadratic in n because all pairs of agents have dedicated connections. Furthermore, the long dedicated links are not simple metal wires, since combinational repeaters are required to linearize the delay of the long wires, or else sequential repeaters to pipeline the link for increased bandwidth. Having such a high number of links constitutes an inefficient use of resources, since it is not possible to use all of the links simultaneously. Point-to-point networks with properly designed links perform very well, but are infeasible due to the high area costs.

**Multi-hop:** as shown Fig.2.1(c), a multi-hop network is a configuration in which traffic travels from one agent to another by making a series of hops along a path of intermediate routers. Nearly all NoCs are multi-hop networks. Arbitration is distributed and simple, as each router only arbitrates between a small number of neighboring routers. The area cost is linear in n because additional agent requires exactly one additional corresponding router. Yet, contrary to the bus, there is no single globally shared link that constrains the overall communication. NoCs are therefore a sort of compromise between buses and point-to-point networks, where area is linear in n but performance is not constrained by a single bus.

Figure 2.1: **Types of Interconnection Networks.** Each shaded block is a an agent comprising a processor core or memory controller, along with associated logic for interfacing it to communication links which are drawn as arrows.

NoCs for heterogeneous designs tend to be parameterized architectures that are customized according to the communication needs of each IP block, whereas NoCs for chip-multiprocessors (CMPs) tend to be uniform on account of the homogeneity of processing elements. Examples of highly-customizable heterogeneous NoCs include ASOC [66], AEthereal [41], Xpipes [33], NOSTRUM [72], SPIN [49], and QNoC [10]. Examples of CMP NoCs include the Tilera TILE64 [105], STI Cell BE [25], Intel Larrabee [92], and Intel Terascale [52].

### 2.2 Defining Characteristics of an NoC

Nearly all NoCs share a set of common characteristics and are based on multi-hop routing to avoid both the quadratic cost of dedicated point-to-point links and the bandwidth limitations of globally shared buses. All NoC architectures consist of a network of interconnected agents, where each agent comprises a router, and a processing element such as a processor core, memory controller, or other functional unit. Each router

interfaces to its processing element through a network interface port, and to the routers of a small subset of other routers. Packet-switching is used to route data packets among routers from a source node to a destination node. At the physical level, a packet is transferred across a channel as some number of "flits", or flow-control-units. A head flit carries information about a packet's destination address, and is followed by some number of payload-carrying body flits and a single tail flit. Despite the many significant commonalities of all modern NoCs, they also vary in a few significant ways. The following subsections highlight briefly a few characteristics that vary across NoC designs.

#### 2.2.1 Topology

A defining characteristic of an NoC is its topology. In heterogeneous networks, where bandwidth requirements vary widely for each node, specialized topologies can be synthesized from communication requirements [82]. Chip multiprocessor NoCs, which tend to have a large number of identical processing cores and a few memory controllers, tend to use a variety of more regular topologies.

A mesh is a topology in which each router exchanges traffic with its neighbors. In an n-dimensional mesh, each router connects to 2n neighbors. Because integrated circuits are planar, 2-dimensional meshes are common, with each node connecting to its 4 neighbors, except for the edge nodes which connect to 3 neighbors, and the corners which connect to 2 neighbors. Examples of industrial 2-dimensional meshes are the Intel Terascale [52] and Tilera TILE64<sup>TM</sup> processors [105].

A torus topology is similar to a mesh, except that it lacks edges. A 2-dimensional torus can be constructed from a 2-dimensional mesh by connecting the left edge to the right edge, and bottom edge to top edge. Hence, in a 2-dimensional torus every node has 4 neighbors, and in a 3-dimensional torus every node has 6 neighbors (i.e. N,S,E,W planar neighbors as well as the neighbors above and below). A torus is a common topology for communication between the many separate chips in supercomputers; for example, IBM Blue Gene uses a 3-dimensional torus [2]. However, torus networks are not well-suited to single-chip many-core designs because of the long wires that connect the nodes on opposite edges of the die. A folded torus is proposed to solve this problem for NoCs [35, 79], but does not appear to be used in any common industrial designs.

Rings are another common topology for NoCs. Rings are used in designs with relatively modest core counts such the 48-core Intel Larrabee processor [92] or 8-core STI Cell BE [25]. To scale beyond tens of rings, hierarchical rings can be used. Various configurations of hierarchical rings are competitive with meshes up to around 128 [88] or 256 [44] cores.

#### 2.2.2 Flow Control

Flow control describes mechanisms for deciding how to allocate channels and buffers to packets. Flow control has a huge performance impact, and a wide variety of optimizations exist to maximize performance. A thorough discussion of flow control options in NoCs is given in the dissertation of Peh [81], and in this

section only basic mechanisms are described.

At a high level, flow control can be classified as either store-and-forward or wormhole. Store and forward networks wait until all flits of a packet are received before forwarding any to the next node, while wormhole networks forward the individual flits of a packet as they arrive. Wormhole networks can have lower latency and use smaller buffers than store and forward [74], but a single packet can be strung out across the network blocking the forward progress of many other traffic flows. This type of blocking is known as head-of-line blocking, and performance analysis of head-of-line blocking is a difficult problem [3]. In some cases, head-of-line blocking can lead to deadlocks.

Virtual channels are a mechanism for avoiding head-of-line blocking. Virtual channels were initially introduced as a mechanism for deadlock avoidance in wormhole networks [36], and later also shown to have desirable performance properties [34]. With virtual channels a single physical channel is shared between multiple logical (i.e. virtual) channels. Each of the virtual channels has its own buffer, but only one virtual channel can be active in a given cycle on account of their sharing of a physical channel. When one of the virtual channels is blocked, another virtual channel can proceed, thus eliminating head-of-line blocking. Some additional logic is required to control how the physical channel is multiplexed to the virtual channels, but virtual channels are ubiquitous in CMP NoCs.

A router will only send traffic across a link to a neighbor if that neighbor is ready to accept the traffic. This readiness is determined either through the use of a credit system or on/off signaling. With credits, the sending router keeps track of the number of open buffer slots in the ingress queue of the receiving router, and halts when the supply of credits is exhausted, as this indicates a full queue. The router only begins sending flits again once it receives a credit to indicate that a slot has now become available. An alternative to credit-based flow control is on/off signaling, where a router does not keep track of the number of free slots, but instead simply keeps sending packets until the receiving router sends a signal to stop.

#### **2.2.3** Routing

Routing in a mesh NoC can be classified as oblivious or adaptive. Oblivious routers use deterministic paths for packets that are independent of congestion, whereas adaptive routing steers packets around congestion. The examples in this dissertation use oblivious routing, and more specifically XY (dimension-order) routing. In XY routing, a packet reaches its destination by first being routed to the appropriate column along the x-dimension, and then being routed to the appropriate row in the y-dimension. XY-routing is guaranteed not to introduce deadlock or livelock [38].

#### 2.2.4 Architectural Parameters

Once the topology, flow control and routing of an NoC are decided, remaining parameters such as buffer depths and channel widths remain to be assigned. The depth of each physical or virtual channel buffer is the

maximum number of flits that can be stored in it; deeper buffers improve performance, but increase the area cost of the NoC [53][55]. Similarly, wider channels (and hence wider flits) allow more data to be transferred per cycle across a channel, but require wider buffers to store the flits and therefore also lead to increased area costs. An overview of these considerations in NoC design is given by Ogras *et al.* [77].

### 2.3 Quality of Service

A correctly-designed NoC should ensure that performance properties are satisfied. First and foremost, the NoC should never deadlock or livelock. But guaranteeing that packets reach their destinations is not a sufficient indicator of correctness in an NoC. To ensure that programs executing on an NoC will perform well, the network must give guarantees on performance of network traffic.

Quality-of-Service (QoS) refers to performance guarantees that are provided by the NoC to users. Some QoS metrics of interest are minimum throughput offered, end-to-end latency bounds, and maximum jitter. Minimum throughput is a lower bound on the number of bytes per second that a source can inject under arbitrary achievable network conditions. Maximum latency is the largest allowable time between when a packet is injected at the network interface of its source agent, and when it is ejected from the network interface of its destination. Jitter refers to irregularity in delay and is especially problematic in streaming traffic, where the existing of jitter may require more conservative buffering. This dissertation focuses primarily on latency bounds. Satisfaction of QoS requirements depends on spatial and temporal properties of injected traffic, so in some cases QoS guarantees are conditioned on traffic constraints.

Packets traveling through an NoC are used for many different purposes; for example, packets in an NoC may be urgent control data, real-time data with deadline requirements, reads or writes between processors and memory controllers, block transfers of large data, and so on. Some NoCs therefore provide differentiated service classes, where high priority traffic is given guaranteed service, and other traffic is given best-effort service. Best effort service refers to the manner in which packets without service guarantees are handled, and the performance of such traffic depends significantly on the amount of competing traffic in the network. The focus in this dissertation is on QoS bounds in NoCs with undifferentiated service, where all traffic can be viewed as best-effort.

### 2.4 Modeling NoC

There are many different ways to model an NoC, and the right model depends on the purpose for which it will be used. While modeling approaches such as GeNoC are tailored to proving functional correctness and liveness [101, 103], the focus in this dissertation is on models more suitable for performance verification. This section broadly splits modeling into cycle-accurate hardware descriptions, and the variety of analytical models. Hardware description languages provide highest accuracy, but can be more detailed than is necessary

for performance analysis because they don't hide any irrelevant details of the network behavior. Furthermore, full hardware descriptions may not exist until late stages of design, potentially making them infeasible for design space exploration. Analytical models are fast and typically admit closed-form solutions, but may not capture all the intricacies of real system behavior, and their applicability often only holds under specific assumptions.

#### 2.4.1 Hardware Description Languages

Before fabrication, every digital circuit first exists as a register transfer level (RTL) model in some hardware description language such as Verilog or VHDL. To minimize the number of logic bugs that reach silicon, extensive functional validation through simulation and formal verification are performed on the RTL model. Performance verification is accomplished by monitoring the timing in simulation of interesting events such as packet injection and ejection times. Clearly the performance observations depend closely on the inputs that are applied, and so finding appropriate inputs is a significant challenge.

To perform simulations, the inputs to the RTL model of the system are driven from a testbench, and the state and output are monitored for violated assertions or unexpected outputs. The execution of the model can be either cycle-driven or event-driven. In a cycle-driven simulator, all state variables are updated in each cycle, and in event-driven simulation state variables are only updated on-demand when one of their inputs changes.

#### Register Transfer Level Model

The canonical example of a simulatable system model of an NoC is the RTL description of the hardware. An RTL description of a digital circuit is system of Boolean state variables often grouped into bit-vector words, and transition relations. Each state variable is computed using a deterministic function over the previous state and the inputs. The RTL representation of a NoC is highly accurate, and captures all logic-level details of a design. Electrical interactions, timing slack, and other non-logical details are abstracted away in RTL.

#### **Testbench Environment Model**

When evaluating performance using a simulatable model, the inputs supplied by the testbench can have a significant impact on the measured performance. In choosing input patterns to apply there exists a tradeoff between having models that are highly general or highly representative of the traffic produced by certain applications of interest.

The most general inputs are those coming from synthetic traffic generators. Synthetic generators can create sequences of non-repeating inputs according some basic assumptions on the destination of packets and the rate at which they are injected. Different distributions such as uniform random and hot-spot are commonly used [38]. Results of performance analysis may vary wildly across different types of synthetic traffic

generators [60], and therefore to obtain meaningful performance measurements it is important to use highly representative traffic.

A highly representative set of traffic patterns can be obtained by running applications of interest on architectural simulators and recording the inter-process communication [80]. This provides a trace of highly relevant inputs that can be simulated. However, the process is very involved compared to using synthetic traffic generators, the finite traces generated in this manner are not very comprehensive.

A compromise between synthetic traffic and architecture-level simulation traces is to use synthetic traffic generators with parameters that are tuned to produce traffic resembling the traces; this synthetic traffic can then be viewed as a generalization of the original traces. Varatkar and Marculescu propose a model for MPEG-2 traffic that models self-similarity using a Hurst parameter [100]. Later, Soteriou *et al.* [96] show that a three parameter model leads to accurate representation of a variety of applications; the three parameters used are a Hurst exponent for temporal burstiness, a spatial hop distribution parameter, and a spatial injection distribution parameter.

#### 2.4.2 Analytical Models

Instead of cycle-accurate RTL models, a second way to reason about performance is through the use of analytical models [78]. Analytical models typically lack state variables, transition relations and synchronous semantics. They instead aim to describe various performance metrics as direct functions of traffic and configuration parameters.

#### **Network Calculus**

Network calculus is an analytical technique for reasoning about classes of discrete event systems using maxplus algebra. Network calculus was first introduced by Cruz for modeling both traffic and network elements [31][32], and relies on bounding envelopes for traffic. Incoming traffic to an element such as a queue is upper bounded by an envelop function known as an arrival curve. If function R(t) represents the number of packets to arrive before time t, then R is bounded by arrival curve a if  $R(t) - R(s) \le a(t-s)$  for all t and s. A common arrival curve is that of a leaky-bucket [31], with arrival curve  $a(x) = \sigma + \rho x$  having a burst-size of  $\sigma$  and long-time average of  $\rho$  packets per cycle. The draining of packets through an element is lower bounded by a service curve, such as a latency-rate service curve [97] in which the number of packet served from a backlog of waiting packets in any time window of duration x is lower bounded by  $s(x) = (x - \gamma) * \kappa$ . Various network elements transform and shape arrival and service curves. If arriving and served traffic are bounded by some arrival and service curves a and a, then closed-form analysis can be used to compute from a and a the upper bounds on queue occupancy and latency (Fig. 2.2).

While the advantage of network calculus is the existence of closed-form analysis, it is not well suited to many types of traffic. Burst-sizes in best effort NoC traffic can be very large, and therefore only enveloped

Figure 2.2: **Arrival and Service Curves in Network Calculus.** Arrival curve is a leaky-bucket with  $(\sigma, \rho) = (5, 1/3)$ . Service curve is latency-rate server with  $(\gamma, \kappa) = (10, 1/2)$ . For a queue with this arrival curve on input, and service curve at output, the horizontal arrow shows the maximum latency of 20 through the queue, and vertical arrow shows the maximum queue occupancy of 9.

by arrival curves that are too conservative to yield meaningful results. Furthermore, self-similar traffic cannot be bounded by any deterministic arrival curve. Work by Qian *et al.* [87] shows that it is possible to derive from self similar traffic an arrival curve that envelopes no less than some known percentage of traffic, but not all of it. From this, probabilistic latency bounds can be obtained using the closed-form network calculus formulation

#### **Queueing Theory**

Queueing theory provides another analytical framework for reasoning about QoS. Whereas network calculus reasons about worst-case behaviors, queueing theory applies to average-case. Under the assumption of Poisson arrival of header flits [76] in each buffer, queueing theory gives closed-form expressions for average buffer utilization, average packet latency per flow, and maximum network throughput. A criticism of queueing theory models for NoCs is given by Bogdan *et al.* [9].

#### 2.4.3 Preview of xMAS Formalism

This dissertation uses extensively a modeling formalism known as xMAS. Full description of xMAS is delayed until Chapter 4, but for now it suffices to remark that xMAS is akin to a simplified form of RTL. While not analytical models in the sense of the previous section, xMAS models are simple enough enough to be reasoned about formally.

### **Chapter 3**

### **Formal Verification**

All designed systems are created with the goal of correctly implementing designer intent, but correctness is more important in some systems than in others. In modern VLSI circuits, the costs of the photolithographic masks for a design are in the millions of dollars, and therefore significant effort is spent to ensure correctness before fabrication. In such situations, formal verification techniques are used to prove that a model of a system satisfies its intended specifications.

An obvious but weak assurance of correctness is obtained from simulation. In simulation, selected inputs are applied, the system model is executed, and properties over state variables and outputs are monitored to check for violation of specifications. Simulation is a sound bug finder, meaning that if a property fails, then the system model is indeed incorrect. However, simulation is woefully incomplete, meaning that no guarantee of correctness can be given if the simulation is free of failures. If no failures are observed in simulation, it is still possible that the model can fail, but that the inputs applied were not the right ones to cause the failure.

Formal verification techniques, in contrast to simulation, can guarantee that a model always satisfies some desirable property. The two main formal verification techniques in use today are model checking and theorem proving; there are significant overlaps between these two techniques, and they are often used in concert. The applicability of formal verification is limited by its cost, as significant human intuition and computationally expensive algorithms are generally required to formally verify a model. However, the cost of formal verification is justified in applications such as VLSI circuits where the cost of failure is also high.

### 3.1 Linear Temporal Logic (LTL)

Correctness of a system model is always defined in terms of properties that the system must satisfy, or properties that it must not satisfy. One way to specify such properties is using Linear Temporal Logic (LTL). Linear Temporal Logic (LTL) was first used for reasoning about systems by Pneuli in 1977 [84], and has

| true           | positive literal   |  |

|----------------|--------------------|--|

| false          | negative literal   |  |

| p              | atomic proposition |  |

| ¬ p            | negation           |  |

| $p \wedge q$   | conjunction        |  |

| $p \lor q$     | disjunction        |  |

| $p \implies q$ | implication        |  |

| F              | Future             |  |

| G              | Globally           |  |

| X              | Next               |  |

| U              | Until              |  |

Table 3.1: LTL operators LTL combines propositional logic operators with temporal operators.

found wide application in the time since. Properties in LTL are specified with respect to execution paths, where an execution path  $\pi$  is a sequence of states  $s_0, s_1, s_2, \ldots$ . The basic LTL operators are given in Tab. 3.1. In each state along a path, an atomic proposition p evaluates to **true** or **false**; a state  $s_i$  where p holds can be written as  $p(s_i)$ , and a state where it does not hold as  $\neg p(s_i)$ . The logical operators  $\neg, \land, \lor, \Longrightarrow$  are applied over propositions to produce **true** or **false** in each state. The temporal operators  $\mathbf{F}, \mathbf{G}, \mathbf{X}$ , and  $\mathbf{U}$  evaluate to **true** or **false** for a state in consideration of the path through the state.

#### 3.1.1 Safety and Liveness Properties

A safety property asserts that some bad condition (e.g. p) must never happen (e.g.  $\mathbf{GF} \neg p$ ), whereas a liveness property asserts that something good (e.g. q) must eventually happen (e.g.  $\mathbf{GF}q$ ). A safety property is disproved by a finite length witness (counterexample) that ends in a non-p (bad) state. A liveness property has no finite-length witness because any finite length trace that does not reach a p state may yet reach a p state in the future. A liveness checking problem can be encoded as safety checking [6], but this causes a blow-up in the model.

#### 3.1.2 Bounded Liveness Properties

A liveness property (e.g. GFp) specifies only that p must hold in some state subsequent to the current state on a path, but does not specify how many other states are visited before a state satisfying p. This makes liveness insufficient for specifying a QoS latency property, where it is necessary to specify that some action (e.g. packet reaches destination), occurs not just in the future, but within a specific number of cycles in the future.

Bounded liveness properties are better suited to checking latencies. A bounded liveness property is a liveness property where a proposition must hold in the future within a specified number of states. A bounded liveness property is written as  $\mathbf{F}^{< x}p$  to specify that p must occur no more than x states into the future. A bounded

liveness property is really a safety property, and is equivalent to Eq. 3.1, where the final property in the disjunction has n nestings of the  $\mathbf{X}$  operator. Kupferman et al. [59] describe a system where all  $\mathbf{F}$  properties are bounded as a "prompt" system.

$$\mathbf{F}^{< n} p \equiv p \vee \mathbf{X} p \vee \mathbf{X} (\mathbf{X} p) \vee \mathbf{X} (\mathbf{X} (\mathbf{X} p)) \vee \dots$$

(3.1)

#### 3.2 Model Checking

Model checking performs verification by exhaustively checking whether a state-transition graph (a model) satisfies a property. The model is M = (S, I, R, L). The set of states of the model are S, the initial states are  $I \subseteq S$ , the transition relation  $R \subseteq S \times S$ , and a labeling  $L : S \mapsto 2^p$ , where p is the number of propositions that evaluate to **true** or **false** in each state of the model.

Model checking suffers from the so-called state explosion problem. This state explosion problem refers to the fact that the number of model states is exponential in the number of Boolean variables. Explicit state model checkers are based on graph-traversal of the model states, and must keep track of visited states. This quickly becomes infeasible as the size of the model grows. Straightforward implementations of explicit-state model checking are therefore unable to scale to models with millions of states or more, as can arise from just 20 or so Boolean variables. Symbolic model checking overcomes state explosion by avoiding explicit graph traversal.

Initial attempts at symbolic model checking [19] are based on Binary Decision Diagrams (BDDs) [17]. Binary decision diagrams are compact representations of sets, and in symbolic model checking BDDs are used to efficiently encode the Boolean formulas for sets of reachable states, and for the model transition relation. A BDD representation of the states that are immediately reachable from a set of current states is computed by direct manipulation of the BDDs for the current states and transition relation. BDD-based symbolic model checking enabled for the first time the checking of properties on systems with up to  $10^{20}$  states [19]. BDD-based model checking, while still used, is limited by the fact that the compactness of BDD-based representation of formulas depends on the variable ordering used in their construction.

SAT-based symbolic model checking has supplanted BDD-based as the dominant approach. SAT-based symbolic model checking avoids variable ordering issues because there is no significance to variable ordering in the conjunctive normal form used by SAT-solvers. Due to the nature of SAT-solvers, most time is spent on the important parts of the problem, where solvers work to resolve conflicts. SAT-based model checking is able to handle larger problems than BDD-based model checking. SAT-based formulation of various model checking algorithms are given in the following sections, and a comprehensive survey of SAT-based model checking is given by Prasad *et al.* [86].

Model checking can be applied to both Boolean formulas and formulas in various theories; this dissertation makes use of both of these variants of model checking. Chapters 5 and 7 use SMT-based model checking as

will be explained in Sec. 3.2.5, and Chapter 6 uses SAT-based model checking.

#### 3.2.1 Boolean Satisfiability Problem

A significant advantage to SAT-based symbolic model checking is that it leverages the tremendous performance improvements in SAT-solvers over the last decade. The Boolean satisfiability problem is, given an expression using  $\land$ ,  $\lor$ ,  $\neg$  over Boolean variables, to find an assignment to the variables that causes the expression to evaluate to **true**, or else to determine with certainty that no such assignment exists. Boolean satisfiability problems are typically written in conjunctive normal form (CNF), as a conjunction of disjunctive clauses; 3-SAT refers SAT where each disjunctive clause has up to 3 variables. The 3-SAT problem is NP-complete [30], meaning that SAT-solvers can be used to solve the variety of interesting problems that are NP-complete [56]; for this reason SAT solving has been the subject of a large amount of research.

SAT-solvers are now routinely able to solve SAT problems with thousands or millions of variables. Most SAT-solvers are based on the DPLL procedure [40, 39] for resolution and backtracking. The capabilities of SAT-solvers showed a dramatic improvement in the last 15 years. The solver GRASP [69] advanced conflict analysis to enable non-chronological backtracking. The later solver Chaff [73] sped up constraint propagation using watched literals. Most modern solvers make use of the techniques pioneered by GRASP and Chaff. This dissertation uses extensively the SAT-solver MiniSat [43].

#### 3.2.2 Bounded Model Checking

SAT-based bounded model checking (BMC) was first introduced in 1999 by Biere *et al.* [7]. Given a model M, BMC addresses the problem of whether it is possible within k frames from the initial state, to falsify a property p. BMC attempts to falsify p by finding a counterexample, which is an input assignment that causes Eq. 3.2 to be satisfied. BMC finds the shortest possible counterexample by first using a small value of k and then for as long as Eq. 3.2 cannot be satisfied, unrolling the problem for an additional cycle by increasing k, until the formula is satisfied (i.e. the property is disproved) or some preset resource limit (e.g. memory or runtime) is exceeded.

In general, if a safety property cannot be disproved by BMC within allotted resource limits, then the validity of the property is unknown. Given that the model has finitely many states, it is of course possible for BMC to be complete when k is sufficiently large, and the value of k required for this is known at the completeness threshold [27]. In general there is no assumption of completeness when using BMC. Due to its incompleteness, BMC is used primarily for bug-finding, and not for proving properties.

$$BMC(M,k,p) \equiv I(s_0) \land \left( \bigwedge_{i=0...k-1} R(s_i, s_{i+1}) \right) \land \left( \bigvee_{i=0...k} \neg p(s_i) \right)$$

(3.2)

#### 3.2.3 Induction

Informally, induction tries to prove a property by assuming that it has always held previously, and then using that fact and the model transition relation to show that it holds in all reachable next states. If it can be shown that no transition exists from state satisfying p to one that does not satisfy p, then p is proved as long as it holds in the initial state. A property p that can be proved in this way is called an inductive invariant.

#### **Simple Induction**

Inductive proof of a safety property p is a two-step process comprising a base case and an inductive step. The base case checks that the property holds for all initial states (denoted  $s_0$ ). The inductive step checks that, if the property holds in some arbitrary state  $s_k$ , then it must hold in all  $s_{k+1}$  that are reachable next states. If INDBASE and INDSTEP (Eq. 3.3) are both unsatisfiable, then all initial states satisfy p, and all states reachable from p states are also p states; this constitutes a deductive proof that  $M \models p$ .

Induction is attractive proof method because it does not require an unrolling of the transition relation past two frames. This translates to a small SAT problem, and ultimately one that is likely to have a fast runtime for a SAT-solver. Unfortunately many properties cannot be proved using simple induction, due largely to the general initial state in INDSTEP. The inductive step begins from an arbitrary state  $s_k$ , with the only constraint being that  $s_k$  is a p state. This allows for the inclusion as  $s_k$  of many unreachable states that happen to be p states, and progression of the model from unreachable p states is often erratic because it is anyway not a meaningful model trajectory.

$$IndBase(M,p) \equiv I(s_0) \land \neg p(s_0)$$

$$IndStep(M,p) \equiv p(s_k) \land R(s_k, s_{k+1}) \land \neg p(s_{k+1})$$

(3.3)

#### **K-Induction**

Properties that cannot be proved using simple induction require strengthening, and one way of strengthening an inductive property is to use k-induction [8, 94]. K-induction is stronger than simple induction due to its handling of the inductive step. Where the inductive step in simple induction assumes that a property holds in a single state, the equivalent step in k-induction assumes that a property holds in k consecutive states. The base case in k-induction (KINDBASE) is equivalent to BMC(M,k,p). Property p is proved using k-induction if KINDBASE and KINDSTEP (Eq. 3.4) are both unsatisfiable.

$$KIndBase(M,k,p) \equiv I(s_0) \wedge \left( \bigwedge_{i=0...k-1} R(s_i, s_{i+1}) \right) \wedge \left( \bigvee_{i=0...k} \neg p(s_i) \right)$$

$$KIndStep(M,k,p) \equiv \left( \bigwedge_{i=0...k} R(s_i, s_{i+1}) \right) \wedge \left( \bigwedge_{i=0...k} p(s_i) \right) \wedge \neg p(s_{k+1})$$

(3.4)

If unique states are enforced in k-induction, then the approach constitutes a complete proof engine if the value of k is not restricted. The completeness comes from the fact that ultimately there are finitely many unique p states to visit, and once the induction depth is sufficient to reach all p states, if still no transition is possible to a non-p state, then p is proved. However, the depth required to reach all p states can be large, and therefore k-induction is not typically used for its completeness.

#### **Invariant Strengthening**

Invariant strengthening plays an important role in inductive and k-inductive proofs. The idea behind invariant strengthening is to prove a property p by proving a stronger property p' that implies p but is easier to prove. Consider for example a model comprising a 10-bit variable x[9:0] where the transition relation increments x in every cycle, except that x=10'd15<sup>1</sup> is followed by x=10'd0 instead of x=10'd16. Now assume that the goal is to prove a property  $p:=x[9:0] \neq 10$ 'd500. All states are p states except for the single state where x=10'd500. The state x=10'd17 is a p state, and the next 485 states that follow are all p states, until reaching the non p state x=10'd500. So the value of k that would be needed to prove p would be at least 485. However, if the property p':=x[9:4]=6'd0 is proved, then the induction depth required to prove it will be greatly reduced. Since  $p' \implies p$ , proving p' provides an easier way to prove the original property p.

#### 3.2.4 IC3 / Property-Directed Reachability

The IC3 algorithm developed by Aaron Bradley is considered a recent breakthrough in model checking [12]. An efficient AIG-based implementation of IC3 that is used in this dissertation is referred to as property directed reachability (PDR) [42]. IC3 is based on automatically finding and refuting candidate incremental inductive invariants. Ultimately, IC3 terminates by finding invariants that over-approximate reachable states but are precise enough to show that non-*p* states are unreachable.

#### 3.2.5 Model Checking using Satisfiability Modulo Theories

An alternative to verifying Boolean formulas with SAT solvers is to use Satisfiability Modulo Theories (SMT) solvers. SMT solvers extend SAT solvers by replacing Boolean variables with predicates in some underlying theory or combination of theories.

<sup>&</sup>lt;sup>1</sup>In notation borrowed from Verilog, 10'd15 is used here to represent a bit-vector of width 10 that has the decimal equivalent of 15.

SMT solvers can be categorized as eager or lazy. An eager solver [62, 93, 4] encodes an SMT problem into an equisatisfiable SAT instance; all inference is done by the SAT solver in the problem's Boolean representation. A lazy SMT solver is based on a generalized DPLL procedure [75], with propagation and learning according to the underlying theory.

Some theories used that are relevant to this work are bit-vectors and linear arithmetic. Bit-vectors are interesting because they match hardware implementations which are naturally restricted to finite-size data. Bit-vector SMT problems can be mapped to Boolean SAT problems by bit-blasting, a process in which each *n*-bit bit-vector variable is replaced by *n* Boolean variables.

The majority of SMT solving in this dissertation is performed using the UCLID verification system [18, 62]. UCLID decides properties in first order logic that contain equality, uninterpreted functions, constrained lambda expressions, integer linear arithmetic, and bit-vector arithmetic. The lambda expressions in UCLID allow it to model memories, and infinite queues or queues of bounded size. UCLID has been previously been used to verify hardware systems [63, 61, 13], software systems [26, 45] and discrete-time hybrid systems [54]. Although UCLID can be used for inductive verification, in this dissertation it is used for bounded model checking. From a given initial state, UCLID performs the necessary unrolling of the transition relation to a specified depth k, and then either outputs an SMT problem in SMT-lib format, or eagerly encodes the problem as a decision procedure and dispatches it to a SAT-solver. If the problem is output in SMT-lib format, then any available SMT solver can be used to check the property.

### **Chapter 4**

## **Formal NoC Modeling**

This dissertation uses finite-state NoC models so that QoS problems can be solved using model checking. To minimize complexity (e.g. the number of states in model), it is therefore desirable to use a model that is as simple as possible while still capturing with sufficient precision the details that determine QoS. The approach for minimizing complexity is to use, to the maximum extent possible, a simple modeling language called xMAS to represent NoC designs. As the xMAS modeling language is not well-suited to certain aspects of control logic, xMAS models are supplemented with arbitrary combinational and sequential logic where needed. The modeling methodology presented in this chapter serves as the basis for all contributions in subsequent chapters of the dissertation.

This chapter is structured as follows. The xMAS modeling language is presented in Sec. 4.1. Two different implementations of xMAS queues are presented in Sec. 4.2. Modeling of NoC router cores is given in Sec. 4.3. Approaches for checking latency bounds as simple safety properties are given in Sec. 4.4, and traffic modeling is in Sec. 4.5. Among the sections of this chapter, Sec. 4.3, Sec. 4.4, and Sec. 4.5 contain novel modeling contributions.

### 4.1 Executable Microarchitectural Specifications (xMAS)

As mentioned in the chapter introduction, the modeling language used heavily in this dissertation is xMAS – standing for executable microarchitectural specifications. The xMAS formalism was developed by researchers at Intel's Strategic CAD Lab as a way to formally model communication fabrics [22]. The development of xMAS was motivated by the observation that communication fabrics are essentially compositions of queues, arbiters, and routing logic, connected and interfaced to each other with a large amount of ad-hoc glue logic. The authors pose the following question in the first paper on xMAS [22]:

Do we need this ad hoc glue logic? Instead can we identify a set of primitives that is rich enough to permit a purely structural description of interesting systems?

In response to this question, xMAS is a way to model networks that obviates the need for ad-hoc glue logic by having all primitives adhere to a uniform interface that allows components to be connected directly without glue logic. By providing a clean formal model of NoCs, xMAS makes it possible to verify NoC properties using model checking [21, 23, 89] and other means [48].

Every xMAS model  $\mathcal{N}$  is a finite state model composed of modeling elements drawn from a library of eight simple parameterized kernel primitives (Fig. 4.2). All primitives communicate over channels using a common handshaking protocol. This provides a simple way to create network models by simply wiring together primitives with channels. xMAS models use synchronous semantics, and each stateful primitive updates its state variables on the same edge of an implicit global clock that is omitted from diagrams of network models. An xMAS model is easily translated into the UCLID modeling language (Chapters 5 and 7) or into synthesizable Verilog (Chapter 6) by mapping each primitive into the appropriate syntax. This provides a convenient tool flow for verifying properties of xMAS models using UCLID or RTL model checking.

#### **4.1.1** Communication over Channels

Communication in xMAS networks occurs between two primitives over a channel. The primitive that is initiating the communication is referred to as the initiator of the channel, and the primitive that is receiving the communication is referred to as the target. Each channel, drawn as a single directed edge in xMAS network diagrams, comprises three signals that are shared between the initiator and target (Fig. 4.1). For any channel c, the initiator primitive controls Boolean signal c.irdy (initiator ready) and c.data, while the target controls c.trdy (target ready). The value of c.data is transferred from initiator to target on any cycle when c.irdy and c.trdy are both asserted.

Figure 4.1: **The Signals Comprising an xMAS Channel.** The upstream primitive, denoted the initiator of channel *c*, controls *c.data* and the Boolean signal *c.irdy*. The downstream primitive, denoted the target, controls *c.trdy*. The value of *c.data* is transferred from initiator to target when *c.irdy* and *c.trdy* are **true** in the same cycle.

The communication protocol used in xMAS is an instance of latency-insensitive design [20], where functional correctness is independent of channel latencies. The channels in xMAS networks obey forward (Eq. 4.1) and backward (Eq. 4.2) persistency. Persistency means that a channel that is ready to initiate or receive data will remain so until a transfer occurs over the channel. The behavior of each primitive ensures that it will always obey forward and backward persistency, provided that all primitives it interfaces to also obey forward and backward persistency.

$$c.irdy \land \neg c.trdy \implies \mathbf{X}c.irdy$$

(4.1)

$$c.trdy \land \neg c.irdy \implies \mathbf{X}c.trdy \tag{4.2}$$

#### 4.1.2 Data Types in xMAS

Each channel has a designated type, in reference to the data signal on the channel. By convention, each channel in this dissertation uses one of two data types: the first type is flit data, and the second type is token data. In xMAS network diagrams with both types, a bold line is used to represent flit data, and a thinner line is used for tokens.

#### Flit Data

Flit data are bit-vectors that represent the individual flits of a packet (in Chapters 5 and 7) that are communicated across links in an NoC. In Chapter 6, flit data is replaced by packet data that represents all of the collective flits of a packet as one single unit of transfer. Flits and packets are grouped together here into the single type "flit" because of their similarity. Using data to represent an entire packet is a higher level of abstraction than representing individual flits, but ultimately the choice of whether to model data at the packet level or flit level depends on the network model. In chapters 5 and 7, flit-level modeling is used to capture the granting of output channels to head flits, and releasing of output channels by tail flits. In Chapter 6, it suffices to model traffic at the packet level.

Flit bit-vectors encode multiple logical fields. The values stored in certain positions of the data bit-vector represent logical fields such as destination addresses and timing information (discussed further in Sec. 4.4). Examples of these fields are shown in Tab. 4.1.

|            | bits of data                                                        |                 |     |

|------------|---------------------------------------------------------------------|-----------------|-----|

|            | 23   22   21   20   19   18   17   16   15   14   13   12   11   10 | 9 8 7 6 5 4 3 2 | 1 0 |

| head flit: | timestamp / age                                                     | x dest y dest   | 01  |

| body flit: | timestamp / age                                                     | payload         | 10  |

| tail flit: | timestamp / age                                                     | payload         | 11  |

Table 4.1: **Data Fields of a Typical Flit.** Head, body, and tail flits all store a timestamp or age in data[24:10]. The bits data[9:2] represent destination information in head flits and arbitrary payload for body and tail flits. Bits data[1:0] represent the flit type.

#### **Token Data**

Tokens channels are channels where the data value is null. The information communicated over such a channel is only an agreement by the initiator and target that a transfer has occurred, and the data value is insignificant. Token channels are used to model the transfer of credits in NoCs.

# 4.1.3 xMAS Primitives

All xMAS networks are compositions of eight simple kernel primitives (Fig. 4.2). The inputs and outputs drawn for each primitive represent channels, but at a more detailed level the inputs and outputs to each primitive are the signals within the channels. More precisely, the input signals to each primitive are (1) the *irdy* and *data* signals on each channel of which the primitive is the target; and (2) the *trdy* signals on each channel of which the primitive is the initiator. The output signals of each primitive are all the channel signals going in the opposite direction of the input signals.

Primitives can be either stateful or stateless. The stateful primitives update their state variables on each clock edge based on their current state and inputs, and also set outputs based on current state and inputs. The stateless primitives set output signals based directly upon their input signals. Among the eight kernel primitives, the source, sink, queue, and merge primitives have state, while the join, fork, switch, and function primitives are stateless.

The primitives as defined in the following paragraphs differ from the original xMAS paper [22] in the type of data transformations that are used. The original xMAS definition allows join primitives to receive two flits as inputs and produce a single output with a data value that is a function of both inputs. The convention is adopted here that the data transformations performed by the primitives are always unary; such primitives have previously been referred to as restricted primitives [22]. Since all data transformations are unary, it suffices to use the function primitive for all data transformations. All other primitives do not modify flits when propagating them from input channel to output channel.

Figure 4.2: **The xMAS Kernel Primitives.** All xMAS networks are created by instantiating combinations of these eight primitives, and connecting them using channels.

#### **Source Primitive**

A source primitive is an interface between the environment and network, and generates traffic that it injects into the network through its output channel o. A flit source primitive has a single Boolean state variable  $blocked := o.irdy \land \neg o.trdy$  that is **true** when a source is blocked from injecting. This state variable is used to ensure that the source satisfies forward persistency (Eq. 4.1) on its output channel, by continuing to retry a blocked transfer until succeeding. Source primitives are used for various purposes, and a few applications are given here:

- An *Eager Token Source* eagerly attempts to inject tokens in every cycle (i.e. *o.irdy* := **true**), and succeeds whenever the target of its output channel is ready to receive.