### Harsh Environment Silicon Carbide Metal-Semiconductor Field-Effect Transistor

Wei-Cheng Lien

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-234 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-234.html

December 20, 2013

Copyright © 2013, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Harsh Environment Silicon Carbide Metal-Semiconductor Field-Effect Transistor

by

Wei-Cheng Lien

A thesis submitted in partial satisfaction of the

requirements for the degree of

Master of Science

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Albert P. Pisano, Chair Professor Tsu-Jae King Liu

Fall 2013

Harsh Environment Silicon Carbide Metal-Semiconductor Field-Effect Transistor

Copyright © 2013

by

Wei-Cheng Lien

#### Harsh Environment Silicon Carbide Metal-Semiconductor Field-Effect Transistor

by Wei-Cheng Lien

#### **Research Project**

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, in partial satisfaction of the requirements for the degree of **Master of Science**, **Plan II**.

Approval for the Report and Comprehensive Examination:

**Committee:**

Professor Albert P. Pisano Research Advisor

(Date)

\* \* \* \* \* \* \*

Professor Tsu-Jae King Liu Second Reader

(Date)

#### Abstract

#### Harsh Environment Silicon Carbide Metal-Semiconductor Field-Effect Transistor

by

#### Wei-Cheng Lien

#### Master of Science in Electrical Engineering and Computer Sciences

#### University of California, Berkeley

Professor Albert P. Pisano, Chair

A harsh environment can be defined by one or more of the following: High temperature, high shock, high radiation, erosive flow, and corrosive media. Among all the harsh environment applications, high temperature applications have drawn lots of attention due to the emerging activity in automotive, turbine engine, space exploration and deep-well drilling telemetry. Silicon carbide has become the candidate for these harsh environment applications because of its wide bandgap, excellent chemical and thermal stability, and high breakdown electric field strength. This work details the fabrication process of n-channel silicon carbide metal-semiconductor field-effect transistors and the device performances are characterized from room temperature to 550 °C. These devices are made along with the fabrication process of silicon carbide junction field-effect transistors. The high transconductance and on/off drain saturation current ratio for the entire temperature range suggest the possibility of using these devices for high temperature operational amplifier applications.

# Contents

| Contents                                                                     | i             |

|------------------------------------------------------------------------------|---------------|

| List of Figures                                                              | ii            |

| List of Tables                                                               | iv            |

| 1. Introduction                                                              | 1             |

| 1.1 Harsh Environment Sensing Application                                    | 1             |

| 1.2 Silicon Carbide                                                          | 2             |

| 1.3 SiC Electronics Low Voltage High Temperature Application                 | 5             |

| 1.4 High Temperature Effects in 4H-SiC                                       | 7             |

| 1.5 Research Objective and Thesis Overview                                   | 8             |

| 2. Physics and Fabrication Process of Metal-Semiconductor Field-Effect Trans | sistor        |

| 2.1 Physics of MESFET                                                        | <b>9</b><br>9 |

| 2.2 Fabrication Process and Characterization Methods                         | 12            |

| 3. Silicon Carbide N-channel Metal-Semiconductor Field-Effect Transistors    | 16            |

| 3.1 Characterization of N-MESFET at Room Temperature                         | 16            |

| 3.2 Characterization of N-MESFET at High Temperatures                        | 18            |

| 4. Conclusion and Future Work                                                | 23            |

| 4.1 Conclusion                                                               | 23            |

| 4.2 Future Work                                                              | 23            |

| References                                                                   | 24            |

# **List of Figures**

| Figure 1.1: The structure of SiC crystal                                                                                                                                                                                                                                                                                                                                                    | 3                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Figure 1.2: Three most common polytypes of silicon carbide. <i>Copyright: Dr. Christo</i><br>S. Roper                                                                                                                                                                                                                                                                                       | -                         |

| Figure 1.3: Bi-layer stacking for the SiC polytypes 3C, 2H, 4H, and 6H                                                                                                                                                                                                                                                                                                                      | 3                         |

| Figure 1.4: Calculated energy bandgap of Si, 6H-SiC, and 4H-SiC versus temperatur                                                                                                                                                                                                                                                                                                           | e7                        |

| Figure 1.5: Intrinsic carrier concentration in Si, 6H-SiC, and 4H-SiC v temperature                                                                                                                                                                                                                                                                                                         |                           |

| Figure 2.1: Visualization of various phases of MESFET operation and the correspondence $I_D$ - $V_D$ characteristics at $V_{GS} = 0$ V. Note the SiC substrate serves as the body biasing The blue color in schematic represents the depletion regions, and the yellow color s the channel region. The shape of the channel is for the purpose of demonstration and not the real situation. | point.<br>hows<br>d it is |

| Figure 2.2: Schematic of a lateral n-channel 4H-SiC MESFET                                                                                                                                                                                                                                                                                                                                  | 13                        |

| Figure 2.3: Fabrication process flow n-channel 4H-SiC MESFET                                                                                                                                                                                                                                                                                                                                | 14                        |

| Figure 2.4: High temperature probe station                                                                                                                                                                                                                                                                                                                                                  | 15                        |

| Figure 2.5: HP 4156B semiconductor parameter analyzer and Agilent B2912A prec<br>source/measurement unit                                                                                                                                                                                                                                                                                    |                           |

| Figure 3.1: Optical image of a n-channel raised gate 4H-SiC MESFET with $L = 2$ .<br>and $W = 50 \ \mu m$                                                                                                                                                                                                                                                                                   | •                         |

| Figure 3.2: $I_{DS}$ - $V_{DS}$ characteristics of a n-channel 4H-SiC MESFET after RTA different $V_{GS}$ and with $W/L=50 \ \mu m/2.5 \ \mu m$ at 25 °C                                                                                                                                                                                                                                    |                           |

| Figure 3.3: (a) $I_{DS}$ - $V_{GS}$ (b) $\sqrt{I_{DS}}$ - $V_{GS}$ characteristics of a n-channel 4H-SiC MESFET $W/L=50 \ \mu\text{m}/2.5 \ \mu\text{m}$ and $V_{DS}=20 \ \text{V}$ at 25 °C                                                                                                                                                                                                |                           |

| Figure 3.4: $I_{DS}$ - $V_{DS}$ characteristics of a n-channel 4H-SiC MESFET under different $V_{GS}$                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and with $W/L=50 \ \mu m/2.5 \ \mu m$ (a) at 100 °C (b) at 200 °C (c) at 300 °C (d) at 400 °C (e) at                                                                 |

| 500 °C (f) at 550 °C19                                                                                                                                               |

| Figure 3.5: $I_{DS}$ - $V_{GS}$ characteristics of a n-channel 4H-SiC MESFET under $V_{DS} = 20$ V and with $W/L = 50 \ \mu m/2.5 \ \mu m$ at different temperatures |

| Figure 3.6: Optical image of a n-channel 4H-SiC MESFET after operating at 600 °C for few minutes which shows the morphology of interconnect changes                  |

| Figure 3.7: Temperature dependence of threshold voltage of a n-channel 4H-SiC MESFET with $W/L=50 \ \mu m/2.5 \ \mu m$                                               |

| Figure 3.8: Temperature dependence of transconductance and intrinsic gain of a n-<br>channel 4H-SiC MESFET with $W/L=50 \ \mu m/2.5 \ \mu m$                         |

# **List of Tables**

| Table 1.1: High temperature electronics applications    2                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2: Mechanical properties of Si and wide bandgap semiconductors. If the thermal expansion coefficient has two values, the first one is along the a-axis and the second one is along the c-axis.         4                                                                                  |

| Table 1.3: Electrical properties of Si and wide bandgap semiconductors. If the electron mobility has two values, the first one is perpendicular to the c-axis and the second one is parallel to the c-axis.                                                                                       |

| Table 1.4: A sampling of published single transistors for high temperature applications6                                                                                                                                                                                                          |

| Table 3.3: Extracted parameters of a n-channel 4H-SiC MESFET with $W/L=50 \ \mu m/2.5 \ \mu m$ at various temperatures. $g_m$ , $R_{on}$ , $r_o$ , $\lambda$ and $g_m r_o$ is based on $V_{GS} = 0$ V. $I_{Dsat}/I_{off}$ is the ratio of current at $V_{GS} = 0$ V to current at $V_{GS} = -9$ V |

### Chapter 1

### Introduction

#### **1.1 Harsh Environment Sensing Application**

Recently, many research efforts are focused on advancing renewable energy resources, such as solar, hydro, wind and geothermal energy. While developing on these new technologies, reducing the inefficiencies in generation and transmission should be considered. For example, the total energy lost is 61% of energy supply in U.S. in 2012 [1]. One method of addressing the inefficiencies in energy use is through the development of harsh environment sensing technology. Power systems can be advanced by integration of electronics (communication, signal processing, microactuator control, etc.) to be operated at high temperature [2, 3]. More specifically, smart harsh environment electronic sensing systems enable real-time condition based monitoring of temperature and incomplete combustion, and reduce emission of greenhouse gas (NO<sub>x</sub> and CO<sub>2</sub>) in gas turbine systems to guide deep-well oil drilling operation or monitors the subsurface environments found in geothermal power plants.

Harsh environment can be defined by one or more of the following: High temperature (> 350 °C), high shock (> 50,000 g), high radiation (> 100 Mrads), erosive flow and corrosive media [6]. Silicon is a widely used semiconductor material because of such factors as its high quality, stable oxide, and low cost. However silicon-based microelectronics are not suitable for harsh environments, because the electronic properties of silicon degrade above 300 °C due to the more intrinsic carrier presented than dopant carriers and mechanical properties degrade above 600 °C due to decline in its elastic modulus [3]. As the need increases for electronics and microelectromechanical systems (MEMS) devices suitable for harsh environment applications, including automobile, aerospace, nuclear and military purposes, several technologies such as silicon-on-insulator (SOI) or wide bandgap (WBG) electronics are needed. SOI technology can extend the CMOS operating temperature due to reduce leakage and less parasitic bipolar action [7]. Wide bandgap material has large energy bandgap of 3 eV so the generation of intrinsic carriers will not surpass the dopant carriers at high temperature.

In order to realize integration of the sensing system, the building block of the sensor system such as sensors and transistors need to be developed. Among all the harsh environment applications, high temperature application has drawn lots of attention due to the emerging activity in many areas (Table 1.1) [3]. In this work, we are focus on

| Application                  | Area                              | Peak<br>ambient<br>(°C) | Chip<br>power<br>(kW) | Target technology |

|------------------------------|-----------------------------------|-------------------------|-----------------------|-------------------|

| Autimotive                   | On-cylinder<br>& Exhaust<br>pipe  | 600                     | < 1                   | WBG               |

| Turbine engine               | Sensors,<br>telemetry,<br>control | 600                     | < 1                   | WBG               |

|                              | Electric actuation                | 600                     | > 10                  | WBG               |

| Spacecraft                   | Power<br>management               | 300                     | > 10                  | WBG               |

|                              | Venus &<br>Mercury<br>exploration | 550                     | 1                     | WBG               |

| Industrial                   | High<br>temperature<br>processing | 600                     | < 1                   | SOI & WBG         |

| Deep-well drilling telemetry | Oil and gas                       | 300                     | < 1                   | SOI & WBG         |

|                              | geothermal                        | 600                     | < 1                   | WBG               |

developing the electronics for high temperature application. Silicon carbide (SiC) has been chose as based semiconductor material for this work due to a wide bandgap, high electric field breakdown strength, high thermal conductivity, and high saturated carrier drift velocity [8].

Table 1.1: High temperature electronics applications [3].

#### **1.2 Silicon Carbide**

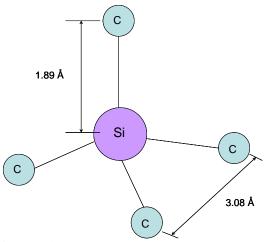

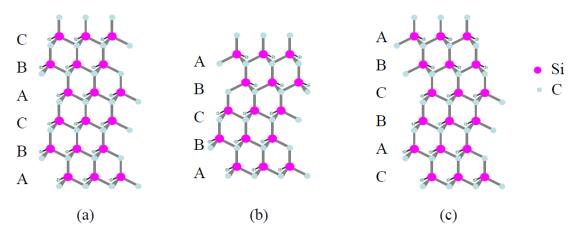

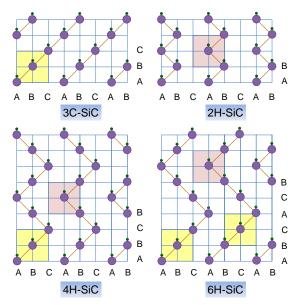

The silicon carbide unit cell is the tetrahedron of four carbon atoms with a silicon atom in the center depicted in Figure 1.1. There are approximately 200 polytypes of SiC existing in the world [9]. Figure 1.2 shows the three most common polytypes of silicon carbide, consisting of different stacking sequences of SiC bilayer. They are cubic (3C,  $\beta$ -SiC) and hexagonal (H,  $\alpha$ -SiC) with the number denoting the number of SiC bilayer stackings [10]. Because of the possible stacking sequences of SiC bilayer, there is lattice sites in SiC that have a surrounding layer stacking in hexagonal form and others with cubic form, which are denoted hexagonal sites and cubic sites, respectively [11]. Figure 1.3 shows that 3C-SiC has one cubic site and 2H-SiC includes only one hexagonal site. 4H-SiC has one hexagonal and one cubic site, while 6H-SiC exhibits one hexagonal and two cubic sites. 4H-SiC and 6H-SiC polytypes already have commercially available wafers and epitaxy, while 3C-SiC is the only polytype that can be grown heteroepitaxially on a Si wafer [12-18]. The basic mechanical and electrical properties of the three SiC polytypes, as well as those for Si, GaN, AlN, and Diamond are shown in Table 1.2 and 1.3 [11, 19, 20].

Figure 1.1: The structure of SiC crystal.

Figure 1.2: Three most common polytypes of silicon carbide [10]. Copyright: Dr. Christopher S. Roper

Figure 1.3: Bi-layer stacking for the SiC polytypes 3C, 2H, 4H, and 6H [11].

|                                                              | Si   | 3C-SiC | 6H-SiC    | 4H-SiC   | 2H-GaN    | 2H-AlN    | Diamond |

|--------------------------------------------------------------|------|--------|-----------|----------|-----------|-----------|---------|

| Lattice a<br>(Å)                                             | 5.43 | 4.36   | 3.08      | 3.08     | 3.189     | 3.112     | 3.567   |

| Lattice c<br>(Å)                                             | NA   | NA     | 15.12     | 10.08    | 5.185     | 4.982     | NA      |

| Thermal<br>expansion<br>coefficient<br>(10 <sup>-6</sup> /K) | 2.6  | 3.28   | 3.35/3.25 | 3.3/3.16 | 5.59/3.17 | 5.27/4.15 | 0.8     |

| Density<br>(g/cm <sup>3</sup> )                              | 2.33 | 3.21   | 3.21      | 3.21     | 6.15      | 3.23      | 3.5     |

| Thermal<br>conductivi<br>ty (W/cm<br>K)                      | 1.5  | 3.6    | 4.9       | 4.9      | 1.3       | 2.85      | 20      |

| Melting<br>point (°C)                                        | 1420 | 2830   | 2830      | 2830     | 2500      | 3000      | 4000    |

| Mohs<br>hardness                                             | 7    | 9      | 9         | 9        |           | 7         | 10      |

Table 1.2: Mechanical properties of Si and wide bandgap semiconductors. If the thermal expansion coefficient has two values, the first one is along the a-axis and the second one is along the c-axis.

|                                                              | Si   | 3C-SiC | 6H-SiC  | 4H-SiC   | 2H-GaN | 2H-AIN | Diamond |

|--------------------------------------------------------------|------|--------|---------|----------|--------|--------|---------|

| Energy<br>bandgap<br>(eV)                                    | 1.12 | 2.4    | 3.0     | 3.23     | 3.4    | 6.2    | 5.6     |

| Breakdown<br>field(MV/c<br>m)                                | 0.25 | 2.5    | 2.5     | 2.2      | 3.0    | 2.0    | 20      |

| Electron<br>saturation<br>velocity (10 <sup>7</sup><br>cm/s) | 1.0  | 2.5    | 2.0     | 2.0      | 2.5    | 2.0    | 2.7     |

| Electron<br>mobility<br>(Cm/V s)                             | 1400 | 1000   | 500/100 | 950/1150 | 1245   | 135    | 2200    |

| Hole<br>mobility<br>(cm/V s)                                 | 600  | 50     | 80      | 120      | 370    | 14     | 1600    |

| Dielectric constant                                          | 11.9 | 9.7    | 10.0    | 10.0     | 9.5    | 8.5    | 5.5     |

Table 1.3: Electrical properties of Si and wide bandgap semiconductors. If the electron mobility has two values, the first one is perpendicular to the c-axis and the second one is parallel to the c-axis.

Owing to the superior mechanical properties of SiC, it is very suitable for the Microelectromechanical systems (MEMS). SiC based MEMS devices have been previously used as temperature and pressure sensors in high temperature environment

[21], high-g accelerometers [22], biomedical sensors [23], and strain sensor [5]. SiC may also be suitable for high frequency MEMS resonators as micromechanical oscillators and filters due to its high  $E/\rho$  ratio, since the resonant frequency of a micromachined device can be expressed as

$$\omega = Cf \sqrt{\frac{E}{\rho}} \tag{1.1}$$

where C is constant, f is a function of Poisson's ratio, E is the material Young's modulus and  $\rho$  is the material density. SiC has been successfully used to fabricate Lamé mode MEMS resonators for signal processing [24].

SiC may be used for high temperature, high power, high frequency and radiation resistance electronics applications. For example, its wide bandgap makes SiC desirable for electronics in high temperature environments. Additionally, breakdown electric field strength ( $E_{max}$ ) is perhaps the most important factor for high power applications: the  $E_{max}$  of SiC is ten times that of silicon. As high-frequency devices, the saturated electron drift velocity of SiC is twice that of silicon, thus enabling microwave devices to reach high channel currents [25-27].

### **1.3 SiC Electronics Low Voltage High Temperature Application**

Lots of progress has been made for the development of high temperature SiC electronic devices for low voltage or low power analog and digital circuit applications. D. M Brown et al. from Generic Electric Company reported a 6H-SiC operational amplifier based on the n-channel enhancement and depletion mode metal-oxide-semiconductor field effect transistors (MOSFETs). It works up to 300 °C with a low frequency gain of 53 dB and the bandwidth of 269 kHz [28]. A monolithic 6H-SiC CMOS digital integrated circuits has been developed [29]. The threshold voltages of PMOS and NMOS at 300 °C are -6 V and 0.5 V, respectively. The effect channel mobilities of PMOS and NMOS at 300 °C are 7.01 and 20.8 cm<sup>2</sup>/Vs, respectively. Raytheon has been developed the 4H-SiC CMOS integrated circuit with operating temperature of 400 °C [30]. The gate leakage current is less than 1 pA at 350 °C.

A differential amplifier using 6H-SiC metal-semiconductor field effect transistor (MESFETs) and thick film hybrid technology has been reported [31]. It has a voltage gain of 61 dB, common mode rejection ratio (CMRR) of 60 dB, bandwidth of 910 kHz, offset voltage of 151 mV, and power dissipation of 178 mW at 350 °C. NASA Glenn Research Center has demonstrated a 4H-SiC MESFET based hybrid, ultra high frequency band differential oscillator [32]. The oscillator delivers 4.9 dBm at 453 MHz at 475 °C. M. Alexandru et al. designed and characterized 4H-SiC MESFET based inverter, NAND and NOR gates that work up to 300 °C [33]. 4H-SiC bipolar junction transistor (BJT) with operating temperature up to 500 °C has been reported [34]. The current gain is approximately 42 at 500 °C using Ti/TiW/A1 metallization.

Numerous studies on SiC junction field effect transistor (JFETs) for high temperature applications. This is because the JFET structure is based on pn junction which are free of oxide reliability and Schottky contact stability existing in MOSFET and MESFET in the temperature range of 500 °C. A back gate n-channel 6H-SiC JFET has been developed and modeled up to 400 °C [35]. Daimler Benz Research Laboratories reported the 6H-SiC implanted-gate n-channel JFETs with working temperature of 400 °C. The transconductance is approximately 0.16 mS/mm and on/off saturation drain current ratio is ~ 106 at 400 °C. NASA Glenn Research Center has demonstrated very stable long term operation of 6H-SiC n-channel JFETs at 500 °C for more than 3007 hours [36]. A 600 °C of NAND and NOR gates have also been developed in this center [37]. A AC coupled differential amplifier using 4H-SiC vertical JFET has been developed, and the voltage gain is 47.8 dB with CMRR of ~ 45 dB at 500 kHz at 450 °C [38]. A. C. Patil et al. has reported a 6H-SiC JFET based two stage differential amplifier with a voltage gain of 69.2 dB and unit gain frequency of 1.4 MHz at 576 °C [39].

Table 1.4 below summarizes the maximum operating temperature of recent works for low voltage high temperature single transistors including SiC, GaN and diamond. It can be seen that SiC shows promising preliminary results of high temperature electronics. However, lots of challenges still need to be address until the commercialization. First, the process of making SiC based electronics devices is not as mature as that for Si CMOS. This is because the design and process approaches for Si based electronics can not be directly used for SiC based electronics due to different materials properties. Besides, the reliability and resistivity of Ohmic contact areas need to be further improved for high temperature operations. Perhaps the most important factor however is that large scale, high quality, and low cost epitaxial or single crystal SiC films have not yet been fully developed. A technology capable of providing these would greatly improve the availability of SiC high temperature electronic devices. In summary, there exist many limitations for SiC based electronics and their integrate circuits but the superior material properties of SiC makes it desirable to be used for extremely high temperature electronics.

| References                                            | Material  | Device   | Max. Temperature (°C) |

|-------------------------------------------------------|-----------|----------|-----------------------|

| IMB-CNM, Spain<br>(2012) [33]                         | 4H-SiC    | MESFET   | 300                   |

| Raytheon, UK (2011)<br>[30]                           | 4H-SiC    | MOSFET   | 350                   |

| Semisouth Lab, USA<br>(2009) [40]                     | 4H-SiC    | VJFET    | 450                   |

| JPL, USA (2010) [41]                                  | AlGaN/GaN | MOS HEMT | 450                   |

| Tokyo Insitute of<br>Technology, Japan<br>(2013) [42] | Diamond   | JFET     | 450                   |

| KTH, Sweden (2013)<br>[34]                            | 4H-SiC    | BJT      | 500                   |

| NASA, USA [36]                                        | 6H-SiC    | JFET     | 500                   |

| University of Ulm,<br>Germany (2012) [43]             | InAlN/GaN | HEMT     | 1000                  |

Table 1.4: A sampling of published single transistors for high temperature applications.

#### **1.4 High Temperature Effects in 4H-SiC**

To successfully design the high temperature 4H-SiC electronics, it is crucial to understand the temperature effect of the fundamental semiconductor physical properties.

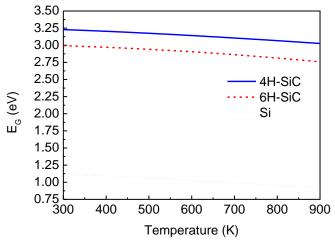

The energy bandgap ( $E_G$ ) in 4H-SiC as a function of temperature is approximated by [44]

$$E_G = 3.265 - 6.5 \times 10^{-4} \left(\frac{T^2}{T + 1300}\right) \tag{1.2}$$

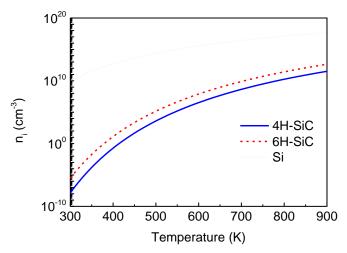

where *T* is temperature. The calculated bandgap of Si, 6H-SiC, and 4H-SiC are plotted in Figure 1.4. 4H-SiC has highest bandgap through the entire temperature. As temperature increases, the bandgap is reduced which results in larger intrinsic carrier concentrations, larger leakage current in pn junctions and poorer device isolation by reversed-biased junctions [39].

Figure 1.4: Calculated energy bandgap of Si, 6H-SiC, and 4H-SiC versus temperature.

The intrinsic carrier concentration  $(n_i)$  in 4H-SiC is given by [45]

$$n_i = \sqrt{N_c N_v} \exp(-\frac{E_G}{2k_B T}) \tag{1.3}$$

$$N_c = 2M_c \left(\frac{2\pi m_n^* k_B T}{h^2}\right)^{3/2} \tag{1.4}$$

$$N_{\nu} = 2\left(\frac{2\pi m_p^* k_B T}{h^2}\right)^{3/2} \tag{1.5}$$

where  $N_c$  and  $N_v$  are effective density-of-states of electrons in the conduction band and holes in the valence band, respectively.  $k_B$  is Boltzmann constant, h is planck's constant,  $M_c$  represent the number of equivalent energy minima in the conduction band which is 3 for 4H-SiC,  $m_n^*$  and  $m_p^*$  are the electron effective mass and hole effective mass, respectively. Figure 1.5 compares the intrinsic carrier concentration of Si, 6H-SiC, and 4H-SiC versus temperature. For a given temperature, 4H-SiC has the smallest  $n_i$  due to the largest bandgap energy. The intrinsic carrier concentration of Si at 900 K is  $4.3 \times 10^{17}$  cm<sup>-3</sup> which is comparable with the dopant carrier concentrations. Even at 900 K,  $n_i$  of 6H-SiC and 4H-SiC are only  $4.32 \times 10^{12}$  and  $3.24 \times 10^{11}$  cm<sup>-3</sup>, suggesting a fundamental advantage of wide bandgap SiC over Si for high temperature application.

Figure 1.5: Intrinsic carrier concentration in Si, 6H-SiC, and 4H-SiC versus temperature.

#### **1.5 Research Objective and Thesis Overview**

High temperature electronics that operate at 300-600 °C are beneficial for in-situ monitoring of fuel combustion, subsurface reservoirs (deep well drilling), and Venus and Jupiter surface exploration. This dissertation details the high temperature performance of the 4H-SiC MESFET.

Chapter 2 describes the physics and the fabrication of the MESFET. In Chapter 3, the study of 4H-SiC n–channel MESFET is presented. The basic properties of MESFET from 25 to 550 °C is characterized and summarized. Finally, in Chapter 4 the contributions of this work are summarized and future research directions are suggested.

### Chapter 2

# **Physics and Fabrication Process of Metal-Semiconductor Field-Effect Transistor**

#### **2.1 Physics of MESFET**

The metal-semiconductor field-effect transistor was invented by C. Mead in 1966 [46]. It is a unipolar transistor which means only one type of carrier is involved in the operation. Unlike MOSFET for high temperature operation, MESFET eliminates the chance of metal-semiconductor-oxide interface traps, increase oxide reliability, and reduces the minority carrier instability [47]. The metal gate using low temperature process compared to pn junction made by high temperature growth or ion implantations [48]. The metal gate has better control of size scaling and hence it is beneficial for enhancing the speed of the transistor.

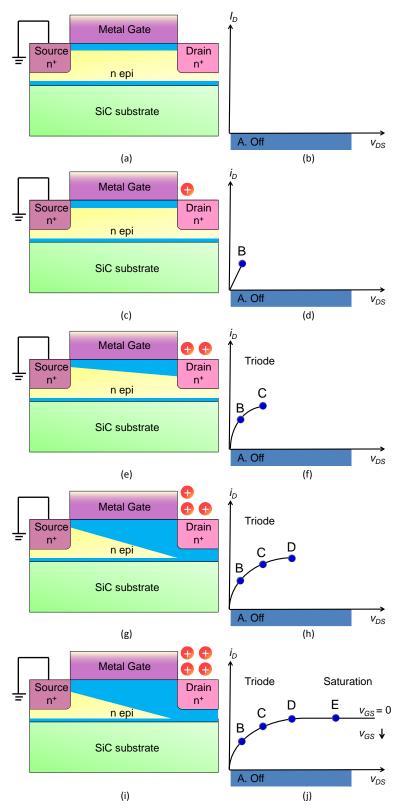

The fundamental operation principle of n-channel MESFET is described as follows [48-50]. First, the gate terminal is grounded and the drain voltage is 0 V. MESFET is in thermal equilibrium. As shown in Figure 2.1 (a), once the metal-n Schottky junction is deposited, the depletion width is formed. Due to the metal gate, the depletion region primarily extends into the n-channel area of the device. The device at this stage is in off state (Figure 3.1 (b)). Applying  $V_D$  to small positive voltages, the channel is formed at the non-depleted and current-carrying region as shown in Figure 3.1 (c). The channel acts like a simple resistor, and the drain current is increased linearly with drain voltage as shown in point B of Figure 3.1 (d). As  $V_D$  keeps increasing, the depletion width around drain side is widened as shown in Figure 3.1 (e). The channel region is still like a resistor, but because of the loss of the conduction channel near the drain side, the resistance between the source and drain is increased and the increasing rate of  $I_D$  is reduced which results the slope of  $I_D$ - $V_D$  characteristic decreases at larger  $V_D$  as shown in point C of Figure 3.1 (f). If we continue to increase the  $V_D$ , the channel is further narrowed and eventually reaches the pinch-off state shown in Figure 3.1 (g). The slope of  $I_D$ - $V_D$  characteristic is approximately zero at the pinch-off set, as shown at point D in Figure 3.1 (h), and the drain bias at this point is called saturation drain voltage ( $V_{Dsat}$ ). As the drain voltage becomes larger than  $V_{Dsat}$ , the pinch-off area widens to the extent of  $\Delta L$ . The voltage difference between  $V_D$  and  $V_{Dsat}$  is mainly dropped along the  $\Delta L$ , and the major mechanism of current flow is through drift current as shown in Figure 3.1 (i). The

corresponding  $I_D$ - $V_D$  characteristic saturates, namely remaining constant at the saturation drain current shown in point E of Figure 3.1 (j).

The drain current  $(I_{DS})$  versus drain-to-source voltage  $(V_{DS})$  characteristics of MESFET can be expressed using the conventional 3/2 power model [48]. The basic assumptions are uniformly doped channel with gradual-channel approximation (i.e., electric field perpendicular to channel is smaller than electric field parallel to channel), abrupt depletion layer, small gate leakage current and constant mobility. The built-in potential  $(V_{bi})$  of MESFET is given by

$$V_{bi} = \phi_{Bn} - \frac{kT}{q} ln \left(\frac{N_c}{N_D}\right)$$

(2.1)

where q is unit electronic charge,  $\phi_{Bn}$  is the Schottky barrier height, k is Boltzmann constant, T is temperature,  $N_D$  is donor impurity concentration, and  $N_C$  is the effective density of states in conduction band. The pinch-off potential  $(V_P)$  is given by

$$V_P = \frac{qN_D D}{2\varepsilon_s} \tag{2.2}$$

where D is the channel depth and  $\varepsilon_s$  is permittivity of 4H-SiC. The normalized pinch-off current  $(I_P)$  is given by

$$I_P' = \left(\frac{q^2 N_D n \mu_n D^3}{6\varepsilon_s}\right) \tag{2.3}$$

where *n* is ionized carrier concentration in the channel and  $\mu_n$  is mobility of carriers. The gate threshold voltage (*V<sub>T</sub>*) around which the MESFET is turned on and off is given by

$$V_T = V_{bi} - V_P \tag{2.4}$$

In triode region, where  $V_{DS} < V_{Dsat} = V_{GS} - V_T$ , the drain current is given by

$$I_{DS} = \left(\frac{W}{L}\right) I_{P}' \left[\frac{3V_{DS}}{V_{p}} - 2\left[\left\{\frac{V_{DS} - V_{GS} + V_{bi}}{V_{p}}\right\}^{3/2} - \left\{\frac{(-V_{GS} + V_{bi})}{V_{p}}\right\}^{3/2}\right]\right] (1 + \lambda V_{DS})$$

(2.5)

In saturation region, where  $V_{DS} \ge V_{Dsat} = V_{GS} - V_T$ ,

$$I_{DS} = \left(\frac{W}{L}\right) I'_{P} \left[1 - 3\left(\frac{-V_{GS} + V_{bi}}{V_{po}}\right) + 2\left(\frac{-V_{GS} + V_{bi}}{V_{po}}\right)^{3/2}\right] (1 + \lambda V_{DS})$$

(2.6)

where W and L are channel width and length, respectively,  $V_{GS}$  is the gate-to-source voltage, and  $\lambda$  is channel length modulation parameter of the MESFET.

Figure 2.1: Visualization of various phases of MESFET operation and the corresponding  $I_D$ - $V_D$  characteristics at  $V_{GS} = 0$  V. Note the SiC substrate serves as the body biasing point. The blue color in schematic represents the depletion regions, and the yellow color shows the channel region. The shape of the channel is for the purpose of demonstration and it is not the real situation.

#### **2.2 Fabrication Process and Characterization Methods**

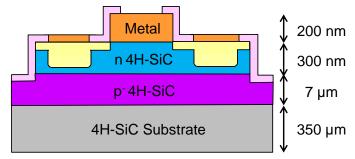

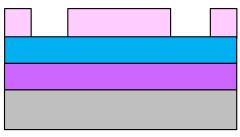

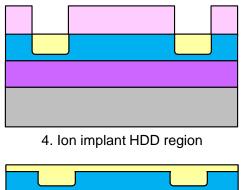

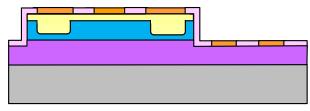

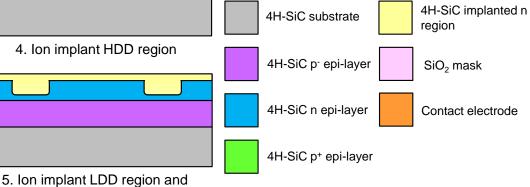

Figure 2.2 is a cross-sectional schematic of a lateral n-channel 4H-SiC MESFET used in this work. The device was fabricated with the same process of n-channel JFET. The transistor consists of p-type 4H-SiC wafer (from Cree Inc.) with three epitaxial layers (from Ascatron AB). A 5 µm p- epitaxial layer with doping concentration of  $2 \times 10^{15}$  cm<sup>-3</sup>, followed by 300 nm n- epitaxial layer with doping concentration of  $1 \times 10^{17}$ cm<sup>-3</sup> and 200 nm p<sup>+</sup> epitaxial layer with doping concentration of  $2 \times 10^{19}$  cm<sup>-3</sup> were grown on the p-type wafer with the resistivity of approximately 1  $\Omega$ -cm. The entire fabrication process flow is shown in Figure 2.3 including seven lithography masks. First, the  $p^+$  layer for gate of JFET was removed by time etched using transformer coupled plasma (TCP) etcher with 90 sccm Cl<sub>2</sub> and 10 sccm BCl<sub>3</sub> under RF bias of 150 W. 1 µm plasmaenhanced chemical vapor deposition (PECVD) SiO<sub>2</sub> was patterned to define the source and drain area with nitrogen implantation at 600 °C which facilitates Ohmic contact to the metal with reduced damage of crystallinity [51]. The implantation of a box profile was formed using  $1.4 \times 10^{15}$ ,  $7 \times 10^{14}$ , and  $3.6 \times 10^{14}$  doses at 60, 40, and 20 keV energies, respectively. The implantation should yield a nitrogen concentration higher than  $10^{19}$  cm<sup>-</sup> <sup>3</sup>. After ion implantation, the oxide layers were removed by the buffer oxide etching solution (hydrofluoric acid). The second lighter-dose nitrogen was implanted using  $3.2 \times 10^{12}$ ,  $8 \times 10^{11}$ ,  $8 \times 10^{11}$ , and  $1 \times 10^{12}$  doses at 33, 24, 18, and 10 keV energies, respectively [37]. The implanted dopants were electrically activated by annealing samples capped with 2 µm PECVD SiO<sub>2</sub> at 1450 °C under an Argon atmosphere for 30 minutes. Note that the second light-dose implantation was for the purpose of reducing the resistance from the gate to source/drain of JFET, and is not necessary for MESFET. A mesa etch was then used to define the device area using a transformer coupled plasma etcher. The MESFET surface was then passivated with PECVD SiO<sub>2</sub> and the 50 nm Ti, 100 nm Ni, and a 50 nm TiW (10% Ti, 90% W) metal gate and contact of source/drain was deposited and patterned via lift-off to form the contact electrode. The metal contacts were annealed with rapid thermal annealing (RTA) at 1000 °C for 2 minute under Ar ambient. 200 nm TiW (10% Ti, 90% W) was used for the 1st level of metal interconnects. Finally, the 20 nm Cr and 180 nm Pt was used for 2nd level of metal interconnect and the backside contact of the wafer. Pt was chosen as the final contact due to the compatibility for wire bonding and also helps contacts operate for a significantly longer time under a high temperature environment by protecting the underlying metals [52].

Figure 2.2: Schematic of a lateral n-channel 4H-SiC MESFET.

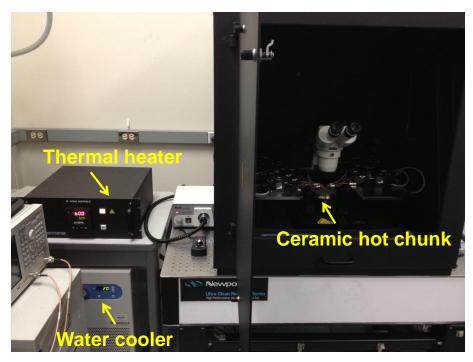

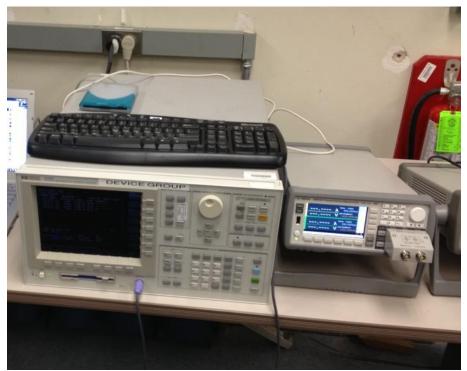

Devices were characterized on a hot chuck of high temperature probe station (Signatone Inc.) as shown in Figure 2.4. This high temperature probe station consists of ceramic hot chunk, thermal heater, and water cooler, and the chunk temperature goes up to 600 °C with low thermal noise of  $10^{-9}$ - $10^{-8}$  A at 600 °C. An HP 4156B semiconductor parameter analyzer and Agilent B2912A precision source/measurement unit with tungsten probe tips were used to measure the I-V characteristics of the devices as shown in Figure 2.5.

| p <sup>+</sup> 4H-SiC (N <sub>A</sub> = 2E19 cm <sup>-3</sup> ) |

|-----------------------------------------------------------------|

| n 4H-SiC (N <sub>D</sub> = 1E17 cm <sup>-3</sup> )              |

| p <sup>-</sup> 4H-SiC (N <sub>A</sub> = 2E15 cm <sup>-3</sup> ) |

| 4H-SiC Substrate                                                |

1. Procure SiC substrate with three epi-layers

6. Micromachine SiC layer with timed etch to define mesa (Mask 3)

2. Remove SiC p<sup>+</sup> epi-layer with timed etch (Mask 1 for JFET gate)

3. Deposit conformal SiO<sub>2</sub> mask (Spacers) and open S/D vias (Mask 2)

7. Passivate structure with conformal SiO<sub>2</sub> and open metal contact vias (Mask 4)

8. Deposit metal contacts. Series steps of metal depositions: Deposit metal contacts, passivate structure with conformal SiO<sub>2</sub>, open metal contact vias (Mask 5), deposit 1<sup>st</sup> metal contacts, passivate structure with conformal SiO<sub>2</sub> and open interconnect vias (Mask 6), and deposit 2<sup>nd</sup> metal (Mask 7).

dopant activation annealing

Figure 2.3: Fabrication process flow n-channel 4H-SiC MESFET.

Figure 2.4: High temperature probe station.

Figure 2.5: HP 4156B semiconductor parameter analyzer and Agilent B2912A precision source/measurement unit.

### Chapter 3

## Silicon Carbide N-channel Metal-Semiconductor Field-Effect Transistors

### **3.1 Characterization of N-MESFET at Room Temperature**

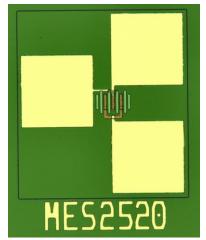

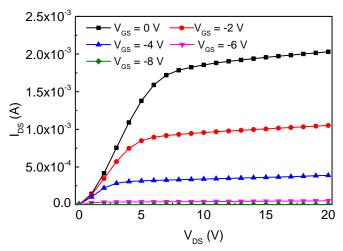

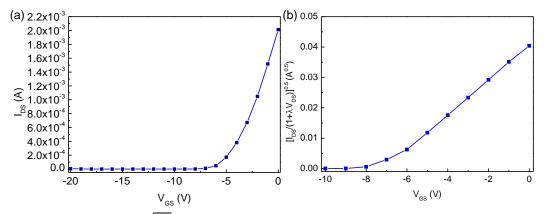

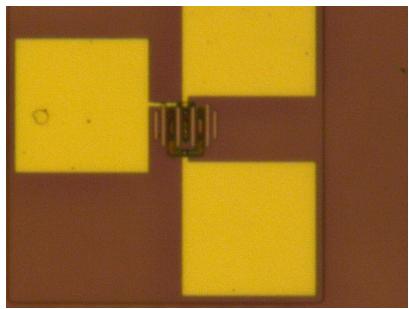

Figure 3.1 shows the optical images of as-fabricated 4H-SiC lateral MESFET. The device has double-finger geometry with  $L = 2.5 \ \mu\text{m}$  and effective  $W = 50 \ \mu\text{m}$ . Figure 3.2 shows the drain current versus drain-to-source voltage characteristics of a 50  $\ \mu\text{m}$  /2.5  $\ \mu\text{m}$ MESFET after RTA at room temperature. The device is fully-on at  $V_{GS} = 0$  V and cut-off at  $V_{GS} = -9$  V.  $\lambda$  is estimated to be  $1.15 \times 10^{-2}$  V<sup>-1</sup>. The drain-to-source saturation current is 40.6 mA/mm and the current density is 738 A/cm<sup>2</sup> at  $V_{DS} = 20$  V and  $V_{GS} = 0$  V. Figure 3.3 (a) shows the drain current versus gate-to-source voltage characteristics at  $V_{DS} = 20$  V and the threshold voltage can be extracted from the extrapolated intercept of x axis of

$\sqrt{\frac{I_{DS}}{1+\lambda V_{DS}}}$  vs.  $V_{GS}$  plot at  $V_{DS} = 20$  V in Figure 3.3 (b). The threshold voltage is approximately -7.07 V at 25 °C.

Figure 3.1: Optical image of a n-channel raised gate 4H-SiC MESFET with  $L = 2.5 \mu m$  and  $W = 50 \mu m$ .

Figure 3.2:  $I_{DS}$ - $V_{DS}$  characteristics of a n-channel 4H-SiC MESFET after RTA under different  $V_{GS}$  and with  $W/L=50 \ \mu m/2.5 \ \mu m$  at 25 °C.

Figure 3.3: (a)  $I_{DS}-V_{GS}$  (b)  $\sqrt{I_{DS}}-V_{GS}$  characteristics of a n-channel 4H-SiC MESFET with  $W/L=50 \ \mu m/2.5 \ \mu m$  and  $V_{DS}=20 \ V$  at 25 °C.

The transconductance  $(g_m)$  could be extracted from square-law model using Taylor expansion near  $V_{GS} = V_T$  as follows [39, 47]

$$k' = \frac{3I'_P}{4V'_{po}} = \frac{\mu_n \varepsilon_s n}{2DN_D}$$

(3.1)

$$g_m = 2\sqrt{\frac{w}{L}k'I_{DS}} = \frac{2I_{DS}}{v_{GS} - v_T}$$

(3.2)

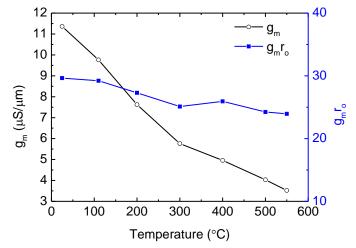

The estimated  $g_m$  of 4H-SiC MESFET is 11.36  $\mu$ S/ $\mu$ m (normalized with the channel width of 50  $\mu$ m) at room temperature. The estimated output resistance ( $r_o$ ) is 5.22×10<sup>4</sup>  $\Omega$ . The intrinsic gain ( $g_m r_o$ ) of single 4H-SiC MESFET is approximately 29.6 or 29.4 dB at  $V_{GS} = 0$  V.

# **3.2 Characterization of N-MESFET at High Temperatures**

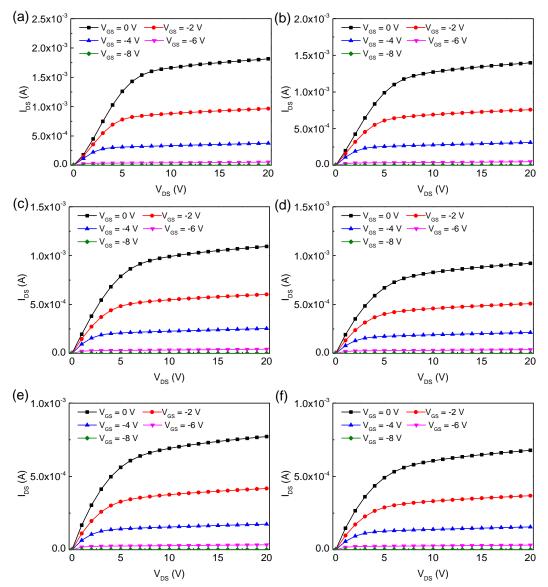

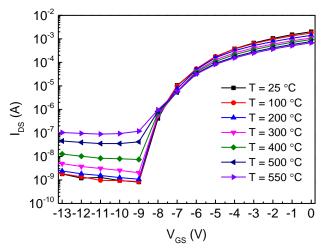

Figure 3.4 (a)-(g) show the  $I_{DS}$ - $V_{DS}$  characteristics of n-channel raised gate 4H-SiC MESFET from 100 to 550 °C. The MESFET shows excellent I<sub>DS</sub>-V<sub>DS</sub> characteristics over the entire temperature range. Figure 3.5 shows the  $I_{DS}$ - $V_{GS}$  curves under a drain-tosource 20 V bias and at incremental temperatures up to 550 °C. A monotonic decrease in saturation current is observed, and this can be attributed to the power law degradation of the electron mobility at elevated temperatures [53]. The degradation of the mobility also causes the  $R_{on}$  to increase from 9.55 to 28.17 m $\Omega$  cm<sup>2</sup>. The  $I_{Dsat}$  of MESFET at  $V_{GS} = 0$  V and 550 °C is approximately 72 % less than its value at room temperature. However, the device is fully functional that the change of  $I_{Dsat}$  is in response to the applied gate voltage at 550 °C, as shown in Figure 3.4 (f). The off current ( $I_{off}$ ) at V = -9 V increases from  $9.4 \times 10^{-10}$  A to  $3.2 \times 10^{-7}$  A as the temperature increase from 25 °C to 550 °C due to the decrease of the energy bandgap of 4H-SiC at elevated temperatures (Figure 1.4) [45, 53]. The calculated on/off drain saturation current ratio  $(I_{Dsat}/I_{off})$  is 2.14×10<sup>6</sup> at room temperature and decreases to  $1.85 \times 10^3$  at 600 °C suggesting a good electrostatic controllability of metal gate. Further increasing the ambient temperature to 600 °C, the devices only work for few minutes and loss the typical I-V characteristics of MESFET. This is because the metal interconnect, 200 nm TiW in this case, has been destroyed as shown in Figure 3.6. More robust metal interconnect which is thermal stable without morphology change is required to extend the working temperature from 550  $^{\circ}$ C to 600  $^{\circ}$ C.

Figure 3.4:  $I_{DS}-V_{DS}$  characteristics of a n-channel 4H-SiC MESFET under different  $V_{GS}$  and with  $W/L=50 \mu m/2.5 \mu m$  (a) at 100 °C (b) at 200 °C (c) at 300 °C (d) at 400 °C (e) at 500 °C (f) at 550 °C.

Figure 3.5:  $I_{DS}$ - $V_{GS}$  characteristics of a n-channel 4H-SiC MESFET under  $V_{DS} = 20$  V and with  $W/L= 50 \mu m/2.5 \mu m$  at different temperatures.

Figure 3.6: Optical image of a n-channel 4H-SiC MESFET after operating at 600 °C for few minutes which shows the morphology of interconnect changes.

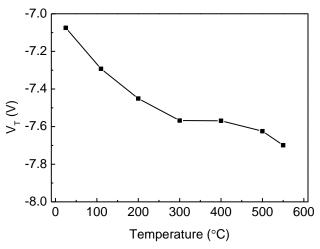

Figure 3.7 shows the extracted threshold voltage at different temperatures. The  $V_T$  is approximately shifted with the rate of -1.03 mV/ °C. The temperature dependencies of estimated transconductances based on the equation 3.2 and the intrinsic gain of the MESFET at  $V_{GS} = 0$  V are shown in Figure 3.8. The  $g_m$  at 550 °C is 3.52  $\mu$ S/ $\mu$ m, which is 31 % of its value at room temperature. The intrinsic gain of the MESFET decreases with temperature, because the output resistance is increased from  $5.22 \times 10^4$  to  $1.36 \times 10^5 \Omega$ , compensating for the effect of the reduced  $g_m$  at high temperatures. The results suggest that 4H-SiC MESFET shows promising performance for high temperature amplifier applications. The complete electrical properties of n-channel 4H-SiC MESFET are listed and summarized in Table 3.1.

Figure 3.7: Temperature dependence of threshold voltage of a n-channel 4H-SiC MESFET with  $W/L=50 \mu m/2.5 \mu m$ .

Figure 3.8: Temperature dependence of transconductance and intrinsic gain of a n-channel 4H-SiC MESFET with  $W/L=50 \ \mu m/2.5 \ \mu m$ .

| Temperature<br>(°C) | $V_T(V)$ | <sup>g</sup> m<br>(μS/μm) | $R_{on} (m\Omega \ cm^2)$ | $r_{o}\left( \Omega ight)$ | $\lambda (V^{-1})$ | $g_m r_o$ | I <sub>Dsat</sub> /I <sub>off</sub> |

|---------------------|----------|---------------------------|---------------------------|----------------------------|--------------------|-----------|-------------------------------------|

| 25                  | -7.07    | 11.36                     | 9.55                      | $5.22 \times 10^{4}$       | 0.0115             | 29.6      | $2.14 \times 10^{6}$                |

| 100                 | -7.29    | 9.76                      | 10.51                     | $5.98 \times 10^{4}$       | 0.0112             | 29.2      | 1.90×10 <sup>6</sup>                |

| 200                 | -7.45    | 7.62                      | 13.59                     | $7.16 \times 10^4$         | 0.0124             | 27.3      | 1.13×10 <sup>6</sup>                |

| 300                 | -7.57    | 5.76                      | 17.32                     | $8.72 \times 10^4$         | 0.0131             | 25.1      | 4.30×10 <sup>5</sup>                |

| 400                 | -7.57    | 4.96                      | 20.56                     | $1.05 \times 10^{5}$       | 0.0130             | 25.9      | 1.18×10 <sup>5</sup>                |

| 500                 | -7.62    | 4.03                      | 24.62                     | $1.20 \times 10^{5}$       | 0.0136             | 24.2      | $2.18 \times 10^4$                  |

| 550                 | -7.70    | 3.52                      | 28.17                     | 1.36×10 <sup>5</sup>       | 0.0137             | 23.9      | 7.23×10 <sup>3</sup>                |

Table 3.3: Extracted parameters of a n-channel 4H-SiC MESFET with  $W/L=50 \ \mu m/2.5 \ \mu m$  at various temperatures.  $g_m$ ,  $R_{on}$ ,  $r_o$ ,  $\lambda$  and  $g_m r_o$  is based on  $V_{GS} = 0$  V.  $I_{Dsat}/I_{off}$  is the ratio of current at  $V_{GS} = 0$  V to current at  $V_{GS} = -9$  V.

### **Chapter 4**

### **Conclusion and Future Work**

### **4.1 Conclusion**

This work details the fabrication process of n-channel 4H-SiC MESFET and the device performance is characterized in the temperature range 25 to 550 °C. The MESFET device is made along with the fabrication process of JFET. The threshold voltage at 25 °C is -7.07 V with a high transconductance of 11.36  $\mu$ S/ $\mu$ m and a small on-resistance of 9.55 m $\Omega$  cm<sup>2</sup>. As the temperature increases, the threshold voltage shifts with the rate of -1.03 mV/ °C. Even at 550 °C, the MESFET still exhibits a transconductance of 3.52  $\mu$ S/ $\mu$ m and an on/off drain saturation current ratio of 7.23×10<sup>3</sup>. The device shows the potential for scaling of the gate length to achieve larger bandwidth of the device while maintain the decent electrostatic characteristics at high temperature.

### 4.2 Future Work

There are several issues need to be addressed before fully understand the temperature dependencies of 4H-SiC MESFET. The Schottky barrier height of Ti/Ni/TiW/Pt metal gate should be characterized for the entire temperature range. More thermal robust metal interconnect should be explored to further extend the operating temperature to 600 °C. The RF performance of MESFET such as S-parameters and maximum frequency should also be studied.

Since MESFET reduces one step of epitaxial film deposition to form the pn junction in JFET structure. It might be worth to explore the possibility of complementary MESFET configuration by using both n-channel and p-channel MESFETs.

### References

- [1] L. L. N. Laboratory. *Energy flow*. Available: https://flowcharts.llnl.gov/

- [2] X. Gong, L. An, and C. Xu, "Wireless passive sensor development for harsh environment applications," in 2012 IEEE International Workshop on Antenna Technology (iWAT), 2012, pp. 140-143.

- [3] P. G. Neudeck, R. S. Okojie, and L.-Y. Chen, "High-temperature electronics-a role for wide bandgap semiconductors?," *Proceedings of the IEEE*, vol. 90, pp. 1065-1076, 2002.

- [4] N. A. Riza, M. Sheikh, and F. Perez, "Hybrid wireless-wired optical sensor for extreme temperature measurement in next generation energy efficient gas turbines," *Journal of Engineering for Gas Turbines & Power*, vol. 132, p. 051601, 2010.

- [5] D. G. Senesky, B. Jamshidi, K. B. Cheng, and A. P. Pisano, "Harsh environment silicon carbide sensors for health and performance monitoring of aerospace systems: A review," *IEEE Sensors Journal*, vol. 9, pp. 1472-1478, 2009.

- [6] M. Mehregany, "Advances in silicon carbide micro-and nano-electro-mechanical systems fabrication technology and applications," in 2013 Transducers & Eurosensors XXVII: The 17th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS & EUROSENSORS XXVII), 2013, pp. 2397-2402.

- [7] F. Udrea, S. Ali, M. Brezeanu, V. Dumitru, O. Buiu, I. Poenaru, M. Chowdhury, A. De Luca, and J. Gardner, "SOI sensing technologies for harsh environment," in 2012 International Semiconductor Conference (CAS), 2012, pp. 3-10.

- [8] J. Casady and R. W. Johnson, "Status of silicon carbide (SiC) as a wide-bandgap semiconductor for high-temperature applications: A review," *Solid-State Electronics*, vol. 39, pp. 1409-1422, 1996.

- [9] M. R. Werner and W. R. Fahrner, "Review on materials, microsensors, systems and devices for high-temperature and harsh-environment applications," *IEEE Transactions on Industrial Electronics*, vol. 48, pp. 249-257, 2001.

- [10] C. S. Roper, "Silicon Carbide Thin Films via Low Pressure Chemical Vapor Deposition for MEMS," Ph. D., Chemical Engineering, University of California at Berkeley, 2007.

- [11] C.-M. Zetterling, *Process technology for silicon carbide devices*: IET, 2002.

- C.-M. Lin, W.-C. Lien, V. V. Felmetsger, M. A. Hopcroft, D. G. Senesky, and A. P. Pisano, "AlN thin films grown on epitaxial 3C–SiC (100) for piezoelectric resonant devices," *Applied Physics Letters*, vol. 97, pp. 141907-141907-3, 2010.

- [13] W.-C. Lien, N. Ferralis, C. Carraro, and R. Maboudian, "Growth of epitaxial 3C-SiC films on Si (100) via low temperature SiC buffer layer," *Crystal Growth & Design*, vol. 10, pp. 36-39, 2009.

- [14] W. C. Lien, D. S. Tsai, S. H. Chiu, D. G. Senesky, R. Maboudian, A. P. Pisano, and J. H. He, "Low-Temperature, Ion Beam-Assisted SiC Thin Films With

Antireflective ZnO Nanorod Arrays for High-Temperature Photodetection," *IEEE Electron Device Letters*, vol. 32, pp. 1564-1566, Nov 2011.

- [15] W.-C. Lien, N. Ferralis, A. P. Pisano, C. Carraro, and R. Maboudian, "Tunable in situ growth of porous cubic silicon carbide thin films via methyltrichlorosilanebased chemical vapor deposition," *Applied Physics Letters*, vol. 95, pp. 101901-101901-3, 2009.

- [16] W.-C. Lien, K. B. Cheng, D. G. Senesky, C. Carraro, A. P. Pisano, and R. Maboudian, "Growth of 3C-SiC Thin Film on AlN/Si (100) with Atomically Abrupt Interface via Tailored Precursor Feeding Procedure," *Electrochemical and Solid-State Letters*, vol. 13, pp. D53-D56, 2010.

- [17] C.-M. Lin, Y.-Y. Chen, V. V. Felmetsger, W.-C. Lien, T. Riekkinen, D. G. Senesky, and A. P. Pisano, "Surface acoustic wave devices on AlN/3C–SiC/Si multilayer structures," *Journal of Micromechanics and Microengineering*, vol. 23, p. 025019, 2013.

- [18] W.-C. Lien, D.-S. Tsai, S.-H. Chiu, D. Senesky, R. Maboudian, A. Pisano, and J.-H. He, "Nanocrystalline SiC metal-semiconductor-metal photodetector with ZnO nanorod arrays for high-temperature applications," in 2011 16th International Solid-State Sensors, Actuators and Microsystems Conference (TRANSDUCERS), 2011, pp. 1875-1878.

- [19] V. Cimalla, J. Pezoldt, and O. Ambacher, "Group III nitride and SiC based MEMS and NEMS: materials properties, technology and applications," *Journal of Physics D: Applied Physics*, vol. 40, p. 6386, 2007.

- [20] E. Monroy, F. Omnes, and F. Calle, "Wide-bandgap semiconductor ultraviolet photodetectors," *Semiconductor Science and Technology*, vol. 18, pp. R33-R51, Apr 2003.

- [21] M. Mehregany, C. Zorman, S. Roy, A. Fleischman, C.-H. Wu, and N. Rajan, "Silicon carbide for microelectromechanical systems," *International materials reviews*, vol. 45, pp. 85-108, 2000.

- [22] A. R. Atwell, R. S. Okojie, K. T. Kornegay, S. L. Roberson, and A. Beliveau, "Simulation, fabrication and testing of bulk micromachined 6H-SiC high-*g* piezoresistive accelerometers," *Sensors and Actuators A: Physical*, vol. 104, pp. 11-18, 2003.

- [23] P. Godignon, "SiC materials and technologies for sensors development," in *Materials Science Forum*, 2005, pp. 1009-1014.

- [24] S. A. Bhave, D. Gao, R. Maboudian, and R. T. Howe, "Fully-differential poly-SiC Lame mode resonator and checkerboard filter," in 18th IEEE International Conference on Micro Electro Mechanical Systems (MEMS 2005), 2005, pp. 223-226.

- [25] W.-C. Lien, "Porous and Epitaxial 3C-SiC Thin Films Technology for Microelectromechanical Systems and Electronics Applications," University of California, Berkeley, 2008.

- [26] W.-C. Lien, D.-S. Tsai, D.-H. Lien, D. G. Senesky, J.-H. He, and A. P. Pisano, "4H–SiC Metal–Semiconductor–Metal Ultraviolet Photodetectors in Operation of 450 °C," 2012.

- [27] W.-C. Lien, A. P. Pisano, D.-S. Tsai, -. H. He Jr, and D. G. Senesky, "Extreme temperature 4H-SiC metal-semiconductor-metal ultraviolet photodetectors," in

2012 Proceedings of the European Solid-State Device Research Conference (ESSDERC), 2012, pp. 234-237.

- [28] D. Brown, E. Downey, M. Ghezzo, J. Kretchmer, V. Krishnamurthy, W. Hennessy, and G. Michon, "Silicon carbide MOSFET integrated circuit technology," *Physica Status Solidi A*, vol. 162, pp. 459-479, 1997.

- [29] S. Ryu, K. Kornegay, J. Cooper Jr, and M. Melloch, "Monolithic CMOS digital integrated circuits in 6H-SiC using an implanted p-well process," *IEEE Electron Device Letters*, vol. 18, pp. 194-196, 1997.

- [30] D. Clark, E. P. Ramsay, A. Murphy, D. A. Smith, R. Thompson, R. Young, J. D. Cormack, C. Zhu, S. Finney, and J. Fletcher, "High temperature silicon carbide CMOS integrated circuits," in *Materials Science Forum*, 2011, pp. 726-729.

- [31] M. Tomana, R. W. Johnson, R. C. Jaeger, and W. C. Dillard, "A hybrid silicon carbide differential amplifier for 350° C operation," *IEEE Transactions on Components, Hybrids, and Manufacturing Technology,* vol. 16, pp. 536-542, 1993.

- [32] Z. D. Schwartz and G. E. Ponchak, "High temperature performance of a SiC MESFET based oscillator," in 2005 IEEE MTT-S International Microwave Symposium Digest, 2005.

- [33] M. Alexandru, V. Banu, M. Vellvehi, P. Godignon, and J. Millán, "Design of Digital Electronics for High Temperature using Basic Logic Gates made of 4H-SiC MESFETs," in *Materials Science Forum*, 2012, pp. 104-108.

- [34] B. G. M. L. Lanni, C.-M. Zetterling, M. Ostling, "A 4H-SiC bipolar technology for high-temperature integrated circuits " in *IMAPS conference & Exhibition on High Temperature Network (HiTEN 2013)*, 2013.

- [35] S. Zappe, M. Leone, F. Yang, and E. Obermeier, "Characterisation of silicon carbide JFETs with respect to microsystems for high temperature applications," *Microsystem technologies*, vol. 3, pp. 134-138, 1997.

- [36] P. G. Neudeck, D. J. Spry, L.-Y. Chen, G. M. Beheim, R. S. Okojie, C. W. Chang, R. D. Meredith, T. L. Ferrier, L. J. Evans, and M. J. Krasowski, "Stable Electrical Operation of 6H–SiC JFETs and ICs for Thousands of Hours at 500," *IEEE Electron Device Letters*, vol. 29, pp. 456-459, 2008.

- [37] P. G. Neudeck, G. M. Beheim, and C. S. Salupo, "600 C Logic Gates Using Silicon Carbide JFET's," in 2000 Government Microcircuit Applications Conference, 2000, pp. 20-23.

- [38] J. Fraley, M. Schupbach, J. Yang, B. Western, and A. B. Lostetter, "A 450° C High Voltage Gain AC Coupled Differential Amplifier," in *Materials Science Forum*, 2012, pp. 1253-1256.

- [39] A. C. Patil, "Silicon Carbide JFET Integrated Circuit Technology For High-Temoerature Sensors," Electrical Engineering and Computer Science, Case Western Reserve University, 2009.

- [40] I. Sankin, V. Bondarenko, D. C. Sheridan, M. S. Mazzola, J. B. Casady, J. Fraley, and M. Schupbach, "SiC Lateral Trench JFET for Harsh-Environment Wireless Systems," in *Materials Science Forum*, 2009, pp. 1087-1090.

- [41] K.-A. Son, A. Liao, G. Lung, M. Gallegos, T. Hatake, R. D. Harris, L. Z. Scheick, and W. D. Smythe, "GaN-based high-temperature and radiation-hard electronics

for harsh environments," in SPIE Defense, Security, and Sensing, 2010, pp. 76790U-76790U-8.

- [42] T. Iwasaki, Y. Hoshino, K. Tsuzuki, H. Kato, T. Makino, M. Ogura, D. Takeuchi, H. Okushi, S. Yamasaki, and M. Hatano, "High-Temperature Operation of Diamond Junction Field-Effect Transistors With Lateral pn Junctions," *IEEE Electron Device Letters*, vol. 34, pp. 1175-1177, 2013.

- [43] D. Maier, M. Alomari, N. Grandjean, J.-F. Carlin, M.-A. Diforte-Poisson, C. Dua, S. Delage, and E. Kohn, "InAIN/GaN HEMTs for Operation in the 1000° C Regime: A First Experiment," *IEEE Electron Device Letters*, vol. 33, pp. 985-987, 2012.

- [44] M. E. Levinshtein, S. L. Rumyantsev, and M. S. Shur, *Properties of Advanced Semiconductor Materials: GaN, AIN, InN, BN, SiC, SiGe*: Wiley, 2001.

- [45] T. Ayalew, "SiC Semiconductor Devices Technology, Modeling, and Simulation, "Technical University of Vienna, 2004.

- [46] C. Mead, "Schottky barrier gate field effect transistor," *Proceedings of the IEEE*, vol. 54, pp. 307-308, 1966.

- [47] P. G. Neudeck, S. L. Garverick, D. J. Spry, L. Y. Chen, G. M. Beheim, M. J. Krasowski, and M. Mehregany, "Extreme temperature 6H-SiC JFET integrated circuit technology," *Physica Status Solidi A*, vol. 206, pp. 2329-2345, Oct 2009.

- [48] S. M. Sze and K. K. NG, *Physics of semiconductor devices*: Wiley, 2007.

- [49] S. L. Garverick, C.-W. Soong, and M. Mehregany, "SiC JFET integrated circuits for sensing and control at temperatures up to 600° C," in *Energytech*, 2012 IEEE, 2012, pp. 1-6.

- [50] R. F. Pierret, *Semiconductor device fundamentals*: Pearson Education India, 1996.

- [51] M. Laube, F. Schmid, G. Pensl, G. Wagner, M. Linnarsson, and M. Maier, "Electrical activation of high concentrations of N<sup>+</sup> and P<sup>+</sup> ions implanted into 4H– SiC," *Journal of Applied Physics*, vol. 92, pp. 549-554, 2002.

- [52] S.-K. Lee, C.-M. Zetterling, M. Östling, J.-P. Palmquist, and U. Jansson, "Low resistivity ohmic contacts on 4H-silicon carbide for high power and high temperature device applications," *Microelectronic Engineering*, vol. 60, pp. 261-268, 2002.

- [53] V. Lauer, E. Niemann, S. Sheppard, and W. Wondrak, "High temperature performance of implanted-gate n-channel JFETs in 6H-SiC," in *Materials Science Forum*, 1997, pp. 1077-1080.