## Design of Multi-Gb/s Multi-Coefficient Mixed-Signal Equalizers

Chintan Thakkar Elad Alon

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2014-189 http://www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-189.html

December 1, 2014

Copyright © 2014, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Design of Multi-Gb/s Multi-Coefficient Mixed-Signal Equalizers

by

Chintan S. Thakkar

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Elad Alon, Chair Professor Ali M. Niknejad Professor Andrew Packard

Fall 2012

### Design of Multi-Gb/s Multi-Coefficient Mixed-Signal Equalizers

Copyright 2012 by Chintan S. Thakkar

#### Abstract

Design of Multi-Gb/s Multi-Coefficient Mixed-Signal Equalizers

by

Chintan S. Thakkar

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Elad Alon, Chair

The explosion of personal devices that need ubiquitous connectivity is making both wireless and wireline communication experience increasingly rapid growth in data-rates. Wireless channels have been 'fortunate' to see new channels/standards being made available over the past decade to meet up to multi-Gb/s demands. One such medium is the wideband 60GHz channel. Wireless mediums, by definition however, are thwarted by multi-path reflection-based inter-symbol interference (ISI) – a problem which becomes only worse at higher speeds. For decades, equalizers have been used efficiently to mitigate such interference. However, wireless equalizers in commercial CMOS products are typically implemented in DSP along multi-level modulation schemes like OFDM, which when scaled to Gb/s speeds dissipate substantial power. This is particularly detrimental for handheld/mobile devices with limited battery capacity.

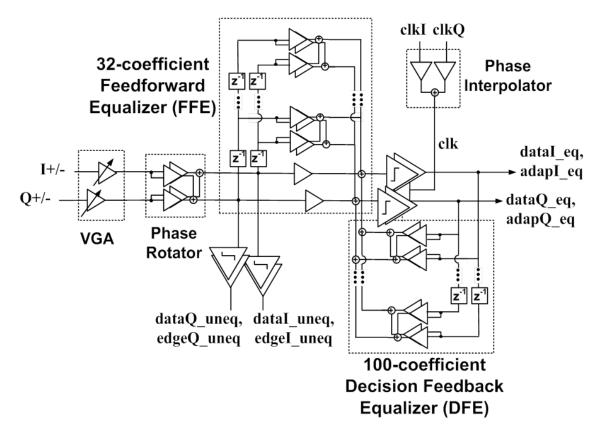

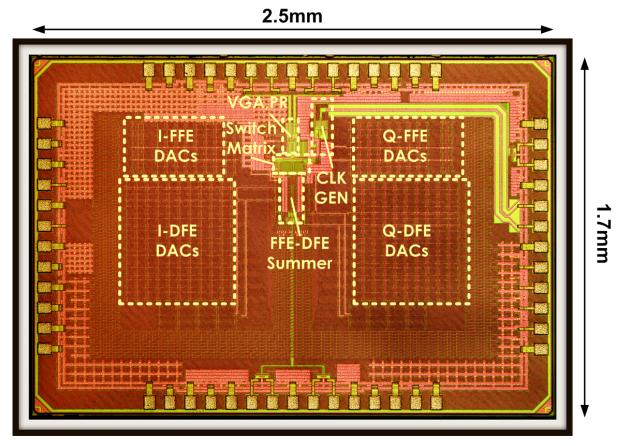

To ease the power bottleneck for equalization, this work instead proposes using mixed-signal techniques. As opposed to classic multi-level ADC/DSP design, such techniques are inspired by high-speed chip-to-chip wired communication that advocates the use of simple modulation schemes (such as QPSK) with few comparators. Since wireless channels suffer ISI with longer delay spreads than their wired counterparts, previously developed wireline equalizers cannot be directly ported. This work therefore enables energy-efficient equalizers to cancel extremely long ISI delay spreads. Our first prototype demonstrated a 40-coefficient complex (I/Q) decision feedback equalizer (DFE) in 65nm CMOS to enable 10Gb/s rates over line-of-sight (LOS) 60GHz channels, while consuming only 14mW of power. The second prototype in 65nm low-power (LP) CMOS enables non-line-of-sight (NLOS) channel equalization as well, by using a 32-coefficient receiver feedforward equalizer (FFE) and a longer 100-coefficient DFE, achieving 3.5-8Gb/s rates while consuming 20-67mW.

While the equalizer prototypes in this dissertation have been targeted towards 60GHz channels, the techniques enable energy-efficient equalization for long ISI delay spreads for any high-speed wireless or wireline communication link.

To my Parents and Grandparents

For making me worthy of writing this.

## Contents

| Contents      |                        |        |                                                                         |      |  |

|---------------|------------------------|--------|-------------------------------------------------------------------------|------|--|

| $\mathbf{Li}$ | $\mathbf{st}$ of       | Figur  | es                                                                      | iv   |  |

| $\mathbf{Li}$ | $\operatorname{st}$ of | Table  | ${f s}$                                                                 | viii |  |

| 1             | Intr                   | oduct  | ion                                                                     | 1    |  |

|               | 1.1                    | 60GH   | z Wireless: A Demonstration Platform for Multi-Coefficient Equalization | on 2 |  |

|               | 1.2                    | Mixed  | l-Signal Time-Domain Equalizers                                         | 6    |  |

|               |                        | 1.2.1  | Decision Feedback Equalizer                                             | 7    |  |

|               |                        | 1.2.2  | Feedforward Equalizer                                                   |      |  |

|               | 1.3                    | Chan   | nel Models for 60GHz Wireless                                           | 9    |  |

|               | 1.4                    | Organ  | nization of Dissertation                                                | 12   |  |

| 2             | DF                     | E Desi | ign using Cascode Current-Summing                                       | 14   |  |

|               | 2.1                    | Conve  | entional Current Summing DFE Architecture                               | 14   |  |

|               | 2.2                    | Propo  | osed Cascode Current-Summing DFE                                        | 19   |  |

|               |                        | 2.2.1  | Concept                                                                 | 19   |  |

|               |                        | 2.2.2  | Analysis                                                                | 20   |  |

|               | 2.3                    | 40-co€ | efficient, 10Gb/s Cascode-Summing DFE Prototype                         | 25   |  |

|               |                        | 2.3.1  | Key Design Issues                                                       | 25   |  |

|               |                        |        | 2.3.1.1 Coefficient-DAC Resolution                                      | 25   |  |

|               |                        |        | 2.3.1.2 Effect of Dithering on DAC Resolution                           |      |  |

|               |                        |        | 2.3.1.3 IIR Effects                                                     | 27   |  |

|               |                        | 2.3.2  | Key Circuit Blocks                                                      | 28   |  |

|               |                        |        | 2.3.2.1 High-Speed Timing Paths                                         | 28   |  |

|               |                        |        | 2.3.2.2 Low-Swing Drivers                                               | 29   |  |

|               |                        | 2.3.3  | Simulations, Test-Chip and Measurements                                 | 30   |  |

|               | 2.4                    | Concl  | usion                                                                   | 34   |  |

| 3             | Alte                   | ernate | DFE Summation Architectures                                             | 36   |  |

| -             |                        |        | testures                                                                | 26   |  |

|              | 3.1.1 Current Integration on a Capacitive Load |                                                          |                            |  |  |  |  |  |

|--------------|------------------------------------------------|----------------------------------------------------------|----------------------------|--|--|--|--|--|

|              | 3.2                                            | 3.2.1 Current Integration on a Capacitive Load           | 39<br>39<br>46<br>50       |  |  |  |  |  |

|              | 3.3                                            | Conclusion                                               | 50                         |  |  |  |  |  |

| 4            | Rec                                            | eive-side Feedforward Equalizer (RX-FFE) Design          | 53                         |  |  |  |  |  |

|              | 4.1                                            | Prior Art                                                | 54<br>55<br>56             |  |  |  |  |  |

|              | 4.2                                            | Proposed Switching-Matrix-Based FFE                      | 58<br>59<br>65             |  |  |  |  |  |

|              | 4.3                                            | Key Circuit Blocks4.3.1 FFE Weight Design4.3.2 Input S/H | 68<br>68<br>70             |  |  |  |  |  |

|              | 4.4                                            | 4.3.3 CLK Design                                         | 71<br>73                   |  |  |  |  |  |

| 5            |                                                | Coefficient FFE, 100-Coefficient DFE Prototype           | 74                         |  |  |  |  |  |

|              | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>  | FFE-DFE Summer Circuit Design                            | 74<br>74<br>78<br>80<br>85 |  |  |  |  |  |

| 6            | Con                                            | clusion                                                  | 88                         |  |  |  |  |  |

| Bi           | bliog                                          | raphy                                                    | 91                         |  |  |  |  |  |

| $\mathbf{A}$ | Ana                                            | lysis of Switched Capacitor-Based DFE                    | 97                         |  |  |  |  |  |

| В            | Ana                                            | lysis of FFE Switching Matrix                            | 104                        |  |  |  |  |  |

| $\mathbf{C}$ | Ana                                            | lysis of Combined FFE-DFE Summer                         | 110                        |  |  |  |  |  |

## List of Figures

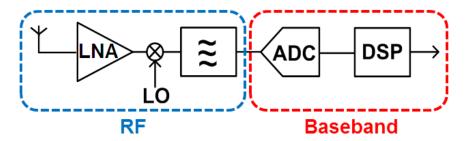

| 1.1  | Typical implementation of a wireless receiver                                                              | 3  |

|------|------------------------------------------------------------------------------------------------------------|----|

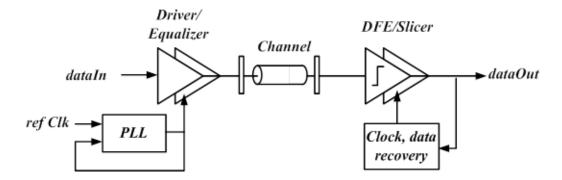

| 1.2  | Typical implementation of a high-speed wireline transceiver                                                | 4  |

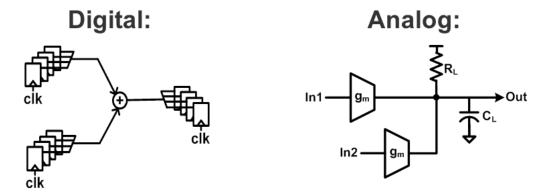

| 1.3  | Comparison between digital and analog processing: Digital processing typically                             |    |

|      | uses more transistor width (and hence more capacitance) per operation and con-                             |    |

|      | sumes more power                                                                                           | 5  |

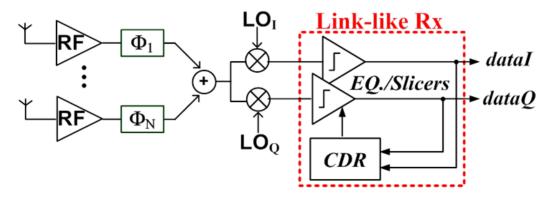

| 1.4  | 60GHz receiver with mixed-signal baseband                                                                  | 5  |

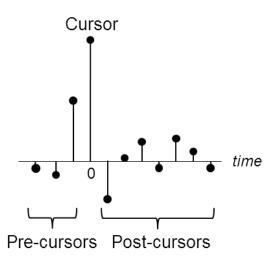

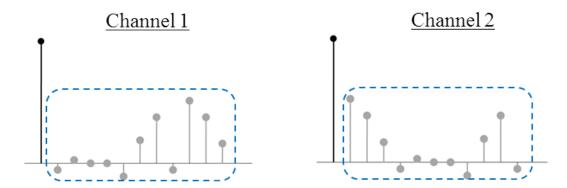

| 1.5  | Channel impulse response                                                                                   | 6  |

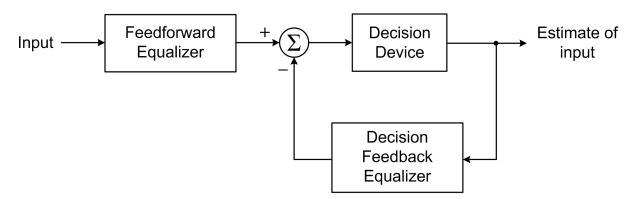

| 1.6  | Block diagram of feedforward and decision feedback equalization [29]                                       | 6  |

| 1.7  | Block diagram of a decision feedback equalizer (DFE) (left); Conventional mixed-                           |    |

|      | signal implementation using resistively-loaded summing of current-steering DACs                            |    |

|      | representing ISI weights (right)                                                                           | 7  |

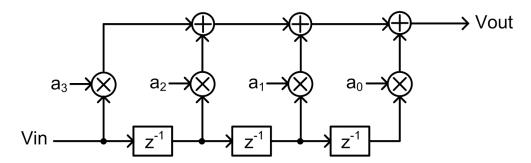

| 1.8  | FFE Block Diagram                                                                                          | 8  |

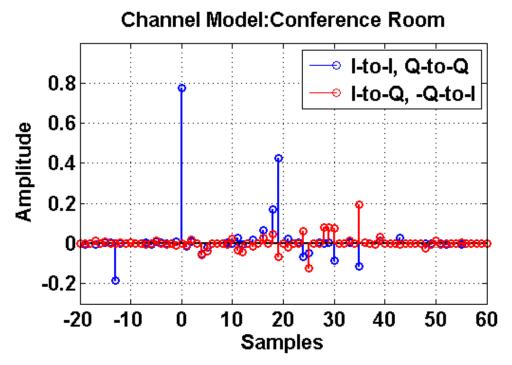

| 1.9  | 60GHz NLOS channel model of conference room using model from [32]. Data-rate:                              |    |

|      | 4GS/s, TX-RX distance: 3m, TX, RX antenna half-power beamwidth (HPBW):                                     |    |

|      | $70^{\circ}$                                                                                               | 10 |

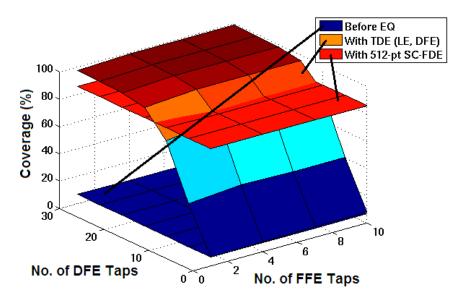

| 1.10 | Time-domain equalizer coverage (percentage of channels equalized to BER $< 10^{-3}$ )                      |    |

|      | vs. 512-pt FFT-based SC-FDE for LOS living-room channel model[34]). Data-                                  |    |

|      | rate: 1.76GS/s, TX-RX distance: 3m, TX, RX antenna HPBW: 30°                                               | 11 |

| 1.11 | Time-domain equalizer coverage (percentage of channels equalized to BER $< 10^{-3}$ )                      |    |

|      | vs. 512-pt FFT-based SC-FDE for NLOS conference-room[32]). Data-rate: 1.76GS/s                             |    |

|      | TX-RX distance: 3m, TX, RX antenna HPBW: 70°                                                               | 12 |

| 2.1  | Gain/bandwidth analysis of a conventional resistively-loaded current-summing                               |    |

|      | DFE. (a) Schematics (feedback shift register not shown) and (b) Single-ended                               |    |

|      | small-signal model                                                                                         | 15 |

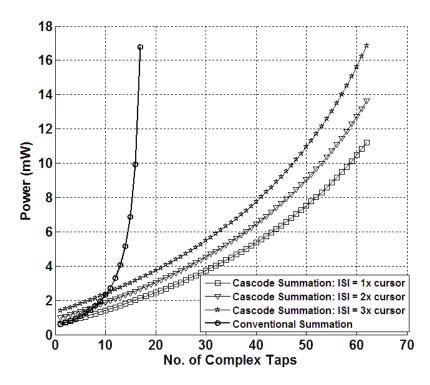

| 2.2  | Conventional current-summing DFE power vs. no. of coefficients at 5GS/s, with                              |    |

|      | $k_{max} = 0.5 \text{ in } 65 \text{nm CMOS}. \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 18 |

| 2.3  | Wireless channel response: While each tap can have a variable weight, not all                              |    |

|      | taps will be at their maximum weight altogether. However, the sum of all tap                               |    |

|      | magnitudes is bounded due to finite transmit power                                                         | 19 |

|      |                                                                                                            |    |

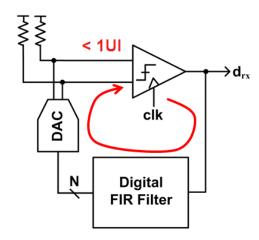

| 2.4        | A fully digital FIR/DAC implementation of the DFE limits the self-loading at the summing node. However, the 1UI latency constraint on the first tap feedback |          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | makes the FIR adder unacceptably expensive in power                                                                                                          | 20       |

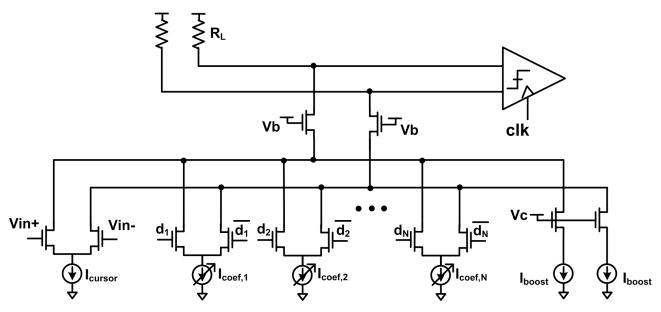

| 2.5        | Cascode current summing structure: Tap switches moved to low-impedance cas-                                                                                  |          |

|            | code, and capacitive load at output node reduced                                                                                                             | 21       |

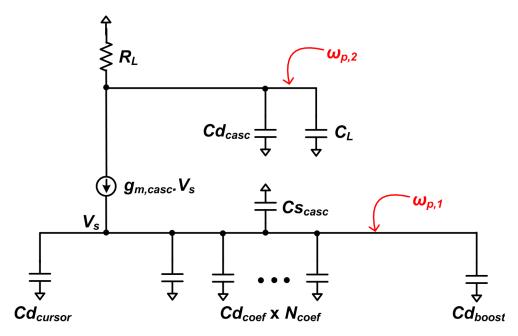

| 2.6        | Small-signal model of a cascode current-summing DFE                                                                                                          | 22       |

| 2.7        | Summing amplifier power vs. no. of complex taps for conventional and cascode-summing structures (10Gb/s QPSK)                                                | 24       |

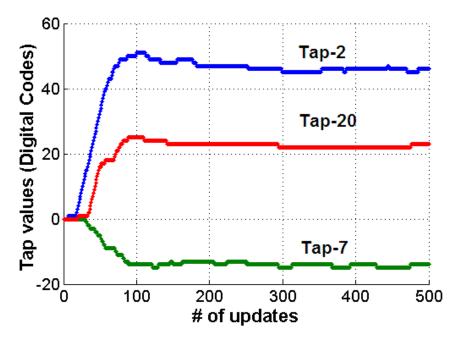

| 2.8        | DFE tap value adaptation and steady-state dithering for I-to-I taps 2, 7, and 20                                                                             | 26       |

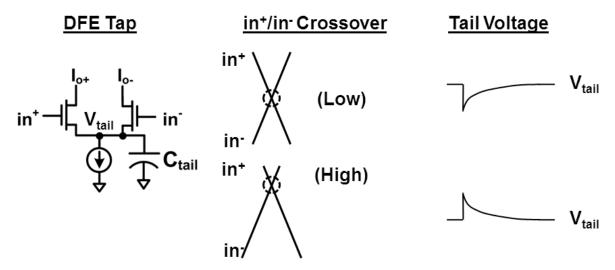

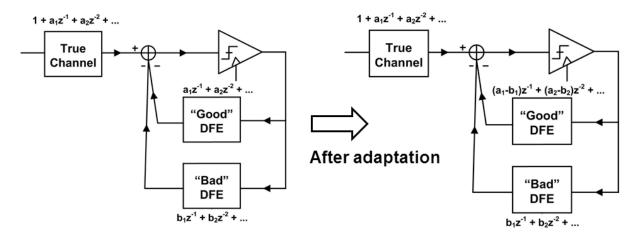

| 2.9        | Infinite impulse response (IIR) effects due to tap switching. The crossover points                                                                           | 27       |

| 0.10       | of in+/in- are exaggerated to highlight the imbalance in voltage                                                                                             |          |

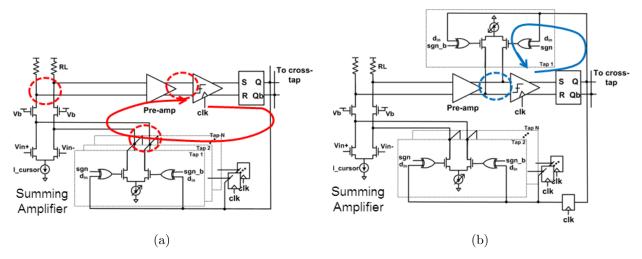

|            | Modeling IIR effects: (left) before and (right) after correction by adaptation Low-swing drivers with embedded XOR for current steering switches             | 28<br>30 |

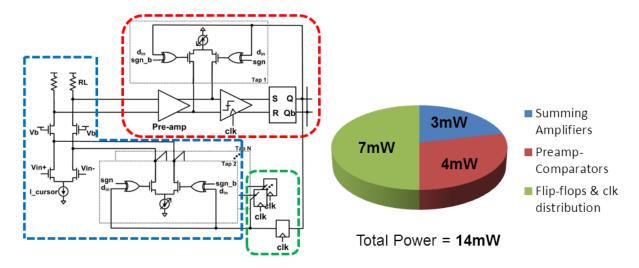

|            | 20-complex-tap cascode current-summing DFE prototype                                                                                                         | 31       |

|            | Cascode-summation DFE power breakdown at 10Gb/s operation                                                                                                    | 32       |

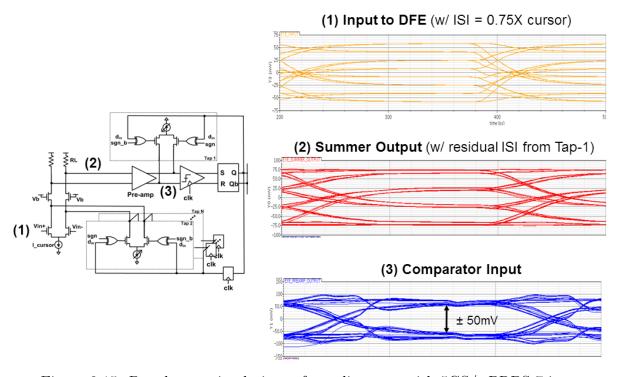

|            | Post-layout simulations of eye diagrams with 5GS/s PRBS-7 input                                                                                              | 32       |

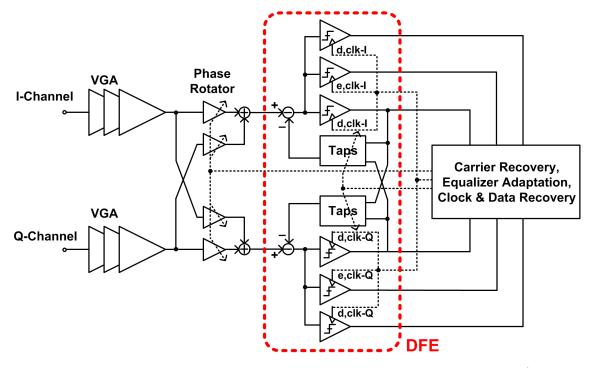

|            | Block diagram of 60GHz baseband test-chip with prototype I/Q DFE                                                                                             | 33       |

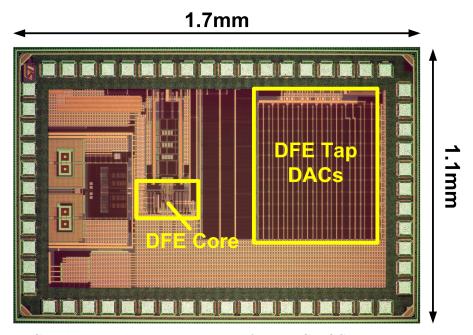

|            | 60GHz baseband die micrograph of 65nm CMOS prototype, with DFE overlaid.                                                                                     | 33       |

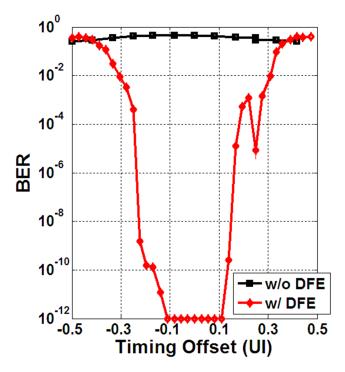

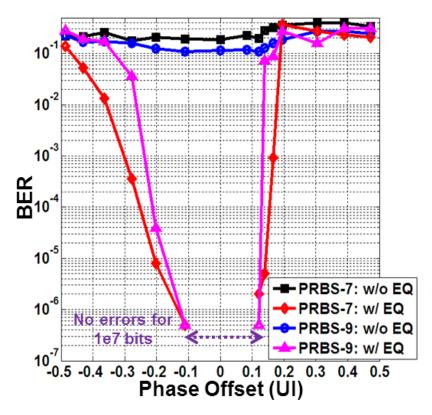

|            | BER vs. timing offset (UI) with and without the DFE turned on                                                                                                | 34       |

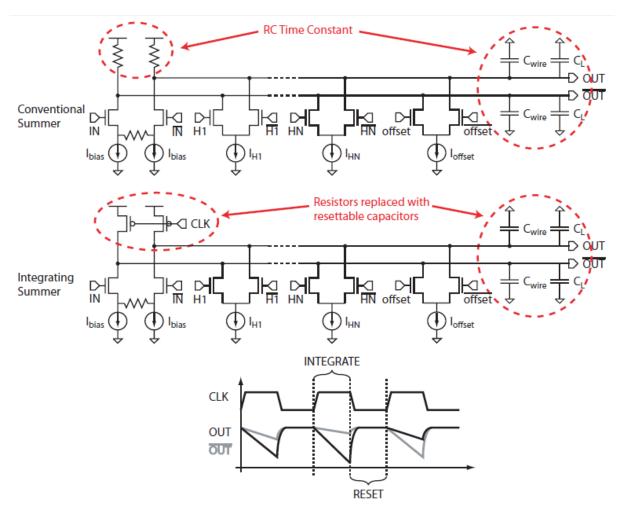

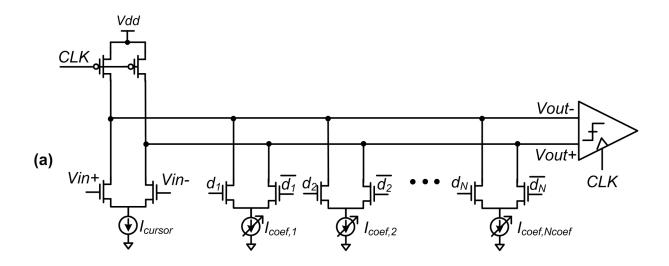

| 3.1        | A 2-tap current-integrating DFE and its comparison with a conventional resis-                                                                                |          |

| 3.2        | tively loaded DFE [50]                                                                                                                                       | 37       |

| 3.3        | (c) Equivalent circuit in the equalization phase                                                                                                             | 38       |

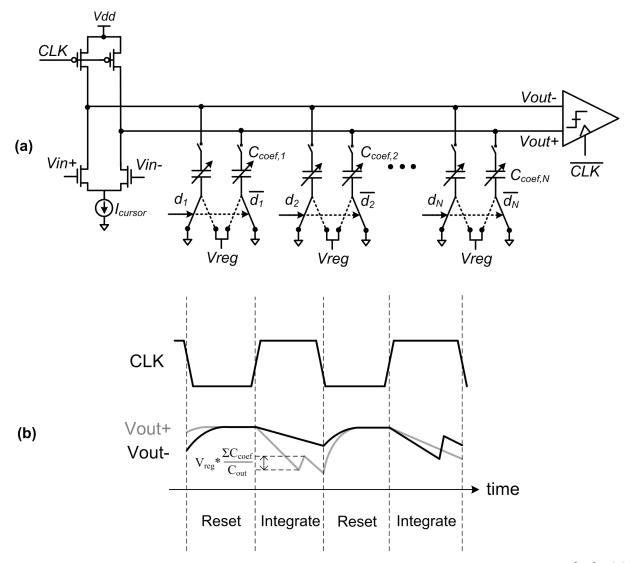

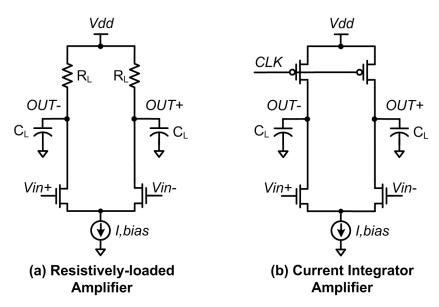

|            | Schematics. (b) Clocking and waveforms                                                                                                                       | 40       |

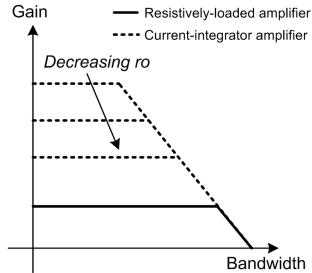

| 3.4        | Resistively-loaded and current-integrating amplifiers                                                                                                        | 41       |

| 3.5        | Resistively-loaded and current-integrating amplifiers: Gain vs. Bandwidth. For equal current consumption, current integration provides higher DC gain        | 41       |

| 3.6        | Gain/bandwidth analysis of a current-integrating DFE [50]. (a) Circuit (top) and                                                                             | 4.0      |

| a <b>-</b> | (b) Single-ended small-signal model (bottom)                                                                                                                 | 42       |

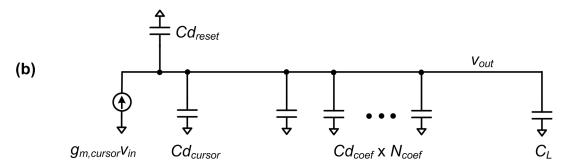

| 3.7        | Current integrating vs. resistively loaded current-summing DFE summer power                                                                                  |          |

|            | vs. no. of complex taps at 5GS/s for $k_{max} = 0.5$ in a 65 nm CMOS technology.                                                                             | 4.       |

| 2.0        | (1 complex tap = 2 I/Q coefficients)                                                                                                                         | 45       |

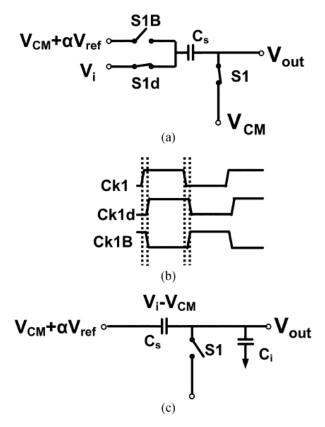

| 3.8        | Schematics of switched-capacitor feedback-based current-integrating DFE [52] .                                                                               | 46       |

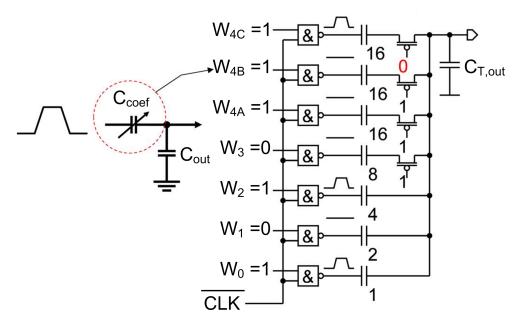

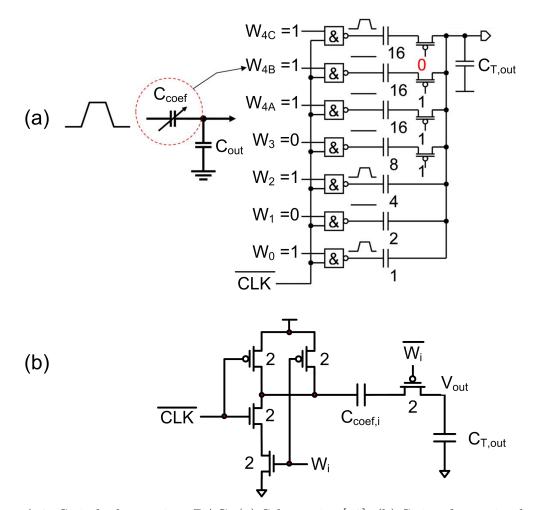

| 3.9        | Schematics of switched capacitor DAC [52]                                                                                                                    | 47       |

| 3.10       | ı , , , , , , , , , , , , , , , , , , ,                                                                                                                      |          |

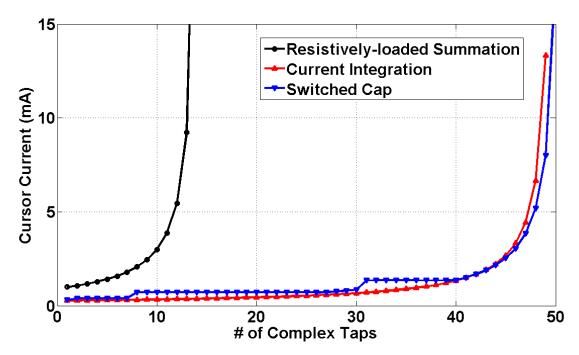

|            | DFE: Summer cursor current vs. no. of complex taps at 5GS/s for $k_{max} = 0.5$ ,                                                                            |          |

|            | using a 65nm CMOS technology. (1 complex tap = $2 \text{ I/Q}$ coefficients)                                                                                 | 49       |

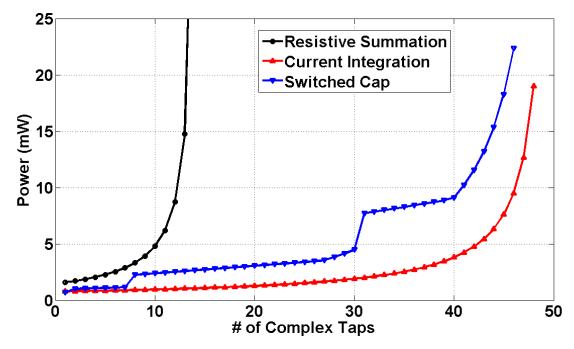

| 3.11       | Switched capacitor, current-integrating, and resistively loaded current-summing                                                                              |          |

|            | DFE: Summer power vs. no. of complex taps at 5GS/s for $k_{max} = 0.5$ , using a                                                                             |          |

|            | 65nm CMOS technology. (1 complex tap = $2 \text{ I/Q}$ coefficients)                                                                                         | 50       |

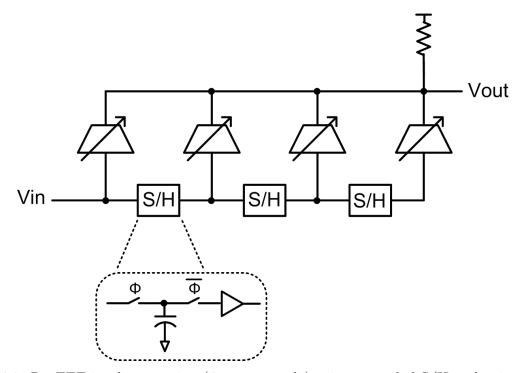

| 4.1         | FFE Block Diagram                                                                                                   | 54           |

|-------------|---------------------------------------------------------------------------------------------------------------------|--------------|

| 4.2         | Rx-FFE implementation (4-tap example) using cascaded S/H and gain compen-                                           |              |

|             | sation                                                                                                              | 54           |

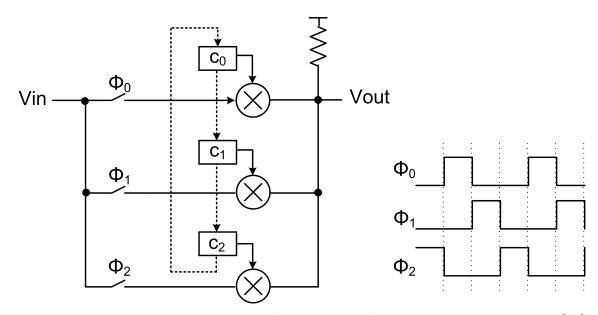

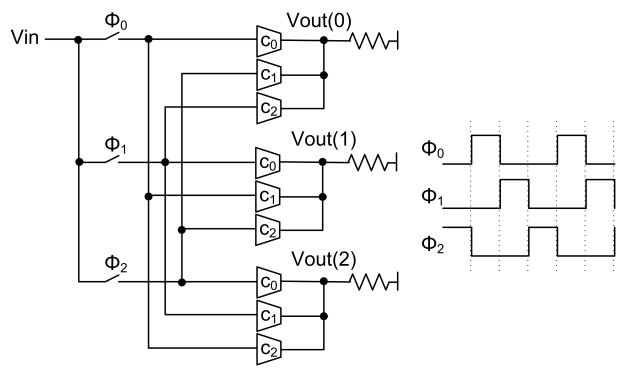

| 4.3         | Rx-FFE implementation (3-tap example) using rotating coefficients [39]                                              | 55           |

| 4.4         |                                                                                                                     | 56           |

| 4.5         | Rx-FFE implementation (3-tap example) using interleaving [40]                                                       | 57           |

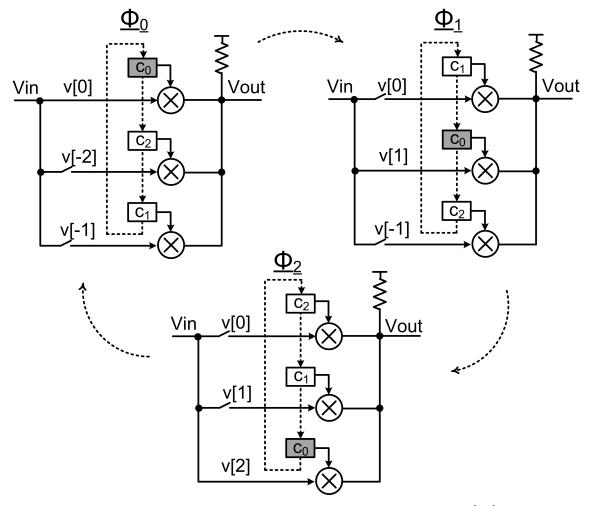

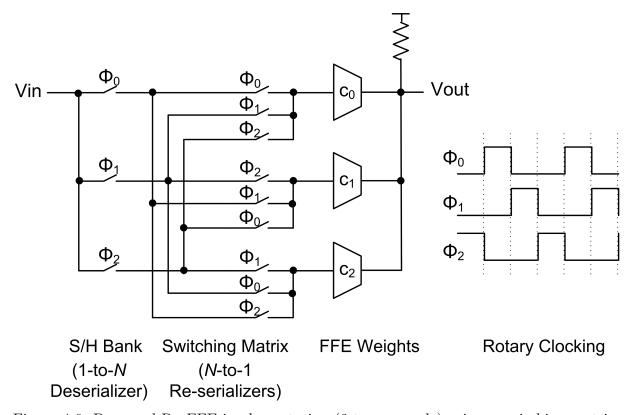

| 4.6         | Proposed Rx-FFE implementation (3-tap example) using a switching matrix                                             | 58           |

| 4.7         | Phase-wise working of the switching matrix (3-tap example)                                                          | 56           |

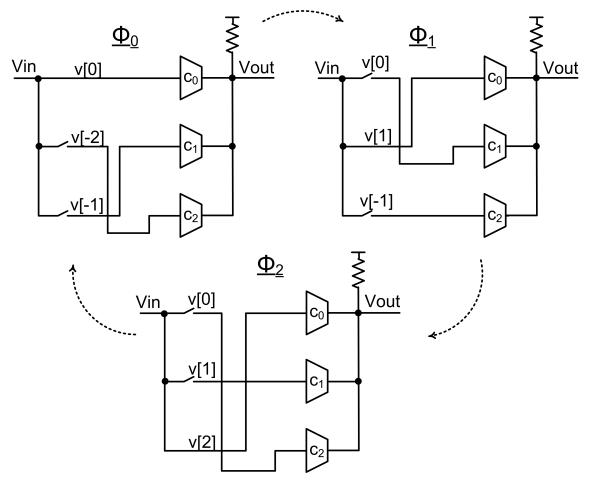

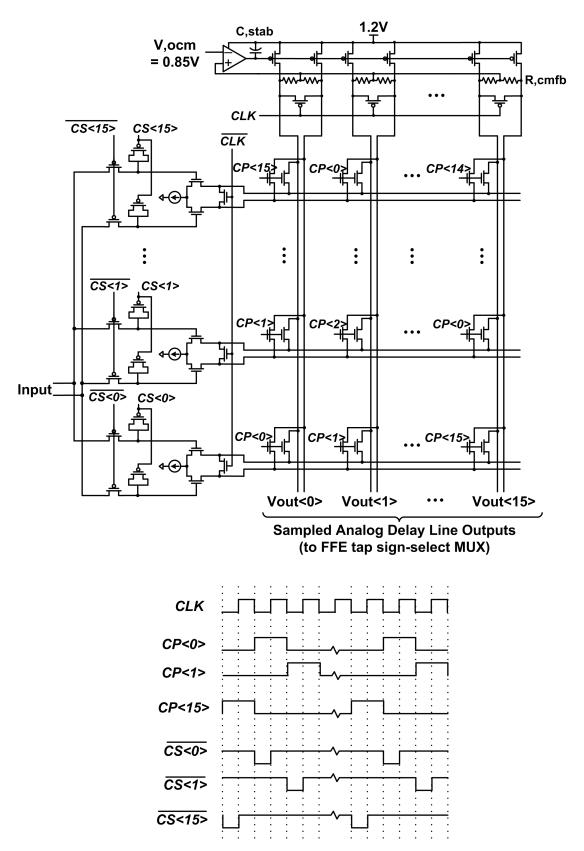

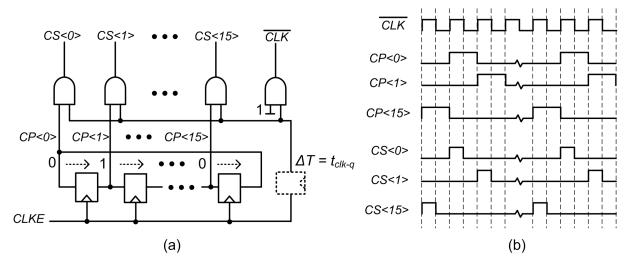

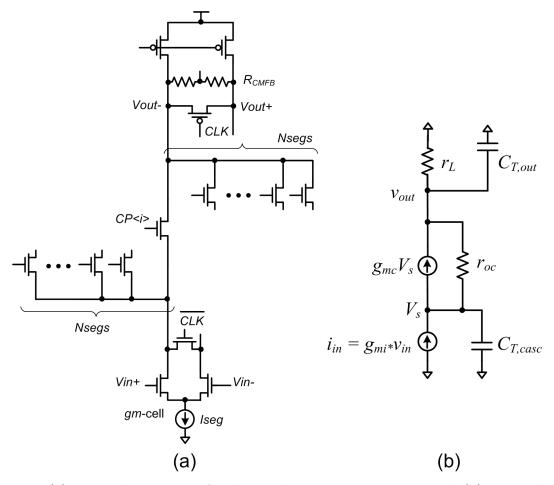

| 4.8         | Schematics of prototype 16-element switching matrix and associated clocking waveforms.                              | 60           |

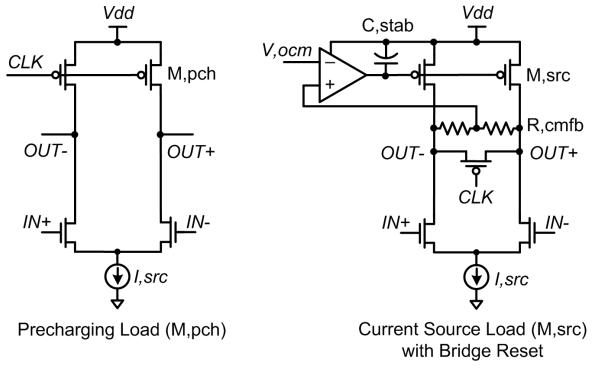

| 4.9         | Typical current integration with a precharging PMOS load [50] (left); current                                       | J            |

| 4.9         |                                                                                                                     | 61           |

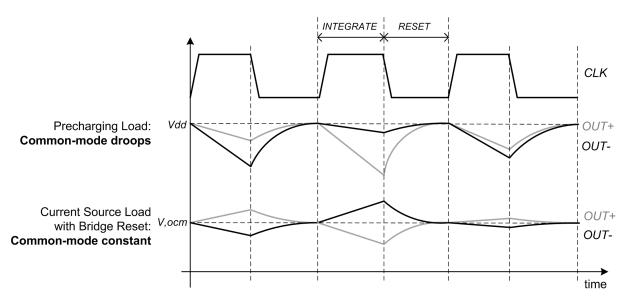

| <i>1</i> 10 | , 9                                                                                                                 | ) ]          |

| 4.10        | Current integrating waveforms with precharging PMOS load [50], and current source load with bridge reset (proposed) | 61           |

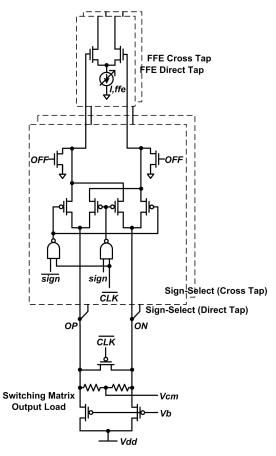

| 4.11        | Sample/hold from switching matrix output to FFE tap, with built-in sign-select                                      |              |

|             | and turn-off capability                                                                                             | 38           |

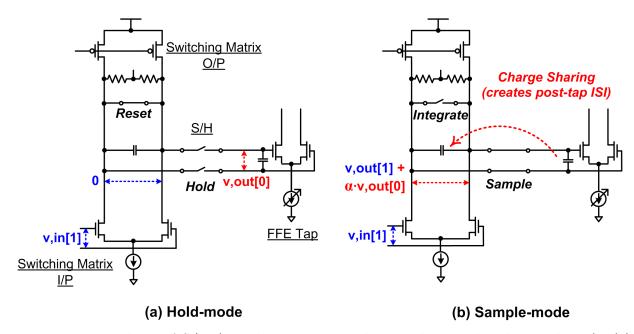

| 4.12        | Working of S/H (switching matrix and sign-selection details not shown): (a) Hold-                                   |              |

|             | mode: Switching matrix resets, tap input holds; (b) Sample-mode: Switching                                          |              |

|             | matrix integrates, tap input samples                                                                                | 64           |

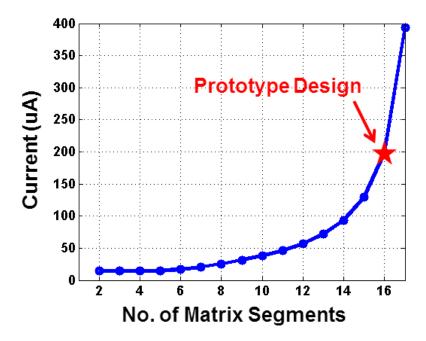

| 4.13        | Switching matrix current per segment $(I_{seg})$ vs. No. of FFE Taps, for $f_s = 5$ GS/s,                           |              |

|             |                                                                                                                     | 65           |

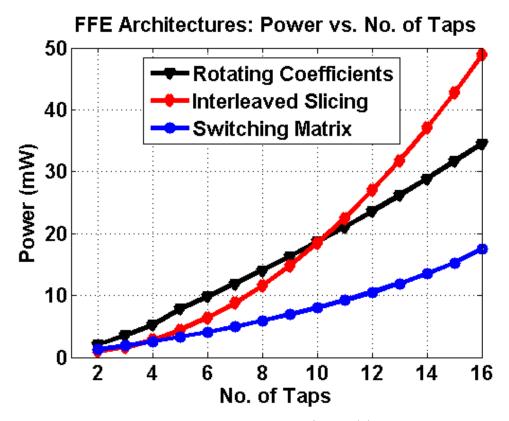

| 4.14        | Power vs. No. of FFE Taps at 5GS/s for (a) rotating coefficients [39], (b) inter-                                   |              |

|             | leaved slicing [40], (c) switching matrix (this work). Note: Power consumption                                      |              |

|             | includes the analog buffer driver, FFE analog delay implementation, FFE-DFE                                         |              |

|             | summer/slicers (DFE tap power excluded) and clocking. Power consumption is                                          |              |

|             | <b>0</b> /                                                                                                          | 67           |

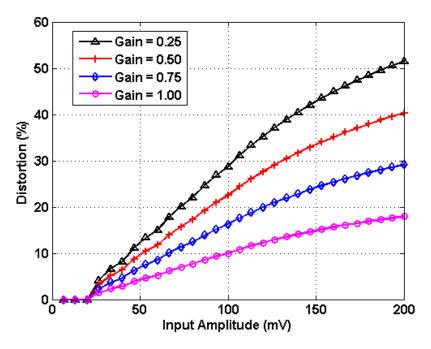

| 4.15        | Simulated FFE tap distortion vs. input amplitude, across different tap gain                                         |              |

|             |                                                                                                                     | 36           |

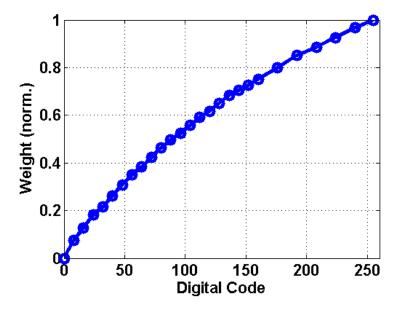

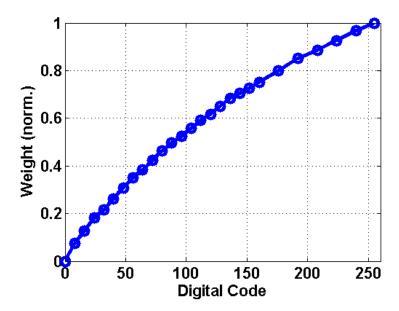

| 4.16        | FFE: Measured coefficient weight (full-scale normalized to 1) vs. digital code                                      |              |

| 4 1 🗖       |                                                                                                                     | 66           |

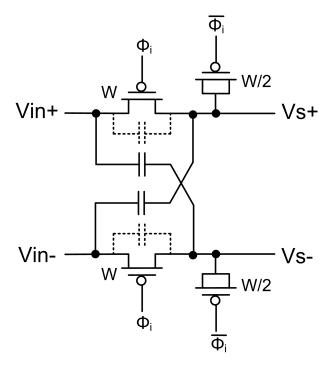

| 4.17        | S/H circuitry with feedthrough cancelation (intrinsic inter-finger capacitors are                                   | <b>-</b>     |

| 4.10        | ,                                                                                                                   | 70           |

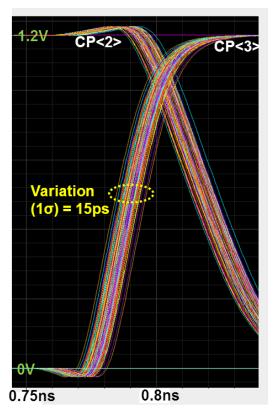

|             |                                                                                                                     | 7]<br>70     |

| 4.19        | Monte-Carlo simulation of post-layout extracted $CP\langle 2\rangle$ , $CP\langle 3\rangle$ at 5GS/s                | 72           |

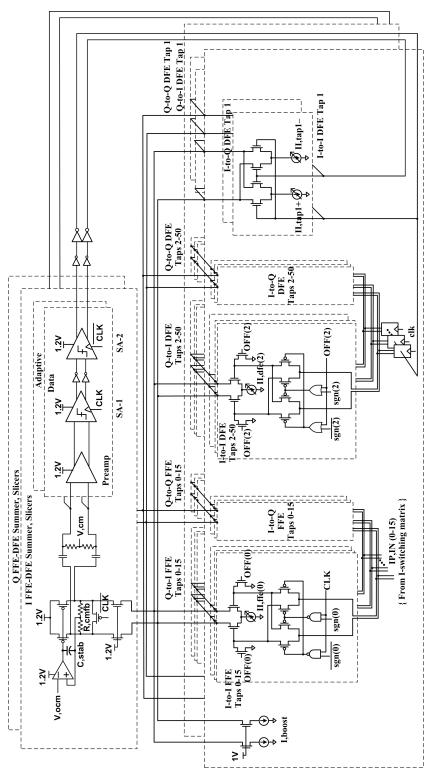

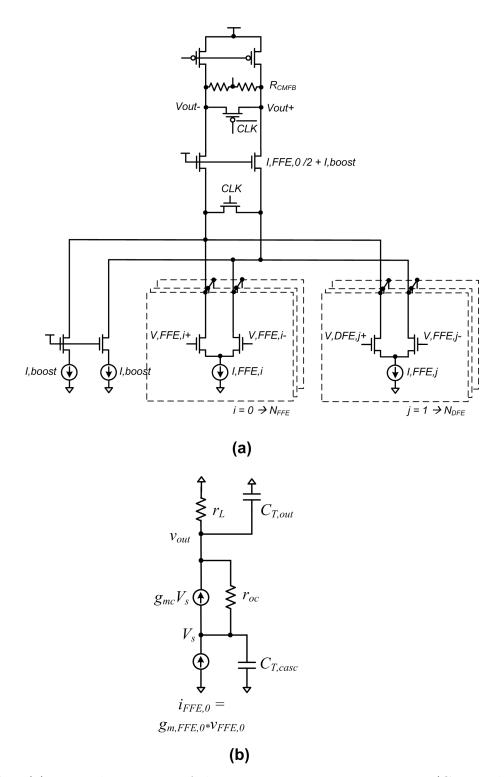

| 5.1         | Detailed schematics of the I/Q 32-coefficient FFE, 100-coefficient DFE summer-                                      |              |

|             |                                                                                                                     | 75           |

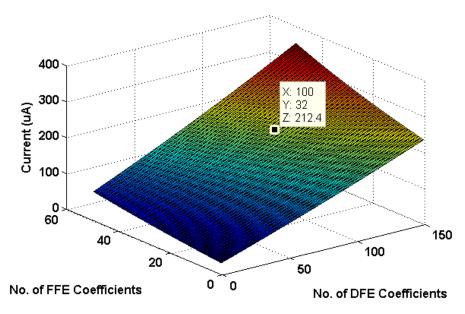

| 5.2         | FFE-DFE Summer: FFE cursor current $(I_{FFE,0})$ vs. No. of FFE, DFE Coeffi-                                        |              |

|             | cients, for $f_s = 5$ GS/s, $G = 1$ , $V^* = 200mV$ , $C_L = 10fF$ , $C_{f,FFE} = C_{f,DFE} = 16F$ .                | <b>-</b> , / |

| <b>-</b> 0  | •                                                                                                                   | 7(           |

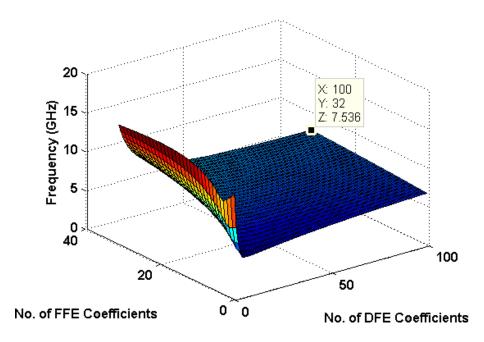

| 5.3         | FFE-DFE Summer: Obtained integrator pole frequency vs. No. of FFE, DFE                                              | _,_          |

|             | Coefficients.                                                                                                       | 77           |

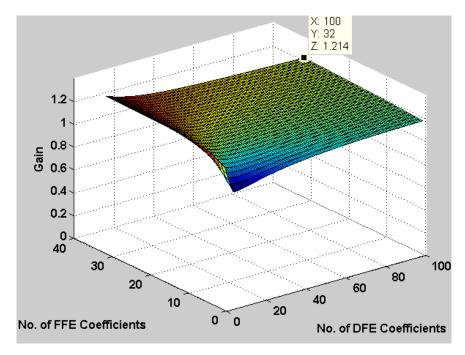

| 5.4  | FFE-DFE Summer: Obtained gain vs. No. of FFE, DFE Coefficients. Targeted gain=1                                                                                                                                        | 77  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

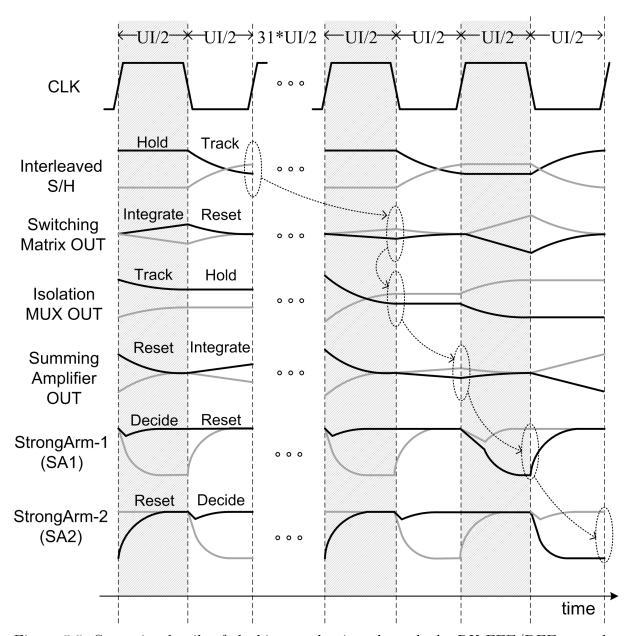

| 5.5  | Step-wise details of clocking mechanism through the RX FFE/DFE cascade                                                                                                                                                 | 79  |

| 5.6  | Block diagram of prototype NLOS 60GHz baseband receiver with 32-coefficient complex FFE and 100-coefficient DFE. The baseband also includes variable gain amplifiers, phase rotator, and phase interpolation circuitry | 80  |

| 5.7  | Die microphotograph overlaid with key design blocks                                                                                                                                                                    | 81  |

| 5.8  | FFE: Measured coefficient weight (full-scale normalized to 1) vs. digital code                                                                                                                                         | -   |

|      | setting.                                                                                                                                                                                                               | 82  |

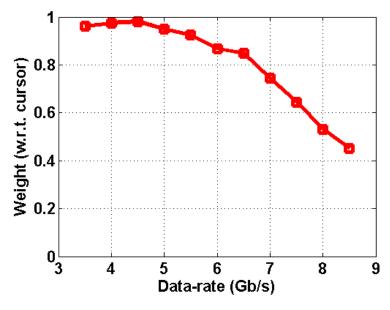

| 5.9  | DFE: Measured weight of 1st coefficient vs. data-rate                                                                                                                                                                  | 82  |

| 5.10 | Bathtub curve: BER vs. CLK phase (UI) offset, with 8Gb/s effective throughput from PRBS-7 and PRBS-9 on I and Q channels, canceling total ISI of 2X cursor                                                             |     |

|      | strength                                                                                                                                                                                                               | 83  |

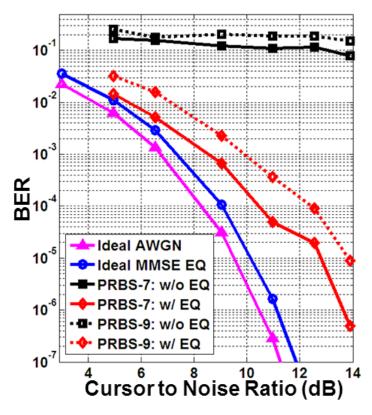

| 5.11 | Measured BER vs. SNR (cursor to thermal noise ratio), and comparison with an ideal AWGN RX and an ideal MMSE equalizer                                                                                                 | 84  |

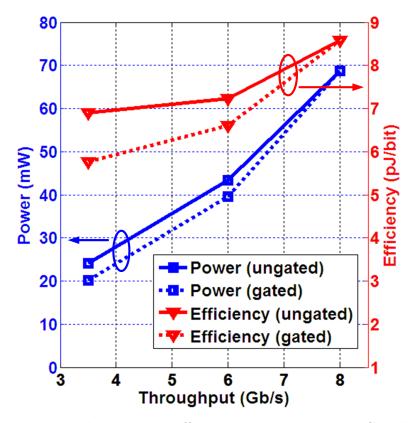

| 5.12 | Total measured power and efficiency vs. throughput. 'Gated' refers to power gating the latter DFE flip-flops at lower data-rates for equal ISI delay-spread                                                            | 85  |

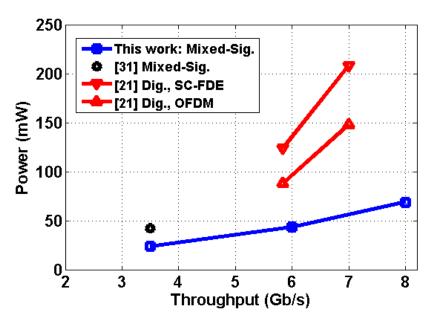

| 5.13 | Measured power vs. throughput, and comparison with prior art                                                                                                                                                           | 86  |

| A.1  | Gain/bandwidth analysis of a switched-capacitor feedback-based current-integrating DFE [52]. (a) Circuit (top) and (b) Single-ended small-signal model (bottom) .                                                      | 98  |

| A.2  | Switched capacitor DAC: (a) Schematics [52], (b) Sizing for optimal delay                                                                                                                                              | 99  |

| B.1  | (a) Equivalent circuit of each switching-matrix segment, and (b) its small signal model. For simplicity, the cascode switches are drawn as single-ended, and CMFB details have been excluded                           | 105 |

| C.1  | (a) Equivalent circuit of the FFE-DFE summer-integrator (CMFB details excluded), and (b) its simplified small signal model                                                                                             | 11  |

## List of Tables

| 4.1 | Comparison of FFE Architectures. |             |      |  | <br> | <br> | • | <br>• | • | 66 |

|-----|----------------------------------|-------------|------|--|------|------|---|-------|---|----|

| 5.1 | Comparison with prior 60GHz NLOS | S equalizer | art. |  | <br> | <br> |   | <br>  |   | 86 |

#### Acknowledgments

Over the last five and half years of doctoral research, I've lost count of the number of times I must have written this page in my head. For being able to reach here, I wish to wholeheartedly thank ...

- ... my research adviser, Prof. Elad Alon for his pool of infinite energy and enthusiasm, relentless attack of integrated circuit problems (and beyond), meticulous hands-on tutorship of circuit design, presentation and writing skills, enabling the exposure to industry, the 3AM phone calls in a nutshell, for being the most super-human mentor possible.

- ... my qualifying examination and dissertation commmittee members Prof. Ali Niknejad for his creative feedback and letters of recommendation, Prof. Jan Rabaey for his solid encouragement, and Prof. Andrew Packard, among other things, for the red-eye flight to Chicago (to be with his ailing father) and back a day before making it to my qualifying examination.

- ... the Berkeley Wireless Research Center (BWRC) as an outstanding environment for infrastructure, collaboration and creativity.

- ... BWRC sponsors and member companies, especially UC Discovery, Panasonic, Nokia, and Qualcomm for funding our research, and NSF Infrastructure Grant No. 0403427 for creating BWRC in brick and mortar.

- ... Brian Richards for wearing numerous hats in technical support, and being the go-to person for anything CAD under the sun.

- ... Susan Mellers and Fred Burghardt for the unenviable task of managing an enviable arsenal of equipment in the BWRC lab.

- ... Leslie Nishiyama and Olivia Nolan for imparting a charming spunk to BWRC.

- ... Tom Boot for his exceptional warmth.

- ... all other BWRC executives and staff, especially Gary Kelson, Ken Tang, Kevin Zimmerman, Pierce Chua, and Ubirata Chaves Coelho.

- ... Intel Corporation for their generous Ph.D. Fellowship.

- ... my managers during internships in industry Ken Chang (Rambus Inc.), Bryan Casper and Christopher D. Hull (Intel Corp.) for giving me opportunities to work in the 'real' world of semiconductors.

- ... my mentors and colleagues in industry Hae-Chang Lee, Ting Wu, Brian Leibowitz (Rambus Inc.), and Randy Mooney, Farhana Sheikh, Frank O'Mahony, James Jaussi, Sudip Shekhar, Glenn Murata, Jay Wang, and Jerome Carmon (Intel Corp.).

- ... Vinayak Nagpal and Bhavna Kapoor for their warmth, hospitality and recreational inspiration, and Animesh Kumar for his invaluable friendship.

- ... Debopriyo Chowdhury and Cristian Marcu for their leadership and patiently answering all my questions during the formative years.

- ... Lingkai Kong for all his pace-setting help throughout the course of this dissertation (especially with the first 60GHz transceiver and baseband projects), and for sharing 5+ years of technical humor across the cubicle.

- ... my other tapeout partners, Abhinav Gupta, Antoine Frappé, Kwangmo Jung, and Nathan Narevsky for all their hard yet patient work through long days (and nights).

- ... my undergraduate helpers/enablers, especially Andrew Ma, Chenchen Zheng and Emen Baghoomian.

- ... all other fellow group members, especially Hanh-Phuc Le, John Crossley, Yue Lu, Yida Duan, Matthew Spencer, George Cramer, and Artemy Baxansky, for all the technical (and extra-technical) discussions.

- ... fellow and senior students at BWRC, especially Rikky Muller, Jiashu Chen, Simone Gambini, Amin Arbabian, Maryam Tabesh, Jun-Chau Chien, and Louis Alarcon.

- ... Siddharth Seth, Kanupriya Bhardwaj, Niket and Ruchika Agarwal, and Arnab Sinha for the time and memories outside of integrated circuit design.

- ... Siva Thyagarajan for all his unselfish help with layout (and much beyond) and steadfast companionship.

- ... Sriramkumar Venugopalan for 4+ years of enthusiasm, innovation in the kitchen (and much beyond), techno-management discussions, and the inspiration for unquenchable optimization.

- ... Piya Pal for her solid support and motivation through the foundational phases of graduate school.

- ... my sister, Urja for being my agony (and ecstasy) aunt.

- ... my aunt, Asha Thakker for giving me the gift of conjugality.

- ... my wife, Vijayeta for creating the single biggest 'equalizing' effect on my life.

- ... my grandparents, Sharda and Pitambar Thakkar, and parents, Hema and Sanjay Thakkar for making me worthy of writing this.

## Chapter 1

### Introduction

The explosion of personal devices that need ubiquitous connectivity is making both wireless and wireline communication experience increasingly rapid growth in data-rates. For wireless communication, new channels and standards have been made available over the past decade to meet up to multi-Gb/s demands (e.g. [1]). Communication over wireless channels is prone to multi-path reflection which causes inter-symbol interference (ISI). As data-rates increase, this interference effectively spreads over a larger number of symbol periods, thus making it more challenging to counter.

Wireline channels on the other hand offer a more controlled environment and typically have shorter ISI delay spreads. However, ever-increasing data-rate requirements have outpaced the bandwidth of these channels. Due to cost limitations, legacy wireline mediums such as PCB traces and backplanes continue to be used. To keep up with networking demands, I/O data-rate requirements for backplanes supporting routers and servers are being pushed by upcoming standards to as high as 25-28Gb/s [2]. When these bandwidth-limited legacy channels are used at such high throughputs, the ISI spreads over a larger number of symbol periods, similar to wireless channels.

A classic technique to counter ISI is by using an equalizer which filters out this ISI in either the time or the frequency domain. Wireline transceivers operating at GS/s rates employ a combination of both frequency and time-domain equalizers. To equalize a wide range of channel responses, time-domain equalizers offer flexibility in shaping the transfer function to equalize the channel response. Such flexibility can also be leveraged for a wireless channel in equalizing multi-path reflections at different time-delays. While this flexibility can also be achieved by linear equalization in the frequency-domain, it requires conversion between time and frequency domains by using FFT/IFFT blocks which tend to be power-intensive. Time-domain equalizers on the other hand have been typically implemented as mixed-signal circuits (most extensively in wireline transceivers) with excellent energy efficiency. The equalization capability required of time-domain equalizers in terms of number of symbol-rate taps is directly proportional to the channel ISI delay spread and the data-rate. As a result, both wireless and wireline communication with high delay spread and/or high data-rates respectively require increased equalization capabilities. The focus of this dissertation

is the design of such time-domain equalizers requiring many taps of equalization.

While wireline transceivers use energy-efficient mixed-signal equalization, wireless base-bands have classically been relegated to using DSP. Wireless equalization is also typically carried out in the frequency domain using multi-level schemes such as orthogonal frequency division multiplexing (OFDM) and single-carrier frequency-domain equalization (SC-FDE). As will be shown in detail shortly, when this approach is scaled to GS/s rates, the power consumption of the DSP is substantial to be used in mobile/handheld devices. So far, the more efficient mixed-signal wireline techniques have not been applied for wireless most likely because wireless equalization requirements in terms of number of coefficients are significantly higher.

The primary focus of this dissertation is therefore the implementation of multi-coefficient time-domain equalizers using energy-efficient analog/mixed-signal circuitry. Aided by these equalizer designs, we will also demonstrate that using mixed-signal circuits in wireless basebands not only dramatically reduces power consumption but also enables significantly higher data-rates. To demonstrate the efficacy of such equalization, in this dissertation we shall use the wireless 60GHz band as a demonstration platform. By means of its wide bandwidth, the 60GHz channel enables multi-Gb/s communication, as will be shown shortly. To make such high data-rates an attractive proposition for mobile/hand-held devices, the baseband power consumption must be kept low. Since equalization consumes a significant portion of the total baseband power, we will demonstrate low-power equalizer design prototypes in this work. Despite the focus of these multi-coefficient designs for wireless channel equalization, the techniques and design frameworks developed in this dissertation will continue to be relevant for wireline equalization, especially in the light of increasing wireline data-rates.

We will first give a quick introduction to 60GHz communication and describe the current state-of-the-art of its mostly digital baseband design that is typical to wireless transceivers. To enable more energy-efficient equalization, we shall then introduce the two main categories of time-domain mixed-signal equalizers – namely decision feedback and feedforward equalizers. Finally, we shall examine the 60GHz channel characteristics across different environments to determine the requirements for these equalizers.

### 1.1 60GHz Wireless: A Demonstration Platform for Multi-Coefficient Equalization

The 60GHz wireless band with its 7GHz of bandwidth [1] has enabled ultra-high data-rate wireless communication. The attractiveness of multi-Gb/s wireless has drawn increasing interest from both academic [3][4][5][6] and industrial groups [7][8][9][10][11]. Commercial transceiver solutions for applications such as home HDTV streaming using the WirelessHD standard [12] are now also available[13].

Despite operating at much higher carrier frequencies and bandwidths, today's 60 GHz radios often bear significant resemblance to lower frequency designs. For example, similar to

Figure 1.1: Typical implementation of a wireless receiver

today's 802.11a/b/g/n wireless LAN radios, current 60 GHz radios often rely on Orthogonal Frequency DivisionMultiplexing (OFDM). This choice of modulation scheme requires relatively high levels of circuit and signal processing complexity, and hence typical 60 GHz implementations utilize the traditional system partitioning shown in Fig. 1.1. The RF front-end provides directionality (typically using a phased array [8]), and performs low-noise amplification followed by downconversion and (optionally) filtering, while the baseband comprises of the data-converters and digital signal processing (DSP). The DSP performs the requisite signal-conditioning to counter the non-idealities of wireless communication, such as OFDM de-modulation (or compensating inter-symbol interference in single-carrier link), performing carrier phase/frequency recovery, clock/data recovery, and error-control coding/decoding.

Following this traditional radio implementation strategy, todays commercial 60 GHz base-bands dissipate roughly 1W of power [13] which is likely to limit the use of these designs in mobile/hand-held devices. Although at first glance one may assume that the multi-GS/s data converters are responsible for the majority of this power, recent advances in such data-converter designs [14][15][16][17][18][19][20][6] have demonstrated energy-efficient designs with figure-of-merit (FOM)<sup>1</sup> of 50-500 fJ/conversion step at sampling rates of 2-10GS/s for 4-8 bits of dynamic range. This indicates that even a 5 GS/s ADC with 5-bit resolution would dissipate well under 25 mW. In a GS/s baseband therefore, the ADC will most likely not be the power bottleneck.

A closer examination thus reveals that the power of a typical 60 GHz baseband is dominated by the various DSP blocks. This can be illustrated by the power dissipation of digital 60 GHz basebands presented recently by Okada et al. in [6] and Hsiao et al. in [21]. The digital baseband in [6] which incorporates a relatively short 8-tap time-domain FIR filter-based equalizer and a power-optimized LDPC decoder, besides carrier recovery and automatic gain control consumes 206 mW and 224 mW for 3.5 Gb/s and 7 Gb/s throughputs using QPSK and 16-QAM respectively. The digital solution in [21] with more comprehensive equalization – specifically 512-pt FFT based orthogonal frequency division multiplexing (OFDM) and single-carrier frequency domain equalizer (SC-FDE) based digital equalizers – consumes 150 mW and 208 mW respectively for the two equalization modes at 7 Gb/s using

<sup>&</sup>lt;sup>1</sup>FOM =  $P/(2^{ENOB} \cdot f_s)$ , where P – power dissipation, ENOB – effective number of bits,  $f_s$  – sample-rate.

Figure 1.2: Typical implementation of a high-speed wireline transceiver

#### 16-QAM.

Furthermore, the above-mentioned designs have only focused on current 60GHz standards [22][23] agreed upon by consortiums/alliances [12][24] supporting a maximum sample-rate of 1.76GS/s. While requirements on throughputs are increasing at breakneck speed, the power efficiency of digital designs – which are already operating close to the limit of feasible speeds in their respective CMOS technology nodes – scales poorly for data-rates higher than 1.76GS/s. These DSP-based multi-GS/s designs which consume hundreds of mW of power (and potentially up to ~1W for higher throughputs) will therefore likely be infeasible for mobile/hand-held devices. It is worthwhile examining alternative communication systems and implementations to seek inspiration for lower-power solutions.

High-speed chip-to-chip electrical links (Fig. 1.2) offer a stark contrast to these high dynamic range mostly-digital wireless transceiver basebands. These designs have shown that for high bandwidths and relatively low dynamic range (implying simple modulation such as 2-PAM), analog processing and a minimal number of comparators is significantly more efficient than multi-bit ADC/DSP-based solutions. Specifically, the energy-efficiency achieved by current state-of-the-art serial link designs using mostly analog processing is 1mW/Gb/s [25][26] while operating at up to 12 Gb/s. For applications with even higher channel losses (25-35 dB) such as backplane-based transceivers requiring high transmit swings (0.6-1.2 V) and powerful equalizers (with as many as 14 taps of equalization), recent serial link designs [27], [28] have been able to achieve data-rates of 12-16 Gb/s with energy efficiencies of 8-15 mW/Gb/s.

Fig. 1.3 illustrates the key benefit offered by analog processing over digital processing. For any signal processing operation, the energy per computation is set by the effective capacitance of the signal processing circuit. A digital processor typically employs multiple blocks per operation, set by the requirements on resolution. Due to minimum device size constraints on each of these constituent blocks, a digital processor will almost invariably have larger effective capacitance (dominated by timing elements such as flip-flops). On the contrary, an analog processor usually has a smaller total device size per operation (as long

Figure 1.3: Comparison between digital and analog processing: Digital processing typically uses more transistor width (and hence more capacitance) per operation and consumes more power.

Figure 1.4: 60GHz receiver with mixed-signal baseband

as it is not constrained by noise or linearity<sup>2</sup>) and can hence achieve lower power. Note that serial links do use digital processing for certain high precision computations; however, since this processing is mostly limited to low-speed calibration/control circuitry, it does not incur a significant power penalty.

Inspired by such low-power high-speed serial links using analog processing, we aim for the design of an energy-efficient mobile mixed-signal 60GHz baseband (Fig. 1.4). Due to multi-path reflections, however, the wireless 60GHz channel (as will be shown in detail in section 1.3) has a much longer delay spread than a typical wireline channel. Mitigating the inter-symbol-interference (ISI) over such a long spread would require multi-coefficient time-domain equalizers that lie beyond the design space of serial links. The emphasis of this dissertation is therefore on designing feedback and feedforward time-domain equalizers for

$<sup>^2</sup>$ In modern sub-micron technologies, up to  $\sim$ 5 bits of linearity can be achieved without incurring a penalty on device size.

Figure 1.5: Channel impulse response

Figure 1.6: Block diagram of feedforward and decision feedback equalization [29].

line-of-sight (LOS) and non-line-of-sight (NLOS) multi-path 60GHz channels.

In the next two sections, we shall first introduce mixed-signal decision feedback and feed-forward equalizers, and then examine channel models for 60GHz wireless links to determine the requirements for these equalizers.

### 1.2 Mixed-Signal Time-Domain Equalizers

Fig. 1.5 shows a generic baseband channel response with ISI. Typically, the strongest response tap is assigned as the cursor. All taps occurring before the cursor in time are labelled as pre-cursors, while all taps occurring after the cursor in time are labelled as post-cursors. Since the ISI tends to reduce the effective received signal-to-noise (SNR) ratio, the presence of ISI is detrimental to the reception of transmitted bits. An equalizer improves reception

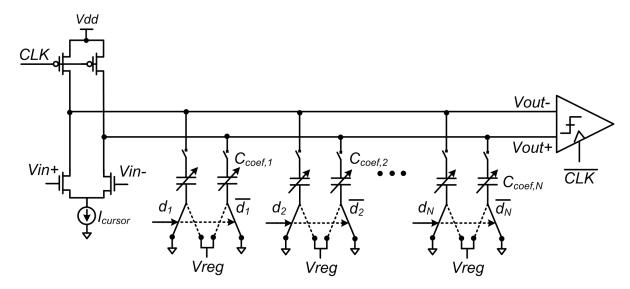

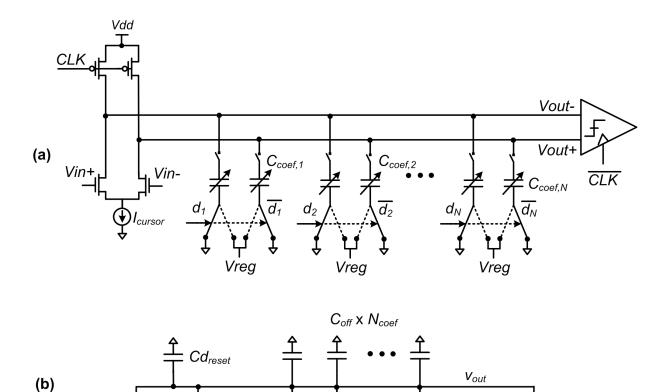

Figure 1.7: Block diagram of a decision feedback equalizer (DFE) (left); Conventional mixed-signal implementation using resistively-loaded summing of current-steering DACs representing ISI weights (right)

by removing the ISI. A time-domain equalizer filter in general can be divided into two categories – feedback (usually referred to as 'decision feedback') and feedforward, as shown in Fig. 1.6. The following subsections introduce the functionality and implementation of decision feedback and feedforward equalizers.

#### 1.2.1 Decision Feedback Equalizer

A decision feedback equalizer (DFE) (Fig. 1.7 (left)) is essentially a non-linear filter which makes use of previous decisions in attempting to estimate the current symbol. Any trailing (post-cursor) ISI caused by previous symbols is reconstructed and then subtracted. Since a DFE generates the ISI canceling signal from the quantized estimate of the received signal, its primary advantage is that it does not amplify the received noise. While receiving signals with very low SNR (and therefore relatively high BER), the DFE is prone to making incorrect decisions, further aggravated by error propagation. For this work, however, which targets BER< 10<sup>-3</sup>, the DFE is not impaired by error propagation, thus making it an excellent candidate to cancel the post-cursor portion of ISI.

DFE's can be implemented efficiently as a mixed-signal circuit, as shown in Fig. 1.7 (right). This conventional mixed-signal DFE structure cancels post-cursor ISI by subtracting currents representing the ISI coefficients at a resistive load. The cancelation currents are implemented by using current-steering DACs, whose values are adapted to the ISI. Within every UI period, every ISI coefficient needs to be settled starting from the respective feedback shift register flip-flop and ending with current settling at the RC-load. For the 1<sup>st</sup> coefficient, since this involves the slicer conversion of a small-signal to CMOS-levels, meeting the feedback latency constraint is particularly challenging. In mixed-signal DFEs, therefore, resolving this constraint has been the single-most explored design challenge.

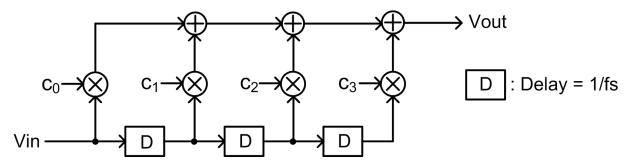

Figure 1.8: FFE Block Diagram

However, in the case of high-throughput wireless communication such as the wideband 60GHz channel, the more significant challenge is related to the delay spread of the ISI. As will be detailed in section 1.3, for targeted symbol rates as high as 5GS/s, a 60GHz channel may exhibit 30-50 complex<sup>3</sup> taps of post-cursor ISI, even with a directional front-end. Adding such a large number of weights in a mixed-signal structure is an unprecedented challenge at GS/s speeds. Previous solutions employing mixed-signal DFEs for 60GHz channels have either been relatively low-speed ([30] operates at 500MS/s, [31] operates at 1.76GS/s) or have limited equalization capabilities ([3] incorporates only a 5-tap complex DFE).

As will be described in detail in Chapter 2, the summing node of the structure is loaded by the parasitic capacitance of the current-steering switches. Therefore, in typical DFE implementations, only a relatively limited number of coefficients can be implemented before this self-loading makes it infeasible (at any power) to achieve the bandwidth required for multi-GS/s operation. In this work, we therefore propose a cascode-summation structure that significantly increases the number of ISI taps that can be efficiently canceled by the DFE, while enabling 10Gb/s quadrature phase shift keying (QPSK) communication. The topology leverages the fact that in any channel, the total multi-path amplitude (and energy) is bounded. To demonstrate this approach, a 65nm CMOS test-chip was designed that included a mixed-signal DFE capable of handling 20 complex ISI taps at 10Gb/s while consuming only 14mW of power. For equalizing channels with even longer delay spreads, the cascode summation approach can be combined with other power-efficient current summation topologies (such as current integration, as described in Chapter 3) to further extend the number of implementable taps.

#### 1.2.2 Feedforward Equalizer

A feedforward or linear equalizer is essentially a finite-impulse-response (FIR) filter (Fig. 1.8) whose function is to collect the energy from a set of ISI taps onto the cursor. Given enough

$<sup>^3</sup>$ Complex refers to the presence of both in-phase and quadrature-phase components. Therefore, in the context of an I/Q baseband, each complex tap consists of (a) a direct tap from I-to-I or Q-to-Q channel and (b) a cross-tap from I-to-Q or Q-to-I channels.

taps, a feedforward equalizer (FFE) may be programmed to mitigate ISI from all taps – precursor and post-cursor. However, since FFE filtering can potentially amplify thermal noise and given that a DFE is efficient at canceling post-cursor ISI without such amplification, the functionality of an FFE is typically limited to handling only pre-cursor taps.

For a wireless channel, in order to ease tap adaptation, an FFE is more convenient to implement at the receiver (RX). However, this creates a requirement for analog delay elements. As shall be seen in detail in Chapter 4, implementing analog delay leads to a tradeoff between linearity, area, and power. The tradeoffs are further aggravated with the requirement of up to 16 taps of feedforward equalization for the wireless 60GHz channel (as detailed in the section 1.3). In this work, we will propose an architecture to implement analog delay efficiently by using a switching matrix. This matrix is effectively a 1-to-N describing delay efficiently by using a switching matrix. This matrix is effectively a 1-to-N describing the proposed architecture enables efficient implementation of the delay line, thus easing the power requirements for the FFE. To demonstrate this approach, a 65nm LP CMOS test-chip was designed that included a complex 16-tap (64 I/Q coefficient) RX-FFE capable of operation up to 8Gb/s, with the switching matrix consuming only 26mW of power. In the following section, we will determine the requirements on both feedback and feedforward equalizers by examining the baseband equivalent channel models for 60GHz wireless links.

#### 1.3 Channel Models for 60GHz Wireless

The 60GHz channel, with its wide bandwidth, makes it amenable to achieve GS/s wireless data-rates. The high throughputs however also imply that even moderate delay spreads in the channel lead to a significant number of ISI taps. In order to quantify the ISI profiles in terms of delay spread and relative magnitude, empirical channel models have been developed in literature, most notably in [33], [32] and [34]. These works have conducted extensive experiments using 60GHz links in both office and residential spaces. The methodology and channel models in [32] and [34] have been used by the IEEE 802.11ad committee for standardization of 60GHz channel models. This section summarizes the findings of these channel models, and computes the requirements for time-domain equalization (TDE) using mixed-signal techniques.

According to the well-known Friis transmission equation [35], the small wavelength in the mm-wave band inherently causes high free-space path loss of as much as 68dB for a 1m TX-RX distance. Experiments with 60GHz radiation conclude that penetration (reflection) through (from) humans, standard building materials and surfaces such as walls and furniture also causes significant attenuation to 60GHz signals. Therefore in contrast with typical lower frequency wireless channels (such as WiFi and cellular frequencies), the 60GHz channel is more deterministic, and can actually be well understood by ray tracing techniques. Due to the finite smoothness of every surface, reflection rays each appear as a group of consecutive ISI taps, and can be modeled by the clustering approach [36]. Human blockers tend to diffract signals, thus raising the rms delay spread [34]. However, the high attenuation of

Figure 1.9: 60GHz NLOS channel model of conference room using model from [32]. Datarate: 4GS/s, TX-RX distance: 3m, TX, RX antenna half-power beamwidth (HPBW): 70°.

materials causes most reflections above second order to disappear below the thermal noise floor [33][32]. Since the high loss at mm-wave enforces the need for directional communication [37] (typically using phased arrays [38]) to satisfy the link budget, this further limits the number of reflections.

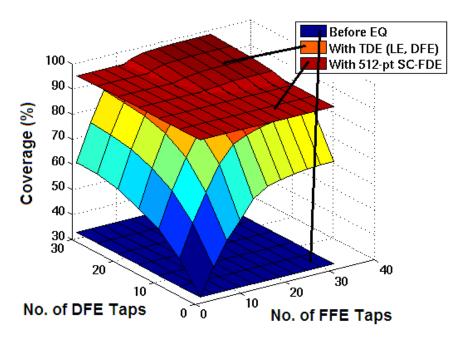

Based on the guidelines by A. Maltsev et al. [32] for the 802.11ad standard for 'WiGig' specifications [24], a statistical model was created. These instantiations were ranked as per their total ISI magnitude relative to the cursor. Fig. 1.9 shows an instantiation of channel models for a conference room around the 95th percentile by total ISI magnitude. In order to quantify the requirements on the equalizer in terms of number of taps, a coverage model was then developed. In this context, coverage is defined as the percentage of statistical channel instantiations that can be equalized by the time-domain equalizer canceling pre-cursor and post-cursor ISI (using an FFE and DFE respectively) to below a target uncoded bit-errorrate (BER). The coverage is also compared to that of a digital SC-FDE using 512-point FFT. Figs. 1.10 and 1.11 show the coverage for an NLOS living room model with high directionality (30° TX, RX antenna half-power beamwidth (HPBW)) and conference room model with lower directionality (70° TX, RX antenna half-power beamwidth (HPBW)). For both these plots, the analysis was done for the WiGig-standard-based 1.76GS/s for an uncoded symbol-rate of BER $< 10^{-3}$  versus number of equalizer taps, before and after equalization. As seen in the figures, at this BER, the SC-FDE achieves 95% coverage. Based on the coverage analysis, it can be concluded that to realize a post-equalization BER of  $10^{-3}$ ,

Figure 1.10: Time-domain equalizer coverage (percentage of channels equalized to BER < 10<sup>-3</sup>) vs. 512-pt FFT-based SC-FDE for LOS living-room channel model[34]). Data-rate: 1.76GS/s, TX-RX distance: 3m, TX, RX antenna HPBW: 30°.

the TDE needs 16 pre-cursor taps and 20 post-cursor taps at 1.76GS/s.

Based on these channel models, the focus of the equalizer design in this dissertation will be two-pronged. The first design prototype strives to enable communication across relatively short 1-1.5m LOS channels with reasonable directionality and a moderate number (20) of post-cursor taps. The equalization of post-cursors is done by using a mixed-signal DFE. While a DFE is an efficient way to cancel post-cursor ISI, the total number of coefficients for this channel is significantly higher than any prior DFE art. Consequently, to implement a power-efficient QPSK design in 65nm CMOS working up to 10Gb/s is challenging.

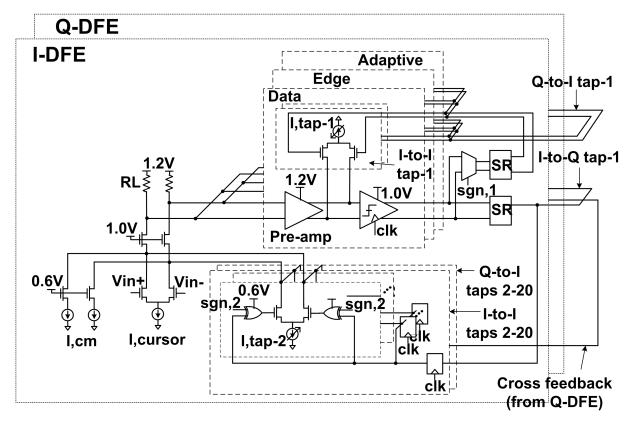

Building upon the techniques developed in the first prototype, the second design targets the more exhaustive NLOS channels for longer (up to 3m) distances. The targeted data-rates vary from WiGig-specified 3.5Gb/s to a maximum of 8Gb/s in a 65nm LP CMOS process.<sup>4</sup> To handle pre-cursor ISI, this design has an additional 16-tap (32-coefficient) I/Q FFE at the receiver. While a 16-tap FFE can comprehensively equalize moderately directional NLOS channels only up to 1.76GS/s, higher data-rates will require increased directionality to satisfy the link budget. The increased directionality limits the precursor delay spread and hence the FFE tap requirements. To handle the increased delay spread of post-cursor ISI, a 50-tap (100-coefficient) I/Q decision feedback equalizer is designed.

$<sup>^{4}</sup>$ Since this is a commercial low-power technology without a provision for low-threshold transistors, the fanout-of-4 (FO4) delay is  $\sim$ 2X slower than the corresponding GP CMOS process. The peak data-rate targeted is therefore 20% lower than the first prototype.

Figure 1.11: Time-domain equalizer coverage (percentage of channels equalized to BER < 10<sup>-3</sup>) vs. 512-pt FFT-based SC-FDE for NLOS conference-room[32]). Data-rate: 1.76GS/s, TX-RX distance: 3m, TX, RX antenna HPBW: 70°.

### 1.4 Organization of Dissertation

The dissertation first presents the design methodology for a mixed-signal DFE in Chapter 2. The methodology is used to explore the design space and compute the power dissipation of a DFE as a function of data-rate and the number of taps (i.e. the channel characteristics). The methodology is also used to highlight the shortcomings of the conventional DFE summing structure, which motivates the proposed cascode current-summing structure to increase the number of feasible taps. The design framework is then extended to highlight these improvements, followed by the implementation of one such prototype 20-complex tap cascode-summation structure in 65nm CMOS operating at 10Gb/s. To enable the implementation of an even higher number of coefficients, Chapter 3 analyzes other coefficient summation techniques developed recently in literature, namely current integration based current summation and switched capacitor based voltage summation. The analysis identifies the architecture most suited for implementing many coefficients.

As a next step towards dealing with the more generic NLOS channels, RX-FFEs are described in Chapter 4. This chapter examines prior RX-FFE art using rotating coefficients [39] and interleaved sampling [40], and explains the limitations in power efficiency of both these architectures for implementing multiple coefficients. The limitations motivate the proposed switching-matrix based architecture that provides an efficient solution for multi-coefficient RX-FFE implementation. Finally, Chapter 5 describes the design and measurement results of a prototype 8Gb/s 32-coefficient RX-FFE, 100-coefficient DFE in 65nm LP CMOS.

As mentioned earlier, while the mixed-signal equalizer prototypes demonstrated for this work were targeted for multi-Gb/s  $60\mathrm{GHz}$  wireless communication, the design techniques that have been developed can be used for any high-speed wireless and wireline communication link requiring energy-efficient multi-coefficient equalization.

## Chapter 2

## DFE Design using Cascode Current-Summing

As a first step towards designing equalizers for high throughput channels with long multi-path delay spreads – such as the wideband 60GHz channel – this chapter addresses the mitigation of post-cursor ISI. As briefly introduced in the previous chapter, a mixed-signal decision feedback equalizer (DFE) is an excellent candidate for efficiently canceling such post-cursor ISI. Such mixed-signal DFEs have been widely used for wireline channel equalization with up to  $\sim$ 15 taps of equalization [2]. As shown in the previous chapter, however, multi-GS/s communication over wireless channels such as 60GHz could require mitigation of up to 40-100 post-cursor ISI coefficients. This increase in the number of DFE coefficients, which is almost an order of magnitude higher than prior art, calls for a deeper understanding of the design limitations of conventional mixed-signal DFE architectures.

The first part of this chapter analyzes the power consumed by a conventional current summation structure as a function of the number of coefficients, and illustrates the limitations of this architecture. These limitations and their dependence on the nature of channel motivate the improvements that can be brought about by a proposed cascode summer design described in the second part of the chapter. An analysis of the cascode-summing architecture is then performed, showing how it significantly eases the dependence of power on the number of coefficients. Finally, to illustrate the power-efficiency of the proposed architecture, a 65nm CMOS prototype of a 40-coefficient cascode-summing DFE for 60GHz channels is described, which operates up to 10Gb/s while consuming only 14mW of power.

# 2.1 Conventional Current Summing DFE Architecture

Representing ISI coefficients as currents and adding them at a resistive load has been the most widely implemented style of DFE summing. The technique has been most popular in wireline receivers to mitigate channel bandwidth limitations, reflections due to impedance mis-

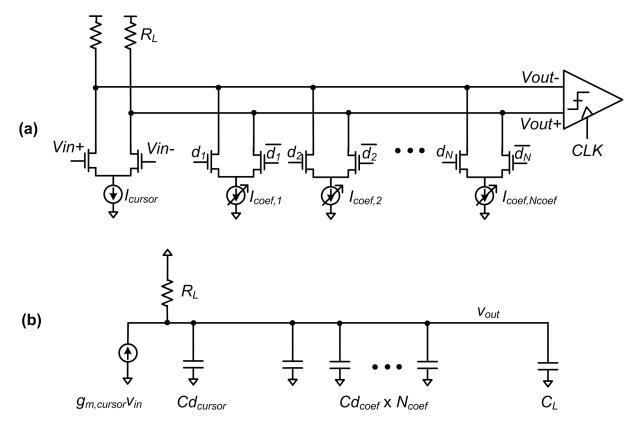

Figure 2.1: Gain/bandwidth analysis of a conventional resistively-loaded current-summing DFE. (a) Schematics (feedback shift register not shown) and (b) Single-ended small-signal model.

matches, or some combination thereof. Initial implementations [41][42] used triode-PMOS loads; however to decrease intrinsic capacitive loading, PMOS loads were eventually replaced by physical resistors [43]. While designing a resistively-loaded DFE, the primary specifications are similar to a Class-A amplifier – voltage gain (to achieve reasonable output swing for the following slicer) and bandwidth (to settle the per-UI switching ISI currents at the RC-load with sufficient accuracy). Given these constraints, it is informative to understand the dependence of power dissipation on the data-rate, the ISI profile/number of coefficients in the DFE, as well as technology-related parameters. As will be shown through the analysis, this dependence highlights the limitations of conventional current summation.

Fig. 2.1 shows a conventional mixed-signal DFE summing amplifier structure, and its small-signal model. To simplify the analysis, the output resistance of all transistors has been ignored. The input cursor amplitude is  $v_{in}$  (excluding the ISI), while the summing amplifier has a DC gain of G and operates at a data-rate of  $f_s$  symbols per second. The DFE has  $N_{coef}$  number of coefficients that can be adapted to work across multiple channels. To enable this flexibility, each DFE coefficient can cancel ISI up to a maximum amplitude of k times the cursor amplitude. While this analysis assumes, for simplicity, the same maximum across all

coefficients, if certain coefficients magnitudes are bounded differently than the others, it is easy to introduce a variable maximum magnitude as a function of coefficient position (say,  $k_i$  for the *i*-th coefficient). In this analysis, the maximum coefficient current,  $I_{coef}$  would be

$$I_{coef} = k \cdot g_{m,cursor} \cdot v_{in} \tag{2.1}$$

In order to properly cancel the ISI, the coefficient-DAC current  $(I_{coef})$  must be steered by the differential data signal (shown as d and  $\overline{d}$ ) from the feedback shift register and satisfactorily settled at the summation node before the next data bit is resolved by the comparator. A full-rate<sup>1</sup> DFE therefore has a 1UI timing constraint for the settling of each coefficient. This timing constraint can be partitioned as  $(1 - \alpha)$ UI for the digital delay of the flip-flop and the XOR gate (for choosing the sign of the coefficient), and  $\alpha$ UI for the analog settling of the coefficient current at the summation node  $(\alpha < 1)$ . The time-constant  $\tau$  of this settling is given by the RC product

$$\tau = R_L \cdot (C_L + Cd_{cursor} + N_{coef} \cdot Cd_{coef}) \tag{2.2}$$

where  $R_L$  is the summation load resistance,  $Cd_{cursor}$  is the drain capacitance of the input transistor,  $Cd_{coef}$  is the drain capacitance of the current steering switch at each coefficient, and  $C_L$  is the loading from the next stage, which is typically the comparator (often with a preamp input-stage to mitigate kickback). Since the input pair is a differential  $g_m$ -stage,

$g_{m,cursor} = \frac{I_{cursor}}{V^*}$ , where  $I_{cursor}$  is the DC bias current of the input pair<sup>2</sup>. The DC gain is therefore given by

$$G = g_{m,cursor} \cdot R_L = \frac{I_{cursor}}{V_{cursor}^*} \cdot R_L \tag{2.3}$$

Of the three capacitors at the summation node in (2.2),  $Cd_{cursor}$  and  $Cd_{coef}$  are attributed to the internal self-loading of the structure and are functions of the summing amplifier currents, while  $C_L$  is a fixed external loading. The internal capacitors can be expressed in terms of technology parameters,  $C_{dI,cursor}$  and  $C_{dI,coef}$ , where  $C_{dI}$  denotes transistor drain capacitance per unit drain current.

$$Cd_{cursor} = C_{dI,cursor} \cdot \frac{I_{cursor}}{2} \tag{2.4}$$

$$Cd_{coef} = C_{dI,coef} \cdot I_{coef} = C_{dI,coef} \cdot (k \cdot g_{m,cursor} \cdot v_{in})$$

$$= C_{dI,coef} \cdot \left(k \cdot \frac{v_{in}}{V_{cursor}^*}\right) \cdot I_{cursor}$$

(2.5)

<sup>&</sup>lt;sup>1</sup>Full-rate implies that the sampling CLK frequency is equal to the data-rate.

$<sup>^{2}</sup>V^{*}$  is defined as  $V^{*}=2I_{bias}/g_{m}$ .

Substituting for  $R_L$ ,  $Cd_{cursor}$ , and  $Cd_{coef}$  in terms of  $I_{cursor}$  (from 2.3, 2.4 and 2.5 respectively), the time constant in (2.2) can be expressed as

$$\tau = \frac{G \cdot V^*}{I_{cursor}} \cdot \left( C_L + C_{dI,cursor} \cdot I_{cursor} + N_{coef} \cdot C_{dI,coef} \cdot k \cdot \frac{I_{cursor}}{V_{cursor}^*} \cdot v_{in} \right)$$

(2.6)

If 1UI is  $T = 1/f_s$ , then the analog settling constraint implies that

$$n_{\tau} \cdot \tau = \alpha \cdot T \tag{2.7}$$

where  $n_{\tau}$  is the required number of time constants of settling. Combining (2.6) and (2.7) gives a complete expression for the cursor current:

$$I_{cursor} = \frac{C_L \cdot \left(\frac{n_{\tau} f_s}{\alpha}\right) \cdot G \cdot V^*}{1 - \left(\frac{n_{\tau} f_s}{\alpha}\right) \cdot G \cdot V_{cursor}^* \cdot \frac{C_{dI,cursor}}{2} \cdot \left(1 + N_{coef} \cdot k \cdot \frac{v_{in}}{V_{cursor}^*} \cdot \frac{2 C_{dI,coef}}{C_{dI,cursor}}\right)}$$

(2.8)

Now, if unity gain frequency,  $\omega_T$  is defined as

$$\omega_T = \frac{g_m}{Cq} = \frac{2 \cdot I_{bias}}{V^*} \frac{\gamma}{Cd} \tag{2.9}$$

in which  $\gamma$  is the ratio of drain to gate capacitance, then  $C_{dI}$  in (2.8) can be re-written as

$$\frac{Cd}{I_{bias}} = C_{dI} = \frac{2\gamma}{V^* \cdot \omega_T} \tag{2.10}$$

Now, in (2.8), let us define  $GBW = G \cdot \frac{n_{\tau} \cdot f_s}{\alpha}$  as the gain-bandwidth product. Let us also define  $I_{nom} = C_L \cdot GBW \cdot V^*$  as the nominal current consumption for a class-A amplifier without self-loading.  $I_{cursor}$  may then be written in a simplified form as:

$$I_{cursor} = \frac{I_{nom}}{1 - \left(\gamma \cdot \frac{GBW}{\omega_{T,cursor}}\right) \left(1 + N_{coef} \cdot k \cdot \frac{v_{in}}{V_{coef}^*} \cdot \frac{2 \omega_{T,cursor}}{\omega_{T,coef}}\right)}$$

(2.11)

Since the coefficient currents  $(I_{coef})$  are proportional to the cursor current  $(I_{cursor})$ , the total power dissipation of the summing amplifier is also proportional to  $I_{cursor}$ . Therefore, power dissipation of a resistively current-summed DFE, P(I, res), as a function of  $N_{coef}$  also takes the form of (2.11), and can be expressed as:

$$P(I, res) \propto \frac{\left(\frac{n_{\tau}}{\alpha}\right) \cdot I_{nom} \cdot V_{dd}}{1 - \left(\gamma \cdot \frac{GBW}{\omega_{T,cursor}}\right) \left(1 + N_{coef} \cdot k \cdot \frac{v_{in}}{V_{coef}^*} \cdot \frac{2 \omega_{T,cursor}}{\omega_{T,coef}}\right)}$$

(2.12)

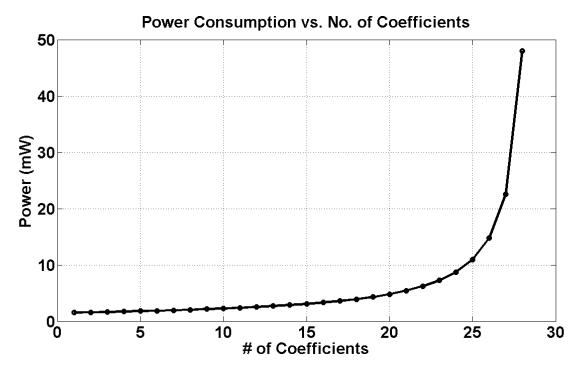

Figure 2.2: Conventional current-summing DFE power vs. no. of coefficients at 5GS/s, with  $k_{max} = 0.5$  in 65nm CMOS.

The form of equations (2.11), (2.12) illustrates how a conventional mixed-signal DFE can only support a limited number of coefficients. When  $N_{coef}$  is small, to handle the extra capacitance of every additional coefficient, the load resistance can be moderately decreased and the current increased in order to maintain a constant gain and bandwidth. However, once the product of GBW and  $N_{coef}$  becomes comparable to the  $\omega_T$  of the technology, the DFE becomes self-loaded to the point that it cannot handle more coefficients for any increase in power, as seen in Fig. 2.2. At the desired data-rate of 5GS/s in a 65nm GP CMOS technology, a conventional DFE structure can implement only  $\sim$ 10 complex taps (i.e. 20 I/Q coefficients) efficiently. Clearly, such a structure is incapable of being directly used in a 60GHz transceiver, which, as seen in the channel modeling analysis, typically needs up to 50 taps (i.e. up to 100 I/Q coefficients) of equalization.

Since the channel to be equalized is typically unknown ahead of time, the DFE needs to incorporate a certain amount of reconfigurability into each tap. Implementing such flexibility invariably involves an overdesign of the taps in terms of their current-handling capability, which exacerbates the self-loading of a conventional summing structure. As will be shown in the next section, the proposed cascode current-summation technique alleviates the penalty associated with this flexibility and is able to significantly extend the number of feasible taps.

Figure 2.3: Wireless channel response: While each tap can have a variable weight, not all taps will be at their maximum weight altogether. However, the sum of all tap magnitudes is bounded due to finite transmit power.

### 2.2 Proposed Cascode Current-Summing DFE

The previous section highlighted the shortcomings of a conventional DFE. The DFE structure is primarily constrained by the self-loading of its taps. In addition, since the channel to be equalized is not fixed, the DFE requires a certain degree of flexibility, which limits the number of taps that can be implemented. In this section, we will show that by making key observations about the impact of channel variability on the DFE design, a cascode current-summing structure is able to incorporate the requisite flexibility while notably improving the number of feasible taps.

### 2.2.1 Concept

Since a wireless channel is time-varying by nature, each tap needs to be designed to cancel a certain maximum magnitude of ISI. From a design standpoint, this sets the size of the current steering switch of each tap to handle this maximum ISI current. If the capacitive loading of each tap handling the maximum ISI current is  $C_{par}$ , the total loading from N taps is  $N \cdot C_{par}$ . However, since the received signal has a limited sum of ISI magnitude (due to finite transmit power), not all taps need to be set to their maximum magnitude at the same time (Fig. 2.3). In other words,

$$||ISI||_1 < \sum_{i=1}^{N_{coef}} |ISI_{i,max}|$$

(2.13)

which in turn means that if the maximum current in each tap is  $I_{max}$  and the maximum possible sum of currents in all taps is  $I_{ISI,max}$ , then  $I_{ISI,max} < N_{coef} \cdot I_{max}$ . Therefore, loading the summation node with a capacitance of  $N \cdot C_{par}$  is inefficient.

Conceptually, the ideal design would be one in which the taps only load the summation node with capacitance corresponding to the maximum possible sum of ISI. One way to realize

Figure 2.4: A fully digital FIR/DAC implementation of the DFE limits the self-loading at the summing node. However, the 1UI latency constraint on the first tap feedback makes the FIR adder unacceptably expensive in power

this would be to use a fully digital FIR filter in the feedback path to sum all taps and cancel the ISI using a DAC, as shown in Fig. 2.4. Since the DAC current would be bounded, the DAC can be designed with bounded capacitive loading at the summation node, thus reducing the power of the summation amplifier. However, since the latency of this FIR/DAC needs to be < 1UI, at GS/s rates the power consumed by the filter in summing such a large number of digital tap values would be unacceptably high.

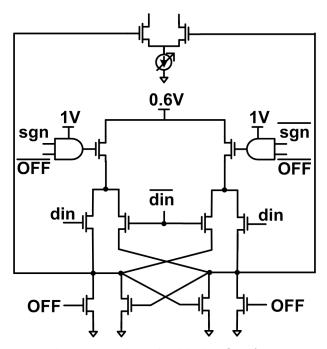

The proposed cascode current summation structure realizes limited capacitive loading by summing all current through a cascode transistor, as shown in Fig. 2.5. The cascode transistor can be sized to handle the bounded ISI current. The cascode transistor width is therefore much smaller than the sum of current steering switch widths, thus reducing the loading at the output of the summing amplifier. Furthermore, the large capacitance of these switches is moved to the low-impedance source node of the cascode. To maintain a high bandwidth at the cascode source, the  $g_m$  of the cascode transistor is increased by applying additional common mode current. As will be shown in the analysis that follows, this structure significantly extends the number of taps that can be implemented by the DFE.

#### 2.2.2 Analysis

Fig. 2.6 shows the small-signal equivalent of the cascode current-summing structure. As with the analysis of the conventional DFE, the input cursor amplitude is  $v_{in}$ , the DC-gain is G, the data-rate is  $f_s$  symbols per second, and the number of coefficients is  $N_{coef}$ . The total cursor DC biasing current is  $I_{cursor}$ , while the common-mode current added to each side is  $I_{boost}$ . Each of the coefficients can cancel ISI up to a maximum amplitude of k times the

Figure 2.5: Cascode current summing structure: Tap switches moved to low-impedance cascode, and capacitive load at output node reduced

cursor, and a total ISI of amplitude of  $k_{ISI,max}$  times the cursor amplitude. Therefore,

$$I_{coef} = k \cdot g_{m,cursor} \cdot v_{in} = k \cdot \frac{I_{cursor}}{V^*} \cdot v_{in}$$

(2.14)

$$I_{coefs,total} = k_{ISI,max} \cdot \frac{I_{cursor}}{V^*} \cdot v_{in}$$

(2.15)