# Understanding and Improving Graph Algorithm Performance

Scott Beamer

# Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2016-153 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-153.html

September 8, 2016

Copyright © 2016, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Understanding and Improving Graph Algorithm Performance

by

Scott Beamer III

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Krste Asanović, Co-chair Professor David Patterson, Co-chair Professor James Demmel Professor Dorit Hochbaum

Fall 2016

# Understanding and Improving Graph Algorithm Performance

Copyright 2016 by Scott Beamer III

#### Abstract

Understanding and Improving Graph Algorithm Performance by Scott Beamer III Doctor of Philosophy in Computer Science University of California, Berkeley Professor Krste Asanović, Co-chair Professor David Patterson, Co-chair

Graph processing is experiencing a surge of renewed interest as applications in social networks and their analysis have grown in importance. Additionally, graph algorithms have found new applications in speech recognition and the sciences. In order to deliver the full potential of these emerging applications, graph processing must become substantially more efficient, as graph processing's communication-intensive nature often results in low arithmetic intensity that underutilizes available hardware platforms.

To improve graph algorithm performance, this dissertation characterizes graph processing workloads on shared memory multiprocessors in order to understand graph algorithm performance. By querying performance counters to measure utilizations on real hardware, we find that contrary to prevailing wisdom, caches provide great benefit for graph processing and the systems are rarely memory bandwidth bound. Leveraging the insights of our workload characterization, we introduce the Graph Algorithm Iron Law (GAIL), a simple performance model that allows for reasoning about tradeoffs across layers by considering algorithmic efficiency, cache locality, and memory bandwidth utilization. We also provide the Graph Algorithm Platform (GAP) Benchmark Suite to help the community improve graph processing evaluations through standardization.

In addition to understanding graph algorithm performance, we make contributions to improve graph algorithm performance. We present our direction-optimizing breadth-first search algorithm that is advantageous for low-diameter graphs, which are becoming increasingly relevant as social network analysis becomes more prevalent. Finally, we introduce propagation blocking, a technique to reduce memory communication on cache-based systems by blocking graph computations in order to improve spatial locality. To my family

# Contents

| Co | onter                                                        | nts                                                                                                                                                                                                         | ii                                                        |  |  |  |  |  |  |

|----|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|

| Li | List of Figures i                                            |                                                                                                                                                                                                             |                                                           |  |  |  |  |  |  |

| Li | st of                                                        | Tables                                                                                                                                                                                                      | viii                                                      |  |  |  |  |  |  |

| 1  | <b>Intr</b><br>1.1<br>1.2                                    | roduction<br>Focus on Shared Memory Multiprocessor Systems                                                                                                                                                  | <b>1</b><br>2<br>3                                        |  |  |  |  |  |  |

| 2  | Bac<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5                       | <b>kground on Graph Algorithms</b> The Graph Abstraction         Topological Properties of Graphs         Graphs in this Work         Graph Algorithms in this Work         Other Types of Graph Algorithms | <b>5</b><br>6<br>7<br>8<br>11                             |  |  |  |  |  |  |

| 3  | Dire<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | ection-Optimizing Breadth-First Search Introduction Conventional Top-Down BFS Bottom-Up BFS Direction-Optimizing BFS Algorithm Evaluation Evaluation Conclusion Conclusion                                  | <b>13</b><br>13<br>14<br>17<br>18<br>20<br>31<br>33<br>35 |  |  |  |  |  |  |

| 4  | <b>GA</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5                 | P Benchmark Suite         Introduction         Related Work         Benchmark Specification         Reference Implementation         Conclusion                                                             | <b>37</b><br>37<br>38<br>39<br>45<br>48                   |  |  |  |  |  |  |

iii

| 5 Graph Workload Characterization                                                                          | 49    |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| 5.1 Introduction $\ldots$ | . 49  |  |  |  |  |  |

| 5.2 Methodology $\ldots$  |       |  |  |  |  |  |

| 5.3 Memory Bandwidth Potential                                                                             |       |  |  |  |  |  |

| 5.4 Single-Core Analysis                                                                                   |       |  |  |  |  |  |

| 5.5 Parallel Performance                                                                                   |       |  |  |  |  |  |

| 5.6 NUMA Penalty                                                                                           |       |  |  |  |  |  |

| 5.7 Limited Room for SMT                                                                                   |       |  |  |  |  |  |

| 5.8 Related Work                                                                                           |       |  |  |  |  |  |

| 5.9 Conclusion $\ldots$   | . 71  |  |  |  |  |  |

| 6 GAIL: Graph Algorithm Iron Law                                                                           | 73    |  |  |  |  |  |

| 6.1 Introduction $\ldots$ |       |  |  |  |  |  |

| 6.2 Graph Algorithm Iron Law                                                                               |       |  |  |  |  |  |

| 6.3 Case Studies Using GAIL                                                                                |       |  |  |  |  |  |

| 6.4 Using GAIL to Guide Development                                                                        |       |  |  |  |  |  |

| 6.5 Frequently Asked Questions                                                                             |       |  |  |  |  |  |

| 6.6 Conclusion $\ldots$   | . 87  |  |  |  |  |  |

| 7 Propagation Blocking                                                                                     | 89    |  |  |  |  |  |

| 7.1 Introduction $\ldots$ |       |  |  |  |  |  |

| 7.2 Background on PageRank                                                                                 |       |  |  |  |  |  |

| 7.3 Locality Challenges for PageRank                                                                       |       |  |  |  |  |  |

| 7.4 Propagation Blocking                                                                                   |       |  |  |  |  |  |

| 7.5 Communication Model                                                                                    |       |  |  |  |  |  |

| 7.6 Evaluation $\ldots$   |       |  |  |  |  |  |

| 7.7 Implementation Considerations                                                                          |       |  |  |  |  |  |

| 7.8 Related Work                                                                                           |       |  |  |  |  |  |

| 7.9 Conclusion $\ldots$   | . 110 |  |  |  |  |  |

| 8 Conclusion                                                                                               | 112   |  |  |  |  |  |

| 8.1 Summary of Contributions                                                                               | . 112 |  |  |  |  |  |

| 8.2 Future Work                                                                                            | . 113 |  |  |  |  |  |

| Bibliography                                                                                               | 116   |  |  |  |  |  |

| A Most Commonly Evaluated Graph Kernels                                                                    |       |  |  |  |  |  |

| A Most Commonly Evaluated Graph Kernels                                                                    | 131   |  |  |  |  |  |

# List of Figures

| 1.1          | Performance per core versus core count for June 2015 Graph 500 rankings [66].<br>Performance measures traversed edges per second (TEPS) executing breadth-first                                                                                                                                                                           |    |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | search                                                                                                                                                                                                                                                                                                                                    | 2  |

| 3.1          | Conventional BFS algorithm                                                                                                                                                                                                                                                                                                                | 15 |

| 3.2          | Single step of top-down approach. Vertex v unvisited if $parents[v] = -1$                                                                                                                                                                                                                                                                 | 15 |

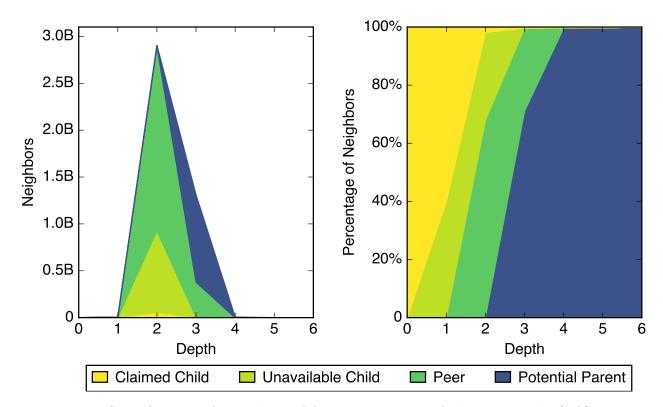

| 3.3          | Classification of neighbors of frontier in terms of absolute totals (left) or normal-<br>ized per depth (right) for a BFS traversal on kron graph (synthetically-generated<br>social network of 128M vertices and 2B undirected edges). A single undirected                                                                               |    |

|              | edge can result in two neighbors of the frontier if both endpoints are in the frontier.                                                                                                                                                                                                                                                   | 16 |

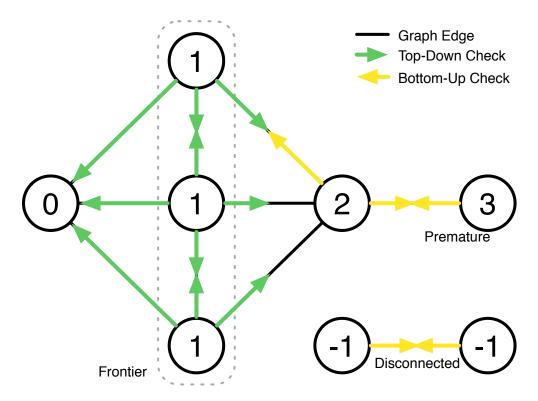

| 3.4          | Categorization of the neighbors of the highlighted vertex for an example BFS traversal. The vertices are labelled with their depths from the BFS, and the                                                                                                                                                                                 |    |

|              | arrows point from child to parent from the BFS                                                                                                                                                                                                                                                                                            | 16 |

| 3.5          | Single step of bottom-up approach                                                                                                                                                                                                                                                                                                         | 18 |

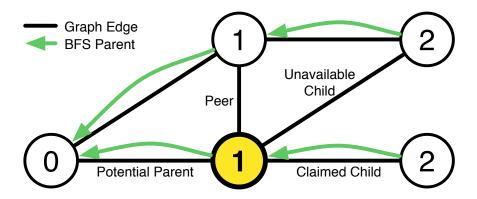

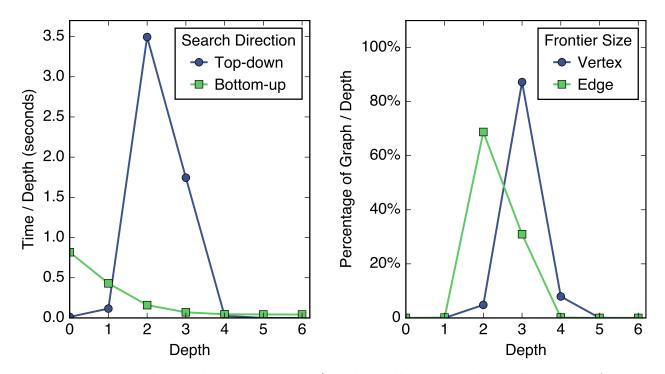

| 3.6          | Example search on kron graph (synthetically-generated social network of 128M                                                                                                                                                                                                                                                              |    |

|              | vertices and 2B undirected edges) on IVB platform from same source vertex as                                                                                                                                                                                                                                                              |    |

|              | Figure 3.3. The left subplot is the time per depth if done top-down or bottom-up                                                                                                                                                                                                                                                          |    |

|              | and the right subplot is the size of the frontier per depth in terms of either vertices                                                                                                                                                                                                                                                   |    |

|              | or edges. The time for the top-down approach closely tracks the number of edges<br>in the frontier, and depths 2 and 3 constitute the majority of the runtime since                                                                                                                                                                       |    |

|              | they constitute the majority of the edges                                                                                                                                                                                                                                                                                                 | 19 |

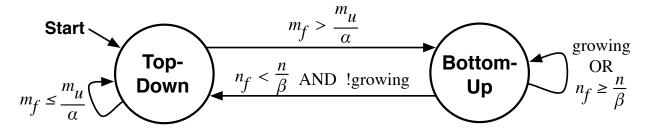

| 3.7          | Finite-state machine to control the direction-optimizing algorithm. When tran-<br>sitioning between approaches, the frontier must be converted from a queue (top-<br>down) to a bitmap (bottom-up) or vice versa. The growing condition indicates<br>the number of active vertices in the frontier $(n_f)$ increased relative to the last | 13 |

|              | depth                                                                                                                                                                                                                                                                                                                                     | 20 |

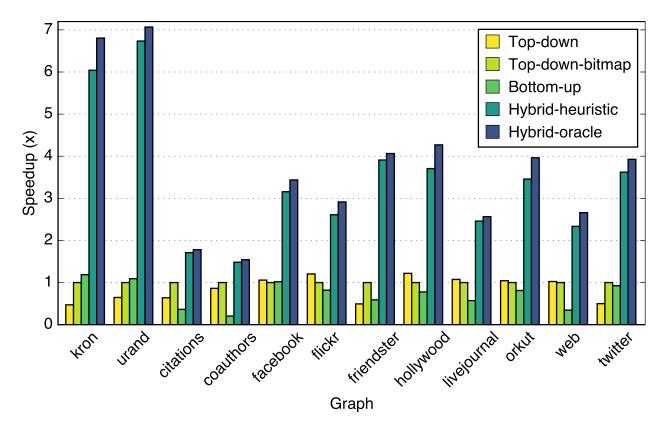

| $3.8 \\ 3.9$ | Speedups on IVB relative to top-down-bitmap                                                                                                                                                                                                                                                                                               | 23 |

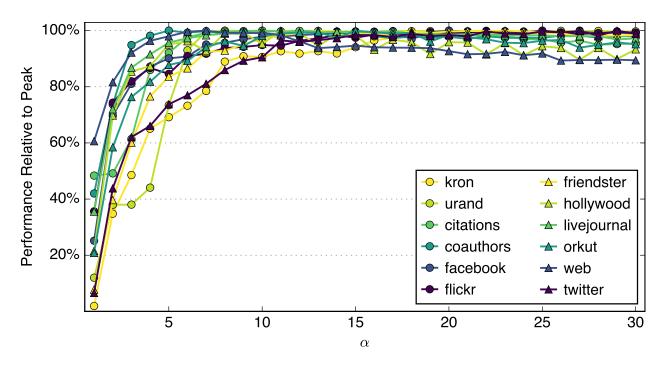

| 3.10         | that graph for the range of $\alpha$ examined. We select $\alpha = 15. \ldots \ldots \ldots$                                                                                                                                                                                                                                              | 25 |

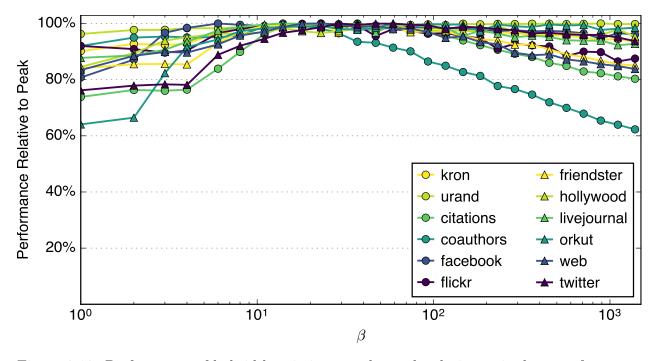

|              | that graph for the range of $\beta$ examined. We select $\beta = 18. \ldots \ldots \ldots$                                                                                                                                                                                                                                                | 25 |

| 3.11       | Comparison of edges examined by top-down and bottom-up on example graph<br>when frontier is at depth 1. Vertices labelled with their final depth                                                                                                                                                                                                                                                                    | 26             |

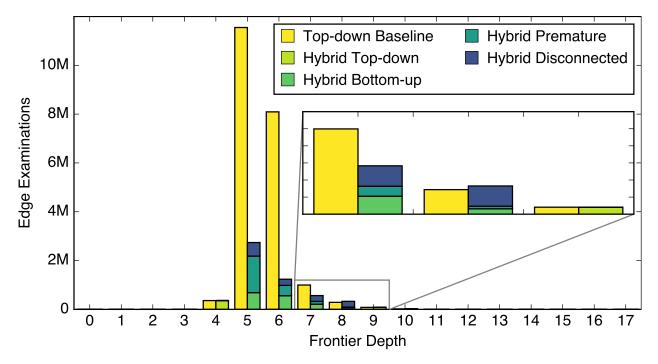

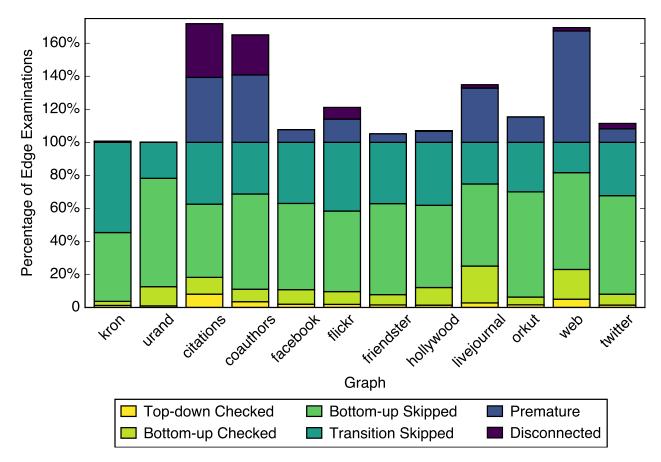

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.12       | Types of edge examinations for top-down versus direction-optimizing for a single search on flickr graph. The direction-optimizing approach switches to the bottom-up direction at depth 5 and back to the top-down direction at depth 9. Due to extremely small frontier sizes, depths 0–4 and 9–17 are difficult to distinguish, however, for these depths the direction-optimizing approach traverses in the top- |                |

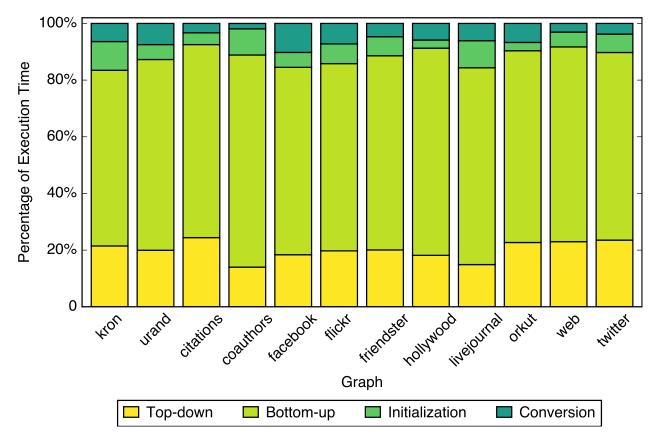

|            | Categorization of execution time by hybrid-heuristic                                                                                                                                                                                                                                                                                                                                                                | 27<br>28<br>29 |

|            | to top-down-bitmap baseline                                                                                                                                                                                                                                                                                                                                                                                         | 30             |

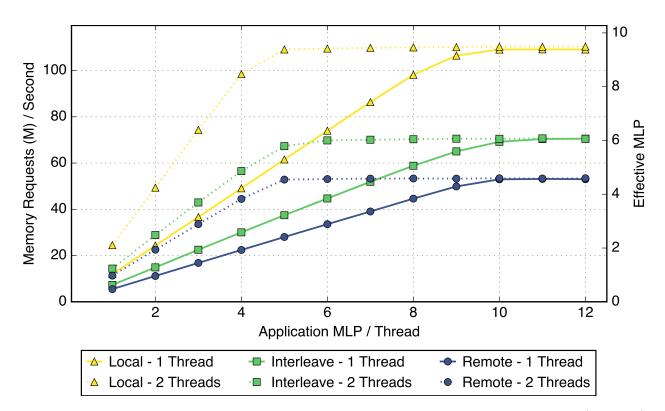

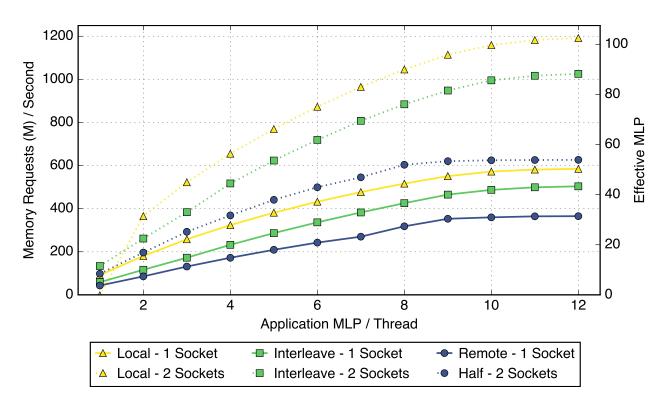

| 5.1<br>5.2 | Parallel pointer-chase microbenchmark for k-way MLP                                                                                                                                                                                                                                                                                                                                                                 | 53             |

|            | interleave).                                                                                                                                                                                                                                                                                                                                                                                                        | 54             |

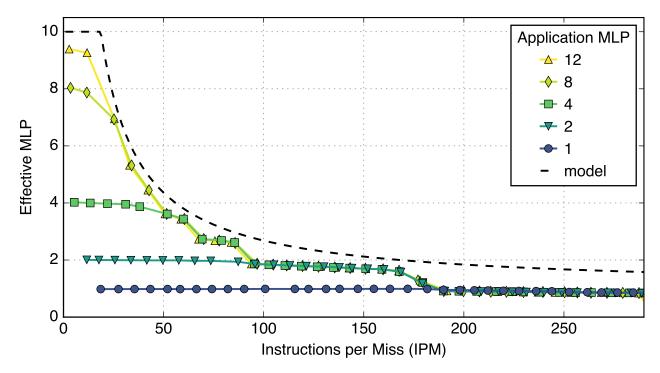

| 5.3        | Memory bandwidth achieved by parallel pointer chase microbenchmark with vary-<br>ing number of nops inserted (varies IPM). Using a single thread with differing                                                                                                                                                                                                                                                     |                |

| - 1        | numbers of parallel chases (application MLP).                                                                                                                                                                                                                                                                                                                                                                       | 55             |

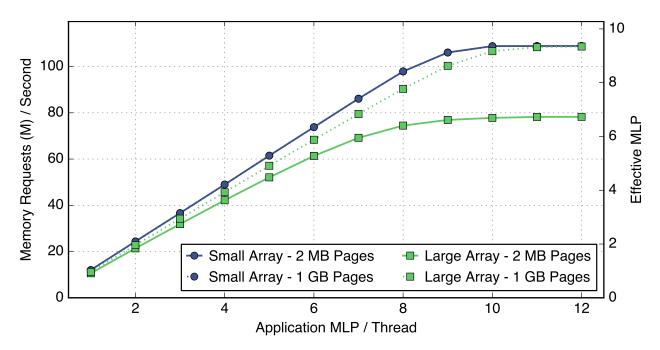

| 5.4        | Impact of 2 MB and 1 GB page sizes on memory bandwidth achieved by single-<br>thread parallel pointer chase for array sizes of <i>small</i> (1 GB) and <i>large</i> (16 GB).                                                                                                                                                                                                                                        | 56             |

| 5.5        | Random bandwidth of a socket or the whole system with different memory allo-<br>cations.                                                                                                                                                                                                                                                                                                                            | 57             |

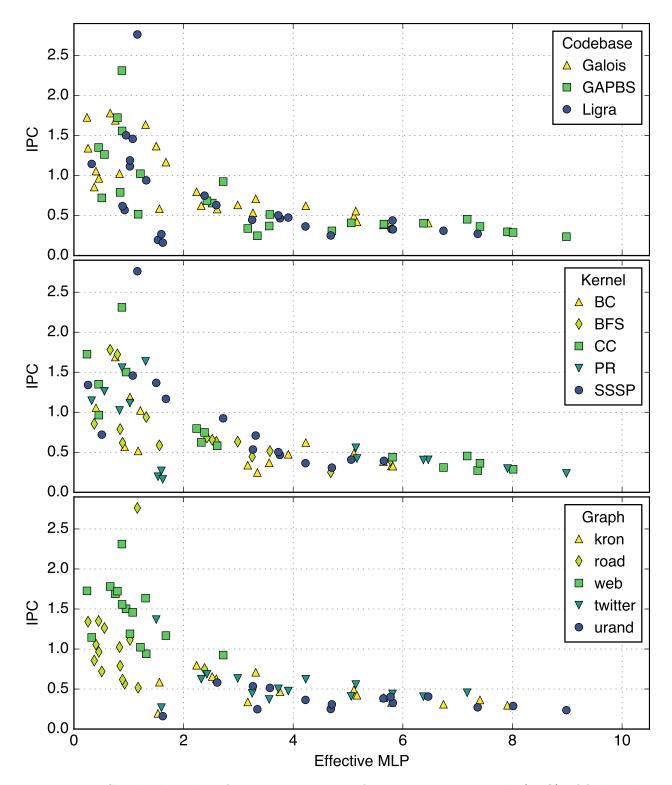

| 5.6        | Single-thread performance in terms of instructions per cycle (IPC) of full workload                                                                                                                                                                                                                                                                                                                                 |                |

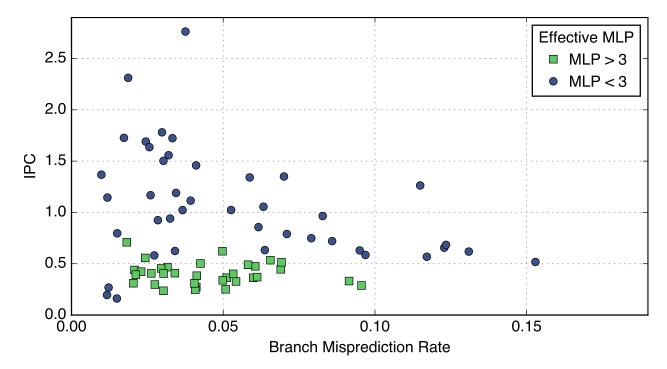

| 5.7        | colored by: codebase (top), kernel (middle), and input graph (bottom) Single-thread performance of full workload relative to branch misprediction rate                                                                                                                                                                                                                                                              | 58             |

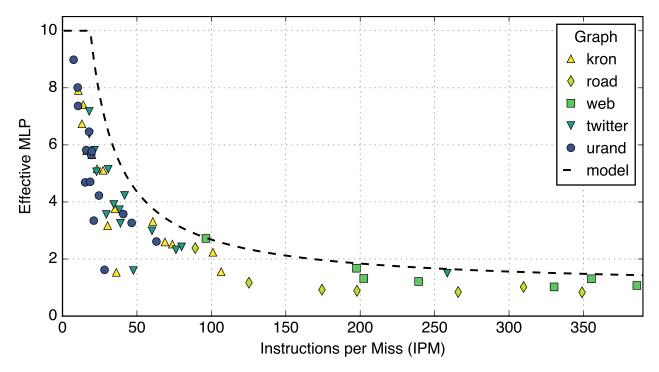

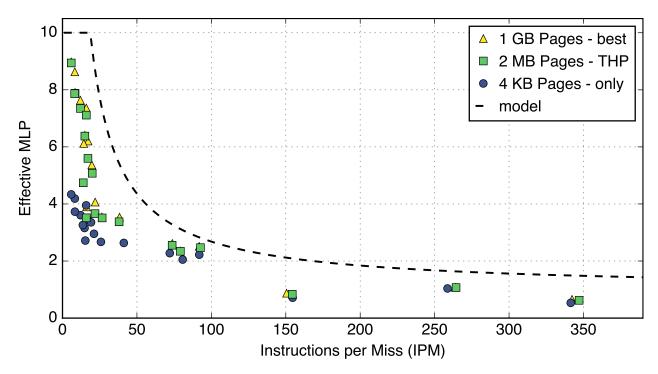

| 5.8        | colored by memory bandwidth utilization                                                                                                                                                                                                                                                                                                                                                                             | 59             |

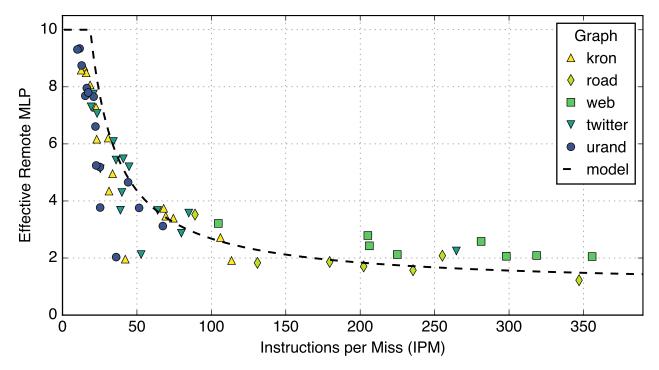

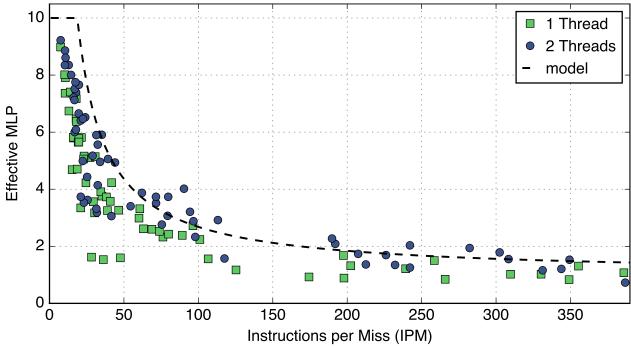

| 0.0        | per miss (IPM). Note: Some points from road $\mathcal{C}$ web not visible due to IPM>1000                                                                                                                                                                                                                                                                                                                           |                |

|            | but model continues to serve as an upper bound                                                                                                                                                                                                                                                                                                                                                                      | 60             |

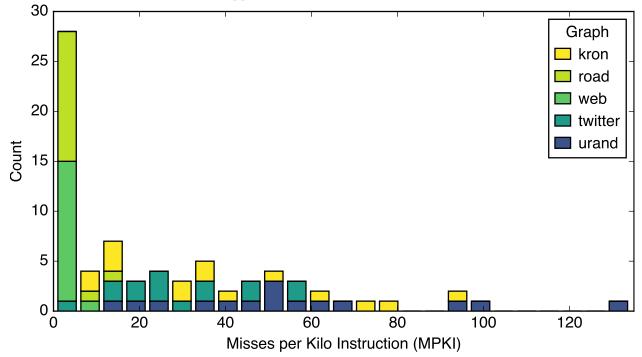

| 5.9        | Histogram of MPKI (in terms of LLC misses) of full workload specified in Sec-                                                                                                                                                                                                                                                                                                                                       |                |

|            | tion 5.2 executing on a single thread. Most executions have great locality (low MPKI), especially those processing the web or road input graphs.                                                                                                                                                                                                                                                                    | 60             |

| 5.10       | Single-thread achieved memory bandwidth of GAPBS for all kernels and graphs                                                                                                                                                                                                                                                                                                                                         | 00             |

|            | varying the operating system page size. 2MB Pages - THP uses Transparent                                                                                                                                                                                                                                                                                                                                            |                |

|            | Hugepages (THP) and lets the operating system choose to promote 4 KB to 2 MB                                                                                                                                                                                                                                                                                                                                        |                |

|            | pages (happens frequently). 1 GB Pages - best is the fastest execution using manually allocated 1 GB pages for the output array, the graph, or both                                                                                                                                                                                                                                                                 | 61             |

v

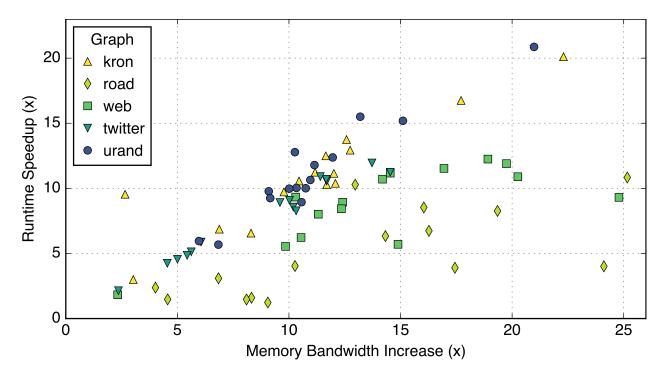

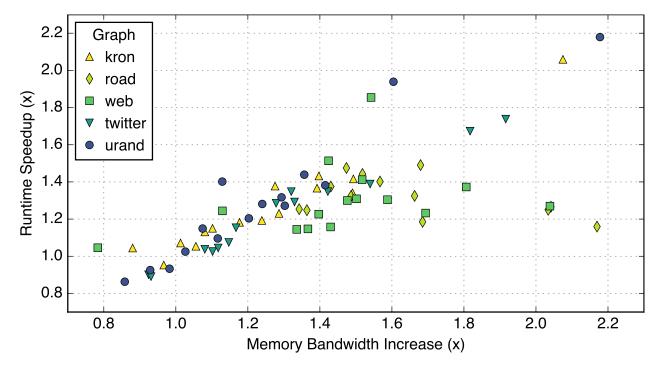

|      | Improvements in runtime and memory bandwidth utilization of full workload for full system (32 threads on 16 cores) relative to single thread performance                                                                                          | 63 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

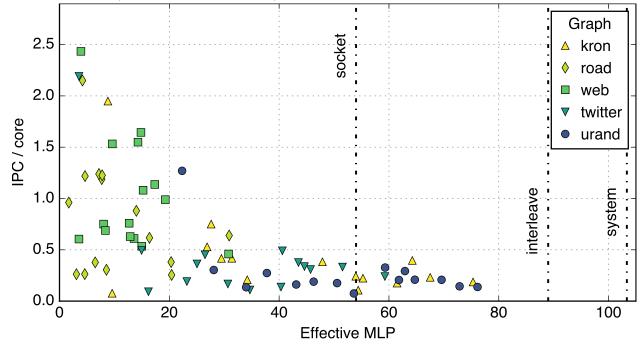

| 5.12 | Full system (32 threads on 16 cores) performance of full workload. Vertical lines are maximum achieved bandwidths (Section 5.3) for a single socket (socket), both                                                                                |    |

|      | sockets with interleaved memory (interleave), and both sockets with local memory                                                                                                                                                                  |    |

| 5.13 | (system)                                                                                                                                                                                                                                          | 63 |

|      | mote memory. Calculating effective MLP with remote memory latency (instead of local memory latency) returns a result similar to local memory results (Figure 5.8).                                                                                | 64 |

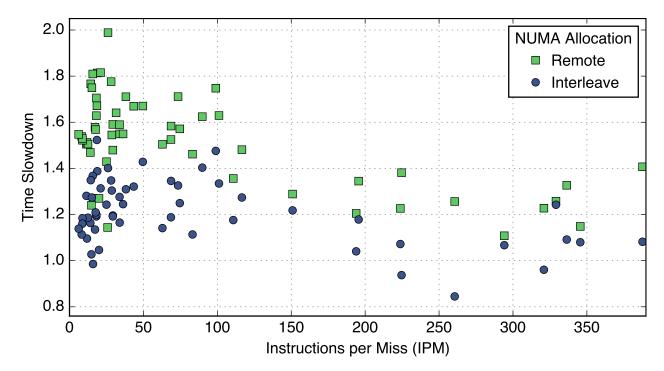

| 5.14 | Full workload slowdowns for single-socket (8 cores) executing out of remote mem-                                                                                                                                                                  | 04 |

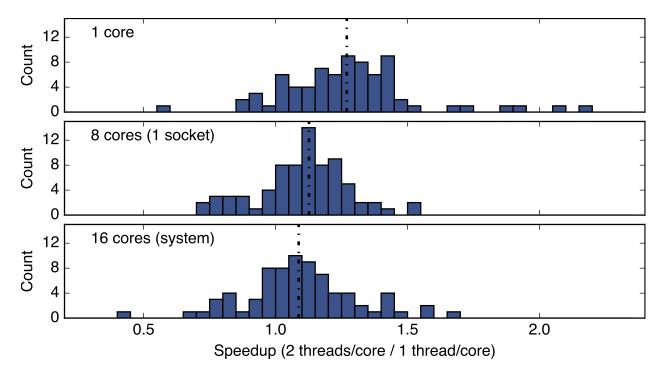

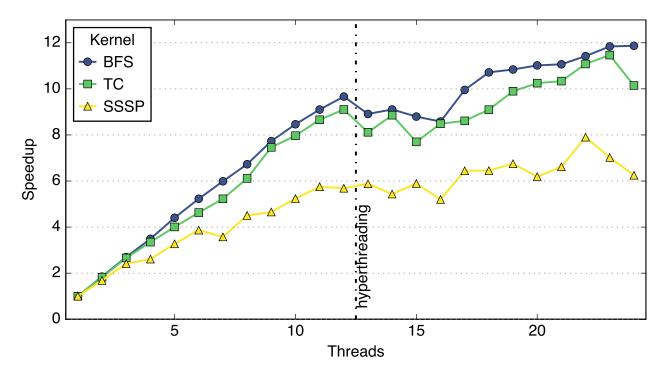

| 5 15 | ory or interleaved memory relative to executing out of local memory Distribution of speedups of using two threads per core relative to one thread                                                                                                 | 65 |

| 0.10 | per core of full workload for one core, one socket $(8 \text{ cores})$ , and whole system $(2$                                                                                                                                                    |    |

| 5.16 | sockets). Dotted line is median                                                                                                                                                                                                                   | 66 |

|      | one core using two threads relative to one thread                                                                                                                                                                                                 | 67 |

| 5.17 | Achieved memory bandwidth of full workload relative to instructions per miss (IPM) with one or two threads on one core.                                                                                                                           | 67 |

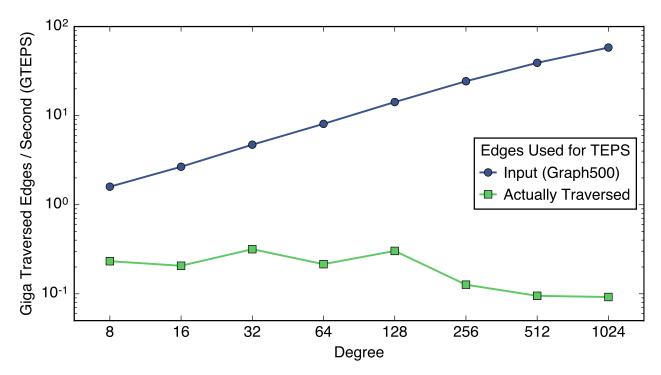

| 6.1  | Impact of calculating TEPS based on input edges or actual edges traversed when                                                                                                                                                                    |    |

|      | scaling the degree of a 8 million vertex synthetically-generated Kronecker graph.<br>Uses GAP direction-optimizing BFS implementation executing on IVB                                                                                            | 74 |

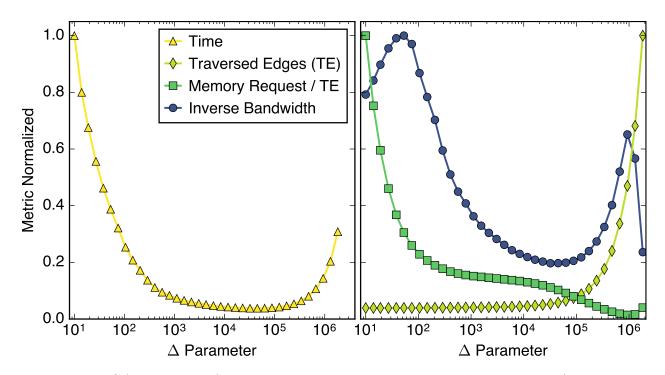

| 6.2  | GAIL metrics for delta-stepping implementation while varying $\Delta$ -parameter travers-<br>ing the road graph using 8-cores on the IVB platform. From the GAIL metrics,                                                                         | (4 |

|      | we see the U-shape in execution time is caused by the L-shape of the number of<br>memory requests per traversed edge and the backwards L-shape for the number                                                                                     |    |

| 6.0  | of traversed edges.                                                                                                                                                                                                                               | 80 |

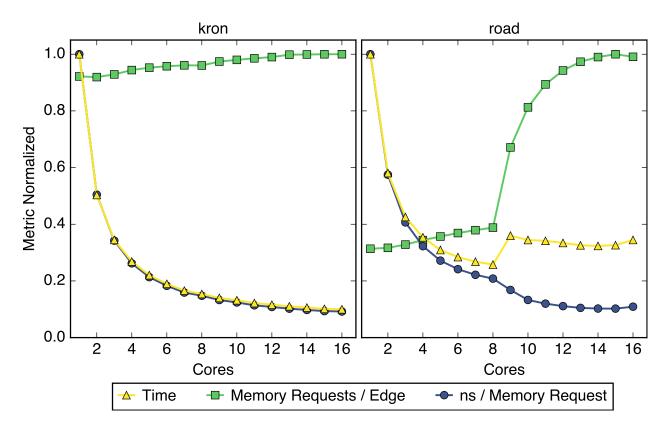

| 6.3  | GAIL metrics for strong scaling (varying number of cores utilized) on IVB for<br>direction-optimizing BFS implementation traversing the kron graph (left) and<br>the road graph (right). Since the implementation is deterministic, the traversed |    |

|      | edges GAIL metric is constant for each graph (not shown)                                                                                                                                                                                          | 82 |

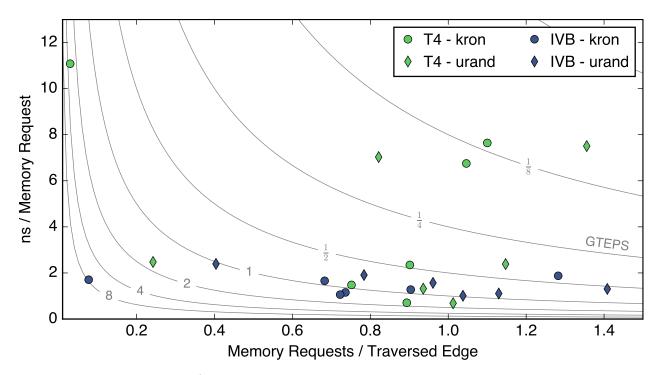

| 6.4  | GAIL metrics (memory requests per traversed edge versus inverse memory band-<br>width) for GAP Benchmark kernels executing on IVB and T4 to process the kron                                                                                      |    |

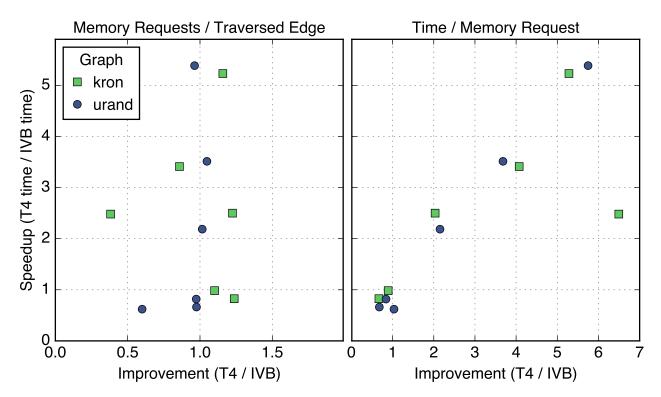

| 65   | and urand graphs. Contours show GTEPS for edges actually traversed Speedup of IVB over T4 versus IVB's improvement over T4 in GAIL metrics                                                                                                        | 83 |

| 6.5  | (memory requests per traversed edge versus inverse memory bandwidth) for GAP                                                                                                                                                                      |    |

|      | benchmark kernels processing the kron and urand graphs.                                                                                                                                                                                           | 85 |

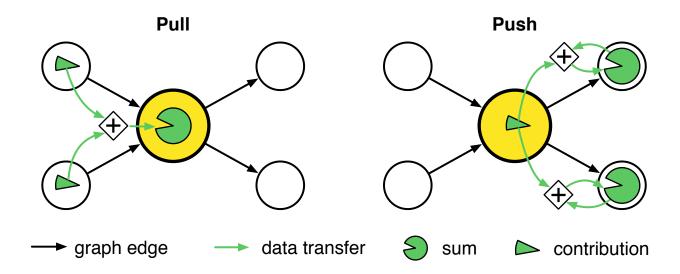

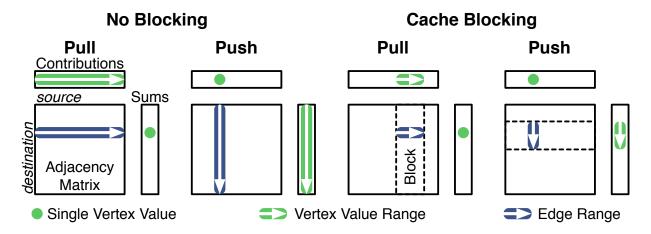

| 7.1  | PageRank communication for pull direction (left) and push direction (right). In<br>the pull direction, the active vertex (shaded) reads the contributions of its incom-                                                                           |    |

|      | ing neighbors and adds them to its own sum. In the push direction, the active vertex adds its contribution to the sums of its outgoing neighbors                                                                                                  | 91 |

|      |                                                                                                                                                                                                                                                   |    |

| 7.2  | PageRank implemented in both directions                                            | 92  |

|------|------------------------------------------------------------------------------------|-----|

| 7.3  | Accesses needed to process one vertex and its neighbors for PageRank, with or      |     |

|      | without 1D cache blocking for both pull (row-major) and push (column-major)        |     |

|      | directions. All approaches enjoy high locality when accessing the adjacency ma-    |     |

|      | trix (edge traffic). The vertex value arrays (contributions or sums) are much      |     |

|      | larger than the cache size, and thus accessing a sparse range within them could    |     |

|      | have low locality. Without blocking (left), one vertex value access obtains high   |     |

|      | locality at the expense of the other. Pull has high temporal locality on the sums, |     |

|      | but low locality reading the contributions. Push has high locality reading the     |     |

|      | contributions, but low locality for the sums. Cache blocking (right) reduces the   |     |

|      | range of vertex values to the current block in order to improve locality           | 93  |

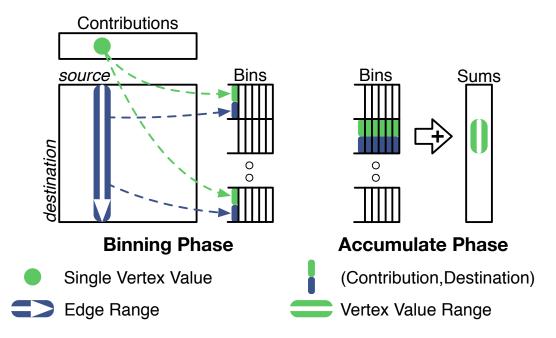

| 7.4  | Propagation blocking. In the binning phase, vertices pair their contributions      |     |

|      | with their destination indices and insert them into the appropriate bins. In the   |     |

|      | accumulate phase, the contributions are reduced into the correct sums              | 95  |

| 7.5  | PageRank by propagation blocking                                                   | 96  |

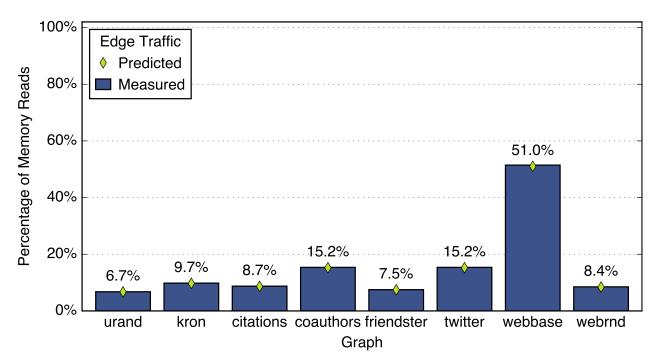

| 7.6  | Fraction of read memory traffic to read graph from CSR                             | 102 |

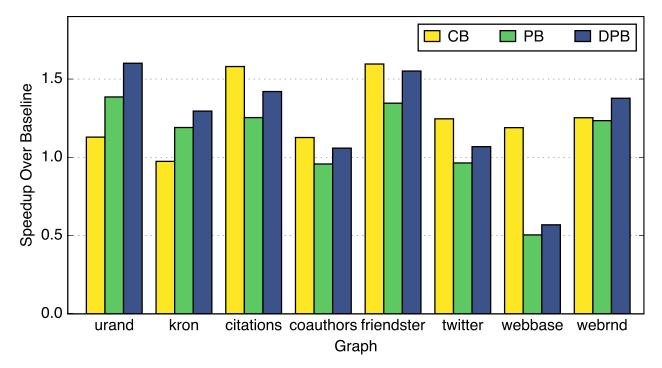

| 7.7  | Execution time improvement over baseline                                           | 104 |

| 7.8  | Communication reduction over baseline                                              | 104 |

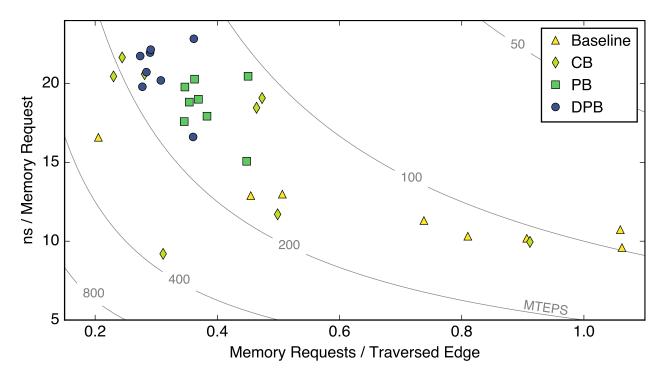

| 7.9  | GAIL metrics across benchmark suite. Traversed edge totals not shown since         |     |

|      | equal for all implementations. Contours represent millions of traversed edges per  |     |

|      | second (MTEPS), so processing rates increase toward the origin                     | 105 |

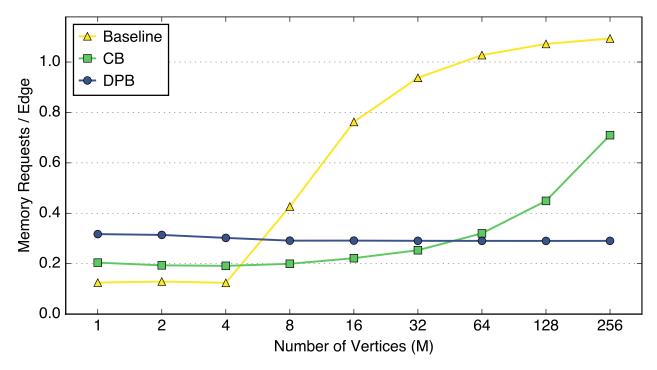

| 7.10 | Communication efficiency for varying number of vertices of a degree=16 uniform     |     |

|      | random graph                                                                       | 106 |

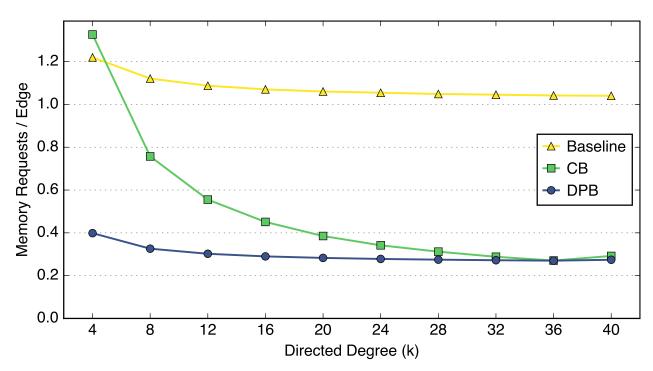

| 7.11 | Communication efficiency for varying degree of a 128M vertex uniform random        |     |

|      | graph                                                                              | 106 |

|      | Bin width impact on total memory communication for DPB by graph                    | 108 |

| 7.13 | Bin width impact on execution time for DPB by graph                                | 108 |

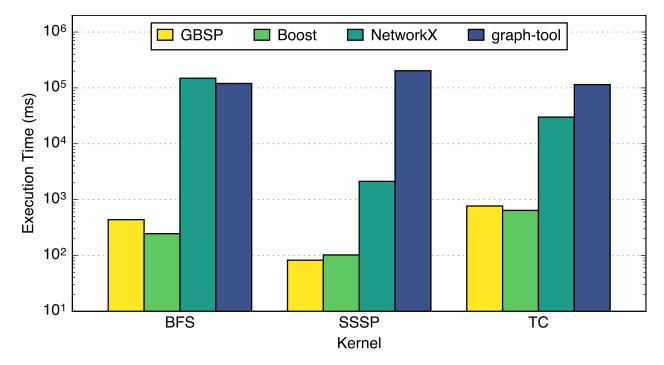

| B.1  | Single-threaded performance comparison                                             | 137 |

| B.2  | GBSP parallel strong-scaling speedup relative to single-threaded performance       | 137 |

|      |                                                                                    | -   |

# List of Tables

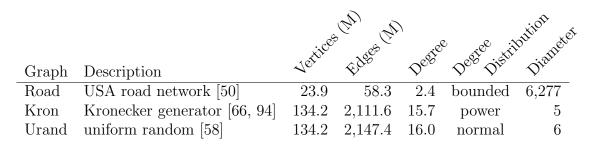

| 2.1<br>2.2                                                                                | Graphs used for evaluation. All of the graphs come from real-world data except<br>kron and urand. In subsequent chapters, we list the subsets of these graphs we use<br>Number of graph framework evaluations using each graph algorithm, categorized<br>by hardware platform. Only 12 most commonly evaluated algorithms are shown.<br>See Appendix A for more information on survey of graph processing frameworks. | e. 8<br>9                |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 0.1                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                        |

| 3.1<br>3.2                                                                                | Low-diameter graphs used for evaluation. All of the graphs come from real-worlddata except kron and urand.IVB system specifications                                                                                                                                                                                                                                                                                   | 21<br>21                 |

| 4.1                                                                                       | Trial counts and output formats for benchmark kernels                                                                                                                                                                                                                                                                                                                                                                 | 44                       |

| $5.1 \\ 5.2 \\ 5.3$                                                                       | Graphs used for characterization                                                                                                                                                                                                                                                                                                                                                                                      | 50<br>51<br>70           |

| $     \begin{array}{r}       6.1 \\       6.2 \\       6.3 \\       6.4     \end{array} $ | Graphs used for case studies                                                                                                                                                                                                                                                                                                                                                                                          | 77<br>78<br>78<br>84     |

| <ul><li>7.1</li><li>7.2</li><li>7.3</li><li>7.4</li></ul>                                 | Graphs used for evaluation. All of the graphs come from real-world data except kron and urand. The kron, urand, and twitter graphs are also in our GAP Benchmark Suite                                                                                                                                                                                                                                                | 100<br>100<br>101<br>102 |

| A.1                                                                                       | Graph kernels used in framework evaluations                                                                                                                                                                                                                                                                                                                                                                           | 132                      |

| B.1                                                                                       | Workload (graph kernels with their input graphs) for evaluation                                                                                                                                                                                                                                                                                                                                                       | 136                      |

#### Acknowledgments

Many people enriched the amazing learning experience I had during my years at UC Berkeley.

First, I would like to thank my co-advisors Krste Asanović and David Patterson. They have been a great advising team, and together, they provided me with wonderful opportunities and invaluable lessons. Krste gave me tremendous freedom and encouraged me to go out and measure and build things. Dave repeatedly taught me not only the lesson of keeping things simple, but also the importance of being able to simply explain an idea. Difficulty explaining an idea simply is an indication that more effort may be required by the explainer to distill the key insight. I would also like to acknowledge the gracious assistance from the rest of my dissertation committee members, James Demmel and Dorit Hochbaum. Jim provided useful information on sparse linear algebra, and Dorit provided helpful critiques.

I'm especially indebted to the great colleagues I had the pleasure of working with throughout my studies. Sarah Bird and Henry Cook were the other computer architecture students in my incoming cohort, and I could not have asked for better company during the long journey. The other Cosmic Cube co-inhabitants Andrew Waterman and Chris Celio provided camaraderie, thoughtful advice, and essential feedback on early ideas. The architecture group has a contagious energy, and I want to acknowledge the other barchitects: Rimas Avižienis, Yunsup Lee, Eric Love, Martin Maas, Adam Izraelevitz, Colin Schmidt, Palmer, Dabbelt, Sagar Karandikar, Donggyu Kim, Jack Koenig, David Biancolin, Albert Magyar, Brian Zimmer, and Ben Keller. The senior students Zhangxi Tan and Heidi Pan set great examples and offered useful advice.

The ParLab introduced me to superb colleagues. Chris Batten was a fantastic mentor and collaborator during the beginning of my graduate studies. Andrew Gearhart provided crucial expertise on the inner workings of Intel performance counters. Shoaib Kamil was a terrific collaborator on the SEJITS effort. Sam Williams provided a deep understanding of multicore performance optimizations. My interactions with Leo Meyerovich led to my dissertation topic. I originally wanted to build a web browser hardware accelerator, but the tree traversals within Leo's parallel page layout code motivated me to consider graph algorithms.

I am grateful to have been a member of both the ParLab and the ASPIRE Lab and for the financial support their sponsors provided. The labs have a sensational support staff that eased or even enabled much of my research. Kostadin Ilov and Jon Kuroda's technical support was indispensable, and they gracefully handled odd requests and pre-production hardware with ease. Tami Chouteau and Roxana Infante skillfully kept the labs and all other matters running smoothly. I am also appreciative of the advice and collaborations provided by other faculty within the labs from Armando Fox, Jonathan Bachrach, and Vladimir Stojanović.

I am thankful for the patience and willingness to help from the members of the graph research community. Aydın Buluç has been a great collaborator and resource for learning more about graph algorithms and their application. Kamesh Madduri taught me much about graph processing, especially when I was just getting started. Jason Riedy continually teaches me new things about graphs and provided access to the mirasol platform.

I want to recognize those that helped guide me throughout my time at Berkeley, including the time before I even attended graduate school. Dan Garcia infected me with not only an excitement for teaching, but also an excitement for computer architecture, which became the focus of my graduate studies. Sheila Humphreys has always been a wonderful resource and a great supporter.

I am also grateful for support from the community outside of the university. Friends and ultimate frisbee teammates helped make everything more worthwhile. I want to thank Zeph Landau for being a great teammate, coach, friend, and mentor. My family has always placed a high value on education, and they provided me with continual encouragement, especially when it was most needed. Kim Long provided both resiliency and inspiration, and getting to know her has been the best part of the last three years.

# Chapter 1 Introduction

Graphs represent connections, and graphs can be used to represent many types of connections in the real world, whether it be friendships between humans or road segments between street intersections. The strength of the graph abstraction is that it allows the same graph algorithms to be reused to process a diverse range of graphs, thus enabling a diverse range of applications. Although the graph abstraction has been used for centuries, there is a renewed interest in graph processing driven in large part by emerging applications in social network analysis [91, 110, 170], science [132], and speech and image recognition [96, 174]. To better support these increasingly relevant graph processing applications, research is ongoing at all levels, including applications, algorithms, implementations, frameworks, and even hardware platforms.

Unfortunately, graph algorithms are notoriously difficult to execute efficiently on current processors [98], and so there has been considerable recent effort to improve the performance of processing large graphs. The connection-centric nature of graph processing results in a communication-centric workload that often has low arithmetic intensity. On a shared memory multiprocessor, graph processing can often simultaneously underutilize both the compute throughput and the memory bandwidth. Such low utilization provides a tremendous opportunity, as it increases the potential speedup possible with a better-utilized similarly-sized hardware platform.

In this dissertation, we strive to understand graph algorithm performance in order to improve performance. To understand graph algorithm performance, we characterize graph processing workloads on real hardware. By understanding how graph algorithm software implementations interact with hardware platforms, we can improve efficiency. Changes to an algorithm can not only impact the amount of algorithmic work, but also change which hardware bottlenecks constrict performance. To help others improve graph algorithm performance via a better understanding of performance, we leverage our workload characterization to contribute a benchmark suite and a simple performance model to reason across abstraction layers. To improve performance, we also provide a novel breadth-first search algorithm that is advantageous for low-diameter graphs and an implementation technique to reduce memory communication on cache-based systems.

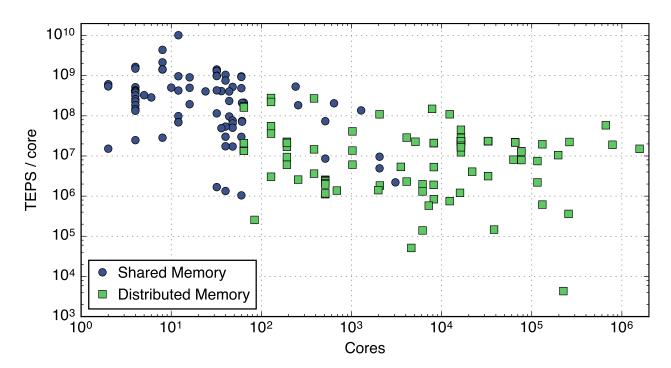

Figure 1.1: Performance per core versus core count for June 2015 Graph 500 rankings [66]. Performance measures traversed edges per second (TEPS) executing breadth-first search.

### 1.1 Focus on Shared Memory Multiprocessor Systems

We focus on single-node shared memory systems for this work. Graph processing research is ongoing for a variety of hardware platforms, such as clusters, semi-external memory systems, and even GPU-based systems, but many of these platforms are built from multiprocessor systems. Analyzing and improving multiprocessor systems first should immediately benefit the other platforms that are built from multiprocessors. Furthermore, we argue multiprocessor systems are well suited for many graph processing applications.

A large cluster is the typical tool for large computational problems, but graph processing frequently exacerbates the communication bottlenecks of large clusters. Since the interprocessor network of a distributed memory cluster is substantially slower than that of a shared memory multiprocessor system, clusters obtain substantially less performance per core for graph processing. For example, on Graph 500 [66], a world ranking of the fastest supercomputers for graph algorithms, the performance per core of distributed memory systems is often one to two orders-of-magnitude lower than that of shared memory systems (Figure 1.1). The high core count shared memory systems are implemented with interconnects similar to cluster interconnects, and their performance is similarly bottlenecked. This communicationbound behavior has led to surprising results, where a single Mac Mini operating on a large graph stored in an SSD is able to outperform a medium-sized cluster [92]. Due to the inefficiency of distributed graph processing, the primary reason to use a cluster for graph processing is if the data is too large to fit on a single node [105]. However, many interesting graph problems are not large enough to justify a cluster. For example, the entire Facebook friend graph can be held in only a few terabytes of uncompressed data [8], which can reside in a current high-end server's memory. Additionally, semi-external memory approaches that expand a server's capacity by using storage (flash or hard drives), are a much more economical means to handle larger problems. Multiprocessor systems have additional benefits, as they are easier to program than the other platforms, and their flexibility allows them to implement the most sophisticated optimized algorithms. For graph processing, multiprocessor systems are surprisingly capable systems that deliver robust performance.

### 1.2 Thesis Overview

In Chapter 2, we provide context for this work. We review our graph terminology to familiarize the reader with our notation. We also introduce the graphs we use and highlight their relevant topological properties. Finally, we survey graph processing research to identify the most commonly evaluated graph kernels that will constitute our workload for analysis.

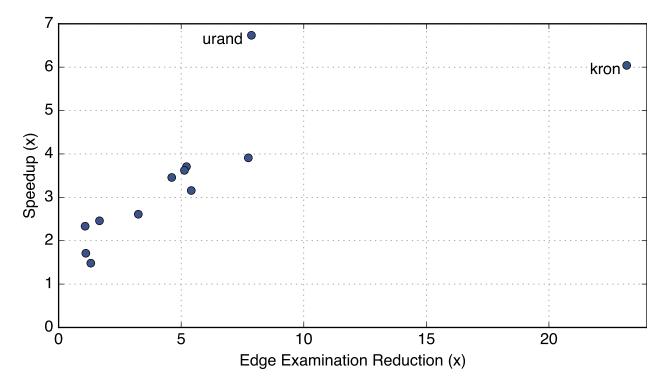

Breadth-first search is a commonly used graph traversal within other algorithms, and in Chapter 3, we introduce our novel direction-optimizing breadth-first search algorithm. Our algorithm has been widely adopted, both by graph processing frameworks and within the Graph 500 competition. On low diameter graphs, our algorithm is able to avoid traversing a large fraction of the graph while still producing the correct result. In practice on real hardware, the speedup obtained by our algorithm is substantially less than the reduction in edges examined, which implies that the implementation of our algorithm is less efficient per traversed edge than our conventional baseline. This loss of efficiency motivates the rest of this work, as an algorithmic improvement resulted in substantial efficiency degradation on current hardware.

To characterize graph algorithms as a workload, we first need a workload to analyze. In Chapter 4, we introduce our GAP Benchmark Suite. We created the benchmark not only to create a workload for our own analysis, but also to help ameliorate the evaluation pitfalls we observe in graph processing research. With our benchmark suite, we hope to guide the community away from common evaluation mistakes such as using too few kernels, using too few input graphs, using input graphs that are too small, using only synthetically generated graphs, or inconsistent methodologies. In addition to a specification of our benchmark, we also provide a high-quality reference implementation for use as a baseline for evaluations.

In Chapter 5, we characterize the workload specified by our benchmark on real hardware. To identify hardware bottlenecks, we access our platform's performance counters to measure utilizations throughout the system. We use a simple model and synthetic microbenchmarks to establish how much memory bandwidth is available on our evaluation platform under various conditions. With this insight into the platform's available memory bandwidth, we observe that contrary to conventional wisdom, graph algorithms are typically not memory bandwidth-bound. We find this low bandwidth utilization is due in large part to the cache hierarchy delivering a substantial number of cache hits.

To ease reasoning about graph algorithm performance, in Chapter 6 we introduce the Graph Algorithm Iron Law (GAIL). GAIL is a simple performance model that attributes performance differences to changes in algorithmic work, cache utility, or memory bandwidth utilization. Using GAIL, we perform a variety of case studies including analyzing our direction-optimizing breadth-first search algorithm. We determine our breadth-first search algorithm is less efficient per edge because it has worse cache locality and lower memory bandwidth utilization. In the chapter, we also argue how GAIL could be useful to a variety of graph researchers, as it can help weigh tradeoffs between algorithms, implementation decisions, and hardware platforms.

To reduce memory communication for graph algorithms, in Chapter 7 we introduce propagation blocking. Our technique is motivated by the observation that communication behavior for graph algorithms is different when accessing values associated with vertices versus accessing graph edges. Our propagation-blocking technique is designed to improve poor spatial locality when accessing vertex values. Despite performing more theoretical communication, our propagation-blocking technique achieves reductions in memory communication on real hardware.

In Chapter 8 we not only conclude this work by summarizing its contributions, but also suggest potential future work based on the results of this dissertation.

# Chapter 2

# **Background on Graph Algorithms**

In this chapter, we provide a background on graph processing in order to provide context for the rest of this work. We review the terminology and notation we use to describe graphs. We also introduce the input graphs we use for evaluations, and we highlight their relevant topological properties. Finally, we describe the graph kernels we use and our justification for selecting them based on their popularity in prior work.

### 2.1 The Graph Abstraction

The graph abstraction is a way to model the connections between objects and the nature of these connections can have many properties. More formally, a graph G(V, E) is composed of a set of vertices V and a set of edges E. An edge (u, v) connects the two vertices u and v. A directed edge (u, v) represents a connection from u to v, while an undirected edge represents a bidirectional connection. If a graph is composed exclusively of undirected edges, it is an undirected graph, otherwise, it is a directed graph. The degree of a vertex is the number of edges connected to it. The degree of a graph is the average degree of all of its vertices (|E|/|V|). To capture the diversity of vertex degrees within a graph, the degree distribution is the distribution of degrees over the vertices within a graph.

The distance d(u, v) between vertex u and vertex v is the fewest number of hops between u to v. The depth of a vertex is the distance between a vertex and a starting source vertex of a traversal. The diameter of a graph is the largest distance between any two vertices in the graph. More informally, diameter often refers to the largest distance that is typical when ignoring outliers. In this work, we use the  $99^{th}$ -percentile distance to define our effective diameter.

Most graph algorithms operate on more than connectivity information and they associate metadata with vertices and edges. For example, many traversal algorithms associate a boolean value with each vertex indicating if it has been visited. A weighted edge (u, v, w)associates a numerical cost w with traversing the edge and a weighted graph is composed of weighted edges. The distance d(u, v) between vertex u and vertex v in a weighted graph is the sum of the edge weights of the minimum total weight path between u and v.

We use some notation to enable concise expressions in this work. We use n and m to refer to the number of vertices (|V|) and the number of edges (|E|) respectively. We use k = m/n to represent a graph's average degree. The set of vertices directly reachable from vertex v (outgoing neighborhood) is  $N^+(v)$  and the set of vertices with edges pointing to vertex v (incoming neighborhood) is  $N^-(v)$ . If the graph is undirected, both neighborhoods are the same  $N^+(v) = N^-(v)$ .

# 2.2 Topological Properties of Graphs

Graph applications are characterized not only by the algorithms used, but also by the structure of the graphs that make up their workload. In this work, we divide commonly used graphs into two broad categories named for their most emblematic members: *meshes* and *social networks* [16]. Meshes tend to be derived from physically spatial sources, such as road maps or the finite-element mesh of a simulated car body, so they can be relatively readily partitioned along the few original spatial dimensions. Due to their physical origin, they usually have a high diameter and a degree distribution that is both bounded and low.

Conversely, social networks come from non-spatial sources, and consequently are difficult to partition using any reasonable number of dimensions. Additionally, social networks have a low diameter ("small-world") and a power-law degree distribution ("scale-free"). In a *smallworld graph*, most vertices are not neighbors of one another, but most vertices can be reached from every other by a small number of hops [160]. More quantitatively, a small-world graph can be recognized by a low diameter. A *scale-free graph* has a degree distribution that follows a power law, at least asymptotically [14]. The fraction of vertices in a scale-free graph having k connections to other vertices is  $P(k) \sim k^{-\gamma}$ , where  $\gamma$  is a parameter typically in the range  $2 < \gamma < 3$ . These two properties can be readily recognized in real life social networks, as typically only a few people have many friendships (scale-free), and a surprisingly low number of friendships connects any two people (small-world) [109].

Meshes are perhaps the most common mental model for graphs, since they are typically used in textbook figures. Unfortunately, they do not capture the challenges posed by the small-world and scale-free properties of social network topologies. The small-world property makes them difficult to partition (few cut edges relative to enclosed edges), while the scalefree property makes it difficult to load balance a parallel execution since there can be many orders of magnitude difference between the work for different vertices. Although the highest degree vertices are rare, their incident edges constitute a large fraction of the graph.

A graph's *sparsity* is determined by its average degree. If vertices are connected to nearly every other vertex, it is a *dense graph*. If vertices are connected to only a few other vertices, it is a *sparse graph*. There is no specific degree cutoff between sparse graphs and dense graphs, but for a graph of *n* vertices, a dense graph has  $O(n^2)$  edges (the maximum) while a sparse graph has O(n) edges. This work restricts itself to sparse graphs since they are used in more emerging graph processing applications and because processing sparse graphs incurs greater communication inefficiencies.

### 2.3 Graphs in this Work

In this work, we use the diverse set of graphs listed in Table 2.1 to guide our investigations. In Chapter 5, we demonstrate that it is important to have a diverse set of graphs, as a graph's topology greatly impacts the workload's characteristics. To keep our work relevant, most of our graphs are generated from real-world datasets. We primarily focus on social network topologies, as they are more challenging than meshes and they are at the epicenter of the renewed interest in graph processing.

The real-world data we use to generate our graphs comes from a variety of sources. Real-world social network data is often difficult to obtain due to anonymity concerns, so we are grateful for the publicly available real-world data we are able to use. The graphs facebook, flickr, friendster, livejournal, orkut, and twitter all represent the links between users on their respective online communities. In addition to considering social relationships, we also consider professional relationships with the hollywood graph that represents film actors and links them if they have performed together. Using the data on academic publications provided by the Microsoft Academic Graph [149], we generate a graph of all paper citations and a graph of all coauthorships. We also include two graphs (web and webbase) generated from web crawls that represent hyperlinks between websites. All of the real-world graphs in this study except the road graph have the social network topology, as they have low effective diameters and a power-law degree distribution. To contrast with the social networks, we include the road graph as an example of a mesh topology with its high diameter, low average degree, and low maximum degree.

Even though our graph suite includes some of the largest publicly available real-world graphs, they do not fully use the memory capacity of our evaluation system. As is done in the Graph 500 benchmark, we synthetically generate arbitrarily large graphs to fill our memory capacity. We generate the kron graph from the Kronecker generator [94] and we generate the urand graph from a uniform random graph generator [58]. We use the kron graph to model a social network and we select the generator parameters to match those of Graph 500 [66]. The urand graph has no locality by design, however, it is also the most unrealistic and serves to discover lower bounds of performance. The urand graph generates the desired number of edges by giving each generated edge an equal probability of connecting any two vertices. Hence, in our urand graph, each vertex tends to be accessed roughly the same number of times, unlike social networks in which the scale-free property causes a few vertices to be accessed disproportionately often. Since urand is generated to be the same size as kron, contrasting the two graphs allows us to observe the impact of the scale-free property.

|             |                                   | ç       | Edges on    | ١     | 2     | ર્ક ુટે      |

|-------------|-----------------------------------|---------|-------------|-------|-------|--------------|

| Graph       | Description                       | Vertice | Edges       | Degle | Diame | Directic     |

| Kron        | Kronecker generator [66, 94]      | 134.2   | 2,111.6     | 15.7  | 5     |              |

| Urand       | uniform random [58]               | 134.2   | $2,\!147.4$ | 16.0  | 6     |              |

| Citations   | academic citations [149]          | 49.8    | 949.6       | 19.0  | 12    | $\checkmark$ |

| Coauthors   | academic coauthorships [149]      | 119.9   | 646.9       | 5.4   | 10    |              |

| Facebook    | social network [163]              | 3.0     | 28.3        | 9.2   | 6     |              |

| Flickr      | social network [110]              | 1.8     | 22.6        | 12.2  | 12    | $\checkmark$ |

| Friendster  | social network [170]              | 124.8   | $1,\!806.1$ | 14.5  | 7     |              |

| Hollywood   | movie collaborations [27, 28, 47] | 1.1     | 57.5        | 50.5  | 5     |              |

| LiveJournal | social network [110]              | 5.3     | 79.0        | 14.7  | 9     | $\checkmark$ |

| Orkut       | social network [110]              | 3.0     | 223.5       | 72.8  | 5     |              |

| Road        | USA road network [50]             | 23.9    | 58.3        | 2.4   | 6,277 | $\checkmark$ |

| Twitter     | social network [91]               | 61.5    | $1,\!468.3$ | 23.8  | 7     | $\checkmark$ |

| Web         | crawl of .sk domain $[47]$        | 50.6    | $1,\!949.4$ | 38.5  | 13    | $\checkmark$ |

| WebBase     | 2001 web crawl [47]               | 118.1   | 632.1       | 5.4   | 16    | $\checkmark$ |

Table 2.1: Graphs used for evaluation. All of the graphs come from real-world data except kron and urand. In subsequent chapters, we list the subsets of these graphs we use.

# 2.4 Graph Algorithms in this Work

In this work, we analyze six graph kernels, and we select them based on their popularity in graph processing framework research evaluations (Table 2.2). For more information on the frameworks we survey, please consult Appendix A. Broadly speaking, the kernels we use can be categorized as either traversal-centric or compute-centric. *Traversal-centric* kernels (BFS, SSSP, and BC) start from a given source vertex and perform their computation outwards from the source vertex. *Compute-centric* kernels (PR, CC, and TC) receive no source vertex as input and operate on the entire graph in parallel.

#### • Breadth-First Search (BFS)

BFS is not even a graph algorithm, but is only a graph traversal order. It is commonly used within other graph algorithms, but BFS can be turned into an algorithm by tracking information related to the traversal. BFS traverses all vertices at one depth before moving onto the next depth. We analyze BFS thoroughly in Chapter 3.

#### • Single-Source Shortest Paths (SSSP)

SSSP returns the distances of shortest paths from a given source vertex to every other reachable vertex. SSSP typically operates on weighted graphs, so the shortest paths consider the edge weights. In this work, we restrict ourselves to non-negative edge

| Platform             | Total | PageRank | Single-source Shortest Paths | Connected Components | Breadth-first Search | Triangle Counting | Betweenness Centrality | Conductance | n-Hop Queries | Alternating Least Squares | Strongly Connected Component | Approximate Diameter | Random Walk Sampling |

|----------------------|-------|----------|------------------------------|----------------------|----------------------|-------------------|------------------------|-------------|---------------|---------------------------|------------------------------|----------------------|----------------------|

| Shared Memory        | 11    | 8        | 7                            | 5                    | 4                    | 2                 | 3                      | 1           | 1             | -                         | 1                            | 2                    | -                    |

| Semi-external Memory | 7     | 5        | 2                            | 5                    | 6                    | 3                 | 1                      | 1           | 1             | 2                         | 1                            | -                    | -                    |

| Distributed Memory   | 29    | 21       | 13                           | 13                   | 7                    | 5                 | 4                      | 2           | 3             | 2                         | 2                            | 1                    | 3                    |

| GPU                  | 4     | 4        | 3                            | 2                    | 4                    | -                 | 1                      | -           | -             | -                         | -                            | -                    | -                    |

| HW Accelerator       | 3     | 3        | 3                            | -                    | 1                    | -                 | -                      | 2           | -             | -                         | -                            | -                    | -                    |

| Total                | 54    | 41       | 28                           | 25                   | 22                   | 10                | 9                      | 6           | 5             | 4                         | 4                            | 3                    | 3                    |

| Percentage $(\%)$    |       | 76       | 52                           | 46                   | 41                   | 19                | 17                     | 11          | 9             | 7                         | 7                            | 6                    | 6                    |

Table 2.2: Number of graph framework evaluations using each graph algorithm, categorized by hardware platform. Only 12 most commonly evaluated algorithms are shown. See Appendix A for more information on survey of graph processing frameworks.

weights. If the graph is unweighted, BFS can return the shortest paths since all edges will have the same unit weight.

In addition to the distances, some SSSP implementations also return the parent vertices along the shortest paths. In Section 6.3 we evaluate the tradeoffs in implementing delta-stepping [107], a pragmatic parallel SSSP algorithm.

#### • PageRank (PR)

PageRank determines the "popularity" of vertices in a graph, and it was originally used to sort web search results [127]. PageRank determines the popularity of a vertex v not only by the number of vertices that point to v, but also the popularity of the vertices that point to v. More formally, the PageRank score (*PR*) for a vertex v with a damping factor d (0.85) is:

$$PR(v) = \frac{1-d}{|V|} + d\sum_{u \in N^{-}(v)} \frac{PR(u)}{|N^{+}(u)|}$$

The above recurrence often results in cyclic dependencies, but as long as the graph is aperiodic, the scores will converge [22]. PageRank typically iterates until the scores

$\tilde{\mathbf{v}}$

converge within a specified tolerance of a fixed point.

PageRank is a popular graph benchmark because it exposes many of the challenges of graph processing while still being simple enough to ease analysis and implementation. Correspondingly, there is considerable prior work on accelerating PageRank. A common optimization for PageRank exploits the differences in vertices' convergence rates by not processing vertices whose scores change too little relative to the previous iteration [96, 146]. Another common optimization is to apply the Gauss-Siedel method and update scores "in-place" by overwriting the previous score with the new score [90]. This optimization improves the convergence rate since the computation will often be operating on newer data.

#### • Connected Components (CC)

The connected components algorithm labels the components of a graph. If there is a path between two vertices, those two vertices are *connected*. A *connected component* is a subgraph such that all of its vertices are connected to each other. A connected component is maximal, as any vertex that is connected to the component is part of the component.

In a directed graph, connection relationships can be asymmetric and thus not commutative. For example, if there is a directed edge from u to v, u is connected to v, but v may not be connected to u. In a directed graph, connected components can either be strongly connected or weakly connected. A *strongly connected component* is a subgraph such that there is a directed path between every pair of its vertices. A *weakly connected component* is a connected component when ignoring edge directions, and a strongly connected component is also a weakly connected component. On a directed graph, the term "connected components" is ambiguous, but typically refers to weakly connected components.

The connected components algorithm labels vertices such that all vertices in the same component get the same label. Vertices of zero degree are not connected to any other vertices and are thus their own components so they get their own labels.

#### • Betweenness Centrality (BC)

Betweenness centrality is a metric that attempts to measure the importance of vertices within a graph. In particular, BC creates a score for each vertex that measures the fraction of shortest paths that pass through that vertex. More formally, if  $\sigma_{st}$  is the number of shortest paths between vertices s and t, and  $\sigma_{st}(v)$  is the number of those shortest paths that pass through vertex v, the betweenness centrality score for v is:

$$BC(v) = \sum_{s,t \in V, s \neq v \neq t} \frac{\sigma_{st}(v)}{\sigma_{st}}$$

BC can be computationally demanding as it requires computing *all* of the shortest paths between *all* pairs of vertices. In practice, this is often accomplished by executing

SSSP from every vertex as a source. Executing SSSP for every vertex is not only a great deal of shortest paths to compute, but can also consume a great deal of memory capacity to store all of the computed shortest paths. The Brandes algorithm greatly reduces memory requirements, as it is able to compact the critical information from a single SSSP execution into a single value per vertex [29]. The reduction in memory capacity requirements greatly improves the tractability of computing BC, however, to compute the exact scores the Brandes algorithm still needs to perform SSSP from every vertex. Many use cases of BC only care about the relative ordering of vertices, so approximations can be sufficient. The easiest way to approximate BC scores is to only perform SSSP from a subset of the vertices, and if these vertices are selected in a sufficiently random way, the approximation is reasonable [13]. The final BC scores are typically normalized to one. Since BC is often performed on unweighted graphs, the SSSP executions can be accomplished by using BFS traversals.

#### • Triangle Counting (TC)

Triangle counting is used to measure the interconnectedness of a graph. A *clique* is a set of vertices that are all directly connected to each other. As the size of a clique grows, the number of edges it contains grows quadratically, so within real-world graphs, large cliques are rarely seen. A *triangle* is a clique of size 3, and due to its small size, it occurs often in nature. For example, in a friendship network, a triangle represents two friends having another friend in common. The presence of many triangles in a graph implies the graph has densely interconnected clusters, even if these clusters do not form perfect cliques.

As triangle counting's name suggests, the algorithm counts the number of triangles in a graph. In some usage scenarios the list of triangles is desired, but in our usage, the output of TC is the total number of triangles in the graph. Triangles are invariant to permutation, so three interconnected vertices can only be counted as a triangle once. We do not consider edge directions when defining a triangle, so for TC, all edges can be treated as undirected.

# 2.5 Other Types of Graph Algorithms

Graphs can be used in many contexts and ways, and this work focuses on some of the more classic and widely used types of graphs and graph algorithms. In this section, we briefly highlight some of the other types of graph processing.

For some graph processing applications, there is so much graph data it cannot fit into the processing system's memory simultaneously. In *streaming graph processing*, the graph "streams" through the system and the algorithms must be able to operate on the edges as they flow through. Depending on the usage scenario, the graph could be read from storage [92] or a network source [151]. For some applications, the data the graph represents is changing in real-time, and so the graph topology also needs to change [54]. In *dynamic graph processing*, the graph topology is changing independently of the algorithm. This plasticity is in contrast to a graph algorithm that deliberately mutates the graph topology as part of its computation. Some sophisticated dynamic graph algorithms can update a prior solution by only computing on the parts of the graph that have changed [55].