# Energy-Efficient Equalization Circuits for High-Speed Wireline Links

Yue Lu

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2016-178 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-178.html

December 1, 2016

## Copyright © 2016, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### **Energy-Efficient Equalization Circuits for High-Speed Wireline Links**

by

Yue Lu

B.E. (Shanghai Jiao Tong University) 2008

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Elad Alon, Chair Professor Seth R. Sanders Professor Paul K. Wright

Fall 2014

|       | The dissertation of Yue Lu is approved. |      |

|-------|-----------------------------------------|------|

|       |                                         |      |

|       |                                         |      |

|       |                                         |      |

|       |                                         |      |

| Chair |                                         | Date |

|       |                                         |      |

|       |                                         | Date |

|       |                                         |      |

University of California, Berkeley Fall 2014 Date

Energy-Efficient Equalization Circuits for High-Speed Wireline Links

Copyright © 2014

by

Yue Lu

#### **Abstract**

Energy-Efficient Equalization Circuits for High-Speed Wireline Links

by

Yue Lu

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Elad Alon, Chair

The explosive development of various computation and communication platforms has demanded the per-pin I/O bandwidth of wireline links to increase at a commensurate rate, with projections to reach 60+Gb/s in less than 10 years. However, unlike the data-rate requirement, the power consumption of these links cannot increase, making improvements in the energy-efficiency of high-speed architectures and circuits crucial. In particular, equalization circuits such as feed-forward equalizers (FFE) and decision-feedback equalizers (DFE) are faced with the burden of compensating higher channel losses while running at faster speeds – all without allowing any increase in power consumption.

To address these challenges, this thesis first presents a feed-forward equalizing transmitter that utilizes voltage-mode signaling along with a shunting branch technique to improve signaling power. Due to the linear mapping between the equalization strength and output impedance segmentation from this technique, the associated decoding logic can be greatly simplified, and, thus, digital power overhead can be substantially reduced. Regulator-based impedance tracking loops are utilized to reduce the parasitics on the high-speed digital path to further reduce the digital power. A 2-tap prototype based on this architecture was taped out in Fujitsu 65nm LP CMOS process and achieves an overall of efficiency of 1pJ/b when operating at 10Gb/s with 200mV differential output signal amplitude.

To enable energy-efficient DFEs at even higher speeds, this thesis will then describe means to reduce the latency of the circuits within the intrinsic feedback loop of such equalizers. Specifically, techniques such as merged latch and summer, optimized signaling swing, and dynamic latches are combined to enable a multi-tap closed-loop DFE architecture that is capable of running at 60+Gb/s. A 3-tap prototype chip was fabricated in TSMC 65nm GP CMOS process, achieving ~0.7pJ/b at 66Gb/s when cancelling a total inter-symbol interference of ~1.65x of the cursor amplitude. This

design represents by far the fastest DFE demonstrated to date with energy efficiency of better than 1pJ/bit, and highlights that the adoption of such techniques may pave the way forward for continued electrical I/O data-rate scaling.

After the introduction of these equalization circuits, this thesis will present a holistic link evaluation framework that aims to achieve more accurate power and performance estimation of link architectures at the beginning of a link design phase. With a compact circuit modeling methodology, circuit power and noise can be explicitly expressed in terms of both technology and system parameters (e.g. equalization-related parameters) such that a link's overall power and bit-error-rate can be directly estimated. An evaluation example shows that using TSMC 65nm GP CMOS process, it is possible to achieve a 64Gb/s data communication speed over a 1m long coax cable-based platform, which aligns with the previous DFE experimental results and thus proves the potentials of using this framework to guide the continued wireline data-rate scaling.

To My Family

## **Contents**

| Contents                                                                                          | ii |

|---------------------------------------------------------------------------------------------------|----|

| List of Figures                                                                                   | v  |

| List of Tables                                                                                    | ix |

| Acknowledgements                                                                                  | X  |

| Chapter 1 Introduction                                                                            | 1  |

| 1.1 Background                                                                                    | 1  |

| 1.2 Equalizers                                                                                    | 3  |

| 1.2.1 Feed-forward Equalizer (FFE)                                                                | 3  |

| 1.2.2 Decision-feedback Equalizer (DFE)                                                           | 5  |

| 1.3 Thesis Organization                                                                           | 6  |

| Chapter 2 Design Techniques for Energy-efficient Voltage-Mode Feed-Forward Equalizer Transmitters | 8  |

| 2.1 Current-Mode Driver vs. Voltage-Mode Driver                                                   | 8  |

| 2.1.1 VM Driver Signaling Power Advantage                                                         | 8  |

| 2.1.2 FFE VM Transmitter Design Challenges                                                        | 10 |

| 2.2 FFE Voltage-Mode Transmitter Power Analysis                                                   | 11 |

| 2.2.1 Signaling Power Analysis                                                                    | 11 |

| 2.2.2 Digital Power Analysis                                                                      | 14 |

| 2.3 Proposed Pre-Emphasis Voltage-Mode Transmitter                                                | 19 |

| 2.4 Transmitter Architecture and Circuit Implementation                                           | 21 |

| 2.4.1 Choice of Impedance Calibration Schemes                                                     | 21 |

| 2.4.2 Overall Architecture                                                                        | 22 |

| 2.4.3 Pre-emphasis Decoder                                                                        | 22 |

| 2.4.4 Driver Segments                                                                             | 23 |

| 2.4.5 Impedance Control Loop with Online Comparator Offset Calibration                            | 24 |

| 2.4.6 Output Amplitude Control Loop                                                               | 26 |

| 2.5 Measurement Results                                                      | 27 |

|------------------------------------------------------------------------------|----|

| 2.6 Conclusions                                                              | 32 |

| Chapter 3 Design Techniques for Multi-Tap Energy-Efficient Decision Feedback |    |

| Equalizers                                                                   | 33 |

| 3.1 Multi-tap Design Challenges                                              | 33 |

| 3.1.1 Closed-loop DFE Timing Constraints                                     | 33 |

| 3.1.2 Loop-unrolling Limitations                                             | 34 |

| 3.2 Proposed Closed-Loop DFE                                                 | 37 |

| 3.2.1 Optimization #1: Merged Summer/Latch                                   | 37 |

| 3.2.2 Optimization #2: Reduced Latch Gain                                    | 38 |

| 3.2.3 Optimization # 3: Dynamic Latch Design                                 | 39 |

| 3.2.4 Noise Analysis and Implications                                        | 43 |

| 3.3 Complete 3-Tap DFE Circuit Design                                        | 46 |

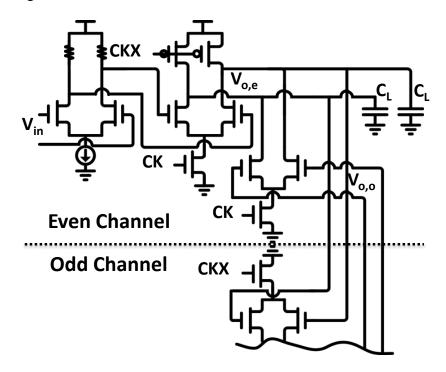

| 3.3.1 Dynamic Latch Circuit and Practical Issues                             | 47 |

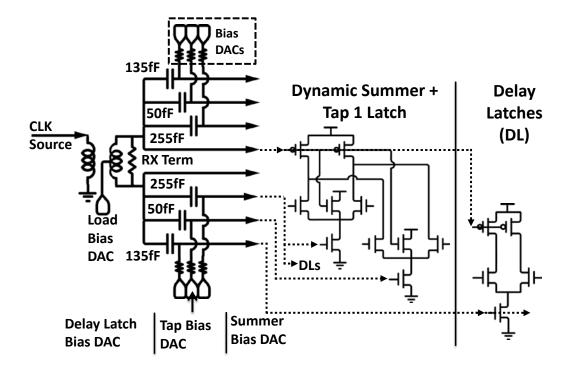

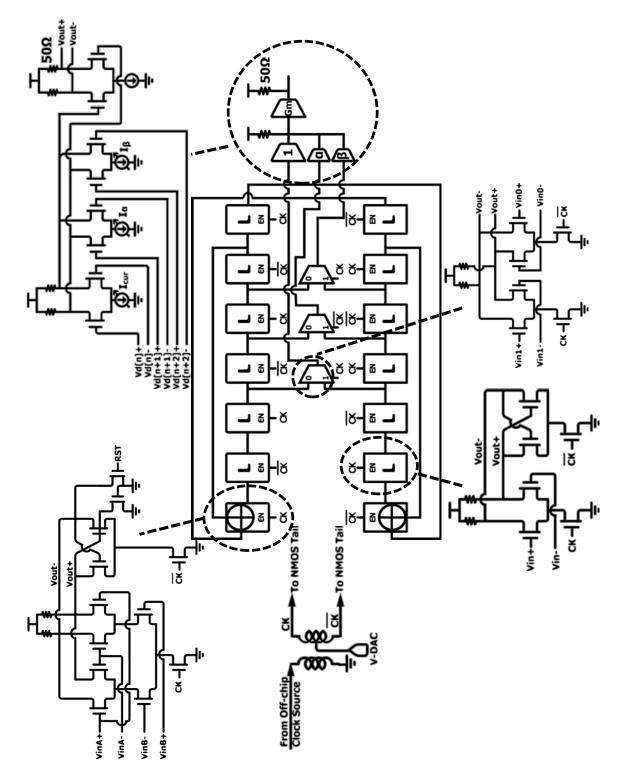

| 3.3.2 Overall 3-Tap DFE Architecture                                         | 49 |

| 3.3.3 Clock Distribution                                                     | 51 |

| 3.4 Complete test-chip and Measurement                                       | 52 |

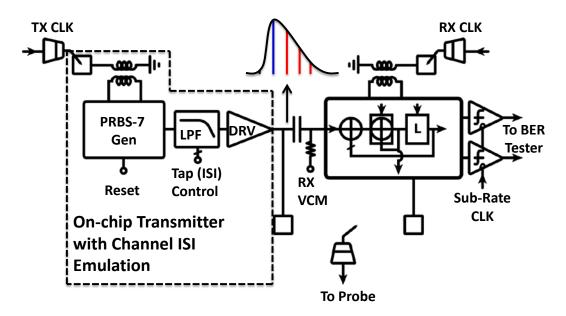

| 3.4.1 On-chip Testing Structures and Test Setup                              | 53 |

| 3.4.2 Measurement Results                                                    | 55 |

| 3.5 Conclusion                                                               | 60 |

| Chapter 4 A Holistic Link Evaluation Platform                                | 61 |

| 4.1 Holistic Evaluation with Circuit Modeling and Device Constraints         | 61 |

| 4.1.1 Circuit Component Modeling                                             | 62 |

| 4.1.2 Building Block Interactions                                            | 65 |

| 4.2 Complete Link Framework and Examples                                     | 68 |

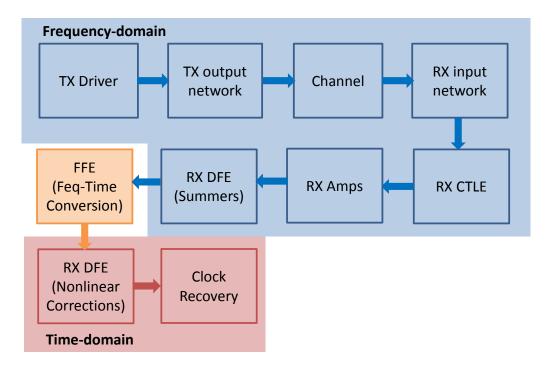

| 4.2.1 Signal Flow and Type Conversion                                        | 68 |

| 4.2.2 Complete Framework                                                     | 69 |

| 4.2.3 Example: Signaling Platform for 2025                                   |    |

| 4.3 Conclusion                                                               |    |

| Chapter 5 Conclusions                                                        |    |

| 5.1 Thesis Summary                                                   | 77 |

|----------------------------------------------------------------------|----|

| 5.2 Future Directions                                                | 78 |

| Bibliography                                                         | 79 |

| Appendix A Analysis of PEVM Transmitters                             | 87 |

| A.1 CVPEVM                                                           | 87 |

| A.2 CIPEVM                                                           | 88 |

| A.3 IMPEVM                                                           | 88 |

| A.4 Proposed PEVM                                                    | 89 |

| Appendix B Comparison of Dynamic Latch and CML Latch Implementations | 90 |

| Appendix C DFE Error Propagation Analysis                            | 93 |

| C.1 Error Propagation Analysis for 1-tap DFE                         | 93 |

| C.2 A Brief Summary for Multi-Tap DFE                                | 97 |

## **List of Figures**

| Figure 1.1: examples of wireline links (source: internet)                             | 1    |

|---------------------------------------------------------------------------------------|------|

| Figure 1.2: per-pin data rate requirement prediction                                  | 2    |

| Figure 1.3: published efficiency vs. data rate for 10+Gb/s electrical links           | 2    |

| Figure 1.4: a general wireline link architecture                                      | 3    |

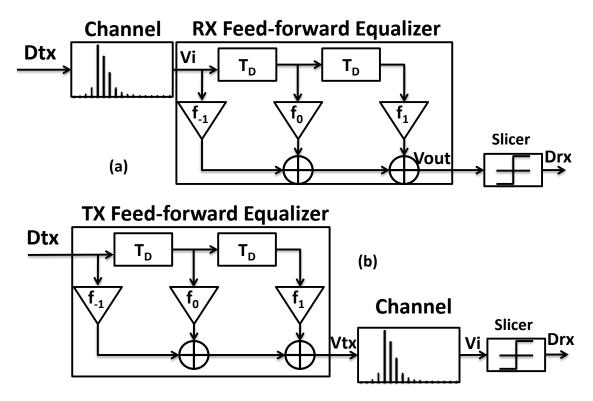

| Figure 1.5: a 3-tap (1-pre and 2-post taps) FFE equalizer implemented on (a) RX side  |      |

| (b) TX side                                                                           | 4    |

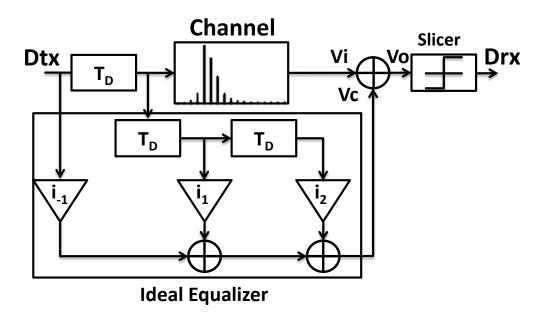

| Figure 1.6: a conceptually ideal equalizer (ignored channel's propagation delay for   |      |

| simplicity)                                                                           | 5    |

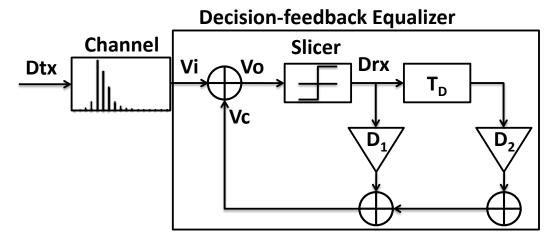

| Figure 1.7: a 2-tap DFE equalizer                                                     | 6    |

| Figure 2.1: (a) simplified model for a terminated CML driver and (b) simplified mod   | lel  |

| for a terminated VM driver when sending a bit "1"                                     | 9    |

| Figure 2.2: (a) simplified model for CML transmitter and (b) simplified model for VI  | M    |

| transmitter                                                                           | 10   |

| Figure 2.3: conventional pre-emphasis scheme                                          | 12   |

| Figure 2.4: (a) constant-current pre-emphasis scheme and (b) its equivalent circuit   | 13   |

| Figure 2.5: (a) impedance modulated pre-emphasis scheme and (b) its equivalent circ   | cuit |

|                                                                                       | 13   |

| Figure 2.6: signaling power comparison of previous drivers                            | 14   |

| Figure 2.7: switched branch conductance vs Vout for different drivers                 | 17   |

| Figure 2.8: normalized digital power vs. # of segments                                | 18   |

| Figure 2.9: number of segments vs. Vout resolution for different designs              | 18   |

| Figure 2.10: equivalent circuit of proposed PEVM                                      | 19   |

| Figure 2.11: signaling power comparison                                               | 20   |

| Figure 2.12: number of segments vs V <sub>out</sub> resolution                        | 20   |

| Figure 2.13: (a) "digital" impedance calibration scheme and (b) "analog" impedance    |      |

| calibration scheme                                                                    | 21   |

| Figure 2.14: overall transmitter architecture                                         | 22   |

| Figure 2.15: decoder and segment schematic                                            | 23   |

| Figure 2.16: schematic of impedance control loop                                      | 24   |

| Figure 2.17: implementation of comparator-based regulator loop                        | 25   |

| Figure 2.18: illustration of interleaved comparator offset calibration and regulation |      |

| process: (a) comparator auto-zeroing (calibration) phase and (b) regulation phase     | 26   |

| Figure 2.19: schematic for swing control loop                                         | 27   |

| Figure 2.20: die photo and TX floor plan                                                             | 27   |

|------------------------------------------------------------------------------------------------------|------|

| Figure 2.21: 10" FR4 PCB trace (a) S21 and (b) simulated 10Gb/s pulse response                       | 28   |

| Figure 2.22: 2 <sup>23</sup> -1 PRBS eye before and after 10" trace with post-tap pre-emphasis tur   | rned |

| off (100mV/div vertical, 20ps/div horizontal)                                                        |      |

| Figure 2.23: 2 <sup>23</sup> -1 PRBS eye before and after 10" trace with post-tap pre-emphasis tur   | rned |

| on (100mV/div vertical, 20ps/div horizontal)                                                         |      |

| Figure 2.24: TX output swing tuning curve                                                            | 29   |

| Figure 2.25: TX output impedance vs. signal amplitude                                                | 30   |

| Figure 2.26: signaling power with 250mV differential amplitude swing vs. pre-empha                   |      |

| setting                                                                                              |      |

| Figure 2.27: TX power vs. output swing and data-rate                                                 | 31   |

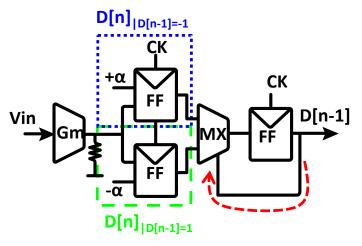

| Figure 3.1: (a) full-data-rate 1-tap closed-loop DFE and (b) double-data-rate 1-tap clo              | sed- |

| loop DFE architectures                                                                               | 34   |

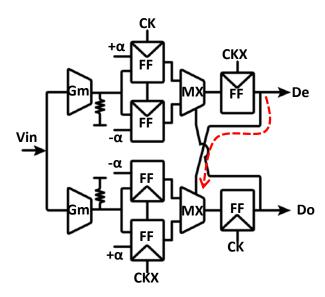

| Figure 3.2: 1-tap loop-unrolled FDR DFE architecture                                                 | 35   |

| Figure 3.3: 1-tap loop-unrolled DDR DFE architecture                                                 | 35   |

| Figure 3.4: 2nd tap critical timing path for (a) 1st tap unrolled and 2nd tap closed-loop            | p    |

| DFE and (b) 2-tap closed-loop DFE                                                                    | 36   |

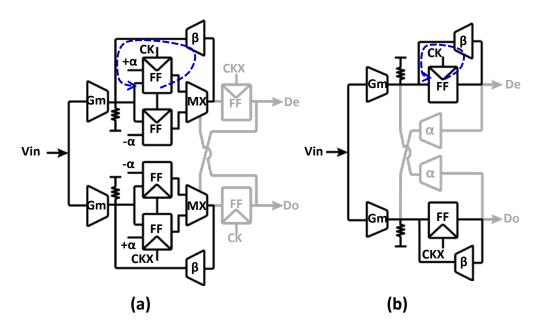

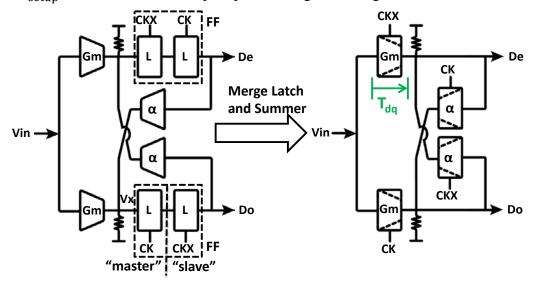

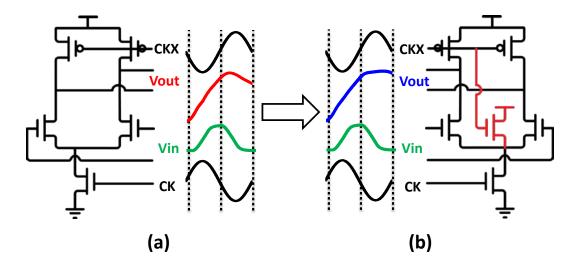

| Figure 3.5: illustration of optimization 1 – merged latch and summer                                 | 37   |

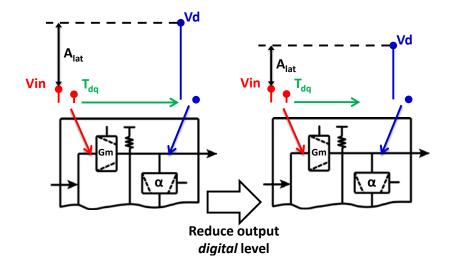

| Figure 3.6: illustration of optimization 2 step 1 – reducing the required output digital             |      |

| level                                                                                                | 38   |

| Figure 3.7: illustration of optimization 2 step 2 – increasing the input analog level                | 39   |

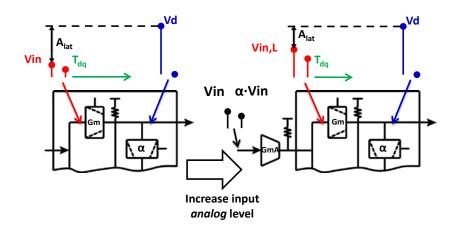

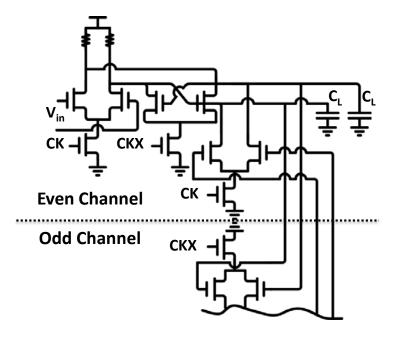

| Figure 3.8: closed-loop 1st tap with dynamic latch                                                   | 40   |

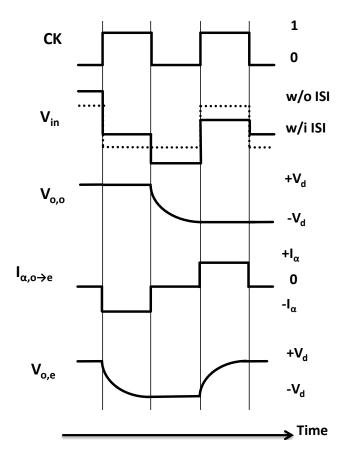

| Figure 3.9: 1st tap operation waveforms with an input data pattern of 10010 that is                  |      |

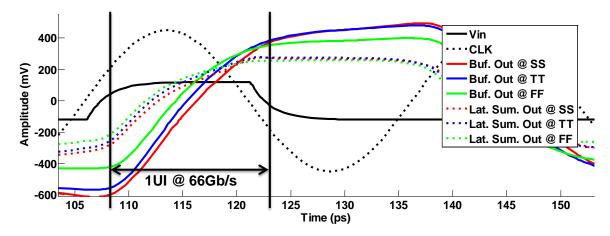

| distorted by a single tap of post-cursor ISI                                                         | 41   |

| Figure 3.10: close-loop 1st tap with CML latch                                                       | 42   |

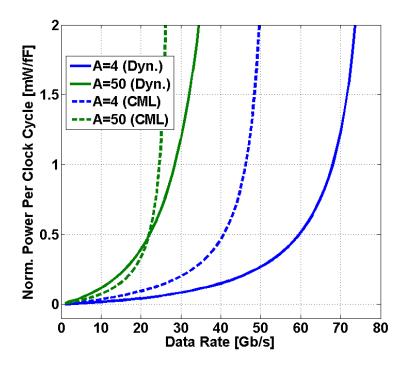

| Figure 3.11: power vs. data rate for both CML and dynamic latch-based designs for                    |      |

| various total gain requirements                                                                      |      |

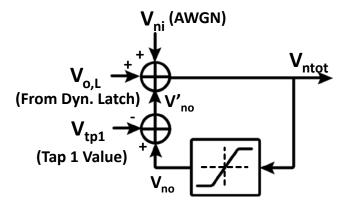

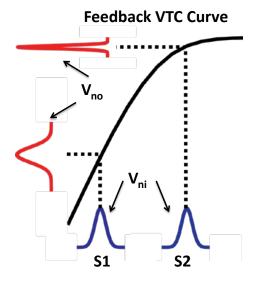

| Figure 3.12: illustration of noise shaping and propagation in the DFE feedback loop                  | 43   |

| Figure 3.13: two examples of noise propagation – S1: the latch output signal level lan               | ds   |

| within the high-gain region of the feedback pair's VTC, and S2: the latch output level               |      |

| lands within the clipping region                                                                     |      |

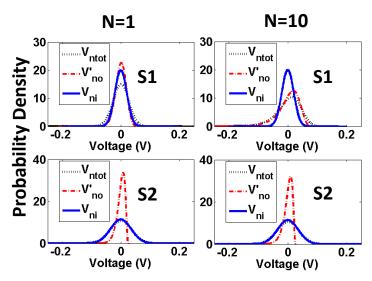

| Figure 3.14: noise PDF after 1 and 10 iterations for the two examples in Figure 3.13                 | 45   |

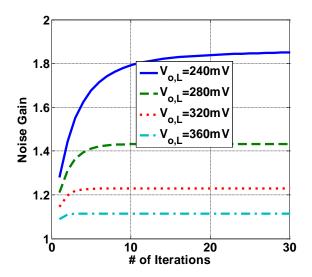

| Figure 3.15: noise gain vs. number of propagations with input SNR (i.e. $V_{O,L}/\sigma_{vni}$ ) = 8 | .45  |

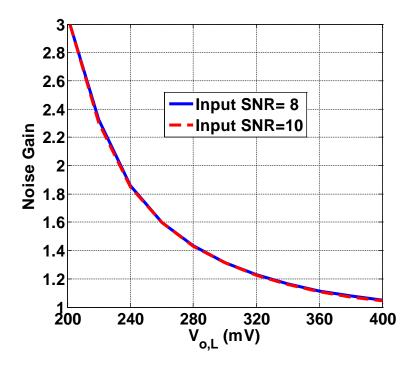

| Figure 3.16: noise enhancement vs. latch output signal level under various input SNR                 | s 46 |

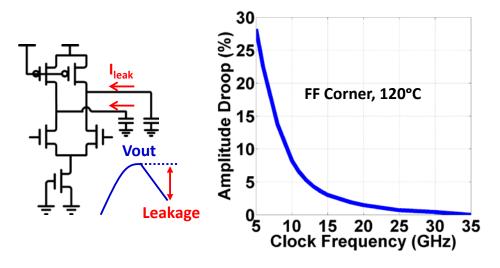

| Figure 3.17: amplitude droop due to dynamic latch leakage vs. clock frequency                        | 47   |

| Figure 3.18: (a) dynamic latch without tail node reset and (b) with tail reset device to             |      |

| improve the latch's aperture                                                                         | 48   |

| Figure 3.19: (a) adjusting the 1st tap correction current $I_{cor}$ by changing the DC gate-b        | oias |

| $V_G$ , and (b) $I_{cor}$ vs. $V_G$                                                                  | 48   |

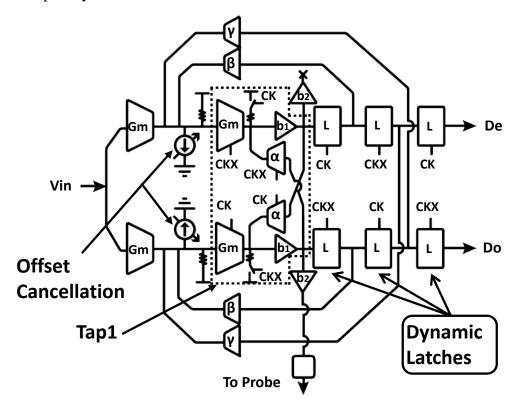

| Figure 3.20: complete proposed 3-tap DFE design                                                 | 49  |

|-------------------------------------------------------------------------------------------------|-----|

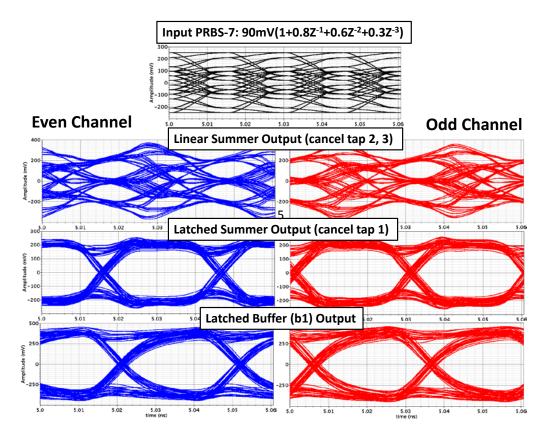

| Figure 3.21: simulated post-layout eye-diagrams in the TT corner at each node of the 3          | 3-  |

| tap DFE                                                                                         | 50  |

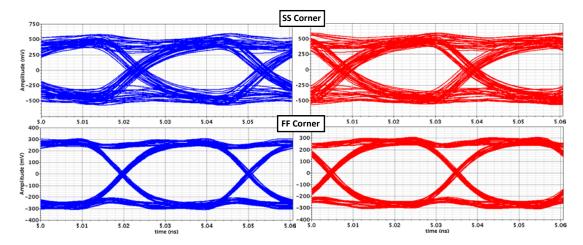

| Figure 3.22: simulated post-layout eye-diagrams in the SS and FF corners at the latche          | ed  |

| buffer (b1) output                                                                              | 50  |

| Figure 3.23: simulated post-layout pulse response at the output of the buffer                   | 51  |

| Figure 3.24: DFE clock distribution network                                                     | 52  |

| Figure 3.25: complete 65nm GP test-chip including the proposed DFE and on-chip                  |     |

| transmitter with channel emulation                                                              | 52  |

| Figure 3.26: transmitter design with DDR PRBS-7 generator and low-pass channel                  |     |

| emulation                                                                                       | 54  |

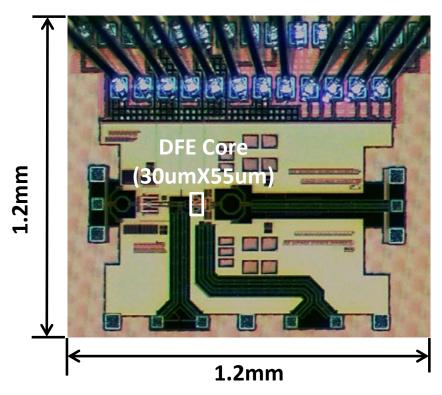

| Figure 3.27: test-chip die photo                                                                | 55  |

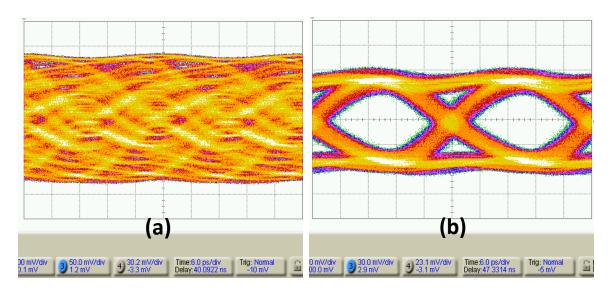

| Figure 3.28: (a) 66Gb/s PRBS-7 single-ended eye-diagram before DFE, (b) 33Gb/s                  |     |

| PRBS-7 single-ended eye-diagram after DFE                                                       | 56  |

| Figure 3.29: (a) 66Gb/s single-ended data waveform before DFE, and (b) 33Gb/s single-ended data | le- |

| ended data waveform after DFE                                                                   | 56  |

| Figure 3.30: circuit configuration used to characterize the feedback pair's clipping            |     |

| voltage                                                                                         |     |

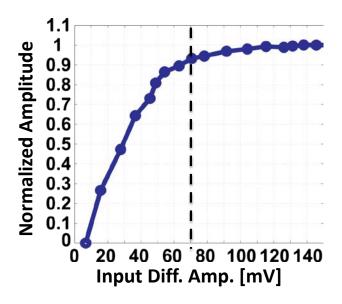

| Figure 3.31: measured overall VTC                                                               |     |

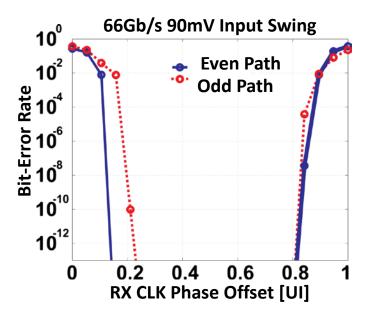

| Figure 3.32: measured bathtub curve with a 90mV differential amplitude input signal             | 58  |

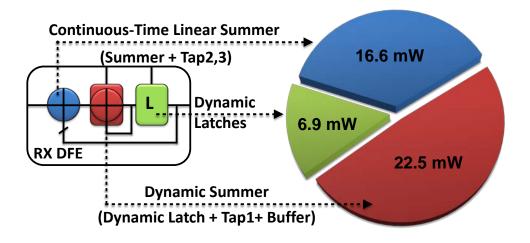

| Figure 3.33: DFE power breakdown                                                                | 59  |

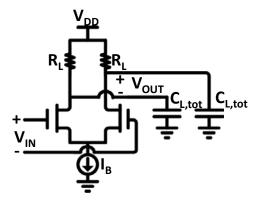

| Figure 4.1: a pre-amplifier example                                                             | 62  |

| Figure 4.2: a source-degenerated CTLE example                                                   | 64  |

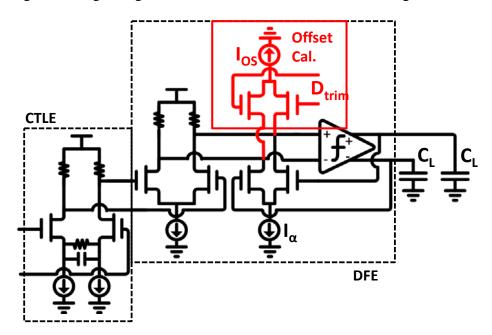

| Figure 4.3: a RX with CTLE + DFE example                                                        | 66  |

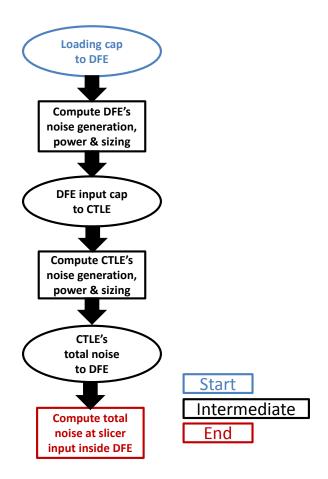

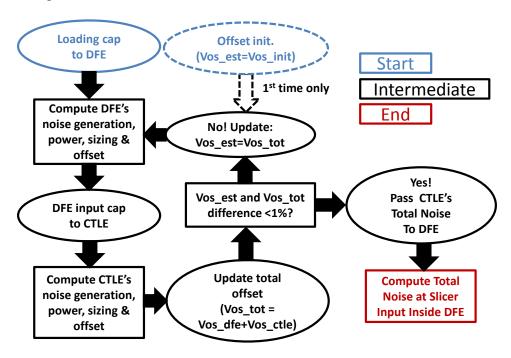

| Figure 4.4: block interactions without offset cancellation                                      | 67  |

| Figure 4.5: block interactions with offset cancellation                                         | 68  |

| Figure 4.6: signal flow and type conversion example                                             | 69  |

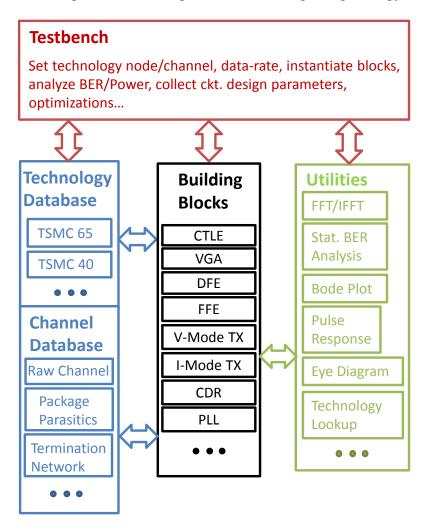

| Figure 4.7: overall framework organization                                                      | 70  |

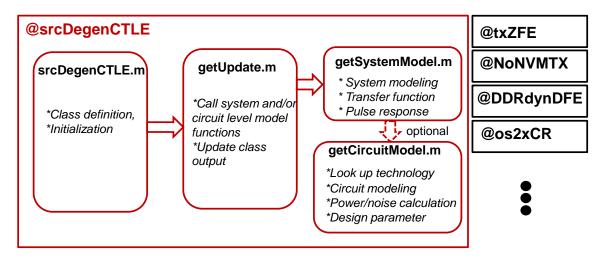

| Figure 4.8: matlab code organization for the CTLE block                                         |     |

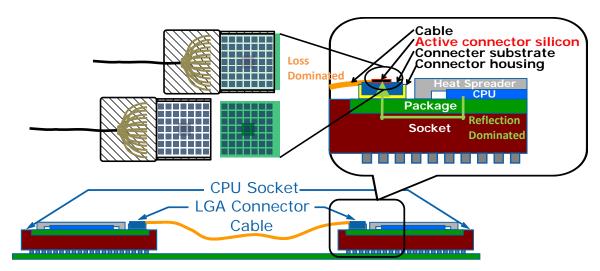

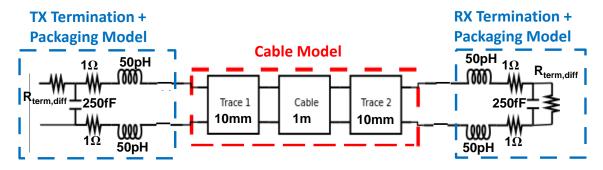

| Figure 4.9: Signaling Platform for 2025 (from Intel)                                            | 73  |

| Figure 4.10: a 1-m cable channel for the 64Gb/s link                                            | 73  |

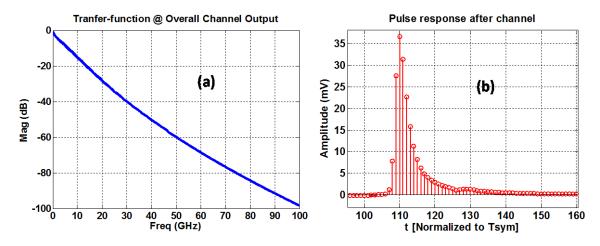

| Figure 4.11: (a) frequency response of the overall channel and (b) 64Gb/s pulse response        | nse |

| with 250mV differential amplitude                                                               |     |

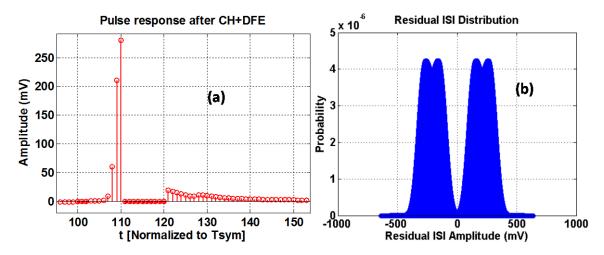

| Figure 4.12: channel equalization using 10-tap DFE only - (a) equalized pulse respons           | e   |

| and (b) residual ISI distribution                                                               | 74  |

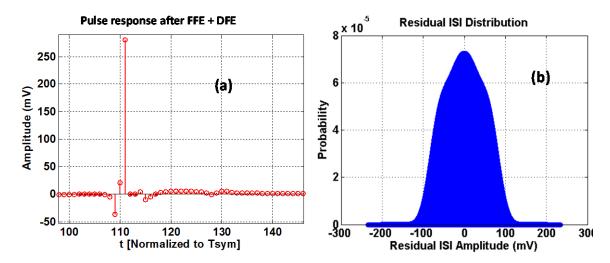

| Figure 4.13: link architecture example with unterminated TX driver + 4-tap FFE + 2-             |     |

| stage pre-amp + 2-tap DFE – (a) equalized pulse response and (b) residual ISI                   |     |

| distribution                                                                                    |     |

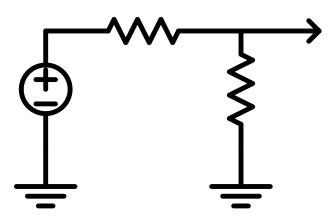

| Figure A.1: Thevenin equivalent circuit for driver analysis                                     | 87  |

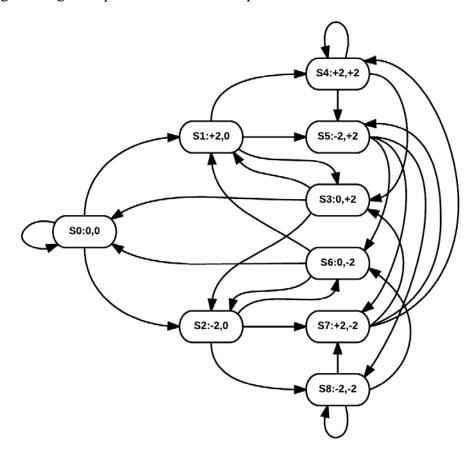

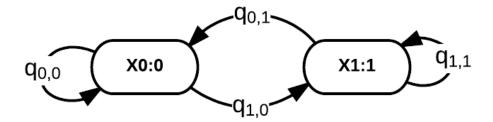

| Figure C.1: 1-tap DFE model                                                       | 93 |

|-----------------------------------------------------------------------------------|----|

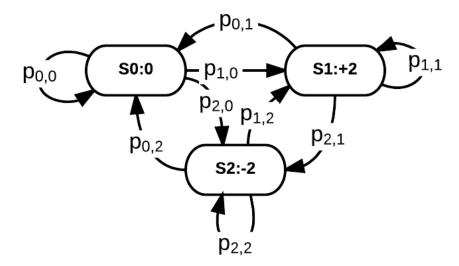

| Figure C.2: 1st-order discrete Markov chain model for the error state transitions | 94 |

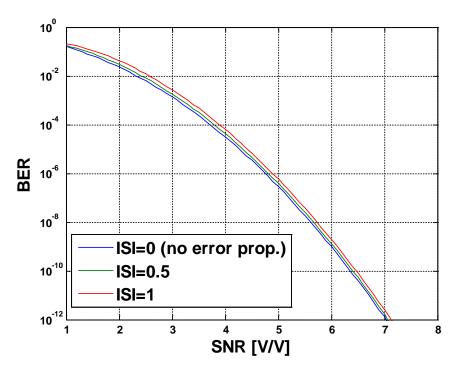

| Figure C.3: steady-state BER vs input SNR wi/wo error propagation                 | 96 |

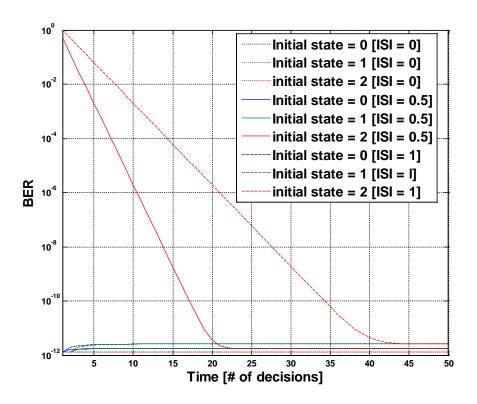

| Figure C.4: BER vs. time with different initial states                            | 97 |

| Figure C.5: 1st-order discreate Markov chain model for a 2-tap DFE                | 98 |

| Figure C.6: 1st-order reduction of STD for the 1-tap DFE example                  | 99 |

## **List of Tables**

| Table 2.1: pre-emphasis voltage-mode transmitter comparison   | 32 |

|---------------------------------------------------------------|----|

| Table 3.1: comparison to state-of-the-art 20+Gb/s DFE designs | 59 |

| Table 4.1: reference item list of the technology LUT          | 71 |

#### Acknowledgements

I cannot imagine a better time than the past 6 years I have spent at UC Berkeley as a graduate student. I feel extremely fortunate to have received so much help and support from so many individuals, without whom I can never reach this finish line of my Ph.D journey. I would like to take this opportunity to express my most sincere gratitude to every one of these companions.

I cannot feel luckier to have Prof. Elad Alon as my advisor. Elad's knowledge, patience as well as his inspiring lectures paved the path for me to become a good IC designer. I can hardly think of a better advisor who is always willing to discuss with me whenever I come up with new ideas and provides all sorts of support to implement them. I still remember the hours of technical discussions we had over the phone, some of those lasted deep into the night even when Elad needed to travel early in the next morning. Without his insightful feedback, I could never conquer the obstacles I had faced during my Ph.D studies. My gratitude to Elad is not limited to just research. He was always happy to share with me his experiences working in both industry and academia, and helped me resolve my concerns and difficult situations I encountered, all of which I found very beneficial to shape a better view of my future career.

I would like to thank Prof. Jan Rabaey, Prof. Seth Sanders and Prof. Paul Wright for being on my thesis and qualification exam committee. Their valuable feedback helped me to reshape my ideas when conducting research. I want to thank Prof. Ali Niknejad for his wonderful RF courses and the enjoyable soccer games he invited me to join. I also want to thank Prof. Haideh Khorramabadi and Prof. Borivoje Nikolic for teaching my ADC and digital IC design classes.

Throughout my Ph.D, I have got the opportunities to collaborate with many talents from various research institutes. I would like to thank Ming-Shuan Chen, Amr Hafez and Prof. Ken Yang of UCLA, Kangmin Hu, Rui Bai and Prof. Patrick Chang of Oregon State University, Amr Suleiman of MIT, Prof. Vladimir Stojanovic of UC Berkeley and Prof. Pavan Hanumolu of UIUC for the fruitful discussions and their insightful comments/feedback on my research. I certainly cannot get my work done without the gracious support from our industry partners and therefore I owe my thanks to Bryan Casper, Tanay Karnik, Mondira Pant of Intel, Yasuo Hidaka and William Walker of Fujitsu Laboratories of America as well as Ken Chang and Yohan Frans of Xilinx. I have met many great people in industry who helped me improve my technical strength. In particular, I would like to thank Jared Zerbe, Brian Leibowitz and Wenbo Liu of Apple, Jihong Ren of Altera and Yueyong Wang of Broadcom.

Berkeley Wireless Research Center is a fabulous place with a group of amazing people. I want to thank all the BWRC staff and especially Tom Boot, Brian Richards,

Fred Burghardt, Bira Coelho, James Dunn, Leslie Nishiyama, Olivia Nolan and Sarah Jordan, without whom I cannot finish my projects so smoothly.

I learned a lot of analog/mixed-signal/RF/mm-wave knowledge beyond my research topic from a lot of senior BWRC students: Jiashu Chen, Lingkai Kong, Lu Ye, Chintan Thakkar, Hanh-Phuc Le, John Crossley, Amin Arbabian, Peng Liu, Yida Duan, Wenting Zhou, Jungdong Park, Ashkan Borna, Tsung-Te Liu, Stanley Chen, Namseog Kim, Kyoohyun Noh, Rikky Muller, Simone Gambini, Zhiming Deng, Richard Su and Ping-Chen Huang. I would like to thank all of them for spending their precious time with me.

I would also like to thank my fellow BWRC colleagues - Jun-Chau Chien, Kwangmo Jung, Siva Thyagarajan, Wen Li, Alberto Puggeli, Shingwon Kang, Charles Wu, Matthew Spencer, Jaehwa Kwak, Steven Callendar, Daniel Yeager, William Biederman, Jaeduk Han, Nathan Narevsky, Nai-Chung Kuo, Dongjin Seo, Christopher Sutardja, Nicholas Sutardja, Pengpeng Lu and Constantine Sideris - for working with me on various projects, discussing new ideas and having fun together.

Getting admitted to UC Berkeley for graduate school was the most exciting news for me as an undergraduate. I would like to thank my undergraduate advisor, Prof. Alex Lee for teaching me analog circuit design and writing me an enthusiastic recommendation letter. I want to thank Prof. David Ricketts for providing me the research opportunities when I was an exchange student at Carnegie Mellon University in my junior year, without which I could not discover my interests in integrated circuit design.

I would like to thank my parents for always supporting me to pursue my dream. Even though we are separated far away by the Pacific Ocean, I can still feel the warmth of their love. I owe my thanks to my dearest wife - Qinru Chu. Without her sacrifice and constant support, I can never get through the hardest time of my Ph.D journey.

## Chapter 1 Introduction

#### 1.1 Background

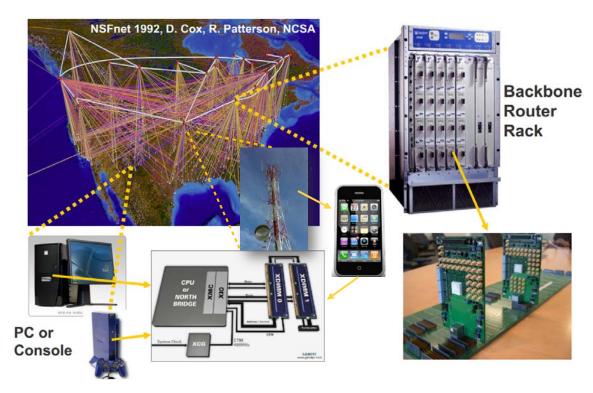

Wireline links are ubiquitous. As shown in Figure 1.1, almost every communication platform requires wireline link to be running in the background. Unsurprisingly, with the explosive development of applications such as cloud storage/computation and sensor networks the future will only witness an increasing demand of high-speed wireline communications.

Figure 1.1: examples of wireline links (source: internet)

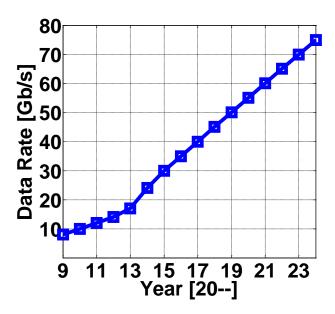

To get a general trend and estimation of how fast links will need to be, the data compiled from the International Technology Roadmap for Semiconductors (ITRS) can be used as a reference. As shown in Figure 1.2, the requirement on per pin throughput of I/Os will increase at 1.1-1.2X/year, reaching 70+Gb/s in about 10 years ([1]). On the other hand, while the throughput of the I/Os keeps on increasing, their absolute power budget should remain essentially unchanged (<10% as estimated in [2]–[4]), requiring the energy-efficiency of these I/Os to be improved ([5], [6]).

Figure 1.2: per-pin data rate requirement prediction

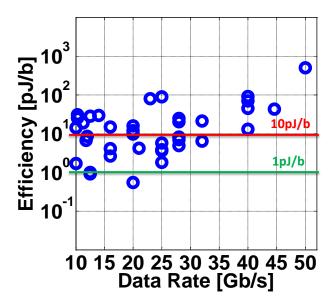

Driven by this need, many researchers have developed promising approaches to push the limits of building energy-efficient high-speed I/Os. As shown in Figure 1.3, published papers from major conferences such as ISSCC, VLSI and CICC have shown that most designs below 30Gb/s can achieve sub-10pJ/b or even sub-1pJ/b energy-efficiency. On the other hand, while links operating at 30+Gb/s and even 40+Gb/s have also been demonstrated, their energy efficiencies are still clustered at the region beyond 10pJ/b. This data indicates there is still much research on both system and circuit levels to be done to further optimize current high-speed link platforms.

Figure 1.3: published efficiency vs. data rate for 10+Gb/s electrical links

#### 1.2 Equalizers

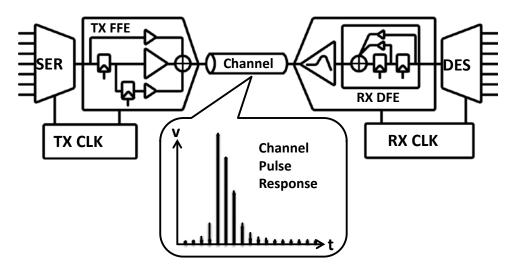

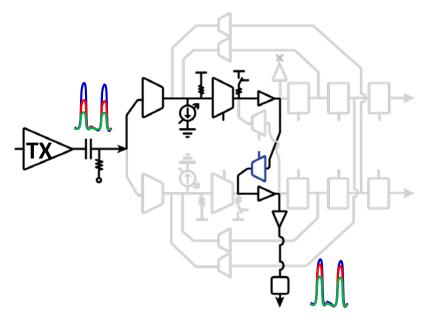

To figure out the power/speed bottlenecks of wireline links, let's begin by examining a typical link architecture as shown in Figure 1.4. Due to the skin effect and dielectric losses, electrical channels often introduce large inter-symbol interference (ISI) that can lead to errors on the receiver side ([7]). To deal with this ISI, equalization circuits – specifically feed-forward equalizers (FFE) and decision-feedback equalizers (DFE) – are widely adopted to restore the transmitted bits on the receiver side to bring down the bit-error-rate to a certain targeted low level (e.g. 1e-12).

Since the ISI is speed dependent, higher data rate operation will only require faster (i.e. higher circuit bandwidth) and stronger (i.e. larger circuit loading) TX and RX equalizations, making transceiver equalizers a critical and potentially power hungry portion of the transceiver ([5], [8]). For this reason, this thesis will focus on circuit design techniques and modeling methodologies for building energy-efficient equalizers and choosing optimum link architectures such that we can keep on improving link's energy efficiency when we keep on increasing data rates. Before diving into the details, however, some basics of the FFE and DFE need to be introduced.

Figure 1.4: a general wireline link architecture

#### 1.2.1 Feed-forward Equalizer (FFE)

The basic structure of a FFE can be illustrated in Figure 1.5. While it can be implemented on either RX side (Figure 1.5(a)) or TX side (Figure 1.5(b)), the basic working principle of the FFE remains the same. It generates multi-path signals (i.e. the main and correction

<sup>&</sup>lt;sup>1</sup> There may be some power and design complexity trade-offs between implementing them on the two sides ([13], [73]).

taps) by applying proper delays from the same signal source before linearly scaling<sup>2</sup> and combining them to cancel the channel ISI.

Figure 1.5: a 3-tap (1-pre and 2-post taps) FFE equalizer implemented on (a) RX side and (b) TX side

To further investigate the FFE's linear property, let's write down the difference equation of a simple 2-tap 1-UI spaced FFE with 1 post-tap correction:

$$V_{\text{out}}[k] = f_0 \cdot V_{\text{in}}[k] - f_1 \cdot V_{\text{in}}[k-1]$$

(1.1)

where  $f_0$  and  $f_1$  are the coefficients for the main tap (i.e. current bit) and correction tap (i.e. previous bit) and both are assumed to be positive. The negative sign before  $f_1$  is to implement the high-pass filter function for the FFE such that it can "inverse" or "equalize" the low-pass characteristic of the channel.

When the previous bit and the current bit are different (i.e.  $V_{in}[k] = -V_{in}[k-1]$  - a clock pattern for instance) and thus a transition happens, the data contains a high-frequency component that will experience a larger loss from the low-pass channel. With the configuration in (1.1) , we will thus get the maximum gain of  $(f_0 + f_1)$  from the FFE. On the other hand, when transmitting/receiving consecutive bits (i.e.  $V_{in}[k] = V_{in}[k-1]$  - a DC pattern for instance), the FFE will result in a minimum gain of  $(f_0 - f_1)$  for the low-frequency data stream. Due to this  $(f_0 + f_1)/(f_0 - f_1)$  gain boosting, the FFE can

2

<sup>&</sup>lt;sup>2</sup> Delay choices include 1-UI based data equalization or ½-UI based edge+data equalization or other fractional UI equalization ([63], [74], [75]). Scaling coefficients can be adapted based on different algorithms such as sign-sign LMS([50], [76]) and minimum BER ([77]).

extend the overall channel bandwidth by increasing the channel's high-frequency content to match the overall low-frequency gain. However, since the high-frequency gain introduced by the equalizer has to be greater than its low-frequency gain to extend the bandwidth, an FFE would amplify more high-frequency noise (e.g. cross-talk noise) and thus tends to compromise the overall equalized signal-to-noise ratio (SNR) of the link. The more ISI that needs to be equalized (i.e. larger gain boosting), the more high-frequency noise will be amplified.

#### 1.2.2 Decision-feedback Equalizer (DFE)

When we take a closer look at the "noise amplification" problem of an FFE, it actually stems from the fact that both the main and correction bits have to go through the channel loss. In other words, due to its linear filter characteristic, we have to combine the "dirty" correction bits to the main signal to equalize the channel ISI. If in some way we can use "clean" correction bits to apply on the main signal path for ISI cancellation, the channel loss will be equalized without introducing any noise amplification. This thought process essentially leads us to a conceptual equalizer architecture as illustrated in Figure 1.6.

Figure 1.6: a conceptually ideal equalizer (ignored channel's propagation delay for simplicity)

With such a configuration, correction bits are clean digital signals from the transmitter that never get contaminated by the channel loss or any other noise sources, and thus can cancel the channel induced ISI without eating the main signal's dynamic range or introducing any extra noise. Of course, in reality there won't exist such a perfect by-pass channel to send the clean TX data to the RX side or we won't need to build equalizers in the first place. Fortunately, in a practical system, the recovered digital bits

after the RX slicer can serve as good proxies of these clean correction bits, leading to the decision-feedback equalizer architecture as shown in Figure 1.7. <sup>3</sup>

As the slicer essentially erases all the noise and memory effect introduced from the channel, its output can then be treated as the desired channel-independent bit source. However, the penalty we pay for using the received bits as the correction is also clear - due to its feedback nature, a DFE cannot cancel pre-cursor ISI.

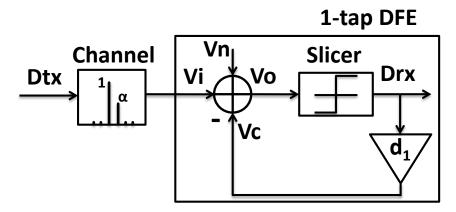

Figure 1.7: a 2-tap DFE equalizer

On the other hand, as we need to utilize the "decisions" to correct post-cursor ISI, one particular concern often raised with DFEs is related to "error-propagation". This occurs when an incorrect decision is made and causes the feedback correction to be the exact opposite polarity. If an ISI tap is substantial (e.g. >0.5 of the main cursor amplitude), it is very likely the next few bits will continue to be wrong. Fortunately, previous works (e.g [9]) have shown that the differences with and without considering error propagations end up giving negligible steady-state BER differences as often times the target BER would be too low to cause any substantial error accumulation. A brief summary of such an analysis is given in the Appendix C for reference.

#### 1.3 Thesis Organization

With the introduction of FFE and DFE in this chapter, the remaining focus of the thesis will then be on the presentation of circuit design techniques to build both energy-efficient feed-forward and decision-feedback equalizers. Starting in Chapter 2, a FFE transmitter architecture that achieves both excellent signaling and digital power consumption will be introduced. Integrated with amplitude control and automatic impedance matching, a 10Gb/s 2-tap transmitter prototype was designed and taped-out in Fujitsu 65nm LP CMOS process and achieved good signaling performance with only 1pJ/bit energy-efficiency. Following that, Chapter 3 introduces a DFE architecture suitable for ultra-high

\_

<sup>&</sup>lt;sup>3</sup> Unlike a FFE, the tap number definition in a DFE doesn't include the main-tap. Like an FFE, the delay can also be chosen to be a fraction of UI ([74]).

speed applications. Design techniques and practical considerations will be discussed to implement such a 3-tap DFE capable of running at 66Gb/s while achieving ~0.7pJ/bit efficiency in a standard TSMC 65nm CMOS process. With the knowledge of designing and implementing these equalizers, Chapter 4 presents a holistic link evaluation framework to assess different link architectures. Taking into account both channel and technology device limits, the proposed framework can substantially shorten the entire design cycle by helping system and circuit designers make early decisions on appropriate link architecture choices before running extensive system & circuit simulations. Finally, Chapter 5 summarizes the thesis and points out future directions.

### **Chapter 2**

### Design Techniques for Energy-efficient Voltage-Mode Feed-Forward Equalizer Transmitters

The pursuit of energy-efficient high-speed links has popularized the use of voltage-mode (VM) transmitters due to their ideally 4x lower signaling power compared to current mode logic (CML) transmitters. These transmitters must typically support impedance matching and pre-emphasis (i.e. FFE function for signal integrity) as well as amplitude control to enable reduce power on clean channels. As will be discussed in more details soon, if not careful enough, the associated digital power overhead when embedding these functions in to a VM transmitter will become dominant and thus compromise the overall energy efficiency. In some cases it may even become more power hungry than a CML design ([10]).

This chapter will analyze the signaling and digital power overhead of preemphasis voltage-mode transmitters. After that, an optimized pre-emphasis scheme will be introduced to give both superior signaling and digital power efficiency. Leveraging this technique, a low-power pre-emphasis voltage mode transmitter architecture with output swing control, pre-emphasis coefficient control, and online impedance calibration is proposed and demonstrated. A 65nm LP CMOS implementation of this architecture dissipates only ~10mW from a 1.2V supply when transmitting 10Gb/s 400mV differential peak-to-peak data with a 2-tap FFE function, achieving 1pJ/bit energy efficiency.

#### 2.1 Current-Mode Driver vs. Voltage-Mode Driver

#### 2.1.1 VM Driver Signaling Power Advantage

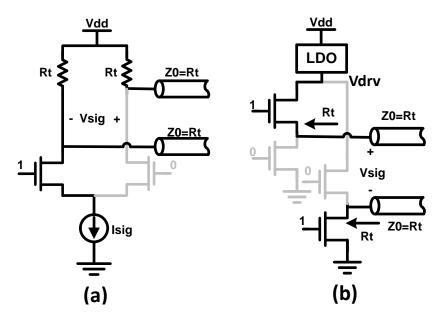

To compare the signaling power efficiency of a current-mode driver and a voltage-mode driver, we need to find how much current each driver consumes when sending the same amount of voltage  $V_{sig}$  at the transmitter output. As shown in Figure 2.1(a), for a terminated CML driver where its driver impedance  $R_t$  is equal to the channel characteristic impedance  $Z_0$ , the overall effective load impedance is only  $R_t/2$ . The required steering signaling current to build up a differential amplitude  $V_{sig}$  is then:

$$I_{\text{sig,CML}} = \frac{V_{\text{sig}}}{R_{\text{t}}/2} = \frac{2V_{\text{sig}}}{R_{\text{t}}}$$

(2.1)

Figure 2.1: (a) simplified model for a terminated CML driver and (b) simplified model for a terminated VM driver when sending a bit "1"

with a supply voltage of  $V_{\mbox{\scriptsize dd}}$ , the signaling power can be computed as:

$$P_{\text{sig,CML}} = V_{\text{dd}} I_{\text{sig,CML}} = \frac{2V_{\text{dd}} V_{\text{sig}}}{R_{\text{t}}}$$

(2.2)

On the other hand, for a VM driver, the mechanism of generating  $V_{sig}$  is very different. Rather than steering current from one-side of the load to the other to create differential voltages, a voltage mode driver essentially forms a voltage divider between the transmitter output and the channel impedance. As shown in Figure Figure 2.1(b), a typical low-swing VM driver requires a low-dropout regulator (LDO) to generate an intermediate voltage  $V_{drv}$  off the supply  $V_{dd}$  in order to build the differential output voltage. In the terminated case, the output impedance of the transmitter is equal to the channel characteristic impedance, and thus the transmitted signal amplitude can be simply expressed as:

$$V_{\text{sig}} = \frac{V_{\text{drv}}}{R_{\text{t}} + R_{\text{t}} + R_{\text{t}} + R_{\text{t}}} (R_{\text{t}} + R_{\text{t}}) = \frac{V_{\text{drv}}}{2}$$

(2.3)

and the signaling current can be found as:

$$I_{\text{sig,VM}} = \frac{V_{\text{drv}}}{4R_{\text{t}}} = \frac{V_{\text{sig}}}{2R_{\text{t}}} \tag{2.4}$$

As this current flows from the LDO (i.e. from the supply  $V_{dd}$ ), the signaling power from the supply is then:<sup>4</sup>

$<sup>^4</sup>$  A DC-DC converter can also be used to generate  $V_{drv}$ . Depending on its achievable efficiency, it may or may not be more power efficient than a LDO topology.

$$P_{\text{sig,VM}} = V_{\text{dd}} I_{\text{sig,VM}} = \frac{V_{\text{dd}} V_{\text{sig}}}{2R_{\text{t}}}$$

(2.5)

Comparing (2.5) and (2.2), we can easily identify that a VM transmitter has the potential advantage of a 4x signaling power efficiency improvement over a CML counterpart.

#### 2.1.2 FFE VM Transmitter Design Challenges

While this signaling power benefit looks appealing, we must be careful about the overhead power consumption when integrating the functionalities of equalization, impedance control and swing control to VM transmitter as it requires more complicated controls as compared to a CML transmitter.

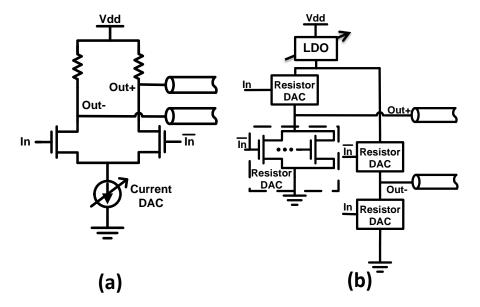

To be more specific, as shown in Figure 2.2(a), in a CML driver, since the driver impedance is purely set by the load resistors (ignoring the high-impedance loading from the transistors), amplitude modulation can be simply achieved by replacing the current source with current DACs without compromising termination. However, unlike the CML transmitter whose output swing and impedance are independently set by current DACs and resistors, in a VM transmitter, output swing and impedance are tightly coupled to each other. In other words, as shown in Figure 2.2(b), any changes to the FFE (or preemphasis) settings which essentially introduce data-dependent dynamic amplitude modulation will require meticulous controls of the resistor DACs to maintain matched termination. These controls inevitably introduce extra logic on the data-path and thus extra power penalty.

Figure 2.2: (a) simplified model for CML transmitter and (b) simplified model for VM transmitter

At low data-rates where the signaling power consumption is relatively large, the power overhead from extra digital gates on the data-path is mild. However, as the data-rate increases and the digital CV<sup>2</sup>f power rises along with it, the power consumed by the complex pre-driver and per-segment logic necessary to support these feed-forward equalization voltage-mode (FFEVM) TXs can eliminate any benefit from the reduced signaling power. The following sections of the chapter therefore analyze in details both the signaling and digital power consumption of a FFEVM transmitter. With the understanding of this power issue, a TX architecture with a new pre-emphasis scheme will be presented to achieve both good signaling and digital power consumption.

#### 2.2 FFE Voltage-Mode Transmitter Power Analysis

Most of the earlier work in FFEVM designs has focused on reducing signaling power overheads due to pre-emphasis. However, if improving the final driver's signaling power results in more parasitic capacitance on the high-speed driver path, the extra digital switching power overhead may easily counteract all of the signaling power savings. Therefore, to improve the overall transmitter power efficiency, both signaling power and digital power must be optimized together. In this section, we will first review how signaling power can be improved by increasing the total supply path impedance. We then analyze the digital power overhead associated with these schemes before proposing our solution. N

#### 2.2.1 Signaling Power Analysis

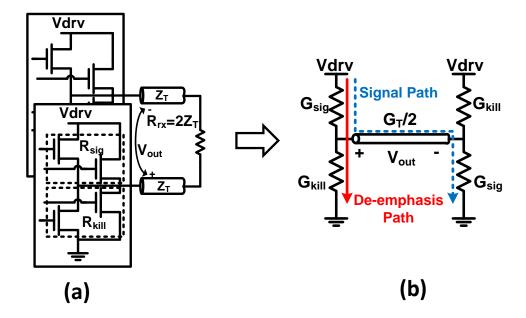

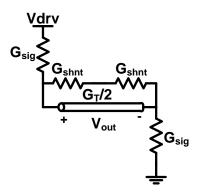

The conventional voltage-mode transmitter design incorporating FFE or pre-emphasis (CVPEVM) was first introduced in [11]. As shown in Figure 2.3 with its equivalent circuit, the output voltage level was lowered (implementing de-emphasis) by creating a path (with a single-ended conductance  $G_{\rm kill}$ ) from  $V_{\rm drv}$  to ground in combination with the main signal path (with a single-ended conductance  $G_{\rm sig}$ ). Since both the  $G_{\rm kill}$  and the  $G_{\rm sig}$  paths are composed of segmented transistors, by moving conductance from one path to the other (i.e. turning on/off transistors in each path) but keeping their sum equal to the channel's characteristic conductance, one can change the output amplitude and hence the pre-emphasis level without sacrificing output termination.

Figure 2.3: conventional pre-emphasis scheme

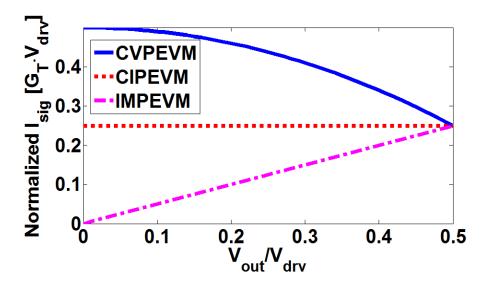

The major issue with this topology, however, stems from its degraded signaling power efficiency. We can express its signaling current  $I_{sig}$  in terms of output differential amplitude  $V_{out}$  as (derived in the Appendix A):

$$I_{\text{sig}} = G_{\text{T}} V_{\text{drv}} \left[ \frac{1}{2} - \left( \frac{V_{\text{out}}}{V_{\text{drv}}} \right)^2 \right]$$

(2.6)

where  $G_T$  is the single-ended characteristic conductance of the channel and  $V_{drv}$  is the supply voltage of the driver. From (2.6), we can see that  $I_{sig}$  increases when  $V_{out}$  is reduced. In other words, the efficiency with back-off is poor since more power is consumed when transmitting lower signal power. This occurs because the total supply path impedance from  $V_{drv}$  to ground is reduced as  $G_{kill}$  is increased in order to deemphasize the transmitted signal.

To deal with this particular signaling power issue, an alternative type of driver — which we will refer to as a constant-current pre-emphasis voltage-mode driver (CIPEVM) — was introduced in [10] to maintain constant  $I_{sig}$  as  $V_{out}$  varies. As shown in Figure 2.4, an extra path (with a single-ended conductance  $G_{shnt}$ ) in parallel with the differential channel is used for de-emphasis. The total supply path impedance can thus be held constant regardless of the output voltage, resulting in a constant  $I_{sig}$ :

$$I_{\text{sig}} = \frac{1}{4} G_{\text{T}} V_{\text{drv}} \tag{2.7}$$

Figure 2.4: (a) constant-current pre-emphasis scheme and (b) its equivalent circuit

Figure 2.5: (a) impedance modulated pre-emphasis scheme and (b) its equivalent circuit

To further reduce the signaling power, the most effective method<sup>5</sup> is to use the impedance modulated pre-emphasis voltage-mode (IMPEVM) transmitter proposed in [12]. As shown by the equivalent circuit in Figure 2.5, V<sub>out</sub> is determined by the voltage divider ratio between the driver's output impedance and the channel's characteristic impedance. By increasing the driver's output impedance we can lower Vout and also

<sup>&</sup>lt;sup>5</sup> Assuming there is no supply or load impedance modulation.

increase the total supply path impedance. Therefore,  $I_{sig}$  can be made to scale linearly with  $V_{out}$ :

$$I_{\text{sig}} = \frac{1}{2} G_{\text{T}} V_{\text{out}} \tag{2.8}$$

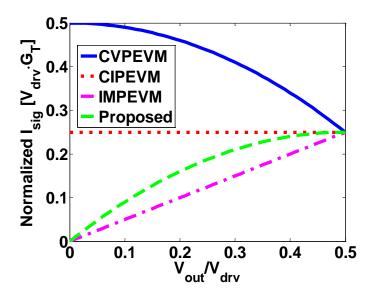

As shown in Figure 2.6, although impedance modulation is attractive in substantially reducing signaling power relative to the original scheme, this approach comes at the expense of sacrificing output termination and hence system linearity (and thus perhaps signal integrity). More importantly, as will be discussed in the next subsection, its pre-driver's digital power overhead due to the non-linear driver conductance to  $V_{out}$  mapping could compromise its overall energy efficiency.

Figure 2.6: signaling power comparison of previous drivers

#### 2.2.2 Digital Power Analysis

To evaluate the digital power consumption from the pre-drivers and associated digital logic, we need to know how the driver should be segmented to enable pre-emphasis control. This can be done by finding the mapping between the conductance of each of the transmitter's devices (i.e.  $G_{sig}$ ,  $G_{kill}$ , etc) to  $V_{out}$ . The detailed derivations are shown in the Appendix A; in this section we will provide only the most important equations that highlight the issue at hand.

For CVPEVM, its pull-up conductance ( $G_{sig}$ ) and pull-down conductance ( $G_{kill}$ ) as a function of  $V_{out}$  are:

<sup>&</sup>lt;sup>6</sup> For all of the analyses below, we will assume that a 1 is being transmitted for the current bit (i.e.,  $V_{out} \ge 0$ ). The output polarity definition matches that shown in Figure 2.2.

$$G_{\text{sig}}(V_{\text{out}}) = \left(\frac{1}{2} + \frac{V_{\text{out}}}{V_{\text{dry}}}\right)G_{\text{T}}$$

(2.9)

$$G_{kill}(V_{out}) = \left(\frac{1}{2} - \frac{V_{out}}{V_{dry}}\right)G_{T}$$

(2.10)

From (2.9) and (2.10) it is apparent that in order to support the maximum pre-emphasis strength – i.e.,  $V_{out}$  covering the range from  $V_{drv}/2$  to  $0-G_{sig}$  should take on values between  $G_T$  and  $G_T/2$ , while  $G_{kill}$  should span from 0 to  $G_T/2$ . Therefore, the maximum required switching conductance is  $G_{sw,MAX} = G_T/2$  in order to achieve the full range of pre-emphasis strength.

To find the required number of segments, we must also know the minimum conductance ( $G_{sw,MIN}$ ) we need to switch from one branch to the other in order to achieve the required pre-emphasis voltage resolution  $V_{out,LSB}$ . This conductance is set by:

$$G_{\text{sw,MIN}} \approx V_{\text{out,LSB}} \cdot \min\left(\left|\frac{dG_{\text{sig}}}{dV_{\text{out}}}\right|, \left|\frac{dG_{\text{kill}}}{dV_{\text{out}}}\right|\right) = \frac{V_{\text{out,LSB}}}{V_{\text{dry}}} G_{\text{T}}$$

(2.11)

With  $G_{sw,MAX}$  and  $G_{sw,MIN}$  known, we can then find the total number of segments  $N_{seg}$ :

$$N_{\text{seg}} = \frac{G_{\text{br,MAX}}}{G_{\text{br,MIN}}} = \frac{G_{\text{T}/2}}{\frac{V_{\text{out,LSB}}}{V_{\text{dry}}}G_{\text{T}}} = \frac{1}{2} \frac{V_{\text{dry}}}{V_{\text{out,LSB}}}$$

(2.12)

For the CIPEVM scheme, the same method can be applied to find the branch conductance mappings, resulting in:

$$G_{\text{sig}}(V_{\text{out}}) = \left[ \left( \frac{V_{\text{out}}}{V_{\text{drv}}} \right)^2 + \left( \frac{V_{\text{out}}}{V_{\text{drv}}} \right) + \frac{1}{4} \right] G_{\text{T}}$$

(2.13)

$$G_{\text{kill}}(V_{\text{out}}) = \left[ \left( \frac{V_{\text{out}}}{V_{\text{drv}}} \right)^2 - \left( \frac{V_{\text{out}}}{V_{\text{drv}}} \right) + \frac{1}{4} \right] G_T$$

(2.14)

$$G_{\text{shnt}}(V_{\text{out}}) = \left[-2\left(\frac{V_{\text{out}}}{V_{\text{drv}}}\right)^2 + \frac{1}{2}\right]G_{\text{T}}$$

(2.15)

From the equations above, it should be clear that  $G_{sw,MAX} = G_T/2$  in order to support the full pre-emphasis range. However, as shown in Figure 2.4, unlike CVPEVM whose branch conductance is linearly proportional to  $V_{out}$ , the branch conductance of CIPEVM changes more quickly at high  $V_{out}$  values and saturates at low  $V_{out}$  values. For this reason, the  $G_{sw,MIN}$  of CIPEVM is set by low  $V_{out}$  values:

$$G_{\text{sw,MIN}} \approx V_{\text{out,LSB}} \cdot \min \left( \left| \frac{dG_{\text{sig}}}{dV_{\text{out}}} \right|, \left| \frac{dG_{\text{kill}}}{dV_{\text{out}}} \right|, \left| \frac{dG_{\text{shnt}}}{dV_{\text{out}}} \right| \right)$$

$$= V_{\text{out,LSB}} \cdot \left| \frac{dG_{\text{shnt}}}{dV_{\text{out}}} \right|_{V_{\text{out}} \approx V_{\text{out,LSB}}} \approx \frac{4V_{\text{out,LSB}}^2}{V_{\text{drv}}^2} G_T$$

(2.16)

The required number of segments can therefore be estimated as:<sup>7</sup>

$$N_{\text{seg}} = \frac{G_{\text{sw,MAX}}}{G_{\text{sw,MIN}}} = \frac{G_{\text{T}/2}}{\frac{4V_{\text{out,LSB}}^2}{V_{\text{dry}}^2}G_{\text{T}}} = \frac{1}{8} \frac{V_{\text{drv}}^2}{V_{\text{out,LSB}}^2}$$

(2.17)

Finally, for the IMPEVM design, the  $G_{\mbox{\scriptsize sig}}$  to  $V_{\mbox{\scriptsize out}}$  mapping is:

$$G_{\text{sig}}(V_{\text{out}}) = \frac{V_{\text{out}}}{V_{\text{dry}} - V_{\text{out}}} G_{\text{T}}$$

(2.18)

from which we find that  $G_{sw,MAX} = G_T$ . Similar to CVPEVM,  $G_{sig}$  is also a non-linear function of  $V_{out}$ (Figure 2.7), and  $G_{sw,MIN}$  is also set by the region with low  $V_{out}$ :

$$G_{\text{sw,MIN}} \approx V_{\text{out,LSB}} \cdot \min\left(\left|\frac{dG_{\text{sig}}}{dV_{\text{out}}}\right|\right) = V_{\text{out,LSB}} \cdot \left|\frac{dG_{\text{sig}}}{dV_{\text{out}}}\right|_{V_{\text{out}} \approx V_{\text{out,LSB}}} \approx \frac{V_{\text{drv}}V_{\text{out,LSB}}}{\left(V_{\text{drv}} - V_{\text{out,LSB}}\right)^2} G_T \approx \frac{V_{\text{out,LSB}}}{V_{\text{drv}}} G_T$$

(2.19)

where the last approximation is valid when  $V_{out,LSB}$  is small, which is usually the case for a reasonable pre-emphasis resolution. Therefore, the total required number of segments for a  $V_{out}$  range of  $0-V_{drv}/2$  can be estimated as:<sup>8</sup>

$$N_{\text{seg}} = \frac{G_{\text{sw,MAX}}}{G_{\text{sw,MIN}}} \approx \frac{G_{\text{T}}}{\frac{V_{\text{out,LSB}}}{V_{\text{drv}}}} = \frac{V_{\text{drv}}}{V_{\text{out,LSB}}}$$

(2.20)

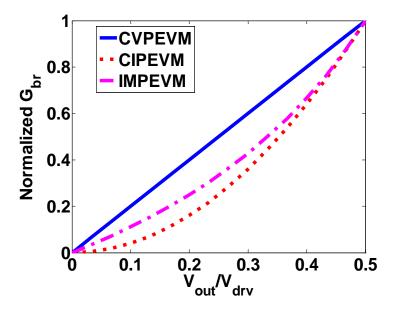

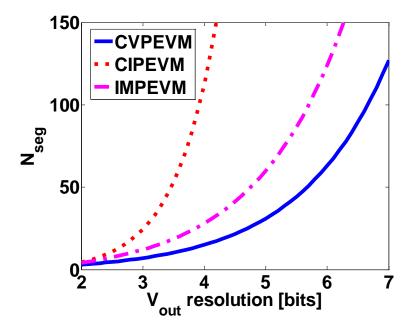

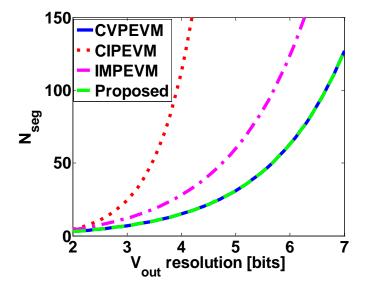

From (2.12), (2.17) and (2.20), we see that due to its linear characteristics, CVPEVM requires a substantially smaller  $N_{seg}$ than the CIPEVM and IMPEVM drivers. As we will describe next, this increase in the number of segments will result in increased switching capacitance, and hence increased digital switching power consumption. Specifically, since each driver segment requires some type of selection logic for preemphasis control and buffers for driving the final signaling transistors, the total switching capacitance for the final driver stage can be approximated as ([13]):

$$C_{fin} = N_{seg}C_{lgc,tot} + C_{gt,tot}$$

(2.21)

where  $C_{lgc,tot}$  is the total capacitance from the logic gates (i.e. MUXes, buffers, etc) and  $C_{gt,tot}$  is the total gate capacitance of the final driver devices.

<sup>&</sup>lt;sup>7</sup> Note that although the non-linearity of the driver can be compensated by using non-uniform segment sizes, as long as the smallest segment doesn't hit the minimum size constraint of a given technology, the total loading from the non-uniform distribution can still be approximated by the uniform segment distribution with  $G_{\text{sw MIN}}$  as the step size.

<sup>&</sup>lt;sup>8</sup> This range was chosen to have a fair comparison with the terminated PEVM, which can only support swings of up to  $V_{\rm drv}/2$ . This does not change the minimum step size of the IMPEVM however. In other words, if we want to take advantage of the IMPEVM's potential for larger  $V_{\rm out}$ , more segments would be required.

Figure 2.7: switched branch conductance vs V<sub>out</sub> for different drivers

The width of the final driver transistors is set by the impedance of the channel, and hence is roughly identical for all of the architectures with the same peak swing. Furthermore, since the impedance of the channel is relatively low, these driver transistors are usually relatively large. Thus, when segmented to enable pre-emphasis control, the size of each segment typically remains larger than minimum (i.e. Cgt,tot remains constant). However, as shown in Figure 2.8, since the capacitive fanout of these digital pre-driver gates is typically greater than 1 (commonly 2-4), the per-segment high-speed gates within each driver cell will often hit the minimum size constraint, resulting in larger final driver switching power for larger N<sub>seg</sub>. As shown for example in Figure 2.9 for a 5-bit preemphasis resolution, N<sub>seg</sub> is ~62 for IMPEVM as compared to 31 for CVPEVM. If the pre-driver devices in the CVPEVM have already hit minimum size, the extra 31 segments required for IMPEVM can cause this design to consume 2x more digital switching power than a CVPEM with the same resolution. To provide some numbers, with  $C_{lgc,tot} \sim 10 fF$ , these 31 extra segments will consume ~1.1mW of additional digital power at 10Gb/s with a 1.2V supply. This 1.1mW is larger than the signaling power of a driver with a 200mV peak differential output amplitude (i.e., 400mV V<sub>drv</sub>), and thus these additional segments would heavily compromise the benefits of low-swing signaling.

Figure 2.8: normalized digital power vs. # of segments

Figure 2.9: number of segments vs. Vout resolution for different designs

Note that if more complex pre-driver and decoder architectures – such as the look-up-tables (LUT) used in [10], [12] – are required to compensate the driver's non-linearity, the digital power overhead will increase even further as compared to a linear driver which requires only simple decoders/unit elements. This combined extra pre- and final-driver switching power can easily exceed the signaling power consumption ([10], [12]), and the benefit of reducing signaling power by utilizing IMPEVM or CIPEVM is compromised.

#### 2.3 Proposed Pre-Emphasis Voltage-Mode Transmitter

As discussed in the previous section, the CIPEVM and IMPEVM architectures have improved signaling power efficiency over CVPEVM due to their higher supply path impedance at lower swings. However, both architectures penalize the digital power as compared to a linear CVPEVM driver.

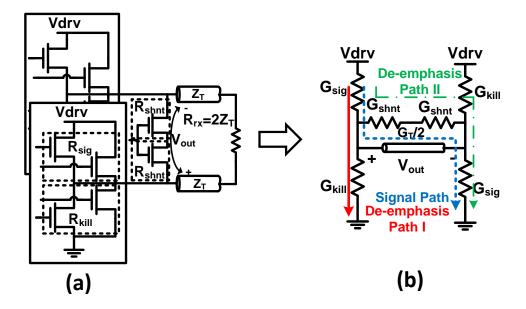

Figure 2.10: equivalent circuit of proposed PEVM

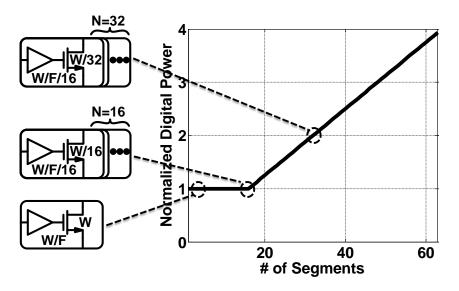

Fortunately, by modifying the means by which pre-emphasis is implemented, we can combine the advantages from IMPEVM and CVPEVM to improve the signaling power and maintain low digital power simultaneously. Specifically, in [11], signaling power is wasted in the crowbar current paths created from  $V_{drv}$  to ground when reduced swing (due to pre-emphasis) is used. Instead, extending the technique used in CIPEVM, the transmitter's output voltage is modulated by using only a shunting path that is in parallel to the channel – as shown in Figure 2.10. When moving conductance from  $G_{sig}$  to  $G_{shnt}$  to reduce  $V_{out}$ , we actually increase the overall supply path impedance from  $V_{drv}$  to ground, and hence reduce signaling current. The output termination is also maintained since the sum of  $G_{sig}$  and  $G_{shnt}$  is kept constant and equal to  $G_{T}$ .  $V_{out}$  vs.  $G_{sig}$  follows the desired linear relationship shown in (2.22):

$$G_{\text{sig}}(V_{\text{out}}) = \frac{2V_{\text{out}}}{V_{\text{dry}}}G_{\text{T}}$$

(2.22)

With  $G_{sw,MAX}$  and  $G_{sw,MIN}$  set to  $G_T$  and  $\frac{2V_{out,LSB}}{V_{drv}}G_T$  respectively, this driver requires the same  $N_{seg}$  as that of CVPEVM:

$$N_{\text{seg}} = \frac{G_{\text{Sw,MAX}}}{G_{\text{sw,MIN}}} = \frac{G_{\text{T}}}{\frac{2V_{\text{out,LSB}}}{V_{\text{drv}}}} = \frac{1}{2} \frac{V_{\text{drv}}}{V_{\text{out,LSB}}}$$

(2.23)

\_

$<sup>^{9}</sup>$  Note that if lower pre-emphasis resolution can be tolerated (or equivalently, more segments for the same resolution), this driver can be operated in IMPEVM mode by disabling the shunting branch and using only the on/off the  $G_{sig}$  path transistors.

$I_{\text{sig}}$  can also be shown to scale down with decreased  $V_{\text{out}}$  in the following manner:

$$I_{\text{sig}} = G_{\text{T}} V_{\text{out}} \left( 1 - \frac{V_{\text{out}}}{V_{\text{drv}}} \right) \tag{2.24}$$

As shown in Figure 2.11, the proposed architecture allows signaling current reduction along with the transmitted swing (albeit not quite proportionally as with IMPEVM) while also maintaining output termination. Its required number of segments follows that of a linear driver and is therefore ~2x smaller than that of IMPEVM (Figure 2.12), thus enabling it to also achieve good digital power efficiency.

Figure 2.11: signaling power comparison

Figure 2.12: number of segments vs V<sub>out</sub> resolution

## 2.4 Transmitter Architecture and Circuit Implementation

Now that we have analyzed the digital power overhead of implementing pre-emphasis, we should also consider the impact of integrating other functionality (i.e., impedance control) on the energy-efficiency of a PEVM. In this section, we will therefore first discuss our choice for the impedance control scheme, and then introduce the overall transmitter architecture. We will then describe the circuit implementations, with an emphasis on the impedance and swing control loops that incorporate an online comparator offset cancellation scheme.

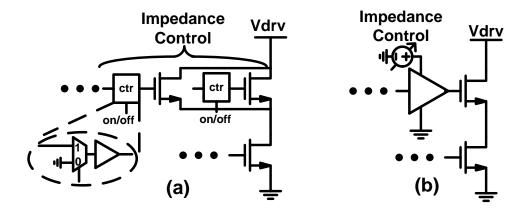

#### 2.4.1 Choice of Impedance Calibration Schemes

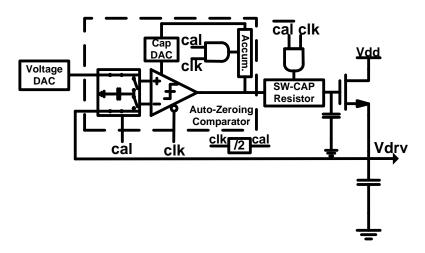

There are two popular schemes for controlling/setting the output impedance of a transmitter. The "digital" approach (Figure 2.13(a)) incorporates both impedance calibration and pre-emphasis control into the segment design ([10], [14]). Although this may simplify the overall implementation, even with non-uniform segments ([14]), this choice tends to compromise the pre-emphasis resolution for a reasonable total number of segments. For example, the design in [14] used 24 segments to achieve 4.6-bit dynamic range in impedance but only ~2-bit dynamic range in pre-emphasis. Therefore, to decouple impedance calibration and pre-emphasis control, and hence increase the pre-emphasis dynamic range, we choose to use the "analog" approach proposed in [11], [15]. Specifically, as shown in Figure 2.13(b), separate regulator-based control loops adjust the supplies of the pre-drivers in order to control the impedance of the pull-up, pull-down, and shunt devices, leaving segmentation only for pre-emphasis coefficient control.

Figure 2.13: (a) "digital" impedance calibration scheme and (b) "analog" impedance calibration scheme

#### 2.4.2 Overall Architecture

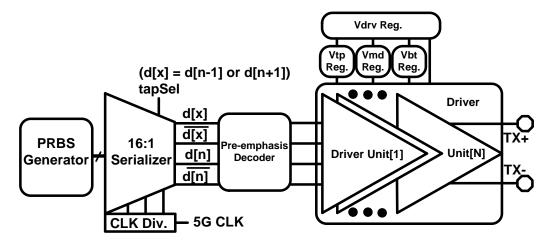

Figure 2.14: overall transmitter architecture

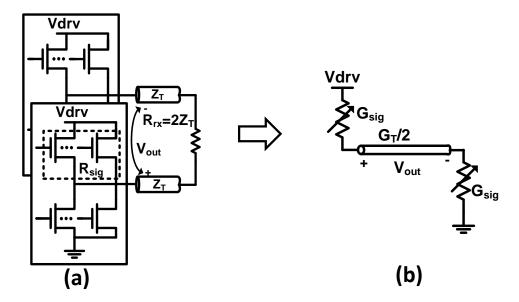

The overall transmitter architecture is shown in Figure 2.14. Since a large number of TX pre-emphasis taps quickly leads to excessive pre-driver power due to complex segment logic, in this design we have chosen to implement only 2 taps of pre-emphasis. <sup>10</sup> The pre-emphasis tap can be assigned to be either the post-cursor or the pre-cursor. Following the 16:1 tree-type serialization, before entering the final driver, the digital data stream is pre-decoded in order to simplify the logic required within each driver segment.

In this design, the final driver comprises of 15 segments, which corresponds to the maximum achievable resolution before the pre-driver logic transistors hit the minimum size constraint. This results in a 4-bit tunable pre-emphasis weight from 0 to 100% with a step of ~6.7%.

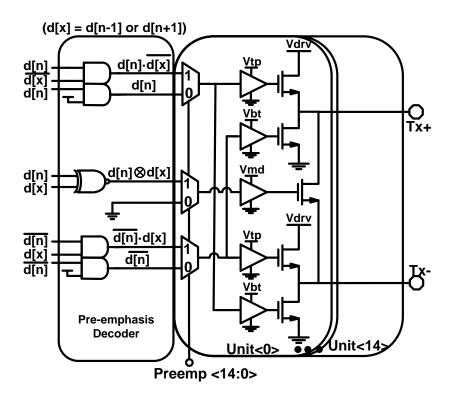

#### 2.4.3 Pre-emphasis Decoder

Knowing that the target TX FIR filter will be high-pass in nature, the pre-emphasis decoder simply looks for differences/similarities between the current bit and the next or previous bits (using XORs and ANDs) in order to provide appropriate signals for the pull-up, pull-down, and shunt devices. As shown in Figure 2.15, the principle motivation for performing this pre-decoding is that these logic gates can be shared amongst all final driver segments. Each individual segment then only needs to include MUXes to decide whether to use the pre-decoder outputs or simply the raw data bit. In comparison to a design which effectively requires multiple complex logic gates within each segment (e.g. [12]), this design moves some logic gates out of the driver segments to a shared non-minimum-sized pre-driver logic and hence results in significantly reduced digital power overhead.

<sup>&</sup>lt;sup>10</sup> A multi-tap design can be implemented by incorporating a more complicated decoder to select driver segments. However, multi-tap equalizers typically require higher resolution on a per-tap basis, leading to additional segments and exacerbating the digital switching power issue. For this reason, receiver equalization is often a more efficient means of dealing with higher-loss channels ([13]).

#### 2.4.4 Driver Segments

The driver segment includes the interface between the full-swing digital data and the transmitted low-swing analog signal. Since the target maximum swing of this particular design is low (<250mV differential amplitude), each segment utilizes an N-over-N voltage mode driver. Similarly, the shunt devices are also implemented with NMOS transistors due to the low output common-mode voltage. The supply voltage of the N-over-N leg is connected to V<sub>drv</sub>, which is generated by the swing control regulator. The gate voltage of the pull-up, pull-down, and shunt devices are connected to 3 buffers, each with a supply of V<sub>tp</sub>, V<sub>bt</sub> and V<sub>md</sub> generated from the impedance control regulators. <sup>11</sup> The pull-up, pull-down and shunt devices are sized to give roughly equal V<sub>tp</sub>, V<sub>bt</sub> and V<sub>md</sub> so that the buffer delays on the three paths can be approximately matched. The buffer chains are composed of an even number of inverters to balance rise and fall times across different corners.

Figure 2.15: decoder and segment schematic

As mentioned earlier, since we have decoupled the impedance control from the pre-emphasis control, as shown in Figure 2.15, MUXes can simply be added to the inputs

<sup>&</sup>lt;sup>11</sup> For transmitters that must support higher peak swing, the N-over-N voltage mode driver could be replaced with a P-over-N type. An NMOS transistor or a transmission gate could be used for the shunt device of a high-swing TX depending on the output common mode and the maximum pre-emphasis strength. For a P-over-N driver, the ground of the pre-driver for the PMOS output device would be regulated (instead of the supply) in order to control the PMOS transistor's impedance.

of each segment in order to achieve coefficient adjustment. If the segment is enabled for pre-emphasis, the MUX within the segment will connect the pull-up, pull-down, and shunt device gates to the outputs of the pre-decoder that compares between the current and next or previous bits. If the segment is not configured for pre-emphasis, the shunt device will be grounded and the pull-up and pull-down devices will be driven purely by the current bit. Utilizing this simplified segment logic that consists of only 2-input MUXes and level-shifting inverters minimizes the final-driver power overhead to ~1.7mW from the per-segment high-speed digital gates.

### **2.4.5** Impedance Control Loop with Online Comparator Offset Calibration

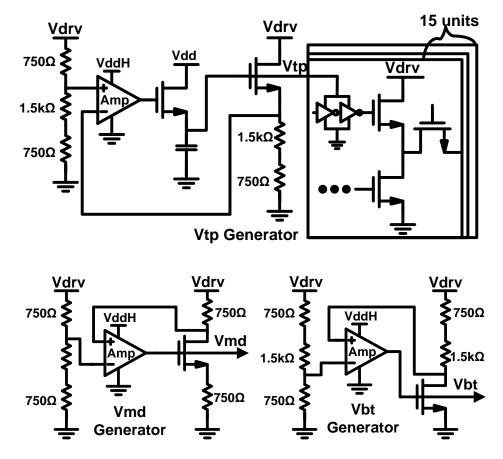

As shown in Figure 2.16, impedance control is achieved through the regulated gate voltages  $V_{tp}$ ,  $V_{bt}$ , and  $V_{md}$ . Similar to the technique used in [15], these voltages are generated by replica-bias circuits that force a replica segment to have the same impedance as a reference resistor string.

Figure 2.16: schematic of impedance control loop

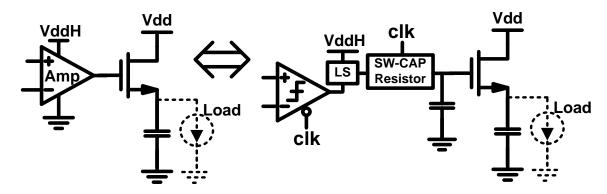

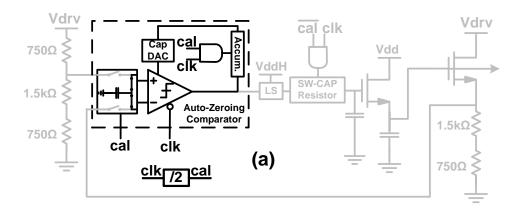

As highlighted in Figure 2.17, the regulator utilizes a comparator-based architecture with a source-follower output stage in order to reduce the power consumed by its feedback loop ([16]). Since  $V_{tp}$  and  $V_{bt}$  as well as perhaps  $V_{md}$  may need to be very close to Vdd, and since the regulator's power device is an NMOS source-follower, the gate voltage of the power device may need to be higher than Vdd. The regulator feedback control loop therefore uses a higher voltage (but very low current) supply VddH (e.g. 1.6V)<sup>12</sup> along with a level shifter to support this higher gate voltage.

Figure 2.17: implementation of comparator-based regulator loop

Given the broadband low output impedance and  $g_m r_o$  intrinsic PSRR of the NMOS source follower power device, the regulator's feedback control loop need not achieve high bandwidth ([16], [17]). Hence, this design utilizes a switched-capacitor resistor (SCR) at the gate of the power device to implement a low-pass filter and attenuate the output voltage ripple due to the loop's dither to a simulated value of less than 1mV (the capacitance at the gate of the power device is ~1000X larger than that of the SCR). Due to the higher supply VddH, the devices in the switched-cap resistor are all thick-oxide to ensure reliability.

The error signal between the replica and the reference resistor string is generated by a comparator. Given the relatively low target swing and hence low common-mode at the comparator's input, the feedback comparator is implemented with a PMOS-input StrongArm latch ([18]). Minimizing the power dissipation of this comparator leads to nearly minimum sized devices. Thus, if left uncompensated, the comparator (and hence the overall regulator) could exhibit >100mV of offset. Moreover, since changing the output swing will change the output common-mode and hence the input-referred offset, online digital offset cancellation was implemented to continuously eliminate the comparator's offset.

This offset cancellation was achieved by time-interleaving the operation of the comparator so that it auto-zeroes its own offset and also provides feedback for the regulator. In the calibration phase (Figure 2.18(a)), the comparator is disconnected from the regulation loop by shorting its inputs to a capacitor that stores the input common-mode voltage. The output of the comparator changes according to its offset value and is

<sup>&</sup>lt;sup>12</sup> Since VddH is effectively used only to set the DC voltage on a capacitor, it supplies minimal current in steady state. Thus, if a suitable externally generated supply was unavailable, VddH could be straightforwardly generated with an on-chip charge-pump ([16]).

fed into an accumulator. The accumulated output controls a 5-bit capacitor-DAC (CDAC) that is connected to the drains of the input devices (similar to [19]) to cancel the comparator's offset. After the calibration phase, the loop enters the regulation phase (Figure 2.18(b)) by re-connecting the comparator inputs to the reference strings/replica cells and by disabling the feedback accumulator. The offset-cancelled comparator then behaves as a normal comparator to amplify the input difference so as to adjust the regulated voltage. In steady-state, the output of the offset accumulator will dither around a certain value. In order to limit this offset dither, the LSB of the CDAC is chosen to be 4mV. The calibration control signal (cal) is a divided by 2 clock pattern from the 78.125MHz clk signal which itself is a divided signal from the global high-speed clock.

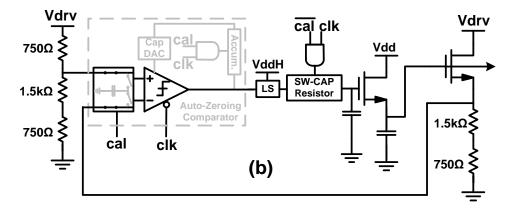

Figure 2.18: illustration of interleaved comparator offset calibration and regulation process: (a) comparator auto-zeroing (calibration) phase and (b) regulation phase

#### 2.4.6 Output Amplitude Control Loop

As shown in Figure 2.19, the swing control loop operates in a manner very similar to the impedance control loops. Swing adjustment is achieved through a voltage regulator that sets  $V_{drv}$  based on a reference voltage generated from a voltage DAC. The same

comparator offset cancellation scheme is used here to track common-mode variation induced offset changes as the swing values are adjusted. Since  $V_{drv}$  is designed to be always  $\leq 500 \text{mV}$ , no extra VddH is required for this NMOS power device.

Figure 2.19: schematic for swing control loop

#### 2.5 Measurement Results

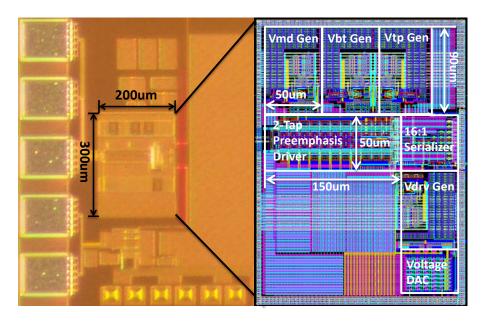

In order to experimentally verify the proposed TX architecture and circuits, a test-chip including this design was fabricated in a 65nm LP CMOS process. The die photo along with the TX layout is shown in Figure 2.20, highlighting that the TX occupies an area of  $\sim 300 \ \mu m \times 200 \ \mu m$ .

Figure 2.20: die photo and TX floor plan

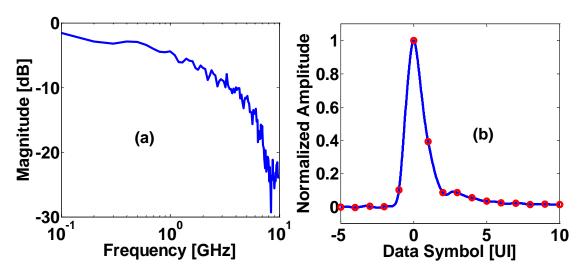

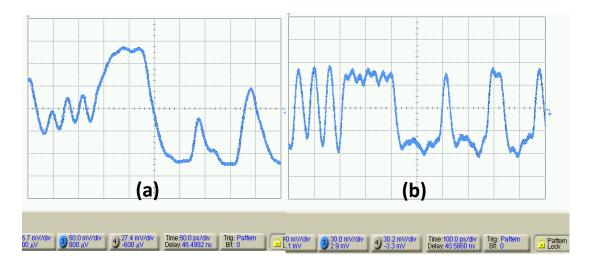

In order to test the TX pre-emphasis functionality, we used the TX to drive a 10" FR4 PCB trace. Before characterizing the TX itself however, we must first measure the characteristics of this channel. Using the channel's measured S21 to simulate the 10Gb/s pulse response (Figure 2.21) shows ~13dB loss at Nyquist (5GHz) and a dominant post-cursor whose magnitude is ~0.4 of the cursor.

Figure 2.21: 10" FR4 PCB trace (a) S21 and (b) simulated 10Gb/s pulse response

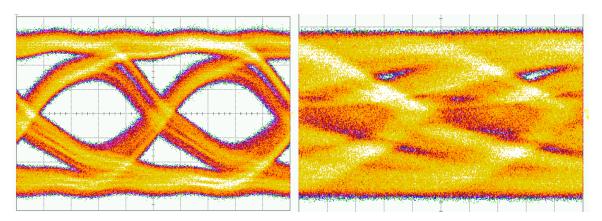

Before turning on pre-emphasis, we measured the eye diagrams with  $2^{23}$ -1 PRBS data and  $V_{out} = 250 \text{mV}$  before and after this channel, as shown in Figure 2.22. Since the total output pad capacitance including ESD is about 1.3pF and there is ~2" of FR4 PCB trace between the test-chip and the connector, the intrinsic output bandwidth of the TX (even without the additional 10" trace) is limited to ~4GHz. This inherent bandwidth limitation is the reason for the ISI apparent in Figure 2.22. After the 10" trace, the eye is completely closed. However, as shown in Figure 2.23, after configuring the TX to apply a pre-emphasis filter of (10x[n]-5x[n-1])/15, the eye is opened with 3.19ps/22.22ps RMS/P2P jitter.

Figure 2.22: 2<sup>23</sup>-1 PRBS eye before and after 10" trace with post-tap pre-emphasis turned off (100mV/div vertical, 20ps/div horizontal)

Figure 2.23: 2<sup>23</sup>-1 PRBS eye before and after 10" trace with post-tap pre-emphasis turned on (100mV/div vertical, 20ps/div horizontal)

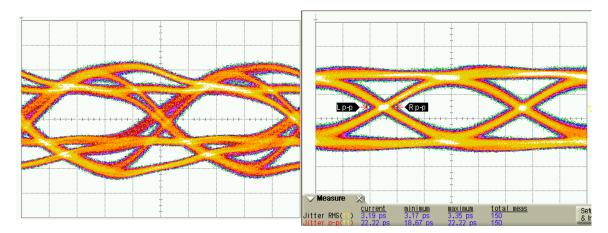

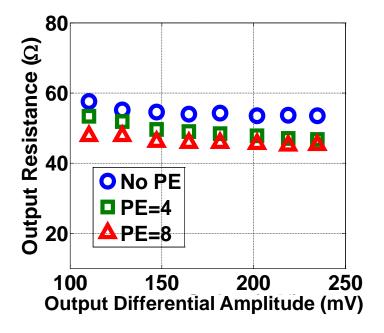

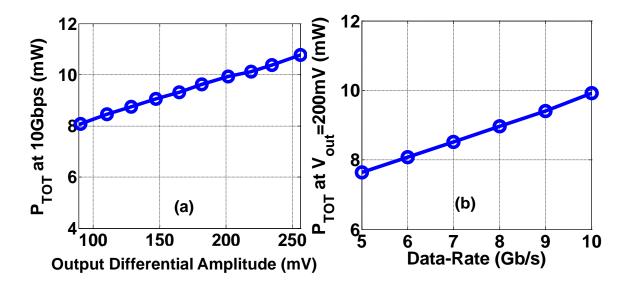

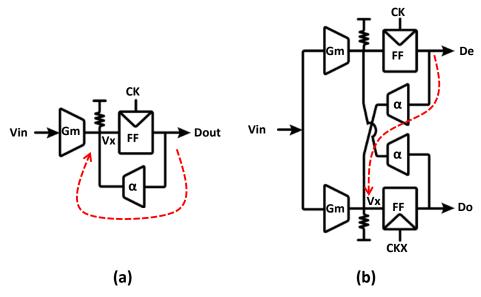

To verify the impedance and swing control loops, Figure 2.24 and Figure 2.25 show the measured characteristics of the transmitter. Across output swings and preemphasis settings (PE code), the output impedance remains nearly  $52\Omega$ , indicating the effectiveness of the impedance loop. Note that the deviation from the ideal  $50\Omega$  value is due to mismatches between the different reference resistor strings within each regulator.

Figure 2.24: TX output swing tuning curve

Figure 2.25: TX output impedance vs. signal amplitude

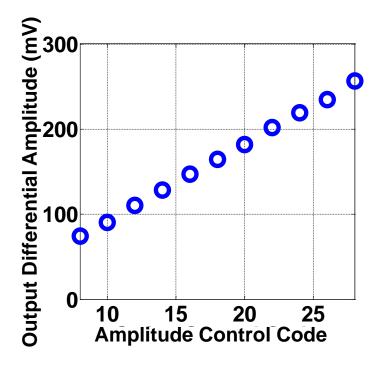

Finally, the power consumption of the TX was characterized. Figure 2.26 shows the signaling power vs. pre-emphasis code at a nominal output swing of 250mV. The measured signaling power drops with lower swing and tracks almost perfectly with the analytical predictions.

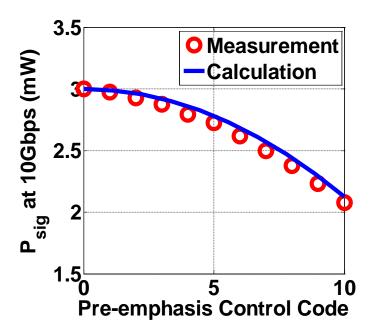

Figure 2.26: signaling power with 250mV differential amplitude swing vs. pre-emphasis setting

The total power vs. output differential amplitude is plotted in Figure 2.27(a), and Figure 2.27(b) shows the total power vs. data-rate. The total power consumption is ~10mW for a 10Gb/s 200mV differential amplitude PRBS sequence. Based on these trends, we can also extract that the analog power is ~5mW, with 2.4mW due to the signaling power and the remaining 2.6mW from other biasing and leakage paths. Similarly, the extracted total digital power is ~5mW, which consists of ~2.8mW for the 16:1 serializer and clock divider chain, ~1.7mW for the final driver, <sup>14</sup> and ~0.5mW for the pre-decoder.