# Time-Division Duplexing Solutions for Wireless Transcievers

Amanda Pratt

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2016-18 http://www.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-18.html

May 1, 2016

Copyright © 2016, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### **Time-Division Duplexing Solutions for Wireless Transcievers**

by

Amanda Pratt

A thesis submitted in partial satisfaction of the requirements for the degree of Master of Science

$\mathrm{in}$

**Electrical Engineering**

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolic, Chair Professor Elad Alon Professor Ali Niknejad

Spring 2014

The thesis of Amanda Pratt, titled Time-Division Duplexing Solutions for Wireless Transcievers, is approved:

| Chair | <br>Date |  |

|-------|----------|--|

|       | <br>Date |  |

|       | <br>Date |  |

University of California, Berkeley

## Time-Division Duplexing Solutions for Wireless Transcievers

Copyright 2014 by Amanda Pratt

#### Abstract

Time-Division Duplexing Solutions for Wireless Transcievers

by

Amanda Pratt

Master of Science in Electrical Engineering University of California, Berkeley Professor Borivoje Nikolic, Chair

The wireless age poses an unprecedented strain on global spectrum resources. As such, the available frequency spectrum is becoming more segmented, creating a need for wireless front-ends with wide bandwidths and unpaired spectrum capabilities. The features of timedivision duplexing (TDD) lend themselves to this current and future need, making it a growing means of wireless communication across the mobile spectrum.

Integrating a high-power transmitter and a highly sensitive receiver on the same antenna, as is desired in TDD, remains a difficult problem for time-division duplexing transceivers. This work describes wide-band TDD solutions which enable the integration of a power amplifier (PA) on the same antenna as a sensitive low-noise amplifier (LNA).

The first part of this work discusses the design of a transmit/receive (Tx/Rx) switch, a solution for transceiver integration, implemented in bulk CMOS. The simulation results from the extracted layout of this design show improved insertion loss performance and power tolerance over the state-of-the-art Tx/Rx switches in CMOS.

The second part of this work presents the design of a second TDD solution, which implements device re-use, a novel approach to the TDD power tolerance problem. This solution overcomes some of the inherent non-idealities of a CMOS Tx/Rx switch, such as insertion loss, by embedding an LNA within the devices of a digital PA. The results from an extracted layout of this device are also presented.

The end result of this work is two different, novel approaches to integrating transmit and receive circuitry on the same antenna, each achieving state-of-the-art performance. We also provide a discussion of the benefits and drawbacks of each solution. This thesis is dedicated to my teachers, mentors, managers, friends, and family members who could see a future for me before I could imagine it and who showed me the way before I knew there was somewhere to go. Thank you

# Contents

| Co | ontents                                                                                                                                                                                                  | ii                                                                     |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Li | st of Figures                                                                                                                                                                                            | iv                                                                     |

| Li | st of Tables                                                                                                                                                                                             | viii                                                                   |

| 1  | Introduction1.1TDD Transciever Architecture Overview1.2TDD Design Limitations1.3Prior Art                                                                                                                | <b>1</b><br>2<br>3<br>5                                                |

| 2  | General Tx/Rx Definitions<br>2.1 Tx/Rx Metrics                                                                                                                                                           | <b>9</b><br>9                                                          |

| 3  | <b>RF-FPGA Series Tx/Rx Switch Design and Results</b> 3.1       Tx/Rx Switch Design                                                                                                                      | <b>15</b><br>15<br>23<br>30                                            |

| 4  | <ul> <li>Principle of Device Reuse between LNA and PA</li> <li>4.1 The PA's Inspiration for Switch Design</li></ul>                                                                                      | <b>31</b><br>31<br>32                                                  |

| 5  | Design of LNA and PA with Device Reuse5.15.1Inverse Class D PA Background5.2Common Gate LNA Design5.3Switch Design for Device Reuse5.4Coexistence via Device Reuse PA/LNA Simulated Results5.5Conclusion | <ul> <li>34</li> <li>35</li> <li>42</li> <li>52</li> <li>57</li> </ul> |

| 6  | Conclusion         6.1       Summary of Work         6.2       Future Work                                                                                                                               | <b>58</b><br>58<br>58                                                  |

Bibliography

60

iii

# List of Figures

| 1.1 | A simplified diagram of the TDD downlink and uplink division in the time domain.                                                                                                                                                                                                                                                                                                                                 | 1  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

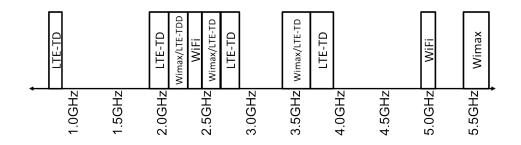

| 1.2 | A simplified diagram indicating spectrum used for some form of mobile TDD communication. Exact spectrum allocations may be found in [3, 4].                                                                                                                                                                                                                                                                      | 2  |

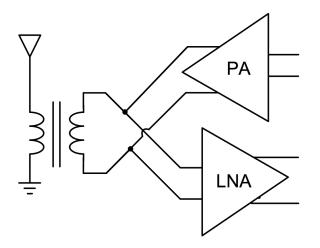

| 1.3 | A simplified diagram of the PA and LNA receive pair connected at one transformer                                                                                                                                                                                                                                                                                                                                 |    |

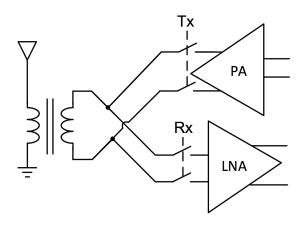

| 1.4 | and antenna                                                                                                                                                                                                                                                                                                                                                                                                      | 3  |

|     | connects its respective device to the antenna. When 'off,' the switch is open and isolates its respective device from the antenna.                                                                                                                                                                                                                                                                               | 4  |

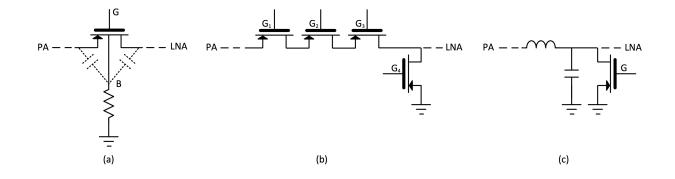

| 1.5 | Tx/Rx bulk CMOS design strategies. (a) Floating wells allow for increased power tolerance. (b) Stacked transistors in the series leg of a series-shunt switch help to increase power tolerance. (c) Inductors act as frequency-dependent resistors when connected to ground during transmit mode, but are resonated out in receive mode when the capacitor is in use. Additional matching network components not | -  |

|     | shown.                                                                                                                                                                                                                                                                                                                                                                                                           | 6  |

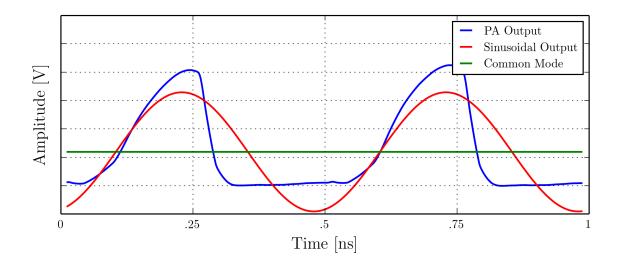

| 2.1 | PA output and sinusoid of equal power and common-mode voltages with common-<br>mode voltage labeled. The known inverse class D PA output and a sinusoid<br>with similar power and common-mode levels are shown in order to illustrate the<br>difference between the two signal shapes and their resulting voltage levels. Switch<br>design should accommodate the worst-case PA output scenario.                 | 14 |

| 3.1 | A simple differential series switch with shunt transistor. One method for creating                                                                                                                                                                                                                                                                                                                               |    |

| 0.1 | an AC ground at the input to the LNTA is to connect the two differential inputs<br>of the LNA with a shunt transistor. Series transistors are used to isolate the AC<br>ground from the PA signal at the antenna.                                                                                                                                                                                                | 16 |

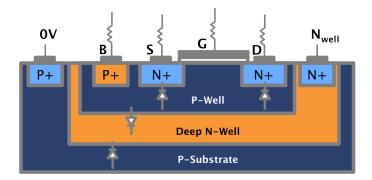

| 3.2 | Cross-section of the deep-Nwell Devices. Thick-oxide deep-Nwell devices are used                                                                                                                                                                                                                                                                                                                                 | 10 |

|     | for the switch's series transistors. The deep-Nwell is set to a fixed voltage while<br>the Pwell, gate, and source/drain nodes are free to oscillate with the incoming<br>signal, preventing the differential voltages from exceeding the requirements of the                                                                                                                                                    |    |

|     | silicon technology                                                                                                                                                                                                                                                                                                                                                                                               | 17 |

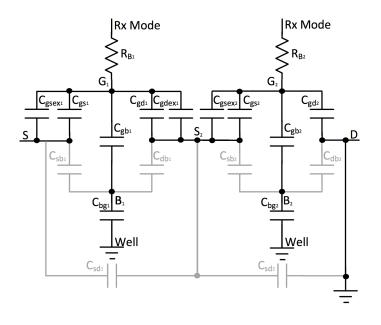

| 3.3   | Complete switch topology. The switch uses two series transistors with floating<br>Pwells to ensure that the differential node voltage limits are satisfied under worst-                                                                                                  |     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.4   | case PA output powers and waveforms                                                                                                                                                                                                                                      | 18  |

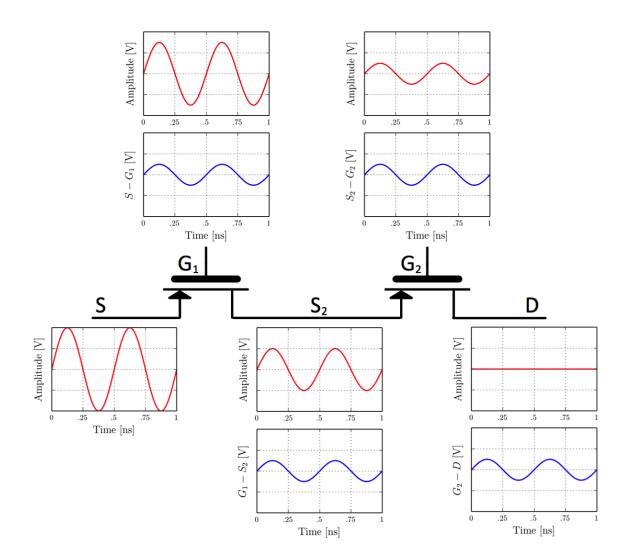

|       | is represented in red. The difference in amplitude between each node is repre-<br>sented in blue                                                                                                                                                                         | 19  |

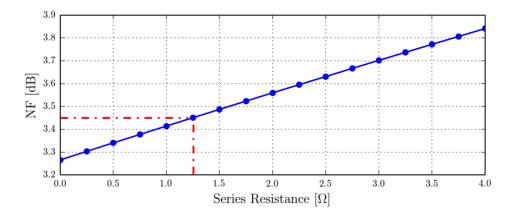

| 3.5   | Noise figure in relation to series resistance at 2 GHz. The noise figure is sensitive to the series resistance at the input of the LNTA. A parametric sweep reveals the                                                                                                  |     |

| 3.6   | relation between resistance and noise figure                                                                                                                                                                                                                             | 20  |

| 0.0   | directly related to insertion loss and thus drives the selection of device width.                                                                                                                                                                                        | 21  |

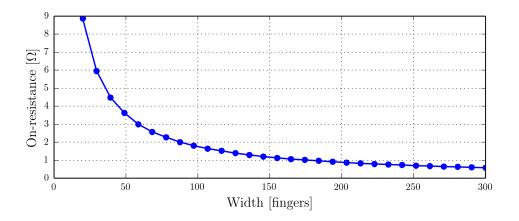

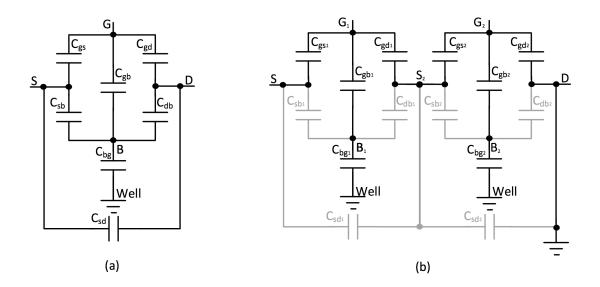

| 3.7   | <ul><li>(a) Transistor parasitic capacitors. The parasitic capacitances between each node of a transistor form a capacitive network, coupling signal between each node.</li><li>(b) Full parasitic capacitance network for switch topology. The signal coupled</li></ul> |     |

|       | between each node is exploited to ensure the differential node voltage limits are                                                                                                                                                                                        |     |

|       | met, as per the technology requirements. Capacitors in grey are small enough                                                                                                                                                                                             |     |

|       | that they do not impact the coupling between nodes                                                                                                                                                                                                                       | 22  |

| 3.8   | Capacitive network with external capacitances added. The external capacitances                                                                                                                                                                                           |     |

|       | ensure the voltage divider caused by the capacitive network divides the PA output                                                                                                                                                                                        | 0.0 |

| 20    | voltage down to AC ground with allowable resulting differential node voltages.                                                                                                                                                                                           | 23  |

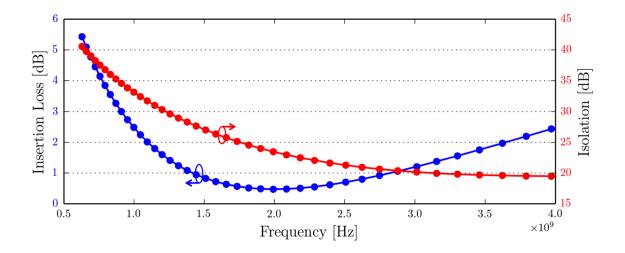

| 3.9   | Loss and isolation of simulated extracted switch using the $S_{21}$ parameter. The simulated loss and isolation of the extracted switch, when placed between two                                                                                                         |     |

|       | ideal 50 $\Omega$ ports is shown. The loss and isolation are comparable to the state of                                                                                                                                                                                  |     |

|       | the art, discussed in Table 3.3.                                                                                                                                                                                                                                         | 24  |

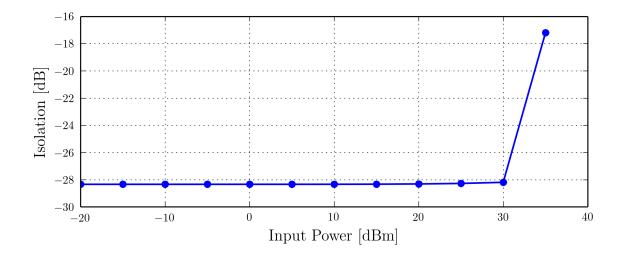

| 3.10  | Power sweep using PSS at 2 GHz in transmit mode. The isolation (measured as voltage gain over switch) does not deviate until greater than 30 dBm of input                                                                                                                |     |

|       | power, showing that the $Tx/Rx$ switch achieves the specified power tolerance.                                                                                                                                                                                           | 25  |

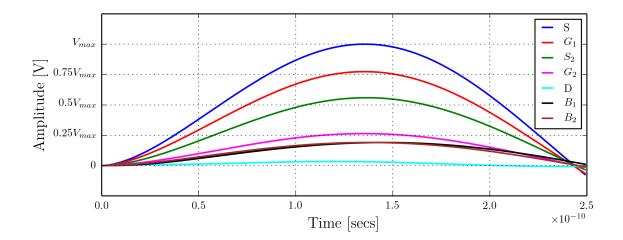

| 3.11  | Extracted AC Node Voltages at 2 GHz, scaled to maximum input voltage and                                                                                                                                                                                                 |     |

|       | plotted with common-mode at 0 V. The voltage division works between nodes,                                                                                                                                                                                               | 20  |

| 9 1 9 | with each node stepping down in voltage by about 25% of the total                                                                                                                                                                                                        | 26  |

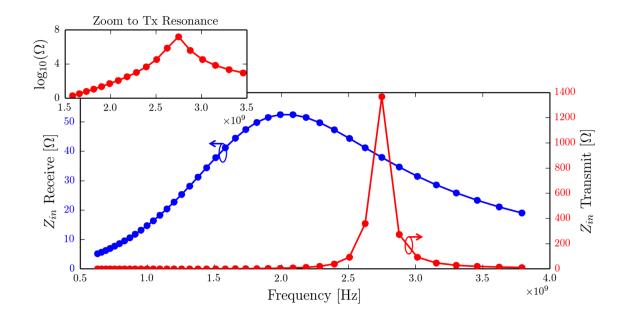

| 3.12  | Input impedance of the Tx/Rx Switch in transmit and receive modes. The input impedance is important for proper power transfer. In transmit mode, the Tx/RX                                                                                                               |     |

|       | switch should have a high input impedance in order to ensure the PA output                                                                                                                                                                                               |     |

|       | power is conveyed to the antenna and not shunted to ground. In receive mode, it                                                                                                                                                                                          |     |

|       | is import to have a input impedance that matches that of the antenna, in order                                                                                                                                                                                           |     |

|       | to ensure that there are not reflections of the signal                                                                                                                                                                                                                   | 27  |

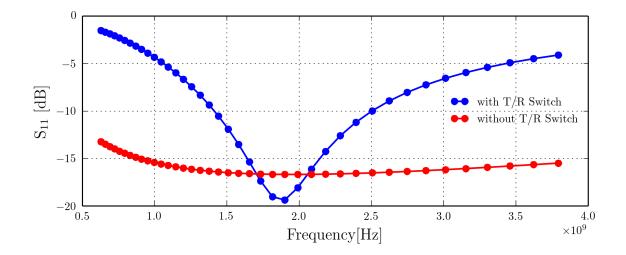

| 3.13  |                                                                                                                                                                                                                                                                          | 00  |

| 211   | edge of the matched band, making the bandwidth 1.4-2.5 GHz                                                                                                                                                                                                               | 28  |

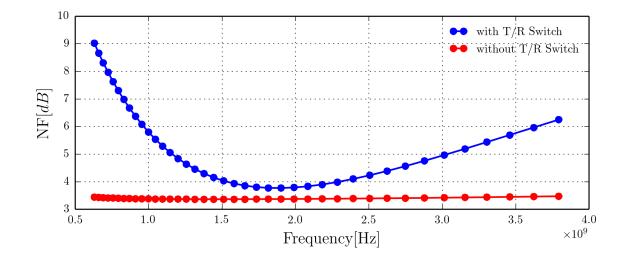

| 3.14  | The noise figure of the schematic LNTA and the LNTA with the extracted switch.                                                                                                                                                                                           | 29  |

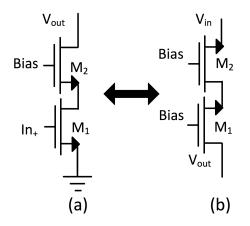

| 4.1   | (A) Leg of class $D^{-1}$ PA (B) Simple common gate amplifier with cascode                                                                                                                                                                                               | 32  |

v

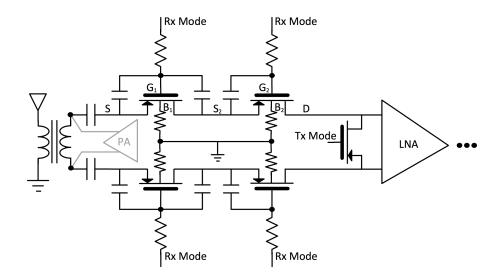

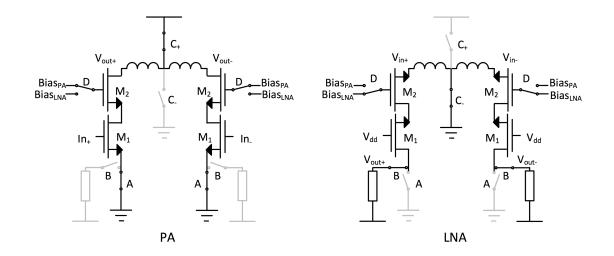

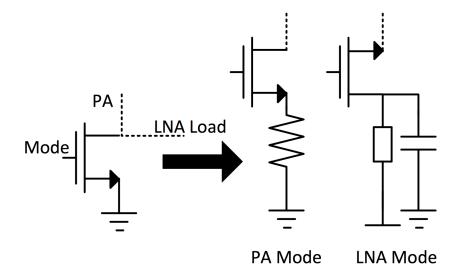

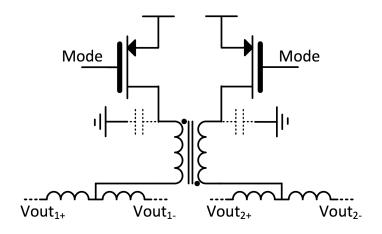

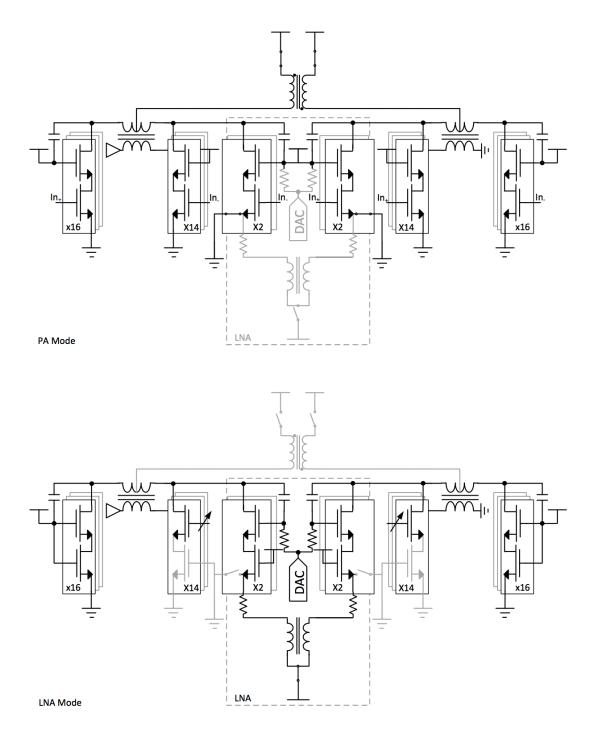

| 4.2 | Device reuse between a class $D^{-1}$ PA and a common-gate LNA. A series of switches, notated A-D, allow the class $D^{-1}$ PA to share the same transistors as a common-gate LNA.                                                                                                                                                                                                                                                                               | 33       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

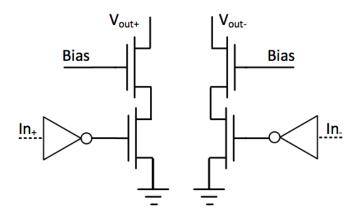

| 5.1 | PA unit cell schematic. A single digital PA unit cell contains only the positive and                                                                                                                                                                                                                                                                                                                                                                             | 95       |

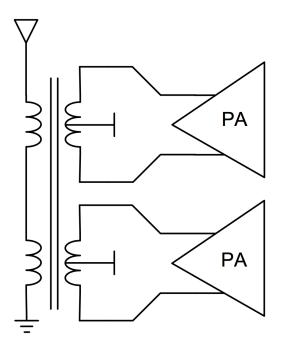

| 5.2 | negative driver devices, their corresponding cascode devices, and driving inverters. Two class $D^{-1}$ PAs on the same power combiner. With a power combiner, the unit cells of each PA may be half the size of a unit cell in a standard digital PA and will see half the output impedance. This topology allows the PA and LNA to have differing input impedances. It also reduces noise in the LNA design, discussed in the following parts of this chapter. | 35<br>36 |

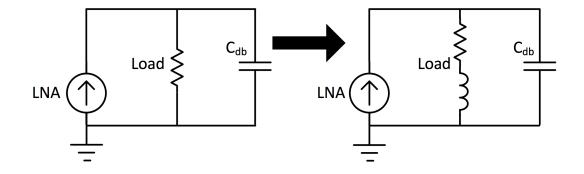

| 5.3 | The current low-pass filter created by the $g_m$ stage of the LNA, the restive load<br>of the LNA, and the parasitics at the output of the LNA. This low-pass filter may<br>be transformed to a band-pass filter through the use of a series load inductance;<br>the resulting topology is called shunt-peaking.                                                                                                                                                 | 37       |

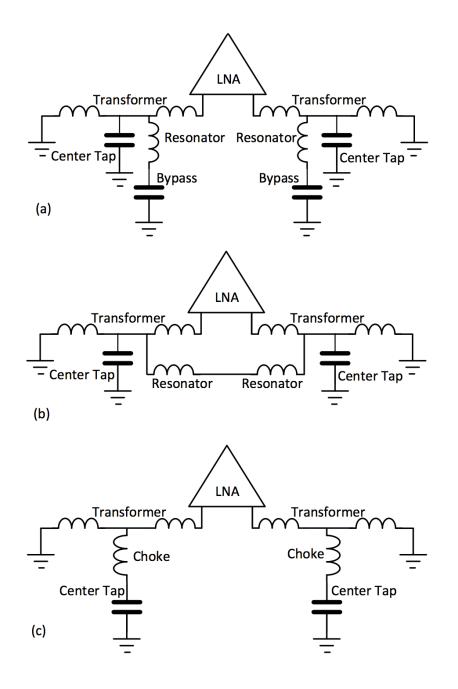

| 5.4 | The PA and LNA center tap locations. By making the center tap locations different depending on mode, the input impedance and parallel inductance can be optimized for each mode.                                                                                                                                                                                                                                                                                 | 39       |

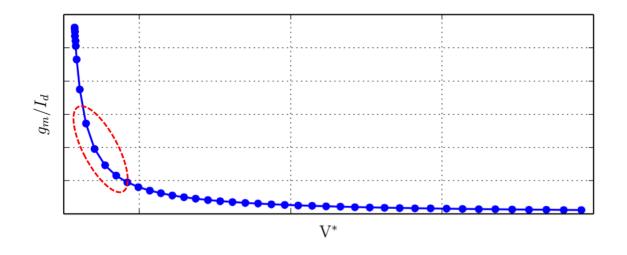

| 5.5 | Unit cell efficiency where $V^* = \frac{2I_d}{q_m}$ , a measure of saturation in short-channel                                                                                                                                                                                                                                                                                                                                                                   |          |

| 5.6 | devices                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40       |

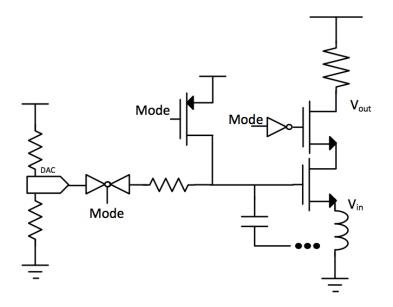

| 5.7 | the LNA bits                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42<br>43 |

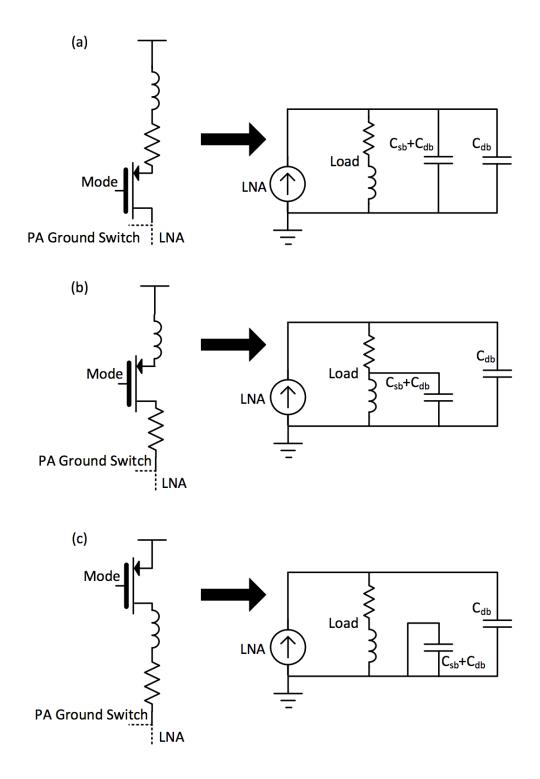

| 5.8 | Different potential placements of the LNA load switch with respect to the load<br>and the resulting effect on the shunt-peaking equivalent circuit. The equivalence<br>assumes that the on-resistance of the load switch is low and that the switch can<br>thus be modeled primarily as capacitance. This is valid as it is less than 5% of                                                                                                                      |          |

| 5.9 | the output load                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45       |

|     | thick-oxide device in order to tolerate the $V_{dd}$ of the LNA                                                                                                                                                                                                                                                                                                                                                                                                  | 46       |

|     | path                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48       |

vi

####

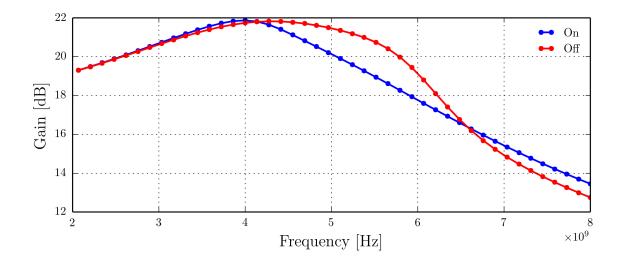

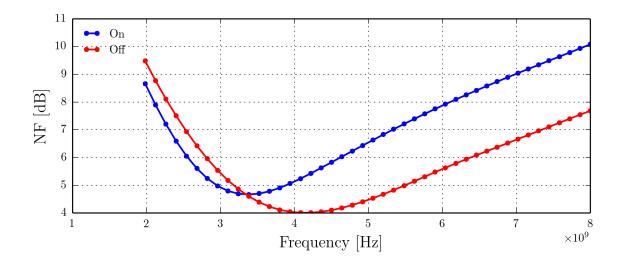

- 5.16  $S_{11}$  of the LNA with and without the additional bit of capacitive tuning. . . . 55 5.17 Gain of the LNA with and without the additional bit of capacitive tuning. . . . 56

- 5.18 Noise Figure of the LNA with and without the additional bit of capacitive tuning. 56

# List of Tables

| 1.1          | Commercially available discrete $Tx/Rx$ switch solutions                                                                                                                                            | 5        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| $3.2 \\ 3.3$ | Differential node requirements                                                                                                                                                                      | 23<br>29 |

| 5.1          | Wide band LNAs in the low GHz found in literature as compared to the LNA herein. The works appearing above the horizontal line are complete transceivers, while works below the line are LNAs only. | 57       |

#### Acknowledgments

I am very grateful to a number of people for their support during my time at UC Berkeley. As is the case with these things, it has taken a village.

First, I would like to acknowledge the three gentlemen on my thesis committee: Professors Borivoje Nikolic, Elad Alon, and Ali Niknejad.

As my research advisor and committee chair, Professor Nikolic has given ongoing support to this work and to my time at Berkeley. From the application process through this final degree requirement, Professor Nikolic has believed in me and helped me to take the opportunities presented to me. Without him, I would not have had the opportunity to complete this work or my degree.

I am also grateful to Professor Alon and Professor Niknejad for their patient advice and expertise both during my coursework at UC Berkeley and during this project. Their willingness to look at design details and answer conceptual questions were integral to the completion of this work.

In the same spirit, this work would not be possible without Xiao (Sharon) Xiao, my co-author and mentor during my time here at UC Berkeley. Her intelligence, attention to detail, patience, and endurance are truly impressive. Working with her has been a pleasure. If anyone reading this is someday in the position to hire her or work for her, you should. She's awesome.

Thank you to DARPA, contract number: HR0011-12-9-001, for financial support of this work. Thank you to the Nokia RF-FPGA project for industrial knowledge and support. And finally thank you to Taiwan Semiconductor Manufacturing Company (TSMC) for the manufacturing of the discussed designs.

I thank several additional people for their technical contributions to this work: Bonjern Yang, for his work with BAG and for providing an initial PA design; Yue Lu, for the use of his DAC in the LNA/PA implementation; Chaoying (Charles) Wu and Nai-chung Kuo, for providing test structures for the Tx/Rx switch, specifically the LNTA and transformer simulation test structures; Sriram Venugopalan, for compiling our two designs onto a single chip for manufacturing and for assistance developing and executing test plans for that chip; James Dunn, for helping to design and source the PCB for testing of the Tx/Rx switch. Thank you also goes to William Biederman, Daniel Yeager, Steven Callender, Lingkai Kong, Jun-Chau Chien, Nathan Narevsky, Greg Lacaille, Luke Calderin, Sameet Ramakrishnan, and Andrew Townley for on-going technical advice and expertise.

Of course, a wonderful work environment goes a long way to making research enjoyable. So, a big thank you also goes to all of COMIC and the Berkeley Wireless Research Center (the BWRC), especially Rachel Hochman, Angie Wang, Jackie Leverett, Milos Jorgovanovic, Katerina Papadopoulou, and Rikky Muller, for their friendship, knowledge, and support during my time here.

Finally, much appreciation needs to be shown for the people outside of the University who have made this work possible. Thank you to my dearest friends Karyn Christianson, Garrett Rodrigues, and Nicolas Le Dortz (and Pepper) who, after many long conversations, were always ready to give a hug, a shoulder, and words of encouragement and to turn the light back on at the end of the tunnel. Thank you also for being equally ready to celebrate even my smallest achievement. You are family by choice.

And keeping the most important for last, I would like to thank my wonderful family for their unwavering support. Mom and Dad, Rich and Whitney, Emily, (and Pumpkin), I love you lots and lots. If I had to chose a family, I might chose to be one of the Gates' children, but you all are a good alternative.

# Chapter 1 Introduction

It is no surprise to note the increased global presence of mobile devices. Since 2000, mobile traffic has risen to a level 18 times the total traffic rate of the internet in 2000 [1]. The economic interest in mobile devices is obvious.

However, with the proliferation of wireless devices, the radio frequency spectrum has become increasingly cluttered. In new standards, such as LTE, related communication bands are disjoint in the frequency domain. In addition, wireless devices must generally support a large number of protocols, such as legacy and country-specific protocols. This has increased the need for more integrated radios in handsets.

The RF-FPGA project will integrate a number of different frequency band transceivers on the same silicon chip in order to support the varied bands and varied protocols required in modern mobile systems. Accordingly, the RF-FPGA project, as designed here at UC Berkeley, will support both frequency-division duplexing (FDD) protocols and time-division duplexing (TDD) protocols. FDD requires a pair of spectrum: one channel to transmit and one channel to receive. TDD does not require paired spectrum, but instead transmits and receives data at alternating time intervals, as shown in Figure 1.1. TDD dominates WiFi, Bluetooth, and government radios.

While LTE-FDD is currently the more common protocol, with a penetration rate 8.3

Figure 1.1: A simplified diagram of the TDD downlink and uplink division in the time domain.

Figure 1.2: A simplified diagram indicating spectrum used for some form of mobile TDD communication. Exact spectrum allocations may be found in [3, 4].

times that of LTE-TDD, TDD is still a major player in both LTE and other mobile solutions [2]. For example, LTE-TDD covered a population 500 million in China alone last year [3].

In addition, LTE-TDD's lack of paired spectrum and ability to change downlink (DL) to uplink (UP) ratios is beneficial as compared to LTE-FDD [3]. The ability to change downlink to uplink ratios will become more important as mobile video traffic, already exceeding 50% of data usage in 2013, increases popularity [1].

Finally TDD solutions are also used in the WiFi and WiMax protocols. With 45% of mobile data being off-loaded to WiFi or femtocells [1], which can use WiMax, TDD represents an important portion of current and future mobile traffic. Finally, TDD is the protocol used in most government transceivers.

Figure 1.2 shows the areas of the frequency spectrum in which a TDD mobile system may operate. The spread of the spectrum in this diagram and the interwoven protocols illustrate the clear need for a wide-band, configurable, TDD transceiver.

In this introduction, we present background information on common TDD architecture topologies and outline the problems of interest in TDD transceivers.

## 1.1 TDD Transciever Architecture Overview

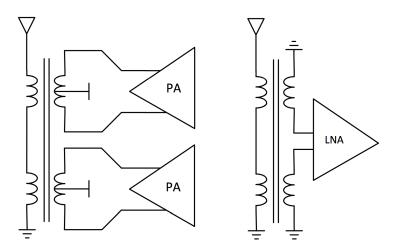

Given that in a TDD system, transmit and receive transmissions happen at the same frequency, the transmitting power amplifier (PA) and the receiving low-noise amplifier or low-noise transimpedance amplifier (LNA/LNTA) are connected, in general, to a single antenna through the same transformer network. A diagram of such a system may be seen in Figure 1.3.

#### **RF-FPGA** Architecture Description

In the final implementation of the RF-FPGA, each band will have a dedicated PA and LNA connected to a transformer. Each transformer will be connected to the single antenna, which will use an interposer to create the appropriate antenna size.

Figure 1.3: A simplified diagram of the PA and LNA receive pair connected at one transformer and antenna.

Additionally, the RF-FPGA will use an inverse class D PA as the front-end of the transmit circuitry. The class  $D^{-1}$  PA is chosen for the transmit architecture as it is efficiently scaled to support different frequency bands, allowing for the reuse of the design in all of the RF-FPGA bands.

Much of the following TDD solutions relies on at least some of the characteristics of an class  $D^{-1}$  PA. Relevant digital class  $D^{-1}$  PA characteristics will be described in Section 2, while other details go beyond the scope of this research and may be found in [5–9].

## **1.2 TDD Design Limitations**

The focus of this work is on a fundamental issue with TDD coexistence. Attaching the transmit and receive circuitry to the same antenna exposures the sensitive receive circuitry to the high output power of the transmitter. Commonly, the power amplifier (PA) outputs a peak power of 30dBm differentially on the antenna when transmitting. Exposing the thin-oxide devices of the LNA input to this type of voltage swing will damage them. However, these cannot be changed to a more power-tolerant device without compromising efficiency of the LNA and reducing the bandwidth due to the addition of parasitic capacitors.

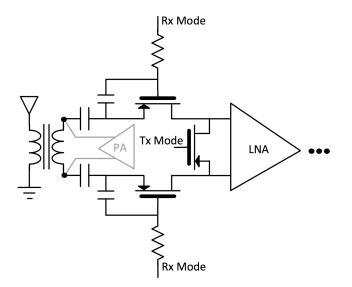

One solution to this 'coexistence' issue is a transmit/receive (Tx/Rx) switch. An conceptual image of the Tx/Rx switch is shown in Figure 1.4.

Tx/Rx switches generally perform the following functions:

- 1. Isolate the LNA from the large PA output power.

- 2. Create a high impedance node at the PA output during receive mode.

Figure 1.4: Location of Tx/Rx switch in simplified transceiver diagram. When 'on,' a switch connects its respective device to the antenna. When 'off,' the switch is open and isolates its respective device from the antenna.

3. Create a high impedance node at the LNA input during transmit mode.

**PA Output Power Isolation** Figure 1.3 shows how the PA output power is incident directly to the LNA. At 30 dBm or 1 Watt of output power, the PA creates a voltage of about 20 V peak-to-peak on the 50  $\Omega$  antenna. The LNA input devices cannot withstand more than a few volts across any of their terminals. In order to isolate the LNA from the PA and prevent damage to the LNA during transmit mode, a Tx/Rx switch is implemented.

**PA Output Impedance** Tx/Rx switches are also used to create a high-impedance node at the PA output during receive mode. For the LNA to absorb maximal receive power, its input impedance should match that of the antenna output impedance. And because the PA output and the LNA input appear in parallel to the antenna, the PA output impedance should be infinite. Thus, an isolation switch is often implemented at the PA output to create a high impedance point in receive mode.

**LNA Input Impedance** A high-impedance node at the LNA input is necessary in transmit mode for the same reasons the PA needs be high impedance during receive mode. However, unlike in receive mode where unretrievable signal is lost, a low impedance node during transmit mode only results in decreased PA efficiency. In addition, a capacitive low impedance node at the LNA during transmit mode may also be able to be tuned out in the matching network. For these reasons, in this discussion, we divorce the LNA input impedance during transmit mode from most of the Tx/Rx Switch design discussion.

|                            | [10]               | [11]                    | [12]          |

|----------------------------|--------------------|-------------------------|---------------|

| Loss (dB) (near 2GHz)      | 0.5                | 0.6 - 0.8               | 0.55          |

| Isolation (dB) (near 2GHz) | -27                | -28                     | -17           |

| Power Tolerance (dBm)      | 34                 | 35                      | 34.5          |

| Bandwidth                  | $0-3 \mathrm{GHz}$ | 2.4-2.5 GHz/4.9-6.0 GHz | 0.1 - 2.5 GHz |

| Technology                 | GaAs MESFET        | GaAs pHEMT              | GaAs pHEMT    |

| Voltage                    | $5\mathrm{V}$      | 3V                      | 3V            |

Table 1.1: Commercially available discrete Tx/Rx switch solutions.

## 1.3 Prior Art

Creating a Tx/Rx switch is a challenging task. These switches impact the performance of the receiver and transceiver and still need to withstand the output power of the PA. The switch design must balance the need to protect itself and the LNA, create the desired impedance nodes, and minimally impact the performance of the overall transceiver. The focus of this work is in improving the performance of CMOS Tx/Rx switches.

Tx/Rx switches can either be outside the transceiver die and package or integrated into the same CMOS as the transceiver. A sampling of the commercially available external Tx/Rxswitches is presented here first for comparison.

#### Discrete Tx/Rx Switches

External Tx/Rx switches can offer somewhat better performance than CMOS Tx/Rx switches and are common commercial solutions for mobile applications. Table 1.1 lists the performance and technology of several of these switches. External Tx/Rx switches generally see better performance than CMOS switches due to their ability to use exotic semiconductor processes for fabrication. For example, an external Tx/Rx switch might use gallium arsenide (GaAs), which is more power tolerant and has better device resistance and isolation properties than bulk CMOS. Unfortunately, this type of technology cannot be integrated into the same die as the CMOS transceiver.

There are additional drawbacks to these switches, including additional die pins, printed circuits board (PCB) area, and component cost. Performance of these switches depreciates from the stated value once integrated due to the loss due to loss in the I/O pads and PCB routing. Thus, it is preferable to find an on-chip solution for Tx/Rx switches.

#### Bulk CMOS Tx/Rx Switches

The traditional CMOS Tx/Rx switch architecture includes a series-shunt transistor arrangement on both the Tx and Rx path. This design creates a high impedance node and isolates the unused element when the opposite element is working [13], [14], [15], [16]. This design suffers from several drawbacks, such as insertion loss and poor power tolerance in

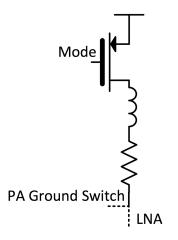

Figure 1.5: Tx/Rx bulk CMOS design strategies. (a) Floating wells allow for increased power tolerance. (b) Stacked transistors in the series leg of a series-shunt switch help to increase power tolerance. (c) Inductors act as frequency-dependent resistors when connected to ground during transmit mode, but are resonated out in receive mode when the capacitor is in use. Additional matching network components not shown.

standard CMOS. Most designs use the series-shunt topology with some application specific modifications, such as the elimination of the shunt transistors [17] to overcome these drawbacks. Switch structures which differ from this topology have been proposed [18]. However, many such designs require appreciable transceiver-level architectural consideration, and their use must be anticipated well before the design of the matching and transformer network.

Most Tx/Rx switch designs, series-shunt and otherwise, achieve the desired isolation, power tolerance, and other design metrics through at least one of three strategies.

- 1. Floating Wells

- 2. Stacked Transistors

- 3. Inductive Tuning

A diagram of each of these strategies may be seen in Figure 1.5. Further innovation of Tx/Rx switch design generally builds off one of these three themes.

**Floating Wells** Floating wells facilitate higher power tolerance. This manifests itself in two ways. First, in the case of a series switch on the transmit side, the switch transistor with a floating well is able to withstand a higher PA output power before forward-biasing source/drain to body diodes than a transistor without floating wells. This is measured as an increase in Tx mode linearity and directly corresponds to power output. [17] and [13] use this methodology. Second, floating wells allow for a the potential to have non-zero body voltages, which increases or to changes the source to body coupling capacitance, as in [14]. The change in capacitance increases isolation and subsequently, power tolerance. Floating wells have the drawback of adding parasitic diodes and capacitances. The parasitic diodes require close attention to ensure that reverse-bias is preserved under worst-case PA output powers. The increased capacitances can impact both isolation and insertion loss, depending on the biasing technique. Thus, it is important to balance the benefits of transmit linearity, LNA isolation, and receive insertion loss.

**Stacked Transistors** Stacked Transistors also allow for an increased power tolerance. Stacked transistors divide the output power across several transistors, reducing the stress on each individual transistor. Effectively, the power tolerance of the switch is the power tolerance of a single transistor multiplied by the number of transistors [13, 16]. The stacked transistor method requires floating gates and source/drain regions, if not floating bodies, to achieve the increased power tolerance.

Feed-forward capacitors can be used to balance the power dissipated across each transistor and subsequently increase power tolerance [13]. This increased performance comes at the cost of die area.

In addition, the stacked methodology also comes at the cost of either increased insertion loss or increased parasitic capacitance. The insertion loss increase is due to the increased series resistance. To mitigate this, larger transistors maybe used, which increases parasitic capacitances.

**Inductive Tuning** Inductive tuning is the most varied methodology of Tx/Rx switch design. It can vary from tuned switches, such as in [19], [15], and [20], to dedicated transformers for the receive mode which may be shorted during transmit mode [18]. Some of these technique may create very low insertion loss and power handling. However, as the tuned switches have a reduced bandwidth, we will not consider this methodology here.

#### Scope of Research

The current bulk CMOS switches are almost uniformly non-ideal solutions for TDD. The series on resistance incurs loss in the receive mode and increase the LNA noise. The additional capacitance of large switch devices can also negatively impact matching in both the transmit and receive modes. An off-chip solution represents a similar amount of performance depreciation as well as other costs associated with pins and PCB area.

In the subsequent chapters, a design methodology for Tx/Rx switches and the resulting performance metrics and tradeoffs will be discussed. The floating well, stacked transistor, and feedforward capacitor techniques are used in the design of this switch, which approaches a more ideal series switch solution for low gigahertz frequencies.

Following the discussion of the Tx/Rx switch, another coexistence solution without a traditional Tx/Rx switch is proposed. Though this work is specific to the TDD solutions for the RF-FPGA project, the design methodology could be used on other PAs with similar topologies.

#### CHAPTER 1. INTRODUCTION

Extracted layout results will be reported for both designs. Comparison to the stateof-the-art in both Tx/Rx switch solutions and other front-end metrics will illuminate the trade-offs within each design methodology and between these two approaches.

# Chapter 2

# General Tx/Rx Definitions

It is important to understand the metrics by which we measure the performance of these coexistence solutions. In this chapter, we discuss the metrics of both receive and transmit mode of the transceiver<sup>1</sup>. After reading this chapter, the reader should be able to easily contextualize the performance of the coexistence design discussed herein.

### 2.1 Tx/Rx Metrics

If the reader is familiar with amplifiers and radio frequency communications, the concepts described below will be a review. If not, this section will serve as a brief introduction to RF metrics and will provide information on the use of these metrics in this application. It is expected that the reader has at least a basic understanding of analog, transistor-level circuit design.

#### Receive

The primary circuit element used in receive mode is the LNA. In order to evaluate the performance of a coexistence solution, we measure the impact of the switch on the LNA metrics: gain, noise figure, linearity, and matching. To the highest degree possible, we want to make the TDD solution 'disappear' in receive mode, allowing the LNA to perform as if isolated from the PA. Here we introduce the metrics of interest in receive mode.

#### Gain and Loss

**Gain** In an LNA, the gain (A) is the amount by which the signal is amplified from input to output. In this case, the gain of amplifiers discussed is always voltage gain  $(A_v)$ .

$$A_v = \frac{V_{out}}{V_{in}} \tag{2.1}$$

<sup>&</sup>lt;sup>1</sup>The theory behind these metrics and other details may be found in more completeness in [21-24].

**Loss** Loss measures the amount of signal removed from the signal path due to a series circuit element. It is measured as the inverse of gain across the element in question. While voltage gain can be used, it does not account for matching in the system. Thus, loss is more commonly reported as the inverse of  $S_{21}$ , or forward voltage gain, of the device under test (DUT) as it accounts for matching, making it congruent with the change in noise figure due to a passive element.

$S_{21}$  parameter is given by the equation

$$S_{21} = \frac{V_2^-}{V_1^+},\tag{2.2}$$

where  $V_1$  is the wave at the input of the circuit element,  $V_2$  is the wave out of the circuit element, and the + and - indicate whether the wave is incident or reflected. In this topology, loss indicates how much of the signal from the antenna reaches the LNA, and one would like loss to be near unity.

Both gain and loss metrics are often represented in their decibel form. The conversion from gain to decibels is

$$A_{dB} = 20log(A_v). \tag{2.3}$$

#### Noise Figure

Noise figure gives an indication of the amount of noise a circuit element injects into the signal path. The amount of noise present at any point in a circuit may be represented by the signal-to-noise-ratio (SNR) equal to  $\frac{P_{Signal}}{P_{Noise}}$ , where  $P \propto V^2$ , P is power, and V is voltage. A representation of the amount of noise injected by a circuit element along the signal path looks at the SNR between two points: the input and output of the circuit. The equation for noise factor is

$$NF = \frac{SNR_{in}}{SNR_{out}}.$$

(2.4)

Noise figure, which is used in this paper, is the decibel representation of NF:

$$NF_{dB} = 10\log(NF). \tag{2.5}$$

The noise figure of a circuit can be found analytically; some examples will be seen in later chapters. However, the noise factor of a completely passive element is directly related to the behavior of the passive element, such that its noise factor is equal to the power loss.

The noise factors of cascaded elements interact. The Friis Equation provides the relationship for this interaction:

$$NF_{eff} = NF_1 + \frac{NF_2 - 1}{A_{P1}} + \frac{NF_3 - 1}{A_{P1} \times A_{P2}} + \dots + \frac{NF_i - 1}{A_{Pi-1} \times \dots \times A_{P1}},$$

(2.6)

where  $A_p$  is the power gain of a stage. Thus, one can see that it is important to keep the loss of the switch low to keep its noise figure and impact on the overall system noise figure low. Increased noise figure reduces the sensitivity of the overall system and negatively affects receiver performance.

#### Linearity

An ideal linear circuit element has the same linear transfer function for any input power. In other words, the linear equation which maps the input to the output should be the same regardless of the input value. In CMOS circuits, there are no perfectly linear circuit elements. Physical systems exhibit different behaviors at different power levels. Most nonlinear functions, however, can be approximated using a Taylor series polynomial expansion.

Two metrics are then used for linearity in this work. The first is the 1dB compression point and the second is the 3rd Intercept Point.

1dB Compression Point The 1dB compression point (P1dB) is the input value at which the transfer function differs from an extrapolated linear function by 1dB.

**3rd Order Intermodulation Intercept Point** The 3rd order intermodulation intercept point (IIP3) is the input value where the extrapolated 3rd order term in the Taylor series polynomial expansion overtakes the 1st order term.

The higher each of these metrics, the less of an impact the non-linearity of the circuit has on the signals of interest. If the solution is a series switch, for example, the switch should have a linearity markedly higher, no less than double, the succeeding LNA, in order to preserve the LNA's linearity.

#### Matching

The input impedance of a circuit element determines how much signal is absorbed and how much signal is 'reflected' off of that element  $^2$ . To maximize the transmitted power and

<sup>&</sup>lt;sup>2</sup>This idea of reflection is often explained through transmission line theory. Dissimilar impedances in series will result in some loss of signal, due to the wave-like properties of voltage and current. To elaborate, the solution to the differential equation describing transmittance of electromagnetic waves allows for both a forward and a reverse component of voltage and current. In system with a open-circuit boundary condition, the reflected wave is positive and equals the forward wave, resulting in a voltage level of a constant positive value. In an short-circuit condition, the reflected wave is negative and equals the forward wave, resulting in a voltage level of 0V. When the termination is some other impedance value, the value of the reflected wave is between the negative and positive of the incident wave value. In a condition of matched impedance, no reflection occurs.

minimize the reflected power, all input impedances in the circuit should match the output resistance of the previous series circuit element.

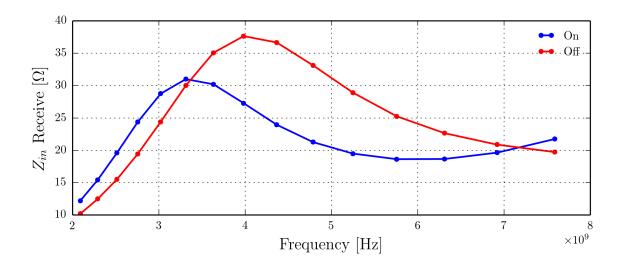

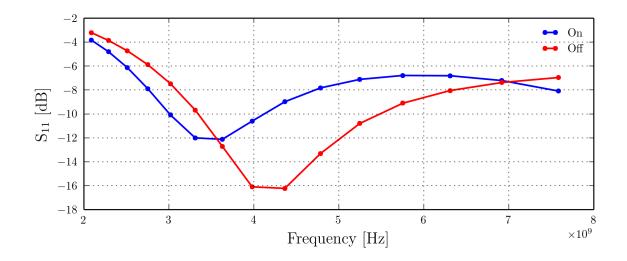

The two measures of matching used in this work are  $S_{11}$  and  $Z_{in}$ .

$S_{11}$  - Input Voltage Reflection Coefficient The equation for  $S_{11}$  is

$$S_{11} = \frac{V_1^-}{V_1^+},\tag{2.7}$$

where  $V_1$  is the wave at the input of the circuit element and the + and - indicate whether the wave is incident or reflected. Thus,  $S_{11}$  is a measure of the input matching accuracy. This value should be as close to zero (or negative infinity in decibels) as possible. Because these parameters are ratios, they are inherently unit-less.

**Z-Parameters** Z-Parameters are a measure of the frequency dependent impedance of the circuit element in relation to the source impedance.

$Z_{11}$  parameters are given by the equation

$$Z_{11} = Z_0 \frac{1 + S_{11}}{1 - S_{11}},\tag{2.8}$$

where  $Z_0$  is the frequency dependent source impedance. If  $S_{11}$  is small, this value should be nearly the value of the source impedance. Similar equations exist for relating any  $S_{xy}$ and  $Z_{xy}$ .

The Z-parameters are also used to find  $Z_{in}$ , which is similar, but not equivalent to  $Z_{11}$ , as it depends on the load. This value, instead of  $Z_{11}$ , is used to find the input impedance in a passive device.

$$Z_{in} = Z_{11} - \frac{Z_{12}Z_{21}}{Z_{22} + Z_L} \tag{2.9}$$

$Z_{in}$  is used in this work.

#### Transmit

The primary circuit element used in transmit mode is the PA. Similarly to the LNA, the PA should function as ideally as possible, as if no coexistence solution were used. However, in transmit mode, unlike receive mode, the effects of the coexistence solution on PA performance are somewhat secondary to the protection the switch provides the LNA in transmit mode. The assumption is that it is more important to ensure the LNA survives the transmit mode than to ensure the transmit mode is optimized.

Thus, in this section, we present basic measures of PA performance and introduce the metrics that measure how well the switch isolates the LNA from the PA signal.

#### **Output Power**

Output power is the total power supplied by an amplifier. In general, the output power is calculated by

$$P_{out} = \frac{V_{rms}^2}{R_{load}},\tag{2.10}$$

where  $V_{rms}$  is the root-mean-square of the voltage at a given node and  $R_{load}$  is the load resistance.

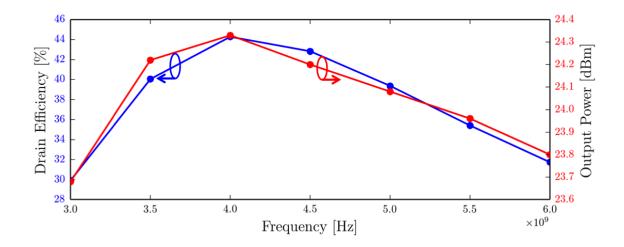

#### **Drain Efficiency**

Drain efficiency is a measure of how well the DC power it converted to AC power at the output of an amplifier. In general, the metric is simply

$$\eta_D = \frac{P_{out}}{P_{total_{DC}}},\tag{2.11}$$

where DC power is the average power which flows out of the DC supply.

#### **Power Tolerance**

Power tolerance is the power level which the switch can withstand before damaging the switch transistor devices. This parameter is determined by architecture, topology, and CMOS technology. The PA output power is measured in decibel-milliwatts (dBm). In the RF-FPGA design, the PA output power seen at the LNA must be at least 12dBm singleended before the maximum allowed voltages are seen at the transistors.

#### Isolation

Isolation indicates the degree to which a signal is blocked by a circuit element. The amount of signal which passes through a series circuit element is measured as the inverse of  $S_{21}$  or voltage gain across the circuit element (See  $A_v$  in 2.1). In a Tx/Rx switch, this measures the amount of the PA signal which reaches the input of the LNA. One would like isolation to be near zero, indicating that the signal is completely blocked; no signal passes through. In this case, isolation should be less than -20dB, as is standard in literature.

#### PA Output Waveform

It is important to note that power level and differential voltage levels across the switch depend upon the waveform incident at the switch. A common assumption for RF signals is that the signal is perfectly sinusoidal and that the initial conditions are the common mode. This, however, may not be the case. A sinusoid and the true PA output with similar common mode and power levels may be seen in Figure 2.1. As one can see, the voltage difference from common mode is greater in the true PA output than in the sinusoidal output.

Figure 2.1: PA output and sinusoid of equal power and common-mode voltages with commonmode voltage labeled. The known inverse class D PA output and a sinusoid with similar power and common-mode levels are shown in order to illustrate the difference between the two signal shapes and their resulting voltage levels. Switch design should accommodate the worst-case PA output scenario.

In the case of an incident sinusoid, the common mode voltage is the arithmetic mean of the maximum and minimum voltage levels. For increasing power levels, the voltage levels increase identically above the common mode. If the waveform is not a sinusoid, this may not be true. In fact, as the waveform approaches a series of impulses, the common mode drops, but the voltage difference from common mode for a given power output increases. Thus, it is important to understand both the output power and signal waveform of the PA to ensure tolerable voltage levels are not violated.

# Chapter 3

# **RF-FPGA** Series Tx/Rx Switch Design and Results

The last chapters discussed both the metrics by which our switch design is measured and prior switch designs. With this context, we present the design of the RF-FPGA Tx/Rx Switch.

## 3.1 Tx/Rx Switch Design

#### Architecture Selection

The first step in designing the Tx/Rx switch is to choose an overall architecture for the switch. The architecture should specify how the switch is situated relative to the PA and LNA, how the switch creates an AC ground at the LNA input, and how the PA affects the input signal during receive mode.

A simple image of the chosen architecture may be seen in Figure 3.1. The selected architecture has only a shunt switch at the input to the LNA and series transistors to separate the PA signal from the input of the LNA.

We situate the switch between the antenna AC coupling capacitance and the LNA for isolation and biasing. The AC coupling capacitance separates the voltages of the switch drain and source regions from the PA DC voltage and allows these regions to be biased separately from the PA. In the transmit mode, the antenna side of the switch sees the AC voltage of the PA output, and the switch isolates the receiver from the transmitter output signal.

The AC ground at the LNA input is created by exploiting the differential input of the RF-FGPA LNTA. Putting a standard shunt transistor between the two differential lines shorts the input nodes of the LNA, creating a DC voltage equal to the average voltage of the two differential lines at the input to the LNA.

Figure 3.1: A simple differential series switch with shunt transistor. One method for creating an AC ground at the input to the LNTA is to connect the two differential inputs of the LNA with a shunt transistor. Series transistors are used to isolate the AC ground from the PA signal at the antenna.

In the RF-FPGA architecture, any single PA is in a high impedance state when not in use. This keeps the receive signal from leaking away through the PA. Thus in this design, the Tx/Rx switch is only required on the receiver side for isolation. In standard designs, the switch often is needed both on the PA and LNA side for high impedance creation and isolation respectively.

#### Technology Voltage Requirements and Bias Voltage Selection

Given the selected topology, the next step is to determine the bias voltages and swing limits needed to ensure that the switch survives the PA output power and operates in receive mode.

#### Transmit Mode

The same thick-oxide devices as the RF-FPGA PA were used in the Tx/Rx switch design to ensure compatibility with the transceiver during integration. A cross-section of a deep-Nwell device is shown in Figure 3.2. Deep-Nwell devices are used to float the device body and increase power tolerance. The acceptable DC and an AC voltage levels between each node of the device must be considered in order to ensure that the device is not damaged during 'worst-case' usage.

Figure 3.2: Cross-section of the deep-Nwell Devices. Thick-oxide deep-Nwell devices are used for the switch's series transistors. The deep-Nwell is set to a fixed voltage while the Pwell, gate, and source/drain nodes are free to oscillate with the incoming signal, preventing the differential voltages from exceeding the requirements of the silicon technology.

| Tx                                       |                                     |  |

|------------------------------------------|-------------------------------------|--|

| S, D > B                                 | To ensure reverse bias diodes       |  |

| $B < N_{well}$                           | To ensure reverse bias diodes       |  |

| G < S, D                                 | To ensure device is off             |  |

| $S_{dc} = D_{dc}$                        | To ensure $V_{sd-max}$ is minimized |  |

| $V_{sd-max} < V_{ac-max}$                | As per DRM                          |  |

| $V_{sb-max} < V_{ac-max}$                | As per DRM                          |  |

| $V_{s-swing} - V_{d-swing} < V_{ac-max}$ |                                     |  |

| Rx                                       |                                     |  |

| $G > S, D + V_t$ To ensure device is on  |                                     |  |

| S, D > B                                 | To ensure reverse bias diodes       |  |

Table 3.1: Differential node requirements

The voltages required for this device are listed in Table 3.1.

Given the waveform of the PA output, discussed in 2.1,  $V_{s-swing} - V_{d-swing} < V_{ac-max}$  is not achieved with a single transistor.

Thus, two switches must be used in series to withstand the output power of the PA, while allowing for the creation of an AC ground at the input to the LNA. Again, the bodies of these switches must be allowed to swing to achieve this increased power tolerance. The resulting topology is shown in Figure 3.3.

The bias voltages of the source and drain regions of all the devices are set by the input bias voltage of the LNA. In order for the source/drain to body diodes to remain reversebiased and minimize the difference between the source and body voltages, the body bias conditions are set such that  $B_{dc} - V_{B-swing} = S_{dc} - V_{s-swing}$ , where  $B_{dc}$  is DC body voltage

Figure 3.3: Complete switch topology. The switch uses two series transistors with floating Pwells to ensure that the differential node voltage limits are satisfied under worst-case PA output powers and waveforms.

and  $V_{B-swing}$  is the amount the body voltage swings.

Now, because the body voltage is ensured to be less than both the source and drain voltages, the gate voltage is set to the body voltage as well. This keeps the device 'off' in transmit mode.

Given that all of the DC voltages are now set, one needs to set only the swing at each node. There are three nodes between the input node and the LNA input, for a total of five nodes. The easiest way to divide the voltage drop is by a quarter of the input voltage between each node. Figure 3.4 shows how the difference in node voltage amplitude is 25% of the input voltage.

#### **Receive Mode**

In receive mode, the conditions for functionality are more easily maintained. The devices simply need to remain completely 'on.' The input voltage is not expected to exceed 2V. Thus,  $G_{dc} > S_{dc} + \frac{1}{2}V_{s-swing} + V_t$  and  $B_{dc} = 0V$  is all that is required.

#### **Receive Mode Noise Figure Requirements and Transistor Sizing**

Once the architecture and topology is selected, one must size the transistors appropriately. The first step to determine the size of the series transistors is to analyze the impact these

Figure 3.4: Desired node voltages at each gate, source, and drain in one series leg of the Tx/Rx Switch. The amplitude of the voltage at each node during transmit mode is represented in red. The difference in amplitude between each node is represented in blue.

Figure 3.5: Noise figure in relation to series resistance at 2 GHz. The noise figure is sensitive to the series resistance at the input of the LNTA. A parametric sweep reveals the relation between resistance and noise figure.

transistors have on the noise figure of a potential receive system<sup>1</sup>.

We start with noise figure, as opposed to insertion loss, because, the effects of insertion loss manifest themselves as an increase in noise figure, see Equation 2.6, and those effects help to determine the insertion loss requirement. Assuming the switch attenuation, or  $\frac{1}{A_1}$ , is approximately equal to its noise figure, an approximation that takes the liberty of assuming the switch is a passive device, one can see how the insertion loss both adds directly to the overall noise figure and causes an increase in the noise contribution of all further elements in the receive chain.

Thus, we characterize the impact of a resistance in series, between the transformer and LNTA, on the noise figure to determine the maximum series resistance that would deliver the desired noise figure performance. Specifications of the RF-FPGA stipulate that the simulated schematic noise figure should only be 0.2 dB greater than the NF of the LNTA without any series resistance. This is believed to give margin for an increase in noise figure due to layout.

Figure 3.5 shows noise figure in relation to various on-resistances at the input of the LNTA over a range of input frequencies. Given the NF requirement, the input resistance was capped at  $1.25 \Omega$ .

After determining the maximum series resistance, we determined the transistor size that yields no more than than the maximum series resistance. Figure 3.6 shows the generalized parametric analysis performed to compare the size of the thick-oxide deep N-well device to its on-resistance. Note that because two series devices are used, the on-resistance of a single device must be half the resistance limit of  $1.25 \Omega$ .

<sup>&</sup>lt;sup>1</sup>The receive test structure is a version of the LNTA used on the RF-FPGA chip, designed by Charles Wu. This structure is also used in Section 3.2.

Figure 3.6: Generalized device on-resistance in relation to width. Device on-resistance is directly related to insertion loss and thus drives the selection of device width.

## **Isolation Requirements and Passive Selection**

Given an architecture and the size of the transistors in the architecture, we select passive components to help satisfy the isolation requirements and ensure the technology requirements, discussed in 3.1.

In this architecture, the parasitic capacitances associated with the transistors form a capacitive network, shown in Figure 3.7. From 3.1, we know the node voltages should be reduced by 25% between each node. In order to ensure these voltage requirements are met, the capacitance values must form a voltage divider accordingly.

One can determine the necessary capacitance values between each node by first determining the value of the impedance between the node closest to AC ground,  $G_2$  and ground bottom node.

The impedance from  $G_2$  to AC ground is

$$Z_{gg_2} = \frac{1}{C_{gd_2}s} || (\frac{1}{C_{gb_2}s} + \frac{1}{C_{bg_2}s} || R_{B_2})$$

(3.1)

$$= \frac{sR_{B_2}(C_{gb_2} + C_{bg_2}) + 1}{C_{gd_2}s(R_{B_2}C_{gb_2}C_{bg_2}s + R_{B_2}C_{gb_2}s + R_{B_2}C_{bg_2}s + 1)},$$

(3.2)

where  $R_{B_2}$  is the resistor used to bias the body voltage.

One can then determine the necessary impedance value between  $S_2$  and  $G_2$ . The voltage ratio between  $G_2$  and  $S_2$  should be one half and is given by the equation

$$G_2 = \frac{Z_{gg_2}}{Z_{gg_2} + Z_{sg_2}} \times S_2. \tag{3.3}$$

Thus, the impedance between  $S_2$  and  $G_2$ , called  $Z_{sg_2}$ , should equal  $Z_{gg_2}$  to create the voltage division equation.

Figure 3.7: (a) Transistor parasitic capacitors. The parasitic capacitances between each node of a transistor form a capacitive network, coupling signal between each node. (b) Full parasitic capacitance network for switch topology. The signal coupled between each node is exploited to ensure the differential node voltage limits are met, as per the technology requirements. Capacitors in grey are small enough that they do not impact the coupling between nodes.

The necessary impedance value between  $G_1$  and  $S_2$  can be found in a similar manner. The voltage ratio between  $S_1$  and  $G_2$  must be two-thirds and is given by the equation

$$S_2 = \frac{Z_{gg_2} + Z_{sg_2}}{Z_{gg_2} + Z_{sg_2} + Z_{gs_1}} \times G_1.$$

(3.4)

Thus,  $Z_{gs_1}$  should equal  $Z_{gg_2}$  as well.

The final impedance is more complicated. The voltage ratio between  $G_1$  and  $S_1$  should be three-fourths. However, the voltage division equation is given by

$$G_{1} = \frac{(Z_{gg_{2}} + Z_{sg_{2}} + Z_{gs_{1}}) || (\frac{1}{C_{gb_{1}s}} + \frac{1}{C_{bg_{1}s}} || R_{B_{1}}))}{(Z_{gg_{2}} + Z_{sg_{2}} + Z_{gs_{1}}) || (\frac{1}{C_{gb_{1}s}} + \frac{1}{C_{bg_{1}s}} || R_{B_{1}}) + Z_{sg_{1}}} \times S_{1}$$

(3.5)

equation,  $Z_{sg_{1}} = \frac{(Z_{gg_{2}} + Z_{sg_{2}} + Z_{gs_{1}}) || (\frac{1}{C_{gb_{1}s}} + \frac{1}{C_{bg_{1}s}} || R_{B_{1}}))}{3}.$

From this equation,  $Z_{sg_1} =$

The capacitances needed to create the voltage divider should have the impedances found in Table 3.2. The capacitance values that create the necessary impedances are likely not the same as the parasitic capacitance values. Figure 3.8 shows how the existing capacitance values may be modified by adding additional capacitors in parallel with the parasitic ones to meet the impedance requirements.

With the choice of capacitance values, the switch design is complete.

| External Cap | Impedance Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $C_{qsex_1}$ | $\frac{(Z_{gg_2} + Z_{sg_2} + Z_{gs_1})  (\frac{1}{C_{gb_1s}} + \frac{1}{C_{bg_1s}}  R_{B_1}))}{3} - \frac{1}{C_{cs_1s}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $C_{gdex_1}$ | $\frac{1}{C_{gd_2s}}   (\frac{1}{C_{gb_2s}} + \frac{1}{C_{bg_2s}}  R_{B_2}) - \frac{1}{C_{gd_1}}  R_{B_2}  R$     |