# Resilient Design Techniques for Improving Cache Energy Efficiency

Brian Zimmer

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2016-182 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-182.html

December 1, 2016

# Copyright © 2016, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Acknowledgement

This work was funded by ST Microelectronics, TSMC, DARPA PERFECT Award Number HR0011-12-2-0016, Berkeley Wireless Research Center sponsors, ASPIRE sponsors, Intel ARO, AMD, and the NVIDIA fellowship.

#### Resilient Design Techniques for Improving Cache Energy Efficiency

by

Brian Matthew Zimmer

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Co-chair Professor Krste Asanović, Co-chair Professor Daniel Tataru

Summer 2015

# Resilient Design Techniques for Improving Cache Energy Efficiency

$\begin{array}{c} \text{Copyright 2015} \\ \text{by} \\ \text{Brian Matthew Zimmer} \end{array}$

#### Abstract

Resilient Design Techniques for Improving Cache Energy Efficiency

by

Brian Matthew Zimmer

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Co-chair

Professor Krste Asanović, Co-chair

Improving energy efficiency is critical to increasing computing capability, from mobile devices operating with limited battery capacity to servers operating under thermal constraints. The widely accepted solution to improving energy efficiency is dynamic voltage and frequency scaling (DVFS), where each block in a design operates at the minimum voltage required to meet performance constraints at a given time. However, variation-induced SRAM bitcell failures in caches at low voltage limit voltage scaling—and therefore energy-efficiency improvements—in advanced process nodes. Analyzing and modeling bitcell failures is necessary to develop resiliency techniques that prevent or tolerate SRAM failure to improve the minimum operating voltage of caches.

This work demonstrates a holistic approach that uses both circuit-level and architecture-level design techniques to improve low-voltage operation of SRAM. A simulation framework and experimental measurements from a 28nm testchip explore failure mechanisms of SRAM bitcells. The simulation framework is further utilized to evaluate the effectiveness of circuit-level SRAM assist techniques using dynamic failure metrics. New circuit-level techniques that use replica timing are developed to make SRAM macros more resilient to process variation. An architecture-level error model is developed to translate bitcell failure probability to yield, and to evaluate a variety of error-correcting code (ECC) and redundancy-based resiliency techniques. New resiliency schemes, named dynamic column redundancy (DCR) and bit bypass (BB), are proposed to tolerate a high bitcell failure rate with low overhead.

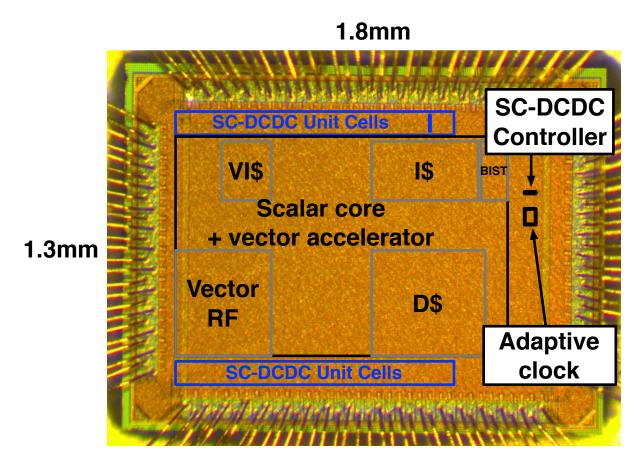

The methodology and proposed schemes were validated with five different 28nm chips. The RAVEN1 testchip measured in-situ threshold voltage variation of 30,000 bitcells and was used to analyze the effect of random telegraph noise on failures. The RAVEN2 testchip explored a single-p-well bitcell design that can compensate for global process variation. The RAVEN3 and RAVEN3.5 chips included processors with on-chip switched-capacitor voltage conversion, and resilient SRAM macros with circuit-level techniques that enable operation down to 0.45V. The SWERVE processor included architecture-level techniques to avoid failing cells, and decreases energy by over 30% with only 2% area overhead, and includes in-situ

pipelined ECC to measure the contribution of intermittent SRAM error sources such as random telegraph noise and aging.

Overall, this dissertation describes a general methodology that is used to evaluate resilient design technique effectiveness for different process and architecture assumptions, and proposes a new set of resilient design techniques that lower the minimum operating voltage of caches with low overhead.

To my wife, Anjali.

# Contents

| C  | Contents         |                                                      |              |  |  |  |  |  |  |

|----|------------------|------------------------------------------------------|--------------|--|--|--|--|--|--|

| Li | st of            | Figures                                              | $\mathbf{v}$ |  |  |  |  |  |  |

| Li | $\mathbf{st}$ of | Tables                                               | ix           |  |  |  |  |  |  |

| 1  | Intr             | roduction                                            | 1            |  |  |  |  |  |  |

|    | 1.1              | Motivation                                           | 1            |  |  |  |  |  |  |

|    | 1.2              | Background                                           | 5            |  |  |  |  |  |  |

|    |                  | 1.2.1 Circuit-level Topics                           | 5            |  |  |  |  |  |  |

|    |                  | 1.2.2 Architecture-level Topics                      | 9            |  |  |  |  |  |  |

|    |                  | 1.2.3 Relationship between Voltage, Energy and Delay | 10           |  |  |  |  |  |  |

|    | 1.3              | Related Work                                         | 11           |  |  |  |  |  |  |

|    | 1.4              | Thesis Outline                                       | 13           |  |  |  |  |  |  |

| 2  | Error Models     |                                                      |              |  |  |  |  |  |  |

|    | 2.1              | Modeling Sources of Error                            | 15           |  |  |  |  |  |  |

|    |                  | 2.1.1 Hard Faults                                    | 15           |  |  |  |  |  |  |

|    |                  | 2.1.2 Soft Errors                                    | 16           |  |  |  |  |  |  |

|    |                  | 2.1.3 Intermittent Errors                            | 16           |  |  |  |  |  |  |

|    | 2.2              | Circuit-level Hard-fault Model                       | 16           |  |  |  |  |  |  |

|    | 2.3              | Microarchitecture-level Hard-fault Model             | 19           |  |  |  |  |  |  |

|    | 2.4              | Circuit-level Soft-fault Model                       | 22           |  |  |  |  |  |  |

|    | 2.5              | Microarchitecture-level Soft-fault Model             | 25           |  |  |  |  |  |  |

|    | 2.6              | Modeling Energy, Area, Delay, and CPI                | 29           |  |  |  |  |  |  |

| 3  | $\mathbf{SR}$    | AM Failure Mechanisms                                | 33           |  |  |  |  |  |  |

|    | 3.1              | Simulating Failure Mechanisms                        | 33           |  |  |  |  |  |  |

|    |                  | 3.1.1 Failure Metrics                                | 34           |  |  |  |  |  |  |

|    |                  | 3.1.2 Failure Analysis                               | 34           |  |  |  |  |  |  |

|    |                  | 3.1.3 Summary                                        | 42           |  |  |  |  |  |  |

|    | 3.2              | Measuring Failure Mechanisms                         | 42           |  |  |  |  |  |  |

|   |      | 3.2.1 Introduction                                      |

|---|------|---------------------------------------------------------|

|   |      | 3.2.2 Characterization Architecture                     |

|   |      | 3.2.3 Random Variation Measurement                      |

|   |      | 3.2.4 Random Telegraph Noise Measurement                |

|   |      | 3.2.5 Joint Effect of RTN and Variation on Writeability |

|   |      | 3.2.6 Summary                                           |

| 4 | Circ | cuit-level Resiliency Techniques 5                      |

|   | 4.1  | Introduction                                            |

|   | 4.2  | Single-p-well Bitcell                                   |

|   | 4.3  | Wide-voltage-range 8T macro                             |

|   |      | 4.3.1 Design Overview                                   |

|   |      | 4.3.2 Writeability Assist                               |

|   |      | 4.3.3 Readability Assist                                |

|   |      | 4.3.4 Energy and Delay Simulation Results 6             |

|   | 4.4  | Summary                                                 |

| 5 | Arc  | hitecture-level Resiliency Techniques 7                 |

|   | 5.1  | Introduction                                            |

|   | 5.2  | Protecting Data Arrays with DCR+LD                      |

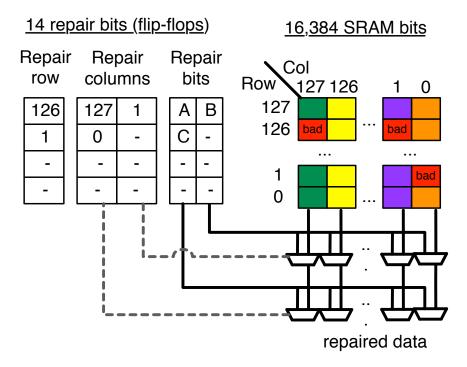

|   |      | 5.2.1 DCR+LD Microarchitecture                          |

|   |      | 5.2.2 Evaluation                                        |

|   |      | 5.2.3 Results                                           |

|   |      | 5.2.4 Discussion                                        |

|   | 5.3  | Protecting Tag Arrays                                   |

|   |      | 5.3.1 Bit Bypass (BB)                                   |

|   | 5.4  | Protecting Against Intermittent Errors                  |

|   |      | 5.4.1 Using ECC for Hard Faults                         |

|   | 5.5  | Summary                                                 |

| 6 | Res  | ilient Processor Design 8                               |

| • |      | Introduction                                            |

|   | 6.2  | System Architecture                                     |

|   | 6.3  | Programmable Built-In-Self-Test (BIST)                  |

|   | 0.0  | 6.3.1 BIST Architecture Overview                        |

|   |      | 6.3.2 BIST Control                                      |

|   |      | 6.3.3 BIST Datapath                                     |

|   |      | 6.3.4 BIST Interface                                    |

|   | 6.4  | Architecture-level Resiliency                           |

|   | 0.4  | 6.4.1 BB Implementation                                 |

|   |      | 6.4.2 DCR Implementation                                |

|   |      | 6.4.3 Line Disable Implementation                       |

|   |      | O.z.o dino dibanie impiememanom                         |

| Bi | bliog | raphy      |                   |           |       |      |      |      |      |      |   | 120 |

|----|-------|------------|-------------------|-----------|-------|------|------|------|------|------|---|-----|

|    | 7.2   | Future V   | Vork              |           |       |      | <br> | <br> | <br> | <br> | • | 118 |

|    |       |            | y of Contribution |           |       |      |      |      |      |      |   |     |

| 7  |       | clusion    |                   |           |       |      |      |      |      |      |   | 117 |

|    | 6.7   | Summar     | у                 |           |       |      | <br> | <br> | <br> | <br> | • | 116 |

|    | 6.6   | Simulation | on Results        |           |       |      | <br> | <br> | <br> | <br> |   | 114 |

|    |       | 6.5.4 E    | rror Logging .    |           |       |      | <br> | <br> | <br> | <br> |   | 111 |

|    |       | 6.5.3 L    | 2 Cache ECC       |           |       |      | <br> | <br> | <br> | <br> |   | 111 |

|    |       | 6.5.2 L    | 1 Data Cache E    | CC        |       |      | <br> | <br> | <br> | <br> |   | 110 |

|    |       | 6.5.1 L    | 1 Instruction Ca  | ache ECC  |       |      | <br> | <br> | <br> | <br> |   | 109 |

|    | 6.5   | In-situ E  | rror Correction   | and Detec | ction |      | <br> | <br> | <br> | <br> |   | 109 |

|    |       | 6.4.5 S    | toring Redunda    | ncy State |       |      | <br> | <br> | <br> | <br> |   | 109 |

|    |       | 6.4.4 R    | tedundancy Prog   | gramming  | Algor | ithm | <br> | <br> | <br> | <br> |   | 107 |

|    |       |            |                   |           |       |      |      |      |      |      |   |     |

# List of Figures

| 1.1        | Measured bitcell area scaling (for individual pre-production cells, cells within arrays, and the effective cell sizes including overhead of peripheral circuitry) versus |            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | ITRS scaling predictions for decreasing technology nodes                                                                                                                 | 6          |

| 1.2        | Variation only has a major effect on the strength ratio between devices at lower                                                                                         |            |

| 1.0        | voltages                                                                                                                                                                 | ٠          |

| 1.3        | Resilient techniques decrease $V_{min}$ by either reducing the bitcell error rate or tolerating failures to increase the acceptable failure rate                         | 4          |

| 1.4        | 6T and 8T SRAM bitcell schematics and naming convention                                                                                                                  | 6          |

| 1.5        | SRAM operation waveforms                                                                                                                                                 | 7          |

| 1.6        | Organization of SRAM bitcells into an array                                                                                                                              | Ö          |

| 1.7        | Generic error-correcting codes (ECC) stores extra bits to repair faults during                                                                                           |            |

|            |                                                                                                                                                                          | 1          |

| 1.8        | Energy efficiency is optimal when the sum of energy from leakage and switching                                                                                           |            |

|            | energy is minimized                                                                                                                                                      | 12         |

| 2.1        | v                                                                                                                                                                        | L 5        |

| 2.2<br>2.3 | Two step algorithm to determine $p_{bit}$                                                                                                                                | 18         |

|            | accuracy and confidence                                                                                                                                                  | 18         |

| 2.4        | Theoretical translation of bitcell failure rate to system failure rate                                                                                                   | 20         |

| 2.5        | Particle strikes can inject current into sensitive NMOS drain nodes (blue) and sensitive PMOS drain nodes (red)                                                          | 23         |

| 2.6        | Transistor-level simulation of particle strike for the high storage node (NMOS                                                                                           | يا و       |

| 2.0        |                                                                                                                                                                          | 23         |

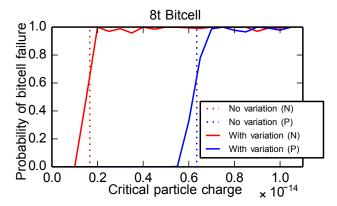

| 2.7        | ,                                                                                                                                                                        | <u>2</u> 4 |

| 2.8        | Transistor-level simulation of particle strike $Q_{crit}$ with and without accounting                                                                                    | -          |

|            |                                                                                                                                                                          | 24         |

| 2.9        |                                                                                                                                                                          | 26         |

| 2.10       | 1 1 0 0                                                                                                                                                                  | 27         |

| 2.11       | <u> </u>                                                                                                                                                                 | 32         |

| 2.12       | <u> </u>                                                                                                                                                                 |            |

|            | * * * * * * * * * * * * * * * * * * * *                                                                                                                                  | 3(         |

|            | Energy per operation for each dataset assuming $2/3$ dynamic energy and $1/3$                                                                              | 32 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1<br>3.2 | Effect of clock period on $V_{min}$                                                                                                                        | 35 |

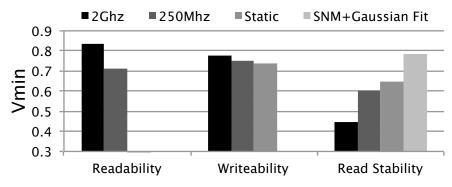

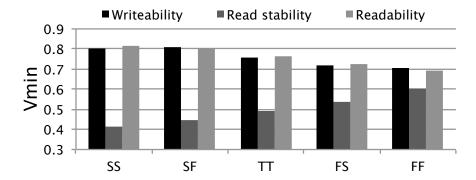

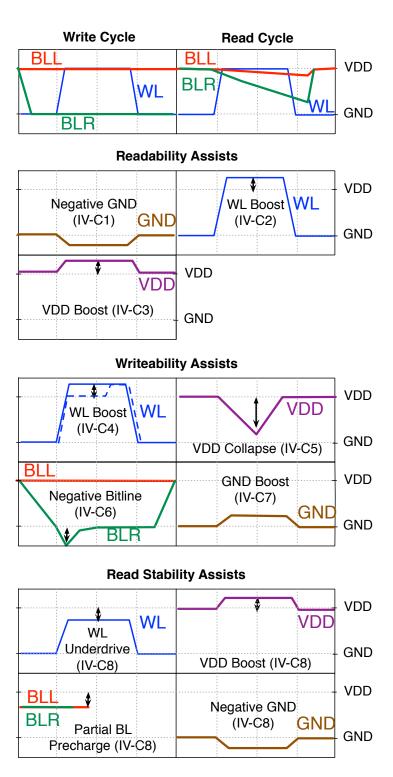

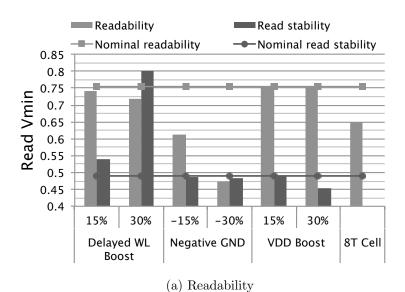

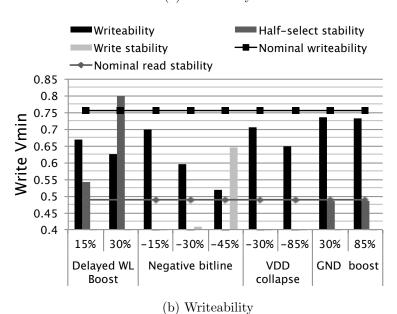

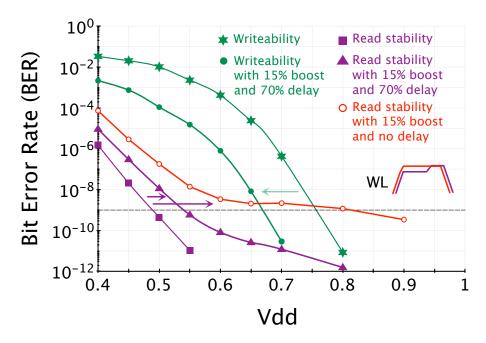

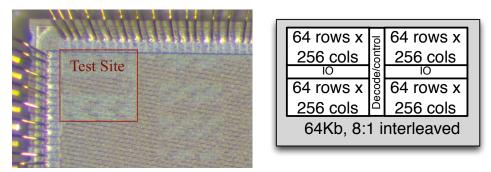

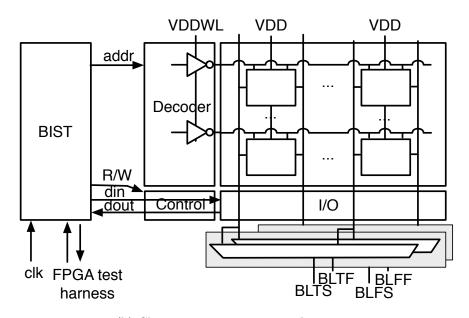

| 3.3<br>3.4 | Summary of assist techniques: negative GND, WL boost, $V_{DD}$ boost, $V_{DD}$ col-                                                                        | 37 |

| 3.5<br>3.6 | Impact of assist techniques on $V_{min}$                                                                                                                   | 39 |

| 3.7        |                                                                                                                                                            | 43 |

| 3.8<br>3.9 | Histogram and normal QQ plots of measured $V_{th}$ distribution for 32k cells from                                                                         | 4  |

| 3.10       | $V_{th}$ measurement difference between measured $V_{th}$ and simulated scheme using                                                                       | 45 |

| 2 11       | 010                                                                                                                                                        | 47 |

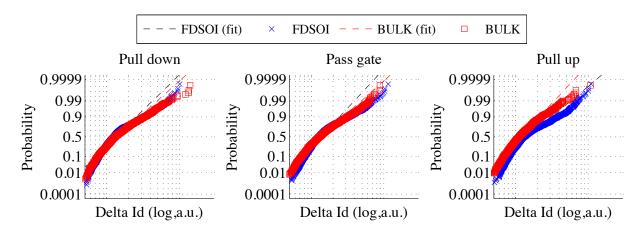

|            | Log-normal probability plot of RTN-induced current differences at cell $V_{th}$ using                                                                      | 4  |

|            |                                                                                                                                                            | 48 |

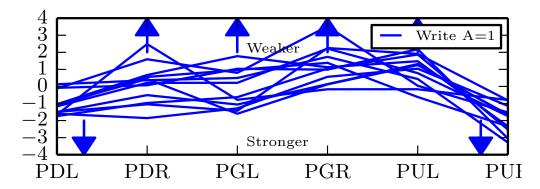

|            |                                                                                                                                                            | 48 |

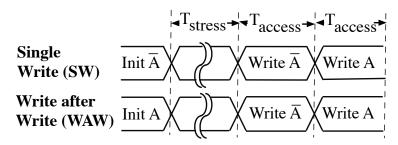

|            |                                                                                                                                                            | 49 |

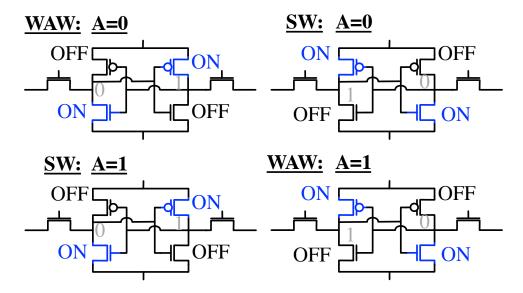

| 3.15       |                                                                                                                                                            | 5( |

| 3.16       | Example measured effect of RTN on $V_{diff}$ for a specific bitcell                                                                                        | 50 |

| 3.17       | Distribution of $V_{min}$ difference between write modes                                                                                                   | 5  |

| 3.18       | Difference in $V_{min}$ for six different chips                                                                                                            | 5. |

| 4.1        | SPW bitcell device cross section view. DNW isolates the PW from the p-substrate enabling wide voltage range PW back biasing                                | 54 |

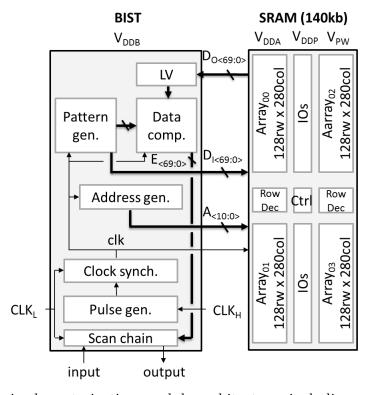

| 4.2        | Dynamic characterization module architecture, including a 140kb SPW SRAM macro clocked by an on-chip pulse generator and controlled by a programmable BIST | 54 |

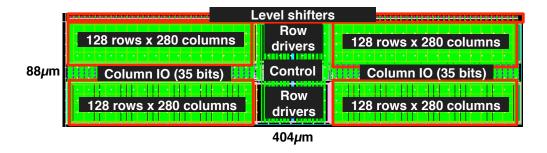

| 4.3        | 6T based high density 32KB SRAM array for failure characterization                                                                                         | 55 |

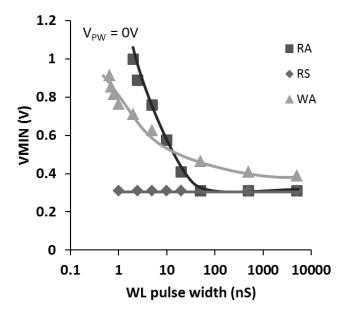

| 4.4        | RS, WA, RA $V_{min}$ versus WL pulse width                                                                                                                 | 55 |

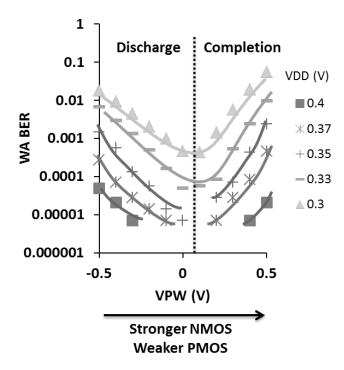

| 4.5        | Writeability bit-error rate (BER) versus $V_{PW}$ for different voltages                                                                                   | 56 |

| 4.6        |                                                                                                                                                            | 5  |

| 4.7        |                                                                                                                                                            | 58 |

| 4.8        |                                                                                                                                                            | 58 |

| 4.9        | <u> </u>                                                                                                                                                   | 60 |

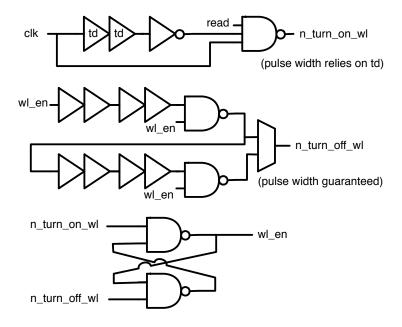

| 4.10       | Read wordline timing.                                                                                                                                      | 6  |

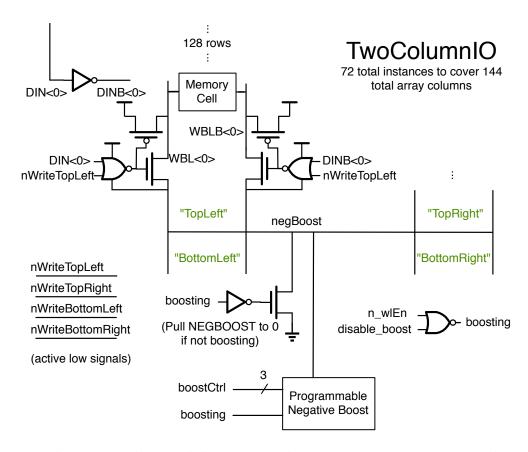

| 4.11 | The proposed writeability assist scheme generates a negative voltage on the bitlines to lower $V_{min}$ for write operations | 62 |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

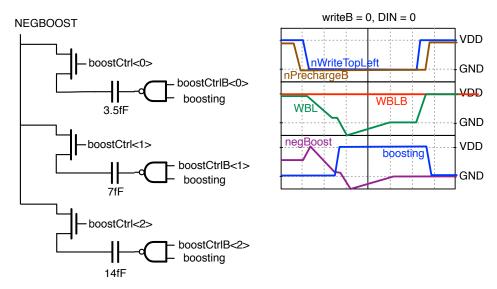

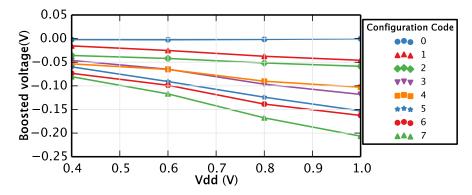

| 4.12 | A bank of programmable capacitance generates different strengths of negative                                                 | Ü- |

|      | assist to optimize energy at different voltages and process corners                                                          | 63 |

| 4.13 | Resulting negative boost amount for different configurations                                                                 | 63 |

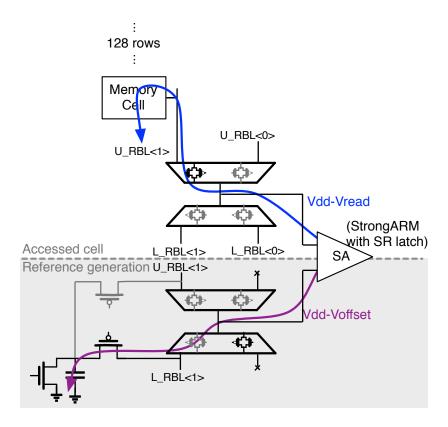

|      | Proposed low-swing single-ended read scheme generates a reference using an un-                                               |    |

|      | accessed bitline                                                                                                             | 65 |

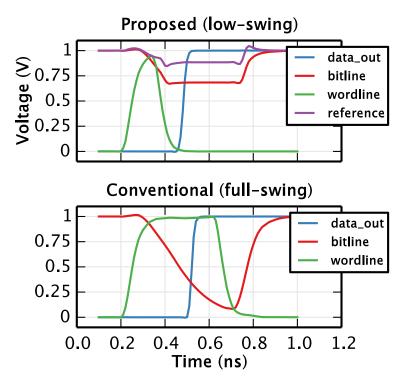

| 4.15 | Simulation-based operational waveforms comparing the proposed low-swing scheme                                               |    |

|      | with the conventional full-swing scheme                                                                                      | 66 |

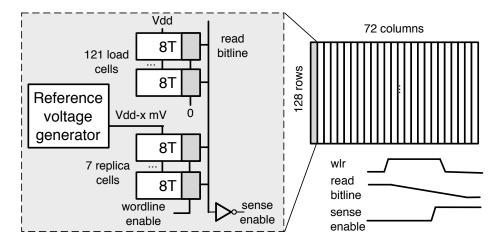

| 4.16 | A replica bitline emulates the weakest cell in the array to turn off the wordline                                            |    |

|      | and turn on the sense amplifier at the optimal time                                                                          | 66 |

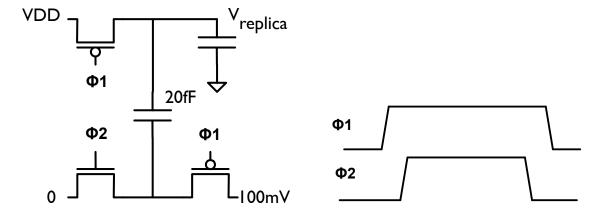

| 4.17 | Replica reference voltage generator subtracts a constant $V_{th}$ offset at the beginning                                    |    |

|      | of every cycle to respond to voltage noise                                                                                   | 67 |

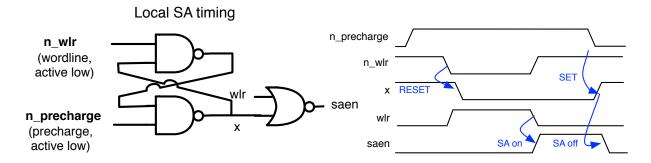

|      | Local sense amplifier timing generation                                                                                      | 67 |

|      | Backup read scheme                                                                                                           | 68 |

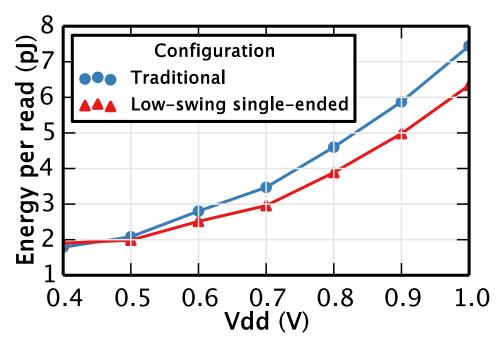

| 4.20 | Energy comparison between a conventional full-swing bitline and the proposed                                                 |    |

|      | low-swing scheme.                                                                                                            | 68 |

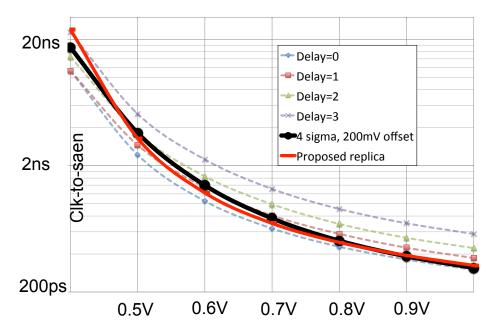

| 4.21 | Replica timing scheme tracks the weakest cell in the array more closely than an                                              |    |

|      | inverter-based delay chain                                                                                                   | 69 |

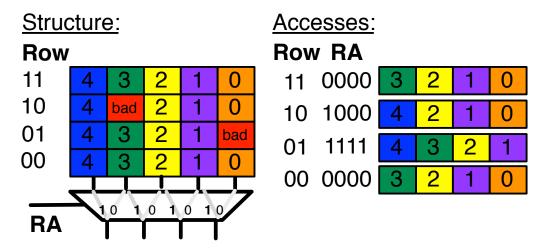

| 5.1  | Overview of the proposed DCR scheme, which reprograms a multiplexer to avoid                                                 |    |

|      | failing columns.                                                                                                             | 72 |

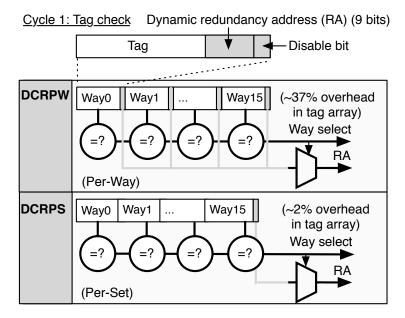

| 5.2  | An extra redundancy address is added to each way in the tag array for DCRPW,                                                 |    |

|      | or to each set for DCRPS                                                                                                     | 73 |

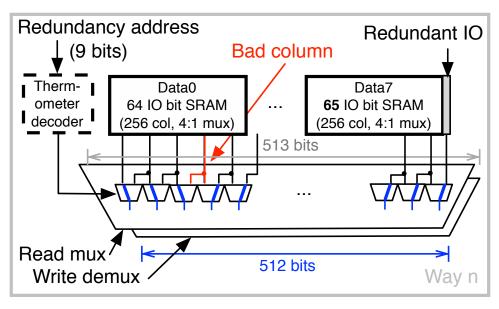

| 5.3  | For L2 caches, the proposed scheme uses the RA to multiplex/demultiplex around                                               |    |

|      | failing columns.                                                                                                             | 74 |

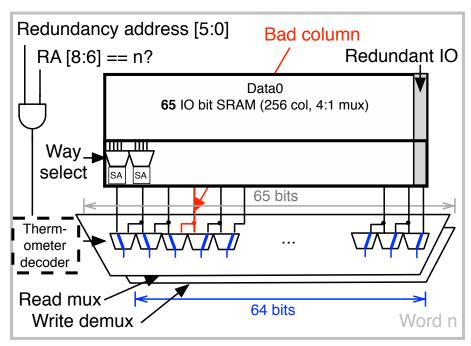

| 5.4  | For L1 caches, the proposed scheme uses a redundant column per array                                                         | 76 |

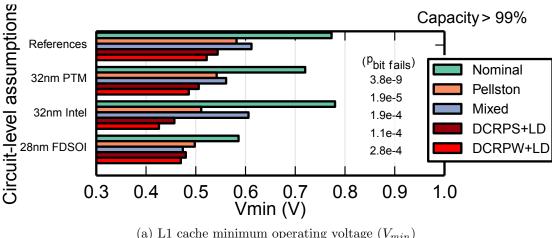

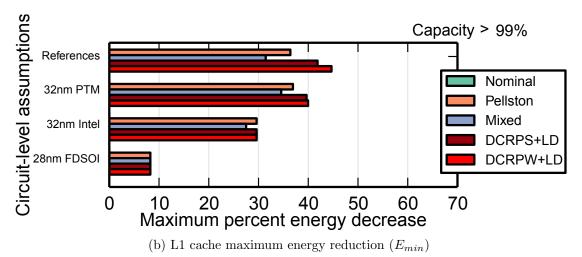

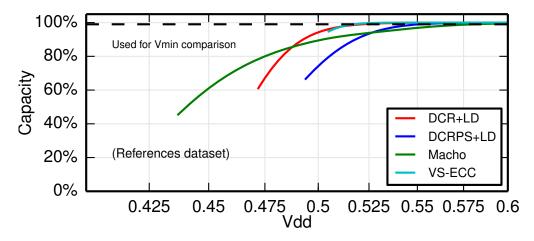

| 5.5  | Evaluation of the lower bound on voltage and energy reduction for L1 caches                                                  | 80 |

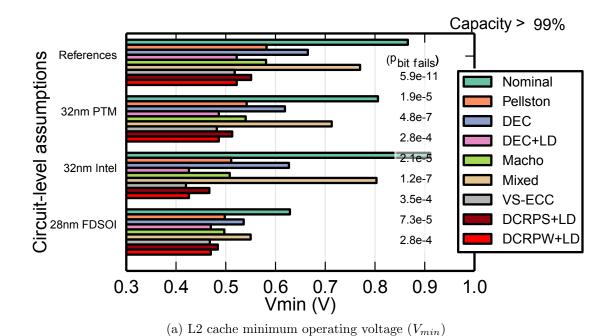

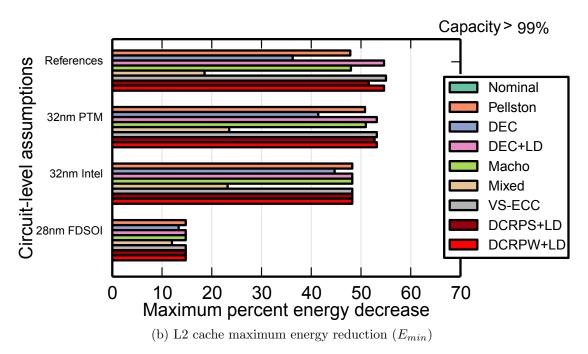

| 5.6  | Evaluation of the lower bound on voltage and energy reduction for L2 caches                                                  | 81 |

| 5.7  | Further $V_{min}$ reduction (< 50mV) is possible with capacity reduction                                                     | 82 |

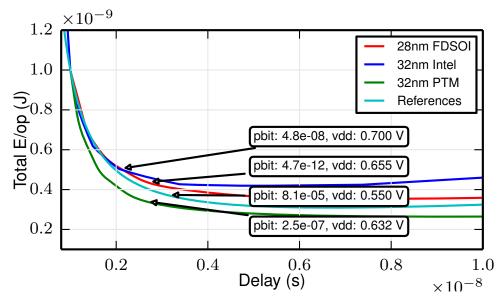

| 5.8  | Energy per operation versus delay with annotated points for minimum $\mathrm{E}^2\mathrm{D}$                                 | 83 |

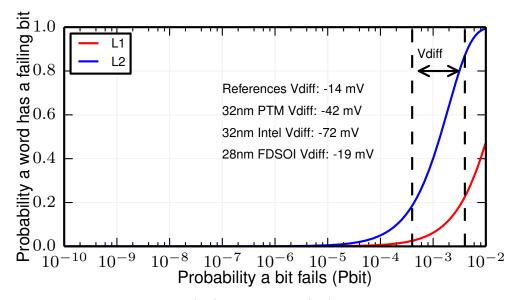

| 5.9  | Probability that a 64 bit (L1) and 512 bit (L2) word has failing bits versus bitcell                                         |    |

|      | failure probability.                                                                                                         | 84 |

| 5.10 | Overview of the proposed bit bypass scheme                                                                                   | 85 |

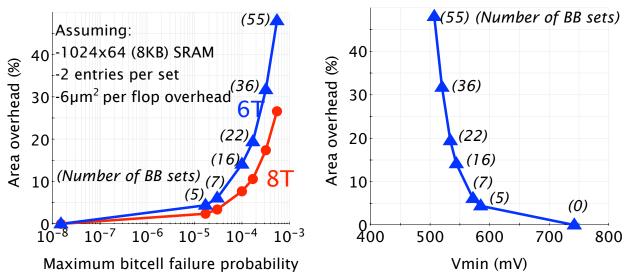

|      | Bit bypass trades off area overhead for increased resiliency                                                                 | 86 |

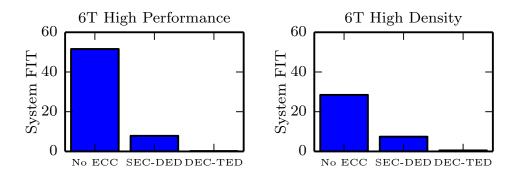

| 5.12 | System FIT (with bitcell FIT= $1\times10^{-3}$ ) with SECDED correction and 1 day of                                         |    |

|      | accumulation                                                                                                                 | 87 |

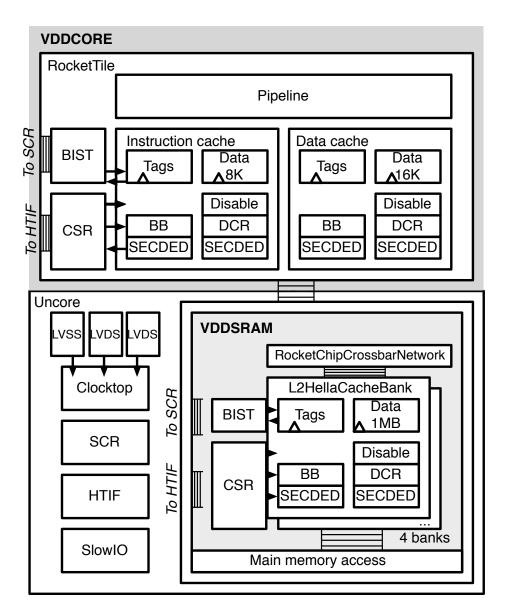

| 6.1  | High-level overview of the SWERVE system architecture                                                                        | 92 |

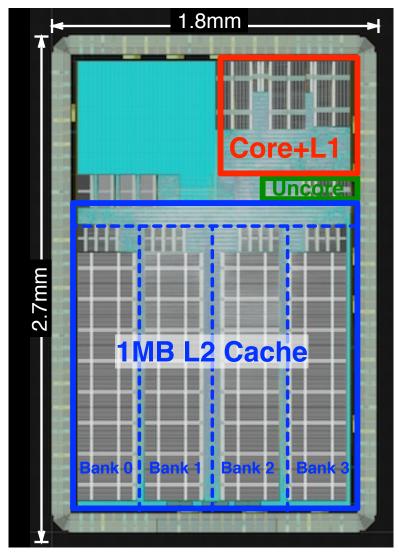

| 6.2  | SWERVE floorplan showing the physical layout of the core, L1 cache, and L2 cache.                                            |    |

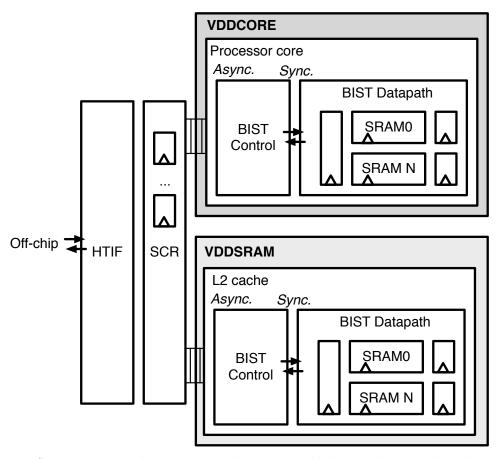

| 6.3  | BIST is organized as separated control and datapath in each voltage domain,     |     |

|------|---------------------------------------------------------------------------------|-----|

|      | and communicates with off-chip through system control registers (SCR) and the   |     |

|      | host-target interface (HTIF)                                                    | 95  |

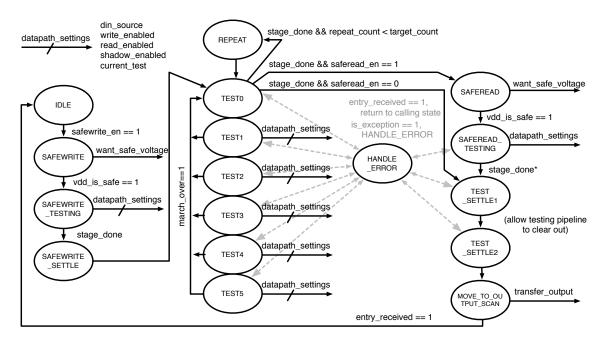

| 6.4  | BIST control state machine allows a wide variety of programmable March tests.   | 96  |

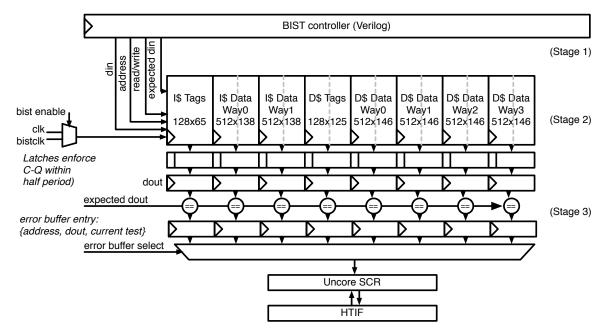

| 6.5  | BIST datapath reads and writes every SRAM in parallel at the maximum SRAM       |     |

|      | frequency                                                                       | 98  |

| 6.6  | Signals to and from BIST are synchronized between differing voltage and fre-    |     |

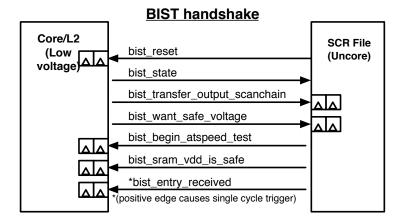

|      | quency domains.                                                                 | 98  |

| 6.7  | Excerpt from example control file implementing the MATS++ SRAM test             | 100 |

| 6.8  | Extra combinational and sequential logic required to implement bit bypass       | 102 |

| 6.9  | Encoding and decoding uses 2:1 multiplexers and a thermometer code to avoid     |     |

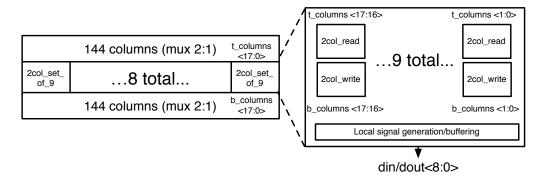

|      | one column.                                                                     | 104 |

| 6.10 | Chisel code implementing the encoding and decoding procedure to avoid a failing |     |

|      | column                                                                          | 105 |

| 6.11 | The redundancy address is accessed in parallel with the data array to identify  |     |

|      | the failing column corresponding to the accessed row                            | 106 |

| 6.12 | Pseudo-random algorithm to choose replacement way among remaining enabled       |     |

|      | ways                                                                            | 107 |

| 6.13 | BIST failure locations are used to program dynamic redundancy                   | 108 |

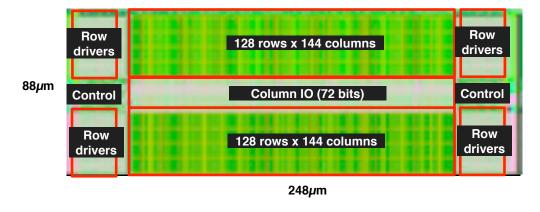

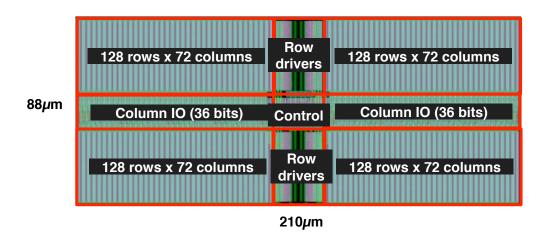

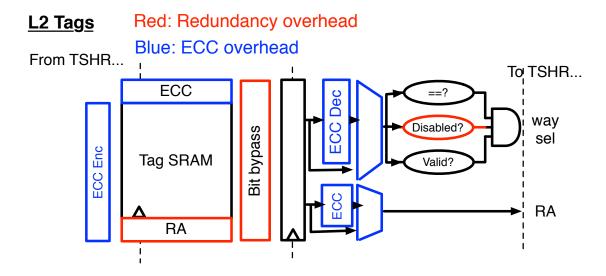

| 6.14 | Implementation of DCR, BB, LD, and SECDED in the L1 instruction cache           | 110 |

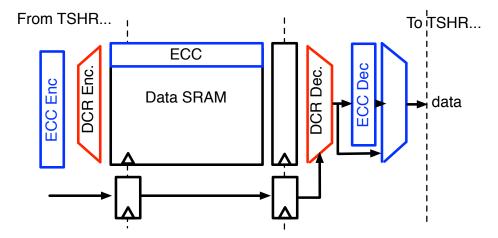

| 6.15 | Implementation of DCR, BB, LD, and SECDED in the L1 data cache                  | 112 |

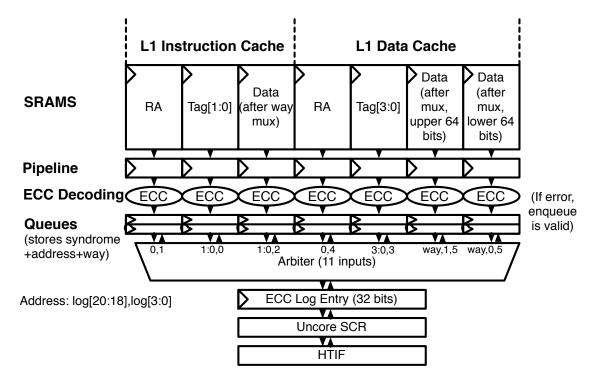

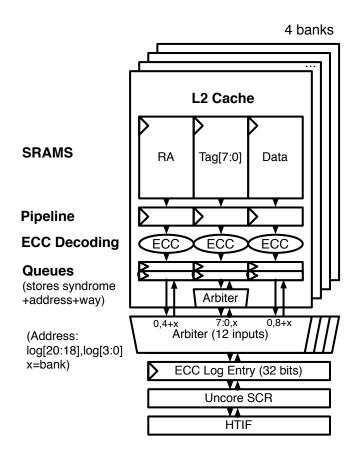

| 6.16 | Implementation of DCR, BB, LD, and SECDED in the L2 cache                       | 113 |

|      | L1 cache error logging                                                          | 114 |

| 6.18 | L2 cache error logging                                                          | 115 |

# List of Tables

| 2.1          | Comparison of including accumulation effects for a 32KB L1 cache with SECDED for a typical FIT rate $(1\times10^{-4})$ and extreme FIT rates during a 1 year-accumulation |            |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|              | period                                                                                                                                                                    | 28         |

| 3.1          | Most probable failure point for writeability at 0.8V                                                                                                                      | 35         |

| 5.1          | Delay and area comparison between SECDED and DCR from synthesized implementations in 28nm                                                                                 | <b>7</b> 4 |

| 5.2          | Inputs to evaluate the minimum operating voltage $(V_{min})$ using the proposed generic model in Equation 2.8 for different architecture-level resiliency techniques.     | 77         |

| 5.3          | Calculation of cache capacity for each scheme                                                                                                                             | 78         |

| 6.1          | List showing a subset of supported March tests by on-chip BIST controller                                                                                                 | 95         |

| 6.2          | Summary of every testable SRAM in the chip, with corresponding size and BIST macro address                                                                                | 96         |

| 6.3          | Effectiveness of bit bypass at increasing the acceptable failure rate and reducing                                                                                        |            |

| 0.4          |                                                                                                                                                                           | 102        |

| $6.4 \\ 6.5$ | Area overhead for bit bypass after synthesis                                                                                                                              | 103        |

|              | for 70 FO4 processor                                                                                                                                                      | 103        |

| 6.6          | O v                                                                                                                                                                       | 104        |

| 6.7          | Effectiveness of DCR at increasing the acceptable failure rate and reducing the                                                                                           |            |

|              | 1 0 0                                                                                                                                                                     | 105        |

| 6.8          | Effectiveness of DCR+LD at increasing the acceptable failure rate and reducing                                                                                            |            |

|              | the minimum operating voltage                                                                                                                                             | 107        |

| 6.9          | · v                                                                                                                                                                       | 115        |

| 6.10         | Ÿ                                                                                                                                                                         | 116        |

| 6.11         |                                                                                                                                                                           | 116        |

| 6 12         | Clock tree metrics for TT 0.9V 25C corner                                                                                                                                 | 116        |

### Acknowledgments

While writing this dissertation, I was constantly reminded that none of this work would have been possible without the support of so many friends and colleagues. I have had a wonderful time at Berkeley over the last five years because I have been fortunate enough to work with so many great people.

First, I would like to thank my co-advisors: Borivoje Nikolić and Krste Asanović. I couldn't have asked for better advisors. I never imagined that I would work for advisors who would spend so much time and energy to make sure that I succeed. Their combined technical expertise from circuits to software was vital for this work. Both are incredibly loyal, care deeply about the personal and professional development of their students, and have created an excellent culture at the BWRC and ASPIRE lab—I can't thank them enough.

Bora's group has many great students working in diverse research areas. Seng's dissertation formed a great foundation for my work, and his continuing advice has helped guide my research decisions; I wish we had overlapped for a longer period of time. Olivier Thomas helped teach me circuit design and collaborated on two tape-outs when I was a brand new student. The RAVEN team was a joy to work with. I credit many of the skills I learned to being able to work in such a supportive, friendly, collaborative, and creative environment—thank you so much Ruzica Jevtić, Ben Keller, Stevo Bailey, Martin Cochet, Jaehwa Kwak, Milovan Blagojević, Alberto Puggelli, and Pi-Feng Chiu. Building chips takes a lot of time and energy, and the huge contributions from this team made RAVEN3 and RAVEN3.5 possible. And to all of the other members of Bora's group over the years that provided moral support and friendship—Katerina Papadopoulou, Matt Weiner, Rachel Hochman, Amanda Pratt, Luis Esteban Hernandez, Milos Jorgovanovic, Dusan Stepanovic, Vinayak Nagpal, Ji-Hoon Park, Nicolas Le Dortz, Dajana Danilovic, Sameet Ramakrishnan, Sharon Xiao, Angie Wang, Amy Whitcombe, Antonio Puglielli, Vladimir Milovanovic, Charles Wu, Nicholas Sutardja, and John Wright—thank you.

The work from Krste's group has been incredible, and the development of RISC-V and processor IP has been invaluable for my research. Andrew Waterman's advice and feedback has been very helpful. Rimas Avižienis helped tape-out RAVEN1, and taught me a lot about the CAD toolflow. I would like to thank Yunsup Lee for being my inspiration and role model throughout my graduate career—his great attitude, effectiveness, vision, and helpfulness are unparalleled, and I feel incredibly fortunate that we were able to work together so closely. Thank you to the rest of the group helped build and support the RTL used in all five of my tape-outs Henry Cook, Huy Vo, Scott Beamer, Christopher Celio, Donggyu Kim, Palmer Dabbelt, Eric Love, Martin Maas, Albert Ou, and Colin Schmidt.

Outside of my advisors' groups, I would like to thank the other students that helped along the way. Nathan Narevsky always seemed to know the answers to all of my questions, and I had a great time developing curriculum and teaching EE141 with him. Stephen Twigg was always there to help me with my Chisel coding. Thanks to Nattapol Damrongplasit and Ying Qiao for teaching me about transistor measurement.

I had a great team of undergraduate researchers help me at various steps in my graduate career. Behzad Boroujerdian helped explore ECC codes; Brian Jenkins investigated BIST algorithms to diagnose error causes; Joey Talia designed an early version of a replica timing script; and Taylor Vincent found the first RTN in RAVEN1.

The Berkeley Wireless Research Center has been an awesome working environment, made possible by awesome staff. Brian Richards has been a joy to work with, patiently sharing his vast expertise throughout my entire graduate career. Thank you to Leslie Nishiyama, Deirdre McAuliffe-Bauer, Bira Coelho, Olivia Nolan, and Sarah Jordan for taking care of all of the administrative work so that I could focus on research. James Dunn is dependable and courageous in tackling new tasks, and has been a great help with IT support and PCB design. Daniel Burke and Fred Burghardt provided much-appreciated lab support.

If having two advisors wasn't enough, many other professors at Berkeley graciously provided help and advice whenever I asked. Elad Alon is extremely helpful and always has answers to our tough technical questions. I would like to thank Cari Kaufman and David Patterson for serving on my qualification committee. Tsu-Jae King Liu provided advice for the RAVEN1 design and measurements. John Wawrzynek and Vladimir Stojanovic were great instructors that I was fortunate to be a teaching assistant for. And thanks to Daniel Tataru for taking the time to be on my dissertation committee.

Industry feedback has been critical to making sure my work was relevant; thank you to Tom Burd, Mark Rowland, and Stephen Kosonocky, for taking the time to provide feedback on my research over the years. I would also like to thank my mentors at NVIDIA—Tom Gray, Bill Dally, Ethan Frazier, Mahmut Sinangil, Brucek Khailany, and John Poulton—for providing an awesome internship experience that taught me many useful skills and renewed my motivation for circuits research halfway through my PhD.

My research was funded by DARPA PERFECT Award Number HR0011-12-2-0016, Berkeley Wireless Research Center sponsors, ASPIRE sponsors, Intel ARO, AMD, and the NVIDIA fellowship. ST Microelectronics has donated four tape-outs, and Philippe Flatresse and Andreia Cathelin provided support that was crucial to the success of my research. TSMC donated a 28nm tape-out for the SWERVE project.

Outside of school, I was fortunate to have a great group of friends and family. Thank you Samarth Bhargava, Siddharth Dangi, Suraj Gowda, Kevin Messer, Ryan Going, Cameron Rose, and Dan Calderone for all of the great times! My twin brother, Michael Zimmer, ended up in the same PhD program as I did at the same time at the same school, which turned out to be one of the luckiest things that has happened to me. Spending time with him and his wife Sarah while sharing the ups and downs of our voyage through graduate school has been an incredible gift. My sister Julie has always given me endless love and encouragement. My parents, Paul and Jean, provided the best childhood anyone could ask for—encouraging me to develop and follow my passions and supporting all of my decisions.

And last I would like to thank my wife, Anjali. I would never have completed this dissertation without her constant love and support, and I am incredibly grateful to have her by my side.

I will cherish my memories at Berkeley because of all of the people who helped along the way—thank you all so, so much.

# Chapter 1

# Introduction

This chapter introduces the overall topic of the dissertation—how resilient design techniques can be used to improve cache energy efficiency. First, the motivation for this work is introduced by describing the importance of SRAM to modern digital systems and summarizing obstacles to further improvements. Next, background information about SRAM and its usage is reviewed, and related work is surveyed to provide information about other potential approaches and solutions. Last, the overall organization of this dissertation is provided.

### 1.1 Motivation

SRAM is the most popular dense memory structure in CMOS, due to the combined attributes of small size and high speed. While the memory element of an SRAM bitcell, a cross-coupled inverter pair, is also used in latches and flip-flops, the SRAM architecture assumes multiple bits are accessed at the same time, and thereby exploits a dense array organization and shared peripheral circuitry to amortize area overhead and enable more aggressive design rules. Embedded DRAM achieves higher area density due to the single transistor storage element, but requires extra process steps, needs refresh operations, and operates more slowly.

Processors are some of the most common digital systems, and SRAM makes up a large proportion of their chip area. Large on-chip caches in processors greatly improve performance and energy efficiency by avoiding unnecessary communication with off-chip memory, so a large portion of die area is necessarily devoted to SRAM bitcells. Processors will remain a workhorse of future integrated circuits—in devices such as laptops, smartphones, or the emerging markets of wearable electronics, internet of things devices, and automotive—so SRAM will endure as a vital system building block that requires constant improvements to performance, energy efficiency, and area. As parallelism increases and communication becomes more expensive, local memory that is dense and fast becomes even more critical to improve performance and save energy.

To minimize energy in digital systems, either the effective switched capacitance or voltage needs to be reduced, as switching energy is proportional to  $CV^2$ . The effective switched ca-

pacitance (C) is reduced with technology scaling and improved architectures that minimize the amount of capacitance that needs to be switched to finish a given task. The advantage of changing the operating voltage (V) is that it can be done during operation. When performance requirements are high, the voltage is increased to reduce transistor delay, but when lower performance is sufficient, the voltage is reduced to save energy in a scheme called dynamic voltage and frequency scaling (DVFS). The quadratic relationship between voltage and active energy makes voltage scaling an especially powerful means of reducing energy—a voltage decrease of only 200mV from 0.9V to 0.7V corresponds to a 40% reduction in energy.

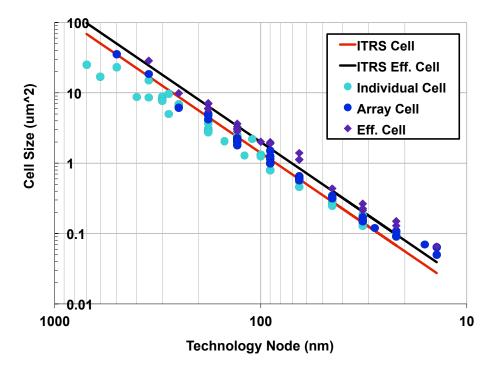

Figure 1.1: Measured bitcell area scaling (for individual pre-production cells, cells within arrays, and the effective cell sizes including overhead of peripheral circuitry) versus ITRS scaling predictions for decreasing technology nodes.

SRAM sets the minimum operating voltage of a system  $(V_{min})$ , due to the billions of extremely small transistors inside SRAM bitcells, and reliance on strength ratios to preserve functionality. To support large SRAM-based caches on-chip, transistor dimensions have been pushed to the extreme limit within each bitcell. SRAM bitcell size has maintained Moore's law scaling over many technology nodes, as shown in Figure 1.1. However, aggressive bitcell sizing yields transistors that have increasing process variation, and the dramatically increasing overall count of bitcells increases the probability of process variation sufficient to cause SRAM failure at low voltage. The read and write mechanisms of SRAM bitcells require specific strength ratios between devices. Figure 1.2 plots a simplified illustration of why SRAM

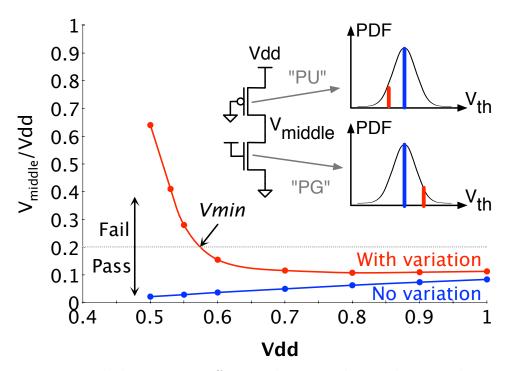

limits  $V_{min}$ . A PMOS and NMOS are connected in series between  $V_{DD}$  and ground, forming a voltage divider, and the middle voltage as a percentage of  $V_{DD}$  is plotted versus voltage. A bitcell cannot be written when the middle voltage surpasses a threshold. Two variation cases are enumerated: no variation at all, and a shift in transistor threshold voltage representing the strongest PMOS and weakest NMOS out of 1 million cells. At high voltages, process variation has little effect, because the gate voltage is far from the threshold voltage. However at lower voltages, the shift in threshold voltage has a significant impact on transistor strength, and the intermediate voltage surpasses the success threshold—representing a failure event. Therefore, making SRAM cells resilient to process variation is necessary to further reduce  $V_{min}$  and improve energy efficiency.

Figure 1.2: Variation only has a major effect on the strength ratio between devices at lower voltages.

One simple solution to avoiding SRAM failures at low voltage is to isolate the SRAM supply from the logic supply in order to keep SRAM at high voltage. However, this approach, sometimes referred to as "dual rail" [2], has a few disadvantages. First, power delivery complexity increases because SRAM arrays are mixed into logic areas. Second, timing verification between two separate voltage domains is complicated and requires additional margining. Third, overall energy efficiency improvements from voltage scaling are limited by the fixed energy consumption of SRAM, especially in L2 or L3 caches where SRAM contributes almost

all of the power consumption. For these reasons, this work dismisses dual rail and focuses on the case where SRAM shares the same power domain as surrounding logic.

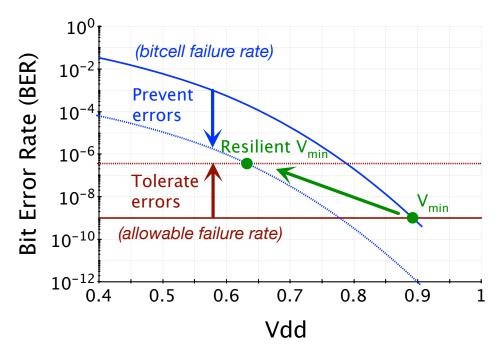

Figure 1.3: Resilient techniques decrease  $V_{min}$  by either reducing the bitcell error rate or tolerating failures to increase the acceptable failure rate.

The other solution, and the focus of this work, is to use resilient design techniques to lower the minimum operating voltage of SRAM. Resiliency refers to the ability to tolerate process variation and prevent device non-idealities from causing system failure. Figure 1.3 shows the general idea of resilient design. Bitcell failure rate is plotted versus operating voltage. The number of cells in a design will set a maximum allowable bitcell failure rate, which is represented as a horizontal line on the plot. The intercept of the failure curve and the allowable failure rate represents  $V_{min}$  of the design. Two general strategies can be used to reduce  $V_{min}$ —either prevent or tolerate bitcell failures. Resiliency techniques that try to prevent process variation from causing failure decrease the probability that a bitcell fails at a given voltage, shifting the curve down and moving the intercept to the left, representing a reduction in  $V_{min}$ . Resiliency techniques that tolerate bitcell failures at a system level increase the maximum allowable bitcell failure rate, shifting the horizontal line up and also moving the intercept to the left, representing another method of reducing  $V_{min}$ . Both strategies can be used together for maximum  $V_{min}$  reduction.

Each resiliency technique reduces  $V_{min}$ , but at the cost of additional overhead in terms of area, energy, delay, and design complexity. Evaluating both effectiveness and overhead of different schemes at a system level is required to choose the appropriate techniques for a particular design.

To summarize, processors need huge SRAM-based on-chip caches that operate at low voltages to maximize energy efficiency and performance in digital systems. Achieving this goal requires using extremely small transistors inside SRAM bitcells that experience large random variations, which are further exacerbated at low voltages. Resiliency techniques that prevent or tolerate errors are necessary to continue innovation in digital systems by improving cache energy efficiency through increased voltage scaling.

# 1.2 Background

Background knowledge about SRAM and its usage is necessary to understand the motivation and context of various solutions in the following chapters. Due to the holistic approach required to improve energy efficiency in caches, a review of both circuit-level and architecture-level topics is necessary.

### 1.2.1 Circuit-level Topics

Circuit-level bitcell topics include describing how SRAM cells are designed, explaining how peripheral circuit reads and writes individual bitcells, and demonstrating how transistor variation can cause failures.

#### **Bitcells**

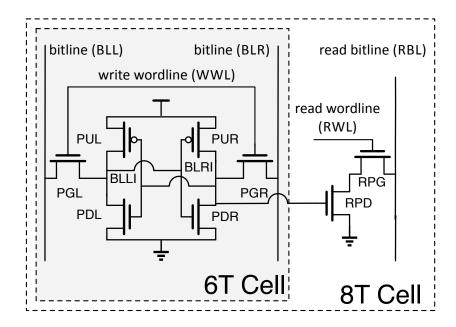

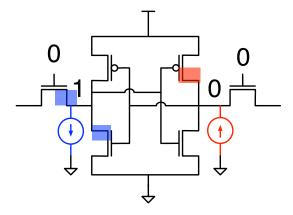

Static random-access memory (SRAM) is a form of on-chip memory that requires a power supply to maintain its contents. Most SRAM uses six transistors (6T) to store one bit of information, while other versions such as the eight-transistor (8T) cell use extra transistors to enable multiple reads or writes per cycle. Figure 1.4 shows both cells and some naming conventions: PU for pull-up, PD for pull-down, PG for pass-gate in the 6T and 8T cell, and additionally RPD for read-pull-down, RPG for read-pass-gate in the 8T cell. The PD and PU devices form the storage element of the SRAM cell using positive feedback to hold differential data on the left and right side of the cell. The PG devices enable access to this bit of memory for either reading or writing. Unlike DRAM, no refresh is needed to maintain the state of the cells. If the voltage falls below the retention voltage  $(V_{ret})$ , the transistors in the storage element effectively turn off, and the contents of the cell are lost. Therefore in sleep states, the state stored in SRAM must either be moved to another location in order to turn off power to the SRAM, or the voltage must be maintained at a specific  $V_{ret}$ .

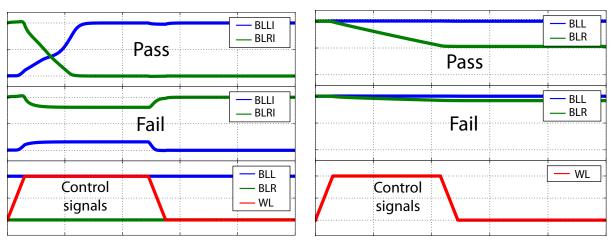

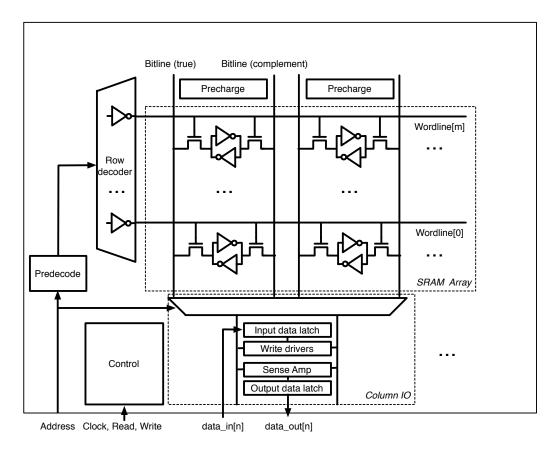

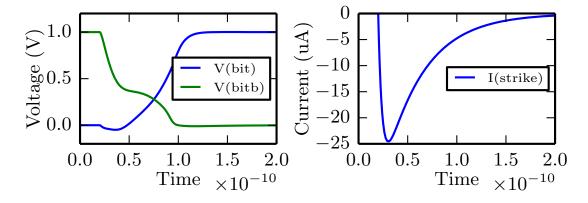

Figure 1.5 depicts how bitcells are read and written with example waveforms showing successful and unsuccessful operations. For a write operation, the desired cell contents are placed differentially on the bitline, so one side will be high while the other will be low. Writeability failures occur when either the high node cannot be pulled low through the pass gate (because the PG is not stronger than the PU) or the low node cannot be pulled high through the PU (because the PD is stronger than the PU and PG). For a read operation,

Figure 1.4: 6T and 8T SRAM bitcell schematics and naming convention.

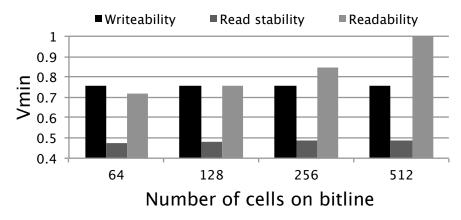

both bitlines will be precharged and left floating at a high value. Readability failures occur when the voltage differential generated on the bitlines does not surpass the sensing offset voltage of the sense amplifiers. Because many bitcells share a single bitline to reduce area overhead, the capacitive loading of the bitline can be quite high, and weak bitcells cannot sink enough read current to discharge the bitline in a given amount of time. Read stability failures occur during either a read access, when the side of the cell holding the low value will experience a voltage bump due to the voltage divider between the PD and PG. If the PD is not sufficiently strong, the voltage can rise above the trip point of the cell and accidentally flip the contents of the cell.

There is an intrinsic conflict between stability and writeability in a bitcell. Large transistors in the storage element (PU and PD) with weak access transistors (PG) would favor stability, while large access transistors and small storage element transistors will favor writeability. In particular, for a cell to be both stable and writable, the PD must be sufficiently stronger than the PG, and the PG must be sufficiently stronger than the PU. Therefore the PG has both a lower and upper bound on strength, and changing PG size will trade-off stability and writeability.

Bitcell failures can be measured with either static or dynamic metrics. Traditionally, static metrics, such as the static noise margin (SNM), were used to estimate  $V_{min}$ . However, static metrics assume infinite access time, and therefore are pessimistic measures of read stability, and optimistic measures of writeability [3]. Dynamic metrics, which account for finite access time of bitcells, closely predict actual  $V_{min}$  [4], and will be used throughout this work.

(a) Example of SRAM writeability.

(b) Example of SRAM readability.

(c) Example of SRAM read stability.

Figure 1.5: SRAM operation waveforms.

#### Sources of variation

There are many sources of device parameter variations caused by an imperfect manufacturing process, such as random dopant fluctuations (RDF) or line-edge roughness (LER) [5]. Random (or local) variations such as RDF exist between each transistor in the design, reducing matching in analog differential pairs or ratioed devices in SRAM cells. Additionally, there are systematic variations that affect all devices on the same die, wafer, or lot—causing all devices to have different drive current versus gate voltage characteristics.

While process parameter variations have dozens of physical sources that change many components of transistor performance, variation can be modeled with a first-order approximation by assuming all variation only affects the threshold voltage of the device. Using 3D simulation, the distribution of the threshold voltage was predicted to be Gaussian to about 3 sigma, then is positively skewed [6]. Random or local variation is represented as the variance of the distribution, while systematic variation corresponds to shifting the mean of the distribution. As technology features decrease in size, the contribution of different physical sources of variation changes. In general, smaller technology nodes have increasing variation, because the fewer dopant ions in the channel increases variation from random dopant fluctuations [5].

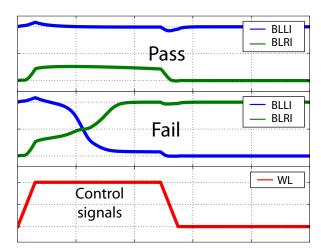

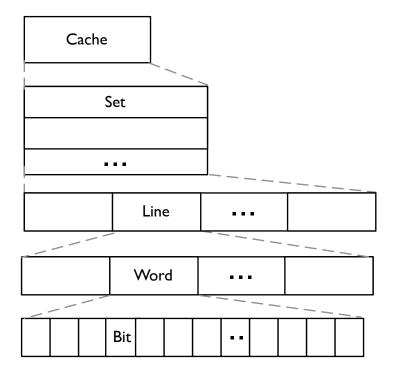

#### Array organization

To amortize the area overhead of peripheral circuits used to read and write the SRAM, bitcells are organized into arrays, as shown in Figure 1.6. When reading a word, the entire wordline is turned on along the row direction, and the data in each cell is transferred onto the differential bitlines along the column direction by discharging one of the bitlines on the side of the cell holding a zero value. Sense amplifiers that detect the voltage difference on the bitlines are generally larger than the width of a cell, so bitcells are physically interleaved to only read 1 out of every N bitcells, where N is a power of two. After the read operation is completed, the bitlines are precharged again to prepare for the next operation. During a write operation, one of the bitlines is discharged low, while the other is held high (or left floating high). When the pass gate transistors are turned on by the wordline, the feedback of the internal inverters is overcome by the pass gates to write a new value into the cell.

From a system perspective, an SRAM appears with a logical width w and depth d, where an access reads or writes w bits (a word), there are d unique addresses to store w bits, and there are  $w \cdot d$  bits total in an array. In a non-interleaved design, there are d wordlines (rows) for each address, and there are w bitline pairs (columns). The shape of the array can be changed by physically interleaving multiple words on a row and using multiplexers to access the desired set of columns. Arranging more cells on each wordline and bitline improves area density, but also increases energy and delay.

In the simplest implementation, the row decoder is placed on either the left or the right side of the array, the column logic is placed above or below the array, and the control logic is placed in one corner. Performance can be increased at the expense of area and additional metal layers by segmenting the wordline, the bitline, or both. In a segmented

Figure 1.6: Organization of SRAM bitcells into an array.

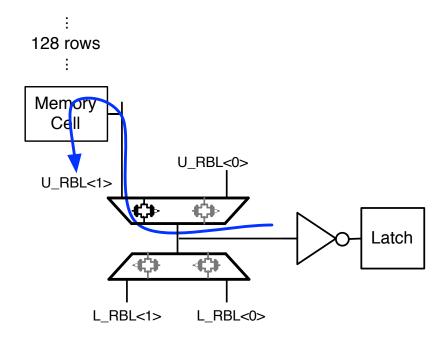

design, the row decoders can be placed in the middle of the array horizontally to reduce wordline length, and the column IO can be placed in the middle of the array vertically to reduce the bitline length by half [7]. To further increase performance, the bitline can be segmented into multiple hierarchical local bitlines that drive larger global bitlines at the expense of area overhead [8],[9].

### 1.2.2 Architecture-level Topics

A level of abstraction separates circuit-level and architecture-level topics. Once an SRAM array is designed and verified at the circuit-level, it is abstracted as a memory that holds a specific number of addressable words of data with a maximum cycle time. These SRAM macros are used at the architecture-level to build larger structures, such as caches, that don't depend on specific circuit issues within each SRAM macro.

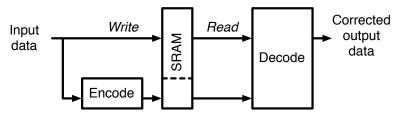

Figure 1.7: Generic error-correcting codes (ECC) stores extra bits to repair faults during SRAM read or write.

#### Cache organization

SRAMs have many different uses in digital system, and are generally used for memory elements with thousands of bits or more. On-chip caches in processors contain many millions of SRAM cells; there are up to 300 million bits in modern 22nm Intel Xeon processors [10].

A cache attempts to hide memory latency by appearing as a much larger memory than it actually is by storing frequently accessed data [11]. Only the lower bits of the address map into each row in the memory, so different data with differing upper address bits could conflict and map to the same constrained resource. Caches generally use SRAM for both the tag and data portion of the cache, where the tag array is a small portion of the overall area.

The caching technique is repeated hierarchically, with usually two to three levels of caching, where the smallest and fastest (level-one or L1 cache) use large bitcells and smaller bitlines to reduce delay, and the last level of the cache (L2 or L3 caches) use the smallest bitcells possible to increase capacity. These multiple levels make caching a particularly interesting design target because each level has very different SRAM design constraints.

#### Error-correcting codes (ECC)

Error-correcting codes, commonly referred to as ECC, detect and correct bit flips during every read operation by decoding additional bits stored with the words. Figure 1.7 explains how a generic error-correcting code protects an SRAM array from failure. ECC detects bit flips from all failure sources including intermittent and soft errors. Numerous ECC codes offer differing correction and detection capabilities. Most commonly, SECDED corrects a single bit per word, white DECTED corrects up to two bits per word. Upgrading from a SECDED code to DECTED code increases the complexity and overhead of the encoder and decoder [12], potentially precluding usage in L1 caches.

# 1.2.3 Relationship between Voltage, Energy and Delay

Improving energy efficiency is crucial for all systems and workloads, as Equation 1.1 illustrates with a high-level abstraction.

Performance

$$\left(\frac{\text{ops}}{\text{s}}\right) = \text{Power}\left(\frac{\text{J}}{\text{s}}\right) \cdot \text{Energy Efficiency}\left(\frac{\text{ops}}{\text{J}}\right)$$

(1.1)

If performance is constrained, the only way to reduce power is to improve energy efficiency, while if power is constrained (either for thermal reasons or limited battery capacity), the only way to improve performance is to improve energy efficiency. Therefore while mobile and server applications have power budgets two orders of magnitude apart, perform different workloads, and have widely varying performance constraints, using voltage scaling to improve energy-efficiency is beneficial in both systems.

Energy consumption in digital systems comes from two sources: switching (or active) and leakage. Additionally, to understand energy-efficiency, the distinction between energy and power (energy per unit time) is important. Switching energy per clock cycle is equal to the total capacitance switched times the voltage squared ( $E_{switch} = C_{effective}V^2$ ), and can be converted to power by estimating the frequency ( $P_{switch} = C_{effective}V^2 \cdot f$ ). The effective switched capacitance changes each cycle based on the activity of the design. Leakage is generally measured as power, but can be converted into energy using the frequency of operation. Leakage power is dependent on process parameters (current versus gate voltage), the voltage, logic gate mixture, and logic state.

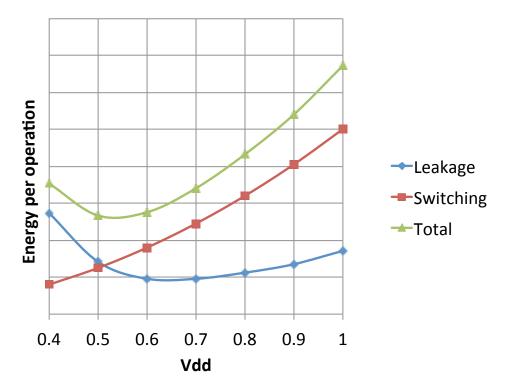

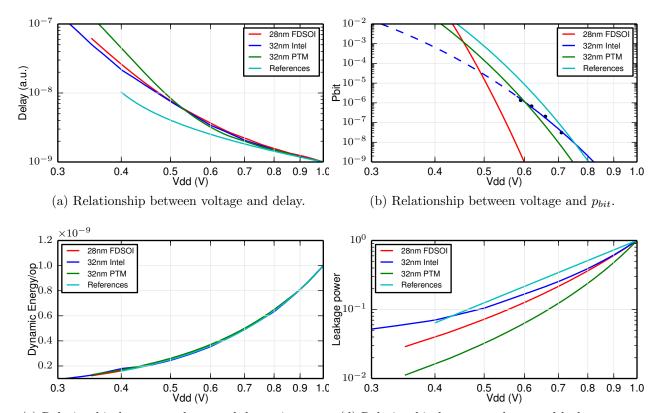

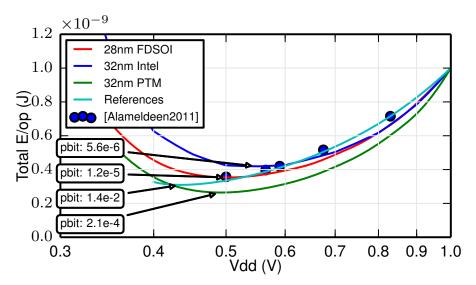

Decreasing the voltage will decrease both the switching and leakage power, but the transistors will have less drive current and the frequency of operation will be reduced. Energy-efficiency will improve as voltage decreases, until the point at which the dramatic increase in transistor delay near the threshold voltage causes more leakage to be integrated per cycle than saved switching energy, creating an optimal energy-efficiency point shown in Figure 1.8. The optimal point is usually well below the  $V_{min}$  of SRAM, so using resiliency to reduce  $V_{min}$  to the optimal point is the goal of this work. The minimum energy point exists near the threshold voltage, but also is a function of the ratio between switching and leakage energy—if switching energy is a higher proportion of total energy either implicitly from the design or due to higher activity, the minimum energy point will be at a lower voltage.

# 1.3 Related Work

Many resilient design techniques have been developed to improve SRAM  $V_{min}$ . Understanding the effect of process variation is vital both for yield improvement and  $V_{min}$  reduction [5]. SRAM bitcell failures due to persistent process variations (such as random dopant fluctuation) have been studied using both simulation and experimental measurements. Simulation-based analysis relies on either static metrics [13] or accelerated-Monte-Carlo simulation to predict rare failure events [14], [15], [16]. Measurement-based analysis uses a combination of individual transistor measurements and at-speed test generators to locate bitcell failures [17], [4]. In addition to persistent process variations, soft error strikes can cause bitcell failures [18], and random telegraph noise and aging change transistor strength over time [19].

Figure 1.8: Energy efficiency is optimal when the sum of energy from leakage and switching energy is minimized.

Circuit-level resiliency techniques have been proposed to prevent extremely weak or strong transistors from causing bitcell failures. Adding two extra transistors to each bitcell to create the single-ended 8T cell decouples the read and write operation to improve low voltage operation [20], [21], [22]. Circuit assist techniques change wordline [8], bitline [23] [24], or cell supply voltages [7] on a cycle-by-cycle basis to strengthen or weaken particular devices during each operation, and have been shown to significantly reduce  $V_{min}$ .

Architecture-level resiliency use redundancy or error correction to repair or avoid bitcell failures. Redundancy-based techniques guarantee working memory cells to compensate for failing cells [25], [26], [27]. Error-correction-based techniques encode data with extra bits that are used to detect and correct bit flips when they occur [28], [29], [30].

In general, existing studies have focused on a single layer of abstraction, comparing circuit solutions to other circuit solutions and architecture techniques to other architecture techniques (with a few exceptions, such as [31]). A comprehensive analysis with a common evaluation framework can determine the optimal set of resiliency techniques to lower  $V_{min}$  for a given set of process and implementation assumptions.

### 1.4 Thesis Outline

This work takes a holistic approach that explores resiliency solutions which enable  $V_{min}$  reduction of SRAM at different levels of abstraction, verifies the models and techniques with fabricated and measured designs in a modern 28nm process, and evaluates each solution within the context of a full system.

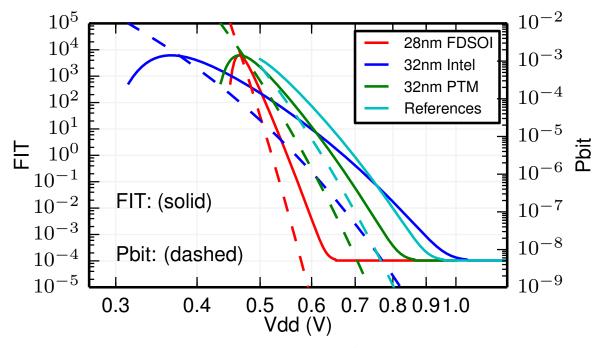

Chapter 2 proposes an error model that translates basic sources of variation and soft error strike models to system yield and FIT as a function of resiliency techniques at both the circuit and architecture level. This model is used in later chapters to gain insight into the effectiveness of different resiliency techniques and provide in-depth analysis and comparison of different ideas. While targeted at SRAM inside cache-like structures, the methodology is easily generalized to any SRAM organization in digital systems.

Chapter 3 explores SRAM failure mechanisms using both simulation and measurement based approaches. Simulation approaches enable a design-time study of the effectiveness of various circuit techniques to improve low voltage SRAM operation. Measurement results from a 28nm testchip validate assumptions about process variation and explore the impact of intermittent sources of variation. These results are crucial for correctly anticipating the behavior of SRAM failures in real silicon for effective design of complete resilient systems.

Chapter 4 proposes a few circuit-level resiliency techniques. A new bitcell, measured in a 28nm design, uses back bias to compensate for systematic process variation. A new macro, part of two more 28nm chips, enables a wide operating range of 0.45V to 1V using a write assist technique and replica timing.

Chapter 5 analyzes the effectiveness of a variety of previously proposed architecture-level resiliency techniques, and proposes new techniques called bit bypass and dynamic column redundancy that significantly increase the maximum allowable bitcell failure rate with very little overhead. Also, a discussion of the analysis summarizes a set of guidelines that provide intuition about different resiliency approaches. Last, redundancy and error-correcting code based techniques are compared using the joint hard and soft error model.

Chapter 6 compiles the results from previous chapters to build a complete processor with resilient cache that avoids bitcell errors to reduce  $V_{min}$  and improve energy efficiency. A memory test identifies failing bitcells at different voltages, and error-correcting codes detect both soft and intermittent errors during operation.

Chapter 7 concludes by summarizing the key contributions and suggesting directions of future research.

# Chapter 2

# Error Models

This chapter describes the error model used throughout this thesis to evaluate different resiliency techniques. The model is holstic, and translates basic physical sources of error to overall cache yield and failures in time while accounting for both circuit and architecture-level resiliency techniques.

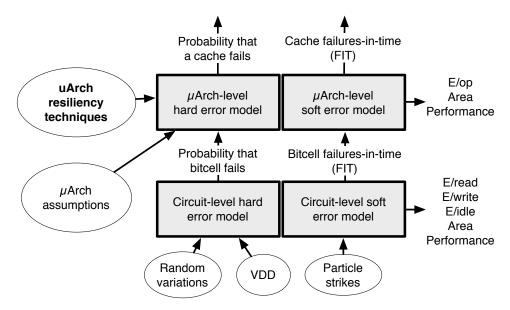

Error models are necessary to evaluate the effectiveness of different resiliency schemes. A memory error model was developed to calculate yield and failures-in-time as a function of cache design, resiliency techniques, expected transistor variation, and operating voltage. As shown in Figure 2.1, the model uses both a circuit-level model and a microarchitecture-level model to translate bitcell failure probability at different operating conditions to cache failure probability. The circuit-level model determines the probability that a single bitcell will fail, based on transistor-level simulations of the bitcell affected by random variation under different operating conditions. The architecture-level model assumes bitcells are organized as a cache, and translates the probability of bitcell failure to cache yield. A similar methodology could be used for any organization of bitcells in a digital system, but most SRAM in digital systems are used in caches, so assuming organization into a cache can provide valuable insight and immediately useful results.

The model focuses on the probability that a cache fails, but *not* the probability that a complete system fails; by avoiding assumptions about architecture and activity, the results are general and widely applicable. Higher-level architecture and application-level error-vulnerability models can translate the probability that a cache will fail to the probability that a system will fail [32], but this higher-level analysis is orthogonal to the evaluation of alternative cache designs. Note that the higher levels can only mask soft errors and not hard faults, under the assumption that a system will rely on all parts of the available cache at some point, and so can only decrease failures-in-time (FIT) and not yield.

This model makes two main contributions. First, the model is holistic—modeling failure rates at both the circuit and architecture level, and accounting for interactions between the two different levels of abstraction. Chapter 5 will show that an architecture-level resiliency scheme's effectiveness is very sensitive to circuit-level assumptions, and that accurately modeling bitcell failure probability as a function of voltage is critical.

Figure 2.1: Memory error model for hard and soft faults.

Second, the microarchitecture-level error model is general, and not specialized to the particular scheme under evaluation. This flexible approach to modeling resiliency schemes enables easy comparison between many different schemes without sacrificing any accuracy.

# 2.1 Modeling Sources of Error

It is important to differentiate between different sources of error, as some resiliency techniques can only protect against specific kinds of errors. Even though there are many physical sources of errors, errors are categorized based only on their characteristics.

#### 2.1.1 Hard Faults

Hard faults (also known as persistent errors) are generally caused by an imperfect manufacturing process and persist for the lifetime of a chip. These errors are localized to particular devices. The hard faults analyzed here are *not* yield faults in the bitcells or periphery that cause failures at nominal voltage, but rather bitcells that work well at high voltage and only begin to fail at lower voltages due to variation. The most common sources of variation are line-edge roughness (LER) and random dopant fluctuation (RDF). These effects are modeled as a shift in the threshold voltage of a device, using a Gaussian distribution with a different standard deviation for each process technology. The circuit-level model translates LER and RDF effects into bitcell failure probability as a function of voltage. A built-in-self-test (BIST) that tests the SRAM can identify the location of these failures.

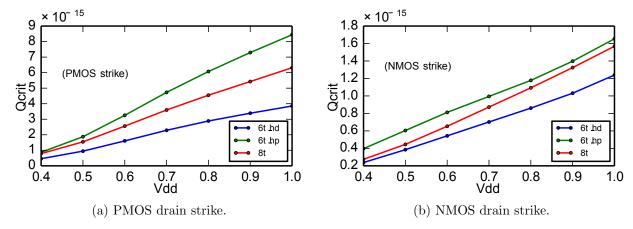

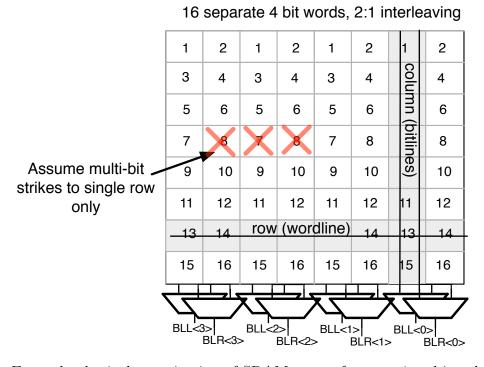

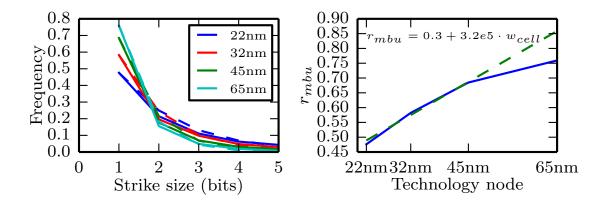

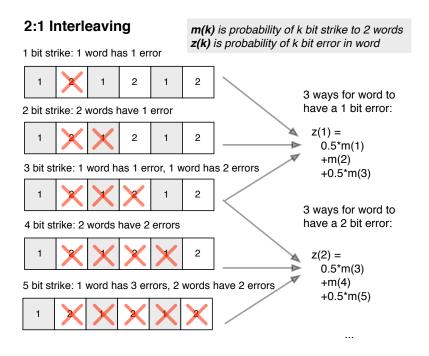

#### 2.1.2 Soft Errors

Soft errors (also known as transient errors) are rare events that cause an error, but do not cause long-term damage. A high-energy particle striking a circuit node results in a voltage pulse that can flip the value of a bitcell. In the model, the case where two or more separate soft error strikes occur in the same cache line is ignored. Detailed analysis showed that the high frequency of cache accesses prevents multiple soft errors from building up in single word, and that physical bitcell interleaving can easily prevent a high-energy multi-bit particle strike from affecting multiple bitcells in the same word.

In a few cases, soft errors can affect the proposed hard-fault model. In some proposed schemes, SECDED is used to correct hard faults without upgrading ECC protection to DECTED, leaving words with hard faults vulnerable to soft errors [31]. An in-depth analysis provided later shows that this design choice can only be justified with particular combinations of assumptions about bitcell failure rates, bitcell FIT, system architecture, system activity, and required system FIT. In general, sharing single-bit ECC between hard faults and soft errors is not acceptable, and so we do not consider this option further in this thesis.

#### 2.1.3 Intermittent Errors

Intermittent errors, such as random telegraph noise (RTN) and aging-related errors, share characteristics of both hard and soft errors. Like soft errors, the probability of occurrence is not 100%, but like hard faults, these defects are bound to specific devices. Because BIST might not detect these faults, repair-based resiliency techniques cannot protect against intermittent errors, and these errors need to be treated as soft errors for failure analysis.

# 2.2 Circuit-level Hard-fault Model<sup>1</sup>

The circuit-level hard fault model translates random variations to memory bitcell probability of failure for different bitcells, voltages, and circuit-level resiliency techniques. This model is essential to correctly compare resiliency techniques, because the slope of voltage versus bitcell failure probability determines the amount of voltage reduction, and therefore energy-efficiency gains, enabled by different resiliency techniques. A steeper failure slope means that resiliency techniques provide less energy-efficiency improvements than a flatter slope, making it more difficult to justify the additional overhead or complexity of a technique.

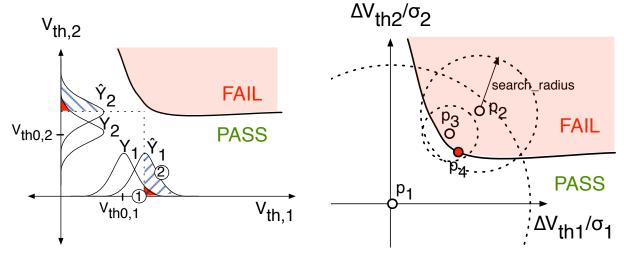

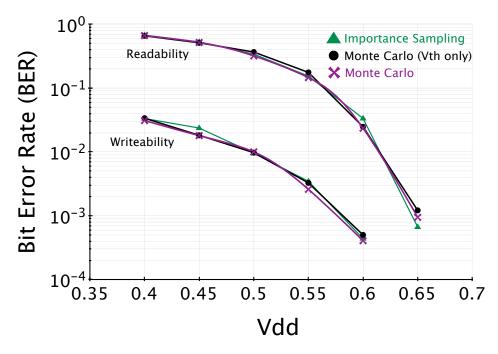

Transient simulations are required to quantify the effect of various design decisions on failure rates, because static metrics poorly match reality [4]. A Monte Carlo simulation can be used to measure the effect of variability with transient simulations, but an infeasible number of simulations would be required to find a rare failure event. Importance sampling (IS) enables enormous speedup for Monte Carlo analysis of rare events [14]. The proposed

$<sup>^{1}\</sup>mathrm{The}$  content in this section was derived from a publication in TCAS-II 2012 [33].

error modeling methodology uses importance sampling of transient simulations to predict SRAM failure rates at different voltages.

To fairly compare between different voltages, the frequency of the simulations is defined in terms of the fanout-of-4 delay (FO4), which remains constant over all voltages while appropriately adjusting actual operating frequency. For a given technology, this model translates assumptions about random variations and voltage to bitcell failure probability, as shown in Figure 2.13b.

### Analysis Methodology

Variation in transistors is modeled in the transistor-level simulation models with distributions that describe variations of various device parameters. Monte Carlo simulation samples from these distributions, and then runs the desired operating point or transient analysis. Analyzing most digital structures only requires a few thousand simulations to model the desired variable as a distribution and extract the mean and variance; for example, leakage is commonly modeled as a log-normal distribution [34]. However, for SRAM cells, the limiting device will exhibit variations in the extreme tail of the distribution at over six standard deviations from the mean, where behavior deviates from an extrapolated value and numerous Monte Carlo simulations would be needed to find a single error. The proposed analysis methodology uses importance sampling to solve this problem by only sampling from the important region of the distribution where failures are more likely, and avoiding unnecessary simulations at points which will not fail.

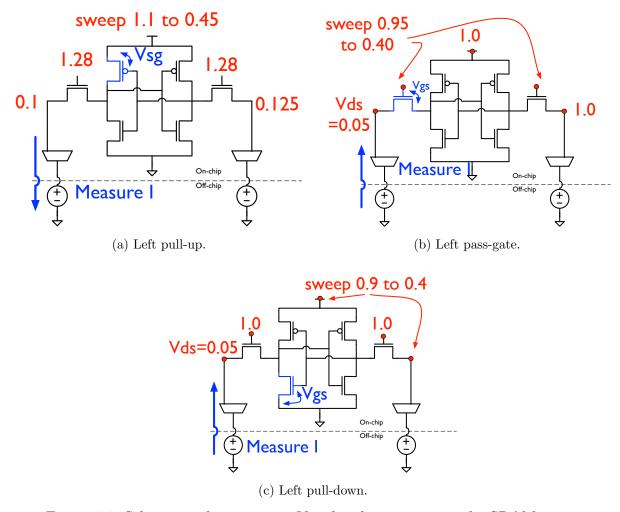

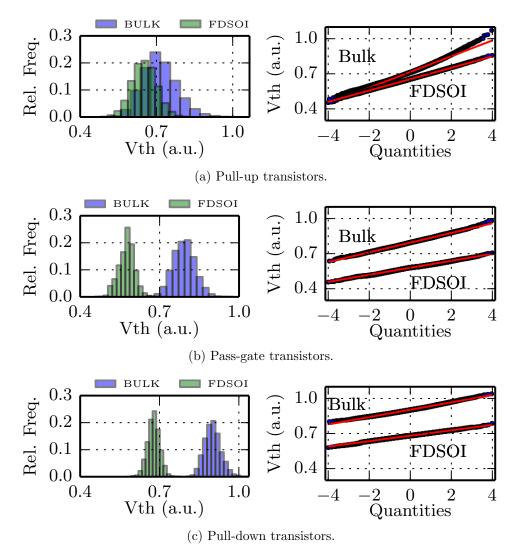

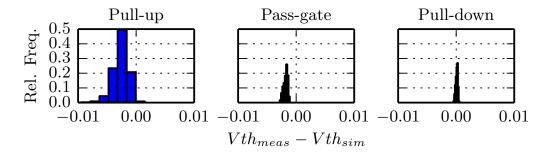

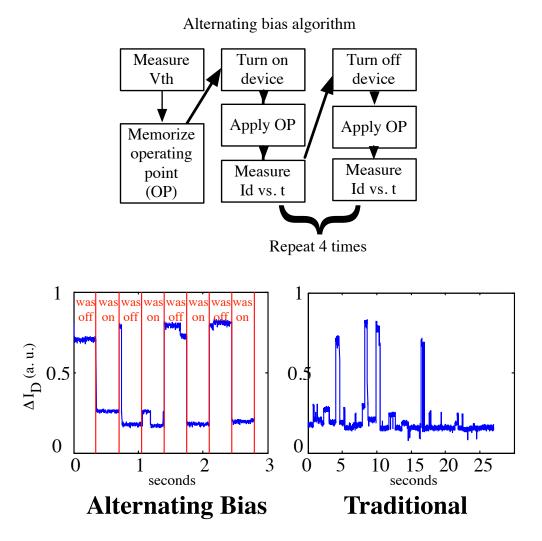

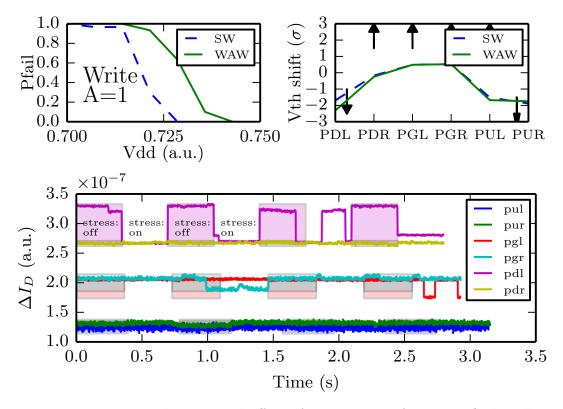

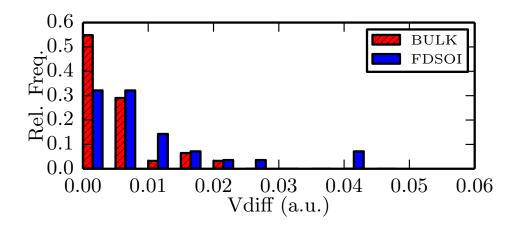

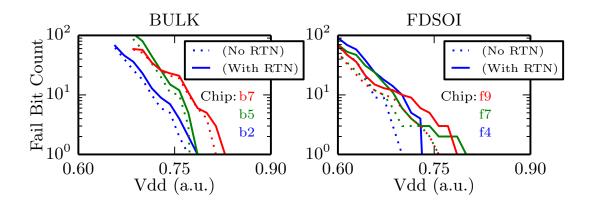

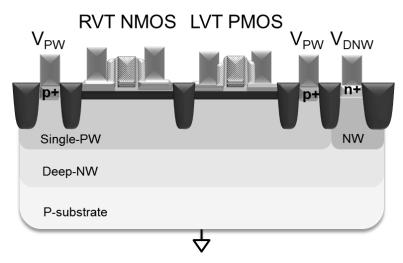

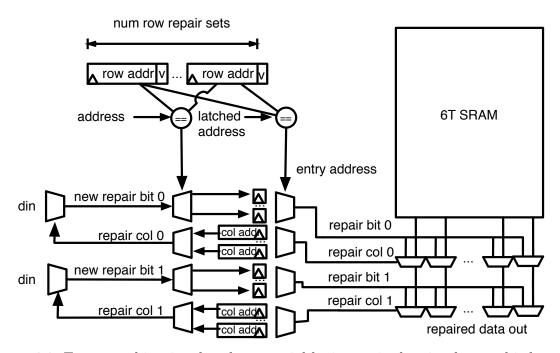

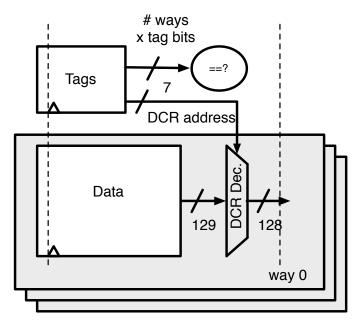

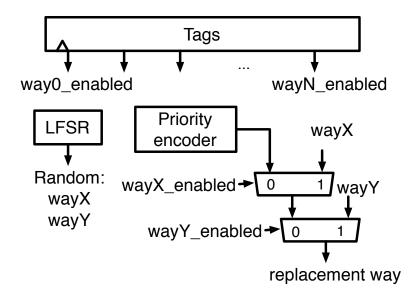

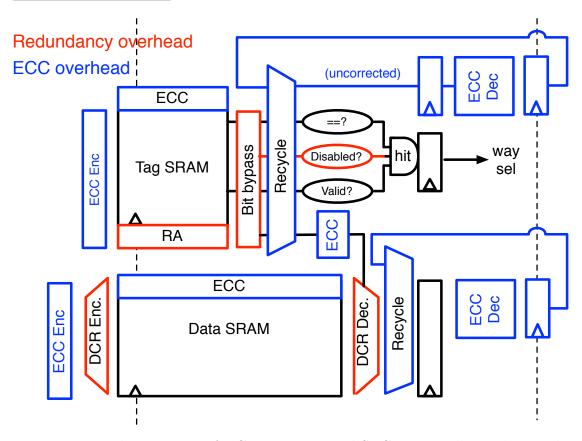

#### **Importance Sampling**