# Secure Computing using Certified Software and Trusted Hardware

Rohit Sinha

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2017-216 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2017/EECS-2017-216.html

December 14, 2017

Copyright © 2017, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Secure Computing using Certified Software and Trusted Hardware

By

### Rohit Sinha

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Sanjit A. Seshia, Chair Professor David Wagner Professor George Necula Associate Professor Antonio Montalban

|             | ion of Rohit Sinh |           | Secure    | Computing      | using | Certified | Software |

|-------------|-------------------|-----------|-----------|----------------|-------|-----------|----------|

| and Trusted | l Hardware, is a  | pproved:  |           |                |       |           |          |

|             |                   |           |           |                |       |           |          |

|             |                   |           |           |                |       |           |          |

|             |                   |           |           |                |       |           |          |

|             | Chair             |           |           |                |       | Date      |          |

|             |                   |           |           |                |       |           |          |

|             |                   |           |           |                |       | Date      |          |

|             |                   |           |           |                |       |           |          |

|             |                   |           |           |                |       | Date      |          |

|             |                   |           |           |                |       |           |          |

|             |                   |           |           |                |       | Date      |          |

|             |                   |           |           |                |       | Date      |          |

|             |                   |           | 4.01.11.2 |                |       |           |          |

|             | U                 | niversity | of Califo | rnia, Berkeley |       |           |          |

|             |                   |           |           |                |       |           |          |

### Secure Computing using Certified Software and Trusted Hardware

Copyright 2017 by Rohit Sinha

#### Abstract

#### Secure Computing using Certified Software and Trusted Hardware

by

#### Rohit Sinha

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Sanjit A. Seshia, Chair

Building applications that ensure confidentiality of sensitive data is a non-trivial task. Such applications constantly face threats due to vulnerabilities in the application's code, or infrastructure attacks due to malicious datacenter insiders and exploits in the lower computing layers (i.e. OS, hypervisor, BIOS, firmware) that the application relies upon.

This dissertation presents a novel approach for developing and verifying applications with provable confidentiality guarantees, even in the presence of such privileged adversaries. Our primary defense against infrastructure attacks is the use of trusted primitives such as Intel SGX enclaves, for isolating sensitive code and data within protected memory regions; enclaves are inaccessible to all other software running on the machine (i.e. OS, hypervisor, etc.), thus removing these large software layers from the trusted computing base (TCB). A central question addressed by this thesis is how the trusted hardware primitives can be used safely to build the trusted components of modern applications with provable guarantees. Prior experience suggests that even expert developers write unsafe programs that leak sensitive data due to programming errors and side channel attacks. To address this problem, this thesis makes contributions in formal threat models, modeling and specification of trusted platforms, and techniques to verify confidentiality properties of enclave programs.

First, this thesis formalizes adversary models, an abstract, interface-level model of trusted platforms (including Intel SGX and MIT Sanctum), and formal semantics of enclave execution. This formal framework is required for reasoning about a program's behavior in the presence of a privileged adversary. Next, this thesis presents tools and techniques for certifying confidentiality (at the binary level), a property that we decompose into the following desiderata: 1) lack of explicit leak of secrets via enclave's outputs, 2) protection against certain side-channel leaks — we only remove leaks via page-level memory access pattern, which is a new channel for privileged adversaries. For both desiderata, we develop verification tools and evaluate them on application's binaries including Map-Reduce programs from the Microsoft VC3 system, SPEC benchmarks, and several machine learning algorithms.

Dedicated to Mummy and Papa

# Contents

| Li | ist of              | Figures                                                                 | vi              |

|----|---------------------|-------------------------------------------------------------------------|-----------------|

| Li | ist of              | Tables                                                                  | ix              |

| A  | cknov               | wledgments                                                              | x               |

| 1  | Intr                | roduction                                                               | 1               |

|    | 1.1                 | Thesis Statement                                                        | 3               |

|    | 1.2                 | Thesis Contributions                                                    | 3               |

|    |                     | 1.2.1 Modeling and Verification of Enclave Programs, Platforms, and Ad- |                 |

|    |                     | versaries                                                               | 4               |

|    |                     | 1.2.2 Design and Verification Techniques for Enclave Programs           | 4               |

|    | 1.3                 | Related Work                                                            | 5               |

|    | 1.4                 | Thesis Organization                                                     | 8               |

| 2  | Bac                 | kground                                                                 | 9               |

|    | 2.1                 | Attacks from a Privileged Software Adversary                            | 9               |

|    | 2.2                 | Enclaves using Trusted Hardware Primitives                              | 10              |

|    |                     | 2.2.1 Intel SGX Enclaves                                                | 12              |

|    |                     | 2.2.2 RISC-V Sanctum Enclaves                                           | 13              |

|    | 2.3                 | Sample Applications of Enclaves                                         | 14              |

|    |                     | 2.3.1 One Time Password Service                                         | 14              |

|    |                     | 2.3.2 VC3: Trustworthy Data Analytics using SGX                         | 16              |

|    | 2.4                 | Challenges of Trusted Computing using Enclaves                          | 17              |

| Ι  | $\operatorname{Tr}$ | usted Platforms: Modeling and Verification                              | 21              |

| 3  | For                 | mal Semantics of Enclave Execution                                      | 23              |

| •  | 3.1                 | Enclave Program Representation                                          | 23              |

|    | 3.2                 | Enclave's State                                                         | $\frac{24}{24}$ |

|    | 3.3                 | Enclave's Inputs and Outputs                                            | 25              |

|    | 3.4                 | Syntax of Enclave Code                                                  | 25              |

Contents

| 3.7 Summary       3:         4 Formal Modeling of Trusted Platform       3:         4.1 The Trusted Abstract Platform       3:         4.1.1 TAP State Variables       3:         4.1.2 TAP Operations       3:         4.1.3 Enclave State, Inputs, and Outputs and the Adversary's State       3:         4.2 Formal Model of a Privileged Adversary       3:         4.2.1 Operations of a TAP Adversary       4:         4.2.2 Observations of a TAP Adversary       4:         4.3 Refinements of the TAP       4:         4.3.1 Refinement Methodology       4:         4.4 Refinement of the TAP: Intel SGX       4:         4.4.1 SGX Overview       4:         4.4.2 SGX Model       4:         4.4.3 SGX Model Refines TAP       4:         4.5 Refinement of the TAP: Sanctum Processor       4:         4.5.1 Sanctum Model       4:         4.5.2 Sanctum Model       4:         4.5.3 Sanctum Model Refines TAP       4:         4.6 Summary       4:         5 Formal Verification of Secure Remote Execution on Enclave Platforms       5:         5.1 Secure Remote Execution of Enclaves       5:         5.2 Proof Decomposition of SRE       5:         5.2.1 Integrity       5:         5.3 Soundn                                                                                                                            |    | 3.5 | Semantics of Enclave Code                                          | 27         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|--------------------------------------------------------------------|------------|

| 4 Formal Modeling of Trusted Platforms and Privileged Adversaries 4.1 The Trusted Abstract Platform 4.1.1 TAP State Variables 3.3 4.1.2 TAP Operations 4.1.3 Enclave State, Inputs, and Outputs and the Adversary's State 3.4 4.2 Formal Model of a Privileged Adversary 4.2.1 Operations of a TAP Adversary 4.2.2 Observations of a TAP Adversary 4.3.1 Refinements of the TAP 4.3.1 Refinement Methodology 4.4 Refinement of the TAP: Intel SGX 4.4.1 SGX Overview 4.4.2 SGX Model 4.4.3 SGX Model Refines TAP 4.5 Refinement of the TAP: Sanctum Processor 4.5.1 Sanctum Model 4.5.2 Sanctum Model 4.5.3 Sanctum Model Refines TAP 4.6 Summary 4.6 Summary 4.7 4.7 4.8 Secure Remote Execution of Enclaves 5.1 Secure Remote Execution of Enclave Platforms 5.1 Secure Remote Execution of Enclaves 5.2 Proof Decomposition of SRE 5.2.1 Secure Measurement 5.5.2.2 Integrity 5.3.3 Soundness of SRE Decomposition 5.4 Application of Secure Remote Execution 5.5.5 Proof of Secure Remote Execution 5.6.1 BoogiePL Model Construction 5.6.2 Verification Results 5.7 Summary  II Secure Enclaves: Design and Verification 56 Formalizing Confidentiality 66 Formalizing Confidentiality 66                                                                                                                                                     |    | 3.6 | Model of Execution within Enclaves                                 | 29         |

| 4.1.1 The Trusted Abstract Platform       33         4.1.2 TAP Operations       33         4.1.3 Enclave State, Inputs, and Outputs and the Adversary's State       33         4.2 Formal Model of a Privileged Adversary       34         4.2.1 Operations of a TAP Adversary       44         4.2.2 Observations of a TAP Adversary       44         4.3 Refinements of the TAP       44         4.3.1 Refinement Methodology       42         4.4 Refinement of the TAP: Intel SGX       44         4.4.1 SGX Overview       44         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       44         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       47         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       45         5.1 Secure Remote Execution of Enclaves       56         5.2.1 Secure Measurement       56         5.2.2 Integrity       55         5.2.3 Confidentiality       55         5.4 Application of Secure Remote Execution       56         5.5 Proof of Secure Remote Execution for TAP       56 </th <th></th> <th>3.7</th> <th>Summary</th> <th>31</th>                                                     |    | 3.7 | Summary                                                            | 31         |

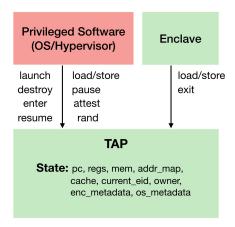

| 4.1.1 TAP State Variables       33         4.1.2 TAP Operations       33         4.1.3 Enclave State, Inputs, and Outputs and the Adversary's State       38         4.2 Formal Model of a Privileged Adversary       38         4.2.1 Operations of a TAP Adversary       44         4.2.2 Observations of a TAP Adversary       42         4.3 Refinements of the TAP       42         4.3.1 Refinement Methodology       44         4.4 Refinement of the TAP: Intel SGX       44         4.4.1 SGX Overview       44         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       47         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       51         5.1 Secure Remote Execution of Enclaves       56         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       55         5.2.2 Integrity       55         5.3 Soundness of SRE Decomposition       56         5.4 Application of Secure Remote Execution       56         5.5 Proof of Secure Remote Execution for TAP       56 <tr< th=""><th>4</th><th>For</th><th>mal Modeling of Trusted Platforms and Privileged Adversaries</th><th>32</th></tr<> | 4  | For | mal Modeling of Trusted Platforms and Privileged Adversaries       | 32         |

| 4.1.2 TAP Operations       33         4.1.3 Enclave State, Inputs, and Outputs and the Adversary's State       38         4.2 Formal Model of a Privileged Adversary       38         4.2.1 Operations of a TAP Adversary       44         4.2.2 Observations of a TAP Adversary       42         4.3 Refinements of the TAP       42         4.3.1 Refinement Methodology       44         4.4 Refinement of the TAP: Intel SGX       42         4.4.1 SGX Overview       44         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       44         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       47         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1 Secure Remote Execution of Enclaves       56         5.2 Proof Decomposition of SRE       56         5.2.1 Secure Measurement       56         5.2.2 Integrity       55         5.2.3 Confidentiality       55         5.3 Soundness of SRE Decomposition       56         5.4 Application of Secure Remote Execution for TAP       56                                                                                                                     |    | 4.1 | The Trusted Abstract Platform                                      | 33         |

| 4.1.3 Enclave State, Inputs, and Outputs and the Adversary's State       38         4.2 Formal Model of a Privileged Adversary       38         4.2.1 Operations of a TAP Adversary       46         4.2.2 Observations of a TAP Adversary       47         4.3 Refinements of the TAP       42         4.3.1 Refinement Methodology       42         4.4.2 SGX Overview       43         4.4.1 SGX Overview       44         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       44         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       47         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       49         5.1 Secure Remote Execution of Enclaves       50         5.2 Proof Decomposition of SRE       56         5.2.1 Secure Measurement       56         5.2.2 Integrity       55         5.3 Soundness of SRE Decomposition       56         5.4 Application of Secure Remote Execution       56         5.5 Proof of Secure Remote Execution for TAP       56         5.6.1 BoogiePL Model Construction       56                                                                                                           |    |     | 4.1.1 TAP State Variables                                          | 33         |

| 4.2. Formal Model of a Privileged Adversary       38         4.2.1 Operations of a TAP Adversary       40         4.2.2 Observations of a TAP Adversary       41         4.3 Refinements of the TAP       42         4.3.1 Refinement Methodology       42         4.4 Refinement of the TAP: Intel SGX       44         4.4.1 SGX Overview       42         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       46         4.5.1 Sanctum Overview       44         4.5.2 Sanctum Model       47         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1 Secure Remote Execution of Enclaves       50         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       51         5.2.2 Integrity       52         5.3 Soundness of SRE Decomposition       55         5.4 Application of Secure Remote Execution       56         5.5 Proof of Secure Remote Execution for TAP       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       56         5.6.2 Verification Results       56         5.6.2 Verific                                                                                                                            |    |     | 4.1.2 TAP Operations                                               | 35         |

| 4.2.1 Operations of a TAP Adversary       44         4.2.2 Observations of a TAP Adversary       42         4.3 Refinements of the TAP       42         4.3.1 Refinement Methodology       42         4.4.2 Refinement of the TAP: Intel SGX       44         4.4.1 SGX Overview       44         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       46         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       44         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5.1 Secure Remote Execution of Enclaves       56         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       55         5.2.2 Integrity       55         5.2.3 Confidentiality       55         5.3 Soundness of SRE Decomposition       56         5.4 Application of Secure Remote Execution       56         5.5 Proof of Secure Remote Execution for TAP       56         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       56         5.7 Summary       58                                                                                                                                                                    |    |     | 4.1.3 Enclave State, Inputs, and Outputs and the Adversary's State | 38         |

| 4.2.2 Observations of a TAP Adversary       41         4.3 Refinements of the TAP       42         4.3.1 Refinement Methodology       42         4.4 Refinement of the TAP: Intel SGX       43         4.4.1 SGX Overview       43         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       46         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       47         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1 Secure Remote Execution of Enclaves       56         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       51         5.2.2 Integrity       55         5.2.3 Confidentiality       55         5.3 Soundness of SRE Decomposition       54         5.4 Application of Secure Remote Execution for TAP       56         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       56         5.7 Summary       58         II Secure Enclaves: Design and Verification                                                                                                                                      |    | 4.2 | Formal Model of a Privileged Adversary                             | 39         |

| 4.3 Refinements of the TAP       42         4.3.1 Refinement Methodology       42         4.4 Refinement of the TAP: Intel SGX       43         4.4.1 SGX Overview       44         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       44         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       44         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       50         5.1 Secure Remote Execution of Enclaves       50         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       50         5.2.2 Integrity       55         5.2.3 Confidentiality       55         5.3 Soundness of SRE Decomposition       54         5.4 Application of Secure Remote Execution       56         5.5 Proof of Secure Remote Execution for TAP       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       56         5.7 Summary       58         II Secure Enclaves: Design and Verification       56         6 Formalizing Confidentiality                                                                                                                                  |    |     | 4.2.1 Operations of a TAP Adversary                                | 40         |

| 4.3.1 Refinement Methodology       42         4.4 Refinement of the TAP: Intel SGX       43         4.4.1 SGX Overview       44         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       46         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       47         4.5 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1 Secure Remote Execution of Enclaves       56         5.2 Proof Decomposition of SRE       56         5.2.1 Secure Measurement       56         5.2.2 Integrity       52         5.2.3 Confidentiality       56         5.4 Application of Secure Remote Execution       56         5.5 Proof of Secure Remote Execution for TAP       56         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       56         5.7 Summary       58         II Secure Enclaves: Design and Verification       58         6 Formalizing Confidentiality       61                                                                                                                                                                                                                                |    |     | 4.2.2 Observations of a TAP Adversary                              | 41         |

| 4.4 Refinement of the TAP: Intel SGX       43         4.4.1 SGX Overview       43         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       46         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       47         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1 Secure Remote Execution of Enclaves       50         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       51         5.2.2 Integrity       52         5.2.3 Confidentiality       52         5.3 Soundness of SRE Decomposition       52         5.4 Application of Secure Remote Execution       52         5.5 Proof of Secure Remote Execution for TAP       53         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       56         5.7 Summary       58         II Secure Enclaves: Design and Verification       58         6 Formalizing Confidentiality       61          6 Formalizing Confidentiali                                                                                                                                    |    | 4.3 | Refinements of the TAP                                             | 42         |

| 4.4.1 SGX Overview       43         4.4.2 SGX Model       44         4.4.3 SGX Model Refines TAP       46         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       47         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1 Secure Remote Execution of Enclaves       50         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       51         5.2.2 Integrity       52         5.2.3 Confidentiality       52         5.3 Soundness of SRE Decomposition       54         5.4 Application of Secure Remote Execution       55         5.5 Proof of Secure Remote Execution for TAP       56         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       56         5.7 Summary       58         II Secure Enclaves: Design and Verification       58         6 Formalizing Confidentiality       61                                                                                                                                                                                                                               |    |     | 4.3.1 Refinement Methodology                                       | 42         |

| 4.4.2       SGX Model       4.4.3       SGX Model Refines TAP       4.6         4.5       Refinement of the TAP: Sanctum Processor       4.6       4.5.1       Sanctum Overview       4.7       4.5.2       Sanctum Model       4.6       4.6       4.5.3       Sanctum Model Refines TAP       4.6       5.2       Summary       4.6       5.2       Summary       4.6       5.2       Formal Verification of Secure Remote Execution on Enclave Platforms       4.6       5.1       Secure Remote Execution on Enclave Platforms       4.6       5.2       Formal Verification of SRE       5.6       5.2       Formal Verification of Enclaves       5.6       5.6       5.2       Formal Verification of SRE       5.6       5.2       Formal Verification of SRE       5.6       5.6       5.2       Formal Verification of SRE       5.6       5.6       5.2       Formal Verification of Secure Remote Execution       5.6       5.2       Formal Verification Results       5.6       5.6       Verification Results       5.6       5.6       7.2       Verification Results       5.6       5.6       7.2       Verification Results       5.6       5.7       5.2       5.2       7.2       7.2       7.2       7.2       7.2       7.2       7.2       7.2       7.2       7.2       7.2       7.2       7.2                           |    | 4.4 | Refinement of the TAP: Intel SGX                                   | 43         |

| 4.4.3 SGX Model Refines TAP       46         4.5 Refinement of the TAP: Sanctum Processor       46         4.5.1 Sanctum Overview       47         4.5.2 Sanctum Model       47         4.5.3 Sanctum Model Refines TAP       47         4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       49         5.1 Secure Remote Execution of Enclaves       50         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       51         5.2.2 Integrity       52         5.2.3 Confidentiality       53         5.3 Soundness of SRE Decomposition       54         5.4 Application of Secure Remote Execution       54         5.5 Proof of Secure Remote Execution       54         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       56         5.7 Summary       58         II Secure Enclaves: Design and Verification       59         6 Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                            |    |     | 4.4.1 SGX Overview                                                 | 43         |

| 4.5       Refinement of the TAP: Sanctum Processor       46         4.5.1       Sanctum Overview       47         4.5.2       Sanctum Model       47         4.5.3       Sanctum Model Refines TAP       47         4.6       Summary       48         5       Formal Verification of Secure Remote Execution on Enclave Platforms       49         5.1       Secure Remote Execution of Enclaves       50         5.2       Proof Decomposition of SRE       50         5.2.1       Secure Measurement       51         5.2.2       Integrity       52         5.2.3       Confidentiality       52         5.3       Soundness of SRE Decomposition       54         5.4       Application of Secure Remote Execution       54         5.5       Proof of Secure Remote Execution for TAP       53         5.6       Verification Results       56         5.6.1       BoogiePL Model Construction       56         5.6.2       Verification Results       58         5.7       Summary       58         II       Secure Enclaves: Design and Verification       59         6       Formalizing Confidentiality       61                                                                                                                                                                                                                         |    |     | 4.4.2 SGX Model                                                    | 44         |

| 4.5.1       Sanctum Overview       47         4.5.2       Sanctum Model       47         4.5.3       Sanctum Model Refines TAP       47         4.6       Summary       48         5       Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1       Secure Remote Execution of Enclaves       56         5.2       Proof Decomposition of SRE       56         5.2.1       Secure Measurement       51         5.2.2       Integrity       52         5.2.3       Confidentiality       52         5.3       Soundness of SRE Decomposition       54         5.4       Application of Secure Remote Execution       54         5.5       Proof of Secure Remote Execution for TAP       56         5.6       Verification Results       56         5.6.1       BoogiePL Model Construction       56         5.7       Summary       58         II       Secure Enclaves: Design and Verification       59         6       Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                                                               |    |     | 4.4.3 SGX Model Refines TAP                                        | 46         |

| 4.5.2       Sanctum Model       47         4.5.3       Sanctum Model Refines TAP       47         4.6       Summary       48         5       Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1       Secure Remote Execution of Enclaves       50         5.2       Proof Decomposition of SRE       50         5.2.1       Secure Measurement       51         5.2.2       Integrity       52         5.2.3       Confidentiality       53         5.3       Soundness of SRE Decomposition       54         5.4       Application of Secure Remote Execution       54         5.5       Proof of Secure Remote Execution for TAP       53         5.6       Verification Results       56         5.6.1       BoogiePL Model Construction       56         5.6.2       Verification Results       58         5.7       Summary       58         II       Secure Enclaves: Design and Verification       59         6       Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                                                           |    | 4.5 | Refinement of the TAP: Sanctum Processor                           | 46         |

| 4.5.3       Sanctum Model Refines TAP       47         4.6       Summary       48         5       Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1       Secure Remote Execution of Enclaves       50         5.2       Proof Decomposition of SRE       50         5.2.1       Secure Measurement       51         5.2.2       Integrity       52         5.2.3       Confidentiality       53         5.3       Soundness of SRE Decomposition       54         5.4       Application of Secure Remote Execution       54         5.5       Proof of Secure Remote Execution for TAP       53         5.6       Verification Results       56         5.6.1       BoogiePL Model Construction       56         5.6.2       Verification Results       58         5.7       Summary       58         II       Secure Enclaves: Design and Verification       59         6       Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                                                                                                      |    |     | 4.5.1 Sanctum Overview                                             | 47         |

| 4.6 Summary       48         5 Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1 Secure Remote Execution of Enclaves       50         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       51         5.2.2 Integrity       52         5.2.3 Confidentiality       52         5.3 Soundness of SRE Decomposition       54         5.4 Application of Secure Remote Execution       54         5.5 Proof of Secure Remote Execution for TAP       55         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       58         5.7 Summary       58         II Secure Enclaves: Design and Verification       59         6 Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |     | 4.5.2 Sanctum Model                                                | 47         |

| 5 Formal Verification of Secure Remote Execution on Enclave Platforms       48         5.1 Secure Remote Execution of Enclaves       50         5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       51         5.2.2 Integrity       52         5.2.3 Confidentiality       52         5.3 Soundness of SRE Decomposition       54         5.4 Application of Secure Remote Execution       54         5.5 Proof of Secure Remote Execution for TAP       55         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       58         5.7 Summary       58         II Secure Enclaves: Design and Verification       59         6 Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |     | 4.5.3 Sanctum Model Refines TAP                                    | 47         |

| 5.1       Secure Remote Execution of Enclaves       56         5.2       Proof Decomposition of SRE       50         5.2.1       Secure Measurement       51         5.2.2       Integrity       52         5.2.3       Confidentiality       53         5.3       Soundness of SRE Decomposition       54         5.4       Application of Secure Remote Execution       54         5.5       Proof of Secure Remote Execution for TAP       55         5.6       Verification Results       56         5.6.1       BoogiePL Model Construction       56         5.6.2       Verification Results       58         5.7       Summary       58         II       Secure Enclaves: Design and Verification       59         6       Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 4.6 | Summary                                                            | 48         |

| 5.1       Secure Remote Execution of Enclaves       56         5.2       Proof Decomposition of SRE       50         5.2.1       Secure Measurement       51         5.2.2       Integrity       52         5.2.3       Confidentiality       53         5.3       Soundness of SRE Decomposition       54         5.4       Application of Secure Remote Execution       54         5.5       Proof of Secure Remote Execution for TAP       55         5.6       Verification Results       56         5.6.1       BoogiePL Model Construction       56         5.6.2       Verification Results       58         5.7       Summary       58         II       Secure Enclaves: Design and Verification       59         6       Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5  | For | mal Verification of Secure Remote Execution on Enclave Platforms   | 49         |

| 5.2 Proof Decomposition of SRE       50         5.2.1 Secure Measurement       51         5.2.2 Integrity       52         5.2.3 Confidentiality       52         5.3 Soundness of SRE Decomposition       54         5.4 Application of Secure Remote Execution       54         5.5 Proof of Secure Remote Execution for TAP       55         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       58         5.7 Summary       58         II Secure Enclaves: Design and Verification       59         6 Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |     |                                                                    |            |

| 5.2.1 Secure Measurement       51         5.2.2 Integrity       52         5.2.3 Confidentiality       53         5.3 Soundness of SRE Decomposition       54         5.4 Application of Secure Remote Execution       54         5.5 Proof of Secure Remote Execution for TAP       55         5.6 Verification Results       56         5.6.1 BoogiePL Model Construction       56         5.6.2 Verification Results       58         5.7 Summary       58         II Secure Enclaves: Design and Verification       59         6 Formalizing Confidentiality       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |     |                                                                    |            |

| 5.2.2 Integrity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |     |                                                                    |            |

| 5.2.3 Confidentiality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |     |                                                                    | 52         |

| 5.3 Soundness of SRE Decomposition 54 5.4 Application of Secure Remote Execution 54 5.5 Proof of Secure Remote Execution for TAP 55 5.6 Verification Results 56 5.6.1 BoogiePL Model Construction 56 5.6.2 Verification Results 58 5.7 Summary 58  II Secure Enclaves: Design and Verification 59 6 Formalizing Confidentiality 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |     |                                                                    |            |

| 5.4 Application of Secure Remote Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 5.3 | · · · · · · · · · · · · · · · · · · ·                              | 54         |

| 5.5 Proof of Secure Remote Execution for TAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 5.4 |                                                                    |            |

| 5.6 Verification Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 5.5 |                                                                    |            |

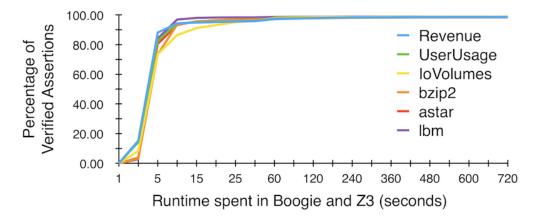

| 5.6.1 BoogiePL Model Construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 5.6 |                                                                    | 56         |

| 5.6.2 Verification Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |     |                                                                    | 56         |

| 5.7 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |     |                                                                    |            |

| II Secure Enclaves: Design and Verification  6 Formalizing Confidentiality  61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 5.7 |                                                                    | 58         |

| 6 Formalizing Confidentiality 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | •   |                                                                    | -          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | II | Se  | ecure Enclaves: Design and Verification                            | <b>5</b> 9 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6  | For | malizing Confidentiality                                           | 61         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | J  |     |                                                                    | 61         |

CONTENTS

|   | 6.2<br>6.3<br>6.4 | Confidentiality                                                      | 62<br>64<br>65 |

|---|-------------------|----------------------------------------------------------------------|----------------|

| 7 | Moa               | at: Verifying Confidentiality of Enclave's Outputs                   | 66             |

|   | 7.1               | Overview of Moat                                                     | 67             |

|   |                   | 7.1.1 Declassification                                               | 72             |

|   |                   | 7.1.2 Assumptions and Limitations                                    | 73             |

|   | 7.2               | Proving Confidentiality                                              | 74             |

|   | 7.3               | Evaluation                                                           | 79             |

|   |                   | 7.3.1 Optimizations                                                  | 79             |

|   |                   | 7.3.2 Case Studies                                                   | 79             |

|   | 7.4               | Related Work                                                         | 82             |

|   | 7.5               | Summary                                                              | 82             |

| 8 | /Co               | ONFIDENTIAL: Scalably Verifying Confidentiality of Enclave's Outputs | 84             |

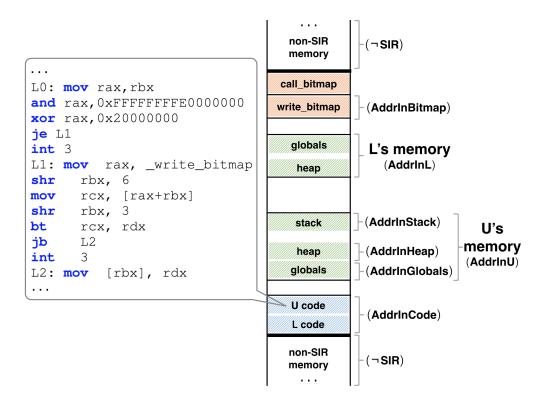

|   | 8.1               | Overview of /Confidential                                            | 86             |

|   |                   | 8.1.1 Verifying confidentiality                                      | 87             |

|   |                   | 8.1.2 Restricted interface                                           | 88             |

|   |                   | 8.1.3 Checking IRC                                                   | 89             |

|   | 8.2               | Decomposing Proof of Confidentiality                                 | 91             |

|   |                   | 8.2.1 WCFI-RW Property of $U_M$                                      | 92             |

|   |                   | 8.2.2 Correctness of L's API Implementation                          | 95             |

|   |                   | 8.2.3 Soundness                                                      | 97             |

|   | 8.3               | Verifying WCFI-RW                                                    | 97             |

|   |                   | 8.3.1 Runtime Checks                                                 | 98             |

|   |                   | 8.3.2 Static Verifier for WCFI-RW                                    | 99             |

|   |                   | 1                                                                    | 103            |

|   |                   |                                                                      | 103            |

|   | 8.4               | 1                                                                    | 104            |

|   | 8.5               |                                                                      | 106            |

|   | 8.6               | Related Work                                                         | 109            |

|   | 8.7               | Summary                                                              | 110            |

| 9 | Ens               | suring Page Access Obliviousness                                     | 111            |

|   | 9.1               |                                                                      | 112            |

|   |                   | 9.1.1 Threat Model                                                   | 113            |

|   |                   |                                                                      | 114            |

|   |                   |                                                                      | 115            |

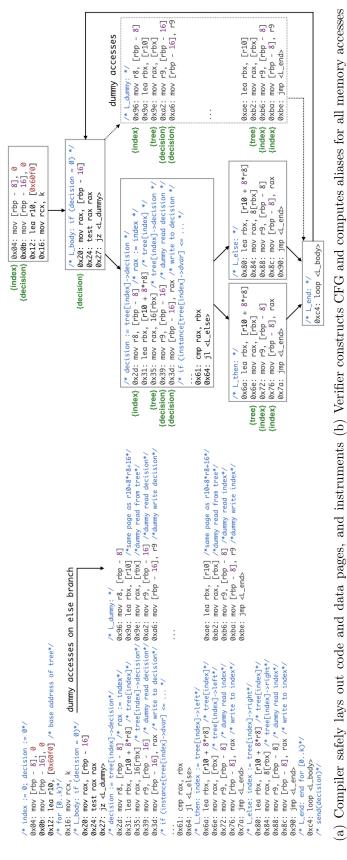

|   | 9.2               |                                                                      | 118            |

|   |                   | 9.2.1 Obliviating Data Accesses                                      | 118            |

|   |                   |                                                                      | 121            |

CONTENTS

|              |       | 9.2.3    | Obliviating Code Accesses                    | 122                                |

|--------------|-------|----------|----------------------------------------------|------------------------------------|

|              |       | 9.2.4    | The Enclanguage                              |                                    |

|              |       | 9.2.5    | Type Checking of Encland programs            |                                    |

|              |       | 9.2.6    | Compiling Encland to Typed Assembly Language | 127                                |

|              |       | 9.2.7    |                                              | 128                                |

|              | 9.3   | Verifyi  | ng PAO                                       | 129                                |

|              | 9.4   |          |                                              | 129                                |

|              | 9.5   | Relate   | d Work                                       | 131                                |

|              | 9.6   | Summ     | ary                                          | 132                                |

|              | ~     |          |                                              |                                    |

| 10           |       |          |                                              | 133                                |

|              |       |          | 9                                            | 133                                |

|              | 10.2  | Future   | Work                                         | 134                                |

| Bi           | bliog | raphy    | 1                                            | 136                                |

| A            | TAF   | P Mod    | el 1                                         | 147                                |

| В            | Mod   | del of l | Intel SGX                                    | 152                                |

| $\mathbf{C}$ | Mod   | del of S | Sanctum                                      | 169                                |

| D            | Pro   | of of T  | Theorem 3 and Theorem 4                      | 178                                |

| _            |       |          |                                              | 178                                |

|              |       |          |                                              | 179                                |

|              |       |          |                                              | $179 \\ 179$                       |

|              | ப.ப   | 1 1001   |                                              | $\mathbf{I} \mathbf{I} \mathbf{J}$ |

# List of Figures

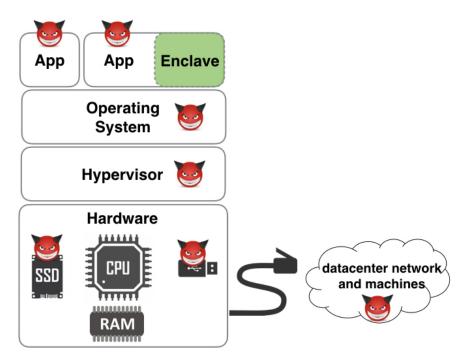

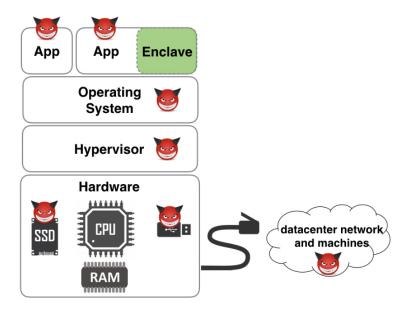

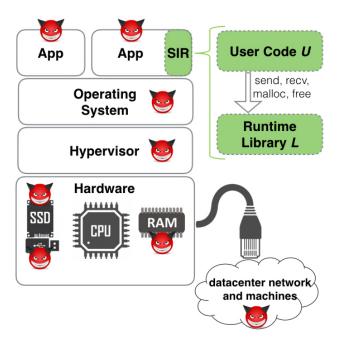

| 2.1        | Threat Model: The adversary controls all privileged software layers on the plat-                                                                  |     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | form, and all hardware units except the CPU and memory. The enclave is the                                                                        |     |

|            | only trusted software component                                                                                                                   | 10  |

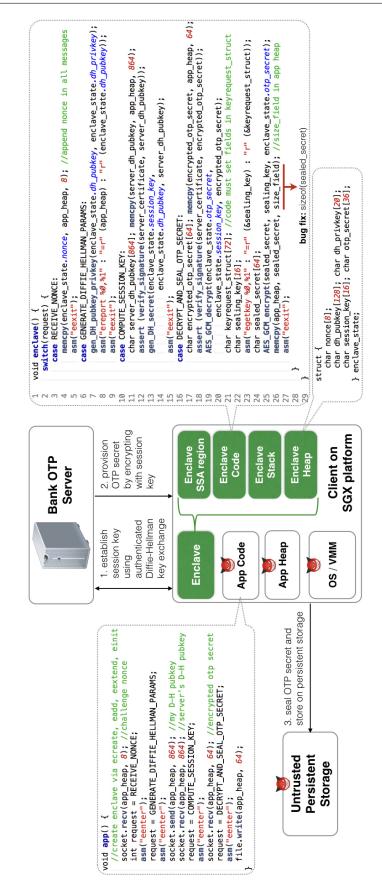

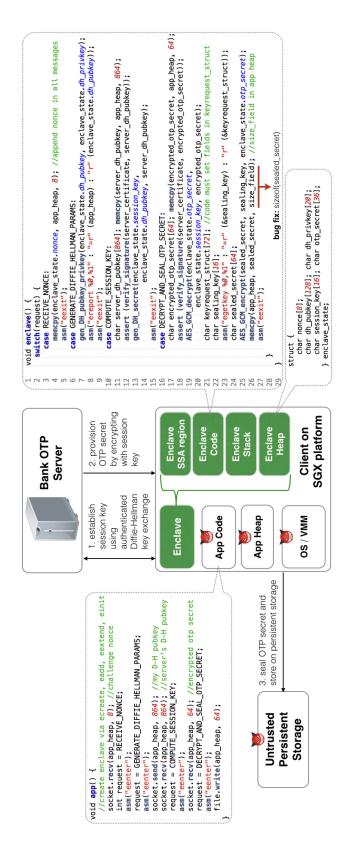

| 2.2        | Running OTP Example. The enclave performs trusted cryptographic operations,                                                                       |     |

|            | and the host application performs untrusted tasks such as UI handling and net-                                                                    |     |

|            | work communications with the OTP server.                                                                                                          | 15  |

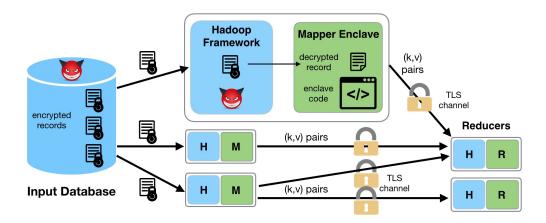

| 2.3        | Map-Reduce computation in VC3. The Hadoop layer only accesses encrypted                                                                           |     |

|            | data, and communication between enclaves is encrypted via TLS. This figure is                                                                     |     |

| a .        | derived from Figure 3 of [107]                                                                                                                    | 17  |

| 2.4        | Executed within an enclave, this reducer method computes on sensitive cleartext                                                                   | 4.0 |

| ~ <b>~</b> | data                                                                                                                                              | 18  |

| 2.5        | Explicit leaks from memory safety errors (left) and implicit leaks from side chan-                                                                | 1.0 |

|            | nels (right)                                                                                                                                      | 19  |

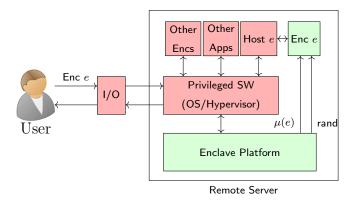

| 3.1        | Outsourced Execution of Enclave Program                                                                                                           | 24  |

| 3.2        | Syntax of Enclave code.                                                                                                                           | 26  |

| 3.3        | Operational semantics of $i \in Instr$ : $(\sigma, \sigma') \in \leadsto \inf \langle i, \sigma \rangle \Downarrow \sigma'$ and $instr(\sigma) =$ |     |

|            | i, where $instr(\sigma)$ is the instruction to be executed next when the platform is                                                              |     |

|            | in state $\sigma$ (computed using values of vmem and pc in $\sigma$ ). $\sigma[x \mapsto y]$ denotes                                              |     |

|            | a state that is identical to $\sigma$ , except variable x evaluates to y. The memory                                                              |     |

|            | update expression $vmem[x := y]$ returns a new memory that is equivalent to $vmem$ ,                                                              |     |

|            | except for index x — multibyte-sized accesses follow the processor's endianness                                                                   |     |

|            | semantics. $next(e)$ is the address of the subsequent instruction in vmem after                                                                   |     |

|            | decoding the instruction starting at address e                                                                                                    | 28  |

|            | decoding the instruction starting at address of the tree tree tree tree tree tree tree                                                            |     |

| 4.1        | TAP: state and operations                                                                                                                         | 33  |

| 4.2        | Conditions for the success of launch. Note that $m[v]_{PA}$ refers to physical address                                                            |     |

|            | that virtual address $v$ points to under the mapping $m$                                                                                          | 37  |

| 4.3        | Threat Model: The adversary controls the OS, hypervisor, all hardware except                                                                      |     |

|            | the CPU and RAM, and other machines on the network. The enclave is the only                                                                       |     |

|            | trusted software component                                                                                                                        | 39  |

| 4.4        | Illustration of Stuttering Simulation                                                                                                             | 43  |

List of Figures vii

| 4.5               | Models for ecreate, load, and eexit instructions                                                                                                                                                                                                          | 44             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 5.1<br>5.2        | Integrity property                                                                                                                                                                                                                                        | 52<br>53       |

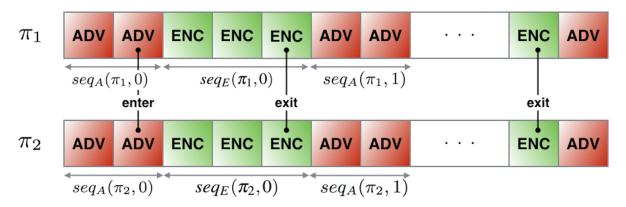

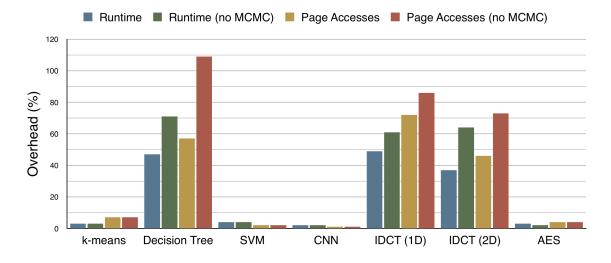

| 6.1               | Illustration of confidentiality definition. The untrusted platform transfers control to the enclave by invoking enter, and enclave transfers control back by invoking exit.                                                                               | 63             |