## Design of Integrated Full-Duplex Wireless Transceivers

Sameet Ramakrishnan Borivoje Nikolic

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2017-24 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2017/EECS-2017-24.html

May 1, 2017

Copyright © 2017, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Design of Integrated Full-Duplex Wireless Transceivers

by

Sameet Ramakrishnan

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolic, Chair Professor Ali Niknejad Professor Paul Wright

Fall 2016

## Design of Integrated Full-Duplex Wireless Transceivers

Copyright 2016 by Sameet Ramakrishnan

#### Abstract

#### Design of Integrated Full-Duplex Wireless Transceivers

by

Sameet Ramakrishnan

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Borivoje Nikolic, Chair

Demand for mobile data traffic is projected to exceed 30 exabytes per month in 2020, representing an over 100x increase since 2010. Prior generations of cellular deployments have serviced increased demand largely through use of more bandwidth - from 200KHz in GSM, to now 100MHz in CA-LTE. This method of scaling is closed, as low frequency spectrum has crowded and saturated. A proposed technique to enhance spectrum access in 5G deployments is agile full-duplex (FD) transceivers, which can transmit and receive at overlapped frequencies, or tune to arbitrarily spaced transmit/receive(TX/RX) frequency division duplexed (FDD) channels, to make use of available spectrum. The key problem in such a system is mitigating the interference the system's own transmitter creates for its receiver during simultaneous operation. Current implementations mitigate TX to RX interference at the antenna interface using off-chip, fixed-frequency duplexers, limiting a device's spectrum access to a handful of pre-defined, widely separated TX/RX band combinations. Accordingly, a universal mobile device tunable across global carrier band combinations does not exist.

This work develops a transceiver architecture enabling simultaneous transmission and reception on a single single shared antenna, over a wide frequency tuning range, for FD/FDD systems. The architecture is enabled by an active TX replica which cancels interference at the RX input, a highly linear passive-mixer first receiver design based on class-AB transconductors which operates linearly in the presence of residual TX interference, and digital adaptation techniques which match the interference over time-varying operating conditions. Analysis is presented for the system's fundamental performance bounds in power and sensitivity, leading to noise mitigation techniques which minimize receiver degradation in the presence of the cancellation circuits. The analysis is validated by two chip prototypes, which demonstrate over >50dB cancellation of a +16dBm peak 20MHz TX signal, from 1GHz to 2GHz, up to an antenna VSWR of 5:1. This work demonstrates the potential for a fully integrated, frequency-tunable FD/FDD transceiver system, which could ultimately double existing mobile network capacity, and enable a universal duplexer-less radio. Dedication

To Mom and Dad.

# Contents

| Co            | onten | lts                                                                                                             | ii   |

|---------------|-------|-----------------------------------------------------------------------------------------------------------------|------|

| Li            | st of | Figures                                                                                                         | iv   |

| $\mathbf{Li}$ | st of | Tables                                                                                                          | viii |

| 1             | Intr  | oduction                                                                                                        | 1    |

|               | 1.1   | Motivation                                                                                                      | 1    |

|               |       | 1.1.1 Boosted Spectral Efficiency                                                                               | 3    |

|               |       | 1.1.2 Universal Radio $\ldots$ | 3    |

|               |       | 1.1.3 Simplified Spectral Planning                                                                              | 4    |

|               |       | 1.1.4 Backhaul and Relaying                                                                                     | 6    |

|               |       | 1.1.5 Control Planes                                                                                            | 6    |

|               | 1.2   | Duplexer Specifications                                                                                         | 6    |

|               | 1.3   | Integrated Self Interference Cancellation: Prior Work                                                           | 10   |

|               |       | 1.3.1 Transformer Hybrids                                                                                       | 10   |

|               |       | 1.3.2 Active Cancellation                                                                                       | 12   |

|               | 1.4   | Wideband Transceivers                                                                                           | 15   |

|               | 1.5   | Research Goals, Scope, and Organization                                                                         | 16   |

| <b>2</b>      | Ana   | lysis of the Active Cancellation System                                                                         | 18   |

|               | 2.1   | Description of Proposed System                                                                                  | 18   |

|               | 2.2   | Replica Power Consumption                                                                                       | 23   |

|               | 2.3   | Thermal Noise                                                                                                   | 25   |

|               |       | 2.3.1 TX Thermal Noise                                                                                          | 25   |

|               |       | 2.3.2 Replica DAC Thermal Noise                                                                                 | 26   |

|               | 2.4   | Phase Noise                                                                                                     | 34   |

|               |       | 2.4.1 Background                                                                                                | 34   |

|               |       | 2.4.2 A Quick Note on Simulation                                                                                | 38   |

|               |       | 2.4.3 Impact of Correlated Phase Noise                                                                          | 38   |

|               |       | 2.4.4 Impact of Uncorrelated Phase Noise                                                                        | 43   |

|               |       | 2.4.5 Phase Noise of an Inverter Chain                                                                          | 44   |

|    | 2.5<br>2.6<br>2.7 | 2.4.6       Sizing Under Constrained Phase Noise | 47<br>49<br>49<br>51 |

|----|-------------------|--------------------------------------------------|----------------------|

| 3  | Full              | y Integrated FDD Transceiver Implementation      | 53                   |

|    | 3.1               | Switched Capacitor Power Amplifier               | 53                   |

|    |                   | 3.1.1 Topology Motivation                        | 53                   |

|    |                   | 3.1.2 SC PA Operation Principle                  | 53                   |

|    |                   | 3.1.3 Cartesian Implementation                   | 55                   |

|    |                   | 3.1.4 Sizing                                     | 62                   |

|    | 3.2               | RX Design                                        | 65                   |

|    | 3.3               | Cancellation DAC                                 | 69                   |

|    | 3.4               | Test Setup                                       | 69                   |

|    |                   | 3.4.1 PCB Design                                 | 71                   |

|    |                   | 3.4.2 Test Equipment                             | 73                   |

|    | 3.5               | Measurements                                     | 74                   |

|    |                   | 3.5.1 RX                                         | 74                   |

|    |                   | 3.5.2 TX                                         | 76                   |

|    |                   | 3.5.3 System                                     | 77                   |

|    |                   | 3.5.4 Antenna Mismatch                           | 83                   |

|    |                   | 3.5.5 Phase Noise Measurements                   | 85                   |

| 4  | Rec               | eiver Design for FD/FDD Systems                  | 93                   |

| -  | 4.1               | Design Motivation                                | 93                   |

|    | 4.2               | Passive Mixer First Receiver                     | 96                   |

|    |                   | 4.2.1 Input Matching                             | 96                   |

|    |                   | 4.2.2 Noise Analysis                             | 100                  |

|    | 4.3               | First Stage RX Amplifier Design                  | 106                  |

|    | 4.4               | RX Second Stage Biquad                           | 116                  |

|    | 4.5               | Chip Implementation                              | 117                  |

|    | 4.6               | Measurements                                     | 120                  |

| 5  | Car               | nclusion                                         | 129                  |

| J  |                   | Thesis Contributions                             |                      |

|    | $5.1 \\ 5.2$      | I nesis Contributions                            | 129<br>120           |

|    | J.2               |                                                  | 130                  |

| Bi | bliog             | graphy                                           | 132                  |

# List of Figures

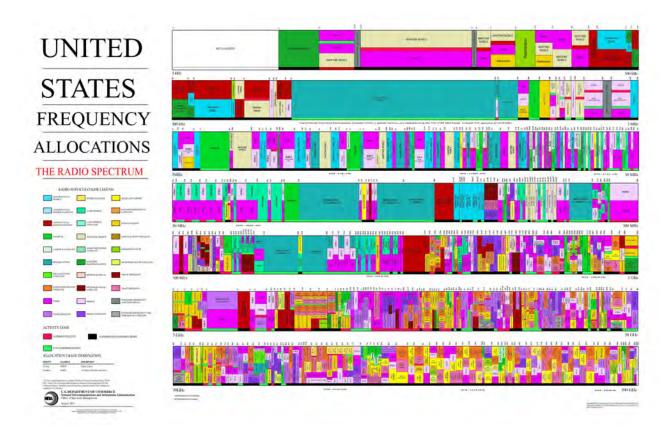

| 1.1  | Frequency allocation in the United States.                                          | 2  |

|------|-------------------------------------------------------------------------------------|----|

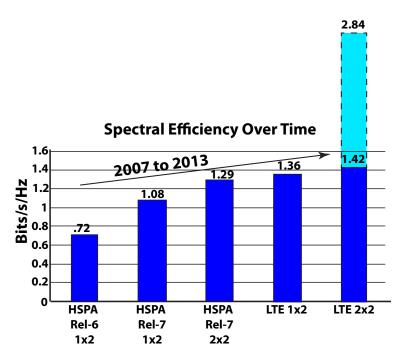

| 1.2  | Spectral efficiency of various standards from 2007 to 2013 - full duplex represents |    |

|      | an opportunity to double.                                                           | 3  |

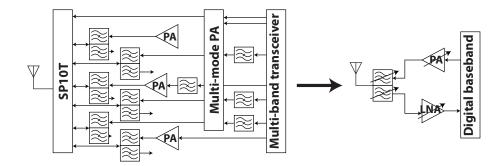

| 1.3  | Self-interference cancellation for universal radio.                                 | 4  |

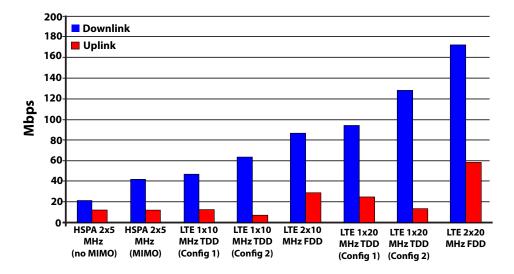

| 1.4  | Comparison of TDD and FDD implementations.                                          | 5  |

| 1.5  | Duplexer functionality.                                                             | 7  |

| 1.6  | Wireless hybrid as an integrated duplexer.                                          | 10 |

| 1.7  | Distributed Tline duplexer.                                                         | 14 |

| 1.8  | Limitations of prior work.                                                          | 14 |

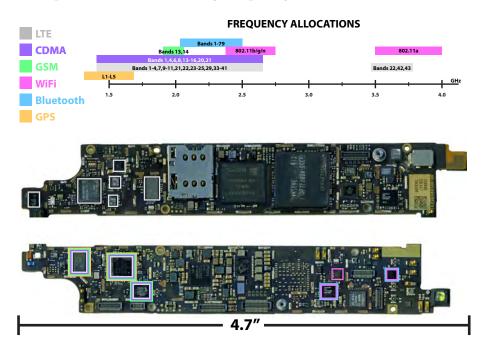

| 1.9  | Frequency spectrum (top) and board components (bottom) for various standards.       | 16 |

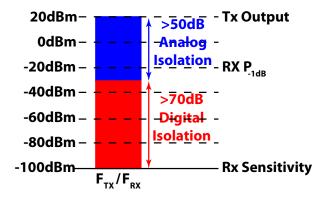

| 1.10 | Requirements for two stage (analog/digital) cancellation                            | 17 |

| 0.1  |                                                                                     | 10 |

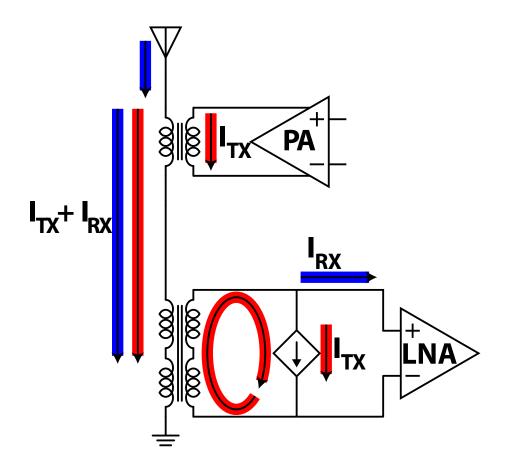

| 2.1  | Simultaneous TX/RX interface.                                                       | 19 |

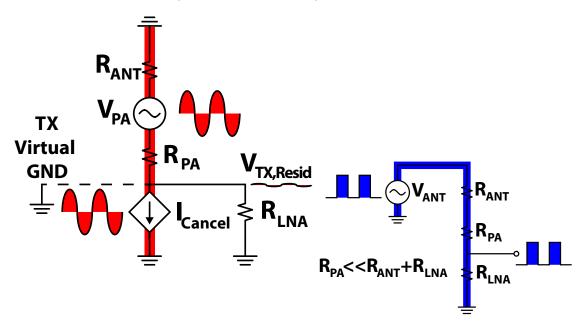

| 2.2  | Models for TX operation (left) and RX operation (right)                             | 20 |

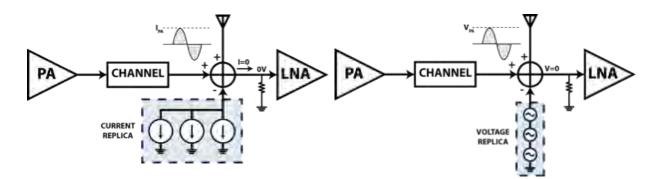

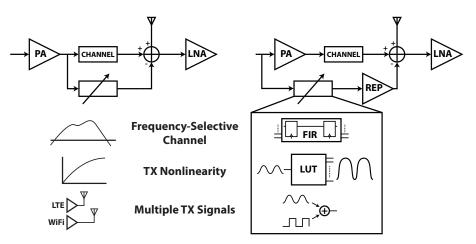

| 2.3  | Current mode (left) and voltage mode (right) cancellation.                          | 22 |

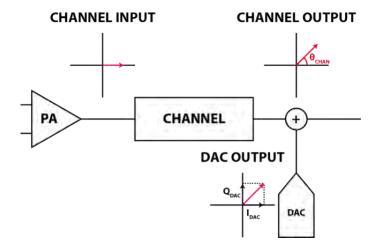

| 2.4  | Digital feedforward adaptation possibilities.                                       | 22 |

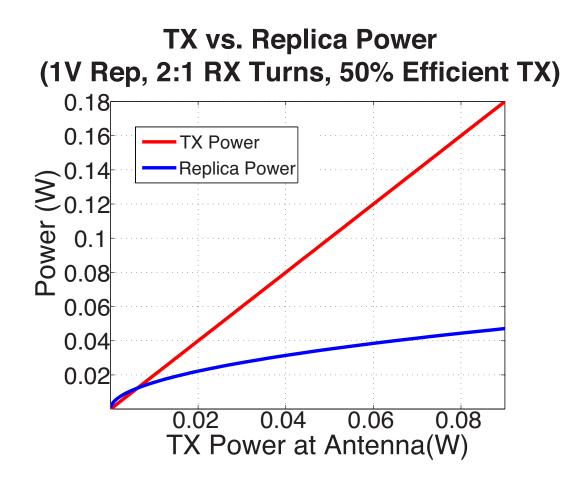

| 2.5  | TX vs. replica power consumption.                                                   | 23 |

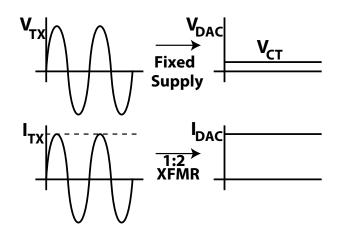

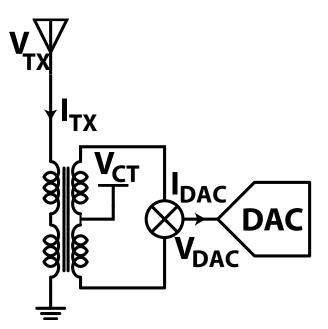

| 2.6  | DAC's current and voltage.                                                          | 24 |

| 2.7  | TX vs. replica power consumption.                                                   | 26 |

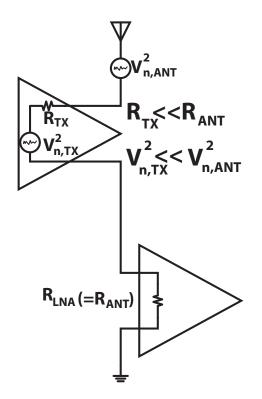

| 2.8  | Noise model for the TX.                                                             | 27 |

| 2.9  | Model for DAC noise analysis.                                                       | 28 |

| 2.10 | Reduction of the high frequency noise via degeneration                              | 28 |

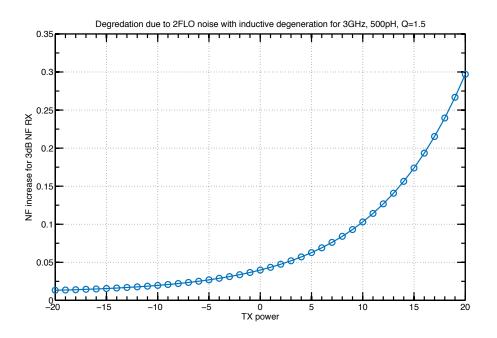

|      | Contribution of DAC $2F_{LO}$ noise with inductive degeneration.                    | 30 |

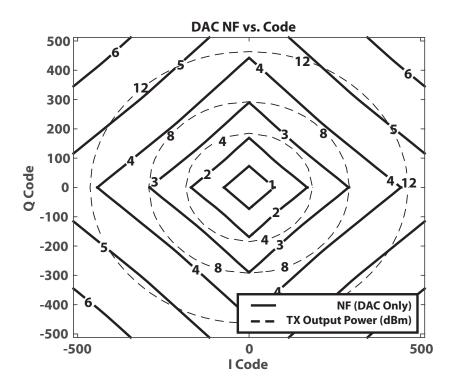

|      | DAC thermal noise contour vs. TX Power                                              | 31 |

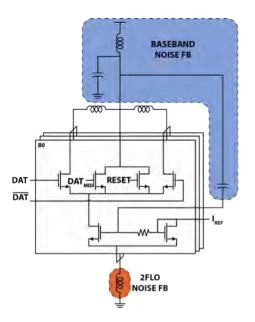

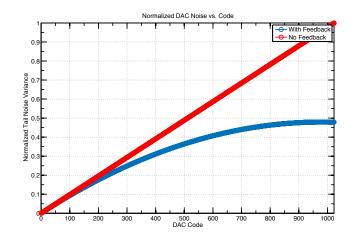

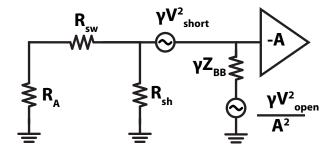

|      | Baseband noise feedback loop.                                                       | 32 |

|      | Model for analysis of DAC noise feedback.                                           | 33 |

|      | Reduction of the low frequency tail noise via feedback.                             | 34 |

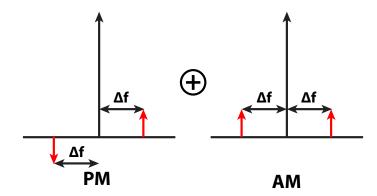

|      | PM and AM noise components.                                                         | 35 |

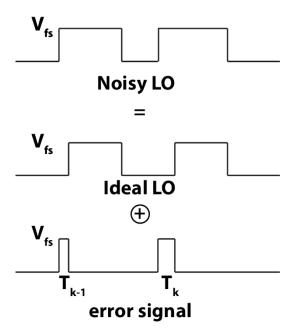

|      | Phase noise as voltage pulses                                                       | 36 |

|      | Phase noise through digital and analog paths.                                       | 39 |

|      | Phase noise through the LO divider.                                                 | 40 |

| 2.20 | Clock divider uncorrelated phase noise                                              | 41 |

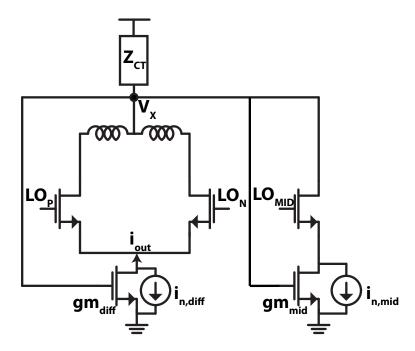

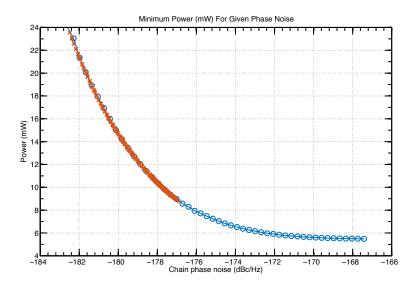

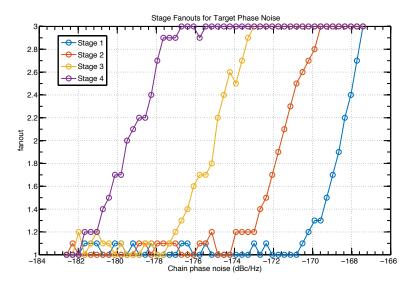

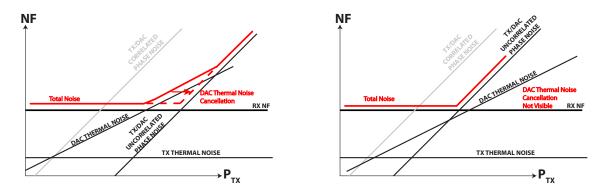

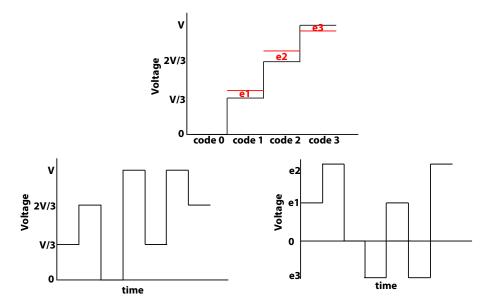

| <ol> <li>2.22</li> <li>2.23</li> <li>2.24</li> <li>2.25</li> </ol> | Inverter noise model.44Noise at the inverter edge crossing.45Minimum power for a length of 5 digital inverters.48Per stage fanouts to achieve minimum power for target phase noise.48Receiver noise scaling vs.TX power. Right - DAC thermal noise appears atmoderate powers.Left - Uncorrelated phase noise appears first.49Top: DAC code vs voltage characteristic, Left: data sequence Right: quantization51 |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

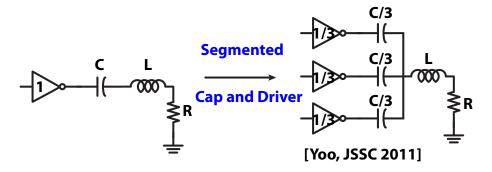

| 3.1                                                                | SC PA as a class D PA                                                                                                                                                                                                                                                                                                                                                                                           |

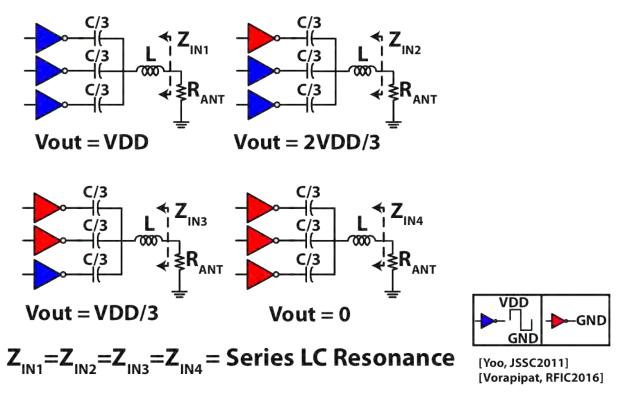

| 3.2                                                                | SC PA operating principle                                                                                                                                                                                                                                                                                                                                                                                       |

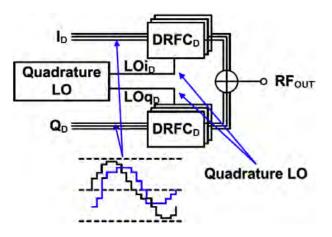

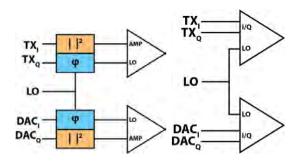

| 3.3                                                                | Cartesian PA model                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.4                                                                | Polar (right) vs Caresian (left) PA                                                                                                                                                                                                                                                                                                                                                                             |

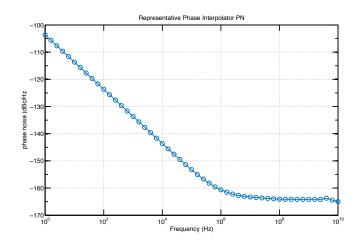

| 3.5                                                                | Simulated phase interpolator phase noise                                                                                                                                                                                                                                                                                                                                                                        |

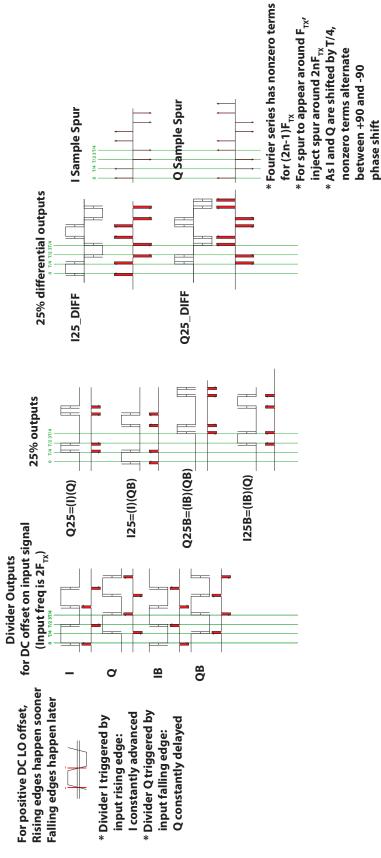

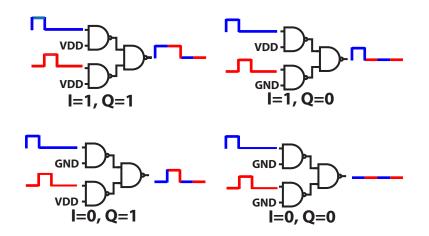

| 3.6                                                                | 25% Cartesian LO combination                                                                                                                                                                                                                                                                                                                                                                                    |

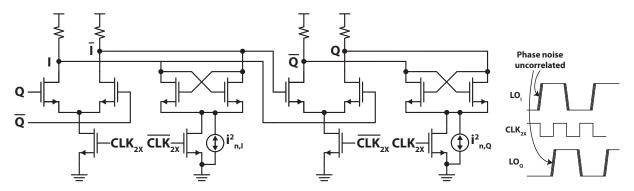

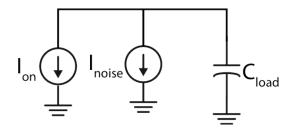

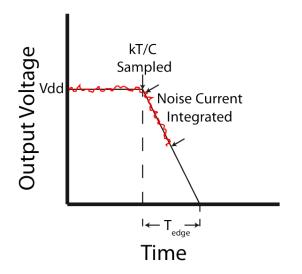

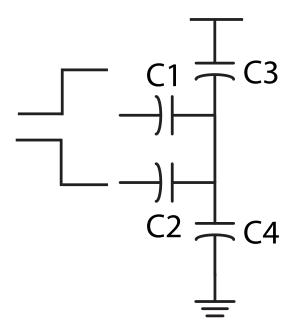

| 3.7                                                                | Charging model for the Q phase                                                                                                                                                                                                                                                                                                                                                                                  |

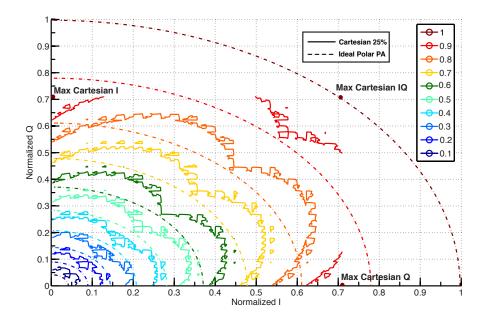

| 3.8                                                                | Cartesian(4 bits binary, 4 bits thermo) vs. Polar efficiency contours. The polar is                                                                                                                                                                                                                                                                                                                             |

|                                                                    | the constant efficiency at constant amplitude circles. The black lines correspond                                                                                                                                                                                                                                                                                                                               |

|                                                                    | to achievable powers for cartesian                                                                                                                                                                                                                                                                                                                                                                              |

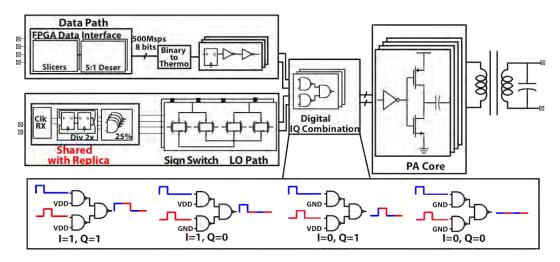

| 3.9                                                                | Top level TX schematic.    62                                                                                                                                                                                                                                                                                                                                                                                   |

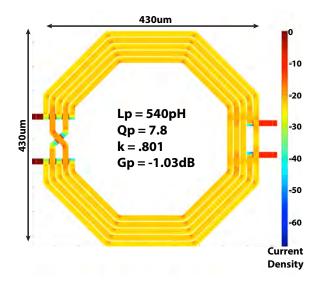

| 3.10                                                               | TX transformer                                                                                                                                                                                                                                                                                                                                                                                                  |

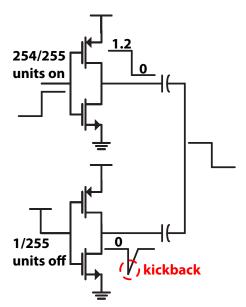

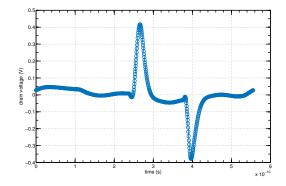

|                                                                    | SC PA drain kickback                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                    | Worst case drain voltage vs. time                                                                                                                                                                                                                                                                                                                                                                               |

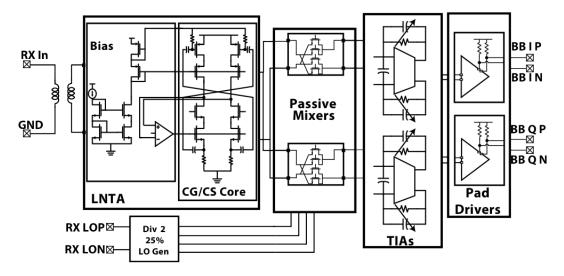

|                                                                    | Top level RX schematic                                                                                                                                                                                                                                                                                                                                                                                          |

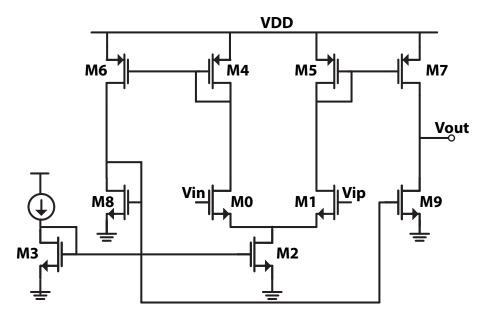

|                                                                    | LNTA schematic                                                                                                                                                                                                                                                                                                                                                                                                  |

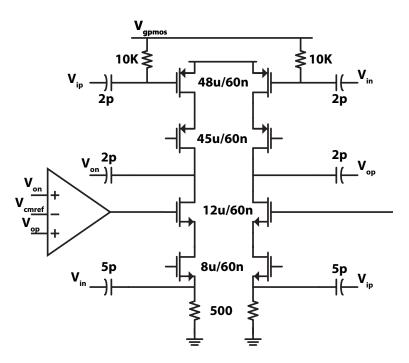

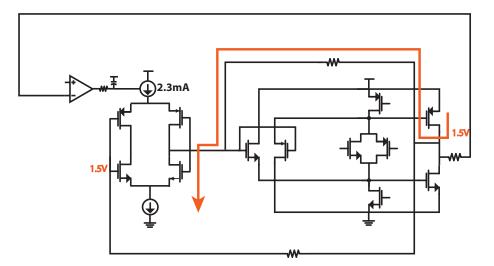

|                                                                    | LNTA CMFB schematic                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                    | TIA schematic                                                                                                                                                                                                                                                                                                                                                                                                   |

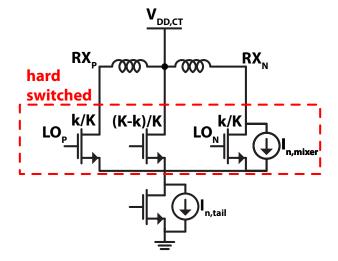

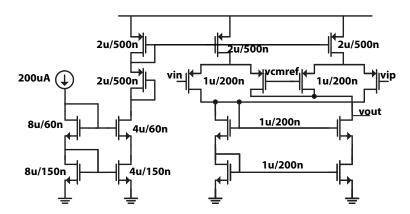

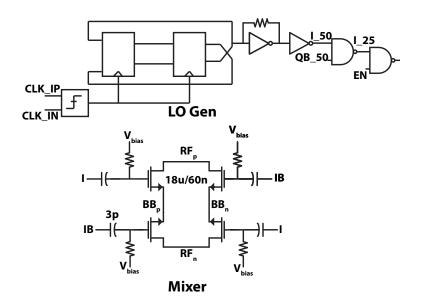

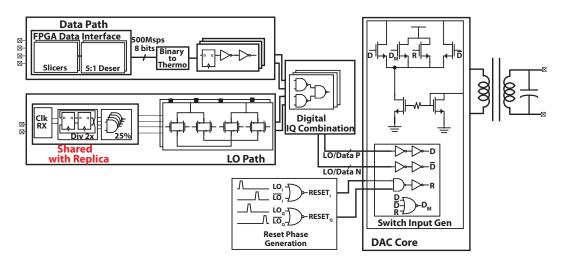

| 3.17<br>3.18                                                       | Mixer/LO path schematic                                                                                                                                                                                                                                                                                                                                                                                         |

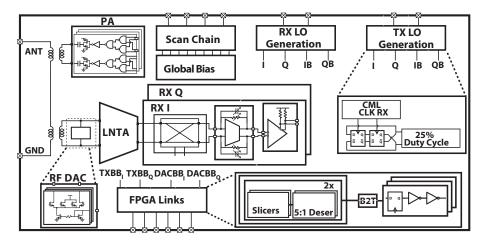

|                                                                    | Top level DAC schematic.    69      Chip top level schematic.    70                                                                                                                                                                                                                                                                                                                                             |

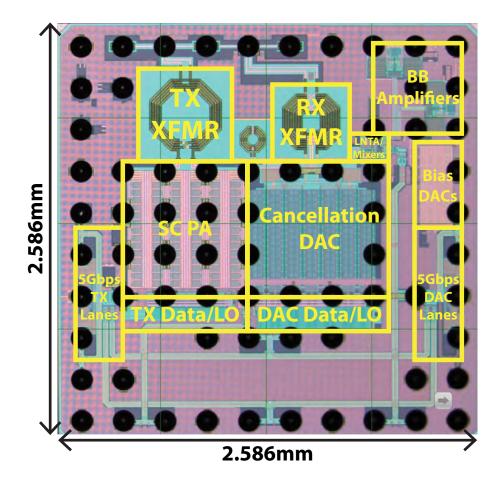

|                                                                    | Die Photo.         70           70                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                    | Die Thoto                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                    | PCB configuration for isolated (left) and system testing (right)                                                                                                                                                                                                                                                                                                                                                |

|                                                                    | Inductor parameters with top 4 layers of PCB cut                                                                                                                                                                                                                                                                                                                                                                |

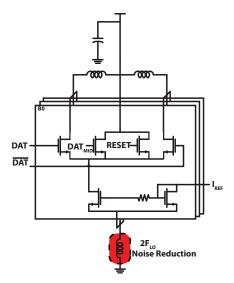

|                                                                    | 2FLO Noise Reduction                                                                                                                                                                                                                                                                                                                                                                                            |

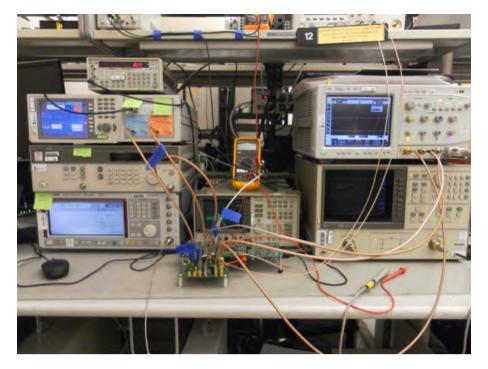

|                                                                    | Test Setup.         74                                                                                                                                                                                                                                                                                                                                                                                          |

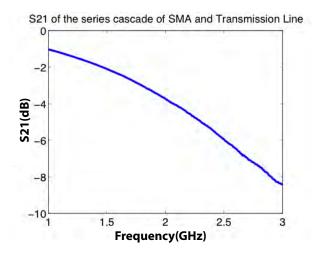

|                                                                    | S21 of the SMA and output transmission line                                                                                                                                                                                                                                                                                                                                                                     |

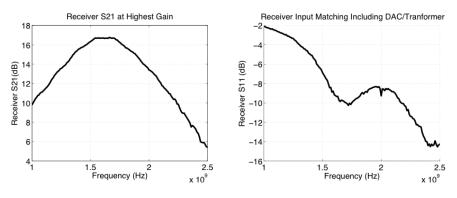

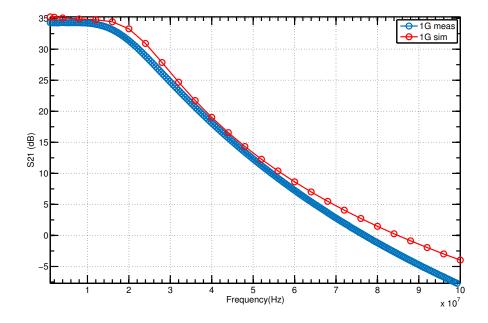

|                                                                    | RX S21 (left) and S11(right). $\ldots$ 75                                                                                                                                                                                                                                                                                                                                                                       |

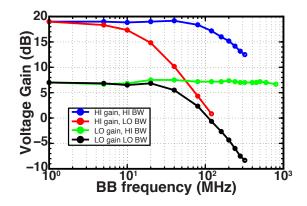

|                                                                    | Various RX gain and bandwidth settings                                                                                                                                                                                                                                                                                                                                                                          |

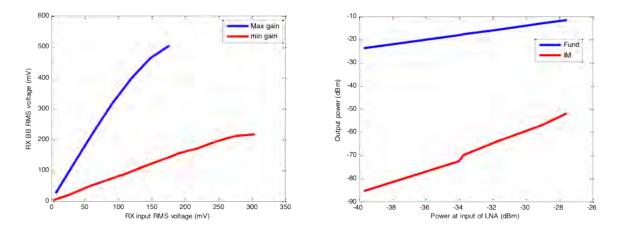

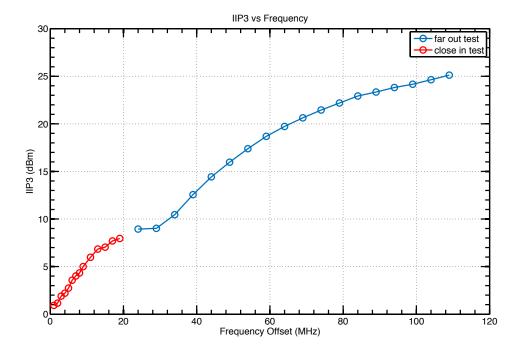

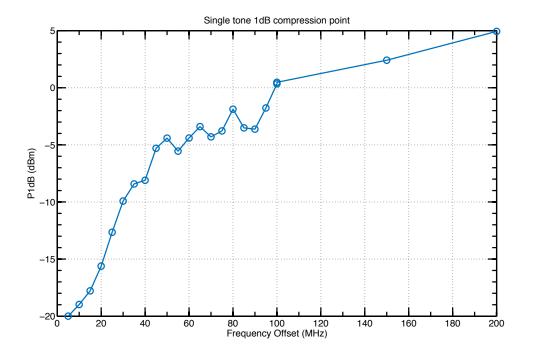

|                                                                    | RX P1dB (left) and IIP3 (right)                                                                                                                                                                                                                                                                                                                                                                                 |

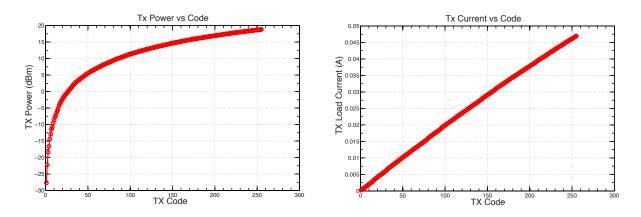

|                                                                    | TX power (left) and current (right) vs. code                                                                                                                                                                                                                                                                                                                                                                    |

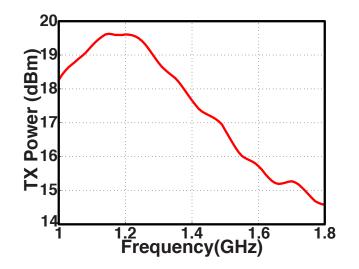

|                                                                    | TX output vs frequency                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                 |

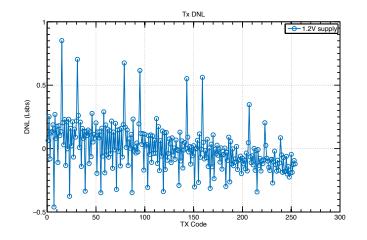

| 3.32 | TX DNL.                                                                           | 78  |

|------|-----------------------------------------------------------------------------------|-----|

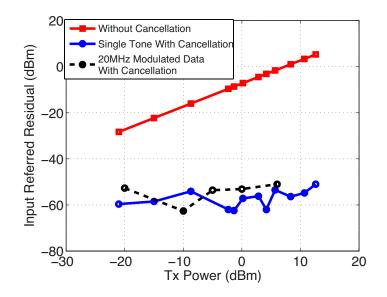

| 3.33 | TX residual referred at RX input vs TX output power                               | 80  |

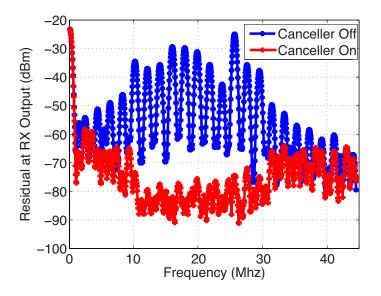

|      | RX band spectrum before and after cancellation.                                   | 80  |

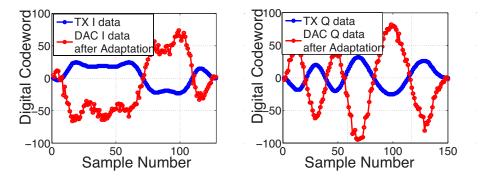

| 3.35 | TX/DAC codes after adaptation.                                                    | 81  |

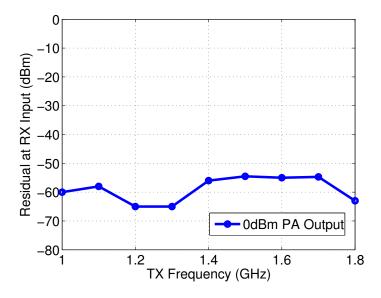

| 3.36 | TX residual vs. center frequency.                                                 | 81  |

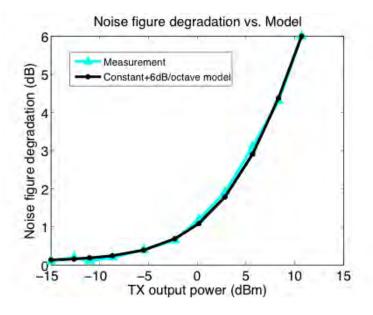

|      | Noise figure degradation measurement vs curve fit of constant $+ 6 dB/decade$ .   | 82  |

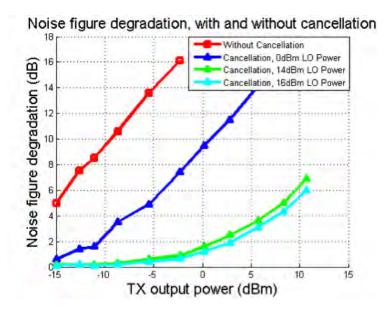

|      | Noise Figure degradation vs TX LO power.                                          | 83  |

| 3.39 | Comparison Table.                                                                 | 84  |

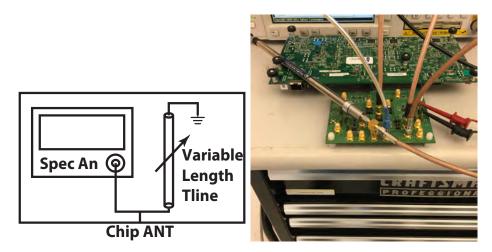

| 3.40 | Measurement setup for VSWR.                                                       | 85  |

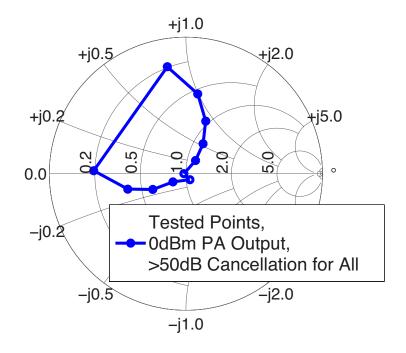

| 3.41 | Antenna impedance points measured                                                 | 86  |

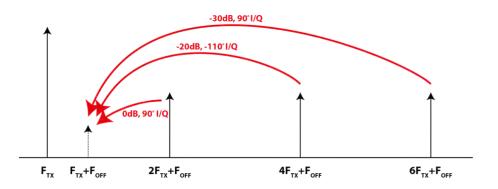

| 3.42 | Phase relationship of I and Q spurs for injected input spurs                      | 86  |

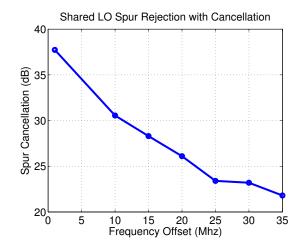

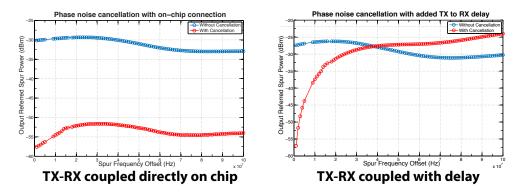

| 3.43 | Spur cancellation vs offset frequency.                                            | 87  |

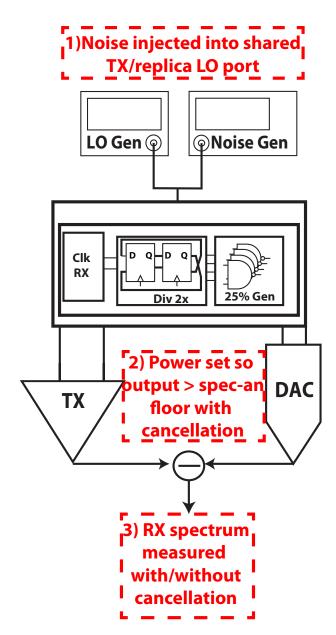

| 3.44 | Test setup for phase noise cancellation                                           | 88  |

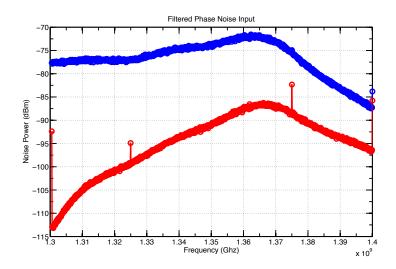

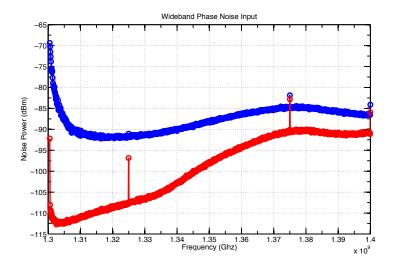

| 3.45 | Filtered input noise spectrum at output before and after cancellation             | 89  |

| 3.46 | Wideband input noise spectrum at output before and after cancellation             | 89  |

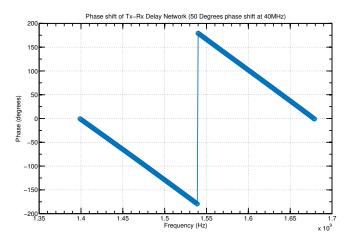

| 3.47 | Phase shift of TX to RX coupling path                                             | 90  |

| 3.48 | TX phase noise cancellation in RX band as the TX-RX leakage path delay increases. | 91  |

| 3.49 | Schematic of the input clock receiver which limits phase noise performance        | 91  |

| 3.50 | Simulated noise contributions of the LO divider                                   | 92  |

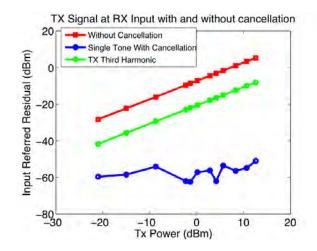

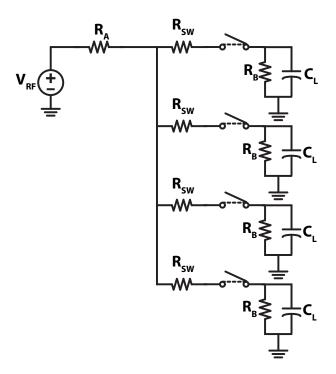

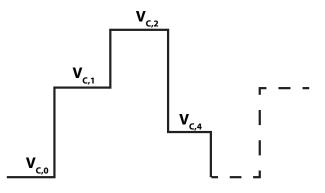

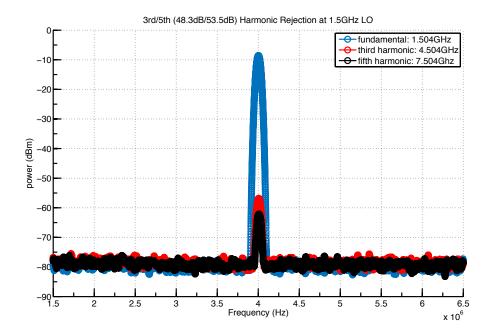

| 4.1  | Third harmonic power vs TX power at antenna.                                      | 94  |

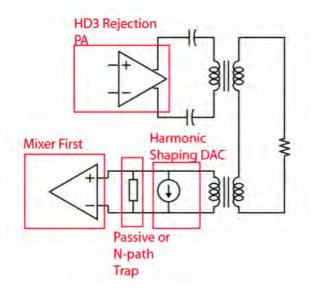

| 4.2  | Potential options for TX third harmonic cancellation.                             | 94  |

| 4.3  | Available gain of the transformer network vs. DAC cap.                            | 95  |

| 4.4  | Passive-mixer-first input match model.                                            | 97  |

| 4.5  | Voltage on RF side of the mixer.                                                  | 98  |

| 4.6  | Equivalent linear impedance model of the RX                                       | 98  |

| 4.7  | S11 offset of the receiver.                                                       | 99  |

| 4.8  | Cross-coupled baseband for complex input impedance creation                       | 99  |

| 4.9  |                                                                                   | 100 |

| 4.10 | -                                                                                 | 101 |

| 4.11 | Noise model of the cross-coupled feedback path.                                   | 102 |

|      |                                                                                   | 104 |

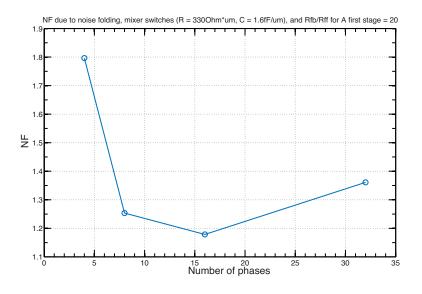

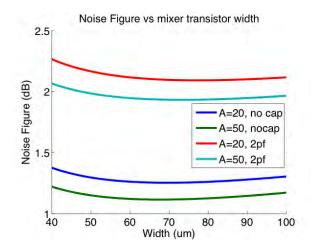

| 4.13 | Noise figure vs. mixer switch size                                                | 104 |

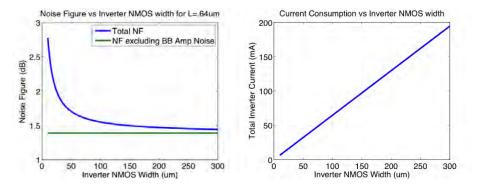

| 4.14 | Noise figure (left) and power consumption (right) vs. inverter size               | 105 |

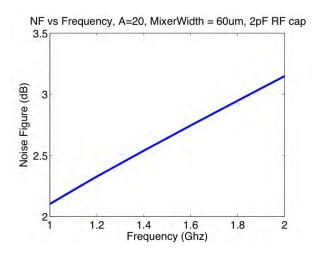

| 4.15 | Noise figure vs frequency.                                                        | 105 |

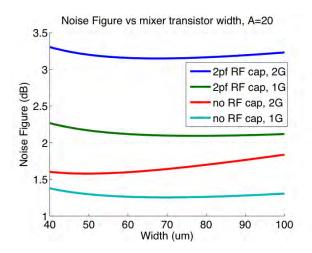

| 4.16 | Noise figure for different RF cap values.                                         | 106 |

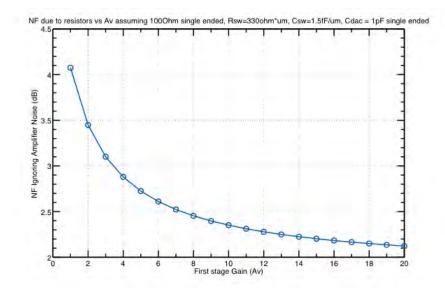

| 4.17 | Noise figure with a noiseless baseband amp.                                       | 107 |

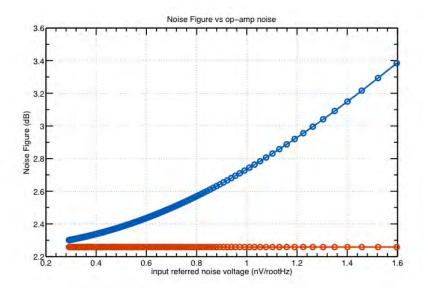

| 4.18 | Noise figure vs amplifier input referred noise                                    | 108 |

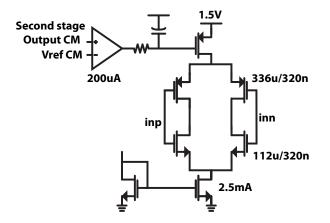

| 4.19 | Complementary first stage schematic.                                              | 108 |

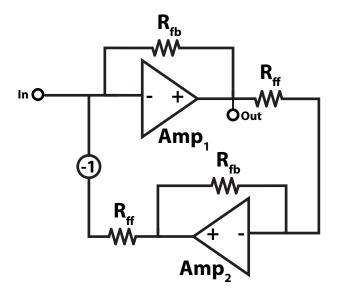

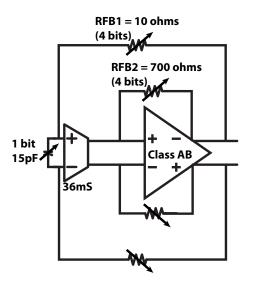

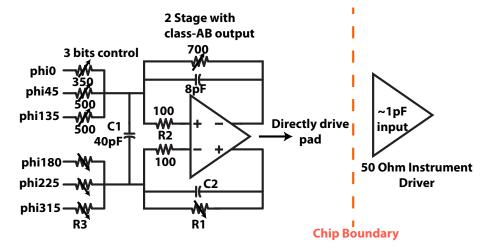

| 4.20 | Baseband amplifier with shunt feedback second stage                               | 109 |

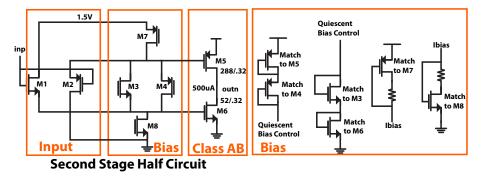

|      | 1                                                                                 | 110 |

| 4.22 | Latchup path for baseband amplifier                                               | 111 |

|      |                                                                                   |     |

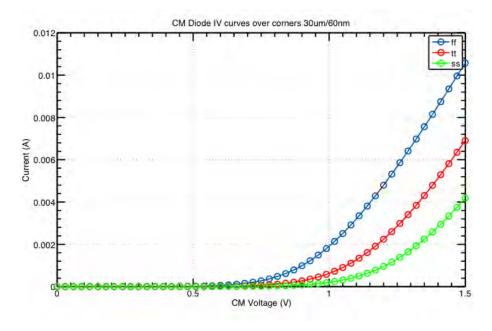

| 4.23 | Common mode diode IV curves                                     | 111 |

|------|-----------------------------------------------------------------|-----|

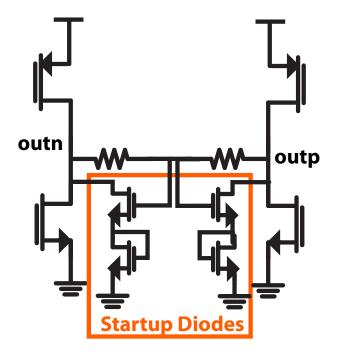

| 4.24 | Common mode pulldown diodes.                                    | 112 |

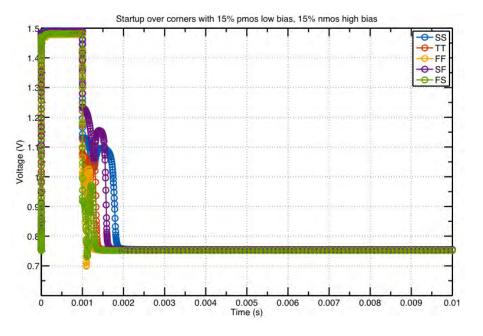

| 4.25 | Baseband amplifier transient startup curves.                    | 113 |

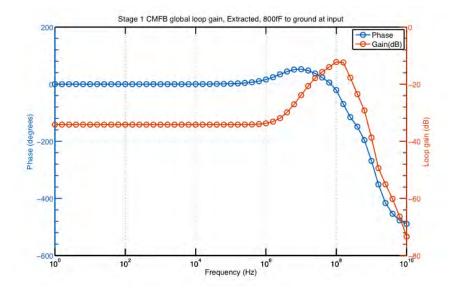

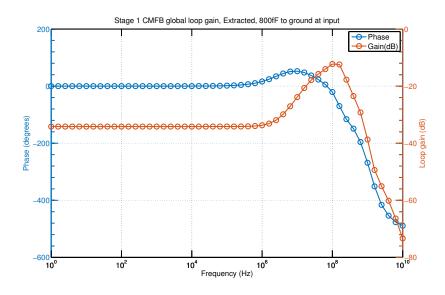

| 4.26 | Local common mode feedback loop gain.                           | 113 |

| 4.27 | Global common mode loop gain                                    | 114 |

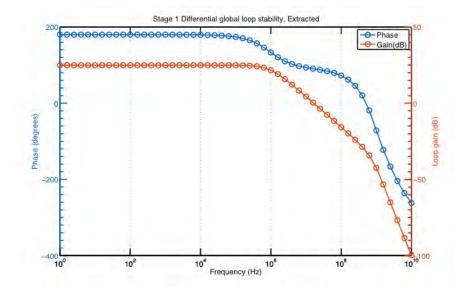

| 4.28 | Differential mode loop gain.                                    | 115 |

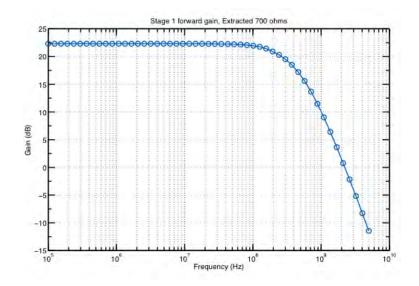

| 4.29 | Baseband amplifier forward gain.                                | 115 |

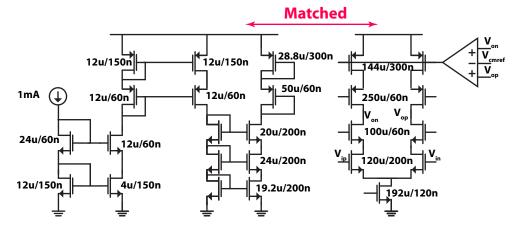

| 4.30 | MFB/harmonic recombination amplifier.                           | 118 |

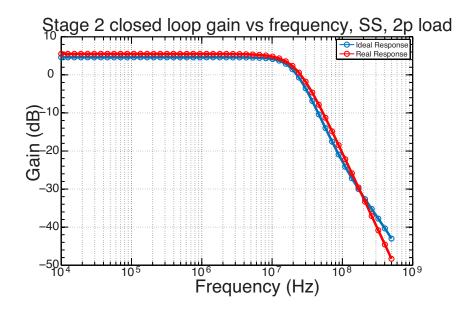

| 4.31 | MFB filter response.                                            | 118 |

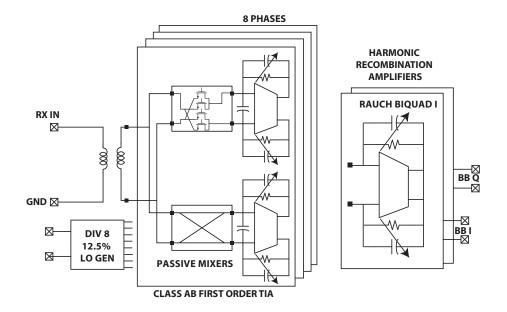

| 4.32 | Receiver top level diagram.                                     | 119 |

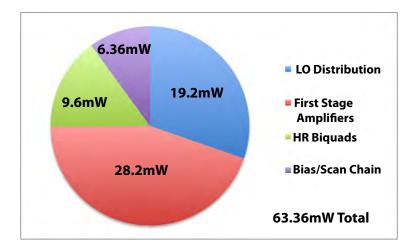

| 4.33 | RX power breakdown.                                             | 119 |

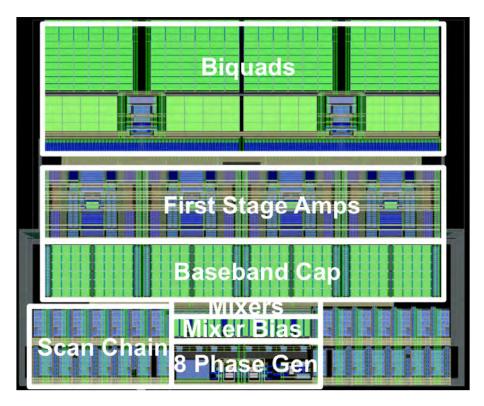

| 4.34 | Receiver top level layout                                       | 120 |

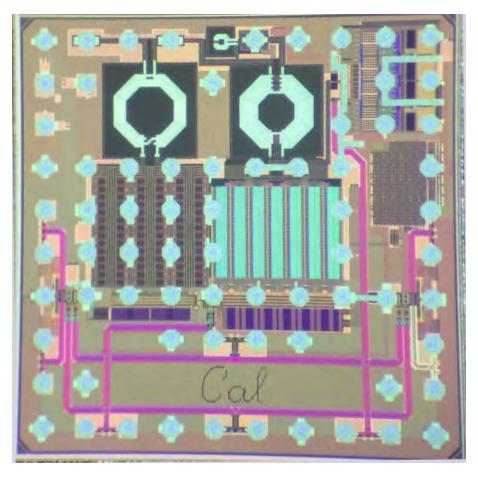

| 4.35 | Die Photo.                                                      | 121 |

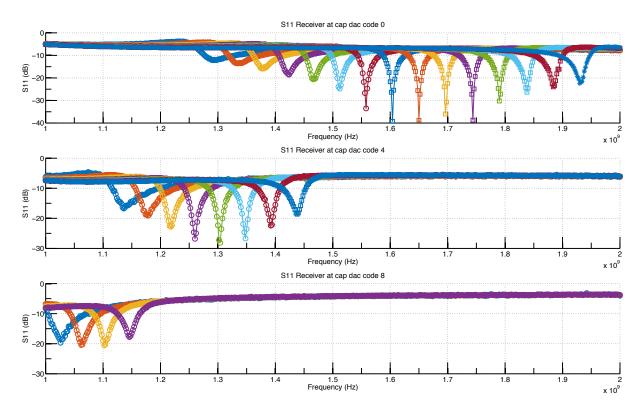

| 4.36 | S11 vs. LO frequency for fixed matching network cap DAC setting | 122 |

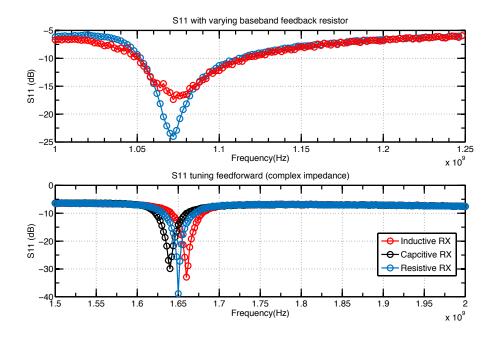

|      | 3                                                               | 123 |

|      |                                                                 | 123 |

|      |                                                                 | 124 |

| 4.40 | Receiver 1dB compression vs frequency offset.                   | 125 |

|      | $\mathbf{J}$                                                    | 126 |

| 4.42 | RX comparison table.                                            | 127 |

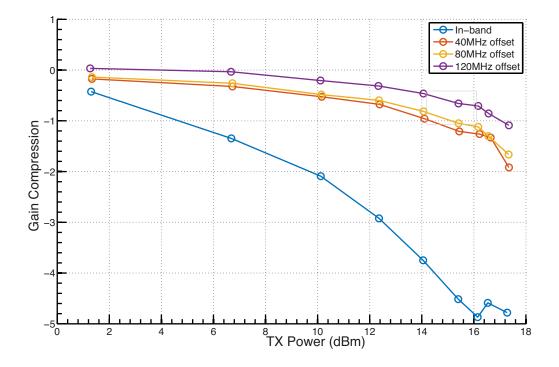

| 4.43 | RX compression vs. TX power.                                    | 128 |

|      |                                                                 |     |

# List of Tables

| 1.1 | Example design specifications from LTE standard                       | 9  |

|-----|-----------------------------------------------------------------------|----|

| 1.2 | Operating frequency range of recently published wideband receivers    | 15 |

| 1.3 | Operating frequency range of recently published wideband transmitters | 15 |

#### Acknowledgments

I owe a great number of people for their support to this point.

First and foremost, I would like to thank my mom and brother Girish. Mom, I can never repay your unconditional love, and sacrifice in putting me above all else.

Professor Nikolic, you're truly an advisor in the purest sense of the word. Your direction on all things, academic and life, since I was 17 years old, have immensely shaped me. As a mentor you always have my best interests in mind. I always hear from people "Bora seems to have a high opinion of you" - I hope I can one day live up to that expectation. Professor Alon, I can't thank you enough for your wisdom, guidance, and support. Its very rare to find a professor who would accommodate weekly meetings over the summer, with a student who wasn't his own - especially when the only time that worked was 12am (not a typo) on Wednesdays. Your ability to listen to a problem I've been thinking about for weeks, dissect it into its simplest form, and get three steps past me in a matter of minutes has astounded me for years. I also thank you for your repeated attempts to teach me circuit design in EE141, EE240, and EE290C. Professor Niknejad, thank you not only for your great course and the constant technical lessons, but also for your friendship outside the classroom. In particular, I admire your natural enthusiasm, whether for new research problems, or on the soccer field. Professor Wright, thank you for serving on my qualifying exam and dissertation committees, and providing feedback. Professor Muller, thank you for conversation and support both while I was deciding on graduate school, and while I was ta-ing EE140.

The majority of this work was done in extremely close collaboration with Lucas Calderin. Luke, I can't imagine working with anyone else for this long, and I've learned an incredible amount from your creativity and work ethic. I hope you've enjoyed our collaboration as much as I have, and I look forward to working together on our next adventures.

Antonio, thank you for the research collaboration and various technical discussions (or arguments), late night shenanigans in BWRC, and the subsequent late night walks home. Bonjern, thank you for for over six years of loyal friendship. Greg (Ozzy), thank you for giving me an entirely new (and sometimes unwanted) perspective on life. Krishna, thank you for the all the Warriors games we watched together, for unconditionally having my back, and for making me smile when I need it most. Nathan, thank you for the friendship and conversations over many lunches.

I'd like to thank others in BWRC, Amy, Andrew, Angie, Naichung, Nandish, and Pavan, for friendship, technical discussion and support, or both. Several older students at BWRC have provided mentorship, guidance, and support, in particular Milos Jorgovanovic, Lingkai Kong, and Charles Wu. Also thanks to members of the ComIC group for making BWRC more enjoyable, including Amanda, Ben, Brian, Dajana, Han-Chih, Jaehwa, John, Katerina, Keertana, Luis, Marko, Matt, Miki, Mira, Nick, Paul, Pifeng, Rachel, Sharon, Stevo, Vinayak, and Vladimir.

The staff at BWRC has made working, taping out, and testing much easier, and I'd like to thank Ajith, Amber, Bira, Brian, Candy, Prof. Dave, Erin, Fred, James, Leslie, Olivia, Sarah, and Yessica. Thanks to Michael Reiha, Tommi Ylamurto, Hans Daneels, and Vason Srini from Nokia, and Farhana Sheikh and Dan Schwartz from Intel for technical discussion, feedback, and funding.

I'd like to thank my friends outside BWRC, who have kept me sane during my time here. Dustin and Rohan, thank you for being my brothers. Thanks to Arjun for top notch Warriors analysis. Phil, thank you for getting angry on my behalf first, asking questions second, and cracking up in laughter third. Alex, Arvind, Jay, thank you for 20 (or more?) years of friendship. Kathy, thank you for Gob.

Finally, the biggest thank you to my dad. I hope this work would make you proud.

This work is funded in part by DARPA RF-FPGA program under contract HR0011-12-9-0013 in collaboration with Nokia and Boeing, and in part by Intel, and Qualcomm.

## Chapter 1

## Introduction

### 1.1 Motivation

Since the advent of mobile devices, the demand for wireless data has grown tremendously. Current projections estimate that global mobile data traffic in 2020 will reach 30 exabytes per month, up 120x from 2010. This corresponds to 28 daily images and 2.5 daily video clips per person on earth. In fact, by 2020, more people are projected to have mobile phones than running water or electricity at home [1].

Prior generations of cellular deployments have serviced this demand largely through increase in bandwidth, from 200KHz in 2G GSM networks focusing on only voice, to 1.25MHz and 5MHz in 3G CDMA/WCDMA systems, to 20 and even 100MHz in 4G LTE. This method of scaling is largely closed - as seen in the US spectrum allocations in figure 1.1, low frequency spectrum is crowded and saturated [2]. Symptomatic of this spectral crowding, radio spectrum has become one of the most valuable commodities on earth. In 2014, the US government sold 65MHz of the so called AWS-3 spectrum around 1700MHz for over 30 billion dollars [3]. Spectrum ownership now represents the dominant cost for mobile operators, over 40% of the 10 year cost of ownership.

A significant hardware issue resulting from overcrowded spectrum is interference between closely spaced radios operating concurrently. In particular, the largest source of interference for a radio receiver (RX) is often a system's own transmitter (TX). For example, in LTE deployments, the transmitter and receiver operate simultaneously, sharing the same antenna. The high power transmit signal must be isolated from the sensitive receiver, in order to maintain RX sensitivity, and prevent RX damage. This problem is exacerbated in a modern handset, which contains transmitters for multiple standards such as WiFi, GPS, and LTE, all operating at the same time. These radios create self-interference, defined as the interference generated by a single system's own transmitter operating simultaneously with the collocated receiver.

In today's systems, the self interference issue is addressed by separating the TX and RX frequency channels, and adding frequency selective filters between the TX and RX

Figure 1.1: Frequency allocation in the United States.

circuits. This scheme of separated TX/RX frequency allocations is known as frequency division duplexing (FDD). TX/RX isolation filters require a large quality factor (Q), in order to achieve sufficiently steep roll-off for closely spaced frequency bands. Due to the high Q required, the filters are placed off the main transceiver chip, and are intrinsically narrowband and difficult to tune. Accordingly, a separate set of filters is required for each band, and a limited number of bands are supported in a single device. This is limited not only by the area and cost constraints of fitting these discrete filters onto the printed circuited board (PCB), but also by the loss incurred from the multiplexing paths through the filter bank.

Additionally, these filters rely on a frequency separation between the transmit and receive bands to provide isolation. It would be beneficial for a transceiver to be able to remove, or "actively cancel" its own self interference, in a frequency agnostic manner, i.e. with arbitrary TX and RX spacings, bandwidths, or even overlapped (full duplex, FD) channels. Several benefits of such a transceiver are highlighted below.

#### 1.1.1 Boosted Spectral Efficiency

Fully overlapped transmit and receive frequency channels can increase the system spectral efficiency, defined in data rate per unit of spectrum allocated (Bits/sec/Hz). Given a finite availability of spectrum, increased data demand can only be met through an increase in spectral efficiency. However, existing standards employing the latest coding and modulation techniques are saturating in their ability to continue to extract further efficiency from the spectrum. This saturation is seen in Fig. 1.2, showing the efficiency of various standards over the past decade.

Figure 1.2: Spectral efficiency of various standards from 2007 to 2013 - full duplex represents an opportunity to double.

Fundamentally, operating the transmitter and receiver simultaneously to uplink and downlink data on overlapped spectrum can as much as double the efficiency per unit of frequency. This represents a method to break the saturation of Fig. 1.2, and would be enabled by self-interference cancellation.

#### 1.1.2 Universal Radio

The FDD resource allocation mode has forced a paradigm of fixed TX/RX band pairings. For example, the LTE standard supports over 40 bands worldwide[4]. A separate discrete, off chip filter is needed to provide the self-interference isolation for each unique band pairing.

#### CHAPTER 1. INTRODUCTION

Accordingly, different subsets are supported in different versions of handset devices depending on the intended geographic region of operation - a universal LTE phone does not exist [5].

A tunable self-interference cancellation circuit, as shown in Fig. 1.3, would enable removal of these off-chip filters in current systems. This would save original equipment manufacturer (OEM) cost and area, and would enable consumers to use any phone across any carrier in any global market. The GSM Association (GSMA) estimates the economic impact of this globally harmonized spectrum access as hundreds of billions of dollars [6].

Figure 1.3: Self-interference cancellation for universal radio.

Additionally, the latest releases of LTE [4] support a new resource allocation mode, carrier aggregation (CA), wherein the radio combines disjoint pieces of spectrum when more bandwidth is needed. When paired with FDD, carrier aggregation results in a exponentially increasing number of these fixed frequency self-interference filters - not only must specific TX/RX band pairings be supported, but filters are needed for combinations as well. A circuit which could adapt the frequency of its interference rejection would unlock flexible use of disjoint spectrum in carrier aggregation scenarios.

Finally, high TX output powers at cellular basestations necessitate bulky, expensive, fixed-frequency cavity filters to be installed even between separate chips, to suppress the transmitter's self-interference into the receiver. Some tunable self interference-cancellation circuit, even one which only provides partial TX/RX isolation, could reduce size and cost of the cellular infrastructure deployment.

#### 1.1.3 Simplified Spectral Planning

As mentioned before, the TX and RX in FDD systems occupy separate frequency bands, enabling frequency selective filters to handle the self interference during simultaneous operation. The overhead of acquiring paired TX/RX spectrum has driven many operators to time division duplex (TDD) standards, namely buying a single unpaired chunk of spectrum to reuse for transmission and reception. These TDD standards are less efficient, as shown in data presented by Nokia-Siemens Networks in Fig. 1.4. There can be a lack of coordination between adjacent cell base-stations, which consequently interfere with each other due to transmission and reception at the same frequency. Additionally, the switching time from transmission to reception adds network overhead, eating into the capacity. However, network operators accept this inefficiency in TDD systems, due to the difficulty in building hardware to support various FDD channel pairs, and the cost of good FDD bonded spectrum.

Figure 1.4: Comparison of TDD and FDD implementations.

A self-interference cancelling transceiver in essence removes the distinction between TDD and FDD systems, creating what some people have termed any-division duplexing (ADD) [7]. Old TDD systems with un-bonded spectrum could be replaced by systems which operate on the same spectrum simultaneously in transmit and receive mode. FDD systems could bond arbitrary channels together, significantly simplifying spectral planning constraints.

Additionally, in order to ease the self-interference problem, guard bands are placed between channels in the same frequency band, due to out of band TX nonlinearity and noise which leak into the systems receiver. This manifests itself in WiFi networks, where a single access point (AP) does not transmit and receive simultaneously, even on separated channels. This problem is expected to be exacerbated in upcoming proposals of LTE-U, which plans to deploy LTE in the unlicensed WiFi bands. A single AP would not be able to service both LTE-U and WiFi in a spectrally dense deployment due to this transmit leakage. A self interference cancelling transceiver would shrink or eliminate guard band requirements, and enable flexible single-device cross standard operation, again simplifying frequency planning.

#### 1.1.4 Backhaul and Relaying

In an effort to increase network capacity, network operators have trended towards smaller, denser cell site deployment. However, backhauling the small cell sites to the main network remains a challenge. Fiber backhaul offers the best performance, but is impractical to widely deploy due to cost. High-frequency millimeter wave backhaul is still limited to line-of-sight (LOS) propagation. New low frequency spectrum is unavailable, and re-using the existing spectrum for backhaul is difficult, as the small cell station must serve its users and backhaul itself at the same time. This is therefore another instantiation of the self interference problem.

A self-interference cancellation transceiver enables a self-backhauled network, where a base station simultaneously receives from its users and backhauls itself on shared, or even overlapped spectrum. In fact, it has been shown in [8] that self-backhauled networks can approach fiber levels of performance. This is because existing LTE macro networks are heavily under-leveraged, at only 25% utilization. Self-backhauled small cells re-use the existing macro network capacity to relay back its information, improving return on the huge investment the mobile operators have already sunk into their deployment.

#### 1.1.5 Control Planes

The control plane is a separate low-rate link between elements in a network used for network coordination purposes. In particular, this coordination information is critical for new cooperative interference mitigation schemes, such as coordinated multi point (CoMP). Interference coordination imposes tight latency requirements on the control plane data. Further, allocating new spectrum for the control plane links is a costly proposition. Simultaneous transmission of data to an end user and control plane information to another base station over shared spectrum represents a low cost, low latency method of building such control planes. This is yet another instantiation of the self interference problem, which could be enabled by frequency flexible active cancellation circuits.

As seen above, self-interference manifests across many wireless applications. Existing hardware has no ability to configure the interference rejection over uplink and downlink frequency bands, which results in bulky, expensive, and functionally limiting implementations. The possibility of overlapping the TX and RX bands opens still further advantages.

This work accordingly focuses on fully integrated transceiver design which can, in frequency agnostic manner, isolate a transmitter and receiver operating on the same antenna.

### **1.2** Duplexer Specifications

A duplexer is defined as a three-port device, pictured in Fig. 1.5, which interfaces the transmitter and receiver to the antenna, and mitigates the self interference. This work, in essence, attempts to integrate the duplexer's functionality directly onto the transceiver chip, using techniques independent of the transmit and receive frequencies, spacings, or bandwidths. To provide fair comparison between existing frequency inflexible off-chip duplexers, research work, and this work, the duplexer's performance is evaluated by the specifications described in this section.

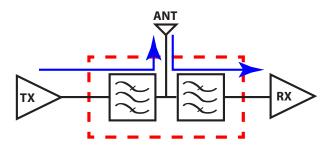

Figure 1.5: Duplexer functionality.

A receiver front-end compresses nonlinearly under a large signal, leading to distortion of the desired receive signal. As the radiated transmit signal at the antenna is significantly larger than this compression point, the transmit signal at the antenna must be isolated from the receiver input to prevent such distortion. This is reflected in the TX-RX isolation metric, which is defined in dB as

$$TX - RX \ Isolation = 10 \log_{10}(\frac{P_{tx,rx}}{P_{tx,ant}})$$

(1.1)

where  $P_{tx,rx}$  is the TX power present at the RX input, and  $P_{tx,ant}$  is the TX power present at the antenna port. This isolation in a duplexer is provided by a frequency selective filter between the antenna and receiver, as shown in 1.5. This filter passes signals in the RX band, while attenuating TX band signals. Additionally, this filter provides some attenuation of external out-of-band RX blockers.

TX-RX isolation must be provided while minimizing the Antenna to RX band attenuation, referred to as RX band insertion loss. As the duplexer is matched to 50 ohms on both sides, any loss directly degrades the signal level while maintaining a constant noise level, thus adding dB for dB to the receiver's noise figure. This insertion loss is defined as

$$RXInsertion \ Loss \ (RX \ IL) = 10 \log_{10}(\frac{P_{rx,rx}}{P_{rx,ant}})$$

(1.2)

where  $P_{rx,ant}$  is the receive signal power present at the antenna, and  $P_{rx,rx}$  is defined as the receive signal power present at the receiver's input.

Due to the dynamic nonlinearity and data quantization noise in a digital transmitter, the TX produces spurious RX band emissions, which can desensitize the receiver. This RX band noise can not be isolated by the Antenna to RX port filter - accordingly, a separate filter is needed on the TX to Antenna interface, rejecting the RX band while passing the TX band, to clean up the TX out of band emissions. This filter additionally ensures the TX meets any spectral mask requirements imposed by the standard. The RX band filtering is defined as

$$TX's RXBand Filtering = 10log_{10}(\frac{P_{tx(rxband),tx}}{P_{tx(rxband),ant}})$$

(1.3)

where  $P_{tx(rxband),tx}$  is the power of the TX spurious emission in the receive band at the transmitters output, and  $P_{tx(rxband),ant}$  is defined as the power of the TX spurious emission in the receive band at the antenna.

This filter must also minimize the amount of loss from the power amplifier output to the antenna input, referred to as TX band insertion loss. This is quite critical, as the TX output power level can be on the order of a Watt, making even a few dB of loss a huge wasted power. For example, 2dB of loss on a 1 Watt TX signal corresponds to 350mW of lost power, enough to power approximately seven receive chains. Additionally, there has been recent research and commercial interest in integrated CMOS power amplifiers (PA) to lower system cost. These CMOS PAs are limited in their ability to deliver high power as compared to non-CMOS counterparts, due to the limited supply voltage and breakdown of the CMOS process. Any loss in the duplexer must be compensated by producing higher output power at the transceiver chip. This can have a super-linear power penalty, due to the need for cascoding or other circuit techniques which reduce the core PA efficiency. The TX band insertion loss is defined as

$$TX Insertion Loss (TX IL) = 10 log_{10}(\frac{P_{tx,ant}}{P_{tx,tx}})$$

(1.4)

where  $P_{tx,ant}$  is the transmit signal power present at the antenna, and  $P_{tx,tx}$  is defined as the transmit signal power present at the transmitter's output.

Lastly, the duplexer provides a matched interface at all three ports, preventing the transmitter and receiver from excessively loading one another.

The LTE standard is taken as a good representative example to guide the specifications targeted for this work. The relevant standard level specifications are summarized in Table 1.1. Note that if a filter-based duplexer is used, the combination of these specs set the require filter order, with the ratio of TX peak power to RX noise figure setting the required rolloff, and the ratio of channel bandwidth to duplex spacing setting the transition band over which this rolloff must occur. The challenge is due to the large dynamic range difference (23dBm TX power vs -100dBm RX sensitivity) between the transmitter and receiver, which must be filtered within a very sharp stop band. In the worst case for the LTE standard, the filter must reach the stop band within 2x the signal bandwidth. This is fundamentally why narrow-band, discrete, high-Q components must be used, and integrated frequency agnostic duplexers do not exist.

The MEMS community has actively attempted to miniaturize these off-chip duplexers into a CMOS process for integration with the radio front-end. For example, bulk acoustic wave (BAW) resonators on top of silicon have been demonstrated and integrated with

| Channel BW              | <20MHz       |

|-------------------------|--------------|

| Duplex Spacing          | 30MHz-700MHz |

| Min (Spacing/BW)        | 2            |

| TX Peak Power           | 23dBm        |

| RX Noise Figure         | <15dB        |

| RX OOB Blocker P1dB     | ~0dBm        |

| (designed, not specced) | /~00DIII     |

Table 1.1: Example design specifications from LTE standard.

CMOS [9]. In fact, recent demonstrations have even shown that arraying many such MEMS filters (particularly those based on capacitive transduction) can address the characteristic impedance and power handling issues that plagued filters based on individual devices [10]. However, the resonant frequency of electromechanical filters is determined by physical dimensions and properties of the materials. Tuning the filter center frequency thus adds intolerable loss due to reduced network Q, or is difficult using electronically controlled means.

The duplexer performance specifications for a commercial Avago LTE duplexer correspond cleanly with the above LTE standard specifications. The TX-RX isolation is about 45-55dB. With a 1Watt (30dBm) transmit signal, this leaves around -20dBm at the RX input. As a state of the art receiver can be designed to compress by 1dB for an out of band blocker of around 0dBm, this leaves sufficient margin to process the RX signal and nearby blockers. The RX band attenuation of the TX signal is around 50dB with for example a 30dBm transmitter quantized to 11 bits, spread out over a 1GHz sampling frequency, the RX out of band quantization level is

$$30dBm - 6 \times 11bits - 10 \times \log_{10}(10^9) = -126dBm.$$

(1.5)

An additional 55dB of filtering puts this below the thermal noise floor level, so as to avoid RX desensitization.

The RX insertion loss is around 2dB, and the TX insertion loss is around 1dB.

Is worth noting that the same metrics apply to proposed full-duplex systems with fully overlapped transmit and receive channels. However, these metrics can not be provided through relying on frequency discrimination, and must be handled through another approach. For fully overlapped transmit and receive channels, a circulator can be used to provide an antenna interface. However, these circulators generally only provide around 20dB of isolation, so self interference cancellation is still necessary. Further, circulators require magnetic components which can not be integrated on to the integrated circuit, and are very expensive - accordingly, a technique that reduces the required isolation from the circulator and enables integration is the key enabler for a FD system.

## 1.3 Integrated Self Interference Cancellation: Prior Work

There have been several prior approaches to integrating the duplexer's functionality using techniques agnostic to center frequency and duplex spacing. This section details the operating principles of these approaches, and the main limitations which this work attempts to overcome.

#### **1.3.1** Transformer Hybrids

The passive hybrid technique originated in telephone networks, and has recently re-emerged in the wireless context as an integrated duplexer. Hybrids networks [11][12][13][14][15] are reciprocal passive 4-port networks, which use a portion of the TX signal to cancel TX interference at the RX port. Often times, these networks are constructed such that the TX signal appears as a common mode perturbation across the RX, while the desired receive signal from the antenna appears in the differential mode.

A key benefit of this structure is that if the balancing network and antenna impedance are sufficiently wide-band, the structure can suppress not only the main TX band signal but also provides some isolation for the TX nonlinearity, quantization noise, and phase noise that falls in the RX band.

Any network composed of entirely reciprocal elements must also be reciprocal. Namely, for any ports i and j,  $s_{ij} = s_{ji}$  where s represents the scattering parameter, or effectively the power flow, between ports. Accordingly, it is impossible for  $s_{tx,ant} = 1$  and  $s_{ant,rx} = 1$  simultaneously, and there is a fundamental insertion loss associated with the structure. This is normally modeled as a fourth port with a loss resistor.

To more closely understand the operation of the hybrid network, and the associated tradeoffs, prior art from [16], shown in Fig. 1.6, is examined.

Figure 1.6: Wireless hybrid as an integrated duplexer.

#### Hybrid Operation Principle

For the TX signal, as shown in Fig. 1.6, with perfectly symmetric transformer, the structure attempts to enforce zero differential voltage across the receiver. This condition is true if half the TX current flows into each of the balancing and antenna branches. However, this results in a 3dB insertion loss on the transmitter. To lower the wasted TX power while maintaining zero differential voltage across the RX port, the  $R_{bal}$  resistor must be increased to flow less current, and the autotransformer turns ratio must be skewed to compensate for the imbalance. As will be shown below, increasing  $R_{bal}$  results in a noise penalty for the receive signal.

For the RX signal, in the balanced condition, the voltage at the balancing port is 0 for a stimulus applied in series with the antenna port. Accordingly, any current in the receive port must flow through  $I_2$  in the autotransformer, and must be induced in  $I_1$  in the other branch of the autotransformer. The current flowing through the TX must be  $2I_{rx}$  by KCL, and the voltage must be half the voltage across the RX by the vertical symmetry across the transmitter - this forces a relationship that  $R_{rx} = 4R_{tx}$ .

To evaluate the noise penalty of the hybrid in the receive side, it is sufficient to find the Thevenin equivalent circuit looking out from the RX port for a stimulus in series with the antenna. The Thevenin resistance can be found by noting that in the balanced condition, a differential RX current should be isolated from the TX port. By KCL, the autotransformer currents must then be 0. This is somewhat confusing in that an ideal transformer can support a voltage across it with 0 current - but it can simply be imagined as a large impedance in the frequency range of interest. The Thevenin resistance is simply the series combination of the antenna and balancing resistors, which sets the available gain, and accordingly the SNR.

Note that the NF penalty of the passive network is only a function of the available gain (the Thevenin resistance), while the insertion loss is a function of both the Thevenin resistance as well as the antenna load. Accordingly, if the RX port is not matched, then RX IL is not necessarily equal to the RX NF degradation. However, there is still a tradeoff between the RX NF and TX IL.  $R_{bal}$  must be large to reduce the TX insertion loss (minimize  $I_2$  in Fig. 1.6), but a large  $R_{bal}$  contributes a large noise voltage relative to the antenna impedance at the receiver input.

#### Performance

The duplexer in [16] achieves 2.5dB TX insertion loss, with >50dB isolation in the TX band, >45dB isolation in the RX band, a cascaded RX NF of 5dB, and an antenna S11 of -8dB. The isolation is maintained up to a maximum VSWR of 2:1 on a 50ohm antenna over 1.5GHz to 2.2GHz. In [16], the antenna is intentionally not matched to the RX (S11 of -8dB) in order to lower the RX noise figure.

#### Structure Limitations

A big limitation inherent to the structure is the previously described tradeoff between TX insertion loss vs. RX noise figure. In particular, the wasted power consumption of such a structure for a transmitter of several hundred milliwatts to a Watt is of the same order of magnitude. This is quite intuitive, as no active elements are used in the isolation structure, so the tapped off wasted portion of the TX signal must be as large as the interference to be cancelled.

Secondly, it is difficult to balance the network with a real antenna across a wide range of operating conditions. Using a 10-bit capacitor/resistor DAC as the balancing impedance, a relatively limited VSWR of 2:1 can be covered. Furthermore, it is difficult to handle high TX powers with such an impedance network, as the CMOS switches used in the capacitive DAC must handle a large voltage swing. While this can be partially overcome through the use of stacked devices, and floating wells, these structures add a signal dependent nonlinearity to the balancing network, and reduce the center frequency tuning range due to reduced  $\frac{C_{on}}{C_{off}}$  of the capacitive DAC.

#### **1.3.2** Active Cancellation

Active cancellation originates in wireline links as a method for transmitting and receiving simultaneously on a single fiber. In this technique, a portion of the transmit signal is tapped off or synthesized, and injected into the receiver to perform a feed-forward cancellation of the TX leakage.

The technique has recently gained interest in the wireless community [17] [18][19], due to its high potential for on-chip integration, and it's flexibility across TX/RX frequency channels and spacing. This frequency independence makes active cancellation a good candidate for tunable duplexer implementation, and for fully overlapped transmit/receive wireless channels for in-band full duplex systems.

The difficulty in adapting this technique from wireline systems to wireless contexts stems from the higher transmit power levels, high-order modulation schemes, lower received signal power which requires high RX sensitivity, and more reflective or longer dispersion TX-RX leakage channels.

A series of active cancellation works were presented by Columbia University [20] [21] [22] [23] [24] [25]. In the first iteration, the TX signal is injected at the gate of a common gate LNTA, providing a cancellation across the  $V_{gs}$  of the low noise transconductance amplifier (LNTA) input device. A noise-cancelling common source branch is included, as proposed in [26] and rediscovered in [27][28][29]. The work proposes an additional injection point after the LNTA for cancellation of the TX noise in the RX band. The work is limited to <+2dBm of TX power, due to the nonlinearity induced in the common gate for a larger injection signal. In this topology, the drain voltage of the LNTA input transistor is still pinned, so only a limited source or gate swing can be suppressed despite the cancellation. Additionally, the work does not integrate the transmitter, and it remains unclear how the TX signal and the TX noise at the second injection point are coupled from the transmitter. Finally, this work only tests suppression for single tone TX signals without any modulation.

In the second iteration, the TX signal is passed through an n-path filter [30] to control the amplitude and phase of the injected TX signal at the RX input, extending the cancellation to a modulated TX bandwidth. This approach is limited to <-4dBm of TX power, potentially due to the nonlinearity induced in the n-path based filter. For 20MHz TX modulation, only 20dB of isolation is provided. Lastly, this work also does not integrate the transmitter, and where the TX signal is coupled from the transmit path in practice is unclear.

In [25], a circulator based on [31] is implemented in CMOS, again using n-path filters. While this work provides 42dB of TX/RX isolation, is it limited to -6dBm of TX power, and incurs a relatively high 10.9dB noise figure. This work again does not integrate the transmitter, and accordingly TX to RX leakage channel may be inaccurately modeled. Many secondary coupling paths, for example via the substrate, can arise when both transmitter and receiver are integrated on the same die, adding a difficult frequency selective portion to the TX/RX coupling path.

Another work targeting a full-duplex implementation is described in [32][33]. This work is relatively similar to [21], where a vector modulator couples the TX signal into the baseband virtual ground of a passive mixer first receiver. This work provides around 27dB of isolation for TX signals, at a limited TX power of <+1.5dBm. Similar to the Columbia work, this does not integrate a transmitter, and accordingly does not address the issue of where the TX signal is coupled.

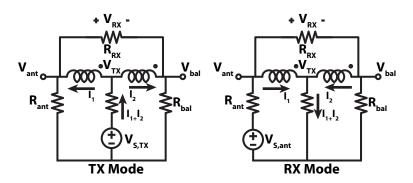

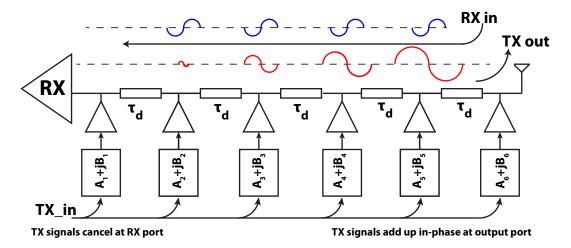

A different active cancellation approach is presented in [34]. The work segments and embeds the PA within an artificial transmission line, with the antenna placed on one side of the transmission line, and the receiver on the other as in Fig. 1.7. The individual PA signals are manipulated such that the TX signals sum out of phase on the antenna side, and in phase on the RX side, providing TX/RX isolation. Additionally, as the TX is in shunt with the receiver, an n-path based degeneration is proposed on the transmitter output stage to avoid excessive RX loss or loading.

This work can operate the RX and TX simultaneously up to around +14dBm of TX output power, while providing around 25dB of TX-RX isolation. One main downside is this limited isolation, potentially due to the required matching or resolution between sub-PAs to achieve out-of-phase summing at the receive port. The work also demonstrates a rather high >12dB NF. One guess is the transmitter's phase noise falling in the receive band does not sum out of phase at the receive port. Additionally, the work is measured at a rather large TX/RX duplex spacing of 115MHz. This is potentially because the work relies on a first order n-path based degeneration to raise the TX impedance present in the RX band, which reduces shunt loss for the receive signal. At a closer TX/RX spacing, the lowered TX impedance may further desensitize the receiver.

A chart summarizing the above, and other works [35][36][37] [38][39] in active cancellation is shown in Fig. 1.8, where the y-axis plots the TX-RX isolation in dB, and the x-axis shows the maximum TX power the cancellation network is able to process. This work attempts to develop a system pushing to the top right of the chart, with high cancellation at high power,

Figure 1.7: Distributed Tline duplexer.

towards the goal of a practical active cancellation transceiver meeting existing standard specifications. This requires around 50dB of isolation at greater than 20dBm of TX output power.

Figure 1.8: Limitations of prior work.

| Receivers                    | Murphy, | Fabiano, | Lin,    | Borremans, | Andrews, | Wu,    |

|------------------------------|---------|----------|---------|------------|----------|--------|

|                              | ISSCC12 | ISSCC13  | ISSCC15 | JSSC11     | JSSC10   | RFIC15 |

| Operating Frequency<br>(GHz) | .08-2.7 | 1.8-2.4  | .1-1.5  | .4-6       | .1-2.4   | .4-3.4 |

Table 1.2: Operating frequency range of recently published wideband receivers.

Table 1.3: Operating frequency range of recently published wideband transmitters.

| Transmitter                  | Imanishi, ASSCC09 | Wang, RFIC14 | Kuo, ASSCC14 |

|------------------------------|-------------------|--------------|--------------|

| Operating Frequency<br>(GHz) | .9-3              | .5-6         | .6-2.4       |

### 1.4 Wideband Transceivers

It is worth questioning if self-interference is truly the limiting factor in enabling an agile universal radio, capable of handling multiple bands and standards across the spectrum. Namely, is it possible that the transmitter and receiver chains themselves simply cannot be built to be tuned across a wide frequency range?

This problem of designing a universal transceiver has generated research interest over the past 5-10 years. On the receiver side, the primary push has been for higher linearity receivers, which can successfully receive a desired signal in the presence of blockers without front-end off-chip filters. This is a difficult problem in a wideband frequency agile system, due to the large tuning range over which blocker rejection must be provided. Research in this space has focused on current-mode receivers, where the linearity issue stemming from limited voltage headroom in a CMOS process is avoided by first converting the input signal into a current. This current is down-converted by highly linear switching passive mixers [40][41], which drive a low-input impedance filter to maintain linearity prior to re-converting to a voltage signal. Variants on this technique include work by [42][43] to eliminate the front-end current converter (LNTA) and drive the passive mixers directly from the antenna to push the linearity even further, as well as work by [29] [28] which attempts to reduce the noise penalty in the passive-mixer-first approach with a differential noise sensing and cancellation path. Such work has demonstrated widely frequency tunable radio receiver designs, at least in a research context, summarized in Table1.2.

On the transmit side, the difficulty is in maintaining high efficiency, high output power, and low harmonics and spectral emissions without bandwidth limiting high Q passive components for impedance transformation. A few of these are summarized in Table 1.3 [44] [45][46][47][48].

As seen through the above tables, relatively mature research methods can push the transceiver chain to cover the majority of the low frequency wireless bands. It is not the receiver or transmitter which provides limits for a reconfigurable radio [49] [50]. A look at the board components in Fig. 1.9 suggests that the main limitation is due to the narrowband,

#### CHAPTER 1. INTRODUCTION

discrete, off-chip components and filters used to provide filtering and interference rejection for the receiver at the antenna interface [51]. Integration of the interference rejection filters would unlock the potential of these widely frequency-tunable transceivers.

Figure 1.9: Frequency spectrum (top) and board components (bottom) for various standards.

### 1.5 Research Goals, Scope, and Organization

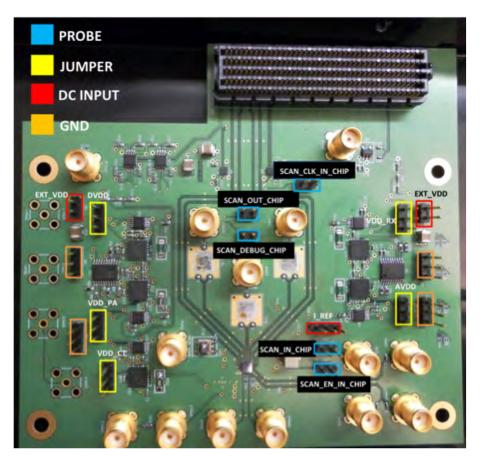

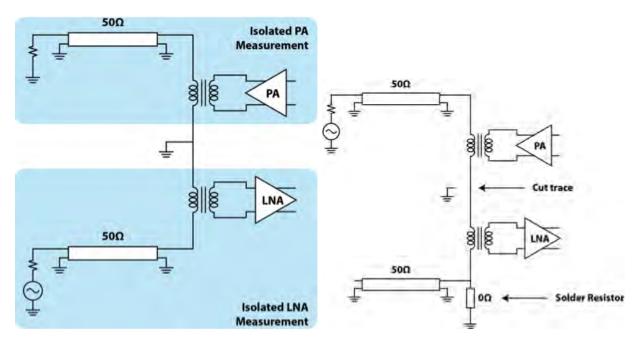

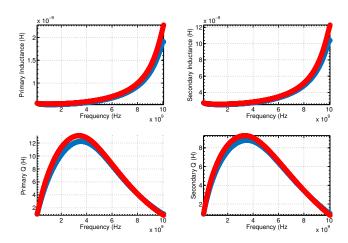

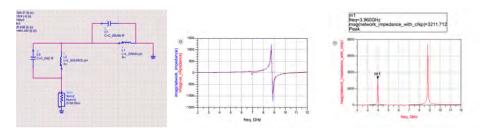

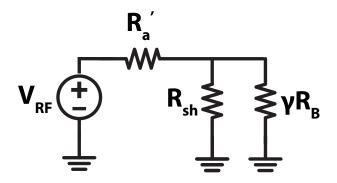

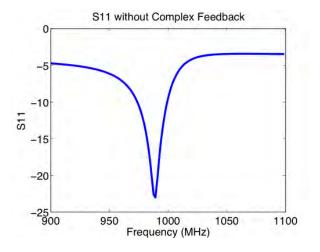

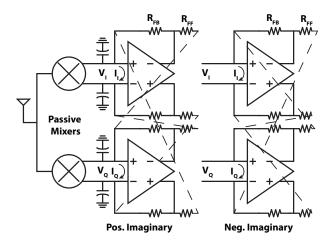

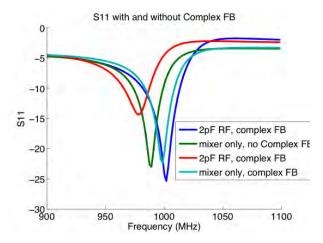

The key goals of this thesis are 1) the description of an active cancellation system which pushes towards the goal of fully integrating the front-end duplexer on chip 2) analysis of the key fundamental performance bounds of this system, many of which are generalizable considerations in all active cancellation systems 3) implementation of the system in a chip prototype 4) design of a new high linearity receiver in a second test chip, boosting the system performance. It is noting that the system described in this thesis could be used as a transceiver with overlapped TX/RX frequency channels, though not directly tested as such. The performance of the test prototype pushes the state of the art in electronic subtraction systems in maximum handled TX power, TX/RX isolation, as well TX/RX bandwidth and spacings.