# Design of Reconfigurable Radio Front-Ends

Xiao Xiao

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2018-142 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2018/EECS-2018-142.html

December 1, 2018

Copyright © 2018, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Design of Reconfigurable Radio Front-Ends

by

Xiao Xiao

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolic, Chair Professor Ali Niknejad Professor Paul Wright

Spring 2016

# Design of Reconfigurable Radio Front-Ends

Copyright 2016

by

Xiao Xiao

#### Abstract

Design of Reconfigurable Radio Front-Ends

by

#### Xiao Xiao

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolic, Chair

Modern and future mobile devices must support increasingly more wireless standards and bands. Currently, multi-band coexistence is enabled by a network of discrete, off-chip components that are bulky, expensive, and narrowband. As transceivers are required to accommodate an increasing number of wireless bands, the required number of discrete components increases accordingly, resulting in greater bill of materials (BoM) cost and front-end module (FEM) area. This work focuses on design techniques to enable front-end integration and reconfigurability in multi-band radios.

In the first part of this work, we present a wideband spectrum sensing receiver with high sensitivity, wide dynamic range, and low power overhead. Reconfigurability in multi-band radios requires environmental awareness, and spectrum sensing can be used for optimal channel selection and adaptive interference suppression. The 300MHz-700MHz spectrum sensing receiver uses subsampling downconversion and digital-analog hybrid correlation to achieve -104dBm sensitivity and 84dB dynamic range for a 6MHz channel while consuming only 28mW of power. In the second part of this work, we present a wideband time division duplex (TDD) front-end with an innovative transmit/receive (T/R) switching scheme. T/R switches conventionally are off-chip components, and existing integrated designs have been narrowband or high loss. We propose a wideband integrated T/R switching technique in which the PA is re-used as an LNA during receive mode, and we demonstrate this in a 20dBm polar transmitter that can be re-purposed into a 3.4GHz-5.4GHz LNA achieving -6.7dBm P1dB and 5.1dB NF. The two systems presented in this thesis contribute key innovations towards fundamental aspects of future reconfigurable radios - greater front-end integration, wideband transceiver design, and spectrum awareness.

# Contents

| CU             | Contents           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                |

|----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Lis            | st of              | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | iii                                                                                            |

| List of Tables |                    | vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

| 1              | Intr<br>1.1<br>1.2 | oduction Scope of Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>1</b><br>3                                                                                  |

| 2              | Low 2.1 2.2 2.3    | Power Spectrum Sensing for Cognitive Radio Applications Spectrum Sensing in the TV Band 2.1.1 UHF TV Band and IEEE 802.22 2.1.2 State of the Art and Related Works 2.1.3 Detection Techniques Evaluation of a Multi-Mode Detection System 2.2.1 Subsampling and Autocorrelation 2.2.2 Simulation Setup 2.2.3 Evaluation of Detection Modes Design of a Dual-Mode, Correlation-Based Spectrum Sensing Receiver 2.3.1 Dual-Mode Detection and Hybrid Correlation 2.3.2 LNA 2.3.3 RF Tracking Filter 2.3.4 Sampler 2.3.5 Baseband Filter Measurement Results | 5<br>6<br>6<br>8<br>10<br>13<br>14<br>14<br>18<br>20<br>25<br>26<br>28<br>31<br>34<br>37<br>39 |

| 3              | <b>Tra</b> : 3.1   | Introduction to TDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46<br>46<br>46<br>48<br>50                                                                     |

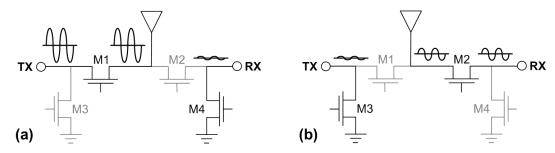

|    |        | 3.2.1  | Basic TRSWs and Substrate Loss                         | 50  |

|----|--------|--------|--------------------------------------------------------|-----|

|    |        | 3.2.2  | Power Handling                                         | 53  |

|    |        | 3.2.3  | Alternate TRSW Topologies                              | 56  |

|    |        | 3.2.4  | State-of-the-Art in Integrated TRSWs                   |     |

|    | 3.3    | Propo  | sed Wideband T/R Switching Technique                   | 63  |

|    |        | 3.3.1  | Switching PAs                                          | 64  |

|    |        | 3.3.2  | PA to LNA Transformation                               |     |

| 4  | Des    | ign of | a Wideband TDD Front-End with Integrated T/R Switching |     |

|    | via    | PA Re  | e-Use                                                  | 70  |

|    | 4.1    | Front- | End Transformer Design                                 | 70  |

|    |        | 4.1.1  | Stacked Transformer for Impedance Co-design            | 71  |

|    |        | 4.1.2  | Design Considerations for LNA Noise and Bandwidth      | 74  |

|    |        | 4.1.3  | Stacked Transformer with Reconfigurable Inductance     | 79  |

|    |        | 4.1.4  | Implementation of 1:1 Transformer                      |     |

|    |        | 4.1.5  | Implementation of Stacked Transformer                  | 83  |

|    | 4.2    | Design | n of PA/LNA Core                                       |     |

|    |        | 4.2.1  | PA Core                                                |     |

|    |        | 4.2.2  | LNA Design                                             |     |

|    |        | 4.2.3  | PA Supply Switch and Center Tap Design                 | 93  |

|    |        | 4.2.4  | PA/LNA Mode Switching                                  |     |

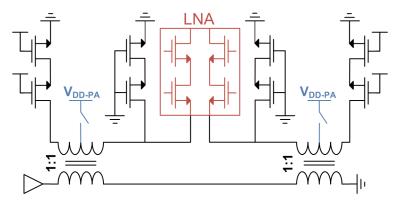

|    | 4.3    | System | m Implementation                                       | 102 |

|    |        | 4.3.1  | TX System                                              | 102 |

|    |        | 4.3.2  | RX Buffer                                              |     |

|    | 4.4    | Measu  | rements                                                | 106 |

|    |        | 4.4.1  | Chip Implementation and PCB Design                     | 106 |

|    |        | 4.4.2  | Measurement Setup                                      |     |

|    |        | 4.4.3  | Measurement Results                                    | 108 |

| 5  | Cor    | clusio | n                                                      | 114 |

| Bi | iblios | graphy |                                                        | 117 |

# List of Figures

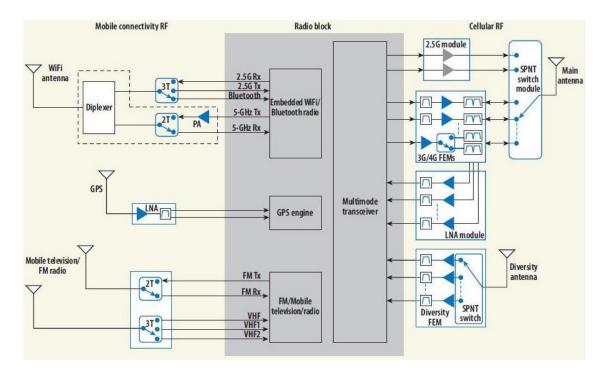

| 1.1  | Front-end architecture of a typical smartphone                                              |

|------|---------------------------------------------------------------------------------------------|

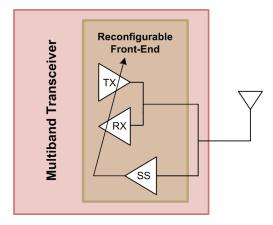

| 1.2  | Conceptual diagram of reconfigurable radio front-end                                        |

| 2.1  | Cognitive radio operating in time and frequency domains                                     |

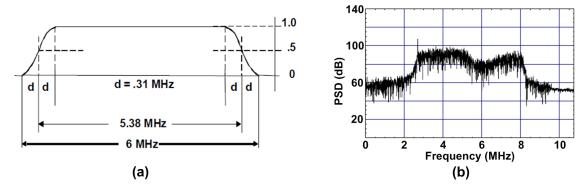

| 2.2  | Spectrum of a DTV channel: (a) ideal (pilot not shown) [7], (b) measured [8].               |

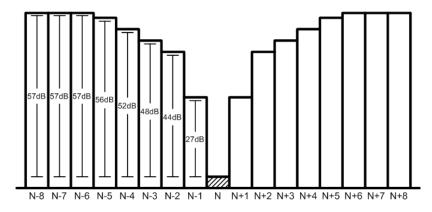

| 2.3  | ATSC blocker profile                                                                        |

| 2.4  | Energy detection on a 4 MHz-wide QPSK signal [16]                                           |

| 2.5  | ATSC pilot tone                                                                             |

| 2.6  | SCF of (a) white noise, and (b) a QPSK signal [4]                                           |

| 2.7  | Time-domain waveform and autocorrelation function of (a) a sinusoid and (b)                 |

|      | white noise                                                                                 |

| 2.8  | High level block diagram of proposed system                                                 |

| 2.9  | Illustration of subsampling with subsampling ratios of 1 and 2                              |

| 2.10 | Noise folding from subsampling: (a) unsampled spectrum, (b) sampled with $f_S$ ,            |

|      | (c) sampled with $2f_S$                                                                     |

| 2.11 | Conversion to baseband with sampling frequency set to (a) carrier frequency, (b)            |

|      | channel center frequency                                                                    |

| 2.12 | Time-domain waveform of (a) a sinusoid, (b) its autocorrelation                             |

| 2.13 | Time-domain waveform of (a) a noisy sinusoid, (b) its autocorrelation                       |

| 2.14 | Transmit signal generation in simulation                                                    |

| 2.15 | Worst case sensing scenario when target channel is (a) occupied, (b) idle 19                |

|      | Receiver modeling in simulation                                                             |

| 2.17 | Equivalent block diagram when (a) only noise is present, (b) signal and noise are           |

|      | present                                                                                     |

|      | Simulated (a) energy and (b) pilot detection at baseband                                    |

|      | Detected SNR as a function of input SNR for energy detection                                |

|      | Probability density functions for signal and noise                                          |

|      | Ideal channel energy detection: (a) $P_{FA}$ , (b) $P_D$                                    |

| 2.22 | Normalized PDF of white noise and its autocorrelation with (a) 10 <sup>6</sup> samples, (b) |

|      | $10^3$ samples                                                                              |

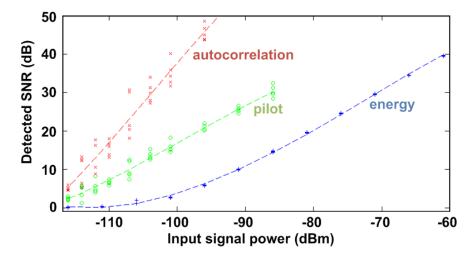

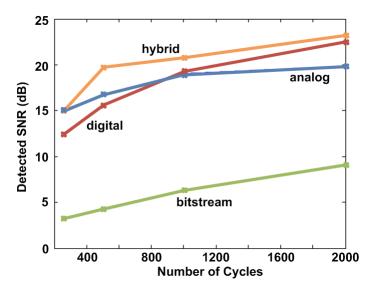

|      | Detected SNR vs. input power for all detection modes                                        |

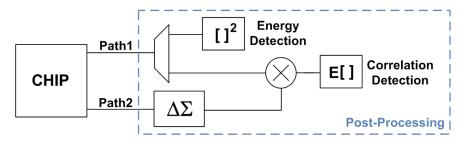

| 2.24 | Block diagram of spectrum sensing system                                                    |

| 2.25 | Block diagram of detection methods in software post-processing                      | 27 |

|------|-------------------------------------------------------------------------------------|----|

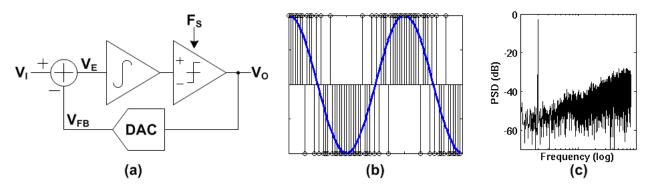

| 2.26 | Sigma-delta modulation: (a) block diagram, (b) time-domain conversion of a          |    |

|      | sinusoid, (c) $\Sigma\Delta$ noise-shaping                                          | 28 |

| 2.27 | Comparison of various correlation implementations                                   | 29 |

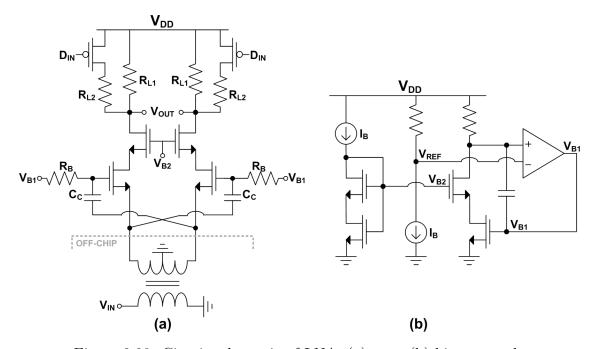

| 2.28 | Circuit schematic of LNA: (a) core, (b) bias network                                | 29 |

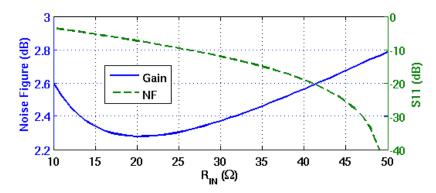

| 2.29 | LNA performance as a function of $R_{IN}$ : (a) NF, (b) S11                         | 31 |

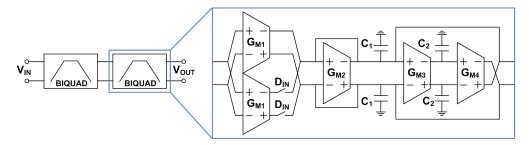

| 2.30 | Block diagram of RF tracking filter                                                 | 32 |

|      | Circuit schematic of a Gm-cell                                                      | 33 |

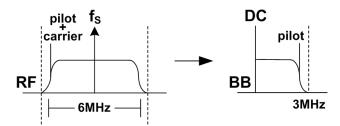

| 2.32 | Downconversion of a 6MHz UHF TV channel                                             | 34 |

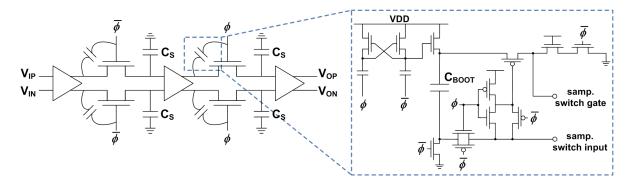

|      | Schematic of downconversion sampler                                                 | 35 |

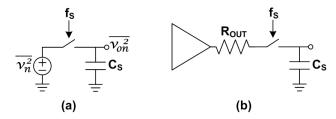

|      | Sample-and-hold noise analysis: (a) sampling switch and capacitor, (b) with buffer. | 35 |

|      | Schematic of a sampler buffer                                                       | 36 |

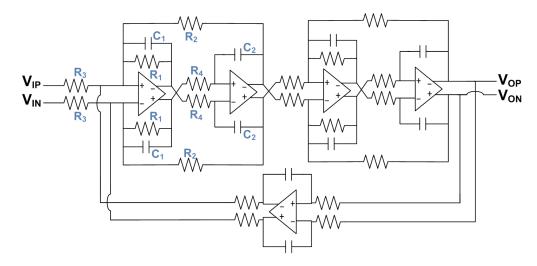

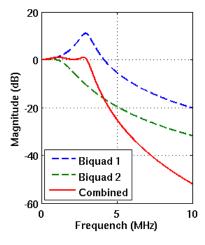

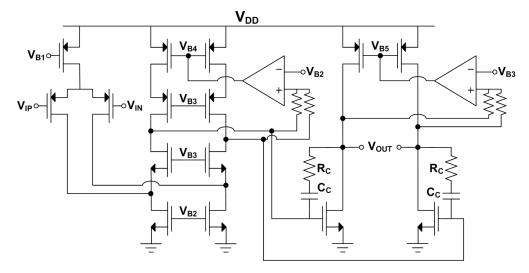

|      | Schematic of 4th order low-pass baseband filter with DC servo                       | 37 |

|      | Frequency response of each biquad along with their combined response                | 38 |

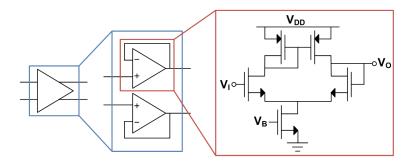

|      | Schematic of baseband operational amplifier (OpAmp)                                 | 36 |

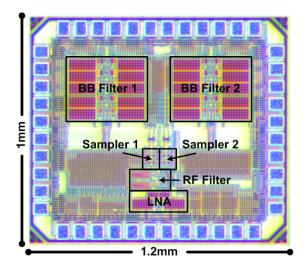

|      | Chip micrograph of implemented spectrum sensing system                              | 40 |

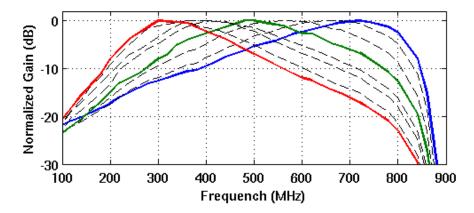

| 2.40 | Normalized gain response of RF front-end for various RF tracking filter frequency   |    |

|      | settings                                                                            | 40 |

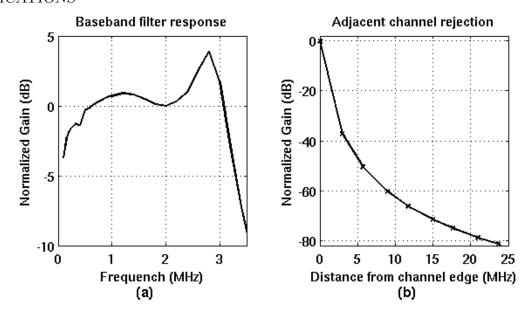

|      | Baseband gain response: (a) passband, (b) adjacent channels                         | 41 |

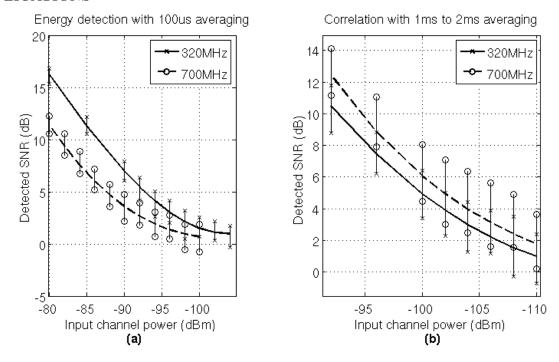

| 2.42 | Measured detected SNR as a functional of input signal power: (a) energy detec-      |    |

|      | tion, (b) correlation detection                                                     | 42 |

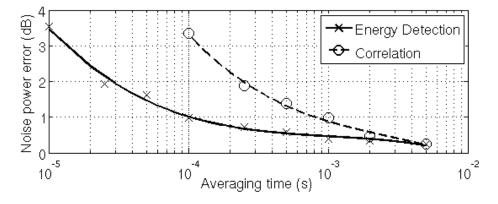

|      | Convergence of noise power with averaging time                                      | 42 |

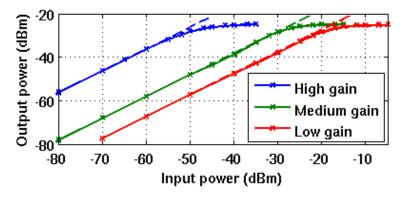

|      | P1dB linearity measurements for high and low gain modes                             | 43 |

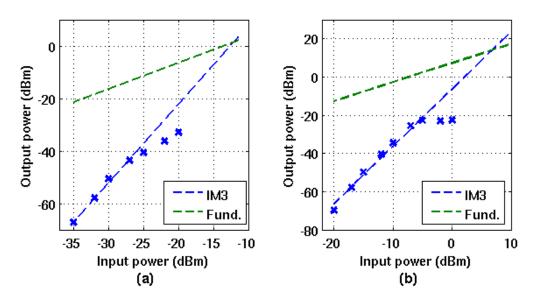

|      | IIP3 linearity measurements: (a) in band, (b) out of band                           | 43 |

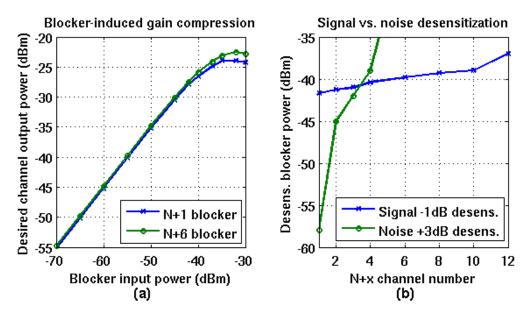

|      | pression, (b) noise vs. gain desensitization                                        | 44 |

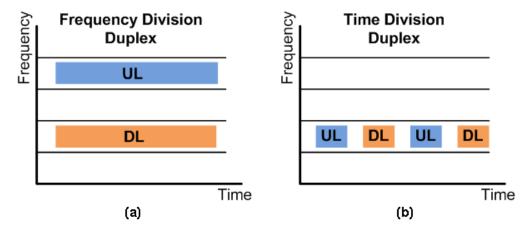

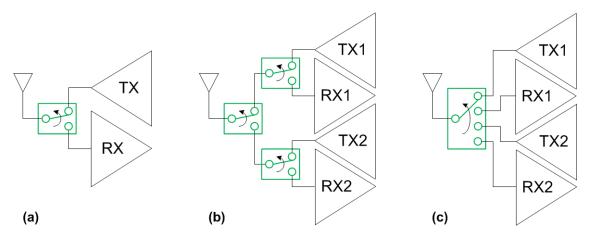

| 3.1  | Conceptual representation of (a) FDD and (b) TDD in time and frequency domains.     | 47 |

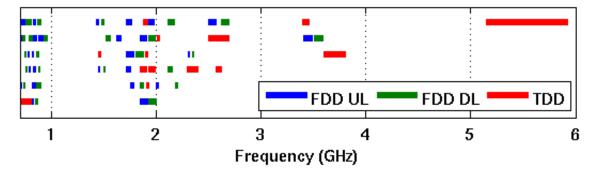

| 3.2  | LTE FDD and TDD bands from 700MHz to 6GHz                                           | 48 |

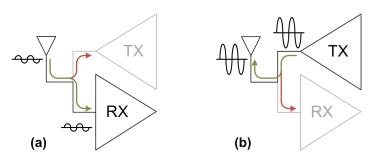

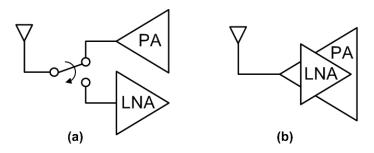

| 3.3  | Conceptual TDD front-end in (a) receive mode, (b) transmit mode                     | 48 |

| 3.4  | Example TDD front-ends with (a) SPDT switch, (b) cascaded SPDT switches,            |    |

|      | (c) SP4T switch                                                                     | 49 |

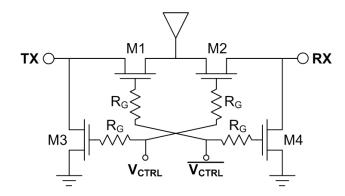

| 3.5  | Fundamental topology for a T/R switch                                               | 51 |

| 3.6  | Port-to-antenna interface in (a) active state, (b) inactive state                   | 51 |

| 3.7  | Schematic of port network in active state at RF: (a) detailed, (b) simplified       | 52 |

| 3.8  | TRSW in (a) TX and (b) RX scenarios                                                 | 53 |

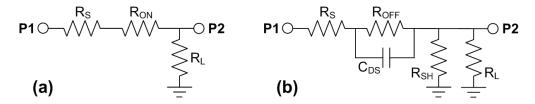

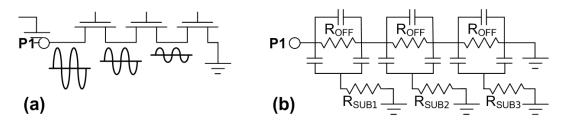

| 3.9  | Stacked switch in OFF mode: (a) schematic, (b) high-frequency circuit model         | 54 |

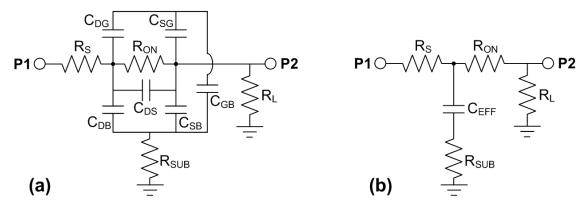

| 3.10 | Diagram of a physical NMOS switch: (a) without isolated P-well, (b) with isolated   |    |

|      | P-well, (c) circuit model of triple-well structure                                  | 55 |

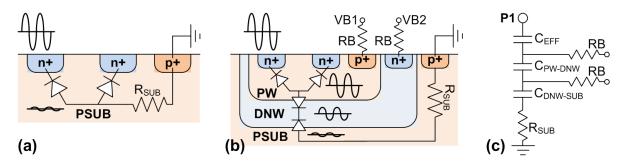

| 3.11 | Inductor-resonance TRSW: (a) schematic, (b) TX mode, (c) RX mode, (d) alter-        |    |

|      | nate topology                                                                       | 56 |

| 3.12 | Transformer-based TRSW: (a) schematic, (b) TX mode, (c) RX mode                     | 57 |

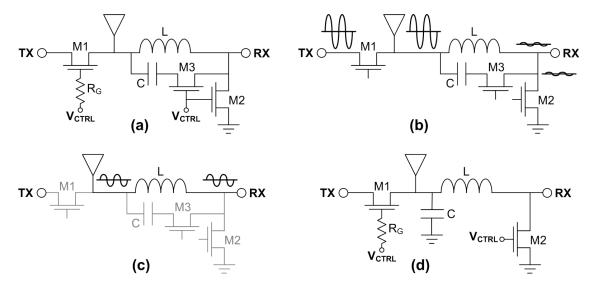

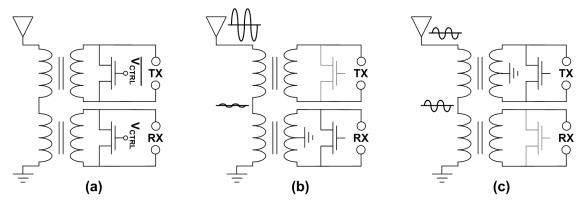

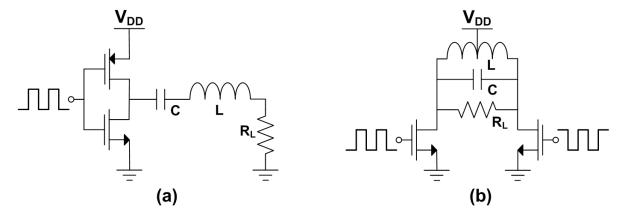

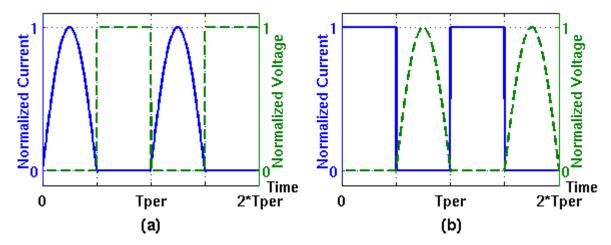

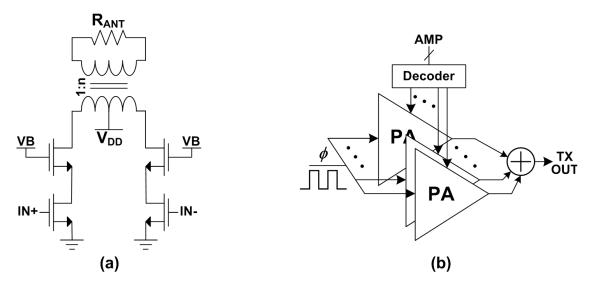

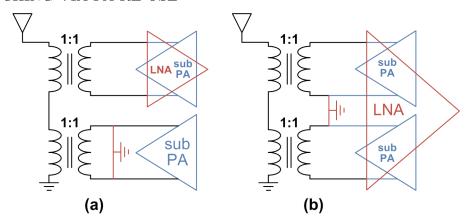

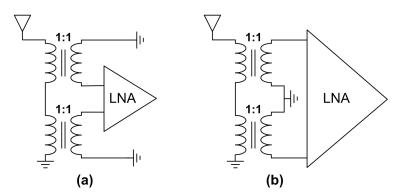

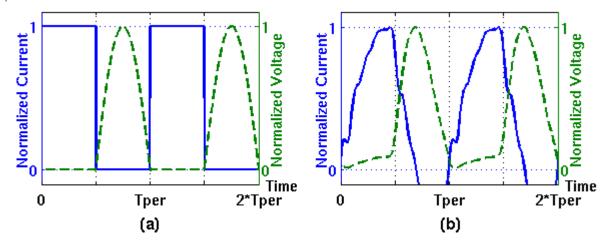

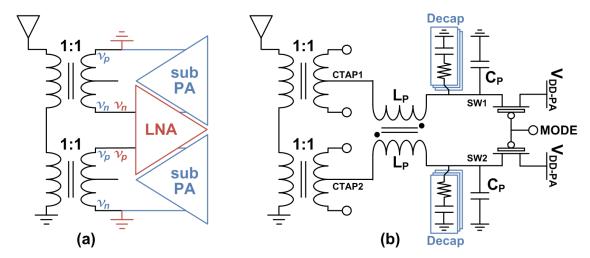

| 3.14 | Conceptual diagram of TDD front-end: (a) conventional, (b) proposed Circuit schematic of switching PA: (a) class-D, (b) inverse class-D Normalized drain current and voltage waveforms of switching PA: (a) class-D, (b) | 63<br>64   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.15 | inverse class-D                                                                                                                                                                                                          | 65         |

| 3.16 | Implementation of mixed-signal transmitters: (a) circuit schematic of a practical inverse class-D PA, (b) block diagram of polar transmitter                                                                             | 67         |

| 3.17 | PA to LNA transformation: (a) PA mode, (b) LNA mode                                                                                                                                                                      | 68         |

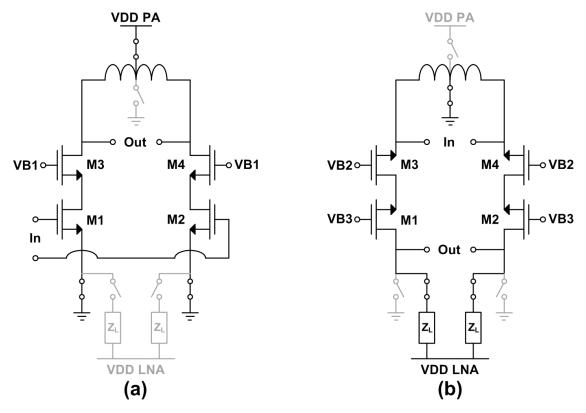

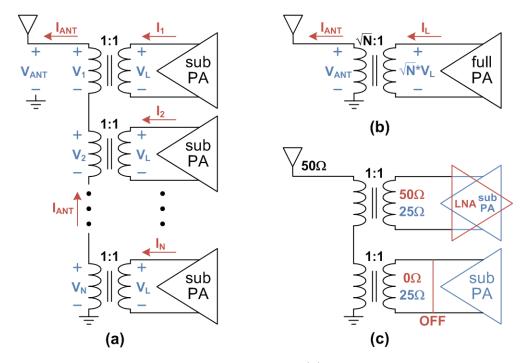

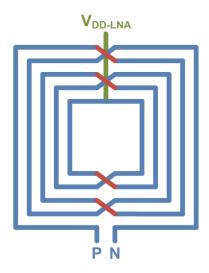

| 4.1  | Transformer-based power combining: (a) combined PA using N sub-PAs and stacked 1:1 transformers, (b) equivalent PA with single transformer, (c) reconfigurable impedance for PA/LNA                                      | 72         |

| 4.2  | Re-using PA as transformer switch: (a) PA in standard configuration, (b) PA re-configured to short transformer.                                                                                                          | 74         |

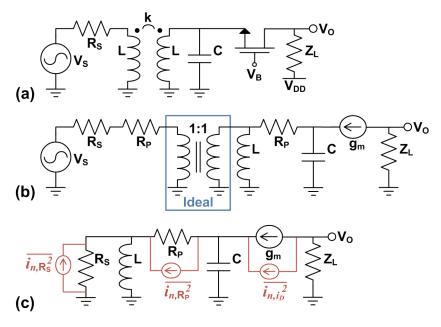

| 4.3  | LNA noise model: (a) CG LNA with source transformer, (b) equivalent circuit model, (c) approximate noise model                                                                                                           | 75         |

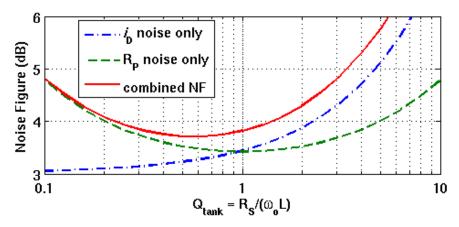

| 4.4  | LNA NF as a function of $Q_{tank}$                                                                                                                                                                                       | 77         |

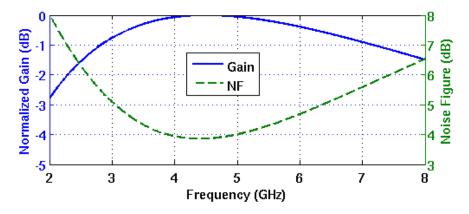

| 4.5  | Frequency response and NF of LNA due to front-end tank                                                                                                                                                                   | 77         |

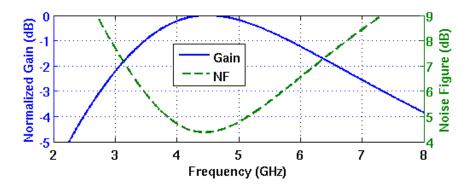

| 4.6  | Front-end noise models for (a) inductor parasitic resistance and (b) capacitor switch resistance                                                                                                                         | 78         |

| 4.7  | Stacked transformer architecture: (a) conventional, (b) transformer-reuse                                                                                                                                                | 80         |

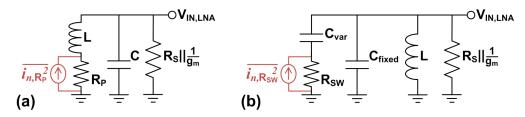

| 4.8  | Frequency response and NF of LNA with transformer-reuse                                                                                                                                                                  | 80         |

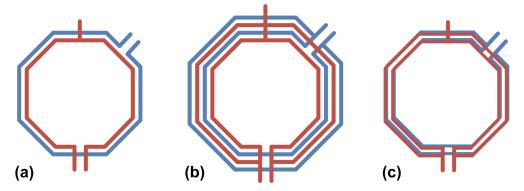

| 4.9  | Transformer layout implementations: (a) single loop, (b) parallel loops, (c) broadside coupling.                                                                                                                         | 82         |

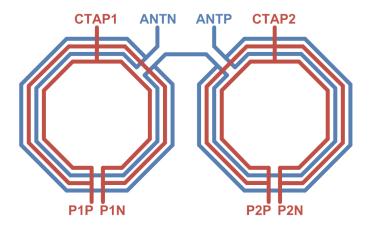

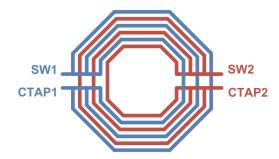

| 4 10 | Layout implementation of stacked transformer                                                                                                                                                                             | 83         |

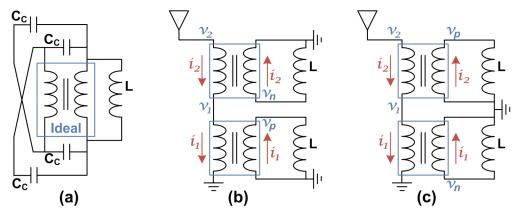

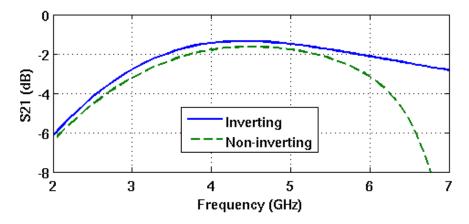

|      | Stacked transformer in LNA mode with (a) inverted coupling, (b) non-inverted coupling                                                                                                                                    | 84         |

| 4.12 | SRF models for (a) single 1:1 transformer, (b) inverting stacked transformer, (c)                                                                                                                                        |            |

| 112  | non-inverting stacked transformer                                                                                                                                                                                        | 85<br>85   |

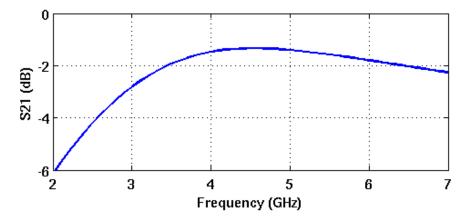

|      | S21 of stacked transformer in PA mode                                                                                                                                                                                    | 86         |

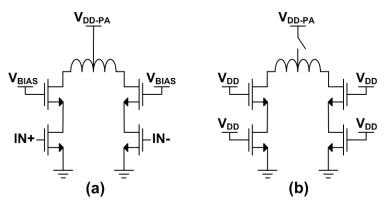

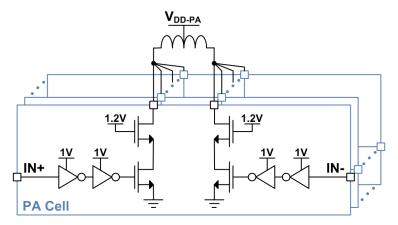

|      | Schematic of a PA cell                                                                                                                                                                                                   | 87         |

|      | PA drain current and voltage waveforms: (a) theoretical ideal, (b) actual imple-                                                                                                                                         | 01         |

| 1.10 | mentation                                                                                                                                                                                                                | 88         |

| 4.17 | Layout diagram of full PA core                                                                                                                                                                                           | 88         |

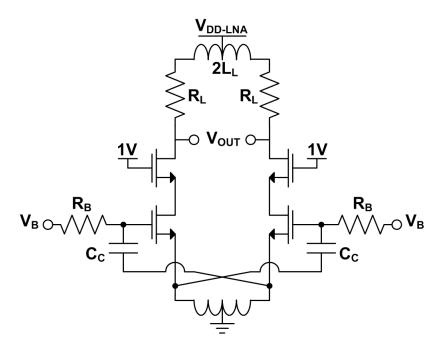

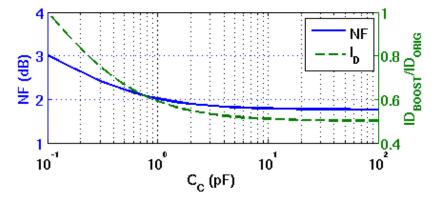

|      | Schematic of LNA architecture                                                                                                                                                                                            | 89         |

|      | NF and normalized bias current of capacitively cross-coupled CG LNA as a function of $C_C$ , for $C_{GS} = 100$ fF and $C_{G0} = 200$ fF                                                                                 | 90         |

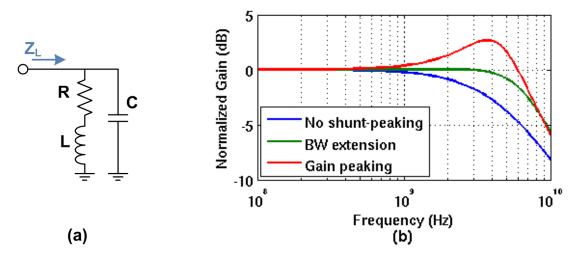

| 4 20 | Shunt-peaking load: (a) schematic, (b) frequency response                                                                                                                                                                | 91         |

|      | Gain-peaking parameters as a function of $\alpha$ : (a) normalized peak gain, (b) -1dB bandwidth, (c) NF                                                                                                                 | 92         |

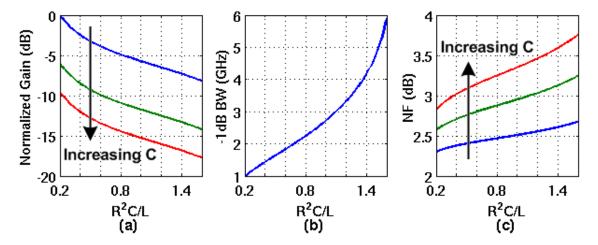

| 1 22 | Layout of shunt-peaking inductor                                                                                                                                                                                         | 93         |

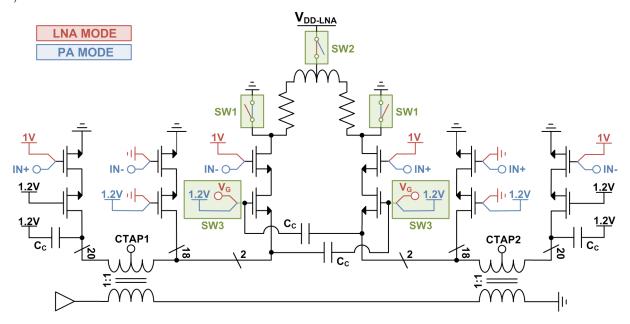

|      | Schematic of PA core in LNA mode.                                                                                                                                                                                        | 93<br>94   |

| 0    | ~ CIII COI CIII III COI CIII III COI CIII III                                                                                                                                                                            | <i>U</i> I |

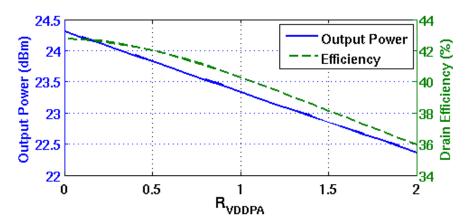

| 4.24 | PA peak output power and drain efficiency as a function of supply switch resistance.    | 94  |

|------|-----------------------------------------------------------------------------------------|-----|

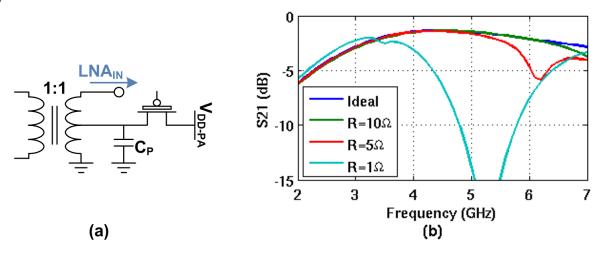

| 4.25 | Parasitic OFF capacitance of PA supply switch: (a) schematic, (b) S21 of front-         |     |

|      | end transformer in LNA mode                                                             | 95  |

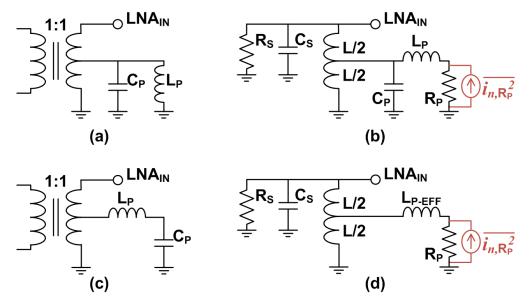

| 4.26 | Options for addressing center tap capacitance $C_P$ : (a) parallel resonance, (b) noise |     |

|      | model for parallel resonance, (c) inductor choke, (d) noise model for inductor choke.   | 96  |

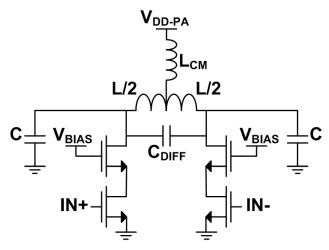

| 4.27 | Schematic of PA core showing differential and common mode output resonance.             | 97  |

| 4.28 | Design of center tap choke: (a) polarity in PA/LNA modes, (b) schematic of PA           |     |

|      | supply and center tap network                                                           | 97  |

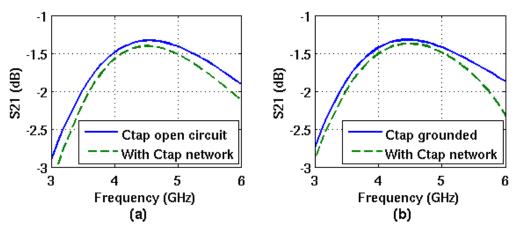

| 4.29 | Layout of center tap choke transformer                                                  | 98  |

| 4.30 | S21 of front-end transformer with center tap network: (a) LNA mode, (b) PA              |     |

|      | mode                                                                                    | 99  |

| 4.31 | Schematic of PA/LNA core                                                                | 100 |

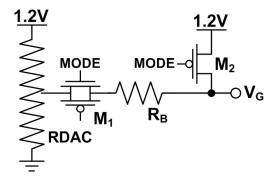

| 4.32 | Schematic of LNA bias network                                                           | 101 |

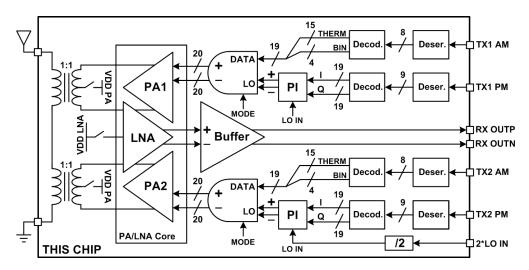

| 4.33 | Block diagram of implemented system top-level                                           | 102 |

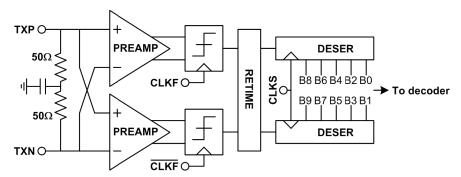

| 4.34 | Block diagram of TX data deserializer                                                   | 103 |

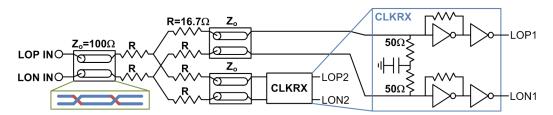

| 4.35 | Schematic of high-frequency LO splitter and clock receiver                              | 103 |

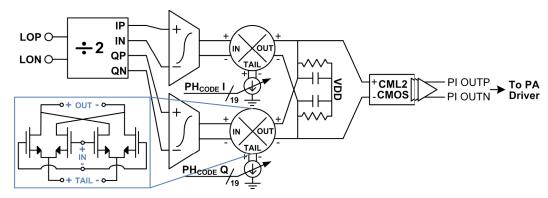

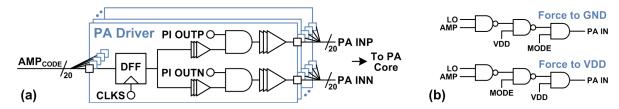

| 4.36 | Block diagram of phase interpolation path                                               | 104 |

| 4.37 | Block diagram of PA driver: (a) base, (b) with added logic for T/R mode switching.      | 104 |

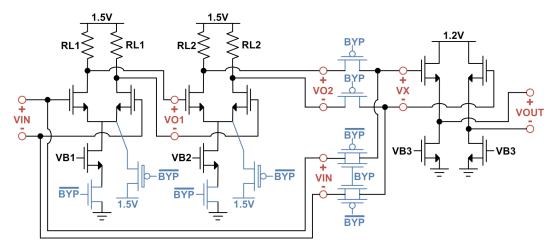

|      | 1                                                                                       | 105 |

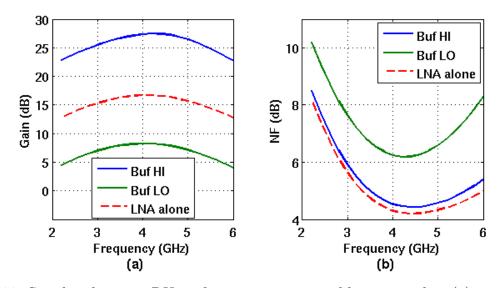

| 4.39 | Simulated system RX performance in gain and bypass modes: (a) gain, (b) NF.             | 105 |

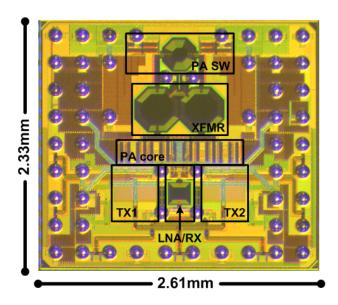

| 4.40 | Chip micrograph of implemented TDD system                                               | 106 |

| 4.41 | PCB implementation: (a) layer stack-up, (b) micrograph of die area from fabri-          |     |

|      | cated PCB                                                                               | 107 |

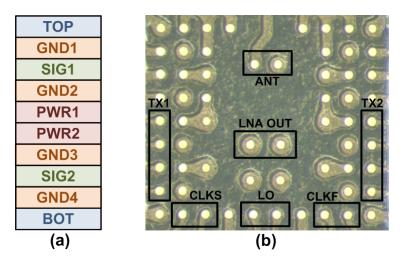

| 4.42 | Measurement setup in (a) PA mode, (b) LNA mode                                          | 108 |

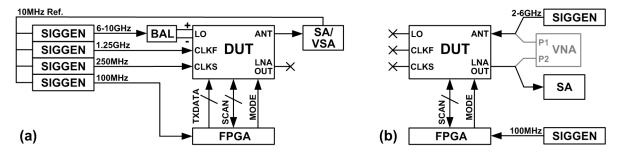

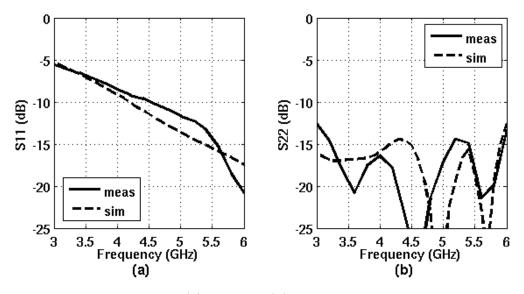

|      | ( ) 1                                                                                   | 109 |

|      | ( ) 1                                                                                   | 109 |

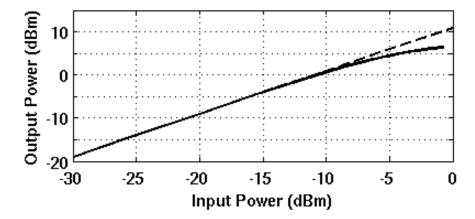

| 4.45 | Measured RX output power as a function of input power                                   | 110 |

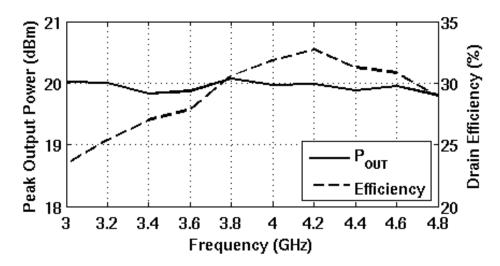

| 4.46 | Measured peak PA output power and peak drain efficiency across frequency                | 110 |

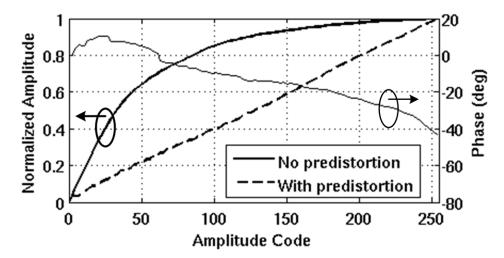

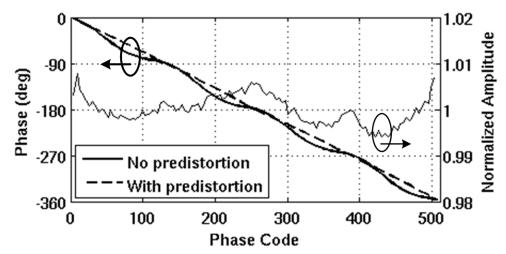

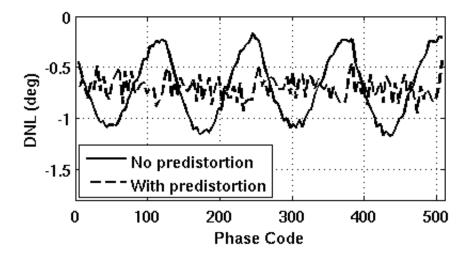

| 4.47 | Measured transmitter AM-AM and AM-PM performance across AM codes                        | 111 |

|      | ı                                                                                       | 112 |

|      |                                                                                         | 112 |

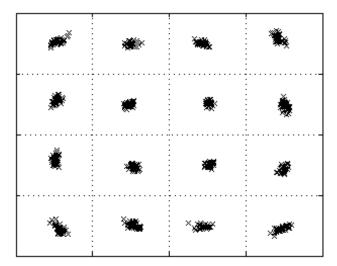

| 4.50 | Sample measured QAM16 constellation with $P_{OUT} = 16.4$ dBm                           | 113 |

# List of Tables

| 2.1 | Summary of spectrum sensing receiver measurements | 45 |

|-----|---------------------------------------------------|----|

| 3.1 | Summary of integrated TRSW works                  | 62 |

| 4.1 | Comparison of transformer layout implementations  | 83 |

### Acknowledgments

First, I would like to thank my research advisor Prof. Borivoje Nikolic for his unyielding support and encouragement. He has been extremely accommodating and sensitive to my needs throughout my graduate school career, and has been tremendously helpful for my personal and professional development. It has been a pleasure to work with him.

I would also like to thank Prof. Ali Niknejad and Prof. Elad Alon for many helpful technical discussions, for providing research guidance, and for being great teachers in the classroom. I would further like to thank Prof. Dave Allstot, for valuable research discussions and feedback, and Prof. Paul Wright, for serving on my qualification and dissertation committees. Thanks also to industrial visitors Dr. Christopher Hull, Dr. Vason Srini, and Dr. Sudhir Aggarwal for being involved in my work and providing helpful feedback.

I am very grateful to all current and past BWRC staff for efficiently handling all the financial, administrative, and technical infrastructure aspects of academic research. Their efforts make BWRC an engaging, bright, and comfortable work environment. I would especially like to thank James Dunn for working closely with me on the TDD project and providing essential PCB and vendor support, even through all the frustrating delays and revisions. Much thanks also to Brian Richards, Fred Burghardt, Deirdre McAuliffe-Bauer, Leslie Nishiyama, Olivia Nolan, Sarah Jordan, and Candy Corpus.

I would like to acknowledge the funding sources that have supported my research as well as me personally, including NSF GRFP, C2S2, and DARPA RF-FPGA program (HR0011-12-9-0013). Special thanks to TSMC University Shuttle Program for chip fabrication and enabling us to perform meaningful integrated circuits research.

I would like to thank Amanda Pratt, who was my research partner on the TDD project. I am grateful to her not only as my project partner, but also for being a source of emotional support and understanding. Thanks to Angie Wang and Bonjern Yang for their direct contributions to the TDD project as well. I would also like to acknowledge all the RF/analog designers at the BWRC who have helped me with technical discussions over the years, and who were always open, friendly, and receptive to my questions and requests. Much thanks to Charles Wu, Will Biederman, Dan Yeager, Steven Callender, Nai-Chung Kuo, Sameet Ramakrishnan, Luke Calderin, Andrew Townley, Ashkan Borna, Yue Lu, Yida Duan, and Hanh-Phuc Le.

In addition to some already mentioned, I would like to thank the following BWRC students and alumni for their camaraderie and friendship. They made my graduate school experience cheerful and fun in joyful times, and they provided much needed empathy and support in more trying times. Thanks to Matt Weiner, Matt Spencer, Milos Jorgovanovic, Katerina Papadopoulou, Jaehwa Kwak, Angie Wang, Pi-Feng Chiu, Rachel Hochman, Mira Midenovic-Misic, Dusan Stepanovic, and Vinayak Nagpal.

I would like to thank my parents for their continuous support, encouragement, and guidance. They instilled in me the values of hard work, perseverance, and inner strength, and it is due to their efforts and their example that I was able to both start and complete this degree.

Lastly, I would like to thank my husband. Christopher, your support and patience have meant the world in my time of focus and stress. So much of my achievement rests upon your sacrifices, that I'd totally give you this Ph.D. if I could. You even wrote this paragraph, perhaps the best of the entire thesis. Your thoughtfulness knows no bounds.

# Chapter 1

# Introduction

Modern and future mobile devices must support increasingly more wireless standards and frequency bands. A current smartphone, for example, generally includes wireless functionality for not only cellular standards, but also Wi-Fi, Bluetooth, GPS, and depending on global region, possibly also FM radio and mobile television. Furthermore, there can be a myriad of different standards and bands even within each wireless application. Wi-Fi can include 802.11a/b/g/n standards and both 2.4GHz and 5GHz frequency bands. Cellular functionality must include the various 2G/3G/4G standards, and 4G LTE alone has more than 40 frequency bands globally spanning 700MHz to 6GHz.

Fig. 1.1 illustrates the typical front-end architecture of a modern smartphone [1]. As shown, multi-standard, multi-band co-existence is currently enabled by a multitude of discrete off-chip components. These include external low noise amplifiers (LNAs) and power amplifiers (PAs), transmit/receive (T/R) and band switches, duplexers, diplexers, and RF filters.

The discrete components use expensive materials, such as GaAs and SiGe processes or mechanical surface-acoustic wave (SAW) devices, to achieve the necessary loss, noise, and filtering performance specifications that could not be attained in bulk silicon CMOS. They are targeted towards specific bands and applications, generally narrowband, and not reconfigurable. Furthermore, they are bulky and expensive. As transceivers are required to accommodate an increasing number of wireless bands, the required number of discrete components increases accordingly, resulting in greater bill of materials (BoM) cost and printed circuit board (PCB) area. Thus, current commercial mobile devices are either regional, where only bands in their intended geographical region of operation are supported, or they support few bands from each region.

The concept of a reconfigurable radio refers to a wireless system that is multi-standard, multi-band, and self-adapting to utilize available bands in the most spectrum efficient and energy efficient manner. The ideal reconfigurable radio differs from traditional transceivers in two fundamental ways. First, it should be able to reconfigure itself to transmit and receive

Figure 1.1: Front-end architecture of a typical smartphone.

on a variety of frequencies, bandwidths, and standards. This mean eliminating inflexible, bulky, and narrowband discrete front-end components. Instead, there should be a wideband and fully-integrated front-end, which allows for the flexibility and the efficient software or digital control that exemplifies reconfigurability.

Thus, a first major step towards the realization of a reconfigurable radio is to develop techniques to enable wideband front-end integration. With a truly integrated wideband transceiver, the system becomes more scalable and cost effective. Transceiver systems can be empowered to support the myriad of current and future wireless bands across the globe without the constraints of exponentially increasing cost and area from discrete front-end components.

The second fundamental aspect of a reconfigurable radio is its cognitive ability and spectrum awareness. It must have knowledge of its spectrum environment in order to select the most efficient frequency bands to operate on, and the sensing of the spectrum must be fast and responsive to rapidly varying environmental factors. Spectrum sensing can be used for optimal channel selection and dynamic blocker suppression, and spectrum awareness enables energy efficiency by liberating the transceiver from having to always operate assuming worst case conditions. Since spectrum sensing is an auxiliary function separate from the core transceiver, it should, in addition to being robust and fast, add low complexity and low overhead to the system.

Moreover, spectrum sensing and cognitive capabilities have also been proposed for spectrum re-use, where unlicensed users re-use licensed bands when their primary users are not present [2]. This scheme takes advantage of the fact that no band is being used everywhere at all times, and spectrum utilization can be significantly increased by allowing unlicensed users onto licensed but sparsely used bands. If every band can be filled to near capacity in this way, that could potentially results in an order of magnitude increase in spectrum efficiency. In a spectrum re-use scenario, however, non-interference with primary licensed users must be guaranteed. Thus, robust spectrum detection with high sensitivity would also be required in addition to rapid sensing time and low overhead.

Figure 1.2: Conceptual diagram of reconfigurable radio front-end.

Fig. 1.2 illustrates a reconfigurable radio front-end conceptually. A multi-band transceiver with wideband, fully-integrated RF front-end connects directly to the antenna with no discrete, fixed-band components, while an efficient, low power spectrum sensing receiver provides real-time environmental knowledge to enable self-adaptation and dynamic reconfigurability.

## 1.1 Scope of Work

This work focuses on two specific aspects of the broad goal towards reconfigurable radios outlined above. First, we investigate optimal circuit and architectural techniques to perform high sensitivity spectrum sensing with minimal complexity and overhead. Our analysis of spectrum sensing specifically targets the ultra-high frequency (UHF) TV band, as it is one of the few bands in which the operation of unlicensed cognitive radio devices has been approved by the Federal Communications Commission (FCC) [3]. We design and implement a high-sensitivity, low power spectrum sensing receiver for UHF TV band applications as a demonstration of the feasibility of robust integrated sensing for mobile applications.

In the second part of this work, we develop a novel integrated T/R switching technique. T/R switches make up a prominent segment of discrete front-end components, and integrated wideband solutions with comparable performance have not yet been demonstrated. We propose an integrated T/R switching method in which the PA can be transformed into and re-used as an LNA, and as proof-of-concept for the proposed technique, we design and implement a wideband integrated time division duplex (TDD) front-end utilizing the PA re-use switching technique. We demonstrate the feasibility of wideband, integrated T/R switching as a stepping stone towards greater front-end integration and reconfigurability.

## 1.2 Thesis Organization

The following chapters of this thesis are organized as follows:

Chapter 2 describes the development of a spectrum sensing receiver for TV band applications. This chapter first reviews the characteristics of the UHF TV band and the FCC requirements for cognitive sensing in the band. Next, an analysis of detection methods and past works are presented. Finally, we describe the design and present the measured results of the implemented spectrum sensing receiver.

Chapter 3 presents the fundamental concepts of T/R switching and proposes an innovative technique for integrated wideband T/R switching. This chapter analyzes the constraints and challenges of T/R switches and presents a survey on current state-of-the-art. We then describe our proposed T/R switching scheme, in which the PA is re-used as an LNA, and how this switching method alleviates the drawbacks of existing techniques.

Chapter 4 describes the design and implementation of a wideband TDD front-end utilizing the proposed PA re-use T/R switching technique. Particular focus is put on the design of a shared PA/LNA front-end transformer, the method of PA/LNA transformation in the shared PA/LNA core, and the power and mode switches used to enable PA/LNA transformation. We then describe the architecture of the full implemented transceiver, some considerations for PCB design, and finally, measured results from the implemented chip.

Chapter 5 summarizes this work and discusses possible future directions.

# Chapter 2

# Low-Power Spectrum Sensing for Cognitive Radio Applications

With the growth of mobile data usage and as users crowd existing cellular bands, the FCC has been experimenting with cognitive radio operations in an effort to improve spectrum utilization and efficiency. Fig. 2.1 illustrates conceptually how a cognitive radio would operate in time and frequency domains [4]. At fixed time intervals, shown in yellow, the cognitive radio would scan the spectrum and identify idle bands, shown in white. It would then operate on those bands, shown in blue, until the return of a primary user has been detected. When this happens, the cognitive radio would vacate the re-occupied band for other bands that are now idle. Since cognitive radios are unlicensed devices operating in licensed bands, spectrum sensing is essential in guaranteeing non-interference with the activities of the bands' primary users.

Figure 2.1: Cognitive radio operating in time and frequency domains.

In 2008, the FCC approved the operation of unlicensed cognitive radio devices in the TV bands, with unlicensed mobile devices approved in the UHF TV band [3]. However, two

years later, the FCC dropped the spectrum sensing requirement for unlicensed TV band devices (TVBDs) due to concerns over its viability, and instead ordered TVBDs to identify idle bands by accessing a geolocation database [5]. One major contribution to the FCC's decision to drop spectrum sensing requirements for TVBDs is the failure thus far of any system to meet the detection specifications set by the FCC.

During a demonstration of industry prototypes conducted in 2008, no system achieved the necessary detection sensitivity of -114 dBm in real world scenarios [6]. In academic research, on the other hand, while there has been much work done on theory topics like detection algorithms and cooperative sensing, there has been a lack of work on physical front-end designs for spectrum sensing applications. Some works may embed sensing functionality into receiver designs, but since the sensitivity required for sensing is much higher than that of conventional receivers, these works all fail to achieve the necessary detection sensitivity as well. Thus, a system targeted specifically for spectrum sensing achieving high detection sensitivity with good dynamic range and low power remains elusive.

Spectrum sensing offers much greater flexibility and lower overhead than a geolocation database or other cognitive radio management methods, It will play a role not only in the future of cognitive radios in the TV band, but also in the path towards general purpose reconfigurable radios. In fact, spectrum sensing functionality is already under consideration in the preliminary standards for 5G. To demonstrate the feasibility of high sensitivity, low power spectrum sensing in mobile devices going forward, we present in this chapter a spectrum sensing receiver for TV band cognitive radio applications.

## 2.1 Spectrum Sensing in the TV Band

In this section, we first look at the characteristic of the UHF TV band in Sec. 2.1.1 and discuss the IEEE 802.22 standard for TV white space sensing. Next, Sec. 2.1.2 surveys existing work that has been done on spectrum sensing for mobile applications. Finally, Sec. 2.1.3 analyzes an assortment of spectrum sensing techniques and their applicability to our application.

#### 2.1.1 UHF TV Band and IEEE 802.22

In the United States, the UHF TV band currently spans from 470MHz to 698MHz, and it is composed of 38 6MHz-wide channels. After the full transition to digital TV (DTV) was completed in 2009, all channels became purely digital, adhering to the Advanced Television Systems Committee (ATSC) standard.

According to the ATSC standard, terrestrial DTV uses 8-level vestigial sideband (8VSB) modulation. Within each 6 MHz channel, data power is spread over the center 5.38MHz bandwidth, giving a 10.76MSymbol/s datarate. Each channel has two 610kHz-wide tran-

sition regions, one on each edge, from the response of the root raised cosine filters [7]. In addition, each channel also has a pilot tone at the frequency of the buried carrier, 310kHz away from the lower channel edge. The pilot, within its narrow 10kHz bandwidth, has a power that is 11.3dB lower than the total data power of the 6MHz channel [7]. Fig. 2.2 illustrates the ideal and measured spectrums of a DTV channel.

Figure 2.2: Spectrum of a DTV channel: (a) ideal (pilot not shown) [7], (b) measured [8].

The minimum signal-to-noise ratio (SNR) required for decoding an ATSC signal is set at 15.2dB. With a maximum adjacent channel splatter of -46.5dBc on the transmit side and a margin of about 4 dB, the adjacent channel blocker power is limited to a maximum of 27dB higher than the wanted signal power in order to maintain sufficient SNR in the wanted channel. The maximum blocker power grows to 44dB higher for the N+/-2 channel, and increases by 4dB with each additional channel spacing until the N+/-6 channel [7]. The overall ATSC blocker profile for weak signals is illustrated below in Fig. 2.3.

Figure 2.3: ATSC blocker profile.

The thermal noise in a 6MHz channel is about -105dBm. Given the required decode SNR of 15.2dB and a margin for receiver noise figure, the minimum sensitivity for DTV receivers,

or the minimum input energy of a decodable signal, is set at -83dBm [9]. However, since the sensitivity requirement must be met under worst case test conditions, many TV tuners in practice have higher sensitivity under common, realistic operating conditions.

In addition to DTV itself, wireless microphones also operate in the UHF band in vacant TV channels. There is no homogenized standard for wireless microphones, but they are usually narrowband, frequency-modulated (FM) signals with a bandwidth of 200kHz [8]. Although wireless microphones are also unlicensed devices, they have priority over TVBDs and are considered primary users.

The IEEE 802.22 standard governs Wireless Regional Area Networks (WRAN), which were developed to operate cognitively in the TV bands. The 802.22 work group, tasked with developing the standard, studied the geographical characteristics of base stations and primary receivers, and the interference and fading characteristics of wireless TV signals. The group then set sensing requirements for TVBDs to ensure an acceptably low level of interference with primary receivers.

In its preliminary standard published in 2008, the 802.22 work group set required sensing sensitivity level to -114 dBm for DTV in its 6 MHz channel bandwidth, for analog TV in its 100kHz carrier bandwidth, and for wireless microphone in a 200kHz bandwidth [3]. The sensitivity levels assume 0dBi antenna gain, and that the receiver antenna is outside and at least 10m above ground, relatively free of obstructions. Since analog TV transmissions no longer exist in the U.S. and wireless microphones are under consideration to be moved into its own dedicated channels, we will focus only on DTV sensing in this work.

The challenge of spectrum sensing arises mainly from the -114 dBm sensitivity requirement, which is much lower than that of a standard receiver and is significantly below the -105dBm thermal noise floor in a 6MHz channel. Furthermore, sensing must occur with a low power overhead for mobile applications, and within a reasonably short sensing time. IEEE 802.22 set the sensing interval to 2 seconds [10]; while this is a lengthy period, the actual sensing time should only be a small fraction since any time spent sensing cannot be spent transmitting and receiving on the detected idle channels. Additionally, IEEE 802.22 set both the probabilities of missed detection and false alarm to 0.1 [10]. Again, while these are relatively lax standards, it is in the interest of a cognitive radio system to minimize these probabilities for operational efficiency.

#### 2.1.2 State of the Art and Related Works

During the development of its WRAN policy, the FCC solicited TVBD prototypes for laboratory and field testing. Five such devices, submitted by Adaptrum, Institute for Infocomm Research, Microsoft, Motorola, and Philips Electronics, were tested in 2008. All prototypes reliably detected -114dBm clean DTV signals in laboratory conditions; however, the sensitivities of the prototypes severely degraded, some up to 60-70dB and others to the point of

malfunction, when given real world conditions and the presence of interference [6]. The failure of the prototypes contributed to the FCC's ultimate decision to drop spectrum sensing requirements for TVBDs.

Aside from their less than desirable performance, the prototypes were designed as bulky and high-powered stationary devices analogous to traditional TV tuners. Detection was performed with power-hungry and time-consuming digital signal processing that put the shortest detection time at 0.1 seconds per channel, and the longer ones at tens of seconds per channel [6]. All of these factors make it evident that alternative approaches are necessary.

In the space of spectrum sensing for mobile devices, the first major work eliminated the need for complex digital signal processing as well as the preceding high-bandwidth, high-resolution analog-to-digital converter (ADC) by using analog correlation [11]. The work cross-correlated the downconverted receive signal with a window waveform, which effectively acted as an easily-tunable narrowband filter in the analog domain. However, since only energy detection was performed on the filtered signal, the sensitivity was limited by the noise floor to -74dBm, which is no better than the sensitivity of standard TV band receivers. Furthermore, the receiver in [11] consumed 180mW during both sensing and receive modes, whereas ideally, the sensing overhead should be much less than the power used for standard receiver operations.

The receiver front-end in a more recent work [12] was able to improve upon the performance of [11], achieving -84dBm detection sensitivity while consuming only 30-44mW. However, while [12] had a state-of-the-art, well-designed RF front-end that achieved good linearity, noise figure, and harmonic rejection with low power, nothing separate or different was dedicated to spectrum sensing functionality save the design of the received signal strength indicator (RSSI) block itself. Thus, the detection sensitivity, while an improvement, was still constrained by the noise floor and no better than that of standard receivers.

The work in [13] proposed an architecture that cross-correlates the received signal from two identical, parallel front-end paths. This results in uncorrelated front-end electronic noise that could ideally average out to zero, effectively lowering the receiver noise figure without harming linearity or dynamic range. The receiver achieved a 4dB noise figure (corresponding to an estimated detection sensitivity of -110dBm) and 89dB of spurious-free dynamic range (SFDR) in a 1MHz bandwidth. This performance, however, came at the cost of high power, due to the use of two full analog front-ends as well as complex digital signal processing (DSP) performing fast Fourier transforms (FFTs) and correlation. Not even including the power of two 14-bit ADCs, the receiver consumed 191mW, which is much too high for mobile applications.

In addition, the work in [13] relied on off-chip discrete components and signal processing in software. Only the RF front-ends of the two receivers were integrated [14]. The analog baseband circuitry was implemented with discrete PCB components, while the ADC and

DSP functions were performed in software.<sup>1</sup> A fully integrated spectrum sensing receiver with high sensitivity and good dynamic range has therefore not yet been demonstrated.

The work in [15], in contrast to previous works, sought to demonstrate that spectrum sensing using digital signal processing could be performed in a fast and low power manner. The digital baseband processor in [15] achieved a detection sensitivity of -115dBm with a detection period of 50ms while consuming only 7.4mW. However, in order to obtain this sensitivity, the processor required digital inputs with 20 bits of precision. Thus, while the processing power itself is low, the power that would be consumed by the RF front-end to provide this 20-bit high dynamic range input would certainly be prohibitively high.

### 2.1.3 Detection Techniques

There have been several proposed techniques to detect the presence of a signal or lack thereof. These methods have been analyzed extensively in theoretical literature, but we now evaluate them for their feasibility and applicability to our specific goal of sensing in the TV band.

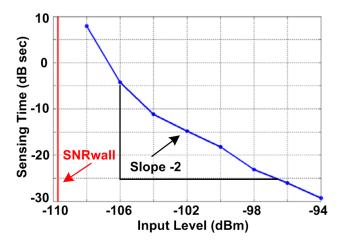

The fastest and simplest detection method is energy detection, where we merely measure the received power. This can be done non-coherently, with knowledge of only the center frequency and the bandwidth of the target signal, and without any complex algorithms or processing. Simple energy detection, however, is incapable of distinguishing signal power from noise power, and hence it fails to detect in highly negative SNR regimes where signal is buried far under noise. For example, [16] evaluated the effectiveness of energy detection on a 4-MHz-wide QPSK signal, and the results are shown in Fig. 2.4.

Figure 2.4: Energy detection on a 4 MHz-wide QPSK signal [16].

<sup>&</sup>lt;sup>1</sup>The power consumption reported in [13] included off-chip components and estimated power for DSP processes. The integrated RF front-ends alone consumed 41-66mW [14].

The authors in [16] looked at sensing time versus input signal power with a constant false alarm rate of 5% and a detection rate of 60%. We see in Fig. 2.4 that even using this extremely lax probability of detection, there exists an SNR wall below which detection is impossible given infinite sensing time. Furthermore, the sensing time remains prohibitively long for at least 10dB above the SNR wall. Thus, alternative detection methods are necessary if we seek to sense down to the -114dBm level.

Since we are targeting sensing specifically at ATSC signals, we can take advantage of certain characteristics specific to ATSC signals. One such characteristic is the sinusoidal pilot tone. As shown in Fig. 2.5, the pilot in its narrow bandwidth has a higher SNR than the signal of the entire channel. Since the pilot is at a known position within the channel, we could simply narrow the bandwidth of detection to just that of the pilot, and gain higher sensitivity with energy detection.

Figure 2.5: ATSC pilot tone.

However, while pilot energy detection can achieve a higher sensitivity, it still has the same fundamental noise-floor limitations as channel energy detection. In addition, when dealing with such a narrow bandwidth, frequency offsets can be problematic and sharp filtering that approximates a brick-wall response is difficult to realize. These issues will all degrade the sensitivity further from the theoretical limit, making other, more robust approaches necessary.

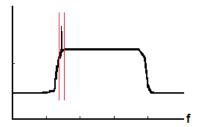

A more robust detection method, cyclostationary feature detection, takes advantage of the fact that human-made, modulated signals are fundamentally different from noise in that they usually exhibit some kind of periodic behavior, either from carrier tones, cyclic prefixes, or other features. This periodicity can be extracted using a spectral correlation function (SCF), which measures the density of correlation between all the spectral components in a signal [4]. The SCFs for white noise and for a QPSK signal are show below.

As shown in Fig. 2.6, white noise is only correlated at identical frequencies, while the spectral components at different frequencies of a modulated signal are also correlated, creating a distinguishable pattern in its SCF. However, feature detection presents many implementation challenges, the foremost of which is the complex processing required to generate the two-dimensional FFT and calculate the correlation functions. Complex processing indicates high

Figure 2.6: SCF of (a) white noise, and (b) a QPSK signal [4].

power and long sensing time, both of which makes this technique unattractive for spectrum sensing in the mobile space.

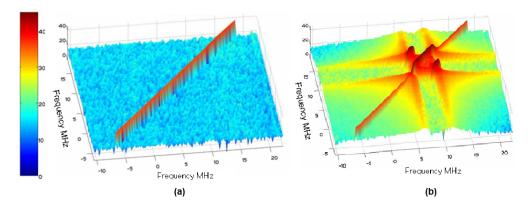

Another simpler approach that can be used to extract periodicity is to autocorrelate the signal. Autocorrelation, correlating a signal with a time-shifted version of itself, is a method that has long been used in spectrum analyzers, radio astronomy, and other applications that require high-sensitivity signal detection. Eq. 2.1 below presents the autocorrelation function  $R(\tau)$ , where X(t) is the signal being correlated and  $\tau$  is the time shift.

$$R(\tau) = E\left[X(t) * X(t+\tau)\right] \tag{2.1}$$

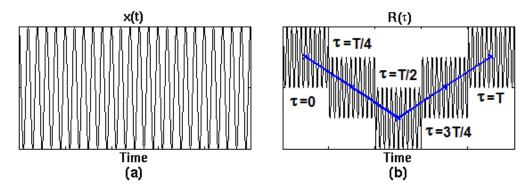

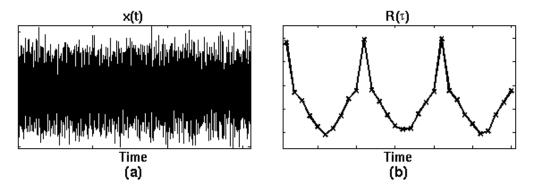

Since white noise is a stationary process that is uncorrelated with itself at different points in time,  $R(\tau)$  for white noise would be 0 everywhere except for when  $\tau = 0$ . For modulated signals which are cyclostationary processes, the signal time-shifted by an integer number of periods should have the same statistical properties as the non-time-shifted version of the signal. Therefore,  $R(\tau)$  should exhibit periodic behavior, with peaks occurring at  $\tau$  equaling 0 as well as each integer period. Fig. 2.7 illustrates this property.

If we look at  $R(\tau)$  with  $\tau$  equaling a non-zero integer period, the additive noise power would ideally average out to zero given enough time, and the resulting SNR of the autocorrelation function would be an improvement over the SNR of the signal itself. However, a digital implementation of autocorrelation still requires a relatively high amount of processing due to the multiplication operations needed to calculate the correlation function. As mentioned in Sec. 2.1.2, [13] demonstrated the power inefficiency of this approach. On the other hand, [11] demonstrated that correlation can be done in a lower power manner in the analog domain. While the system in [11] was high powered, much of it was used for generating the window waveforms, and the actual correlation operation itself consumed only 8mA. We thus see that autocorrelation in the analog domain could potentially be a low-power, high-sensitivity solution to spectrum sensing.

Figure 2.7: Time-domain waveform and autocorrelation function of (a) a sinusoid and (b) white noise.

## 2.2 Evaluation of a Multi-Mode Detection System

An optimal spectrum sensing system should use a combination of channel energy detection, pilot energy detection, and autocorrelation. The pilot tone, as a pure sinusoid, provides an ideal candidate to extract the periodicity from using autocorrelation. The channel energy detection mode would be used for a fast, coarse scan of all the channels to eliminate ones that have strong signals residing within. Pilot detection and autocorrelation, being more time consuming, would only be used on a few likely-vacant channels where the signal, if present, is too weak to be sensed with energy detection.

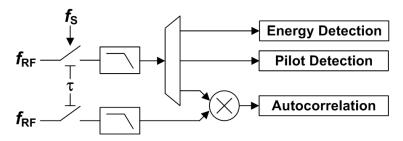

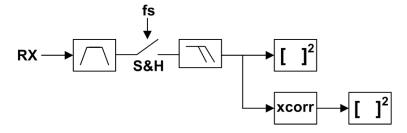

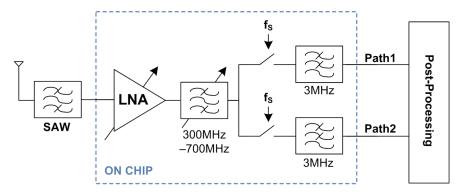

To evaluate achievable performance of the various sensing methods in a practical implementation, we constructed in simulation the multi-mode detection system shown in Fig. 2.8. We adopt the equivalent-time sampling technique from [17] to implement autocorrelation in the time domain. The input  $f_{RF}$  is captured in parallel by two samplers, with the sampling clocks offset from each other by a time delay  $\tau$ . By correlating the two sampled signals, and by varying  $\tau$  in discrete steps, the autocorrelation of the input is captured as a function of  $\tau$ .

Using the equivalent-time sampling autocorrelation method, the resolution of the sampled signal is determined not by the actual sampling frequency but by the minimum  $\tau$ -step, with effective sampling frequency equaling  $1/\tau_{step}$ . Thus, this method enables power savings by using a sampling frequency below the Nyquist rate. Since subsampling also acts as a mixer and downconverts the RF signal to baseband, the signal is then immediately channel-

Figure 2.8: High level block diagram of proposed system.

filtered following the sampler.<sup>2</sup> In the top path, the filtered channel signal undergoes energy detection and pilot detection. For autocorrelation mode, the signals from the two paths are multiplied together in the analog domain as  $\tau$ , the time delay between the two paths, is varied.

Sec. 2.2.1 delves into the detailed mechanisms of subsampling and autocorrelation, and how these techniques apply to our spectrum sensing system. Then, Sec. 2.2.2 describes a Matlab-based simulation platform built to evaluate the proposed multi-mode detection system. Finally, Sec. 2.2.3 presents the theoretical performance of the proposed system in each of its detection modes.

### 2.2.1 Subsampling and Autocorrelation

In traditional Nyquist sampling, the number of points per cycle that are sampled scales linearly with the ratio of sampling frequency to signal frequency. Thus if we want to sample many points per cycle in order to not lose signal fidelity through the sampling process, we must oversample the signal with a much higher sampling frequency. If the input frequencies are in the hundreds of megahertz, oversampling becomes very power-inefficient and unattractive. Subsampling, on the other hand, maintains high signal fidelity while using lower sampling frequencies.

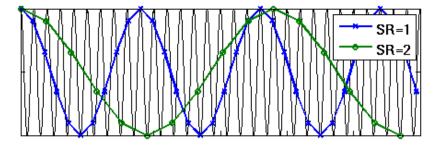

Fig. 2.9 illustrates the subsampling operation conceptually. The signal is sampled once per period for subsampling ratio (SR) of 1, and once every two periods for SR of 2. Each sample occurs at a different temporal location within the signal period, and if given enough signal cycles, the entire characteristic of a periodic signal will be sampled. The result is a high-fidelity signal with numerous sampled points per cycle, albeit translated to a a lower frequency.

Based on the number of samples per cycle, the equivalent oversampling frequency  $f_{S-EQ}$  of

<sup>&</sup>lt;sup>2</sup> "Subsampling" refers to sub-Nyquist sampling with  $f_S < 2 * f_{RF}$ . It is used interchangeably with "equivalent-time sampling" in this work."

Figure 2.9: Illustration of subsampling with subsampling ratios of 1 and 2.

a subsampled signal is:

$$f_{S-EQ} = \frac{f_{RF} * f_S}{f_{RF} - N * f_S}, \qquad 0.5 * f_{RF} < N * f_S < f_{RF}$$

(2.2)

where  $f_S$  is the subsampling frequency,  $f_{RF}$  is the signal frequency, and N is the subsampling ratio. An extremely high  $f_{S-EQ}$  can be obtained with an extremely low  $f_S$  if N is large. More importantly, the linear relationship between samples per cycle and sampling frequency has been broken: a higher  $f_{S-EQ}$  can be achieved by simply minimizing  $(f_{RF} - N * f_S)$ .

The translated lower frequency after subsampling is:

$$f_{sampled} = f_{RF} - N * f_S,$$

$0.5 * f_{RF} < N * f_S < f_{RF}$  (2.3)

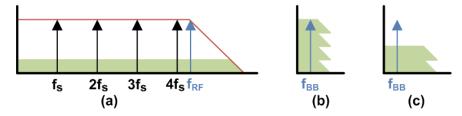

We can easily choose N and  $f_S$  so that  $f_{sampled}$  falls in the baseband, providing a convenient mixing step as well. This frequency aliasing effect, however, also causes noise folding, in which the noise around every harmonic of  $f_S$  is translated to baseband as well. The mechanism of noise folding is illustrated in Fig. 2.10. Thermal noise is represented in green, and we assume a low-pass filter has attenuated high-frequency noise above the desired signal (in red in Fig. 2.10(a)).

Figure 2.10: Noise folding from subsampling: (a) unsampled spectrum, (b) sampled with  $f_S$ , (c) sampled with  $2f_S$ .

Fig. 2.10(b) demonstrates the sampled signal  $(f_{BB})$  using sampling frequency  $f_S$  and SR = 4. Noise from each harmonic accumulates in the same frequency band, and the signal at baseband has severely degraded SNR. Bandpass anti-alias filters can be used at RF to mitigate noise folding, but the noise generated from the sampler itself still has a low-pass characteristic and will not be filtered. The folding of sampler noise has resulted in subsampling mixers generally having prohibitively high noise figures, making them unattractive for low noise systems [18]. Alternatively, baseband SNR can be improved with a lower subsampling ratio, such as SR=2 in Fig. 2.10(c). The tradeoff is higher power consumption associated with higher-frequency clock generation and distribution networks.

Spectrum sensing systems, in order to achieve the required high sensitivities, must be low noise. We therefore choose for our system the low subsampling ratio of 1, so that noise is folded only once. The noise is also spread over the full spectrum up to the sampling frequency and is not concentrated purely in the baseband, which further improves noise figure. While the power benefits of subsampling are lessened with SR = 1, it is still a factor of 2 improvement over the minimum Nyquist sampling frequency, and more critically, we still gain the benefit of higher  $f_{S-EQ}$ .

Next, we consider the options for choosing  $f_S$ . Standard receivers would set the mixing frequency to the carrier frequency, and use I and Q paths to reject aliased images. A Hilbert filter would then reconstruct the real baseband signal from the downconverted vestigial sideband in order to allow signal decoding [19]. However, since the pilot also falls on the carrier frequency, this provides several problems for our purposes. Firstly, the pilot power, as a DC component, becomes vulnerable to DC offset and low frequency flicker noise. Moreover, the pilot is in a 10kHz bandwidth, indicating that a lengthy time will be required to collect enough samples for an accurate measurement.

Figure 2.11: Conversion to baseband with sampling frequency set to (a) carrier frequency, (b) channel center frequency.

A better solution, shown in Fig. 2.11, is to sample at the center frequency of each channel instead of at the carrier. This results in true direct conversion where image rejection and I and Q paths are no longer necessary, as no out-of-channel signals would fall in-band. Without image rejection and Hilbert filters, the signal would fold onto itself to create an un-decodable baseband signal. However, since we only seek to detect the presence of a signal and not to receive it, a non-real signal is acceptable for our system. In addition, the pilot falls at the low IF frequency of 2.69MHz. This alleviates the flicker noise problem and eliminates the DC offset problem altogether. Pilot power can also be measured more rapidly, and the pilot retains its periodicity to allow autocorrelation detection.

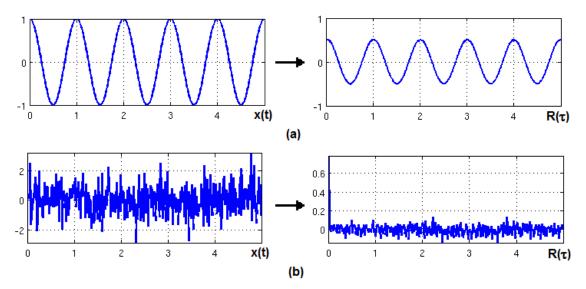

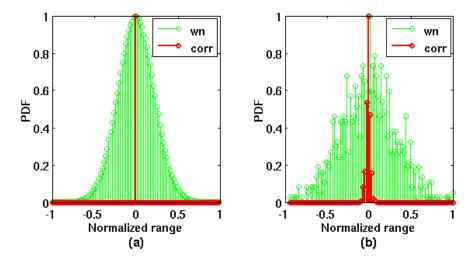

To perform autocorrelation in analog time domain, we step the time shift  $\tau$  between the two samplers. Fig. 2.12(a) shows an example sinusoid signal, and Fig. 2.12(b) shows 5  $\tau$ -steps encompassing 1 cycle of its autocorrelation in time domain. In post-processing, the mean at each  $\tau$ -step would be calculated to obtain autocorrelation as a function of  $\tau$ . Fig.2.12(b) plots  $R(\tau)$  in blue.

Figure 2.12: Time-domain waveform of (a) a sinusoid, (b) its autocorrelation.

Fig. 2.13 demonstrates the extraction of periodic autocorrelation behavior from a noisy signal. Fig. 2.13(a) plots the time domain signal, in which a sinusoid has been buried in noise and cannot be distinguished by energy detection. Its autocorrelation in Fig. 2.13(b), on the other hand, extracts the periodicity of the signal and demonstrates clear SNR improvement.

Stepping through multiple autocorrelation cycles as in Fig. 2.13(b) is useful if we eventually want to extract frequency information through a FFT; however, it is unnecessary for our purposes. Since the pilot is a pure sinusoid, one autocorrelation cycle is adequate to gain its entire characteristic and to make a detection decision. There should be no difference (statistically) between the autocorrelated results of, for example,  $\tau = T/4$  and  $\tau = 5T/4$ . Thus, performance could be better improved by averaging at each  $\tau$ -step for a longer period of time rather than incorporating more  $\tau$ -steps and multiple autocorrelation cycles. This eliminates the need for long, variable delay lines, and phase-shifting the sampling clock is sufficient to create all necessary all  $\tau$ -steps where  $\tau < T$ . Due to the properties of

subsampling, a phase shift in the sampling clock translates directly to an identical phase shift in the subsampled baseband signal.

Figure 2.13: Time-domain waveform of (a) a noisy sinusoid, (b) its autocorrelation.

### 2.2.2 Simulation Setup

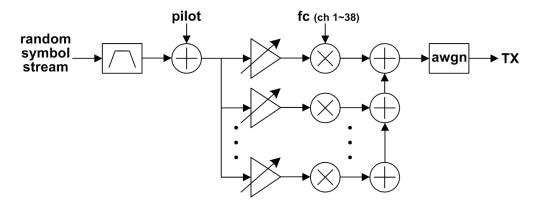

Realistic spectrum sensing scenarios using the multi-mode detection system were modeled in Matlab. Fig. 2.14 illustrates how transmit signals were generated in the modeling environment. A random stream of 8-level symbols in baseband are filtered to obtain the VSB frequency response, and a pilot is then added as a DC level. Next, for every channel where we desire a signal to exist, we scale the signal power as desired and up-mix it to its appropriate RF channel position. Finally, additive white Gaussian noise (AWGN) is applied to model environmental thermal noise.

Figure 2.14: Transmit signal generation in simulation.

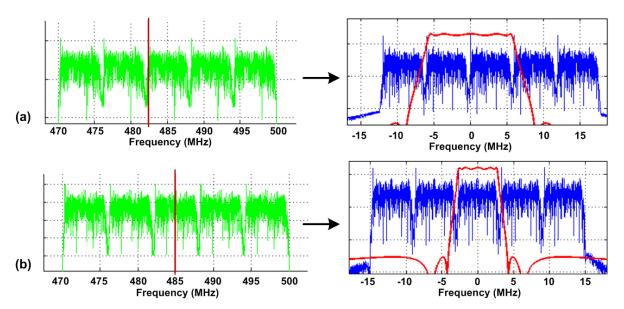

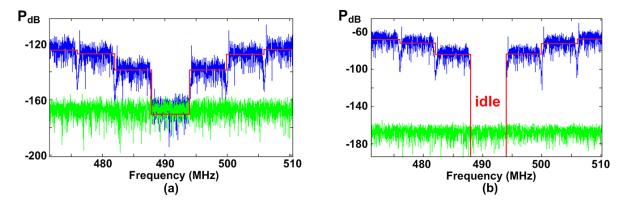

For example, a simulated model of the worst case sensing scenario is shown in Fig. 2.15. The signal power (with additive thermal noise) is shown in blue and pure noise is shown in green. Fig. 2.15(a) shows a 7-channel worst case blocker profile with a weak -114dBm signal

in the center channel. On the other hand, when a channel is idle like the center channel of Fig. 2.15(b) is, the power of its surrounding channels can be arbitrarily high. We seek to differentiate between the two scenarios by detecting the presence or lack thereof of the weak signal in the center channel.

Figure 2.15: Worst case sensing scenario when target channel is (a) occupied, (b) idle.

Fig. 2.16 illustrates how the receiver is modeled in simulation for the measurement of detected power. First, a coarse bandpass filter is applied to the entire UHF band to attenuate out-of-band noise and thus reduce noise-folding during subsampling. We ignore out-of-band interference and assume they have been sufficiently attenuated at this point in the receive path. We then subsample the signal at the desired channel with a sampling frequency equal to the channel frequency. The downconverted signal is filtered by either a channel filter or an ideal narrowband pilot filter, and the resulting power of the signal is measured using square law energy detection. For autocorrelation, we apply ideal mathematical autocorrelation to the filtered pilot, and then again apply square law energy detection to measure the power of the autocorrelated signal.

Figure 2.16: Receiver modeling in simulation.

To establish a metric to evaluate the performance of each detection strategy, we look at the two scenarios in Fig. 2.17. In the first scenario, when no signal is present, the receiver will detect only the power of the noise from the environment; we denote this quantity  $N_{DET}$ . For

simplicity, we assume pure thermal noise and ignore non-white interference at this junction. In the second scenario, when a signal is present, the receiver picks up that signal along with the environmental noise, and we denote the total detected power under this condition  $S_{DET}$ .

Figure 2.17: Equivalent block diagram when (a) only noise is present, (b) signal and noise are present.

If we denote the power of the input signal  $S_{IN}$ , power of the environmental thermal noise  $N_{THERM}$ , power of the receiver electronic noise at its output  $N_{RX-OUT}$ , and the total gain through the receiver  $A_{RX}$ , then for naive energy detection:

$$N_{DET} = A_{RX} * N_{THERM} + N_{RX-OUT}$$

$$S_{DET} = A_{RX} * (S_{IN} + N_{THERM}) + N_{RX-OUT}$$

$$(2.4)$$

Given a receiver noise figure, we can define  $N_{RX-OUT}$  in terms of the input thermal noise and the noise factor  $F_{RX}$ :

$$N_{RX-OUT} = A_{RX} * N_{THERM} * (F_{RX} - 1)$$

(2.5)

The SNR of an input signal is the ratio of the signal power to the thermal noise power. We can similarly define a term "detected SNR" to be the ratio of  $S_{DET}$  to  $N_{DET}$ , or the ratio of power detected when a signal is present to power detected when only noise is present. Using equations Eq. 2.4 and Eq. 2.5, we find:

$$Detected SNR = \frac{S_{DET}}{N_{DET}} = \frac{S_{IN}/N_{THERM} + F_{RX}}{F_{RX}} = \frac{Input SNR + F_{RX}}{F_{RX}}$$

(2.6)

From Eq. 2.6, when the receiver adds infinite noise, the detected SNR reaches its lower bound of 1, or 0 dB. This indicates that inputs with the signal present and without the signal present are indistinguishable from each other at the point of detection. Conversely, when the receiver noise figure is very small, the detected SNR tracks with the input SNR.

#### 2.2.3 Evaluation of Detection Modes

Using the simulation framework described in Sec. 2.2.2, we evaluate the theoretical performance of our spectrum sensing system in each of its detection modes. Simulated energy

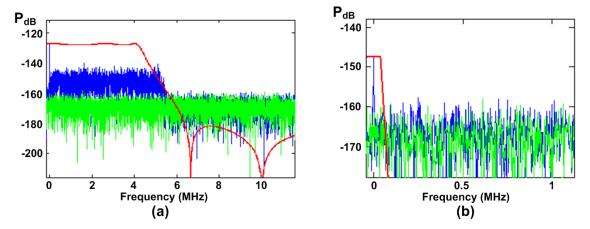

Figure 2.18: Simulated (a) energy and (b) pilot detection at baseband.

and pilot detection are shown in Fig. 2.18, where the power spectrum densities of signal and noise are shown in blue and green respectively. The red outlines illustrate example baseband filter responses.

In Fig. 2.18(a), where signal power is distinctively higher than noise power, we can perform energy detection by filtering the entire channel and measuring the resultant power. On the other hand, in Fig. 2.18(b), we see that for weak inputs, the signal power is completely buried in noise and indistinguishable from it. However, the narrowband pilot tone still rises above the noise floor. In this case, we can perform pilot detection by narrowing the filter response to just the bandwidth of the pilot, and then, again, measuring the resultant power.

To evaluate the performance and limitations of energy and pilot detection, we first note that thermal noise power is given by:

$$N_{THERM} = k * T * \Delta f \tag{2.7}$$

where k is Boltzmann's constant equaling  $1.38 \times 10^{-23} \text{JK}^{-1}$ , T is temperature in Kelvin, and  $\Delta f$  is the noise bandwidth under consideration.

At room temperature, kT gives -204dB/Hz, or -174dBm/Hz, of noise power. In a 6MHz bandwidth, the noise power becomes -105dBm, and an input signal at -114dBm has a -9dB input SNR. In a 10kHz bandwidth, the noise power lowers to -133dBm. However, the power of the pilot in its narrow bandwidth is 11.3dB below the total channel power. Thus, the minimum pilot power is -125.3dBm, making the minimum input SNR of the pilot 7.7dB.

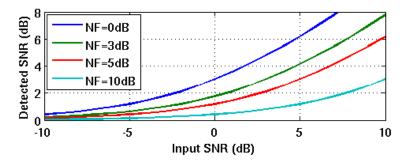

Using Eq. 2.6, we can plot detected SNR as a function of input SNR for various receiver noise figures. Shown in Fig. 2.19, for an input SNR of -9dB for channel energy detection, the detected SNR in the ideal case (with no added receiver noise) is about 0.5dB. Similarly, the detected SNR in the ideal case for pilot energy detection is about 8.4dB.

Figure 2.19: Detected SNR as a function of input SNR for energy detection.

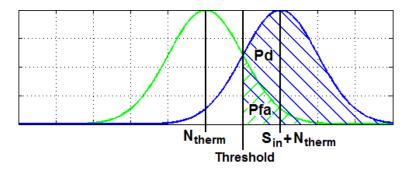

Decision statistics and algorithms for spectrum sensing are outside the scope of this work; however, we will briefly discuss at this juncture the factors that determine the detected SNR threshold for sensing and their implications on system design. In theory, the probabilities of false alarm  $(P_{FA})$  and detection  $(P_D)$  are functions of where the decision threshold is set and how many samples are used. More samples allow more averaging, resulting in a more accurate measurement that is less sensitive to instantaneous variances in noise and signal power. To find  $P_{FA}$  and  $P_D$ , we can model the probability density function (PDF) of noise with a Gaussian distribution and use Neyman-Pearson hypothesis testing. This process is illustrated in Fig. 2.20 [16].

Figure 2.20: Probability density functions for signal and noise.

In Fig. 2.20, the green shows the PDF for pure noise, and the blue shows the PDF for signal with noise, where the mean power has shifted but the shape remains Gaussian. The decision threshold should be set somewhere between the two means, and anything above threshold in the noise distribution results in a false alarm, while anything above threshold in the signal distribution indicates a correct, desired detection. The shaded areas of  $P_{FA}$  and  $P_D$  can be quantified as:

$$P_{FA} = Q\left(\frac{N * (SNR_{THR} - 1)}{\sqrt{2 * N}}\right)$$

(2.8)

$$P_D = Q \left( \frac{N * (SNR_{THR} - SNR_{DET})}{\sqrt{2 * N * SNR_{DET}^2}} \right)$$

(2.9)

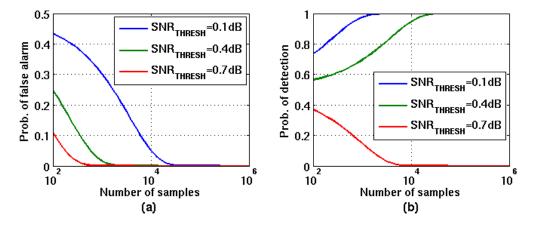

where  $SNR_{DET}$  is detected SNR,  $SNR_{THR}$  is the decision threshold detected SNR, N is the number of samples, and Q(x) is the tail function for a normal distribution. For an ideal channel detection scenario, where the detected SNR is about 0.5dB, we gain the following  $P_{FA}$  and  $P_D$  as a function of N shown in Fig. 2.21. As expected, a higher threshold results in a longer detection time, but a lower false alarm rate. And when the decision threshold (in the form of detected SNR) is set to 0.7dB>0.5dB, the system fails to detect completely.

Figure 2.21: Ideal channel energy detection: (a)  $P_{FA}$ , (b)  $P_D$ .