# A Highly Productive Implementation of an Out-of-Order Processor Generator

Christopher Celio

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2018-151 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2018/EECS-2018-151.html

December 1, 2018

Copyright © 2018, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### A Highly Productive Implementation of an Out-of-Order Processor Generator

by

Christopher Patrick Celio

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Emeritus David A. Patterson, Chair Professor Krste Asanović, Co-chair Assistant Professor Zachary Pardos

Fall 2017

# A Highly Productive Implementation of an Out-of-Order Processor Generator

Copyright 2017 by Christopher Patrick Celio

#### Abstract

A Highly Productive Implementation of an Out-of-Order Processor Generator

by

Christopher Patrick Celio

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Emeritus David A. Patterson, Chair

Professor Krste Asanović, Co-chair

General-purpose serial-thread performance gains have become more difficult for industry to realize due to the slowing down of process improvements. In this new regime of poor process scaling, continued performance improvement relies on a number of small-scale micro-architectural enhancements. However, software simulator-based models, which computer architecture research has largely relied upon, may not be well-suited for evaluating ideas at the necessary fidelity.

To facilitate architecture research during this fallow period of Moore's Law, we propose using processor simulators built from synthesizable processor designs. This thesis describes the design of a synthesizable, industry-competitive processor built on recent advancements in open-source hardware: we leverage the new open-source RISC-V instruction set architecture, the new *Chisel* hardware construction language, and the *Rocket-chip* processor generator.

Our processor generator is called BOOM, and it designed for use in education, research, and industry. Like most contemporary high-performance cores, BOOM is superscalar (able to execute multiple instructions per cycle) and out-of-order (able to execute instructions as their dependencies are resolved and not restricted to their program order).

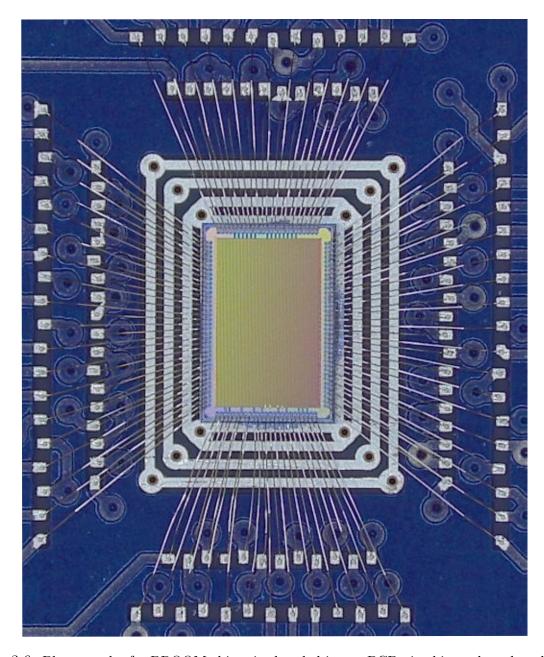

The BOOM generator was implemented using the *Chisel* hardware construction language, allowing for the rapid implementation of parameterized designs. The *Chisel* description generates synthesizable implementations of BOOM that can target both FPGAs and ASIC tool-flows. The BOOM effort culminated in a test chip that was fabricated in the TSMC 28 nm HPM process (high performance mobile) using the foundry-provided standard-cell library and memory compiler.

This thesis highlights two aspects of the BOOM design: its industry-competitive branch prediction and its configurable execution datapath. The remainder of the thesis discusses the BOOM tape-out, which was performed by two graduate students and demonstrated the ability to quickly adapt the design to the physical design issues that arose.

To my parents, for the many opportunities that they gave me.

# Contents

| $\mathbf{C}$  | onter | nts                                                           | ii   |

|---------------|-------|---------------------------------------------------------------|------|

| $\mathbf{Li}$ | st of | Figures                                                       | vi   |

| Li            | st of | Tables                                                        | viii |

| 1             | Intr  | roduction                                                     | 1    |

|               | 1.1   | Leveraging New Infrastructure                                 | 1    |

|               | 1.2   | Contributions                                                 | 2    |

|               | 1.3   | Thesis Outline                                                | 3    |

| 2             | Bac   | ekground                                                      | 4    |

|               | 2.1   | Motivation                                                    | 4    |

|               | 2.2   | Technology and Research Trends                                | 5    |

|               |       | 2.2.1 Impact of Performance Slowdown on Architecture Research | 10   |

|               | 2.3   | Computer Architecture Research Trends                         | 12   |

|               |       | 2.3.1 Architectural Simulators                                | 12   |

|               |       | 2.3.2 RTL Implementations                                     | 15   |

|               |       | 2.3.3 Energy Modeling Methodologies                           | 18   |

|               | 2.4   | Processor Microarchitecture                                   | 20   |

|               | 2.5   | Out-of-order Processor Microarchitectures                     | 23   |

|               |       | 2.5.1 The Data-in-ROB Design (Implicit Renaming)              | 23   |

|               |       | 2.5.2 The Physical Register File Design (Explicit Renaming)   | 25   |

|               |       | 2.5.3 The Differences Between the Two Styles                  | 25   |

|               | 2.6   | History of Out-of-order Processors                            | 27   |

|               | 2.7   | The Value of Out-of-order Execution                           | 28   |

|               | 2.8   | Conclusion                                                    | 29   |

| 3             | во    | OM Overview                                                   | 31   |

|               | 3.1   | The RISC-V Instruction Set Architecture                       | 31   |

|               | 3.2   | The BOOM Microarchitecture                                    | 33   |

|               |       | 3.2.1 The BOOM Pipeline                                       |      |

|   |             | 3.2.2         | Instruction Fetch and Branch Prediction                             | 35        |

|---|-------------|---------------|---------------------------------------------------------------------|-----------|

|   |             |               | 3.2.2.1 Branch Target Buffer (BTB)                                  | 35        |

|   |             |               | 3.2.2.2 Return Address Stack (RAS)                                  | 35        |

|   |             |               | 3.2.2.3 Conditional Branch Predictor (BPD)                          | 35        |

|   |             | 3.2.3         | The Decode Stage and Resource Allocation                            | 36        |

|   |             | 3.2.4         | The Register Rename Stage                                           | 36        |

|   |             | 3.2.5         | The Reorder Buffer (ROB) and Exception Handling                     | 36        |

|   |             | 3.2.6         | The Issue Unit                                                      | 38        |

|   |             | 3.2.7         | The Register File and Bypass Network                                | 38        |

|   |             | 3.2.8         | The Execution Pipeline                                              | 38        |

|   |             | 3.2.9         | The Load/Store Unit (LSU)                                           | 38        |

|   |             | 3.2.10        | The Memory System                                                   | 36        |

|   | 3.3         | Design        | Methodology                                                         | 36        |

|   |             | 3.3.1         | RTL Design                                                          | 36        |

|   |             | 3.3.2         | RTL Verification                                                    | 40        |

|   |             | 3.3.3         | The Chisel Hardware Construction Language                           | 42        |

|   |             | 3.3.4         | The Rocket-chip System-on-a-Chip Generator                          | 44        |

|   | 3.4         | FPGA          | Implementation                                                      | 44        |

|   | 3.5         | ASIC I        | Implementation                                                      | 45        |

|   |             | 3.5.1         | SRAM Generation                                                     | 50        |

|   |             | 3.5.2         | Custom Bit Array Register File                                      | 50        |

|   |             | 3.5.3         | Timing Analysis                                                     | 52        |

|   | 3.6         | Parame        | eters                                                               | 53        |

|   | 3.7         | Perform       | mance Evaluation                                                    | 53        |

| 4 | Dana        | l. D          | a. 11: a4: a                                                        | ۲.        |

| 4 | <b>Б</b> га |               | ediction<br>round                                                   | <b>59</b> |

|   | 4.1         | _             |                                                                     | 60        |

|   |             |               | Deficiencies of Trace-based, Unpipelined Models                     | 61        |

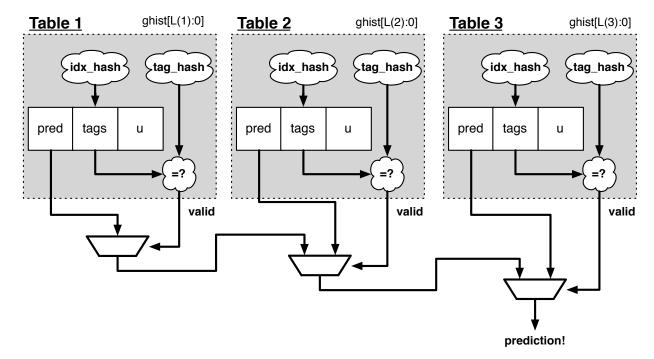

|   |             | 4.1.2 $4.1.3$ | The State-of-the-art TAGE Predictor                                 | 62        |

|   | 4.2         | _             | OOM RTL Implementation                                              | 64        |

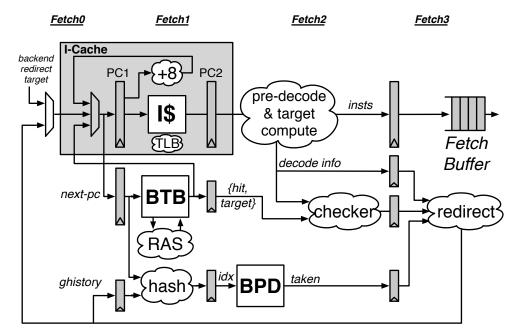

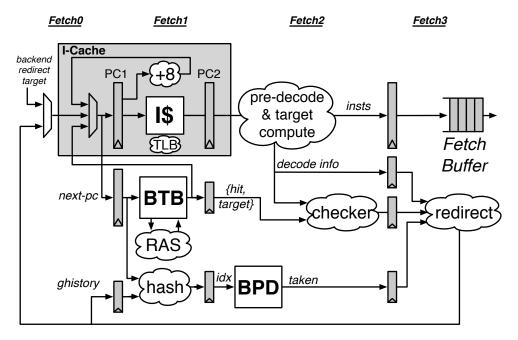

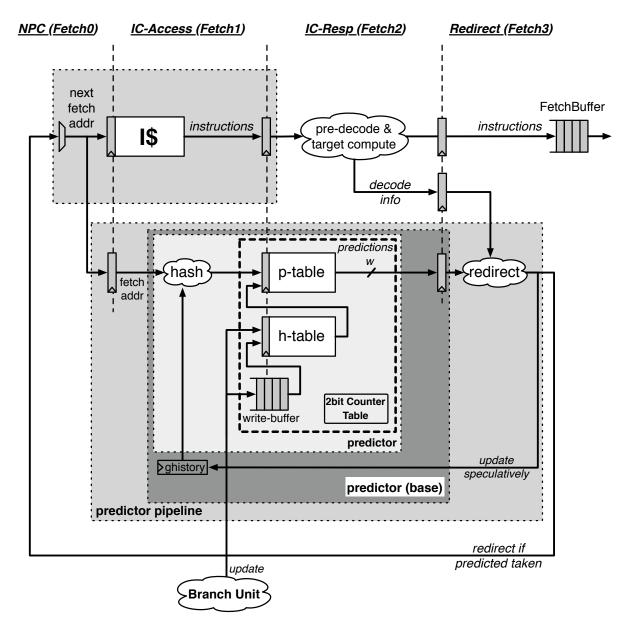

|   | 4.2         | 4.2.1         | The Frontend Organization                                           | 64        |

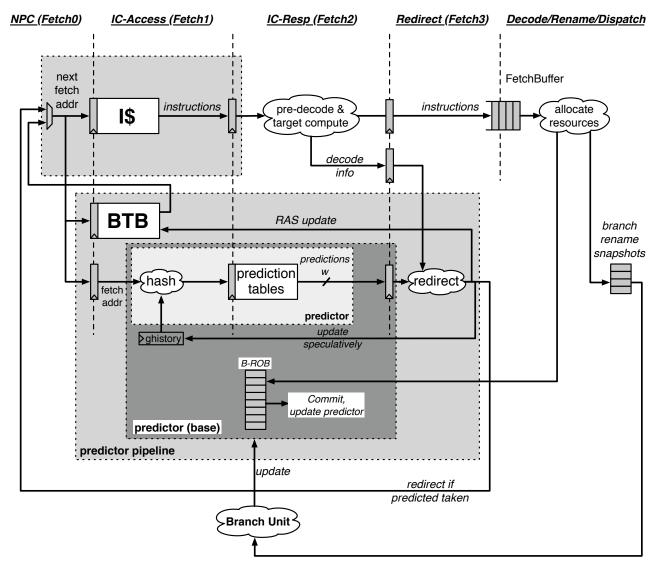

|   |             | 4.2.1         | Providing a Branch Predictor Framework                              | 66        |

|   |             | 4.2.2         | Managing the Global History Register                                | 66        |

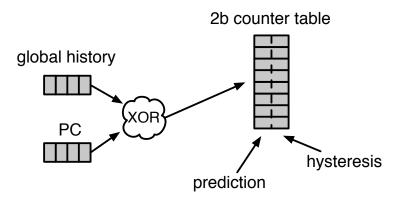

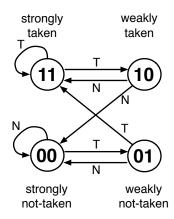

|   |             | 4.2.4         | The Two-bit Counter Tables                                          | 69        |

|   |             | 4.2.5         | Superscalar Predictions                                             | 70        |

|   |             | 4.2.6         | The BOOM GShare Predictor                                           | 71        |

|   |             | 4.2.7         | The BOOM TAGE Predictor                                             | 71        |

|   |             | 1.4.1         | 4.2.7.1 TAGE Global History and the Circular Shift Registers (CSRs) | 73        |

|   |             |               | 4.2.7.2 Usefulness Counters (u-bits)                                | 73        |

|   |             |               | 4.2.7.3 TAGE Snapshot State                                         | 74        |

|   | 4.3         | Addres        | ssing the Gaps Between RTL and Models                               | 74        |

|   | _, _        |               | 0                                                                   |           |

|   |     | 4.3.1 Superscalar Prediction                            | 74  |

|---|-----|---------------------------------------------------------|-----|

|   |     | 4.3.2 Delayed History Update                            | 75  |

|   |     | 4.3.3 Delayed Predictor Update                          | 76  |

|   |     | 4.3.4 Accurate Cost Measurements                        | 76  |

|   |     | 4.3.5 Implementation Realism                            | 77  |

|   | 4.4 | Proposed Improvements for Software Model Evaluations    | 77  |

|   | 4.5 | Conclusion                                              | 78  |

| 5 | Des | cribing an Out-of-order Execution Pipeline Generator    | 80  |

|   | 5.1 | Goals and Challenges                                    | 81  |

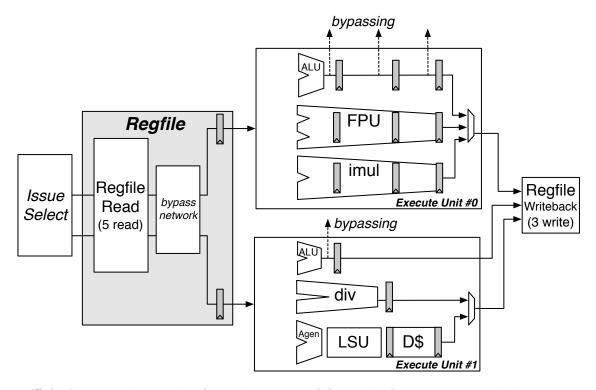

|   | 5.2 | The BOOM Execution Pipeline                             | 83  |

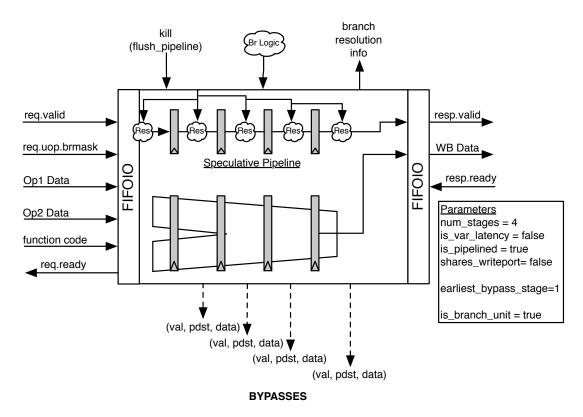

|   |     | 5.2.1 Branch Speculation                                | 83  |

|   |     | 5.2.2 Execution Units                                   | 83  |

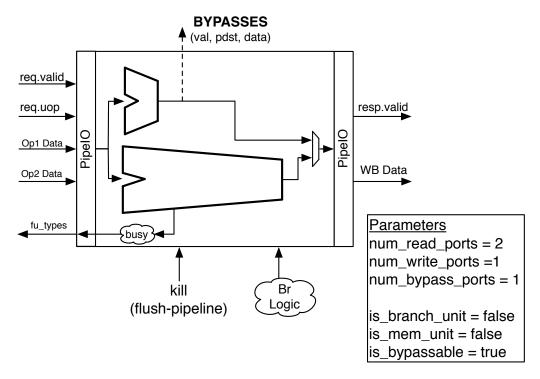

|   |     | 5.2.3 Functional Units                                  | 86  |

|   |     | 5.2.3.1 Pipelined Functional Units                      | 86  |

|   |     | 5.2.3.2 Iterative Functional Units                      | 89  |

|   |     | 5.2.4 The Load/Store Unit                               | 89  |

|   | 5.3 | Case Study: Adding Floating-point Support               | 89  |

|   |     | 5.3.1 Register File and Register Renaming               | 91  |

|   |     | 5.3.2 Issue Window                                      | 91  |

|   |     | 5.3.3 Floating-point Control and Status Register (fcsr) | 91  |

|   |     | 5.3.4 Hardfloat and Low-level Instantiations            | 92  |

|   |     | 5.3.5 Pipelined Functional Unit Wrapper                 | 92  |

|   |     | 5.3.6 Adding the FPU to an Execution Unit               | 94  |

|   |     | 5.3.7 Results                                           | 94  |

|   | 5.4 | Case Study: Adding a Binary Manipulation Instruction    | 97  |

|   |     | 5.4.1 Decode, Rename, and Instruction Steering          | 97  |

|   |     | 5.4.2 The Popcount Unit Implementation                  | 97  |

|   | 5.5 | <u> </u>                                                | 100 |

|   | 5.6 |                                                         | 102 |

| _ |     |                                                         |     |

| 6 |     | 1                                                       | 104 |

|   | 6.1 | 0                                                       | 105 |

|   | 6.2 |                                                         | 105 |

|   | 6.3 |                                                         | 109 |

|   |     | /                                                       | 109 |

|   |     |                                                         | 112 |

|   |     |                                                         | 112 |

|   | 6.4 | 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1                | 113 |

|   | 6.5 |                                                         | 117 |

|   | 6.6 | v v                                                     | 120 |

|   | 6.7 | Conclusion                                              | 120 |

| 7            | Conclusion                      | 122 |

|--------------|---------------------------------|-----|

|              | 7.1 Contributions               | 123 |

|              | 7.2 Future Directions           | 124 |

|              | 7.3 Final Remarks               | 125 |

| $\mathbf{A}$ | A Selection of Encountered Bugs | 127 |

| Bi           | bliography                      | 133 |

# List of Figures

| 2.1 | Cell phone subscriber counts as provided by the United Nations                    |

|-----|-----------------------------------------------------------------------------------|

| 2.2 | 45 years of microprocessor and technology trends                                  |

| 2.3 | 40 years of processor performance                                                 |

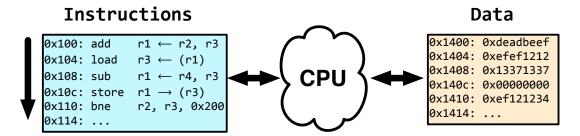

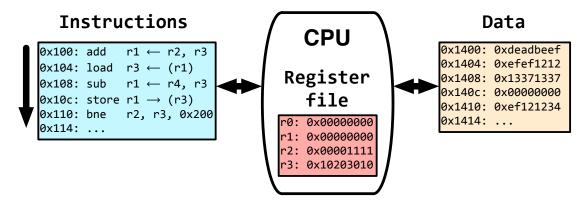

| 2.4 | A processor takes a stream of instructions and performs computations as specified |

|     | by each instruction                                                               |

| 2.5 | A common general-purpose processor architecture is the register-register load/s-  |

|     | tore architecture                                                                 |

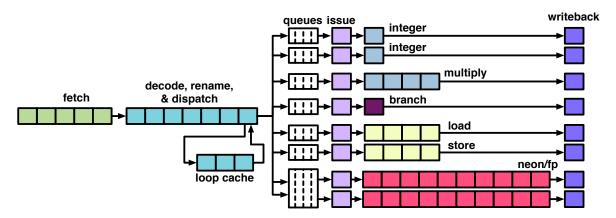

| 2.6 | An ARM Cortex-A15 pipeline                                                        |

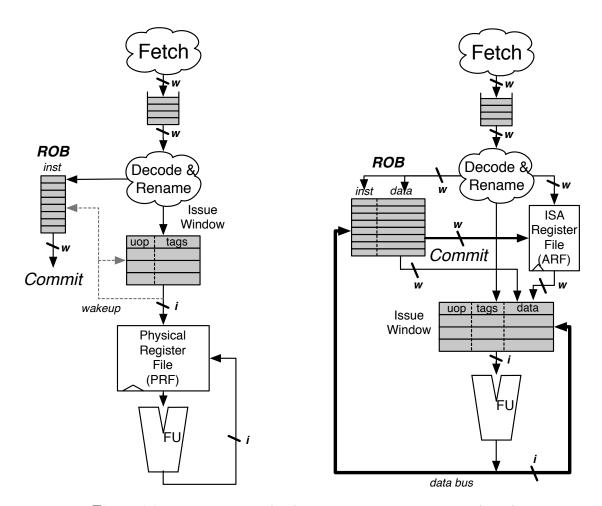

| 2.7 | A physical register file design and a data-in-ROB design                          |

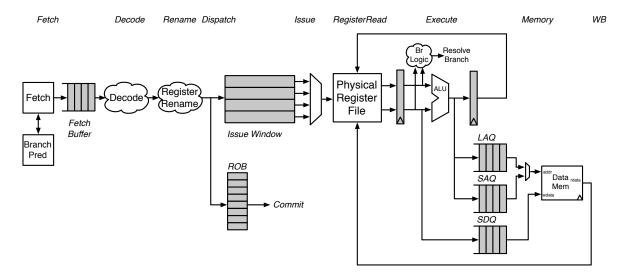

| 3.1 | A conceptual outline of the BOOM pipeline                                         |

| 3.2 | The instruction fetch frontend to BOOM                                            |

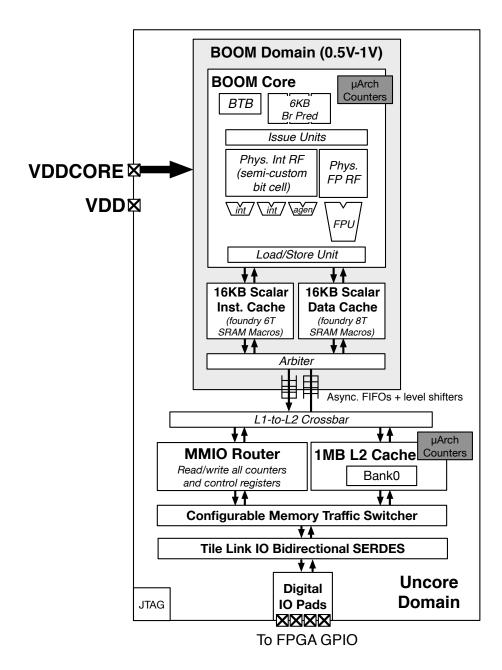

| 3.3 | Block diagram of the BROOM test chip                                              |

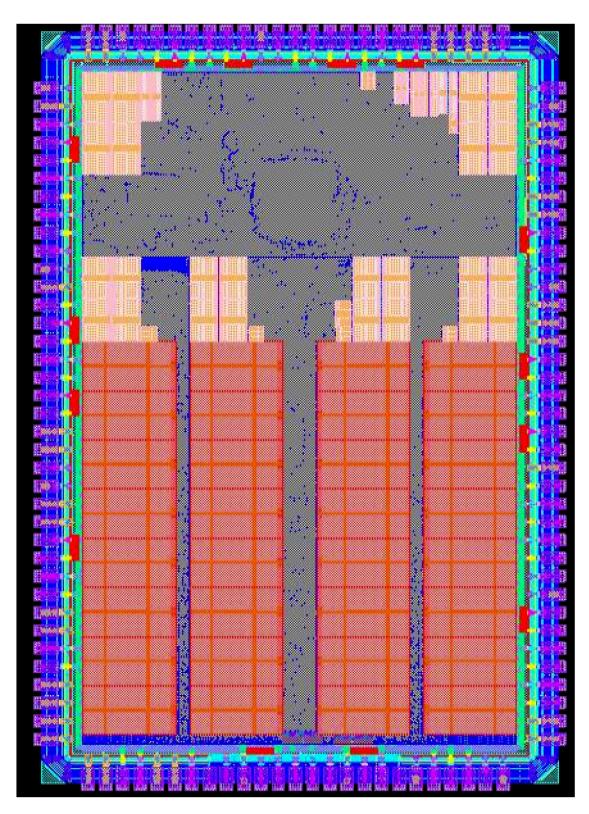

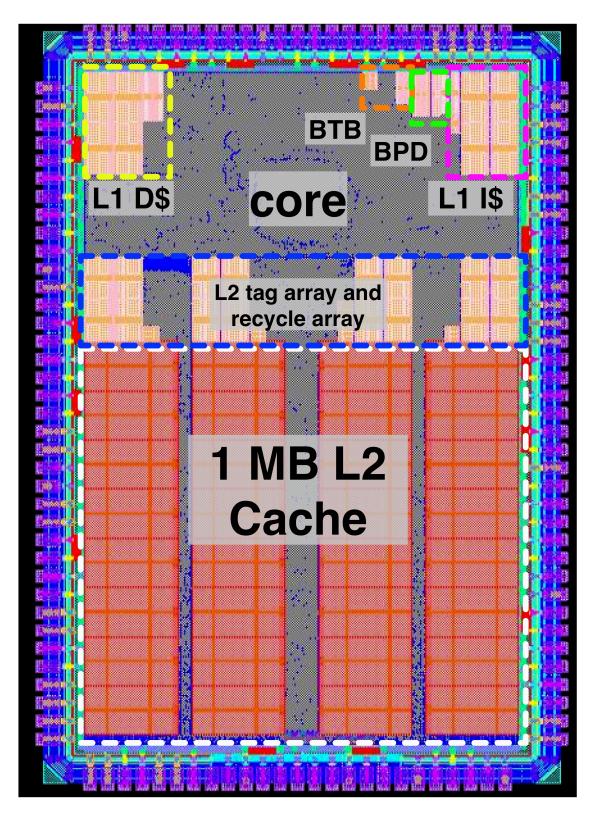

| 3.4 | BROOM place-and-routed chip plot                                                  |

| 3.5 | BROOM place-and-routed chip plot with annotations                                 |

| 3.6 | Photograph of a BROOM chip wire-bonded into a PCB                                 |

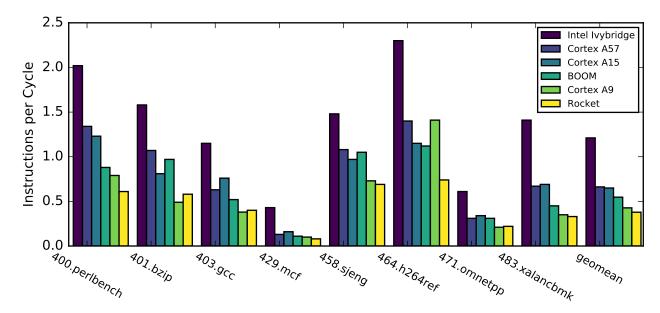

| 3.7 | Instruction-per-cycle comparison running SPECint2006                              |

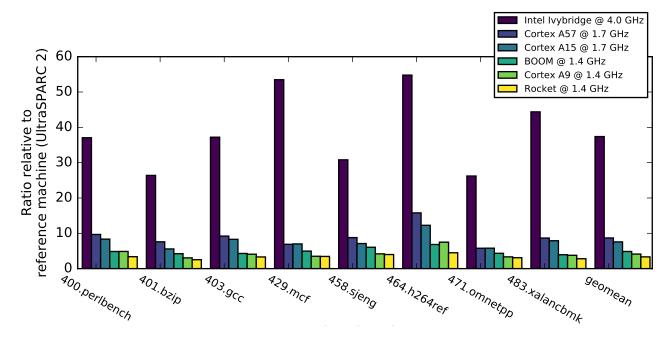

| 3.8 | Performance ratio relative to the SPEC reference machine (a 296 MHz Ultra-        |

|     | SPARC II)                                                                         |

| 4.1 | The TAGE predictor                                                                |

| 4.2 | The BOOM Fetch Unit                                                               |

| 4.3 | The branch prediction framework                                                   |

| 4.4 | A gshare predictor uses the global history hashed with the fetch address to index |

|     | into a table of 2-bit counters                                                    |

| 4.5 | Two-bit counter state machine                                                     |

| 4.6 | The gshare predictor pipeline                                                     |

| 5.1 | An example pipeline for a dual-issue BOOM                                         |

| 5.2 | An example Execution Unit                                                         |

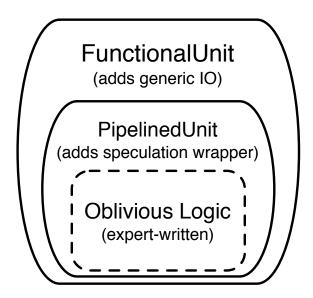

| 5.3 | The abstract Pipelined Functional Unit class                                      |

| 5.4 | The functional unit abstraction allows for the easy encapsulation of expert-written |     |

|-----|-------------------------------------------------------------------------------------|-----|

|     | functional unit logic.                                                              | 88  |

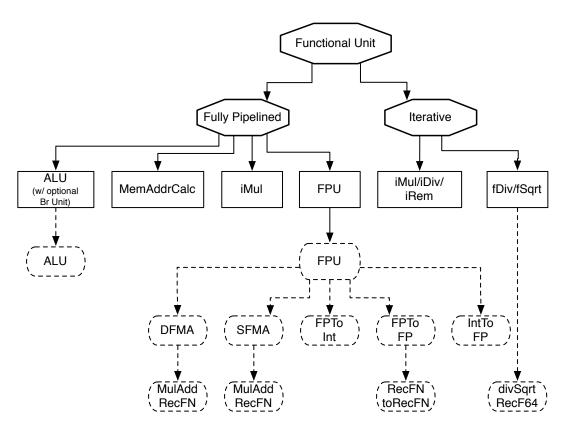

| 5.5 | The Functional Unit class hierarchy                                                 | 90  |

| 5.6 | Support for the RISC-V single-("F") and double-("D") precision extensions was       |     |

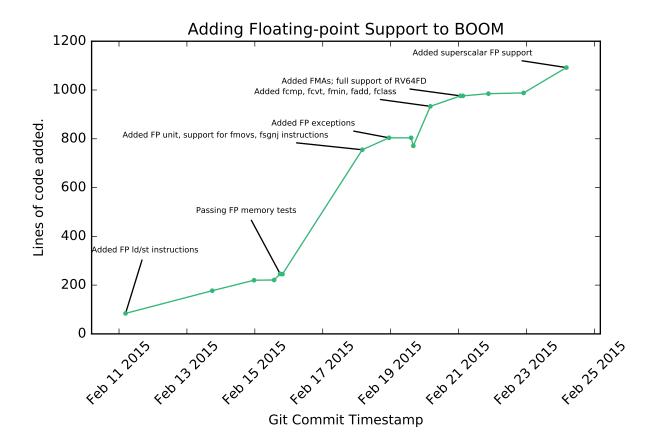

|     | implemented over a two week period                                                  | 96  |

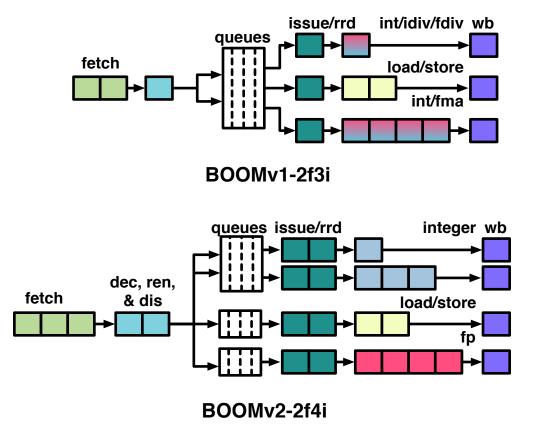

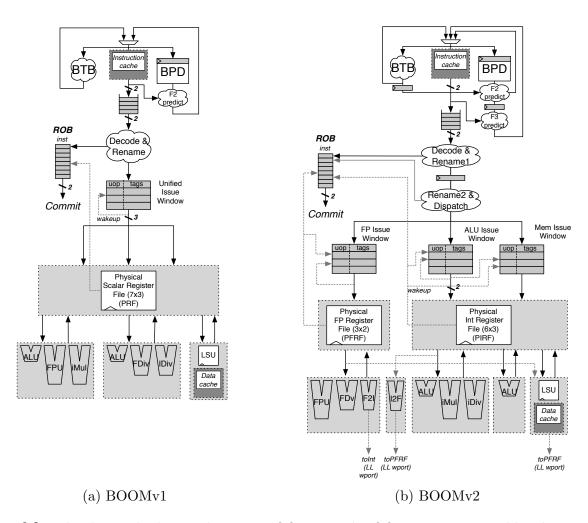

| 6.1 | A comparison of a three-issue BOOMv1 and four-issue BOOMv2 pipeline                 | 106 |

| 6.2 | The datapath changes between BOOMv1 and BOOMv2                                      | 108 |

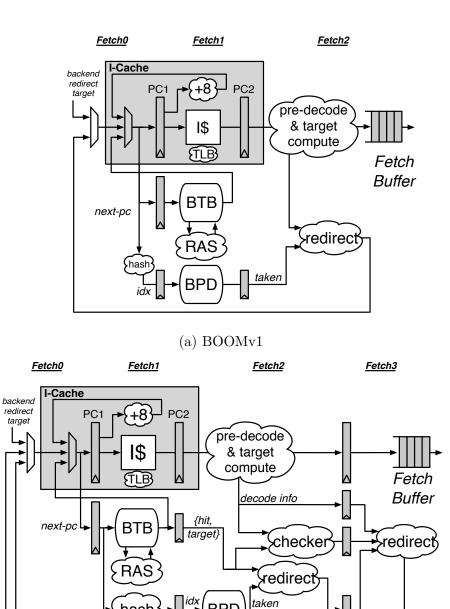

| 6.3 | The frontend pipelines for BOOMv1 and BOOMv2                                        | 110 |

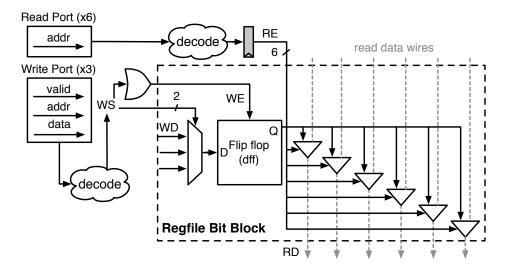

| 6.4 | A Register File Bit manually crafted out of foundry-provided standard cells         | 114 |

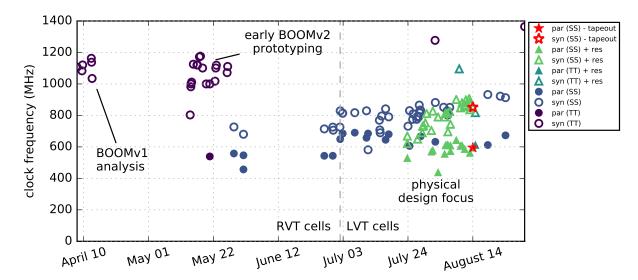

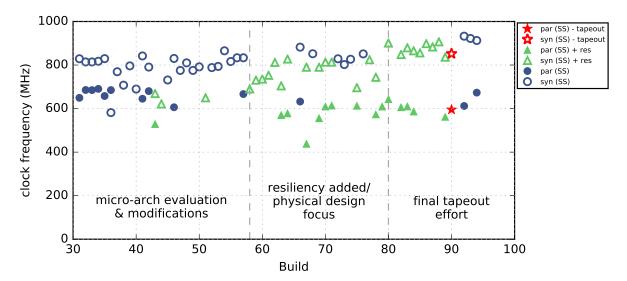

| 6.5 | All VLSI builds by date                                                             | 115 |

| 6.6 | VLSI builds using LVT cells and arranged by build number                            | 115 |

# List of Tables

| 2.1     | 2005)                                                                                 | 8   |

|---------|---------------------------------------------------------------------------------------|-----|

| 2.2     | The scaling factors of a single transistor in a post-Dennard Scaling regime (post-    | 0   |

|         | 2005)                                                                                 | 8   |

| 2.3     | A sample of simulators                                                                | 16  |

| 2.4     | A sample of academic out-of-order processors and the open-source UltraSPARC           |     |

|         | T2                                                                                    | 16  |

| 2.5     | The differences between the data-in-ROB design and the physical register file design  | 26  |

| 3.1     | The compile and simulation times for the Verilator and VCS RTL simulators             |     |

|         | when built using a 12-core Intel Xeon E5-2643 v2 (3.5 GHz)                            | 41  |

| 3.2     | The set of bare-metal benchmarks provided by the riscv-tests repository               | 43  |

| 3.3     | The configurations used for each of the SRAMs used in a BOOM core                     | 51  |

| 3.4     | The parameters chosen for the tapeout of BOOM                                         | 54  |

| 3.5     | CoreMark, Area, and Frequency Comparisons of Industry Processors                      | 55  |

| 3.6     | Instruction-per-cycle comparison running SPECint2006                                  | 58  |

| 3.7     | Performance ratio relative to the SPEC reference machine (a 296 MHz Ultra-            | 00  |

| <b></b> | SPARC II)                                                                             | 58  |

| 5.1     | A survey of industry execution datapaths and the different functional units available | 82  |

| 5.2     | The hierarchy from an abstract FunctionalUnit to an expert-written fused multply-     |     |

|         | add block                                                                             | 92  |

| 6.1     | The parameters chosen for analysis of BOOM                                            | 107 |

| 6.2     | The critical path length for each of the VLSI builds from the BROOM tapeout.          | 118 |

#### Acknowledgments

A thesis is an enormous task, but thankfully, it is not something that is done alone. Many friends, family, and mentors contributed to this work in both tangible and intangible ways.

First, I would like to thank my advisors, Krste Asanović and Dave Patterson, for allowing me to pursue a topic that excited me, no matter how foolish I was being. Krste was always eager to dive into the details (like designing the freelist restore scheme), while Dave helped me focus on the big picture. I would also like to thank my other committee member, Zachary Pardos, for his guidance and Johnathan Bachrach for his participation in my qualification exam. I also appreciated Jonathan's foundational work on *Chisel* and his sincere enthusiasm for my project.

I owe my early interest in computer architecture to Chris Terman and to Anant Agarwal of MIT. Chris's excellent 6.004 lectures sparked my fascination with processors, and I am very thankful for his mentoring of my 6.111 project where I built my first FPGA processor. I have been hooked ever since. As a senior without a clear plan for the future, Anant took me into his lab and guided me to pursue graduate work in computer architecture.

Going back even further, I would like to thank Jeffrey Friedman of Rockefeller University for taking a crazy chance on a high school student. I am forever grateful for the patient mentoring by researchers in his molecular genetics lab, and in particular Esra Asilmaz and Gulya Fayzikhodjaeva. From them I learned that there are many important problems science can solve, and I wanted to be a part of that. I would also like to thank Geoff Crowley of Southwest Research Institute for his mentorship that helped further guide my path into research.

I would like to thank the ASPIRE Lab (and before that, the Par Lab) for providing a comfortable home for me and my work throughout grad school. Our corner cubicle, the *Cosmic Cube* (Scott Beamer, Sarah Bird, Henry Cook, and Andrew Waterman), helped make me feel at home, especially during my early years. I'd also like to thank Andrew for always answering my constant stream of questions, while he was busy building the stuff my research depended on.

I would like to give a big thank you to Donggyu Kim for bravely using BOOM as part of his own research, for collecting data, and finding many of the harder-to-find bugs. I would also like to thank Pi-Feng Chiu for her absolutely heroic effort in bringing BOOM to life in silicon form, and Professor Borivoje Nikolić for championing the tape-out.

Thanks to everyone who has sacrificed their time and sanity making *Chisel* a great language that is now used by real companies shipping real products. Many people have contributed, including Jonathan Bachrach, Huy Vo, Andrew Waterman, Jim Lawson, Chick Markley, Richard Lin, Jack Koenig, Adam Izraelevitz, Albert Magyar, Stephen Twigg, and Donggyu Kim.

Thanks to everyone who developed and improved *Rocket-chip*, and whose tape-out experiences helped Pi-Feng and I start our own tape-out standing on second base. Many people have contributed — the upstream open-source *Rocket-chip* has over 50 contributors and it is now used in many RISC-V companies' products — but in particular I would like to thank

Rimas Avižienis, Jonathan Bachrach, Scott Beamer, David Biancolin, Henry Cook, Palmer Dabbelt, John Hauser, Adam Izraelevitz, Sagar Karandikar, Benjamin Keller, Donggyu Kim, John Koenig, Yunsup Lee, Eric Love, Martin Maas, Albert Magyar, Howard Mao, Miquel Moreto, Albert Ou, Brian Richards, Colin Schmidt, Stephen Twigg, Huy Vo, and Andrew Waterman.

The ASPIRE Lab and Par Lab were unbelievably lucky in the quality and dedication of their staff, including Roxana Infante, Tamille Chouteau, Ria Briggs, Kostadin Ilov, and Jon Kuroda. In particular, I would like to thank system administrator Kostadin for working miracles and doing everything in his power to help every student. Even when all of Lake Tahoe got snowed out for the Winter Retreat in 2017, Kostadin still managed to make it there and set everything up anyways.

Speaking of which, I would also like to thank all of the industry sponsors and attendees of our lab's biannual retreats. It is one of the things that has made my graduate school experience unique, and I appreciate the enthusiasm and support provided to me and my crazy venture. Specifically, I would like to thank Mark Rowland for his advice, support, and entertaining war stories that helped me feel that what I was doing mattered.

Triple Rock, Jupiters, and Beta Lounge also deserve recognition for providing a constant and comfortable collaboration space in which to grow friendships and share ideas over the years. Often I found that I was too busy during the working hours to get any work done, and it was only afterwards when the real research discussions could commence, away from computers and email.

I would like to thank my best friend and wife Kimberlee, for her support throughout grad school (and especially while I lingered in the finishing up stage), and for being a sounding board for many of my ideas. You have been my biggest cheerleader, and that has meant the world to me.

Finally, to my family. My brother Andrew Celio, for being my first and longest friend. And to my parents, for guiding me, looking out for me, and always being engaged. I appreciate that I got my first taste of "research" building all manner of contraptions in our garage together.

# Chapter 1

# Introduction

Computer architecture research centers on the study and evaluation of computer systems, their organization, their interfaces, and their implementations. And yet, due to the complexity of modern computer processors, architecture researchers only rarely design and implement entire systems.

There are many valid reasons to eschew the arduous process of implementing full systems. The man-power and the time required to take a project from conception to completion is high. The level of re-use between chip-building research projects is also poor, exacerbating the amount of effort required by each new team to construct a complete system. And certainly, many ideas can be adequately evaluated using software simulators, where researchers can add their one sliver of innovation to an existing research platform.

But some ideas are best evaluated in the context of a full system, and with enough detail to provide performance, power, and area numbers. This thesis aims to provide a piece of the puzzle by implementing — at the register-transfer-level (RTL) — a complete out-of-order processor. We focus not just on the design, but on the manner in which it has been productively produced using a new, more modern hardware construction language. We also discuss how we implemented not just a single processor instance, but rather, a hardware generator that can construct an entire family of out-of-order cores. We call our processor generator the Berkeley Out-of-Order Machine, or BOOM.

## 1.1 Leveraging New Infrastructure

The feasibility of BOOM is in large part due to the available open-source infrastructure that has been developed in parallel at UC Berkeley.

BOOM implements the open-source RISC-V Instruction Set Architecture (ISA), which was designed from the ground-up to enable VLSI-driven computer architecture research. The RISC-V ISA is clean, realistic, and highly extensible. Available software includes the *GCC* and *LLVM* compilers and a port of the Linux operating system. The clean and simple design of RISC-V allowed us to focus on our processor generator's design without getting weighed

down with awkward instructions that demand undue attention. And the advantage of an open-source community-driven ISA allowed us to leverage an existing tool-chain and software base without spending time away from processor implementation to manage software porting efforts.

BOOM is written in *Chisel*, an open-source hardware construction language developed to enable advanced hardware design. *Chisel* allows designers to utilize concepts such as object orientation, functional programming, parameterized types, and type inference which makes it easier to implement highly parameterized hardware generators. From a single *Chisel* source, *Chisel* can generate a cycle-exact Verilog software simulator, Verilog targeting FPGA designs, and Verilog targeting ASIC tool-flows. One of *Chisel*'s strengths is its focus on generating well-formed, synthesizable Verilog. This feature decreased design risk. *Chisel* also brings software development-level productivity to RTL coding. Other hardware description languages feel unwieldy with many common design patterns being awkward or verbose to describe. But *Chisel* lets us focus more time on the ideas we wanted to express, and less time on figuring out *how* to express them.

UC Berkeley also provides the open-source *Rocket-chip* System-on-a-Chip (SoC) generator, which has been successfully taped-out over a dozen times in multiple different, modern technologies by multiple groups [4, 57, 107]. BOOM makes significant use of *Rocket-chip* as a library – the caches, the uncore, and the functional units all derive from *Rocket*. In total, over 11,500 lines of code is instantiated by BOOM from the *Rocket-chip* repository.

### 1.2 Contributions

This thesis makes the following contributions:

- A complete implementation of a superscalar, out-of-order processor generator We built a superscalar, out-of-order processor generator. BOOM implements the entire RISC-V RV64G ISA and the page-based virtual memory Sv39 Privileged ISA such that we can boot the Linux operating system and run user-level applications.

- A competitive implementation BOOM achieves comparable (or better) branch prediction accuracy and instructions-per-cycle performance relative to similarly sized industry out-of-order processors.

- A productive implementation We demonstrated our productive processor generator design by implementing it using only 16k lines of code. We were able to accomplish this task by leveraging many new artifacts in the nascent open-source hardware ecosystem. Specifically, we were able to leverage the open-source RISC-V ISA and its accompanying tool-chain and testing infrastructure, the open-source *Chisel* hardware construction language, and the open-source *Rocket-chip* SoC generator.

• Demonstrated productivity with an Agile tape-out — We further demonstrated our productivity and agility by making significant micro-architectural design changes as part of a two-person tape-out performed over four months.

#### 1.3 Thesis Outline

In Chapter 2 we discuss the state of the industry and of research, and of the technology trends that are motivating changes in both. In particular, there is a growing requirement for high fidelity RTL-based simulations that can provide greater system depth and a higher degree of confidence in performance and power estimations. In Chapter 3 we provide an overview of our superscalar, out-of-order processor generator called BOOM. Chapter 4 discusses in detail our implementation of the branch prediction and instruction fetch pipelines, and how we were able to implement complex branch predictors that can be easily modified and changed to explore new ideas. In Chapter 5 we discuss in more detail how we leveraged the *Chisel* language to productively describe a superscalar, out-of-order datapath generator; we also discuss how we leveraged expert-written functional units to increase our productivity in describing a full processor system capable of executing floating-point applications. And finally, in Chapter 6 we demonstrate our productivity through a case study in which we taped-out an instantiation of BOOM as part of a test-chip fabricated using the TSMC 28 nm HPM process.

# Chapter 2

# Background

This chapter provides the background and motivation for implementing the open-source Berkeley Out-of-Order Machine (BOOM). Section 2.1 discusses the importance of computers and provides motivation for studying computer architecture. Section 2.2 discusses the trends in technology regarding Moore's Law and Dennard Scaling and their effect on processor design and computer architecture research. Section 2.3 discusses the current state-of-the-art in computer architecture research regarding processor simulators as well as related work regarding similar register-transfer-level (RTL) implementation efforts. Section 2.4 describes the organization, or microarchitecture, of a typical, modern processor and introduces the out-of-order microarchitecture. Section 2.5 provides a taxonomy of out-of-order processors while Section 2.6 discusses the history of out-of-order processors. Section 2.7 elaborates on the performance advantages that out-of-order processors have over other processor designs and Section 2.8 concludes.

### 2.1 Motivation

For the past half-century, computers have been a key enabler in technological and societal change. The number of processors worldwide has continued to proliferate with little sign of slowing despite the industry upheaval caused by the current slowing of Moore's Law and the end of Dennard Scaling in 2005.

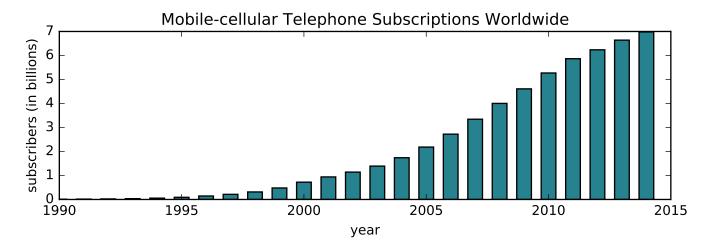

Computer usage has been growing on many fronts. For cell phones, the numbers are absolutely staggering. From the United Nation's World Telecommunication/ICT Indicators Database, over 6 billion people own a cell phone [116] (see Figure 2.1). As a point of comparison, only 4.5 billion people have access to toilets or latrines [115]. For many, cell phones have been an enabler for economic development and societal progress [1, 28, 96].

Cellphones are not the only benefactors of computer architectural innovation. The growth of *Software as a Service* (SaaS) has led to a rise of a new class of computer – the Warehouse-Scale Computer (WSC). There are many demanding applications running on WSCs: search, media delivery, gaming, shopping, social networking, and machine learning. WSCs are typi-

Figure 2.1: Cell phone subscriber counts as provided by the United Nations [116].

cally built in locations where the price of power is cheap as they require megawatts to power (and cool) tens of thousands of compute nodes [77]. Over a ten year period, 30% system cost of a WSC may go to energy, power distribution, and thermal management [77]. However, using wimpier but more power-efficiency cores can dramatically degrade service response times, making the trade-off between performance and power-efficiency a non-trivial design problem [45].

At the opposite end of the compute spectrum, the *Internet of Things* (IoT) promises to create a world of billions of "smart" sensors, dwarfing the current number of deployed processors [9]. However, each device will likely have to be less than \$1 and able to sustain itself on a tiny power budget – perhaps sipping the necessary power from the environment itself [80].

While the number of processors will continue to grow into the near future at all parts of the compute spectrum, from small microwatt processors (IoT) to megawatt computers (WSC), there are a number of challenges that designers face such as cost, reliability, service response time, thermal constraints, and energy-efficiency [45].

### 2.2 Technology and Research Trends

Changes in semiconductor technology have provided computer architects with many new tools with which to pursue higher performance processors in a variety of computing environments. *Moore's Law* has provided architects with more (and faster) transistors with which to implement more complex designs while *Dennard Scaling* has allowed the power requirements to stay manageable. However, the end of Dennard Scaling has made power a first-order design constraint and seriously limited full-frequency transistor utilization.

In 1965, Gordon Moore released a report discussing the trends in transistor technology.

Data available at http://www.karlrupp.net/2015/06/40-years-of-microprocessor-trend-data.

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten.

New plot and data collected for 2010-2015 by K. Rupp.

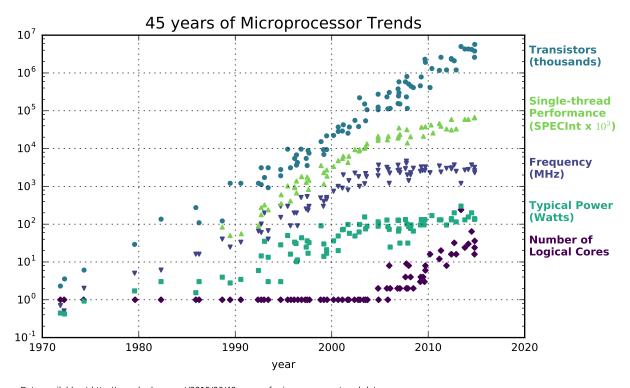

Figure 2.2: Although signs of slowing have begun to show, transistor counts have otherwise continued to scale as predicted by Moore's Law for over 45 years. However, around 2005 processors began to be restricted by power and thermal budgets at around 100 watts (the "power wall") as Dennard Scaling came to an end. This new power constraint prevented frequency from scaling any further, which in turn adversely affected the scaling of single-core performance. Unable to improve scalar performance at the same rates as before, transistor budgets have been redirected to focus on other techniques for delivering value to the user. One technique has been to focus on increasing parallel performance by increasing the number of logical cores.

He noted that electronics became cheaper as more transistors could be placed onto a single circuit chip reducing the total number of chips needed. However, as the number of transistors increased, so did the probability of having a bad transistor, lowering the manufacturing yield and increasing the cost of each chip. These two economic forces worked against each other. But as manufacturing yield improves, cost-efficiency motivates smaller and smaller transistors. In short, transistors would continue to become smaller very quickly, incentivized by economics [72].

Moore noticed that the number of transistors per chip was doubling every year and — from only five data points — predicted that this trend would continue for "at least 10 years" into the future. Indeed, "Moore's Law" — that the most cost-effective transistor size would continue to shrink leading to a doubling of transistor counts roughly every 18 to 24 months — has been maintained for over 50 years.

Three years after publishing his report, Gordon Moore, along with Robert Noyce, founded Intel (originally called NM Electronics). Their first microprocessor, the Intel 4004 used 2,300 transistors in 10 um technology in 1971. 45 years later, the Intel Broadwell-EP Xeon E5-2600 V4 shipped with 7.2 billion transistors using 14 nm technology [79]. Although the number of foundries who can afford the rising costs of pursuing smaller technology nodes has dwindled, some foundries have nonetheless released details of their intentions for delivering 7 nm technology [51].

Moore's Law has provided computer architects an abundance of transistors with which to implement new ideas and techniques for improving processor performance. However, while Moore's Law may end soon [70], the end of Denard Scaling ten years ago signaled the beginning of a real crisis in the industry.

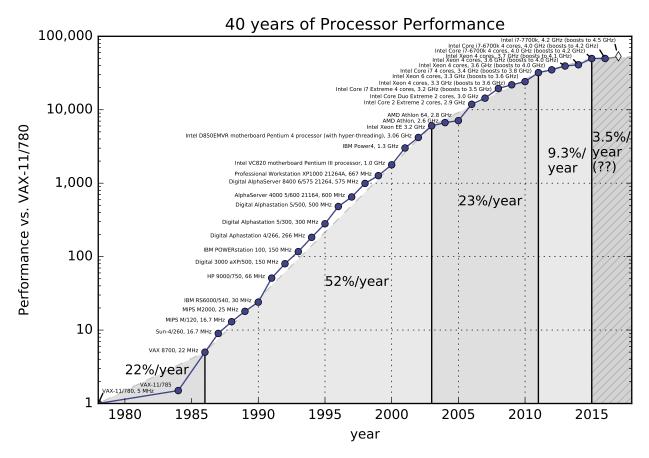

Table 2.1 shows the transistor scaling factors under a Dennard Scaling regime. By scaling voltage, doping, and transistor size together, the signal delay through the transistor could be increased by the same factor while maintaining the same power density as before. In summary, under Dennard Scaling, as a transistor's length and width were halved, new processors could have four times as many transistors, be clocked twice as fast, and use the same amount as power as the previous generation. This led to a golden era of computer architecture in the 1980s and 1990s as transistor counts doubled every 18 months and processor clock frequencies doubled every 36 months. Software became faster by the virtue of Dennard Scaling, and computer architects could explore more complex and transistor-hungry designs to exploit the growing transistor budgets while still hitting their power budgets. Technology improvements working in concert with microarchitectural innovations has led to a 50,000x increase in single-core processor integer performance over the last 45 years as shown in Figure 2.3.

Although the scaling had never been perfect, around 2005, technology scaling fully diverged from the ideal scaling rates described by Dennard, as the voltage could no longer be scaled even as transistors continued to become smaller [104]. As the gate oxide thickness  $(t_{ox})$  grew smaller (which directly sets the threshold voltage  $t_{th}$ ), the current leakage across the gate grew, leading to a rising *static* power and a reduction in transistor reliability [46]. This static power is now significant enough to be a considerable factor in a processor's power

Table 2.1: The scaling factors of a single transistor under a Dennard Scaling regime (1965-2005) [27]. By scaling the voltage and doping along with the size of the transistor each by  $\kappa$ , each transistor can now be clocked  $\kappa$  times faster while maintaining the same power density as the previous generation transistor.

| Device or Circuit Parameter        | Dennard Scaling Factor |

|------------------------------------|------------------------|

| Device dimension $(t_{ox}, L, W)$  | $1/\kappa$             |

| Device quantity (A)                | $\kappa^2$             |

| Doping concentration $(N_a)$       | $\kappa$               |

| Voltage $(V)$                      | $1/\kappa$             |

| Current $(I)$                      | $1/\kappa$             |

| Capacitance $(\epsilon A/t)$       | $1/\kappa$             |

| Delay time / circuit $(VC/I)$      | $1/\kappa$             |

| Power dissipation / circuit $(VI)$ | $1/\kappa^2$           |

| Power density $(VI/A)$             | 1                      |

| Utilization (1/Power)              | 1                      |

Table 2.2: The scaling factors of a single transistor in a post-Dennard Scaling regime (post-2005). As voltage can no longer be scaled down with transistors, each transistor now dissipated the same power as before leading to an increase in power density equal to the increase in transistor density. Constrained by power and thermal requirements, this leads to successive generations of processors that are unable to use more and more of its transistors at full frequency at a rate of  $1/\kappa^2$ . This inability to utilize all of the chips transistors at full frequency simultaneously is known as Dark Silicon [104].

| Device or Circuit Parameter        | Post-Dennard Scaling Factor |

|------------------------------------|-----------------------------|

| Device dimension $(t_{ox}, L, W)$  | $1/\kappa$                  |

| Device quantity (A)                | $\kappa^2$                  |

| Voltage $(V)$                      | 1                           |

| Capacitance $(\epsilon A/t)$       | $1/\kappa$                  |

| Delay time / circuit $(VC/I)$      | $1/\kappa$                  |

| Power dissipation / circuit $(VI)$ | $1/\kappa^2$                |

| Power density $(VI/A=AFC^2)$       | $\kappa^2$                  |

| Utilization (1/Power)              | $1/\kappa^2$                |

budget. With the threshold voltage unable to scale any further, the supply voltage  $(V_{dd})$  scaling has also stopped. The supply voltage  $V_{dd}$  provides a quadratic relationship to the processor's dynamic power [24].

$$Power_{cpu} = Power_{static} + Power_{dynamic}$$

(2.1)

Static power is largely a function of the leakage current across the gate which worsens as the threshold voltage is lowered.

Dynamic power is dissipated on every transistor state transition, and is thus dependent on how often and how many transistors flip from off to on (and vice versa). The  $\alpha$  term denotes what fraction of transistors transit every cycle and is dependent on the workload, f denotes the clock frequency, and C is the *load capacitance* of the processor.<sup>1,2</sup>:

$$Power_{dynamic} = \alpha * C * V_{dd}^2 * f \tag{2.2}$$

As frequency f is typically coupled to  $V_{dd}$ , this provides the following relationship to dynamic power:

$$Power_{dynamic} \propto V_{dd}^3$$

(2.3)

With the supply voltage staying constant in a post-Dennard Scaling regime, each transistor now dissipates the same amount of power as before, leading to growing power density as the number of transistors on a chip continues to increase. As Moore's Law has continued past the end of Dennard Scaling, this has meant that processors can no longer switch every transistor at full frequency without exceeding the power or thermal limitations of the chip. Instead, computer architects have had to rely on a number of techniques to manage the new "power wall" limitations [104]. Table 2.2 describes this new scaling regime.

One change was a move to multicore processors. Instead of a single, monolithic, high frequency core, processors moved to a modest number of processor cores that were clocked at a slightly slower frequency than the previous generation. As shown by Equations 2.2 and 2.3, a slight reduction in frequency allows for a slight reduction in voltage which leads to a significant reduction in power. However, the move to multicore processors has been a significant burden on programmers. One problem with the shift to multicore processors is the fact that most applications have a fundamental serialization limit, codified by *Amdahl's Law*. This serialization bottleneck restricts the maximum potential speedup from parallelizing a particular algorithm [2].

Another approach to managing the power wall has been to rely on specialization. A particular algorithm may only utilize a small, but highly specialized fraction of the chip. As the program goes through different phases and utilizes different algorithms for each phase,

<sup>&</sup>lt;sup>1</sup>These equations assume the voltage swing is equal to the supply voltage [99].

<sup>&</sup>lt;sup>2</sup>Particularly for high-frequency processors, there is an added "short-circuit" power dissipation term that occurs when both transistors in a CMOS gate are on simultaneously, connecting the power source to ground, and is a function of activity factor  $\alpha$  and frequency f [109].

different parts can be turned on or off as needed. Specialized circuits, known as *accelerators*, have been used for cryptography, compression, graphics, and machine learning. Accelerators can provide performance and energy-efficiency improvements in the range of 100-1000x over a general-purpose processor core [104].

### 2.2.1 Impact of Performance Slowdown on Architecture Research

The end of Dennard Scaling has led to significant challenges in the field of computer architecture. Processor frequency gains and single-core performance has stalled. As shown in Figure 2.3, it is becoming more and more challenging to realize additional gains in single-core performance. For this reason, we believe it is becoming more important to simulate and evaluate microarchitectural ideas at a higher level of fidelity than was needed in the past.

There are many different levels of fidelity for describing a processor. High-level, *cycle-approximate* models are used to simulate a processor to provide a high-level view of how the performance might change.

The register-transfer-level (RTL) is a level in which the processor description encompasses the behavior and movement of data between hardware registers. Although RTL was originally used as a relatively high-level simulation abstraction to provide a cycle-accurate simulation of a design, VLSI tools have since evolved to map RTL descriptions directly to physical realizations.

While high-level, cycle-approximate models provide the flexibility to quickly iterate and explore the design space, they have significant blind spots. RTL models provide a list of advantages. First, coupled with the appropriate CAD tools, RTL implementations can provide area, power, and timing information that is not available in higher-level models. Second, RTL implementations are more likely to be grounded in reality. This grounding has a number of advantages. It provides a higher degree in confidence, it can prevent correctness errors from changing research conclusions, and it can motivate new design ideas that must manage realistic constraints.

Despite industry's best efforts, the gains in single-thread performance has continued to slow. From the data from [53] and [78] (Figures 2.2 and 2.3), the SPECINT performance has increased by only around 9% per year in the last six years. The most recent Intel processor, the 2017 Kaby Lake, uses the same technology process and the same microarchitecture as its 2015 predecessor Skylake. Kaby Lake represents as "optimization" stepping in which Intel utilized low-level optimizations to provide a 7% improvement in the peak clock frequency. However, this peak frequency can only be realized by a small fraction of the processor at any one point in time. Intel calls this "Turbo Boosting" in which a single core may be clocked at a higher frequency while keeping the other cores in a lower energy state so long as the total processor's power and thermal requirements are maintained.

To realize these continued gains often requires a few new microarchitectural tricks, each providing only a few percent gains each in performance. Thus, to evaluate a new, industry-

Figure 2.3: Microarchitectural ideas for improving performance are becoming harder and harder to come by. Data is shown comparing SPECIntbase performance relative to a VAX-11/780. Early performance gains were largely technology driven. In the 1980s and 1990s, computer architectural innovations – such as the ability to recognize and exploit instruction-level parallelism (ILP) – worked together with continued technological improvements to deliver even greater performance gains. However, the end of Dennard Scaling in 2005 caused processor frequencies to stall. Around the same time, the remaining ILP had become more difficult to extract. Both of these factors have conspired to slow single-core performance gains. Performance once again appears to be limited to technology improvements and circuit-level techniques that provide more efficient usage of power. As SPEC is updated over time, performance is estimated by use of a scaling factor to normalize across different versions of SPECInt (SPEC89, SPEC92, SPEC95, SPEC2000, SPEC2006). The scaling factor is empirically determined by running multiple versions of SPEC on a subset of the provided machines. The SPEC performance of the just-released Kaby Lake i7-7700k is synthetically created by comparing the relative Geekbench results [37] and the clock frequency improvement to the Skylake i7-6700k, with which it shares the same micro-architecture and process technology. Data is provided by [78].

worthy idea requires a significant degree of fidelity to provide the necessary confidence. Current methodologies are geared towards finding integer factor improvements, and are not well suited for exploring small wins on the order of 2-3%. These small gains suggests a requirement for higher fidelity methodologies that include utilizing RTL implementations.

# 2.3 Computer Architecture Research Trends

In a perfect world, computer architecture researchers would design, implement, and then fabricate their research designs to fully analyze and evaluate their ideas. Although there are a few examples of such ambitious research projects [88, 105, 57, 100], this methodology is largely infeasible for a number of reasons. First, the feedback loop from generating an idea to measuring a single implementation takes many years; the man-power and fabrication costs can be prohibitive; and some research ideas attempt to explore future designs that speculate technological abilities that are not yet available.

For these reasons, most computer architecture research relies on simulators to model processors. Simulators can allow a very small team of researchers to quickly implement and explore a design space before providing recommendations. Even industry first relies on insights gained by simulators before spending resources implementing a physical design.

Ideal simulators attempt to achieve the following goals:

- 1. The **fidelity** of the simulator does it accurately model the intended target?

- 2. The simulation **speed** of the simulator how many design points (or workloads) can we explore in a fixed period of time?

- 3. The **scope** of the simulator does it provide area, power, and timing insight into the design?

- 4. The **flexibility** of the simulator can new ideas be quickly and easily implemented and evaluated?

Unfortunately, these traits are in competition; there is no perfect simulator.

#### 2.3.1 Architectural Simulators

Computer architecture research is largely carried out using simulators to model future hypothetical processor designs. Unfortunately, most research has focused on ease of implementing new ideas at the cost of fidelity, speed, and accuracy. Attempts to improve these metrics have largely be zero-sum with the ease of implementing new ideas.

SimpleScalar, released in 1996, models an out-of-order processor which implements a simplified derivative of the MIPS IV ISA [17]. However, SimpleScalar can only execute user-level code making it difficult to explore interactions between user and privilege-level code

like operating systems [16]. Users would also have to compile their benchmarks specifically for SimpleScalar and could not study commercial or off-the-shelf software.

Simics is an functional architectural simulator released in 2002. It executes unmodified software programs and is able to simulate a full system including supervisor instructions and provides interfaces to many different I/O devices. However, it only provides functional simulation and provides no microarchitectural or timing information [61]. Later efforts from other groups have added their own timing models on top of Simics [62].

The SESC ("Super ESCalar") simulator (2004) splits the execution model from the timing model. One advantage of this separation of concerns is it allows small errors in the timing model to not affect the correctness of the simulation. In a few cases, SESC developers purposefully eschew rare corner-cases that could affect the simulation speed or complexity of the simulator. SESC is not a full-system simulator and must trap all application system calls and emulate them [75]. Although it targets a MIPS ISA, it requires a custom toolchain to build applications to run on SESC. SESC is around 120k lines of code spread across nearly 400 files [52].

The QEMU emulator (2005) is a very fast functional full-system emulator. It uses dynamic binary translation to translate instructions from the target architecture into a sequence of host instructions. QEMU then caches, or remembers, these translations for future iterations through the program. This optimization allows QEMU to run close to native host processor speeds, simulating over 1 billion instructions per second (1 GIPs) [12]. QEMU, by itself, provides no timing modeling.

The gem5 simulation infrastructure (2011) provides both microarchitectural timings models and a full-system simulator able to simulate many different commercial ISAs. The gem5 system provides a flexible, modular framework that can utilize a number of processor models, memory system models, and network models. The range of models of varying complexity and accuracy allow users to trade off simulation speed for fidelity. Gem5 also provides a full system simulation mode which simulates user-level and privilege-level software while also providing models of device drivers for the OS to interface with. Checkpoint saving and restoring support is available, allowing researchers to avoid painful start-up overheads by loading up the same architectural state from a particular workload onto different microarchitectures under study [14].

MARSS (Micro Architectural and System Simulator) is a simulator (2011) built on top of the QEMU emulator [12]. When executing in a low-level, cycle-approximate detailed simulation mode, it is able to simulate a multicore processor at a simulation speed of 200 to 400 kilo instructions per second (KIPs) [76].

An updated version of SESC, called ESESC ("Enhanced SESC"), also uses QEMU for its execution model, allowing it to simulate the ARM instruction set. ESESC approaches simulating multi-threaded applications across multiple cores using Time-Based Sampling (TBS). The ESESC developers found the average error of the time-based sampling method to be within 4.99% compared to full simulation for a number of target configurations and applications [5]. ESESC integrates with the McPAT energy modeling tool to provide models for power and temperature. By utilizing sampling, ESESC can achieve up to 9 MIPs. The

full ESESC repository contains over 14 million lines of C and C++ code, which includes the tool chains, the QEMU simulator, and the McPAT energy model. The ESESC-specific timing models are more manageable at 100k lines of code and the thermal and power code is 300k lines of code [32].

SimFlex is another simulator that relies on statistical sampling to provide wider coverage across long-running workloads. Flexus is a full-system simulation infrastructure built on top of Simics. SimFlex is a methodology built on top of Flexus which uses a mixture of restoring workload checkpoints, fast microarchitectural warming, and detailed simulation of small simpoints to approximate the performance of a full workload [121].

Simulating processor cores at a high level of fidelity naturally leads to very slow simulations — the simulation model (which runs on the order of 100s of kilohertz) is typically on the order of 10,000 times slower than a real processor (running in the range of a gigahertz). As processors move to using multiple cores, the simulation slow-down is exacerbated. Tan [103] reported that the number of simulated cycles per benchmark in ISCA in 1998 was the same in 2008, but that the simulated core counts had increased from 1 to 16, diluting the number of simulated cycles per core.

The Sniper Multi-core Simulator tackles this problem by simulating each core at a higher level of detail using "interval simulation" [38, 43]. Instead of simulating the core at a cycle-approximate level, Sniper builds an analytical model as it executes a program. It begins by breaking up programs into "intervals" based on the "miss events", which are expensive, slower operations such as cache misses or branch mispredictions. Sniper then analyzes how these expensive miss events interact and provides an estimation for how much time each interval adds to the simulation time. This higher level of abstraction allows Sniper to run at "around 1 MIPS for an 8-core simulation" [5]. Sniper was validated against multi-socket Intel Core2 and Nehalem systems and provides average performance prediction errors within 25% while achieving a speed of up to several MIPS [43].

Simulating even higher core counts has proven difficult, as the additional cores further degrade the simulation speed. Ideally, each simulated ("target") core could be simulated on a single "host" core. However, to provide a cycle-accurate model, the host cores would have to synchronize after simulating every target cycle. Also, any communication between the target cores would have to be handled between the host cores before the next cycle of target simulation could begin. The goal of Graphite is to enable thousand-core processor simulations. Graphite accomplishes this by being a distributed parallel multi-core simulator that relies on relaxing the strict ordering of events between the simulated cores. Each target core is broken into two pieces — a core model and a memory model — each piece is simulated via its own host thread. The threads are then scheduled across a cluster. When target cores send data to one another, they also synchronize their clocks, allowing core clocks to skew within a bounded amount of time. Running 1024 cores on eight 8-core processors exhibited a 41x slow-down from native execution [69]. Graphite is built on top of Pin to provide dynamic binary translation [59]. Pin allows off-the-shelf x86 ISA applications to be functionally simulated while also providing event handlers to hook into the Graphite timing model.

ZSim is another thousand-core simulator that utilizes dynamic binary translation techniques to create "instruction-driven timing models", as opposed to "event-driven models". It also introduces a technique called "bound-weave", a two-phase technique in which cores may skew events with respect to each other for a bounded period of time for the first phase, and in the second phase replay the trace of events to determine the actual latencies [85].

A major downside to all of these software simulators is the roughly  $\approx 10,000x$  simulation penalty to model any level of microarchitectural timing. One solution is to run the simulator on a Field Programmable Gate Array (FPGA). FPGAs are silicon chips that are "programmable" – RTL hardware designs may be synthesized and "simulated" on the FPGA. As FPGAs run on the order of 10s to 100s of MHz, FPGA-based simulators can provide orders of magnitude increases in simulation speeds [23, 102].

Ramp Gold is a one example of an FPGA-based simulator [103, 102]. It simulates 64 SPARC in-order cores on a single \$750 FPGA board. It accomplishes this by a) decoupling the FPGA's clock from the simulated target clock (many FPGA clock cycles are required to simulate a single target cycle), b) abstracting some of the uncore timing models to allow for higher-level descriptions, and c) multi-threading the single, physical processor pipeline and sharing it across 64 simulated target cores. RAMP Gold's FPGA clock ran at 50 MHz, or 0.0156 MHz target frequency, for a speedup of roughly 250x relative to a detailed Simics+GEMS simulation of a similar target platform. The Ramp Gold functional model is roughly 35,000 lines of SystemVerilog while the timing model is only 1,000 lines of SystemVerilog [103]. However, Ramp Gold's major downside is the difficulty in modifying Ramp Gold to explore other processor design points. The timing model and the functional model are fairly wedded to simulating homogenous, in-order cores.

Many of the simulators discussed all suffer from similar problems: 1) many do not support full systems, 2) they suffer from slow simulation speeds (generally less than 200 kHz for software simulators [85]), 3) they cannot produce area, power, or timing numbers, and 4) they produce hard to trust or verify results when exploring new designs that look significantly different from current industry designs.

Unfortunately, the challenges imposed by the power constraints brought on by the end of Dennard Scaling make it vitally important that microarchitectural ideas are evaluated not just by their effect on performance but also on area and power. Perhaps more importantly, the significant slow-down in single-core performance improvements necessitate that any ideas we explore must be done so with high fidelity.

### 2.3.2 RTL Implementations

Due to the limitations of simulators as described in the previous section, there have been a few academic efforts to implement cores at the register-transfer-level (RTL). We will focus on out-of-order cores which attempt to capture the highest level of general-purpose single-core performance.

The Illinois Verilog Model (IVM) is a "latch-accurate" model of a 4-issue, out-of-order core designed to study transient faults [119]. Written in Verilog-95, IVM originally relied

Table 2.3: A sample of simulators. Many modern simulators use dynamic binary translation (DBT) to accelerate execution, typically leveraging existing functional emulators QEMU [12] or Pin [59]. Data compiled with help from [85].

| Simulator         | year | Engine         | Parallelization           | Detailed   | Full   | unmodified |

|-------------------|------|----------------|---------------------------|------------|--------|------------|

|                   |      |                |                           | Uarch      | System | binaries   |

| SimpleScalar [16] | 1996 | emulation      | sequential                | 000        | no     | no         |

| Simics [61]       | 2002 | emulation      | sequential                | no         | yes    | yes        |

| SESC [75]         | 2004 | emulation      | sequential                | OOO        | no     | no         |

| QEMU [12]         | 2005 | DBT            | sequential                | no         | yes    | yes        |

| Graphite [69]     | 2010 | DBT (Pin)      | skew                      | approx-IO  | no     | yes        |

| Ramp Gold [103]   | 2010 | FPGA           | sequential                | IO         | no     | yes        |

| gem5 [14]         | 2011 | emulation (m5) | sequential                | OOO        | yes    | yes        |

| MARSS [76]        | 2011 | DBT (QEMU)     | sequential                | OOO        | yes    | yes        |

| Sniper [43]       | 2012 | DBT (Pin)      | skew                      | approx-OOO | no     | yes        |

| ESESC [5]         | 2013 | DBT (QEMU)     | $\operatorname{sampling}$ | OOO        | yes    | yes        |

| ZSim [85]         | 2013 | DBT (Pin)      | bound-weave               | DBT-OOO    | no     | yes        |

Table 2.4: A sample of academic out-of-order processors and the open-source UltraSPARC T2. The UltraSPARC T1, also open-source, was modified by Princeton to create the OpenPiton many-core processor [11].

|                     | IVM             | SCOORE   | FabScalar                   | Sharing         | BOOM           | UltraSPARC T2 |

|---------------------|-----------------|----------|-----------------------------|-----------------|----------------|---------------|

|                     | [119]           | [10]     | [29, 84]                    | [126]           |                | [74]          |

| industry            |                 |          |                             |                 |                |               |

| fully synthesizable | $\sqrt{}$       |          | $\sqrt{}$                   | $\sqrt{}$       | $\sqrt{}$      | ,<br>V        |

| FPGA                | •               | <b>√</b> | ·<br>√                      | •               | · /            | ·<br>√        |

| parameterized       |                 | ·        | <b>v</b>                    |                 | <b>v</b>       | •             |

| floating point      |                 | <b>√</b> | •                           |                 | <b>v</b>       | 1/            |

| atomic support      |                 | ·        |                             |                 | <b>v</b>       | v<br>√        |

| L1 cache            | <b>√</b>        | <b>√</b> | <b>√</b>                    | <b>√</b>        | <b>v</b>       | <b>v</b>      |

| L2 cache            | v               | ·        | <b>v</b>                    | <b>v</b>        | <b>v</b>       | 1/            |

| virtual memory      |                 |          | V                           | v               | v<br>√         | <b>v</b>      |

| boots Linux         |                 |          |                             |                 | v<br>√         | v<br>√        |

| multi-core          |                 |          | 1/                          |                 | 1/             | 1/            |

| ISA                 | Alpha (sub-set) | SPARCv8  | PISA (sub-set) <sup>†</sup> | Alpha (sub-set) | RISC-V         | SPARCv9       |

| lines of code       | 30,000          | ?        | 75,000 <sup>†</sup>         | 31,900          | 9,000 + 11,500 | 1,900,000     |

<sup>†</sup>Information was gathered from publicly available code at [33].

on some unsynthesizable constructs (such as while loops that do not terminate on constant synthesis-time values), but it has since been patched to be fully synthesizable [24].

The Santa Cruz Out-of-Order RISC Engine (SCOORE) was designed to efficiently target both ASIC (1 Ghz at 90 nm) and FPGA generation (200 MHz) [67]. Unfortunately, SCOORE lacks a synthesizable fetch unit and was never completed.

FabScalar is a tool for composing synthesizable out-of-order cores. It searches through a library of parameterized components of varying pipeline width and depth to find an optimal core design for a given benchmark set, guided by performance constraints given by the designer [24]. FabScalar has been demonstrated on an FPGA [29], however, as FabScalar did not implement caches, all memory operations were treated as cache hits. Later work incorporated the OpenSPARC T2 caches in a tape-out of FabScalar [84].

The Sharing Architecture is composed of a two-wide out-of-order core (or "slice") that can be combined with other slices to form a single, larger out-of-order core. By implementing a slice in RTL, they were able to accurately demonstrate the area costs associated with reconfigurable, virtual cores [126].

Unfortunately, there are currently no open-source industry implementations of an out-of-order core. However, Sun has released two of their SPARC v9 server-level processors, the UltraSPARC T1 and UltraSPARC T2 cores under a GPL license in 2006 and 2007 [74]. The T1 and T2 processors are in-order multi-threaded eight-core processors, supporting four and eight threads respectively.

The goal of the UltraSPARC design was not to have beefy, complex, and expensive cores, but rather to have a larger number of simpler cores that can support multiple threads each to provide higher aggregate throughput. The T1 processor was produced in 2005 at 1.2 GHz in 90 nm. The whole chip was 279 M transistors in  $378mm^2$  and used roughly 70 watts [66].

OpenPiton is an academic research processor built using the UltraSPARC T1 source code. Although they utilized the T1 cores (with some modifications), they implemented their own uncore and network interconnects to build a many-core processor that could scale to hundreds, if not thousands, of cores. They taped out a 25 core version on IBM 32 nm SOI process on a  $36mm^2$  die with a target frequency of 1 GHz [11].

Although our discussion has currently centered on academic research, industry has their own need for RTL-level emulation of hardware designs. Engineers use "hardware emulation" platforms to test and verify new chip implementations before sending the design out for manufacturing. Even for industry, full-scale product prototypes are typically too expensive to rely on (and are often too opaque to debug as problems arise).

Unfortunately FPGAs are typically capacity-constrained and are unable to fully contain a processor design that is on the order of 100s of millions to billions of transistors. Intel demonstrated emulating a complex Intel Nehalem out-of-order core<sup>3</sup>, but it required five Virtex-5 FPGAs, required changes to the 5% of the RTL code, and could only run at a target frequency of 520 KHz. Splitting the design to fit across an FPGA is a manual process that includes needing to implement the infrastructure to communicate across the boundaries.

<sup>&</sup>lt;sup>3</sup>An 8-core Xeon Nehalem-EX is 2.3 billion transistors.

The other challenge is in translating the design to be synthesizable for FPGAs. Some constructs, such as double-phase latch RAMs and aggressive clock gating, have no direct FPGA analogue. Finally, after performing the remapping to a different implementation technology, engineers then have to reverify that the design is still the same [86].

One solution used by industry is the Palladium hardware emulation platform from Cadence Design Systems. Palladium allows engineers to directly simulate their designs without requiring RTL code changes. And to handle capacity issues, Palladium tools can seamlessly partition a single design across an entire Palladium cluster. In a blogpost from 2011, NVIDIA's Emulation Lab discussed their use of multi-million dollar Palladium XP systems to debug and verify their graphic processor (GPU) designs. Although they used multiple Palladium clusters to simulate their GPUs, the entire lab could only simulate 4 billion transistors in total [60]. For comparison, a single multimillion dollar 16-chassis Palladium emulator was used by NVIDIA to debug their Fermi microarchitecture, a 3 billion transistor GPU in 40 nm [95]. The more recent Palladium XP II platform provides support of up to 2.3 billion ASIC gates of design capacity and can emulate designs at speeds up to 4 MHz. Palladium also provides some power analysis modeling, including the ability to identify power peaks and to model low-power modes [19, 87, 20].

For established companies shipping large and complex designs, Palladium provides a productive solution for verifying designs before manufacturing. However, Palladium is not a good match for smaller teams that cannot afford the multi-million dollar price tag, or for engineers who need closer-to-real-time performance for running longer software workloads, or for early-stage design exploration where some aspects of the project may be abstracted for flexible modifications of the system under test.

### 2.3.3 Energy Modeling Methodologies

After the end of Denard Scaling, power consumption and energy efficiency have become a first-order design constraint. This "power wall" is further exacerbated for mobile processors, which demand desktop-level user experiences in a roughly 1 watt envelope.

Power usage is important for all environments, though for different reasons. For mobile processors, poor energy-efficiency directly limits the length of time between required battery charges. High power-usage can create thermal issues and even physically burn the user. For desktop processors, more power-usage requires louder air-cooling solutions. For servers, there is a fundamental limit to how much power can be brought physically into the building for powering the chips and the cooling systems to manage the heat given off by the processors.

Unfortunately, analyzing the power and energy usage of designs has proven to be very difficult, and the most accurate measurements can only be made after a design has been taken to the floorplanning phase (or better yet, measured from a physical chip). Instead, a common technique is to couple analytical power models with micro-architectural simulators.

Wattch is a framework at the architectural level that connects to the SimpleScalar simulator, allowed early culling of the design space via high-level power estimation. The functional simulator generates microarchitectural event counts, such as instruction fetches or cache accesses, which are then fed into an abstract power model. However, Wattch only provides dynamic power modeling; it does not provide area, timing information, or static power modeling. As transistors have become smaller, static power usage due to increased leakage current has now become a significant fraction of total system power [15].

A similar energy estimation framework is SimplePower. SimplePower plugs into SimpleScalar and models a 5-stage pipeline, L1 caches, and off-chip memory. It uses simple analytical models for estimating memory power usage. For the busses between different levels in the memory hierarchy, SimplePower uses a transition-sensitive approach, taking into account both the switching activity and the interconnect capacitance on the bus lines. It also models transition-sensitive functional units to get the data path power usage. However, it only provides energy estimation for an integer RISC ISA using a 5-stage pipeline [118].

McPAT is the current popular tool that provides timing, area, and power estimations for multi-core and many-core processors. McPAT supports both in-order and out-of-order cores. McPAT can be integrated into any performance simulator, such as ESESC or gem5, by taking in the dynamic activity event counts and feeding them into its power models. McPAT also has the ability to model different processor energy states, and even feed that information back into the architectural simulation to model power and thermal events during the lifetime of the workload [58].