# Bottom-up Memory Design Techniques for Energy-Efficient and Resilient Computing

Pi-Feng Chiu

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2018-156 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2018/EECS-2018-156.html

December 1, 2018

Copyright © 2018, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Bottom-up Memory Design Techniques for Energy-Efficient and Resilient Computing

by

Pi Feng Chiu

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Krste Asanović Professor Lane Martin

Spring 2018

# Bottom-up Memory Design Techniques for Energy-Efficient and Resilient Computing

Copyright 2018 by Pi Feng Chiu

#### Abstract

Bottom-up Memory Design Techniques for Energy-Efficient and Resilient Computing

by

Pi Feng Chiu

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

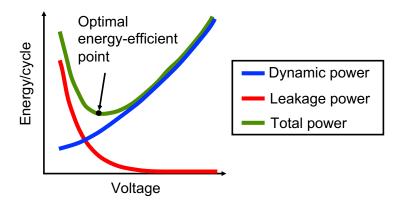

Energy-efficient computing is critical for a wide range of electronic devices, from personal mobile devices that have limited battery capacity to cloud servers that have costly electricity bills. The increasing number of IoT devices has resulted in a growing demand for energy-efficient computing for battery-powered sensor nodes. The energy spent on memory access is a major contributor of total energy consumption, especially for new, data-intensive applications. Improving memory energy efficiency helps build energy-efficent computing systems. One effective way to achieve better energy efficiency is to lower the operating voltage by using the dynamic voltage and frequency scaling (DVFS). However, further reductions in voltage are limited by SRAM-based caches. The aggressive implementation of SRAM bit cells to achieve high density causes larger variation than in logic cells. In order to operate the processor at the optimal energy-efficient point, the SRAM needs to reliably work at a lower voltage.

The sense amplifier of the memory circuit detects the small signal from the bit cell to enable high-speed and low-power read operation. The mismatch between the transistors due to process variation causes an offset voltage in the sense amplifier, which could lead to incorrect results when the sensing signal is smaller than the offset. The double-tail sense amplifier (DTSA) is proposed as a drop-in replacement for a conventional SRAM sense amplifier to enable robust sensing at low voltages. The dual-stage design reduces the offset voltage with a pre-amplification stage. The self-timed regenerative stage simplifies the timing logic and reduces the area. By simply replacing the conventional sense amplifier with DTSA, SRAM can operate with a 50mV Vmin reduction at faster timing.

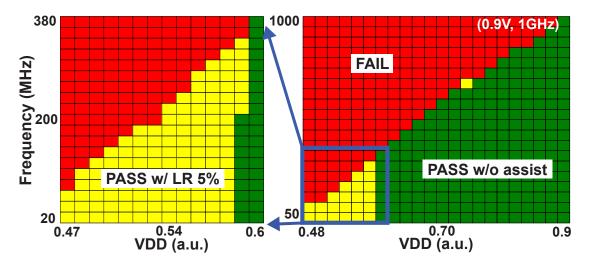

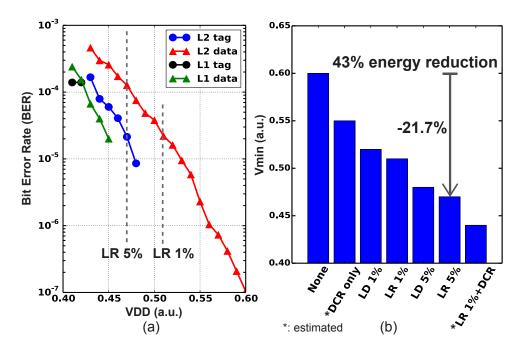

Memory resiliency can be achieved through architecture-level assist techniques, which enable low-voltage operation by avoiding failing cells. The line disable (LD) scheme deactivates faulty cache lines in a set-associative cache to prevent bitcell with errors from being accessed. The Vmin reduction of LD is limited by the allowable capacity loss with minimum performance degradation. The line recycling (LR) technique is proposed to reuse two disabled faulty cache lines to repair a third line. By recycling the faulty lines, 1/3 of the capacity

loss due to LD can be avoided for the same Vmin, or one-third as many faulty cache lines can be ignored.

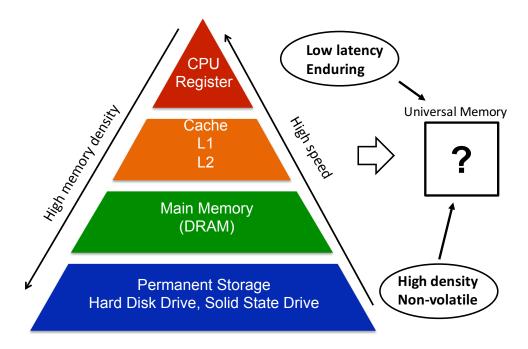

Emerging nonvolatile memory (NVM) technologies, such as STT-MRAM, RRAM, and PCM, offer a tremendous opportunity to improve energy efficiency in the memory system while continuously scaling. The new technologies are faster and more durable than NAND flash, therefore, can be placed closer to the processing unit to save the energy by powering off. However, reliable access to NVM cells faces several challenges, such as shifting of cell resistance distributions, small read margins, and wear-out.

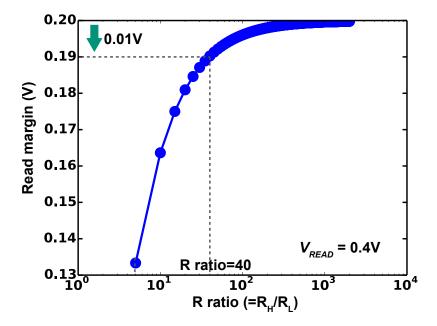

The proposed differential 2R crosspoint resistive random access memory (RRAM) with array segmentation and sense-before-write techniques significantly improves read margin and removes data-dependent IR drop by composing one bit with two complementary cells. The proposed array architecture ensures large read margin (>100mV) even with a small resistance ratio  $(R_H/R_L=2)$ .

In summary, this dissertation introduces techniques at different levels of memory design (device, circuit, and micro-architecture) that can work in concert to build a resilient and energy-efficient memory system. The proposed techniques are demonstrated on several chips fabricated in a 28nm CMOS process.

To my husband, Wei-Han.

# Contents

| Contents |                                                               |                                             | ii  |  |  |

|----------|---------------------------------------------------------------|---------------------------------------------|-----|--|--|

| Li       | $\mathbf{st}$ of                                              | Figures                                     | iv  |  |  |

| Li       | st of                                                         | Tables                                      | vii |  |  |

| 1        |                                                               | roduction                                   | 1   |  |  |

|          | 1.1                                                           | Energy-efficient computing                  | 1   |  |  |

|          | 1.2                                                           | Semiconductor memory technologies           | 2   |  |  |

|          |                                                               | 1.2.1 Memory                                | 2   |  |  |

|          |                                                               | 1.2.2 Storage                               | 4   |  |  |

|          |                                                               | 1.2.3 Storage class memory (SCM)            | 6   |  |  |

|          | 1.3                                                           | Limitation on energy-efficient memory       | 6   |  |  |

|          | 1.4                                                           | Techniques at different levels              | 7   |  |  |

|          | 1.5                                                           | Scope of the dissertation                   | 8   |  |  |

|          | 1.6                                                           | Thesis outline                              | 9   |  |  |

| 2        | Sense Amplifiers for Low-Voltage SRAM                         |                                             |     |  |  |

|          | 2.1                                                           | Basic SRAM operations                       | 11  |  |  |

|          | 2.2                                                           | Challenges for low-voltage sensing          | 13  |  |  |

|          | 2.3                                                           | Conventional Sense Amplifiers and Pior Work | 15  |  |  |

|          | 2.4                                                           | Double-Tail Sense Amplifier                 | 16  |  |  |

|          | 2.5                                                           | Silicon Measurement Results                 | 20  |  |  |

|          | 2.6                                                           | Comparison                                  | 23  |  |  |

|          | 2.7                                                           | Conclusion                                  | 25  |  |  |

| 3        | Cache Resiliency with Architecture-level Assist Techniques 26 |                                             |     |  |  |

|          | 3.1                                                           | Introduction                                | 26  |  |  |

|          | -                                                             | 3.1.1 ECC-based techniques                  | 28  |  |  |

|          |                                                               | 3.1.2 Redundancy-based techniques           | 29  |  |  |

|          |                                                               | 3.1.3 Disable-based techniques              | 30  |  |  |

|          | 3 2                                                           | Line Recycling (LR)                         | 31  |  |  |

|    |       | 3.2.1 Implementation                              | 33     |

|----|-------|---------------------------------------------------|--------|

|    | 3.3   | Bit Bypass with SRAM implementation (BB-S)        | 35     |

|    |       | 3.3.1 Implementation                              | 37     |

|    | 3.4   | Error Model                                       | 38     |

|    | 3.5   | Resilient Out-of-Order processor                  | 40     |

|    |       | 3.5.1 Berkeley Out-of-Order Machine (BOOM)        | 41     |

|    |       | 3.5.2 Implementation of the Resiliency Techniques | 43     |

|    | 3.6   | Conclusion                                        | 47     |

| 4  | Imp   | plementation of Resilient Out-of-Order Processor  | 48     |

|    | 4.1   | Overview                                          | 48     |

|    | 4.2   | Preparing the design                              | 49     |

|    | 4.3   | Synthesis                                         | 50     |

|    | 4.4   | Placement and routing                             | 51     |

|    | 4.5   | Sign-off                                          | 52     |

|    | 4.6   | Case Study: Implementation of the Register File   | 53     |

|    | 4.7   | Measurement                                       | 54     |

|    |       | 4.7.1 Measurement setup                           | 56     |

|    |       | 4.7.2 Measurement Results                         | 57     |

|    | 4.8   | Conclusion                                        | 60     |

| 5  | Eme   | erging Nonvolatile Memory                         | 61     |

|    | 5.1   | Introduction                                      | 61     |

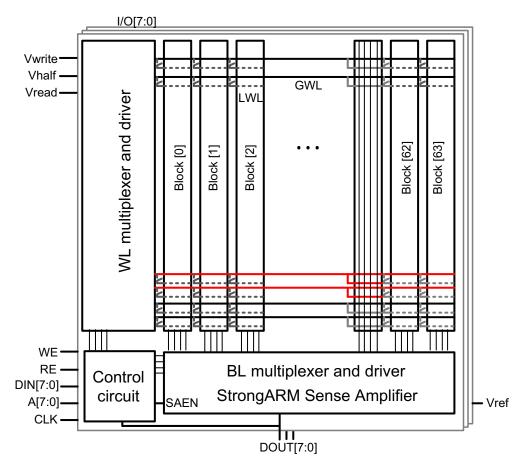

|    | 5.2   | Array architecture                                | 62     |

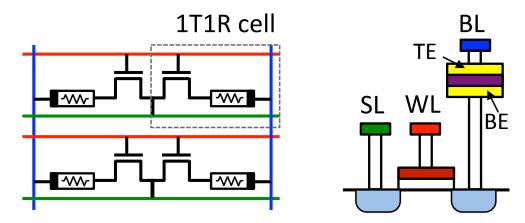

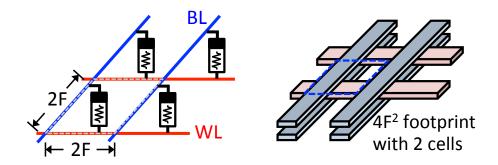

|    | J     | 5.2.1 RRAM bitcell structure                      | 62     |

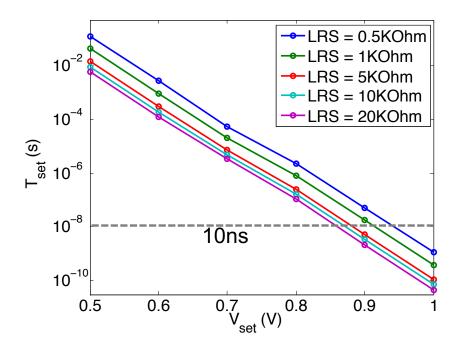

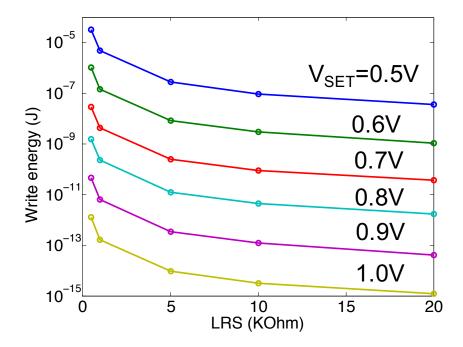

|    |       | 5.2.2 Switching behavior                          | 64     |

|    |       | 5.2.3 Analysis of leakage current                 | 65     |

|    | 5.3   | Differential 2R Crosspoint Array                  | 67     |

|    | 0.0   | 5.3.1 Circuit Implementation                      | 68     |

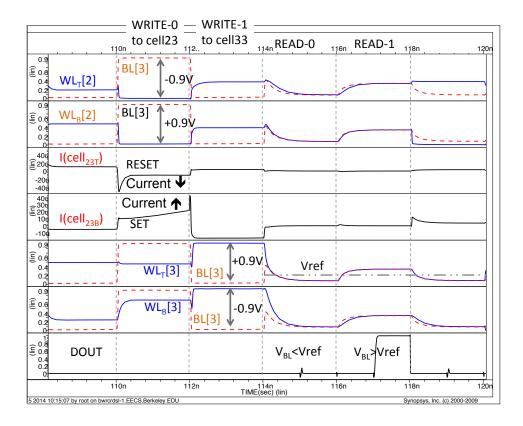

|    |       | 5.3.2 Simulation Results                          | 71     |

|    | 5.4   | Differential RRAM in memory hierarchy             |        |

|    | 5.5   | Conclusion                                        | 74     |

|    | 0.0   | Conclusion                                        | 14     |

| 6  |       | nclusion                                          | 75     |

|    | 6.1   | Summary of Contributions                          | 75<br> |

|    | 6.2   | Future Work                                       | 76     |

| Bi | bliog | graphy                                            | 78     |

# List of Figures

| 1.1  | Trade-offs of dynamic energy consumption and leakage energy consumption and                                                                                |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | the definition of the optimal energy enfficient point                                                                                                      | 2  |

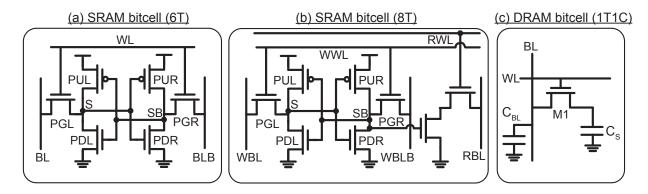

| 1.4  | 1T-1C DRAM bit cell                                                                                                                                        | _  |

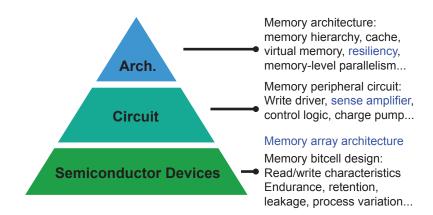

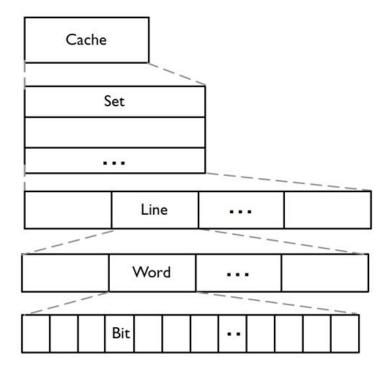

| 1.3  | Different levels of memory design, including semiconductor devices, circuit, and architecture.                                                             |    |

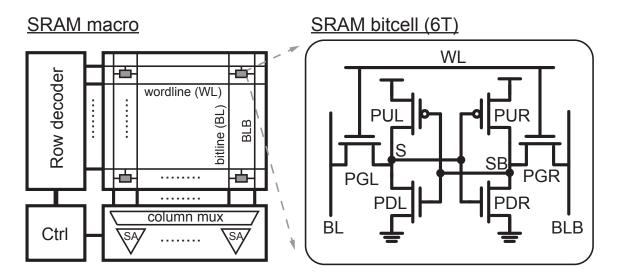

| 2.1  | Block diagram of an SRAM macro with an array, decoder, control logic, column multiplexer, and sense amplifiers. The bitcell is composed of six transistors | 12 |

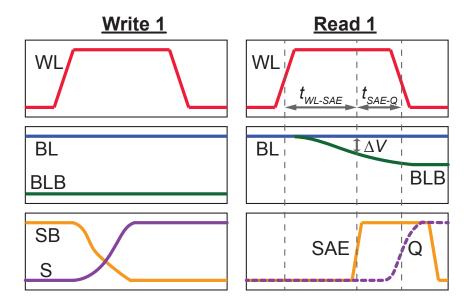

| 2.2  | Waveforms of SRAM read/write operation                                                                                                                     | 13 |

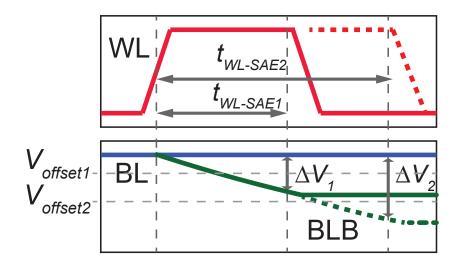

| 2.3  | A longer WL pulse and WL-SAE delay result in a larger $\Delta V$ for a more reliable                                                                       |    |

|      | sensing but degrade the read speed and power consumption                                                                                                   | 14 |

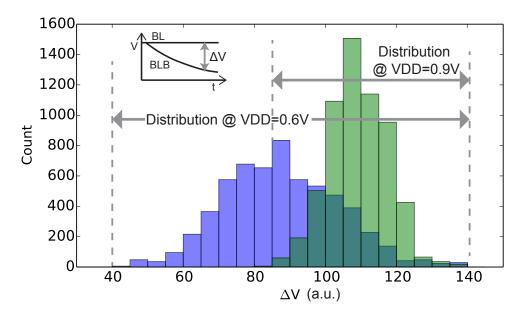

| 2.4  | Histogram of bitline swing ( $\Delta V$ ) at 0.9V and 0.6V                                                                                                 | 14 |

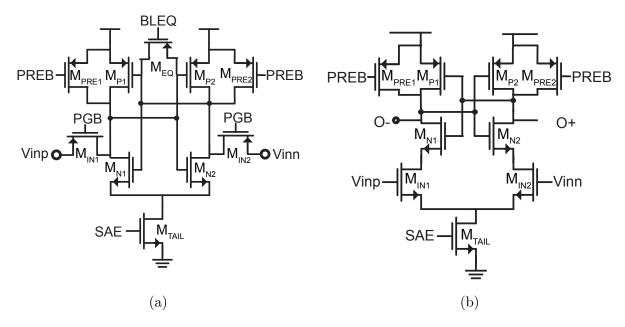

| 2.5  | The schematic of (a) a conventional SA and (b) a StrongArm SA                                                                                              | 16 |

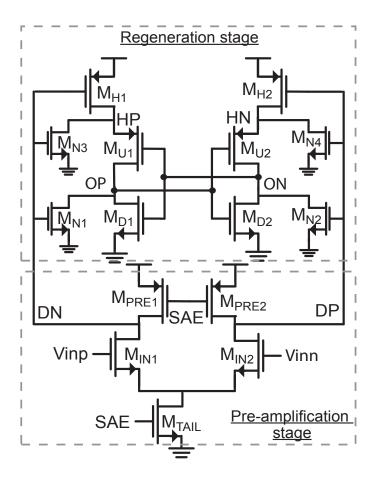

| 2.6  | Circuit diagrams of the double-tail sense amplifier, consisting of the preamplifi-                                                                         |    |

|      | cation stage and the regeneration stage                                                                                                                    | 17 |

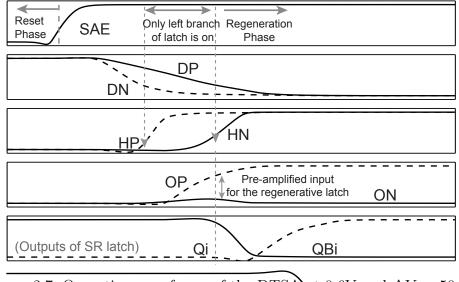

| 2.7  | Operation waveforms of the DTSA at 0.6V and $\Delta V = 50$ mV                                                                                             | 18 |

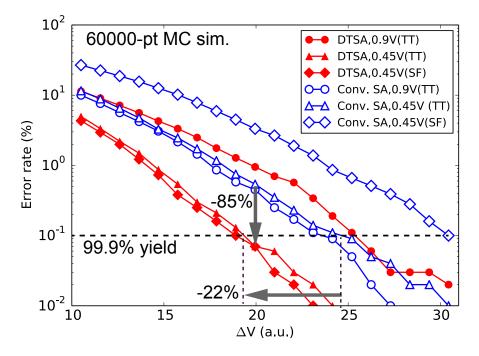

| 2.8  | Simulated error rate with various $\Delta V$ for the conventional SA and the DTSA                                                                          | 18 |

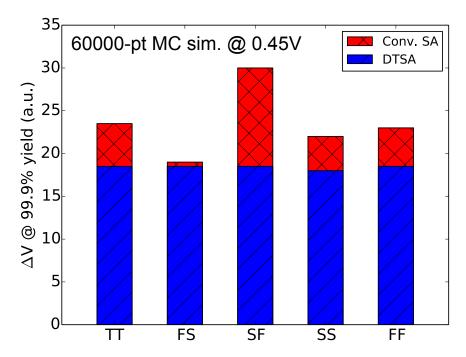

| 2.9  | Offset voltages at different process corners (VDD=0.45V)                                                                                                   | 19 |

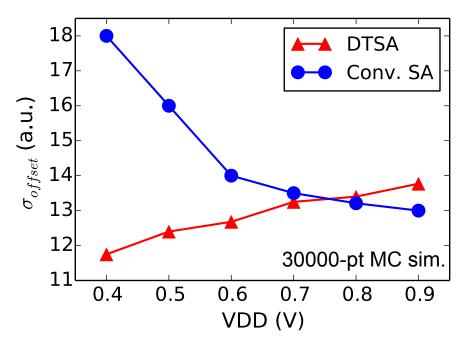

| 2.10 | The offset voltage of the conventional SA and the DTSA at different supply voltages.                                                                       | 20 |

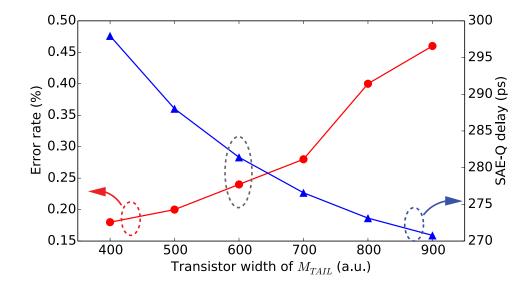

| 2.11 | Trade-off between error rate and SAE-Q delay for various sizings of $M_{TAIL}$                                                                             | 2  |

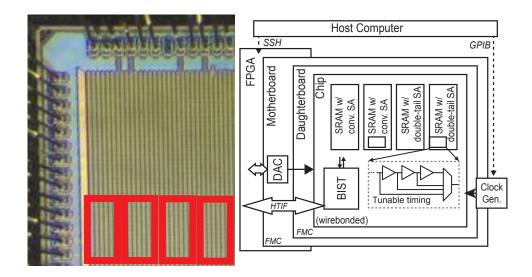

|      | Die photo and measurement setup                                                                                                                            | 21 |

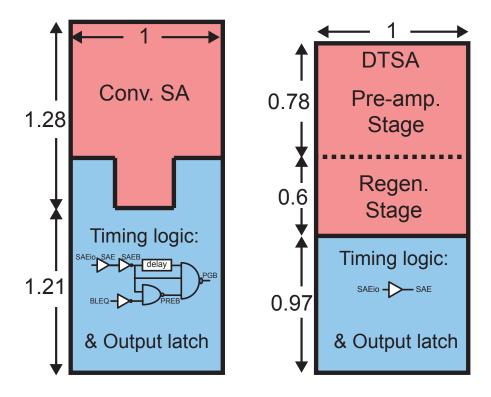

|      | Dimensions of the conventional SA and the DTSA (normalized to width)                                                                                       | 22 |

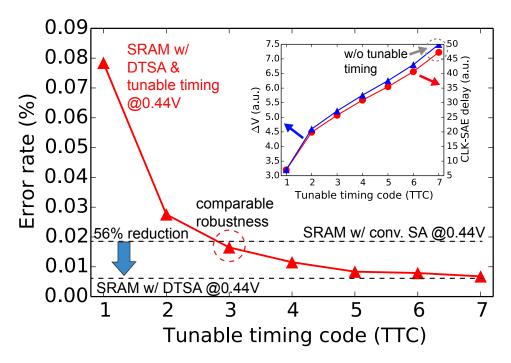

| 2.14 | Measured error rate for various tunable timing settings at 0.44V (averaged across                                                                          |    |

|      | 6 chips)                                                                                                                                                   | 23 |

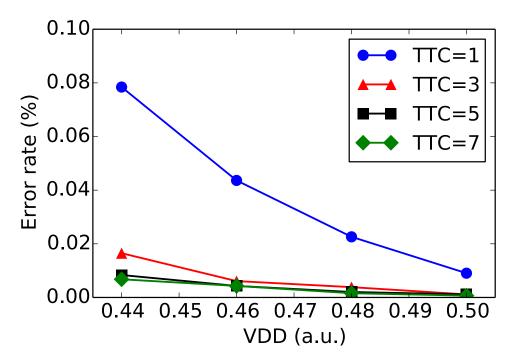

| 2.15 | Measured error rate at different VDD and tunable timing settings (averaged                                                                                 |    |

|      | across 6 chips)                                                                                                                                            | 24 |

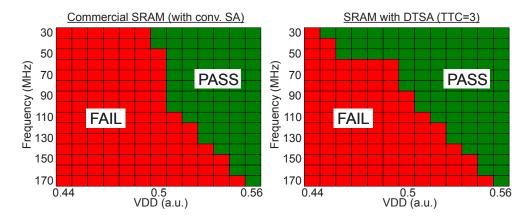

| 2.16 | Shmoo plots of the SRAM with the conventional SA and the DTSA                                                                                              | 2  |

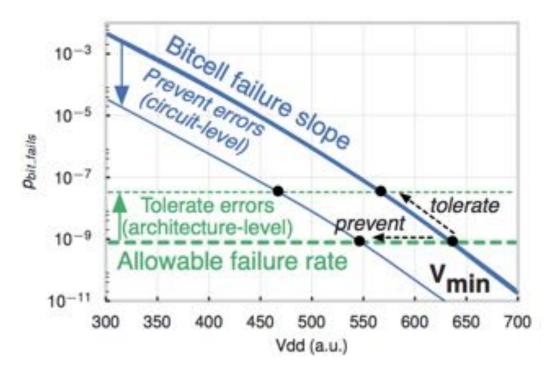

| 3.1  | Circuit-level techniques lower Vmin by improving bitcells while architecture-level                                                                         |    |

|      | techniques lower Vmin by tolerating bitcell failures. [1]                                                                                                  | 28 |

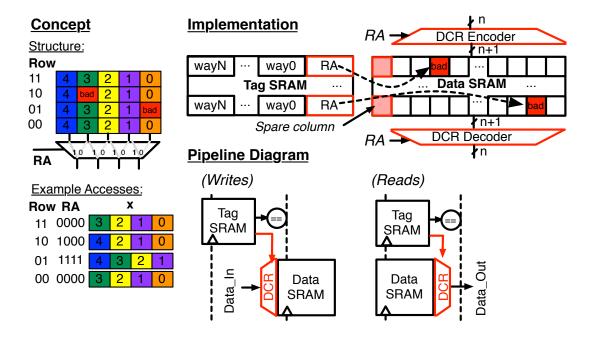

| 3.2         | Dynamic column redundancy exploits cache architectures to repair a single bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20         |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.2         | per set in cache data arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30         |

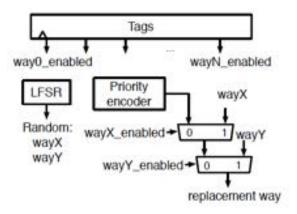

| 3.3         | Way replacement mechanism for the disabled way                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31         |

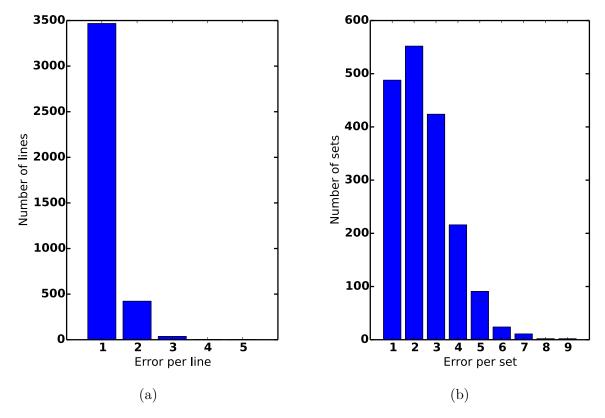

| 3.4         | The measured distribution of the number of errors in (a) a cache line and (b) a set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32         |

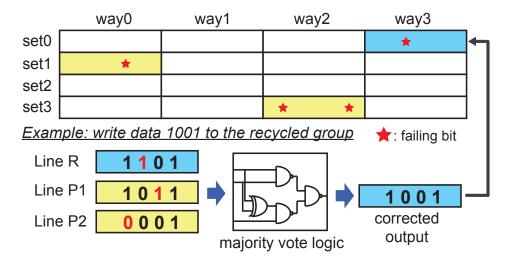

| 3.5         | The concept of line recycling: reusing two disabled cache lines to repair a third                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20         |

| 0.0         | one via majority vote.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33         |

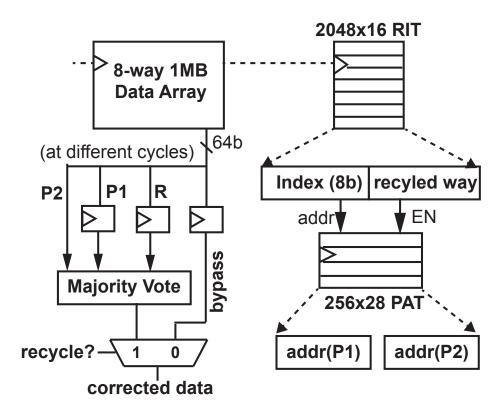

| 3.6         | Block diagram of the implementation of line recycling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34         |

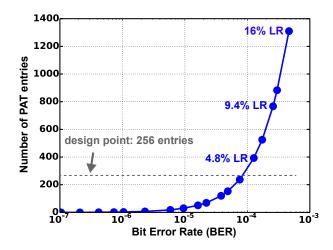

| 3.7         | The number of PAT entries required for different BER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35         |

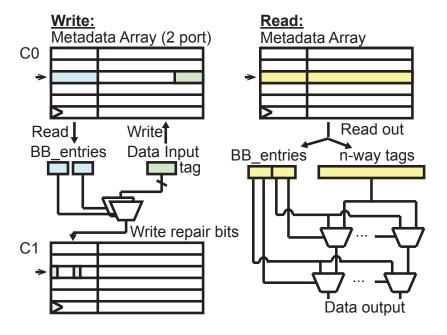

| 3.8         | Block diagram of Bit Bypass (BB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35         |

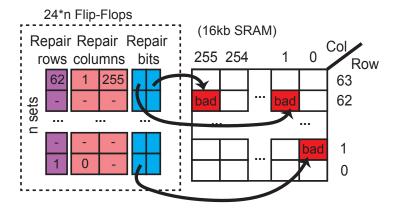

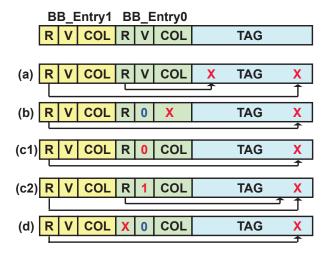

| 3.9<br>3.10 | Block diagram of Bit Bypass with SRAM implementation (BB-S) Four cases when the error bits are at different locations. (R: Repair bit, V: Valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36         |

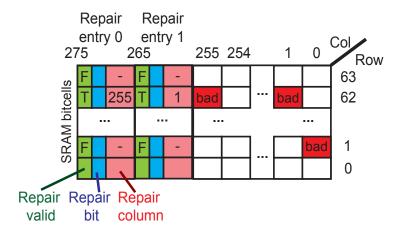

|             | bit, COL: Error column location)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37         |

| 3.11        | Block diagram of the implementation of BB-S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38         |

|             | Description of the notation used in the error model framework that translates bitcell failure rate to system yield                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39         |

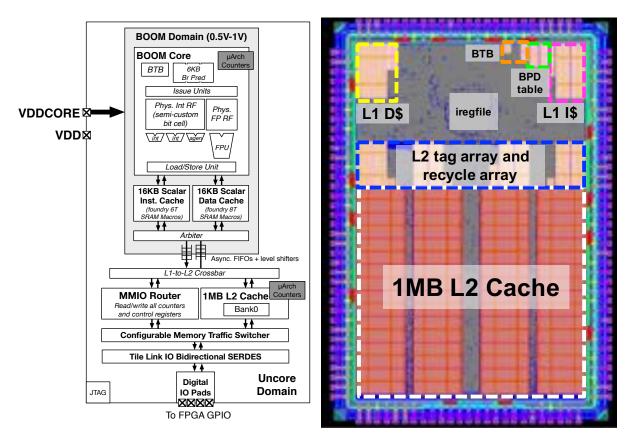

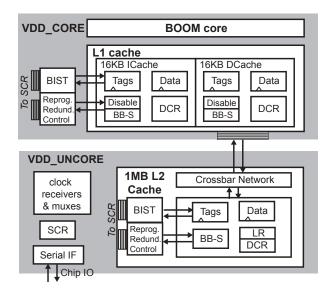

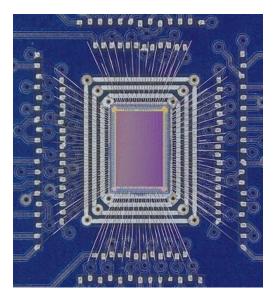

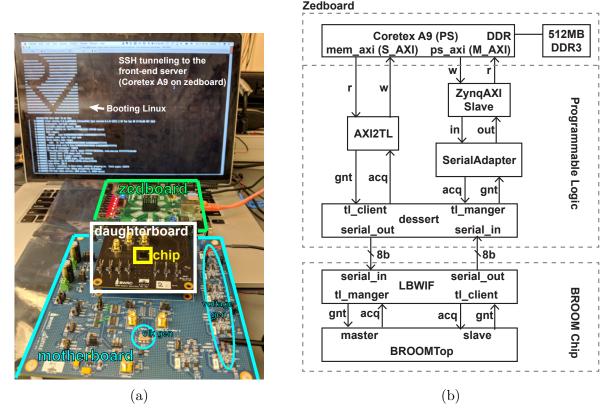

| 2 12        | Block diagram and layout of BROOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41         |

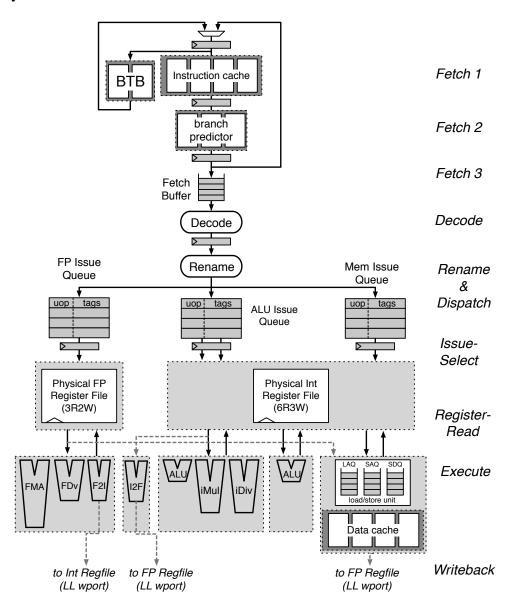

|             | The nine-stage pipeline BOOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42         |

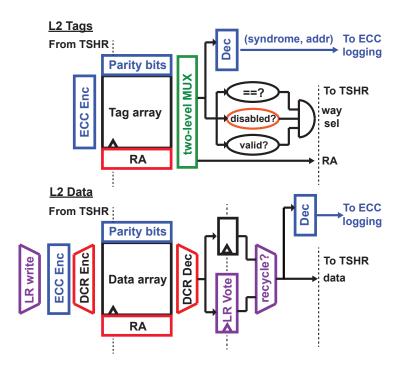

|             | Resiliency schemes implemented in BROOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43         |

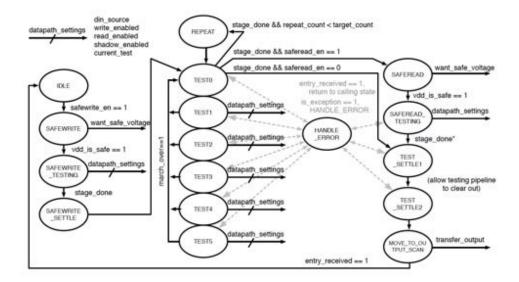

|             | The BIST control state machine allows a wide variety of programmable March                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40         |

| 5.10        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4        |

| 2 17        | tests. [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44         |

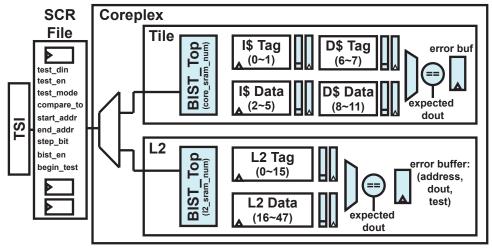

|             | Data path of the BIST in the memory system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45         |

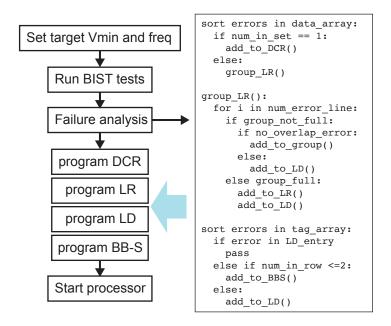

| 3.18        | Flow chart of reprogramming the resiliency techniques and the pseudo codes of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 <i>C</i> |

| 3.19        | the failure analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46         |

|             | LR overheads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47         |

| 11          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

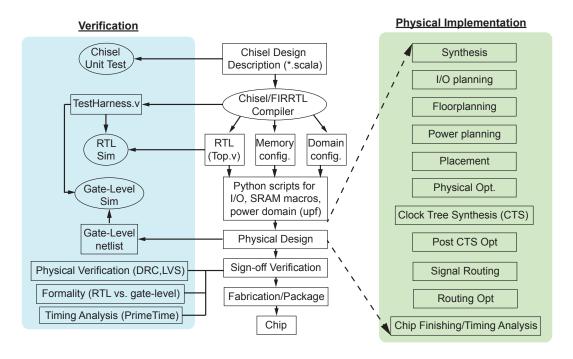

| 4.1         | The flow of chip implementation from Chisel to fabrication. Verification and physical design and both accountial to a graphical design and both accountial to a graphical design and the control of the c | 50         |

| 4.0         | ical design are both essential to a working chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50         |

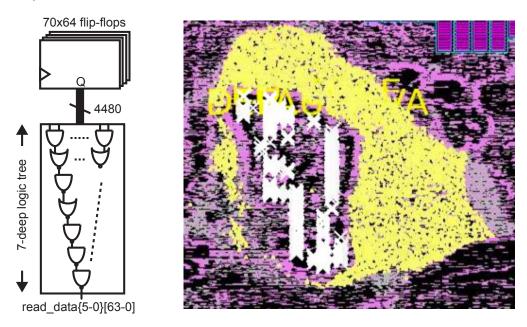

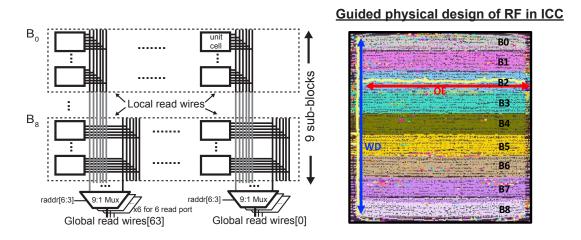

| 4.2         | The register file implemented with flip-flops is a bottleneck for routing, resulting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>5</b> 0 |

| 4.0         | in shorts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53         |

| 4.3         | The schematic of a full-custom cell for the register file and the implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

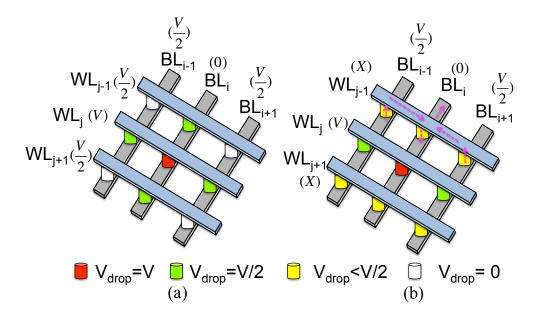

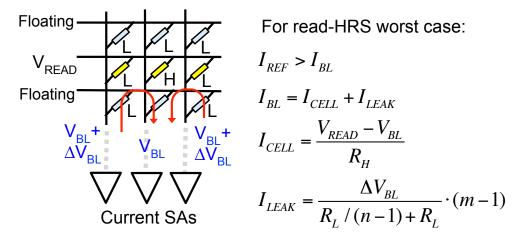

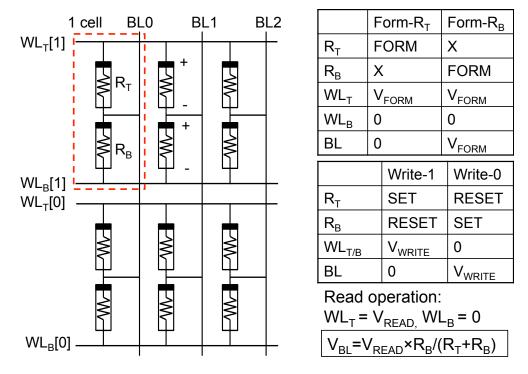

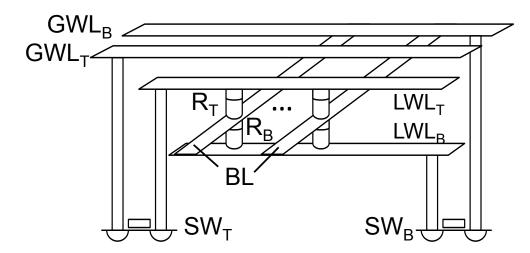

|             | with standard cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55         |